Lúcia Margarida da Mata Antunes Software Defined Radio em FPGA

#### Departamento de Universidade de Aveiro Electrónica, Telecomunicações e Informática 2009

Lúcia Margarida da Mata Antunes

# Software Defined Radio em FPGA

Dissertação apresentada à Universidade de Aveiro para cumprimento dos requisitos necessários à obtenção do grau de Mestre em Engenharia Electrónica e Telecomunicações, realizada sob a orientação científica do Doutor José Manuel Neto Vieira e do Doutor Arnaldo Silva Rodrigues de Oliveira, Professores do Departamento de Electrónica, Telecomunicações e Informática da Universidade de Aveiro

# o júri / the jury

| presidente / president       | <b>Professor Doutor Nuno Miguel Gonçalves Borges de Carvalho</b><br>Professor Associado da Universidade de Aveiro (por delegação da Reitora da Universidade de Aveiro) |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| vogais / examiners committee | <b>Professor Doutor José Carlos dos Santos Alves</b><br>Professor Associado da Faculdade de Engenharia da Universidade do Porto (Ar-<br>guente Principal)              |

|                              | <b>Professor Doutor José Manuel Neto Vieira</b><br>Professor Auxiliar da Universidade de Aveiro (Orientador)                                                           |

|                              | Professor Doutor Arnaldo Silva Rodrigues de Oliveira                                                                                                                   |

Professor Auxiliar Convidado da Universidade de Aveiro (Co-orientador)

# agradecimentos / acknowledgements

This dissertation would not have been possible without the help and support of so many people.

First of all, I would like to thank my coordinators for their help, guidance and sometimes patience during this last year.

Dr. Manuel Violas and *Instituto de Telecomunicações* for providing me the opportunity to develop my work in their facilities and with their XtremeDSP Development Kit-IV platform.

Daniel Albuquerque for having helped me to take the first step in the OFDM theory and implementation, as well as for having taught me how to work with latex.

My present and past roommates, but above all my friends! With them I passed a lot of memorable moments that I will never forget!

All my friends that I have met in the *University*, for their support on the good and bad times. Without them, these last years would not have been the best ever.

My friends from *Abrantes* for all weekends and summers that we spent together. Thank you for having been always ready for me, whether to have fun, to talk or just to relax.

And the most important: my Family! To have always supported me, listened me, encouraged me, helped me, advised me,..., but above all: loved me! *Obrigado por tudo! Sem vocês não teria sido possível chegar aqui!*

#### Resumo

Esta dissertação teve como objectivo o desenvolvimento de parte de um receptor para *Digital Audio Broadcasting* (DAB) recorrendo aos conceitos ditados por *Software Defined Radio* (SDR). O receptor de rádio inclui a conversão de digital para analógico e a subsequente desmodelação de bandabase, pelo que é possível aceder à *bit stream* em qualquer ponto do sistema.

A dissertação foi dividida em duas fases. Na primeira, o receptor completo foi simulado em MATLAB. Na segunda, o mesmo sistema foi implementado e testado numa placa *XtremeDSP Development Kit-IV*, a qual contém um *Field-Programmable Gate Array* (FPGA).

O sistema simulado foi testado com dois tipos de amostras. As primeiras consistiram em sinais DAB gerados em MATLAB e posteriormente distorcidos por diferentes canais também simulados pelo mesmo software. Foi assim possível fazer um estudo da probabilidade de erro quando o sinal é exposto a diferentes perturbações, como ruído, desvios na frequência e no tempo. O sistema foi ainda testado com amostras DAB reais. As constelações desmodelados mostraram o correcto funcionamento do sistema.

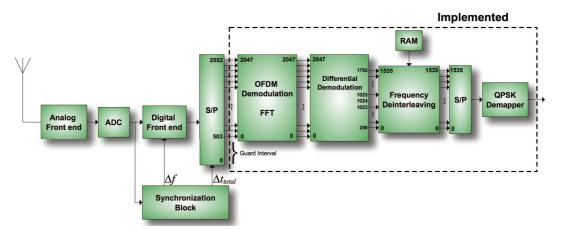

Apenas parte do receptor simulado foi implementado no FPGA. A parte já desenvolvida consiste nas funções de desmodelação: desmodelação OFDM, desmodelação diferencial, *frequency deinterleaving* e demapeamento QPSK. O sistema de sincronização DAB não foi implementado. O sistema já desenvolvido é assim capaz de desmodelar um sinal DAB gerado no MATLAB, desde que este não contenha qualquer distorção.

#### Abstract

The aim of this dissertation was the development of part of a *Digital Audio Broadcasting* (DAB) receiver by means of *Software Defined Radio* (SDR). This radio receiver includes the Intermediate Frequency (IF) to baseband conversion and the subsequent baseband demodulation, thus one may access the *bit stream* in any point of the system.

This dissertation was divided in two phases. In the first one, the whole DAB system was simulated in MATLAB. In the second, the receiver was implemented and tested in an *XtremeDSP Development Kit-IV* platform, which includes a *Field-Programmable Gate Array* (FPGA).

The simulated system was tested with two kinds of samples. The first ones were generated in MATLAB and subsequently distorted by different channel conditions also simulated in the same software. This well known DAB digital signal allowed us to perform a Bit Error Rate (BER) study with several channel conditions, such as noise, multipath, frequency and time offsets. Further on, real DAB samples were used for testing. The demodulated QPSK constellations showed the correct operation of the system.

Only part of the simulated receiver was implemented in the FPGA. This part consists in the channel demodulation functions: OFDM demodulation, differential demodulation, frequency deinterleaving and QPSK demapper. The DAB synchronization block was not implemented. The developed system is able to recover the modulated bit stream from the digital signal produced in MATLAB, since this signal is free of noise, frequency and time offsets.

# Contents

| C             | onter          | nts                                                      | i            |  |  |  |  |  |  |

|---------------|----------------|----------------------------------------------------------|--------------|--|--|--|--|--|--|

| $\mathbf{Li}$ | st of          | Figures                                                  | $\mathbf{v}$ |  |  |  |  |  |  |

| $\mathbf{Li}$ | st of          | Tables                                                   | ix           |  |  |  |  |  |  |

| A             | crony          | yms                                                      | xi           |  |  |  |  |  |  |

| 1             | Introduction   |                                                          |              |  |  |  |  |  |  |

|               | 1.1            | Overview                                                 | 1            |  |  |  |  |  |  |

|               | 1.2            | Objectives                                               | 1            |  |  |  |  |  |  |

|               | 1.3            | Contributions                                            | 2            |  |  |  |  |  |  |

|               | 1.4            | Outline                                                  | 3            |  |  |  |  |  |  |

| <b>2</b>      | Soft           | Software Defined Radio                                   |              |  |  |  |  |  |  |

|               | 2.1            | Introduction                                             | 5            |  |  |  |  |  |  |

|               | 2.2            | Software Defined Radio Configurations                    | 6            |  |  |  |  |  |  |

|               |                | 2.2.1 Baseband Digitalization                            | 7            |  |  |  |  |  |  |

|               |                | 2.2.2 IF Digitalization                                  | 7            |  |  |  |  |  |  |

|               |                | 2.2.3 RF Digitalization                                  | 8            |  |  |  |  |  |  |

|               | 2.3            | Key Components of Software Defined Radio                 | 8            |  |  |  |  |  |  |

|               |                | 2.3.1 Analog Front-Ends                                  | 9            |  |  |  |  |  |  |

|               |                | 2.3.2 Analog-to-Digital and Digital-to-Analog Converters | 11           |  |  |  |  |  |  |

|               |                | 2.3.3 Digital Signal Processing Circuits                 | 11           |  |  |  |  |  |  |

|               |                | 2.3.4 SDR Platforms                                      | 12           |  |  |  |  |  |  |

|               |                | 2.3.5 Cognitive Radio                                    | 13           |  |  |  |  |  |  |

| 3             | $\mathbf{Dig}$ | ital Audio Broadcasting                                  | 15           |  |  |  |  |  |  |

|               | 3.1            | Introduction                                             | 15           |  |  |  |  |  |  |

|               | 3.2            | The DAB System                                           | 16           |  |  |  |  |  |  |

|               | 3.3            | DAB Modes                                                | 16           |  |  |  |  |  |  |

|               | 3.4            | Transport Mechanisms                                     | 17           |  |  |  |  |  |  |

|               |                | 3.4.1 Main Service Channel                               | 18           |  |  |  |  |  |  |

|               |                | 3.4.2 Fast Information Channel                           | 20           |  |  |  |  |  |  |

|               |                | 3.4.3 Synchronization Channel                            | 20           |  |  |  |  |  |  |

|               | 3.5            | Physical layer                                           | 21           |  |  |  |  |  |  |

|               |                | 3.5.1 Transmission Frame                                 | 21           |  |  |  |  |  |  |

|              |     | 3.5.2   |                                                                                                                            | 22         |

|--------------|-----|---------|----------------------------------------------------------------------------------------------------------------------------|------------|

|              |     | 3.5.3   |                                                                                                                            | 22         |

|              |     | 3.5.4   | Differential Modulation                                                                                                    | 23         |

|              |     | 3.5.5   | OFDM Modulation                                                                                                            | 23         |

|              | 3.6 | Orthog  | gonal Frequency Division Multiplexing                                                                                      | 24         |

|              |     | 3.6.1   | OFDM as a Multicarrier Transmission                                                                                        | 24         |

|              |     | 3.6.2   | OFDM System Implementation                                                                                                 | 25         |

|              |     | 3.6.3   | · ·                                                                                                                        | 27         |

|              |     | 3.6.4   | -                                                                                                                          | 28         |

| 4            | Rec | eiver S | Simulation in MATLAB 3                                                                                                     | 1          |

| -            | 4.1 |         |                                                                                                                            | 31         |

|              | 4.2 |         |                                                                                                                            | 32         |

|              | 1.4 | 4.2.1   |                                                                                                                            | 32         |

|              |     | 4.2.2   |                                                                                                                            | 33         |

|              | 4.3 |         |                                                                                                                            | 33         |

|              | 4.0 | 0       |                                                                                                                            |            |

|              |     | 4.3.1   |                                                                                                                            | 34         |

|              |     | 4.3.2   |                                                                                                                            | 35         |

|              |     | 4.3.3   |                                                                                                                            | 36         |

|              |     | 4.3.4   | • • • • • •                                                                                                                | 36         |

|              | 4.4 | -       |                                                                                                                            | 37         |

|              |     | 4.4.1   |                                                                                                                            | 37         |

|              |     | 4.4.2   | 0                                                                                                                          | 38         |

|              | 4.5 | Result  | s5                                                                                                                         | 52         |

|              |     | 4.5.1   | DAB Transmitter                                                                                                            | 52         |

|              |     | 4.5.2   | Channel Simulation                                                                                                         | 54         |

|              |     | 4.5.3   | Multipath Propagation                                                                                                      | 52         |

|              |     | 4.5.4   | Real DAB Signal    6                                                                                                       | 64         |

| <b>5</b>     | Rec | eiver I | mplementation in FPGA Technology 6                                                                                         | 57         |

|              | 5.1 | Introd  | $uction \dots \dots$ | 37         |

|              | 5.2 |         |                                                                                                                            | <u>5</u> 9 |

|              |     |         |                                                                                                                            | 70         |

|              |     | 5.2.2   |                                                                                                                            | 73         |

|              |     | 5.2.3   |                                                                                                                            | 76         |

|              |     | 5.2.4   |                                                                                                                            | 77         |

|              | 5.3 |         | • • •                                                                                                                      | 78         |

|              | 0.0 | 5.3.1   |                                                                                                                            | 78         |

|              |     | 5.3.2   |                                                                                                                            | 31         |

|              |     | 0.0.2   | FIGA Resources                                                                                                             | , T        |

| 6            |     |         | ns and Future Work 8                                                                                                       |            |

|              | 6.1 |         |                                                                                                                            | 33         |

|              | 6.2 | Future  | e Work                                                                                                                     | 34         |

| $\mathbf{A}$ | DA  | B Emis  | ssion Block Diagram 8                                                                                                      | 5          |

| в            | MA  | TLAB    | Functions 8                                                                                                                | 57         |

# C DAB Objects

| D            | $\mathbf{X}\mathbf{tr}$ | eme DSP Development Kit-IV            | 93  |

|--------------|-------------------------|---------------------------------------|-----|

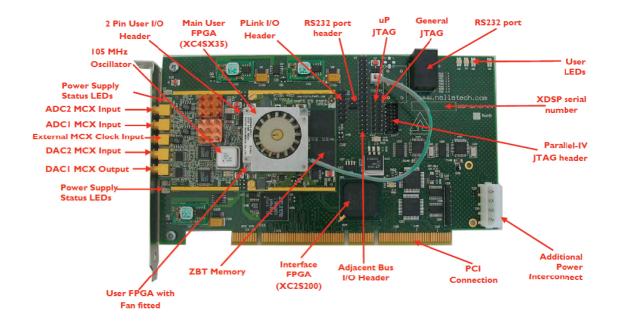

|              | D.1                     | Introduction                          | 93  |

|              | D.2                     | Key Features                          | 93  |

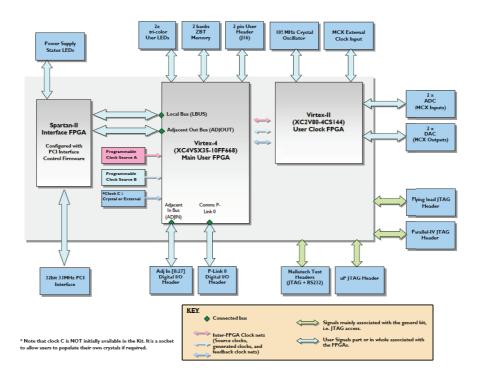

|              |                         | Functional Diagram                    |     |

|              | D.4                     | Nallatech and Xilinx Software Support | 95  |

| $\mathbf{E}$ | Xili                    | nx System Generator for DSP           | 97  |

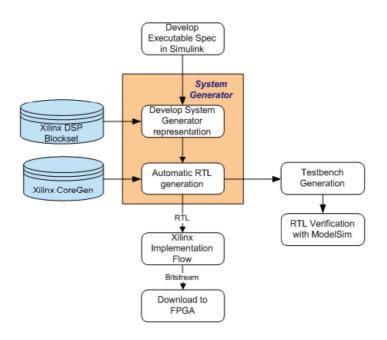

|              | E.1                     | Introduction                          | 97  |

|              | E.2                     | System Generator Design Flow          | 97  |

|              | E.3                     | Xilinx DSP Blockset                   |     |

|              |                         | E.3.1 Basic Blocks                    | 99  |

|              |                         | E.3.2 System Control Blocks           | 100 |

|              |                         | E.3.3 Memory Blocks                   | 100 |

|              |                         | E.3.4 Multirate System Blocks         | 101 |

|              |                         | E.3.5 Signal Processing Blocks        | 102 |

|              | E.4                     | Co-simulation                         |     |

# Bibliography

105

91

# List of Figures

| 0.1  |                                                                                                                                  |

|------|----------------------------------------------------------------------------------------------------------------------------------|

| 2.1  | The "ideal" SDR architecture. [Alb09]                                                                                            |

| 2.2  |                                                                                                                                  |

| 2.3  | IF digitalization architecture.                                                                                                  |

| 2.4  | RF digitalization architecture.                                                                                                  |

| 2.5  | Superheterodyne front-end architecture.                                                                                          |

| 2.6  | Superheterodyne front-end derivation architecture 10                                                                             |

| 2.7  | Homodyne front-end architecture                                                                                                  |

| 2.8  | Multiband front-end architecture                                                                                                 |

| 2.9  | Typical SDR signal chain                                                                                                         |

| 2.10 | Time evolution of the radio technology. $[Gue 07]$                                                                               |

| 3.1  | Conceptual block diagram of the DAB transmitter                                                                                  |

| 3.2  | Conceptual block diagram of the MSC encoder                                                                                      |

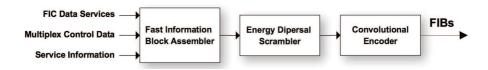

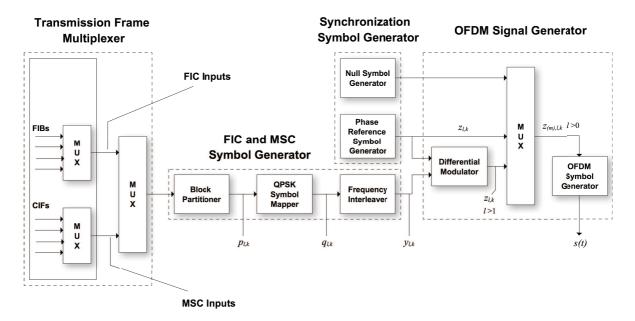

| 3.3  | Conceptual block diagram of the FIC encoder                                                                                      |

| 3.4  | Conceptual block diagram of the Physical Layer. [Eur06]                                                                          |

| 3.5  | DAB transmission frame structure                                                                                                 |

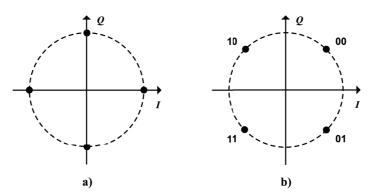

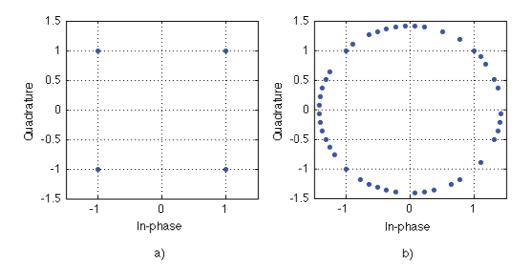

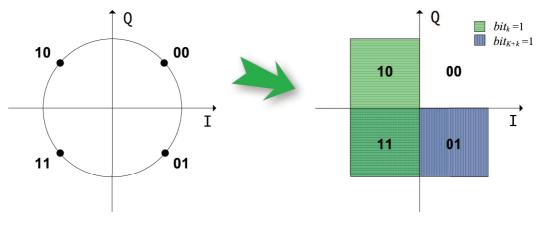

| 3.6  | QPSK constellations used by the PRS a) and the remaining symbols b) 22                                                           |

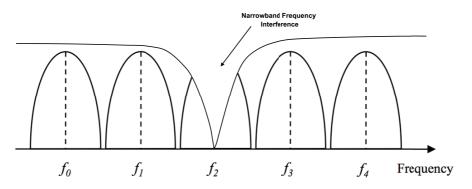

| 3.7  | Narrowband frequency interference effects in a FDM modulation system 2                                                           |

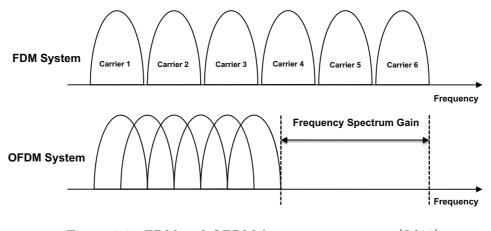

| 3.8  | FDM and OFDM frequency spectrums. [Sil08]                                                                                        |

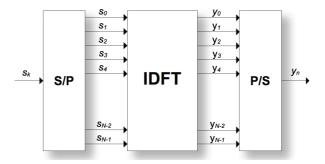

| 3.9  | Block diagram of an OFDM transmitter                                                                                             |

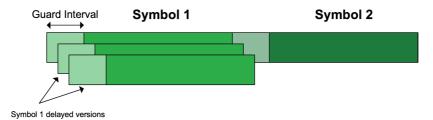

| 3.10 | Guard interval and its role in a multipath channel. [Sil08]                                                                      |

| 3.11 | QPSK symbols before OFDM modulation a) and after OFDM demodulation                                                               |

|      | with a time offset of one sample $b$ )                                                                                           |

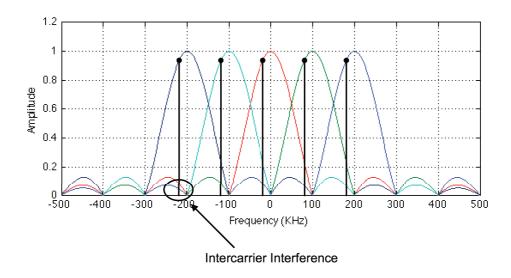

| 3.12 | Effect of a frequency offset in an OFDM demodulated signal                                                                       |

|      |                                                                                                                                  |

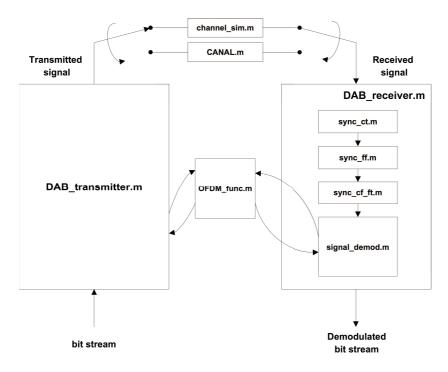

| 4.1  | General block diagram                                                                                                            |

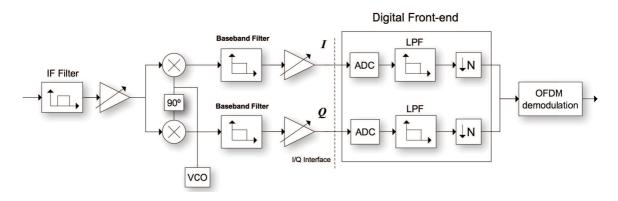

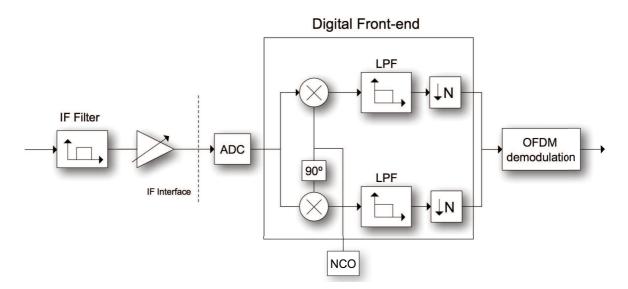

| 4.2  | Receiver architecture with an $I/Q$ interface. $\ldots \ldots 32$ |

| 4.3  | Receiver architecture with an IF interface                                                                                       |

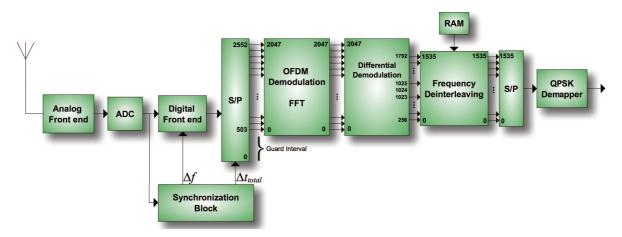

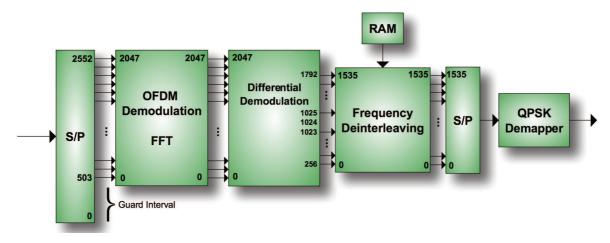

| 4.4  | Signal demodulation system block diagram                                                                                         |

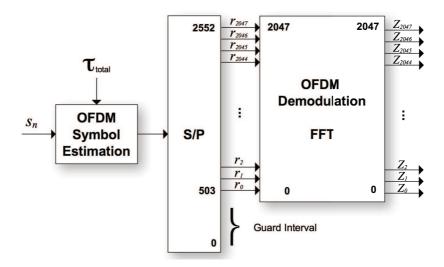

| 4.5  | OFDM demodulation block diagram                                                                                                  |

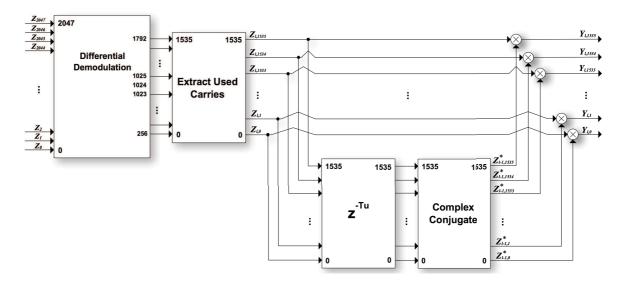

| 4.6  | Differential demodulation block diagram                                                                                          |

| 4.7  | QPSK symbol demapper illustration                                                                                                |

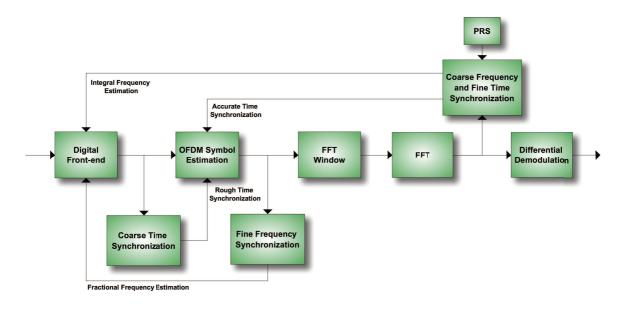

| 4.8  | Synchronization block diagram                                                                                                    |

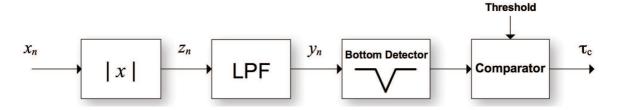

| 4.9  | Coarse time synchronization block diagram                                                                                        |

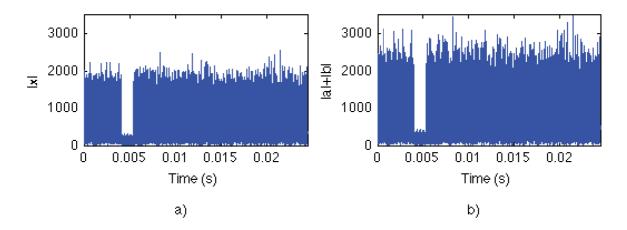

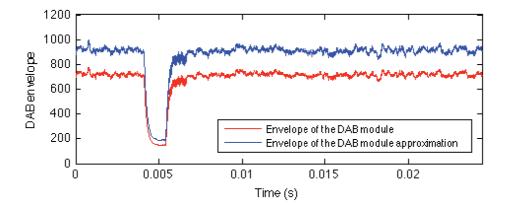

| 4.10 | Module of the DAB signal a) and its approximation b)                                                                             |

| 4.11 | Envelopes of the DAB signal module and its approximation                                                                         |

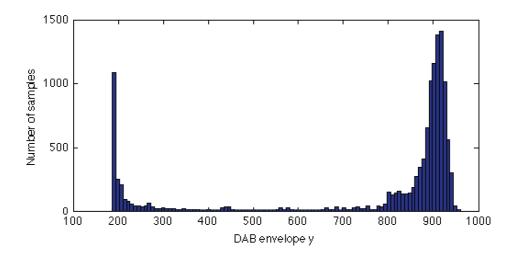

| DAB signal histogram                                                                                                                                                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

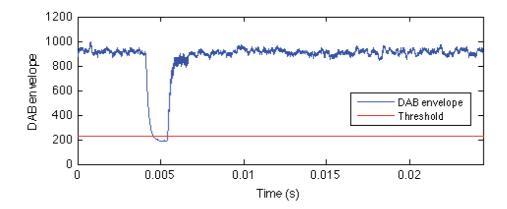

| Envelope of the DAB signal and coarse time synchronization threshold 4                                                                                                                 |

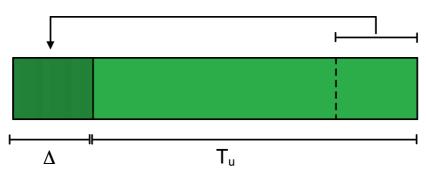

| DAB symbol and its cyclic prefix                                                                                                                                                       |

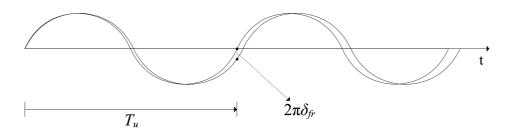

| Fractional frequency offset Illustration                                                                                                                                               |

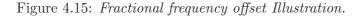

| Fine frequency synchronization block diagram.                                                                                                                                          |

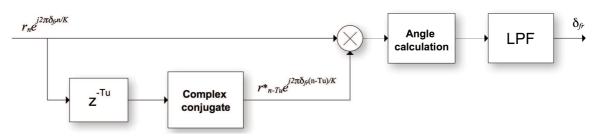

| Coarse frequency synchronization block diagram.                                                                                                                                        |

| Coarse frequency synchronization illustration.                                                                                                                                         |

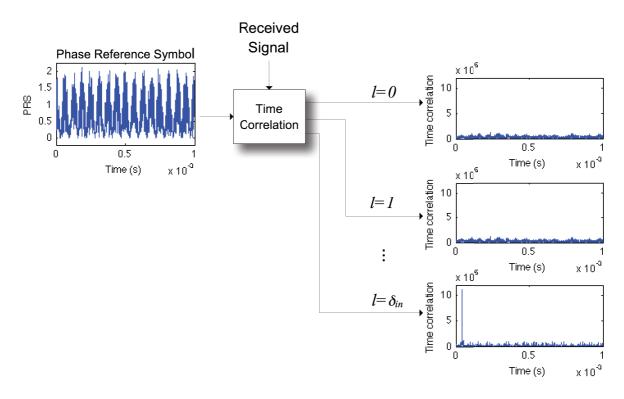

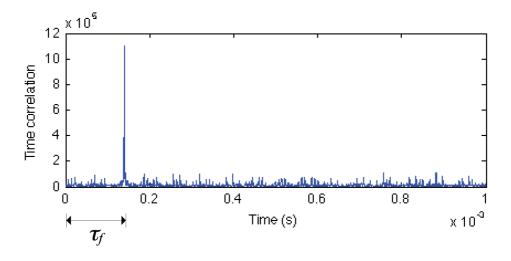

| Fine time synchronization illustration                                                                                                                                                 |

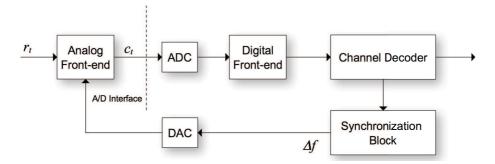

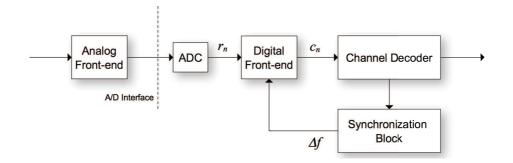

| Analog frequency correction                                                                                                                                                            |

| Digital frequency correction                                                                                                                                                           |

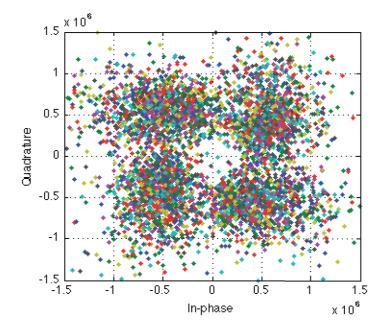

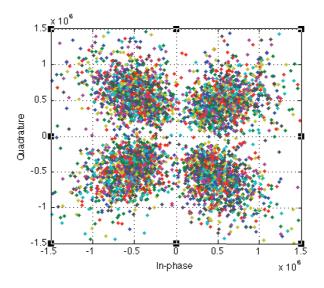

| QPSK symbols constellation of three OFDM symbols                                                                                                                                       |

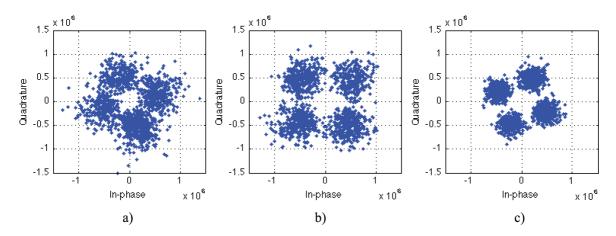

| QPSK symbols constellations of three different subcarriers: the 36th carrier a),                                                                                                       |

| the 768th carrier b) and the 1500th carrier c). $\ldots \ldots \ldots$ |

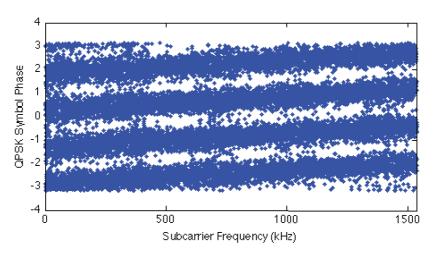

| QPSK symbol phase over the subcarrier frequency                                                                                                                                        |

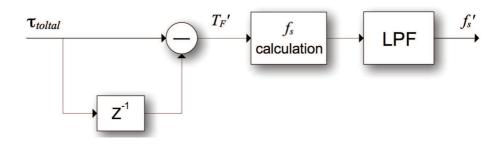

| Sampling frequency estimation block diagram                                                                                                                                            |

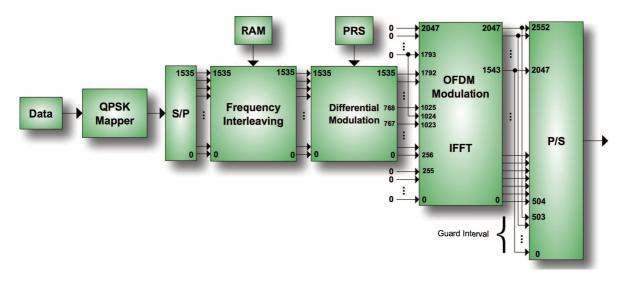

| DAB transmitter block diagram                                                                                                                                                          |

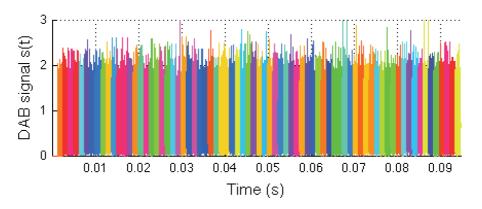

| DAB frame in the time domain                                                                                                                                                           |

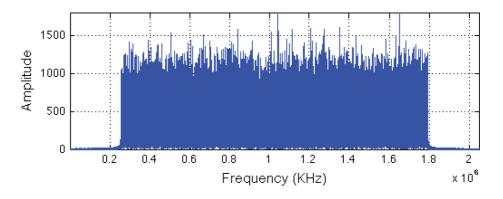

| DAB frame in the frequency domain                                                                                                                                                      |

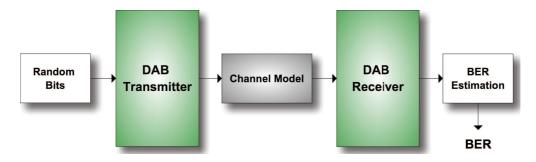

| Test bench block diagram                                                                                                                                                               |

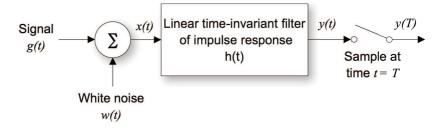

| <i>Receiver model.</i> [ <i>Hay00</i> ]                                                                                                                                                |

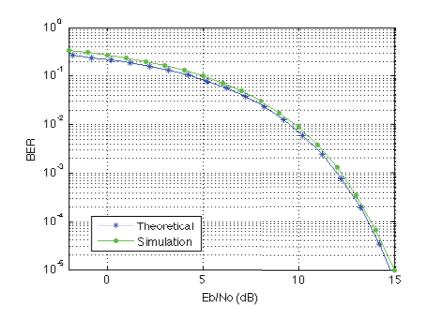

| BER performance in an AWGN channel (simulated with 1MB data per trans-                                                                                                                 |

| mission). $\ldots \ldots 5$                                                          |

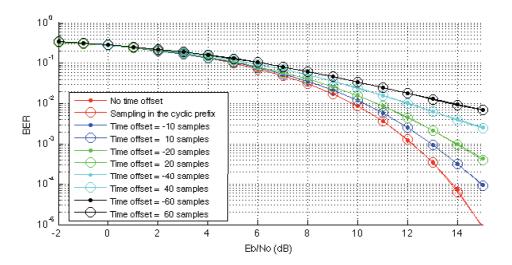

| BER versus time offset in an AWGN channel (simulated with 1MB data per                                                                                                                 |

| transmission)5                                                                                                                                                                         |

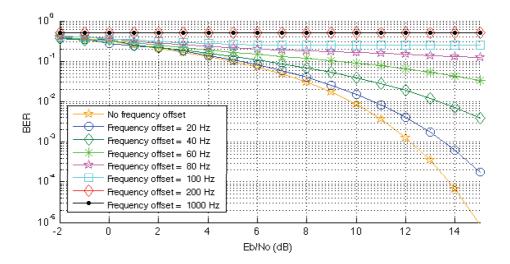

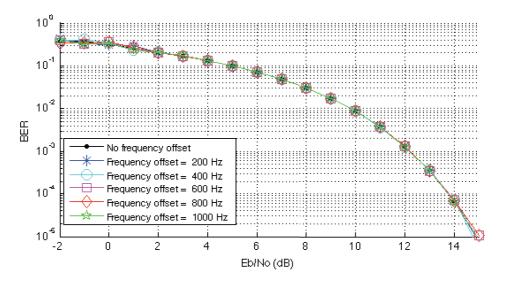

| BER versus carrier frequency offset in an AWGN channel (simulated with 1                                                                                                               |

| MB data per transmission)                                                                                                                                                              |

| BER performance with carrier frequency offset compensation in an AWGN                                                                                                                  |

| channel. (simulated with 1 MB data per transmission) 6                                                                                                                                 |

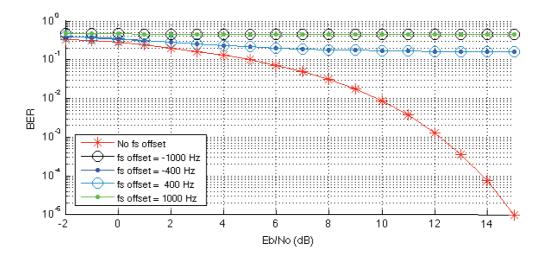

| BER versus sampling frequency offset in an AWGN channel (simulated with 1                                                                                                              |

| $MB \ data \ per \ transmission). \qquad \qquad$                |

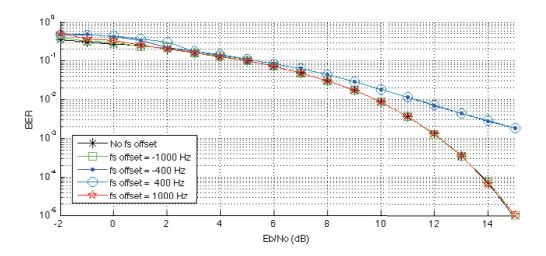

| BER performance with sampling frequency offset compensation in an AWGN                                                                                                                 |

| channel (simulated with 1 MB data per transmission)                                                                                                                                    |

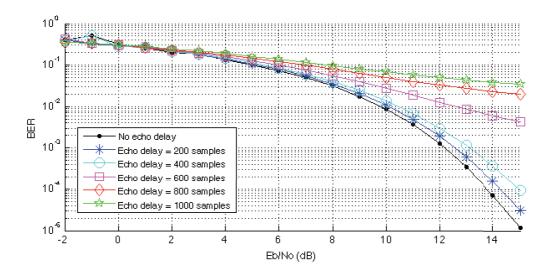

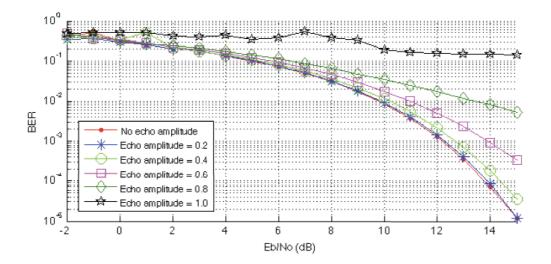

| BER versus echo delay in an AWGN channel (simulated with 1 MB data per                                                                                                                 |

| transmission)                                                                                                                                                                          |

| BER versus echo amplitude in an AWGN channel (simulated with 1 MB data                                                                                                                 |

| per transmission)                                                                                                                                                                      |

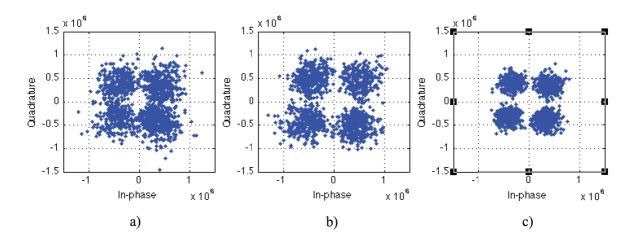

| QPSK symbols constellation of three OFDM symbols after sampling frequency                                                                                                              |

| correction                                                                                                                                                                             |

|                                                                                                                                                                                        |

| quency correction: the 36th carrier a), the 768th carrier b) and the 1500th                                                                                                            |

| $carrier c). \ldots \ldots$                                     |

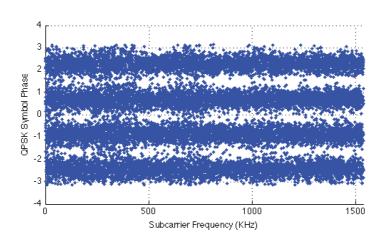

| QPSK symbol phase over the subcarrier frequency after sampling frequency                                                                                                               |

| <i>correction</i>                                                                                                                                                                      |

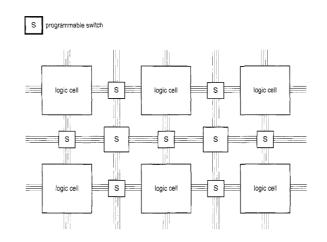

| Conceptual structure of an FPGA device [Chu08]                                                                                                                                         |

|                                                                                                                                                                                        |

| General block diagram.                                                                                                                                                                 |

|                                                                                                                                                                                        |

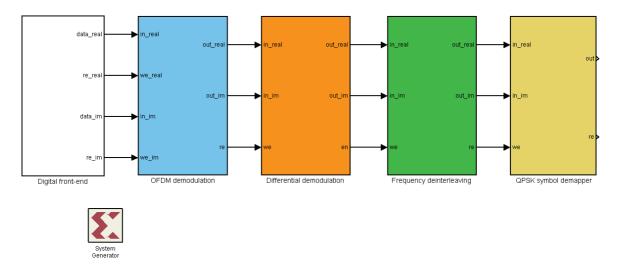

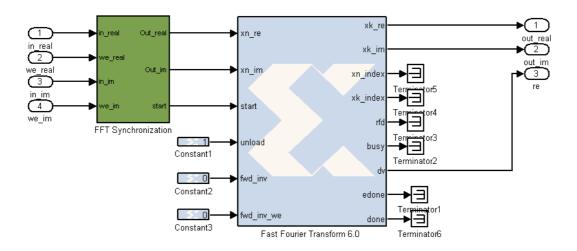

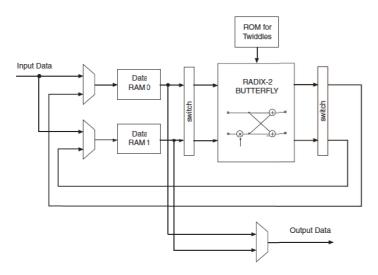

| 5.4  | OFDM demodulation subsystem in the System Generator                          | 70  |

|------|------------------------------------------------------------------------------|-----|

| 5.5  | Radix-2, Burst I/0 architecture [Xil08a]                                     | 71  |

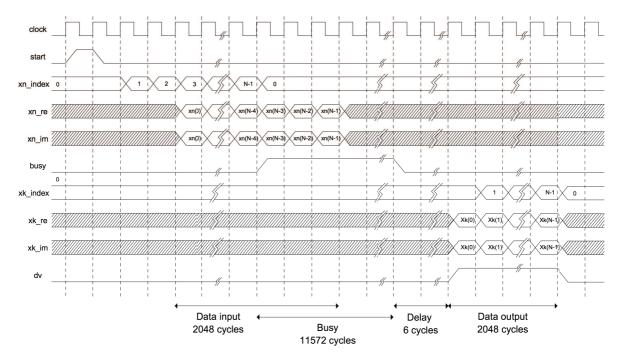

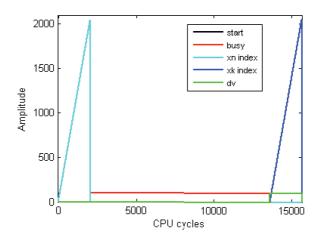

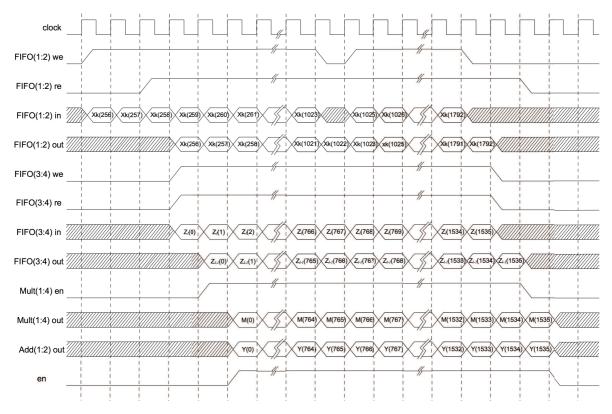

| 5.6  | Temporal behaviour of the FFT input and output signals                       | 72  |

| 5.7  | FFT block control signals.                                                   | 73  |

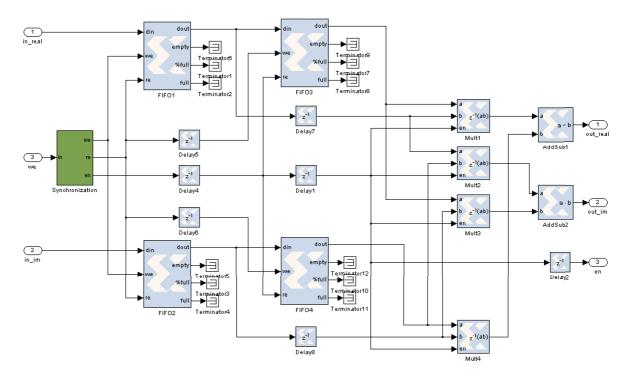

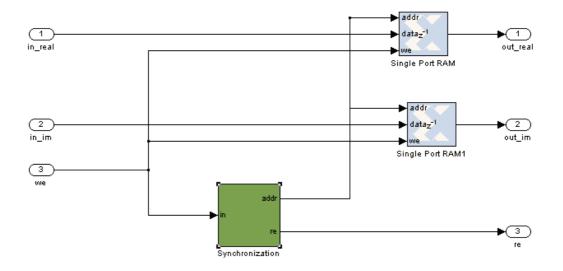

| 5.8  | Differential demodulation subsystem in the System Generator                  | 74  |

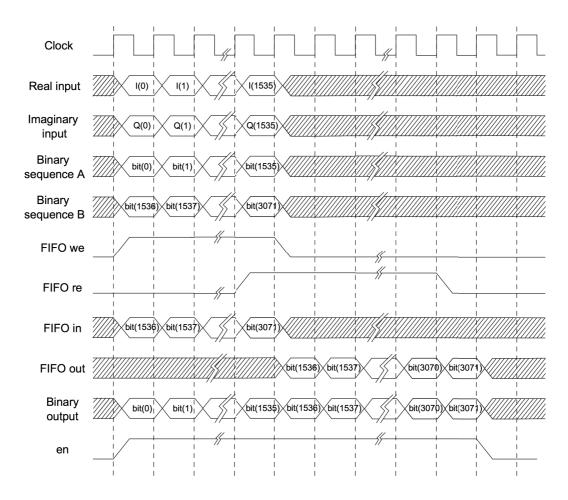

| 5.9  | Temporal behaviour of the differential demodulation subsystem signals        | 75  |

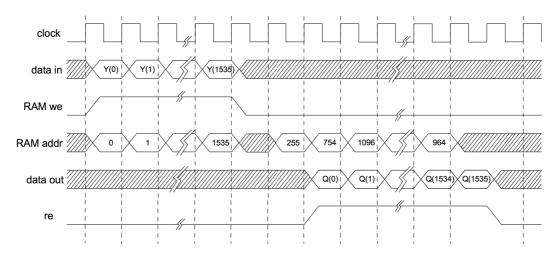

| 5.10 | Frequency deinterleaving subsystem in the System Generator.                  | 76  |

| 5.11 | Temporal behaviour of the frequency deinterleaving subsystem signals         | 76  |

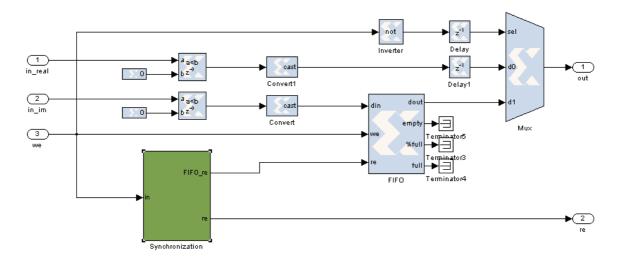

| 5.12 | QPSK symbol demapper subsystem in the System Generator.                      | 77  |

| 5.13 | Temporal behaviour of the QPSK symbol demapper subsystem signals             | 78  |

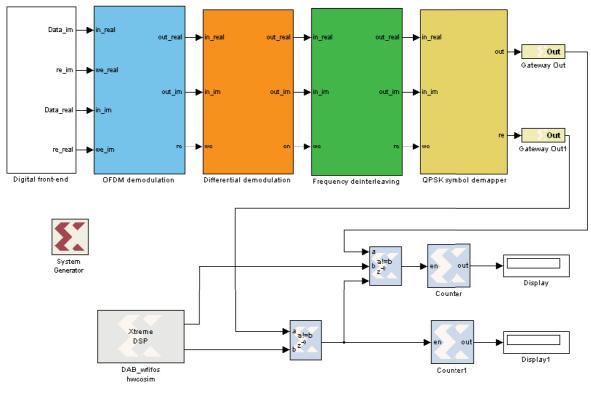

|      | Runtime block for DAB receiver co-simulation.                                | 79  |

|      | Co-simulation with a single-step clock.                                      | 80  |

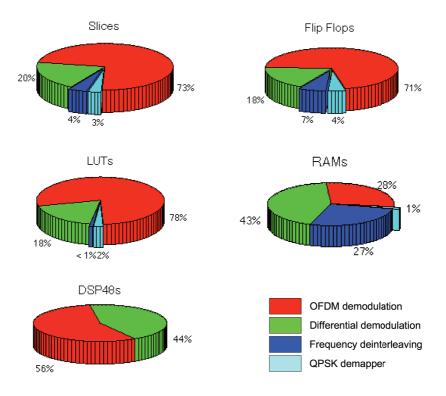

| 5.16 | Pie graphs of the several FPGA resources distribution among the DAB receiver |     |

|      | subsystems.                                                                  | 82  |

| A.1  | Conceptual DAB emission block diagram. [Eur06]                               | 85  |

| B.1  | Signal flow through the several MATLAB functions.                            | 87  |

| D.1  | XtremeDSP Development Kit-IV. [Nal07]                                        | 94  |

| D.2  | XtremeDSP Development Kit-IV functional diagram. [Nal07]                     | 95  |

| E.1  | System Generator design flow. [Xil08b]                                       | 98  |

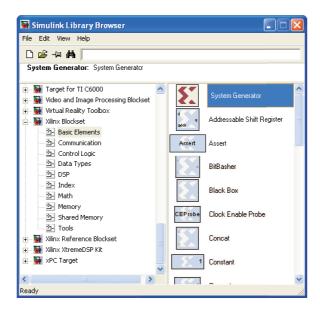

| E.2  | Simulink Library browser and Xilinx DSP blockset.                            | 98  |

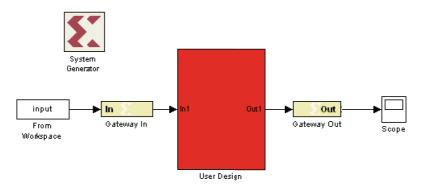

| E.3  | System Generator design example.                                             | 99  |

| E.4  | Property editor of the System Generator Token block.                         | 99  |

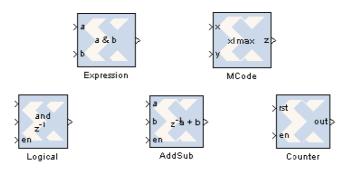

| E.5  | System Generator system control blocks.                                      | 100 |

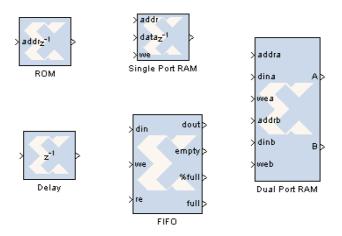

| E.6  | System Generator memory blocks.                                              | 101 |

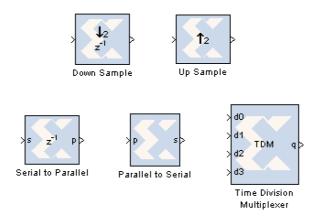

| E.7  | System Generator multirate system blocks.                                    | 101 |

| E.8  | System Generator signal processing blocks.                                   | 102 |

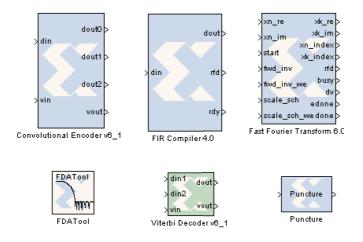

| E.9  | System Generator co-simulation library.                                      | 103 |

| E.10 | Property editor of the System Generator co-simulation block.                 | 104 |

|      |                                                                              |     |

# List of Tables

| 3.1 | DAB transmission signal parameters. [Eur06]                                                                                                   | 24         |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------|------------|

|     | Frame timing estimation results in an AWGN channel $(Eb/No = 8 \ dB)$<br>Frame 1 timing estimation results in several AWGN channel conditions | $58 \\ 59$ |

| 4.2 |                                                                                                                                               |            |

| 4.3 | Frequency estimation results in an AWGN channel $(Eb/No = 8  dB)$                                                                             | 60         |

| 4.4 | Frequency estimation results in several AWGN channel conditions for a carrier                                                                 |            |

|     | frequency offset of 1200 Hz                                                                                                                   | 60         |

| 5.1 | FPGA resources used by the DAB receiver.                                                                                                      | 81         |

| 5.2 | DAB receiver time behaviour and frequency constraints.                                                                                        | 82         |

# Acronyms

**ADC** Digital-to-Analog Converter.

$\mathbf{AGC}\,$  Automatic Gain Control.

${\bf AM}\,$  Amplitude Modulation.

**ASIC** Application-Specific Integrated Circuit.

**AWGN** Additive White Gaussian Noise.

${\bf BER}\,$  Bit Error Ratio.

**CA** Conditional Access.

**CIF** Common Interleaved Frame.

**CPU** Central Processing Unit.

**CRC** Cyclic Redundancy Check.

CU Capacity Unit.

**DAB** Digital Audio Broadcasting.

**DAB+** Digital Audio Broadcasting plus.

${\bf DAC}\,$  Analog-to-Digital Converter.

${\bf DFT}\,$  Discrete Fourier Transform.

${\bf DMB}\,$  Digital Multimedia Broadcasting.

**DQPSK** Differential Quadrature Phase-Shift Keying.

**DSP** Digital Signal Processor.

**DTV** Digital Television.

Eb/No Symbol Energy to Noise Ratio.

${\bf EEP}\,$  Equal Error Protection.

Es/No Symbol Energy to Noise Ratio.

${\bf ETSI}\,$  European Telecommunications Standards Institute.

FDM Frequency Division Multiplexing.

**FFT** Fast Fourier Transform.

FIB Fast Information Block.

FIC Fast Information Channel.

FIDC Fast Information Data Channel.

FIFO First-In/First-Out.

**FIR** Finite Impulse Response.

**FM** Frequency Modulation.

FPGA Field Programmable Gate Array.

**GPP** General Purpose Processor.

I In-phase.

I/O Input/Output.

**IC** Integrated Circuit.

**ICI** Intercarrier Interference.

**IDFT** Inverse Discrete Fourier Transform.

**IEEE** Institute of Electrical and Electronic Engineers.

**IF** Intermediate Frequency.

${\bf IFFT}$  Inverse Fast Fourier Transform.

**IIR** Infinite Impulse Response.

**ISI** Intersymbol Interference.

**ITU** International Telecommunication Union.

LFSR Linear Feedback Shift Register.

**LNA** Low Noise Amplifier.

${\bf LPF}\,$  Low Pass Filter.

**MCI** Multiplex Configuration Information.

$\mathbf{MMIC}\,$  Monolithic Microwave Integrated Circuit.

MP2 MPEG Audio Layer II.

${\bf MSC}\,$  Main Service Channel.

**NCO** Numerical Controlled Oscillator.

**OFDM** Orthogonal Frequency Division Multiplexing.

**P/S** Parallel/Serial.

**PRBS** Pseudo Random Binary Sequence.

**PRS** Phase Reference Symbol.

${\bf Q}\,$  Quadrature.

${\bf QPSK}\,$  Quadrature Phase-Shift Keying.

${\bf RAM}\,$  Random Access Memory.

${\bf RF}\,$  Radio Frequency.

${\bf ROM}\,$  Read Only Memory.

**RTP** Rádio e Televisão de Portugal.

**S/P** Serial/Parallel.

**SDR** Software Defined Radio.

**SI** Service Information.

${\bf SiGe} \ {\rm Silicon} \ {\rm Germanium}.$

**SNR** Signal to Noise Ratio.

${\bf SoC}$  System-on-Chip.

${\bf TII}\,$  Transmitter Identification Information.

**UEP** Unequal Error Protection.

$\mathbf{VCO}$  Voltage-Controlled Oscillator.

# Chapter 1

# Introduction

### 1.1 Overview

The concept of Software Defined Radio (SDR) has been acquiring a great deal of attention in the past several years. Created in 1991 by Joseph Mitola, it is "a radio whose channel modulation wave-forms are defined in software" [III00]. This will allow users to operate the radio in different environments and applications. This system is characterized by its flexibility and reconfigurability, since changing its behaviour only requires modifying or replacing the software [CLA<sup>+</sup>09]. Due to actual technology progress limits, the ideal concept is not completely achievable since it is still necessary an analog front-end to downconvert the Radio Frequency (RF) signal to an Intermediate Frequency (IF). The resulting signal can be sampled by an Digital-to-Analog Converter (ADC) and finally be fully processed using digital techniques.

Since our major goal is to study the SDR concept and its implementation related problems, we have decided to develop a receiver for the radio transmission standard *Digital Audio Broadcasting (DAB)* using that concept.

DAB is a digital radio transmission standard developed by the European Project Eureka 147. Unlike the traditional Frequency Modulation (FM) radio, DAB permits to tune up to 10 radio stations within the same frequency and in any place of the country. Some of the DAB advantages include easy program selection, improved reception, program-associated data, information services and the most important "one receiver does it all". Orthogonal Frequency Division Multiplexing (OFDM) is one of the main features of this system. It divides a high data rate stream in K parallel lower data rate streams, which will modulate K different subcarriers. Hence, the symbol duration will be increased by a factor of K and the system will be more robust against multipath and noise. DAB has already regular services in 30 countries, more than 990 DAB receivers are commercially available and more than 12 million have already been sold all around the world. DAB is seen as the future of the radio!

### 1.2 Objectives

The objective of this dissertation was to develop part of a DAB receiver by means of SDR using an XtremeDSP Development Kit-IV, which includes a *Field Programmable Gate Array (FPGA)*. The receiver should comprise the physical layer related functions, i.e., the downconversion from RF to IF, the time and frequency synchronization mechanisms and the baseband signal demodulation functions.

The receiver development was thought to be done in two parts. In the first one, the whole DAB system might be simulated in MATLAB. In the second, the receiver should be implemented and tested in the FPGA. The final system shall be able to recover the modulated bit stream from the digital signal produced in MATLAB.

## **1.3** Contributions

The complete physical layer of a DAB receiver was simulated in MATLAB. The final system is able to synchronize and subsequently demodulate a real DAB baseband signal. The synchronization block performs frame time synchronization, as well as estimates and corrects possible carrier or sampling frequency offsets. The remaining system demodulates the DAB signal in order to recover the original bit stream. The following demodulation functions are performed: OFDM demodulation, differential demodulation, frequency deinterleaving and Quadrature Phase-Shift Keying (QPSK) demapper.

The signal demodulation functions of the DAB receiver were also implemented in an FPGA using the Xilinx System Generator tool. The developed system is able to recover the modulated bit stream from the digital signal produced in MATLAB, since this signal is free of noise, frequency and time offsets.

To my contributions I would like to add the very helpful contribution of others to my work.

Thus, I will start with Andreas Muller. While searching on the Internet, I found his semester thesis dissertation called "DAB Software Receiver Implementation" [Mul08]. Its main goal was to develop a complete real-time software receiver for DAB using GNU Radio, an open-source toolbox to learn about, build and develop SDR systems. After contacting him, he kindly provided me several real DAB samples and the contact of Nicolas Alt, who has implemented a complete DAB receiver in MATLAB. Moreover, Andreas' semester thesis [Mul08] provided a lot of helpful information.

Nicolas Alt has also gently shared his receiver with me, as well as some DAB samples. Although none of the code and used techniques of his receiver implementation were used in this dissertation, they were an essential starting point to my DAB synchronization implementation. On the other hand, his DAB samples were intensively used through this dissertation. Furthermore, having a working software model and "known to work samples" was very useful to verify each step of my implementation. Additionally, the idea of using the distance between two Null symbols to estimate the sampling frequency was adopted from Nicolas' code.

The OFDM knowledge of Daniel Albuquerque was also fundamental for developing this master thesis dissertation. He kindly discussed with me some important DAB implementation issues and provided several MATLAB functions, such as OFDM implementation examples and a channel simulator. These were intensively used in this dissertation's MATLAB implementation.

Paulo Ferreira, who is responsible for the DAB ensemble in Rádio e Televisão de Portugal (RTP), has also provided me very useful information about this digital radio transmission in Portugal.

Finally, Afonso Silva has also nicely given me his Xilinx WebCase access and Xilinx System Generator projects [Sil08]. Although the former one was not very helpful, the later ones were a very good starting point for my FPGA receiver implementation. My co-coordinator kindly helped me with the first problem.

# 1.4 Outline

The dissertation is organized through five chapters.

- Introduction presents the project idea, objectives and contributions.

- **Software Defined Radio** explains the concept of SDR, its related problems and possible architectures.

- **Digital Audio Broadcasting** gives an overview of the DAB standard, its features and transmitter architecture, as well as explains the OFDM modulation technique and its main concerns.

- **Receiver Simulation in MATLAB** provides a detailed explanation of the DAB receiver, its MATLAB implementation and achieved results.

- **Receiver Implementation in FPGA Technology** describes the implementation of the same DAB receiver in the XtremeDSP Kit-IV development platform and presents the achieved results.

- **Conclusions and Future Work** reviews the dissertation, draws some conclusions and, finally, explains what can still be done in a future work.

# Chapter 2

# Software Defined Radio

## 2.1 Introduction

During the last two decades, the fast advances in the semiconductor field made possible the emergence of a new concept called *Software Defined Radio* (SDR). SDR was first introduced by Joseph Mitola in 1991, which he described as:

"A software radio is a radio whose channel modulation waveforms are defined in software. That is, waveforms are generated as sampled digital signals, converted from digital to analog via a wideband Analog-to-Digital Converter (DAC) and then possibly upconverted from IF to RF. The receiver, similarly, employs a wideband ADC that captures all of the channels of the software radio node. The receiver then extracts, downconverts and demodulates the channel waveform using software on a general purpose processor." [Mit95]

Basically, SDR is a radio that uses as much digital technology as possible. Typical components that were usually implemented using analog hardware, such as amplifiers, filters, mixers, modulators/demodulators and detectors (among others), are now implemented using software in a Digital Signal Processor (DSP). This system is characterized by its flexibility and adaptability, due to the fact that changing its behavior only requires modifying or replacing the software.

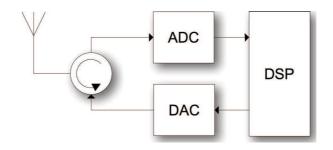

A typical radio transmitter or receiver has a dedicated analog circuit for filtering, tuning and modulating/demodulating. If one needs to use two or more standards, the radio would need a dedicated circuit for each of these. As one can imagine it would not be feasible in terms of size, power consumption and cooler system. SDR can be the solution for this problem, since a single radio can support different standards just by changing the transmission/reception software on the system without the need of dedicated circuits. Ideally, the receiver samples the signal just after the antenna and the remaining radio signal processing would be done by a DSP, as represented in Figure 2.1. This "ideal" SDR would be able to demodulate a signal with any carrier frequency (carrier flexibility), bandwidth (wideband) and kind of modulation (modulation flexibility). As will be explained in the next subsections, the state of the art in what concerns both analog and digital domains does not allow this simplified version of a SDR. In order to overcome this problem, several solutions have been proposed to get partial solutions to the SDR concept.

One early implementation of SDR systems was the United States military project called

Figure 2.1: The "ideal" SDR architecture. [Alb09]

SpeakEASY that was started in 1991. SpeakEasy handled different modulations techniques and frequencies to make possible to communicate with more than 10 different types of military radio standards. SpeakEASY allowed digital frequency conversion and wideband signal processing, and showed that modular radio components, such as analog front-ends, DACs, ADCs and DSPs, can be combined in an open architecture bus. This open-architecture approach is able to increase production volume and reduce costs [Mor00]. Since then we have witnessed an explosion of interest in SDR, which is currently being developed for both communication and broadcasting applications, such as second-generation cellular phones, third generation CDMA cellular phones, the Digital Televisions (DTVs) and DAB.

SDR is seen as the future of the wireless communications. Since it will use public radio wave spectrum, it is highly necessary to create standards and rules about SDRs specifications. A group called SDR Forum, working in collaboration with the Institute of Electrical and Electronic Engineers (IEEE), has worked to establish the definition of SDR that will provide consistency and a clear overview of the technology and its associated benefits [For09a].

## 2.2 Software Defined Radio Configurations

One of the main steps of a SDR system is digitalization, which is the process of converting an analog signal into a digital sequence. This process is done in accordance with the sampling theorem, which states:

"If the highest frequency contained in an anolog signal  $x_a(t)$  is  $F_{max} = B$  and the signal is sampled at a rate  $F_s > 2F_{max} \equiv 2B$ , then  $x_a(t)$  can be exactly recovered from its sample values." [PM06]

The sampling rate  $F_N = 2F_{max}$  is called the Nyquist rate.

Ideally, the digitization would take place right after the antenna, since it allows processing the signal fully in software. However, this SDR configuration is currently impracticable due to the state-of-the-art of ADCs and DACs and the limitations on computational capacity of contemporary processors. In order to overcome this problem, several solutions have been proposed to get partial solutions to the SDR paradigm. These have increased the flexibility of the radios and many of them are already in use.

Considering the frequency in which the digitalization takes place, three different types of SDR configurations can be defined: Baseband digitalization, IF digitalization and RF digitalization. The following subsections will take a quick look at each of these configurations. For better readability, only the receiver side is discussed. The transmitter side is based on the same configuration, but in the reverse order.

#### 2.2.1 Baseband Digitalization

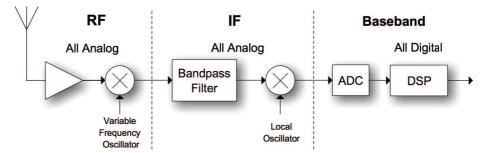

Digitization at baseband level is the most common used in nowadays radios. The simplified baseband radio configuration is illustrated in Figure 2.2.

Figure 2.2: Baseband digitalization architecture.

The analog front-end downconverts the RF signal to an IF and, subsequently, to the baseband. Thus, the analog front-end will have at least one stage for each band frequency transition. Following the chain, the signal will be sampled at the ADC and the remaining radio functions will be implemented in a programmable processing technology. Thus, the signal modulation, channel and source decoding functions will be completely performed through digital means.

This SDR configuration should not be confused with a common analog radio that also samples the signal at the baseband. In that case, the *bitream* is directly extracted from the analog signal and fed into subsequent digital stages to profit from digital signal processing techniques such as music equalization. This is a common practice in widely used devices such as stereo music equipment. Since none of the demodulation functions is carried out in software, these radios are not considered to be a SDR [Man07].

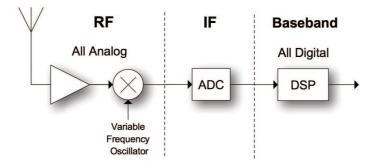

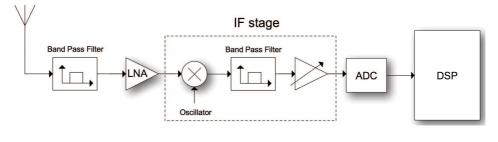

#### 2.2.2 IF Digitalization

Thanks to recent advancement of semiconductor technology, the SDR has being moved toward the antenna. Thus, the most emergent architecture implemented in SDRs is the IF digitization. This architecture is depicted in Figure 2.3 and consists of an antenna, an analog front-end, an IF stage and software to perform all the baseband computation.

The analog front-end will downconvert the RF signal to a frequency which can be processed by the ADC. It is comprised by, among others, a Low Noise Amplifier (LNA), a filter and a mixer. Following the chain, the signal will be sampled at the ADC and the remaining radio functions will be implemented through reconfigurable software operating on programmable processing technologies. These devices include DSPs, FPGAs, General Purpose Processors (GPPs), System-on-Chip (SoC) or other application specific programmable processors [For09a].

Since part of the frequency translation process takes place in the digital domain, the number of received channels can be much bigger than in the previous architecture, making this architecture more flexible and, therefore, desirable.

Figure 2.3: IF digitalization architecture.

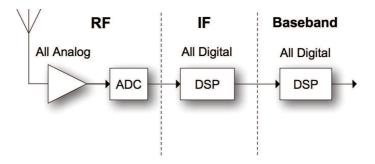

#### 2.2.3 RF Digitalization

As already mentioned, an "ideal" SDR system would sample the RF signal directly from the wideband antenna. The remaining signal processing would be done by digital means, including the band pass filtering, automatic gain control, frequency translation, low-pass filtering, and demodulation of the desired signal [Mor00]. The simplified block diagram of this configuration can be seen in Figure 2.4. With this configuration, the radio system would be

Figure 2.4: RF digitalization architecture.

able to process the whole spectrum and support any standard just by changing its software. Although this configuration is the most desirable, the actual ADCs and DACs capacities make it unfeasible. Nevertheless, significant research efforts are being taken to surmount this problem.

The several configurations standardized by SDR Forum can be found in [Gro02].

## 2.3 Key Components of Software Defined Radio

While the concept of SDR is not new, there are several factors that have enabled its large development over the last few years. First, the emerging standards require a lower dynamic range than some of earlier standards because of coding and processing gain. This made possible some "relaxations" in terms of overall performance. Second, and more important is the continued and rapid advancement of semiconductor processes and systems [BB08]. The end result is the availability of key components that enable SDR technology, which provides a flexible, robust and less expensive solution when compared with traditional analog radios.

#### 2.3.1 Analog Front-Ends

The analog front-end is one of the most critical parts of the radio system. It has a main role in the overall system performance, power consumption and size, and it is where the receiver can, within limits, be designed for the best Signal to Noise Ratio (SNR) [Bow08].

Thanks to recent advances of semiconductor technology, it is now possible to incorporate most if not all of the analog radio functions such as filters, amplifiers and mixers, in a single chip. Monolithic Microwave Integrated Circuit (MMIC) is the technology used for integrating RF components in one chip [BB08]. It is a type of Integrated Circuit (IC) device that operates at microwaves frequencies (300 MHz to 300 GHz) and it may be based on widely different semiconductor processes, such as conventional silicon CMOS and advanced Silicon Germanium (SiGe) technologies. Many efforts are being made to reduce the size and improve the performance of these circuits, with a key focus on lowering the noise and improving the linearity [Bow08].

Next, we will take a quick look at the analog front-end configurations that are usual used in digital telecommunications, the homodyne and superheterodyne front-ends. It will be also presented the multiband front-end configuration already used by several SDR systems. Normally, the transmitter design challenges are very similar to those of the receiver. Hence, the following subsections will only present the receiver side of the different architectures.

#### Superheterodyne Front-End

The superheterodyne receiver is divided in two main stages, an IF stage and a subsequent baseband stage. Its simplified configuration is depicted in Figure 2.5.

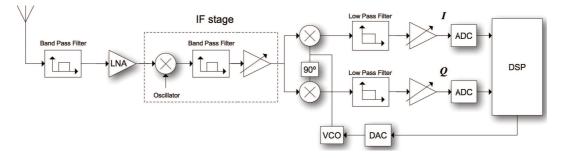

Figure 2.5: Superheterodyne front-end architecture.

First, the RF signal is downconverted to an IF frequency. Subsequently, the signal is filtered and amplified in order to select the desired channel. In the next stage, the signal is downconverted toward the baseband and amplified by an Automatic Gain Control (AGC) to fit the ADCs dynamic range. However, this configuration has some disadvantages. Since it has two stages, more components are needed and, therefore, an increased power consumption. Moreover, the superheterodyne must be designed according to a specific standard, which do not make this architecture suitable for wideband receivers as an SDR system. [Alb09]

To overcome this problem, a superheterodyne architecture derivation was proposed. Its simplified configurations can be seen in Figure 2.6. As one can see through the figure, instead of place the ADC at the output of the second downconverter stage, it is placed after the first down-converter stage. Since the quadrature downconversion is performed on the digital domain, this approach simplifies the hardware receiver design and, mainly, can deal with

Figure 2.6: Superheterodyne front-end derivation architecture.

wideband signals. This superheterodyne derivation is one of the simplest front-ends that can be built for use in SDR. [Alb09]

#### Homodyne Front-End

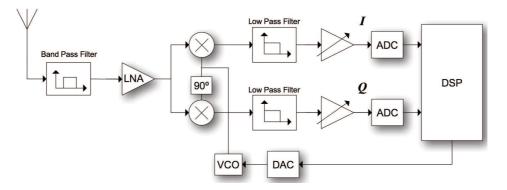

The simplified configuration of a homodyne receiver is depicted in Figure 2.7.

Figure 2.7: Homodyne front-end architecture.

In the homodyne receiver, the signal is firstly filtered and amplified in order to choose a specific channel. Subsequently, the signal is directly downconverted to the baseband by a Voltage-Controlled Oscillator (VCO). The resulting signal is filtered and amplified by an AGC to fit the signal to the ADCs dynamic range. This approach is very efficient because it only needs a few components when compared to the superheterodyne architecture. Although the homodyne architecture is not flexible, it can receive wideband signals. Thus, this front-end architecture is suitable for SDR systems. [Alb09]

#### Multiband Front-End

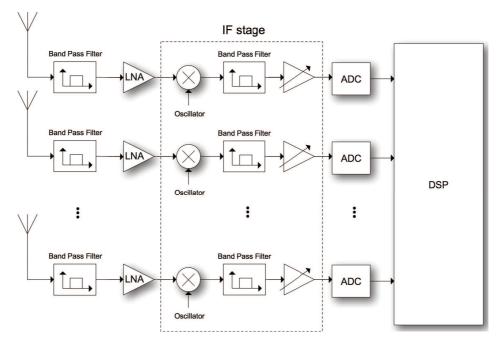

One of the main aims of a SDR receiver is to be a multiband system, thus a high bandwidth ADC is highly necessary. Since these components are not yet available, several solutions were proposed to overcome this problem. One of those architectures is based on several front-ends connected to the same DSP, each one receiving a different frequency band. Its simplified configuration is illustrated in Figure 2.8.

Although this system approach be fixed to the implemented front-ends, it is possible to add a new one if necessary. Thus, it is inflexible, but it has also some level of scalability.

Figure 2.8: Multiband front-end architecture.

Moreover, this architecture can be simplified if the system does not have to receive all the bands at the same time. [Alb09]

#### 2.3.2 Analog-to-Digital and Digital-to-Analog Converters

ADCs and DACs have a fundamental role in the evolution of SDR. The continued progress in this area made possible the signal conversion at higher and higher analog input frequencies, which allowed SDRs to move to the IF frequency.

The major parameters that define the performance of ADCs and DACs are the dynamic range and sampling rate. While dynamic range has not improved as in other technologies, a focused effort on increasing performance at higher frequencies has finally enable us to perform the signal digitalization at an IF frequency. Hence, while bit precision has only improved two bits (12 to 14 bits) over the last 5 years, the linearity has significantly improved by 40 dB (60 to 100 dBc for harmonics) for IF sampling [BB08].

Speed and power consumption are also an important tradeoff in what concern ADCs and DACs. If an ADC is fast, its power consumption is higher than a slower one. This is a very important issue in nowadays radios, mainly in mobile devices where cooling systems cannot be installed and the battery life is an extremely limiting factor. Currently, there are two trends among ADCs' researchers, some focus on increasing speeds and others on reducing power consumption [Man07].

#### 2.3.3 Digital Signal Processing Circuits

After signal digitalization, the remaining radio functions in the signal chain must be processed digitally. Hence, the digitalized IF signal must be firstly downconverted, filtered and decimated. Next, the same or another digital signal processor performs the slower speed signal processing such as channel and source decoding. The transmitter side is similar, but follows the reverse path.

Signal processing of high speed and wideband signals requires a very powerful and highspeed signal processing circuit. Thanks to the continuing reduction in feature size, more functions can be packaged into a single die while at the same time the total cost of those chips is also reduced. This technology has been notably used to increase the processing power of general purpose DSPs, but it has also been used to create cost effective high speed devices such as FPGAs and Application-Specific Integrated Circuits (ASICs), all key components used within a software defined radio system [BB08]. A DSP chip does signal processing by fetching instructions and data from memory, performing operations and storing the results back to memory [Mor00]. It has a higher speed than a regular Central Processing Unit (CPU), more resources and provides also some degree of parallelism. An ASIC is an integrated circuit that is designed to perform a fixed specific task such as digital downconversion and digital filtering. An ASIC has a better performance and higher speed then a DSP, however the user cannot change its functionalities. The FPGA comes to bridge the gap between DSPs and ASICs. One can perform any task in an FPGA just by mapping it to the hardware wherever needed. Thus, it provides the flexibility and complexity of an ASIC, but with the shorter turn-around time and reconfigurability of a programmable device.

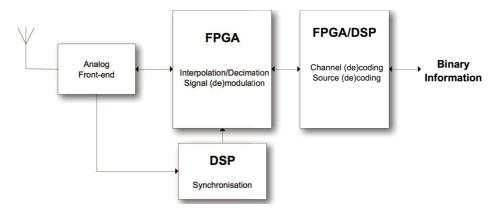

Since reconfigurability is one of the most important features of a SDR, the key components to perform the signal processing tasks are DSPs and FPGAs. Usually, the FPGA performs the radio functions, which follow the ADC such as downconverting, filtering and decimating. The DSP comes after in the radio chain to perform the slower speed signal processing such as channel and source decoding.

#### 2.3.4 SDR Platforms

Summarizing, the radio receiver chain starts with the antenna and is followed by an analog front-end where the signal is downconverted toward an IF frequency or the baseband. If we are in the presence of an IF configuration, the signal must be fed into an FPGA that downconverts the signal to the baseband. The same FPGA or a different DSP comes next to perform the slower speed signal processing such as signal demodulation, channel and source decoding. Moreover, an alternative DSP can be used to perform the radio synchronization functions, since they are independent from the rest. Figure 2.9 illustrates a typical SDR signal chain.

From the previous subsections, one could see that the development of high-performance SDR systems can present significant challenges in both design complexity and time to market. Thus, specific platforms are available in order to provide complete development environments and to enable faster and easier designs. Depending on the platform, all or some of the previous SDR key components are provided. The following platforms are some commercially available examples:

- LYRtech Virtex-4 FPGA SDR Development Platform two Xilinx Virtex-4 FPGAs, TI DSP, two ADCs @ 125 MS/s (14 bits), two DACs @ 500 MS/s (16 bits) and a RF module.

- **Texas SFF SDR Development Platform** Xilix Virtex-4 FPGA, 2 TI DSPs, two ADCs @ 125 MS/s (14 bits), two DACs @ 500 MS/s (16 bits). Modular architecture, one

Figure 2.9: Typical SDR signal chain.

RF module and an optional second RF module for full-duplex operation or to cover additional bands.

- *Ettus Research Universal Software Radio Peripheral (USRP)* Altera FPGA, gigabit Ethernet interface, two ADCs @ 64 MS/s (12 bits), two DACs @ 128 MS/s (14 bits), high-speed USB 2.0 controller and several RF module options. The USRP has an open design with freely available schematics, drivers and free software to integrate with GNU Radio. GNU Radio is a free software toolkit for learning about, building, and deploying SDR systems. The USRP is developed by a team led by Matt Ettus.

- Nallatech Virtex-4 XtremeDSP Development Kit Platform XilinxVirtex-4 FPGA, Spartan-II FPGA, two ADCs @ 105 MS/s (14 bits), two DACs @ 160 MS/s (14 bits), two banks of ZBT-SRAM and status LEDs. Support for external clock, on board oscillator, and programmable clocks.

These are only some examples of the many options available on the market. Some of them provide a FPGA, a DSP and a RF modulo, while others only provide one or two of these components (among others). A SDR developer should choose the one that most fits his SDR system. The *Virtex-4 XtremeDSP Development Kit* was the platform used to develop our DAB receiver

#### 2.3.5 Cognitive Radio

The concept of SDR brought up a new idea, the *Cognitive Radio* (CR). Also thought by Mitola [IM99, III00], it is essentially a SDR that senses its environment, tracks changes, and reacts according to its findings [CLA<sup>+</sup>09]. Thus, a CR should be able to detect holes on the frequency spectrum (opportunistic), estimate channel conditions and adapt its modulation parameters based on it, as well as transmit power controlled signals to reduce interference among systems. CRs should have a wideband front-end in order to sense the frequency spectrum and communicate with large bandwidth waveforms.

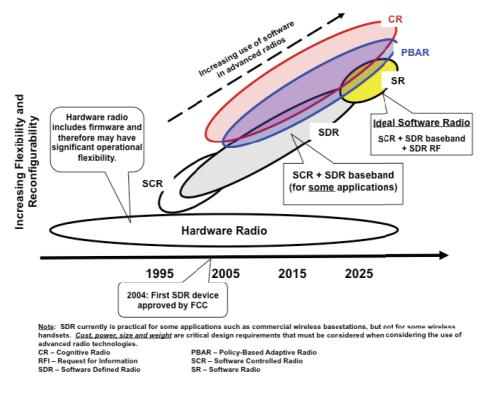

CRs are widely regarded as being the next step in the evolution of radio system, since it can adapt itself to every situation, replacing the traditional single function radios. Figure 2.10 illustrates a rough time evolution of the radio technology.

Figure 2.10: Time evolution of the radio technology. [Gue07]

Through Figure 2.10, one can observe that radio technology is moving toward the digital domain. Nowadays, some SDR approaches are already in use, but its ideal concept was not reached yet. Moreover, CRs are from all radio technologies the most flexible one.

# Chapter 3

# **Digital Audio Broadcasting**

### 3.1 Introduction

Digital Audio Broadcasting (DAB) is a digital radio broadcasting system developed within the Eureka 147 project in the 1980s. The protocol specification was finalized in 1993 and it was recognized as a world standard by International Telecommunication Union (ITU) in 1995 and by European Telecommunications Standards Institute (ETSI) in 1997 [Eur06].

Unlike the traditional analog radio, DAB combines multiple services onto a single broadcast frequency through the application of multiplexing and compression techniques. Besides the indispensable audio channels, it can also transmit programme-associated data such as song titles, lyrics, weather maps, traffic information and general advertisements, as well as information services from other sources which include news headlines, weather information or even the latest stock prices [For09b].

Since DAB was originally designed for terrestrial mobile reception it is able to eliminate the multipath interferences that commonly disturb analog systems (e.g. Amplitude Modulation (AM) and FM) while on move. This feature could not be possible without the so-called technique OFDM. This technique distributes the information to be transmitted over a great number of orthogonal carriers. Since selective frequency interferences only affect some of those carriers, with additional information redundancy and digital error correction techniques it is possible to reconstruct the sequence of bits in the receiver. For this reason, a driver is able to cross an entire country staying tuned to the same station with no signal fade and without the need of changing the frequency [For09b].

However, it has been shown that the audio quality on DAB systems is sometimes lower than on FM systems for stationary receivers due to the use of lower bit rates in order to increase the number of channels within the same DAB ensemble. To solve this problem, an upgraded version of the system was realized in February 2007. Digital Audio Broadcasting plus (DAB+) is based on the original DAB standard and provides the same services, but uses a more efficient audio codec. The MPEG Audio Layer II (MP2) was replaced by the HE-ACC v2 (AAC+), which allows an equivalent or better subjective audio quality while broadcasting at lower bit rates [For09b].

The *Eureka 147* Family of standards, which includes DAB, DAB+ and Digital Multimedia Broadcasting (DMB), has experienced a great progress throughout the past few years. Its key area of development is Europe, but also China, Korea and the majority of the Asia Pacific Region including Australia [For08]. Nowadays, DAB has regular services in more than 30 countries, more than 990 DAB receivers are commercially available and more than 12 million have already been sold all around the world.

In Portugal, the DAB pilot broadcasts started in January of 1998 and several initiatives promoting DAB were developed during Expo 98. *RTP* won the license for installing and operating the national DAB ensemble in March of 1999. These radio transmissions operate on the 12B channel at the frequency of 225.648 MHz. RTP is also the provider of the five audio channels currently transmitted within the DAB ensemble, which are *Antena 1*, *Antena 2*, *Antena 3*, *RDP África* and *RDP Internacional*. According to Paulo Ferreira, who is working on RTP, the five audio channels are being transmitted in stereo with a bit rate of 192 kbit/s. Currently, there are 42 transmitters that cover more than 75% of the population, mainly in the coastline [For08].

The *Eureka 147* Family of standards has the potential to replace the existing AM and FM radio broadcasting systems in a near future, some say that it is the future of the radio!

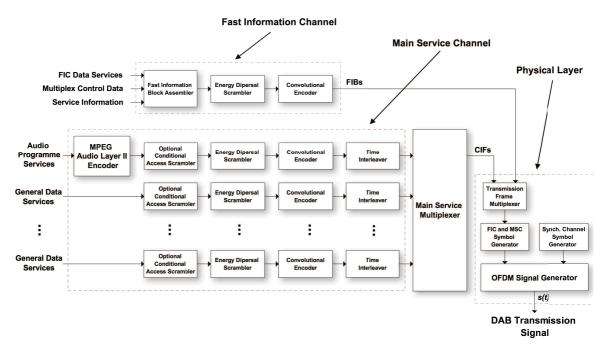

### 3.2 The DAB System

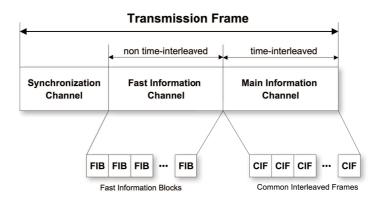

The DAB system can be divided in three parts. Two of them are related with the main transport mechanisms, the Main Service Channel (MSC) and the Fast Information Channel (FIC). Starting with the MSC, each service signal is encoded individually at source level, error protected and time interleaved in the channel encoder. Then the services are multiplexed in the MSC according to a pre-determined multiplex configuration. In the FIC side, the multiplex control and service information are also encoded and error protected. Finally, the MSC is combined with the FIC to form the transmission frame. The third part comes in the transmission chain just after the previous two. This is responsible for the physical layer, which includes frequency interleaving, Differential Quadrature Phase-Shift Keying (DQPSK) and OFDM modulations. At the end, the signal is converted to the radio frequency band, amplified and transmitted [For09b].

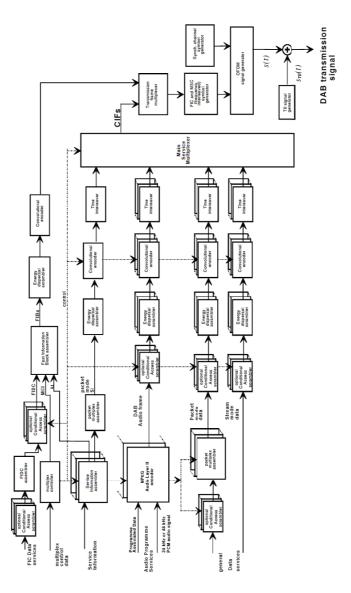

The conceptual block diagram of a DAB transmitter is given in Figure 3.1. The complete block diagram that is provided in [Eur06] can be found in Appendix A.

The next subsections shall describe each part of the DAB transmitter, as well as its transport mechanism and transmission modes. The receiver is similar to the transmitter, but follows the reverse path. Further information can be found in [Eur06]. Moreover, the last subsection shall present a brief overview of OFDM given that it is one of the main features of the DAB system.

### 3.3 DAB Modes

As will be discussed later, the OFDM parameters must be chosen according to the requirements of the channel. A long symbol length  $T_s$  with a long cyclic prefix make the system robust against long echoes, but sensitive against high Doppler frequencies [SL05]. Since DAB was design to operate in a wide range of frequencies (300MHz - 3GHz) and in several channels (terrestrial, satellite, cable), four transmissions modes have been defined with different sets of parameters (see subsection 3.5.5). The different modes are specified to accommodate different frequency ranges and operating conditions. In Section 15.1 of the DAB standard [Eur06], suitable conditions are described as follows (quote):

Figure 3.1: Conceptual block diagram of the DAB transmitter.

- Transmission mode I is intended to be used for terrestrial Single Frequency Networks (SFN) and local-area broadcasting in Bands I, II and III.

- Transmission modes II and IV are intended to be used for terrestrial local broadcasting in Bands I, II, III, IV, V and in the 1452 MHz to 1492 MHz frequency band (i.e. L-Band). It can also be used for satellite only and hybrid satellite-terrestrial broadcasting in L-Band.

- Transmission mode III is intended to be used for terrestrial, satellite and hybrid satelliteterrestrial broadcasting below 3 000 MHz.

- For cable distribution, transmission mode III is the preferred mode because it can be used at any frequency available on cable. However, transmission modes I, II and IV may also be used, depending on the chosen frequency band.

One of the most important DAB features is the possibility of using SFN, i.e., multiple geographically separated transmitters broadcasting at the same frequency. This requires that the transmitters have a maximum distance among them and be accurately time synchronized, by this way interferences at the receiver can be avoided [Mul08].

Although these different transmission modes also affect the FIC and the MSC, the main differences are on the physical layer.

### **3.4** Transport Mechanisms

As already said, there are two mechanisms for data transporting: the MSC and the FIC. The first one carries user information, such as audio data and other services. The FIC is intended to transport the information that will allow the receiver to understand the MSC multiplex structure and to know which programmes are transmitted in the ensemble. Furthermore, a third mechanism called synchronization channel is used within the transmission system for synchronization and demodulation purposes. The next subsections shall describe each of these three channels.

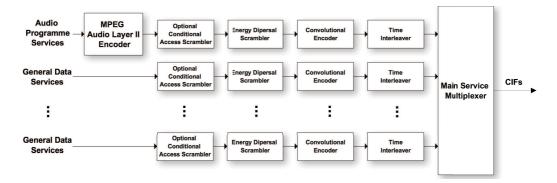

#### 3.4.1 Main Service Channel

The MSC is made up of Common Interleaved Frames (CIFs), each of these transports Audio Programme Services, Service Information or general Data Services. Obviously, the main service carried in the MSC is the stream based audio data. Depending on the service requirements, a packet based or a stream based mode can be used. All services contained in the MSC are multiplexed according to the information carried in the FIC. The simplified block diagram of the MSC chain is illustrated in Figure 3.2.

Figure 3.2: Conceptual block diagram of the MSC encoder.

Each sub-channel is individually encoded at source level, scrambled, error protected and time interleaved in the channel encoder. The next subsections shall describe each of this functions.

#### MPEG Audio Layer II codec

The available MSC gross bit rate is about 2.3 Mbit/s, including the audio programme data and error protection data. The balance of these two kinds of data establishes a tradeoff between ruggedness of mobile reception and programme capacity. The ideal balance for terrestrial transmission would be an equal amount for both kinds of data, in this case 1.2 Mbit/s. However, a single stereo audio signal requires a bit rate of at least 1.5 Mbit/s [Gan03]. The source encoder is used to solve this problem by reducing the bit rate of the audio programme data. The DAB system uses MP2, which can reduce the required bit rate by a factor of 6 or more. The encoder can operate in stereo or mono mode and the output bit rate ranges from 8 kbit/s to 384 kbit/s [Eur06].

#### Conditional access scrambler