### Vítor Hugo Martins Silva

# Desenvolvimento de Componentes para Sistemas de Segurança Crítica

### Vítor Hugo Martins Silva

## Desenvolvimento de Componentes para Sistemas de Segurança Crítica

dissertação apresentada à Universidade de Aveiro para cumprimento dos requisitos necessários à obtenção do grau de Mestre em Engenharia Electrónica e Telecomunicações, realizada sob a orientação científica do Professor Doutor Arnaldo Silva Rodrigues de Oliveira, Professor Auxiliar Convidado do Departamento de Electrónica, Telecomunicações e Informática da Universidade de Aveiro e do Mestre Valter Filipe Miranda Castelão da Silva, Assistente de 2º Triénio na Escola Superior de Tecnologia e Gestão de Águeda.

### o júri

### presidente

### Doutor José Alberto Gouveia Fonseca

professor associado do Departamento de Electrónica, Telecomunicações e Informática da Universidade de Aveiro

### Doutor José Carlos Meireles Monteiro Metrôlho

professor adjunto do Departamento de Engenharia Informática da Escola Superior de Tecnologia do Instituto Politécnico de Castelo Branco

### Doutor Arnaldo Silva Rodrigues de Oliveira

professor auxiliar convidado do Departamento de Electrónica, Telecomunicações e Informática da Universidade de Aveiro

### Mestre Valter Filipe Miranda Castelão da Silva

assistente de 2º Triénio na Escola Superior de Tecnologia e Gestão de Águeda

### agradecimentos

Desde o inicio desta tese que tive o apoio e contribuição de várias pessoas, umas com o seu conhecimento, outras com palavras de incentivo, mas foram todas muito importantes e sem elas a conclusão deste trabalho não seria possível. Por esses motivos quero deixar aqui os devidos agradecimentos a todos eles.

Quero começar por agradecer ao Prof. Doutor José Alberto Fonseca que numa fase inicial contribuiu com o seu conhecimento e orientação. Agradeço também ao Mestre Valter Filipe Silva que em algumas fases do trabalho me ajudou a ultrapassar alguns obstáculos. Em particular gostaria de agradecer ao Prof. Doutor Arnaldo Silva Rodrigues de Oliveira que inicialmente começou como meu co-orientador e mais tarde como orientador, por todo o tempo dispendido, conhecimento partilhado, sugestões e discussões que contribuíram de uma forma muito importante na minha formação e que se reflectiu na qualidade desta dissertação.

Por último, gostaria de agradecer à minha família e amigos por todo o apoio que me deram, em especial à minha mãe que sempre me incentivou e apoiou nas alturas mais difíceis. É com muito orgulho que dedico este trabalho à minha mãe.

### palavras-chave

Comunicações Industriais, Segurança Critica, FPGAs, Sistemas Digitais Reconfiguráveis, Sistemas Tempo-Real, CAN.

#### resumo

Hoje em dia é muito frequente a utilização de sistemas de controlo em aplicações de segurança crítica, por exemplo nos aviões, automóveis, etc. Um sistema de segurança crítica é assim designado porque em caso de falha pode resultar em grandes prejuízos monetários ou, no pior cenário, em perdas de vidas humanas. Este tipo de sistemas têm que ser robustos e tolerantes a falhas para falhar o mínimo possível e de uma forma segura. É também necessário que estes sistemas atendam a requisitos temporais para garantir o seu correcto funcionamento, sendo por isso designados de sistemas temporeal. Quando tais sistemas são distribuídos, como em redes de sensores, actuadores e controladores interligados por barramentos de campo, a comunicação desempenha um papel importante no comportamento temporal.

Tem-se assistido nos últimos anos a um incremento da investigação e desenvolvimento da área de sistemas de segurança crítica. Têm vindo a ser criados alguns standards nesta área, sendo actualmente muito utilizado o CAN – *Controller Area Network*. No DETI tem-se realizado muita investigação em torno do CAN, tendo-se recentemente trabalhado em sistemas que permitem introduzir redundância e maior largura de banda no barramento sem modificação dos módulos a ele ligados. Os sistemas *x-by-wire* são um exemplo de sistemas de segurança crítica utilizados nos automóveis onde a questão da largura de banda é muito importante. Esta dissertação é uma continuação desse trabalho, onde se pretende implementar na prática um sistema que introduza estas características a um barramento CAN.

As principais contribuições originais desta dissertação são o desenvolvimento de alguns dos componentes projectados no trabalho de investigação em curso, nomeadamente um gestor de topologia e um comutador. Estes componentes permitem adicionar barramentos redundantes e gerir de uma forma dinâmica a topologia numa rede CAN. Para tal foram utilizadas FPGAs — *Field Programmable Gate Arrays*, um processador da Xilinx e algum hardware desenvolvido no DETI, o CLAN e o respectivo controlador que permite a sua interface com microprocessadores. A prototipagem em FPGAs facilitou e simplificou a tarefa de simulação da lógica necessária à implementação, tanto do gestor de topologia como do comutador.

#### keywords

Industrial Communications, Critical Security, FPGAs, Reconfigurable Digital Systems, Real Time Systems, CAN.

#### abstract

Nowadays, the use of control systems in critical security applications is very common, for instance in airplanes, automobiles, etc. It is called critical security application because in case any fault occurs, it can cause huge monetary damages or, in the worst scenario, it can cause the death of human lives. This type of system must be strong and fault tolerant in order to fail the least as possible and in a secure and safe way. It is also necessary that these systems answer to time requirements so that they can guarantee their proper performance, being therefore known as real-time systems. Whenever these systems are distributed, as in sensor networks, activators and controllers interconnected by fieldbuses, communication assumes an important role in time behavior.

In the past few years we have been watching to an increase in the critical security systems research and development area. Some standards have been created in this field, being CAN - Controller Area Network one of the most used in the present. In DETI, plenty of research has been made about CAN, and recently important work has been done in systems that allow the introduction of redundancy and greater bandwidth in the bus without modifying the modules which are attached to it. The systems x-by-wire are just an example of critical security systems which are used in cars, and where the matter of bandwidth is actually very important. This dissertation is therefore a continuation of that work that has been developed so far, which aims to implement, in practice, a system that is able to introduce these features in a CAN bus.

The most original and more important contributions of this dissertation are the development of some of the components projected in this work of ongoing research, namely a topology manager and a commuter. These components allow to attach redundant buses and to manage, in a dynamic kind of way, a topology in a CAN network. In order to achieve it, there have been used FPGAs – Field Programmable Gate Arrays, a processor from Xilinx and some hardware which had been developed in DETI, CLAN and the corresponding controller that allows its interface with microprocessors. The prototyping in FPGAs has facilitated and simplified the task of simulating the logic that was necessary to the implementation, whether from the topology manager whether from the commuter.

## Índice

| 1. | Int   | rodu   | ıção                                                                   | 1    |

|----|-------|--------|------------------------------------------------------------------------|------|

| 1  | .1.   | Enq    | uadramento                                                             | 1    |

| 1  | .2.   | Mot    | tivação                                                                | 5    |

| 1  | .3.   | Obje   | ectivos                                                                | 9    |

| 1  | .4.   | Orga   | anização da Dissertação                                                | . 10 |

| 2. | Sist  | tema   | as Distribuídos13                                                      | 3    |

| 2  | 2.1.  | Con    | ceitos Básicos                                                         | . 13 |

| 2  | 2.2.  | Mod    | delo OSI                                                               | . 15 |

| 2  | 2.3.  | Barr   | ramentos de Campo                                                      | . 16 |

| 2  | 2.4.  | Seg    | urança Crítica                                                         | . 19 |

| 2  | 2.5.  | Tole   | erância a Falhas                                                       | . 21 |

|    | 2.5.  | 1.     | Falhas do Tipo Falha-Silêncio                                          | . 22 |

|    | 2.5.  | 2.     | Falhas do Tipo Falha-Pára ou Falha-Consistente                         | 22   |

|    | 2.5.3 | 3.     | Falhas do Tipo Falha-Inconsistente (maliciosa ou bizantina)            | 23   |

| 3. | 0 P   | roto   | ocolo CAN                                                              | 5    |

| 3  | 3.1.  | Intro  | odução                                                                 | 25   |

| 3  | 3.2.  | Cam    | nada Lógica                                                            | . 28 |

|    | 3.2.  | 1.     | Arbitragem no Acesso ao Barramento                                     | . 28 |

|    | 3.2.  | 2.     | Formato das Tramas CAN                                                 | 29   |

|    | 3.    | .2.2.1 | L. Trama de Dados                                                      | . 29 |

|    | 3.    | .2.2.2 | 2. Trama Remoto                                                        | . 33 |

|    | 3.    | .2.2.3 | 3. Trama de Sinalização de Erro                                        | . 34 |

|    | 3.    | .2.2.4 | 1. Trama de Sinalização de Sobrecarga                                  | 35   |

| 3  | 3.3.  | Cam    | nada Física                                                            | . 35 |

|    | 3.3.  | 1.     | Codificação dos Bits                                                   | . 35 |

|    | 3.3.2 | 2.     | Temporização dos Bits e Sincronização                                  | 37   |

|    | 3.3.3 | 3.     | Interdependência entre Taxa de Transmissão e Comprimento do Barramento | 38   |

|    | 3.3.  | 4.     | Meio Físico                                                            | . 39 |

|    | 3.3.  | 5.     | Parâmetros do Meio Físico                                              | 40   |

| 4. | Tol   | erân           | icia a Falhas em Sistemas Distribuídos de Segurança Crítica 45 |    |

|----|-------|----------------|----------------------------------------------------------------|----|

| 4  | l.1.  | Intro          | odução                                                         | 45 |

| 4  | 1.2.  | Red            | CAN                                                            | 45 |

| 4  | 1.3.  | The            | Columbus' egg Idea for Bus Media                               | 49 |

| 2  | 1.4.  | CAN            | centrate e ReCANcentrate                                       | 51 |

| 2  | 1.5.  | Flex           | Ray                                                            | 53 |

| 4  | 1.6.  | Flex           | CAN                                                            | 56 |

| 2  | 1.7.  | Dyn            | amic Topology Management em CAN                                | 58 |

| 2  | 1.8.  | Com            | nparação das Várias Abordagens Apresentadas                    | 59 |

| 5. | Ges   | tão            | Dinâmica da Topologia em CAN                                   |    |

| Ē  | 5.1.  | Net            | work Switch Unit (NSU)                                         | 61 |

| Ē  | 5.2.  | Тор            | ology Manager Unit (TMU)                                       | 64 |

|    | 5.2.  | 1.             | Protocolo de Replicação da TMU                                 | 66 |

| Ę  | 5.3.  | Tipo           | s de Falhas Suportados pelo Sistema                            | 66 |

|    | 5.3.  | 1.             | Falhas no Nodo                                                 | 67 |

|    | 5.3.2 | 2.             | Falhas do Tipo Transiente no Meio de Transmissão               | 67 |

|    | 5.3.3 | 3.             | Atomicidade das Mensagens                                      | 67 |

|    | 5.3.4 | 4.             | Falhas Permanentes no Meio de Transmissão                      | 68 |

|    | 5.3.5 | 5.             | Partições no Barramento                                        | 68 |

| Ç  | 5.4.  | Cen            | ários de Operação                                              | 69 |

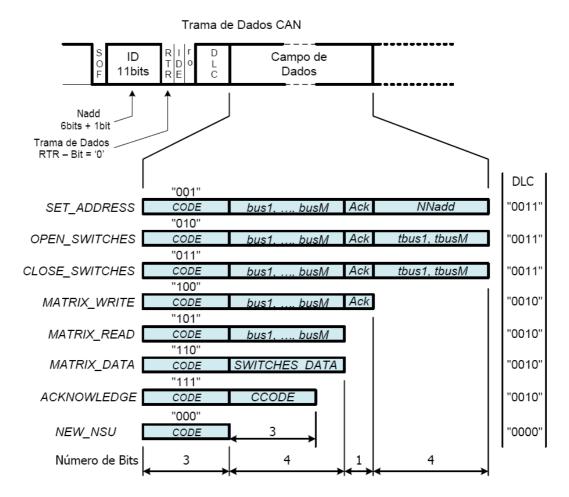

|    | 5.5.  | Com            | nandos do Sistema                                              | 71 |

|    | 5.5.2 | 1.             | Comandos de Descoberta e de Configuração                       | 72 |

|    | 5.5.2 | 2.             | Comandos de Operação                                           | 73 |

|    | 5.5.3 | 3.             | Mapeamento dos Comandos em Tramas CAN                          | 75 |

| 6. | Imp   | olem           | nentação da NSU 77                                             |    |

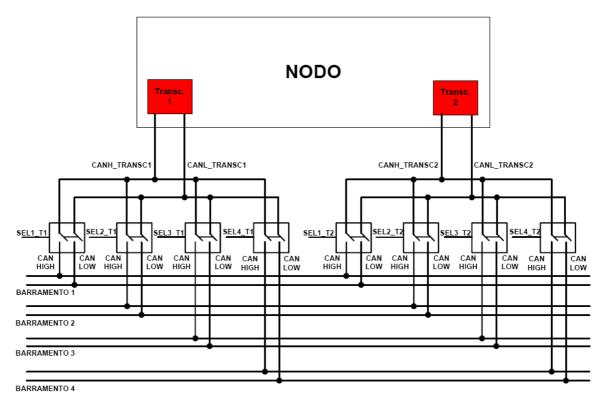

| 6  | 5.1.  | Arqı           | uitectura da Switch Matrix                                     | 77 |

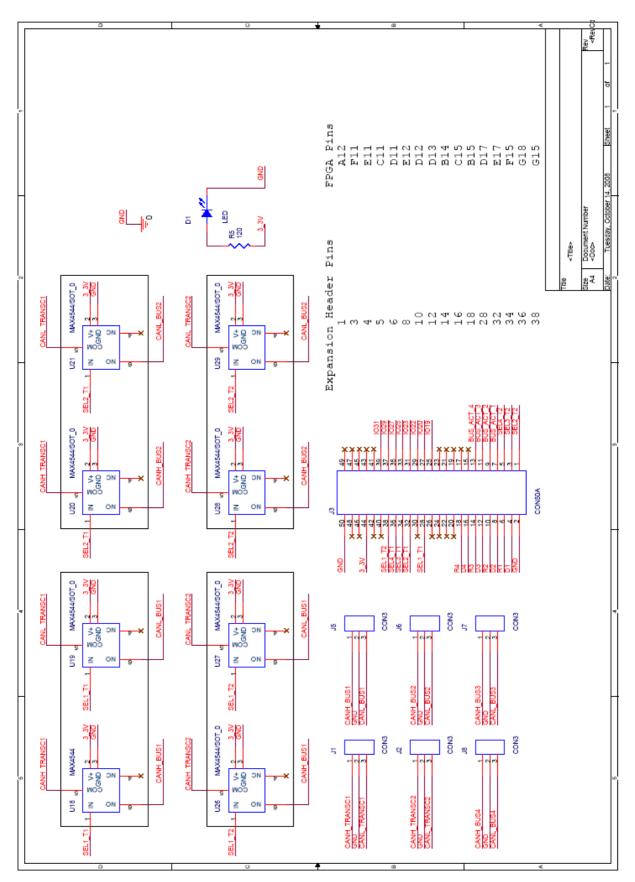

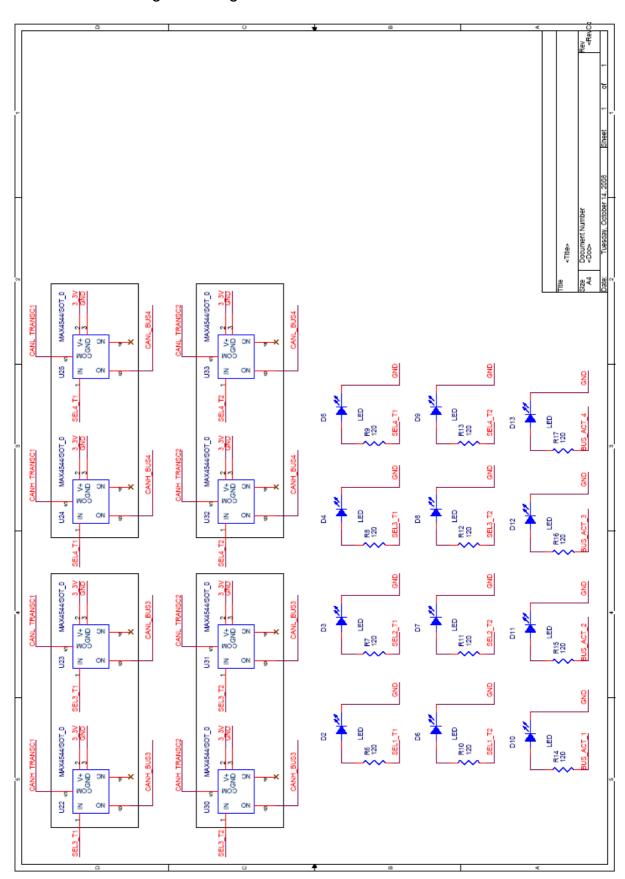

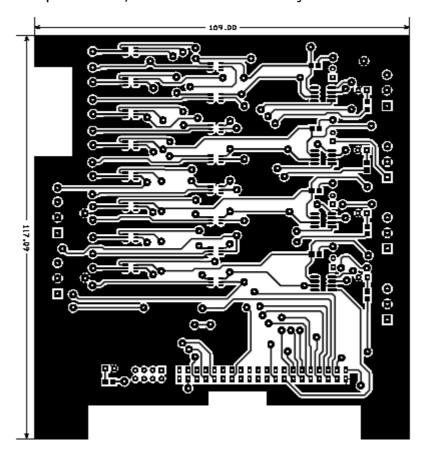

|    | 6.1.  | 1.             | Circuito e PCB da Switch Matrix                                | 79 |

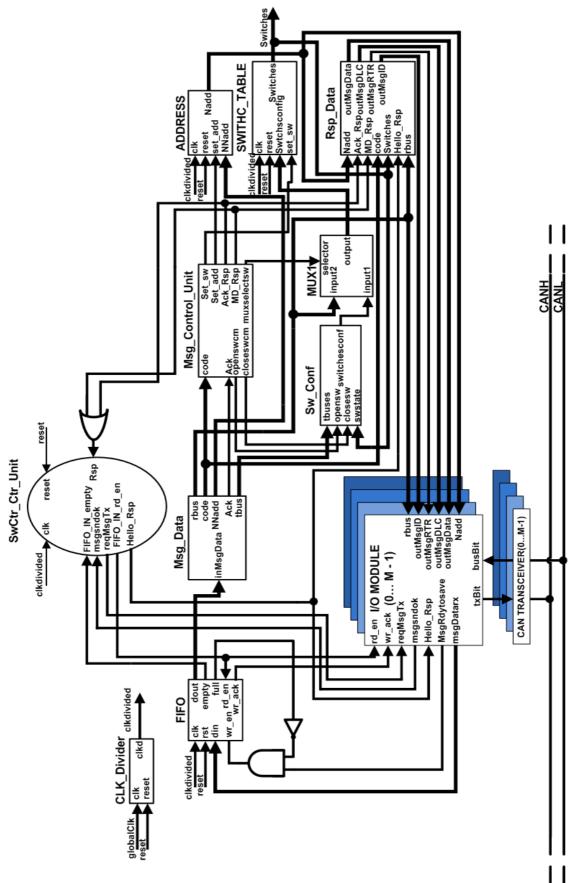

| 6  | 5.2.  | Arqu           | uitectura do Switch Controller                                 | 79 |

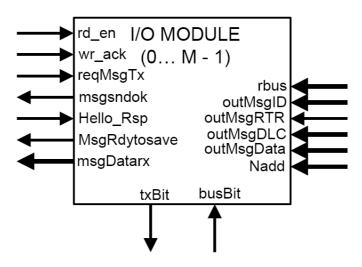

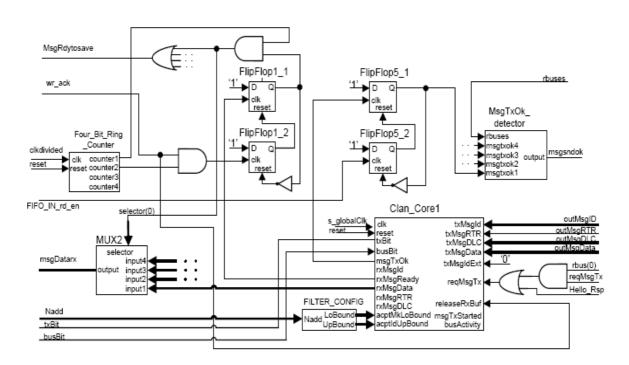

|    | 6.2.  | 1.             | Módulo I/O                                                     | 82 |

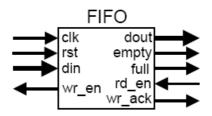

|    | 6.2.2 | 2.             | FIFO                                                           | 84 |

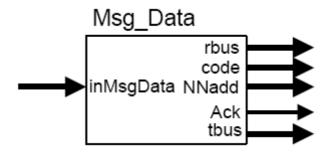

|    | 6.2.3 | 3.             | MSG_Data                                                       | 85 |

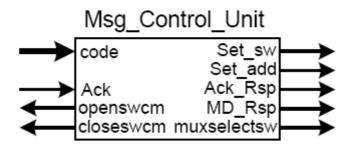

|    | 6.2.4 | 4.             | Msg_Control_Unit                                               | 87 |

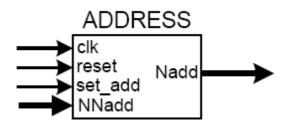

|    | 6.2.5 | <del>5</del> . | ADDRESS                                                        | 88 |

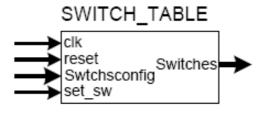

|      | 6.2.6.   | SWITCH_TABLE                                                        | 89  |

|------|----------|---------------------------------------------------------------------|-----|

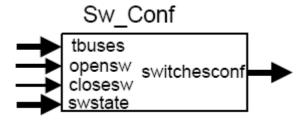

|      | 6.2.7.   | Sw_Conf                                                             | 90  |

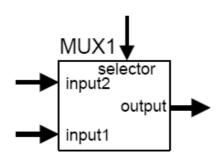

|      | 6.2.8.   | MUX1                                                                | 91  |

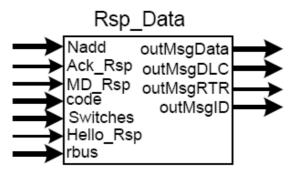

|      | 6.2.9.   | Rsp_Data                                                            | 92  |

|      | 6.2.10.  | SwCtr_Ctr_Unit                                                      | 93  |

|      | 6.2.11.  | CLK_Divider                                                         | 96  |

|      | 6.2.12.  | Teste Efectuado à NSU                                               | 97  |

| 6.3  | 3. VHC   | L (linguagem de descrição de hardware)                              | 98  |

| 7.   | Implem   | nentação da TMU1                                                    | 01  |

| 7.3  | 1. Mic   | oprocessador <i>Picoblaze</i>                                       | 101 |

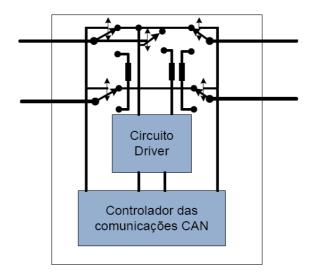

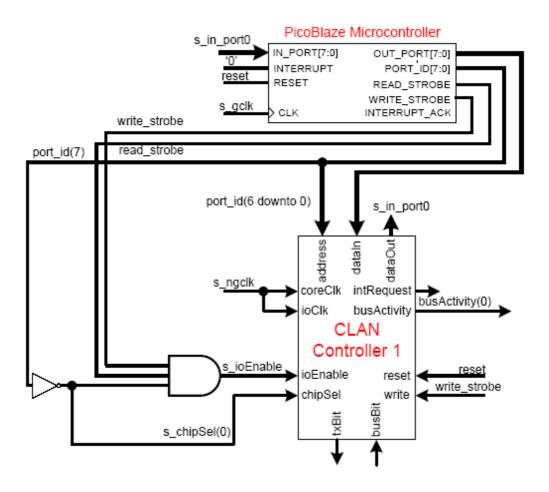

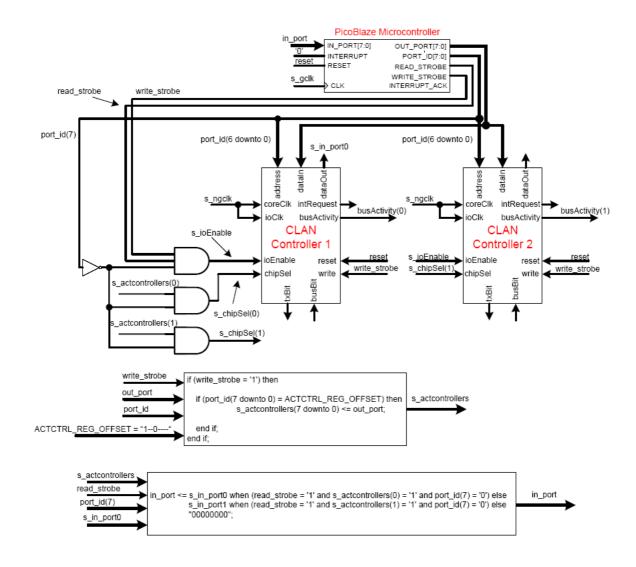

|      | 7.1.1.   | Interface Controlador CLAN - PicoBlaze                              | 103 |

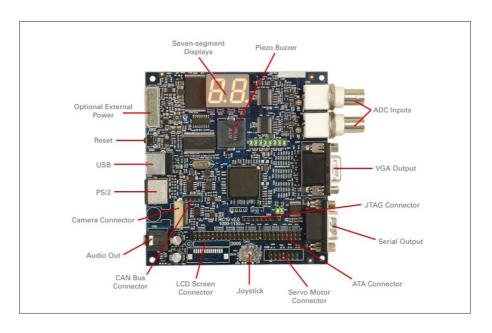

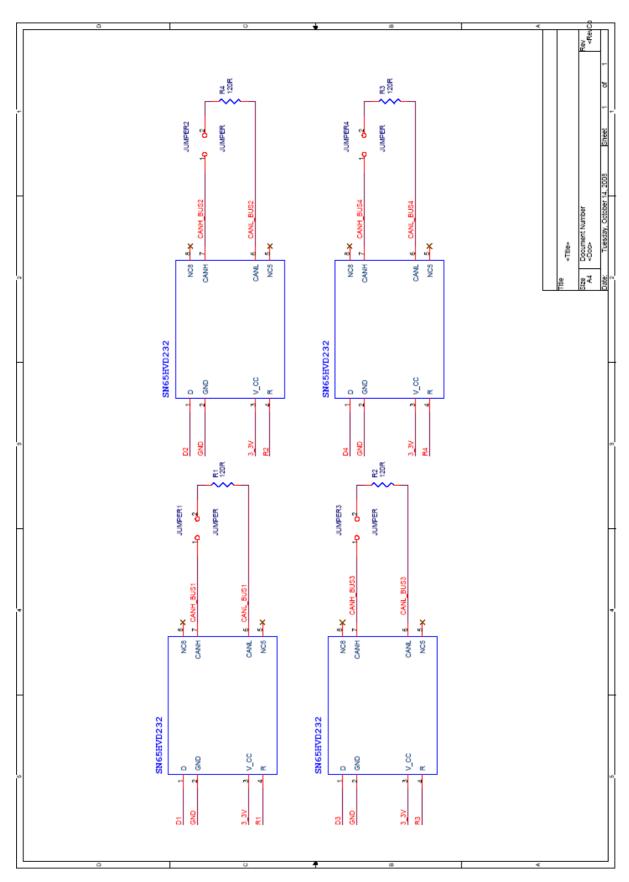

| 7.2  | 2. Plac  | a de Interface da TMU com os Barramentos CAN                        | 104 |

| 7.3  | 3. Test  | e à Abordagem Híbrida Software/Hardware para a Implementação da TMU | 105 |

| 8.   | Conclus  | são1                                                                | 07  |

| 8.2  | 1. Resi  | umo do Trabalho Realizado                                           | 107 |

| 8.2  | 2. Dire  | cções de Trabalho Futuro                                            | 110 |

| Α.   | Inform   | ação Adicional Sobre o Hardware da NSU1                             | 11  |

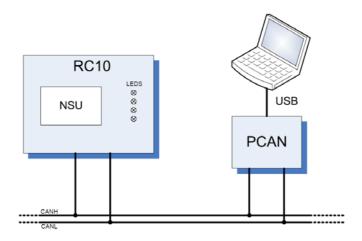

| Α.:  | 1. Plac  | a de Desenvolvimento RC10                                           | 111 |

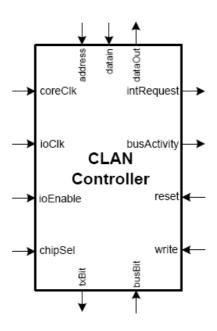

| Α.:  | 2. Con   | trolador CAN (CLAN)                                                 | 112 |

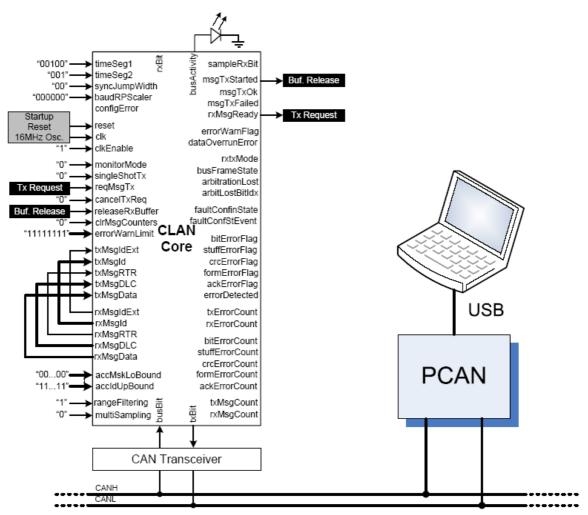

|      | A.2.1    | Teste ao CLAN                                                       | 114 |

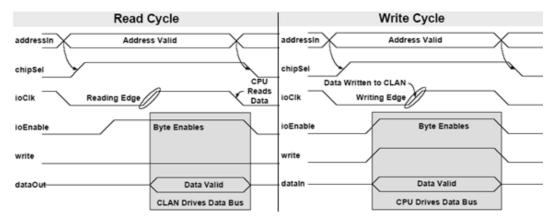

| Α.:  | 3. Inte  | rface CLAN com Microprocessador                                     | 115 |

| Α.   | 4. Tecr  | nologias para Projecto e Implementação da <i>Switch Matrix</i>      | 117 |

| Α.   | 5. Circ  | uito da <i>Switch Matrix</i>                                        | 127 |

| В.   | Inform   | ação Adicional Sobre o Hardware da TMU1                             | 33  |

| В.:  | 1. Plac  | a de Interface                                                      | 133 |

| C.   | Progran  | ma de Monitorização PCAN1                                           | 37  |

| D.   | Lista de | Acrónimos1                                                          | 39  |

| Bibl | iografia | 1                                                                   | 43  |

## Lista de Figuras

| Figura 1: a) Abordagem distribuída; b) Abordagem centralizada                               | 2   |

|---------------------------------------------------------------------------------------------|-----|

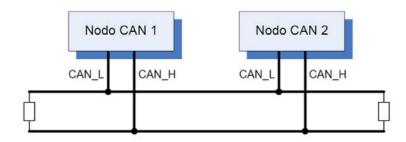

| Figura 2: Barramento CAN, comunicação entre dois nodos                                      | 4   |

| Figura 3: Barramento com 2-níveis de redundância.                                           | 5   |

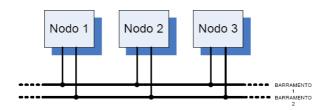

| Figura 4: Topologia estrela circular                                                        | 6   |

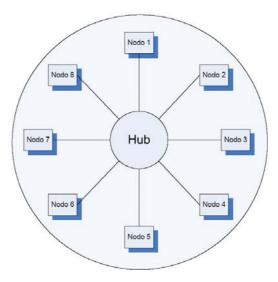

| Figura 5: Topologia estrela em linha                                                        |     |

| Figura 6: Rede com replicação de barramentos                                                | 7   |

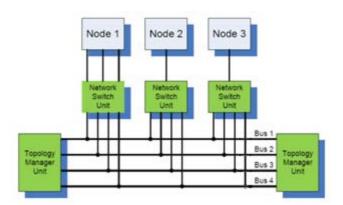

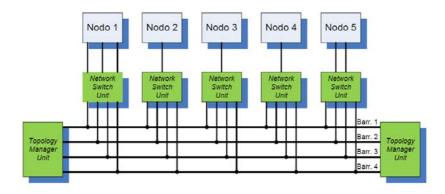

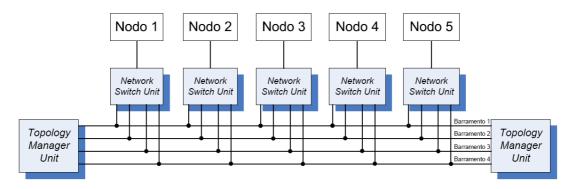

| Figura 7: Arquitectura de rede proposta                                                     | 8   |

| Figura 8: Abordagem distribuída para o caso da topologia barramento                         |     |

| Figura 9: Camadas do modelo OSI                                                             |     |

| Figura 10: Versão colapsada do modelo OSI aplicado a barramentos de campo                   |     |

| Figura 11: Exemplos de topologias genéricas                                                 | 17  |

| Figura 12: FTU tolerante à falha do tipo falha-silêncio com dois nodos                      | 22  |

| Figura 13: FTU com três nodos e mecanismo de votação TMR                                    | 23  |

| Figura 14: FTU com quatro nodos e protocolo (Byzantine-Resilient Agreement Protocol)        |     |

| Figura 15: Camadas do modelo OSI utilizadas pelo CAN                                        | 26  |

| Figura 16: Exemplo de um processo de arbitragem de acordo com o protocolo CAN               | 29  |

| Figura 17: Formato da trama de dados e trama remoto (formato base)                          | 30  |

| Figura 18: Formato do campo arbitragem                                                      | 31  |

| Figura 19: Formato do campo de controlo                                                     | 31  |

| Figura 20: Formato do campo CRC                                                             | 32  |

| Figura 21: Formato do campo acknowledgement.                                                | 33  |

| Figura 22: Formato de uma trama de erro activo.                                             | 34  |

| Figura 23: Comparação entre o código NRZ e o código Manchester                              | 36  |

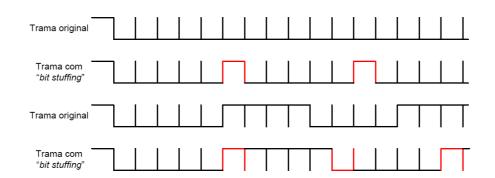

| Figura 24: Exemplos da técnica "bit stuffing" usada no protocolo CAN                        | 36  |

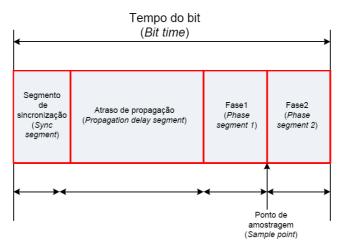

| Figura 25: As várias fases num tempo de bit                                                 | 37  |

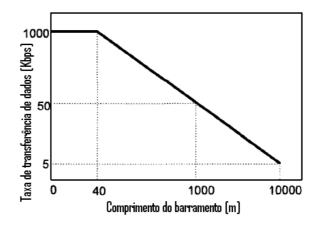

| Figura 26: Relação entre a taxa de transferência de dados e o comprimento do barramento     | 38  |

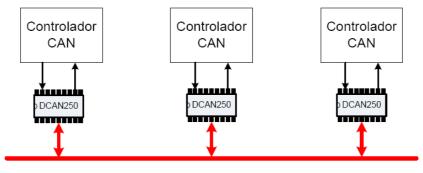

| Figura 27: Modo de utilização do DCAN250                                                    | 40  |

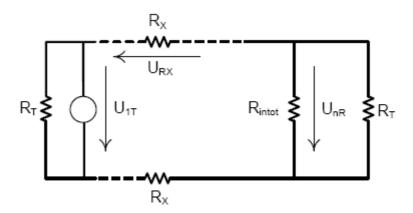

| Figura 28: Resistências que normalmente se encontram num barramento CAN bifilar             | 41  |

| Figura 29: Circuito LC equivalente do barramento.                                           | 42  |

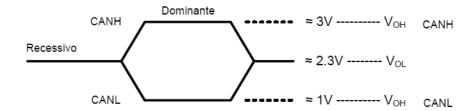

| Figura 30: Voltagens características do estado recessivo e dominante do circuito SN65HVD23: | 2D. |

|                                                                                             | 43  |

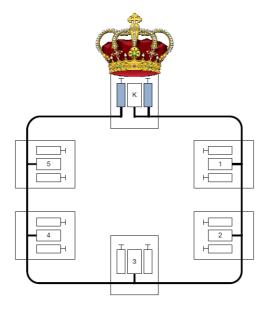

| Figura 31: Arquitectura Reino para CAN com cinco cidades                                    | 46  |

| Figura 32: Módulo RedCAN no modo transparente                                               | 46  |

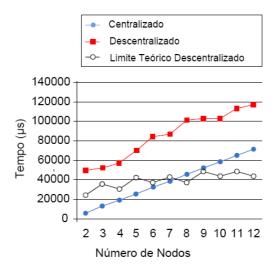

| Figura 33: Tempos de arranque sem erros no sistema                                          | 48  |

| Figura 34: Tempos de reconfiguração na presença de erros                                    | 48  |

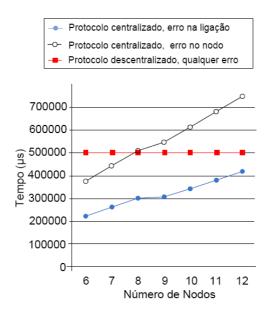

| Figura 35: The Columbus' egg idea for bus media em CAN                                      | 50  |

| Figura 36: Dupla redundância, replicação da camada MAC e meio de transmissão                | 50  |

| Figura 37: Arquitectura CANcentrate                                                         | 51  |

| Figura 38: Arquitectura ReCANcentrate                                                       | 52  |

| Figura 39: Exemplo de estrutura de barramento híbrida para FlexRay                          | 54  |

| Figura 40: Safety Layer e Safeware sohre a stack do modelo OSI                              | 57  |

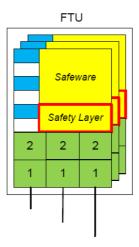

| Figura 41: Componente FTU (fault tolerant unit) utilizado pelo protocolo SafeCAN                  | 57    |

|---------------------------------------------------------------------------------------------------|-------|

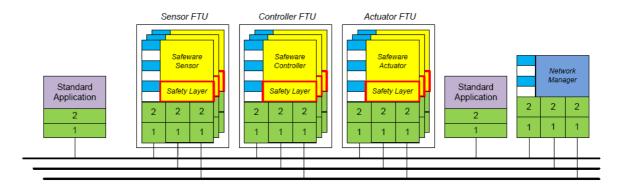

| Figura 42: Exemplo de aplicação envolvendo componentes replicados                                 | 58    |

| Figura 43: Arquitectura de rede proposta DTM                                                      | 59    |

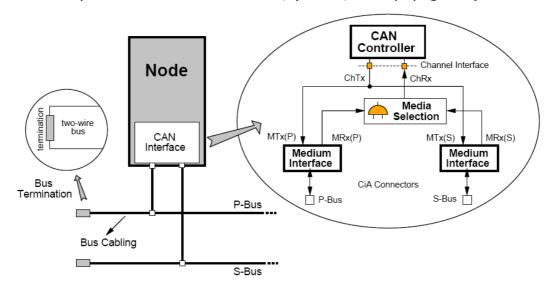

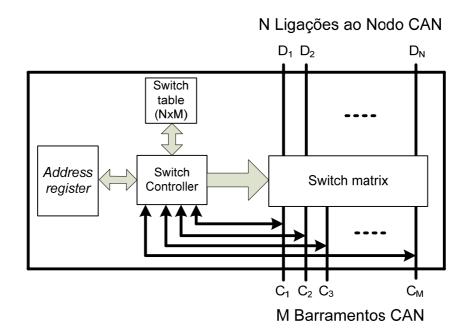

| Figura 44: Arquitectura interna da NSU - Network Switch Unit                                      | 62    |

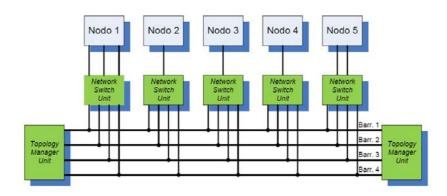

| Figura 45: Exemplo de uma configuração utilizando a DTM                                           | 63    |

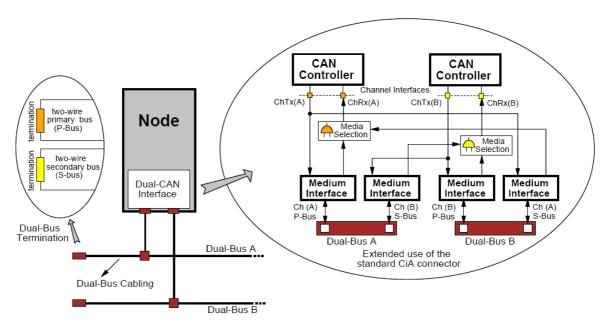

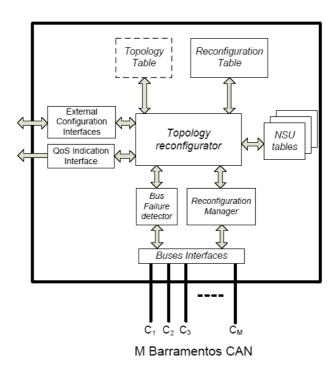

| Figura 46: Arquitectura da TMU - Topology Manager Unit                                            | 64    |

| Figura 47: Exemplos de algumas falhas possíveis na topologia barramento                           | 68    |

| Figura 48: Exemplo com topologia dinâmica                                                         | 69    |

| Figura 49: Exemplo com NSUs 2:4                                                                   |       |

| Figura 50: Exemplo com caminhos virtuais                                                          | 70    |

| Figura 51: Exemplo com estrela virtual                                                            | 71    |

| Figura 52: Mapeamento dos comandos no campo de dados das mensagens CAN                            | 75    |

| Figura 53: Exemplo com as ligações dos transceivers CAN do nodo aos barramentos por               |       |

| intermédio dos interruptores da <i>switch matrix</i> (para o caso de duas interfaces com o nodo e |       |

| quatro barramentos 2:4)                                                                           | 78    |

| Figura 54: Arquitectura do Switch Controller                                                      | 81    |

| Figura 55: Módulo I/O da NSU                                                                      | 83    |

| Figura 56: Arquitectura detalhada do módulo de I/O                                                | 83    |

| Figura 57: FIFO da NSU                                                                            |       |

| Figura 58: Componente <i>Msg_Data</i> da NSU                                                      | 86    |

| Figura 59: Componente <i>Msg_Control_Unit</i> da NSU                                              | 87    |

| Figura 60: Componente ADDRESS da NSU (endereço da NSU)                                            | 89    |

| Figura 61: Componente SWITCH_TABLE da NSU                                                         | 89    |

| Figura 62: Componente Sw_Conf da NSU                                                              | 90    |

| Figura 63: Componente <i>MUX1</i> da NSU                                                          | 91    |

| Figura 64: Componente Rsp_Data da NSU                                                             | 92    |

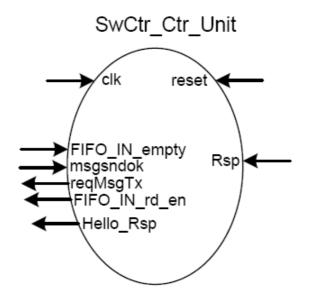

| Figura 65: Componente SwCtr_Ctr_Unit da NSU                                                       | 94    |

| Figura 66: Diagrama da máquina de estados finita SwCtr_Ctr_Unit                                   | 95    |

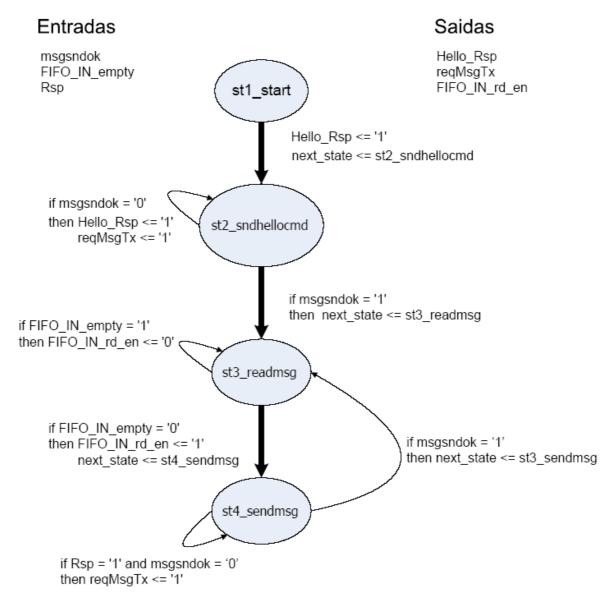

| Figura 67: Componente <i>CLK_Divider</i> da NSU                                                   | 97    |

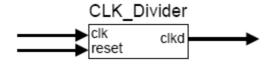

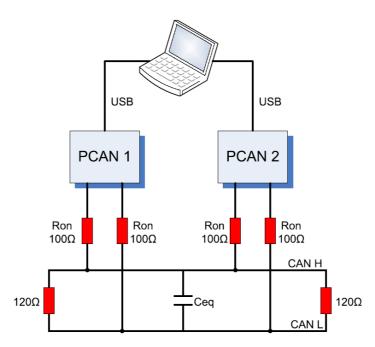

| Figura 68: Montagem utilizada no teste da NSU                                                     | 98    |

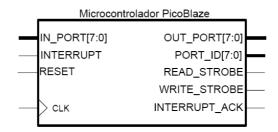

| Figura 69: Portas de interface do <i>PicoBlaze</i>                                                | . 102 |

| Figura 70: Exemplo da interface entre o <i>PicoBlaze</i> e o Controlador do CLAN                  | . 104 |

| Figura 71: Circuito de teste à abordagem híbrida hardware/software                                | . 106 |

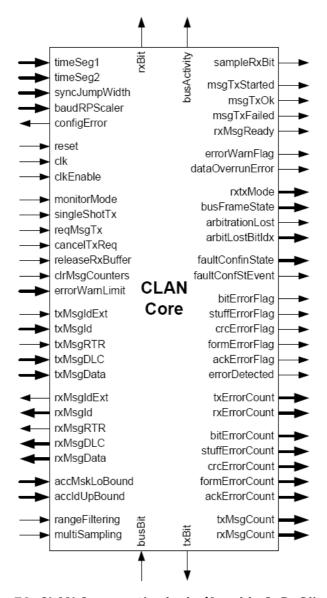

| Figura 72: CLAN Core                                                                              | . 113 |

| Figura 73: Montagem para o teste ao CLAN                                                          | . 114 |

| Figura 74: Módulo de interface do CLAN                                                            | . 115 |

| Figura 75: Ciclo de leitura e escrita do controlador                                              | . 116 |

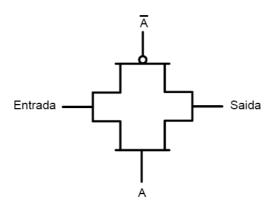

| Figura 76: CMOS Transmission Gate                                                                 | . 118 |

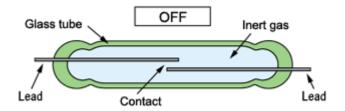

| Figura 77: Relé de palheta ou Reed Switch                                                         | . 120 |

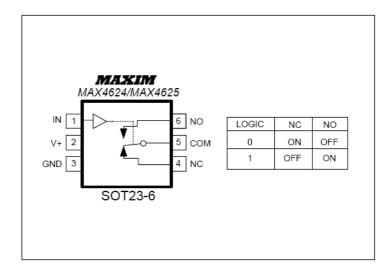

| Figura 78: Vista superior do componente MAX4624/MAX4625 e sua tabela da verdade                   | . 123 |

| Figura 79: Montagem utilizada no teste                                                            | . 125 |

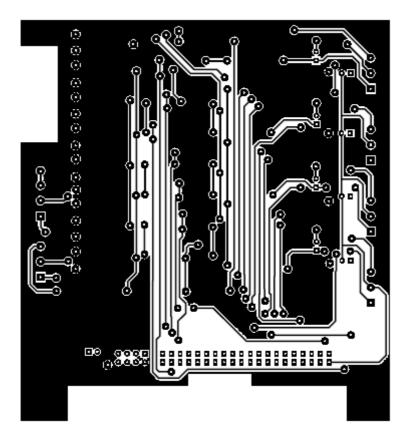

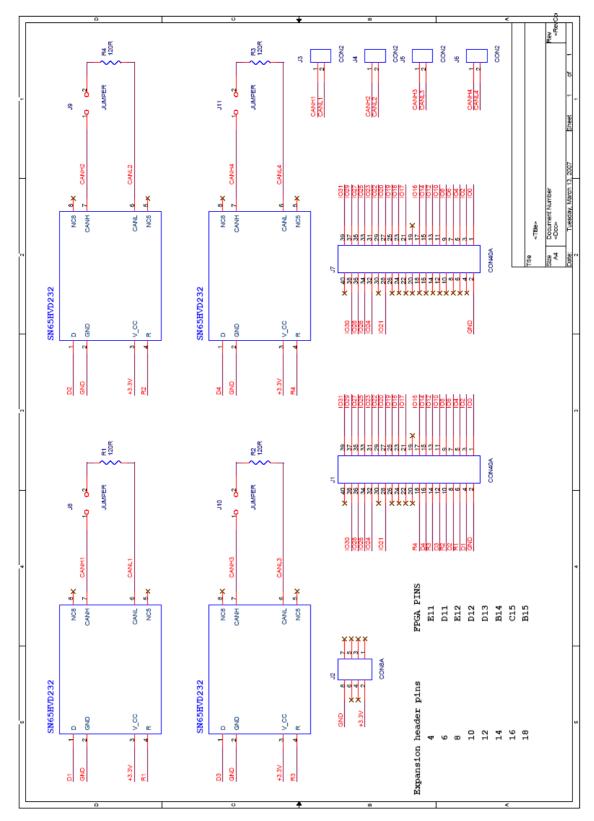

| Figura 80: Página 1 do circuito da Switch Matrix                                                  | . 129 |

| Figura 81: Página 2 do circuito da S <i>witch Matrix</i>                                          | .130  |

### LISTA DE FIGURAS

| Figura 82: Página 3 do circuito <i>Switch Matrix</i>                         | 131 |

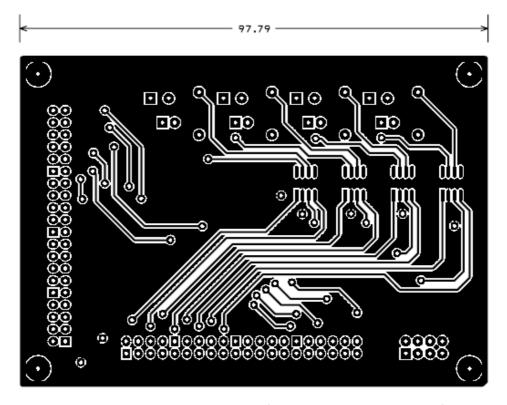

|------------------------------------------------------------------------------|-----|

| Figura 83: Face de "cima" da PCB (dimensões em milímetros)                   | 131 |

| Figura 84: Face de "baixo" da PCB                                            | 132 |

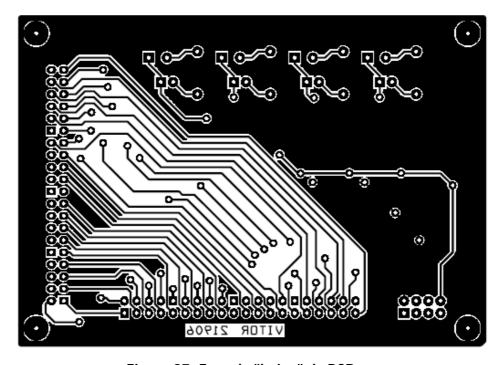

| Figura 85: Circuito da placa de interface da TMU                             | 134 |

| Figura 86: Face de "cima" da PCB (dimensões em milímetros)                   | 135 |

| Figura 87: Face de "baixo" da PCB                                            | 135 |

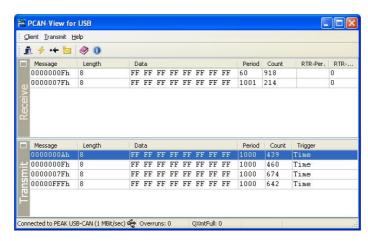

| Figura 88: <i>PCAN-View,</i> programa de monitorização ( <i>sniffer</i> CAN) | 137 |

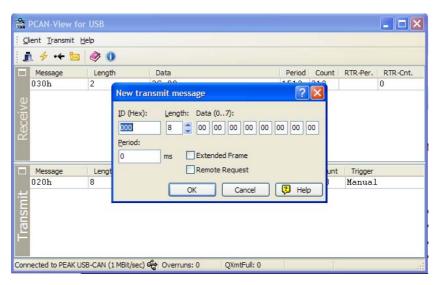

| Figura 89: Introduzir nova mensagem de transmissão no PCAN-View              | 138 |

| Figura 90: Exemplo de envio da mensagem SET_ADDRESS                          | 138 |

## Lista de Tabelas

| Tabela 1: Camada física - Topologia de interligação                                                 | 18     |

|-----------------------------------------------------------------------------------------------------|--------|

| Tabela 2: Camada física - Meio                                                                      | 19     |

| Tabela 3: Comparação entre <i>FlexRay</i> e CAN, ambos na sua forma nativa                          | 55     |

| Tabela 4: Comparação de algumas características das abordagens apresentadas                         | 60     |

| Tabela 5: Tabela da NSU                                                                             | 63     |

| Tabela 6:Descrição da função das portas de entrada e saída do módulo <i>I/O</i> da NSU              | 84     |

| Tabela 7:Descrição da função das portas de entrada e saída do FIFO                                  | 85     |

| Tabela 8: Descrição da função das portas de entrada e saída do componente <i>Msg_Data</i>           | 86     |

| Tabela 9: Descrição da função das portas de entrada e saída do componente <i>Msg_Control_U</i>      | nit.88 |

| Tabela 10: Descrição da função das portas de entrada e saída do componente ADDRESS                  | 89     |

| Tabela 11: Descrição da função das portas de entrada e saída do componente SWITCH_TABL              | E 90   |

| Tabela 12: Descrição da função das portas de entrada e saída do componente <i>Sw_Conf.</i>          | 91     |

| Tabela 13: Descrição da função das portas de entrada e saída do componente <i>MUX1.</i>             | 92     |

| Tabela 14: Descrição da função das portas de entrada e saída do componente <i>Rsp_Data</i>          | 93     |

| Tabela 15: Descrição da função das portas de entrada e saída da máquina de estados                  |        |

| SwCtr_Ctr_Unit                                                                                      | 96     |

| Tabela 16: Descrição da função das portas de entrada e saída do divisor de relógio <i>CLK_Divid</i> | er. 97 |

| Tabela 17: Relógios da RC10                                                                         | 112    |

| Tabela 18: Portas do módulo de interface                                                            | 116    |

| Tabela 19: Nome e endereço dos registos                                                             | 117    |

| Tabela 20: Dados da bobine fornecidos pelo fabricante                                               | 121    |

| Tabela 21: Nome e função de cada pino do componente                                                 | 123    |

| Tabela 22: Capacidade equivalente por comprimento do barramento                                     | 125    |

| Tabela 23: Correspondência entre os pinos do <i>header</i> de expansão e os pinos da FPGA           | 133    |

## Capítulo 1

## 1. Introdução

## 1.1. Enquadramento

Um sistema de controlo distribuído, tal como o próprio nome indica, possui seus elementos fisicamente distribuídos e interligados por uma rede de comunicação. Estes elementos, genericamente designados por nodos, podem estar ligados a sensores, ou actuadores, ou desempenhar funções de controlo. A comunicação e partilha de informação entre os nodos é feita por intermédio de redes de comunicação, que possuem para isso um protocolo que traduz um conjunto de regras que permitem a comunicação entre duas camadas homólogas (no mesmo nível). O modelo OSI, definido pela ISO (ISO, 1947), é um conjunto de protocolos abertos, desenvolvido para permitir a comunicação entre sistemas destinados a funcionar em rede.

Os sistemas distribuídos são frequentemente utilizados na indústria ou em sistemas embutidos que se podem encontrar nos automóveis, aviões, centrais de produção e distribuição de energia, etc. Nestes casos, os sistemas distribuídos são utilizados em aplicações de segurança crítica, uma vez que possuem restrições ao nível temporal na troca de mensagens entre os vários nodos que têm que ser cumpridas, caso contrário, pode resultar em graves danos materiais e no pior dos cenários na perda de vidas humanas.

Uma abordagem distribuída (ver Figura 1 a), possui vantagens em relação a uma abordagem centralizada (ver Figura 1 b), destacando-se a escalabilidade que permite um crescimento do sistema de acordo com as necessidades. No entanto, a distribuição das funcionalidades por vários nodos levanta também diversos desafios do ponto de vista da tolerância a falhas. Estes desafios, problemas e respectivas soluções têm sido um tópico de investigação muito importante e activo. Desafios estes, que se prendem com o facto de ser necessária uma grande

capacidade destes sistemas lidarem com alterações relevantes que podem afectar todo o seu funcionamento. Alterações relevantes compreendem desde nodos em falha, curto-circuito nos barramentos, particionamento da rede, entre outros, que podem afectar as comunicações e o correcto funcionamento do sistema. Assim, estes sistemas terão que ser robustos e flexíveis, através da utilização de mecanismos tolerantes a falhas, ao ponto de serem capazes de se adaptar a alterações na configuração para manter ou até melhorar o desempenho em cenários dinâmicos. O melhoramento de desempenho pode ser feito em sistemas de comunicação com redundância ao nível dos meios de comunicação, onde podem ser definidos barramentos dedicados à comunicação entre dois nodos, havendo assim uma melhor gestão da largura de banda.

Figura 1: a) Abordagem distribuída; b) Abordagem centralizada.

Alterações na configuração podem fazer com que ocorram erros de transmissão e consequente perda de mensagens, ou até conflitos de acesso ao meio de comunicação e dessincronização entre os vários nodos. É necessária portanto uma grande coordenação entre os vários nodos do sistema, para permitir uma reconfiguração dinâmica mantendo assim o sistema em funcionamento durante e após a adaptação. Contudo, em sistemas distribuídos existem vários

pontos de falha<sup>1</sup> que podem comprometer a coordenação do processo de adaptação e deixar todo o sistema inconsistente. São necessários portanto mecanismos de tolerância a falhas que permitam o correcto funcionamento do sistema na presença de falhas mesmo que isso implique o seu funcionamento num modo degradado.

O CAN – Controller Area Network (CiA, 2001-2008) é um dos standards mais utilizados na actualidade como infra-estrutura para sistemas de comunicação baseados em barramentos partilhados. Na sua forma nativa, o CAN possui vários pontos de falha e não determinismo temporal. Por este motivo têm vindo a ser feitos esforços para o tentar melhorar tendo em vista aumentar a sua fiabilidade e assim ser possível garantir que cumpra todos os requisitos para a sua aplicação em sistemas de segurança crítica. Uma característica do CAN que é desfavorável à sua aplicação em sistemas deste tipo é o facto da transmissão de mensagens ser baseada no paradigma event-triggered, não havendo por isso determinismo temporal. Assim, foi feita uma extensão ao protocolo CAN original tornando-o time-triggered (TTCAN) (CiA, 2001-2008). Com esta alteração foi possível a sua aplicação em sistemas de tempo-real do tipo crítico, que normalmente são sistemas de segurança crítica (por exemplo x-by-wire), onde é necessário assegurar que todas as mensagens cumprem as suas restrições temporais mesmo quando o barramento está sobrecarregado. Como o protocolo CAN suporta comunicações event-triggered, a extensão TTCAN permite combinar comunicações do tipo time-triggered e event-triggered em janelas temporais distintas.

Uma das características do CAN que deprecia a sua fiabilidade é o facto da sua topologia de rede ser baseada apenas num barramento (ver Figura 2). Assim sendo, os erros propagam-se pelo meio de transmissão que é comum a toda a rede, havendo a possibilidade de um nodo em falha afectar e até mesmo bloquear

<sup>&</sup>lt;sup>1</sup> Um ponto único de falha ou ponto crítico de falha é uma tradução vinda da língua inglesa da expressão *Single Point of Failure* (en:SPOF) para designar um local num sistema que, caso falhe, provoca a falha de todo o sistema.

todo o sistema. Como exemplo de falhas num barramento podemos ter cabos que se partem, curto-circuitos, nodos em falha, etc.

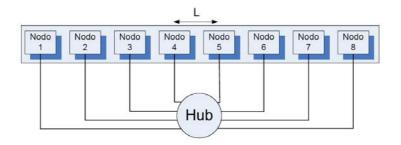

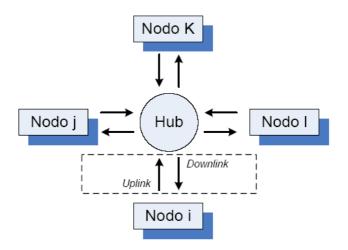

Figura 2: Barramento CAN, comunicação entre dois nodos.

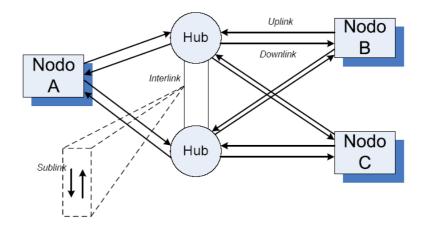

Na tentativa de melhorar o CAN original tendo em vista alterar a sua topologia de rede com apenas um ponto de falha, têm vindo a ser desenvolvidas algumas soluções baseadas na replicação de barramentos. Uma solução que já havia sido adoptada pela *Ethernet* (ISO, 2003), *FlexRay* (FlexRay, 2009) e *TTP/C* (TTA-Group, 1998), é a topologia em estrela que, para além da vantagem de ser possível replicar barramentos, possui também a vantagem de evitar falhas de proximidade, pois as ligações só ficam próximas umas das outras perto do *hub* central. Nesta topologia o barramento é seccionado e todos os nodos são ligados ao *hub* central através de ligações ponto-a-ponto. Isto permite evitar que nodos em falha comprometam todas as comunicações. Esta topologia pode ser aplicada ao CAN sendo completamente compatível com todos os controladores existentes. No entanto, nesta topologia o *hub* central pode representar um ponto de falha, sendo necessário replicar este componente, quando os requisitos de segurança assim o exijam, o que faz aumentar a sua complexidade.

Uma alternativa à topologia em estrela é combinar de forma flexível a simplicidade da topologia de barramento com a fiabilidade da topologia em estrela para que seja possível a sua aplicação com facilidade a cada situação em particular. Hoje em dia é dada muita importância à fiabilidade e a elevadas larguras de banda nos barramentos, pelo que são bastante apreciadas soluções que envolvam a replicação de barramentos e que satisfaçam ambas as exigências.

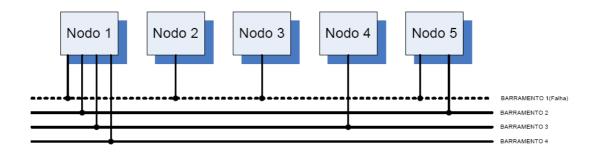

Dependendo da aplicação, é possível e relativamente simples implementar características que permitam gerir tolerância a falhas e usar a largura de banda para fazer transmissões redundantes de mensagens. É possível também reagir a falhas no barramento, permitindo a continuação da comunicação através da utilização dos barramentos disponíveis em ausência de falhas. Na Figura 3 está representado um pequeno exemplo de um barramento com 2-níveis de redundância.

Figura 3: Barramento com 2-níveis de redundância.

É assim possível transmitir tráfego não crítico e modificar durante o decorrer da transmissão o modo de operação para modos degradados na presença de falhas no barramento. Isto é feito na infra-estrutura da rede apenas, sem modificar os nodos do sistema distribuído (Silva, et al., 2006). A implementação ao ser feita na infra-estrutura da rede facilita a aplicação do sistema sem que seja necessário substituir ou modificar os nodos já existentes, sendo apenas necessário acrescentar o hardware necessário entre os nodos e os barramentos.

## 1.2. Motivação

A topologia de rede em estrela possui características importantes que permitem isolar falhas. Neste tipo de topologia um elemento central controla o fluxo de dados da rede, ficando ligado ponto-a-ponto a cada nodo. É esta característica que permite isolar um nodo em falha, evitando assim que o resto da rede seja afectada, permitindo assim a continuação de um bom funcionamento da

rede. Esta é uma das razões que tornaram esta topologia muito popular nas redes de campo<sup>2</sup>. No entanto, esta topologia tem a desvantagem de requerer maiores comprimentos de cabo para a implementar do que numa rede baseada em barramentos (Silva, et al., 2006). Mesmo colocando todos os nodos alinhados como num barramento, as ligações necessitam de mais cablagem, estas situações estão representadas na Figura 4 e Figura 5.

Figura 4: Topologia estrela circular - adaptado de (Silva, et al., 2006).

Figura 5: Topologia estrela em linha - adaptado de (Silva, et al., 2006).

A quantidade de cablagem necessária para implementar uma topologia de rede torna-se muito importante quando se pretende implementar replicação de

6

<sup>&</sup>lt;sup>2</sup> Classificação generalista utilizada para praticamente todas as redes industriais de dados. Visam a interligação de sensores, actuadores, placas de entrada/saída e sistemas de controlo local em instalações industriais.

barramentos para adicionar capacidades de tolerância a falhas, uma vez que o custo e complexidade aumentam com este parâmetro.

No caso específico do CAN a sua limitação em termos de largura de banda tem sido motivo de preocupação para o seu uso em aplicações, como por exemplo, em sistemas *X-by-wire* (Shaheen, et al., 2003). Replicação de barramentos pode adicionar maior largura de banda e fiabilidade. Para o caso específico do CAN é possível adicionar nodos com apenas uma ligação a um barramento ou com capacidade de ligação a barramentos replicados. Como se pode ver na Figura 6, numa rede com replicação de barramentos, uma falha num barramento tem consequências diferentes conforme o tipo de nodo. Considerando o caso demonstrado na Figura 6, caso o barramento 1 falhe, o nodo 1 vai funcionar com tripla replicação, o nodo 5 vai deixar de ter replicação e os nodos 2 e 3 ficam isolados da rede perdendo a capacidade de comunicar.

Figura 6: Rede com replicação de barramentos - adaptado de (Silva, et al., 2006).

Se a replicação for gerida ao nível da rede permite esconder todos os detalhes da gestão da replicação de quem desenvolve a aplicação. Além de facilitar o desenvolvimento de aplicações também providencia melhores propriedades de tolerância a falhas, pois a gestão de replicação é desenvolvida, acedida e validada por especialistas e usada por quem desenvolve as aplicações que muitas das vezes não está familiarizado com questões de tolerância a falhas.

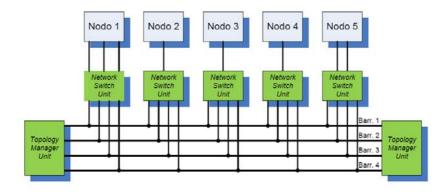

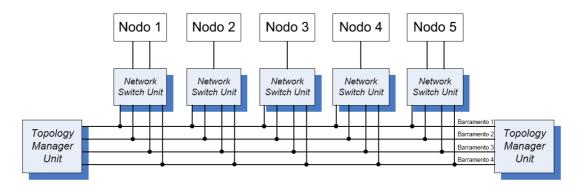

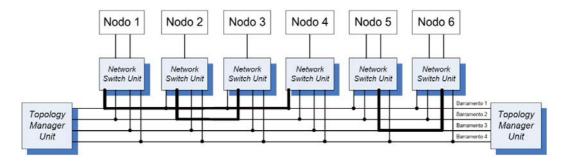

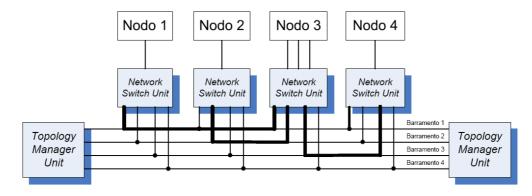

Na Figura 7 está representada a arquitectura proposta em (Silva, et al., 2006), designada por DTM - *Dynamic Topology Management*. Com esta arquitectura é possível montar uma rede que preserva todas as características do

CAN. Possui barramentos replicados, aumentando assim a largura de banda e permite a sua reconfiguração em caso de falha. O aumento da largura de banda é feito através da atribuição de barramentos dedicados à comunicação entre dois ou mais nodos, ficando ainda assim, barramentos livres para a comunicação entre os restantes nodos. Para gerir estas tarefas a arquitectura proposta possui dois tipos de componentes, uma NSU - Network Switch Unit e duas TMU - Topology Manager Unit. A TMU é responsável por definir a topologia usada em cada instante, fazendo isto através do envio de mensagens para a NSU indicando qual o barramento que o nodo deve usar para comunicar. Neste mecanismo os barramentos utilizados numa comunicação entre nodos podem ser comutados durante a transmissão caso seja detectada uma falha num deles. Além disso, esta operação é transparente para o nodo. Como se pode ver ainda na Figura 7, existem duas TMU sendo uma, réplica da outra. Esta replicação é necessária pois assim deixaremos de ter apenas um ponto de falha, começando uma TMU a funcionar em caso de avaria da outra. Esta replicação requer um protocolo para reforçar o determinismo e sincronismo em caso de falha na TMU activa.

Figura 7: Arquitectura de rede proposta - adaptado de (Silva, et al., 2006).

Com esta arquitectura é possível reagir a falhas permanentes no barramento e reconfigurar dinamicamente a topologia do sistema. Através da substituição de um barramento em falha é possível manter o sistema a funcionar correctamente, possivelmente com uma qualidade de serviço degradada. De notar, que numa situação limite a arquitectura de rede proposta pode ser

configurada como uma estrela virtual, sendo o nodo central o *hub*. Para tal é necessário que este nodo tenha tantas interfaces quanto o número de nodos com o qual vai comunicar.

## 1.3. Objectivos

O trabalho a realizar tem como principal objectivo a concepção, desenvolvimento e validação dos dois componentes da arquitectura DTM que permitem a gestão dinâmica de uma rede CAN com redundância, nomeadamente a NSU e a TMU. Este objectivo pode ser subdividido nas seguintes partes:

- Conceber e implementar uma TMU Topology Manager Unit. Este componente permite, entre outras funcionalidades, detectar falhas em barramentos redundantes e programar as NSUs para ligarem a interface do respectivo módulo a determinados barramentos. Este componente será implementado em lógica programável, numa placa de desenvolvimento que possui uma FPGA da Xilinx.

- Construir e ensaiar uma NSU Network Switch Unit. As NSUs recebem comandos provenientes da TMU e comutam as ligações consoante as instruções recebidas. Estes componentes também serão implementados em lógica programável.

- Desenvolver novas partes de hardware e adaptar um controlador CAN, o CLAN (Arnaldo S. R. Oliveira), já desenvolvido no DETI.

- Adaptar o controlador do CLAN, alterando algumas das suas características, para facilitar a sua interface com processadores de 8bits.

## 1.4. Organização da Dissertação

Além deste capítulo introdutório, esta dissertação é composta pelos seguintes capítulos:

- Capítulo 2 Sistemas Distribuídos Neste capítulo é feito um resumo de conceitos fundamentais sobre sistemas distribuídos. É introduzido o modelo OSI e apresentados os barramentos de campo como a infra-estrutura de comunicação normalmente utilizados em sistemas distribuídos de controlo. Finalmente é feita uma introdução aos sistemas de segurança crítica e de algumas técnicas de tolerância a falhas.

- Capítulo 3 Protocolo CAN Neste capítulo é feito um resumo das várias partes constituintes da camada lógica e da camada física do protocolo CAN.

- Capítulo 4 Tolerância a falhas em sistemas distribuídos de segurança crítica Neste capítulo é feito um resumo sobre o estado da arte com a apresentação de algumas abordagens, arquitecturas e protocolos pensados para a sua utilização em sistemas de segurança crítica. Algumas dessas abordagens, arquitecturas e protocolos foram pensados para melhorar a camada lógica e física do CAN do ponto de vista de tolerância a falhas, tornando-o mais adequado para aplicações em sistemas de segurança crítica.

- Capítulo 5 Gestão Dinâmica da Topologia em CAN Neste capítulo é feita uma descrição detalhada de todas as partes constituintes do sistema Gestão Dinâmica da Topologia em CAN e seus modos de operação. Este é o sistema utilizado como base deste trabalho.

- Capítulo 6 Implementação da NSU Neste capítulo é apresentada a arquitectura e descrito o desenvolvimento da NSU, como um dos módulos

constituintes do sistema apresentado no capítulo 5. É feita também uma apresentação das ferramentas utilizadas para este efeito.

- Capítulo 7 Implementação da TMU Neste capítulo é apresentado todo o hardware utilizado para implementar a TMU, um dos módulos constituintes do sistema DTM apresentado no capítulo 5.

- Capítulo 8 Conclusões Neste capítulo é resumido o trabalho apresentado nesta dissertação, bem como analisados os objectivos alcançados. São também apresentadas algumas possíveis direcções de trabalho futuro.

Os apêndices A e B possuem informação adicional sobre a implementação dos componentes NSU e TMU, partes constituintes do sistema apresentado no capítulo 5.

- Apêndice A Descrição detalhada da Implementação da NSU Neste apêndice é feita uma descrição adicional de algum hardware utilizado e projectado para a implementação da NSU.

- Apêndice B Descrição detalhada da Implementação da TMU Neste apêndice é feita uma descrição adicional de algum *hardware* utilizado e projectado para a implementação da TMU.

- Apêndice C Programa de monitorização PCAN Neste apêndice é feita uma apresentação da ferramenta utilizadas para monitorização de barramentos CAN, o PCAN-View. Um pequeno exemplo demonstra como é feito o envio de mensagens.

- Apêndice D Lista de Acrónimos Este apêndice possui a lista de acrónimos utilizados na dissertação.

## Capítulo 2

### 2. Sistemas Distribuídos

### 2.1. Conceitos Básicos

Num sistema distribuído os nodos, (sensores, controladores, actuadores, consola) estão fisicamente distribuídos por uma dada área. Para interligar estes elementos é necessária uma rede de comunicação, como por exemplo, um barramento de campo. No caso de o sistema de comunicação ser partilhado simplifica a cablagem e aumenta a flexibilidade do sistema. A troca de mensagens entre os vários elementos é, portanto, efectuada no mesmo sistema de comunicação. Na Figura 8 está representado um exemplo de uma abordagem distribuída para implementar um sistema de controlo baseado num barramento de campo.

Figura 8: Abordagem distribuída para o caso da topologia barramento.

Um nodo pode ser composto por um microprocessador, ou microcontrolador e um controlador de comunicações. O SLIO - *Serial Linked I/O P82C150* da *Philips* é um exemplo de um nodo que contém um microprocessador que prepara os dados a serem transmitidos para o barramento CAN e processa os dados recebidos do barramento CAN. Possui também um controlador CAN que cuida de todas as questões relacionadas com o protocolo CAN, nomeadamente a camada física e ligação de dados do modelo OSI (ver Figura 9). Um nodo pode ser

um componente inteligente e a sua utilização pode trazer alguns benefícios, tais como, a sua facilidade de configuração, teste e auto-verificação. Para além disso, pode acarretar menores custos de produção, maior facilidade de instalação e manutenção e também uma maior flexibilidade.

Existem algumas vantagens e desvantagens na abordagem distribuída relativamente a uma abordagem centralizada (Kopetz, 1997). Como vantagens temos as seguintes características:

- A extensibilidade do sistema que permite adicionar facilmente novos módulos ao sistema. Esta característica permite uma fácil evolução de um sistema, sempre que seja necessário adicionar-lhe novas propriedades ou funções;

- A composabilidade relativamente às propriedades dos nodos. É possível construir sistemas de dimensões consideráveis sem que haja incompatibilidades entre as propriedades específicas de cada nodo;

- O confinamento de erros aos vários nodos. É possível particionar a rede de comunicação de forma a criar zonas de confinamento de erros, sendo por isso mais fácil detectar a origem destes erros e corrigi-los antes que estes afectem o sistema. Numa abordagem centralizada é mais difícil definir uma zona de confinamento de erros porque muitos dos recursos do sistema estão multiplexados por vários serviços.

- A tolerância a falhas através da replicação de nodos ou meios de comunicação.

Como desvantagens temos as seguintes características:

Criticalidade do sistema de comunicação, que se deve aos erros de transmissão e consequente perda de mensagens, aos conflitos de acesso ao meio de comunicação e dessincronização entre os vários nodos;  A separação física impede que um nó tenha conhecimento do estado global do sistema num dado instante. Esta situação pode dar origem a atrasos indeterminados na comunicação e falhas.

### 2.2. Modelo OSI

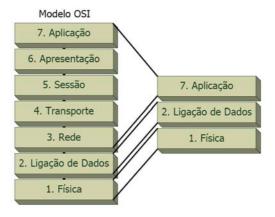

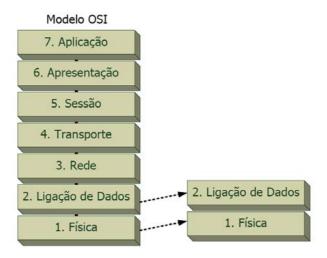

O modelo OSI – *Open Systems Interconnect* (ISO, 1947), foi formalmente definido pela organização ISO e consiste numa forma comum de conectar computadores. Esta arquitectura é um modelo que divide as redes de computadores em sete camadas, de forma a se obter camadas de abstracção. As várias camadas do modelo OSI estão representadas na Figura 9.

Figura 9: Camadas do modelo OSI.

Cada uma destas camadas presta um conjunto de serviços, baseada num conjunto de protocolos. Quando uma aplicação pretende enviar dados para uma outra aplicação, esses dados são entregues à camada *Aplicação*, camada 7, através dos serviços de comunicação existentes. Cada camada invoca os serviços da camada inferior fornecendo-lhe os dados com alguma informação de controlo adicionada. A camada física é responsável pelo envio dos dados. O sistema que

recebe os dados fá-lo por intermédio da camada física. Posteriormente, cada camada retira a informação de controlo respectiva e passa a restante à camada superior, até à camada *Aplicação*.

## 2.3. Barramentos de Campo

Designa-se por barramento de campo o sistema de comunicação que interliga os equipamentos ou nodos de um sistema de controlo distribuído, (e.g., sensores, actuadores, controladores, reguladores). Actualmente o *ProfiBus* (Profinet, 1989), o *WorldFIP* (WorldFip, 1993), o *P-Net* (IPUO, 1983), o *DeviceNet* (ODVA, 2008) e o CAN, são alguns dos barramentos de campo mais utilizados.

Em barramentos de campo as mensagens transferidas entre nodos contêm geralmente pequenas quantidades de informação organizada em bytes. O comportamento temporal é bem definido, ou seja, é possível determinar os atrasos de comunicação no pior caso. É necessário um esforço adicional de computação e de largura de banda para efectuar as várias operações entre as várias camadas do modelo OSI. Este esforço introduz atrasos inerentes ao processamento dos serviços em todas as camadas do modelo de referência, bem como da largura de banda com informação de controlo. Para reduzir este atraso os barramentos de campo costumam usar uma versão adaptada do modelo OSI (ver Figura 10).

Figura 10: Versão colapsada do modelo OSI aplicado a barramentos de campo.

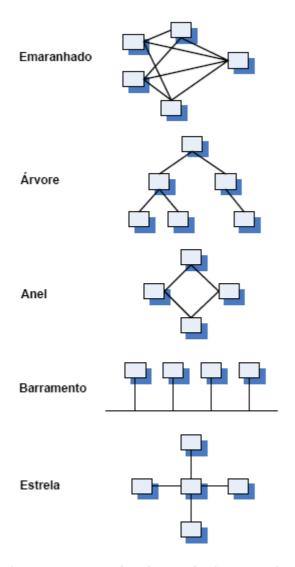

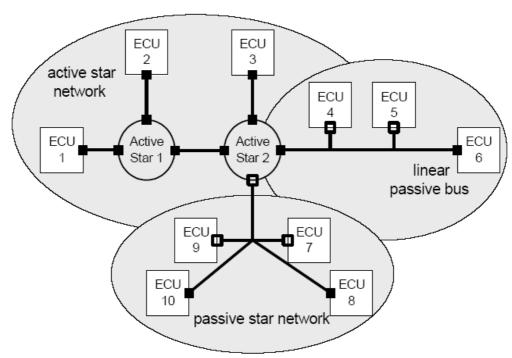

Existem várias topologias utilizadas em barramentos de campo, sendo as mais conhecidas a topologia em barramento, a topologia em anel, o emaranhado, a árvore e a estrela. Um pequeno esquema representativo de cada tipo de topologia pode ser visto na figura seguinte (ver Figura 11).

Figura 11: Exemplos de topologias genéricas.

Dependendo do tipo de aplicação a que cada uma destas topologias se destina pode haver vantagens e desvantagens ao nível das ligações, ao nível da cablagem e da tolerância a falhas. Na Tabela 1, estão apresentadas algumas vantagens e desvantagens de cada uma destas topologias de ligação.

| Topologia  | A favor                                                                                                                      | Contra                                                                                             |

|------------|------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| Emaranhado | Ligações ponto-a-ponto. Vários percursos alternativos.                                                                       | Necessidade de encaminhamento ( <i>routing</i> ). Interligações complexas e de difícil manutenção. |

| Árvore     | Ligações ponto-a-ponto.<br>Comunicação simultânea em<br>ramos paralelos. Isolamento<br>entre ramos.                          | Atrasos na comunicação entre<br>nodos em ramos distantes –<br>necessidade de encaminhamento.       |

| Anel       | Cablagem simplificada. Maior robustez em relação a erros de transmissão – facilidade de confirmação.                         | Ligações ponto-a-ponto mas usadas como meio partilhado - controlo do acesso ao meio mais complexo. |

| Barramento | Cablagem simplificada. Nodos comunicam directamente, não é necessário encaminhamento.                                        | Meio de comunicação partilhado - controlo do acesso ao meio mais complexo.                         |

| Estrela    | Maior tolerância a falhas devido<br>a não existir um meio<br>partilhado. Ligações ponto-a-<br>ponto. Isolamento entre ramos. | Necessita de um <i>hub</i> central.                                                                |

Tabela 1: Camada física - Topologia de interligação - adaptado de (Almeida, 2001).

Ao nível do meio de comunicação, as várias tecnologias utilizadas podem ter vantagens ou desvantagens dependendo da aplicação a que se destina. Na tabela seguinte, Tabela 2, estão apresentadas algumas vantagens e desvantagens das várias tecnologias utilizadas no meio de comunicação, camada física.

| Tipo de meio      |                     | Vantagens                                                    | Desvantagens                                             |

|-------------------|---------------------|--------------------------------------------------------------|----------------------------------------------------------|

| Cablagem de cobre |                     | Interfaces e cabos baratos.                                  | Sensível a interferências electromagnéticas (EMI).       |

| Fibra óptica      |                     | Imune a EMI, baixa<br>atenuação, grande largura de<br>banda. | Interfaces e cabos caros.                                |

| Sem fios          | Infra-<br>vermelhos | - Mobilidade.                                                | Nodos em "linha de vista",<br>sensível a interferências. |

|                   | Rádio<br>frequência |                                                              | Sensível a interferências.                               |

Tabela 2: Camada física - Meio.

Em termos de ligação de dados, o acesso ao meio pode ser controlado ou não. No caso de o acesso ser controlado, existe uma forma acordada de controlo para acesso ao meio que determina quando é que cada nodo pode transmitir, por exemplo, mestre-escravo (*master-slave*), testemunho (*token*). No caso do acesso não controlado, cada nodo inicia a transmissão assim que a respectiva aplicação assim o determina. Existem métodos que resolvem as colisões que ocorrem, por exemplo, o CSMA-CD — *Carrier Sense Multiple Access with Collision Detection* ou o CSMA-DCR — *Carrier Sense Multiple Access with Deterministic Collision Resolution*. Para fazer o escalonamento do tráfego é utilizada a arbitragem como método para resolver conflitos no acesso ao meio. Como exemplos de sistemas de comunicação onde são utilizados métodos de arbitragem temos, o WorldFIP (WorldFip, 1993) onde a arbitragem é centralizada e o escalonamento qualquer, o CAN onde a arbitragem é distribuída (CSMA-DCR) com escalonamento por prioridades fixas.

# 2.4. Segurança Crítica

Os sistemas de segurança crítica são assim designados por várias razões, de entre as quais, o consequente prejuízo elevado em caso de falha, apertadas restrições sobre a utilização de recursos e os ambientes onde operam que são perigosos. Como consequência de tais factores, estes sistemas são obrigados a operar numa margem muito estreita de erro. Para além disso, o tempo disponível para tomar acções correctas no caso de haver uma falha em sistemas tempo-real pode ser extremamente limitado, especialmente nas fases mais críticas. Uma falha grave num sistema deste tipo pode resultar na morte ou ferimentos graves em

pessoas, estragos ou perda completa de equipamento ou até mesmo numa tragédia ambiental. Quando do bom funcionamento do sistema dependem vidas humanas, a probabilidade de falha para o qual o sistema é projectado pode chegar a  $10^{-10}$  por cada hora de funcionamento, (Nissanke, cop. 1997 p. 323).

O desenvolvimento de sistemas de segurança crítica começa com o reconhecimento de que a segurança é um objectivo muito importante a ser considerado ao nível do sistema, que não deve ser desvalorizado a favor de outros objectivos do projecto e poupança na tentativa de redução do custo final. Assim, um sistema de segurança crítica deve ter os seguintes atributos: disponibilidade, fiabilidade, segurança, confidencialidade e integridade. Segundo (Nissanke, cop. 1997 p. 311), o desenvolvimento de sistemas de segurança crítica começa também por definir o que é a segurança crítica, isto envolve:

- a) Identificar os riscos, (perigos), envolvidos.

- b) O que é que a segurança significa em termos de comportamentos indesejados do sistema. Estes devem ser explicitamente identificados nas especificações pretendidas e são referidas como requerimentos de segurança.

- c) Com que rigor devem ser observados os requisitos de segurança. Estes requisitos devem ser expressos através de critérios probabilísticos reflectindo parcialmente os vários níveis de risco.

- d) O que a segurança significa em termos de quantificação das perdas em caso de falha.

Os requisitos c) e d) juntos constituem o que normalmente se chama de "risco". Assim, grandes provisões de riscos reflectem em custos elevados devido a uma elevada antecipação da probabilidade de falha.

O objectivo das medidas que se tomam no que respeita a tolerância a falhas, no contexto de sistemas de segurança crítica, é localizar os efeitos de falhas para que o desempenho de todo o sistema não seja afectado por falhas em pequenos componentes e que o sistema falhe em segurança em caso de falha em

componentes de maior importância. A complexidade de tais mecanismos em função do grau de tolerância a falhas, criticalidade do sistema, definem o rácio custo-eficácia na altura do projecto e desenvolvimento de tais sistemas.

## 2.5. Tolerância a Falhas

Tolerância a falhas é uma propriedade que permite que um sistema continue a funcionar normalmente, ou num modo degradado, mesmo após falhas em alguns dos seus componentes. Esta propriedade está associada a sistemas de segurança crítica e sistemas de alta disponibilidade. É possível aplicar as técnicas de tolerância a falhas ao nível da arquitectura (tolerância a falhas sistemática), e ao nível da aplicação (tolerância a falhas especifica da aplicação). A tolerância a falhas sistemática permite diminuir a complexidade da aplicação, transferindo-a, para hardware e software adicionais.

Um nodo de um sistema distribuído pode ser considerado um ponto de falha do sistema. Para dar a volta a este problema é possível utilizar a redundância ao nível do nodo, através da replicação deste elemento. Existem várias técnicas relacionadas com tolerância a falhas em sistemas distribuídos baseados em nodos como pontos de falha. O controlo de presença é uma técnica que permite saber quais os nodos operacionais, utilizando para isso uma *flag* num registo que é activada periodicamente. A gestão da redundância é uma outra técnica que efectua a detecção de discrepâncias entre as saídas de nodos replicados e controla a entrada e saída de funcionamento das réplicas.

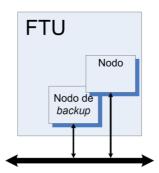

Quando se incorporam técnicas de tolerância a falhas ao nível do nodo é necessário utilizar unidades tolerantes a falhas (*FTUs – Fault-Tolerant Units*). Estas unidades funcionam da mesma forma que o nodo base, mas possuem serviços suplementares que lhes permitem ter um certo nível de tolerância a falhas.

Existem vários tipos de falhas com que as FTU têm de lidar, nomeadamente:

- Falhas do tipo falha-silêncio;

- Falhas do tipo falha-pára ou falha-consistente;

- Falhas do tipo falha-inconsistente (maliciosa ou bizantina).

De seguida será feita a descrição de cada um destes tipos de falha.

## 2.5.1. Falhas do Tipo Falha-Silêncio

Falhas do tipo falha-silêncio, são falhas que quando ocorrem, o nodo ou fornece respostas correctas ou então simplesmente não responde. Quando o nodo base de uma FTU só apresenta falhas do tipo falha-silêncio, é necessário no mínimo a utilização de dois nodos (ver Figura 12). No caso de um dos nodos falhar o outro continua a responder.

Figura 12: FTU tolerante à falha do tipo falha-silêncio com dois nodos - adaptado de (Almeida, 2001).

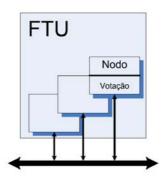

# 2.5.2. Falhas do Tipo Falha-Pára ou Falha-Consistente

Falhas do tipo falha-pára ou falha-consistente, são falhas onde o nodo, após a ocorrência de uma falha, pode continuar a enviar um valor errado mas

consistente. Neste caso são necessários três nodos na FTU e um mecanismo para determinar de entre as três saídas a que está correcta, (*TMR – Triple Modular Redundancy*) (ver Figura 13).

Figura 13: FTU com três nodos e mecanismo de votação TMR - adaptado de (Almeida, 2001).

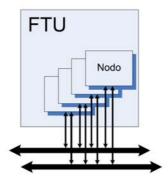

# 2.5.3. Falhas do Tipo Falha-Inconsistente (maliciosa ou bizantina)

Falhas do tipo falha-inconsistente (maliciosa ou bizantina), são falhas em que o nodo, após uma falha, pode continuar a produzir valores errados e inconsistentes. Neste caso é necessário utilizar quatro nodos e um protocolo que permita determinar qual o nodo que está a produzir um valor errado (ver Figura 14). Com este protocolo todos os nodos da FTU trocam mensagens entre si com o valor das respectivas saídas, (*Byzantine-Resilient Agreement Protocol*).

Figura 14: FTU com quatro nodos e protocolo (*Byzantine-Resilient Agreement Protocol*) – adaptado de (Almeida, 2001).

# Capítulo 3

## 3. O Protocolo CAN

## 3.1. Introdução

O protocolo CAN - Controller Area Network (CiA, 2001-2008), conta já com 22 anos de existência, foi apresentado pela primeira vez no congresso "Society of Automotive Enginners (SAE)" por Robert Bosch GmbH. Não será com certeza um exagero dizer que é hoje em dia um dos mais bem sucedidos protocolos de barramentos de campo. Foi inicialmente desenvolvido para a indústria automóvel para suportar comunicações de baixo nível entre módulos, (por exemplo, nos sistemas de travagem como o ABS - Anti-lock Braking System, ou nos sistemas de estabilidade como o ESC - Electronic Stability Control, mas hoje em dia é também usado noutros tipos de veículos tais como, comboios, aviões, navios, entre outros. O sucesso da utilização do CAN deve-se ao baixo preço dos controladores que são produzidos em grande quantidade e às suas características técnicas que o tornam relativamente fiável. A utilização do CAN em aplicações de segurança crítica não pode ser feita utilizando-o na sua forma nativa. Por exemplo em sistemas de segurança critica como o x-by-wire, normalmente utilizados nos automóveis, é necessário utilizar redundância e características que permitem ao sistema falhar de uma forma segura (Touloupis, et al., 2003).

O CAN é baseado na topologia barramento e utiliza o mecanismo de acesso ao meio CSMA/DCR para resolver as colisões. A transmissão de dados no CAN é feita através de um modelo binário de bits "dominantes" e "recessivos" onde o dominante representa o estado lógico '0' e o recessivo representa o estado lógico '1'. O controlo do acesso ao meio por parte dos nodos é feito utilizando um sistema de arbitragem que utiliza este modelo binário de bits "dominantes" e "recessivos". Durante o processo de arbitragem, o nodo que pretende aceder ao

barramento para transmitir, "escuta" o barramento e compara o valor do bit que está a tentar transmitir com o valor presente no barramento. Se no barramento estiver presente um valor dominante, isto significa que outro nodo está a transmitir uma mensagem de maior prioridade e o nodo que estava a tentar aceder ao barramento perde a arbitragem. Para evitar a omissão ou perda da mensagem, o nodo atrasa a transmissão até haver outra arbitragem.

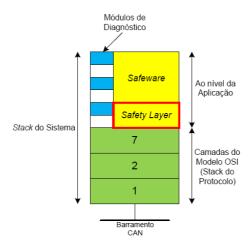

O protocolo CAN define duas camadas do modelo OSI, a camada dois, ligação de dados, e parte da camada um, camada física (ver Figura 15).

Figura 15: Camadas do modelo OSI utilizadas pelo CAN.

Existem especificações standard definidas pela ISO para o CAN, como por exemplo a ISO 11898-1:2003 que especifica a camada de dados e as sinalizações físicas para um protocolo de comunicações série que suporta controlo tempo-real e multiplexagem para uso em veículos (ISO, 2003).

A troca de informação entre nodos CAN é feita através de tramas que possuem um identificador que pode ter 11 bits num formato base e 29 bits num formato extendido. O campo de dados das tramas é de tamanho variável e pode variar de 0 até 8 bytes (ver Figura 17). O identificador da trama define a prioridade da mensagem durante o processo de arbitragem e informa os restantes nodos da rede sobre o conteúdo desta mensagem. As tramas não possuem informação sobre o destinatário, sendo enviadas para todos os nodos, logo cada nodo tem que decidir quais as tramas que lhes interessam. Desta forma os nodos

recebem as tramas em simultâneo e podem tomar acções sobre a mesma mensagem. O identificador de uma trama é produzido apenas por um nodo na rede, sendo portanto original e específico do nodo em questão.

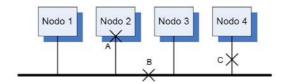

Muitos dos problemas de fiabilidade do CAN estão directamente relacionados com a sua topologia de rede. O principal problema provém do facto de existir apenas um barramento, que representa um único ponto de falha, onde estão electricamente ligados vários nodos entre si sem que haja um adequado confinamento de erros. Um nodo que, por algum motivo, comece a gerar erros vai comprometer as comunicações até que o contador de erros exceda um determinado valor. Na Figura 47, na página 68, no caso A está representado um exemplo deste tipo de falha onde, por exemplo, um nodo transmite para o barramento um valor de bit fixo bloqueando assim as comunicações entre os restantes nodos. Outra situação que pode ocorrer está representada na Figura 47, caso B, onde um possível corte no meio de comunicação divide o barramento, criando assim uma partição, isolando os nodos um e dois dos nodos três e quatro. O último caso, caso C, representa uma falha no meio de comunicação entre o nodo e o barramento. Este tipo de falha isola o nodo da restante rede mas não faz com que as comunicações entre os restantes nodos terminem. Este tipo de falha é a que menos impacto tem nas comunicações.

## 3.2. Camada Lógica

Nos subcapítulos seguintes será descrito o princípio da arbitragem e o formato das tramas no CAN.

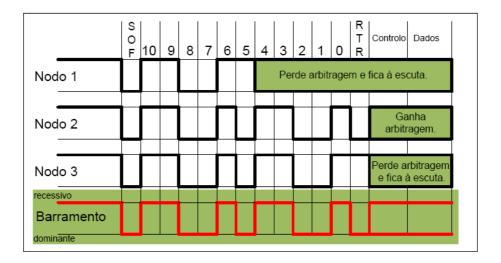

## 3.2.1. Arbitragem no Acesso ao Barramento

Uma vez que no CAN o barramento é partilhado, é necessário haver um mecanismo de controlo de acesso ao meio que evite colisões. O CAN utiliza o CSMA-DCR - *Carrier Sense Multiple Access with Deterministic Collision Resolution*. Quando vários nodos começam a transmitir simultaneamente, apenas o nodo que estiver a transmitir a mensagem com maior prioridade ganha o acesso ao barramento. Este processo de arbitragem é não destrutivo, ou seja, nenhuma trama é destruída, não havendo por isso necessidade de retransmissões.

Na fase de arbitragem (ver Figura 16) os nodos concorrentes transmitem cada um o identificador da sua mensagem bit a bit, verificando ao mesmo tempo se o nível presente no barramento corresponde ao nível que está a ser transmitido. Quando um nodo encontra um nível no barramento diferente ao que está a ser transmitido, então ele perde o acesso ao barramento porque outro nodo está a transmitir uma mensagem de maior prioridade. Todos os nodos que perdem o acesso, tornam-se automaticamente receptores da mensagem com a maior prioridade.

Existem dois formatos para as mensagens CAN, o chamado "base format" que possui 11bits no campo do identificador e o "extended format" com 29 bits no identificador. No caso de dois nodos concorrerem ao acesso ao barramento para transmitir uma mensagem, uma com identificador de 11bits e outra com identificador de 29bits, mas ambas com identificador de base iguais, ganha sempre o acesso ao barramento o nodo que pretende enviar a mensagem com identificador de 11bits. É esta a forma que o protocolo tem de resolver colisões entre mensagens com identificadores base iguais.

Figura 16: Exemplo de um processo de arbitragem de acordo com o protocolo CAN - adaptado de (CiA, 2001-2008).

#### 3.2.2. Tramas CAN

O protocolo CAN define os seguintes quatro tipos de trama:

- Trama de dados (*Data frame*)

- Trama pedido de transmissão (*Remote frame*)

- Trama de sinalização de erro (*Error frame*)

- Trama de sinalização de sobrecarga (*Overload frame*)

De seguida será feita a descrição de cada um dos tipos de trama.

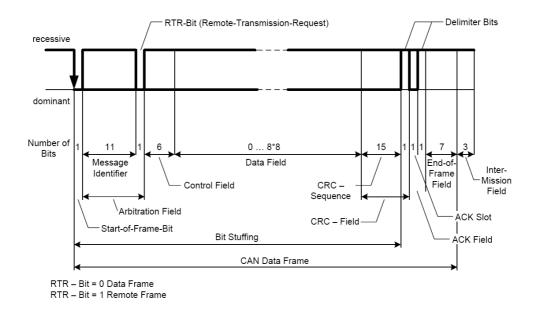

#### 3.2.2.1. Trama de Dados

Na Figura 17 está representada uma trama de dados que consiste nos seguintes campos: SOF - *Start-of-Frame*, Arbitragem (*Arbitration Field*), Controlo (*Control Field*), Dados (*Data Field*), CRC - *Cyclic Redundant Check*, ACK - *Acknowledgement* e EOF - *End-of-Frame*. O campo de dados é opcional podendo ter entre 0 e 8 bytes. O campo EOF - *End-Of-Frame Flag* sinaliza o final da trama de dados e é constituído por uma sequência de sete bits no estado recessivo.

Figura 17: Formato da trama de dados e trama remoto (formato base) - adaptado de (Etshberger, 2001).

Bit de inicio de trama (Start-of-Frame Bit):

Este bit marca o início de uma trama de dados ou trama de pedido de transmissão (*Remote Frame*), sendo representado por apenas um bit dominante. Só é permitido a um nodo iniciar a arbitragem quando o barramento está livre.

#### Campo arbitragem (*Arbitration Field*):

Na Figura 18, está representado o campo de arbitragem numa trama CAN. Este campo é composto pelo identificador e o bit RTR. No formato base, o identificador possui apenas 11bits, o que permite 2048(2<sup>11</sup>) tramas diferentes. As tramas de dados e as tramas de pedido de transmissão são diferenciadas pelo bit RTR. Para que as tramas de dados sejam mais prioritárias que as tramas de pedido de transmissão, o bit RTR de uma trama de dados é transmitido no estado

dominante (valor lógico 0), enquanto numa trama de pedido de transmissão o bit RTR é transmitido no estado recessivo (valor lógico 1).

Figura 18: Formato do campo arbitragem - adaptado de (Etshberger, 2001).

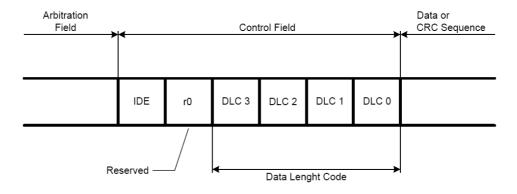

#### Campo de controlo (Control Field):

O campo de controlo (ver Figura 19) possui seis bits incluindo o DLC, de acordo com as especificações do CAN 2.0 B. O primeiro bit deste campo, *identifier extension bit* (IDE), permite fazer a distinção entre os formatos "base" ou "extended". No formato base o IDE Bit é transmitido no estado dominante. O segundo bit, r0, está reservado para futuras expansões do CAN e é transmitido no estado dominante. Os últimos quatro bits deste campo, conhecidos como *data lenght code* (DLC), permite definir quantos bytes de dados estão a ser transmitidos.

Figura 19: Formato do campo de controlo - adaptado de (Etshberger, 2001).

#### Campo de dados (Data Field):

Este campo contém os dados a transmitir numa trama CAN. Os dados podem ir desde 0 a 8 bytes, sendo os bits mais significativos os primeiros a ser transferidos.

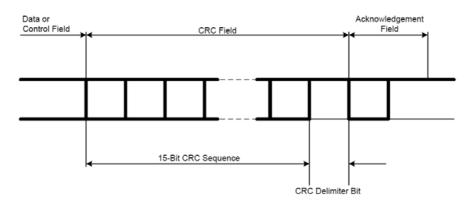

#### Campo CRC (CRC Field):

Este campo permite ao nodo receptor verificar se os dados estão corrompidos ou não. Com este método é possível garantir uma grande probabilidade na detecção de erros. O campo CRC consiste numa sequência de 15bits mais um bit CRC que serve como delimitador (ver Figura 20).

Figura 20: Formato do campo CRC - adaptado de (Etshberger, 2001).

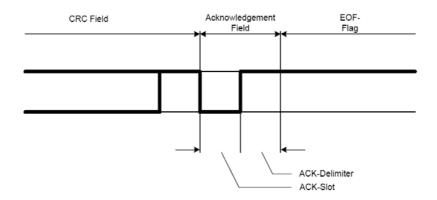

#### Campo de reconhecimento (Acknowledgement Field):

Este campo é constituído por um ACK-*Slot - Acknowledgement Slot* de dois bits de reconhecimento. O primeiro dos bits é um *slot* de reconhecimento e o segundo um delimitador (ver Figura 21).

Figura 21: Formato do campo acknowledgement - adaptado de (Etshberger, 2001).

Estes dois bits de reconhecimento são transmitidos com alta prioridade por um nodo transmissor, que depois aguarda a confirmação do reconhecimento da trama transmitida por pelo menos um dos nodos receptores. O nodo receptor que receber uma trama correctamente, sem erros, reporta ao transmissor o envio bem sucedido, sobrepondo o bit no estado recessivo enviado pelo transmissor pelo estado dominante durante o *slot* de reconhecimento.

#### 3.2.2.2. Trama Remoto

Com este tipo de trama é possível requisitar dados a um determinado nodo. O bit RTR define se a trama é de dados ou se é uma trama de requisição de dados, ou seja, se o bit RTR da trama estiver a um (RTR-Bit = 1) trata-se de uma trama remoto, se o bit RTR estiver a zero (RTR-Bit = 0) então trata-se de uma trama de dados. Esta diferença no nível do bit RTR permite em caso de colisão de duas tramas com o mesmo identificador na fase de arbitragem, que a trama de dados seja mais prioritária vencendo assim a arbitragem. Para além da diferença do estado do bit RTR, as tramas remoto diferem também das tramas de dados no campo de dados, pois este campo não existe neste caso.

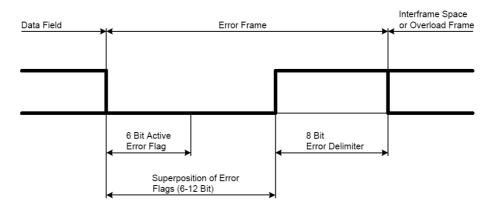

#### 3.2.2.3. Trama de Sinalização de Erro

No protocolo CAN, uma sequência de bits com mais de cinco bits de igual valor, numa trama de dados ou trama remoto, é considerada uma trama de sinalização de erro. Esta sequência viola a regra da técnica *bit stuffing* (técnica descrita na subsecção 3.3.1) obrigando assim o transmissor a repetir a transmissão. Uma trama de sinalização de erro é constituída por dois campos, o campo "*error flag*" e o campo "*error delimiter*" (ver Figura 22). A detecção de erros numa trama de erro ou trama de sobrecarga obriga a uma nova transmissão de uma trama de sinalização de erro.

Figura 22: Formato de uma trama de erro activo - adaptado de (Etshberger, 2001).

A *flag* de erro (*Error Flag*) pode ter as duas formas seguintes, *flag* de erro activo ou *flag* de erro passivo. Como se pode ver na Figura 22, a *flag* de erro activo consiste numa sequência de seis bits dominantes. A *flag* de erro passivo consiste numa sequência de seis bits recessivos, caso não tenham sido sobrepostos por bits dominantes de outros nodos.

Após a transmissão de uma *flag* de erro, cada um dos nodos envia bits no estado recessivo e monitora o nível de barramento até detectar um bit recessivo. Quando o bit no estado recessivo é detectado, o nó inicia a transmissão de mais sete bits no estado recessivo. Este campo, "*error delimiter*", indica se foi o nodo o primeiro a detectar o erro.

#### 3.2.2.4. Trama de Sinalização de Sobrecarga

É composta por um campo "overload flag" e um campo "overload delimiter". Este tipo de trama é utilizado por um nodo receptor para pedir um atraso no envio da próxima trama de dados ou trama de pedido de transmissão, ou quando o receptor detecta um bit dominante no ultimo bit do delimitador de fim de trama.

## 3.3. Camada Física

Nas subsecções seguintes serão descritas algumas características da camada física do CAN, tais como, a codificação dos bits, a temporização dos bits e sincronização, a interdependência entre taxa de transmissão e comprimento do barramento, o meio físico e os parâmetros do meio físico.

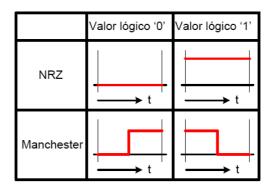

## 3.3.1. Codificação dos Bits

O método utilizado para a codificação dos bits em CAN é o NRZ - Non-Return-to-Zero (CiA, 2001-2008). Como se pode ver na Figura 23, com a codificação NRZ o sinal fica constante durante o tempo de bit, ao contrário da codificação Manchester, o que pode ser uma vantagem uma vez que aumenta a imunidade ao ruído. O facto de o sinal ficar constante durante o tempo de bit faz com que não haja uma mudança de estado no barramento para cada bit transmitido, o que dificulta a sincronização entre os nodos. No caso de uma sequência de bits iguais (recessivos ou dominantes), os nodos podem ter dificuldades na sincronização uma vez que podem não conseguir reconhecer os limites dos bits. Para ultrapassar este problema é utilizada uma técnica chamada bit stuffing que permite uma melhor sincronização das mensagens por parte dos nodos receptores. Quando o transmissor pretende enviar uma sequência de cinco bits de igual valor, introduz na mensagem um bit de valor complementar a sequir