# **UNIVERSITY OF THESSALY**

# DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

# Temporospatial Organization of Circuits and Tasks over the Cloud.

by

Panagiotis Oikonomou

A thesis submitted in fulfilment of the requirements for the degree of Ph.D.

Volos, July 2017

**ACKNOWLEDGEMENTS**

Firstly, I would like to express my sincere gratitude to my advisor Prof. Georgios

Stamoulis for the continuous support of my Ph.D study and related research, for his

patience, motivation, and immense knowledge. His guidance helped me through all the

time of my research and the writing of this thesis. I could not have imagined having a

better advisor and mentor for my Ph.D study.

Besides my advisor, I would like to thank the rest of my thesis committee: Asst Prof.

Aspasia Daskalopoulou and Asst Prof. Elpiniki Papageorgiou for their insightful

comments and encouragement which assisted me in widening my research interests.

I am also grateful to the members of my committee for their patience and support in

overcoming numerous obstacles I have faced throughout my research. Furthermore, I

would like to express my gratitude to the staff of University of Thessaly and especially to

the Depts. of Electrical and Computer Engineer and Computer Science where I have

found an intimate environment manned by magnificent researchers.

Finally, I would like to thank my family: my mother, my father and my sister for

supporting me spiritually throughout writing this thesis and my life in general.

This thesis is dedicated to:

My mother

11

#### ΠΕΡΙΛΗΨΗ ΤΗΣ ΔΙΑΤΡΙΒΗΣ

# Χουνοχωρική Οργάνωση Διεργασιών και Κυκλωμάτων σε Υπολογιστικό Νέφος

Η ταχεία και συνεχιζόμενη ανάπτυξη των υπολογιστικών συστημάτων έχει αλλάξει τον τρόπο με τον οποίο οι ερευνητές αντιμετωπίζουν τα προβλήματα ελαχιστοποίησης της κλάσης NP-hard. Οι απαιτήσεις των χρηστών για ταχύτερες ηλεκτρονικές συσκευές και πιο ποιοτική εμπειρία στο διαδίκτυο επηρεάζουν όλο και περισσότερο τις σύγχρονες αρχιτεκτονικές υπολογιστών και δικτύων ενώ οδηγεί στην επίλυση νέων προβλημάτων (βελτιστοποίησης). Οι λύσεις σε τέτοια προβλήματα μπορεί να έχουν σημαντικές ομοιότητες και διαφορές σχετικά με τις χρησιμοποιούμενες τεχνικές, καθώς και στο γενικό πλαίσιο στο οποίο έχει τεθεί το πρόβλημα. Για παράδειγμα, το πρόβλημα του ΙC placement εμφανίζει χωρικές πτυχές, ενώ ο χρονοδρομολόγηση εργασιών σε υπολογστικό νέφος αποτελείται από χρονικά χαρακτηριστικά. Στην παρούσα Διατριβή προτείνουμε και αξιολογούμε αποτελεσματικές εναλλακτικές λύσεις και στις δύο κατευθύνσεις (χωρικές και χρονικές) με στόχο την ελαχιστοποίηση του χρόνου εκτέλεσης, τη βελτίωση των λύσεων και τη ταυτόχρονη μείωση της κατανάλωσης ενέργειας και της διαδικτυακής κίνησης.

#### **ABSTRACT**

# Temporospatial Organization of Circuits and Tasks over the Cloud

The rapid and on-going spread of computational systems has changed the way that researchers tackle minimization problems of NP-hard class. Users demand on faster electronic devices and better online experience increasingly affects modern computer and network architectures while it triggers new (optimization) problems to be solved. Solutions to such problems may have substantial similarities and differences regarding the techniques which are used as well as the general framework in which the problem is set. For instance, IC placement problem exhibit spatial aspects while Cloud scheduling consists of temporal ones. In this thesis we propose and evaluate efficient alternatives to both directions (spatial and temporal) under the objective to minimize running time, to improve solutions quality and to reduce simultaneously energy consumption and internode network traffic, while meeting the quality requirements.

#### TABLE OF CONTENTS

| TABLE        | OF CONTENTS                                       | V   |

|--------------|---------------------------------------------------|-----|

| LIST OF      | F FIGURES                                         | VII |

| LIST OF      | TABLES                                            | IX  |

| 1. IN        | TRODUCTION                                        | 10  |

|              | OBJECTIVES AND CONTRIBUTION OF THE THESIS         |     |

| 1.1.<br>1.2. | CONTRIBUTIONS                                     |     |

| 1.2.         | OUTLINE                                           |     |

|              | ACEMENT IN ELECTRONIC DESIGN AUTOMATION           |     |

| 2.1.         | OVERVIEW                                          |     |

|              | -                                                 |     |

|              | N FORMULATING AND TACKLING IC PLACEMENT AS A SO   |     |

| PROBL        | EM                                                |     |

| 3.1.         | MOTIVATION                                        | 20  |

| 3.2.         | PROBLEM FORMULATION                               |     |

| 3.2          | ·-· - · · · · · · · · · · · · · · · · ·           |     |

| 3.2          |                                                   |     |

| 3.2          |                                                   |     |

| 3.2          |                                                   |     |

|              | 2.4.1. Removing the Knapsack Component            |     |

|              | 2.4.2. Making Critical Path Calculation Tractable |     |

|              | 2.4.3. Slot Speedup Calculations                  |     |

| 3.2          |                                                   |     |

| 3.2          | 1 2                                               |     |

| 3.3.         | HEURISTICS                                        |     |

| 3.4.         | Experiments                                       |     |

| 3.4          | 4                                                 |     |

| 3.4          | .=, , , , ,                                       |     |

| 3.4          | 10. 0. coay 75. 1 a                               |     |

| 3.4          |                                                   |     |

| 3.4          | 4.5. Discussion                                   | 33  |

| 4. HE        | EURISTICS FOR IC LEGALIZATION                     | 34  |

| 4.1.         | MOTIVATION                                        | 34  |

| 4.2.         | Tetris Heuristics                                 | 38  |

| 4.2          | 2.1. Classic Tetris (CT)                          |     |

| 4.2          |                                                   |     |

| 4.2          |                                                   |     |

| 4.2          |                                                   |     |

| 4.2          |                                                   |     |

| 13           | EVDEDIMENT PECH TO                                |     |

|    | 4.3.1. | Evaluating heuristics combinations                              | 44  |

|----|--------|-----------------------------------------------------------------|-----|

| 5. | PARA   | ALLELIZING LEGALIZATION PROCEDURE                               | 52  |

|    | 5.1.   | MOTIVATION                                                      | 52  |

|    | 5.2.   | ABACUS overview                                                 |     |

|    | 5.3.   | DOMOCUS PARALLEL ALGORITHM                                      |     |

|    |        | Experiment                                                      |     |

|    |        | IC PLACEMENT OVER THE CLOUD                                     |     |

| 6. | JOB    | SCHEDULING OVER THE CLOUD                                       | 63  |

|    | 6.1.   | Overview                                                        | 63  |

|    | 6.2.   | OVERVIEW ON SCHEDULING HEURISTICS FOR LIVE VIDEO TRANSCODING ON |     |

|    |        | DGES                                                            |     |

|    | 6.3.   | OVERVIEW ON SCHEDULING VIDEO TRANSCODING JOBS OVER THE CLOUD    |     |

|    | 6.3.1. | 07 33 7                                                         |     |

|    | 6.3.2. | 0                                                               |     |

|    | 6.3.3. | Cloud Transcoding                                               | 69  |

| 7. | VIDE   | O TRANSCODING ON CLOUD EDGES                                    | 72  |

|    | 7.1.   | MOTIVATION                                                      | 72  |

|    |        | Problem definition                                              |     |

|    | 7.3.   | SCHEDULING HEURISTICS                                           |     |

|    | 7.3.1. |                                                                 |     |

|    | 7.3.2. | Scheduling with Relaxed Task QoS Requirements                   |     |

|    | 7.4.   | Experiments                                                     |     |

|    | 7.4.1. |                                                                 |     |

|    | 7.4.2. | •                                                               |     |

|    | 7.4.3. |                                                                 |     |

| 8. | SCHI   | EDULING VIDEO TRANSCODING JOBS OVER THE CLOUD                   | 85  |

|    | 8.1.   | MOTIVATION                                                      | 85  |

|    | 8.2.   | System Model                                                    |     |

|    | 8.3.   | SCHEDULING ALGORITHMS                                           |     |

|    | 8.3.1. | O                                                               |     |

|    | 8.3.2. |                                                                 |     |

|    | 8.3.3. |                                                                 |     |

|    |        | Experiments                                                     |     |

|    | 8.4.1. | 1                                                               |     |

|    | 8.5.   | RESULTS                                                         | 98  |

| 9. | COM    | BINATORIAL OPTIMIZATION                                         | 104 |

|    | 9.1.   | QUADRATIC ASSIGNMENT PROBLEM (QAP)                              | 104 |

|    |        | FILE ALLOCATION PROBLEM (FAP)                                   |     |

|    | 9.3.   | CAPACITATED PLANT LOCATION PROBLEM                              |     |

|    | 9.4.   | WEB PROXY PLACEMENT                                             | 108 |

| 10 | CON    | CUSSIONS AND FUTURE DESEARCH                                    | 111 |

#### LIST OF FIGURES

| Figure Page                                                                    | Number   |

|--------------------------------------------------------------------------------|----------|

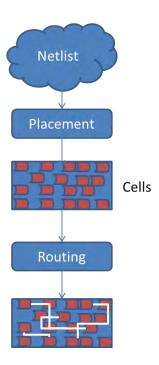

| FIGURE 2-1 IC PLACEMENT-ROUTING WORKFLOW                                       | 14       |

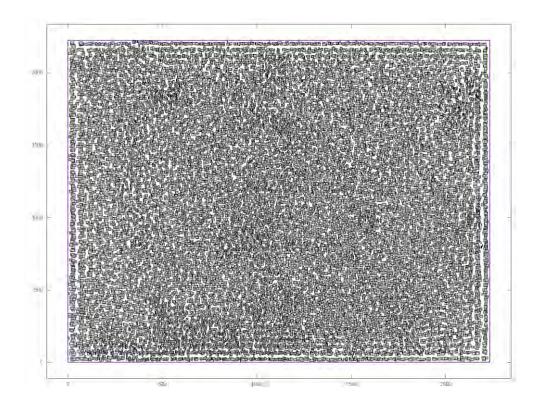

| FIGURE 2-2 GLOBAL PLACEMENT OF IBM05 CIRCUIT USING NTUPLACE3                   | 17       |

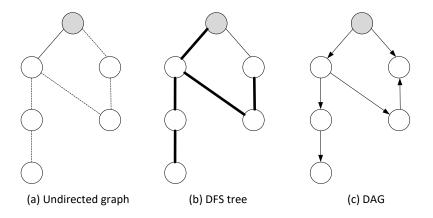

| FIGURE 3-1 PSEUDOCODE FOR LONGEST PATH CALCULATION IN DAG(G)                   | 24       |

| FIGURE 3-2 AN EXAMPLE OF DAG CONSTRUCTION                                      | 25       |

| FIGURE 3-3 AN EXAMPLE OF DISTANCE CALCULATION WITH 4 SOURCES                   | 26       |

| FIGURE 3-4 AN EXAMPLE OF SPEEDUP FACTOR CALCULATION                            | 27       |

| FIGURE 3-5 PSEUDOCODE FOR THE GREEDY HEURISTIC                                 |          |

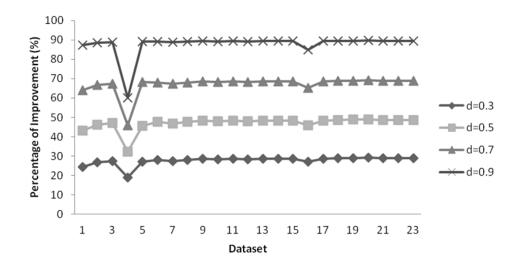

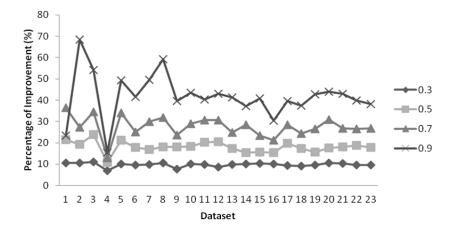

| FIGURE 3-6 PERFORMANCE IMPROVEMENT OF GREEDY VS. INITIAL LONGEST PATH (D=0     | .3, 0.5, |

| 0.7, 0.9)                                                                      | 30       |

| FIGURE 3-7 PERFORMANCE IMPROVEMENT OF GREEDY VS. RANDOM (D=0.3, 0.5, 0.7, 0.9  | )31      |

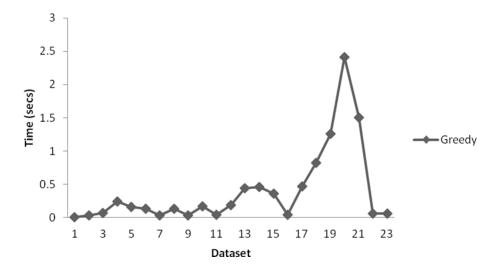

| FIGURE 3-8 RUNTIME OF GREEDY (SECS).                                           |          |

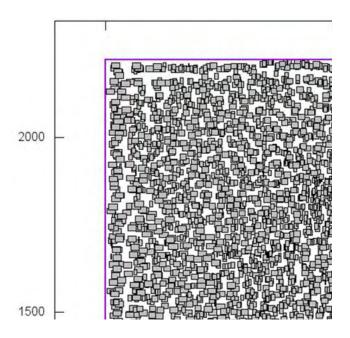

| FIGURE 4-1 THE OUTPUT OF NTUPLACE3 GLOBAL PLACER                               | 35       |

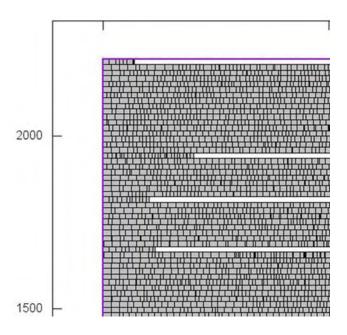

| FIGURE 4-2 THE OUTPUT AFTER LEGALIZATION WITH TETRIS ALGORITHM                 |          |

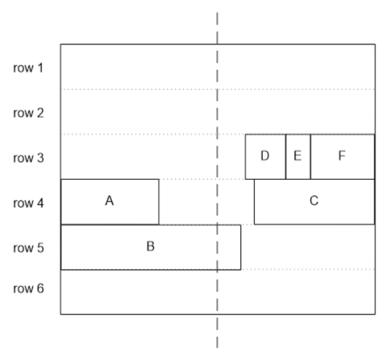

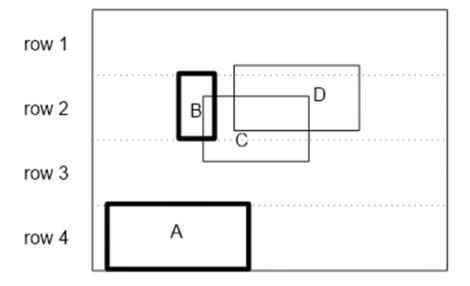

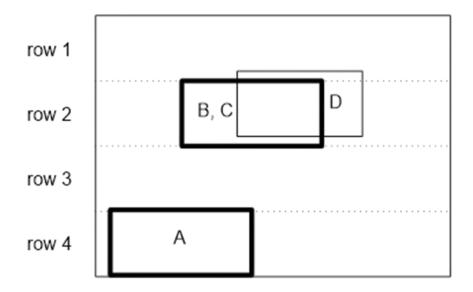

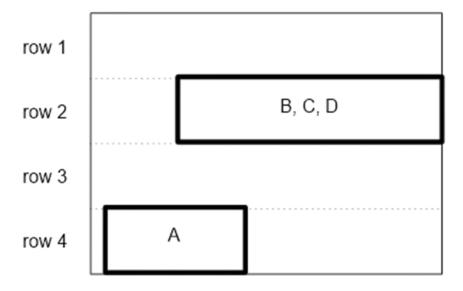

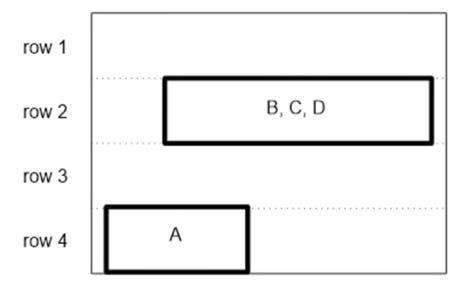

| FIGURE 4-3 INITIAL PLACEMENT                                                   |          |

| FIGURE 4-4 POSSIBLE POSITIONS FOR D CELL                                       |          |

| FIGURE 4-5 FINAL PLACEMENT BY CT                                               |          |

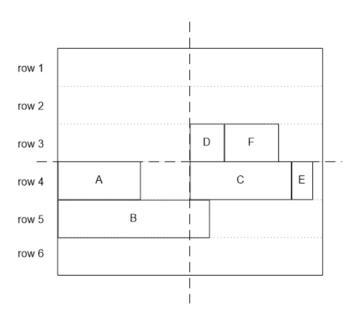

| Figure 4-6 The initial placement and the virtual split of the chip area in two |          |

| PARTITIONS                                                                     |          |

| FIGURE 4-7 FINAL PLACEMENT BY LR HEURISTIC                                     |          |

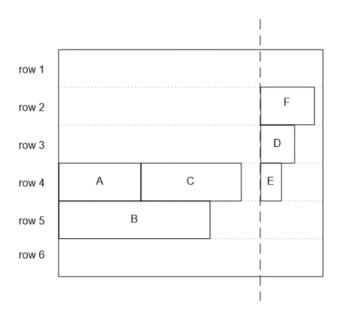

| Figure 4-8 The split in $2\times 2$ grid and the output of AC2 heuristic       |          |

| Figure 4-9 The vertical split in two areas and the placement performed by $CC$ |          |

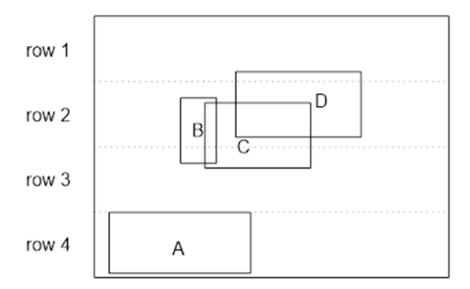

| FIGURE 5-1 INITIAL GLOBAL PLACEMENT                                            |          |

| FIGURE 5-2 PLACEMENT OF A AND B CELLS.                                         |          |

| FIGURE 5-3 CLUSTER FORMATION WITH B AND C CELLS                                |          |

| FIGURE 5-4 D IS APPENDED TO THE CLUSTER                                        |          |

| FIGURE 5-5 CLUSTER MOVED TO OPTIMAL POSITION                                   |          |

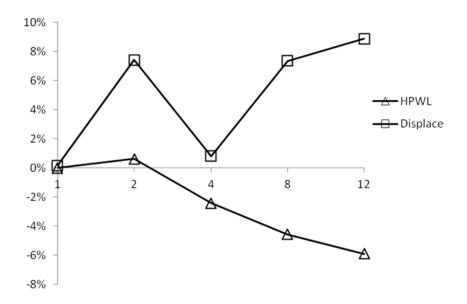

| Figure 5-6 Average performance improvement (%) for the HPWL and displace       |          |

| METRICS (X-AXIS SHOWS THREAD NUMBER)                                           |          |

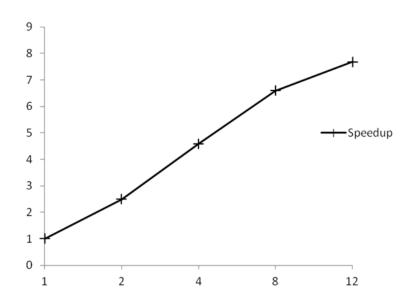

| FIGURE 5-7 SPEEDUP OVER THE SEQUENTIAL EXECUTION (X-AXIS SHOWS THREAD NUMB     |          |

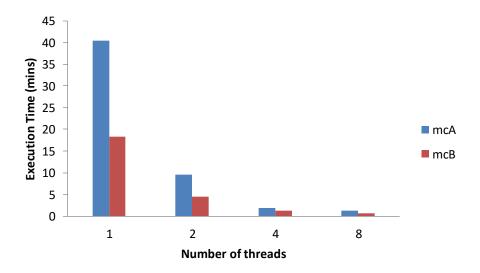

| FIGURE 5-8 CLOUD VS. DEDICATED INSTANCE EXECUTION TIME                         |          |

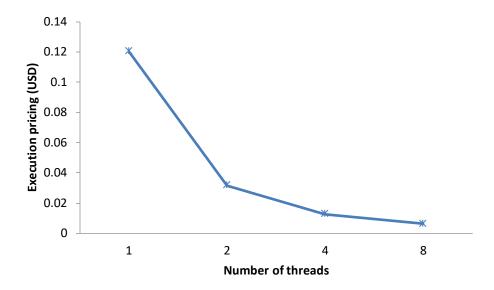

| FIGURE 5-9 CLOUD EXPENSES TESTING DOMOCUS LEGALIZER                            |          |

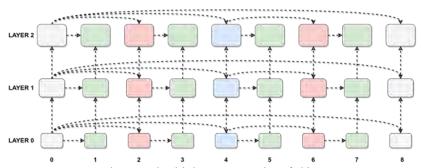

| FIGURE 6-1 SPATIAL-TIME REPRESENTATION OF VIDEO CODING IN LAYERS ACCORDING TO  |          |

|                                                                                |          |

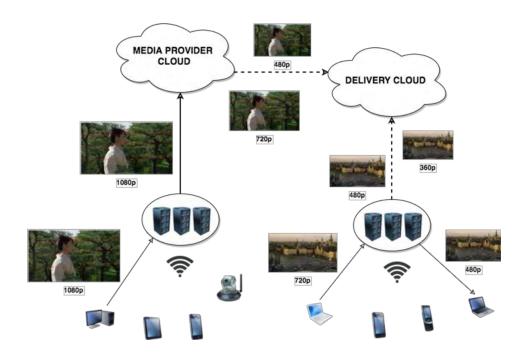

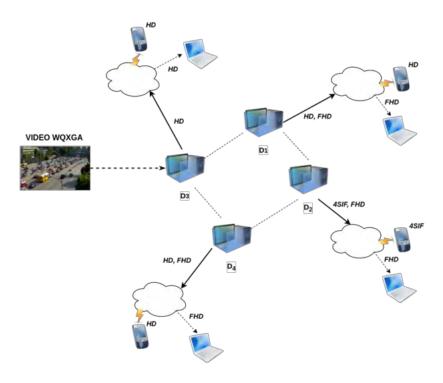

| FIGURE 7-1 EXAMPLE SYSTEM MODEL WITH EDGE TRANSCODING                          |          |

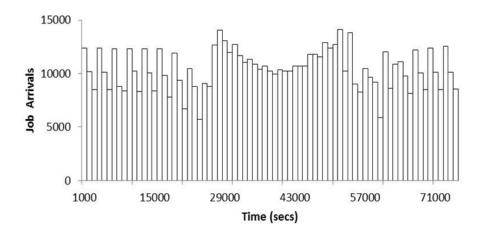

| FIGURE 7-2 HISTOGRAM FOR BROADCASTING ARRIVAL RATES                            |          |

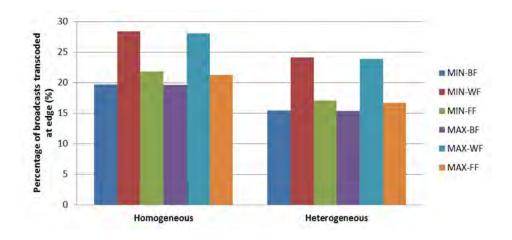

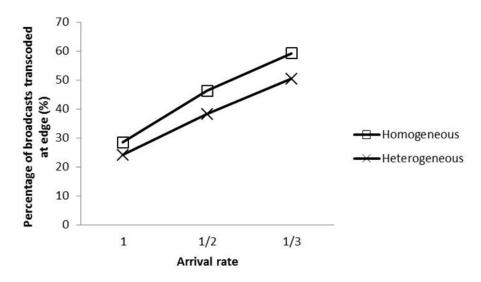

| FIGURE 7-3 PERCENTAGE OF BROADCASTS PROCESSED BY THE EDGE (1000 SERVERS, FUL   |          |

| DATASET). TWO DIFFERENT CASES: HOMOGENEOUS AND HETEROGENEOUS                   |          |

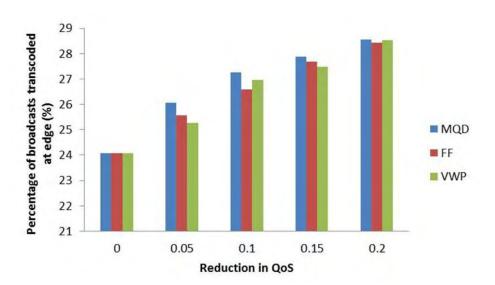

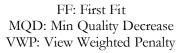

| FIGURE 7-4 PERCENTAGE OF BROADCASTS PROCESSED BY THE EDGE FOR DECREASING A     |          |

| RATE (1000 SERVERS)                                                            | 83       |

| FIGURE 7-5 PERCENTAGE OF BROADCASTS PROCESSED BY THE EDGE FOR VARYING QOS      | 0.4      |

| REDUCTION PERCENTAGES (FULL DATASET, HETEROGENEOUS SERVERS)                    |          |

| FIGURE 7-6 AVERAGE QOS OF VIEWERS AS THE ALLOWABLE REDUCTION IN QOS FOR ED     |          |

| TRANSCODING JOBS IS INCREASED (FULL DATASET, HETEROGENEOUS SERVERS)            |          |

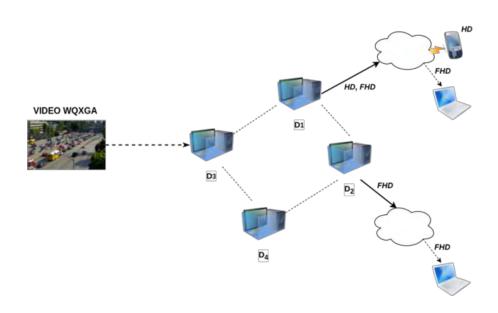

| FIGURE 8-1 AN EXAMPLE OF A CLOUD TRANSCODING SERVICE                           | 86       |

| FIGURE 8-2 AN EXAMPLE TRANSCODING JOB WITH TWO CORRESPONDING TASKS           | 92      |

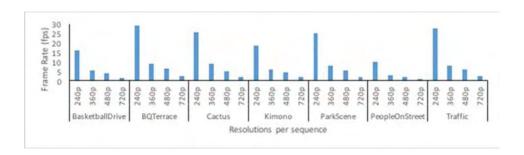

|------------------------------------------------------------------------------|---------|

| FIGURE 8-3 FRAME RATE CODING TIMES FOR COMMON TEST VIDEO SEQUENCES IN VARIO  | OUS     |

| RESOLUTIONS                                                                  |         |

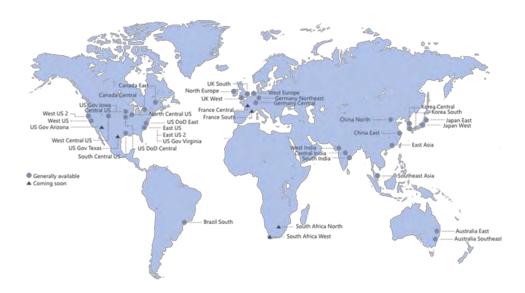

| Figure 8-4 Azure regions                                                     |         |

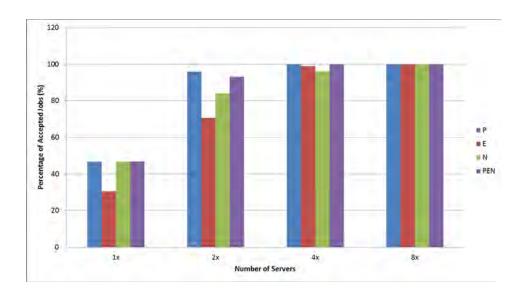

| FIGURE 8-5 PERCENTAGE OF ACCEPTED JOBS AS THE NUMBER OF SERVERS PER DATACEN  | TER     |

| INCREASES (LIVE CASTING SCENARIO)                                            | 100     |

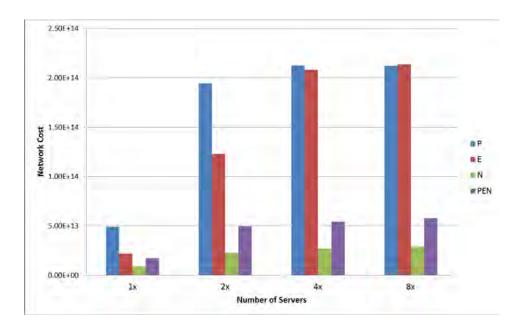

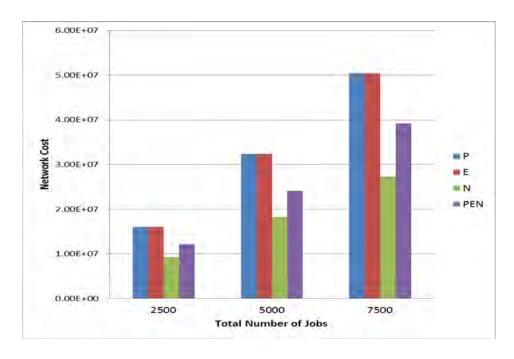

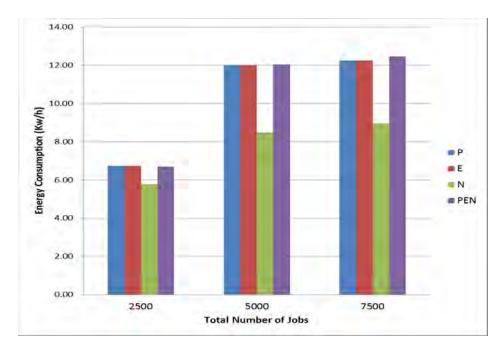

| FIGURE 8-6 NETWORK COST AS THE NUMBER OF SERVERS PER DATACENTER INCREASES (  | LIVE    |

| CASTING SCENARIO)                                                            | 100     |

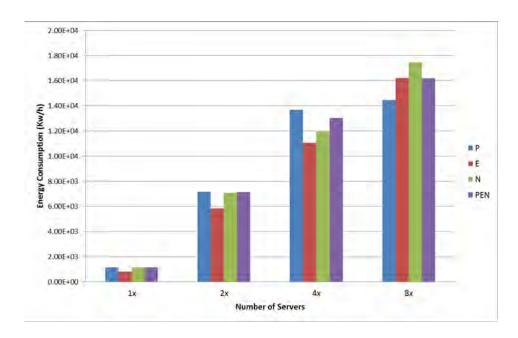

| FIGURE 8-7 ENERGY CONSUMPTION AS THE NUMBER OF SERVERS PER DATACENTER INCF   | REASES  |

| (LIVE CASTING SCENARIO)                                                      | 101     |

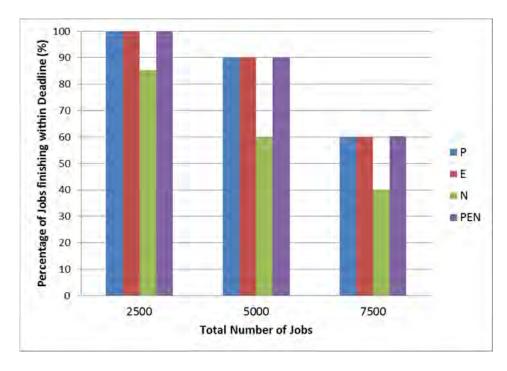

| FIGURE 8-8 PERCENTAGE OF JOBS FINISHING WITHIN THEIR DEADLINES AS THE NUMBER | OF      |

| SERVERS PER DATACENTER INCREASES (FACEBOOK SCENARIO)                         | 101     |

| FIGURE 8-9 NETWORK COST AS THE NUMBER OF SERVERS PER DATACENTER INCREASES    |         |

| (FACEBOOK SCENARIO).                                                         | 102     |

| FIGURE 8-10 ENERGY CONSUMPTION AS THE NUMBER OF SERVERS PER DATACENTER INC   | CREASES |

| (FACEBOOK SCENARIO)                                                          | 102     |

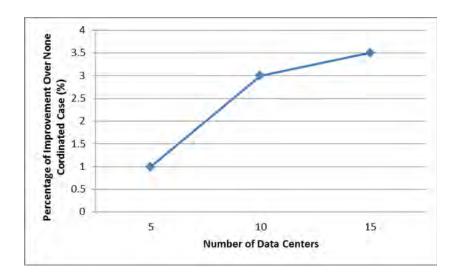

| FIGURE 8-11 IMPROVEMENT IN ACCEPTED JOBS (LIVE CASTING SCENARIO, PEN-K)      | 103     |

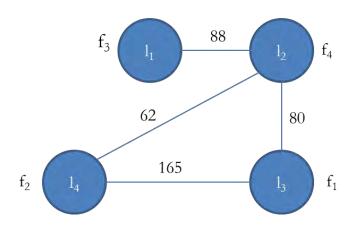

| FIGURE 9-1 LOCAL OPTIMAL ASSIGNMENT M={4,3,1,2}                              | 105     |

| FIGURE 9-2 GLOBAL OPTIMAL ASSIGNMENT M={3,4,1,2}                             | 106     |

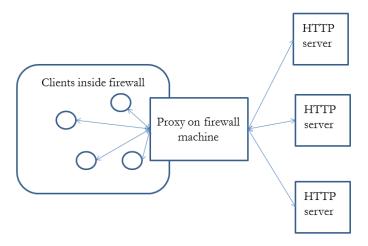

| FIGURE 9-3 INSTALLING PROXY ON A FIREWALL MACHINE                            | 109     |

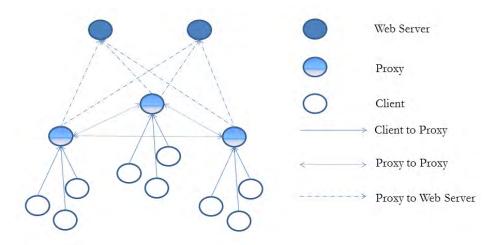

| FIGURE 9-4 A GENERIC CASHING SCHEME                                          | 110     |

#### LIST OF TABLES

| Table                                                                   | Page Number |

|-------------------------------------------------------------------------|-------------|

| TABLE 4-1 CONTRIBUTION OF INTERCONNECT CAPACITANCE TO TOTAL SWITCHED    |             |

| CAPACITANCE (IN PF)                                                     | 48          |

| TABLE 4-2 PERFORMANCE IMPROVEMENT OF STANDALONE HEURISTICS OVER CT      |             |

| TABLE 4-3 PERFORMANCE IMPROVEMENT OF AC HEURISTIC COMBINATIONS OVER     | CT49        |

| TABLE 4-4 PERFORMANCE IMPROVEMENT OF CC HEURISTIC COMBINATIONS OVER     | CT50        |

| TABLE 4-5 DOMINATING HEURISTICS                                         | 50          |

| TABLE 4-6 INTERCONNECT POWER OF HEURISTICS AS A FRACTION OF CT INTERCON |             |

|                                                                         | 51          |

| TABLE 7-1 DATASET FOR BROADCASTERS (GENERAL CHARACTERISTICS)            | 79          |

| TABLE 7-2 VIDEO SEQUENCES USED FOR WEIGHT CALCULATION                   |             |

| TABLE 8-1 NOTATION USED IN THIS CHAPTER                                 | 88          |

| TABLE 8-2 VIDEO SEQUENCES                                               | 96          |

| Table 9-1 Facilities Workflow F                                         | 104         |

| Table 9-2 Facilities Distance D                                         |             |

#### 1. Introduction

#### 1.1. Objectives and contribution of the thesis

A plethora of classic optimization problems exhibit spatial or temporal properties. An example of the first, is the 2D Knapsack problem [67] where the target is to place rectangles within a fixed sized plain so that no overlaps occur and the total benefit (summation of the benefits of the placed objects) is maximized. Concerning the temporal property, perhaps the 2-processor scheduling problem [63] and its various variants studied in the field of parallel and distributed computing, e.g., [123], [28], are the most prominent representatives in this category. Inspired by the importance of the spatial and temporal aspects rising in optimization problems, but also by modern problem settings of high practical value that came along with the popularity of the Computational Cloud, in this thesis we focus on providing contributions towards both directions (spatial and temporal). Specifically, we provide contributions to the field of standard cell placement in IC circuits [106] and to the field of Cloud scheduling [122].

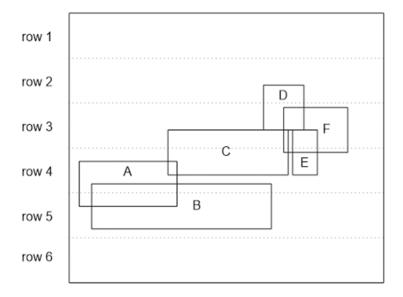

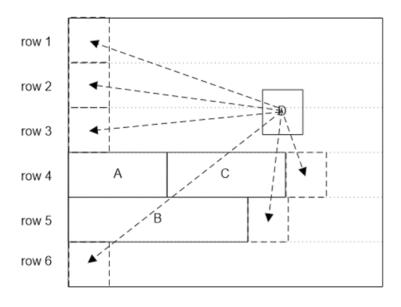

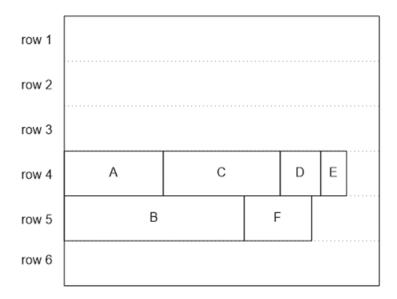

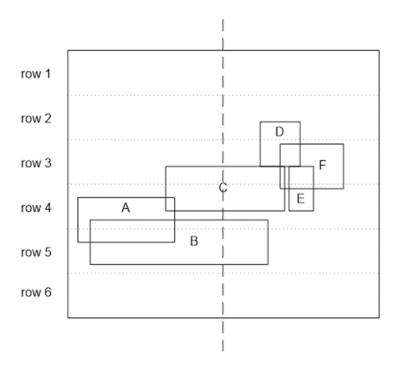

In standard cell placement, the cells of a circuit (rectangles of equal height but different length) must be placed on a chip area that is split into fixed equally height rows such that: (i) all cells rest within the chip area, (ii) no cells overlap, (iii) cell positions are row aligned and (iv) some target function is optimized, e.g., total wire length [103], congestion [147] etc. It is straightforward that (i)-(iii) impose constraints of spatial nature that can be seen as special variants of the 2D Knapsack constraints. Quite surprisingly, it turns out that depending on the optimization function (iv), the standard cell placement problem might also exhibit a temporal aspect, distinctly linking it to scheduling problems, as discussed in Chapter 3.

Concerning scheduling problems per se, we focused on modern settings involving the Computational Cloud. Rather than assuming generic job tasks or scientific workflows that apply on a rather restricted audience we tackled the problem of scheduling tasks related to video encoding and transcoding [60]. Video encoding refers to the process of compressing an initially raw video sequence using some standard, e.g., H.264 [146], while transcoding refers to producing multiple outputs from an initial (compressed) sequence, that correspond to various quality levels/bitrates and might even involve a change in

#### **CHAPTER 1. INTRODUCTION**

standard e.g., from H.264 to VP9 [49] or HEVC [133]. Since the vast majority of Internet traffic is video related [40] and users access it through devices and network connections of various capabilities, the need for efficient video coding and transcoding is becoming of paramount practical importance. This is also manifested by the number of related companies offering video transcoding as a service, e.g., Amazon Elastic Transcoder [11].

#### 1.2. Contributions

The contributions of the thesis can be summarized as follows.

- Concerning the cell placement problem we show its relation to scheduling and provide scheduling heuristics for the case where voltage drop is taken into account.

- We develop fast but efficient legalization heuristics, i.e., heuristics that start

from an initial invalid placement and attempt to perform small changes so

that spatial constraints are fulfilled. The heuristics developed are shown to

achieve comparable solution quality with a state of the art method [128] but

at almost two orders of magnitude less running time.

- We provide a fast parallel implementation for a state of the art legalization method [128] that achieves good speedup without affecting solution quality.

- We consider the case of scheduling video transcoding tasks between a network edge and a central datacenter and develop heuristics to maximize edge usage assuming different QoS levels.

- We consider the case of scheduling transcoding tasks among the various datacenters available for a related service. Quite surprisingly the current state of the art even for the most elaborated services, e.g., Amazon Elastic Transcoder [11] involves manual decisions. We develop heuristics that distribute the load so that network usage (among others) is minimized.

11

**CHAPTER 1. INTRODUCTION**

1.3. Outline

The rest of the thesis is organized in the following manner.

Chapter 2 provides a comprehensive literature survey concerning Integrated Circuit (IC) placement on Electronic Design Automation (EDA).

Chapter 3 illustrates the IC Placement problem relevance to job scheduling. Specifically, a detailed formulation of the placement problem is given and steps to reduce its inherent difficulty are illustrated. Additionally, we model the resulting problem rigorously and discuss its complexity, we also demonstrate its relation to the job scheduling problem and outline directions for heuristic design and finally, we evaluate the merits of a greedy approach that takes advantage of the formulation. Parts of this chapter appeared in [114].

Chapter 4 examines the evaluation of standalone variations to the basic Tetris algorithm that aim at significantly improving its performance. Furthermore, we introduce combinations of the standalone heuristics while all of them are evaluated with commonly used benchmark circuits. Parts of this chapter appeared in [44].

Chapter 5 presents the procedure of speeding up the legalization algorithms that offer top quality solutions, such as Abacus, using parallelization. Concretely, we propose a lock-free parallelization framework that can be applied over various legalization schemes, also, we implemented and tested the framework over a legalization algorithm (Abacus) known for its solution quality but also slow running time. Parts of this chapter appeared in [112].

Chapter 6 provides a survey concerning Cloud scheduling, especially under the light of video transcoding jobs.

Chapter 7 analyses the case of live video transcoding on Cloud Edges by way of scheduling heuristics that decide on which jobs should be assigned to an edge mini-datacenter and which to a backend datacenter. Through simulation experiments with

12

#### **CHAPTER 1. INTRODUCTION**

different QoS requirements we conclude on the best alternative. Parts of this chapter appeared in [113].

Chapter 8 investigates the problem of scheduling transcoding jobs over a distributed system comprising of processing nodes that are geographically dispersed and might be whole clusters or even separate data centers. In this chapter we propose algorithms to minimize both the inter-node network traffic and the intra-node energy consumption, while meeting the deadlines and quality requirements. Parts of this chapter are submitted to the ACM Symposium on Cloud Computing 2017 (SoCC'17).

Chapter 9 provides a study about combinatorial optimization. This study consists of four well known optimization problems.

Finally, Chapter 10 summarizes the thesis and provides directions for future work.

### 2. Placement in Electronic Design Automation

#### 2.1. Overview

Integrated circuit (IC) Placement is a major design problem, especially with the continuous growth in the complexity of modern integrated circuits there is an urgent need for fast placers offering good quality results. Placement is an essential step in Electronic Design Automation (EDA) and an important part in the Physical Design procedure. An indicative abstract description of a Placer, as seen in Figure 2-1, could be a machine that takes as an input a net list and a cell specification library and produces the exact location of each cell while minimizing a number of objective functions such as Half Perimeter Wire Length (HPWL), congestion and power consumption to ensure that a circuit meets its performance demands. IC placement is a difficult problem to solve, an ineffective placer usually leads to more wire which affects the performance and the timing of the circuit. Also, if placement is inefficient next tool in the flow, the router, will become unable to connect all wires or to meet timing.

Figure 2-1 IC Placement-Routing workflow

Cell placement has attracted much research interest in the past where a variety of standard cell placers has been proposed by the EDA industry and academia. Placement methodologies can be crudely divided in three major categories based on the way they tackle the problem. The global placement where an initial solution, that contains overlaps and minimizes the cost function, is produced. An intermediate step named legalization that removes all the cell overlaps and finally the detailed placement that refines the final solution to achieve better results.

Global placers solve the problem of placing and spreading cells sufficiently while optimizing the cost function. Various cost functions were considered in the literature such as wire length, routability, time delay, voltage drop and power consumption. Optimization in the global phase is most commonly done without enforcing validity constraints and by incorporating in the model some kind of a repelling force among cells in order to spread them in the chip area. Global placement is the intermediate step between logic synthesis and routing which generates a first and sometimes congested cell distribution in which placement constrains are violated. Such violations include but are not limited to cell overlaps, exceeding critical path delay and net congestion. Global placers can be divided into three major categories: simulated annealing, min-cut partitioning and analytical approaches.

Simulated annealing is a mathematical scheme which can be applied to a number of optimization problems. It starts by calculating a feasible solution and through iterative local changes it computes a better solution. The main drawback of simulated annealing is that it experiences slow convergence rate in large problem set. Timberwolf [125] it was applied as a local optimizer of sub problems. Timberwolf is a probabilistic, iterative improvement technique which approximates the global optimal through iterative cell swaps and moves.

The main idea behind min-cut partitioning is the recursive dividing of the chip area and the design's components, until the regions are small enough to apply a legalization algorithm. Capo [135] is one of the most known placement algorithms that exploit this technique. Dragon2005 [136] and Feng Shui [6] both perform min-cut multi-way

partitioning using hMetis [1] to spread the cells in the chip area, with the former applying simulated annealing to pinpoint the optimal locations

Quadratic and nonlinear techniques constitute the two main subcategories in analytical approaches whereby optimization objectives are modelled by sets of mathematical equations. In Quadratic Optimization the circuit's connectivity is used for the formulation of a quadratic problem and the subsequent minimization of an overall cost function. Examples of this category are: GORDIAN [88], BornPlace [25] and FastPlace [147]. The GORDIAN algorithm is a divide-and-conquer global placement method that is composed of alternating and interacting optimization and partitioning steps that are followed by an optimization of the area utilization. GORDIAN's operation can be divided into three steps, area partitioning, cell partitioning and quadratic calculations. The iterations conclude when there are no sub-partitions left that meet the cell and area constraints we have set (sub-partition dimensions and cell count) while at each iteration a constrain is calculate the center of gravity for the cells belonging to the specific partition. Bonnplace [25] also uses a min-cost flow formulation. The algorithm iteratively augments flows along paths, ensuring that the only flow augmentations that are chosen and applied before the next augmentation step are the ones than can be realized exactly by cell movements. In this way finding the optimal flow isn't guaranteed, nevertheless, the produced solution is always feasible.

In Non-Linear Optimization an approximation of the total wire length is calculated together with cell density using high order models in order to produce better solutions at the expense of runtime. Examples here include: [29], [75], [84], [103] and [110]. White-space reallocation together with force directed placement were used as sub-components of a multilevel optimization approach whereby starting from an initial nonlinear optimization problem that is hard to solve, successive relaxation steps involving cell clustering were applied in an iterative manner. More recent trends include force directed placers whereby cells are spread using a mixture of repelling and attractive forces. Through an iterative procedure equilibrium is reached so that design constraints are satisfied. Two well-known force directed placers are Kraftwerk2 [129] and ePlace [103].

Taking into consideration geometrical constrains in a design, min-cut placers such as [29], [5] and [7] attempt to identify components that should be placed together.

The output of global placement as seen in Figure 2-2 doesn't align cells with rows and might also contain overlaps. Therefore a second legalization step is necessary to meet constraints. An approach is to have as goal the minimum cell displacement between the global placement and the final one (abacus)-(tetris). It is in our best interest to perturb as little as possible each cell's position during legalization, hence the importance of the displacement metric. Contributions in the area of legalization can be classified in two major categories, local and global legalizers.

Figure 2-2 Global Placement of ibm05 circuit using NTUplace3

Local approaches achieve legalization by moving cells separately in free spaces or in a ripple motion [77] while the overall congestion is controlled based on white space reallocation [33] or by iterative local refinement algorithms [147]. Some local legalizers

such as [74] and [98] include wire length and displacement minimization using clustering and bin division techniques. Others, such as [114] focus on voltage drop optimization. Dynamic programming is used in [5] and [85] for row fragmentation and placement and in [128] to identify the most promising cell-row assignments. The above methods mainly consider cell placement in a one by one fashion. The simplest and fastest legalization method is the Tetris [73] approach which is used as a yardstick for the performance evaluation of more complex methods that sacrifice running time to achieve better placement. Tetris still remains a popular choice for legalization since it burdens total runtime at a minimum degree, a critical issue for billion cells designs. Abacus [128] also places cells one by one in order of their position on the x-axis. However, in case the vertical alignment of a cell with a candidate row incurs overlaps, a cluster is formed between the cell that is inserted and the ones with which it overlaps and the best position of the cluster is defined through a quadratic formulation. In other terms the key difference of the algorithms is that Abacus might move previously placed cells whereas Tetris doesn't do so. This explains the fact that Abacus achieves lower displacement compared to Tetris but at the cost of increased runtime. In HiBin [98] a bin merged procedure is incorporated, where two different shapes of integrated bins are developed in order to limit the movable scope of each cell. A similar to Abacus approach was followed in [74] with the objective being to minimize cell displacement and HPWL. The presented algorithm uses a row indexing scheme to speed-up the process of finding the best row to insert a cell. In [38] an extension of the clustering method of Abacus is presented that takes into account existing obstacles in the chip area, i.e., preplaced modules that are immoveable. Contrary to Abacus cells are examined in order of their length rather than their position in the x axis as Abacus and Tetris does. In [46] the Abacus legalization scheme was adapted in order to tackle fence regions whereby certain cells must be placed within while others should be excluded. In [118] an Abacus inspired legalization scheme called Jezz is proposed. Jezz considers for row insertion cells, white spaces and blockage nodes in order to cope with obstacles. The resulting scheme was shown to achieve a better performance compared to Abacus but is considerably slower by roughly 20 times.

On the other hand global legalization techniques determine on the positions of multiple cells in a single iteration. Examples of this category are [22], [24], [37] and [53] to

name a few, whereby network flows are used to obtain solution and [42] and [86] that perform cell clustering to reduce search space. Finally, for some restricted problem versions optimal solutions can be found. For instance, for the case of a single row where the assigned cells and their order (left to right) are known, the optimal placement can be found as per [23], while optimal area partitioning is possible in order to offload high density regions as described in [27]. In [37] a history-based legalization scheme is proposed. Min-cost flow formulation is used in order to find a legal placement that presents minimal displacement. Once a viable flow solution is obtained, it is translated to cell movements. During iterations, legalization failures are recorded, and subsequently used in future iterations by a history engine, in order to avoid similar flow realization attempts. In [24] each cell is assigned to a specific region based on its location after the global placement step. A min-cost flow problem is formulated with region boundaries considered as a soft constraint. Dynamic programming is used to decide which cells are going to be moved, therefore realizing the flow.

# 3. On Formulating and Tackling IC Placement as a Scheduling Problem

#### 3.1. Motivation

Most research on cell placement focused on minimizing the total wire length, hoping to optimize simultaneously the critical path delay as a byproduct. Ideally, a cell placement optimizer should take into account both goals, i.e., wire length and critical path delay offering a set of viable pareto optimal solutions for the designer to choose. One way of tackling the aforementioned two-function optimization problem is to start with one (or more) initial "promising" placements and alter them presumably to gain more towards one or both of the optimization goals. Developing an optimizer with the above characteristics is part of our ongoing work.

In this chapter we present a novel formulation of the cell placement problem with the goal of deriving fast heuristics to output initial placements that have the potential of acting as "good" starting points in a more complex optimization process. Towards this end, we consider optimizing critical path delay in the cell interconnection graph based on individual cell delay characteristics and the premise that placing cells near power sources results in better performance.

Our contributions include the following: (a) we give a detailed formulation of the placement problem and illustrate steps to reduce its inherent difficulty (asymptotic complexity remains the same); (b) we model the resulting problem rigorously and discuss its complexity; (c) we demonstrate its relation to job scheduling problem and outline directions for heuristic design and (d) we evaluate the merits of a greedy approach that takes advantage of the formulation.

#### 3.2. Problem Formulation

#### 3.2.1. Preliminary Definitions

Let C be the set of cells in the circuit we want to place. Cells are the minimal circuit components and can correspond to gates, latches etc. Let  $c_i$  denote the i<sup>th</sup> cell assuming a total order of them. Wired connections exist between cells. We can represent the circuit structure using a graph G(C, E) with vertices depicting cells and edges depicting direct

connections between cells. For most circuit inputs the resulting graph G is undirected and contains circles.

Each  $c_i$  is a rectangle of fixed width (let n) and varying length  $m_i$  and is associated with a nominal delay value  $t_i$ . The chip we wish to design is represented by an  $N \times M$  2D-plane with N showing width and M showing length in the same measurement unit used in w and  $m_i$ s.

A chip contains a set P of pins. Each pin might be connected with one or more cells. Positions of pins in the plane are assumed to be fixed and part of the input, while pin sizes and delays are considered to be zero. To represent the above, we augment the previous graph forming a new *weighted graph* G'(V, E') with the set of vertices  $V = P \cup C$  and E' depicting both cell and pin connections. Each vertex u in the graph is associated with a weight  $w(u) = t_i$  if it corresponds to the ith cell, otherwise (it corresponds to a pin) w(u) = 0. Henceforth, for simplicity, we will refer to G' as G(V, E), replacing the previous definition of G which is not further needed. We refer to the chip plane together with the pin placement as  $Plane\_Input$  and to the graph G together with cell sizes as  $Circuit\_Input$ .

#### 3.2.2. Generic Problem Statement

Let  $p_k = \{u_1, u_2, ..., u_k\}$  be a path in G involving k vertices, not necessarily distinct. Path weight  $w(p_k)$  is the aggregate weight of vertices in the path, i.e.,  $w(p_k) = \sum_{i=1}^k w(u_k)$ . We define the critical (longest) path to be the path p in G of maximum weight. Notice that if G contains circles the longest path weight is infinite. Therefore, we define the critical path in G to be the maximum weight path among the paths satisfying the property that each vertex is visited at most once.

We can now give the generic statement of the placement problem studied in this chapter as follows: Given Circuit\_Input and Plane\_Input place the cells in the plane so that: (a) no cell exceeds plane boundaries, (b) no cells overlap and (c) critical path delay is minimized. Criteria (a) and (b) impose validity constraints, while (c) is the optimization target. In the absence of further details (given in the following subsection), all possible valid placements regarding (a)

and (b), result in the same performance concerning (c) which is equivalent to finding the critical path in *G*.

Notice that even by ignoring validity constraints (a) and (b), the problem is still intractable since it is equivalent to finding the longest path in an undirected graph which is known to be NP-hard. On the other hand, we claim (proof omitted) that ignoring the optimization criterion (c) also results in a relevant decision problem (placing all cells so as to satisfy (a) and (b)) that is NP-complete in general, having a knapsack component. Summarizing the above remarks we can state that even with the simplest of the assumptions concerning path delays, the problem discussed in this chapter is hard and requires clever heuristics to master.

As a last remark we would like to mention that in practice, the Knapsack component of the problem is not expected to be the primary challenge. This is because cell sizes do not vary arbitrarily and chip plane usually has significant extra space compared to the total cell area. The methodology presented in section 3.2.4 takes advantage of the above observations.

#### 3.2.3. Time Delay Estimation

The actual delay experienced in a path of the circuit is affected by a plethora of parameters e.g., wire lengths, gate (cell) type etc. Analytical calculations are performed by commercial CAD tools to obtain accurate enough estimations. However, in most cases such calculations can only be performed after the circuit is placed on the chip plane. This is due to the fact that voltage drop depends (aside from other parameters) on the density of placement in a specified region. Given the above remark and the problem's toughness even in the simplest scenario, we decided that adopting sophisticated analytical delay calculations hinters the ability to develop fast and elegant heuristics for the problem, thus, exceeds the scope of this chapter.

Instead, we followed a simple intuitive approach to model the dependencies between cell placement and path delays. Namely, we assume that the "sweetest" spot for placing a particular cell is as close to a power pin as possible. We also assume that the performance

drop is linear to the distance from the power source up to a maximum predefined value d. In the presence of multiple power sources we consider the distance from the closest one.

#### 3.2.4. Reducing Problem Complexity

Here, we present the decisions taken in order to reduce the complexity of the placement problem to allow for efficient heuristics.

#### 3.2.4.1. Removing the Knapsack Component

We start by completely removing the knapsack component of the problem namely, criteria (a) and (b). Specifically, from the initial  $N\times M$  plane area we only consider for placement reasons the  $Rn\times M$  space, where n is the cell width and R an integer such as:  $Rn \le N < (R+1)n$ . In other words we split the chip plane in rows such that cells fit exactly in every row width-wise. In case the plane cannot be divided exactly in rows of width n, the last row that is a fraction of n in width is discarded. Next, we split the  $Rn\times M$  plane in D = |C|/R columns of equal length M/D. Essentially, this splits the whole plane in equally sized slots arranged in R rows and D columns such that their number equals the number of circuit cells C and that a cell can fit in a slot width wise. In general, a circuit cell can be placed anywhere in the plane accounting for increased complexity regarding the three problem criteria. Let  $s_i$  denote the jth slot in a total ordering of them. By assuming all cells to be of equal size length-wise and fit exactly to the slot length, i.e.,  $m_i = M/D \ \forall 1 \le i \le |C|$  the potential placement positions of a cell equal |C|, the number of slots. This significantly reduces search space and can be elegantly encoded in a  $|C| \times |C|$  placement matrix X of Boolean values, whereby  $X_{ij} = 1$  iff  $s_i$  is placed in slot  $s_i$ , 0 otherwise.

# longestPathCalculation(DAG(G))M:=Topological sort array of DAG(G); for all $1 \le i \le |C|$ visit[i]:=false; endfor longestPath:=NINF; while (exists i: visit[i]=false) do s:=min{i: visit[i]=false}; cost:=calculateCost(s); if (cost>longestPath) then longestPath:=cost; endif endwhile return longestPath; calculateCost(s) u:=M[s]; Visit[s]:=true; cost:=w(u);if (u has no outgoing edges in DAG(G)) then return cost; endif for all v: (u, v) exists in DAG(G) temp:= w(u) + calculateCost(v);if (temp>cost) cost:=temp; endif endfor return cost;

Figure 3-1 Pseudocode for longest path calculation in DAG(G).

#### 3.2.4.2. Making Critical Path Calculation Tractable

As mentioned in section 3.2.1 longest path calculation in a weighted undirected graph is NP-hard. Therefore, in order to make critical path calculation tractable, we transform the graph G that is part of the *Circuit\_Input*, into a directed acyclic graph DAG(G) using the following steps. First we run DFS starting from all input pins. The result of this step is a forest of DFS trees in which some of the original edges are missing. Then we perform topological sort and construct DAG(G) by taking every undirected edge (u, v) in G and adding a directed edge (u, v) in DAG(G) iff (u, v) doesn't already exist and u appears before v in the topological order. Otherwise, in case (v, u) doesn't exist in DAG(G) and u appears after v in the topological order, the directed edge (v, u) is added in DAG(G).

Having constructed DAG(G) in a preprocessing step and calculated its topological order, longest path calculation can be performed in O(|DAG(E)|) time where DAG(E) is the set of edges in DAG(G). Notice that from the DAG construction process |DAG(E)| = |E|/2, where E is the set of edges in G. Figure 3-1 shows longest path calculation in pseudocode. As a final note we would like to note that the longest path computed in DAG(G) needs not be equal to the longest path that exists in G (in fact the opposite would imply that P=NP). In constructing DAG(G) we lost some of the information graph G contained. Figure 3-2 illustrates an example. Assuming all vertex weights to equal 1, the initial undirected graph G (Figure 3-2-a) has a longest path of 5 shown in dashed lines. One possible outcome of applying DFS in G starting from the grey vertex, is shown in Figure 3-2-b which depicts the DFS tree in bold lines. Based on this tree the final constructed DAG is given in Figure 3-2-c.As it can be observed the resulting graph has a longest path of 3.

Figure 3-2 An example of DAG construction

#### 3.2.4.3. Slot Speedup Calculations

As mentioned in section 3.2.3 we assume that the time delay introduced in a cell is linear to the distance from the closest power source. Here, we model the interdependence of the placement decision and cell delay as a speedup factor of slots. As it will be discussed in following sections this modeling allows us to view the cell placement problem as a scheduling problem, thus, being able to benefit from the rich

literature that exists in scheduling, e.g., [95] for a somehow old survey. We illustrate the process through the following example.

|   | <b>X</b>   |     |     |     |     |     |     |     |

|---|------------|-----|-----|-----|-----|-----|-----|-----|

|   | 1          | 1.4 | 2.2 | 2   | 1   | 0   | 1   | 2   |

| > | <b>〈</b> 0 | 1   | 2   | 2.2 | 1.4 | 1   | 1.4 | 2.2 |

|   | 1          | 1.4 | 2.2 | 2.8 | 2.2 | 2   | 2.2 | 2.8 |

|   | 2          | 2.2 | 2.8 | 3.6 | 3.2 | 3   | 3.2 | 3.6 |

|   | 3          | 3.2 | 3.6 | 4.2 | 4.1 | 3.6 | 3.2 | 3   |

|   | 2          | 2.2 | 2.8 | 3.6 | 3.6 | 2.8 | 2.2 | 2   |

|   | 1          | 1.4 | 2.2 | 3.2 | 3.2 | 2.2 | 1.4 | 1   |

| > | <b>c</b> 0 | 1   | 2   | 3   | 3   | 2   | 1   | 0   |

Figure 3-3 An example of distance calculation with 4 sources.

Consider the case where a circuit of 64 cells, each being a perfect square with edge size of 1, must be placed in a chip plane of size 8×8. Figure 3-3 shows the plane arranged in 8×8 slots. Let there be 4 power sources with their places shown as an x mark in Figure 3-3. Slots containing power sources are assumed to have a distance of zero. For the remaining (slot, source) pairs, the Euclidean distance is calculated between the slot's center and the center of the slot containing the power source. In the example, 4 such distances will be calculated per slot (one for each source). Figure 3-3 records for each slot the smallest of the four calculated distances (let  $dist_1$  for slot  $s_1$ ).

Afterwards, for each slot  $s_i$  a speedup factor (let  $f_i$ ) is calculated as follows. The slot with the largest distance  $dist_{max}$  (grey slot in the example) is assumed to have a speedup factor of 1 and decrease performance compared to a slot with distance 0 by a factor of  $d \in [0,..1]$ . This means that the speedup factor of a distance 0 slot (let  $f_{max}$ ) is set to 1/(1-d). The remaining  $f_i$  factors (see Figure 3-4) are calculated proportionally as follows:

$$f_j = (1 - d\frac{dist_j}{dist_{\text{max}}})/(1 - d)$$

(3.1)

| 1.33             | 1.29                                 | 1.20                                                                                          | 1.22                                                                                                                                                                                                                   | 1.33                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                       | 1.33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1.22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------|--------------------------------------|-----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>&lt;</b> 1.42 | 1.33                                 | 1.22                                                                                          | 1.20                                                                                                                                                                                                                   | 1.29                                                                                                                                                                                                                                                                                      | 1.33                                                                                                                                                                                                                                                                                                                                                  | 1.29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1.20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1.33             | 1.29                                 | 1.20                                                                                          | 1.14                                                                                                                                                                                                                   | 1.20                                                                                                                                                                                                                                                                                      | 1.22                                                                                                                                                                                                                                                                                                                                                  | 1.20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1.14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1.22             | 1.20                                 | 1.14                                                                                          | 1.06                                                                                                                                                                                                                   | 1.10                                                                                                                                                                                                                                                                                      | 1.12                                                                                                                                                                                                                                                                                                                                                  | 1.10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1.06                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1.12             | 1.10                                 | 1.06                                                                                          | 1                                                                                                                                                                                                                      | 1.01                                                                                                                                                                                                                                                                                      | 1.06                                                                                                                                                                                                                                                                                                                                                  | 1.10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1.12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1.22             | 1.20                                 | 1.14                                                                                          | 1.06                                                                                                                                                                                                                   | 1.06                                                                                                                                                                                                                                                                                      | 1.14                                                                                                                                                                                                                                                                                                                                                  | 1.20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1.22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

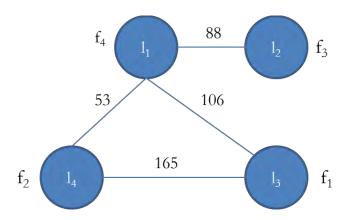

| 1.33             | 1.29                                 | 1.20                                                                                          | 1.10                                                                                                                                                                                                                   | 1.10                                                                                                                                                                                                                                                                                      | 1.20                                                                                                                                                                                                                                                                                                                                                  | 1.29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1.33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |