## Architectural Implications of Automatic Parallelization With HELIX-RC

The Harvard community has made this article openly available. <u>Please share</u> how this access benefits you. Your story matters

| Citation     | Brownell, Kevin Matthew. 2015. Architectural Implications of<br>Automatic Parallelization With HELIX-RC. Doctoral dissertation,<br>Harvard University, Graduate School of Arts & Sciences.                                                                              |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Citable link | http://nrs.harvard.edu/urn-3:HUL.InstRepos:23845453                                                                                                                                                                                                                     |

| Terms of Use | This article was downloaded from Harvard University's DASH<br>repository, and is made available under the terms and conditions<br>applicable to Other Posted Material, as set forth at http://<br>nrs.harvard.edu/urn-3:HUL.InstRepos:dash.current.terms-of-<br>use#LAA |

## Architectural Implications of Automatic Parallelization with HELIX-RC

A DISSERTATION PRESENTED BY Kevin Matthew Brownell TO The School of Engineering and Applied Sciences

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

for the degree of Doctor of Philosophy in the subject of Engineering Sciences

Harvard University Cambridge, Massachusetts September 2015 ©2015 – Kevin Matthew Brownell all rights reserved.

## Architectural Implications of Automatic Parallelization with HELIX-RC

#### Abstract

As classic Dennard process scaling fades into the past, power density concerns have driven modern CPU designs to de-emphasize the pursuit of single-thread performance, focusing instead on increasing the number of cores in a chip. Computing throughput on a modern chip continues to improve, since multiple programs can run in parallel, but the performance of single programs improves only incrementally. Many compilers have been designed to automatically parallelize sequentially written programs by leveraging multiple cores for the same task, thereby enabling continued single-thread performance gains. One such compiler is HELIX, which can increase the performance of a mixture of SPECfp and SPECint benchmarks by  $2 \times$  on a 6-core Nehalem CPU.

Previous approaches to automatically parallelize irregular programs have focused on removing apparent dependences through thread-level speculation, which limits the type of code that can be targeted. In contrast, this dissertation increases the amount of code that can be parallelized by addressing the specific communication demands of that code. The dissertation proposes a specialpurpose extension of the cache hierarchy, called *ring cache*, to greatly reduce the perceived communication latency between cores running an automatically parallelized program. This co-design of ring cache and the HELIX compiler, called HELIX-RC, increases the speedup of 10 SPEC benchmarks running on 16 simulated in-order cores from an average of  $2 \times$  to an average of over  $8 \times$ . Speedups are slightly reduced to  $7 \times$  on out-of- order cores, which extract instruction-level parallelism on their own. A fully synthesized Verilog implementation of ring cache is evaluated and is shown to consume less than 25mW of power with an area of less than 0.275 square millimeters.

This dissertation includes a study comparing single program per core multiprogramming and HELIX-RC. Counterintuitively, some HELIX-RC parallelized benchmarks not only surpass simple multiprogramming in terms of single program performance, but can also beat multiprogramming in terms of total multicore throughput by reducing the effective per-core working set of a program.

With communication bottlenecks removed by ring cache, automatic parallelization with HELIX-RC restores a decade of lost single-thread performance improvements.

## Contents

| 0 | Int         | RODUCTION                                                               | Ι  |  |  |

|---|-------------|-------------------------------------------------------------------------|----|--|--|

|   | 0.1         | Performance Scaling Hits a Speed Bump                                   |    |  |  |

|   | 0.2         | Extracting Multicore Performance                                        | 4  |  |  |

|   |             | 0.2.1 Single-Program Parallelism                                        | 5  |  |  |

|   |             | 0.2.2 Multiple-Program Parallelism                                      | 5  |  |  |

|   | 0.3         | Core Utilization Remains Low                                            | 6  |  |  |

|   | 0.4         | Automatic Parallelization Can Improve Utilization                       | 6  |  |  |

|   | 0.5         | Contribution of the Dissertation                                        | 7  |  |  |

|   | 0.6         | Organization of the Dissertation                                        | 8  |  |  |

| I | Pri         | or Parallelization of Irregular Workloads Limited by Loop Size          | 9  |  |  |

|   | 1.1         | Thread Extraction Techniques                                            | 12 |  |  |

|   |             | I.I.I Cyclic Multithreading                                             | 12 |  |  |

|   |             | I.I.2 Pipelined Multithreading                                          | 17 |  |  |

|   | I.2         | Speculation and Additional Hardware For Increasing Performance          | 21 |  |  |

|   |             | I.2.I Software Speculation                                              | 22 |  |  |

|   |             | I.2.2 Hardware Speculation                                              | 24 |  |  |

|   |             | I.2.3 Custom Architectures                                              | 28 |  |  |

|   | 1.3         | Automatic Parallelization of Irregular Programs Must Handle Small Loops | 30 |  |  |

|   |             | 1.3.1 Hardware Requirements for Parallelizing Small Loops               | 31 |  |  |

| 2 | Exi         | sting Hardware Cannot Handle Requirements of Small Loops                | 33 |  |  |

|   | <b>2.</b> I | Cache Coherence Protocols                                               | 34 |  |  |

|   | 2.2         | Scalar Operand Networks                                                 | 39 |  |  |

|   |             | 2.2.1 Tile Processor STN                                                | 39 |  |  |

|   |             | 2.2.2 TRIPS OPN                                                         | 40 |  |  |

|   | 2.3         | User-Controlled On-Chip Networks                                        | 4I |  |  |

|   |             | 2.3.1 The Cell Processor Ring Network                                   | 41 |  |  |

|   |             |                                                                         |    |  |  |

|   |     | 2.3.2 Tile Processor UDN                                    | 42  |

|---|-----|-------------------------------------------------------------|-----|

|   | 2.4 | Other Hardware for Accelerating Communication               | 43  |

|   |     | 2.4.1 Multiscalar's Distributed Register File               | 44  |

|   | 2.5 | Conclusion                                                  | 46  |

| 3 | Au  | romatic Parallelization of Irregular Programs with HELIX-RC | 48  |

|   | 3.I | Background and Opportunities                                | 50  |

|   |     | 3.1.1 Limits of Compiler-only Improvements                  | 50  |

|   |     | 3.1.2 Opportunity                                           | 52  |

|   | 3.2 | The HELIX-RC Solution                                       | 57  |

|   |     | 3.2.1 Approach                                              | 57  |

|   |     | 3.2.2 Decoupling Communication From Computation             | 58  |

|   | 3.3 | Compiler                                                    | 61  |

|   | 3.4 | Architecture Enhancements                                   | 63  |

|   |     | 3.4.1 Ring Cache Architecture                               | 64  |

|   |     | 3.4.2 Memory Hierarchy Integration                          | 67  |

|   | 3.5 | Evaluation                                                  | 68  |

|   |     | 3.5.1 Experimental Setup                                    | 68  |

|   |     | 3.5.2 Speedup Analysis                                      | 72  |

|   |     | 3.5.3 Sensitivity to Architectural Parameters               | 75  |

|   |     | 3.5.4 Analysis of Overhead                                  | 76  |

|   | 3.6 | Conclusion                                                  | 77  |

| 4 | Rin | g Cache Detail and Implementation                           | 78  |

|   | 4.I | Memory Hierarchy Integration                                | 79  |

|   |     | 4.1.1 Request and Reply Networks                            | 81  |

|   |     | 4.1.2 Reducing Remote Loads                                 | 82  |

|   | 4.2 | Signal Buffer Implementation                                | 83  |

|   |     | 4.2.1 Synchronization Epochs                                | 83  |

|   |     | 4.2.2 Signal Buffer Architecture                            | 90  |

|   |     | 4.2.3 Signal Buffer Optimization                            | 90  |

|   | 4.3 | Ring Cache Synthesis Evaluation                             | 93  |

|   |     | 4.3.1 Signal Buffer Parameter Sweeps                        | 96  |

|   | 4.4 | Conclusion                                                  | 101 |

| 5 | Fuт  | 'URE D | IRECTIONS FOR HELIX-RC                             | 102 |

|---|------|--------|----------------------------------------------------|-----|

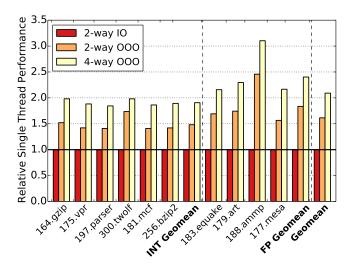

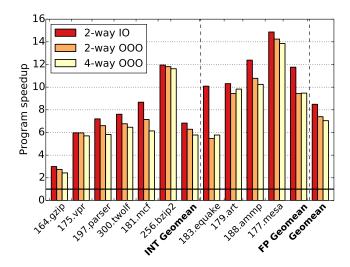

|   | 5.1  | HELD   | X-RC With Out-of-Order Cores                       | 103 |

|   |      | 5.I.I  | Out-of-Order Execution                             | 104 |

|   |      | 5.1.2  | Speedup Degradation in Out-of-Order Cores          | 106 |

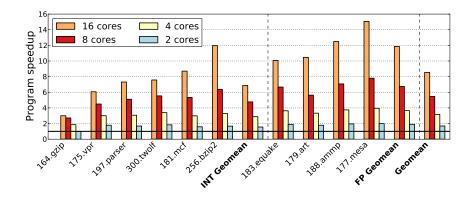

|   | 5.2  | HELD   | X-RC vs. Multiprogram Parallelism                  | 112 |

|   |      | 5.2.I  | Experimental Setup                                 | 113 |

|   |      | 5.2.2  | Evaluation                                         | 115 |

|   | 5.3  | Potent | ial HELIX-RC Research Opportunities                | 119 |

|   |      | 5.3.1  | Compiler Engineering Improvements                  | 119 |

|   |      | 5.3.2  | Compiler Sweeps                                    | 119 |

|   |      | 5.3.3  | Multiple-Loop Execution Model                      | 121 |

|   | ~    |        |                                                    |     |

| 6 | Cor  | ICLUSI | ON                                                 | 123 |

| A | PPEN | dix A  | Ring Cache Technical Report                        | 124 |

|   | А.1  | Introd | uction                                             | 124 |

|   | A.2  | Backgr | ound                                               | 125 |

|   |      | A.2.1  | HELIX Execution Model                              | 126 |

|   |      | A.2.2  | Parallel Code                                      | 128 |

|   |      | A.2.3  | Decoupling Data Communication                      | 129 |

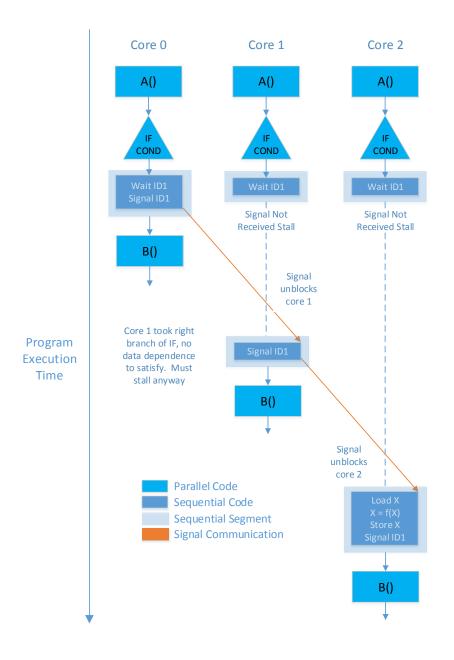

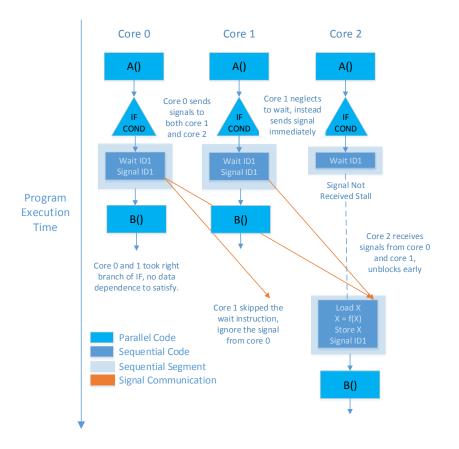

|   |      | A.2.4  | Decoupling Signal Forwarding                       | 133 |

|   | A.3  | Ring ( | Cache Overview                                     | 137 |

|   |      | A.3.1  | Core–Node Interaction                              | 138 |

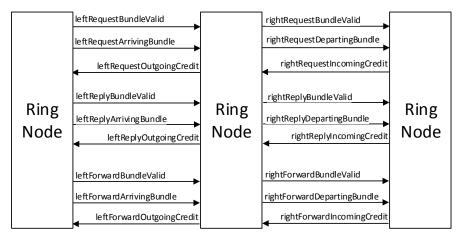

|   |      | A.3.2  | Node to Node Connection                            | 140 |

|   |      | A.3.3  | Memory Hierarchy Integration                       | 142 |

|   | A.4  | Ring ( | Cache Implementation                               | I43 |

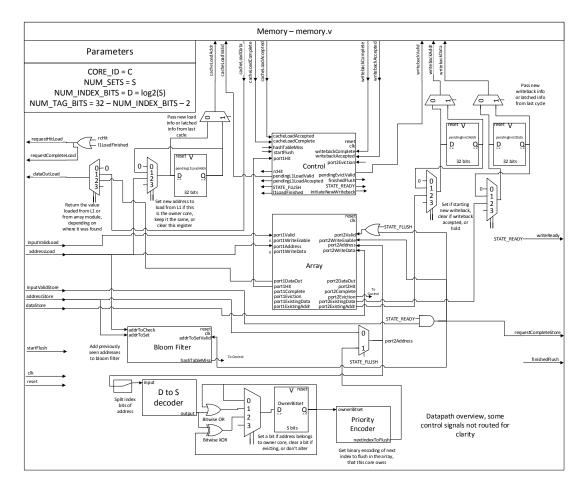

|   | A.5  | Datapa | ath Overview                                       | I44 |

|   | A.6  | Extern | al Interfaces                                      | I45 |

|   |      | А.6.1  | Core Interface                                     | 145 |

|   |      | A.6.2  | L1 Cache Interface                                 | 151 |

|   | A.7  | Netwo  | rk Interfaces                                      | 154 |

|   |      | A.7.1  | Credit Based Flow Control                          | 156 |

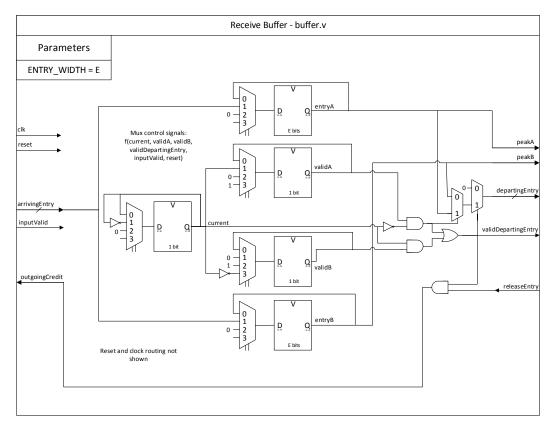

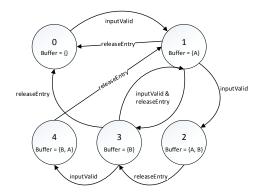

|   |      | A.7.2  | Buffer Module                                      | 159 |

|   | A.8  | Memo   | ry Flushing                                        | 162 |

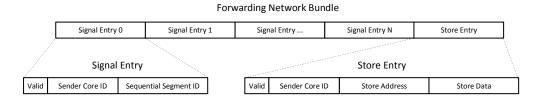

|   | A.9  |        | g Shared Data and Signals - The Forwarding Network | 165 |

|   | -    |        |                                                    | -   |

|                                                             | A.9.1 Netwo                                                                                                                                                 | ork Bundle                           |                                |                                       |             |                                       |                                                                                                                                                                                                                                                                                                                                                     | •••••                 | 168                                                                       |

|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--------------------------------|---------------------------------------|-------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|---------------------------------------------------------------------------|

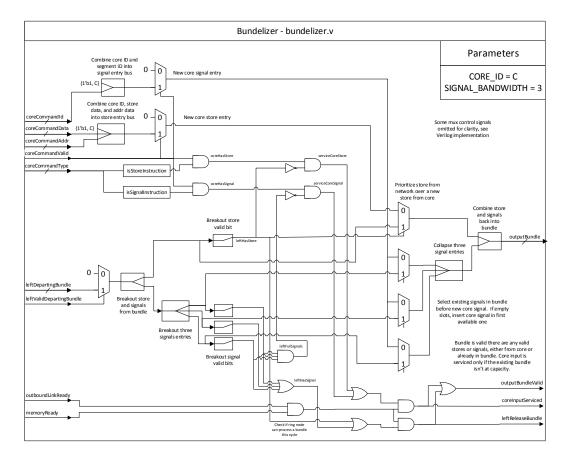

|                                                             | A.9.2 Bundl                                                                                                                                                 | eizer Module                         |                                |                                       |             |                                       |                                                                                                                                                                                                                                                                                                                                                     |                       | 168                                                                       |

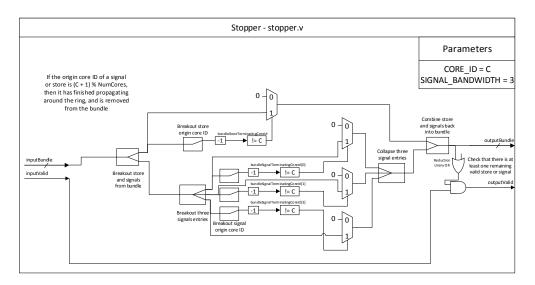

|                                                             | A.9.3 Stopp                                                                                                                                                 | er Module                            |                                |                                       | • • • •     |                                       |                                                                                                                                                                                                                                                                                                                                                     |                       | . I72                                                                     |

| А.10                                                        | Loading Share                                                                                                                                               | d Data - The Req                     | uest/Reply                     | y Networ                              | ks          |                                       |                                                                                                                                                                                                                                                                                                                                                     |                       | 173                                                                       |

|                                                             | A.10.1 Reque                                                                                                                                                | st and Reply Netv                    | vorks                          |                                       | • • • •     |                                       |                                                                                                                                                                                                                                                                                                                                                     |                       | 176                                                                       |

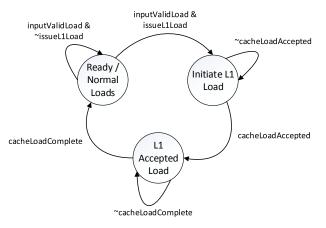

|                                                             | A.10.2 Load                                                                                                                                                 | Jnit Module                          |                                |                                       |             |                                       |                                                                                                                                                                                                                                                                                                                                                     | ••••                  | 180                                                                       |

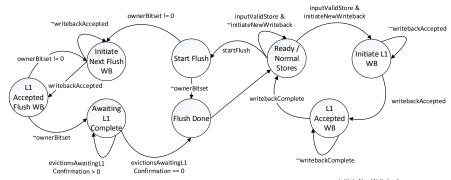

| А.п                                                         | Ring Cache M                                                                                                                                                | emory                                |                                |                                       | • • • •     |                                       |                                                                                                                                                                                                                                                                                                                                                     |                       | 192                                                                       |

|                                                             | A.II.I Memo                                                                                                                                                 | ry Module                            |                                |                                       |             |                                       |                                                                                                                                                                                                                                                                                                                                                     | ••••                  | 195                                                                       |

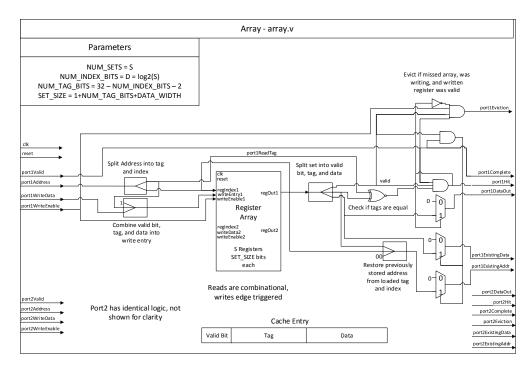

|                                                             | A.11.2 Array                                                                                                                                                | Module                               |                                |                                       |             |                                       |                                                                                                                                                                                                                                                                                                                                                     | ••••                  | 204                                                                       |

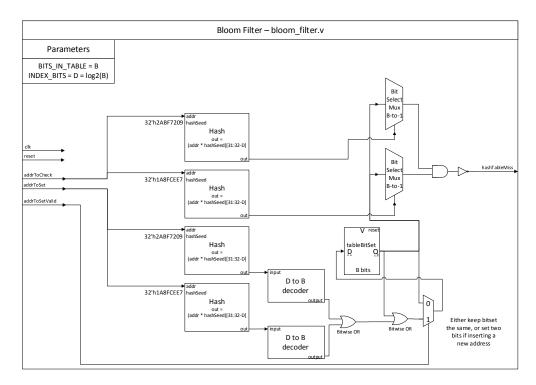

|                                                             | A.11.3 Bloom                                                                                                                                                | Filter Module .                      |                                |                                       |             |                                       |                                                                                                                                                                                                                                                                                                                                                     | ••••                  | 207                                                                       |

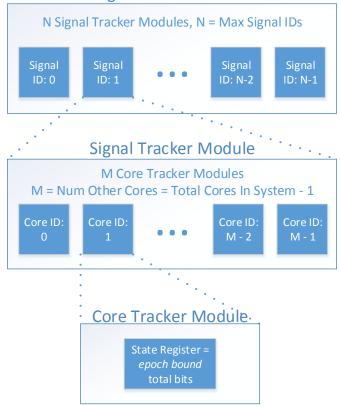

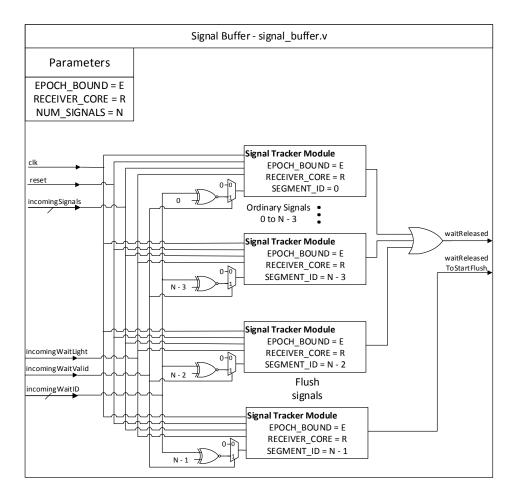

| A.12                                                        | Signal Buffer                                                                                                                                               |                                      |                                |                                       |             |                                       |                                                                                                                                                                                                                                                                                                                                                     |                       | 212                                                                       |

|                                                             | A.12.1 Synch                                                                                                                                                | ronization Epochs                    |                                |                                       |             |                                       |                                                                                                                                                                                                                                                                                                                                                     |                       | 212                                                                       |

|                                                             | A.12.2 Signal                                                                                                                                               | Buffer Module .                      |                                |                                       |             |                                       |                                                                                                                                                                                                                                                                                                                                                     |                       | 219                                                                       |

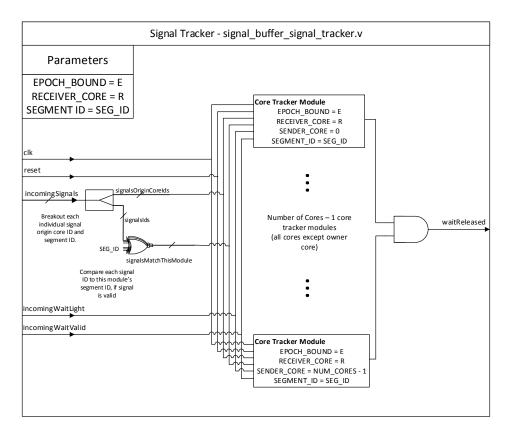

|                                                             | A.12.3 Signal                                                                                                                                               | Tracker Module                       |                                |                                       |             |                                       |                                                                                                                                                                                                                                                                                                                                                     | ••••                  | 226                                                                       |

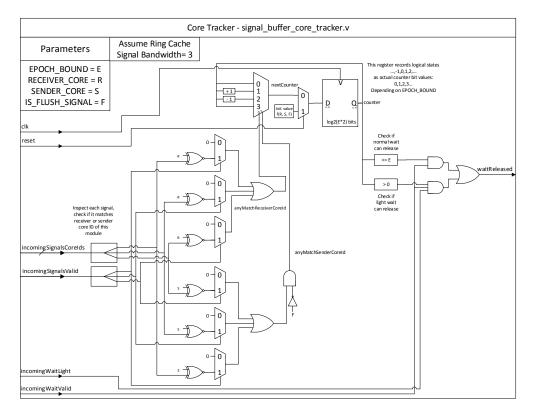

|                                                             | A.12.4 Core 7                                                                                                                                               | fracker Module .                     |                                |                                       |             |                                       |                                                                                                                                                                                                                                                                                                                                                     | ••••                  | 227                                                                       |

|                                                             | A.12.5 Signal                                                                                                                                               | Buffer Optimizati                    | ons                            |                                       |             |                                       |                                                                                                                                                                                                                                                                                                                                                     | ••••                  | 232                                                                       |

|                                                             | A.12.6 Previo                                                                                                                                               | us Implementatio                     | ns                             |                                       | ••••        |                                       |                                                                                                                                                                                                                                                                                                                                                     |                       | 234                                                                       |

| A.13                                                        | OS/Multiprog                                                                                                                                                | gramming Conside                     | erations .                     |                                       | ••••        |                                       |                                                                                                                                                                                                                                                                                                                                                     |                       | 235                                                                       |

| A.14                                                        | Synthesis Res                                                                                                                                               | ılts                                 |                                |                                       |             |                                       |                                                                                                                                                                                                                                                                                                                                                     | ••••                  | 236                                                                       |

|                                                             | -                                                                                                                                                           | nce Design                           |                                |                                       |             |                                       |                                                                                                                                                                                                                                                                                                                                                     |                       |                                                                           |

|                                                             | A.14.1 Refere                                                                                                                                               |                                      |                                |                                       |             |                                       | • • •                                                                                                                                                                                                                                                                                                                                               | •••••                 | . 236                                                                     |

|                                                             |                                                                                                                                                             | Buffer Parameter                     |                                |                                       |             |                                       |                                                                                                                                                                                                                                                                                                                                                     |                       |                                                                           |

| Appen                                                       | A.14.2 Signal                                                                                                                                               | •                                    | Sweeps .                       |                                       |             |                                       |                                                                                                                                                                                                                                                                                                                                                     |                       | 240                                                                       |

| Appens<br>B.1                                               | A.14.2 Signal<br>DIX B RING                                                                                                                                 | Buffer Parameter<br>Cache Verilo     | Sweeps .<br>G CODE             |                                       | ••••        |                                       |                                                                                                                                                                                                                                                                                                                                                     |                       | 240<br>245                                                                |

| _                                                           | A.14.2 Signal<br>DIX B RING<br>defines.v                                                                                                                    | Buffer Parameter<br>CACHE VERILO     | Sweeps .<br>G CODE<br>         |                                       | ••••        |                                       |                                                                                                                                                                                                                                                                                                                                                     |                       | 240<br>245<br>246                                                         |

| В.1<br>В.2                                                  | A.14.2 Signal<br>DIX B RING<br>defines.v<br>ring_cache.v                                                                                                    | Buffer Parameter<br>Cache Verilo<br> | Sweeps .<br>G CODE<br>         |                                       | • • • • •   | · · · · ·                             | <br><br>                                                                                                                                                                                                                                                                                                                                            | · · · · · · · ·       | 240<br>245<br>246<br>248                                                  |

| В.1                                                         | A.14.2 Signal<br>DIX B RING<br>defines.v<br>ring_cache.v<br>buffer.v                                                                                        | Buffer Parameter<br>CACHE VERILO     | Sweeps .<br>G CODE<br><br>     | · · · · ·                             | · · · · ·   | · · · · ·                             | · · · ·<br>· · · ·                                                                                                                                                                                                                                                                                                                                  | · · · · · · · · ·     | 240<br>245<br>246<br>248<br>248<br>258                                    |

| B.1<br>B.2<br>B.3                                           | A.14.2 Signal<br>DIX B RING<br>defines.v<br>ring_cache.v<br>buffer.v<br>bundleizer.v                                                                        | Buffer Parameter                     | Sweeps .<br>G CODE<br><br>     | · · · · · · · · · · · · · · · · · · · | · · · · · · | · · · · ·                             | · · · ·<br>· · · ·<br>· · · ·                                                                                                                                                                                                                                                                                                                       | · · · · · · · · ·     | 240<br>245<br>246<br>248<br>248<br>258<br>262                             |

| B.1<br>B.2<br>B.3<br>B.4                                    | A.14.2 Signal<br>DIX B RING<br>defines.v<br>ring_cache.v<br>buffer.v<br>bundleizer.v<br>stopper.v                                                           | Buffer Parameter<br>CACHE VERILO     | Sweeps .<br>G CODE<br><br><br> | <br><br>                              | · · · · · · | · · · · · · · · · · · · · · · · · · · | · · · ·                                                                                                                                                                                                                                                                                                                                             | · · · · · · · · ·     | 240<br>245<br>246<br>248<br>248<br>258<br>262<br>266                      |

| B.1<br>B.2<br>B.3<br>B.4<br>B.5                             | A.14.2 Signal<br>DIX B RING<br>defines.v<br>ring_cache.v<br>buffer.v<br>bundleizer.v<br>stopper.v<br>load_unit.v .                                          | Buffer Parameter                     | Sweeps .<br>G CODE<br><br><br> | · · · · · · · · · · · · · · · · · · · | · · · · · · | · · · · · · · · · · · · · · · · · · · | · · · ·<br>· · · ·<br>· · · ·                                                                                                                                                                                                                                                                                                                       | · · · · · · · · ·     | 240<br>245<br>246<br>248<br>248<br>258<br>262<br>266<br>268               |

| B.1<br>B.2<br>B.3<br>B.4<br>B.5<br>B.6                      | A.14.2 Signal<br>DIX B RING<br>defines.v<br>ring_cache.v<br>buffer.v<br>bundleizer.v<br>stopper.v<br>load_unit.v .                                          | Buffer Parameter                     | Sweeps .<br>G CODE             | · · · · · · · · · · · · · · · · · · · | · · · · · · | · · · · · · · · · · · · · · · · · · · | · · · ·<br>· · · ·<br>· · · ·<br>· · · ·                                                                                                                                                                                                                                                                                                            | · · · · · · · · · ·   | 240<br>245<br>246<br>248<br>258<br>262<br>266<br>268<br>268               |

| B.1<br>B.2<br>B.3<br>B.4<br>B.5<br>B.6<br>B.7               | A.14.2 Signal<br>DIX B RING<br>defines.v<br>ring_cache.v<br>buffer.v<br>bundleizer.v<br>stopper.v<br>load_unit.v .<br>memory.v                              | Buffer Parameter                     | Sweeps .<br>G CODE<br><br><br> | · · · · · · · · · · · · · · · · · · · |             | · · · · · · · · · · · · · · · · · · · | · · · ·<br>· · · ·                                                                                                                                                                                                                                                                                      | · · · · · · · · · · · | 240<br>245<br>246<br>248<br>258<br>262<br>266<br>266<br>268<br>275<br>285 |

| B.1<br>B.2<br>B.3<br>B.4<br>B.5<br>B.6<br>B.7<br>B.8<br>B.9 | A.14.2 Signal<br>DIX B RING<br>defines.v<br>ring_cache.v<br>buffer.v<br>bundleizer.v<br>stopper.v<br>load_unit.v .<br>memory.v<br>priority_encod<br>array.v | Buffer Parameter                     | Sweeps .<br>G CODE<br><br><br> | · · · · · · · · · · · · · · · · · · · | · · · · · · | · · · · · · · · · · · · · · · · · · · | <ul> <li></li> <li></li></ul> |                       | 240<br>245<br>246<br>248<br>258<br>262<br>266<br>268<br>275<br>285<br>286 |

| B.12 signal_buffer.v                | 293 |

|-------------------------------------|-----|

| B.13 signal_buffer_signal_tracker.v | 296 |

| B.14 signal_buffer_core_tracker.v   | 299 |

| References                          | 309 |

## Listing of figures

| Ι        | Historical clock frequency scaling trend                                       | 2  |

|----------|--------------------------------------------------------------------------------|----|

| 2        | Historical single-threaded performance scaling.                                | 3  |

| 3        | Number of cores on a single die                                                | 4  |

| I.I      | A candidate loop for DOACROSS parallelization                                  | 13 |

| 1.2      | Decomposition of loop iteration by DOACROSS                                    | 13 |

| 1.3      | A loop schedule for DOACROSS parallelization                                   | 15 |

| I.4      | A loop schedule for DOACROSS parallelization with high communication latency . | 16 |

| 1.5      | A loop schedule for DOACROSS parallelization with a small parallel region      | 17 |

| 1.6      | Decomposition of loop iteration by HELIX                                       | 18 |

| I.7      | A loop schedule for HELIX parallelization with a small parallel region         | 18 |

| 1.8      | Decomposition of loop iteration by DSWP                                        | 19 |

| 1.9      | A loop schedule for DSWP parallelization with unbalanced stages                | 20 |

| I.IO     | A loop schedule for DSWP parallelization with balanced stages                  | 21 |

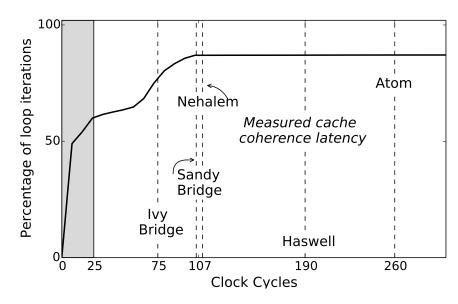

| 2.I      | Decomposition of loop iteration by HELIX with synchronization instructions     | 36 |

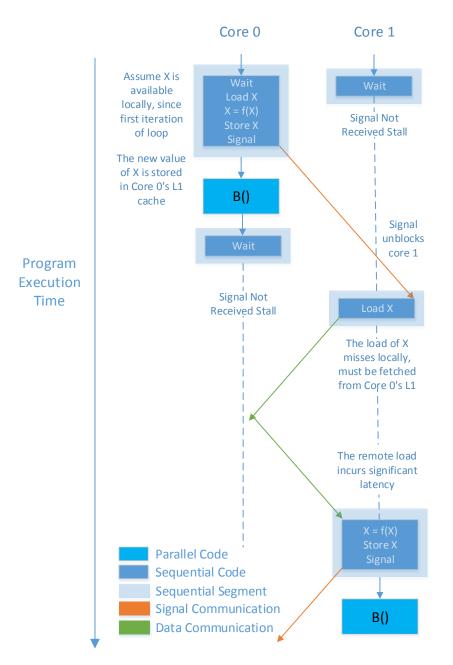

| 2.2      | HELIX communication penalty with reactive data transfer                        | 37 |

| 2.3      | HELIX communication penalty with hypothetical proactive data transfer          | 38 |

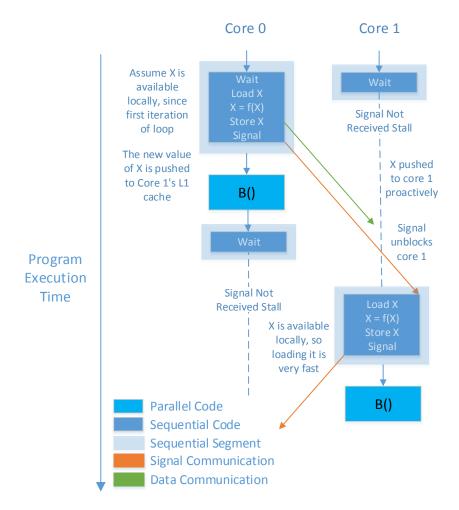

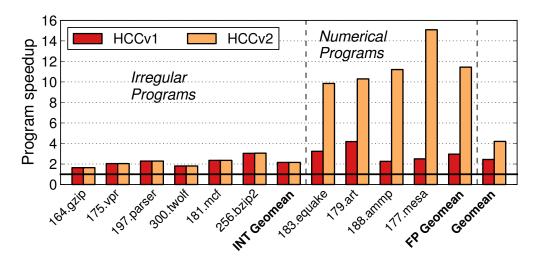

| 2.4      | Multiscalar Distributed Register File                                          | 44 |

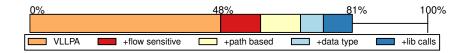

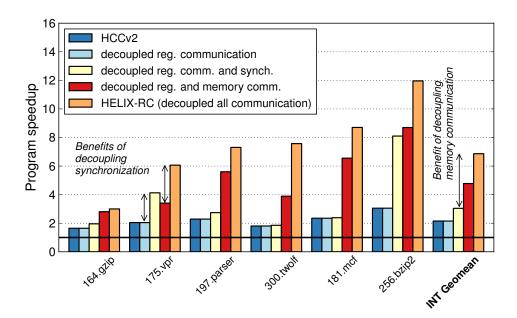

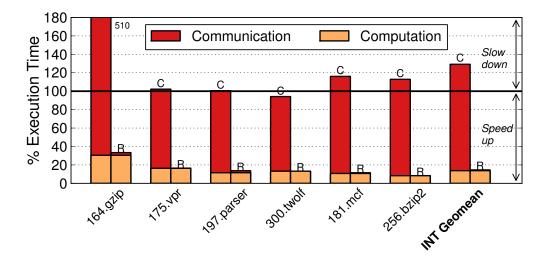

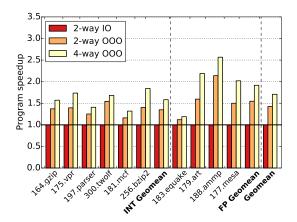

| 3.1      | Augmenting the HELIX compiler does not improve irregular program performance   | 51 |

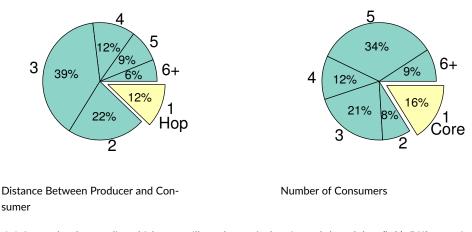

| 3.2      | Accuracy of dependence analysis for small hot loops in irregular benchmarks    | 54 |

| 3.3      | Short loop iterations in SPECint 2000                                          | 54 |

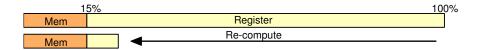

| 3.4      | Predictability of variables reduces register communication in small hot loops  | 55 |

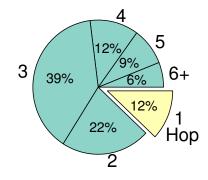

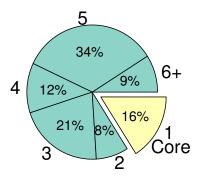

| 3.5      | Distribution of required communication distance between 16 cores               | 55 |

| 3.6      | Most shared data is consumed by multiple cores                                 | 56 |

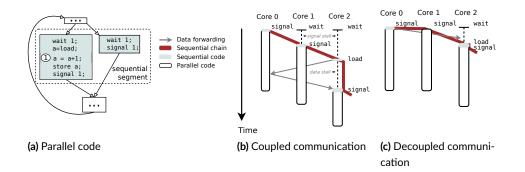

| 3.7      | Example of decoupled data and signal communication.                            | 60 |

| 3.8      |                                                                                | (  |

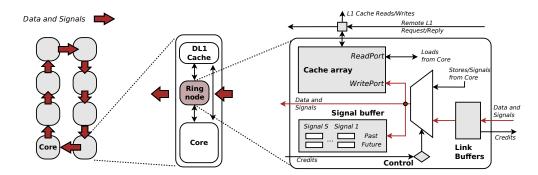

| <i>J</i> | Ring cache architecture overview                                               | 64 |

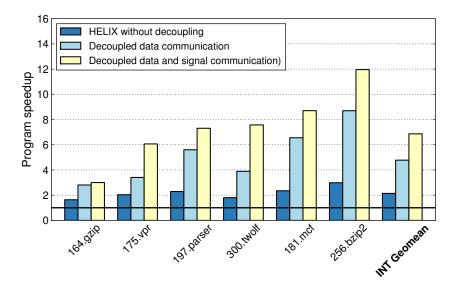

| 3.10         | Breakdown of benefits of decoupling communication from computation                | 71  |

|--------------|-----------------------------------------------------------------------------------|-----|

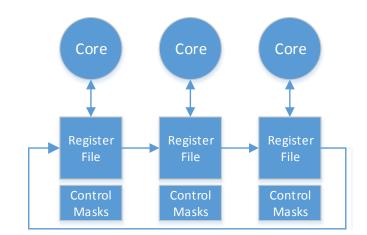

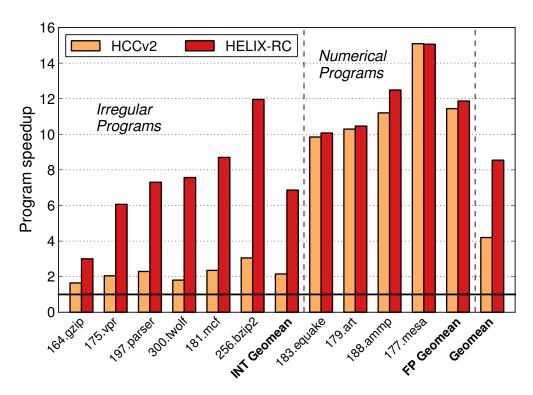

| 3.11         | Code generated assuming the existence of ring cache slows down on normal hardware | 73  |

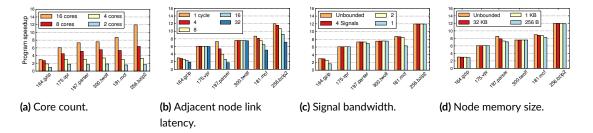

| 3.12         | Speedup sensitivity to core count and ring cache parameters                       | 75  |

| 3.13         | Breakdown of overheads that prevent HELIX-RC from achieving ideal speedup         | 75  |

| 4 <b>.</b> I | Ring cache must be carefully integrated the normal cache hierarchy                | 80  |

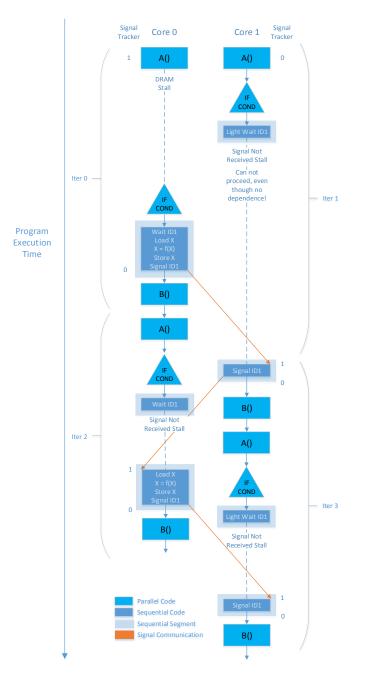

| 4.2          | An empty sequential segment is protected only be a <i>light wait</i>              | 84  |

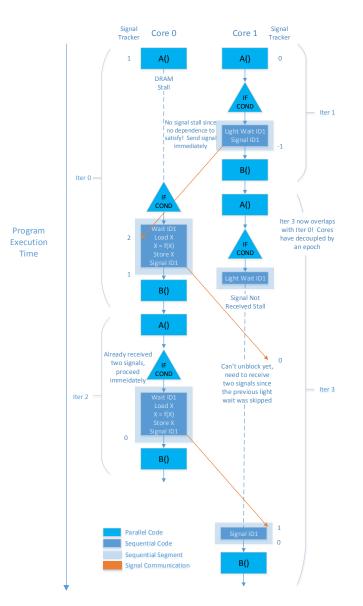

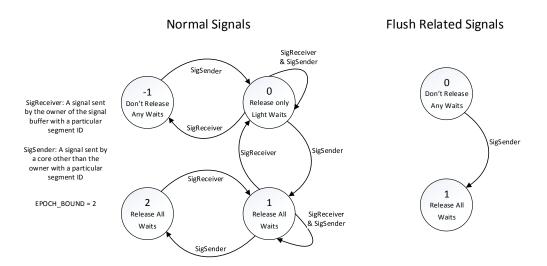

| 4.3          | Cores constrained to a single epoch have reduced performance                      | 87  |

| 4.4          | Cores that can decouple by an additional epoch have higher performance            | 89  |

| 4.5          | Signal Buffer architecture                                                        | 91  |

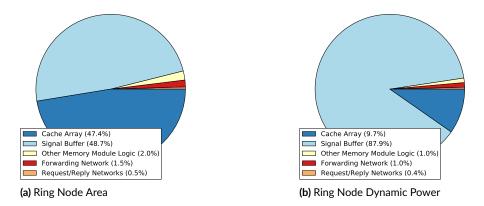

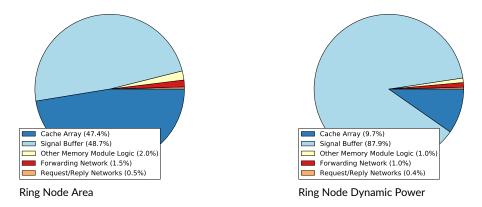

| 4.6          | Synthesized ring cache power and area                                             | 96  |

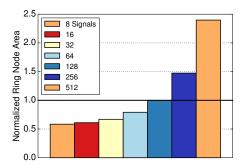

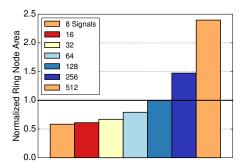

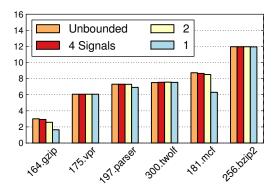

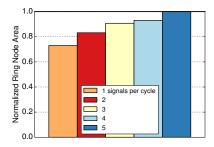

| 4.7          | Total ring node area as total signal ID capacity is swept from 8 to 512           | 97  |

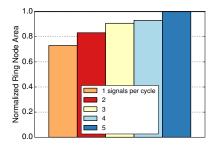

| 4.8          | Increasing signal bandwidth increases signal buffer and network buffer sizes      | 98  |

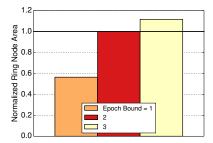

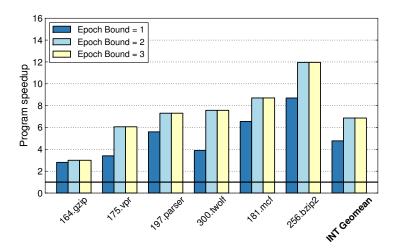

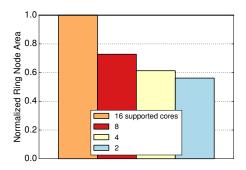

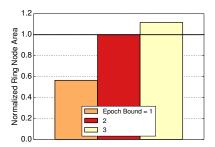

| 4.9          | Increased decoupling increases ring cache area                                    | 99  |

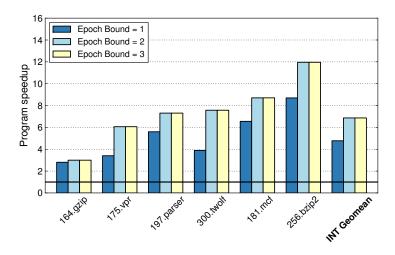

| 4.10         | Speedups plateau at two epochs of decoupling                                      | 99  |

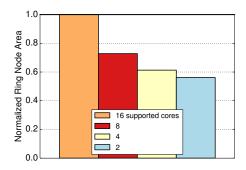

| 4.II         | Ring cache area reduces when there are fewer cores in the system                  | 100 |

| 5.1          | Singled-threaded SPECint 2000 performance on different core types                 | 103 |

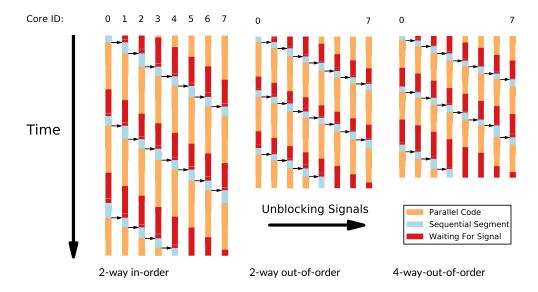

| 5.2          | HELIX-RC SPEC CPU2000 speedups on different core types                            | 104 |

| 5.3          | Overall HELIX-RC performance always increases for higher performance cores        | 105 |

| 5.4          | Performance bottlenecks on a single sequential segment                            | 107 |

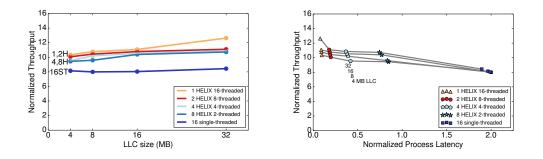

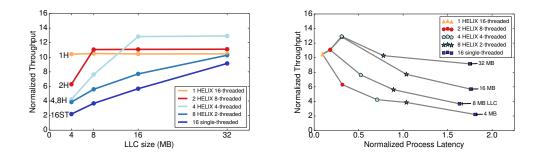

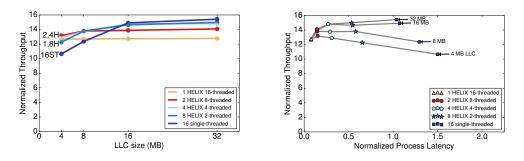

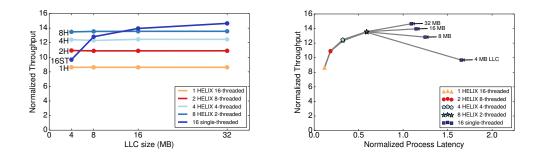

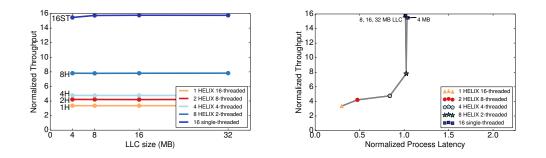

| 5.5          | Program latency vs. multicore throughput for 183.equake                           | 115 |

| 5.6          | Program latency vs. multicore throughput for 179.art                              | 116 |

| 5.7          | Program latency vs. multicore throughput for 188.ammp                             | 116 |

| 5.8          | Program latency vs. multicore throughput for 197.parser                           | 117 |

| 5.9          | Program latency vs. multicore throughput for 164.gzip                             | 118 |

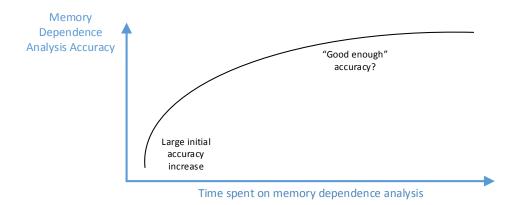

| 5.10         | HELIX's memory dependence analysis encounters diminishing returns                 | 120 |

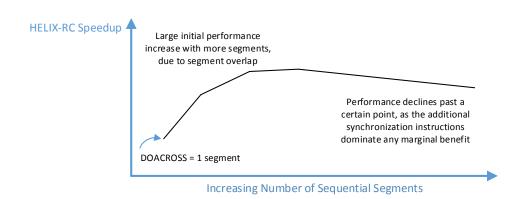

| 5.11         | Splitting sequential segments improves HELIX-RC speedups up to a certain point .  | 120 |

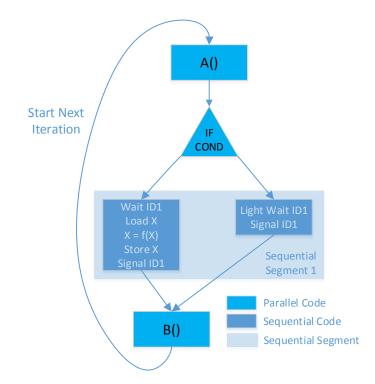

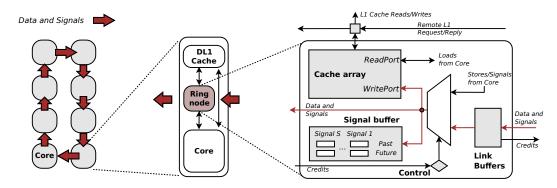

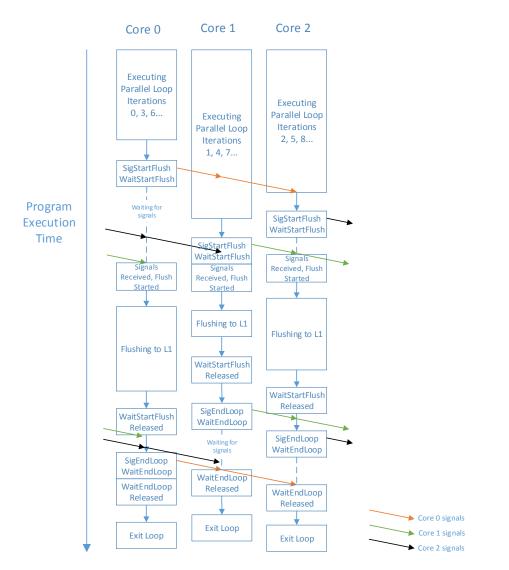

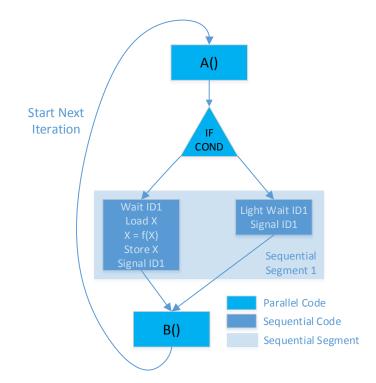

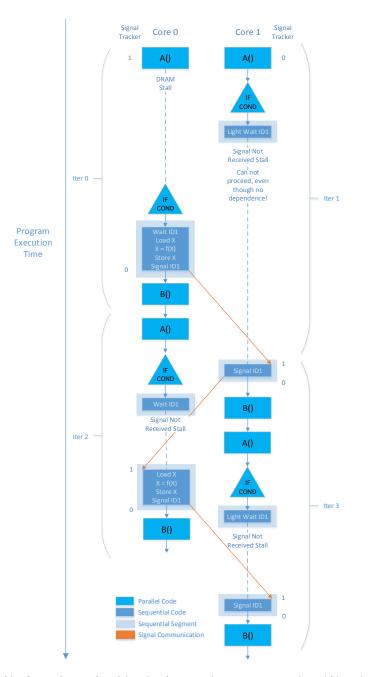

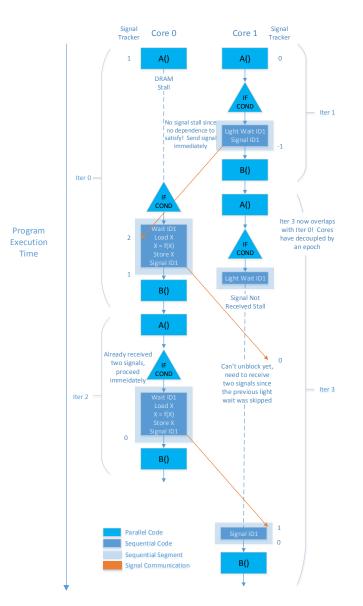

| А.1          | HELIX execution model                                                             | 127 |

| A.2          | A HELIX paralellized loop                                                         | 128 |

| A.3          | Reactive communication produces worse performance than proactive communication    | 130 |

| A.4          | Shared data is often accessed by an unpredictable number of cores                 | 131 |

| A.5          | Decoupling data and synchronization communication is vital for speedups           | 132 |

| A.6          | Sequential forwarding chains limit HELIX-style parallelization                    | 134 |

| A.7 Breaking sequential forwarding chains improves parallel performance               | 135 |

|---------------------------------------------------------------------------------------|-----|

| A.8 Ring cache architecture overview                                                  | 137 |

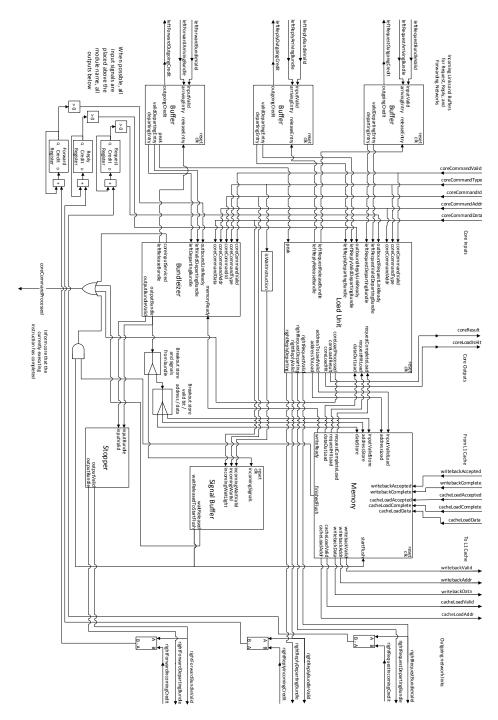

| A.9 Schematic of top level ring cache module.                                         | 146 |

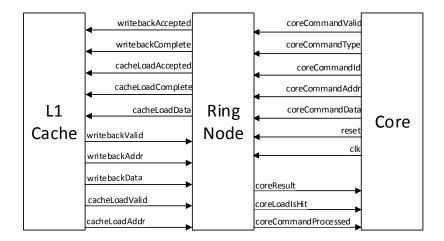

| A.10 A ring node has direct connections to its local core and its local L1 cache.     | I47 |

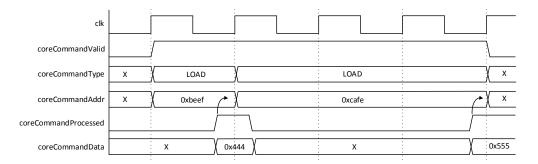

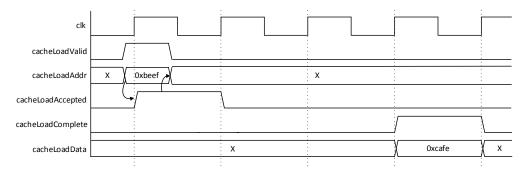

| A.11 Load timing diagram for ring cache hit                                           | 150 |

| A.12 Load from ring node to L1 cache                                                  | 151 |

| A.13 A ring node is connected with its neighbor ring node by three different networks | 155 |

| A.14 Schematic of the buffer module                                                   | 160 |

| A.15 Control FSM for buffer module                                                    | 161 |

| A.16 Ring cache flush timing diagram                                                  | 163 |

| A.17 Forwarding network bundle                                                        | 165 |

| A.18 Schematic of bundleizer module                                                   | 166 |

| A.19 Schematic of stopper module                                                      | 167 |

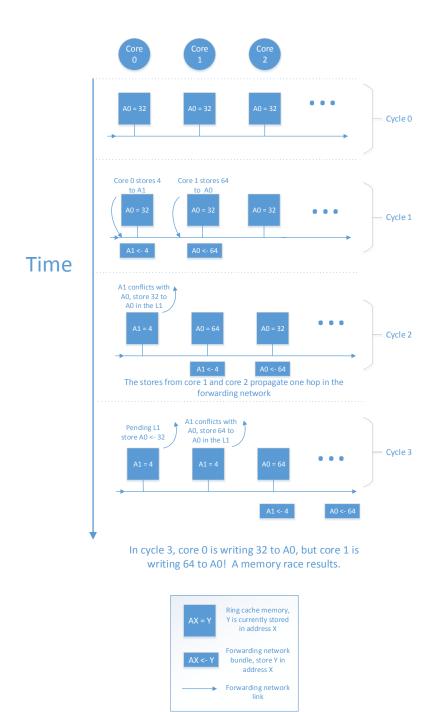

| A.20 Incorrect ring cache memory hierarchy integration                                | 174 |

| A.21 Request/reply network bundles                                                    | 176 |

| A.22 Schematic of load unit module                                                    | 181 |

| A.23 Load unit FSM for local loads                                                    | 187 |

| A.24 Load unit FSM for remote loads                                                   | 188 |

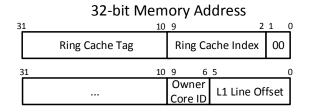

| A.25 Cache bits and owner bits for a ring cache memory address                        | 192 |

| A.26 Schematic of memory module                                                       | 196 |

| A.27 Memory module FSM for loads                                                      | 202 |

| A.28 Memory module FSM for stores and flushes                                         | 203 |

| A.29 Schematic of array module                                                        | 204 |

| A.30 Schematic of bloom filter module                                                 | 208 |

| A.31 Empty sequential segments are protected by modified light waits                  | 213 |

| A.32 One bit of signal buffering allows cores to decouple by only one epoch           | 214 |

| A.33 Two bits of signal buffering allows cores to decouple by two epochs              | 215 |

| A.34 Schematic of signal buffer                                                       | 220 |

| A.35 Signal entry bits                                                                | 220 |

| A.36 Schematic of signal tracker module                                               | 221 |

| A.37 Schematic of core tracker module                                                 | 222 |

| A.38 Core tracker FSM                                                                 | 223 |

| A.39 Core tracker module initialization                                               | 223 |

| A.40 Power and area for a single ring node                                            | 239 |

| A.41 Total ring node area as total signal ID capacity is swept from 8 to 512          | 240 |

|---------------------------------------------------------------------------------------|-----|

| A.42 Sensitivity of signal bandwidth on speedup                                       | 24I |

| A.43 Increasing signal bandwidth increases the signal buffer and network buffer sizes | 242 |

| A.44 Decoupling synchronization from one to two epochs increases area significantly   | 242 |

| A.45 Decoupling synchronization up to two epochs increases speedups                   | 243 |

| A.46 HELIX-RC scales relatively well on a small number of cores                       | 244 |

| A.47 Signal buffer area is linear with number of supported cores                      | 244 |

## Listing of tables

| 3.1 | Characteristics of parallelized benchmarks         | 69  |

|-----|----------------------------------------------------|-----|

|     | Ring cache parameters for the reference design     |     |

| 4.2 | Synthesis results for a single reference ring node | 95  |

| 5.1 | Working set sizes for SPECint 2000                 | 114 |

| А.1 | Ring Cache parameters for the reference design.    | 237 |

| A.2 | Synthesis results for a single reference ring node | 238 |

### Previous Work

#### Portions of this dissertation have appeared in:

SIMONE CAMPANONI, KEVIN BROWNELL, SVILEN KANEV, TIMOTHY M. JONES, GU-YEON WEI, AND DAVID BROOKS. "HELIX-RC: AN ARCHITECTURE-COMPILER CO-DESIGN FOR AUTOMATIC PARALLELIZATION OF IRREGULAR PROGRAMS." IN PROCEEDING OF THE 41ST ANNUAL INTERNATIONAL SYMPOSIUM ON COMPUTER ARCHITECUTURE, PP. 217-228. IEEE Press, 2014.

AND

Kevin Brownell. "Ring Cache Technical Report."

#### Portions of this dissertation are in submission to:

ACM Transactions on Architecture and Code Optimization (TACO)

## **O** Introduction

IN 1965, GORDON MOORE OBSERVED THAT THE NUMBER OF TRANSISTORS per unit area on an integrated circuit was increasing by a factor of two year after year [42]. Although the timeframe of his original forecast was not entirely correct, Moore's Law heralded the general trend of regular doublings of transistor density as the semiconductor industry strived to integrate more and more transistors. After nearly 50 years of process technology improvements, the number of transistors in a chip has increased from hundreds in the 1960s to well over a billion today. Along with the explosion in the transistor count came a seemingly relentless increase in computing performance. A portion of this increase was due to CPU architecture improvements, but a larger portion was the result of faster and faster transistors [5].

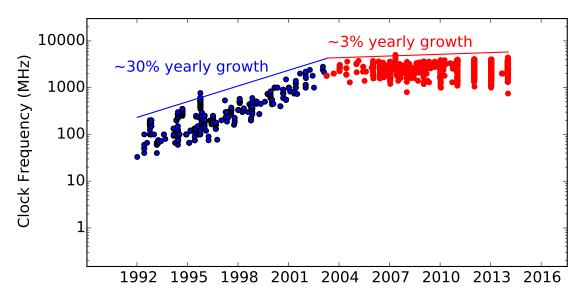

**Figure 1:** Due to a breakdown of Dennard scaling, the growth rate of nominal CPU clock frequencies dramatically decreased about a decade ago. Rising power density made further increases infeasible. Historical data from the Stanford CPUDB project [17].

For decades, smaller transistor sizes provided what seemed to be a free lunch. As feature sizes decreased by a predictable factor, so too did capacitance. By decreasing the supply and threshold voltages by the same factor, the speed of transistors could also be increased and their power consumption decreased. Through this process, known as Dennard scaling [18], the power density of a chip remained constant as clock frequencies steadily increased. This resulted in reliable single-threaded performance increases—every new process technology meant that the previous year's programs now ran faster.

#### 0.1 Performance Scaling Hits a Speed Bump

Unfortunately, in the early 2000s, Dennard scaling began to break down. Due to increasing amounts of leakage current, the previously steadily decreasing threshold voltage began to plateau [36]. Consequently, clock speeds could not continue to increase, or so too would the power density of a chip. Given limitations in the ability to cool a chip beyond a certain power ceiling, the industry had no

**Figure 2:** The "power" wall resulted in sharply decreased historical single-threaded performance gains. CPU performance has been normalized across multiple generations of the SPECint benchmark suite. Only CPUs from the database with SPECint numbers are plotted. Historical data from the Stanford CPUDB project [17].

choice but to significantly reduce the aggressiveness of clock frequency increases. Figure 1 shows the dramatic slowdown in clock frequency gains that resulted from the breakdown of Dennard scaling. Nominal CPU frequencies plateaued around 2004, in the 3–4 GHz range.

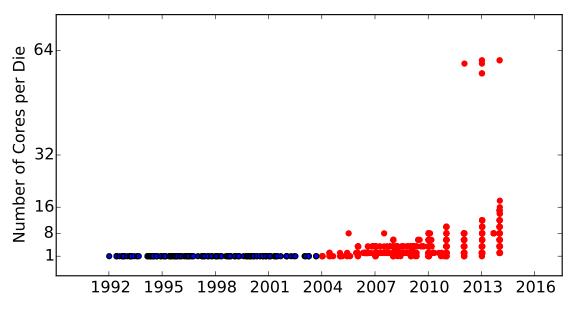

Hand in hand with stalls in clock frequency gains, single-thread performance gains stalled as well. Figure 2 shows normalized single-threaded performance around this time period for a large variety of CPUs. The performance data, taken from the Stanford CPUDB project [17], has been normalized across multiple generations of the SPECint benchmark suite. Prior to 2004, when clock frequencies were still increasing, overall single-threaded CPU performance increased by nearly 46% per year. After Dennard scaling broke down, performance still increased, but at the much slower rate of 19% per year. Had the original 46% trend continued past 2004, CPU performance would be 5–10× higher today. With this "power wall" blocking single-threaded performance gains, the industry decided to instead use their still growing transistor budget to integrate multiple identical general-purpose cores on a single die. Figure 3 shows the dramatic increase in the number of cores

**Figure 3:** Facing the power wall, industry transitioned to placing multiple cores on a single die. Historical data from the Stanford CPUDB project [17], representing only general purpose CPUs.

starting in 2004. Since clock frequency ultimately has a cubic relationship with power, multiple cores clocked at lower frequencies may still fit within a fixed power budget while at the same time providing higher theoretical computing performance. This higher performance can only be realized, however, if the multiple cores can all be utilized simultaneously, at least for some fraction of the time.

#### 0.2 EXTRACTING MULTICORE PERFORMANCE

Broadly, there are two primary ways to extract performance from a general-purpose multicore processor. First, a single program can be decomposed into different execution threads to exploit threadlevel parallelism (TLP) to gain performance on multiple cores. Alternatively, multiple programs can independently use different cores at the same time. Although these techniques are usually easily applicable to simple and regular programs, they are often lacking for irregular workloads that contain complex data and control flows.

#### 0.2.1 SINGLE-PROGRAM PARALLELISM

Although parallel computing had already long existed, the introduction of multiple cores in a single chip opened the door for finer-grained parallel computing, which previously had been limited to workloads that could tolerate the long communication latencies between different chips and machines. Decomposing a program into multiple threads, each of which can run on a different core, can significantly improve the performance of a single program running on a multicore chip. An increasing variety of modern tools and programming models have been introduced to facilitate multithreaded programming. Depending on workload complexity and available programmer time as well as programmer ability, some programs are easier to split into threads than others. In general, multithreaded programs are much more difficult to create, maintain, and debug than single-threaded programs. Additionally, it is often difficult for programmers to create balanced amounts of work for the threads, so that the realized performance increase from multithreading is often far less than the theoretical performance increase. As a result, programmers often feel that it is not worth the effort needed to make a program parallel, and they tend instead to rely entirely on the slower single-thread performance scaling to gain performance.

#### 0.2.2 Multiple-Program Parallelism

An easier way to extract multicore performance is through the use of multiple-program parallelism: instead of trying to parallelize a single program, multiple programs can be run on different cores at the same time. Even though single-threaded performance does not increase, the total throughput does, so multicore computing resources are not wasted. Multiple-program parallelism also has the benefit of scaling relatively well as long as the multiple programs do not interact destructively. As more cores are added to a chip, the total throughput may increase by a predictable amount. Unfortunately, the large amount of shared resources on a multicore processor (shared caches, DRAM bandwidth, on-chip network bandwidth, etc.) can result in less than ideal throughput scaling.

#### 0.3 Core Utilization Remains Low

Both single-program and multiple-program parallelism have been insufficient for keeping multicore utilization high. For datacenter-scale computing, core utilization is usually well below 50% on average [3]. One reason for the low utilization is the desire to isolate latency-sensitive applications, so that processors are intentionally underprovisioned to ensure that multiple programs don't overly contend for shared resources [39]. Another reason is the desire to ensure that spare computing capacity is available if demand increases. Either way, the result is that cores sit idle.

In the mobile realm (e.g., phones and tablets), core utilization is dramatically lower than one would expect, considering the ever-increasing number of cores generation after generation. Studies have shown that although popular applications tend to have some TLP, most mobile applications use less than two cores on average [20]. Additionally, typical mobile device interactions generally encourage use of only a single application at a time, so multiple-program parallelism is also limited. The theoretical performance from having up to 8 cores on a single mobile device is thus largely wasted.

#### 0.4 Automatic Parallelization Can Improve Utilization

Given the difficulty of manually extracting TLP from sequential code, automatic parallelization offers a promising route for increasing multicore utilization. Not only can automatic thread extraction make use of an increasing number of cores; it can also increase single-program performance. Historically, a variety of techniques sought to parallelize programs across multiple chips and/or multiple machines by automatically extracting threads [16, 28]. Each of these extracted threads would run on a different processor/machine, and they would communicate when necessary for synchronization or sharing data. While these techniques realized some success, they were as a rule only applicable to workloads that had minimal communication or synchronization requirements, generally those with very regular control and data flow. Due to the large latency between chips and machines, if a program required frequent or irregular communication, the time spent communicating would dominate the total execution time.

As the multicore era took hold, there was renewed interest in leveraging automatic parallelization to regain lost single-thread performance. With multiple cores close together on a die, communication costs decrease and inter-core bandwidth increases, making previously unscalable techniques more realistic for a larger variety of workloads. A growing number of compiler techniques to extract threads have proved to be feasible for previously unparallelizable irregular programs, most of these techniques variations of either cyclic-multithreading or pipelined-multithreading parallelism [12, 46, 48, 60]. Efforts have also been made to extract parallelism by combining compiler techniques with custom hardware [25, 38, 54, 53, 56], with some success. Despite this revitalized interest, however, there is still much room for improvement—specifically, there is a need for a technique that 1) is broadly applicable to a large number of irregular programs, 2) produces high speedups on those programs, and 3) doesn't require large changes to existing general-purpose multicore architectures.

#### 0.5 Contribution of the Dissertation

In this dissertation, I first examine a recent compiler technique for automatic parallelization called HELIX [12], detailing its intrinsic performance limitations and bottlenecks. In order to boost the performance of HELIX, I propose a co-design comprising an improved version of HELIX and a light-weight hardware extension. This co-design, called HELIX-RC, boosts the speedup of sequentially written irregular code—that is, code that contains complex data and control flows—from  $2 \times$  to  $6.85 \times$ , which buys back a large portion of the single-threaded performance gains lost over the last 10 years. The speedup improvements stem from the ability of the co-designed compiler and hard-

ware to extract parallelism from loops with much higher communication requirements than prior initiatives have been able to address. Moreover, by efficiently utilizing non-core resources, HELIX-RC can achieve higher multicore throughput even in cases where multiple-program parallelism is already abundant. The additional hardware component, ring cache, is easily integrated into existing commodity multicore architectures at minimal power and area costs. The architectural implications and the implementation of ring cache are evaluated in detail.

#### 0.6 Organization of the Dissertation

The rest of this dissertation is organized as follows. First, Chapter 1 details relevant historical and modern automatic parallelization techniques, with an emphasis on their limitations with respect to parallelizing irregular workloads. The characteristics of the hardware support needed to boost the performance of these workloads are described. Next, Chapter 2 presents existing hardware mechanisms for inter-core communication and explains why existing hardware fails to address the communication needs of irregular programs. Chapter 3 details and evaluates the proposed compiler-architecture co-design, which is a combination of the HELIX compiler and some novel hardware, the ring cache. Chapter 4 presents selected implementation details for ring cache, in addition to synthesis results from a cycle-accurate Verilog model of the hardware. The full ring cache implementation report appears in Appendix A. Finally, Chapter 5 examines some architectural tradeoffs regarding HELIX-RC, including its potential effect on different core architectures and its use for tradeoffs between program execution time and overall multicore processor throughput, along with possible future compiler extensions to further increase performance.

# Prior Parallelization of Irregular Workloads Limited by Loop Size

While some computing problems often translate to either inherently parallel or easy-to-parallelize numerical programs, sequentially designed, irregular programs with complicated control (e.g., execution paths) and data flows (e.g., aliasing) are much more common but difficult to analyze precisely. For years, many attempts have been made to accelerate single-thread performance beyond what has been provided by traditional process scaling and architectural improvements. Although the conventional wisdom is that irregular programs cannot make good use of multiple cores, research in the past decade has made steady progress towards extracting TLP from complex, sequen-

tially designed programs such as the integer benchmarks from the SPEC CPU suites.

Some of this past research has focused primarily on compiler techniques to automatically extract parallel threads from sequentially written code. Other work combines compiler techniques with special-purpose hardware in an attempt to overcome some of the limitations of the compileronly strategies. In general, these strategies are most successful on so-called *regular* (or *numerical*) workloads—those with predictable control flow and data access. For *irregular* workloads, these techniques tend not to be so successful.

The two primary approaches for automatic thread extraction are cyclic multithreading and pipelined multithreading. Both operate by transforming sequentially written loops into multiple threads that run on different cores or, historically, on different machines. Inter-thread communication is used to satisfy any required synchronization or data dependence forwarding. Cyclic multithreading assigns different loop iterations to different threads. Any loop-carried dependence (i.e., a dependence between different loop iterations) is communicated between threads from older iterations to younger iterations, forming a cycle between the threads. In contrast, pipelined multithreading forms a pipeline between threads, rather than a cycle. A loop iteration is split into multiple stages (e.g., the first half of every iteration belongs to one stage and the second half of every iteration belongs to a stage), with each stage assigned to a different thread. Thus, unlike cyclic multithreading, every thread runs a portion of every iteration in pipelined multithreading. Although many variations of these techniques exist, the core transformation of loops into thread cycles or pipelines remains roughly the same.

For both categories of thread extraction, loops with larger iterations generally contain larger amounts of code that can run in parallel, with less required communication. Smaller loops tend to be more tightly coupled—and with such short loop bodies, the cost of performing any kind of communication can quickly dwarf any benefit of parallelization. Since small loops require at least some amount of communication, both cyclic multithreading and pipelined multithreading tend to perform poorly for them, even though the loops may contain large amounts of potential parallelism. For this reason, most state-of-the-art parallelization techniques target relatively large loops.

Unfortunately, complex control and data flows in irregular programs—both exacerbated by ambiguous pointers and ambiguous indirect calls—make accurate data dependence analysis difficult. In addition to actual dependences that require communication between threads, a compiler must conservatively handle apparent dependences that are never realized at runtime. Additionally, larger loops are harder to analyze, due to the increased lexical scope and amount of variables/memory being considered. If all of the apparent dependences need to be synchronized, performance will suffer greatly.

A common way to handle a large number of apparent dependences is through speculation [35, 38, 56], which avoids the need for accurate data dependence analysis by speculating that some apparent dependences are not realized. However, thread-level speculation (TLS) suffers from the overhead needed to support misspeculation and therefore is primarily limited to targeting relatively large loops in order to amortize penalties.

A potential alternative strategy to existing parallelization solutions is to target small loops instead, as these are much easier to analyze via state-of-the-art control and data flow analysis, which significantly improve accuracy. Furthermore, this ease of analysis enables transformations that simply recompute shared variables in order to remove a large fraction of actual dependences. This strategy increases TLP and reduces core-to-core communication. Such optimizations do not readily translate to TLS because the complexity of TLS-targeted code typically spans multiple procedures in larger loops.

In the remainder of this chapter, I first discuss some of the primary compiler techniques for automatic thread extraction and detail their strengths and drawbacks, especially with regard to accelerating irregular programs. Next, I discuss refinements of these techniques that attempt to overcome some of the limitations of compiler-only solutions, such as compiler–architecture co-designs and those that use TLS. Then I explore an opportunity to increase performance even further by targeting small loops, an untapped source of parallelism that has so far been left on the table. This opportunity is only realizable, however, if the significant communication requirements of small-loop parallelization are fulfilled.

#### **I.I THREAD EXTRACTION TECHNIQUES**

There are two primary models for extracting parallel threads from sequentially written loops. The two approaches, cyclic multithreading and pipelined multithreading, underpin most automatic parallelization techniques. In the following subsections, I describe the general transformation of sequential code to parallel threads, as well as the primary performance bottlenecks and potential pitfalls of each technique.

#### I.I.I CYCLIC MULTITHREADING

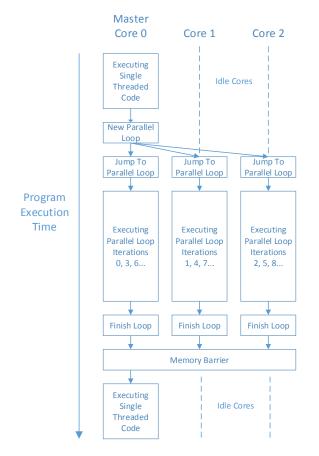

Cyclic multithreading was one of the first parallel processing paradigms to be introduced, in 1966 [4]. In general, cyclic multithreading (CMT) operates by assigning loop iterations to different threads, which are then executed on different cores or processors. Once a core *i* completes iteration *i*, it next executes iteration i + n, where *n* is the number of cores in the system (e.g., on a 4-core system, core o would execute iteration o, then iteration 4, and so on). For simple loops that have no loop-carried dependences (a degenerate case of CMT, often called DOALL), the threads can more or less run independently. Unfortunately, other than relatively trivial or basic number-crunching scientific applications, the vast majority of programs contain loops with control and data dependences. For these nontrivial loops, the DOACROSS [16] strategy, which partitions iterations into a sequential portion and a parallel portion, was developed. The sequential portion contains any loop-carried dependences and must be executed in loop iteration order, in effect forming a cycle between threads as older iterations feed data to younger iterations. The parallel portion can be executed completely

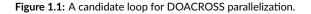

```

Node* node = root;

int mySum = node->data;

for(int i = 0; i < 8; i++) {

node = node->next;

mySum = mySum + node->data;

work(mySum, node->data);

}

```

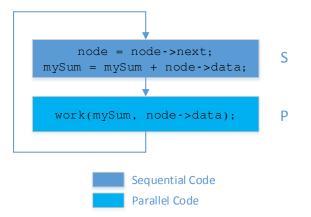

Figure 1.2: A loop iteration is decomposed into sequential and parallel portions for DOACROSS parallelization.

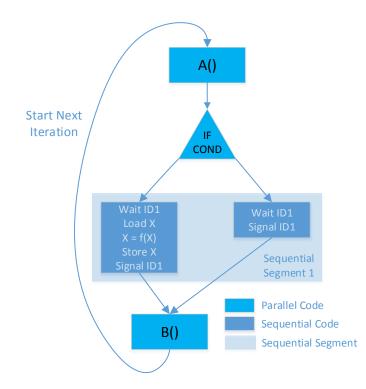

independently. More recently, a generalization of DOACROSS called HELIX [12] has further split the sequential portion of each iteration into multiple smaller sequential segments. This potentially enhances performance by enabling parallelism between different sequential segments.

#### DOACROSS

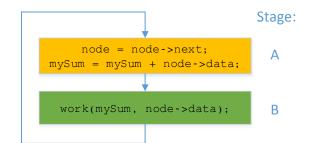

To illustrate the DOACROSS transformation, consider the code example in Figure 1.1. This loop contains two loop-carried dependences. First, the *node* pointer for the linked list is updated by every iteration as the linked list is traversed. Second, the *mySum* variable contains the running sum of the data located at each node. Let us assume that the subsequent *work* function is completely independent and does not access any memory or registers shared between iterations. Figure 1.2 shows a

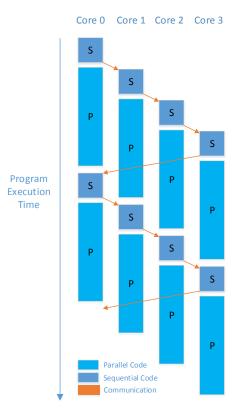

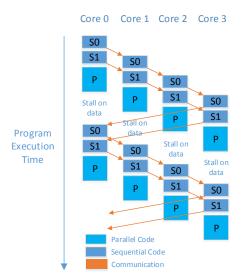

transformed version of an iteration of this loop. DOACROSS places the two loop-carried dependences into a sequential region, which must be executed in loop iteration order (enforced by synchronization instructions; not shown), and the independent *work* function (which relies only on values produced by the current iteration of the loop) into a parallel region. Execution of the parallel region can overlap with the sequential region of any younger iteration and the parallel region of any other iteration. An execution timeline for eight iterations of this loop on four cores is shown in Figure 1.3. The values of loop-carried dependences flow undirectionally from older iterations to younger iterations—from core o to core 1, 2, and 3, and then back to core o, forming a cycle. Note that because the parallel region has a long execution time relative to the sequential portion, there is a significant performance gain from the large amount of code that can execute in parallel.

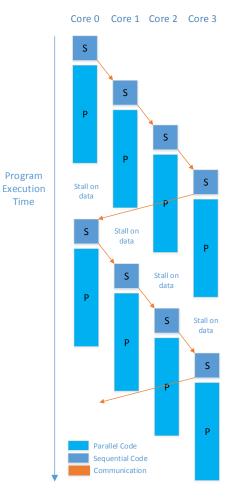

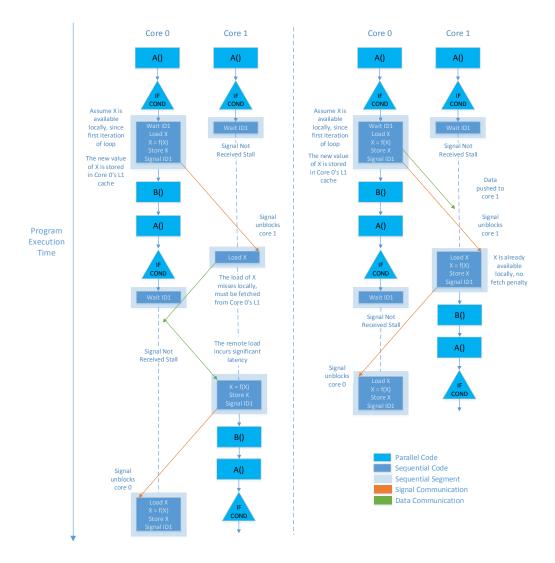

There are two primary bottlenecks that can severely limit the performance of DOACROSS. Consider Figure 1.4, where the time it takes for data to transfer between cores is tripled, leading to cores stalling as they wait for loop-carried data to transfer. Execution time in this scenario is much longer due to the tight coupling between cores intrinsic to CMT, making *communication latency* a significant factor for DOACROSS. The second primary bottleneck is the size of the sequential portion of the iteration relative to the parallel portion. If there is a large number of loop-carried dependences compared to the size of the independent code, there will be limited opportunities for overlap between threads, which in turn reduces performance. Figure 1.5 depicts an execution timeline with a much shorter *work* function, resulting in significant stalls. This highlights the importance of having a larger parallel-to-sequential code ratio.

Unfortunately, irregular workloads not only have a large number of actual loop-carried dependences (relative to regular workloads), but are also susceptible to a large number of apparent dependences (i.e., dependences that do not manifest at runtime), which bloat the size of the sequential portion of the loop iteration. In order to achieve good performance, DOACROSS must be able to keep the sequential portion small and must have very fast inter-thread communication.

Figure 1.3: Four cores execute eight iterations of a DOACROSS loop, with data flowing from older iterations to younger iterations. Since the communication delay is small and the parallel region is large, all four cores have high utilization.

Figure 1.4: With slightly higher communication latency, communication stalls hurt DOACROSS performance.

#### HELIX

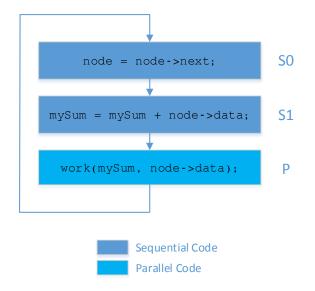

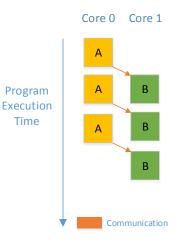

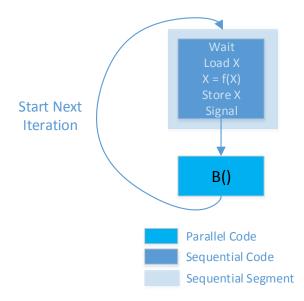

HELIX [12], an evolution of DOACROSS, addresses the sequential portion bottleneck by splitting the sequential portion into multiple sequential segments (it may also create multiple parallel segments). Although each sequential segment still needs to run in loop iteration order, different segments can execute simultaneously, to exploit parallelism among them. Figure 1.6 shows how HE-LIX decomposes the original loop body shown in Figure 1.1. Note that there are now two different independent sequential segments, so and s1. Segment zero relies only on the previous iteration's

Figure 1.5: If the parallel region of a DOACROSS loop is short, there can potentially be severe performance degradation.

value for *node*, and segment one relies only on the previous iteration's value of *mySum* (it uses the current iteration's value of *node*). Even when the parallel region is small, as was the case in Figure 1.5, HELIX can improve performance by allowing so and s1 to overlap their execution, as shown in Figure 1.7. However, as with DOACROSS, HELIX<sup>III</sup>s speedups are limited by communication latency. Despite this remaining bottleneck, HELIX was able to achieve a speedup of  $2.25 \times$  for a mixture of SPEC CPU 2000 integer and floating point benchmarks.

#### 1.1.2 PIPELINED MULTITHREADING

In contrast to CMT, pipelined multithreading (PMT) splits loop iterations into different stages, each of which is then assigned to a single thread. The data dependences that need communicating in this case are not loop-carried, as with CMT—instead, they are intra-iteration dependences.

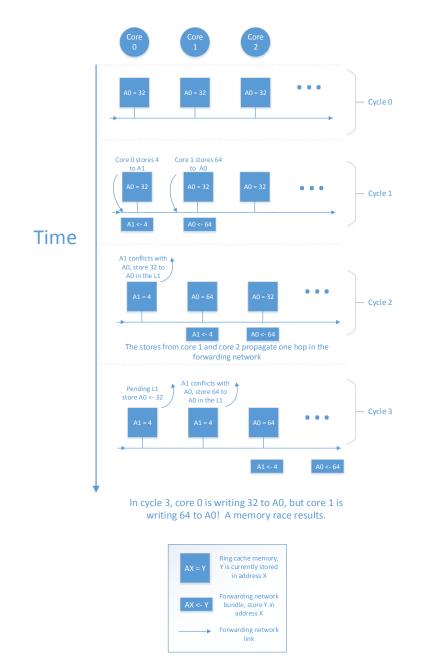

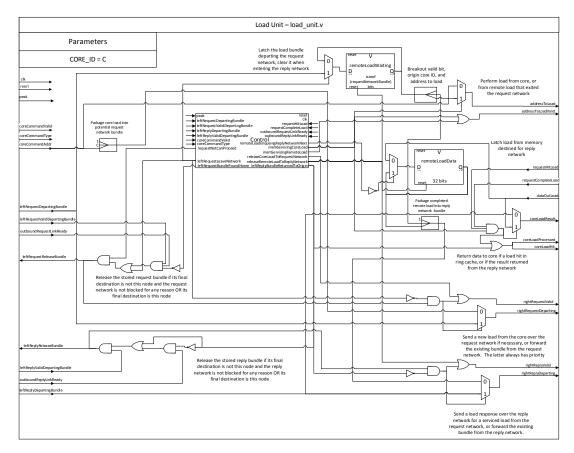

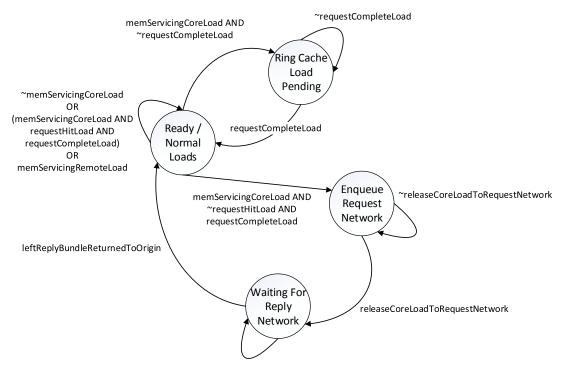

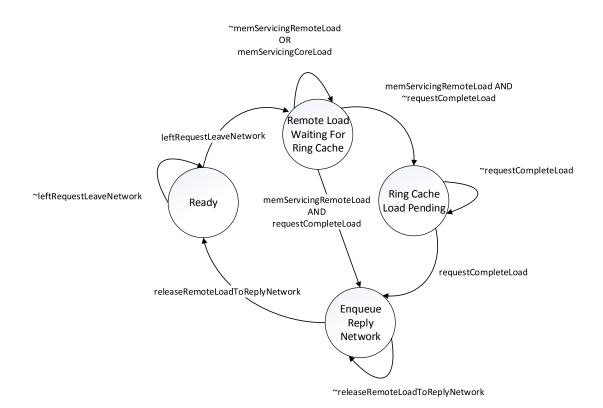

Figure 1.6: A loop iteration is decomposed into sequential and parallel portions for HELIX parallelization. DOACROSS would have created only one sequential portion.