#### UNIVERSIDADE DE LISBOA FACULDADE DE CIÊNCIAS DEPARTAMENTO DE INFORMÁTICA

# Named Data Networking with Programmable Switches

#### MESTRADO EM ENGENHARIA INFORMÁTICA

Especialização em Arquitetura, Sistemas e Redes de Computadores

### **Rui Miguel Carvalho Marques**

Dissertação orientada por: Prof. Doutor Fernando Manuel Valente Ramos

#### Acknowledgments

To professor Fernando Ramos, for proposing so interesting a subject for my dissertation, and supervising it.

To my open office coworkers for the friendly, fun mood, the evening karaokes and all the giggles.

To Mihai Budiu of VMware, Antonin Bas of Barefoot Networks and Nate Foster of Cornell University for the continued attention to my e-mail messages and my interventions on the p4lang GitHub repositories.

To Engineer Jeferson Santiago da Silva, MSc by Polytechnique Montréal, for responding to my e-mails regarding P4 externs so promptly and kindly.

To Salvatore Signorello, for reviewing my written draft and pointing errors in it.

To my (some current, some former) colleagues Ana Pereira, João Ferreira, Henrique Califórnia Mendes and Inês Gouveia for approaching me on my first spooky week in the Faculty of Sciences and integrating me into their group. If it hadn't been for that, I might have given up on university.

To former colleagues Ricardo Tomaz and (again) Ana Pereira for the good times during our first year and the endless laughters.

A special one to the conference group at my secondary school for being the most serious people I know. In particular, to Professor Armando Pedrosa.

Another special one to Professor Guilherme Arroz of IST-ULisboa and doctor Luísa Barreto for being a source of encouragement.

And a final one to my family for the support!

**Funding** This work was partially supported by the European Commission through project FP7 SEGRID (607109) and project H2020 SUPERCLOUD (643964), and by national funds of Fundação para a Ciência e a Tecnologia (FCT) through project UID/CEC/00408/2013 (LaSIGE).

#### Resumo

As redes IP, que são universais atualmente, apresentam um conjunto de problemas que encontra a sua génese nos seus propósitos originais. Na génese do IP, o objetivo era a partilha de recursos. Hoje em dia, as redes de computadores já não se baseiam num computador *mainframe* a disponibilizar recursos de hardware. São usadas como meio de disseminação alargada de uma panóplia de média, como ficheiros de hipertexto, imagens e vídeos.

Grande parte das dificuldades no uso das redes IP advém do uso de endereços. A necessidade do endereço como identificador indispensável à comunicação obrigou ao aparecimento de esquemas complexos à medida que as redes cresceram: refere-se o DNS, o DHCP e a gestão de prefixos associada às unidades autónomas (*autonomous systems*, conhecidas também pela sigla AS). Já quase se esgotou o espaço público de endereços, para além de que a gestão dos reservatórios públicos e privados é um processo complicado e propenso a erros.

A par deste panorama, o hardware da rede foi otimizado para desempenho e os dispositivos de encaminhamento (*routers*) e comutação (*switches*) tornaram-se caixas negras fechadas, correndo vários protocolos em hardware para maximizar o desempenho. O software dos hospedeiros (*hosts*), por seu turno, materializou-se na API de sockets que usamos até hoje.

As redes baseadas em nomes (named data networks, ou NDN) divergem fundamentalmente da rede IP. Enquanto que a última tem como objectivo transportar um pacote para um destino com base no seu endereço, as NDN não fazem qualquer uso de endereços. O problema é reformulado em como levar dados com um determinado nome de um produtor para os consumidores. Assim, na rede NDN circulam apenas dois tipos de pacotes: *Interest* e *Data*. Os pacotes *Interest* são emitidos por consumidores que procuram dados. Estes dados estão globalmente e univocamente ligados a um pedaço de informação. A rede NDN trata de encaminhar o pedido Interest até um produtor. Em resposta, o produtor emite um pacote *Data*, que alberga, no seu interior, o pedaço de informação correspondente ao que foi pedido no Interest.

Os nomes são o centro da NDN. Podem ser *flat*, mas também podem ser utilizados de forma hierárquica. Por exemplo, "ulisboa/fciencias/index.html"é um nome hierárquico.

Cada troço do nome separado por '/' chama-se um **componente**. Esta hierarquia é fundamental para conferir contexto ao nome e escalar a NDN.

Esta mudança de paradigma oferece vantagens. Desde logo, o endereço torna-se desnecessário, evitando assim processos de gestão intermédios, exaustão do reservatório de endereços públicos e o uso dos *Network Address Translators* (NATs). Para além disso, todos os pacotes Data vêm assinados, pelo que as NDN dispõem de segurança inerente e, a par disto, de uma maior dificuldade em atacar alvos específicos, dado que todos os dispositivos na rede, quer nós intermediários quer hospedeiros, estão desprovidos de identificação. Os problemas de segurança existem, mas reduzem-se, desta forma, a distribuição de chaves segura, buracos negros (*black holes*) e ataques *distributed denial of service* (DDoS).

O encaminhamento em NDN é semelhante ao que ocorre no IP, mas, em vez de manter endereços de 32 bits nas tabelas de comutação, os encaminhadores utilizam os nomes, de comprimento arbitrário para decidir por onde encaminhar os pacotes. As tabelas são populadas de modo análogo ao que acontece no IP, por exemplo através de um protocolo *link-state* para NDN, homólogo do OSPF. As tabelas de comutação têm, portanto, pares (*string, integer*), associando um nome a uma dada interface (que pode ser física ou lógica) do dispositivo. Quando um nome faz *match* com mais de uma entrada, é selecionada aquela que tiver maior número de componentes (e, portanto, for o prefixo mais comprido).

Quando recebe um pacote Interest, o encaminhador consulta a sua *content store* para verificar se pode servir o conteúdo diretamente. Nesse sentido, a content store é uma funcionalidade absolutamente fundamental neste paradigma, pois permite trazer o conteúdo para perto dos consumidores. Este caching feito ao nível da rede é considerado uma das grandes mais-valias das NDN. Se puder servir diretamente, fá-lo. Caso contrário, o Interest segue para a Tabela de *Interests* Pendentes (*Pending Interest Table*, ou PIT), onde se mantém registo dos pedidos na forma de uma lista de interfaces que pediram um determinado nome.

Se esta lista está vazia, então este Interest é o primeiro pedido para este nome. Será assim encaminhado para uma interface do dispositivo determinada pela FIB (forwarding information base). A FIB mantém associações (nome,interface) e comuta o pacote se encontrar um nome que seja prefixo do nome inscrito no Interest em processamento; realiza, deste modo, um longest prefix matching de nomes à granularidade do componente. Se a lista não está vazia, então outra interface já requisitou os mesmos dados. Nesse caso, o encaminhador pode descartar o Interest que acabou de receber, pois o pedido para esse nome já foi anteriormente lançado. Apenas adiciona à lista a interface de onde veio este Interest repetido.

Quando recebe um pacote Data, o encaminhador consulta a PIT para verificar se está à espera de dados para este nome. Se não, então descarta o pacote. Se está, efetua uma difusão *multicast* para todas as interfaces que registou na lista para o respetivo nome.

Desta forma se consegue garantir que os conteúdos requisitados chegam a todos os consumidores que os pediram. Se os campos de metadados do Data assim o permitirem, o encaminhador também armazenará o Data na *content store*.

Um dos grandes problemas deste novo paradigma é a sua materialização prática. Como vimos, um encaminhador NDN é fundamentalmente diferente do seu homólogo em IP, ou de qualquer outro tipo de comutador de pacotes, e por isso não é possível adaptar equipamento tradicional para NDN. Recentemente, porém, foram propostos comutadores programáveis, alguns já em produção (e.g., Tofino da Barefoot Networks). Estes dispositivos permitem definir precisamente o modo como o equipamento de rede processa pacotes, e reprogramá-lo sempre que necessário.

Todavia, programar estes dispositivos, utilizando a sua interface de baixo nível, é quase como programar em microcódigo, e portanto não se trata de uma tarefa fácil. Esta lacuna foi uma das motivações para a linguagem de alto-nível, P4.

A linguagem P4 surge no seio das redes programáveis, bem como das redes definidas por software, propiciada pela rigidez do OpenFlow quanto ao conjunto de protocolos que suporta. No entender dos seus criadores, um OpenFlow ideal seria aquele que permitisse ao operador de rede definir os seus próprios cabeçalhos e criar os seus próprios protocolos. Assim, a linguagem P4 tem três grandes objetivos. Primeiro, não estar dependente de nenhum protocolo específico, permitindo, pelo contrário, que estes sejam definidos pelo controlador. Segundo, poder ser reconfigurada pelo plano de controlo a qualquer momento. Terceiro, não estar dependente de nenhuma arquitetura subjacente; isto é, poder ser escrita (e depois compilada) para um qualquer dispositivo da mesma maneira que um programa escrito na linguagem C pode ser escrito sem preocupações relativamente à arquitetura de processador subjacente.

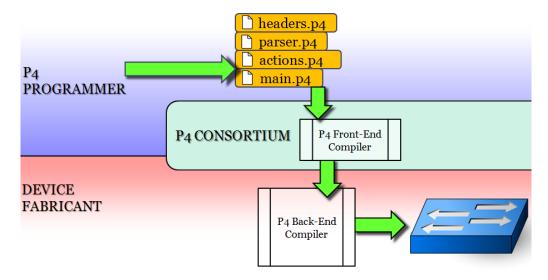

O consórcio P4 oferece um compilador *front-end* que transforma a linguagem P4 numa representação intermédia (IR), enquanto que o vendedor do dispositivo disponibiliza um compilador *back-end* que processa a IR e traduz para a linguagem própria do aparelho. Um dispositivo assim concebido é **compatível com P4** (*P4-compatible*). Com P4, é assim possível definir cabeçalhos, *parsers* e uma sequência de tabelas de *match-action* à escolha para um qualquer aparelho compatível e definir as ações a partir de um conjunto de primitivas oferecidas pela linguagem.

Neste trabalho, propomos a conceção de um *router* NDN utilizando a linguagem P4. O nosso trabalho parte de um anterior chamado NDN.p4 por Signorello *et al*, que foi implementado na versão 14 do P4 (abreviado P4-14). É um protótipo do encaminhador NDN, proporcionando uma tabela de interesses pendentes (PIT) e uma FIB. A PIT é descrita utilizando registos, que mantêm estado no comutador P4. A capacidade de ter estado e de o manusear é indispensável para implementar um encaminhador NDN, como se deduz da nossa anterior descrição sobre o respetivo funcionamento.

O trabalho anterior tem, no entanto, limitações. Em primeiro lugar, não dispõe de

uma *content store*, uma das peças principais deste paradigma. Para além disso, o recurso a matching ternário e exato tem problemas de escalabilidade e não há suporte a multicast de pacotes Data.

Nesta dissertação, desenhámos e construímos, da forma mais modular e genérica possível, um encaminhador NDN utilizando a versão mais recente do P4, P4-16, providenciando, para além da PIT e da FIB — que faz longest prefix matching utilizando um método inovador —, uma *content store* implementada quer em registos, quer diretamente no *switch* P4. As principais inovações são as seguintes:

- Implementação da *content store*, que armazena pacotes e permite ao encaminhador NDN servir pedidos de imediato. Numa primeira versão, concebêmo-la em registos P4. A segunda versão é editada diretamente num *target*, o *simple\_switch*.

- Utilização de um método inovador para conseguir longest prefix matching (lpm) em redes NDN. O método proposto por Signorello et al apoia-se num mecanismo relativamente complicado de matchings ternário e exato que não escala bem. Optámos por utilizar diretamente o método lpm, mantendo a ideia de efetuar hashing dos componentes do nome. Os resultados dos cálculos de dispersão dos componentes são concatenados pela mesma ordem em que aparecem os componentes respectivos. O produto final desta concatenação figura assim como entrada na tabela, com uma máscara de rede que será o comprimento do resultado da função vezes o número de componentes.

- Realização de *multicast*, quer em linguagem P4 (neste caso, para um número máximo de portos, devido à falta de mecanismos de iteração), quer diretamente no *software switch*.

Finalmente, avaliámos a nossa solução através de vários testes de funcionalidade e comparámos ao NDN.p4 em termos de espaço ocupado pelas entradas da FIB.

Palavras-chave: redes programáveis, nomes, P4, encaminhadores

#### **Abstract**

Named data networks (NDN) differ substantially from traditional TCP/IP networks. Whereas the TCP/IP communications stack focuses on delivering a packet to a destination based on its address, NDN abolishes the use of addresses and reformulates the problem as how to fetch data with a given name and bring it closer to its consumers. For this purpose, consumers emit Interest packets, writing the name for the resource they desire. The network routes that packet to a producer of the data uniquely associated to that name. NDNs achieve this by employing routers whose functions are similar to those of traditional networks, with a central difference: they route Interests based not on an address, but on a name. Another fundamental innovation of this paradigm is the introduction of a content store in NDN routers. This gives the ability to perform caching in the network, and as such is key to improve network efficiency.

The main challenge of NDN is that of deployment. As the design is radically different, current routers and switches cannot be "extended" to offer NDN. Fortunately, the emergence of programmable switches, and of a high-language level to program them (such as P4), gives hope for the state of affairs to change. With P4 it is possible to define precisely how packets are processed in these programmable switches, allowing the definition of headers, parsers, match-action tables, and the entire control flow of packets in the switch.

In this dissertation we propose the design of an NDN router and implement it using the P4 language. We improve over previous work in two main aspects: our solution includes, for the first time, a content store. In addition, we propose an innovative method to perform longest prefix matching that requires significantly less memory per route than the former, allowing the FIB to scale more easily. We evaluate our solution using P4 switches, in terms of the main NDN functionality required.

**Keywords:** P4, NDN, routers, programmable, switches

## **Contents**

| Li | st de   | Figures       |                                                         | XV   |

|----|---------|---------------|---------------------------------------------------------|------|

| Li | st of ' | <b>Fables</b> |                                                         | xvii |

| 1  | Intr    | oductio       | o <mark>n</mark>                                        | 1    |

|    | 1.1     | Motiv         | ation                                                   | . 1  |

|    | 1.2     | Object        | tives                                                   | . 2  |

|    | 1.3     | Contri        | ibutions                                                | . 2  |

|    | 1.4     | Docum         | ment structure                                          | . 3  |

| 2  | Bac     | kgroun        | d & Related work                                        | 5    |

|    | 2.1     | Name          | d Data Networks (NDN)                                   | . 6  |

|    |         | 2.1.1         | Routing and forwarding                                  | . 7  |

|    |         | 2.1.2         | Packet encoding                                         | . 9  |

|    | 2.2     | Progra        | ammable Networks                                        | . 10 |

|    |         | 2.2.1         | P4-14 vs P4-16                                          | . 12 |

|    |         | 2.2.2         | P4-16 program example for the v1model architecture      | . 13 |

|    |         | 2.2.3         | Behavioral Model 2 (BMv2) and p4c                       | . 17 |

|    | 2.3     | NDN.          | p4                                                      | . 18 |

|    |         | 2.3.1         | Type-length-value parsing                               | . 18 |

|    |         | 2.3.2         | Forwarding Information Base (FIB)                       | . 19 |

|    |         | 2.3.3         | Pending Interest Table (PIT)                            | . 20 |

|    | 2.4     | Summ          | nary                                                    | . 20 |

| 3  | Desi    | gn            |                                                         | 21   |

|    | 3.1     | Partiti       | on                                                      | . 21 |

|    |         | 3.1.1         | Motivation for a new solution                           | . 22 |

|    |         | 3.1.2         | An innovative concept: the partition                    | . 22 |

|    |         | 3.1.3         | The advantages of using a partition to represent a name | . 25 |

|    |         | 3.1.4         | A note on hash collisions                               | . 25 |

|    |         | 3.1.5         | Attempts at collision prevention                        | . 26 |

|    | 3.2     | Packet        | t Processing                                            | . 27 |

|    | 3.3           | FIB Longest-prefix Matching                           | 28 |

|----|---------------|-------------------------------------------------------|----|

|    | 3.4           | Pending Interest Table                                | 28 |

|    |               | 3.4.1 Record keeping                                  | 28 |

|    |               | 3.4.2 Data multicast                                  | 29 |

|    | 3.5           | Content Store                                         | 31 |

|    | 3.6           | Summary                                               | 32 |

| 4  | Imp           | lementation                                           | 33 |

|    | 4.1           | Compiler and Target Limitations                       |    |

|    | 4.2           | Type-length-value Parsing                             |    |

|    | 4.3           | Forwarding Information Base Implementation            |    |

|    | 4.4           | Pending Interest Table Implementation                 |    |

|    |               | 4.4.1 Table                                           |    |

|    |               | 4.4.2 Registers                                       |    |

|    | 4.5           | Content Store                                         |    |

|    |               | 4.5.1 CS as registers                                 |    |

|    |               | 4.5.2 CS in the switch target                         | 41 |

|    | 4.6           | History of Development                                | 42 |

|    | 4.7           | Summary                                               |    |

| 5  | Eva           | luation                                               | 45 |

|    | 5.1           | Developed Testing Tools                               | 45 |

|    |               | 5.1.1 rawpkt                                          |    |

|    |               | 5.1.2 makeFIBrules2.py                                |    |

|    | 5.2           | Environment                                           |    |

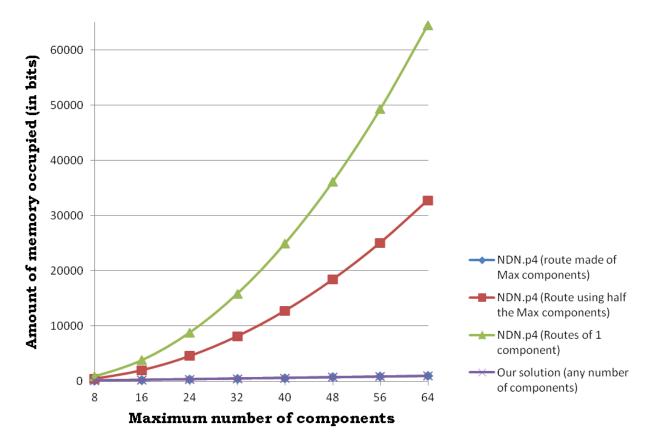

|    | 5.3           | Evaluation of Memory Requirements                     |    |

|    | 5.4           | Functionality Tests                                   | 49 |

|    |               | 5.4.1 Parser and deparser                             | 49 |

|    |               | 5.4.2 FIB                                             |    |

|    |               | 5.4.3 Egress pipeline                                 | 52 |

|    |               | 5.4.4 Ingress pipeline                                | 52 |

|    |               | 5.4.5 Multicast and Content Store in the SimpleSwitch | 54 |

|    | 5.5           | Summary                                               | 56 |

| 6  | Con           | clusion & Future Work                                 | 57 |

| Bi | bliog         | raphy                                                 | 61 |

|    | · -~ <b>5</b> |                                                       |    |

| A  |               | Our main parser as it parses name components          | 63 |

|    | Δ 1           | Our main parcer as it parces name components          | 63 |

| B |             |                                                                             | 65 |

|---|-------------|-----------------------------------------------------------------------------|----|

|   | <b>B</b> .1 | Merged tcpdump logs sniffing on switch interfaces s1-eth1 and s1-eth2 in    |    |

|   |             | test 4                                                                      | 65 |

|   | <b>B.2</b>  | tcpdump logs sniffing on interfaces h1-eth0, h2-eth0 and h3-eth0 in test    |    |

|   |             | 5 (the labels in square brackets and question marks are artificial), merged |    |

|   |             | by increasing timestamp.                                                    | 66 |

## **List of Figures**

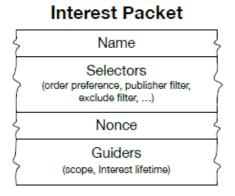

| 2.1 | A NDN Interest packet [32]                                            | 6  |

|-----|-----------------------------------------------------------------------|----|

| 2.2 | A NDN Data packet [32]                                                | 6  |

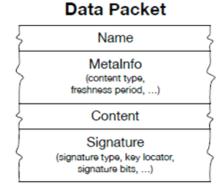

| 2.3 | An example of an asset name [21]                                      | 7  |

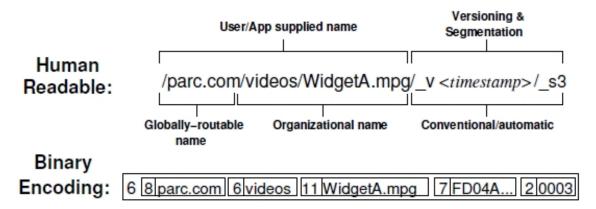

| 2.4 | Forwarding on an NDN router [32]                                      | 8  |

| 2.5 | An example of a Type-Length-Value                                     | 9  |

| 2.6 | High-level perception of an NDN packet and its encoding as TLV        | 10 |

| 2.7 | The P4 abstract forwarding model [17]                                 | 11 |

| 2.8 | Workflow of a P4 programmer                                           | 12 |

| 2.9 | A loose, very simplified excerpt of the BMv2 class diagram            | 17 |

| 3.1 | The Interest matches a FIB entry by lpm                               | 23 |

| 5.1 | Variation of the memory occupied in function of the maximum number of |    |

|     | components, with a fixed hash output length of 16 bits                | 48 |

| 5.2 | Terminal at h1 after the packet is sent                               | 50 |

| 5.3 | Terminal at s1 after the packet is sent                               | 50 |

| 5.4 | Terminal at s1 in experiment FIB, after h1 sends the first packet     | 51 |

## **List of Tables**

| 2.1 | A FIB in NDN.p4 containing 2 routes, one for "a/b" and another for    |    |

|-----|-----------------------------------------------------------------------|----|

|     | "a/b/c". An Interest for "a/b/c/d" matches two entries. $Max = 4$     | 19 |

| 3.1 | A port bit array of 8 positions (meaning the device has 8 interfaces) | 28 |

## Chapter 1

## Introduction

The primary use case of the Internet has changed, from a simple connection-oriented message passing paradigm to distribution of a large plethora of diverse media, such as hypertext, images and videos. As a result, Internet system developers struggle to meet their requirements when distribution comes into play.

One of the solutions for this problem is to change the focus of the network from connections to data. Named data networks (NDN) [32] are a new architecture that aims to jointly solve many of the problems of IP as a whole by following this approach.

NDN switching equipment routes content based on naming data, instead of computer addresses. The routers cache data whenever possible (in a structure called the **Content Store**), multicast it to its consumers, and suppress many of the complex mechanisms to map data to locations, such as the Domain Name System (DNS). In addition, NDNs have some inherent security design, by authenticating content and making targeted attacks more difficult.

In short, the named data network is an architecture that much better fits today's Internet than the IP network. This better conformity stems from NDN directing its focus to what the Internet is most commonly trying to achieve: distributing content.

#### 1.1 Motivation

There is a substantial difference between the requirements of an NDN router to those of an IP router. As a consequence, despite the fact that the concept was proposed over a decade ago, no production hardware has ever been built specifically for NDN. Caching data in a network forwarding device is indeed atypical. Software constructs, such as NFD [16], are useful for experimentation with current and novel features of NDN technology, but are limited in terms of performance, and the solutions cannot be easily exported to switching hardware.

With the advent of programmable networks [22], building production NDN systems may now be closer to becoming a reality. Because network devices can now be pro-

grammed [18], it becomes easier to make forwarding devices run new protocols. These capabilities gave birth to novel programming languages to express a wide range of functionality, putting a premium on expressiveness and portability, such as P4 [17], the first language to program switches.

On this regard, NDN.p4 [26] was an important step. This was the first attempt to implement an NDN router using the P4 language. This has two great advantages. First, it enables NDN in real switches, as P4 is designed to be compiled down to forwarding hardware. Second, this language has attracted the attention of several renowned companies and its adoption is growing rapidly [2], so it is expected to become the norm to program switching hardware. In fact, Barefoot Tofino, the first programmable hardware switch, already supports P4.

However, NDN.p4 still bears a number of limitations. Namely, it does not provide a Content Store, which is the main key to NDN's success as a distribution network. Second, its FIB matching process does not to scale well. Finally, it does not distribute content correctly when multiple clients request the same content (i.e., it does not offer multicast).

Furthermore, NDN.p4 was implemented using version 14 of P4 (P4-14 for short). This version is expected to be deprecated soon. The new version of P4, P4-16, provides a stable programming language definition, that promotes backwards-compatibility. In addition, it gives more freedom for switch designers to include novel data plane functionality outside the scope of P4, but that can be used by P4 programs via an extern primitive. The fact that this will most certainly be the main version of the language used in production systems, motivates us to focus our attention in P4-16.

#### 1.2 Objectives

Our goal in this dissertation is to implement an NDN router in P4's most recent version, P4-16, that goes beyond that of NDN.p4 and bridges its constraints, by handling Data packets and multicast, by caching content in the Content Store, and by improving the FIB scalability.

#### 1.3 Contributions

The main contributions of this dissertation are the following:

- The design and implementation of an NDN router using the latest version of P4, P4-16, for the first time;

- Our NDN solution improves the previous [26], by including a content store, an innovative method for longest prefix matching, and the ability to multicast Data packets;

• We evaluate the functionality provided to demonstrate its correctness and the conformity of our implementation to NDN's core protocol.

In the midst of our progress, we contributed to the P4 language and community by reporting a number of compiler bugs [6][7][14][15], helping others [9][10] and suggesting improvements [13].

The result of this work, including the tools developed for testing purposes as reported in §5.1, are available publicly in our working group's repository<sup>1</sup>.

#### 1.4 Document structure

The document is structured as follows. We first study the background and related work in §2, including NDN.p4. Then, we look into the design of our new NDN router using P4, in §3. Following that, we explain our implementation in §4. We finish with an evaluation composed of several feature tests to prove the correctness of our implementation, in §5, and conclude in §6.

<sup>&</sup>lt;sup>1</sup>https://github.com/netx-ulx/NDN.p4-16

## Chapter 2

## **Background & Related work**

The purpose of a computer network, such as the Internet, at the time of its genesis in the 60's and 70's, was to let computers share resources. The resulting communication model was basically a conversation between two hosts: one wishing to use a resource, the other willing to share it. This motivated the use of (source and destination) addresses [21], both to identify *and* locate a host in order to achieve communication.

Many of the problems that the Internet faces today are due to that ancillary, simplistic purpose, on top of the forecast that the network would never be larger than a few thousand hosts. Computers then became unexpensive commodities. The network grew and proliferated. Now widespread, it faces several difficulties, including:

- The use of addresses and the incompatibility of the Internet's original design with the use cases of the modern Internet. Availability<sup>1</sup>, security and location-dependence issues surface, leading to complicated retrieval schemes like CDNs (content distribution networks) and P2P networks, as well as complex name-to-location mapping workarounds such as DHCP and DNS [21]. On top of it, the reservatory of public addresses is exhausted, forcing a change to IPv6, that is yet to be fully materialized;

- Switches and routers are closed, black boxes interpolated in the network, performing functions tailored in hardware for maximum performance, since general-purpose CPUs have remained two orders of magnitude slower than dedicated switching chips [18]. They are hard to manage and must be configured individually [22]. The set of supported protocols they run is fixed and rigid. Supporting new ones requires changes in hardware, and the hope that the manufacturer will include support in its new generation of equipment and, even so, with results seen only several years later [25];

- The Sockets API was created around 30 years ago to tackle the very specific problem of supporting TCP in BSD Linux and providing an interface to its users. The

We invite the reader to [24], which introduces a formal reflection on this topic.

Internet is now predominantly data and service oriented (as opposed to connection-based), but the sockets API, based on a connection-oriented model, has a solid grip as the most widespread communications toolbox throughout [19].

Several solutions have been proposed to resolve these problems, but changes happen slowly. In this chapter, we first present the two that promise to modify the state of affairs, and that are central to this dissertation: named data networks, in §2.1, and programmable networks, in §2.2. In §2.3 we describe the first solution — and only to the moment, to the best of our knowledge — that proposes an NDN router using programmable switches. We include the limitations of this solution that are the main motivation for our work.

Tangent related work includes good practices on design and implementation for NDN software [31]. In this paper, authors divides routers into two categories, core and edge, and proposes a relaxation of requirements for core routers. On the topics of stateful forwarding devices, [29] designs (but does not build) *Caesar*, a stateful, fast packet processing router for information-centric networks (a supergroup of which NDN is an instance).

#### 2.1 Named Data Networks (NDN)

**Named data networks** (NDN) [32] follow the content-centric approach [21], differing significantly from traditional IP networks. They provide an unified way of solving the issues flagged earlier at the beginning of this chapter as a whole. Whereas IP networks, such as today's Internet, still base communications on location, Jacobson et al argue that the focus should be shifted to the information itself, by naming data and not endpoints [21]. Accordingly, the problem the network aims to solve changes from "deliver a packet to a destination identified by this address" to "fetch data identified by this name" [32].

Figure 2.1: A NDN Interest packet [32].

Figure 2.2: A NDN Data packet [32].

An NDN is composed of hosts and **routers**. Of these hosts, some – the **consumers** — desire named resources<sup>2</sup>. Others — the **producers** – offer them. Two types of pack-

<sup>&</sup>lt;sup>2</sup>We call them, interchangeably, as resources, data, or assets.

ets circulate in this network: **Interest** and **Data** (see Figure 2.1 and Figure 2.2), both of which include the name of an asset. Communication is propelled by the consumer, who puts the name of the resource he desires in an Interest packet and flushes it into the network. The network will route it **upstream** to a node that contains the corresponding asset. That node, the producer, will then build and digitally sign a Data packet carrying the requested content. The signature binds the name to the content. The network then returns it **downstream** towards the consumer who emitted the request.

Names are at the heart of named data networks. They can be flat, which is suitable for local environments, but hierarchical namespaces are essential to contextualize data and scale the routing system [32]. Names can therefore be divided into **components**, which are typically separated by '/', similar to how URLs are structured (see Figure 2.3). Data that is globally accessible necessarily has a globally unique name.

Figure 2.3: An example of an asset name [21].

We will now cover how routers operate and how packets are encoded when sent to the network.

#### 2.1.1 Routing and forwarding

Routers perform their function by relying on names. When forwarding Interests, the router looks into its forwarding table for a matching prefix. If multiple prefixes match, then the router chooses the longest. For example, if the router contains two route entries, one for "pt/ulisboa" and another for "pt/ulisboa/fciencias", then an Interest targeting "pt/ulisboa/fciencias/index.html" will match the latter entry. This longest prefix matching with a component-based granularity is therefore similar to how IP lookups operate, but, instead of using 32-bit (or 128-bit, in the case of IPv6) integers, they use names. These FIBs are updated through routing protocols; for example, NSLR is an equivalent of the OSPF protocol for NDNs.

In order to fulfill their duties, routers are equipped with three data structures (see Figure 2.4).

- The **Pending Interest Table (PIT)** maps names to a list of interfaces<sup>3</sup>. When the router receives an Interest, it adds the interface from where it arrived to the list for that name.

- The **Forwarding Information Base** (**FIB**) maps names to outgoing ports. When multiple nodes request the same resource, the router forwards only the first Interest upstream. The remaining ones are only recorded on the PIT;

- The **Content Store** caches Data packets temporarily. If the producer permits it (by filling certain fields on the Data packet), the router can archive it and serve directly whenever it finds an Interest for the same name.

**Figure 2.4:** Forwarding on an NDN router [32].

This is the essential setup for the NDN router. Some literature [30][32] proposes extra functional blocks, such as an adaptive forwarding module and a FIB with multiple outgoing ports for the same name, for fault tolerance.

The two main advantages of NDNs are the possibility of in-network caching, that brings information closer to its users, and its inherent security. With respect to the latter, devices have no identification. Hence, directing attacks at specific targets becomes much harder. At most, one could try to forge bogus Data packets, but, since they are signed, the consumer will discover the integrity of the packet has been compromised when verifying the signature. The set of security problems is thus mostly reduced to distributed denial of services, black holes, and key distribution.

<sup>&</sup>lt;sup>3</sup>In this text we use the terms "interfaces" and "ports" interchangeably. Nama data networking literature sometimes uses the word "face" as a hyperonym for both.

#### 2.1.2 Packet encoding

At the network level, NDN packets are structured as a hierarchy of Type-Length-Values (TLVs) [4]. A TLV is a structure that contains, in this order:

- An unsigned byte named **type**;

- An unsigned byte named **length** (we also call it "**len**" or "**lencode**");

- And a string of arbitrary octets known as value.

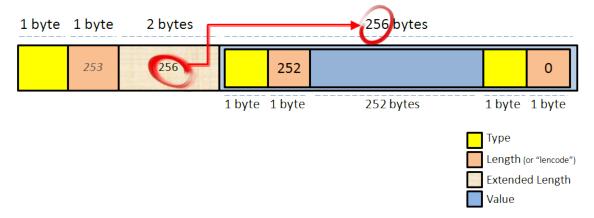

The type is up for applications using TLVs to interpret. Length expresses the size of the Value that follows. The maximum size is 252 bytes; if the lencode has a value of 253, 254 or 255, then there is an extra field sitting after the lencode. We henceforth call it "extended length" or "length extension". It expresses the real size of the Value that follows (see Figure 2.5).

**Figure 2.5:** An example of a Type-Length-Value.

- If lencode has a value of 253, then the length extension is 2 bytes, and the dimension of the TLV value can go up to 2<sup>16</sup> bytes<sup>4</sup> (64 megabytes), instead of just 252 bytes.

- If the lencode is 254, then this extended length is 4 bytes long, and therefore allows the TLV value to have up to  $2^{32}$  bytes (4 gigabytes) of data.

- Lencode equal to 255 means the length extension is 8 bytes long, making it possible for the value to contain  $2^{64}$  bytes of information (16 zetabytes, which is roughly  $1.76 \times 10^{13}$  gigabytes).

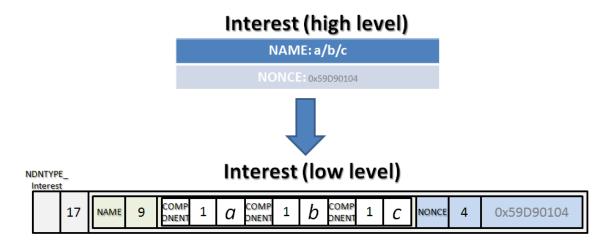

The structure of NDN packets is well defined (see [4]). A parent TLV, called  $TLV_0$ , is the sole container for the entire packet payload. Its type is Interest (0x05) or Data (0x06).  $TLV_0$  inholds all of the NDN packets' structure according to the type. In particular, the first child TLV (in either case) is always  $TLV_N$ , which is the TLV whose children are the name components. Each component is also a TLV (see Figure 2.6).

<sup>&</sup>lt;sup>4</sup> Minus one.

Figure 2.6: High-level perception of an NDN packet and its encoding as TLV.

#### 2.2 Programmable Networks

**Software-defined Networks** [22] were the first instance of programmable network that has reached to production. SDN enables control plane programmability, but the data plane maintains itself fixed, as common switches and routers are fixed-function, in order to operate at the required very high speeds. Recently, however, the market has seen the emergence of programmable switching chips [18]. Despite being programmable, these devices operate at terabit speeds [18].

SDN separates the control plane (which manages the forwarding tables) from the data plane. This enriches network flexibility, enabling easier configuration, bandwidth allocation and security enforcement. The data plane components become mere packet-forwarding devices, relying on the controller to setup route state by means of (usually) the OpenFlow protocol [22][23].

OpenFlow started by supporting a small set of protocols. As new use cases started arising, this set has expanded version after version. Nevertheless, it remains rigid. An operator who desires to run a very specific protocol in his company's network cannot make use of OpenFlow if it does not support that protocol. Faced with this limitation, and with the availability of programmable switches, P4 [17] was proposed as a high-level language to program network devices, endowed with three great advantages.

- 1. **Reconfigurability:** The controller<sup>5</sup> can redefine packet parsing and processing on the field.

- 2. **Protocol Independence:** The language is flexible and unconstrained to specific protocol headers. On the contrary, P4 permits one to define his own headers and how the packet should be parsed and processed.

<sup>&</sup>lt;sup>5</sup> Although the paper mentions a controller, using P4 does not make it mandatory to have one on the network.

3. **Target Independence:** Programming a switching chip using a low-level interface is similar to microcode programming, and nontrivial. A P4 program, however, can be written with no regard for the end device. This is in all similar to a C program written obliviously with regard to the underlying CPU architecture.

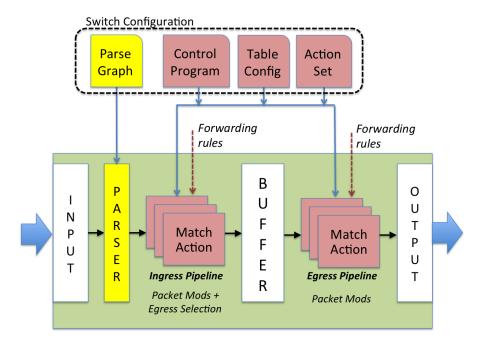

**Figure 2.7:** The P4 abstract forwarding model [17].

When the packet arrives to a P4-compliant switch, it is handled by the **parser** (see Figure 2.7). Parsing assigns logical labels to physical bit granularity segments of the packet. When the packet arrives to the **ingress** and **egress** processing pipelines, it uses those logical names, chosen by the programmer, to refer to the packet fields. For example, imagine the parser begins by extracting an Ethernet header, which we decided to call "eth". Suppose we defined that header as having three fields – the first two with 48 bits and the third with 16 bits, named "etherType". From thereon, if we write eth.etherType, the P4 switch knows it's a reference to bytes 12 and 13 of the physical packet.

In turn, the processing pipelines, ingress and egress, run the packet through a series of match+action tables. These tables can, among other things, modify header fields, set their output ports, or even clone the packet [3].

As a high-level language, P4 must be compiled down to the switch target. The P4 Consortium provides a front-end compiler that analyses the program for syntax correctness and transforms it to an intermediate representation (IR). The device manufacturer, in turn, must provide their back-end compiler to transform the IR to the device's own internal language (see Figure 2.8).

The original paper mentions a **table dependency graph** (**TDG**) that we deduce comes from the IR. As the name suggests, dependencies between tables constraining parallel

**Figure 2.8:** Workflow of a P4 programmer.

execution can be inferred using the TDG [17].

P4 has already gained notoriety [2] and is supported by companies such as Google, Amazon, Intel and Microsoft, among others. A number of works have already used the language, such as [27].

#### 2.2.1 P4-14 vs P4-16

The previous version of the P4 language, P4-14, assumes a specific architecture composed of the parser, ingress and egress processing pipelines [3][17], as in Figure 2.7. P4-16 does not make this assumption, supporting any architecture the manufacturer wishes to describe in an **architecture description file** [8].

Logically, since it supports any architecture, we can write one such file to describe the architecture P4-14 assumes by default. This has already been done by the P4 Consortium, in a file called v1model.p4. We henceforth refer to this architecture as v1model. It is the only architecture supported by the P4 software switch [1]. It provides a set of primitives and useful stateful memories, like the counters and registers.

The advantage of supporting multiple architectures is that manufacturers can now expose more capabilities of their device to differentiate. In addition, P4-16 restricted the set of primitives enabling it to promote backwards-compatibility. As such, it is expected this current release of the language to quickly become the reference.

This is the main reason we chose P4-16 to implement our NDN router. But there were other motivations as well. First, the previous work on P4 for NDN, described in §2.3, uses P4-14 [26], somewhat constraining this solution. For example, the maximum number of NDN name components is hardwired, due to P4-14's intrinsic nature. An expansion of the max components is therefore a challenging task, involving hand-writing code to support that increase of maximum components. P4-16, on the other hand, comes with numerous

parametrization features by default.

Second, and following from the above, we wished to make our solution as generic and modular as possible. As P4-14 constrains register sizes to a specific bit width [3], this would compromise storing Data content (in the Content Store), that does not have a fixed size, for instance.

Third, and most importantly, as P4 enables new switch architectures, it gives flexibility to innovate without the constraints of P4, by means of extern functions. We believe this to be crucial to materialize, in practice, fundamental structures such as the content store, an option we consider in our work.

#### 2.2.2 P4-16 program example for the v1model architecture

During our brief overview of P4 ( $\S2.2$ ), we learned that we could program devices using this high-level language, provided they are compatible, by offering a back-end compiler to translate an intermediate representation to the device's own language. This section surveys the features P4 provides. We construct a very simple switch that parses and forwards only the IP datagrams it receives.

#### **Data:** headers and structs

P4 programs begin with **header** definitions. They are defined similarly to C structs, indicating any number of fields sequentially aligned in memory. P4-16 also allows the definition of **struct** for various purposes, such as user metadata, the logical, parsed packet representation, temporary variables, among others. When working with this architecture, the user is obliged to use them to at least define the parsed packet (see Listing 2.1) and the user-defined metadata (not represented).

**Listing 2.1:** Header and struct definitions in P4-16.

```

header ethernet_h {

bit<48> dstAddr;

bit<48> srcAddr;

bit<16> ethernet_h ethernet;

}

```

#### **Parser**

Just as we parse a string in Java, for example, to grab an integer, we parse the packet in P4 to attempt to assign logical names to physical portions of the packet. Namely, the headers.

**Listing 2.2:** Parser definition in P4-16.

```

state start {

b.extract(p.ethernet);

transition select(p.ethernet.ethType) {

0x800: accept;

_: reject;

}

}

```

Listing 2.2 shows an example of a parser. It starts by extracting an Ethernet header, as defined in Listing 2.1, from the physical packet, represented by the object packet\_in. It is thus assumed that this is the first header of the packet. Then, it checks bytes 12 and 13 using the logical name p.ethernet.ethType. If it finds the value 0x800, then the packet is assumed to be an IP datagram, and proceeds to the processing pipeline. Otherwise, it is rejected and dropped.

#### **Processing pipelines**

The v1model architecture declares ingress and egress pipelines for packet processing, so we're going to define them. After parsing, our IP datagram follows to the ingress pipeline. Now, we need to read the destination MAC address and set the output port accordingly.

**Listing 2.3:** Ingress and egress definitions in P4-16.

```

control TopIngress(inout Parsed_packet p, inout Metadata m,

inout standard_metadata_t stdm) {

action Drop()

{ mark_to_drop(); }

action Set_Egress_Spec(bit<9> port)

{ stdm.egress_spec = port; }

table egress_arbitier {

reads = {

p.ethernet.dstAddr : exact;

}

actions = {

Set_Egress_Spec;

Drop;

default_action = Drop;

}

//The actual flow of execution begins here.

apply {

egress_arbitier.apply();

```

```

}

}//End of ingress pipeline.

control TopEgress(inout Parsed_packet p, inout Metadata m,

inout standard_metadata_t stdm)

{

}

```

Listing 2.3 shows the processing flow. The ingress pipeline, which we name TopIngress, acts upon a parsed packet, the user-defined Metadata, and the standard metadata. Since they all have **inout** status, we can read from and write to all of them. Previously, we saw the Parsed\_packet structure as **out**, which is a status of a parameter that has not been initialized. **in** means read-only.

The ingress processing flow is made of a single call for egress\_arbitier to be applied. This table reads the parsed packet's ethernet destination address and executes one (and only one) of two actions: drop or set output port. Whether one or the other occurs depends on what entries are there to match on. Remember P4 is meant to define only the data plane. It can read from tables, but it cannot modify them. Tables are populated at boot and/or run time by the control plane.

If we find a matching entry whose action is Set\_Egress\_Spec, then we modify the standard metadata egress\_spec field to indicate that the packet should follow through that port.

After we've switched the packet appropriately, there's nothing left to be done. Therefore, our TopEgress is empty.

#### Other blocks, data types and features

The architecture offers three other control blocks: the deparser, the checksum calculator and the checksum verificator. The deparser is a novel feature in P4-16 which allows the programmer to selectively deparse headers, omitting or rearranging them. In principle, we should write b.emit (p.ethernet), indicating that we wish for the Ethernet header to be returned to the packet and transferred back to the network with it.

Throughout our demonstration, we encountered the **bit** type multiple times. This datatype represents an unsigned bit vector of whatever length known at compile-time. There are other types available, such as int < x >, which is a signed integer, or **bool**.

There are other constructs in the language which deserve mentioning<sup>6</sup>:

• One of the most important is perhaps the **varbit** datatype, which is a variable length bit string. There are two catches to using this datatype. First, when declaring

<sup>&</sup>lt;sup>6</sup> Throughout this text, the reader may encounter words like **table**, **parser**, and **header\_union** in bold and colored blue or teal. These are P4 keywords, not emphasis.

a **varbit**, it is mandatory to specify its  $\underline{\text{maximum width}}$ , a compile-time known constant. For example,  $\underline{\text{varbit}} < 2048 > \text{means the field is at most 2048 bits long.}$

The second catch to using varbits is that the language offers no ways to interact with them, other than: 1) extracting packet data into them; 2) emitting them in the departs block; 3) copying over the data to a varbit of the same maximum size, and 4) hashing the value held by the varbit through the primitive action or P4-16's **extern** equivalent. Therefore, information can be stored within varbit, but, once there, it is generally inaccessible for reading or processing.

- Both versions of P4 also possesses the notion of **header stack**, which is no more than an array of headers of the same type. It is useful to deal with layers of MPLS, for example.

- P4-16 has a **header union**, which is a data type paradigm similar to C unions. The header union is defined as a set of headers, and only one of them is filled at all times. This is useful when we encounter a crossroads between several possible header shapes (for example, TCP options). Unlike C unions, however, they do not have underlying memory quirks, behaving more like tagged unions [11].

- Novel to P4-16, and perhaps most important of all, is the **extern**. These are constructs implemented by manufacturers directly on the device, while their interface is specified using P4 syntax in the architecture description file. This permits vendors to expose more functionality. For the software switch, implementing an extern could imply creating a C++ class.

- P4-14 provided stateful memories such as the counter, the meter and the register to maintain inter-packet state. When P4-16 was released and P4-14's architecture became v1model, these features were declared as **extern** in its architecture description file.

Externs come in two flavors: extern functions and extern instantiable blocks. Functions are invoked in the way you'd expect to do whatever work they're programmed internally to do. Instantiable blocks introduce P4 to the object-oriented paradigm. Their interface provides a series of methods and may contain generic types. They are instantiated inside the P4 program and bound to a specific P4 datatype.

Although the program we presented is syntactically correct, and is accepted by the front-end compiler, the software switch back-end compiler rejects it due to its limitations. We explore those limitations later in §4 (Implementation). The reader interested in further exploring P4-16's capabilities may read the full P4-16 specification in [8].

### 2.2.3 Behavioral Model 2 (BMv2) and p4c

There is an implementation of a P4 software switch called Behavioral Model 2 that almost completely supports both P4-14 and P4-16 programs, though prepared for P4-14's default architecture, v1model.p4 [1]. We conclude this analysis with a brief overview of BMv2, also known as the "P4 software switch" [1]. This analysis is important so that we can understand the terms, as well as the differences between what the P4 language defines and what the current software switch supports.

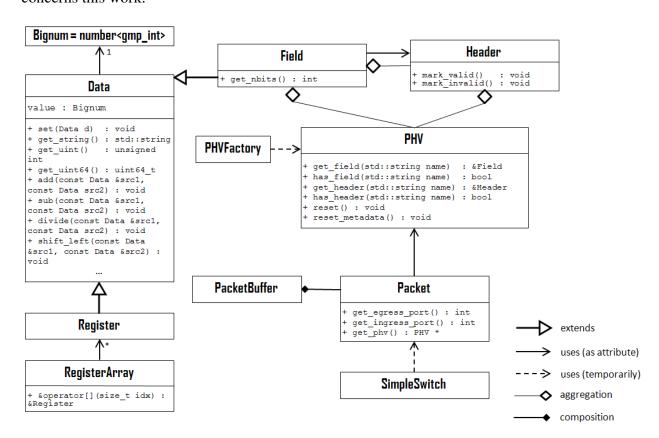

First, it is important to make a distinction. BMv2 itself is a C++ library. It possesses an object model that seems familiar to our context. Its classes include Packet, Header, Field, Data, and so on. See Figure 2.9 for a simplified version retaining the part that concerns this work.

Figure 2.9: A loose, very simplified excerpt of the BMv2 class diagram.

BMv2 also has a directory named **targets**. These are, in fact, the runnable components. Each of these targets implements the P4-14 specification [3], in software, to a different extent. For example, 12switch implements only three or four primitives, using the object model provided by the BMv2 library.

Of the three targets provided by the P4 Consortium, the most complete is  $simple_switch$ . However, it does have limitations, some of which we ran into during our work. We explore them in  $\S4.1$ .

As mentioned in §2.2, the p4 compiler is divided into front-end and back-end. The front-end verifies the program's syntax and semantics to conform to the specification. This exempts manufacturers from having to repeatedly build a compiler for syntax checking. The back-end converts the IR to something the device can understand. BMv2 (in particular, simple\_switch) is a software target, and therefore has a back-end compiler for it as well. P4-14 and P4-16 programs can be compiled for it using p4c [12], the official, yet still alpha-stage, p4 compiler. One of its runnables is p4c-bm2-ss, which, as the name suggests, is the back-end compiler for BMv2 simple\_switch.

# 2.3 NDN.p4

NDN.p4 [26] was the first attempt to define an NDN router's data plane as a P4 program, and it is therefore the work closer to ours. This work proposes a basic version of the PIT and the FIB. The main limitations of this solution is that it does not include a content store, vital for the success of the NDN as a distribution network, and, by using P4-14, its flexibility is limited, and real deployments are not to be expected in practice.

We study NDN.p4's implementation in this section.

## 2.3.1 Type-length-value parsing

NDN.p4 begins by defining five header types<sup>7</sup>. The first has 8 bits of type, 8 bits of lencode and a variable amount of bits for the value. The other headers have 16, 32 or 64 bits of extended length, but no variable field for the value. These are called "TL" headers, meaning they represent only the type and length.

When parsing, NDN.p4 begins by looking 2 bytes ahead. Scanning the last of those two bytes, it decides what header should be extracted. Concretely, it jumps to one of four states: one extracts the TL header which has 16 bits of extended length, the other extracts the header type with 32 bits of length extension, and the last extracts the header type with a 64 bit extension. By default, it extracts the header containing 8 bits of type and 8 bits of length (see Listing 2.4).

Listing 2.4: Parsing TLV0 in [26].

```

parser parse_ndn {

return select(current(8,8)) {

253 : parse_medium_tlv0;

254 : parse_big_tlv0;

255 : parse_huge_tlv0;

default : parse_small_tlv0;

}

}

```

<sup>&</sup>lt;sup>7</sup> Keep in mind this solution was written using P4-14, which syntactically is quite different from P4-16.

$TLV_0$  and  $TLV_N$  are the only ones that can have this extended field (and no value, since they are parent-TLVs). For all other NDN packet fields except content, NDN.p4 assumes a small TLV; that is, of up to 252 bytes of value.

The Data content is not treated. The parser extracts the type, the length and the extension into a TL header, but does not parse any content value whatsoever. This seems to hint that NDN.p4 is therefore unfinished with regard to basic Data packet processing.

### **2.3.2** Forwarding Information Base (FIB)

P4 does not support longest prefix match on strings. To workaround this, [26] backs up on two other match types: exact and ternary.

First, the router hashes aggregations of components. More concretely, given a name made of components  $c_0$ ,  $c_1$ , ...,  $c_n$ , the router employs a hash function h (in practice, crc-16) to calculate  $h(c_0)$ , then  $h(c_0, c_1)$ ... and finally  $h(c_0, c_1, ..., c_n)$ , where n is the number of components. It does this both when inserting route entries into the FIB and when an Interest is received.

- When the control plane inserts a route, it has to add a number of entries to the FIB given by Max n + 1, where n is the component count of the name being inserted and Max is the maximum number of components the device is programmed to parse. The entries are inserted with the concatenation of all hash outputs and with a number of components that goes from n to Max (see the layout of Table 2.1 for an example).

- When an Interest is received, the router calculates the aggregations as mentioned above. Then, it performs an <u>exact match</u> on the number of components and a ternary match on the aggregation with the right number of components.

Considering an example where the router receives an Interest for "a/b/c/d" and the FIB contains two routes as displayed in Table 2.1, then the Interest still matches two entries from those two different routes (highlighted in yellow on the table). The number of components matches (4 components). Also, the router calculated h("a/b"), yielding BF41, which matches the third rule, and h("a/b/c"), yielding 357F, which matches the fifth rule.

| Route   | Ternary | Match | ncomps | <b>Egress Port</b> |   |    |

|---------|---------|-------|--------|--------------------|---|----|

| "a/b"   | 0x ???? | BF41  | ????   | ????               | 2 | 13 |

| "a/b"   | 0x ???? | BF41  | ????   | ????               | 3 | 13 |

| "a/b"   | 0x ???? | BF41  | ????   | 3333               | 4 | 13 |

| "a/b/c" | 0x ???? | ????  | 357F   | ????               | 3 | 21 |

| "a/b/c" | 0x ???? | ????  | 357F   | 3333               | 4 | 21 |

**Table 2.1:** A FIB in NDN.p4 containing 2 routes, one for "a/b" and another for "a/b/c". An Interest for "a/b/c/d" matches two entries. Max = 4

Recall our objective is longest prefix match, so the bottom rule should be chosen, and the Interest should exit towards port 21. To disambiguate, NDN.p4 adds an extra priority field to the FIB (not shown in Table 2.1), which is set higher for routes with a bigger number of components.

### 2.3.3 Pending Interest Table (PIT)

The PIT was built as a set of 16 bit hashes. When an Interest arrives, the router consults the PIT to see if its set contains the name hash. If it doesn't, then the Interest is forwarded out the corresponding output port.

Looking into the source code, one can see the authors meant to implement Data multicast by relying on a bit mask<sup>8</sup>. The compiler would then be modified to replicate the code in order for the Data packet to be copied and sent out in accordance to that bit mask. However, the lines that were supposed to be part of that process are commented out. Thus, multicast of Data is not supported.

In its latest setup, NDN.p4 stores no port upon processing an Interest. When receiving a Data packet, the action is to send it out a fixed port that was determined in a file that populates tables at boot time. This is another limitation: Data packet forwarding does not happen correctly.

# 2.4 Summary

In this chapter, we explored two proposals to change the network that were motivated by the problems of IP, namely, named data networks (NDN), in 2.1, and programmable networks, in 2.2, both of which provide the core context to our dissertation. We finished by exploring NDN.p4 in 2.3, which is the main background work on which ours improves.

<sup>&</sup>lt;sup>8</sup>We employ an identical scheme, though we arrived at it independently.

# Chapter 3

# **Design**

In this chapter we discuss our solution design to meet the objectives proposed at the beginning of this dissertation. It would be uninteresting to be exhaustive about possibilities when, in the end, we would have to adapt the solution to the constraints imposed by P4 and programmable switches in general. Therefore, bear in mind these algorithms were envisaged taking P4's capabilities into account.

This chapter is organized as follows. We describe the general architecture of our solution. Afterwards, we introduce the reader to the partition structure ( $\S 3.1$ ), which is key in our improved FIB design. Then, after an overview of the processing flow ( $\S 3.2$ ), we study our design of the FIB lpm matching ( $\S 3.3$ ), the PIT ( $\S 3.4$ ) and the Content Store ( $\S 3.5$ ).

We strictly follow the name data networking architecture as presented in Figure 2.4. As we have mentioned, our solution is the first to design and implement a full NDN router with all its core functionalities, so the building blocks faithfully abide to those represented in the figure.

## 3.1 Partition

Recall from §2.1 that NDN uses arbitrarily long names, and not 32-bit addresses, to route Interests, obeying the longest prefix match (lpm) rule applied at the granularity of the component. For example, when the router receives an Interest for "pt/ulisboa/fciencias/in-dex.html", it should prefer a route for "pt/ulisboa/fciencias" over a route for "pt/ulisboa". Interests seen by the router for the first time are forwarded using the structure known as the FIB, which maps names to output interfaces.

Any solution envisioning the use of (variable-length) strings cannot be materialized directly because P4 offers little support for fields of arbitrary length. P4 registers and tables do not accept, respectively, storing/reading or matching on arbitrary length fields (varbit). Therefore, any solution is required to map strings to a construct of a width deducible at compile time. This is an intricate limitation of *any* P4 implementation. NDN.p4

[26], for example, leveraged on P4's capability we mentioned earlier of making it possible to hash variable length fields.

#### 3.1.1 Motivation for a new solution

NDN.p4's [26] method backed up on ternary match of an aggregated hash of components and exact match on the number of components. The authors set the maximum number of components to 4, and the FIB was defined as a table that made: an exact match on the number of components, and 4 ternary matches on the following fields:  $h(c_1)$ ,  $h(c_1, c_2)$ ,  $h(c_1, c_2, c_3)$ , where  $c_i$  is component number i, and finally the hash of the whole name.

To insert a route onto the FIB, the control plane should add Max - n + 1 rules, where Max = 4 and n is the number of components of the route name. NDN.p4 [26] uses crc-16, therefore its hash length is 16 bits.

So, each rule necessarily has at least 4 fields (not counting priority or number of components), of 16 bits each. If there are two components, then one needs to add 4-2+1=3 rules. In total, this amounts to  $16\times4\times3=192$  bits.

The resulting size of adding so many rules does not scale well. For a 25 maximum component device, a route of 19 components, and a hash function of 16 bit output, a route occupies at least  $25 \times 19 \times 16 = 7600$  bits, again not counting the number of components and priority matching fields.

## 3.1.2 An innovative concept: the partition

Recycling Signorello et al's [26] idea, we employed hashes as well. Let Max be the maximum number of components the device can parse. Consider a hash function of output length n. We can think of crc-16 (n=16 bits) and 64 maximum components as an example. Given this, we create a structure composed of 64 blocks of 16 bits; generically, in Max blocks of n bits. We decided to call this multipartite structure a **partition**.

<u>DEFINITION</u>: A **Partition**<sup>1</sup> is a structure divided in a number of equally-sized blocks, where each block i keeps the result of processing component i of a NDN name through a common hash function, or 0 if no such component exists.

The reader can think of the partition as a processed name. Therefore, the PIT, which stored an association of <name, interface list>, stores an association of <partition, interface list> in our solution. The FIB also maps partitions to outgoing ports.

In Algorithm 1, we explain the process to build the partition from the name. It must be used when inserting entries onto the FIB or when matching Interests against them.

Our objective with this algorithm is the following. We hash the first component and place it in the leftmost block; then we hash the second component and place it in the

<sup>&</sup>lt;sup>1</sup> Throughout this dissertation, we use the terms "partition", "name partition" and "partition of hashed components" interchangeably.

Chapter 3. Design 23

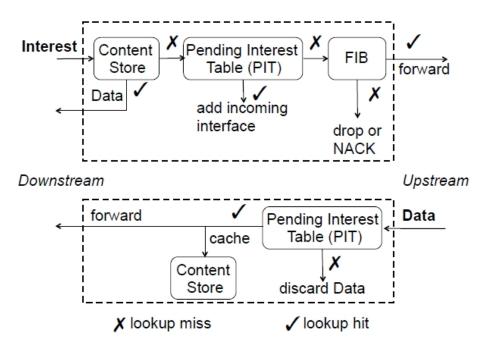

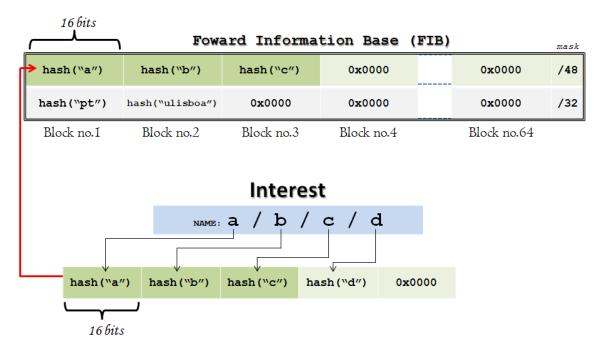

**Figure 3.1:** The Interest matches a FIB entry by lpm.

second block; and so on. This will later serve to perform longest prefix matching, as per Figure 3.1.

An interesting thing to note about this algorithm is that it has a cycle, but P4 has no iteration or recursion. In any programming paradigm, when the number of instances of some input isn't known beforehand, the solution is to cycle through the input. However, while parsing the TLV structure of the packet, it is impossible to know the number of components ahead of time. TLVs indicate their size, but not the number of children they have. For example, if we find that  $TLV_N$  is 6 bytes long, it is impossible to know if it is composed of two components of 1 byte each ("a/b"), or a single component of 4 bytes ("jazz").

One solution to deal with this problem would be to count the number of components by parsing the entire packet once, store in metadata, and then resubmit the packet to the parser with its metadata. This represents a huge overhead; each packet would approximately count for two. Fortunately, the parser is a state machine, and P4 has no problem with a state machine transitioning to itself. Therefore, we wrote a parser state that transitions to itself while we haven't parsed a number of bytes equal to the advertised  $TLV_N$  size.

#### An example

Let us analyze the algorithm more carefully. This algorithm is invoked when we begin parsing  $TLV_N$ , whose value is a series of  $TLV_S$ . As we parse, the first thing we encounter is the  $TLV_N$  type and length, as well as the extension if there is one. We remember the

**Algorithm 1** Calculation of a partition of hashed components, given a hash function h producing output of length n

```

1: function BUILDPARTITION(TLV_N)

2:

Read the next component TLV into c

len \leftarrow TLV_N.size - 2 - c.extensionsize - c.size \triangleright size is indicated by

3:

lencode or extension

4:

acc \leftarrow h(c.value)

count \leftarrow 1

Names must have at least 1 component

5:

while len > 0 do

6:

if count > MAX then

7:

Abort and signal error

8:

end if

9:

Read the next component TLV into c

10:

11:

acc \leftarrow acc \ll n

\triangleright « is bitwise shift-left

acc \leftarrow acc | h(c.value) |

12:

len \leftarrow len - 2 - c.extensionsize - c.size

▷ c.size includes type, lencode

13:

and extension

14:

count \leftarrow count + 1

15:

end while

return acc \ll ((MAX - count) \times n)

16:

17: end function

```

size seen ( $TLV_N.size$  in the algorithm) so as to know when to stop. We do not know how many components there are, but all names have at least one component, so we parse the next component (line 2) and subtract its total size, including the 2 bytes occupied by its type and lencode, as well as the size occupied by the length extension (line 3, c.extensionsize).

We hash the value of the first component TLV and place it inside an accumulator (line 4). The number of components is important to know when the device has reached its limit, but we will need it later as well (line 16).

Let's study an example for an hash algorithm of 16 bit-wide output. Imagine MAX is equal to 4 and the router is going to parse an Interest for "a/b". These components occupy 1 byte each, and their type and length will occupy 2 bytes each. Therefore,  $TLV_N.size = 6$ . In line 3 we parse the first component immediately, and len becomes 6-2-0-1=3. The accumulator acc is basically a partition being built. Let us represent its state after line 4 by EMPTY|EMPTY|h("a"), where each segment separated by pipe ('|') is a 16 bit block of the partition accumulator (the pipe here is a block delimiter, not bit-OR).

In lines 7 through 9, count is 1, which is less than MAX=4, so we proceed to line 10 and read the TLV that encodes "b". The accumulator is shifted left by 16, becoming EMPTY|EMPTY|h("a")|EMPTY. On the next line (line 12), we bit-OR<sup>2</sup> the hash of the next component value, "b", with the accumulator. The accumulator then becomes:

<sup>&</sup>lt;sup>2</sup> Addition would have worked just as well, but bitwise operations are computationally cheaper.

```

EMPTY|EMPTY|h("a")|h("b").

```

Line 13 sets the len variable to 3-2-0-1=0, so the cycle stops when re-evaluated. Line 14 sets count=2. Our partition building process is almost complete. However, remember that the purpose of the partition was to be a tool for the FIB to achieve longest prefix matching. The significant information covered by the lpm mask is always found on the left side of IP addresses, and the same applies here.

Line 16 performs this last step. Below follow the sequence of performed operations:

```

EMPTY|EMPTY|h("a")|h("b") \ll ((Max - 2) \times 16)

= EMPTY|EMPTY|h("a")|h("b") \ll (2 \times 16)

= h("a")|h("b")|EMPTY|EMPTY

```

### 3.1.3 The advantages of using a partition to represent a name

Recall our previous example of a device that parses at most 64 components (therefore, a partition has 64 blocks) and uses crc-16, whose hash output is 16 bits long (each block is 16 bits-wide). Take that example and examine Figure 3.1. It is elucidating on the interactions described in the previous paragraphs. In the figure, an Interest for "a/b/c/d" matches, by lpm, the first entry of the FIB ("a/b/c"). If an entry existed on the FIB for "a/b", it would be turned down, because the matching entry in the figure has a longer mask.

Note, also, that using a partition, built for a maximum of 25 components and 16 bit hash output, to represent a FIB route would occupy  $25 \times 16 = 400$  bits, significantly less (approximately 5%) than in NDN.p4, which, as we said above, occupies 7600 bits.

#### 3.1.4 A note on hash collisions

By now, the reader should be wondering about hash collisions. Informally, it is trivial this problem may occur if we observe that our hash length is only 16 bits (65535 possible values), while the theoretical name length is bounded only by the size of the NDN packet. Logically, if the set of names is larger than the set of hash outputs, then a (total) surjective function exists from the former to the latter; consequently, there are at least two names with the same hash. Let "pt" and "en" be two 16-bit mask entries in our FIB. If, by misfortune, hash("pt") == hash("en"), then the router will be performing wrong forwarding decisions.

The limit case is when the router forwards the Interest back to its incoming port. In a traditional IP network, this would result in sending a packet back and forth until the TTL or hop count reached zero. Fortunately, in NDNs, the Interest nonce would serve for the downstream router to detect that the Interest is repeated, therefore discarding the packet.

NDN.p4 does not address the problem of hash collisions. The authors admit that hash

Chapter 3. Design 26

collisions may occur when registering PIT records, in which case an existing entry is replaced. This is a necessary consequence of the lack of iteration and recursion in P4, as well as the appropriate map data structure. It is not stated what are the consequences of hash collisions on FIB entries, but we assume the aforementioned problem holds.

Because we also employ hashes, our solution can therefore also suffer from the consequences of hash collisions. Since the environment is a forwarding device, we can consider a limited set of options.

- We may use a sophisticated hash (such as a cryptographic one) that is more resistant to collisions, but its use is nontrivial in switches.

- We may increase the hash length to reduce the probability of hash collisions, but we pay for this with increased entry size.

- We may reduce the maximum number of name components, thus reducing table size, but we'll be limiting applications' namespaces.

We took a mental note of these facts to make the resulting P4 implementation (§4) flexible regarding hash length and maximum number of components.

## 3.1.5 Attempts at collision prevention

For a more formal presentation, let A be the alphabet of possible characters for a name component and |A| its length. For exemplification sake, let  $A = \{a..z, 0..9\} \implies |A| = 36$ . Let  $c \in \mathbb{N}$  be the <u>maximum</u> number of characters in a component. If our hash is 16 bits long, then

$$\sum_{i=1}^{c} 36^i < 2^{16} - 1$$

is a necessary condition to ensure the possible hash function output is a set large enough to accommodate the possible combinations of characters<sup>3</sup>. Solving this inequation through simple iteration of possible values for c is not too complicated. It yields

$$c \leq 3$$

What this result means is that components may have up to 3 characters (amounting to  $36^3 + 36^2 + 36 = 47988$  string combinations, which is less than  $2^{16} - 1 = 65535$  hash outputs). Examples: "www/cam/ac/uk", or "www/fc/ul/pt" (all components have no more than 3 characters, and all these characters are in A).

Generalizing from the formula above,

<sup>&</sup>lt;sup>3</sup> This does not prove there are no collisions; that, of course, depends on the hash function, but the contrary condition ensures that some 2 strings share the same hash output.

$$\sum_{i=1}^{c} |A|^{i} < 2^{h} - 1$$

27

(h is the hash length) is a condition that ensures the set of hash outputs is larger than the possible string combinations for a component.

# 3.2 Packet Processing

Algorithm 2 describes the processing flow we want NDN packets to undergo. Read below for a description of the algorithm.

```

Algorithm 2 Flow of processing for a packet

```

```

1: function PROCESS(packet)

p \leftarrow BUILDPARTITION(packet)

See Algorithm 1

v \leftarrow \text{PIT.get}(p)

\triangleright The bit vector for this name is retrieved into v

3:

if packet.type = INTEREST then

4:

d \leftarrow \text{CS.retrieve}(p)

5:

if d \neq NULL then

> CS had cached Data for this name

6:

7:

Serve d through packet's ingress port

Drop

8:

9:

return

end if

10:

UPDATEPIT(p)

See Algorithm 3

11:

if v = 0 then

▶ First Interest seen for this name!

12:

Run packet through the FIB

13:

end if

14:

15:

else if packet.type = DATA then

16:

if v = 0 then

▶ Empty port vector means this Data is unwarranted

17:

Drop

18:

return

19:

20:

end if

21:

multicast(packet, v)

PIT.clean(p)

22:

23:

end if

24: end function

```

Lines 4 and 16 check what type of packet we're dealing with.

• If we're dealing with an Interest (line 4), then we check the Content Store for Data (line 5). If we find Data cached for this name/partition, then we can serve directly (line 7) and drop the current packet (line 8). Otherwise, we update the PIT to record the partition (line 11). This call will set the bit corresponding to the port whence

this Interest came. If, before that update, the bit array (extracted in line 3) was 0, then we must forward it upstream (line 13).

• If we're dealing with Data (line 16), then we check the partition we loaded to see if it is non-empty. If it is empty (line 17), then this is a spurious Data packet and should be dropped (line 18). Otherwise, we multicast it to all set ports (line 21). Afterwards, we can clean this entry (line 22).

Intentionally, we do not detail what happens in the ingress and what happens in egress. The call to *multicast* can be thought of as a two-phased wrapper for Algorithm 4 and Algorithm 5, which, as we'll see, are quite similar in design.

# 3.3 FIB Longest-prefix Matching