# COLLABORATIVE HARDWARE-SOFTWARE MANAGEMENT OF HYBRID MAIN MEMORY

by

## Santiago Bock

B.S. in Computer Science, University of Los Andes, Bogotá, 2007B.S. in Computer Engineering, University of Los Andes, Bogotá, 2007

Submitted to the Graduate Faculty of

the Kenneth P. Dietrich School of Arts and Sciences in partial

fulfillment

of the requirements for the degree of

Doctor of Philosophy

University of Pittsburgh

2017

## UNIVERSITY OF PITTSBURGH DIETRICH SCHOOL OF ARTS AND SCIENCES

This dissertation was presented

by

Santiago Bock

It was defended on

November 3rd 2017

and approved by

Bruce R. Childers, Department of Computer Science

Rami Melhem, Department of Computer Science

Daniel Mossé, Department of Computer Science

Jun Yang, Department of Electrical and Computer Engineering

Dissertation Director: Bruce R. Childers, Department of Computer Science

## COLLABORATIVE HARDWARE-SOFTWARE MANAGEMENT OF HYBRID MAIN MEMORY

Santiago Bock, PhD

University of Pittsburgh, 2017

DRAM has long been the preferred technology choice for main memory. With new challenges of high energy and scalability of DRAM, emerging non-volatile memory technologies, such as phase-change memory (PCM), are being considered. Typically, PCM is used in conjunction with DRAM to form a hybrid main memory. Exposing both the PCM and DRAM to the system software and managing it through the operating system (OS) is a viable architecture. The advantage of this organization is that current systems are more easily adapted to support a partitioned DRAM/PCM address space with only small changes to their design. In addition, this architecture is the easiest path forward to incorporate persistence in the main memory hierarchy by reserving part of PCM for storage.

However, the performance of software-managed hybrid memory is not on par with hardwareonly approaches, such as the DRAM cache. This is caused by the large granularity at which data is migrated (OS pages) and the low visibility that the OS has of the access patterns of applications. This thesis proposes an experimental framework for studying softwaremanaged hybrid memory and uses it to understand the causes of its low performance. In addition, this thesis proposes and evaluates several hardware-software co-designed mechanisms to alleviate the performance impacts of managing hybrid memory in software. Lastly, this thesis proposes a new migration policy specifically designed to take advantage of the new hardware support. These contributions show that software-managed hybrid memory with specialized hardware support for migration and monitoring is a viable architecture for PCM-based hybrid main memory.

## TABLE OF CONTENTS

| 1.0 | IN' | <b>FRODUCTION</b>                          | 1 |

|-----|-----|--------------------------------------------|---|

|     | 1.1 | Relevance                                  | 2 |

|     | 1.2 | Elements of a Good Solution                | 4 |

|     | 1.3 | Approach Overview                          | 5 |

|     | 1.4 | Thesis Contributions                       | 7 |

|     | 1.5 | Thesis Organization                        | 8 |

| 2.0 | BA  | CKGROUND AND RELATED WORK                  | 9 |

|     | 2.1 | Phase Change Memory                        | 9 |

|     | 2.2 | Architectural Support for PCM              | 0 |

|     |     | 2.2.1 Write Reduction                      | 1 |

|     |     | 2.2.2 Write Cancellation and Write Pausing | 2 |

|     |     | 2.2.3 Wear Leveling                        | 3 |

|     | 2.3 | Hybrid Main Memory                         | 4 |

|     |     | 2.3.1 Hardware-Managed Hybrid Memory       | 5 |

|     |     | 2.3.2 DRAM Caches                          | 5 |

|     |     | 2.3.3 Smart Memory Controllers             | 7 |

|     |     | 2.3.4 Software-Managed Hybrid Main Memory  | 7 |

| 3.0 | SIN | IULATOR INFRASTRUCTURE         1           | 9 |

|     | 3.1 | Overview                                   | 0 |

|     | 3.2 | Memory Hierarchy                           | 1 |

|     | 3.3 | Memory Manager                             | 3 |

|     | 3.4 | HMMSim API                                 | 3 |

|     | 3.5 | Trace Compression                         | 24 |

|-----|-----|-------------------------------------------|----|

|     | 3.6 | Performance                               | 26 |

|     |     | 3.6.1 Execution Time                      | 27 |

|     |     | 3.6.2 Memory Usage                        | 28 |

|     |     | 3.6.3 Trace Compression                   | 28 |

|     | 3.7 | Summary                                   | 29 |

| 4.0 | CH  | ARACTERIZATION OF OVERHEAD                | 30 |

|     | 4.1 | Overview                                  | 30 |

|     | 4.2 | Page Migration Latency                    | 31 |

|     | 4.3 | Other Limiting Factors                    | 32 |

|     | 4.4 | Analysis                                  | 34 |

|     |     | 4.4.1 Zero-Interference Migration         | 35 |

|     |     | 4.4.2 Offline Migration Policy            | 36 |

|     |     | 4.4.3 Memory Latency Attribution Analysis | 37 |

|     |     | 4.4.4 Factor Isolation Analysis           | 38 |

|     | 4.5 | Page Migration Overhead                   | 40 |

|     |     | 4.5.1 Methodology                         | 41 |

|     |     | 4.5.2 Memory Latency Attribution          | 42 |

|     |     | 4.5.3 Factor Isolation Analysis           | 46 |

|     |     | 4.5.4 Migration Policy Overhead           | 47 |

|     | 4.6 | Design Implications                       | 48 |

|     | 4.7 | Summary                                   | 49 |

| 5.0 | CO  | NCURRENT PAGE MIGRATION                   | 50 |

|     | 5.1 | Overview                                  | 50 |

|     |     | 5.1.1 Memory Management                   | 50 |

|     |     | 5.1.2 Page Migration                      | 51 |

|     | 5.2 | Concurrent Page Migration                 | 53 |

|     |     | 5.2.1 Buffering Writes                    | 53 |

|     |     | 5.2.2 Page Migration                      | 54 |

|     | 5.3 | Hardware Support                          | 56 |

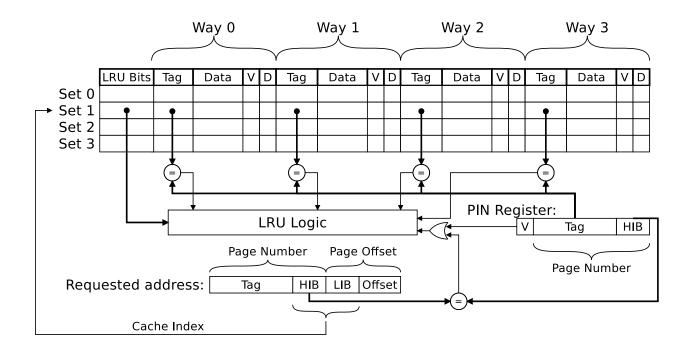

|     |     | 5.3.1 Overview of Architecture and Changes                                                                                                              | 56 |

|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     |     | 5.3.2 Cache                                                                                                                                             | 58 |

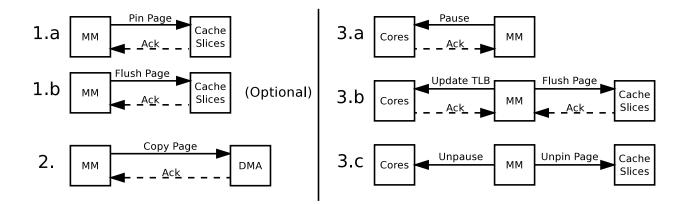

|     |     | 5.3.3 Concurrent Page Migration                                                                                                                         | 61 |

|     | 5.4 | Evaluation                                                                                                                                              | 62 |

|     |     | 5.4.1 Methodology                                                                                                                                       | 63 |

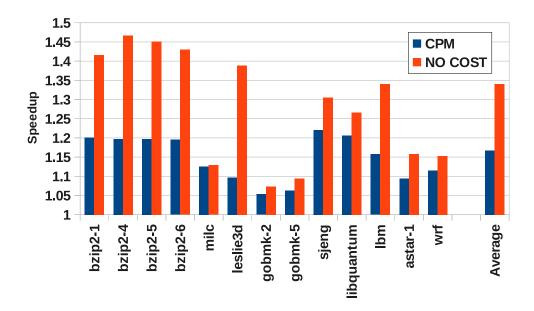

|     |     | 5.4.2 Single-Programmed Benchmarks                                                                                                                      | 64 |

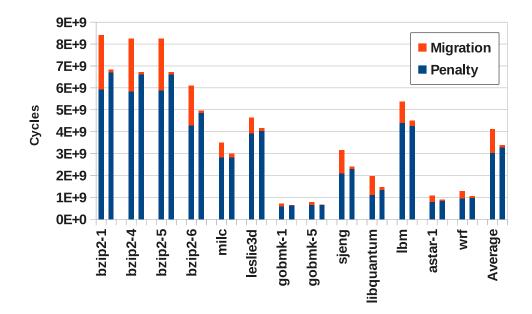

|     |     | 5.4.3 Stall Behavior                                                                                                                                    | 65 |

|     |     | 5.4.4 Energy                                                                                                                                            | 67 |

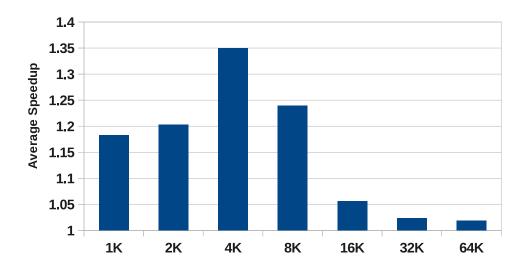

|     |     | 5.4.5 Sensitivity to Migration Cost                                                                                                                     | 68 |

|     |     | 5.4.6 Multi-Programmed Workloads                                                                                                                        | 69 |

|     | 5.5 | Summary                                                                                                                                                 | 71 |

| 6.0 | CO  | NCURRENT MIGRATION OF MULTIPLE PAGES                                                                                                                    | 72 |

|     | 6.1 | Concurrent Migration of Multiple Pages                                                                                                                  | 72 |

|     |     | 6.1.1 Migration Policy                                                                                                                                  | 74 |

|     |     | 6.1.2 Concurrent Migration                                                                                                                              | 74 |

|     |     | 6.1.2.1 Promotion                                                                                                                                       | 75 |

|     |     | $6.1.2.2 Demotion \ldots \ldots$ | 76 |

|     |     | 6.1.3 On-Demand Block Migration                                                                                                                         | 77 |

|     |     | 6.1.4 Access Redirection                                                                                                                                | 77 |

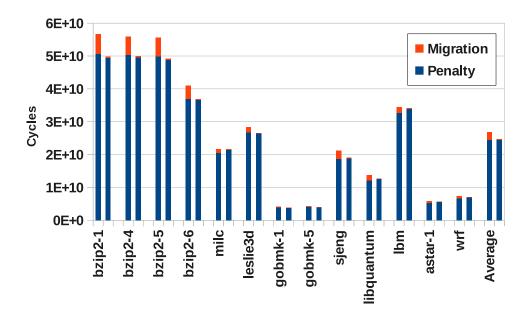

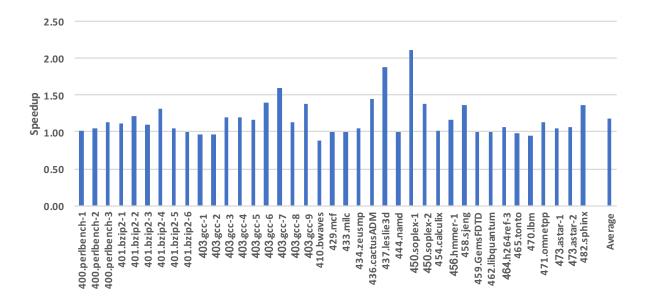

|     | 6.2 | Experimental Results                                                                                                                                    | 79 |

|     |     | 6.2.1 Methodology                                                                                                                                       | 79 |

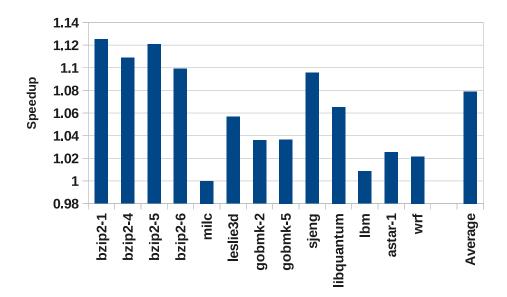

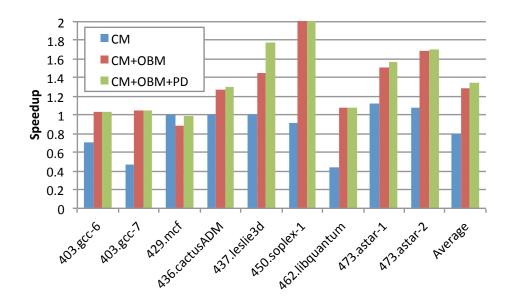

|     |     | 6.2.2 Performance                                                                                                                                       | 80 |

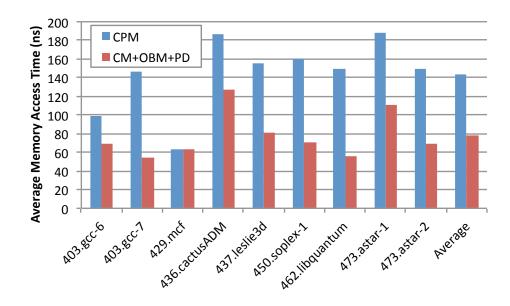

|     |     | 6.2.3 Average Memory Access Time                                                                                                                        | 83 |

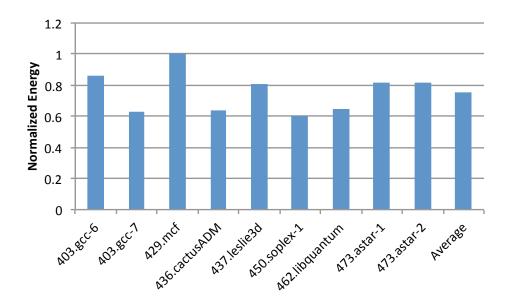

|     |     | 6.2.4 Energy                                                                                                                                            | 83 |

|     | 6.3 | Summary                                                                                                                                                 | 84 |

| 7.0 | тн  | IRESHOLD MIGRATION POLICY                                                                                                                               | 85 |

|     | 7.1 | Overview                                                                                                                                                | 85 |

|     | 7.2 | Threshold Migration Policy                                                                                                                              | 87 |

|     |     | 7.2.1 Monitoring                                                                                                                                        | 87 |

|     |     | 7.2.2 Data Structures                                                                                                                                   | 87 |

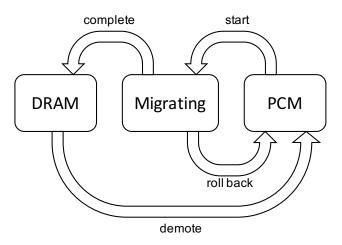

| 7.2.3 Completion, Demotion and Rollback | 89  |

|-----------------------------------------|-----|

| 7.2.4 Analysis                          | 91  |

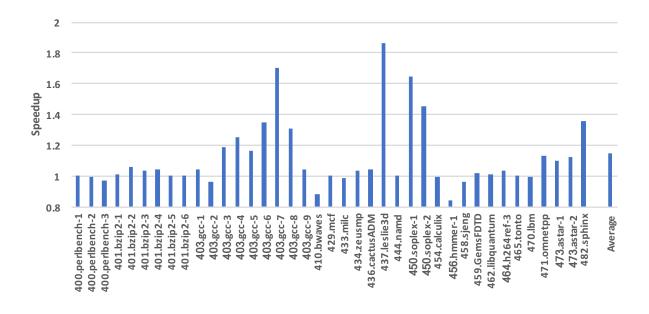

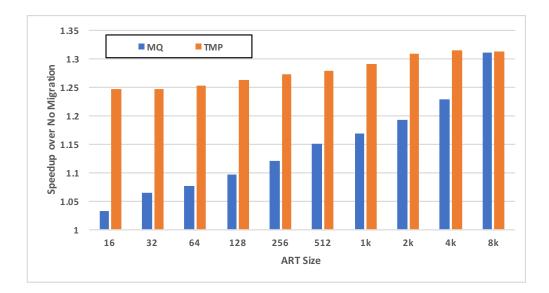

| 7.3 Evaluation                          | 91  |

| 7.3.1 Methodology                       | 91  |

| 7.3.2 Performance                       | 93  |

| 7.4 Comparison to Ideal System          | 96  |

| 7.5 Summary                             | 98  |

| 8.0 CONCLUSIONS                         | 99  |

| BIBLIOGRAPHY                            | 101 |

### LIST OF TABLES

| 1  | Comparison of DRAM and PCM Parameters                                 | 10 |

|----|-----------------------------------------------------------------------|----|

| 2  | Comparison of some existing memory simulators                         | 21 |

| 3  | Main API components and their methods currently provided by HMMSim    | 25 |

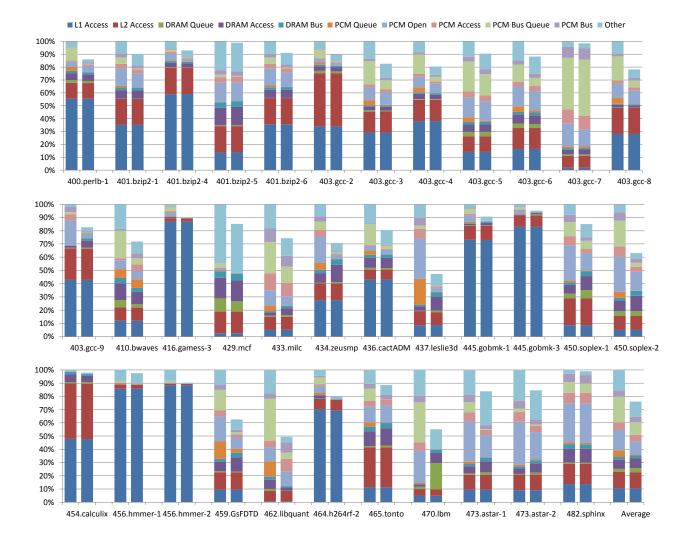

| 4  | Memory components where application reads accumulate time             | 37 |

| 5  | Variables used in the analytic model. X stands for either DRAM or PCM | 39 |

| 6  | List of variables and associated overhead                             | 40 |

| 7  | Architectural parameters                                              | 42 |

| 8  | Architectural parameters                                              | 63 |

| 9  | Architectural parameters                                              | 79 |

| 10 | Architectural parameters                                              | 92 |

## LIST OF FIGURES

| 1  | Average speedup over no-migration for different migration rates                 | 3  |

|----|---------------------------------------------------------------------------------|----|

| 2  | Overview of the proposed system.                                                | 6  |

| 3  | Overview of Hybrid Main Memory Simulator                                        | 22 |

| 4  | Splitting of traces for compression.                                            | 26 |

| 5  | Execution time of HMMSim for different configurations and simulated cores       |    |

|    | counts                                                                          | 27 |

| 6  | Resident memory of HMMSim for different configurations and simulated cores      |    |

|    | counts                                                                          | 29 |

| 7  | Normalized execution time of selected benchmarks without and with (baseline)    |    |

|    | migration cost                                                                  | 32 |

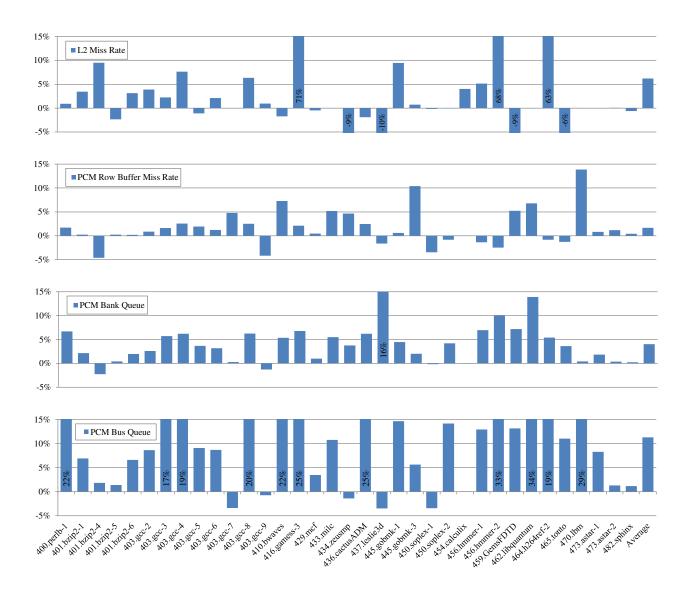

| 8  | MLAA for Offline. For each workload, first bar is Full-Interference and second  |    |

|    | bar is Zero-Interference.                                                       | 43 |

| 9  | Potential L2 access latency reduction that can be obtained by eliminating 4     |    |

|    | different factors that cause overhead                                           | 45 |

| 10 | L2 access latency reduction from using the Offline migration policy relative to |    |

|    | Multi-Queue                                                                     | 47 |

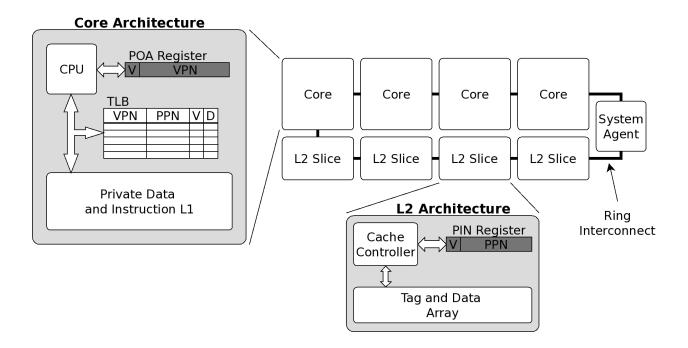

| 11 | Overview of architecture changes for CPM. New components are shown in dark      |    |

|    | gray. Changes to the system agent are shown in Figure 12                        | 57 |

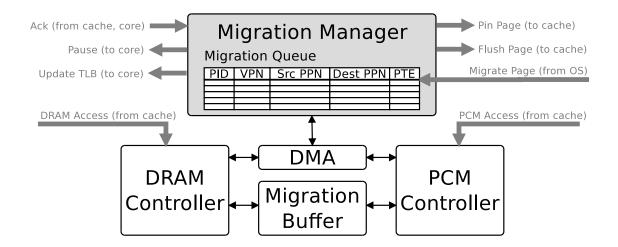

| 12 | The modified system agent, showing new components in gray. Gray arrows          |    |

|    | represent messages from/to the cores, LLC cache slices and OS                   | 58 |

| 13 | Cache organization with support for page pinning.                               | 60 |

| 14 | Steps for hardware for CPM.                                                     | 61 |

| 15 | Single-programmed: Speedup.                                                   | 65 |

|----|-------------------------------------------------------------------------------|----|

| 16 | Single-programmed: Number of cycles waiting. First bar is baseline and second |    |

|    | bar is CPM.                                                                   | 66 |

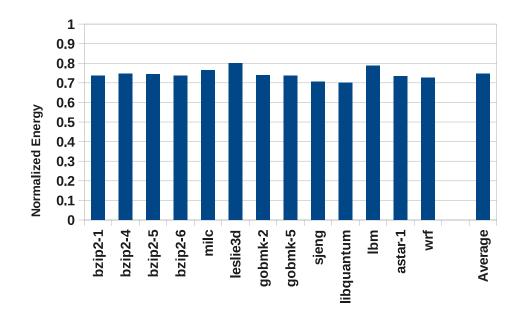

| 17 | Single-programmed: Energy consumption                                         | 67 |

| 18 | Average speedup of CPM with single-programmed workloads for different mi-     |    |

|    | grations costs in cycles.                                                     | 69 |

| 19 | Multi-programmed: Speedup                                                     | 70 |

| 20 | Multi-programmed: Number of cycles waiting.                                   | 71 |

| 21 | Overview of software and hardware components for CMMP                         | 73 |

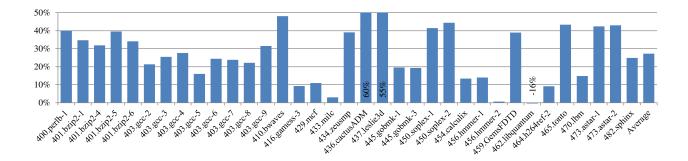

| 22 | Speedup of CMMP, normalized to the baseline                                   | 81 |

| 23 | Average memory access time of CMMP                                            | 82 |

| 24 | Energy of CMMP, normalized to the baseline                                    | 84 |

| 25 | Possible state of pages that use OBM and PD                                   | 86 |

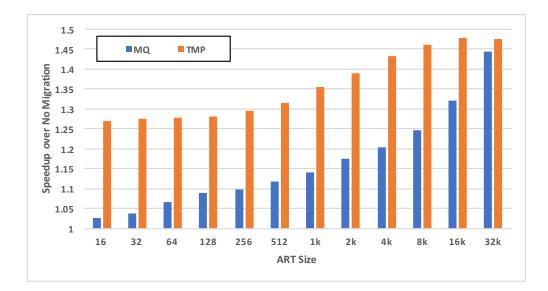

| 26 | Speedup of Multi-Queue and TMP, normalized to No Migration                    | 93 |

| 27 | Speedup of TMP for different ART sizes, normalized to the baseline            | 94 |

| 28 | Speedup of TMP for multi-core workloads, normalized to the baseline           | 95 |

| 29 | Speedup of Multi-Queue and TMP for different ART sizes for multi-core work-   |    |

|    | loads, normalized to No Migration                                             | 96 |

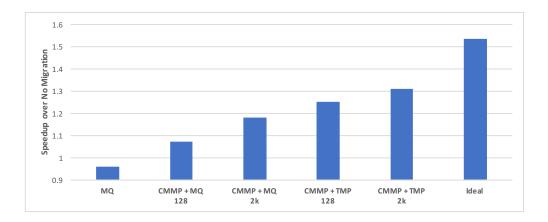

| 30 | Comparison of CMMP with Multi-Queue and TMP and two ART sizes against         |    |

|    | state-of-the-art (Multi-Queue without CMMP) and ideal systems                 | 97 |

## LIST OF ALGORITHMS

| 1  | Offline migration policy                                                  | 36 |

|----|---------------------------------------------------------------------------|----|

| 2  | Sequence of steps performed during conventional page migration            | 52 |

| 3  | Sequence of steps performed during concurrent page migration              | 55 |

| 4  | PCM to DRAM migration (promotion)                                         | 75 |

| 5  | DRAM to PCM migration (demotion)                                          | 76 |

| 6  | Access Redirection                                                        | 78 |

| 7  | Algorithm for updating data structures in TMP when page monitoring infor- |    |

|    | mation is read from the PACT                                              | 89 |

| 8  | Process for updating the CCL list with information read from the ART      | 89 |

| 9  | Steps for selecting a page for completion                                 | 90 |

| 10 | Steps for selecting a page for demotion                                   | 90 |

| 11 | Steps for selecting a page for rollback                                   | 90 |

#### 1.0 INTRODUCTION

A growing number of applications that run in today's data centers have very large memory footprints, often exceeding tens of gigabytes [1, 2]. Due to recent advances in microarchitecture and device manufacturing, modern servers have very high core counts (128 cores or more), enabling the execution of multiple applications in the same machine. To cope with the increasing demand in memory capacity, data centers use servers with huge amounts of memory, often in the terabyte range [2].

Due to its relatively good performance and low cost, DRAM has been the prevailing memory technology used in compute servers during the past 40 years. However, the scalability of DRAM is expected to hit a wall in the near future [3]. This will not only increase the cost of DRAM but also make it more vulnerable to soft errors. In addition, the large memory size of current systems is making the high static power consumption of DRAM impractical, especially since most of DRAM's energy is spent by self-refresh operations while the memory is idle [4].

To deal with these problems, researchers have proposed *hybrid memory*, which combines a small amount of DRAM with a large amount of Phase Change Memory (PCM) [5, 6, 7, 8, 9, 10]. The properties of PCM (high density, slow reads and even slower writes, low static power, low read power, and high write power), make it a good candidate for storing large amounts of data that are not updated frequently. However, since most of the data resides in PCM, the bandwidth and latency of hybrid memory systems is limited.

A viable architecture for combining DRAM and PCM is *software-managed hybrid memory*, where both DRAM and PCM are addressable by the CPU and managed by the operating system (OS) [5, 10, 11, 12, 9]. Apart from exposing a larger physical address space to applications, software-managed hybrid memory allows greater flexibility to manage memory resources because OS policies can be tailored to the needs of application workloads. Importantly, this architecture is the easiest path forward to incorporate persistence in the main memory hierarchy by reserving part of PCM for storage [13, 14, 15].

Nevertheless, the performance of software-managed hybrid memory suffers from several drawbacks, which must be addressed before it can be adopted [16, 17]. First, current commodity systems do not provide hardware to perform page migration efficiently without OS involvement, resulting in frequent interrupts that degrade performance. Second, data is managed at the granularity of pages, which can lead to excessive data movement that steals bandwidth from applications, hurting performance. Third, the OS has low visibility of application access patterns, particularly at the main memory level (below the caches). As a result, the OS cannot react quickly to changes in application behavior, potentially causing poor data migration decisions between DRAM and PCM.

The hypothesis of my thesis is that software-managed hybrid main memory can effectively provide high performance with low hardware cost by using a carefully hardware-software co-designed system that offloads performance-critical tasks to hardware and leaves complex decision-making tasks in software.

#### 1.1 RELEVANCE

In a hybrid memory system, the small DRAM space and the large PCM space are managed by a *migration policy*, which decides whether and when data should be moved between memories. In addition, a migration policy decides what data should be *promoted* to DRAM, and what data should be *demoted* to PCM. Migration policies can be implemented in hardware or in software. An example of a hardware migration policy is found in hardware DRAM caches [8, 6], in which blocks are moved to DRAM on demand. The accessed block is promoted, and the least recently used block is demoted.

In software-managed hybrid memory, the OS initiates the migration of memory pages between DRAM and PCM while applications continue to execute. Pages are not transferred to DRAM on demand. Instead, accesses to pages residing in PCM are serviced directly from

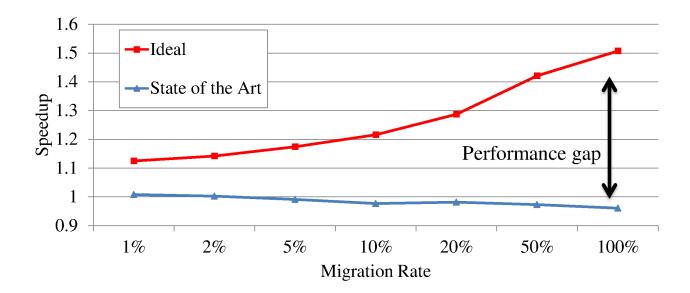

Figure 1: Average speedup over no-migration for different migration rates.

PCM, without moving the page to DRAM. While applications execute, the OS keeps track of memory access patterns and migrates pages in the background. An example of a software migration policy is the Multi-Queue algorithm [9], which ranks pages according to access count, and migrates pages between DRAM and PCM to keep the most frequently accessed pages in DRAM.

Page migration allows the OS to move frequently used data to DRAM and keep less frequently used (colder) data in PCM. This reduces access latency and dynamic power by serving most requests from DRAM. If done correctly, page migration can have a significant effect on performance: Figure 1 compares the state-of-the-art software-managed hybrid memory [9] with an ideal system. The ideal system uses an oracle page migration policy and assumes page migration does not interfere with regular application requests. The graph shows average speedup of both the state-of-the-art and the ideal system relative to a system that does no migration. The no-migration system allocates pages on first touch to DRAM until the DRAM capacity is exhausted. At this point, subsequent pages are allocated to PCM. The x-axis shows *migration rate*, which is the fraction of execution time during which the OS migrates pages. At low rates, the state-of-the-art system performs close to the baseline. At high rates, however, it does worse due to interference between application and migration memory requests. An ideal memory system with no interference and a "good" migration policy can achieve high performance, especially at high migration rates.

#### 1.2 ELEMENTS OF A GOOD SOLUTION

A good solution for software-managed hybrid memory must satisfy a number of requirements. The first requirement is that the time overhead of managing hybrid memory in software should be low. If the overhead is too high, this approach will simply not be able to compete with a hardware approach (DRAM cache) and will therefore not be adopted. Since managing hybrid memory entirely in software is potentially time consuming, a good solution must include some hardware support to accelerate certain operations. Therefore, the system should use hardware for simple, performance-critical operations, and perform more complex ones in software.

The second requirement is flexibility of choice in the migration policy. Each application has a preferred policy that maximizes its performance, and the preferred policy for each application is different. To maximize overall performance, each application should be able to choose its own migration policy. This flexibility also enables the development of migration policies specifically tailored to an application.

The third requirement is that the additional hardware support be as small as possible while still allowing the system to perform well and be flexible enough to be able to use most migration policies. Making only small, simple hardware changes means that hardware manufacturers will be more likely to include them in future processors, increasing the chances of adoption.

#### 1.3 APPROACH OVERVIEW

In this research, I propose a memory management system for hybrid DRAM/PCM architectures. The proposed system uses hardware-software co-design to separate performancecritical tasks from other tasks that can be implemented in software without high overhead. By co-designing software and hardware, my approach provides a flexible substrate for the OS to implement custom policies.

The proposed system manages memory at the software level with small hardware support for some performance-critical operations. Data migration decisions between DRAM and PCM are performed by the OS based on monitoring information collected by hardware. The actual migration of pages is performed by hardware once the OS has selected the source and destination.

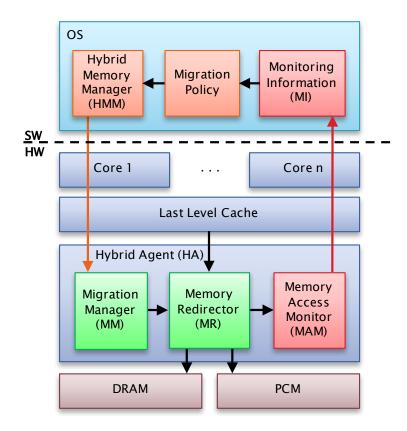

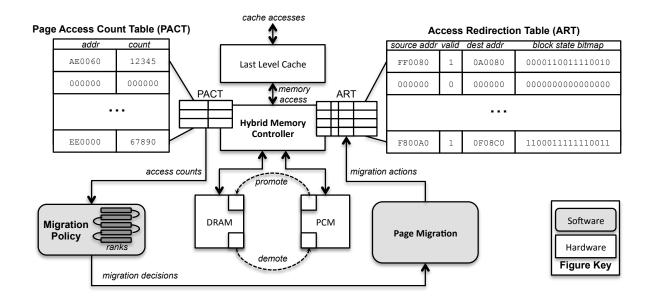

Figure 2 shows an overview of the proposed system. The system has two main new components. The Hybrid Memory Manager (HMM) is a software module that is part of the OS. The Hybrid Agent (HA) is a hardware component that is part of the chip multi-processor.

The HMM is the central component. It is in charge of coordinating all actions of the system, including communication with other modules (software and hardware). The HMM uses one or more migration policies. In general, each application has its own migration policy tailored to its specific memory access patterns.

The migration policy relies on monitoring information. This information is stored in the Monitoring Information (MI) component, and can be accessed directly from software. However, the information is not collected by the OS. Instead, a hardware module, called Memory Access Monitor (MAM), collects this information and passes it to the MI.

The other main new component of the system is the HA, which is composed of the Migration Manager (MM), the Memory Redirector (MR), and MAM. The MR is in charge of deciding where memory requests should be directed to (PCM or DRAM), based on their physical address. The MR is aware of ongoing page migrations, and can redirect memory requests of pages under migration to the correct location. The MR also notifies the MAM of memory requests. The MAM updates its data structures with the new information, which

Figure 2: Overview of the proposed system.

is later stored in the MI for use by the migration policies.

When the HMM decides to migrate one or more pages, it communicates with the MM. The MM is in charge of coordinating all hardware actions necessary for performing page migrations, including copying pages between memories, updating page table and TLB entries and flushing the caches. The MM also notifies the MR of page migrations, so that the MR can update its data structures.

To characterize the performance bottlenecks of hybrid memory and evaluate the proposed architecture, I developed a new simulation infrastructure specifically tailored for softwaremanaged hybrid memory. Although the infrastructure is capable of simulating a wide range of systems, the focus of this thesis is on mobiles devices, such as smartphones and tablets. These devices can benefit greatly from the low energy consumption of PCM-based hybrid memory.

#### 1.4 THESIS CONTRIBUTIONS

This thesis contributes new hardware mechanisms and software algorithms for enabling software management of hybrid main memory. This approach offers an alternative to hardwareonly hybrid memory, such as DRAM caches. This thesis opens up new research opportunities for developing migration policies, which can be tailored to the access patterns of applications. In addition, it provides an evaluation infrastructure that can be easily adapted to new policies.

This thesis makes the following contributions:

- A simulation infrastructure to evaluate software-managed hybrid main memory is developed. This includes components to simulate migration policies, which model the software side of the proposed system. Furthermore, the infrastructure includes a detailed model of caches, memory devices (DRAM and PCM) and specialized hardware for hybrid memory [18].

- A characterization study to determine the most important factors that limit performance in software-managed hybrid memory is presented. This study is the building block that guides the development of the proposed mechanisms of this thesis [17].

- Two hardware mechanisms for supporting page migration in hardware to reduce OS overhead are proposed. The first mechanism prevents applications from pausing when they write to a page currently under migration. The second mechanism extends and generalizes the first one to allow for multiple simultaneous migrations [16].

- A hardware-software co-designed mechanism to reduce the bandwidth consumption of software-managed hybrid memory is proposed. This design corrects the main drawback of multiple simultaneous migration (high migration bandwidth) by preventing unnecessary movement of data [19].

- A hardware-software co-designed mechanism for monitoring memory access patterns is proposed. This mechanism requires a small amount of hardware resources but provides

enough monitoring information to make good migration decisions. The design is flexible enough to accommodate a wide range of migration policies [19].

• A new migration policy designed specifically to be used with the new migration and collection mechanisms is proposed. This policy requires a small amount of processing power in the OS but provides better page placement than the current state of the art.

#### 1.5 THESIS ORGANIZATION

The rest of this thesis is organized as follows. Chapter 2 presents background and related work including PCM, architectural support for PCM and hybrid memory. Chapter 3 introduces the simulator infrastructure developed specifically to address the challenges of evaluating hybrid memory. Chapter 4 presents the characterization study that guides the development of the proposed mechanisms. Chapters 5 and 6 propose two mechanisms for performing migration in hardware, including the proposed scheme for bandwidth reduction and the access monitoring mechanism. Next, Chapter 7 presents the new migration policy. Finally, a summary of this work and future research directions are presented in Chapter 8.

#### 2.0 BACKGROUND AND RELATED WORK

#### 2.1 PHASE CHANGE MEMORY

Phase Change memory (PCM) [20, 21] is a non-volatile memory technology that stores information by changing the physical state or phase of chalcogenide material. PCM works by applying electrical currents of different intensity and duration to a small volume of phasechanging material. These varying currents melt the material and let it cool at different rates, which determine its final phase. When the material cools quickly, ions do not have enough time to form a lattice, and the material ends up in an amorphous phase. Conversely, when the material cools slowly, ions form a crystalline structure.

The resistance of the phase-change material depends on its physical state. When the material is in a crystalline phase, electrons can move more freely within the material because they encounter less resistance from aligned atoms. Hence, the resistance of the material is low. Conversely, when the material's phase is amorphous, electrons move more slowly because of the increased friction caused by randomly placed atoms. When amorphous, the resistance of the material is high.

Changing the phase of chalcogenide material is a complex process that involves carefully controlling the profile of the current that is applied to each cell. Due to this complex process and to the slow cool-down period when changing the state to crystalline, writing to PCM is orders of magnitude slower than writing to DRAM.

Because PCM stores information by changing the configuration of atoms inside the material, the energy required to change the stored value is higher than in DRAM, which maintains information by changing the amount of stored charge. This fact has two important consequences. First, the state of PCM cells persist for longer periods of time. Since there is no

|                       | DRAM      | PCM      |

|-----------------------|-----------|----------|

| Read Latency (ns)     | 13.7      | 60       |

| Write Latency (ns)    | 12.5      | 150      |

| Read Energy (pJ/bit)  | 1.17      | 2.47     |

| Write Energy (pJ/bit) | 0.39      | 16.82    |

| Endurance (writes)    | $10^{15}$ | $10^{8}$ |

Table 1: Comparison of DRAM and PCM Parameters

need to periodically refresh the contents of memory, PCM requires very little energy when idle, and can be used as non-volatile storage. Second, actually changing the state of the material requires more energy than simply moving electric charge. Hence, writing to PCM is more energy-consuming than writing to DRAM.

A major disadvantage of PCM is that its cells lose the ability to change their physical state after they have been written a large number of times. This is caused by detachment of the phase-change material from the electrodes that provide the programming current, and it is generally irreversible. Hence, the endurance of PCM is limited to between  $10^6$  and  $10^9$  write cycles.

In summary, PCM is slower than DRAM, especially when writing. Dynamic energy consumption is also higher than DRAM, also especially when writing. Static energy consumption, on the other hand, is lower in PCM than DRAM. Table 1 shows a comparison of PCM and DRAM, based on values from a recent paper [22].

#### 2.2 ARCHITECTURAL SUPPORT FOR PCM

Due to its characteristics, PCM cannot be used as a direct DRAM replacement without considerable performance, energy and lifetime penalties. Researchers have proposed several mechanisms that provide architectural support for enabling PCM in main memory. The following subsections describe some of these mechanisms. Hybrid main memory, the primary mechanism for supporting PCM, is described in Section 2.3.

#### 2.2.1 Write Reduction

One of the main drawbacks of PCM is that writes are costly in terms of performance, energy consumption and lifetime. Therefore, reducing the number of writes that PCM devices sustain has a direct impact on energy consumption and device lifetime. In addition, reducing the amount of time the memory spends on slow write operations increases the average read time due to higher availability of the device.

Lee *et al.* propose tracking dirty data in the processor caches at the granularity of a word [22]. Upon a LLC write-back, only the dirty words within a cache line are actually written to the PCM device. The main advantage of this technique is that no comparison between new and old data is necessary to determine which bits can be safely ignored during write-backs. However, this is done at the expense of additional on-chip area (3.1% for 4-byte words and 64B-byte cache lines). This technique can improve memory lifetime by up to 8 times compared to keeping track of dirty data at cache line granularity.

Bock *et al.* propose a software technique for identifying dead blocks in the LLC or in a DRAM cache using calls to the memory allocator [23]. A dead block contains data that will not be read before it is written again. Hence, dead blocks can be discarded without affecting the correctness of the program. When a dead block is evicted from the cache, its contents are not written back to the next level of the memory hierarchy (the PCM). This technique reduces the number of writes to PCM and reduces energy consumption.

Ferreira *et al.* propose a technique called Read-Write-Read (RWR) to determine exactly which bytes of a write operation have been modified [6]. RWR works by reading the original contents of PCM before issuing a write operation, and comparing the old and new versions of the data. Only modified data is written to PCM. This technique can indeed reduce the number of writes to PCM. However, this is done at the expense of one additional read before every write. Lifetime savings depend on how much data is modified while it is in the cache hierarchy. If data is heavily modified, the lifetime will be close to that of the baseline system. Energy savings also depend on how much each write benefits from RWR. If the energy spent in reading the data from PCM is not offset by writing fewer data, the net energy savings will be negative.

A similar technique, called Data-Comparison Write (DCW), was proposed by Yang *et al.* [24]. Like RWR, DCW also compares stored data with the new version of the data. The main difference with RWR is that DCW operates at the device level. Hence, the granularity of data comparison can be much smaller (DCW's granularity is the bit). On average, DCW can reduce the number of written bits by half, although the actual value depends on the data being written.

Flip-and-Write builds upon DCW by adding an additional bit to each word of stored data that keeps track of whether the word is stored inverted [25]. When writing new data, the bit-by-bit comparison counts how many bits must be actually changed from their current state. If more than half of the bits need to be changed, the data is stored inverted and the new bit indicating this is set. Flip-and-write guarantees that at most half of the bits in each write are actually changed.

#### 2.2.2 Write Cancellation and Write Pausing

One of the disadvantages of PCM is its slow write latency, which can be between 2 and 4 times slower than the read latency, and 10 times slower than DRAM's write latency. In general, memory write latency is not exposed directly to an application's execution time because the completion of a write is not required by the CPU to continue execution (as is the case for reads). Write buffers can store writes and delay them until the memory becomes idle. Once a write request has been issued, however, subsequent read requests must wait for the write to finish, exposing additional latency to the processor. With slow PCM writes, this additional latency can have a considerable impact on performance.

To address this issue, Qureshi *et al.* propose two techniques that allow reads to preempt ongoing writes, reducing the latency of reads as seen by the CPU [26]. *Write cancellation* simply cancels ongoing writes, allowing reads to start executing earlier. Writes are only canceled when they are less than 80% completed. The original write is scheduled to execute later, when memory resources become available or when write buffer utilization exceeds a predefined threshold.

The disadvantage of write cancellation is that canceled writes waste memory cycles because the write needs to be performed again, and previous work performed on the canceled write is lost. This wastes memory bandwidth because the average write time increases. To avoid this problem, the authors also propose *write pausing*, which allows the memory to remember the progress of preempted writes so that they can be restarted closer to when they were interrupted. This technique takes advantage of PCM's iterative writing process, in which the current state of the device is compared to the desired state [27]. After several cycles of writing and comparing, the desired state is achieved and the process finishes. Write pausing leverages this iterative process to reduce the time wasted due to restarts of writes.

#### 2.2.3 Wear Leveling

Another important disadvantage of PCM is its low write endurance. Current PCM devices can sustain between  $10^5$  and  $10^9$  write cycles [28, 29, 30]. When used in main memory, PCM devices have a lifetime ranging from a few months to several years, depending on the write rate and the memory access patterns of applications. Wear leveling can extend the lifetime of PCM devices by uniformly distributing the writes across all memory locations within a device. This prevents the memory from failing due to repeated writes to a few memory locations, which can happen in a short period of time. Several wear leveling mechanisms have been proposed to address the issue of limited write endurance in PCM.

Zhou *et al.* propose two wear leveling schemes that work at different data granularities [31]. *Row shifting* distributes the writes within a device row by shifting or rotating the contents of the row by a specified amount in increments of one byte. The shifting amount is stored together with the row so that the data can be correctly reconstructed when the row is read. The second mechanism, called *segment swapping*, distributes writes across 1MB segments by introducing an additional level of indirection that maps the address generated by the core to the address actually used in the device. A table is used to keep this maping, as well as metadata about the number of writes to each segment and the last time it was swapped. The wear leveling algorithm periodically swaps hot and cold segments to ensure that each segment has a similar number of writes.

Although wear leveling at the page or 1MB segment granularity does extend the lifetime of PCM devices, the overhead of updating the mapping table on every write and of searching through the table to find swapping candidates can be very high. To address this issue, Ferreira *et al.* propose a similar mapping scheme that chooses the swapping candidates randomly [32]. This avoids the overhead of updating the access counts and of searching the hottest and coldest segments at the expense of reduced lifetime. However, for current devices and applications, it is enough to guarantee several years of operation.

Start-gap wear leveling uses algebraic mapping between logical and physical address to avoid the mapping table, which consumes area and energy, and adds latency to each memory request [33].

#### 2.3 HYBRID MAIN MEMORY

The problem of using PCM in main memory has been widely studied in recent years. Because of its slow performance, high energy consumption and low endurance, PCM has not been considered as a direct DRAM replacement. Instead, researchers have proposed using it together with DRAM in a hybrid memory architecture, where a small DRAM is combined with a large PCM.

There are traditionally two approaches for architecting a hybrid memory system. In hardware-managed hybrid memory, PCM is invisible to software, and hardware is entirely responsible for managing data and providing the correct data to applications. In softwaremanaged hybrid memory, the OS is aware of both DRAM and PCM memory spaces, and it manages data by allocating memory pages and initiating their migration. A discussion of these two approaches follows in the next sections. A third approach which combines both hardware and software mechanisms, is the focus of my thesis.

#### 2.3.1 Hardware-Managed Hybrid Memory

In hardware-managed hybrid memory, the OS has a homogeneous view of memory and is not aware that the physical memory is composed of DRAM and PCM. Hardware decides where a particular block of data is placed, and keeps track of where each block is using hardware structures. When a memory access misses in the LLC, the hardware consults this hardware structure to retrieve the physical address of the requested block, and forwards the request to the appropriate location.

#### 2.3.2 DRAM Caches

The simplest organization of a hardware hybrid memory is the DRAM cache [8, 6]. In this architecture, hybrid memory is organized as a non-inclusive set-associative hardware cache that is accessed after the LLC. Cached blocks are stored in DRAM, and the rest are in PCM. A tag array keeps track of which blocks are currently in DRAM. Upon an access, the tag array is first queried to determine whether the requested address is cached. If it is, the address of the block is constructed based on the original address and on the number of the way that hit in the cache, and the requested is forwarded to the correct DRAM address. If it is not, the request is forwarded to the original address in PCM.

In hardware DRAM caches, the size of the block used in the cache has several important consequences on performance and other design considerations. First, the tag array area depends on the block size. If the block size is too small and the DRAM size too large, the area required to store all tags can become impractically large. For example, a 1GB DRAM cache requires a 96MB tag array when using 64-byte blocks [36]. Second, the block size has a big impact on PCM bandwidth utilization. When using large blocks (for example, 4KB), the amount of data that is transferred between DRAM and PCM while servicing requests and writing dirty data back can saturate the available bandwidth of PCM. This causes the memory system to slow down considerably, hurting performance. Third, exploiting spatial locality is less effective when blocks are small, as less data is pre-fetched into DRAM on a miss.

To deal with the area overhead of small blocks, researchers have proposed various meth-

ods. Sub-blocking uses large blocks but keeps individual present and dirty bits for each sub-block [6]. Upon a miss, only the requested sub-block is brought into DRAM. Since there are less blocks to keep track of, the required tag array area is smaller. However, sub-blocking is not as efficient as using smaller blocks in terms of capacity management because part of the DRAM space and the tag array capacity is wasted. Sub-blocking also reduces bandwidth utilization because not all parts of a block are brought into DRAM.

Another technique to reduce the area overhead of small blocks is to keep tags in DRAM instead of in the tag array. Upon a memory request, the DRAM is accessed twice: once to read the tag array and once to get the actual data. Since accessing DRAM is considerably slower than on-chip SRAM tag arrays, the latency overhead of this architecture is usually too high to be practical. Compound scheduling partially solves this problem by co-locating the tags and the corresponding data in the same DRAM row [36]. When accessing memory, the tag for that particular set is retrieved from the DRAM row, and the row is left open. Upon a hit, the data is read from the still-open row buffer.

Other techniques have been proposed to deal with the overhead of keeping tags in DRAM. A miss map can be used in conjunction with compound scheduling to reduce the latency of misses and bandwidth utilization [36]. An on-chip SRAM miss map keeps track of which blocks may be in DRAM but does not keep perfect information, which reduces area requirements. The miss map does not know whether a block is definitely in DRAM, but does know whether one is definitely not there. Therefore, miss maps can reduce the miss penalty and bandwidth consumption of DRAM caches that keep tags in DRAM.

Another technique for reducing the latency overhead of DRAM tags is to use a directmapped cache [37]. When using caches with large associativities, the number of blocks that need to be read from DRAM to perform the tag checks is high. For example, 3 blocks need to be read to check the tag array of a 29-way set-associative cache with 64-byte blocks [37]. Using a direct-mapped cache means fewer blocks need to be accessed and transferred. This reduces the latency of both hits and misses at the expense of a higher miss rate. With large cache sizes, which have low miss rates, the average access latency is reduced.

Finally, the footprint cache allocates data at the granularity of pages, but fetches only the cache blocks that will actually be used by the CPU while the page is in the DRAM cache [38]. To determine which blocks should be fetched, this scheme keeps track of blocks while the page is in the cache. Upon eviction, this information is stored in a predetermined location in memory. When the page is brought back to the cache again, only those blocks that were previously touched are transferred to the cache.

#### 2.3.3 Smart Memory Controllers

Ramos *et al.* describe a sophisticated memory controller that ranks pages based on the frequency and recency of memory accesses using the Multi-Queue algorithm [9]. The hardware is able to perform migrations based on this information without involving the OS. Hardware structures keep track of which physical addresses have had their data moved to a new location. When these hardware structures are full, the OS is notified of page migrations, and it updates its own data structures accordingly.

Although the OS is aware of both DRAM and PCM address spaces, this scheme is still categorized as a hardware hybrid memory because the memory controller performs all of the operations required for migrating and ranking pages. The OS does not implement migration policies or performs migrations. It is simply aware that the hardware can change the location of data depending on memory access patterns.

#### 2.3.4 Software-Managed Hybrid Main Memory

In software-managed hybrid memory, DRAM and PCM have non-overlapping physical address ranges which are directly accessible from the CPU (via virtual-to-physical mappings). The OS is aware of this separation and must choose which type of memory to assign to each virtual page that it allocates. Hardware determines the type and location of a memory request solely by its physical address and the address ranges of DRAM and PCM, without consulting hardware structures.

The OS can change the type of a virtual page by migrating it to a new memory location. To do this, the OS must pause the application (or execute until the virtual page is written to, then pause), copy the physical page to the new location, flush the page out of all caches and update the page table and TLB entries of the virtual page. This is generally a costly operation, although its overhead can greatly be reduced by using specialized hardware support for migration.

From the perspective of the OS, managing hybrid memory consists of deciding what data should be in DRAM and what data in PCM. For most workloads, the available DRAM space is not enough to hold all data. Therefore, some data must be kept in DRAM and some in PCM. Ideally, the OS should try to keep the most frequently used data in DRAM. However, this is not easily accomplished, for several reasons. First, the set of most frequently used data changes over time as applications enter other phases of execution. Second, actually determining the set of most frequently used pages is difficult because the OS cannot record and keep track of every memory access. Third, page migration is costly in terms of latency to copy the page and how it affects the latency of other memory requests. Therefore, the OS can not blindly migrate pages constantly because this can affect other requests and can waste precious memory bandwidth.

A migration policy is a set of rules or an algorithm that determines what pages are migrated between DRAM and PCM and when they are migrated. A migration policy must constantly determine when to migrate data, what data to move from DRAM to PCM (demotion or eviction), and what data to move from PCM to DRAM (promotion). This is similar to the decisions made by cache replacement policies or paging algorithms, which must decide on what cache block or page to evict from the cache or from memory. A migration policy is different in that, in addition to selecting an eviction candidate, it must also decide whether to migrate a page at all and select a promotion candidate. In a cache replacement policy or paging algorithm the decision of when to migrate is done tacitly (migrate when there is a cache miss), as well as the decision of what to promote (promote the page that missed in the cache).

A major advantage of software-managed hybrid memory is the flexibility in choosing a migration policy. Since it is implemented in software, a new migration policy can be easily deployed and tuned for a particular application. Researchers have proposed a number of policies, each aimed at solving a particular problem of using PCM in main memory [10, 5].

#### 3.0 SIMULATOR INFRASTRUCTURE

While researching new hardware mechanisms and migration policies for software-managed hybrid memory, it is important to have the appropriate tool for the job. One of the main challenges of researching software-managed hybrid memory is the need to model different parts of a computer's hardware and software hierarchy. For instance, a simulator must be capable of modeling details about a computer's processor, cache hierarchy and memory system, and at the same time be able to simulate the migration policies that would run as part of the OS in a real system. Another challenge is the trade-off between accuracy and performance of the simulation. When prototyping new migration policies, it's advantageous to be able to run simulations and obtain results quickly. However, abstracting away too many details in the simulator can lead to inaccurate results. Another challenge of simulating software-manage hybrid memory is the tool's ease of use. When researching new policies, it's important to be able to implement them easily without major changes to the simulator or the simulated OS. In addition, it must be possible to implement different types of policies without being limited to a particular family of policies.

To aid in the design and evaluation of new hardware mechanisms and migration policies for software-managed hybrid memory, I created HMMSim, a trace-driven simulator for hardware-software co-design of hybrid main memory [18]. HMMSim is capable of simulating DRAM and PCM in several hybrid memory organizations, including single-memory systems, DRAM cache, and software-managed hybrid memory. HMMSim simulates the entire memory hierarchy, including the load store units at the CPUs, caches and their queues, main memory controllers, queues, banks and buses, as well as interactions caused by OS page management in the hierarchy (e.g., flushing of pages from the caches after migration). HMMSim can also emulate the behavior of the OS related to page migration as well as different migration policies.

There are many memory simulators available, each with its own degree of accuracy, performance, flexibility and ease of use. However, none of them is well suited for modeling both hardware and software in a flexible and extensible way. Table 2 shows a comparison of features of three of the most popular memory simulators. Both DRAMSim2 and USIMM provide detailed DRAM models but do not support PCM. NVMain supports PCM and hybrid memory. However, using it to simulate a software-managed system, including the complete hierarchy and OS emulation, requires using and potentially modifying another simulator such as gem5 [43]. One of the contributions of HMMSim is that it provides this capability in a single tool that abstracts away the details of the OS, allowing for easy changes to migration policies.

This chapter describes the architecture of HMMSim and details about some of the new techniques used in the simulator. It describes the Application Programming Interface (API) that HMMSim provides for extending functionality to model new mechanisms. Lastly, this chapter reports figures about the performance of HMMSim and show that it is fast and scalable.

The next section provides an overview of the HMMSim software architecture, and describes the design of the simulator and implementation choices.

#### 3.1 OVERVIEW

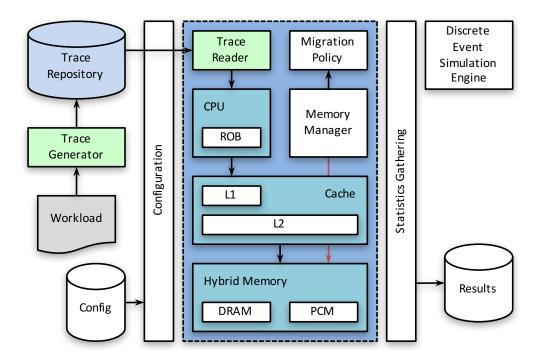

Figure 3 shows the architecture of the simulator. Traces are gathered with Pin [47] and stored in a high compression format. The configuration of the simulated system is read from a file that specifies the value of each parameter. There are over 100 configurable parameters in HMMSim, most of which can be easily set from processor and memory specifications. The simulator includes several components that model the CPUs, caches, DRAM and PCM memory, OS memory management and migration policies. Each component can define *statistics*, which are registered with a centralized gathering component that writes the value of each statistic at the end of simulation. The discrete event simulation engine allows any object

| Feature   | DRAMSim2<br>[44] | USIMM<br>[45] | NVMain<br>[46] | HMMSim |

|-----------|------------------|---------------|----------------|--------|

| DRAM      | Yes              | Yes           | Yes            | Yes    |

| PCM       | No               | No            | Yes            | Yes    |

| Hybrid    | No               | No            | Yes            | Yes    |

| Memory    |                  |               |                |        |

| Software- | No               | No            | No             | Yes    |

| Managed   |                  |               |                |        |

| Hybrid    |                  |               |                |        |

| memory    |                  |               |                |        |

| Complete  | No               | No            | No             | Yes    |

| Hierarchy |                  |               |                |        |

| OS Emula- | No               | No            | No             | Yes    |

| tion      |                  |               |                |        |

Table 2: Comparison of some existing memory simulators

to schedule an event in the future and receive a callback when the simulation reaches the specified cycle.

#### 3.2 MEMORY HIERARCHY

The memory hierarchy is composed of three main components: CPUs, caches and memory. The CPU reads entries from the trace reader and recreates the instructions executed during trace collection. Each instruction consists of an instruction memory access and zero or more data memory accesses. The CPU first sends the instruction memory access to the level 1 instruction cache (I-L1) and waits for a response. Once the instruction access comes back, the CPU sends the data requests to the level 1 data cache (D-L1). The CPU tracks in-flight instructions with a data structure similar to a reorder buffer (ROB) that only tracks memory operations. The CPU retires instructions in order after all data reads have completed. Multicore systems are modeled by creating multiple CPU objects, each connected to its own trace reader.

The simulator models the cache hierarchy by connecting several cache objects to form a

Figure 3: Overview of Hybrid Main Memory Simulator

multi-level cache that can be configured with any number of private or shared levels. Cache objects receive requests from the CPUs or from previous levels in the hierarchy. On a cache hit, the requested data is sent back to the previous level. On a miss, the cache forwards the request to the next level (another cache level or memory). Each cache has a queue that limits the number of requests being serviced at this or lower levels. If a queue is full, requests from previous levels are stalled until a slot becomes available.

HMMSim simulates memory through a set of configurable objects that can model either DRAM or PCM accessible through a DDR interface. The model includes multiple banks, row buffers, per-bank or global queues, a bus and a scheduler, as well as support for different address mappings and row buffer policies. HMMSim also provides a hybrid memory controller that redirects requests to either DRAM or PCM based on physical address, migrates pages and collects monitoring information.

The flow of simulation starts at the CPUs and proceeds down the hierarchy through the caches and to memory. Each component of the hierarchy that receives a request must either

return a response to the previous level or forward the request to the next level. Components model internal delays (such as tag access latency or bank operations) by scheduling events with the simulation engine. When a request is satisfied, the response is sent to the CPU by calling back each component in the hierarchy that forwarded the original request until the response reaches the CPU.

#### 3.3 MEMORY MANAGER

The purpose of the memory manager is to translate a virtual address (collected in the trace) to a physical address that is used by the memory hierarchy. The memory manager follows an *allocation policy* for assigning virtual pages to DRAM or PCM. HMMSim supports several allocation policies, including round robin and random.

In software-managed hybrid memory, the memory manager must also perform page migration. The manager orchestrates all the necessary actions related to page migration, including changing address translation maps, copying the data, flushing the caches and preventing applications from accessing pages under migration. A *migration policy* that is invoked by the memory manager decides whether to migrate pages and what pages to migrate. A policy uses monitoring information retrieved from hardware to make migration decisions, as well as other information available to the emulated OS, such as page type information and offline access counts. HMMSim offers several migration policies, including Multi-Queue and Oracle, and allows for easy creation of new policies.

#### 3.4 HMMSIM API

HMMSim provides a C++ API to extend the functionality of the simulator. Table 3 lists the main components, interfaces and the methods offered. The API has a method for scheduling an event that triggers a callback after the specified amount of cycles. All objects that schedule events have a reference to a singleton Engine object and must implement the IEventHandler

interface. I provide methods for registering and resetting statistics, and for creating counters that trigger interrupts after they reach a threshold (e.g., for counting executed instructions). Memory hierarchy components must implement the IMemory and/or the IMemoryCallback interface so that they can be connected with other components. In addition, the caches implement the IFlushable interface and objects that issue flush requests (such as caches and the hybrid memory manager) must implement the IFlushCallback interface to be notified when the flush completes. Lastly, HMMSim has an interface for different memory managers (single memory, hybrid) and arbitrary migration policies.

#### 3.5 TRACE COMPRESSION

Since HMMSim simulates memory accesses as they traverse the entire memory hierarchy, traces must collect memory accesses before the caches. Storing traces of a few seconds of native execution requires significant storage capacity, even when traces are compressed.

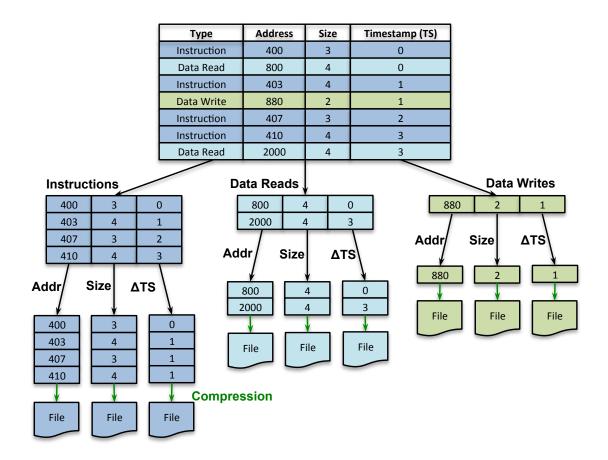

To solve this problem, I created a special trace format that splits the contents of the original traces into various sub-traces and compresses them individually. This results in a higher compression ratio because entries within each sub-trace are similar. Figure 4 shows the trace compression format. Each entry in the original trace is encoded in binary (to achieve higher compression) and contains the type, address size and timestamp (sequence number) of the memory access. The trace is first split into 3 sub-traces according to the entry type. Note that the entry type no longer needs to be stored: it is implicit in the name of each sub-trace. Each sub-trace is further divided into 3 sub-traces, each containing either the address, size or timestamp. The timestamp is delta encoded (the value is the difference between this and the previous entry) to reduce the number of possible values to store, increasing the compression ratio.

HMMSim has several command line tools for manipulating traces. A text converter can be used to output the trace in text format for analysis. The converter can also be used to convert a trace stored in another format into HMMSim's own format. In addition, there are tools for analyzing the contents of the trace directly, without converting to text first. These

| API Component     | API Component De-                                                                          | API Meth-             | Notes                                                                 |

|-------------------|--------------------------------------------------------------------------------------------|-----------------------|-----------------------------------------------------------------------|

|                   | scription                                                                                  | ods                   |                                                                       |

| Engine            | Discrete event simulation engine                                                           | addEvent              | Add event                                                             |

| IEventHandler     | Callback for Engine event                                                                  | process               | Process event                                                         |

| ITraceReader      | Interface for trace readers                                                                | readEntry             | Read next entry in trace                                              |

|                   |                                                                                            | insert                | Register statistic                                                    |

| StatContainer     | Statistics container                                                                       | reset                 | Reset value of statistics                                             |

|                   |                                                                                            | print                 | Print all statistics                                                  |

|                   | Counter that triggers                                                                      | setHandler            | Sets interrupt handler                                                |

| Counter           | interrupts when threshold                                                                  | add                   | Adds a value to the counter                                           |

|                   | is reached                                                                                 | reset                 | Resets the counter                                                    |

| IInterruptHandler | Callback for counter inter-                                                                | process               | Called when interrupt hap-                                            |

|                   | rupt                                                                                       |                       | pens                                                                  |

| IMemory           | Interface for components<br>that receive memory re-<br>quests (e.g., caches and<br>memory) | access                | Issue memory request                                                  |

| IMemoryCallback   | Interface for components<br>that issue memory<br>requests (e.g., CPU and                   | accessDone<br>unstall | Called when memory re-<br>quest completes<br>Called when component is |

|                   | caches)                                                                                    | unstan                | no longer stalling                                                    |

| IFlushable        | Interface for caches that are flushable                                                    | flush                 | Issue cache flush request                                             |

| IFlushCallback    | Callback for flush requests                                                                | flushDone             | Called when cache flush completes                                     |

| IMemoryManager    | Interface for memory<br>managers (single, hybrid)                                          | access                | Translate virtual to physical address                                 |

|                   |                                                                                            | allocate              | Allocate physical page to<br>virtual address                          |

| IMigrationPolicy  | Interface for migration                                                                    | allocate              | Decide where to allocate page                                         |

| 0                 | policies                                                                                   | migrate               | Decide what page to mi-<br>grate                                      |

|                   |                                                                                            | monitor               | Called when memory is accessed                                        |

Table 3: Main API components and their methods currently provided by HMMSim

include counting number of accesses of each type, and counting the number of unique caches blocks or pages accessed.

Figure 4: Splitting of traces for compression.

#### 3.6 PERFORMANCE

This sections evaluates the performance and resource requirements of HMMSim. For all experiments, I ran HMMSim on a lightly loaded machine with a 2.8 GHz Intel Xeon processor, 25MB of LLC and 128GB of main memory. I measure execution time as reported by the *time* utility (wall clock time) and memory resident size as reported by *top*. I use million of instructions per second (MIPS) as our figure of merit for simulation performance.

I simulate three memory configurations: DRAM-only, PCM-only and software-managed hybrid memory. Each configuration runs one SPEC CPU2006 benchmark at a time. Each benchmark is run for one billion instructions. I report the average over all benchmarks

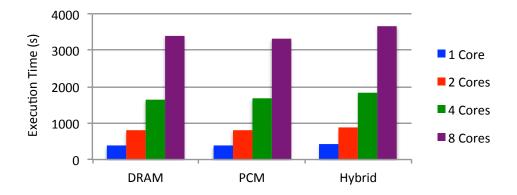

Figure 5: Execution time of HMMSim for different configurations and simulated cores counts.

because the variation among different workloads is small. I simulate systems with four core counts to show that execution time scales linearly with the number of simulated events.

### 3.6.1 Execution Time

Figure 5 shows the average execution time of HMMSim for 1, 2, 4 and 8 simulated cores. As expected, each doubling of the cores results in twice as many instructions being simulated. The execution time, however, increases by a little over 2 times. This is due to an increase in the LLC miss rate of the simulated system, which results in more events being simulated. However, the effect is small: on average there is less than 6% slowdown in MIPS for each doubling of the cores.

In general, the performance of HMMSim lies between 2.1 and 2.6 MIPS. This is approximately the same performance as a full system simulator, such as Simics, running a fast functional model without caches and memory. I believe this is an adequate speed for testing and experimenting with new ideas without having to spend considerable resources modifying complex tools.

#### 3.6.2 Memory Usage

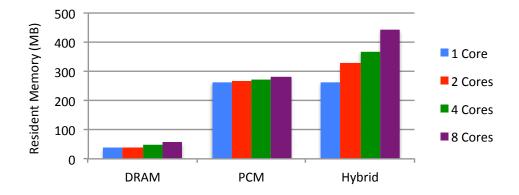

Figure 6 shows the resident memory size of HMMSim for different simulated core counts. For a DRAM-only system, memory usage varies from 38MB to 57MB as core count increases; for PCM-only, memory usage is between 262MB and 282MB, and for hybrid it varies from 262MB to 443MB.

Memory usage does not change after initialization and remains stable during the entire execution. The amount of memory used is linearly correlated with core count. This increase is due to some objects within the simulator being replicated when more cores are simulated, such as private caches, CPUs and traces readers. The difference in resident memory size between the three memory configurations is due to the particular organization of DRAM and PCM that is being simulated. PCM is configured to have more banks of smaller size than DRAM, requiring more memory. The hybrid configuration has the highest resident size because it contains both types of memory and needs other data structures to manage page migration.

The memory usage of HMMSim is relatively low and scales well with core count. The memory requirements are well within the capacity of current servers. HMMSim can simulate memory organizations with large number of components (PCM has 128 banks in this example).

### 3.6.3 Trace Compression

To show that the storage requirements of HMMSim can be handled by current infrastructure using typical storage capacity, I measured the size of SPEC CPU2006 memory traces stored in our high compression trace format. Each trace contains 1 billion instructions and a variable number of data accesses which depend on the characteristics of the workload. Typically, for each instruction there are between 0.2 and 0.7 data accesses. Traces are collected after a 5 billion instructions of the benchmark's execution have completed to avoid tracing the warm-up phase.

Trace sizes vary from 385MB to 1.45GB, with an average of 838MB. The difference in sizes is due to variation in data accesses per instruction and compression ratio of individual

Figure 6: Resident memory of HMMSim for different configurations and simulated cores counts.

sub-traces. In the worst case, storing traces containing 200 billion instructions, which is more that enough to evaluate the performance of current benchmark suites, would take at most 300GB. The overall compression ratios of the traces are between 21 and 74, with an average of 41. Storing 200 billion instructions without compression would take at least 5TB of storage.

## 3.7 SUMMARY

This chapter presented HMMSim, a trace-driven simulator for software-hardware co-design of hybrid main memory. HMMSim models the entire hybrid memory system, including the processor, caches, DRAM and PCM, and migration policies that run in the OS. HMMSim provides an easy-to-use API for extending its functionality. HMMSim uses a novel trace compression scheme that significantly reduces the amount of storage required for traces.

## 4.0 CHARACTERIZATION OF OVERHEAD

As shown in Figure 1 in Chapter 1, there is great potential for achieving high performance in software-managed hybrid main memory by reducing interference and using good migration policies. However, before setting out to design hardware for reducing interference or new migration policies, it's imperative to first analyze and understand why current systems experience high overhead due to page migration [17].

## 4.1 OVERVIEW

Current commodity memory systems do not provide hardware support for page migration. In these systems, page migration is performed in software by the OS, which can have a detrimental impact on performance due the long duration of migrations. This long duration is caused by the slow write performance of PCM, which results in application pauses during page migration. Section 4.2 analyzes the potential impact of reducing the duration of migrations.

In addition to the impact of pauses due to long migrations, interference in the memory system due to data migration between DRAM and PCM affects the performance of softwaremanaged hybrid memory. In Sections 4.3 to 4.5, I present analysis and simulation techniques to investigate the nature of this performance gap and understand how to make softwaremanage hybrid memory perform better. I characterize the overhead of page migration and study the delays that applications experience in the memory hierarchy. I identify the factors that cause the highest overhead.

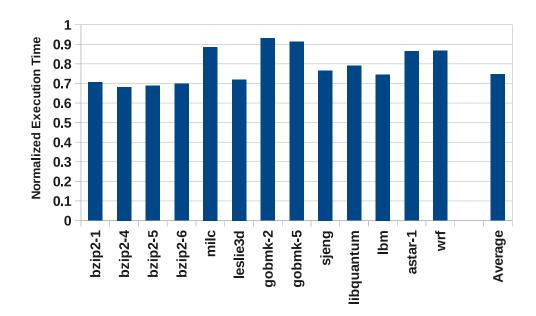

## 4.2 PAGE MIGRATION LATENCY

To quantify the cost of pausing during page migration, I conducted experiments to measure the potential performance improvement that eliminating migration latency can bring. The cost of migration clearly depends on many parameters, including size of the DRAM and page migration policy; these results are illustrative of the problem. I measure the execution time of several SPEC CPU2006 benchmarks, as a proxy for general-purpose applications in smartphones and tablets. I compare total execution time when the latency of copying a page is *zero* and compare it to the total execution time when copy latency realistically accounts for memory subsystem parameters, which I briefly describe next.

To mask as much write latency as practical, I provision the memory system with significant parallelism. I use an 8-bank memory with 4 KB pages and 64-byte cache blocks. PCM reads take 125 cycles and PCM writes take 1K cycles, which is equivalent to Qureshi et al. [26] for a 64-byte cache block. With this organization, a DRAM to PCM migration takes 8K cycles with a page striped across 8 banks (there are 8 writes per memory bank for each migration). I use the Multi-Queue page migration selection policy [9].