# Monitor-Based In-Field Wearout Mitigation for CMOS RF Integrated Circuits

by

Doo Hwang Chang

A Dissertation Presented in Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy

Approved November 2017 by the Graduate Supervisory Committee:

Sule Ozev, Chair Bertan Bakkaloglu Jennifer Kitchen Umit Ogras

ARIZONA STATE UNIVERSITY

December 2017

#### **ABSTRACT**

Performance failure due to aging is an increasing concern for RF circuits. While most aging studies are focused on the concept of mean-time-to-failure, for analog circuits, aging results in continuous degradation in performance before it causes catastrophic failures. In this regard, the lifetime of RF/analog circuits, which is defined as the point where at least one specification fails, is not just determined by aging at the device level, but also by the slack in the specifications, process variations, and the stress conditions on the devices. In this dissertation, firstly, a methodology for analyzing the performance degradation of RF circuits caused by aging mechanisms in MOSFET devices at design-time (pre-silicon) is presented. An algorithm to determine reliability hotspots in the circuit is proposed and design-time optimization methods to enhance the lifetime by making the most likely to fail circuit components more reliable is performed. RF circuits are used as test cases to demonstrate that the lifetime can be enhanced using the proposed design-time technique with low area and no performance impact. Secondly, in-field monitoring and recovering technique for the performance of aged RF circuits is discussed. The proposed in-field technique is based on two phases: During the design time, degradation profiles of the aged circuit are obtained through simulations. From these profiles, hotspot identification of aged RF circuits are conducted and the circuit variable that is easy to measure but highly correlated to the performance of the primary circuit is determined for a monitoring purpose. After deployment, an on-chip DC monitor is periodically activated and its results are used to monitor, and if necessary, recover the circuit performances degraded by aging mechanisms. It is also necessary to co-design the monitoring and recovery mechanism along with the primary circuit for minimal

performance impact. A low noise amplifier (LNA) and LC-tank oscillators are fabricated for case studies to demonstrate that the lifetime can be enhanced using the proposed monitoring and recovery techniques in the field. Experimental results with fabricated LNA/oscillator chips show the performance degradation from the accelerated stress conditions and this loss can be recovered by the proposed mitigation scheme.

Dedicated to my beloved parents and family

#### **ACKNOWLEDGMENTS**

First of all, I would like to express my appreciation to God who has always guided the way for me.

During my Ph.D years, I have received support and encouragement from a great number of individuals without whom this dissertation might not have been written and to whom I am greatly indebted.

I would like to thank Dr. Sule Ozev for allowing me to have such a great opportunity as a Ph.D student. Because of her valuable advice and kind encouragement, I have greatly enjoyed my Ph.D years and earned valuable research and life experiences. There is no word to express my deepest gratitude to my advisor, Dr. Sule Ozev.

I would also like to give my sincere appreciation to Dr. Jennifer Kitchen, who has shown his great support and guidance which have been valuable resources for my research.

I would also express my gratitude to Dr. Bertan Bakkaloglu and Dr. Umit Ogras for accepting to be my committee members.

I would like to show my great appreciation to Rizwan Ahmed at Intel Corporations and Laurenz Van Der Meer at NXP Semiconductor for offering me summer internships and for their valuable comments and support.

In addition, I would really appreciate all the members in RF Design & Test Group at ASU.

Lastly, I would like to give my best thanks to my beloved parents, my parents-inlaw in South Korea showing their unconditional love and support throughout my life. I sincerely would like to express my deepest gratitude to my wife, Soyoun Kim who have always loved, sacrificed, and supported me. I also thank to my daughter and son – Ariana Gion and Jake Jiho.

## TABLE OF CONTENTS

| Page                                                                |

|---------------------------------------------------------------------|

| LIST OF TABLES ix                                                   |

| LIST OF FIGURESx                                                    |

| CHAPTER                                                             |

| 1 INTRODUCTION                                                      |

| 1.1. Background                                                     |

| 1.2. Reliability Models for CMOS Transistors and Analog/RF Circuits |

| 1.2.1. Hot Carrier Injection (HCI)                                  |

| 1.2.2. Negative Bias Temperature Instability (NBTI)                 |

| 1.2.3. Electromigration (EM)                                        |

| 1.2.4. Process Variation                                            |

| 1.3. Reliability Simulation at Circuit Level                        |

| 1.4. Outline of Dissertation12                                      |

| 2 DESIGN-TIME RELIABILITY ENHANCEMENT USING HOTSPOT                 |

| IDENTIFICATION FOR RF CIRCUITS                                      |

| 2.1. Simulation Framework for Aging Mechanisms                      |

| 2.2. Design-Time Optimization Methodology                           |

| 2.3. Case Studies                                                   |

| 2.3.1. Low Noise Amplifier with HCI and EM Analysis                 |

| 2.3.2. CMOS LC Oscillator with HCI and NBTI Analysis                |

| 2.4. Hotspot Identification                                         |

| CHAPTER                                                                 | Page |

|-------------------------------------------------------------------------|------|

| 2.5. Design-Time Optimization in RF Circuits                            | 28   |

| 2.6. Conclusion                                                         | 32   |

| 3 MONITOR-BASE IN-FIELD WEAROUT MITIGATION FOR CMOS LC                  |      |

| OSCILLATOR                                                              | 33   |

| 3.1. In-field Detection and Recovery Scheme                             | 33   |

| 3.1.1. Hotspot Identification                                           | 35   |

| 3.1.2. Monitoring Scheme                                                | 36   |

| 3.1.3. Reconfiguration Scheme                                           | 36   |

| 3.2. Case Study of PMOS and NMOS Oscillator                             | 37   |

| 3.2.1. Reliability Analysis and Hotspot Identification of LC Oscillator | 38   |

| 3.2.1.1. Reliability Analysis of Cross-coupled Transistors of           |      |

| LC Oscillator                                                           | 39   |

| 3.2.1.2. Reliability Analysis of Tail Transistor of LC Oscillator       | 41   |

| 3.2.1.3. Hotspot Identification of LC Oscillator                        | 44   |

| 3.2.2. Performance Monitoring                                           | 46   |

| 3.2.3. Reconfiguration Hardware                                         | 48   |

| 3.2.4. Lifetime Enhancement                                             | 50   |

| 3.2.5. Area Impact                                                      | 54   |

| 3.3. Experimental Results of Class-C Oscillator                         | 55   |

| 3.4. Conclusion                                                         | 59   |

| 4 IN-FIELD RECOVERY OF RF CIRCUITS FROM WEAROUT BASED                   |      |

| PERFORMANCE DEGRADATION                                                 | 61   |

| CHAPTER                             | Page                                         |

|-------------------------------------|----------------------------------------------|

| 4.1. Reliability Analysis and Hotsp | oot Identification of Low Noise Amplifier 61 |

| 4.1.1. Reliability Analysis of Lov  | w Noise Amplifier 62                         |

| 4.1.2. Hotspot Identification of L  | ow Noise Amplifier 64                        |

| 4.2. In-field Lifetime Enhancement  | Method                                       |

| 4.2.1. DC Monitor for In-field M    | onitoring69                                  |

| 4.2.2. Low-cost ADC and Bias T      | uning Architecture for In-field Recovery 71  |

| 4.3. LNA Case Study                 |                                              |

| 4.3.1. In-field Monitoring          | 74                                           |

| 4.3.2. In-field Recovery            | 80                                           |

| 4.4. Experimental Results           |                                              |

| 4.5. Conclusion                     | 87                                           |

| 5 SUMMARY AND CONCLUSIO             | N                                            |

| REFERENCES                          | 90                                           |

# LIST OF TABLES

| Table |                                                        | Page |

|-------|--------------------------------------------------------|------|

| 1.1.  | Summary of HCI Aging Model                             | 7    |

| 2.1.  | Comparison of Circuit Specifications for Aging Effects | 32   |

| 3.1.  | Summary of Chip Measurements                           | 57   |

| 4.1.  | Specifications of Low Noise Amplifier                  | 74   |

| 4.2.  | Summary of Chip Measurements                           | 85   |

# LIST OF FIGURES

| Figure | I                                                                         | Page |

|--------|---------------------------------------------------------------------------|------|

| 1.1.   | Performance Degradation of RF Amplifier for Reliability Study             | 3    |

| 1.2.   | Sub-circuit Implementation of Aging Effect Model Using Verilog-A          | 11   |

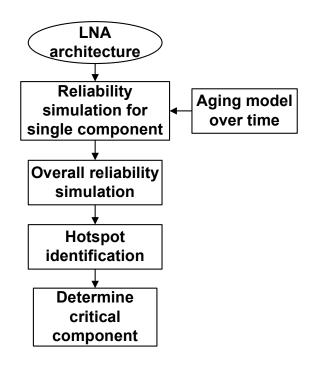

| 2.1.   | Flow of the Reliability Simulation Approach                               | 16   |

| 2.2.   | Flow of the Proposed Design-time Optimization Method                      | 17   |

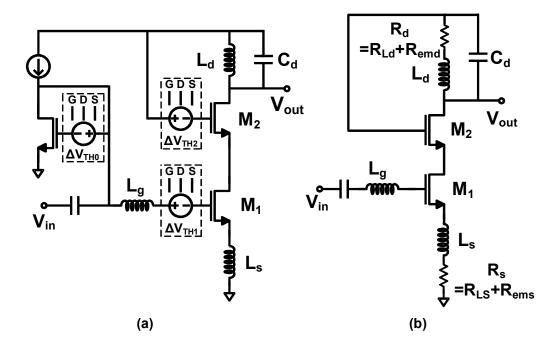

| 2.3.   | (a) HCI Analysis and (b) EM Analysis of Cascode LNA                       | 19   |

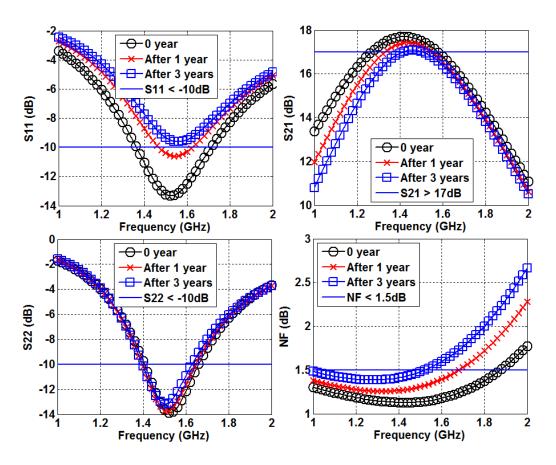

| 2.4.   | Performance Degradation Due to HCI Effect in Cascode LNA During           |      |

|        | One and Three Years of Operation at Room Temperature                      | 20   |

| 2.5.   | EM Simulation Results                                                     | 21   |

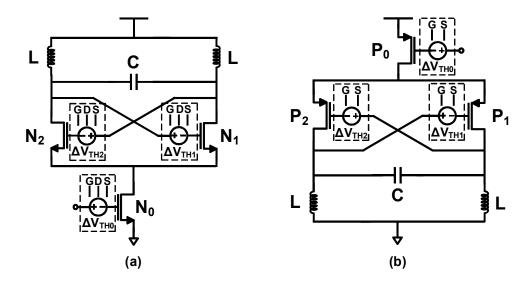

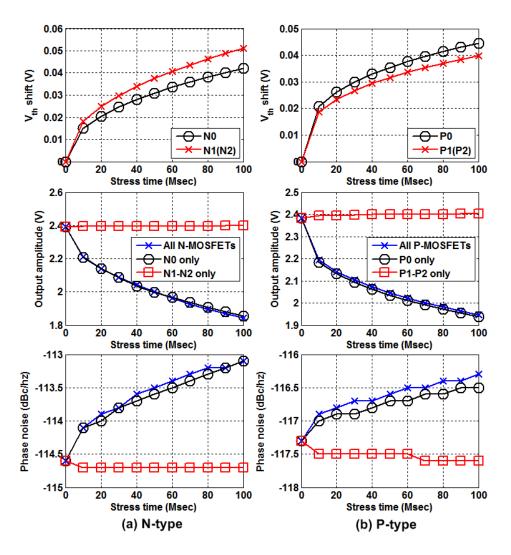

| 2.6.   | (a) HCI Analysis of N-type and (b) NBTI Analysis of P-type LC Oscillators | . 22 |

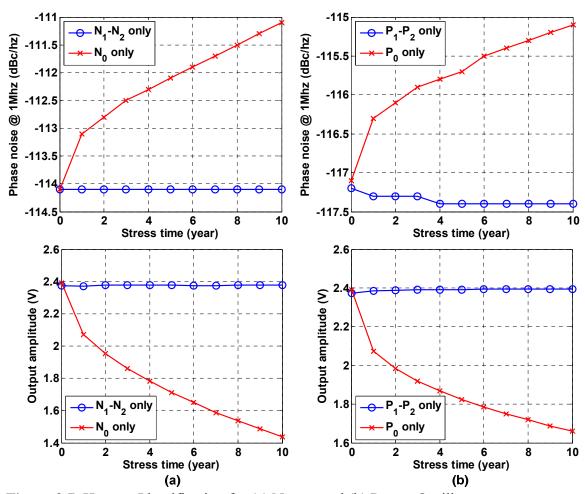

| 2.7.   | Performance Degradations of (a) N-type and (b) P-type LC Oscillators      |      |

|        | versus Stress Time                                                        | 23   |

| 2.8.   | Hotspot Identifications of LNA Due to HCI Effects                         | 25   |

| 2.9.   | (a) $R_s$ and $R_d$ Variations Due to EM Effects over Stress Time and     |      |

|        | (b) Lifetime Enhancement of LNA Due to EM Effects                         | 26   |

| 2.10.  | Impacts of Each EM Resistor on Circuit Performances                       | 26   |

| 2.11.  | Lifetime Enhancement of LNA Due to HCI Effects                            | 29   |

| 2.12.  | Lifetime Enhancement of (a) N-type and (b) P-type LC Oscillators          | 30   |

| 3.1.   | Flow Diagram for the Proposed Methodology                                 | 34   |

| 3.2.   | N-type and P-type LC Oscillator                                           | 38   |

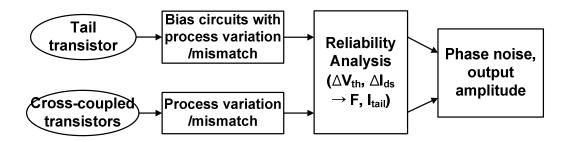

| 3.3.   | Reliability Analysis of LC Oscillator                                     | 39   |

| Figure | Pa                                                                        | age  |

|--------|---------------------------------------------------------------------------|------|

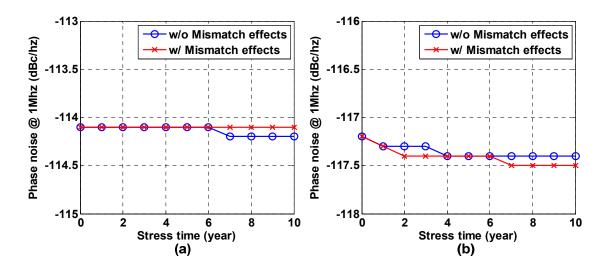

| 3.4.   | Simulation of Phase Noise Degradation Due to Cross-coupled Transistors    |      |

|        | of (a) N-type and (b) P-type Oscillator under Nominal Stress Conditions . | . 40 |

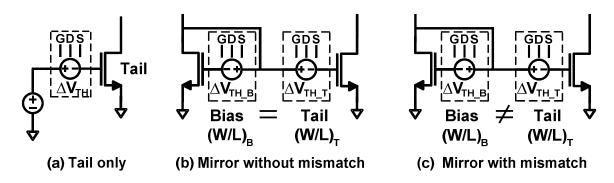

| 3.5.   | Reliability Analysis of a Tail Transistor with Different Bias Designs     | . 42 |

| 3.6.   | Phase Noise Degradation Due to Tail Transistors with Different Biasing    |      |

|        | Techniques in (a) N-type and (b) P-type Oscillator                        | . 44 |

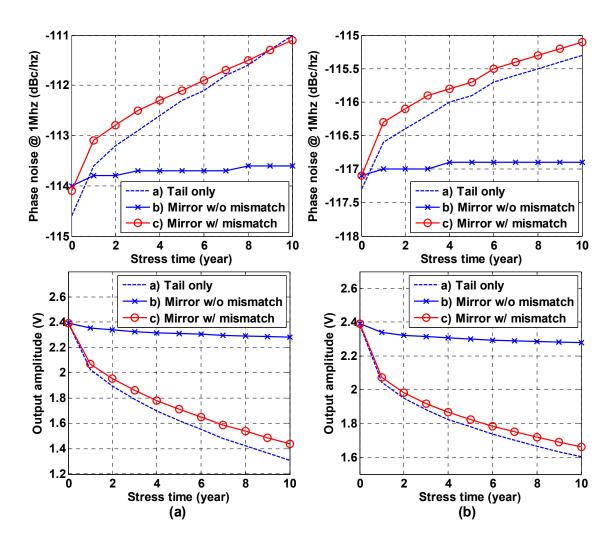

| 3.7.   | Hotspot Identification for (a) N-type and (b) P-type Oscillators          | . 46 |

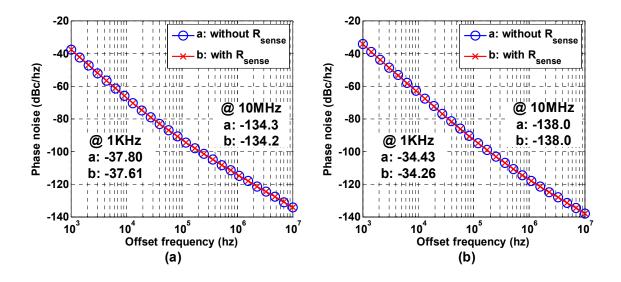

| 3.8.   | Phase Noise Degradation of (a) N-type and (b) P-type Oscillator with and  |      |

|        | without the Sensing Resistor                                              | . 48 |

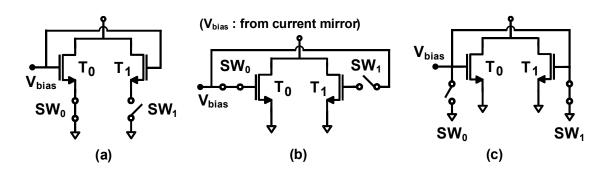

| 3.9.   | Possible Insertion Points for Digitally Controlled MOS Switches           | . 49 |

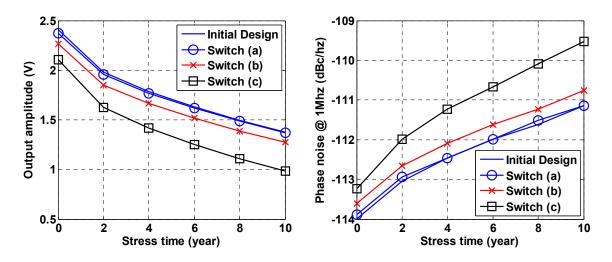

| 3.10.  | Performance Comparison with Different Locations of MOS Switches in        |      |

|        | N-type Oscillator                                                         | . 50 |

| 3.11.  | (a) N-type Oscillator with Proposed Monitoring and Mitigating Circuits    |      |

|        | and (b) the Overall Flow Chart of the Proposed Mechanism                  | . 51 |

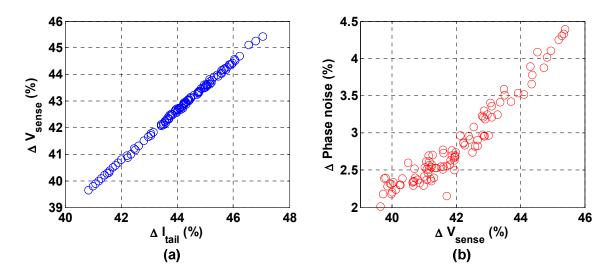

| 3.12.  | Correlation Between Circuit Performances from Monte Carlo Simulation      |      |

|        | of 100 LC Oscillators after 10 Years under Nominal Stress Conditions.     | . 52 |

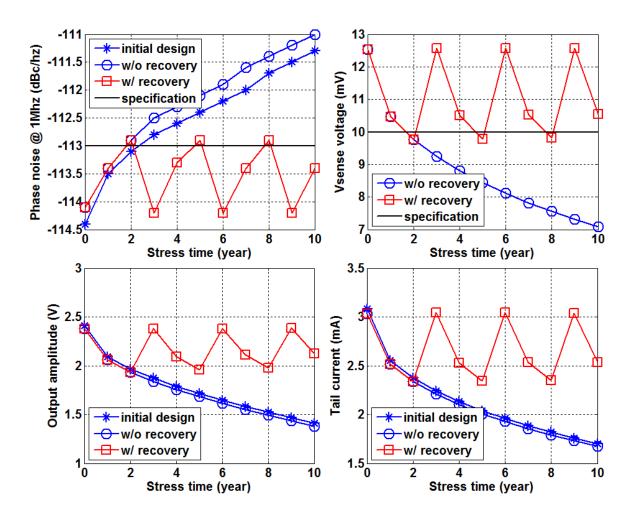

| 3.13.  | Simulation Results of Enhanced Lifetime Using the Proposed Method         | . 53 |

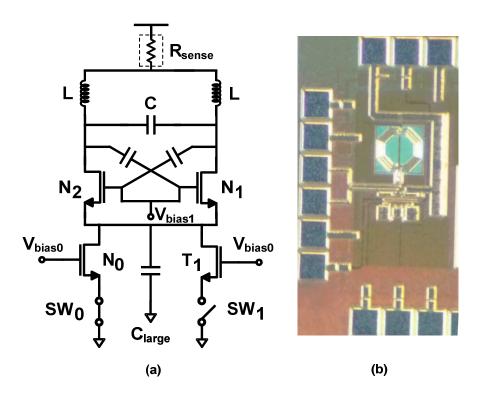

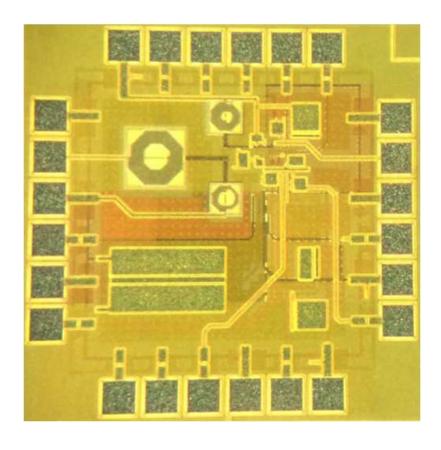

| 3.14.  | (a) Schematic of the Proposed Class-C Oscillator and (b) Die Photograph   |      |

|        | of the Proposed Design                                                    | . 56 |

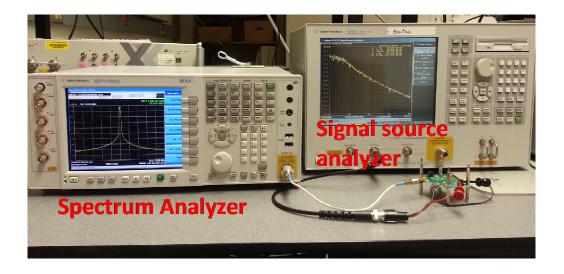

| 3.15.  | Initial Measurement Set-up                                                | . 57 |

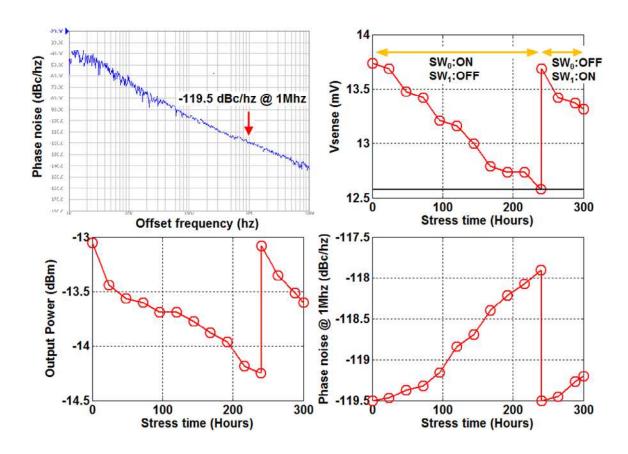

| 3.16.  | Measurement Results of Enhanced Lifetime Using the Proposed Method        | . 59 |

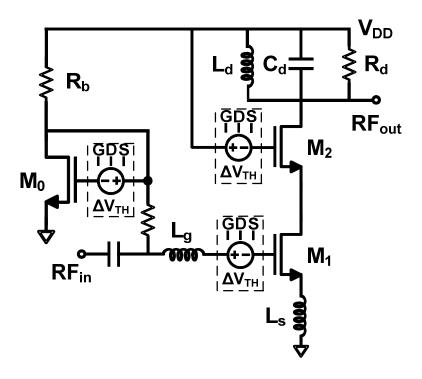

| 4.1.   | Schematic of Low Noise Amplifier with HCI Aging Models                    | . 63 |

| Figure | P                                                                         | age  |

|--------|---------------------------------------------------------------------------|------|

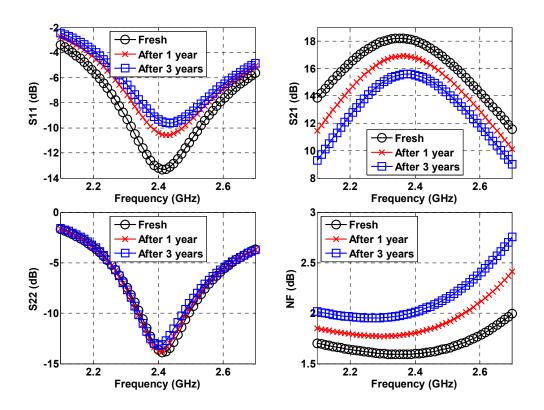

| 4.2.   | Performance Degradation Due to HCI Effect in Cascode LNA after 1 and      |      |

|        | 3 Years of Operation at the Room Temperature                              | . 64 |

| 4.3.   | Flow of the Proposed Methodology for Hotspot Identification of LNA        | . 66 |

| 4.4.   | Hotspot Identification Results of LNA Due to HCI Effects                  | . 66 |

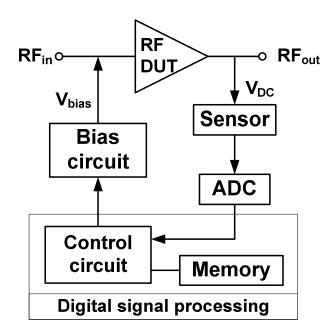

| 4.5.   | Proposed In-field Monitoring and Recovery Mechanism                       | . 69 |

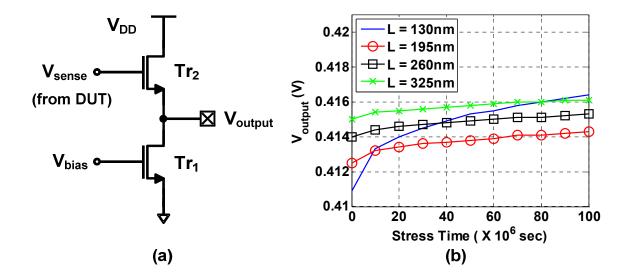

| 4.6.   | Proposed DC-based In-field (a) Monitoring Circuit and (b) DC $V_{output}$ |      |

|        | Voltage Variances under Various L                                         | . 71 |

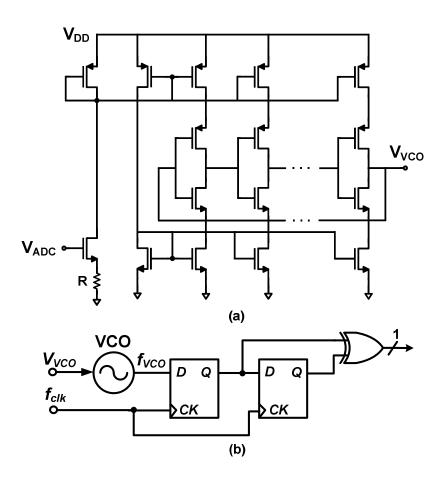

| 4.7.   | (a) Baseline VCO Architecture and (b) Block Diagram of                    |      |

|        | Frequency-to-digital Converter (FDC) for 1-bit Quantization               | . 72 |

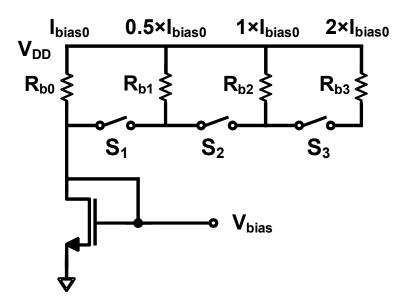

| 4.8.   | Proposed Tunable Recovery Circuit                                         | . 74 |

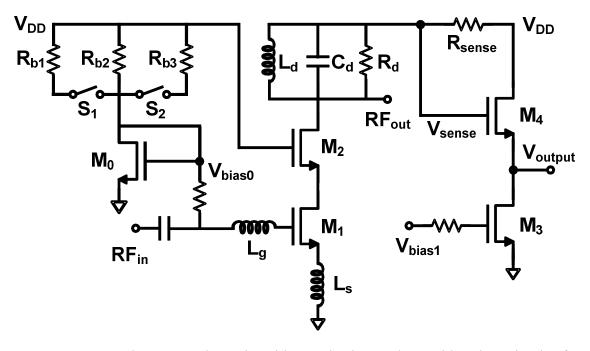

| 4.9.   | Cascode LNA Schematic with Monitoring and Tunable Bias Circuits for       |      |

|        | Recovery Process                                                          | . 76 |

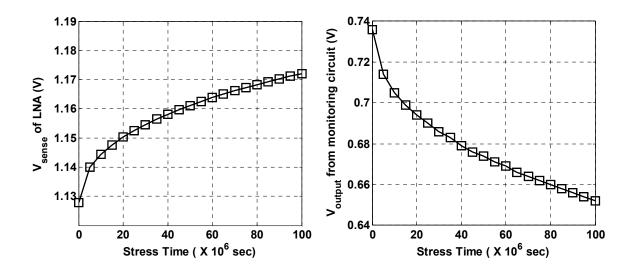

| 4.10.  | DC Voltage (Vsense and Voutput) Changes versus Stress Time                | . 76 |

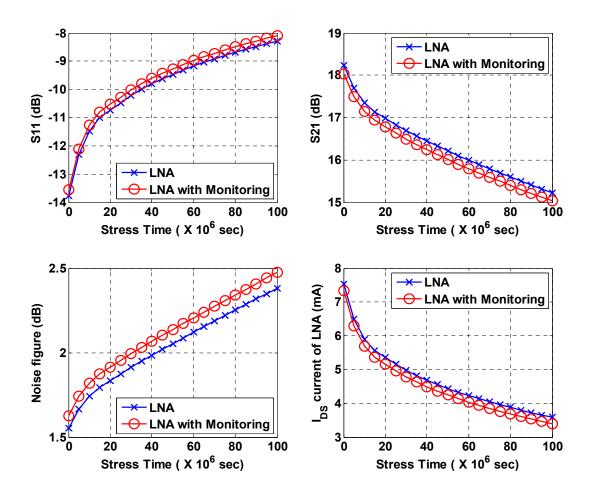

| 4.11.  | S-parameters and Bias Current Degradations versus Stress Time             | . 78 |

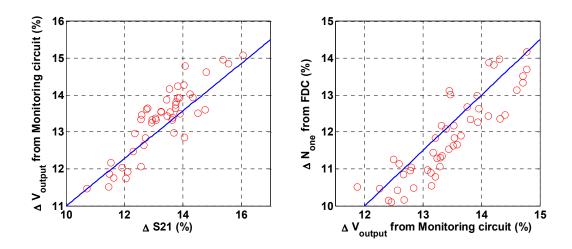

| 4.12.  | Correlation Between Circuit Performances from Monte Carlo Simulation of   | ?    |

|        | 50 LNAs after 3 Years under Nominal Stress Conditions                     | . 78 |

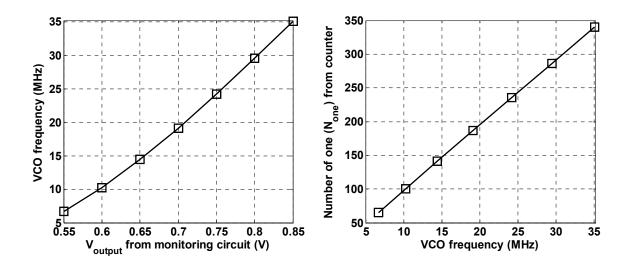

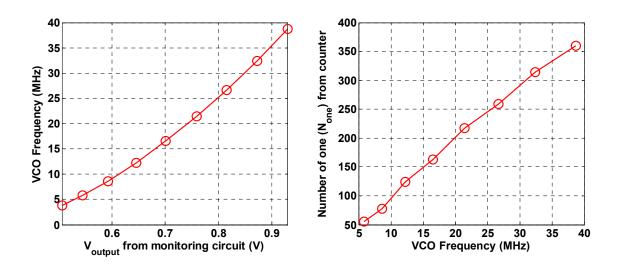

| 4.13.  | Characteristics of a VCO-based FDC                                        | . 80 |

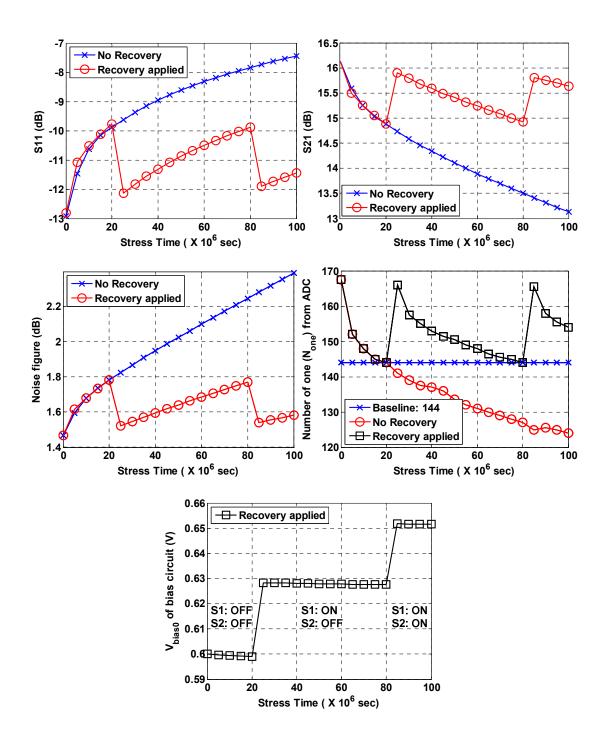

| 4.14.  | Simulation Results of Enhanced Lifetime Using the Proposed Recovery       |      |

|        | Technique                                                                 | . 82 |

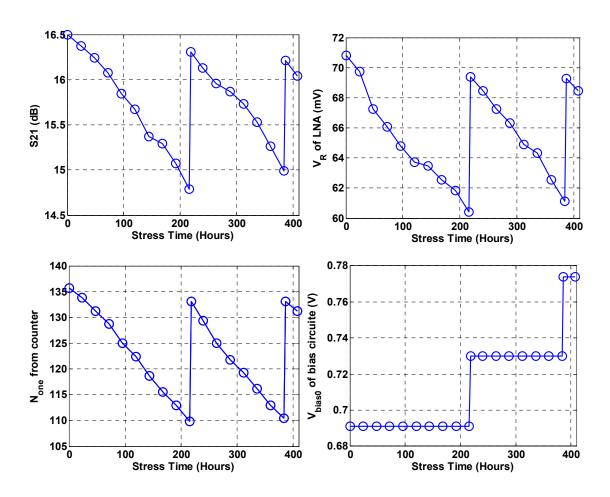

| 4.15.  | Die Photograph of the Proposed Design                                     | . 84 |

| 4.16.  | Measured Characteristics of a VCO-based FDC                               | 84   |

| Figure |                                                                   | Page |

|--------|-------------------------------------------------------------------|------|

| 4.17.  | Measured Results of Enhanced Lifetime Using the Proposed Recovery |      |

|        | Technique                                                         | 86   |

#### CHAPTER 1

#### INTRODUCTION

## 1.1. Background

Integration of RF/analog and digital subsystems is considered as the way to meet stringent specifications in terms of performance, power consumption, and form factor. These integrated systems consist of high performance mixed-signal designs with analog/digital blocks and sensitive RF frontends. In order to meet the ever increasing performance demands, digital circuits necessitate the use of advanced digitally-tuned processes. However, these processes are inherently less stable in terms of variations and are subject to wearout mechanisms in transistor parameters, which can cause malfunction in analog circuits long before the underlying devices are deemed to catastrophically fail [1, 2]. Hence, it is essential to ensure that a circuit operates with respect to all specifications to meet lifetime requirements at specified use conditions.

While in-field degradation due to aging for digital circuit is a continuing challenge, concerns for analog/RF circuits have scarcely been researched. In the context of analog and RF circuits, reliability is defined as the ability of a circuit to conform to its specifications over a specified period of time under specified conditions [3]. Several researchers have focused on analysis of aging degradation in various analog/RF circuits. These mechanisms include hot carrier injection (HCI) [3-5], time dependent dielectric breakdown (TDDB) [6-8], negative bias temperature instability (NBTI) [9-11], and electromigration (EM) [12], [13]. Of these mechanisms, HCI and NBTI are determined to

be the most critical for deep submicron designs [2][10]. As CMOS technology scales to the nano-meter range, the threshold voltage shift due to increased internal electric fields becomes more prominent on transistor. Major mechanisms of the circuit aging as HCI and NBTI eventually result in an increase in the absolute threshold voltage and reduction in device current, thereby degrading circuit performance such as speed, gain, and data stability. An analysis of the performance of CMOS LC-tank oscillators under HCI stress is presented in [5], [14]. The authors conclude that HCI causes increased phase noise because of the decrease in the oscillation amplitude due to the degraded NMOS transistors. In [11], various analog circuits are simulated for NBTI reliability and their degradation is analyzed. The authors conclude that when these circuits are implemented using fine-geometry digital processes, performance degradation starts within the first few months of device use and gradually accelerates. In [15], the authors develop a time scaling model to relate experimental data from accelerated aging studies to nominal operational use.

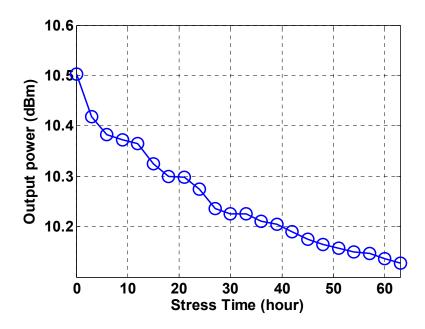

In order to assess the reliability risk on silicon for RF circuits experimentally, aging studies have conducted on a commercial RF amplifier (MAX1472). This amplifier was subjected to a temperature of 120°C and 10% supply voltage overdrive to enhance the effects of aging degradation. Fig. 1.1 shows the degradation in the amplifier gain with respect to stress time. After about 60 hours of continuous stress, the gain of the amplifier has dropped by 0.5dB, which is a significant loss. Under nominal supply voltage, 60 hours of stress time is projected to 5400 hours of continuous operation, which may make the device parametrically fail within the first 7 months of deployment. This experiment

demonstrates that analog/RF circuits are just as susceptible to aging related failures as digital circuits.

**Figure 1.1.** Performance Degradation of RF Amplifier for Reliability Study.

With mounting evidence on the impact of device aging for analog circuits, many techniques have been developed to analyze circuit reliability at design time [14], [16-18]. Design-time improvements at the circuit-level and at the layout level, such as using higher than minimum length, can ensure that statistically, most manufactured devices will not experience significant degradation in their parameters. For example, NBTI and process variations are exacerbated with technology scaling based on Pelgrom's law [19], [20]. In digital circuits such as SRAM, by using larger devices, the delay spread due to process variations can be reduced as a function of device dimension ( $\propto 1/\sqrt{LW}$ , where L is gate length and W is the gate width), and the impact of NBTI on circuit reliability also can be reduced. However, aging is a random process and cannot be ruled out even with

design-time adjustments. More importantly, there are no known techniques to identify devices that will experience faster aging during operation time. Wholesale use of reliability enhancement techniques at the device level is also counterproductive in terms of performance and area [21]. Hence, an in-field mechanism to monitor and mitigate the effects of device aging is needed.

While prior work in RF reliability addresses the analysis of aging phenomena on RF circuits, there has been little to no work to make use of this knowledge in the field as the device ages. Since aging results in continuous degradation after the device is deployed, it can be detected by monitoring the circuit performance. Once it is known that aging mechanisms have started causing noticeable degradation, remedial action can be taken by introducing compensation circuits. As a result, it is necessary to monitor the degradation of the circuit while the circuit is in the field.

Unfortunately, direct monitoring of RF/analog circuit performance is often not feasible since many specifications, such as noise, third order input intercept, or S-parameters, cannot be measured in the field. Therefore, alternative measurement mechanisms need to be developed for in-field monitoring that relies on information from easy-to-design circuits. This monitoring strategy requires establishing a strong correlation between the current and future status of the circuit and the monitor response. Existing work for design-for-reliability focuses on compensating for PVT variations [22]-[24]. However, they require significant increase in design area and time to incorporate for self-compensation.

## 1.2. Reliability Models for CMOS Transistors and Analog/RF Circuits

Of the various mechanisms of degradation, HCI and NBTI have been identified as the most detrimental to the device operation for deep sub-micron technologies. In this section, the aging mechanisms are reviewed, and a simulation and analysis method for these aging mechanisms under process variations and mismatch is presented.

#### 1.2.1. Hot Carrier Injection (HCI)

Time-dependent aging effects will cause a shift of transistor parameters as a function of time. Hot-Carrier injection (HCI) is one such degradation mechanism mainly affecting N-type MOSFETs. During hot carrier stress caused by high electric field near the drain region, either an electron or a hole at the end of the drain junction gains sufficient kinetic energy to overcome the potential barrier, and then migrates toward the oxide silicon surface. These hot-carriers can cause both interface state generation and charge traps which increase the leakage substrate current and decrease drain current. After hot carrier stress, the transistor characteristics, such as threshold voltage and channel mobility, may shift, changing the characteristics of the device.

The impact of HCI effect is more pronounced for RF/analog circuits due to the strong dependency of performance parameters on the threshold voltage of critical transistors. Effects of HCI on the RF characteristics of single N-type MOSFET and RF circuits have been studied [8].

HCI can be physically shown as the generation of charges in the region close to the Si/SiO2 interface. Charge generation is localized to drain region making HCI to be a

strong function of drain-source (lateral field) voltage,  $V_{ds}$ . For a given stress time and assuming interface trap generation for HCI occurs at drain end, it is possible to derive the closed form equation for threshold voltage  $V_{th}$  shift of a device under HCI stress [10][26]. For example, for a constant gate voltage increasing drain voltage results in higher  $V_{th}$  shift. At higher gate-source voltage  $V_{gs}$  for thin oxide devices, the electric field across oxide increases which causes higher scattering of electrons for the same drain voltage. Thus, HCI depends both on  $V_{ds}$  and  $V_{gs}$ .

The set of analytical models governing the HCI effect with respect to the stress time, t, is given in Table 1.1.  $E_{OX}$  is the vertical electric field (due to  $V_{gs}$ ),  $E_m$  is the lateral electric field,  $\varphi_{it}$  is the minimum energy in eV required by hot electron to create impact ionization,  $\lambda$  is the mean free path,  $E_0$  is the activation energy, K is the fitting parameter and n is the time exponent. The model parameters can be characterized for a given technology node and implemented in a circuit simulation environment. This model has been experimentally verified for a multitude of bias conditions [10][27].

$$\Delta V_{th\_HCI} = \frac{q}{C_{ox}} K \sqrt{Q_i} \exp(\frac{E_{ox}}{E_0}) \exp(-\frac{\varphi_{it}}{q\lambda E_m}) t^n$$

#### SUMMARY OF PARAMETERS IN AGING MODELS

| $E_m$        | $(V_{ds} - V_{dsat}) / l$ | $E_{ m ox}$            | $(V_{gs} - V_{th}) / t_{ox}$ |

|--------------|---------------------------|------------------------|------------------------------|

| $E_0$ (V/nm) | 0.8                       | $Q_{\mathrm{i}}$       | $C_{ox}(V_{gs}-V_{th})$      |

| λ (nm)       | 7.8                       | $K(nm \cdot C^{-0.5})$ | 1.7×10 <sup>8</sup>          |

| δ            | 0.5                       | $arphi_{ m it}$        | 3.7                          |

**Table 1.1.** Summary of HCI Aging Model.

## 1.2.2. Negative Bias Temperature Instability (NBTI)

The negative bias temperature instability (NBTI) occurs in PMOS devices when a negative bias is applied to the gate or equivalently, when the gate is grounded and a positive bias is applied to the source/drain. NBTI is caused by the interface traps and fixed charge under negative gate voltage bias and accelerates when the operation temperature increases. In other words, NBTI is caused by the reaction-diffusion (R-D) mechanism, where holes initiate the breaking of Si–H bonds (reaction phase) at the silicon substrate/oxide interface by a combination of electric field and temperature. The broken hydrogen species diffuse away from the interface into gate oxide and the polysilicon gate (diffusion phase) and thus, interface charges are generated [28]. Therefore, NBTI leads to a shift in the threshold voltage, which is proportional to the interface trap generation. This threshold voltage shift decreases the drain current under

constant voltage bias. For current bias, the threshold voltage shift will result in increased gate-to-source bias voltage. Hence, if a transistor is biased through a current mirror, the mismatch between the mirror transistor parameters is the major source of degradation.

NBTI effects can be categorized by two models depending on the stress conditions, namely, static NBTI and dynamic NBTI. Static NBTI is experienced under constant stress, as in the case of DC bias. This form of NBTI degradation cannot be recovered. For dynamic NBTI, the device undergoes AC operation and experiences positive and negative stresses, which generates a cycle of degradation/recovery. Finally, the threshold voltage degradation due to NBTI at a time t can be obtained by  $\Delta V_{th\_NBTI} = C_{NBTI} \cdot t^{n'}$  where  $C_{NBTI}$  is a parameter depends on process variations, voltage, and temperature. n' is the time exponent [10], [26].

Based on this stress/recovery cycle, one might conclude that NBTI is not a big issue for oscillators where voltage swing is comparable to DC bias. However, the large swing is only experienced by the coupled transistors, and is not symmetric.

## 1.2.3. Electromigration (EM)

Shrinking metal thickness leads to higher current density flowing through interconnects, exacerbating electromigration (EM) effects on circuit performance and reliability. Even though some new materials with better immunity to EM failures have been used as on-chip interconnects to replace Aluminum (Al), EM is still a reliability concern. EM is the process of mass transport caused by momentum transfer between conducting electrons and metal atoms. During electromigration, the metal atoms move in the direction of electron flow along the grain boundaries. Over time, enough material

may move resulting in significant change in the metal resistance. As in the case of HCI and NBTI, research has focused mostly on catastrophic failure, and the well-established Black's model is used for calculating MTTF [29]:

$$MTTF = \frac{A}{J^n} \exp(\frac{E_a}{kT}) \tag{1.1}$$

where A is a material parameter dependent on structure and geometric properties of the conductor, n is the current exponent factor, J is the current density,  $E_a$  is the activation energy, k is the Boltzmann constant, and T is the temperature. While most EM research has focused on digital circuits and catastrophic failure modes [30][31], studies show that EM results in continuous increase of trace resistances as soon as current starts flowing through the metal [32][33].

#### 1.2.4. Process Variation

Parametric variations present one of the toughest challenges in reliability analysis and modeling for RF/analog circuits [17], [18], [21]. Variations exist both in physical process parameters, such as threshold voltage, and in degradation model parameters, such as the trap generation energy. Hence, it is imperative to take process variations into account. Process variations are classified as die-to-die variations and within-die (mismatch) variations [34][35]. Die-to-die variations, which shift parameters of all devices on the same die in the same fashion, are larger compared to mismatch variations, which affect each device randomly. Traditionally, die-to-die variations have been the main concern in CMOS digital circuit designs. However, as CMOS technology scales down, within-die variations are a growing concern for maintaining the specified

performance [36]. Since analog/RF circuits are very sensitive to mismatch, both die-to-die and mismatch variations need to be taken into account. There have been literature works in the past which considered process variations and the aging in RF/analog circuit simultaneously at the simulation level [1], [18], [37]. However, mismatch in degradation parameters is typically considered negligible. In this dissertation, a hybrid simulator/model based technique is used to evaluate random circuit instances and a mismatch in both process and degradation parameters is included in the analysis.

## 1.3. Reliability Simulation at Circuit Level

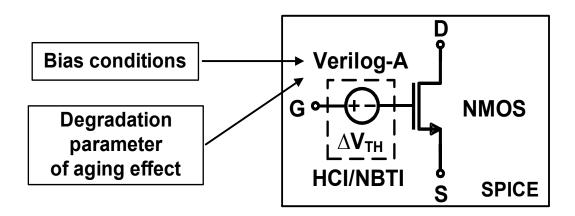

In order to analyze the effect of the failure mechanisms on circuit reliability, a simulator is needed. However, most reliability simulators that are commercially available are not amenable to analog operation where devices undergo different bias/swing conditions. In order to identify the reliability hotspots, it is required to be able to turn the degradation on or off for each transistor or transistor pair. In [37], a reliability simulation framework is presented that integrates variability with reliability by employing transistor drain current surrogate models. A transistor-level circuit simulator is employed to measure the degradation of performance parameters of fresh and aged circuits [38-40]. The proposed method uses a similar hybrid methodology by adapting a sub-circuit model of the threshold voltage shift of the aged transistors [41]. The analytical model of each aging effect (HCI of NMOS and NBTI of PMOS) is implemented to a Verilog-A simulator and modeled as a voltage-controlled voltage source (VCVS) in series to the gate of the aged transistor as illustrated in Fig. 1.2. In each time step during a transient circuit simulation, the threshold voltage shift is determined based on the current bias

conditions of a transistor and degradation parameters of the aging effect. Finally, this VCVS-based aging model is inserted into SPICE environment for each NMOS/PMOS transistor. Since the model is calibrated for various bias conditions during the operation, the sub-circuit model accurately captures the aging degradation. The complete sets of analytical models of aging effects are summarized in [10], [42]. These model coefficient can be easily characterized for a given technology and implemented in the circuit simulation environment. The major difference in this work is that a mismatch between aging parameters of various transistors is taken into account during circuit simulation environment.

Figure 1.2. Sub-circuit Implementation of Aging Effect Model Using Verilog-A.

#### 1.4. Outline of Dissertation

In this dissertation, RF BIST methods for advanced RF transceiver such as RF polar transceiver and RF phased array are proposed. In addition, robust amplitude and gain measurement for RF BIST application are proposed and discussed.

In chapter 2, a systematic approach to design on RF circuit with expected lifetime as a specification parameter is proposed. In the proposed framework, parametric aging effects for RF circuits are analyzed and the overall lifetime is determined. An algorithm to determine reliability hotspots in the circuit and design-time optimization methods to enhance the lifetime by making the most likely to fail circuit components more reliable are presented. Based on the information that has been collected from simulations, it is possible to enhance the lifetime of the circuit without changing its performance if reliability is taken into consideration at design time.

In chapter 3, a comprehensive systemic methodology for co-designing CMOS LC oscillators together with in-field monitoring and recovery mechanisms to enable aging mitigation with minimal performance and area overheads. The proposed technique includes hotspot identification to determine the weakest component, monitor/reconfiguration network design, and an algorithm to automatically swap the aged transistor with a new one to enhance the lifetime. In order to demonstrate the proposed technique, cross-coupled LC oscillator circuits are used for simulations and a CMOS class-C LC oscillator is fabricated in 180nm IBM process for experimental results.

In chapter 4, a methodology for enhancing the lifetime of RF circuits in the field using low-impact circuit level monitor and recovery techniques. The particular aging mechanism focusing on is hot carrier injection (HCI) although the proposed method

would work with any aging mechanism that can be modeled to enable simulations. Since the monitoring circuit is also prone to process variations, the monitoring mechanism is designed as a relative measurement, based on the amount of change in the monitor circuit output, rather than the absolute value. In order to demonstrate the concepts of reliability analysis and monitor and recovery circuit design, a generic LNA architecture is implemented as a case study.

#### CHAPTER 2

# DESIGN-TIME RELIABILITY ENHANCEMENT USING HOTSPOT IDENTIFICATION FOR RF CIRCUITS

## 2.1. Simulation Framework for Aging Mechanisms

To develop a design-for-reliability approach for RF circuits, a framework for simulating aging effects is necessary. While commercial tools exist to simulate for digital circuits, they typically report an overall lifetime in terms of a catastrophic failure, mean-time-to failure (MTTF). Therefore, an aging simulation method that is based on SPICE is developed to:

- 1) Analyze each circuit component and each aging mechanism independently and

- 2) Evaluate parametric degradation in specifications and determine lifetime.

To enable these simulations using existing tools (e.g., SPICE), each circuit component model is modified with an equivalent that changes circuit parameters with respect to the amount of degradation. The degradation amount with stress time for presilicon simulation is determined based on well-established reliability models [10], [27] and the current state of the circuit performance. In this proposed simulation framework, the aging effects of HCI, NBTI, and EM are included.

Similar to [40], the proposed simulation framework uses improved circuit components to model the degradation effects. However, [40] aims to analyze the effect of degradation on the circuit when all circuit components are under stress. This approach does not provide the necessary information for hotspots identification. Moreover, device-to-device mismatch for process or degradation parameters has not been previously

considered. Mismatch results in unequal degradation in different transistors and has a profound effect on analog circuit performance. In the proposed framework, it is necessary to pay particular attention to the following issues:

- 1) Circuit components are subject to both die-to-die and within-die (mismatch) variations.

- 2) Degradation model parameters are also subject to mismatch variations among circuit components.

- 3) Each circuit component is subject to differing levels of stress due to bias conditions and dynamic signal behavior.

- 4) Circuit bias conditions change over time; simulations based on an initial bias point are unreliable.

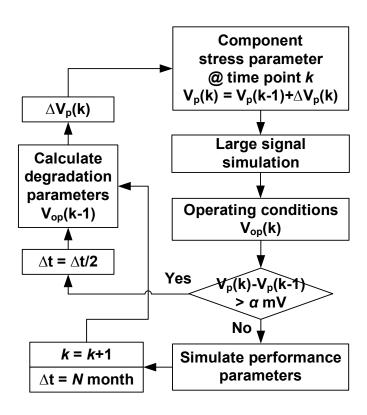

- Fig. 2.1 shows the flow of the reliability simulation approach. Initial bias voltages and currents are determined via simulations. For small-signal operation, degradation parameters (e.g., threshold voltage) can be determined using dc bias. For large-signal operation, dynamic signals also need to be considered. An initial time step (e.g., N months) is used to calculate degradations in circuit component parameters. The circuit is simulated again to determine the change in dc operating point. If the shift in dc point is above a tolerable threshold (e.g.,  $> \alpha$  mV), the time step is reduced and the prediction is repeated. Otherwise, the circuit is simulated for performance evaluation (e.g., gain and phase noise). With this simulation framework, it is possible to simulate the aging effect for a single or multiple components.

Figure 2.1. Flow of the Reliability Simulation Approach.

## 2.2. Design-Time Optimization Methodology

After analyzing the reliability impact of aging mechanisms on the circuits in several steps, the reliability simulation can concentrate on each circuit component and determine at what point it will cause a specification failure, assuming that it is the only contributor to degradation. This proposed method can determine the reliability hotspots and concentrate design optimization efforts on these circuit components. If the projected lifetime is not satisfactory, the most dominant lifetime-limiting component is modified so as to increase its reliability.

Fig. 2.2 shows an overview of the proposed methodology. The first step in the process is to analyze the aging effects on circuit performances using the analytical models of each aging effect. One aging effect for one device is activated at a time to isolate the hotspot device and the cause of the degradation. The stress time is gradually increased with an adaptive time interval and the aging impact on circuit specifications is analyzed. This information combined with the circuit specifications yields a certain time point at which the specification will fail. The sensitivity of circuit specifications with respect to each circuit component degraded by aging effects differs. Due to different sizes and operating points, this profile will be different for each circuit component. Therefore, each circuit component will cause a distinct failure time for each specification.

**Figure 2.2.** Flow of the Proposed Design-time Optimization Method.

Note that at this point, the method focuses on one circuit component at a time to determine the lifetime-limiting factors. The actual failure point of the circuit will differ from this first-level sensitivity study, since all circuit components simultaneously age, albeit at a differing rate. This process iteratively go through each circuit component and track the failure time of the each circuit specification. Once all the failure times are collected, it is possible to decide the most vulnerable component to aging effects. Component-centric lifetime enhancement can be done using established techniques by adjusting the component parameters. Clearly, once one component is modified, circuit specifications shift, thus requiring modifications on other components. Hence, circuit modifications need to be done incrementally to avoid ping-pong behavior of the optimization process. Moreover, a circuit component is not modified to enhance the lifetime to beyond what is limited by another circuit component.

#### 2.3. Case Studies

## 2.3.1. Low Noise Amplifier with HCI and EM Analysis

A cascode low noise amplifier (LNA) is used as an example to demonstrate the RF performance degradation due to HCI and EM effects. Fig. 2.3 (a) shows a narrow-band LNA where the transistors are enhanced to account for degradation effects [43]. The circuit is designed with the following specifications:

[S21 > 17 dB, S11 < -10 dB, S22 < -10 dB and NF < 1.5 dB] @ 1.5 GHz.

Figure 2.3. (a) HCI Analysis and (b) EM Analysis of Cascode LNA.

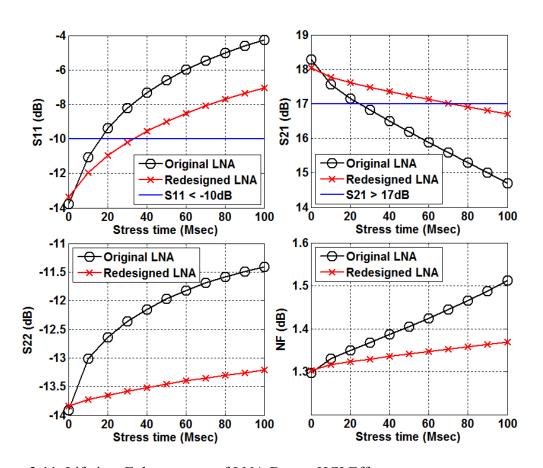

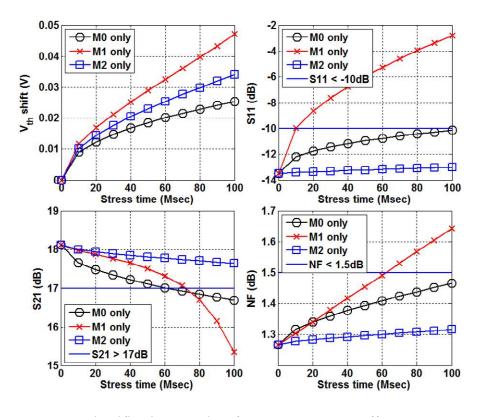

Reliability simulations of the LNA due to HCI effects are performed using the framework outlined previously over three years of stress time. Time-varying threshold voltage shift of HCI is modeled as a dependent voltage source with input node voltages. These node voltages are connected to gate, drain, or source of the device and updated after each time step to obtain more accurate actual simulation responses. In this design example, there are three voltage sources  $\Delta V_{TH0,1,2}$  at the gate of each nMOSFET to consider the effects of threshold voltage shift. Degradation profiles of the LNA specifications, such as S-parameters and noise figure (NF) are shown in Fig. 2.4. Due to the degradation of threshold voltage, it reduces the drain-source current of transistor and hence its transconductance  $g_m$ , thus resulting in degradation in specifications [43]. From the simulations, it is observed that the circuit is likely to fail input return loss (S11), gain (S21) and NF between 1 and 3 years of lifetime, which is generally not acceptable.

**Figure 2.4.** Performance Degradation Due to HCI Effect in Cascode LNA During One and Three Years of Operation at Room Temperature.

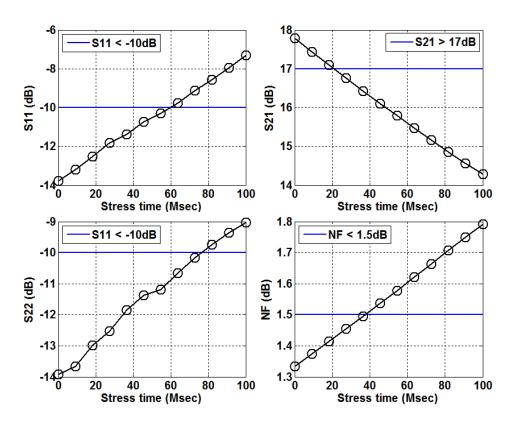

To analyze the reliability impact of EM on the LNA, it is important to concentrate on conductors (via and inductor) as shown in Fig. 2.3 (b). Both on-chip inductors,  $L_d$  and  $L_s$  are implemented using metals. The inductor Q is modeled using the resistors  $R_{Ld}$  and  $R_{Ls}$ , in series with ideal inductors,  $L_d$  and  $L_s$ , respectively. The inductor EM model  $R_{emd}$  and  $R_{ems}$  are additional resistances in series with  $R_{Ld}$  and  $R_{Ls}$ . Since there is no dc current into the gate of the input transistor, there is no EM effect on  $L_g$ . EM results in a slow linear change in the resistance of the metal line [33]. LNA S-parameter degradation due to increasing line resistances within three years is shown in Fig. 2.5. This result shows

that the circuit is projected to fail the gain specification within eight months ( $\sim 20 \times 10^6$  s) of its deployment.

Figure 2.5. EM Simulation Results.

## 2.3.2. CMOS LC Oscillator with HCI and NBTI Analysis

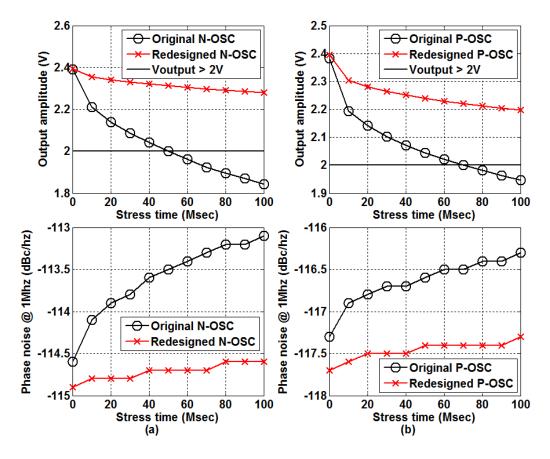

Fig. 2.6 (a) and (b) shows the two types of CMOS LC-tank oscillators used in the circuit experiments. Important performance parameters of the LC oscillator are phase noise and output amplitude [44]. The N-type oscillator is designed to yield a phase noise better than -114 dB/Hz at 1-MHz offset and an output amplitude higher than  $2V_{pp}$  at 5-GHz center frequency.

**Figure 2.6.** (a) HCI Analysis of N-type and (b) NBTI Analysis of P-type LC Oscillators.

Fig. 2.7 (a) shows the performance degradations in N-type LC oscillator over stress time. Note that the cross-coupled transistors degrade faster due to higher voltage stress. Therefore, a lifetime of  $< 60 \times 10^6$  seconds is predicted when output amplitude is higher than  $2V_{pp}$ .

The performance degradation for the P-type oscillator is similar to the N-type. However, NBTI has unique characteristics due to stress recovery [10]. In a P-type oscillator circuit, the cross-coupled transistors are exposed to ac stress, while the tail transistor is under dc stress. Due to the recovery phase of the NBTI, the parameter degradations on cross-coupled transistors are less compared with the tail transistor, although the stress conditions for cross-coupled transistors are greater than the tail transistor in the P-type LC oscillator. Fig. 2.7 (b) also represents the simulation results for the P-type oscillator after NBTI effect.

**Figure 2.7.** Performance Degradations of (a) N-type and (b) P-type LC Oscillators versus Stress Time.

Fig. 2.7 also shows the reliability simulation results of cross-coupled transistors with  $\pm 5\%$  mismatch in process parameters and aging parameters. While these transistors undergo similar stress patterns, in both dc and ac domains, there is still some mismatch in their parameters. This is due to the mismatch in process and degradation patterns. It is observed that the degradation in cross-coupled transistors does not cause a significant degradation in the overall performance. This result may be at first counterintuitive.

However it can be explained with the phase noise model [44]. The  $g_m$  of the cross-coupled transistors plays a role in determining the equivalent resistance, hence the phase noise. However, it is primary determined by the tail transistor, since the transistor size does not change. Hence, a change in the threshold voltage of cross-coupled transistors does not cause significant degradation in the phase noise, unless it alters the bias so significantly that the circuit diverts from the desired operating point.

## 2.4. Hotspot Identification

The degradation of threshold voltage and LNA performances due to the HCI effect during three years of stress time are shown in Fig. 2.8. This analysis indicates that the S11 will fail earliest due to the degradation in transistor  $M_1$ . Hence, for the first iteration,  $M_1$  is determined as the reliability hotspot due to HCI.

**Figure 2.8.** Hotspot Identifications of LNA Due to HCI Effects.

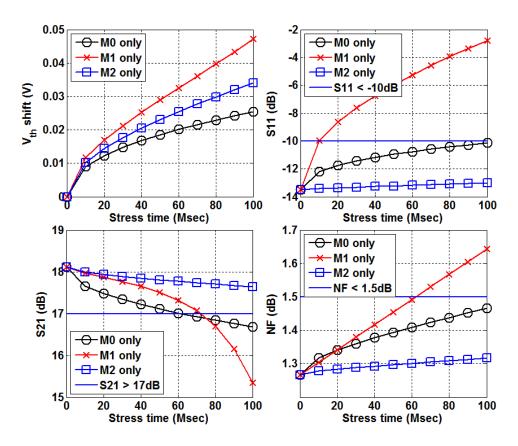

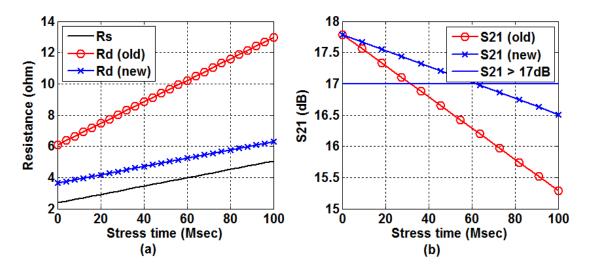

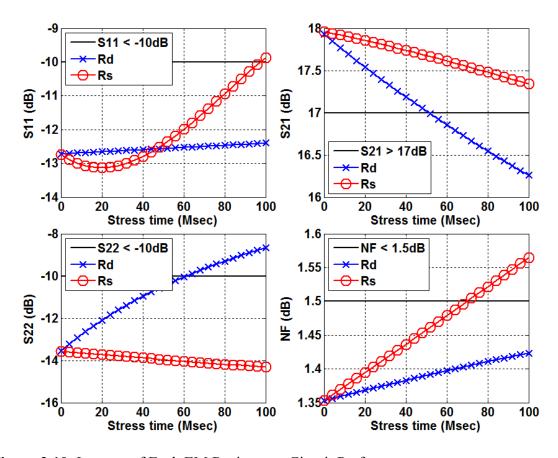

To identify the critical component of EM resistances on LNA lifetime, the functions relating the resistance of  $R_s$  (=  $R_{Ls}$ + $R_{ems}$ ) and  $R_d$  (=  $R_{Ld}$ + $R_{emd}$ ) to stress time are shown in Fig. 2.9 (a) by scaling the slope for the design's current density. EM results in a linear increase in resistances  $R_{emd}$  and  $R_{ems}$  with stress time. The variations in LNA performance parameters due to EM are shown in Fig. 2.10. Based on these simulations, it is concluded that the  $R_{emd}$  resistance is the critical component for S21. For specifications (S21 > 17 dB and S11 < -10 dB), the lifetime of this device is estimated as  $50 \times 10^6$  seconds ( $\sim$ 20 months). Thus, the reliability of this design is limited by the current path through  $L_d$ .

**Figure 2.9.** (a)  $R_s$  and  $R_d$  Variations Due to EM Effects over Stress Time and (b) Lifetime Enhancement of LNA Due to EM Effects.

Figure 2.10. Impacts of Each EM Resistor on Circuit Performances.

For the N-type LC oscillator shown in Fig. 2.6 (a), the degradation model of each transistor is adjusted by HCI effect. First, the threshold voltage shift model of tail transistor is adopted to analyze the performance with gradually increased stress time. Because both tail transistor and cross-coupled transistor are biased with different dc bias conditions, different amounts of degradation in threshold voltage shift are determined and applied to the circuit. The overdrive voltage at the tail transistor is usually kept low to allow a higher output swing. Thus, the transistor at the cross-coupled pair experience a dc bias voltage of  $V_{ds} = V_{gs} \approx V_{dd}$ . From the degradation results, shown in Fig. 2.7 (a), although the degradation of threshold voltage in cross-coupled transistor is higher than tail transistor, the degradation performances, such as phase noise and output amplitude, for tail transistor N<sub>0</sub> only aged are more significant than those of cross-coupled only aged during three years. It is concluded that the tail transistor of N-type LC oscillator is a critical device due to HCI.

The same simulation process is implemented for the P-type LC oscillator. The degradation model of NBTI effect is used to demonstrate the threshold voltage shift under the stress condition. Fig. 2.7 (b) represents the reliability simulation results for a P-type oscillator considering NBTI. As predicted earlier, the cross-coupled transistors will introduce less degradation effects on the performance than the tail transistor because of the recovery phase in the cross-coupled transistors. Therefore, the tail transistor P<sub>0</sub> of the P-type LC oscillator is the critical device causing degradations due to NBTI.

# 2.5. Design-Time Optimization in RF Circuits

To reduce or eliminate the HCI and NBTI effects, the circuits are redesigned with adjusted bias to relieve the stress on the hotspot. After identifying the critical transistor(s) with HCI or NBTI effects, it is possible to minimize the performance degradation by changing the size of this critical transistor(s). HCI effect has a strong dependence on the channel length of the nMOS device. For the cascode LNA and N-type LC oscillator with the HCI effect, as the length of the nMOSFET device is reduced, the lateral channel electric field increases, and the HCI effect becomes more significant [10]. Therefore, redesigned LNA and N-type LC oscillator have increased critical transistor length from 65 to 130 nm, thus reducing the lateral electric field through the channel, and reducing threshold voltage degradation. The critical transistor's bias conditions and the RF performance of the original and redesigned circuits should be the same at initial stress time. To achieve comparable performance to the original design, it is required to codesign the circuits by adjusting circuit parameters, such as transistor dimensions and passive component values, in the redesigned circuits. The reliability simulation results shown in Fig. 2.11 confirm that the redesigned LNA with 130-nm critical transistor length has less performance degradations than the original LNA with 65-nm transistor length. Furthermore, lifetime has been increased significantly. For instance, the lifetime of original cascode LNA, which is estimated as 15×10<sup>6</sup> seconds due to a failure in S11 (S11 < -10 dB), has increased to  $35 \times 10^6$  seconds after the redesign technique is applied. The simulation results illustrating the enhanced performance in the N-type and P-type oscillators are shown in Fig. 2.12. For specifications (output amplitude > 2V), the original N-type oscillator's lifetime is estimated

as 50×10<sup>6</sup> seconds. However, it is possible to achieve longer lifetime (>100×10<sup>6</sup> seconds) by adopting the longer channel length for the tail transistor. Therefore, the proposed design technique mitigates the degraded performance and increases both the LNA and N-type LC oscillator's lifetimes.

Figure 2.11. Lifetime Enhancement of LNA Due to HCI Effects.

Figure 2.12. Lifetime Enhancement of (a) N-type and (b) P-type LC Oscillators.

While designing a P-type LC oscillator to reduce the NBTI effect, it is required to consider the bias condition of critical device which is a tail transistor in the P-type LC oscillator. Contrary to HCI, NBTI is relatively independent of the channel length of device. Because the higher vertical electric field across the gate oxide results in the NBTI effect of the pMOSFET, one can select a lower tail transistor gate bias voltage to reduce the degradation in threshold voltage shift. By decreasing the gate bias voltage and increasing the tail transistor's device width, the RF performance remains the same as the original circuit. The source-drain voltage and transconductance of the pMOS tail

transistor are chosen to have similar values to the original circuit so that the phase noise and output amplitude of the redesigned circuit are comparable with the original circuit.

The performance degradation and lifetime limitation of RF circuits due to EM are mainly due to current stress. To increase the lifetime of degraded circuits, the current density through the critical component should be decreased. Decreasing actual current would affect other circuit performance parameters. Therefore, a layout improvement technique that increases the metal line width(s) to decrease current density is proposed for mitigation of the EM effect. As presented in previous section, the critical EM components in the cascode LNA are the drain inductors  $L_d$ . For inductors, increasing the line width has two effects. First, it decreases the initial baseline resistance, making the initial point lower. Second, it decreases the rate of the resistance degradation. By increasing the width of  $L_d$ , lifetime can be increased. The total resistance  $R_d$  at the drain side with a wider width of  $L_d$  will have less series resistance compared with the original design at a certain stress time. Although a decrease in resistance is achieved by the increase in total area, a decreased resistance of the inductor can improve RF performance and extend the LNA lifetime. An area penalty exists, but this technique is better than blindly resizing all components. From Fig. 2.9 (b), modifying the critical device within layout increases the circuit lifetime by 100%, from 30×10<sup>6</sup> to 60×10<sup>6</sup> s. Table 2.1 shows circuit specifications such as power, area, and lifetime when redesign technique is used. Compared with the results of redesign layout technique without hotspot identification, which means all circuit components are resized blindly, it should be noted that focusing the layout technique on the critical device identified through hotspot analysis enhances lifetime without a large area penalty.

| Aging effects                 | HCI in n-type OSC |               |                | NBTI in p-type OSC |               |                |

|-------------------------------|-------------------|---------------|----------------|--------------------|---------------|----------------|

| Redesign technique            | Initial<br>Design | w/<br>hotspot | w/o<br>hotspot | Initial design     | w/<br>hotspot | w/o<br>hotspot |

| Power (mW)                    | 4.89              | 5.08          | 5.13           | 5.07               | 5.23          | 5.3            |

| Area (×μm²)                   | 112500            | 113600        | 114000         | 111500             | 113300        | 113800         |

| Lifetime ( $\times 10^6$ s)   | 50                | >100          | >100           | 70                 | >100          | >100           |

|                               |                   |               |                |                    |               |                |

| Aging effects                 | HCI in LNA        |               |                | EM in LNA          |               |                |

| Redesign technique            | Initial<br>design | w/<br>hotspot | w/o<br>hotspot | Initial design     | w/<br>hotspot | w/o<br>hotspot |

| Power (mW)                    | 8.50              | 8.81          | 8.9            | 8.48               | 8.51          | 8.53           |

| Area (×µm²)                   | 216400            | 218100        | 218800         | 216500             | 233000        | 242000         |

| Lifetime (×10 <sup>6</sup> s) | 15                | 35            | 35             | 30                 | 60            | 60             |

**Table 2.1.** Comparison of Circuit Specifications for Aging Effects.

## 2.6. Conclusion

In this chapter, a methodology to analyze the performance of RF circuits degraded by aging mechanisms, such as HCI, NBTI and EM is presented. The proposed method is focused on finding the device that is most critical for circuit performance degradation. Once the critical device of RF circuits is determined, remedial action can be taken to mitigate the circuit performance degradations. It shows the demonstration of the proposed technique on an LNA and two LC oscillators as case studies. Experimental results show that the degradation performance and the lifetime were enhanced by increasing the critical transistor size or widening the inductor line. The methodology should be applied to the particular design at hand to fully gauge the impact of aging effects.

#### CHAPTER 3

# MONITOR-BASE IN-FIELD WEAROUT MITIGATION FOR CMOS LC OSCILLATOR

In this chapter, a comprehensive systemic methodology for co-designing CMOS LC oscillators together with monitoring and reconfiguration mechanisms is proposed to enable aging mitigation with minimal performance and area overheads. Specifically, the contributions in this work are as follows:

- (1) Analysis of hotspot identification in CMOS LC oscillator

- (2) Analysis of a method for determining low impact reconfiguration mechanism

- (3) An algorithm for determining recovery trigger conditions in the field

- (4) Low cost on-chip measurement of monitoring voltage

- (5) Detailed analysis of area overhead of the entire monitoring / recovery circuits

- (6) Manufactured CMOS LC oscillator in 180nm IBM process with monitoring mechanism, accelerated aging experiments, and results on aging and recovery.

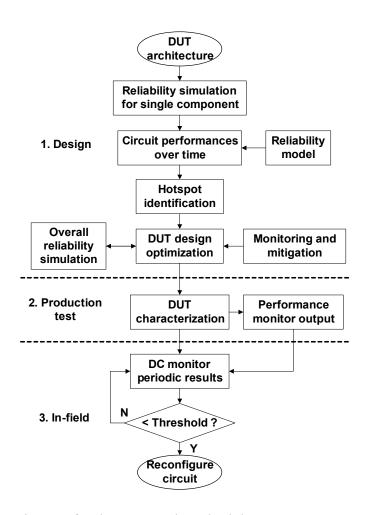

#### 3.1. In-field Detection and Recovery Scheme

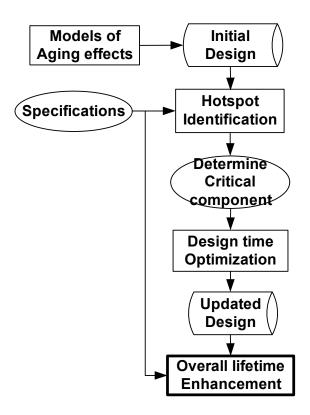

Fig. 3.1 shows the overview of the proposed methodology. At design time, given the DUT (Design under Test) architecture and initial design point, reliability simulations are conducted to obtain circuit performance profiles over time by aging one device at a time. While the predicted lifetime will not be accurate, this analysis will help to identify reliability hotspots to effectively monitor device performance. Appropriate monitor

location as well as the reconfiguration mechanisms are included in the design and the DUT is co-optimized with these monitoring and recalibration hooks.

Fabricated devices will be characterized during production test along with the monitor output. Specification margin of each manufactured circuit will be different due to process variations. This margin is used to determine the allowable degradation and thus the threshold to initiate reconfiguration.

Once the device is deployed in the field, the monitor response will be periodically evaluated and circuit will be reconfigured if necessary.

**Figure 3.1.** Flow Diagram for the Proposed Methodology.

# 3.1.1. Hotspot Identification

The first step is to analyze the reliability of the circuit and determine the hotspots, such as the transistors or components that are predicted to cause parametric failures.

The analytical degradation model of each MOSFET is used to extrapolate the degradation of its parameters (e.g. threshold voltage) during operation time (e.g. years) based on nominal stress conditions that is obtained from the circuit simulator. Circuit performance is re-evaluated at each time point. The extrapolated device parameters are used to modify the parameters in the degradation model and the circuit is re-simulated to obtain the updated stress conditions. Hence, the performance of the circuit gradually shifts in time. This information combined with the circuit specifications yields a certain time point at which the specification will fail. This time point is chosen as the failure time of the circuit. Due to different sizes and operating points, the degradation patterns will be different for each circuit component. Thus, each circuit component will cause a distinct failure time for each circuit performance over stress time. The process iteratively go through each circuit component and track the degradation profile of the each circuit parameter. Once all the degradation patterns are analyzed, it is possible to determine the most vulnerable component to aging effects. This process called hotspot identification, concentrates on each circuit component and identifies the circuit component that causes a specification failure at the earliest time [45]. Note that this is not necessarily the lifetime of the circuit. The actual failure time (lifetime) of the circuit will differ from the failure time determined by hotspot identification since all circuit components age at the same time, albeit at a differing rate.

# 3.1.2. Monitoring Scheme

A second step in the proposed method is to add a simple monitoring circuit to detect performance degradation. In order to enable the proposed recovery, a monitoring mechanism is required to detect performance degradation. For LC oscillators, phase noise is the most stringent performance parameter and it is the one that fails first under stress [14]. However, direct on-chip measurement of phase noise is not feasible. Hence, it is necessary to identify a circuit parameter, preferably in the low frequency domain, that is most correlated to phase noise. In the next section, the proposed methodology is applied to two designed LC oscillators and determine how this monitoring can be enabled with low impact and high accuracy.

# 3.1.3. Reconfiguration Scheme

A third step is to improve the predicted circuit lifetime (for most devices) by redesigning the circuit. In other words, if the projected lifetime is not satisfactory, the

lifetime-limiting component is adjusted by changing the transistor sizes and re-designing

the entire circuit around the new sizes. It should be noted that this enhancement strategy

is not always feasible, especially when frequency domain operation is taken into account.

This design-time reliability enhancement strategy is common to most procedures in the

literature [26], [34]. It is observed that even when design-time enhancements are

employed, degradation is unavoidable and cannot be easily predicted at production time.

In order to mitigate the effects of aging, additional circuit components are included.

Finally, a recovery strategy that includes spare transistors is employed to replace the

transistor that is identified as the hotspot.

# 3.2. Case Study of PMOS and NMOS Oscillator

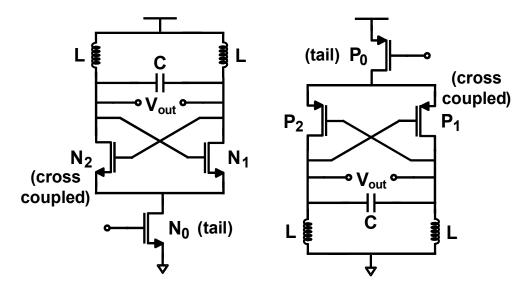

CMOS LC oscillators are widely used in high performance PLLs and frequency synthesizers due to their relatively good phase noise and ease of design. As shown in Fig. 3.2, there are two kinds of oscillators (N-type and P-type) for case studies. The fundamental of tail current due to filtering in LC tank creates differential output voltage of across the tank as in Eqn. (3.1) [46].

$$V_{out} = \frac{4}{\pi} I_{tail} R_{eq} \tag{3.1}$$

where  $R_{eq}$  is the equivalent resistance of the tank. The phase noise of an LC oscillator at an offset frequency  $\omega_m$  from the frequency of oscillation  $\omega_0$  normalized with respect to the carrier is given by Eqn. (3.2) and (3.3) [46], [47].

$$L(\omega_m) = 10 \log \left[ \frac{4kTFR_{eq}}{V_{out}^2} \left( \frac{\omega_0}{2Q\omega_m} \right)^2 \right]$$

(3.2)

$$F = 2 + \frac{8\gamma R_{eq} I_{tail}}{\pi V_{out}} + \frac{8}{9} \gamma g_{m_{tail}} R_{eq}$$

(3.3)

where F denotes the noise factor,  $\gamma$  is the noise factor of a single transistor. The value of  $\gamma$  is 2/3 for long-channel transistors and may rise to between 2 and 3 in short-channel devices.  $V_{out}$  is the output amplitude of the differential oscillator output, and  $g_{m\_tail}$  is the transconductance of the tail transistor, and Q is the quality factor of the tank inductor and capacitors.

**Figure 3.2.** N-type and P-type LC oscillator.

# 3.2.1. Reliability Analysis and Hotspot Identification of LC Oscillator

Fig. 3.3 shows the proposed method for reliability analysis of the LC oscillator. The most common reliability issues of HCI and NBTI are analyzed for the effects on CMOS LC oscillators.

HCI and NBTI cause degradation in the threshold voltage for N- and P-type devices, respectively. Considering these effects, threshold voltage shifts are modeled according to [10]. Since these shifts are dependent on operating conditions, they are changed at each time step for the simulation. As shown in Eqn. (3.3), there are three terms in the noise factor F. The first term which ends up being a constant, shows the noise generated in the resonator, which has insignificant impact on the reliability analysis since it is composed of passive devices. The second and third terms are from the noise generated by the cross-coupled transistors and the noise generated by the tail transistors, respectively. Therefore,

in order to perform the reliability analysis with respect to the phase noise of LC oscillator, it is imperative to focus on those transistors, which may degrade due to aging.

Figure 3.3. Reliability Analysis of LC Oscillator.

# 3.2.1.1. Reliability Analysis of Cross-coupled Transistors of LC Oscillator

Fig. 3.4 shows reliability simulation results in terms of phase noise and output amplitude of one random N-type and P-type LC oscillator instance from Monte Carlo simulations. Statistical simulations within 10% variation from nominal values are used to explore not only the effects of process variation and mismatch, but the aging parameters between cross-coupled transistors.

**Figure 3.4.** Simulation of Phase Noise Degradation Due to Cross-coupled Transistors of (a) N-type and (b) P-type Oscillator under Nominal Stress Conditions.

In both LC oscillator circuits, cross-coupled transistors experience AC stress while the tail transistor is under DC stress. Because of the large voltage swing up to  $2V_{dd}$  across the cross-coupled transistors, the total stress on these transistors will be higher than the tail transistor and they will experience faster degradation compared to the tail transistor. While the cross-coupled transistors undergo high stress conditions, it is observed that the degradation in cross-coupled transistors with the mismatch effects does not cause a significant degradation in the overall phase noise performance. This result may be at first counter-intuitive. However, it can be explained with the phase noise model by substituting Eqn. (3.1) in Eqn. (3.2) and (3.3).

$$L(\omega_{m}) = 10 \log \left[ \frac{4kTR_{eq}(2 + 2\gamma + \frac{8}{9}\gamma D_{n}\sqrt{I_{tail}}R_{eq})}{(\frac{4}{\pi}I_{tail}R_{eq})^{2}} \left( \frac{\omega_{0}}{2Q\omega_{m}} \right)^{2} \right]$$

(3.4)

$$F = 2 + 2\gamma + \frac{8}{9}\gamma D_n \sqrt{I_{tail}} R_{eq}$$

(3.5)

where  $D_n$  is  $\sqrt{2\mu_n C_{ox}(W/L)}$ . From Eqn. (3.4),  $L(\omega_m)$  can be written to display dependence on  $I_{tail}$  and  $R_{eq}$ , which are separately affected by the tail transistor, and by the cross-coupled transistors. It is shown that the phase noise is primary determined by the tail current  $I_{tail}$ . The  $g_m$  of the cross-coupled transistors plays a role in determining the equivalent resistance, hence only the oscillation condition ( $R_{eq} \ge 1/g_{m\_cross}$ ). Therefore, a change in the threshold voltage of cross-coupled transistors does not cause significant degradation in the phase noise of the oscillator, unless it alters the bias conditions so significantly that the circuit diverts from the desired oscillation condition. It is shown later with simulation results that phase noise is insensitive even to large degradations of cross-coupled transistors. Moreover, thanks to the recovery phase of the NBTI which is a unique feature for PMOS aging effect, the degradations on cross-coupled transistors in the P-type oscillator are less compared to those in the N-type oscillator.

# 3.2.1.2. Reliability Analysis of Tail Transistor of LC Oscillator

Degradation of the tail transistor due to the increase in threshold voltage causes a decrease in both the tail current and the transconductance, which are dominant parameters in the phase noise model. Moreover, Eqn. (3.1) indicates that the output amplitude of the differential oscillator is directly proportional to the tail current. Hence, the performance of the tail transistor significantly affects the overall performance. This analysis assumes that the tail current is voltage biased such that a shift in the transistor threshold voltage results in a shift in the tail current. However, most design techniques use a separate bias block and mirror the current to various locations in the circuit. Hence, it is required to take this current mirror into account. If the bias circuit transistors and the

tail transistor undergo identical stress conditions, and possess identical process and degradation parameters, the tail current will not be changed, hence there will be no degradation. However, this is typically not the case, since the bias block is designed with many circuit blocks in mind and generally uses larger transistors. Large transistors are not preferable for oscillators since they degrade circuit performance and cause increased thermal noise. Moreover, mismatch between the bias circuit transistors and the tail transistor will still cause significant change in the threshold voltage. This intuitive analysis is confirmed with reliability simulations under various biasing design conditions.

**Figure 3.5.** Reliability Analysis of a Tail Transistor with Different Bias Designs.

The different biasing designs are shown given in Fig. 3.5, where a) tail only refers to voltage biasing technique, b) mirror without mismatch refers to current mirror biasing where bias transistors and the tail transistor are assumed identical in every respect (which is not realistic but is included as a point of comparison), and c) mirror with mismatch refers to current mirror biasing where transistors have mismatch effects in terms of their design, process, and degradation parameters. In general, because these transistors undergo similar stress patterns in DC domain, and due to the layout proximity, it is hard to expect big variations in circuit performances. However, there is still some mismatch in

aging parameters. In Fig. 3.6, one N- and P- type LC oscillator instance with different biasing designs is selected from Monte Carlo samples and simulated for phase noise performance. Especially, in the design c), 10% variation from nominal values are used for process variation and mismatch effects in Monte Carlo simulation. Fig. 3.6 shows the simulation results for the worst case of corner when matched transistors are at opposing mismatch corners. The simulation results show that unless a precise matching in the bias conditions is assured, degradation in the tail transistor will cause a significant degradation in the overall performance within the first few years of the operation under nominal stress conditions. Fig. 3.6 also shows that N-type and P-type oscillators have a similar degradation pattern even if the aging mechanisms and degradation profiles are different. Therefore, it is certain that phase noise degradation is primarily due to the aging of the tail transistor for both N-type and P-type oscillators.

**Figure 3.6.** Phase Noise Degradation Due to Tail Transistors with Different Biasing Techniques in (a) N-type and (b) P-type Oscillator.

#### 3.2.1.3. Hotspot Identification of LC Oscillator

For hotspot identification, each transistor is aged separately, and monitor the circuit response, both in terms of performance and in terms of additional parameters that can be monitored. First, the threshold voltage shift model of the tail transistor is adopted to analyze the performance with gradually increased stress time. Since tail transistor and cross-coupled transistors are biased with different DC bias conditions, they experience different amounts of degradation in threshold voltage, which are identified and applied to

the circuit. The overdrive voltage at the tail transistor is usually kept low to allow a higher output swing. Thus, the transistors at the cross-coupled pair experience a DC bias voltage of  $V_{ds} = V_{gs} \approx V_{dd}$ .

The results of this analysis for the N-type oscillator are given in Fig. 3.7 (a). Although the degradation in cross-coupled transistors is higher than the degradation in the tail transistor, the degradation of the overall performance in terms of phase noise is significantly higher for the tail transistor,  $N_0$ . Hotspot identification process shows similar results from reliability analysis mentioned in previous section. In other words, it is clearly noted that the aging of cross-coupled pair has no visible effect on the phase noise of oscillator even if there are process variation or mismatch effects in these transistors. Contrary to cross-coupled transistors, aging of tail transistor causes an increase in phase noise and decrease in oscillation amplitude.

The same simulation process is examined for a P-type LC oscillator. The degradation model of NBTI effect is used to demonstrate the threshold voltage shift under the nominal stress conditions (10 years stress time). The results are similar to the N-type LC oscillator. Fig. 3.7 (b) represents the hotspot identification results for a P-type oscillator. As mentioned earlier, the cross-coupled transistors will introduce less degradation effects on the performance than the tail transistor because of the recovery phase in the cross-coupled transistors. Therefore, it is clear that the tail transistor of the P-type LC oscillator is determined as a critical device which causes significant degradation due to NBTI.

Figure 3.7. Hotspot Identification for (a) N-type and (b) P-type Oscillators.

#### 3.2.2. Performance Monitoring

Since it is impossible to directly measure a phase noise on-chip with reasonable overhead, an alternative parameter that is easy to measure needs to be determined. Reliability analysis of LC oscillator has identified that the reduction in oscillation amplitude is primarily due to aging and is strongly correlated to aging based degradation. For the monitoring purpose, a peak detector circuit can be employed to measure the output amplitude for this purpose. Another alternative is to attempt to measure the tail current directly. A mirror-based approach cannot be used since the mismatch in the

mirror will eventually lead to inaccurate results. However, a sense resistor can be inserted into the current path for the monitoring purpose. Both options are implemented and shows that using the sense resistor leads to more reliable results and low impact in terms of performance. Since the tail current has a strong correlation with output amplitude and phase noise of the oscillators shown in Eqn. (3.1) and (3.2), it can be used as a low frequency alternative to monitor the degradation.

There are two possible locations for inserting the resistor, at the tail transistor side and at the LC tank side. For the N-type LC oscillator, inserting the sense resistor at the tail end will increase the source voltage of the tail transistor, causing a small difference between the source and the body voltage. Thus, this will cause inaccuracy in the measurement of the tail current. The second location of inserting the resistor is between the LC tank and the supply voltage/gnd. This location has a very small effect on the performance of the oscillator. The presence of the resistor connected with LC tank can cause a shift in the oscillation frequency. Moreover, adding sense resistor in series with the spiral inductor L can increase inductor loss. However, it is possible to reduce or completely eliminate these effects by taking this resistor into account at design time and co-designing the primary circuit with the monitoring circuit. If the value of the resistor is kept much smaller than the inverse of the transconductance, the noise from the sense resistor is negligible compared to the noise generated by the transistor. Therefore, it shows that the sense resistor has negligible effect on the overall performance at design time. The phase noise simulation in the presence and absence of the resistor is presented in Fig. 3.8.

**Figure 3.8.** Phase Noise Degradation of (a) N-type and (b) P-type Oscillator with and without the Sensing Resistor.

On-chip sense resistor must be kept small to avoid significant voltage drop. Measuring a small deviation around a large DC value using traditional ADC architecture is challenging. However, a VCO-based ADC is suitable for the monitoring the small voltage from the sense resistor since it provides adequate resolution around a fixed point at very compact area [48]. A VCO-based ADC with 7 inverter stages is used for the measurement of the voltage across the sense resistor. This ADC has been shown to provide  $50\mu V$  resolution for a 200 mV range [48].

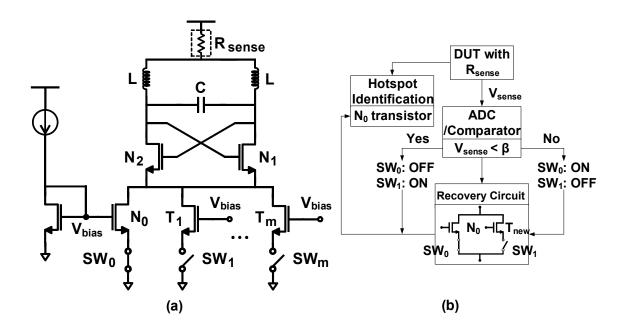

## 3.2.3. Reconfiguration Hardware

In order to recover the degraded performance of aged oscillator, mitigation circuit consists of fresh transistors and digitally controlled MOS switches which can replace the aged transistor. Since the tail transistor is identified as the reliability hotspot, this aged tail device will be substituted with the fresh devices when the voltage across the sense