High Gain DC-DC and Active Power Decoupling Techniques for Photovoltaic

Inverters

by

Jinia Roy

A Dissertation Presented in Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy

Approved November 2017 by the Graduate Supervisory Committee:

Raja Ayyanar, Chair George Karady Jiangchao Qin Qin Lei

ARIZONA STATE UNIVERSITY

December 2017

#### ABSTRACT

The dissertation encompasses the transformer-less single phase PV inverters for both the string and microinverter applications. Two of the major challenge with such inverters include the presence of high-frequency common mode leakage current and double line frequency power decoupling with reliable capacitors without compromising converter power density. Two solutions are presented in this dissertation: half-bridge voltage swing (HBVS) and dynamic dc link (DDCL) inverters both of which completely eliminates the ground current through topological improvement. In addition, through active power decoupling technique, the capacitance requirement is reduced for both, thus achieving an all film-capacitor based solution with higher reliability. Also both the approaches are capable of supporting a wide range of power factor.

Moreover, wide band-gap devices (both SiC and GaN) are used for implementing their hardware prototypes. It enables the switching frequency to be high without compromising on the converter efficiency. Also it allows a reduced magnetic component size, further enabling a high power density solution, with power density far beyond the state-of-the art solutions.

Additionally, for the transformer-less microinverter application, another challenge is to achieve a very high gain DC-DC stage with a simultaneous high conversion efficiency. An extended duty ratio (EDR) boost converter which is a hybrid of switched capacitors and interleaved inductor technique, has been implemented for this purpose. It offers higher converter efficiency as most of the switches encounter lower voltage stress directly impacting switching loss; the input current being shared among all the interleaved converters (inherent sharing only in a limited duty ratio), the inductor conduction loss is reduced by a factor of the number of phases.

Further, the EDR boost converter has been studied for both discontinuous conduc-

tion mode (DCM) operations and operations with wide input/output voltage range in continuous conduction mode (CCM). A current sharing between its interleaved input phases is studied in detail to show that inherent sharing is possible for only in a limited duty ratio span, and modification of the duty ratio scheme is proposed to ensure equal current sharing over all the operating range for 3 phase EDR boost. All the analysis are validated with experimental results. ...to my daughter, Anika

#### ACKNOWLEDGMENTS

The work outlined in this dissertation could never have been possible without the constant help, support, and encouragement of several people who I wish to acknowledge. First and foremost, I would like to express my sincere gratitude to my adviser, Dr. Raja Ayyanar for giving me an opportunity to work at the Power Electronics Lab at ASU, and for fostering a research environment that encouraged ideas, accommodated criticism, over-came failure, and celebrated success. I am also extremely grateful to my committee members Dr. George Karady, Dr. Jiangchao Qin, and Dr. Qin Lei for their valuable time.

I would like to thank my colleagues Siddharth, Xia, Pavan, Tong, Ziwei, Scott, Chenhao, Nikhil, Arkanath, and Ramnathan with whom I have had the opportunity to work and discuss research problems and have enjoyed their company inside the lab.

I would like to express my sincere gratitude to my parents Paresh Nath Roy and Ramala Roy, sister Runia Roy, and my husband Tanmoy Chatterjee for always being there for me during the highs and lows of life and being the source of my inspiration and motivation. The last phase of PhD was a wonderful experience with my four months old daughter Anika who was born on 11th of July, 2017 and I would like to express my appreciation to my parents and in-laws for their help in taking care of my little one. Above all, I thank The Almighty for having bestowed upon me His blessings.

Finally I also wish to thank the Office of Energy Efficiency and Renewable Energy (EERE), U.S. Department of Energy, under Award Number DE-EE0006521 with North Carolina State University, PowerAmerica Institute that has funded my research.

| TABLE OF | CONTENTS |

|----------|----------|

|----------|----------|

|        |      | $\operatorname{Pag}$                           | çe |

|--------|------|------------------------------------------------|----|

| LIST C | )F Т | TABLES i                                       | x  |

| LIST C | )FF  | FIGURES                                        | х  |

| CHAP   | ГER  | R                                              |    |

| 1 ]    | INT  | RODUCTION                                      | 1  |

|        | 1.1  | PV Inverter                                    | 1  |

|        |      | 1.1.1 Central Inverter                         | 1  |

|        |      | 1.1.2 String Inverter                          | 2  |

|        |      | 1.1.3 Microinverter                            | 3  |

|        | 1.2  | Transformer-less Single Phase PV Inverter      | 5  |

|        |      | 1.2.1 Challenge I: Capacitive Ground Current   | 6  |

|        |      | 1.2.2 Challenge II: Power Decoupling           | 6  |

|        |      | 1.2.3 Challenge III: High Volatage Gain        | 8  |

| -      | 1.3  | High Gain Transformer-less DC-DC Boost Stage   | 9  |

| -      | 1.4  | Objectives and New Contributions of the Work 1 | 1  |

| -      | 1.5  | Chapter Overview 1                             | 5  |

| 2 ]    | ЕХЛ  | TENDED DUTY RATIO BOOST CONVERTER 1            | 7  |

| 2      | 2.1  | Introduction 1                                 | 7  |

| 2      | 2.2  | <i>M</i> -Phase EDR Boost Converter            | 8  |

| 2      | 2.3  | Operating Principles 2                         | 20 |

|        |      | 2.3.1 Zone I                                   | 1  |

|        |      | 2.3.2 Zone II                                  | 24 |

|        |      | 2.3.3 Zone III                                 | 5  |

| 2      | 2.4  | Current Sharing 2                              | 26 |

|        |      | 2.4.1 Zone II                                  | 26 |

|   |     | 2.4.2  | Zone III                                          | 30 |

|---|-----|--------|---------------------------------------------------|----|

|   |     | 2.4.3  | Implementation                                    | 35 |

|   | 2.5 | Discor | tinuous Conduction Mode                           | 36 |

|   | 2.6 | Exper  | imental Results                                   | 36 |

|   |     | 2.6.1  | Hardware Prototype                                | 36 |

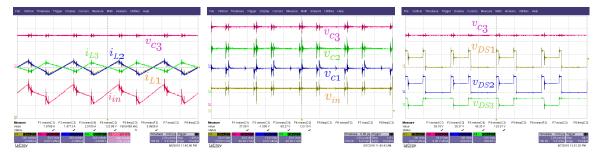

|   |     | 2.6.2  | Converter Operation Without Duty Ratio Adjustment | 37 |

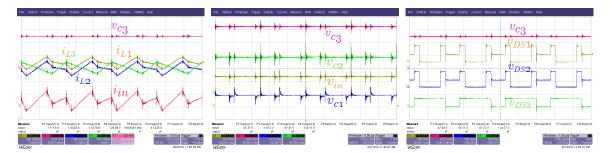

|   |     | 2.6.3  | Converter Operation With Duty Ratio Adjustment    | 39 |

|   | 2.7 | Conclu | ision                                             | 42 |

| 3 | DIS | CONTI  | NUOUS CONDUCTION MODE OPERATION OF EDR BOOS       | ST |

|   | CON | IVERT  | ER                                                | 48 |

|   | 3.1 | Introd | uction                                            | 48 |

|   | 3.2 | Opera  | ting Principles                                   | 48 |

|   |     | 3.2.1  | Zone I Operation                                  | 49 |

|   |     | 3.2.2  | Zone II Operation                                 | 51 |

|   | 3.3 | Zone I | II Operation                                      | 51 |

|   |     | 3.3.1  | Case I                                            | 51 |

|   |     | 3.3.2  | Case II                                           | 54 |

|   |     | 3.3.3  | Case III                                          | 56 |

|   | 3.4 | Simula | ation and Experimental Results                    | 58 |

|   |     | 3.4.1  | Hardware Prototype                                | 58 |

|   |     | 3.4.2  | Experimental Results                              | 59 |

|   | 3.5 | Conclu | usion                                             | 62 |

| 4 | HAI | LF BRI | DGE VOLTAGE SWING INVERTER                        | 67 |

|   | 4.1 | Introd | uction                                            | 67 |

|   | 4.2 | Circui  | t Configuration                             | 68 |

|---|-----|---------|---------------------------------------------|----|

|   |     | 4.2.1   | Power Decoupling                            | 69 |

|   | 4.3 | Capac   | itance Optimization and Operation           | 72 |

|   |     | 4.3.1   | Case Studies                                | 72 |

|   |     | 4.3.2   | Optimization Problem                        | 75 |

|   |     | 4.3.3   | Pulsating Power Elimination                 | 77 |

|   |     | 4.3.4   | Operating Principles                        | 78 |

|   | 4.4 | Integra | ated Magnetics                              | 79 |

|   |     | 4.4.1   | Magnetic Circuit Analysis                   | 81 |

|   |     | 4.4.2   | Finite Element Analysis                     | 81 |

|   |     | 4.4.3   | Simulation Results                          | 82 |

|   | 4.5 | Efficie | ncy Optimization                            | 83 |

|   |     | 4.5.1   | Minimum DC-Link Average Voltage Requirement | 85 |

|   |     | 4.5.2   | Adaptive DC-Link Scheme                     | 86 |

|   | 4.6 | Contro  | oller Implementation                        | 87 |

|   |     | 4.6.1   | Controllers                                 | 87 |

|   |     | 4.6.2   | ADCL Calculation Block                      | 89 |

|   | 4.7 | Hardw   | vare Prototype and Experimental Results     | 91 |

|   |     | 4.7.1   | Hardware Prototype                          | 91 |

|   |     | 4.7.2   | Steady State Experimental Results           | 91 |

|   |     | 4.7.3   | ADCL Waveforms                              | 94 |

|   |     | 4.7.4   | Efficiency                                  | 95 |

|   | 4.8 | Conclu  | ision                                       | 96 |

| 5 | DOU | JBLY (  | GROUNDED DYNAMIC DC-LINK (DDCL) INVERTER    | 97 |

## CHAPTER

|      | 5.1  | Introd | uction                                            |

|------|------|--------|---------------------------------------------------|

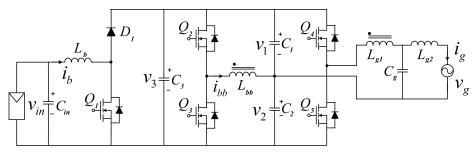

|      | 5.2  | Opera  | ting Principles                                   |

|      | 5.3  | Capac  | itance Optimization                               |

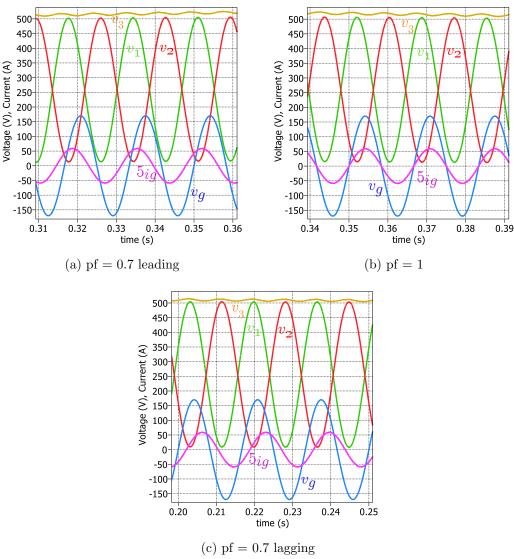

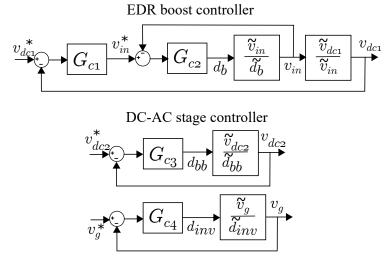

|      | 5.4  | Contro | oller Design and Simulation Results               |

|      |      | 5.4.1  | Controller Design                                 |

|      |      | 5.4.2  | Simulation Results                                |

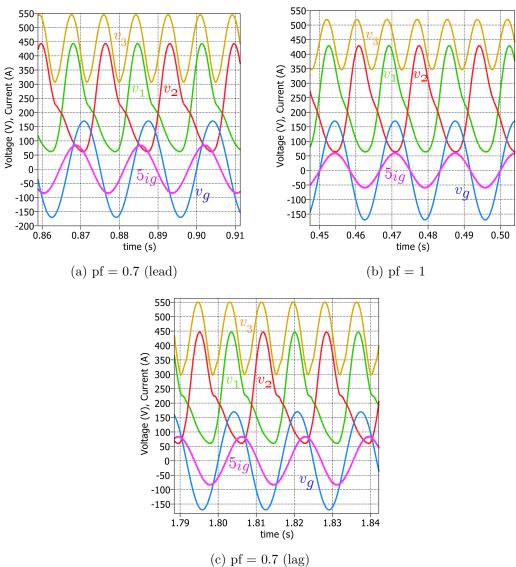

|      | 5.5  | Hardw  | vare Implementation and Experimental Results      |

|      |      | 5.5.1  | Component Selection and Hardware Prototype 104    |

|      |      | 5.5.2  | Switching Level Experimental Results              |

|      |      | 5.5.3  | Steady State and Dynamic Experimental Results 106 |

|      |      | 5.5.4  | Efficiency                                        |

|      | 5.6  | Conclu | usion                                             |

| 6    | CON  | ICLUS  | ION AND FUTURE WORK                               |

|      | 6.1  | Conclu | 112 usion                                         |

|      | 6.2  | Future | e Work                                            |

| REFE | EREN | CES    |                                                   |

## LIST OF TABLES

| Table | Page                                                              |

|-------|-------------------------------------------------------------------|

| 2.1   | Zone I $(2/3 \le D \le 1)$ Operating Modes                        |

| 2.2   | Zone II $(1/3 \le D < 2/3)$ Operating Modes                       |

| 2.3   | Zone III $(0 \le D < 1/3)$ Operating Modes                        |

| 2.4   | Gain Summary                                                      |

| 2.5   | Converter Specification                                           |

| 2.6   | Component Details                                                 |

| 3.1   | Computing Operating Interval for Case I Operation in Zone III 54  |

| 3.2   | Computing Operating Interval for Case II Operation in Zone III 57 |

| 3.3   | Converter Specification                                           |

| 3.4   | Component Details 58                                              |

| 3.5   | Zone III $(2/3 \le D \le 1)$ Case I                               |

| 3.6   | Zone III $(2/3 \le D \le 1)$ Case I (Contd)                       |

| 3.7   | Zone III $(2/3 \le D \le 1)$ Case II                              |

| 3.8   | Zone III $(2/3 \le D \le 1)$ Case II (Contd)                      |

| 4.1   | Converter Specification                                           |

| 4.2   | Component Details                                                 |

| 5.1   | Converter Specification                                           |

| 5.2   | Component Details                                                 |

| 5.3   | Performance Comparisons with Various Other Topologies             |

| LIST | OF | FIG | URES |

|------|----|-----|------|

|      |    |     |      |

| Figure | Р                                                                        | age |

|--------|--------------------------------------------------------------------------|-----|

| 1.1    | Central Inverter System                                                  | 2   |

| 1.2    | String Inverter System                                                   | 3   |

| 1.3    | Microinverter System.                                                    | 4   |

| 1.4    | Power Decoupling Concept                                                 | 7   |

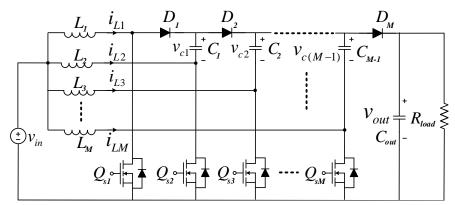

| 2.1    | Topology for <i>M</i> -Phase Extended Duty Ratio (EDR) Boost             | 18  |

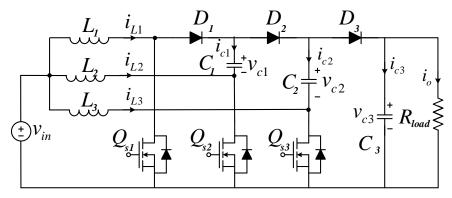

| 2.2    | Topology for 3-Phase EDR Boost                                           | 20  |

| 2.3    | Current Path Corresponding to Each of the Operating Intervals/Modes      |     |

|        | for 3-Phase EDR Boost.                                                   | 22  |

| 2.4    | Gate Signal, Inductor Current, and Device Voltage at Three Operating     |     |

|        | Zones for 3-Phase EDR Boost.                                             | 23  |

| 2.5    | Adjusted Duty Ratio for Three Phases to Balance Current in Zone II       |     |

|        | Operating Region for 3-Phase EDR Boost                                   | 27  |

| 2.6    | Adjusted Duty Ratio of Three Phases to Reduce the RMS Current            |     |

|        | Error in Zone III (Case 1) Operating Region for 3-Phase EDR Boost        |     |

|        | with $1 \le k_{III} \le 3$                                               | 32  |

| 2.7    | Modified Duty Ratio of Three Phases Ensuring Equal Current Sharing       |     |

|        | in Zone III (Case 2) for 3-Phase EDR Boost with $3 \le k_{III} \le 3.94$ | 34  |

| 2.8    | Implementation Flow Diagram of Current Sharing with Modified Duty        |     |

|        | Ratio for 3-Phase EDR Boost.                                             | 35  |

| 2.9    | Experimental Prototype for 3-Phase EDR Boost                             | 37  |

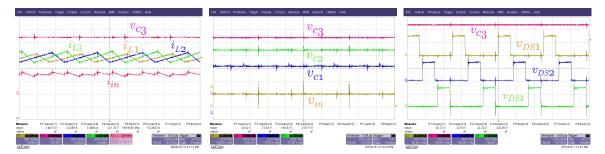

| 2.10   | Waveforms for Zone I 3-Phase EDR Boost with $D_1=D_2=D_3=0.73$ .         | 38  |

| 2.11   | Waveforms for Zone II 3-Phase EDR Boost with $D_1 = D_2 = D_3 = 0.55$    | 39  |

| 2.12   | Waveforms for Zone III 3-Phase EDR Boost with $D_1 = D_2 = D_3 = 0.27$   | 39  |

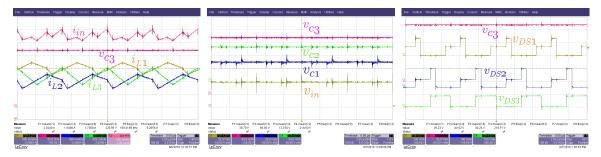

| 2.13 | Waveforms with Modified Duty Ratio Scheme for Zone II 3-Phase EDR        |    |

|------|--------------------------------------------------------------------------|----|

|      | Boost with Symmetric PWM                                                 | 40 |

| 2.14 | Waveforms with Modified Duty Ratio Scheme for Zone III (Modified         |    |

|      | D-Higher Gain)                                                           | 40 |

| 2.15 | Waveforms with Modified Duty Ratio Scheme for Zone III (Modified         |    |

|      | D-Lower Gain)                                                            | 41 |

| 3.1  | Topology for 3-Phase Extended Duty Ratio (EDR) Boost Converter. $\ldots$ | 49 |

| 3.2  | Gate Signal, Inductor current, and Device Voltages for DCM Operation     |    |

|      | in Zone I for 3-Phase EDR Boost                                          | 50 |

| 3.3  | Gate Signal, Inductor Current, and Device Voltages for DCM Opera-        |    |

|      | tion in Zone III, Case I for 3-Phase EDR Boost                           | 52 |

| 3.4  | Gate Signal, Inductor Current, and Device Voltages for DCM Opera-        |    |

|      | tion in Zone III, Case II for 3-Phase EDR Boost                          | 55 |

| 3.5  | Experimental Prototype for 3-Phase EDR Boost                             | 58 |

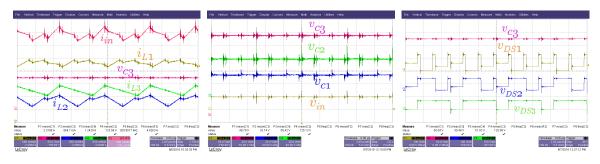

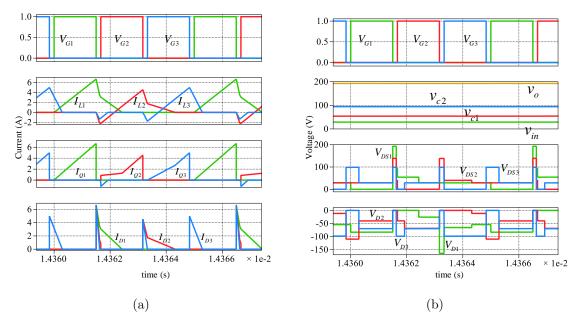

| 3.6  | Waveforms for DCM Operation of 3-Phase EDR Boost for (a) Zone I,         |    |

|      | (b) Zone II                                                              | 59 |

| 3.7  | Waveforms for Zone III 3-Phase EDR Boost for (a) Case I, (b) Case II.    | 60 |

| 3.8  | PLECS Simulation Waveforms for Case I of Zone III 3-Phase EDR            |    |

|      | Boost.                                                                   | 61 |

| 3.9  | PLECS Simulation Waveforms for Case II of Zone III 3-Phase EDR           |    |

|      | Boost.                                                                   | 61 |

| 4.1  | Proposed Half Bridge Voltage Swing (HBVS) Inverter for Transformer-      |    |

|      | less PV Application.                                                     | 68 |

# Figure

| 4.2  | Analytic Plots for Operating Condition Corresponding to $V_g = 120$ V,                               |    |

|------|------------------------------------------------------------------------------------------------------|----|

|      | $P = 1 \text{ kW}, v_3 = 530, A 250, C = 43 \ \mu\text{F}$                                           | 70 |

| 4.3  | Waveforms from PLECS for Operating Condition Corresponding to $V_g$                                  |    |

|      | = 120 V, P = 1 kW, $v_3$ = 530, A 250, C = 43 $\mu$ F                                                | 73 |

| 4.4  | Waveforms from PLECS for Operating Condition Corresponding to $V_g$                                  |    |

|      | = 120 V, P = 1 kW, $v_3 = 530$ , $A = 200$ , $C_3 = 30 \ \mu\text{F}$ , and $C = 12 \ \mu\text{F}$ . | 77 |

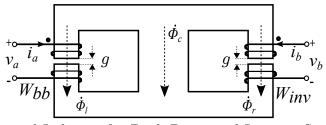

| 4.5  | Proposed Integrated Magnetic Based Transformer-less String Inverter                                  | 79 |

| 4.6  | Integrated Inductor for Buck-Boost and Inverter Stage                                                | 79 |

| 4.7  | Gyrator Capacitor Model for the Integrated Inductor in Buck-Boost                                    |    |

|      | and Inverter Stage                                                                                   | 80 |

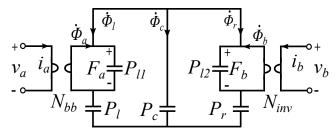

| 4.8  | Flux Density Distribution in the Magnetic Core at One Instant for the                                |    |

|      | Integrated Inductor                                                                                  | 80 |

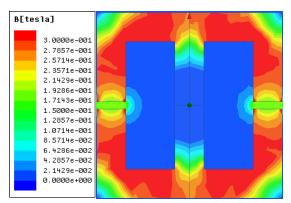

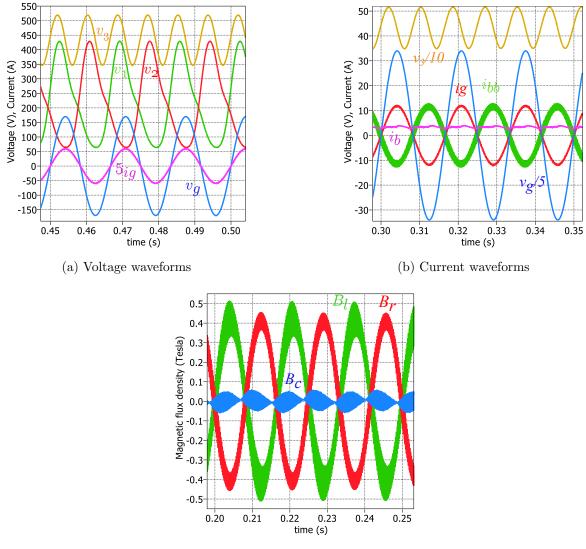

| 4.9  | PLECS waveforms for UPF Operation at $V_g = 120$ V, P = 1 kW, $v_3 =$                                |    |

|      | 530, $A = 200$ , $C_3 = 30 \ \mu\text{F}$ , and $C = 5 \ \mu\text{F}$                                | 82 |

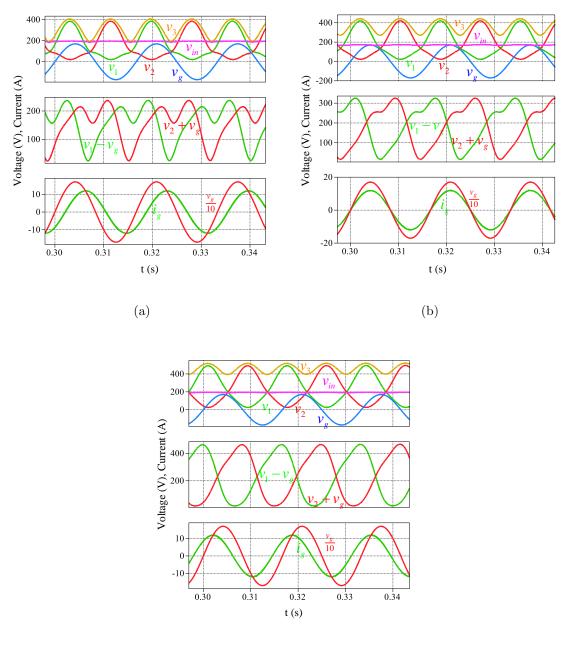

| 4.10 | Steady State Waveforms at 1 kVA for HBVS Inverter                                                    | 84 |

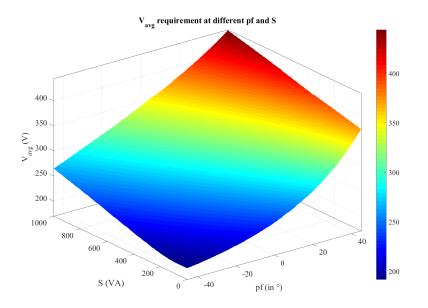

| 4.11 | Relationship between the Minimum $V$ Required to Satisfy (4.5) for                                   |    |

|      | Various Combinations of $S_g$ and $pf$ in the Given Operating Range                                  | 87 |

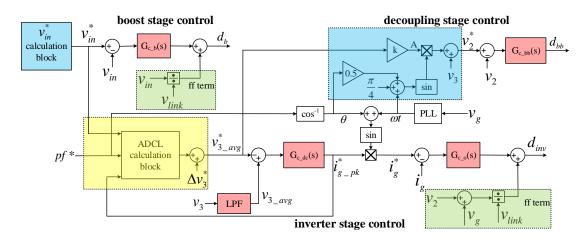

| 4.12 | Controller Block Diagram of HBVS Inverter in Grid Connected Mode                                     | 88 |

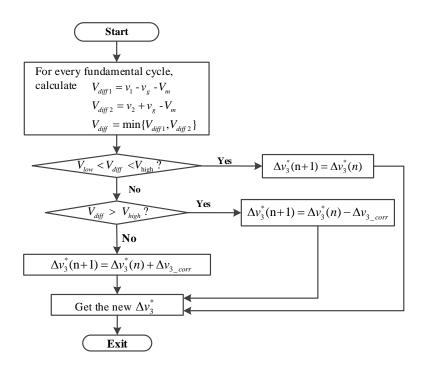

| 4.13 | Flow-chart for Calculating $\Delta v_3^*$ for the ADCL Voltage Controller Block.                     | 90 |

| 4.14 | 1 kVA Experimental Prototype for the SiC Based Proposed HBVS                                         |    |

|      | Inverter                                                                                             | 92 |

| 4.15 | Steady State Waveforms at 1 kVA, UPF Operation with 165 V input,                                     |    |

|      | 375 V DC-Link Average, and 120 V/60 Hz Output $\hfill \ldots \ldots \ldots$                          | 93 |

| 4.16 | Instantaneous 100 kHz Switching Level Waveforms at 1 kVA, UPF $$               |

|------|--------------------------------------------------------------------------------|

|      | Operation                                                                      |

| 4.17 | Steady State Waveforms at 1 kVA (a) Leading pf with 453 V DC-Link              |

|      | Average, (b) Lagging pf with 311 V DC-Link Average                             |

| 4.18 | Step Change Response with the ADCL Control Implementation for                  |

|      | 500 W to 1 kW Step-up Load Showing the Voltage Margin                          |

| 4.19 | Efficiency of HBVS Inverter with ADCL Voltage Control Scheme Im-               |

|      | plemented                                                                      |

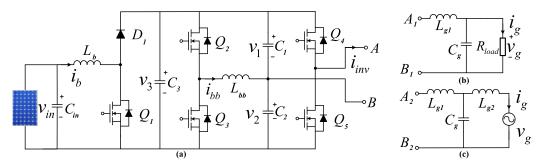

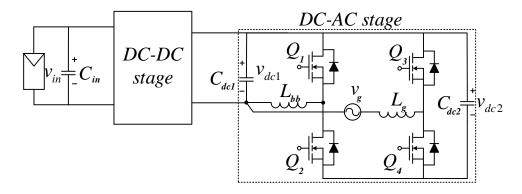

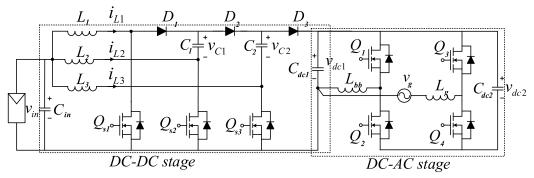

| 5.1  | Transformer-less Microinverter Topology with a DC-DC Stage and                 |

|      | Doubly Grounded DC-AC Stage                                                    |

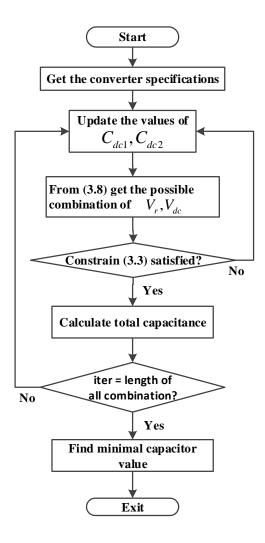

| 5.2  | Capacitance Optimization Flow Chart for the Proposed Transformer-              |

|      | less Microinverter Topology 101                                                |

| 5.3  | Controller Block Diagram in Stand-alone Operation for the Proposed             |

|      | Transformer-less Microinverter Topology 102                                    |

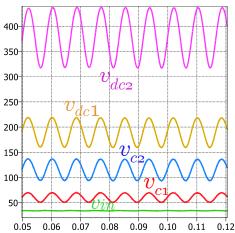

| 5.4  | PLECS Simulation Waveforms for Input, DC-link, and all the Inter-              |

|      | mediate Capacitor Voltages at 300 W Operation103                               |

| 5.5  | PLECS Simulation Waveforms at 300 W Operation103                               |

| 5.6  | Transformer-less Microinverter Topology with a DC-DC Stage and                 |

|      | Doubly Grounded DC-AC Stage104                                                 |

| 5.7  | GaN Based Hardware Prototype of Transformer-less Microinverter with            |

|      | EDR Boost and Doubly Grounded DDCL inverter                                    |

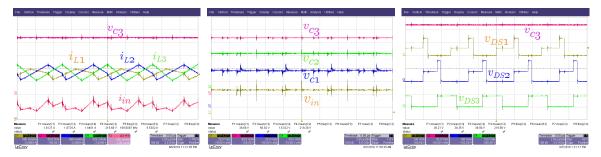

| 5.8  | $100~\mathrm{kHz}$ Instantaneous Switching Level Waveforms for the Dc-ac Stage |

|      | at 300 W, UPF Operation                                                        |

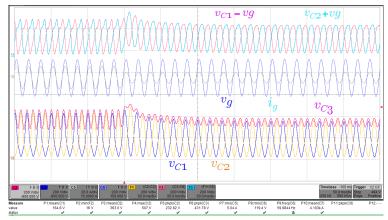

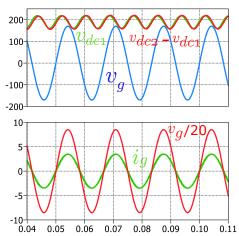

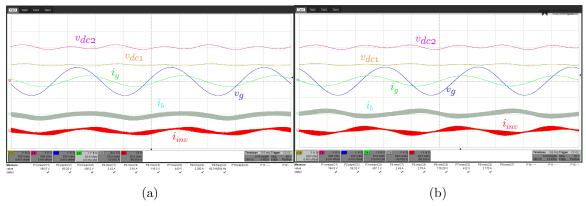

| 5.9  | Steady State Experimental Waveforms for GaN Based Transformer-      |

|------|---------------------------------------------------------------------|

|      | less Microinverter Operating from 35 V DC Input to 120 V, 60 Hz $$  |

|      | AC Output at 300 W Showing (a) Output and Two DC-link Voltages,     |

|      | and Output, Buck-boost Stage Inductor, and Inverter Stage Inductor  |

|      | Currents, (B) Input, Output, and First DC-link Voltages, and Output |

|      | Current                                                             |

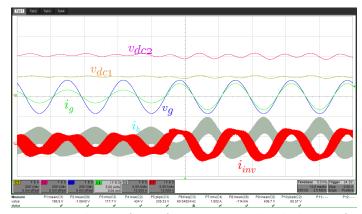

| 5.10 | Steady State Experimental Results for Gan Based Transformer-less    |

|      | Microinverter Operating at Nominal Operating Condition Illustrating |

|      | the Converter Waveforms                                             |

| 5.11 | Experimental Result for a Step-up Load Change from 150 W to 300 $$  |

|      | W at UPF Showing All the Converter Waveforms                        |

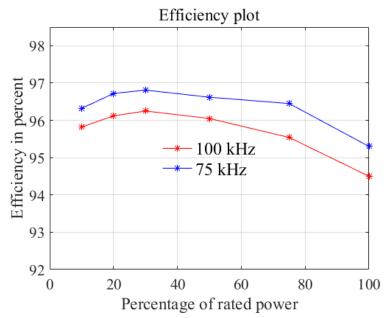

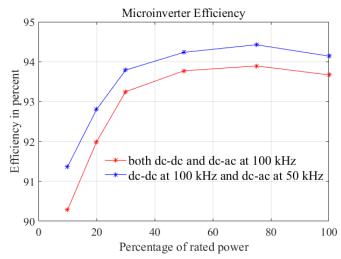

| 5.12 | Microinverter Efficiency Plot                                       |

#### Chapter 1

## INTRODUCTION

Solar energy is among the fastest growing renewable energy resources which accounts for an increasing and significant share of new generation capacity additions each year [1]. In the U.S. new solar installations have exceeded 1 GW DC in each quarter since 2014, reaching a total capacity of 29 GW DC in March 2016. In Q1 of 2016, solar photovoltaic (PV) systems accounted for 64% of new electric generation added in the U.S. market, making it the largest source of capacity addition across all the fuel types [1]. The distributed PV systems are garnering the interest of both the utility providers and residential consumers with the reducing solar panel costs, government incentive programs, and regulatory policies [2, 3]. The power electronic converter is a key component of the grid connected PV systems, extracting maximum power from PV panels and interfacing them to the grid.

## 1.1 PV Inverter

Currently, there are three widely used grid interactive PV systems: the centralized inverter system, the string inverter system, and the microinverter system [4].

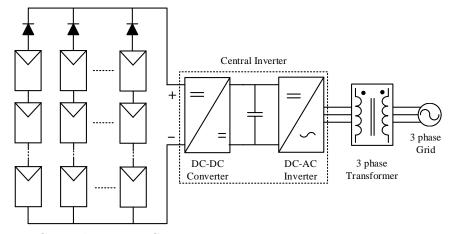

## 1.1.1 Central Inverter

The central inverters are typically in the 100 - 1000 kW range with three-phase topology and modular design for large power plants and typical unit sizes of 100, 150, 250, 500 and 1000 kW. The PV modules are arranged in series-parallel combinations, connected to one common central inverter as shown in Figure 1.1. The following are the merits and demerits of central inverter system.

Figure 1.1: Central Inverter System.

- High efficiency (more than 98 %) power conversion

- Cost effective for utility scale applications

- Maximum power point tracking (MPPT) control is disproportionate as it is common for the combined PV array

- Reduction in energy yield in case of partial shading, and may lead to hot spot failure under significantly unequal shading

- Loss of a single inverter leads to the loss of the entire or a large part of the power generation, so the system is not reliable

- Need for high-voltage DC cables between PV panels and inverter.

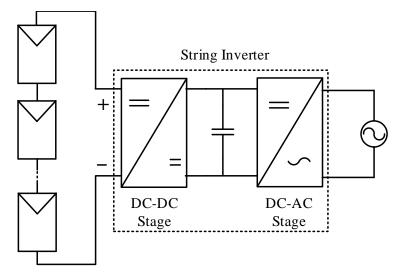

## 1.1.2 String Inverter

The string inverters, shown in Figure 1.2, are based on a modular concept, where PV strings, made up of series-connected solar panels, are connected to separate inverters. The string inverters are paralleled and connected to the grid. If the string voltage is high enough then no voltage boosting is necessary, thereby improving the system efficiency. Fewer PV panels can also be used, but then a DC/DC converter

Figure 1.2: String Inverter System.

or a line/high frequency transformer is needed for a boosting stage. The advantages compared to the central inverter are as follows:

- No losses in string diodes (no diodes needed)

- Separate MPPTs for each string so better power yield, but still it is not optimal.

However, due to the series connection of modules, the current from the PV string is limited by the weakest link, i.e., a shaded module, and therefore, the loss of generation is still larger than the corresponding microinverters for partial shading with string inverters.

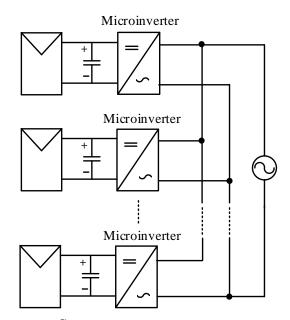

## 1.1.3 Microinverter

The microinverter, as shown in Figure 1.3 is popular for the power level ranging from 200-500 W. Each such power processing device is responsible for the independent MPPT of every single PV panel, thus maximizing the power production. It converts the PV output to the AC voltage through one or more stages of power conversion, and is integrated to the grid individually. It outperforms the string inverters under

Figure 1.3: Microinverter System.

partial shading conditions created, for example, by-passing clouds. The output from the unshaded modules is not affected under partial shading condition, and hence, the total power is significantly higher. The following are the advantages of microinverter system.

- The microinverter is an integrated part of the PV panel. It remove losses due to the mismatch between panels and support panel level MPPT. For a string inverter or a centralized inverter, a string or multistring of PV panels shares a single MPPT controller, but the mismatch loss is significant in partial shading conditions [5]. Considering the mismatch loss together with the DC/AC conversion loss contributing to the whole PV system loss, string/centralized inverters may have lower system efficiency than microinverters due to higher mismatch loss although they usually have higher DC/AC conversion efficiency than microinverters.

- Panel level hot-spot risk is removed and panel lifetime can be improved. Hot

spot takes place when a shaded cell within a partially shaded panel becomes reverse biased and dissipates power in the form of heat [6]. For series connected PV panels used with a string/centralized inverter, a by-pass diode is added to each panel in practice. For the microinverter solution, the by-pass diode is not necessary because each panel has its own power processing unit, leading to no direct connection between the PV panels.

• Its 'plug and play' feature simplifies system installation and maintenance. The microinverter solution allows for more flexible PV project planning and multi-faceted PV panel installation.

## 1.2 Transformer-less Single Phase PV Inverter

The focus of the present work encompasses the transformer-less single phase PV inverters, both the string and the microinverter implementation. The transformerless PV inverters are becoming increasingly more attractive due to their lower cost, reduced footprint, and improved efficiency compared to inverters with transformer isolation. However, a major challenge with the transformer-less inverters is the presence of common mode leakage currents [7] which can increase the system loss, distort the grid current, and induce severe electromagnetic interference.

In addition, similar to most single-phase converters, another main challenge is the presence of double line frequency power ripple [8,9], which is the difference between the instantaneous grid injected power and the constant dc power corresponding to the maximum power point (MPP) from the PV panels, necessitating the use of large filters in conventional topologies.

Finally, for the transformer-less microinverter application, another challenge is to achieve a very high gain DC-DC stage simultaneously maintaining a high conversion efficiency. The following gives a detailed discussion of the implementation challenges.

#### 1.2.1 Challenge I: Capacitive Ground Current

The frame of a PV module is required by codes to be grounded. There is significant parasitic capacitances between the positive and negative PV terminals to the frame, and hence to the ground. When the positive and/or negative terminals are connected to a switching node of the inverter with respect to ground, it can lead to significant, common mode ground currents through these parasitic capacitances. [7,10–13] present different methods to mitigate this problem in transformer-less PV inverters.

The straight-forward way to address this issue would be directly connecting the PV terminal ground to the grid neutral with topological variations which would generate no common mode voltage [14,15] or at least ensuring a low-frequency (typically fundamental frequency) or constant potential of the PV negative terminal relative to the grid neutral using half-bridge, or neutral point clamped (NPC) inverters [16]. For a conventional full bridge DC-AC inverter with unipolar sinusoidal pulse width modulation (SPWM), the voltage across this stray capacitance swings at switching frequency, increasing the leakage current, whereas realization with bipolar SPWM reduces the common mode ground currents. Other solutions to the ground current issue would involve disconnecting the PV negative from the grid neutral at certain operating inverval over a cycle with additional switches and diodes [17,18].

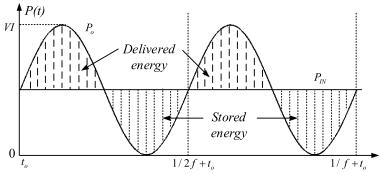

## 1.2.2 Challenge II: Power Decoupling

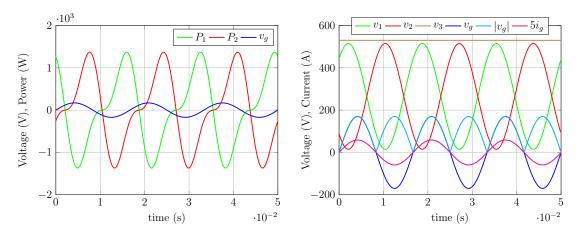

Figure 1.4 shows the power decoupling consideration required for single phase inverters. The input power from the PV array being purely DC as shown by  $P_{IN}$ and the output being a sinusoidally varying power superimposed on a DC average as shown by  $P_O$ , the instantaneous power from input is clearly not equal to that of the output. Considering the grid voltage and current as given in (1.1), the grid power is given in (1.2) which is a double line frequency varying ripple power.

$$v_g = V_g \sin(\omega t); \quad i_g = I_g \sin(\omega t + \theta)$$

(1.1)

$$P_g = \frac{V_g I_g}{2} \left( \cos \theta - \cos(2\omega t + \theta) \right) \tag{1.2}$$

Thus a energy storage element, like a large DC-link capacitor is required to store and deliver the balance power over one fundamental cycle. This ensures that the PV input is free from any voltage ripple which would otherwise degrade the MPPT efficiency of the converter. The state-of-the-art approaches predominantly use electrolytic capacitors for these decoupling purposes, which have relatively high equivalent series resistance (ESR) and low RMS current rating per  $\mu$ F. Moreover, these capacitors have limited lifetime [19] which further degrades with electrical and thermal stresses, and thermal cycling [20]. Consequently they pose reliability challenges to the inverters, which require to compete with the 25 years of warranted lifetime of the PV module [21].

Thus an extensive research has been directed to replace these electrolytic capacitors with corresponding film capacitors and increase the reliability of the inverters. But as the capacitor to volume ratio of a film capacitor is low compared to an electrolytic capacitor, so instead of directly replacing them, novel power decoupling tech-

Figure 1.4: Power Decoupling Concept.

niques are proposed in literature [8, 19, 22–27] to reduce the capacitor requirement and address the double line frequency power with smaller capacity energy storage component.

Some converters address the issue by adding an additional conversion stage (an auxiliary circuit) to handle the ripple power [22,24], which can be connected in either series or parallel to the primary converter. The main disadvantages of such approaches are higher cost, complex circuitry, and often higher losses with the addition of more active components. They also have to encounter higher current stress on the auxiliary circuit if connected in series [24] or higher voltage stress if connected in parallel.

For power factor correction (PFC) applications, [25] achieves reduction in the capacitance by allowing higher voltage ripple across the DC-link but at the cost of distorted line input current. Other papers have discussed sophisticated control schemes to reduce the DC-link capacitor without affecting the power quality [26, 27]. But all these approaches do not essentially stretch the limit on reducing the capacitors to the minimum and there is still much room for improvement. As such decoupling capacitor volume reduction remains an active area of research. In a recent study in [28], several decoupling approaches have been compared including DC side decoupling and AC side decoupling, with DC side decoupling shown to outperform AC decoupling approaches. The best solution shown in [28] achieves 15 F/kW at 800 V, but using six switches and without considering the ground current issues or non-unity power factor operation.

## 1.2.3 Challenge III: High Volatage Gain

As mentioned in Section 1.1, the microinverters are directly connected to each of the PV panel with typical input voltage spanning from 20 to 40 V, whereas, to interface to the grid the AC output voltage needs to be 120 V/230 V RMS. This

necessitates a high voltage boost for interfacing a PV panel to the grid. Thus a high voltage gain is required by the DC-DC stage and with a transformer-less implementation, it poses a big challenge. A review of the high gain DC-DC boost is discussed in the following Section 1.3.

#### 1.3 High Gain Transformer-less DC-DC Boost Stage

Though ideally the conventional boost or buck-boost converter can achieve high gain, in practical implementation their voltage gain is limited, typically to 5-8, by the inductor series resistance and losses incurred by the semiconductor components which need to operate under extreme-duty-ratio, high voltage stress, and overall poor converter performance as duty ratio approaches unity. Hence, alternate topologies for high step-up conversion and improved system operation is an active area of research exploring both isolated and non-isolated converters.

A high frequency transformer-isolated DC-DC converter is a popular choice in applications which necessitate galvanic isolation between the input and output ports [29, 30]. It can also be employed in high step-up applications not demanding isolation as it has the advantage of achieving high gain with a flexible selection of the transformer turns ratio at the design stage. But it has the drawback of higher switch voltage stress, current spike, and lower efficiency due to the transformer leakage inductance and parasitic capacitance formed between its primary and secondary winding. Active clamp or snubber circuit can be implemented to avoid voltage spike, but these lead to complex circuitry and loss in the auxiliary circuit [31, 32]. Integrated magnetic based isolated converters can also be implemented to increase the power density and efficiency with added performance features like soft switching of the converter switches [33, 34]. Resonant converter based isolated converters are further proposed where the transformer leakage inductance is used as the resonant inductance [35–37]. On the other hand, non-isolated high gain converter has the benefits of higher efficiency, smaller foot-print, reduced volume, and lower cost with the elimination of the lossy and bulky transformer. A wide variety of non-isolated topologies based on switched capacitor [38–41], voltage multiplier cell (VMC) [42–45], three state switching cell (3SSC) [46–48], coupled and/or interleaved inductor [49–54], or a combination of these [55–61] are available in literature. A number of soft switching approaches to improve the efficiency with the above mentioned voltage boost techniques or even with the conventional converters extreme-duty-ratio-operation have also been reported [62, 63].

Switched capacitor based high step-up converters [38–41] have been presented to attain improved efficiency, higher power density, and better performance as it has no magnetic components making it a low noise with minimal radiated electromagnetic interference (EMI) solution [40]. Due to its modular structure, the voltage scaling is flexible with this technique. But it has the disadvantages of pulsating input current and poor voltage regulation as the voltage gain is predetermined by the circuit structure and the input must be an integer fraction of the output voltage. The VMC based converters [42–45] more commonly referred to as hybrid switched capacitor can be used to circumvent this problem. Primarily the voltage multiplier cell is composed of capacitor-diode-resonance inductor which can be integrated to classical DC-DC converters. The resonance inductor allows the zero current switching (ZCS) turn-on of the main switch, but is not mandatory for basic operation of the multiplier cell [44].

For high gain applications, 3SSC converters based on acitve switches, diodes, and coupled inductor are alternatively proposed to reduce inductor size, lower input and output current ripple, and decrease the voltage stress of the main switch [46, 47]. In fact the voltage stress across the switch is naturally clamped by the output filter capacitor. [48] attains high gain by integrating VMC and 3SSC approaches. Besides, the coupled inductor based converters can provide high voltage stepup by manipulating the turns ratio but maintaining lower voltage switch stress and conduction loss [49,50]. However, these have high ripple at the input and the ripple increases with the increase of turns ratio to meet the higher voltage gain requirement. Also their efficiency is degraded due to the losses associated with the leakage inductors and active clamping is proposed to recycle the leakage energy at the cost of circuit complexity [51, 52, 64]. For high input current application, interleaving has been proven to provide lower input ripple, reduced passive component size, and lower loss, but the voltage gain is still the same as the classical boost converter [53, 54].

Converters combining the features of previously discussed approaches are demonstrated to provide high gain with improved system performance but have inherently complex implementations. [55, 56] combine the features of coupled inductor and switched capacitor technique, while [57,58] integrate coupled inductor and VMC attributes. The coupled inductor and 3SSC techniques are merged in [59,60], whereas in a recent publication in [61], features of coupled inductor, VMC, and 3SSC are all integrated in one converter. Additionally, the hybrid boost-flyback topology is introduced to achieve high static gain with low voltage stress across the switches, but it requires large input filters as the input current is pulsed [65, 66]. For improved efficiency [62, 63] propose soft switching technique with the interleaved converter.

#### 1.4 Objectives and New Contributions of the Work

The dissertation focuses on developing single phase transformer-less PV intervers for string and microinverter application, ensuring higher efficiency, high power density, wide band-gap device based high switching frequency, and reduced decoupling capacitance requirement through active power decoupling. The new contributions of this work are:

- extended duty ratio (EDR) boost converter has been thoroughly analyzed and implemented for high gain purpose as the DC-DC stage for the non-isolated microinverter application;

- a novel sensor-less current sharing technique with duty ratio and phase shift modification of the carrier signal has been proposed to ensure wide input/output voltage range of operation for the EDR boost converter;

- discontinuous conduction mode (DCM) operation for the EDR converter is studied for different operating zones for high gain dc-dc light load application;

- an active power decoupling scheme with large sinusoidal swing of the half-bridge capacitors and a double line frequency DC-link voltage ripple termed as half-bridge voltage swing (HBVS) inverter has been proposed to reduce the capacitor requirement; the proposed converter is studied, implemented and tested for its performance validation in string inverter application;

- another active power decoupling scheme with dynamic DC-link (DDCL) approach has been analyzed, implemented, and tested for microinverter application which uses only four switches and reduced capacitance for decoupling purposes along with the feature of double grounding.

The papers published during the course of this dissertation are:

- J. Roy and R. Ayyanar, "Sensor-Less Current Sharing Over Wide Operating Range for Extended-Duty-Ratio Boost Converter," in IEEE Transactions on Power Electronics, vol. 32, no. 11, pp. 8763-8777, Nov. 2017.

- Y. Xia; J. Roy; R. Ayyanar, "A capacitance-minimized, doubly grounded transformerless photovoltaic inverter with inherent active-power decoupling," in IEEE Transactions on Power Electronics, vol. 32, no. 7, pp. 5188-5201, July 2017.

- Y. Xia; J. Roy; R. Ayyanar, " A T-Type Single Phase Transformer-less String Inverter with Dynamic and Adaptive DC-Link Voltage Control," under revision in IEEE Transactions on Power Electronics.

- R. Ayyanar, Y. Xia, and J. Roy, Arizona State University, Reduced volume single-phase double-grounded transformer-less photovoltaic inverter with active power decoupling, Patent pending, Application No. 62/263,068, Dec 2015

- J. Roy; R. Ayyanar, "Seamless Transition of the Operating Zones for the Extended-Duty-Ratio Boost Converter," accepted in 2017 IEEE Energy Conversion Congress and Exposition (ECCE), Cincinnati, Ohio, 2017.

- J. Roy; Y. Xia; R. Ayyanar, "GaN-based High Gain Soft Switching Coupled-Inductor Boost Converter," accepted in 2017 IEEE Energy Conversion Congress and Exposition (ECCE), Cincinnati, Ohio, 2017.

- J. Roy; Y. Xia; R. Ayyanar, "Sliding Mode Control of a Single Phase Transformerless PV Inverter with Active Power Decoupling," accepted in 2017 IEEE Energy Conversion Congress and Exposition (ECCE), Cincinnati, Ohio, 2017.

- Y. Xia; J. Roy; R. Ayyanar, "Optimal Variable Switching Frequency Scheme for Grid Connected Full Bridge Inverters with Bipolar Modulation Scheme," accepted in 2017 IEEE Energy Conversion Congress and Exposition (ECCE), Cincinnati, Ohio, 2017.

- Y. Xia; J. Roy; R. Ayyanar, "A Single Phase Doubly Grounded, PV Inverter using Coupled Inductor with Integrated Magnetics and Active Power Decoupling Technique," accepted in 2017 IEEE Energy Conversion Congress and Exposition (ECCE), Cincinnati, Ohio, 2017.

- J. Roy; R. Ayyanar, "A single phase transformer-less string inverter with integrated magnetics and active power decoupling," accepted in 2017 IEEE Applied Power Electronics Conference and Exposition (APEC), March, 2017.

- J. Roy; Y. Xia; R. Ayyanar, "GaN based transformer-less microinverter with extended-duty-ratio boost and doubly grounded voltage swing inverter," accepted in 2017 IEEE Applied Power Electronics Conference and Exposition (APEC), March, 2017.

- Y. Xia; J. Roy; R. Ayyanar, "A GaN based doubly grounded, reduced capacitance transformer-less split phase photovoltaic inverter with active power decoupling," accepted in 2017 IEEE Applied Power Electronics Conference and Exposition (APEC), March, 2017.

- J. Roy; R. Ayyanar, "GaN based high gain non-isolated DC-DC stage of microinverter with extended-duty-ratio boost," in 2016 IEEE Energy Conversion Congress and Exposition (ECCE), presented, Sept 2016.

- J. Roy; Y. Xia; R. Ayyanar, "A single phase transformerless string inverter with large voltage swing of half bridge capacitors for active power decoupling," in 2016 IEEE Energy Conversion Congress and Exposition (ECCE), presented, Sept 2016.

- Y. Xia; J. Roy; R. Ayyanar, "A high performance T-type single-phase doubly grounded transformer-less photovoltaic inverter with active power decoupling," in 2016 IEEE Energy Conversion Congress and Exposition (ECCE), presented, Sept 2016.

- A. Sastry et al., "Failure modes and effect analysis of module level power electronics," Photovoltaic Specialist Conference (PVSC), 2015 IEEE 42nd, New

Orleans, LA, 2015, pp. 1-3.

### 1.5 Chapter Overview

**Chapter 2** discusses the EDR boost for transformer-less high step-up application. Comprehensive analysis of converter operating principles, key theoretical waveforms, and steady state circuit performance corresponding to all the possible zones of operation have been presented for a 3-phase EDR boost converter. Methods for sensor-less current sharing among the different phases of the 3-phase EDR boost have been introduced. The sharing scheme has been convincingly demonstrated in a 250 W GaN based hardware prototype for different operating regions.

The EDR converter shows interesting performance features and current sharing characteristics in the discontinuous conduction mode (DCM) operation. For an M-phase converter in DCM, all the boost inductors would still share the current equally inherently in each of Zone I to Zone M-1, while only Zone M (the least gain region) would not experience inherent equal current sharing. In fact, in Zone M, the inductor current for phases 2 to M will have negative excursion at certain operating interval. A comprehensive analysis of the operation of 3-phase EDR boost converter in DCM for each of its operating zones is presented in **Chapter 3**. Further, the results are validated from the GaN-based 3-phase 100 W experimental prototype.

In Chapter 4, a power decoupling scheme for single phase inverters has been proposed. The converter termed as half-bridge voltage swing (HBVS) inverter is a combination of boost and half-bridge stages along with a power decoupling stage. A large sinusoidal swing of the half-bridge capacitors are allowed along with a double line frequency DC-link voltage ripple to address the power decoupling with a reduced capacitor value of only 54  $\mu$ F/ kW at a peak of 550 V DC-link voltage. Further, the inductors of the buck-boost and the half-bridge inverter stages are integrated in one single core to reduce the converter volume and cost. The experimental results with the integrated inductors at 1 kW output are provided for validation of the concept for string inverter application.

In Chapter 5, another power decoupling technique is introduced based on a doubly grounded transformer-less PV inverter topology with active power decoupling built into the basic topology termed as dynamic DC-link (DDCL) inverter. It is based on a single stage of power conversion by a unique combination of boost-coupled half bridge circuit using only four switches overall and capable of supporting a wide range of power factor. The simulation and experimental results at 300 W output are provided for validation of the concept for microinverter application with a high-gain DC-DC stage as the front-end converter.

The report is concluded in **Chapter 6** with the summary and future work of this research contribution.

#### Chapter 2

## EXTENDED DUTY RATIO BOOST CONVERTER

#### 2.1 Introduction

The extended-duty-ratio (EDR) boost converter (*M*-phase version is shown in Figure 2.1), has been studied for the high step-up implementation. It inherits the merits of switched capacitors and interleaved inductor technique and offers lower converter losses as most of the switches encounter lower voltage stress, and thus switches with lower voltage rating and thus lower  $R_{DS(ON)}$  can be used. Also the input current is shared among all the interleaved converters (inherent sharing only in a limited duty ratio), so the inductor conduction loss is reduced by a factor of the number of phases. Besides, the current through the switches is a fraction of the input current resulting in minimized conduction and switching losses. Buck implementation of EDR converter is proposed in a number of previous works intended for voltage stepdown applications as voltage regulators (VR) or point of load (POL) implementation [67–70], whereas its variations are reported in [71–78]. These papers primarily studied the converter in only one operating zone, where the phase currents (output inductor currents for buck operation) are being shared inherently. In a recent work EDR converter has been employed in a bidirectional application [79].

In this chapter, the operation of the EDR boost converter in different operating zones is studied in detail along with the current sharing between its interleaved input phases.

Figure 2.1: Topology for *M*-Phase Extended Duty Ratio (EDR) Boost.

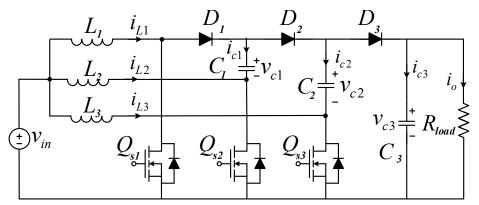

2.2 *M*-Phase EDR Boost Converter

Figure 2.1 shows the *M*-phase EDR boost topology. It is a combination of interleaved inductor with switched capacitor configuration. The circuit consists of *M* switched capacitors  $C_M$  whose voltage levels  $v_{cM}$  are a fraction of the output voltage  $v_{out}$ , and *M* interleaved boost inductors which share the input current in equal or unequal proportion depending on the operating duty ratio of the converter. The load is connected across the final capacitor i.e.,  $v_{cM} = v_{out}$ . Each boost phase is interleaved which means that they are phase shifted by  $(360/M)^{\circ}$ .

For a comprehensive analysis and design of a general M-phase converter, the operation needs to be studied under M different zones with the duty ratio for the  $m^{th}$  zone given by (2.1).

$$\frac{M-m}{M} \le D \le \frac{M-m+1}{M} \text{ for all } m \in [1, M]$$

(2.1)

The converter gain in different zones cannot be expressed with any general expression, as the operating modes in each zone is not the same. As an example for Zone I (this is the zone with maximum voltage gain), the operating modes only encompass intervals with either all M phases being simultaneously on or intervals where (M-1)phases are on in a certain pattern depending on interleaving sequence. Here, the lower switch turned on is referred to as the phase being on. The voltage gain of the converter in this zone is given by (2.2).

$$k_I = \frac{M}{1-D} \text{ for } m = 1 \tag{2.2}$$

On the contrary, for Zone M (this is the zone with minimum voltage gain), the operating modes only encompass intervals with either a single phase being on or intervals where neither of the phases are on. And the gain in this zone is given by (2.3).

$$k_M = \frac{1}{(1-D)^M} \text{ for } m = M$$

(2.3)

It is also interesting to notice that the current is inherently shared among all the interleaved boost inductors only in Zone I operation. This can be verified with the basic capacitor charge balance principle for all the switched capacitors. Thus it is the preferred operating zone as the maximum voltage gain is also obtained in this region. However, with a wide range of operating input and output voltages, the converter is required to be operated for an expanded range of duty ratio forcing the converter to also operate in some other M - 1 operating zones where the current is no longer shared equally inherently.

So outside this region some of the phases might be overloaded, if a proper current sharing scheme is not employed. This would lead to higher switching and conduction losses in overloaded phases leading to hot spot; the inductors might also saturate altogether disrupting the converter operation. So it is very important to address the current sharing issue.

Current sensors can be employed to realize the current sharing by advanced control technique [69]. But it would incur higher component count as each phase would require separate sensor and associated conditioning circuitry, increased control complexity, and higher cost. It has been observed that in the rest of the (M-1) zones where the phase currents are not inherently shared, either the magnitude or the phase-shift of the duty ratio of each interleaved phase can be modified to ensure input current being shared equally or more evenly between the phases. This property has been exploited to ensure current sharing in EDR boost converter.

## 2.3 Operating Principles

The following analysis considers the converter operating in continuous conduction mode (CCM) where the inductor current of all the boost phases would always be continuous.

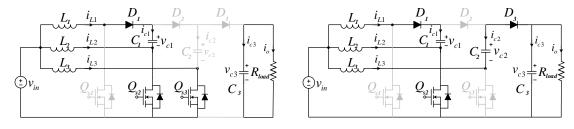

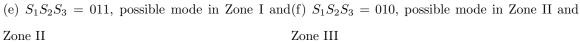

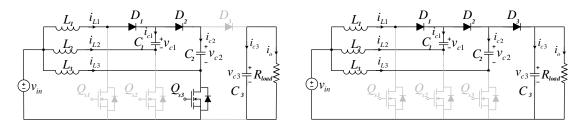

As has been discussed in Section 2.1, to get an insight of the converter operation in various zones, each operating zone with unique combination of operating modes needs to be analyzed individually. A basic 3-phase topology as given in Figure 2.2 is considered to comprehend the converter operation where M = 3. Figure 2.3 shows the different operating modes of the converter resulting from different combination of the switching pattern. For example, Figure 2.3a with  $S_1S_2S_3 = 111$  mode signifies that all the switches are on; whereas, Figure 2.3h with  $S_1S_2S_3 = 000$  mode signifies that all the switches are off. The rest of the modes can be similarly recognized from

Figure 2.2: Topology for 3-Phase EDR Boost.

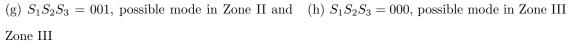

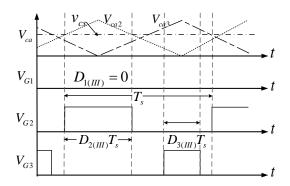

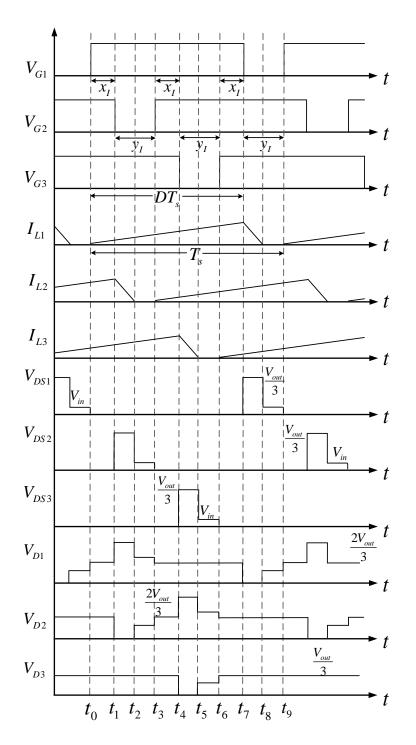

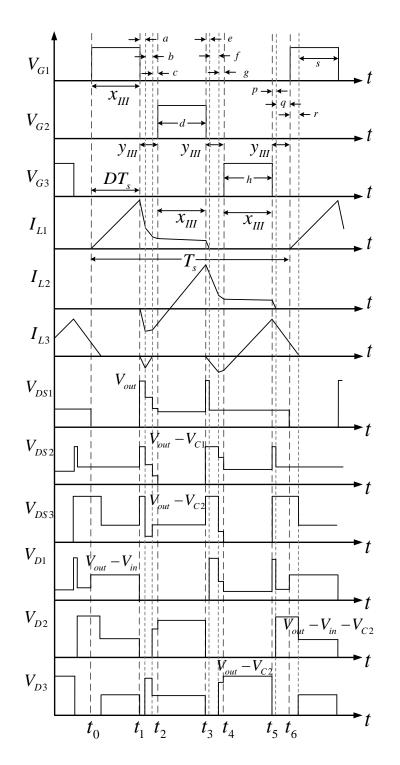

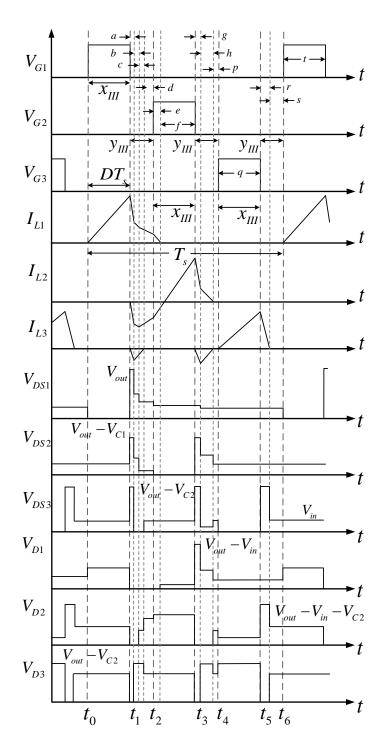

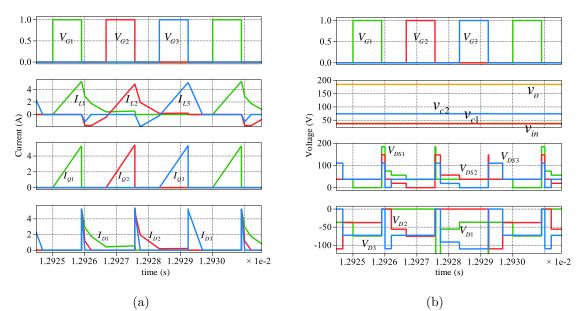

Figure 2.3b to Figure 2.3g. Figure 2.4 shows the typical gate signal, corresponding inductor current, and switch voltage stress in each of the operating zones for 3-phase converter.

## 2.3.1 Zone I

Table 2.1 gives the detail of the operation in Zone I where duty ratio of each phase is equal and is between  $2/3 \leq D \leq 1$ . The switch states, time interval, and corresponding inductor current and capacitor voltage slopes have been tabulated along with the figure reference for the operating modes. It also gives the charging/discharging conditions of the passive component in these intervals denoted by  $\uparrow$ and  $\downarrow$  respectively. Figure 2.4a shows the typical gate signal, corresponding inductor current, and switch voltage stress, both the diode (denoted by  $V_D$ ) and MOSFETs (denoted by  $V_{DS}$ ) in this zone of operation, where  $x_I = (D-2/3)T_s$  and  $y_I = (1-D)T_s$ .

The voltage  $v_{cM}$  for each capacitor can be established in terms of the input voltage  $V_{in}$  by applying the inductor volt-second balance and is given by (2.4) where  $v_{c3}$  is also the output voltage,  $v_{out}$ .

$$v_{c1} = \frac{V_{in}}{(1-D)}; \quad v_{c2} = \frac{2V_{in}}{(1-D)}; \quad v_{c3} = \frac{3V_{in}}{(1-D)}$$

(2.4)

In this zone the input current is inherently shared among all the three boost phases. This can be analyzed from Table 2.1 by applying capacitor charge balance principle. As each of the intermediate capacitors are carrying current only in two operating intervals, it is straightforward to understand the inherent current share. For example, the charge balance of  $C_1$  shows  $i_{L1} = i_{L2}$ . The current in each boost inductor is given by (2.5).

(a)  $S_1 S_2 S_3 = 111$ , possible mode in Zone I

(b)  $S_1 S_2 S_3 = 110$ , possible mode in Zone I and Zone II

(c)  $S_1S_2S_3 = 101$ , possible mode in Zone I and(d)  $S_1S_2S_3 = 100$ , possible mode in Zone II and Zone II Zone III

**Figure 2.3:** Current Path Corresponding to Each of the Operating Intervals/Modes for 3-Phase EDR Boost.

Figure 2.4: Gate Signal, Inductor Current, and Device Voltage at Three Operating Zones for 3-Phase EDR Boost.

$$i_{L1} = i_{L2} = i_{L3} = \frac{i_o}{(1-D)} \tag{2.5}$$

Finally, the gain of the converter for this zone follows in (2.6). As  $v_{c1}$  and  $v_{c2}$  are integer fractions of  $v_{c3}$ , it is to be noted from Table 2.1 that the voltage applied across each input inductor is equivalent, i.e., they have the same voltage magnitude and duration, and thus equivalent current slope, but phase shifted by  $360/3 = 120^{\circ}$  for interleaving.

$$k_I = \frac{v_{c3}}{V_{in}} = \frac{i_{L1} + i_{L2} + i_{L3}}{i_o} = \frac{3}{(1-D)}$$

(2.6)

#### 2.3.2 Zone II

Table 2.2 gives the details of the operation in Zone II where duty ratio of each phase is equal and is between  $1/3 \leq D < 2/3$ . Similar to Table 2.1 the details of the switch states, time interval, and corresponding inductor current and capacitor voltage are tabulated along with the figure reference for the operating modes. By applying inductor volt-second balance, the voltage  $v_{cM}$  for each capacitor is obtained and is given by following sets of equation.

$$v_{c1} = \frac{V_{in}(D^2 - 5D/3 + 7/9)}{(1 - D)^3}$$

(2.7)

$$v_{c2} = \frac{V_{in}(D^2 - 2D + 10/9)}{(1 - D)^3}$$

(2.8)

$$v_{c3} = \frac{V_{in}(2D^2 - 4D + 19/9)}{(1-D)^3} \tag{2.9}$$

It can be observed that unlike Zone I, the intermediate capacitor voltage is not an integer fraction of the output voltage. Figure 2.4b shows the typical gate signal, corresponding inductor current, and switch voltage stress both the diode (denoted by  $V_D$ ) and MOSFETs (denoted by  $V_{DS}$ ) in this zone of operation, where  $x_{II} = (D - 1/3)T_s$  and  $y_{II} = (2/3 - D)T_s$ . The inductor current is derived by applying the capacitor charge balance principle and is given in (2.10)-(2.11).

$$i_{L1} = \frac{i_o}{(1-D)}; \qquad i_{L2} = \frac{i_o}{3(1-D)^2}$$

(2.10)

$$i_{L3} = \frac{i_o(D^2 - 5D/3 + 7/9)}{(1 - D)^3}$$

(2.11)

It can be clearly noticed that current is not the same in each of the phases, it is the highest in phase 1, and the lowest in phase 2. (2.12) gives the converter gain in this operating zone.

$$k_{II} = \frac{v_{c3}}{V_{in}} = \frac{(2D^2 - 4D + 19/9)}{(1 - D)^3}$$

(2.12)

2.3.3 Zone III

This is the zone for minimum converter gain with the least duty ratios. Table 2.3 gives the detail of the operation in Zone III where duty ratio of each phase is considered equal and is between  $0 \le D < 1/3$ . Similar to the previous two Tables 2.1 and 2.2, the attributes of the switch states, time interval, and corresponding inductor current and capacitor voltage are tabulated along with the figure reference for the operating modes. The capacitor voltage  $v_{cM}$  is obtained by applying inductor volt-second balance, and is given in (2.13)-(2.14).

$$v_{c1} = \frac{V_{in}D}{(1-D)^3}; \qquad v_{c2} = \frac{V_{in}D(2-D)}{(1-D)^3}$$

(2.13)

$$v_{c3} = \frac{V_{in}}{(1-D)^3} \tag{2.14}$$

Similar to Zone II, the intermediate capacitor voltage is not an integer fraction of the output voltage. Thus from Table 2.3 and from  $v_{cM}$  expressions it can be seen that the inductor voltage of each phase is not equivalent to each other. The inductor current is derived by applying the capacitor charge balance principle and is given in (2.15).

$$i_{L1} = \frac{i_o}{(1-D)}; \quad i_{L2} = \frac{i_o D}{(1-D)^2}; \quad i_{L3} = \frac{i_o D}{(1-D)^3}$$

(2.15)

Even in this zone, the current is not the same in each phase; phase 1 has the highest current and phase 2 the least. Figure 2.4c shows the typical gate signal, corresponding inductor current, and switch voltage stress for this zone both the diode (denoted by  $V_D$ ) and MOSFETs (denoted by  $V_{DS}$ ), where  $x_{III} = DT_s$  and  $y_{III} = (1/3 - D)T_s$ . (2.16) gives the converter gain in this operating zone.

$$k_{III} = \frac{v_{c3}}{V_{in}} = \frac{1}{(1-D)^3}$$

(2.16)

# 2.4 Current Sharing

Equal duty ratio does not ensure equal current sharing except in Zone I, as mentioned in Section 2.3. Therefore, this paper proposes suitable adjustment of duty ratios for each phase to ensure equal current sharing or at least to minimize the current RMS error in the worst scenario. Since in Zone I current is inherently shared with duty ratio of all the phases being in the range of  $2/3 \leq D \leq 1$ , the discussion here would consider the remaining two operating zones. Depending on the operating zone, the correction of duty ratio of each phase would be different with the objective of either sharing the current equally between phases or minimizing the standard deviation of the current error.

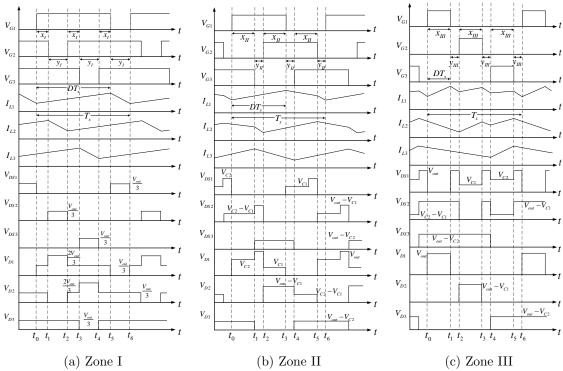

# 2.4.1 Zone II

As shown in Section 2.3, in Zone II the current in phase 1 is the highest and that in phase 2 is the least, i.e.,  $i_{L1} > i_{L3} > i_{L2}$ . Also from Table 2.2 and Figure 2.4b, it can be seen that  $i_{L1}$  is charged from  $t_0$  to  $t_3$  for an interval of  $DT_s$  and discharged from  $t_3$  to  $t_6$  for an interval of  $(1 - D)T_s$ . So to decrease the average of  $i_{L1}$ , it could be as simple as decreasing the duty ratio of phase 1 by a certain value, lets assume it *a*. Similar analysis would indicate increasing the duty ratio of phase 2 by *b* to

(a) Asymmetric PWM: true for  $a_1T_s \leq x_{II}$  (b) Symmetric PWM: true for  $a_2T_s \leq x_{II}$ **Figure 2.5:** Adjusted Duty Ratio for Three Phases to Balance Current in Zone II Operating Region for 3-Phase EDR Boost.

increase the average of  $i_{L2}$ , and keeping the duty ratio of phase 3 unchanged. The carrier signals ( $V_{ca1}$ ,  $V_{ca2}$ ,  $V_{ca3}$ ) and modified duty ratios are shown in Figure 2.5 for two different pulse width modulation (PWM) generation schemes, asymmetric (saw-tooth carrier) and symmetric (triangle carrier) PWM. Finally, this modification of duty ratio of each phase would lead to the change in the converter gain, which is now an involved function of a, b, and D.

This section discusses the estimation of a and b for meeting the specified gain of the converter for Zone II operation for both asymmetric and symmetric PWM schemes. The operation with unequal duty ratios affects the two PWM schemes differently and imposes different restrictions on the limit of duty ratio modification. Thus the converter is analyzed separately in each of the two PWM schemes of operation.

# Case I (Asymmetric PWM)

For asymmetric PWM, the duty control signal of phase 1 is decreased by  $a_1$ , and that of phase 2 is increased by  $b_1$ . Thus the modified duty ratio of each phase becomes:  $D_{1(II)} = D - a_1, D_{2(II)} = D + b_1$ , and  $D_{3(II)} = D$ . The corresponding gate and carrier signals along with the primary control signal  $(v_{cs})$  are shown in Figure 2.5a. The inductor current and capacitor voltage would be modified accordingly as involved functions of  $a_1$ ,  $b_1$ , and D as given in (2.17)-(2.22) obtained by capacitor charge and inductor volt-second balance principles respectively.

$$i_{L1} = \frac{i_o}{\gamma} (1 - D - b_1) \tag{2.17}$$

$$i_{L2} = \frac{i_o}{\gamma} (1/3 + a_1 + b_1) \tag{2.18}$$

$$i_{L3} = \frac{i_o(D^2 - \frac{5}{3}D + \frac{7}{9} + 2Db_1 + \frac{a_1}{3} - \frac{5}{3}b_1 - a_1b_1)}{(1 - D)\gamma}$$

(2.19)

$$v_{c1} = \frac{V_{in}D^2}{\zeta} - \frac{V_{in}(\frac{5}{9} - b_1^2 - a_1b_1 + \frac{5}{3}a_1 + \frac{4}{3}b_1)D}{(\frac{1}{3} + a_1 + b_1)\zeta} + \frac{V_{in}(\frac{7}{9}a_1 - \frac{2}{3}a_1b_1 - \frac{2}{3}b_1^2 + \frac{5}{9}b_1 + \frac{7}{27})}{(\frac{1}{3} + a_1 + b_1)\zeta}$$

(2.20)

$$v_{c2} = \frac{V_{in}}{\zeta} (D^2 - D(2 - b_1) + \frac{1}{3}a_1 - \frac{2}{3}b_1 + \frac{10}{9})$$

(2.21)

$$v_{c3} = \frac{V_{in}}{\zeta} (2D^2 - D(4 + a_1 - 2b_1) + \frac{4}{3}a_1 - \frac{5}{3}b_1 - a_1b_1 + \frac{19}{9})$$

(2.22)

where,  $\zeta = (1-D)(D^2 - D(2+a_1-b_1) + (1+a_1)(1-b_1))$  and  $\gamma = (1-D)^2 - D(a_1 - b_1) + a_1 - b_1 - a_1b_1$ . To impose equal current sharing among all the phases, (2.23) needs to be satisfied (where k is the corresponding converter gain).

$$i_{L1} = i_{L2} = i_{L3} = \frac{ki_o}{3} \tag{2.23}$$

With further simplification of (2.17)-(2.19) by using (2.23), the condition for equal current among all the phases can be derived as (2.24).

$$a_1 = 2/3 - D; \quad b_1 = 0$$

(2.24)

The relationship between duty ratio and gain in this operating region is given in (2.25) which is interestingly independent of  $a_1$  and  $b_1$ .

$$k_{II(1)} = 1/(\frac{5}{9} - \frac{2}{3}D); \qquad D = \frac{1}{6}(5 - \frac{9}{k_{II(1)}})$$

(2.25)

It is worth noting that this condition is only true for  $a_1T_s \leq x_{II}$ , i.e.,  $a_1 \leq (D-1/3)$ , implying  $D \geq 0.5$  beyond which the operating modes would no longer be the same as given in Table 2.2 for Zone II, and condition (2.24) would not anymore ensure equal current sharing. Finally by clubbing the condition in (2.25) it is seen that the minimum gain with asymmetric PWM in Zone II is 4.5, with the current being shared equally among the phases.

#### Case II (Symmetric PWM)

With the similar reasoning as the asymmetric PWM, the duty control signal of phase 1 in symmetric PWM is decreased by  $a_2$ , and that of phase 2 is increased by  $b_2$  as shown in Figure 2.5b along with the carrier signals and the primary control signal  $(v_{cs})$ . Thus the modified duty ratio of each phase becomes:  $D_{1(II)} = D - 2a_2$ ,  $D_{2(II)} = D + 2b_2$ , and  $D_{3(II)} = D$ . Similar to the asymmetric case, the corresponding inductor current and capacitor voltage would be altered as involved functions of  $a_2$ ,  $b_2$ , and D which are not provided here to avoid lengthy repetition. The condition for equal current among all the phases can be derived as (2.26) by using (2.23).

$$a_2 = \frac{4}{5}(2/3 - D); \quad b_2 = \frac{2}{5}(2/3 - D)$$

(2.26)

Finally the relationship between duty ratio and gain in this operating region is given in (2.27) which is again independent of  $a_2$  and  $b_2$ .

$$k_{II(2)} = 1/(\frac{23}{45} - \frac{3}{5}D); \quad D = \frac{23}{27} - \frac{5}{3k_{II(2)}}$$

(2.27)

It is to be noted that this condition is only true for  $a_2T_s \leq x_{II}$ , i.e.,  $a_2 \leq (D-1/3)$ , and  $b_2T_s \leq y_{II}$ , i.e.,  $b_2 \leq (2/3-D)$  Beyond these values, the operating modes would no longer be the same as given in Table 2.2 for Zone II, and (2.26) would not anymore ensure equal current sharing. The limit on  $a_2$  is stringent than on  $b_2$ , in fact, the condition on  $b_2$  is always true for (2.26). The limit on  $a_2$  implies  $D \geq 3/7$ . Thus the range of duty ratio for which (2.23) is satisfied is expanded from asymmetric PWM scheme of [2/3, 1/2] to symmetric PWM scheme of [2/3, 3/7]. Finally by clubbing the condition in (2.27) the minimum gain of 3.94 is obtained for this case with current being shared equally among the phases.

For the rest of the region in this zone i.e., for  $1/3 \le D < 3/7$ , the converter duty ratio modification would be discussed in the next sub-section as the analysis would be similar to that of Zone III.

#### 2.4.2 Zone III

In this zone the current in phase 1 is the highest and that in phase 2 is the least, i.e.,  $i_{L1} > i_{L3} > i_{L2}$  (shown in Section 2.3). Also from Table 2.3 and Figure 2.4c, it can be seen that  $i_{L3}$  is charged from  $t_4$  to  $t_5$  for an interval of  $D_3T_s$  and discharged from  $t_0$  to  $t_4$  and  $t_5$  to  $t_6$  for an interval of  $(1 - D_3)T_s$ ,  $i_{L2}$  is charged for an interval of  $(D_2 + D_3)T_s$  and discharged for an interval of  $(1 - D_2 - D_3)T_s$ , and  $i_{L1}$  is charged for an interval of  $(D_1 + D_2 + D_3)T_s$  and discharged for an interval of  $(1 - D_1 - D_2 - D_3)T_s$ . From this discussion it is clear that the average of  $i_{L3}$  could be increased by increasing the duty ratio of phase 3. But it would also increase the average of the  $i_{L1}$  and  $i_{L2}$ . With similar reasoning the average of  $i_{L2}$  cannot be increased with a simultaneous decrease of  $i_{L1}$  and thus current balance is not possible in this case with interleaved phases.

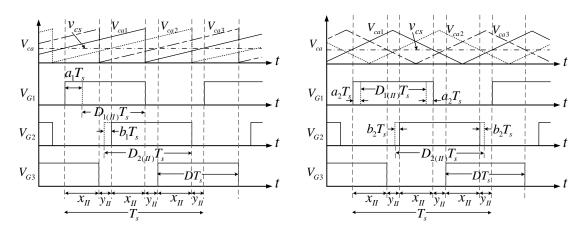

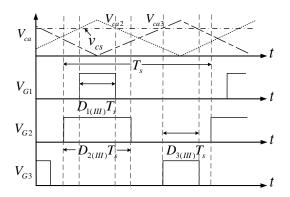

# Case I $(1 \le k_{III} \le 3)$

The average of  $i_{L1}$  would be the minimum if the duty of phase 1 is set to 0, i.e.,  $D_{1(III)} = 0$  and the duty of other phases are varied according to the converter gain requirement. Figure 2.6 shows the duty ratio for this scenario, along with the modulating signals.  $V_M$  are now interleaved by  $360/2 = 180^\circ$ , thus the converter would retain the operating modes of Zone III as discussed in Section 2.3 for  $0 \leq D_{n(III)} \leq 1/2$ rather than for only  $0 \leq D_{n(III)} \leq 1/3$ , where  $D_{n(III)}$  is the modified duty ratio of phase n in this zone; and the analysis would be less complex. The operation in this case for both the asymmetric and symmetric PWM would be similar.

The inductor current and capacitor voltage would be modified accordingly as a function of  $D_{2(III)}$  and  $D_{3(III)}$ . The corresponding expressions are given in (2.28)-(2.33) obtained by capacitor charge and inductor volt-second balance principles respectively.

$$i_{L1} = i_o \tag{2.28}$$

$$i_{L2} = \frac{i_o D_{2(III)}}{(1 - D_{2(III)})} \tag{2.29}$$

$$i_{L3} = \frac{i_o D_{3(III)}}{(1 - D_{2(III)})(1 - D_{3(III)})}$$

(2.30)

$$v_{c1} = 0$$

(2.31)

**Figure 2.6:** Adjusted Duty Ratio of Three Phases to Reduce the RMS Current Error in Zone III (Case 1) Operating Region for 3-Phase EDR Boost with  $1 \le k_{III} \le 3$ .

$$v_{c2} = \frac{V_{in} D_{2(III)}}{(1 - D_{2(III)})(1 - D_{3(III)})}$$

(2.32)

$$v_{c3} = \frac{V_{in}}{(1 - D_{2(III)})(1 - D_{3(III)})}$$

(2.33)

As  $i_{L1}$  in (2.28) is independent of the duty ratio, equal current sharing is not a function of  $D_{2(III)}$  and  $D_{3(III)}$  anymore, and under only one condition with  $D_{2(III)} =$ 1/2 and  $D_{3(III)} = 1/3$ , (2.23) holds true where each phase current is equal to  $i_o$  i.e.,  $i_{L1} = i_{L2} = i_{L3} = i_o = i_{in}/3$ . And the converter gain at this condition is 3 as obtained from the converter gain relationship given in (2.34).

$$k_{III(1)} = \frac{1}{(1 - D_{2(III)})(1 - D_{3(III)})}$$

(2.34)

Further from (2.28)-(2.30) it is clear that for a given converter gain, the current in phase 1 is constant while that of phase 2 and 3 are variable depending on the values of  $D_{2(III)}$  and  $D_{3(III)}$ . Thus a minimization problem to find the best combination of  $D_{2(III)}$  and  $D_{3(III)}$  can be formulated so as to decrease the per unit RMS error of the phase current  $i_e$  (2.35), with the equality constraint on converter gain (2.34) and inequality constraint on the duty ratios (2.36) ensuring no overlap of the phases with 180° interleaving.

$$i_e = \frac{1}{\sqrt{3}i_{in}} \left[ \left(\frac{i_{in}}{3} - i_{L1}\right)^2 + \left(\frac{i_{in}}{3} - i_{L2}\right)^2 + \left(\frac{i_{in}}{3} - i_{L3}\right)^2 \right]^{0.5}$$

(2.35)

where,  $i_{in} = i_{L1} + i_{L2} + i_{L3} = k_{III}i_o$

$$D_{2(III)} \le 0.5$$

$D_{3(III)} \le 0.5$  (2.36)

This is a non-linear minimization and need not be solved on-line to save on the controller computation time. Optimization solver in MATLAB is used to solve the minimization problem and compute a look-up table in advance with the values of  $D_{2(III)}$  and  $D_{3(III)}$  vs  $k_{III(1)}$  to be used during converter operation.

Alternatively, this can also be solved by Lagrange multiplier method with the problem formulation as defined in (2.37). Here,  $\mathscr{L}$  is the Lagrangian with  $f(D_{2(III)}, D_{3(III)})$ as the function to be minimized subject to the constraint  $g(D_{2(III)}, D_{3(III)})$ .

$$\mathscr{L} = f - \lambda g$$

where,  $f = i_e$

and  $g = k_{III} - \frac{1}{(1 - D_{2(III)})(1 - D_{3(III)})} = 0$  (2.37)

(2.38) gives the duty ratio values in terms of the converter gain as obtained from solving the Lagrangian  $\mathscr{L}$ . The solution is similar to that obtained from the previous minimization technique from MATLAB.

$$D_{2(III)} = \frac{k_{III} - 1}{k_{III} + 1}; \qquad D_{3(III)} = \frac{D_{2(III)}}{1 + D_{2(III)}}$$

(2.38)

Case II  $(3 \le k_{III} \le 3.94)$

Until now the converter operation with modified duty ratio is discussed with gain in the range of [9, 3.94] and [3, 1]. For the rest of the operating region, the function would be mostly similar to case 1 in Zone III but with modified  $D_{1(III)}$ . In case

**Figure 2.7:** Modified Duty Ratio of Three Phases Ensuring Equal Current Sharing in Zone III (Case 2) for 3-Phase EDR Boost with  $3 \le k_{III} \le 3.94$ .

1,  $i_{L1}$  is always higher than corresponding  $i_{L2}$  and  $i_{L3}$ , whereas, with k > 3,  $i_{L1}$  becomes less than the rest two. Thus  $D_{1(III)}$  is modified to be non-zero and overlap  $D_{2(III)}$  in phase, which increases the average value of  $i_{L1}$  and modifies  $i_{L2}$  but has no effect on the converter gain or other capacitor voltages. The corresponding gate and modulating signals are shown in Figure 2.7.

The modified current expressions are given in (2.39) and (2.40), the rest of the variables remain the same as in case 1. Here the constraint (2.36) is modified to  $D_{2(III)} + D_{3(III)} \leq 1$ , and only with symmetrical PWM phase 2 and 3 overlapping is restricted, which are still 180° interleaved.

$$i_{L1} = \frac{i_o}{(1 - D_{1(III)})} \tag{2.39}$$

$$i_{L2} = \frac{i_o(D_{2(III)} - D_{1(III)})}{(1 - D_{1(III)})(1 - D_{2(III)})}$$

(2.40)

Again by applying (2.23), (2.41) is obtained, i.e., under this condition equal current sharing is ensured in this region.

$$D_{1(III)} = 1 - \frac{3}{k_{III(2)}}; \quad D_{2(III)} = \frac{1}{2} + \frac{D_{1(III)}}{2}$$

Figure 2.8: Implementation Flow Diagram of Current Sharing with Modified Duty Ratio for 3-Phase EDR Boost.

$$D_{3(III)} = 1/3 \tag{2.41}$$

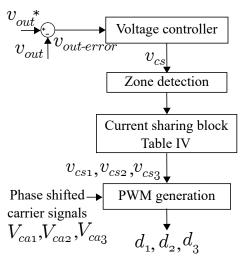

# 2.4.3 Implementation

Table 2.4 provides the summary of operating duty ratio, the status of current sharing, and converter gain at different operating regions for a quick reference. Figure 2.8 shows the implementation flow diagram of current sharing with modified duty ratio for 3-phase EDR boost. The output voltage error (difference of a reference voltage and the sensed output voltage) is fed to a voltage controller to generate a common control signal  $v_{cs}$ . The operating zone is determined based on its value which then determines the individual control signal for each phase in the current sharing block. Finally, the corresponding PWM signals are generated by comparing the control signals with the phase shifted carrier signals.

#### 2.5 Discontinuous Conduction Mode

The EDR boost converter might also potentially operate in discontinuous conduction mode (DCM) when the load current is quite low. For an M phase converter, all the boost inductors would still share the current equally inherently in each of Zone I to Zone M - 1, while only Zone M would not experience inherent equal current sharing. In fact, in Zone M, the inductor current for phases 2 to M will have negative excursion (phase 1 is defined as the one which is closest to the input as seen from Figure 2.1) which would lead to circulating current resulting in higher RMS current of all the inductors, diodes, and MOSFETs, and consequently lower efficiency. Whereas, in buck version of EDR converter, the DCM operation would lead to negative current excursion and uneven current sharing in all the possible operating zones. Shenoy and Amaro [80] has proposed an improved interleaving technique to address the negative phase current problem in 2-phase converter by uneven phase interleaving approach. In this chapter, the analysis of improved modulation technique for equal phase current sharing is primarily focused on the CCM operation of EDR boost.

# 2.6 Experimental Results

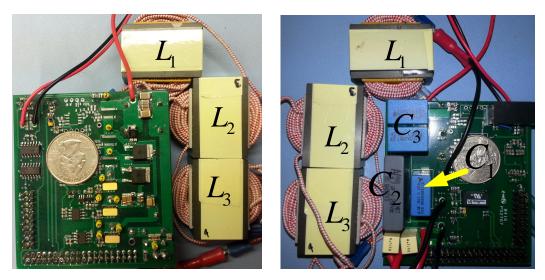

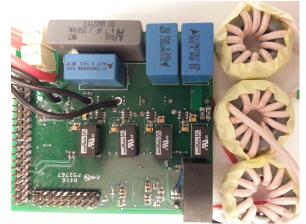

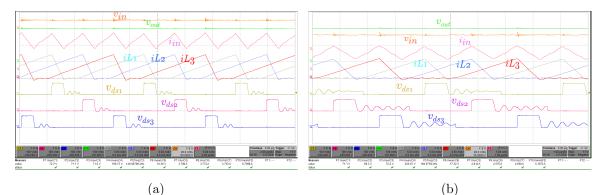

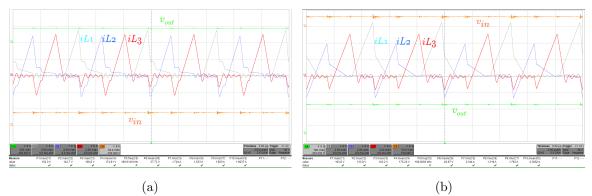

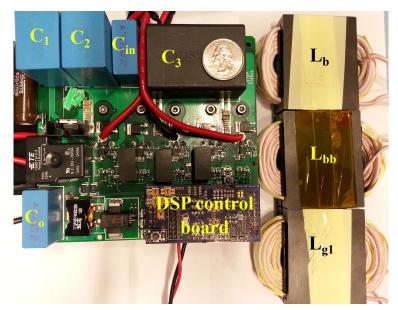

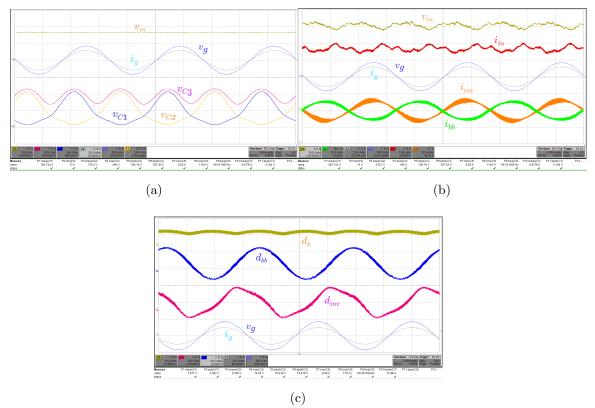

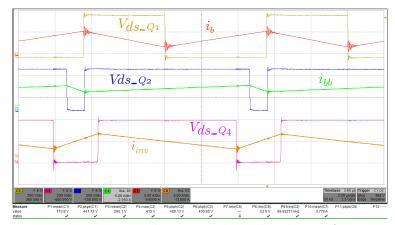

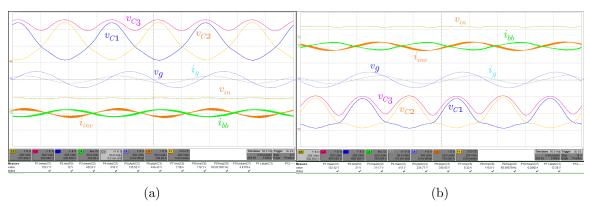

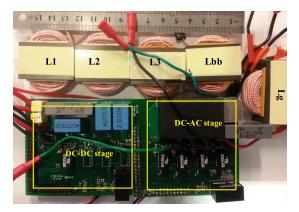

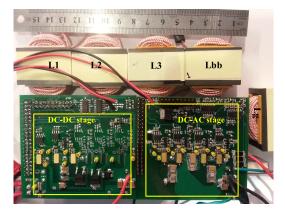

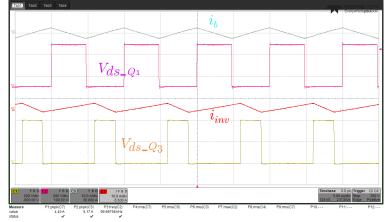

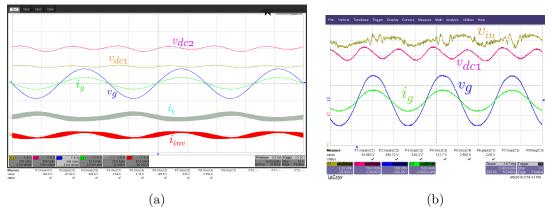

#### 2.6.1 Hardware Prototype