# Gallium Phosphide Integrated with Silicon Heterojunction Solar Cells

by

# Chaomin Zhang

A Dissertation Presented in Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy

Approved September 2017 by the Graduate Supervisory Committee:

Christiana Honsberg, Co-Chair Richard King, Co-chair Stephen Goodnick Nikolai Faleev Stuart Bowden

ARIZONA STATE UNIVERSITY

December 2017

### **ABSTRACT**

It has been a long-standing goal to epitaxially integrate III-V alloys with Si substrates which can enable low-cost microelectronic and optoelectronic systems. Among the III-V alloys, gallium phosphide (GaP) is a strong candidate, especially for solar cells applications. Gallium phosphide with small lattice mismatch (~0.4%) to Si enables coherent/pseudomorphic epitaxial growth with little crystalline defect creation. The band offset between Si and GaP suggests that GaP can function as an electron-selective contact, and it has been theoretically shown that GaP/Si integrated solar cells have the potential to overcome the limitations of common a-Si based heterojunction (SHJ) solar cells.

Despite the promising potential of GaP/Si heterojunction solar cells, there are two main obstacles to realize high performance photovoltaic devices from this structure. First, the growth of the polar material (GaP) on the non-polar material (Si) is a challenge in how to suppress the formation of structural defects, such as anti-phase domains (APD). Further, it is widely observed that the minority-carrier lifetime of the Si substrates is significantly decreased during epitaxially growth of GaP on Si.

In this dissertation, two different GaP growth methods were compared and analyzed, including migration-enhanced epitaxy (MEE) and traditional molecular beam epitaxy (MBE). High quality GaP can be realized on precisely oriented (001) Si substrates by MBE growth, and the investigation of structural defect creation in the GaP/Si epitaxial structures was conducted using high resolution X-ray diffraction (HRXRD) and high resolution transmission electron microscopy (HRTEM).

The mechanisms responsible for lifetime degradation were further investigated, and it was found that external fast diffusors are the origin for the degradation. Two practical

approaches including the use of both a  $SiN_x$  diffusion barrier layer and P-diffused layers, to suppress the Si minority-carrier lifetime degradation during GaP epitaxial growth on Si by MBE were proposed. To achieve high performance of GaP/Si solar cells, different GaP/Si structures were designed, fabricated and compared, including GaP as a heteroemitter, GaP as a heterojunction on the rear side, inserting passivation membrane layers at the GaP/Si interface, and GaP/wet-oxide functioning as a passivation contact. A designed of a-Si free carrier-selective contact  $MoO_x/Si/GaP$  solar cells demonstrated 14.1% power conversion efficiency.

#### ACKNOWLEDGMENTS

First of all, I would like to deeply appreciate Dr. Christiana Honsberg for the opportunity to be a part of the group and one part of QESST. Dr. Honsberg has tons of knowledge and ideas from years of experience in photovoltaics. I am extremely grateful to have your support and guidance through my career as a graduate student in the group. And I also would like to thank Dr. Richard King as my co-advisor and I gained a lot knowledge from your guidance. And thank you for the time you spent to revise my manuscripts.

Then, I would like to thank Dr. Stephen Goodnick, who provided me a chance to work on photovoltaics and introduced me into Dr. Honsberg's group. I appreciate your enthusiasm and patient to help and support for me. I am grateful to Dr. Nikolai Faleev for teaching me the MBE operations and crystalline characterization tools. My GaP growth would never go smoothly if it is not your expertise and knowledge.

I am seriously indebted to all my coworkers in the solar power lab. To Dr. Yeongho Kim, who really taught me how to be a researcher and taught me the processing of III-V solar cells and all kinds of characterization methods. You are always ready to help me and willing to share your knowledge and experience. It would be more difficult to complete this work without your help. To Dr. Som Dahal, who always guides me a lot in my career as a friend and to the hours we worked side-by-side. To Dr. Stanislau Yur'yevich Herasimenka, your knowledge and experience in Si solar cells and your knowledge in photovoltaics help me a lot. To Dr. Bill Dauksher, who is the lab manager of solar power lab, without your maintenance and management of the lab, my processing would never be smooth. To Ehsan Vadiee, who is always willing to spend his personal time helping me

check my abstracts and manuscripts. To Dr. Aymeric Maros, who helped me do some Hall measurements for measuring the doping levels in GaP layers.

I also would like to thank the "FPACE" team for the valuable discussions in the internal meetings, including Dr. Mathieu Boccard, Dr. Laura Ding, Dr. Mariana Bertoni, Dr. Zachary Holman, Dr. Stuart Bowden. Especially, Dr. Mathieu Boccard and Dr. Laura Ding, who spent a lot time helping me prepare wafers. I learnt a lot from the meetings and conversations with you guys, especially, the meetings we had every Friday morning at 8 o'clock. I also would like to thank Dr. David Smith and Allison Boley for the TEM measurements.

I would like to thank Dr. Sarah Kurz and Dr. Kirstin Alberi for the opportunity to work in NREL in the summer, from which I learnt a lot about the epitaxial growth. I would like to thank Dr. Dan Beaton and Dr. Kwangwook Park for teaching the MBE growth and help in research in NREL.

Most importantly, I would like to thank my family and friends for all the support throughout my lifetime. My parents and two older brothers for the unwavering support for me and my education. It is not easy for me having the oversea education alone for the last six years, thank you very much for the endless support and encouragement. I love you guys and I always feel fortune to have such an awesome family. I cannot wait for all the good times we will have as a family in the future.

## TABLE OF CONTENTS

|                                                  | Page |

|--------------------------------------------------|------|

| LIST OF TABLES                                   | viii |

| LIST OF FIGURES                                  | ix   |

| CHAPTER                                          |      |

| 1 INTRODUCTION                                   | 1    |

| 1.1 Need for Solar Energy                        | 1    |

| 1.2 The Potential of III-V/Si Solar Cells        | 2    |

| 1.3 Epitaxial Challenges                         | 4    |

| 1.4 GaP/Si Heterojunction Solar Cells            | 7    |

| 1.5 Thesis Structure                             | 8    |

| 2 GAP EPI-GROWTH ON SI VIA MBE                   | 10   |

| 2.1 Introduction                                 | 10   |

| 2.2 Experimental Setup                           | 11   |

| 2.2.1 Epitaxial Growth of GaP-Si(001) structures | 11   |

| 2.2.2 Characterization Methods                   | 13   |

| 2.3 Results and Discussion                       | 14   |

| 2.3.1 Investigation of MEE-grown Structures      | 14   |

| 2.3.2 Investigation of MBE-grown Structures      | 16   |

| 2.4 Conclusions                                  | 25   |

| 3 SI MINORITY-CARRIER LIFETIME CHALLENGES AND    |      |

| APPROACHES                                       | 26   |

| 3.1 Introduction                                 | 26   |

| CHAPTER  |                                                                       | Page |

|----------|-----------------------------------------------------------------------|------|

| 3.2 Exp  | perimental Details                                                    | 27   |

| 3.3 Si I | ifetime Degradation                                                   | 30   |

| 3.4 App  | proaches to Recover Lifetime                                          | 36   |

| 3.4.1    | Impact of Gettering on the Degraded Wafers                            | 36   |

| 3.4.2    | SiN <sub>x</sub> Protective Coating                                   | 37   |

| 3.4.3    | Phosphorus Diffusion Layers                                           | 44   |

| 3.5 Cor  | nclusions                                                             | 46   |

| 4        | GAP AS A HETEROEMITTER FOR SI SOLAR CELLLS                            | 47   |

| 4.1 Intr | oduction                                                              | 47   |

| 4.2 Exp  | perimental Details                                                    | 48   |

| 4.3 Res  | sults and Analysis                                                    | 50   |

| 4.3.1    | Device A and Device B                                                 | 50   |

| 4.3.2    | Unintentionally Doped GaP Layers                                      | 54   |

| 4.4 Cor  | nclusions                                                             | 56   |

| 5        | GAP AS A BACK ELECTRON-SELECTIVE CONTACT                              | 57   |

| 5.1 Intr | oduction                                                              | 57   |

| 5.2 Exp  | perimental Details                                                    | 58   |

| 5.3 Res  | sults and Analysis                                                    | 63   |

| 5.3.1    | GaP/Si Solar Cell Grown at Low Temperature (structure I)              | 63   |

| 5.3.2    | GaP/Si Solar Cell with "n+ layer" as a Gettering Agent (structure II) | 65   |

| 5.3.3    | a-Si/n-Si/n+Si/GaP Solar Cell (structure IIIA)                        | 66   |

| 5.3.4    | MoO <sub>X</sub> /n-Si/n+Si/GaP Solar Cell (structure IIIB)           | 69   |

| CHAPTER  |                                                                  | Page |

|----------|------------------------------------------------------------------|------|

| 5.3.5    | GaP/Si Structure with SiN <sub>x</sub> Protection (structure IV) | 73   |

| 5.4 Dev  | vice Analysis                                                    | 75   |

| 5.4.1    | Surface Recombination of GaP/Si Interface                        | 75   |

| 5.4.2    | Band-alignment at the GaP/Si Interface                           | 79   |

| 5.5 Cor  | nclusions                                                        | 80   |

| 6        | GAP ON PASSIVATION MEMBRANE LAYERS                               | 82   |

| 6.1 Intr | oduction                                                         | 82   |

| 6.2 Diff | ferent Passivation Membrane Layers                               | 83   |

| 6.2.1    | Tunnel Oxide                                                     | 83   |

| 6.2.2    | a-Si or SiC Layers                                               | 85   |

| 6.2.3    | ALD-Al <sub>2</sub> O <sub>3</sub> Layers                        | 90   |

| 6.3 Cor  | nclusions                                                        | 92   |

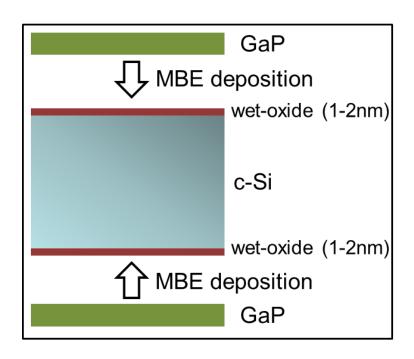

| 7        | GAP/WET-OXIDE AS A PASSIVATION CONTACT                           | 93   |

| 7.1 Syn  | mmetric GaP/wet-oxide Structure                                  | 93   |

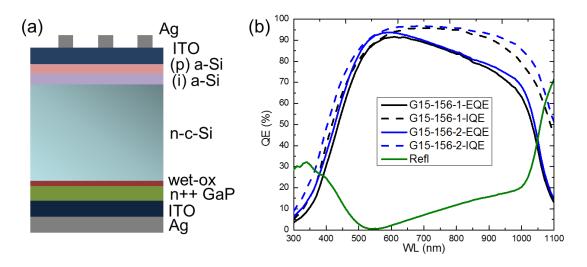

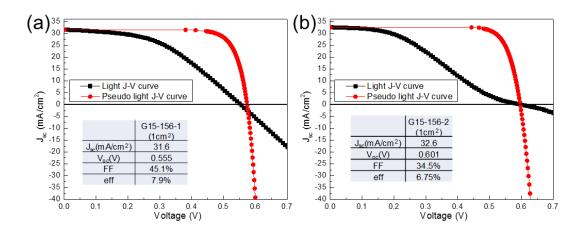

| 7.2 GaI  | P/wet-oxide for Solar Cell Applications                          | 96   |

| 7.3 Sun  | nmary                                                            | 97   |

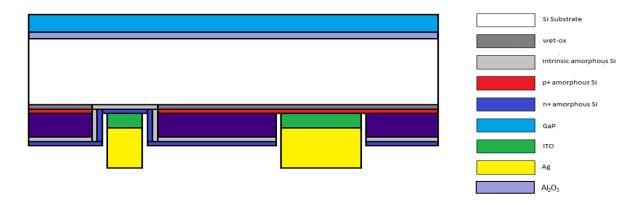

| 8        | CONCLUSION AND FUTURE WORK                                       | 99   |

| 8.1 Cor  | nclusion                                                         | 99   |

| 8.2 Fut  | ure Work                                                         | 101  |

| DEEEDE   | NCES                                                             | 105  |

# LIST OF TABLES

| Table Page                                                                                 |

|--------------------------------------------------------------------------------------------|

| 2-1 XRD Results of Various Thicknesses MBE-grown GaP/Si Samples                            |

| 2-2 RSM Results of Various Thicknesses MBE-grown GaP/Si Samples                            |

| 4-1 Electrical Characteristics of GaP/Si Solar Cells under 1 Sun Illumination              |

| 4-2 Parameters of GaP/p-Si Solar Cells with Various GaP Thickness Compared to the          |

| Reference Si Cell                                                                          |

| 5-1 Light and Pseudo J-V Values for GaP/Si Heterojunction Solar Cells of Structure I, II,  |

| IIIA and B64                                                                               |

| 5-2 Double Diode Device Parameters of Structure IIIA and IIIB                              |

| 6-1 Parameters of GaP/Si with A-Si Passivation Layers Structures                           |

| 6-2 The Parameters of GaP/Si Solar Cells that GaP Deposited at 340°C and 280°C 90          |

| 6-3 Minority-carrier Lifetime and $iV_{oc}$ of Different Doping GaP Deposited on $Al_2O_3$ |

| Coated n-Si and p-Si Substrates91                                                          |

# LIST OF FIGURES

| Figure                                                                                                 |

|--------------------------------------------------------------------------------------------------------|

| 1-1 The Evolution of Annual PV Installations [1]                                                       |

| 1-2 Cost Analysis of a High Concentration PV Module and Inserted Figure is a Typical                   |

| Structure of a Lattice-match Device on a Ge Substrate [6]                                              |

| 1-3 Growth of a Heteroepitaxial Layer on a Mismatched Substrate with Two Different                     |

| Cubic Lattice Constants: (a) Pseudomorphic Layer; (b) Partially Relaxed                                |

| Layer (Star Mark Presents the Misfit Dislocations)                                                     |

| 1-4 Lattice Constants and Bandgap of III-Vs, Si, and Ge at 300 K, and AM1.5G                           |

| Spectrum. 5                                                                                            |

| 1-5 The Lattice Constant of Gap and Si at Various Temperatures, and Also the                           |

| Corresponding Lattice Mismatch Strain. 6                                                               |

| 1-6 (a) Typical Front Junction Silicon Heterojunction (SHJ) cell. (b) Schematic of                     |

| Carrier-elective Contacts (CSC).                                                                       |

| 2-1 (a) DC Coherent $\omega$ -2 $\theta$ RCs Measured in the Vicinity of Si-GaP (004) Reflections. (b) |

| The Corresponding GaP TC ω RCs                                                                         |

| 2-2 TEM Cross-section Micrographs of MEE Grown Structures: (a) GaP Grown on                            |

| Precise Si Wafer (MEE-II structure), (b) GaP Grown on Offcut Si Wafer                                  |

| (MEE-I Structure)                                                                                      |

| 2-3 1μm×1μm AFM for Different P/Ga Flux Ratio: (a) 6.9; (b) 5.9; (c) 4.8; (d) 4.5; (e)                 |

| 4.3; (f) 3.1                                                                                           |

| 2-4 (a) DC Coherent $\omega$ -2 $\theta$ RCs Measured in the Vicinity of Si-GaP (004) Reflections. (b) |

| The Corresponding GaP TC ω RCs                                                                         |

| Figure                                                                                                         |

|----------------------------------------------------------------------------------------------------------------|

| 2-5 TEM Images of 37 nm GaP Sample with Optimized MBE Growth Conditions 18                                     |

| 2-6 DC Coherent ω-2θ RCs Measured in the of Vicinity of Si-GaP (004) Reflections.                              |

| Black and Red bars Specify the Angle Position of Fully Elastically Stressed                                    |

| GaP Layer and Si(004) Substrate Peaks. TC $\omega$ RCs Shown Insert                                            |

| 2-7 Experimental DC Coherent ω-2θ Rocking Curve of 250 nm GaP Compared to                                      |

| Simulation Curve                                                                                               |

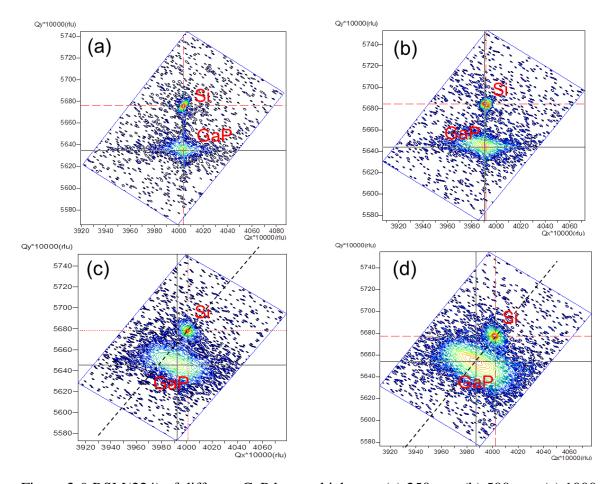

| 2-8 RSM(004) of Different GaP Layers Thickness: (a) 250 nm, (b) 500 nm, (c) 1000 nm                            |

| and (d) 2000 nm                                                                                                |

| 2-9 RSM(224) of Different GaP Layers Thickness: (a) 250 nm, (b) 500 nm, (c) 1000 nm                            |

| and (d) 2000 nm                                                                                                |

| 2-10 TEM of Different GaP Layers Thickness: (a) 250 nm, (b) 500 nm, (c) 1000 nm and                            |

| (d) 2000 nm                                                                                                    |

| 3-1 Injection-dependent Effective Minority-carrier Lifetimes of Different FZ-Si Wafers:                        |

| a Reference that was not Processed in the MBE, a Sample with GaP Grown                                         |

| on One Side, and the Same Sample after Etching the GaP Layer and ${\sim}3~\mu\text{m}$                         |

| of Silicon from Each Surface                                                                                   |

| 3-2 Effective Minority-carrier Lifetime (at the injection level of $1 \times 10^{15}$ cm <sup>-3</sup> ) of Si |

| Wafers Annealed in the MBE Chamber for 30 min at Different                                                     |

| Temperatures                                                                                                   |

| 3-3 Effective Minority-carrier Lifetime (at an Injection Level of $1\times10^{15}$ cm <sup>-3</sup> ) of       |

| Different Types of Si wafers (n-FZ, p-FZ, and n-Cz) before and after 800°C                                     |

| Annealing in the MBE Chamber for 30 min                                                                        |

| Figure        | Page                                                                                                 |

|---------------|------------------------------------------------------------------------------------------------------|

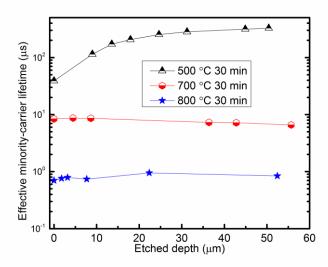

| 3-4 Depth-p   | rofile of the Effective Minority-carrier Lifetime (at the Injection Level of                         |

|               | 1×10 <sup>15</sup> cm <sup>-3</sup> ) for n-FZ Si Samples Annealed at Different Temperatures         |

|               | (500°C, 700°C, 800°C)                                                                                |

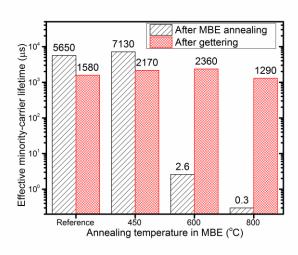

| 3-5 Effective | e Minority-carrier Lifetime of n-Fz Si Samples Annealed in the MBE                                   |

|               | Chamber at Different Temperatures before and after Gettering by POCl <sub>3</sub>                    |

|               | Diffusion (at an Injection level of 1×10 <sup>15</sup> cm <sup>-3</sup> , except for the 800°C-      |

|               | annealed Samples at $1\times10^{14}\mathrm{cm}^{-3}$ ). The "Reference" Wafer was not MBE-           |

|               | annealed                                                                                             |

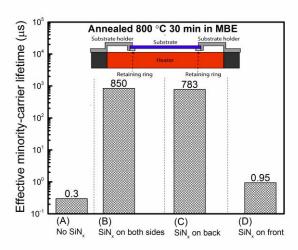

| 3-6 Effective | e Minority-carrier Lifetime of Fz (n) Si wafers with a SiN <sub>x</sub> Coating                      |

|               | Deposited on (A) no SiN <sub>x</sub> , (B) both sides, (C) back side, and (D) front side,            |

|               | after the Indicated Treatment (at an Injection Level of 1x10 <sup>15</sup> cm <sup>-3</sup> , except |

|               | for the Annealed Sample in (A) and (C) at $1x10^{14}\text{cm}^{-3}$ ). The $SiN_x$ films             |

|               | were Removed by Etching and the Wafers Surface Re-passivated before                                  |

|               | Lifetime Measurement                                                                                 |

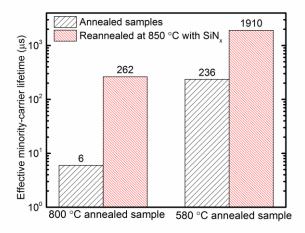

| 3-7 Change    | in the Effective Minority-carrier Lifetime (at an Injection Level of $1\times10^{15}$                |

|               | cm <sup>-3</sup> ) of High Resistivity FZ Rilicon Samples Annealed Initially without                 |

|               | $SiN_x$ Protective Coating and Re-annealed with $SiN_x$ Coated on the Back in                        |

|               | MBE Chamber at 850 °C for 8 min                                                                      |

| 3-8 External  | Quantum Efficiency of the Solar Cells Processed from the Thermally                                   |

|               | Treated p-type FZ Si Wafers T                                                                        |

| 3-9 Schemat   | ic of the Growth Sequence of GaP and the RHEED Patterns Observed                                     |

|               | During the Growth                                                                                    |

| Figure                                  | Page                                      |

|-----------------------------------------|-------------------------------------------|

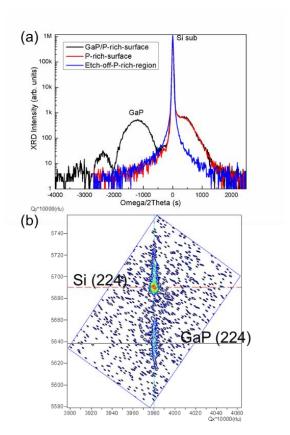

| 3-10 (a) XRD ω Rocking Curve of the GaP | Layer and (b) Reciprocal Space Map Around |

| 3-10 (a) XRD $\omega$ Rocking Curve of the GaP Layer and (b) Reciprocal Space Map Around |

|------------------------------------------------------------------------------------------|

| the Asymmetric Si/GaP (224) Diffraction Spots. The Same Qx Position of                   |

| the Both Si and GaP Diffraction Spots, Elongated Along the Qy Direction,                 |

| Demonstrates the Lack of Relaxation of the Initial Elastic Stress in GaP                 |

| Layer During Epitaxial Growth                                                            |

| 3-11 Si Bulk Lifetime as a Function of Injected Minority-carrier Density for the a-Si:H  |

| Passivated GaP/Si Sample Before (as-deposited) and After the RTA 44                      |

| 3-12 The Effective Minority-carrier Lifetime of Si Wafers Annealed in the MBE            |

| Chamber at Different Temperatures for 30 minues At the Injection Level of                |

| 10 <sup>15</sup> cm <sup>-3</sup> (Error Bars Are Also Indicated)                        |

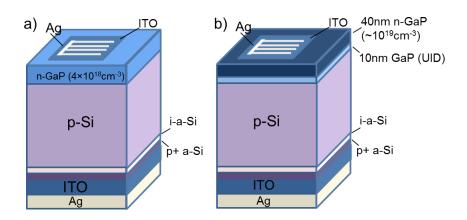

| 4-1 The Schematic Structures of GaP/Si Solar Cell Devices: (a) Device A and (b) Device   |

| B50                                                                                      |

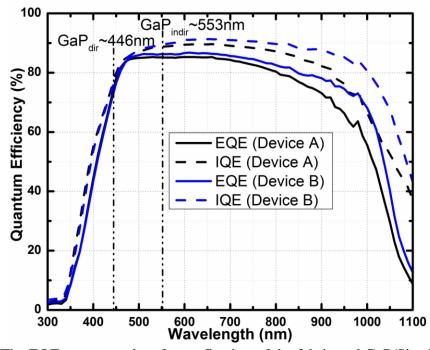

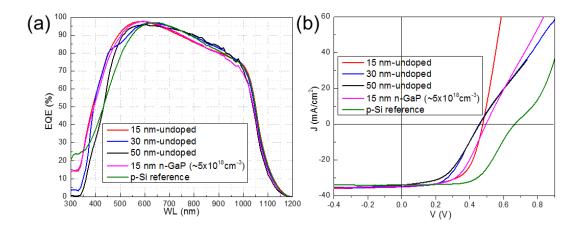

| 4-2 The EQE Spectra and Surface Reflection of the Fabricated GaP/Si Solar Cells 53       |

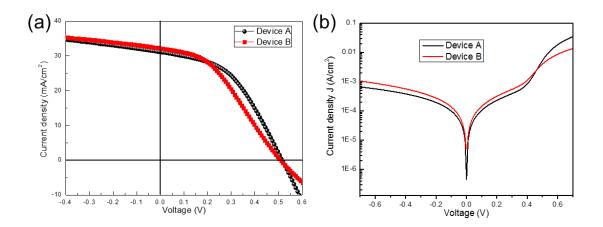

| 4-3 (a) AM1.5G Illuminated Current-voltage; (b) Dark Current-voltage of Device A and     |

| Device B                                                                                 |

| 4-4 (a) External Quantum Efficiency (EQE) and (b) Light J-V Curves of GaP/p-Si Solar     |

| Cells with Various GaP Thickness Compared to the Reference Si Cell 55                    |

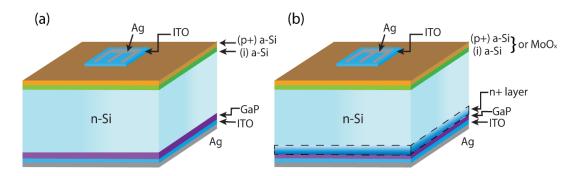

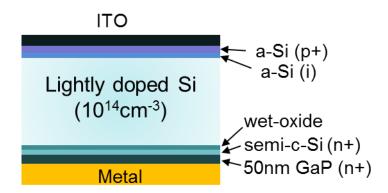

| 5-1 (a) Schematic of Structure I, Structure II and Structure IV. (b) Schematic Structure |

| IIIA with a-Si-based Layers On Top. Structure IIIB Has MoO <sub>X</sub> Layer            |

| Instead of a-Si as a Hole Selective Contact. The Active Area of The Solar                |

| Cells is Defined as the Area within the Aperture $(1 \times 1 \text{ cm}^2)$ that is not |

| Shaded by Metal 60                                                                       |

| Figure        | Page                                                                               |

|---------------|------------------------------------------------------------------------------------|

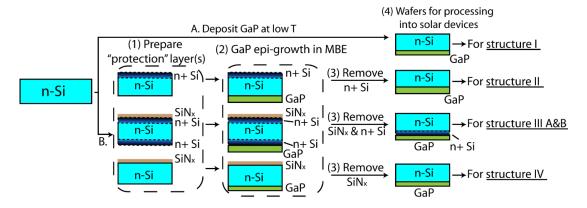

| 5-2 Simplifie | ed Schematic Diagram of Preparing GaP/Si Structures for Structure I, II,           |

|               | IIIA, IIIB and IV                                                                  |

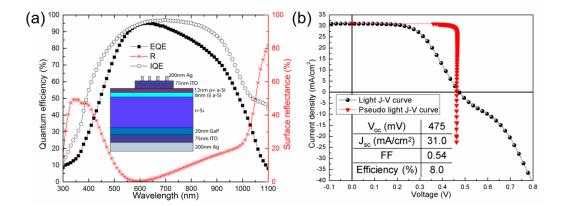

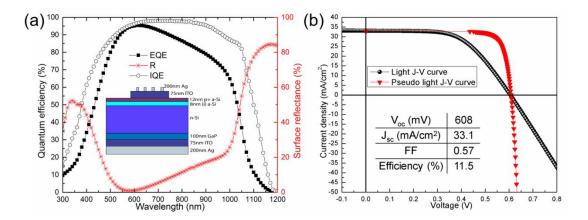

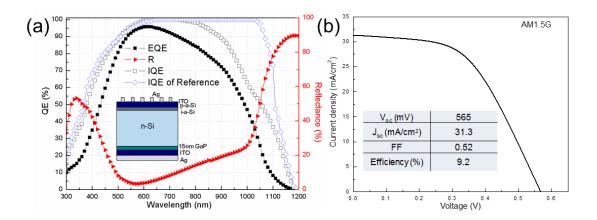

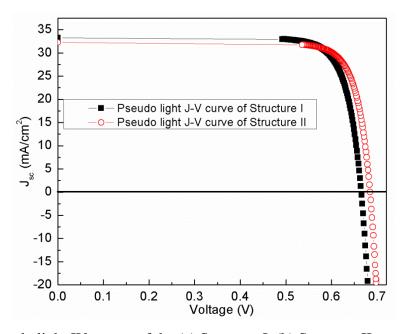

| 5-3 (a) EQE   | , IQE, and Surface Reflectance of Structure I. (b) Light and Pseudo J-V            |

|               | Curves of Structure I (under AM1.5G Spectrum with Irradiation Intensity            |

|               | of 1000 W.m <sup>-2</sup> ). IQE is Generated from the EQE Data and the Absorption |

|               | Data according to IQE = $EQE/(1 - R)$ . 64                                         |

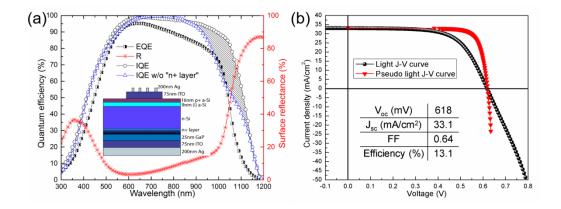

| 5-4 (a) EQE   | , IQE, and Surface Reflectance of Structure II. (b) Light and Pseudo J-V           |

|               | Curves of Structure II (under AM1.5G Condition with Irradiation Intensity          |

|               | of 1000 W/m <sup>2</sup> )                                                         |

| 5-5 (a) Doub  | ole Crystal ω-2θ Rocking Curves Scanned in the Vicinity of (004) Reflection        |

|               | (under Symmetric Geometry). (b) Reciprocal Space Map of the GaP/n+/Si              |

|               | Sample at (224) Reflection. 67                                                     |

| 5-6 (a) EQE   | , IQE and Surface Reflectance of Structure IIIA. (b) Light and Pseudo J-V          |

|               | Curves of Structure IIIA (under AM1.5G Condition with Irradiation                  |

|               | Intensity of 1000 W.m <sup>-2</sup> ). The Shaded Region Shows the Optical Gain at |

|               | Long Wavelength Regime (~900 nm - ~1150 nm) Due to Implementation                  |

|               | of the n+ Layer between the n-Si and the n-GaP Layers                              |

| Page Page                                                                                   |  |  |

|---------------------------------------------------------------------------------------------|--|--|

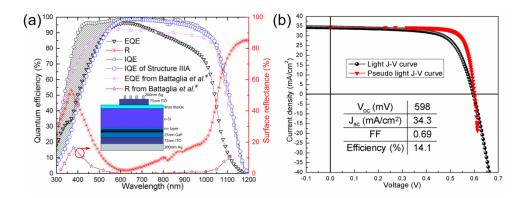

| 5-7 (a) The EQE, IQE and Surface Reflectance of Structure IIIB (Compared to the IQE         |  |  |

| of Structure IIIA and the EQE of $MoO_x/Si/a$ -Si Solar Cell Reported by                    |  |  |

| Battaglia et al. [56]). (b) Light and Pseudo J-V Curves of Structure IIIB                   |  |  |

| (under AM1.5G Condition with Irradiation Intensity of $1000 \text{ W/m}^2$ ). The           |  |  |

| Shaded Region Shows the Difference between the IQE Curves of Structures                     |  |  |

| IIIA and IIIB                                                                               |  |  |

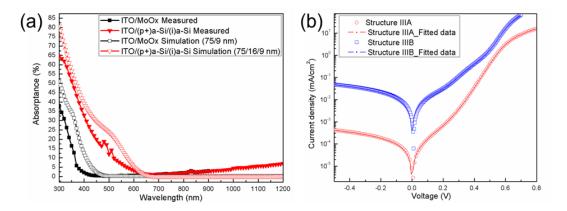

| 5-8 (a) Simulated and Measured Absorptance of ITO/MoO <sub>x</sub> and ITO/(p+)a-Si/(i)a-Si |  |  |

| Front Layers Used in the GaP/Si Heterojunction Solar Cells. (b)                             |  |  |

| Experimental and Simulated Dark J-V Curves of 13.1% and 14.1%-                              |  |  |

| Efficient GaP/Si Heterojunction Solar Cells. The Curve was Fitted with a                    |  |  |

| Two-diode Model with $R_{\text{SH}}$ , $R_{\text{S}}$ , and Two Recombination Terms (No     |  |  |

| Lifetime-minority Correction Factor was Considered)                                         |  |  |

| 5-9 (a) EQE, IQE and Surface Reflectance of the n-Si/GaP Solar Cell and the n-Si            |  |  |

| Reference Cell (Inset: the n-Si/GaP Schematic Structure). (b) The                           |  |  |

| Corresponding Light I-V Curve74                                                             |  |  |

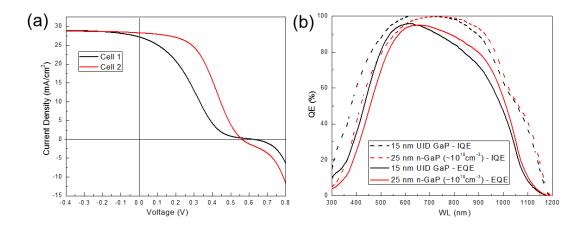

| 5-10 (a) Light I-V Curves of n-Si/n-GaP Solar Cells. (b) The QE (EQE and IQE) Spectra       |  |  |

| of GaP/Si Solar Cells with Different Doping in GaP Layers                                   |  |  |

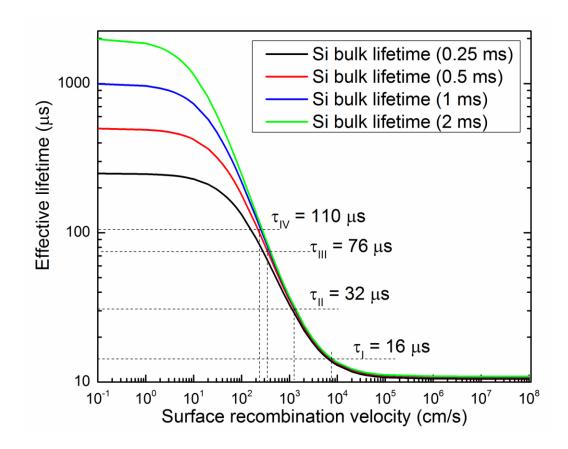

| 5-11 The Effective Lifetime as a Function of Surface Recombination Velocity at              |  |  |

| Different Si Bulk Lifetimes. The Effective Lifetimes of Structure I, II, III,               |  |  |

| and IV are Marked78                                                                         |  |  |

| Figure |  | Page |

|--------|--|------|

|        |  |      |

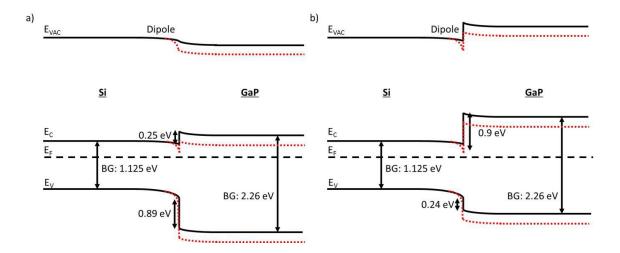

| 5-12 (a) Band Diagram Predicted by Anderson's Rule and (b) Band Diagram Derived          |

|------------------------------------------------------------------------------------------|

| from the Extensive X-ray Photoelectron Spectroscopy (XPS) and Cross-                     |

| sectional Kelvin Probe Force Microscopy (KPFM) Data. The Black Curve                     |

| Presents the Band Alignment for Lightly n-doped Si. The Red Curve Takes                  |

| an n+-doped Si Layer at the Interface into Account. Therefore, the                       |

| Conduction Band Tunneling Barrier Is Decreased. [7]                                      |

| 6-1 The Schematic Device Structure of GaP Integrated with Tunnel Oxide Solar Cells. 84   |

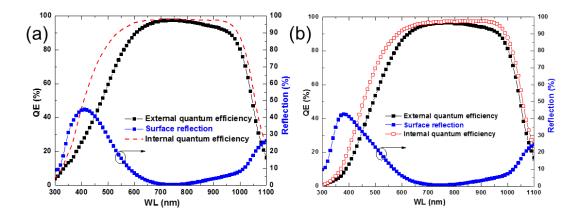

| 6-2 Pseudo Light IV Curves of the (a) Structure I, (b) Structure II                      |

| 6-3 Quantum Efficiency (QE) and Surface Reflection of (a) Structure I, (b) Structure II. |

| 85                                                                                       |

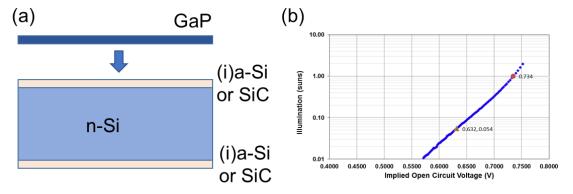

| 6-4 (a) Schematic of GaP Deposited on a-Si or SiC Passivated Si Wafers. (b) Implied      |

| Open Circuit Voltage of the Sample after GaP Deposition                                  |

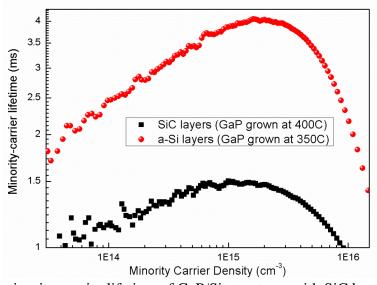

| 6-5 The Minority-carrier Lifetime of GaP/Si Structures with SiC Layers or a-Si Layers 86 |

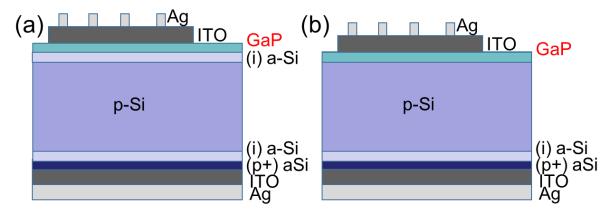

| 6-6 Schematic of the GaP/Si Solar Cell with a-Si Passivation Layers and GaP is as a      |

| Heteroemitter87                                                                          |

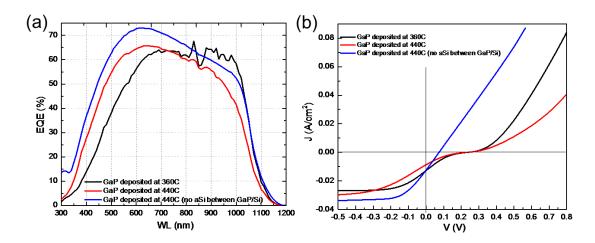

| 6-7 (a) The EQE spectra, and (b) Light-JV Curves of GaP/Si with a-Si Passivation         |

| Layers Structures for GaP Deposited at Two Different Temperatures and                    |

| Compared to the Sample without Passivation Layers                                        |

| 6-8 Schematic of GaP/Si Structure with a-Si Passivation Layers and Si Wafer is           |

| Textured89                                                                               |

| 6-9 (a) The EQE Spectra, and (b) Light-JV Curves of the GaP/Si Solar Cells that GaP      |

| Deposited at 340°C and 280°C                                                             |

| Figure                                                                                                       |

|--------------------------------------------------------------------------------------------------------------|

| 6-10 (a) Schematic of GaP Deposited on Al <sub>2</sub> O <sub>3</sub> Coated Si Substrate. (b) The PL Map of |

| the GaP Deposited on Al <sub>2</sub> O <sub>3</sub> Coated Si Substrate91                                    |

| 6-11 The Minority-carrier Lifetime of GaP with Various Doping Deposited on Al <sub>2</sub> O <sub>3</sub>    |

| Coated (a) n-type and (b) p-type Si Substrates                                                               |

| 7-1 Schematic Symmetrical GaP/wet-oxide/c-Si/wet-oxide/GaP Structure                                         |

| 7-2 (a) Device Structure with GaP/wet-oxide Passivation; (b) Quantum Efficiency                              |

| Spectrum (Blue and Black) of Two Device Samples and Surface Reflection                                       |

| (Green)                                                                                                      |

| 7-3 The Pseudo Light IV Curve and Illuminated IV Curve of Samples (a) 850°C20min                             |

| (G15-156-1) and (b) 850°C1hr (G15-156-2). The Inset Shows the                                                |

| Performance of the Devices. 97                                                                               |

| 8-1 The Schematic of Interdigitated Back-contact (IBC) Heterojunction Si Solar Cells                         |

| with GaP/Al <sub>2</sub> O <sub>3</sub> Integrated on the Surface                                            |

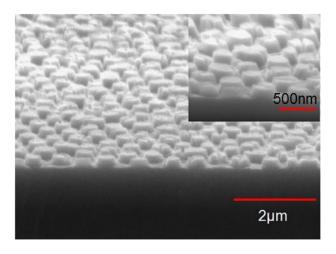

| 8-2 SEM Image of GaP Nanopillar Structures Fabricated by MACE. [71]                                          |

| 8-3 The Schematic of 3-terminal Monolithically Integrated Si Tandem Solar Sells 104                          |

### Chapter 1

## **INTRODUCTION**

#### 1.1 Need for Solar Energy

The renewable energy is increasing rapidly as a result of the exhaustion of fossil fuels and environment pollution issues. Photovoltaics as one of the renewable energy has developed from a niche market into a significant energy source for the over three decades, which can realize the electricity generation allowing locally generated, high efficiency, scalable and environmentally benign energy systems.

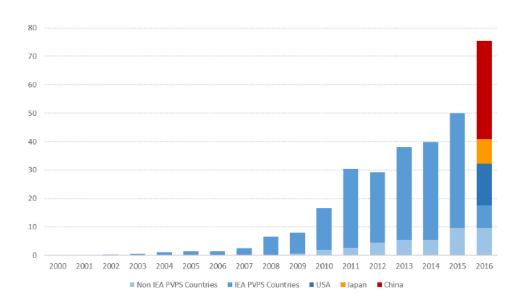

The installed capacity of PV systems has increased dramatically over the last years. As reported by International Energy Agency (IEA) [1], 24 countries have passed the gigawatt (GW) PV installation mark and the 300 GW mark has been reached. In 2017, the solar ranked No. 2 source of new electric generating capacity with 30% in the U.S. [2]. However, the negative impact of high PV penetration is an obstacle for residential PV installation. Among the issues are the technical impacts of non-dispatchable generation on grid stability and a possible rapid increase in demand on conventional generators when photovoltaic power decreases (e.g. "duck curves"). These concerns, along with decreases in the price of PV systems, have led to reduced incentives or disincentives for customers to adopt PV, including reduced subsidies for PV systems purchase. To estimate the cost of electricity generated by photovoltaic (PV), a parameter called levelized cost of electricity (LCOE) can be used for analysis. It was analyzed the levelized price of electricity paid by owners of residential PV systems under various revised net metering policies and show that the price of electricity including battery systems can still achieve residential grid parity

[3]. The benefits of PV systems with storages could encourage the adoption of PV systems and the PV market will keep increase.

Figure 1-1 The evolution of annual PV installations [1].

#### 1.2 The Potential of III-V/Si Solar Cells

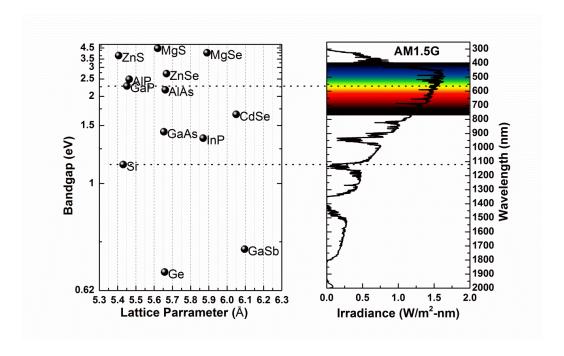

Silicon solar cells are the most commercial due to their low cost comparing to other types of solar cells. Currently, solar cell technology based on silicon substrates is the dominant commercial photovoltaic technology, while the record Si solar cells have exceeded 26% conversion efficiency [4]. The properties of III-V solar cells, such as their direct energy bandgap and high absorption coefficient, make them become much potential to be widely used. In order to improve the efficient of light usage, multijunction solar cells and intermediate bands solar cells have attracted a lot of attention over the past two decades. Multijunction solar cells allow higher efficiency than single junction solar cells by enabling both high voltage and absorption of a large portion of the solar spectrum. "Champion" efficiency tandem solar cells have shown efficiency of 46% under

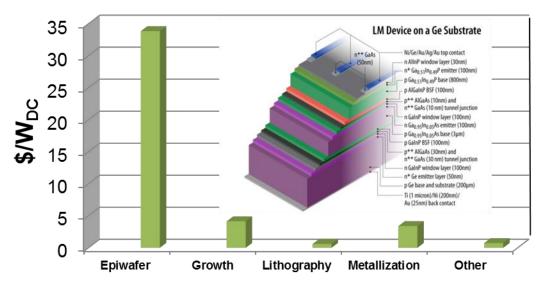

concentrated sunlight (508 suns) [5]. Despite these high efficiencies, wide spread commercial use of concentrating photovoltaics requires further cost reductions. Cost analysis [6] as shown in the Figure 1-2 of the lattice matched (LM) multijunction solar cells shows that the Ge or GaAs epi-wafer used as a substrate or bottom cell is the major cost of today's concentrated photovoltaics (CPV) technology. Replacement of the bottom Ge or GaAs substrates by Si can dramatically reduce cost and enable CPV technology for large-scale terrestrial applications.

Figure 1-2 Cost analysis of a high concentration PV module and inserted figure is a typical structure of a lattice-match device on a Ge substrate [6].

High efficiency of Si-based solar cells, coupled with the steady increase efficiency of III-V compound semiconductor based solar cells enables high efficiency tandem solar cells. In addition, a tandem solar cell with Si as the active bottom layer integrated with III-V is promising for large scale production, allowing larger wafer sizes.

### 1.3 Epitaxial Challenges

Si with its small mass, good thermal conductivity, and low cost is a good candidate as the substrate of III-V compounds. However, the crystalline defects, such as anti-phase domains (APD) generated of these III-V on Si structures due to the lattice mismatch, difference in thermal expansion coefficients and polar-on-nonpolar interface.

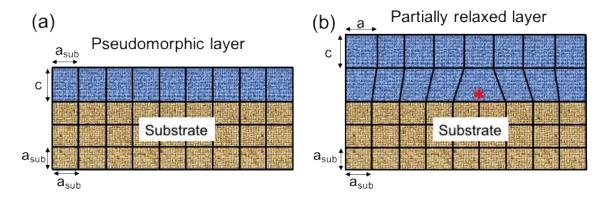

In the heteroepitaxial growth, the relaxation is known to occur by the formation of misfit dislocations and/or stacking faults. The lattice mismatch strain is defined as  $f \equiv \frac{a_{sub} - a_{epi}}{a_{epi}}$ , where  $a_{sub}$  and  $a_{epi}$  are the relaxed lattice constant of the substrate and the epitaxial layer, respectively. For  $a_{sub} < a_{epi}$ , f < 0, it is called a compressive system, while it is a tensile system for  $a_{sub} > a_{epi}$ . In the low lattice mismatch heteroepitaxial growth (|f| < 1%), the initial growth tends to be coherent/pseudomorphic and the epitaxial layer is fully stained on the substrate as shown in Figure 1-3(a). The stain energy increases as the epitaxial layer thickness increases. When it reaches to some thickness (critical thickness), it becomes energetically favorable for the introduction of misfit dislocations to release some strain. In the partially relaxed layer as schematic in Figure 1-3(b), the in-plane lattice constant of the epitaxial layer has not relaxed to fully relaxed value, but it is greater than the substrate lattice constant ( $a_{sub} < a < a_{epi}$ ) and so some of the mismatch is still accommodated by the elastic strain. A portion of the mismatch is accommodated by misfit dislocations called plastic strain.

Figure 1-3 Growth of a heteroepitaxial layer on a mismatched substrate with two different cubic lattice constants: (a) pseudomorphic layer; (b) partially relaxed layer (star mark presents the misfit dislocations).

The lattice mismatch between GaAs and Si is about 4%, while GaP and Si has one order small lattice mismatch of 0.4%. Low-lattice-mismatched GaP epitaxially grown on Si substrates enables a pseudomorphic layer growth and provides a path for the high quality epitaxial growth of III-V materials for multijunction solar cells applications.

Figure 1-4 Lattice constants and bandgap of III–Vs, Si, and Ge at 300 K, and AM1.5G spectrum.

Figure 1-5 The lattice constant of GaP and Si at various temperatures, and also the corresponding lattice mismatch strain.

For different temperatures, the lattice constant of an epitaxial layer can be calculated:  $a(T) = a(300K)[1 + \frac{A+BT+CT^2+DT^3}{100}]$ , where the constants A, B, C, and D are thermal expansion coefficients. The thermal expansion coefficient of GaP is larger than those of Si, and so GaP should have a larger lattice constant than Si at the growth temperature. The lattice mismatch between GaP and Si increases as the temperature increases as shown in Figure 1-5. High quality thin GaP layers grown on Si using molecular beam epitaxy (MBE) have been recently reported by many researchers [7]–[10]. Compared to metalorganic chemical vapor deposition (MOCVD), the growth of GaP on Si via MBE is at much lower temperature and much lower V/III ratio, *i.e.* lower P flux. Growth parameters, such as substrate temperature, V/III flux ratio, growth rate and growth methods are affecting the quality of GaP on silicon substrate. During the GaP initial nucleation

stage, it is a common issue that the formation of separate large-sized islands that the coalescence contributes high density of defects and it shows the formation of point reflections characterizing as 3D growth observed from the *in-situ* reflection high-energy electron diffraction (RHEED). It was shown that GaP was nucleated on the Si by migration-enhanced epitaxy (MEE) and molecular beam epitaxy (MBE) methods at GaP/Si initial growth stages [11]. The clear isolated islanding growth was observed in the case of MBE growth, while the MEE growth, alternating Ga and P layers, formed wider lateral size and lower height which indicates that MEE growth enhances the two-dimensional (2D) growth. Therefore, it is critical to optimize the GaP growth conditions and growth methods to achieve high quality of GaP layers on Si substrates.

### 1.4 GaP/Si Heterojunction Solar Cells

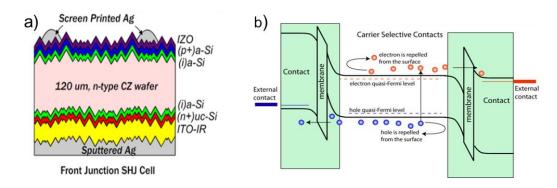

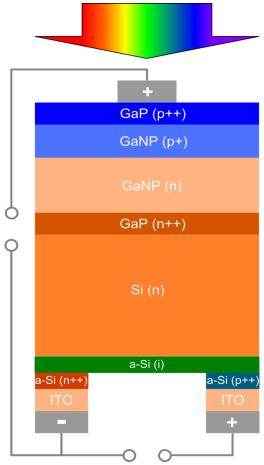

As shown in Figure 1-6a, in a typical heterojunction (SHJ) solar cell, optimized intrinsic a-Si as passivation and p-type doped a-Si for forming a p-n junction with the substrate. The a-Si layers on the front have excellent passivation for the substrate, while a transparent conductive oxide (TCO) is required to provide lateral transport of the collected carriers to the metal electrode grid. However, most of the carriers generated in the front layers (a-Si:H, TCO) are lost due to recombination, parasitic absorption loss, which limits the ultimate performance of these SHJ solar cells. Potential gain in current density is up to 2.1 mA/cm<sup>2</sup> [12]. High bandgap, low optical absorption and high mobility should be integrated with silicon to minimize parasitic loss. GaP with high bandgap (2.26 eV) and indirect bandgap is promising for reducing parasitic loss at the front of silicon solar cells. In addition, a carrier-selective contact (CSC) (Figure 1-6b) on silicon substrates has been

scrutinized to develop high efficiency heterojunction silicon solar cells by effectively separating minority carriers. GaP, whose band offset with Si at the valence band  $\Delta E_v$ =1.05 eV and at the conduction band  $\Delta E_c$ =0.09 eV [13], is considered to be an excellent candidate as an electron selective contact for silicon.

Figure 1-6 (a) Typical front junction silicon heterojunction (SHJ) cell. (b) Schematic of carrier-elective contacts (CSC).

#### 1.5 Thesis Structure

In this manuscript, first the epitaxial growth of GaP by MEE and MBE methods is discussed, and the structural defects formation is investigated via high resolution X-ray diffraction (XRD) and transmission electron microscopy (TEM) in Chapter 2. Chapter 3 is devoted to reveal the Si minority-carrier lifetime degradation issues during GaP growth on Si in the MBE chamber and two approaches are proposed to suppress the lifetime degradation during III-V on Si integration. Chapter 4 describes GaP as a heteroemitter in GaP/Si solar cells and electrical properties are compared for different structures. Chapter 5 compares different heterojunction GaP/Si solar cells with GaP as an electron-carrier selective contact on the back and different approaches are analyzed to improve the device performances of GaP/Si solar cells. In Chapter 6, GaP was deposited on passivation membrane layers and the device performance is discussed. Chapter 7 is describing a novel

structure with GaP/wet-oxide functional as passivation layers for Si wafers and such solar cells are demonstrated. Chapter 8 is a summary of this dissertation and also an outlook for this work.

### Chapter 2

#### **GAP EPI-GROWTH ON SI VIA MBE**

#### 2.1 Introduction

It has been a long-lasting goal to epitaxially integrate III-V alloys with Si substrates [14], which can enable low-cost microelectronic and optoelectronic systems. Structural degradation during the growth of III-V compounds on Si due to the non-zero lattice mismatch is the main obstacle for developing high performance optoelectronic devices. It is a challenge to integrate polar III-V materials onto non-polar Si substrates. Among all the III-V alloys, GaPN can be lattice-matched to Si, however, the however, the direct growth of nitride alloy will generate other crystalline defects on the interface by the creation of silicon nitride on the Si surface [15]. Gallium phosphide (GaP), which has a relatively small lattice mismatch (0.37%) with Si, is a good candidate, such as serving as a buffer layer, for this III-V/Si integration, especially for multijunction solar cell applications [16], and many other solar applications [17], [18]. The almost pseudomorphic growth of GaP-based materials on Si can address this issue by delaying the onset of defect creation. However, symmetry change at the diamond-zinc blende interface additionally affects defect creation during epitaxial growth.

It was shown that degradation of crystal quality of GaP layers grown on Si substrate can be delayed by using the migration-enhanced epitaxy (MEE) technique and a post-growth annealing procedure [9], [10], [16], [19], [20]. Although the off-cut ( $\geq 4^{\circ}$ ) Si wafers have been demonstrated reduced density of anti-phase domains (APD) [7], [20]–[23], precisely orientated Si(001) wafers are widely used in the standard complementary metal oxide semiconductor (CMOS) logic circuit fabrication [24] and solar cell structures.

Therefore it is important to investigate the defect formation for the GaP layers grown on the off-cut and exactly oriented Si(001) substrates under the same growth conditions. Due to the lattice mismatch pseudomorphic layers can be grown almost coherently strained, but beyond the specific layer thickness, depending on growth conditions, amount of already created misfit dislocations becomes sufficient to relieve relaxation some of the mismatch stress [24]. In the GaP/Si heteroepitaxial system initially by low lattice mismatch and symmetry change deteriorated it is critical to understand thickness related defect creation during the stress relaxation for comparison with low lattice mismatched III-V on III-V epitaxial structures [25].

In this chapter, a defect-free GaP layer on an off-cut Si substrate by MEE was grown, and the same growth condition was applied to a precisely oriented Si substrate. Later, GaP layers were grown by traditional MBE growth procedure with optimizing the V/III ratio and a series of GaP structures were grown for revealing the defects formation in the GaP/Si system. High-resolution X-ray diffraction (XRD) and transmission electron microscopy (TEM) structural investigations were conducted to reveal correlations between the growth conditions and the crystal perfection of the epitaxial structures.

#### 2.2 Experimental Setup

### 2.2.1 Epitaxial Growth of GaP-Si(001) structures

The GaP epitaxial layers were grown on Si(001) substrates using a solid-source Veeco GEN III MBE system with a phosphorus valved cracker. The Si wafers were n-type float-zone material, precisely oriented (001) or with 4° offcut towards the [110] direction. This wafer misorientation should help to form double steps on the substrate surface during epitaxial growth and possibly minimize APD creation during GaP epitaxial growth [24].

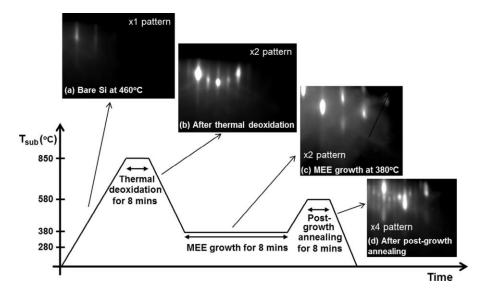

Prior to deposition, Si wafers were chemically cleaned using the standard RCA solution, which was finally combined with 5% hydrogen fluoride (HF) for surface refresh. The GaP layers were grown on the Si substrates following preheating at 820°C for 5 min to fully remove the residual native silicon oxide layer. Surface reconstructions during the preheating and deposition were monitored in situ by reflection-high-energy electron diffraction (RHEED). Initially, under the presence of the native oxide, (1×1) RHEED patterns were observed, while clear and streaky (2×1) patterns, indicative of native-oxide removal and perfect surface reconstruction, were observed after the substrate preheating. After annealing, the substrate temperature was then decreased to the growth temperature for epitaxial growth.

Two MEE-grown GaP-Si(001) heterostructures of 50-nm GaP layer thickness were deposited at 440°C onto off-cut (MEE-I structure) and precisely oriented (MEE-II structure) Si wafers. The deposition loop consisted of a sequence of 5 second Ga deposition, 1 s pause with closed Ga and P sources, 8 s exposure under P flux, and 5 s pause, with the loop being repeated for a total of 184 cycles. Before commencing MEE growth, the P shutter was opened for 30 s and then closed for 12 s before the initial Ga deposition. The P and Ga flux ratio was about 5.

Together with the MEE growth process, a traditional MBE growth method for GaP layers was investigated. To optimize the growth conditions for GaP on precisely oriented (001) Si substrates, different V/III (P/Ga) ratios from 6.9 to 3.1 were conducted at 580°C at a growth rate of 0.52 µm/hr. A well below the critical thickness 37 nm GaP was epitaxially grown. At the initiation of growth, the P shutter was open for 20 s for P deposition, then 10 loops of (GaP-P) short-period quasi-super lattice with 5 s GaP

deposition and 5 s pause under P-flux were applied to improve the planarity of the growth front, and then the main growth process was started. Several GaP-Si(001) epitaxial structures with GaP layer thicknesses ranging from 37 nm up to 2  $\mu$ m were epitaxially grown by MBE using a P/Ga ratio of ~ 4.5, which is the optimized growth condition for epitaxial growth at 580°C and precisely oriented wafers.

#### 2.2.2 Characterization Methods

High-resolution XRD studies were performed using an X'Pert MRD diffractometer with a multilayer focusing mirror under double- and triple-axis alignment. Hybrid Ge(220) monochromator ensured 18 arc.sec collimated and monochromatic CuK $\alpha$ -1 incident radiation, while a Ge(220) analyzer with 12 arc.sec acceptance angle allows spatially separate coherent and diffuse-scattered radiation in the vicinity of the (004) and (224) reflections. Coherent double-crystal (DC) and triple-crystal (TC)  $\omega$ -2 $\theta$  and  $\omega$  rocking curves (RCs) were used to determine layer composition and strain conditions to specify the type, spatial distribution, and density of crystal defects. Atomic force microscopy (AFM) was conducted by multimode scanning probe microscope (SPM) to study the surface morphology.

Specimens suitable for TEM observation were prepared using focused-ion-beam milling as well as additional argon-ion-milling to remove some surface milling artifacts. Observations were made with a FEI-Philips CM200 high-resolution electron microscope, operated at 200 keV, equipped with a double-tilt specimen holder, and an aberration-corrected ARM-200F microscope. Cross-section observations were made along {110}-type zone axes so that the surface normal would be perpendicular to the incident-beam direction.

#### 2.3 Results and Discussion

#### 2.3.1 Investigation of MEE-grown Structures

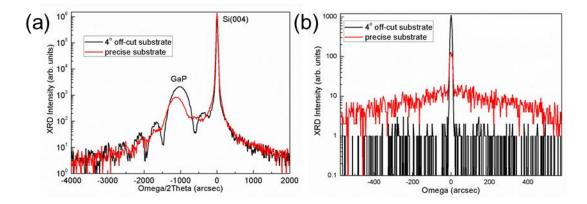

50-nm-thick GaP layers were epitaxially grown on two Si substrates, one 4° offcut (MEE-I structure) and one precisely oriented (001) Si wafers (MEE-II structure). Strong and extended interference pattern around GaP peak on DC  $\omega$ -2 $\theta$  RC and narrow coherent central peak without diffuse base on TC  $\omega$  RC as shown in Figure 2-1a, b (black curves) confirm high crystal perfection of GaP layer grown on off-cut Si wafer. Based on the FWHM of the TC  $\omega$  RC the bending of the structure is low, while volumetric density of crystal defects may be evaluated as ~2×10<sup>5</sup> cm<sup>-2</sup>.

On the other hand, noticeable diffusion of GaP related interference pattern for the DC  $\omega$ -20 RC of the MEE-II structure (Figure 2-1a, b red curves) means the deterioration of X-ray vertical scattering coherence of the GaP layer, which is caused by crystal defects with edge segment(s) in the volume of the epitaxial layer created during epitaxial growth. Most probably, these defects would be identified as stacking faults, created on the interface and intersected in the volume of the epitaxial layer, diminishing vertical coherence of the epitaxial layer. The diminished intensity of the central narrow peak and the wide diffuse base for the MEE-II TC  $\omega$  RC confirms this suggestion. FWHM ( $\approx$  600 arc.sec) of diffuse base allows evaluate the density of these defects as  $\sim$ 1.3×10 $^{9}$  cm $^{-2}$ . Low intensity of diffused scattered radiation suggests that despite high density these defects occupy relatively small volume of the epitaxial layer, while narrow central coherent peak means that the elastic stress caused by these defects do not overlap in the layer and hence do not deteriorate entire volume of the epitaxial layer as well.

Figure 2-1 (a) DC coherent  $\omega$ -2 $\theta$  RCs measured in the vicinity of Si-GaP (004) reflections. (b) The corresponding GaP TC  $\omega$  RCs.

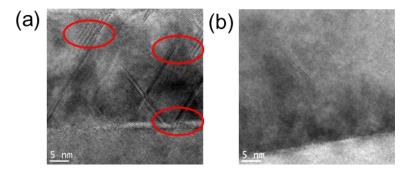

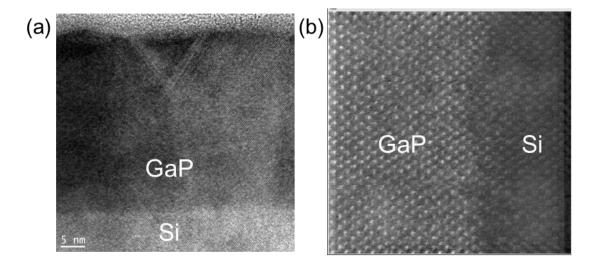

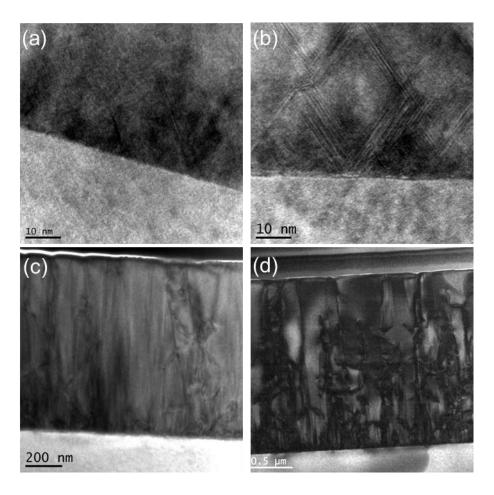

TEM cross-section micrographs (Figure 2-2) visually confirm the trends of the XRD results. The MEE-I structure (Figure 2-2a) showed no extended crystal defects over large lateral distances. By comparison, the MEE-II GaP sample (Figure 2-2b) revealed many stacking faults and multiple twins in the volume of the GaP layer, some of them with stacked planes (red circles), others without. Therefore, defect-free GaP can be grown on the off-cut Si substrate at this MEE growth condition, however, it is not suitable for the precisely orientated Si substrate.

Figure 2-2 TEM cross-section micrographs of MEE grown structures: (a) GaP grown on precise Si wafer (MEE-II structure), (b) GaP grown on offcut Si wafer (MEE-I structure).

## 2.3.2 Investigation of MBE-grown Structures

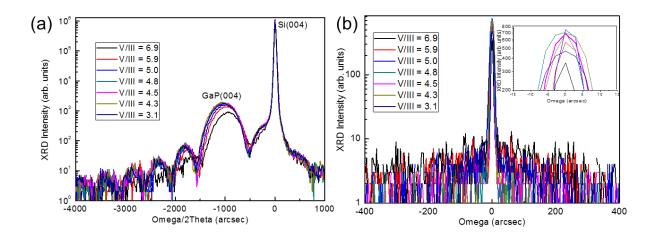

A thickness of 37 nm GaP layer was grown by MBE procedure on Si substrates with different P/Ga ratio and the AFM measured surface morphology is shown in Figure 2-3. As the P flux reduced from P/Ga ratio of 6.9, the surface becomes smooth and the peak-to-valley distance is reduced to 4.3 nm at the P/Ga ratio of 4.5. If the flux ratio decreases below 4.3, the P flux is not sufficient to maintain P-stable surface and Ga droplets form and producing rough surface, which is consistent with [21]. From HR-XRD measurement to these samples (Figure 2-4), the sample grown at 580°C with 4.5 P/Ga flux ratio demonstrates the highest crystal perfection (ω-2θ and ω RCs look similar to 4° off-cut MEE structure RCs on Figure 2-1a, b) and lowest dislocation density, estimated as 2.6×10<sup>5</sup> cm<sup>-2</sup>. The TEM (Figure 2-5) shows an abrupt and coherent GaP/Si interface and although the top surface is slightly uneven there are virtually no structural defects visible in the GaP layer across large lateral distances. However, antiphase boundaries can be observed from the TEM image in Figure 2-5b, which was formed during GaP epitaxially grown on the single step surface of precisely oriented Si substrate.

Figure 2-3  $1\mu m \times 1\mu m$  AFM for different P/Ga flux ratio: (a) 6.9; (b) 5.9; (c) 4.8; (d) 4.5; (e) 4.3; (f) 3.1.

Figure 2-4 (a) DC coherent  $\omega$ -2 $\theta$  RCs measured in the vicinity of Si-GaP (004) reflections. (b) The corresponding GaP TC  $\omega$  RCs

Figure 2-5 TEM images of 37 nm GaP sample with optimized MBE growth conditions.

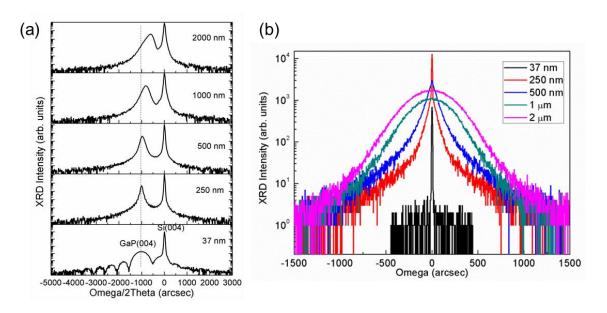

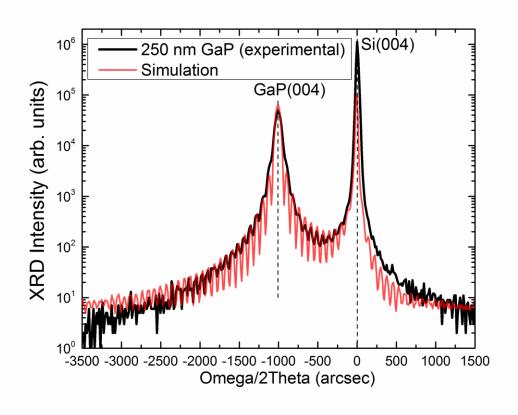

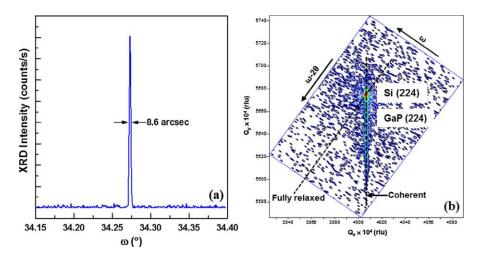

To investigate defect formation for GaP/Si structures and their structural transformation during epitaxial growth, a set of thicker GaP layers were grown under established growth condition and investigated. The MBE-grown structures exhibited high crystal perfection for the thin (37 nm) GaP layer, while the thicker ~ 250 nm thick GaP layer structure clearly demonstrates beginning of defect creation on both, coherent DC  $\omega$ -2 $\theta$  and TC  $\omega$  RCs (Figure 2-6). As the DC  $\omega$ -2 $\theta$  RCs plotted in Figure 2-6, the shift of GaP peak towards to Si peak indicates that the relaxation of the initial elastic stress gradually increasing for GaP layers thicker than 250 nm. Noticeable diffusion and angle shrinking of the entire interference pattern, and intensity diminution of the interference fringes on  $\omega$ -2 $\theta$  RC (Figure 2-7) confirm that. Despite that an angle position of GaP(004) peak on  $\omega$ -2 $\theta$  RC and position of the diffraction spots on asymmetrical (224) Reciprocal Space Map (RSM) (Figure 2-8 and Figure 2-9) reveal the lack of relaxation of the initial elastic stress in this structure.

TC  $\omega$  RC of 250 nm GaP sample, shown in Figure 2-6b, also confirms the initial stage of defect creation: coexistence of strong and narrow (FWHM = 8.85 arc.sec) central coherent peak, corresponding to the main almost perfect crystalline matrix of GaP epitaxial layer, and low intensity diffuse base, caused by X-ray scattered on crystal defects, created during epitaxial growth. Based on the FWHM of the diffused pedestal ( $\sim$  85 arc.sec) the bending of the crystal planes of the epitaxial layer corresponds to  $\sim$  2.6 – 2.7  $\times$  10<sup>7</sup> cm<sup>-2</sup> crystal defects in the epitaxial layer. Low intensity of the diffused base means that crystal defects, created during epitaxial growth and responsible for diffused scattering, occupy small, most probably, bottom part of the GaP layer, while the elastic strain, induced by these defects, still affects only a small part of the epitaxial layer.

The lack of interference fringes on the tails of the  $\omega$  RCs, typical for the initial stage of relaxation at polar III-V low deteriorated epitaxial structures [26], means the lack of spatial ordering of crystal defects in low deteriorated III-V epitaxial layers deposited on non-polar substrates, while an entire coincidence of the shape of the  $\omega$  RCs and diffused base, in particular, collected at two [110] and [1-10] azimuth directions suggests that GaP epitaxial layers grown on non-polar Si(001) substrate do not inherit structural anisotropy typical for Zinc-Blende (ZB) epitaxial layers grown on polar substrate.

Increase of the thickness of GaP layer to 500 nm totally diffused interference fringes on DC  $\omega$ -20 RC and also revealed onset of relaxation of the initial elastic stress in this structure (Figure 2-6b). Shape of the  $\omega$  RCs for both <110> azimuth directions also noticeably transformed in comparison with 250 nm structure. Central narrow peak almost fully disappeared, overlapped by wide diffused peak induced by crystal defects. FWHM of this peak (~ 133 arc.sec) corresponds to ~  $6.5 \times 10^7$  cm<sup>-2</sup> crystal defects in the epitaxial

layer. Dislocation density, increased in  $\sim$  2.5 times in comparison with 250 nm layer, led to structural deterioration of the almost entire volume of the epitaxial layer, supposedly, caused by the lateral overlapping of the elastic stress induced by crystal defects (their dislocation cores) created on interface/in the volume of GaP layer. Well coincidence of the shape of the  $\omega$  RCs measured for two azimuth directions shows the lack of azimuth <110> anisotropy of 500 nm thick GaP layer.

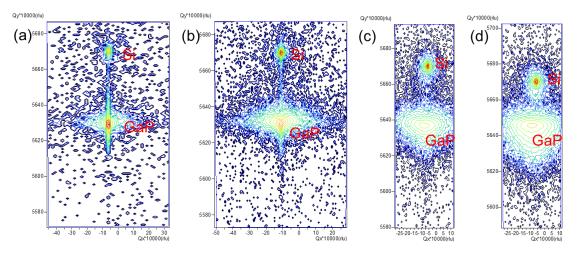

Thicker (~ 1 and 2 µm thick) GaP epitaxial layers demonstrate gradual structural transformation of crystal perfection: further increase of the bending of the layer and increase of the extent of relaxation up to 75%, extracted from (004) and (224) RSMs (Figure 2-8 and Figure 2-9). Significant difference between these trends for non-polar Si-GaP and low deteriorated III-V polar epitaxial structures [25] suggests that crystal defects, created in GaP layers have different nature in comparison with crystal defects created in polar epitaxial structures. Noticeable diminution of the layer bending demonstrated by low deteriorated polar epitaxial layers most probably is related to volumetric intersection of 60° dislocations in the volume of the epitaxial layer and final compensation of dislocation screw components.

Bending evolution of the epitaxial structures, correlated with the type and density of extended defects, is different in comparison with other low deteriorated and partially relaxed epitaxial structures [10]. Density of these defects, as evaluated by the FWHM of the  $\omega$  RCs (as listed in Table 2-1), is steadily increasing ( $\sim$ 6.5  $\times$  10<sup>7</sup> cm<sup>-2</sup> in 500 nm,  $\sim$ 7.3  $\times$  10<sup>8</sup> cm<sup>-2</sup> in 1  $\mu$ m, and  $\sim$ 1.1  $\times$  10<sup>9</sup> cm<sup>-2</sup> in 2  $\mu$ m GaP layer), as well as the bending elastic stress that is induced by them. Such behavior suggests the possibility of other types of crystal defects being created in the volume of thicker GaP epitaxial layers.

The electron microscopy observations (see Figure 2-10) confirm the trends in defect development that are predicted from the X-ray data. The thick ( $\sim$  2  $\mu$ m) GaP layer contains a high density of threading dislocations, as well as considerable {111}-type inclined stacking faults.

Figure 2-6 DC coherent  $\omega$ -20 RCs measured in the of vicinity of Si-GaP (004) reflections. Black and red bars specify the angle position of fully elastically stressed GaP layer and Si(004) substrate peaks. TC  $\omega$  RCs shown insert.

Figure 2-7 Experimental DC coherent  $\omega$ -2 $\theta$  rocking curve of 250 nm GaP compared to simulation curve.

Figure 2-8 RSM(004) of different GaP layers thickness: (a) 250 nm, (b) 500 nm, (c) 1000 nm and (d) 2000 nm.

Figure 2-9 RSM(224) of different GaP layers thickness: (a) 250 nm, (b) 500 nm, (c) 1000 nm and (d) 2000 nm.

Figure 2-10 TEM of different GaP layers thickness: (a) 250 nm, (b) 500 nm, (c) 1000 nm and (d) 2000 nm.

Table 2-1 XRD results of various thicknesses MBE-grown GaP/Si samples

| t <sub>GaP</sub> (nm) | DC ω-2θ RC<br>GaP peak<br>FWHM<br>(arc.sec) | GaP Layer<br>Vertical<br>Coherence<br>(nm) | TC ω RC<br>GaP peak<br>FWHM<br>(arc.sec) | Dislocation Density (cm <sup>-2</sup> ) |

|-----------------------|---------------------------------------------|--------------------------------------------|------------------------------------------|-----------------------------------------|

| 37 nm                 | 482                                         | ~36.5                                      | 11.0                                     | 2.6×10 <sup>5</sup>                     |

| 250 nm                | 85                                          | 246                                        | 11.2 / 86                                | $2.7 \times 10^7$                       |

| 500 nm                | 133                                         | 143                                        | 133                                      | 6.5×10 <sup>7</sup>                     |

| 1.0 μm                | 216                                         | 89                                         | 455                                      | 7.3×10 <sup>8</sup>                     |

| · | 2.0 μm | 237 | 80 | 545 | 1.05×10 <sup>9</sup> |

|---|--------|-----|----|-----|----------------------|

|---|--------|-----|----|-----|----------------------|

Table 2-2 RSM results of various thicknesses MBE-grown GaP/Si samples

| $t_{GaP}$ (nm) | $Sym (004) RSM  q_x/q_y (rlu)$ | Asym (224) RSM $q_x/q_y$ (rlu) | Relaxation (%) |

|----------------|--------------------------------|--------------------------------|----------------|

| 250 nm         | 0 / 0.004067                   | 0.000028 / 0.004041            | 0              |

| 500 nm         | 0 / 0.003983                   | 0.000093 / 0.003899            | 9              |

| 1.0 μm         | 0.000231/ 0.003328             | 0.000813 / 0.003164            | 40             |

| 2.0 μm         | 0.000286/ 0.002405             | 0.001510 / 0.002273            | 50 => 76       |

### 2.4 Conclusions

Crystal perfection of MEE and MBE grown Si(001)-GaP structures were investigated by high-resolution XRD and TEM. MEE structures grown under the same growth conditions revealed that 4 degrees offcut angle significantly affects crystal perfection of GaP. Higher perfection of offcut structure most probably related to atomic migration and atomic incorporation on the growth front. The growth conditions of MBE growth structures on precisely orientated substrates allowed significantly postponed defects creation and hence beginning of relaxation in elastically stressed epitaxial structure. Crystal perfection of MBE grown structures revealed high crystal perfection of the thin GaP layer, then gradual relaxation of the initial elastic stress by 60° and Lomer dislocations in thicker GaP layers. Different bending of the thick GaP structures caused by threading dislocations, created in these layers.

## Chapter 3

#### SI MINORITY-CARRIER LIFETIME CHALLENGES AND APPROACHES

#### 3.1 Introduction

In order to develop high performance GaP/Si solar cells, the silicon must have a high minority-carrier lifetime in the millisecond range, which is required to obtain more than 725 mV open-circuit voltage for wafers with thickness of 100-160 µm. The growth of high quality GaP on precisely oriented (001) silicon has been demonstrated in Chapter 2. And to get high performance, more attention needs to be focused on conserving a high minority-carrier lifetime in silicon. Recent results reported by multiple research groups, looking at developing of both MJ and carrier selective contact, such as GaP, solar cells, have shown a dramatic deterioration in the silicon minority-carrier lifetime during the growth of III-V layers, both by molecular beam epitaxy (MBE) and metalorganic chemical vapor deposition (MOCVD) [9], [27]–[32]. The degradation is attributed to forming recombination centers from the fast diffusing species or intrinsic defects. The most prevalent approach thus far to recover the degraded lifetime is by phosphorus gettering or hydrogen passivation. For example, gettering has been demonstrated either by phosphoryl chloride (POCl<sub>3</sub>) diffusion [28], [29], [33], or by phosphine (PH<sub>3</sub>) diffusion [31], or by hydrogen defect passivation [31]. While gettering or hydrogen passivation enable at least partial recovery of the minority-carrier lifetime in the silicon, the optimum approach is to understand and effectively prevent the lifetime degradation. High temperature post-growth gettering processes, such as phosphorus diffusion, can be detrimental to the properties of III-V epitaxial films and may be difficult to incorporate into a full solar cell process. Similarly, hydrogen passivation of defects makes the device highly dependent on subsequent temperature processing, as hydrogen may out diffuse at temperatures below 400°C. Moreover, Varache *et al.* reported that a 500-nm-thick SiN<sub>x</sub> coating on both sides of a p-type Cz wafers preserved the bulk lifetime in the hundreds of microseconds range after annealing in their MOCVD reactor [27]. Recently, SiO<sub>2</sub>/SiN<sub>x</sub> diffusion barriers were applied to prevent the iron contamination and minimize Si lifetime degradation in the MOCVD reactor [18].

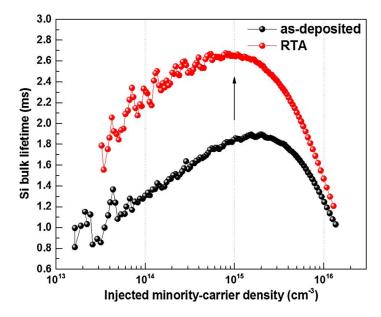

In this chapter, we systematically investigate the effect of GaP growth conditions on GaP crystal quality as well as the effect of annealing conditions for Si wafer on Si bulk lifetime. Significant lifetime degradation of Si wafers is observed when annealed at high temperatures (> 700°C). This lifetime reduction is prevented by depositing SiN<sub>x</sub> film, acting as a diffusion barrier and/or getter, on the backside of Si wafer. The SiN<sub>x</sub> also enables the epitaxial growth of high-quality GaP layers on Si wafer. We investigate the Si minority-carrier lifetime after GaP epitaxial growth in an MBE system and approaches to mitigate lifetime degradation. By subsequently thinning down annealed samples with acids, the different lifetime profiles for different annealing temperatures reveal the signature of extrinsic impurity diffusion. Furthermore, we evaluate the impact of gettering via POCl<sub>3</sub> diffusion on MBE thermally treated Si wafers. Finally, we investigate two effective methods to mitigate the lifetime degradation during the MBE growth, which offers a path for higher quality III-V growth on active Si substrate and the development of high performance III-V/Si solar cells.

#### 3.2 Experimental Details

In order to investigate the lifetime evolution during GaP grown on Si in the MBE system, four different types of (100)-oriented Si substrates with thicknesses between

$\mu$ m and 380  $\mu$ m were used in this work. These wafers are: (i) high resistivity intrinsic float-zone (FZ) wafers (>400  $\Omega$ cm), (ii) n-type P-doped FZ wafers, 1–5  $\Omega$ cm, (iii) p-type B-doped FZ wafers, 1–5  $\Omega$ cm, and (iv) n-type P-doped Czochralski (Cz) wafers, 1–3  $\Omega$ cm. All Si wafers were chemically cleaned in an RCA (Radio Corporation of America) solution and etched in a diluted hydrofluoric acid (HF) (10%) for 30 s before loading in the MBE pre-chamber which was pumped down to a pressure of about 1×10<sup>-8</sup> Torr. After baking, the wafers were transferred to the growth chamber which was maintained at a pressure below 2×10<sup>-10</sup> Torr. We used a solid-source Veeco GEN-III MBE system, equipped with a phosphorus valved cracker cell and Ga source. A temperature ranges from 700°C to 850°C was used in the processes for the decomposition of the native oxide on the Si substrate, which was monitored via changes in the *in-situ* reflection high-energy electron diffraction (RHEED) patterns. The surface reconstruction that the transition from (1×1) spotty RHEED patterns to (2×1) streaky patterns indicates the Si surface is clean and ready for epitaxial growth.

Unless otherwise indicated, all samples for the lifetime measurement were passivated on both sides after removal from the MBE chamber with 50-nm-thick intrinsic hydrogenated amorphous silicon (a-Si:H) films prepared by plasma-enhanced chemical vapor deposition (PECVD) at 250°C. The a-Si:H passivation enables a surface recombination velocity as low as 1 cm/s [34], which is low enough to estimate the Si bulk lifetime directly from measured effective minority-carrier lifetimes of the passivated silicon wafers. The Si effective minority-carrier lifetimes were measured by quasi steady state photoconductance decay (QSSPC) using a Sinton Lifetime Tester.

The samples were divided into two general groups. In one set, 15 nm thick GaP was grown on a polished high resistivity FZ Si substrate at 380 °C via migration enhanced epitaxial (MEE) method and post-growth annealed in the MBE chamber under a P flux at 580°C for 8 min. After measurement of the Si minority-carrier lifetime with GaP on the front and a-Si:H on the rear, a mixture of hydrofluoric, nitric and acetic acids (HNA) with a volume ratio of 10:73:17 at room temperature was used to isotropically etch the GaP layer and Si (c-Si or a-Si). The sample is then passivated with the a-Si:H process described above, and remeasured.

The second set of samples was used to investigate the influence of temperature on Si degradation. They were prepared by heating n-type FZ 280-µm-thick wafers in the MBE chamber between 350°C and 800°C for 30 min. There was no growth of GaP or other materials. To obtain the lifetime profile for the thinned-down wafers, we repeated the following sequence until the preferred depth was achieved: (1) etching in HNA solution, (2) PECVD surface passivation and (3) effective lifetime measurement. The amount of Si successively removed from each side was estimated by weighing the wafer.

For the gettering process, degraded n-type FZ samples were examined the lifetime with a-Si:H passivation and then the passivation layers were removed by HNA. And wafers were exposed to a flow of oxygen and POCl<sub>3</sub>, at 850°C in a diffusion furnace, with a 25 min drive in step.

In the samples with a  $SiN_x$  diffusion barrier, all the amorphous  $SiN_x$  films were 150-nm-thick and deposited at 350°C by PECVD on the surface of cleaned Si wafers. After thermal treatment in the MBE, the  $SiN_x$  layer was removed by etching in a concentrated HF solution.

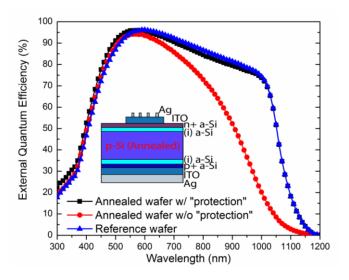

Also, we investigated the effect of such a SiN<sub>x</sub> protection on the performance of an a-Si:H/c-Si heterojunction solar cell. We compared three p-type Si FZ wafer: a reference not annealed in the MBE, a bare Si wafer and a wafer coated with a SiN<sub>x</sub> film at the back, both annealed at 820°C for 5 minutes in the MBE. and a third sample with a SiN<sub>x</sub> film on the back After removing the SiN<sub>x</sub> film from the third sample, a 6-nm-thick intrinsic a-Si:H layer was deposited on both sides of all three samples, including the reference cell, followed by a 10 nm (n) a-Si on the front side and a 10 nm (p) a-Si on the back side by PECVD. Indium-tin-oxide (ITO) with a thickness of ~75 nm was then deposited on top and also back as a current spreading layer. Finally, a 200 nm Ag was deposited on the front as fingers and on the back as a back contact. ITO and Ag were deposited by RF sputtering. External quantum efficiency (EQE) of the fabricated cells was measured by the solar cell spectral response measurement system (QEX10), manufactured by PV Measurements. The I-V characteristics were measured with a continuous Oriel class A solar simulator equipped with a Xenon ARC lamp (AM1.5G), which was calibrated with an original equipment manufacturer Si reference cell.

### 3.3 Si Lifetime Degradation

Figure 3-1 shows the effective minority-carrier lifetime of a high resistivity silicon wafer having a grown GaP layer on one side and a-Si:H on the other (red markers). Lifetime for this sample is two orders of magnitudes lower than that of a reference FZ Si wafer passivated on both sides with a-Si:H. By comparing these different lifetimes, the low lifetime of the GaP/Si/a-Si:H sample can originate from two factors: (i) the surface recombination at the GaP/Si interface before the GaP is etched; (ii) a strong increase in recombination in the Si wafer triggered by the growth process in the MBE system. The

effective minority-carrier lifetime depends on both surface and bulk recombination; therefore, to decouple which is impacted by the growth process, we removed the GaP layer and about 3  $\mu$ m of Si from each side by etching in an HNA solution. After appropriate cleaning and repassivation with a-Si:H on both sides, the measured minority-carrier lifetime (blue markers) was higher than that of the GaP/Si/a-Si:H sample, but still significantly lower than the reference sample. During GaP growth, the phosphorous and the gallium diffusion if any are estimated in the first 3  $\mu$ m of the Si on the surface. By etching the first 3  $\mu$ m of the Si, the phosphorous and the gallium diffusion are not playing significant roles any more in the lifetime degradation process. The low lifetime (blue markers) of the sample after etching compared to the reference sample indicates that the degradation happened in the Si bulk.

Figure 3-1 Injection-dependent effective minority-carrier lifetimes of different FZ-Si wafers: a reference that was not processed in the MBE, a sample with GaP grown on one side, and the same sample after etching the GaP layer and  $\sim 3~\mu m$  of silicon from each surface.

The second set of samples was used to investigate the influence of temperature on Si degradation. They were prepared by heating n-type FZ 280-µm-thick wafers in the MBE

chamber between 350°C and 800°C for 30 min. There was no growth of GaP or other materials. We measured the lifetime as a function of Si etched, so as to separate the surface and bulk contamination. To obtain the lifetime profile for the thinned-down wafers, we repeated the following sequence until the preferred depth was achieved: (1) etching in HNA solution, (2) PECVD surface passivation and (3) effective lifetime measurement. The amount of Si successively removed from each side was estimated by weighing the wafer.

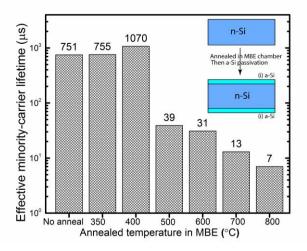

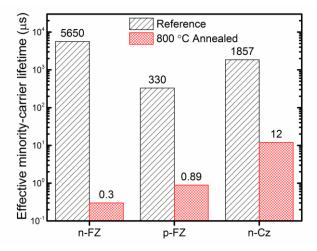

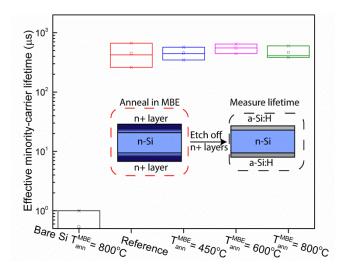

Figure 3-2 Effective minority-carrier lifetime (at the injection level of  $1\times10^{15}$  cm<sup>-3</sup>) of Si wafers annealed in the MBE chamber for 30 min at different temperatures.

Figure 3-3 Effective minority-carrier lifetime (at an injection level of  $1\times10^{15}$  cm<sup>-3</sup>) of different types of Si wafers (n-FZ, p-FZ, and n-Cz) before and after 800°C annealing in the MBE chamber for 30 min.

To further identify the cause of the reduced bulk minority-carrier lifetime, we performed a series of isochronal annealings of bare n-type FZ Si wafers in the MBE chamber at different temperatures for 30 min. The as-received wafers used were single side polished and required additionally chemically polished by HNA and appropriate clean before the processing.

After removal from the chamber, wafers were passivated with 50 nm a-Si:H. As shown in Figure 3-2, the effective minority-carrier lifetime increases slightly after annealing at 400°C, which may be related to the deactivation of intrinsic defects after low-temperature annealing [35]. However, the effective minority-carrier lifetime drops significantly for annealing at 500°C, and as the temperature further increases, the lifetime decreases to less than 10 µs at 800°C. As there was no growth for these samples, the Sibulk degradation mechanism is not due to the growth of the III-Vs on the Si but caused by the temperature treatment, with a low threshold temperature of 500°C.

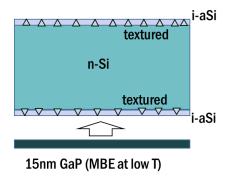

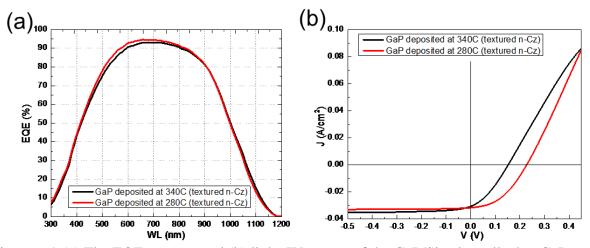

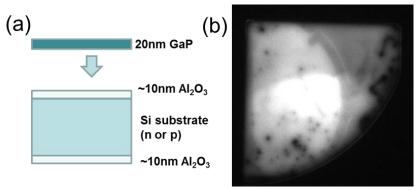

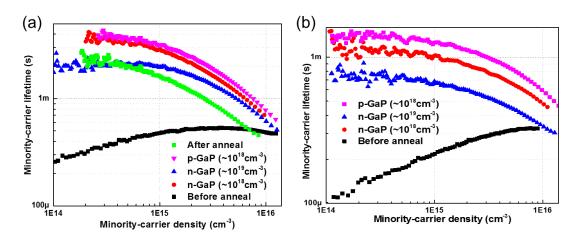

While there have been previous reports of thermal activation of grown-in defects, such as the lattice-impurity or impurity-impurity metastable defects, in FZ wafers as described in [28], there are several arguments that suggest that the lifetime degradation is rather originating from thermally activated diffusion of extrinsic impurities [36]: (i) There is a significantly stronger lifetime degradation in this work than in [28], with no sign of lifetime recovery at temperatures above 800°C (not shown). Similar thermal annealing was conducted to p-type FZ wafers and no significant degradation was observed in a high-purity furnace [32]; and (ii) We observed similar lifetime degradation occurs for Cz and FZ wafers (Figure 3-3), whereas Cz wafers should, according to [35], not accommodate the type of intrinsic defect causing the thermally activated degradation. This additionally implies that