# Dynamic Performance of Voltage Balancing and Circulating Current Suppression Control for Modular Multilevel Converter

By

Congqi Yin

Thesis submitted in partial fulfilment for the degree of Doctor of Philosophy In the School of Electrical & Electronic Engineering Newcastle University

UK.

Submitted in April 2017

Abstract: Global power consumption has increased by approximately 3% each year over the past 15 years. The growing demand for energy has stimulated the spread of clean and reliable renewable energy networks and power grid interconnections throughout the world. For example, in Europe, there are 23 High Voltage Direct Current (HVDC) Transmission lines under construction which are scheduled for completion before 2024. The Modular Multilevel Converter (MMC) is one of the most attractive candidates for the HVDC transmission system converter technology. Its high flexibility and controllability make it an attractive option for HVDC transmission. However, the higher initial investment and the unfavourable conditions for using associated DC circuit breakers have always been a barrier to further installations. Since ABB successfully developed the HVDC DC circuit breakers in 2012, there is increasing interest in DC grids using the MMC HVDC transmission system. However, one of the common problems existing in the HVDC transmission system is the control of the capacitor voltage in each submodule of the MMC. However, in the transmission systems, especially in the renewable energy systems, there are disturbances existing. The conventional voltage balancing control is weak to the disturbances, such as power and sampling frequency changes. Therefore, the proposed voltage balancing control in this thesis has improved the responding time and precision of the control. It determines the charging state of each submodule by deriving the capacitor voltage variations, thereby ensuring the voltage of each capacitor is within pre-defined range regardless the disturbance. In later study, both simulation and experimental results have shown the proposed control approach has strong immunity to the sampling frequency noise compared to the conventional control. However, even with the proposed voltage balancing control, the capacitor voltage difference cannot be eliminated entirely. They will cause circulating current flowing among the phases of the circuit. Therefore, causing unnecessary pressures to the affected components. The circulating current suppression control proposed in this thesis can eliminate the AC component of the circulating current, by regulating it according to the power going through the converter. It gets rid of the two PID controllers and abc-dq transformation which are commonly used in conventional circulating current control approach. The simulation and experiment results have shown the suppression of the proposed control approach regarding the AC components in the circulating current, and the fast response time taking effect within one control cycle. In this thesis, both proposed control approaches are presented with simulation results and validated with the scaled down experiment model.

#### Acknowledgement

Foremost, I would like to express my sincere gratitude to my supervisor Dr. David Atkinson for his continuous supports to my Ph.D. study and research, for his patience, motivation, enthusiasm, and immense knowledge and his guidance through the completion of this thesis. I am extremely proud of having a supervisor who is experienced, well-acknowledged, and passionate about the project all the time. His understanding and help in the designing and building of the experiment demonstrated the extremely high standard skill level as an electrical engineer which will be helpful in my later career. I would also like to express my appreciation to my second supervisor Dr. James Yu who has been dedicated to the pursuit of the leading technology for his support not only in academic but also in my leisure time set the first step of my Ph.D. study and have been supporting through my whole Ph.D. life. He was the one who made not only the project but my personal goal come true.

I would also like to express my appreciations to all the colleagues at Newcastle University who have spent their time and efforts during my Ph.D. study. I would specially thank Mr. Darren Mackie and Mr. Jeffrey Warren for their insightful comments and patience whenever something went wrong during the experiment testing, not only for their expertise in electrical engineering but also for their kindnesses and warm-hearted support for my study. Last, but not least, I would like to thank my parents for their quiet support and love for their son, not only during my study but also through my entire life.

# TABLE OF CONTENTS

| Chapter 1 | Introduction                                                    | 1  |

|-----------|-----------------------------------------------------------------|----|

| 1.1 In    | ntroduction                                                     | 1  |

| 1.2 Th    | The development of the high voltage transmission system         | 3  |

| 1.2.1     | Two-level or three-level VSC structure                          | 7  |

| 1.2.2     | Modular multilevel converter                                    | 8  |

| 1.2.3     | Other potential converters                                      | 11 |

| 1.3 Re    | Research background of the MMC                                  | 12 |

| 1.3.1     | Mathematical representations of MMC                             | 12 |

| 1.3.2     | Control signal modulation method                                | 14 |

| 1.3.3     | Selection of the arm inductor and submodule capacitor           | 15 |

| 1.3.4     | The external control loop                                       | 16 |

| 1.3.5     | The internal control loop                                       | 17 |

| 1.3.6     | The converter efficiency and performance under fault conditions | 19 |

| 1.4 Re    | Research contribution                                           | 20 |

| 1.4.1     | Mathematical model                                              | 20 |

| 1.4.2     | The modulation methods                                          | 20 |

| 1.4.3     | The capacitor voltage balancing control                         | 20 |

| 1.4.4     | Circulating current suppression control                         | 21 |

| 1.5 Pu    | Publications raised from the works                              | 22 |

| Chapter 2 | Converter modelling and parameter selection                     | 24 |

| 2.1 In    | ntroduction                                                     | 24 |

| 2.2 M     | Iodelling of the MMC                                            | 24 |

| 2.3 Pa    | Parameter Selection                                             | 34 |

| 2.4 Co    | Conclusion                                                      | 36 |

| Chapter 3 | Comparison and the modulation methods                           | 37 |

| 3.1 In    | ntroduction                                                     | 37 |

| 3.2 Co    | Control philosophy                                              | 40 |

| 3.2.    | 1 Circulating Current                                          | 43  |

|---------|----------------------------------------------------------------|-----|

| 3.2.    | 2 Submodule and one phase module                               | 44  |

| 3.3     | Simulation results                                             | 46  |

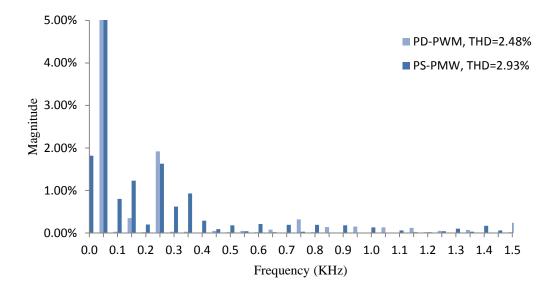

| 3.3.    | 1 Comparison between PD-PWM and PS-PWM                         | 46  |

| 3.3.    | 2 Converter output harmonics                                   | 52  |

| 3.3     | Conclusion                                                     | 57  |

| Chapter | 4 Proposed voltage balancing control                           | 58  |

| 4.1     | Introduction                                                   | 58  |

| 4.2     | Modelling                                                      | 60  |

| 4.3     | Mathematical representation of the MMC                         | 62  |

| 4.4     | Proposed control approach                                      | 66  |

| 4.5     | Simulation validation                                          | 67  |

| 4.6     | Experimental results                                           |     |

| 4.7     | Conclusion                                                     | 81  |

| Chapter | 5 Circulating current control                                  |     |

| 5.1     | Introduction                                                   |     |

| 5.2     | Modelling                                                      | 83  |

| 5.2.    | 1 Mathematical model                                           | 85  |

| 5.3     | Proposed control for circulating current suppression           | 86  |

| 5.4     | Simulation results                                             | 88  |

| 5.4     | .1 The simulation results for one-phase MMC scaled down model  | 88  |

| 5.4     | .2 The simulation results for two-end HVDC transmission system |     |

| 5.5     | Experiment results                                             |     |

| 5.6     | Conclusion                                                     | 104 |

| Chapter | 6 The experiment test rig design                               | 106 |

| 6.1     | Introduction                                                   | 106 |

| 6.2     | System units                                                   | 106 |

| 6.2.    | 1 Control unit IV                                              | 107 |

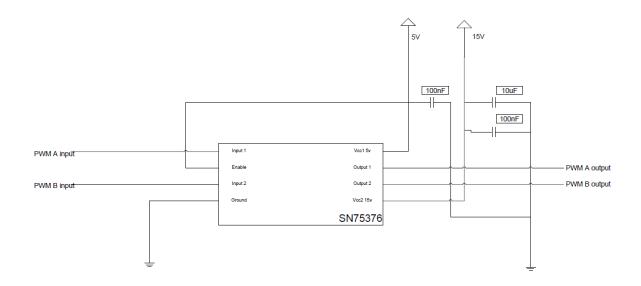

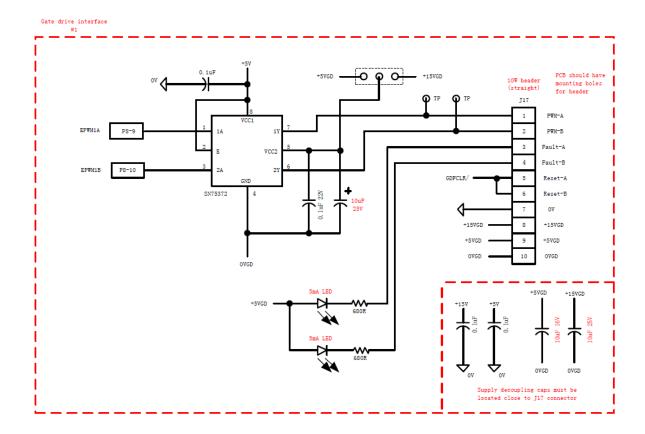

| 6.2.2       | The level shifter and the dual gate drive controller                     | 109 |

|-------------|--------------------------------------------------------------------------|-----|

| 6.2.3       | Submodules and MMC circuit                                               | 110 |

| 6.2.4       | Voltage sensors and current sensors                                      | 110 |

| 6.3 Ex      | perimental setup                                                         | 111 |

| 6.3.1       | The measurement of the capacitor voltage                                 | 112 |

| 6.3.2       | The measurement of the arm current                                       | 113 |

| 6.3.3       | PWM generation                                                           | 115 |

| 6.3.4       | Priority code generation                                                 | 117 |

| 6.3.5       | The implementation of the proposed control approaches                    | 118 |

| Chapter 7 C | Conclusion and future works                                              | 121 |

| 7.1 Int     | roduction                                                                | 121 |

| 7.2 Fin     | ndings with regard to the modelling and experimental test rig of the MMC |     |

| 7.2.1       | The mathematical model                                                   | 121 |

| 7.2.2       | Selection and comparison of the PWM scheme                               | 122 |

| 7.2.3       | The proposed voltage balancing control                                   | 123 |

| 7.2.4       | AC current suppression control                                           | 124 |

| 7.2.5       | The experimental test rig setup                                          | 124 |

| 7.3 Ge      | neral conclusions                                                        | 125 |

| 7.4 Fut     | ture work                                                                | 126 |

| Reference   |                                                                          | 140 |

# Lists of Figures, Tables, and Symbols

| Figure 1: The transmission line setup of the HVAC/HVDC transmission systems, the       |   |

|----------------------------------------------------------------------------------------|---|

| investment cost along with the transmission distance                                   | 4 |

| Figure 2: The four-terminal configuration of the HVDC transmission system              | 6 |

| Figure 3: The topology of the conventional (a) two-level converter (b) the three-level |   |

| converter                                                                              | 8 |

| Figure 4: The typical structure of a three-phase MMC.                                  | 9 |

| Figure 5: The submodule structure of the (a) half-bridge MMC (b) full-bridge MMC           | 10  |

|--------------------------------------------------------------------------------------------|-----|

| Figure 6: The topology of the matrix converter in a back-to-back application               | 12  |

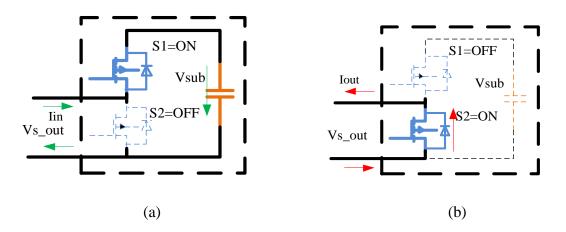

| Figure 7: Arm current flowing when the submodule capacitor is (a) connected to the circuit |     |

| (b) in bypassing mode                                                                      | 26  |

| Figure 8: The on/off states of the full-bridge submodule                                   | 26  |

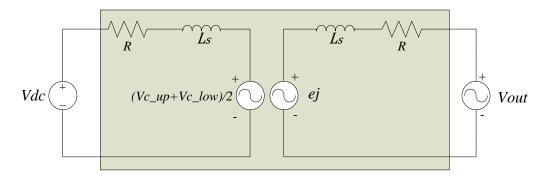

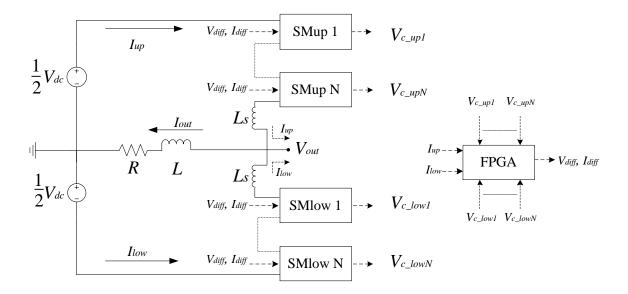

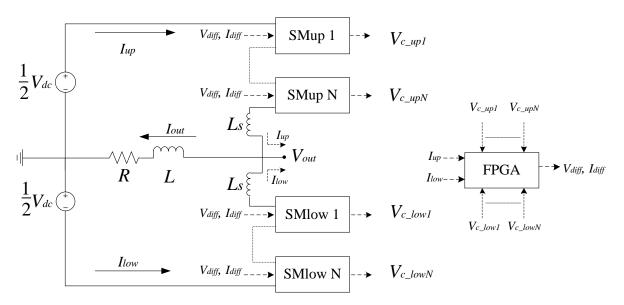

| Figure 9: The equivalent model of the MMC                                                  | 27  |

| Figure 10: Representation of the voltage steps in MMC                                      | 29  |

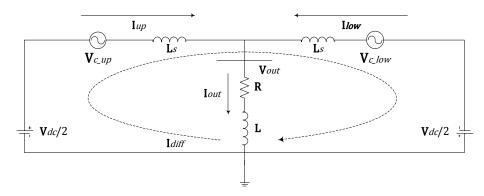

| Figure 11: The equivalent decoupling circuit of the MMC.                                   | 31  |

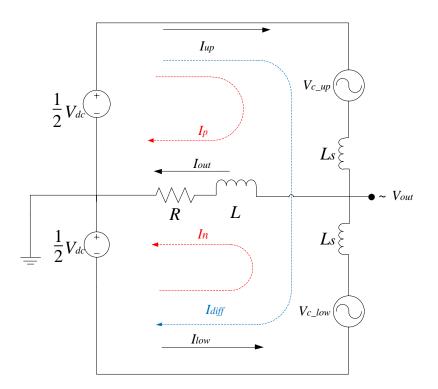

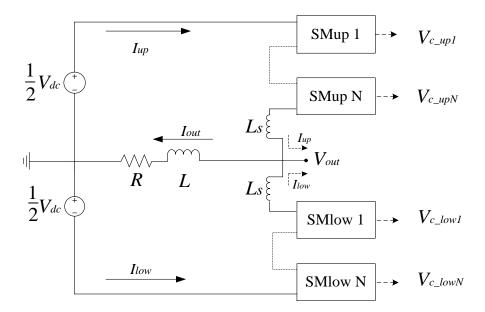

| Figure 12: The equivalent model of the single phase MMC                                    | 32  |

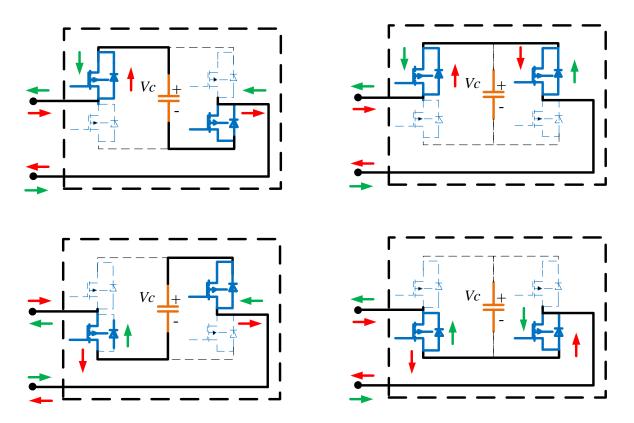

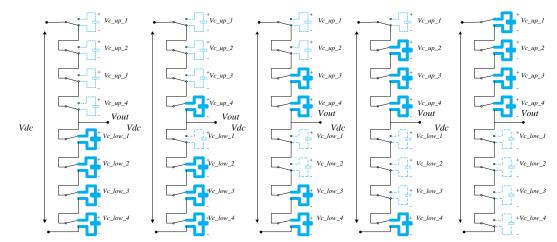

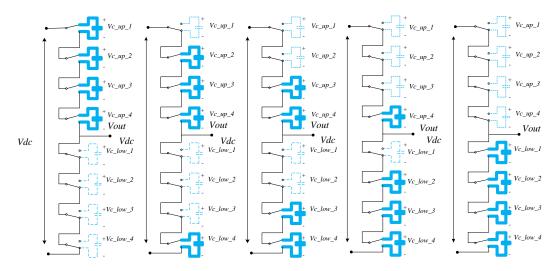

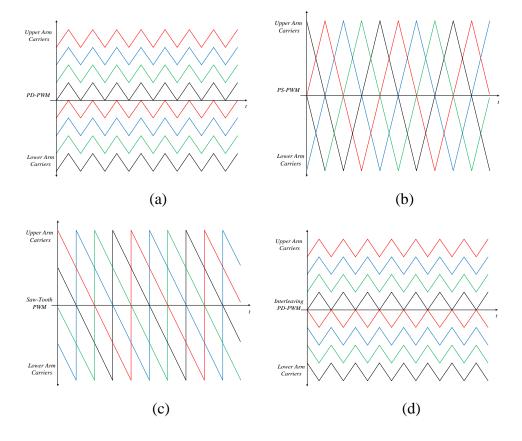

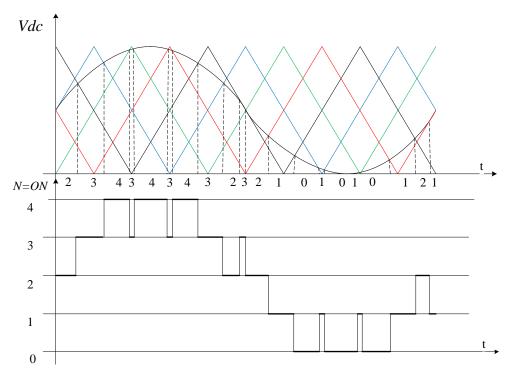

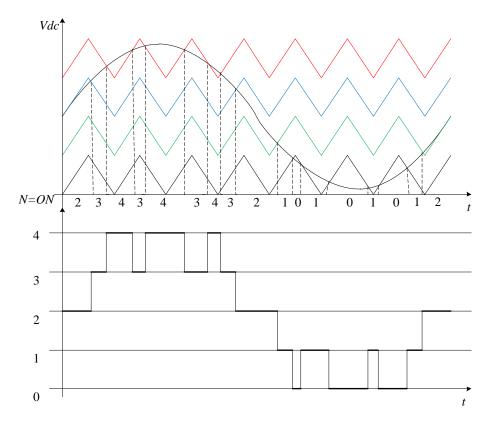

| Figure 13: The (a) PD-PWM (b) PS-PWM (c) Saw-Tooth PWM (d) Interleaving PWM                |     |

| patterns for the four-level MMC                                                            | 33  |

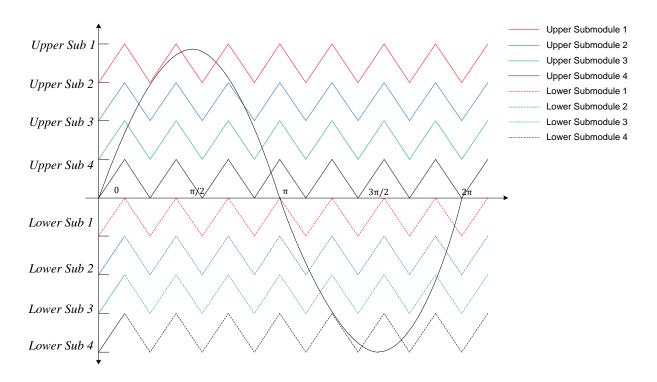

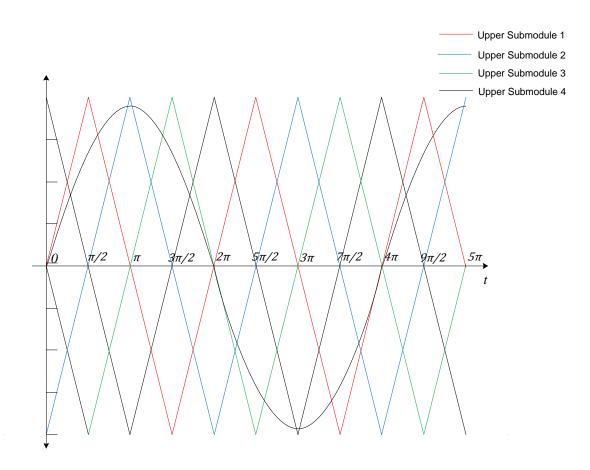

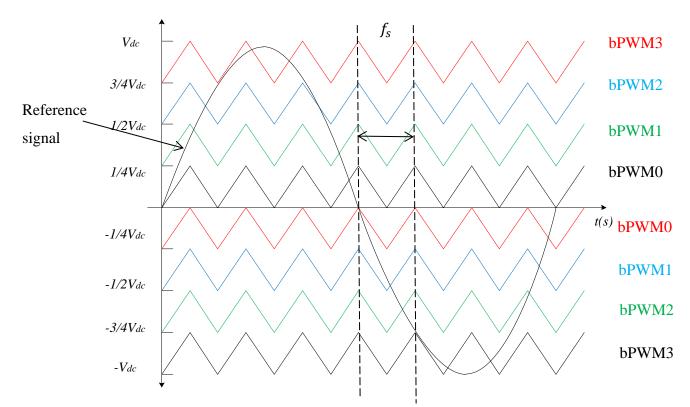

| Figure 14: The modulation of the MMC based on PS-PWM                                       | 38  |

| Figure 15: The modulation of the MMC based on PD-PWM                                       | 38  |

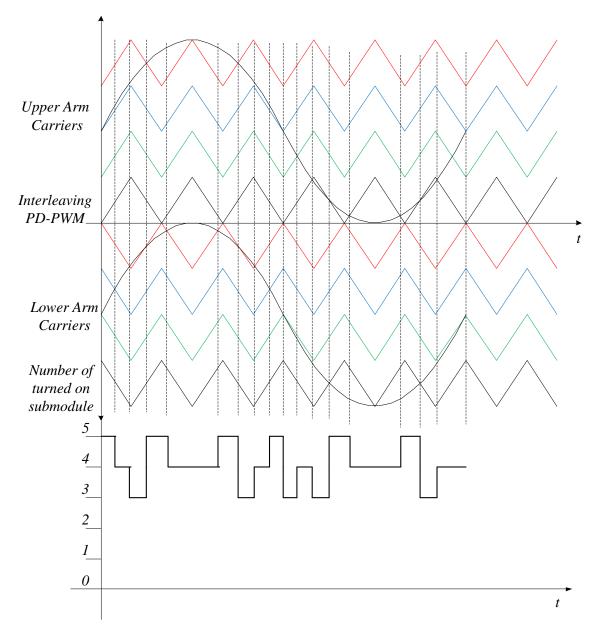

| Figure 16: The interleaving technology applied in MMC                                      | 39  |

| Figure 17: Voltage balancing control                                                       | 41  |

| Figure 18: Upper and lower arm carrier waveforms using PD-PWM signal                       | 42  |

| Figure 19: Upper and lower arm carrier waveforms using PS-PWM signal                       | 42  |

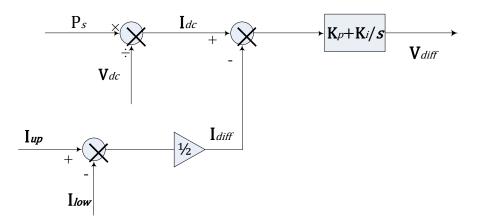

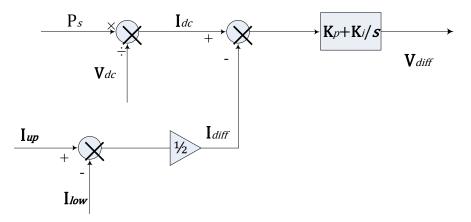

| Figure 20: Circulating current suppressing scheme                                          | 44  |

| Figure 21: One phase module of the Modular Multilevel Converter                            | 45  |

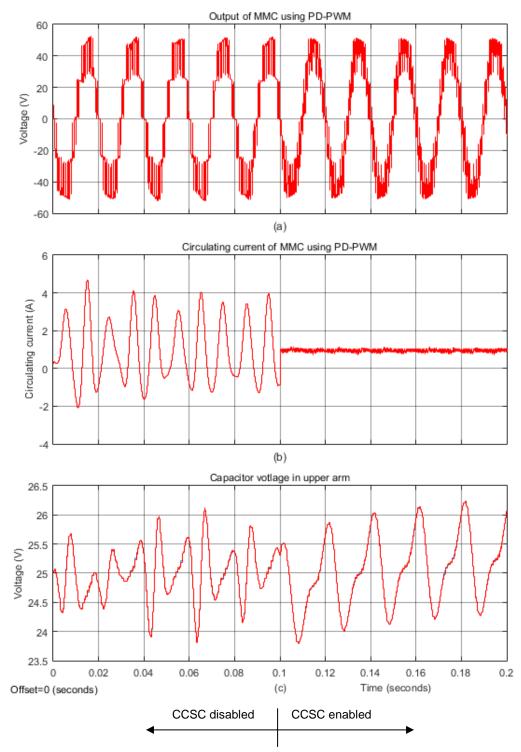

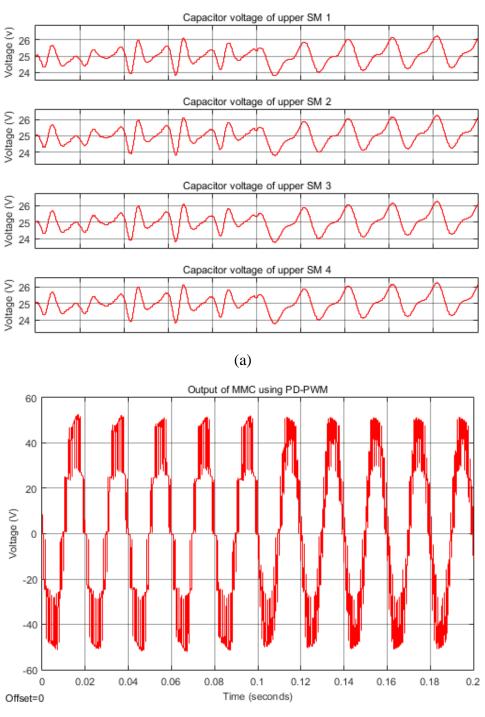

| Figure 22: The simulation results of PD-PWM scheme with CCSC, phase-a (a) output volta     | ıge |

| (b) Circulating current (c) Capacitor voltage.                                             | 47  |

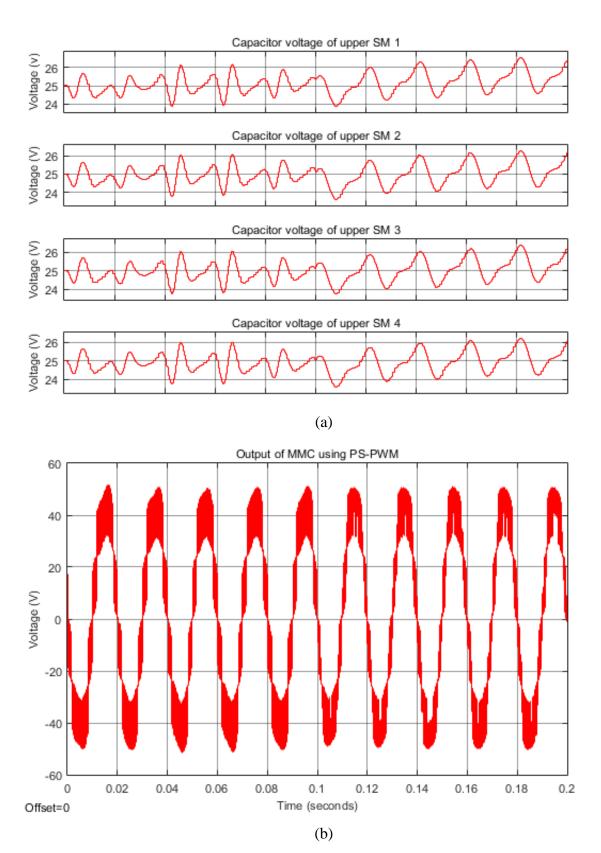

| Figure 23: The simulation results of PS-PWM phase-a (a) output voltage (b) Circulating     |     |

| current (c) Capacitor voltage                                                              | 48  |

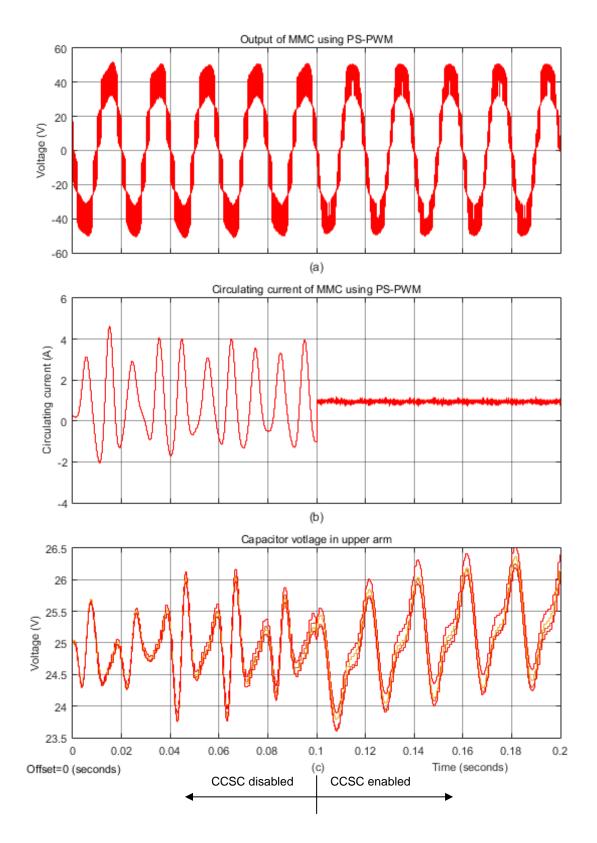

| Figure 24: The output of the MMC using PD-PWM with CCSC applied at 0.1s (a) the upper      | r   |

| arm capacitor voltages (b) the output voltage                                              | 49  |

| Figure 25: The output of the MMC using PS-PWM with CCSC applied at 0.1s, (a) the upper     | r   |

| arm capacitor voltages (b) the output voltage                                              | 50  |

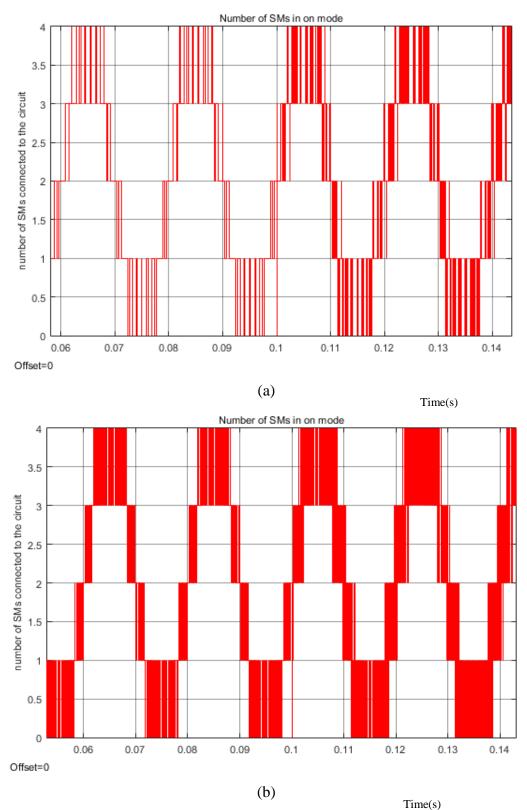

| Figure 26: The gate signals for the upper submodules using (a) PD-PWM (b) PS-PWM           | 51  |

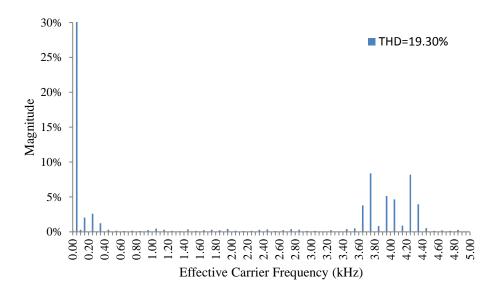

| Figure 27: The converter output voltage harmonics.                                         | 52  |

| Figure 28: The converter output harmonics regarding the harmonics orders                   | 57  |

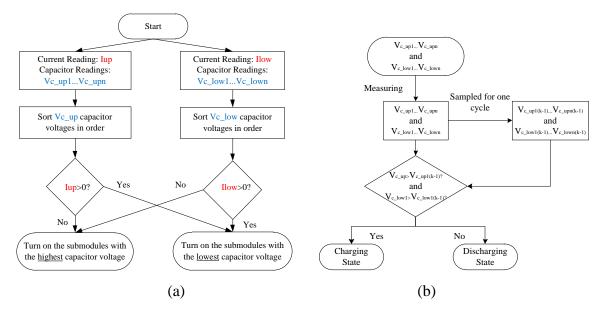

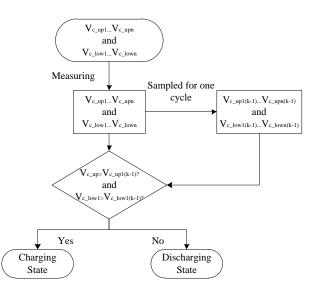

| Figure 29: Flow chart of the (a) conventional voltage balancing (b) proposed voltage       |     |

| balancing controlling approach during normal operations.                                   | 60  |

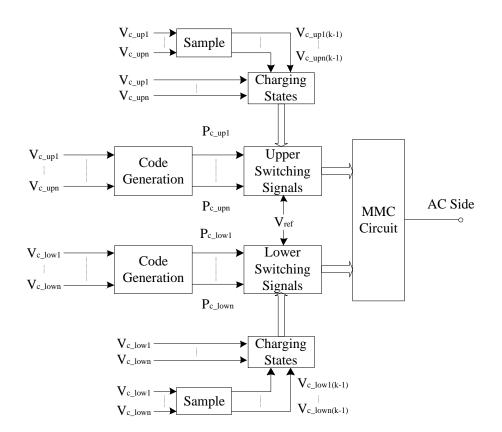

| Figure 30: The proposed voltage balancing control scheme implemented in the simulation     |     |

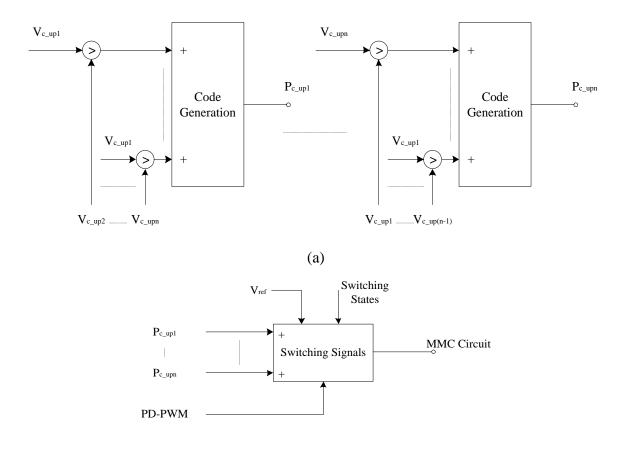

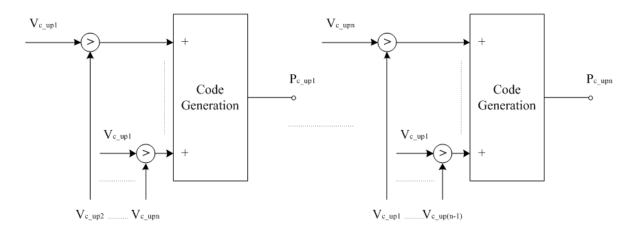

| model                                                                                      | 61  |

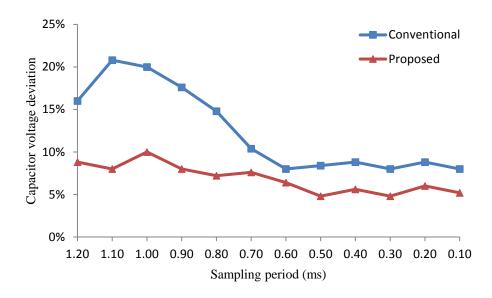

| Figure 31: The generation of the (a) priority code (b) switching signal for the proposed       |  |  |

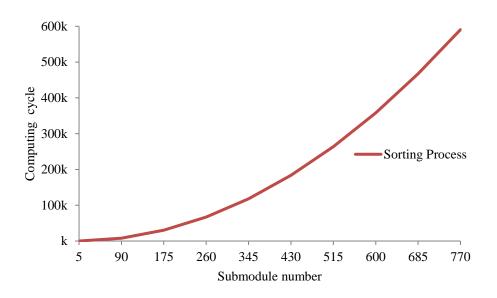

|------------------------------------------------------------------------------------------------|--|--|

| voltage balancing control                                                                      |  |  |

| Figure 32: The capacitor voltage deviations with different sampling periods                    |  |  |

| Figure 33: The computation cycle with different submodule numbers                              |  |  |

| Figure 34: The simulation model of the single phase MMC68                                      |  |  |

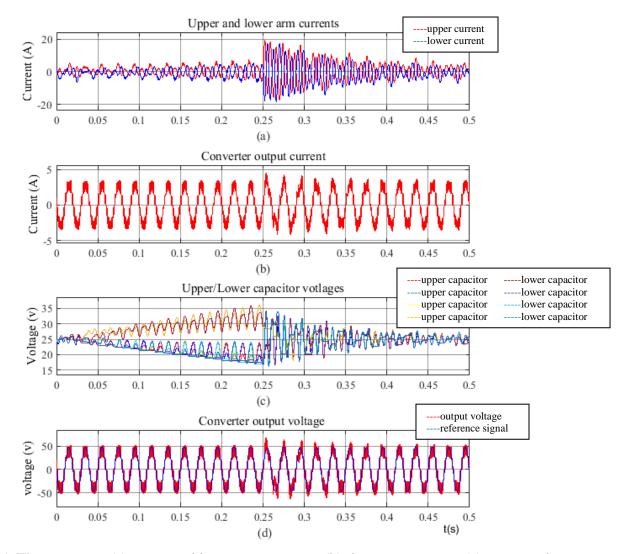

| Figure 35: The converter (a) upper and lower arm currents (b) the current output (c) upper and |  |  |

| lower arm capacitor voltages (d) voltage output when the sampling frequency is insufficient.   |  |  |

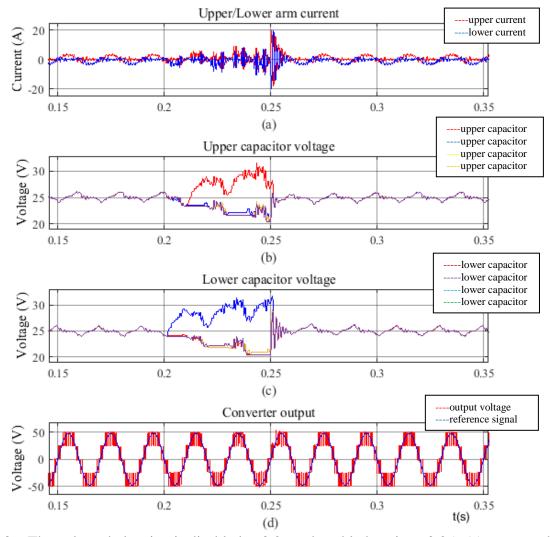

| Figure 36: The voltage balancing is disabled at 0.2s and enabled again at 0.25s (a) upper and  |  |  |

| lower arm current (b) upper arm capacitor voltages (c) lower arm capacitor voltages (d) load   |  |  |

| voltage and reference signals                                                                  |  |  |

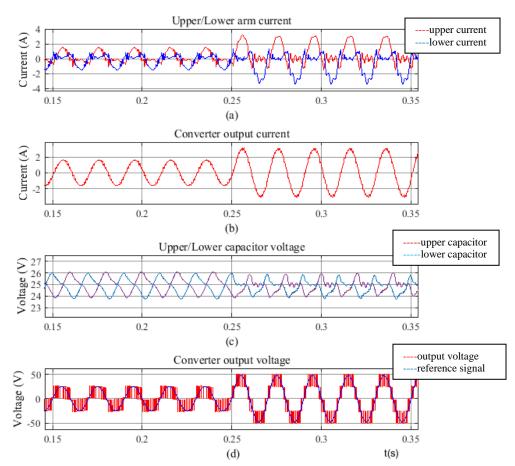

| Figure 37: The simulation results (a) the upper and lower arm current (b) the load current (c) |  |  |

| upper and the lower arm capacitor voltages (d) load voltage with reference signal when the     |  |  |

| modulation index changes from 0.5 to 0.95 at 0.25s71                                           |  |  |

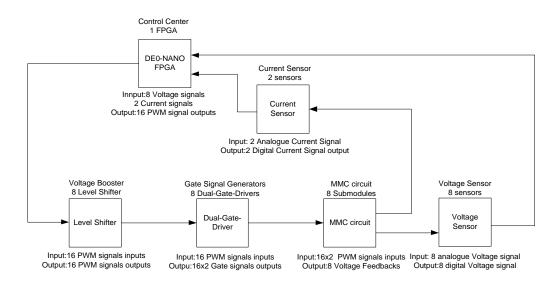

| Figure 38: The flow diagram of the experiment model73                                          |  |  |

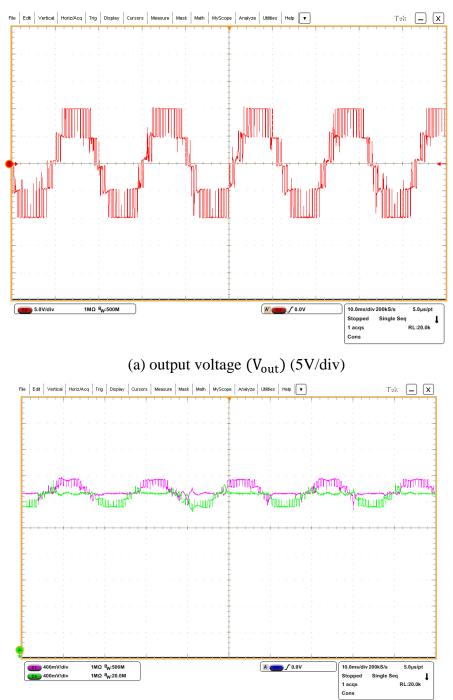

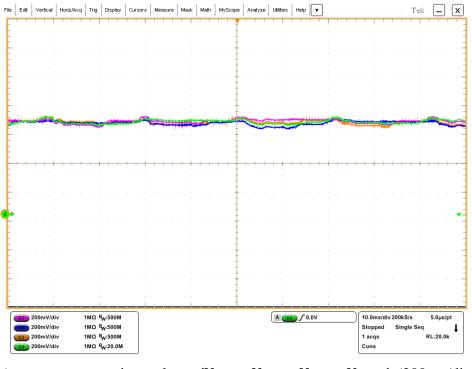

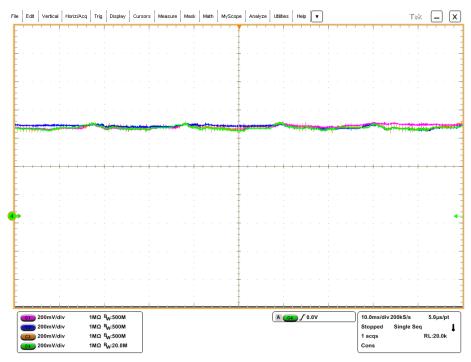

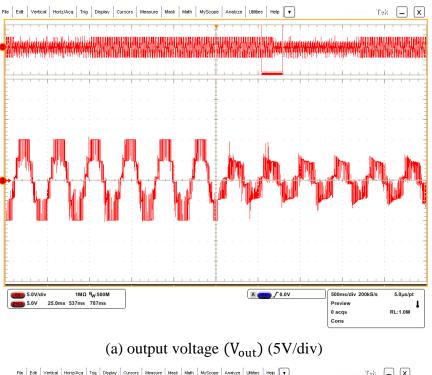

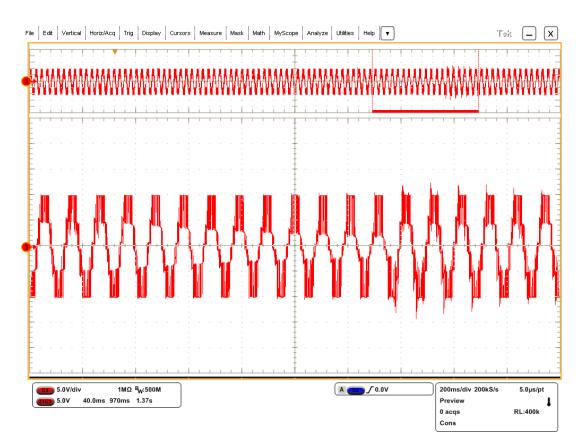

| Figure 39: Experimental results during normal operation using new voltage balancing control    |  |  |

| where MI=0.95, F =50Hz75                                                                       |  |  |

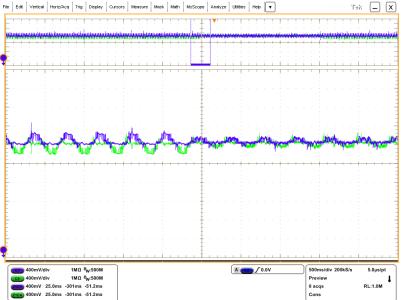

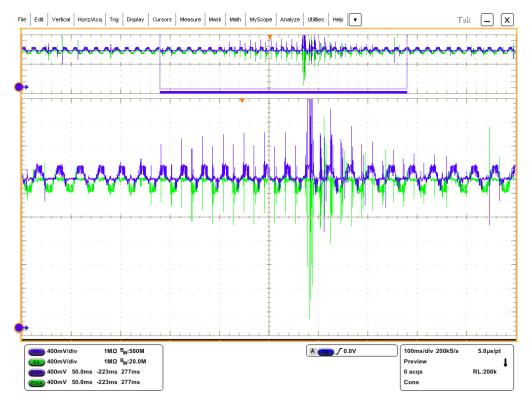

| Figure 40: Experimental results for the new voltage balancing control where MI has changed     |  |  |

| from 0.95 to 0.5                                                                               |  |  |

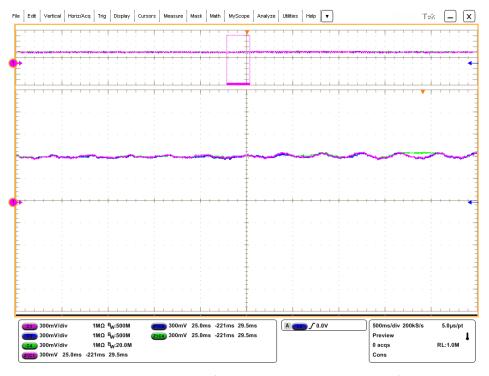

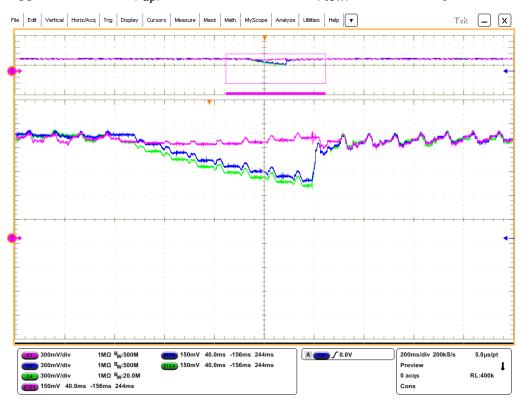

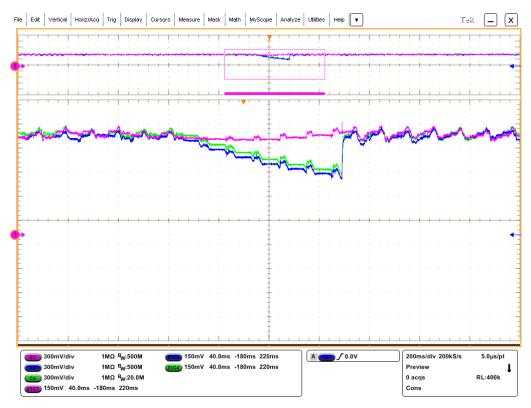

| Figure 41: Experimental results for the new voltage balancing control when disabled and        |  |  |

| enabled again after a short period80                                                           |  |  |

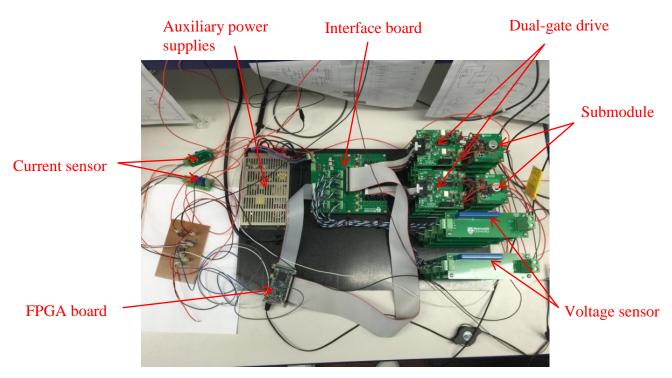

| Figure 42. A photograph of the experimental test rig                                           |  |  |

| Figure 43: The three phase MMC model                                                           |  |  |

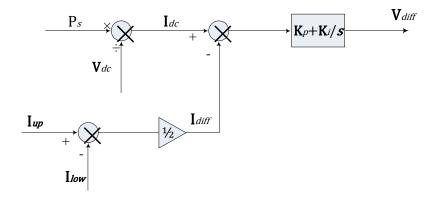

| Figure 44: the feedforward controller for circulating current suppressing                      |  |  |

| Figure 45: The single-phase scale-down model of the simulation for voltage balancing and       |  |  |

| circulating current suppressing                                                                |  |  |

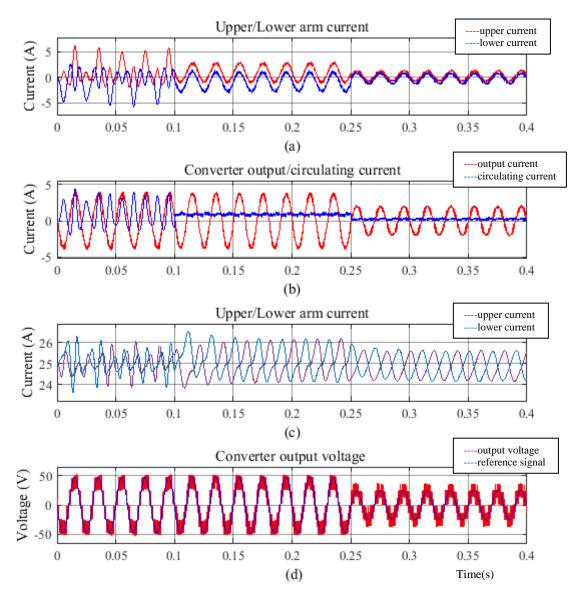

| Figure 46 Simulation results for of the CCSC when it is activated at 0.1s and the modulation   |  |  |

| was changed from 0.95 to 0.5 at 0.25s, (a) the upper and lower arm currents, (b) converter     |  |  |

| output current and circulating current, (c) upper and lower arm current, (d) converter output  |  |  |

| voltage and reference signal                                                                   |  |  |

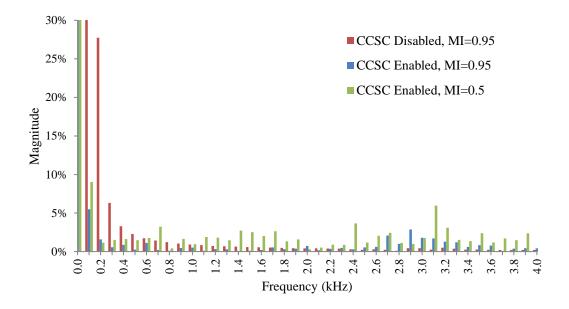

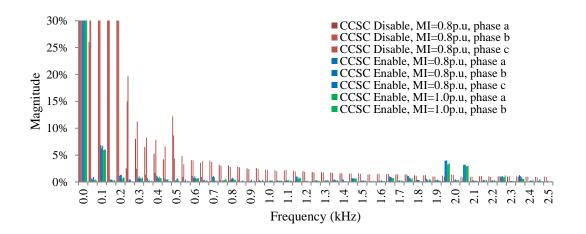

| Figure 47 FFT analysis of the circulating current in 3 different stages (a) CCSC disabled,     |  |  |

| MI=0.95, (b) CCSC Enabled, MI=0.95, (c) CCSC Enabled, MI=0.591                                 |  |  |

| Figure 48 The output voltage analysis before/after the CCSC has been enabled92                 |  |  |

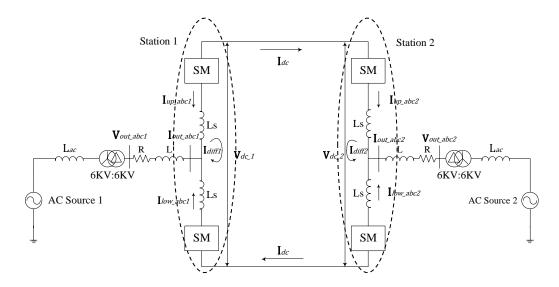

| Figure 49. Two-terminal transmission system                                                    |  |  |

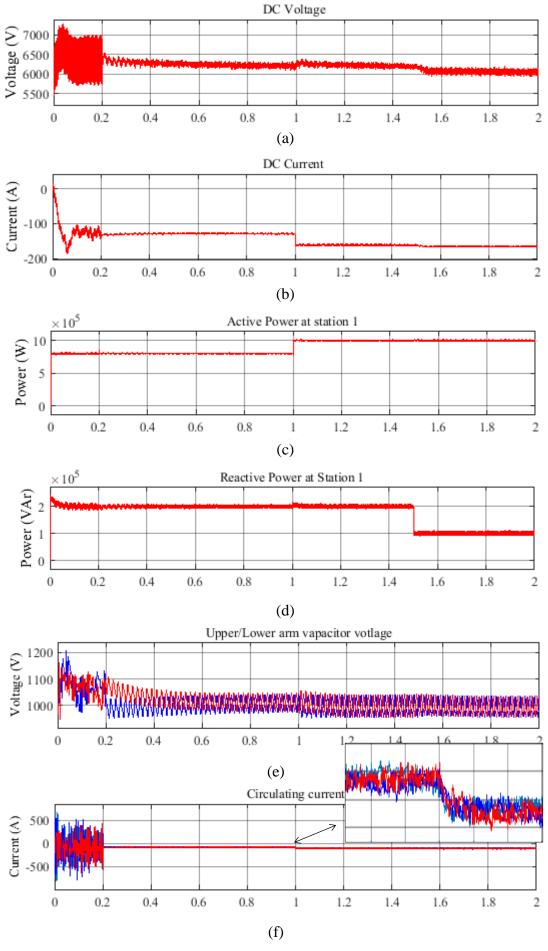

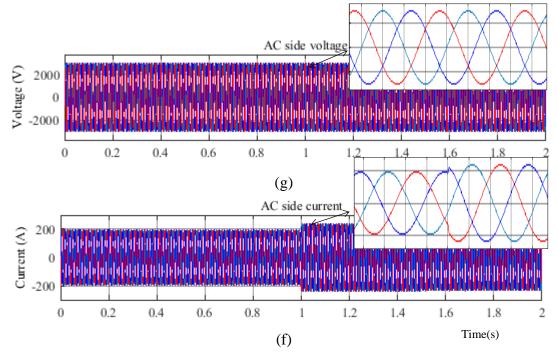

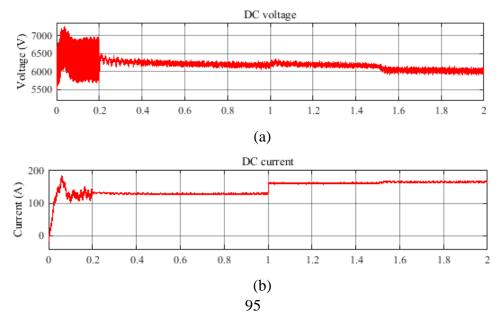

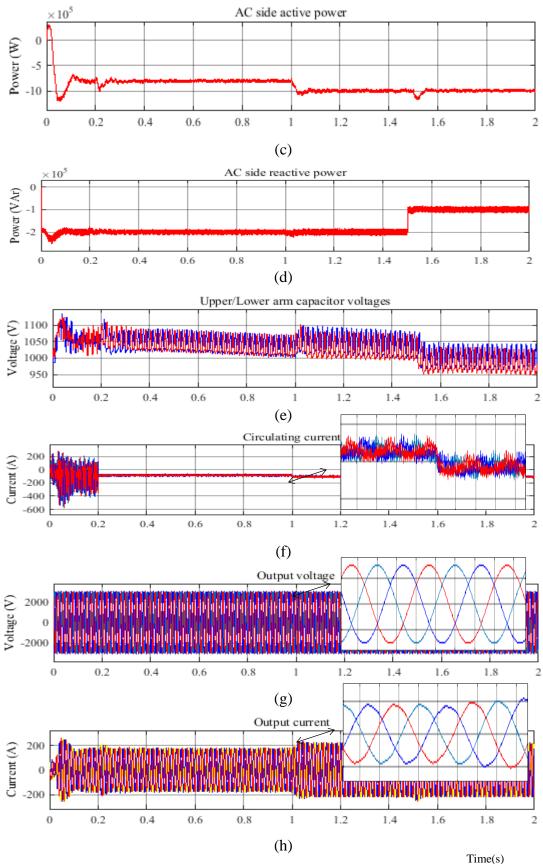

| Figure 50 simulation results for station one (a) DC voltage (b) Direct current (c) activ | ve power   |

|------------------------------------------------------------------------------------------|------------|

| (d) reactive power (e) upper/lower arm voltages (f) circulating current (g) AC side vo   | oltage (h) |

| AC side current.                                                                         |            |

| Figure 51 Simulation results for station two (a) DC voltage (b) DC current (c) active    | power      |

| (d) reactive power (e) upper/lower arm voltages (f) circulating current (g) AC side vo   | oltage (h) |

| AC side current.                                                                         |            |

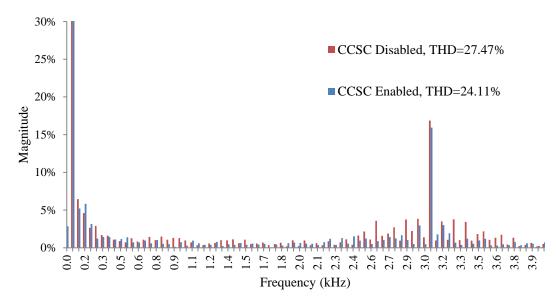

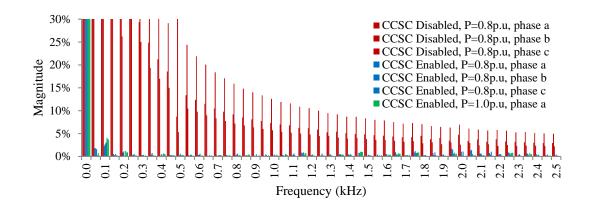

| Figure 52 FFT analysis of the circulating current in station one (a) before applying th  | ne CCSC    |

| (b) after applying the CCSC with P=0.8MW (c) after applying CCSC with P=1MW              |            |

| Figure 53 FFT analysis for the circulating current in station two (a) before applying t  | the        |

| CCSC (b) after applying the CCSC with P=0.8MW (c) after applying CCSC with P=            | 1MW. 97    |

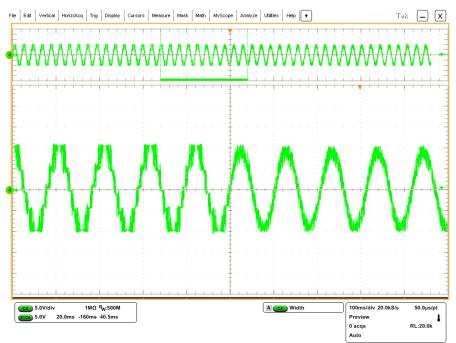

| Figure 54 The experiment results of the single phase MMC model, the CCSC is initia       | ally       |

| disabled and enabled again later.                                                        | 100        |

| Figure 55 The FFT analysis of the output voltage before/after the CCSC has been ena      | bled.101   |

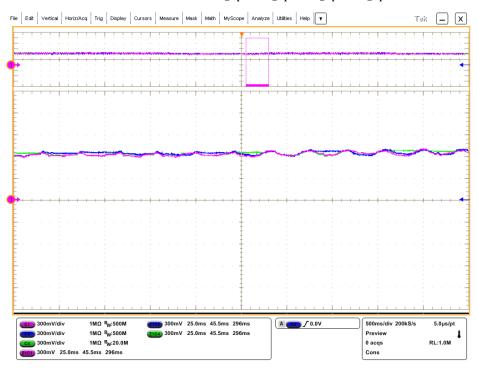

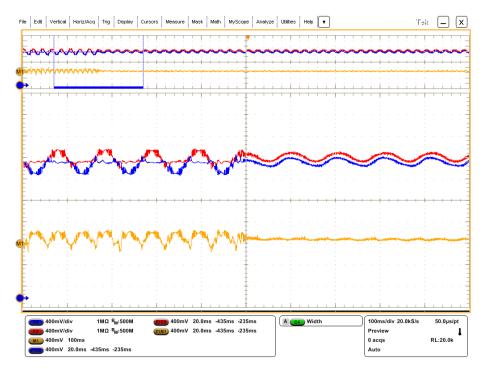

| Figure 56 The experiment results of the single-phase MMC model where the MI is in        | itially    |

| set at 0.95 and later was changed to 0.5                                                 | 104        |

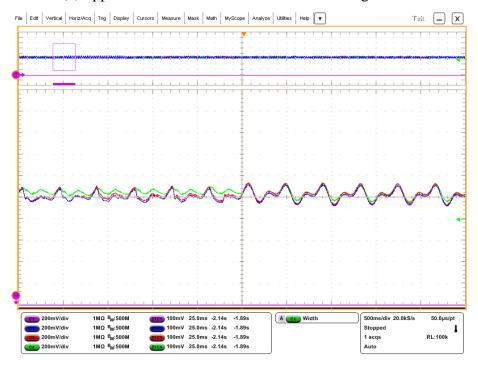

| Figure 57 the FFT analysis of the circulating current (a) before the CCSC has applied    | 1 (b)      |

| after the CCSC has applied and MI=1 (c) after the CCSC has applied and MI=0.5            | 104        |

| Figure 58: Block diagram of the experiment test rig.                                     | 107        |

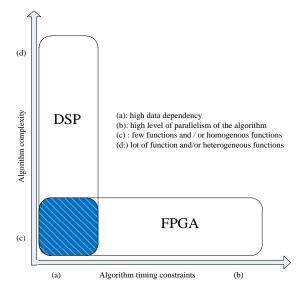

| Figure 59: the use of the DSP and FPGA regarding the time constraints and the comp       | lexity.    |

|                                                                                          | 107        |

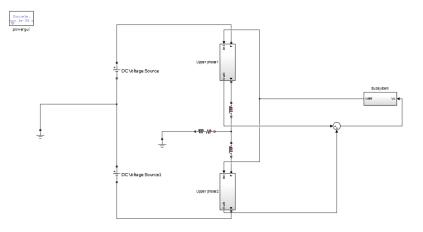

| Figure 60: The experiment model of the hall-bridge based MMC.                            | 111        |

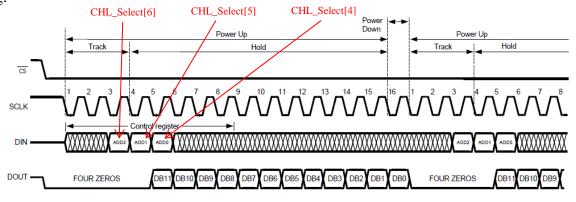

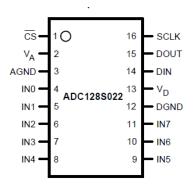

| Figure 61: The timing diagram of the ADC128S002                                          | 113        |

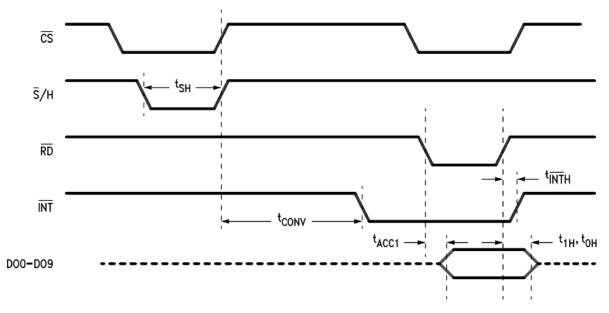

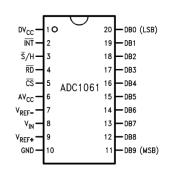

| Figure 62: The timing diagram of the ADC1061CIN                                          | 114        |

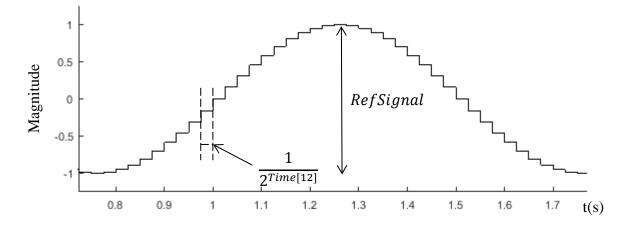

| Figure 63: The PWM carrier signal and the reference signal.                              | 116        |

| Figure 64: The assign of the priority codes                                              | 117        |

| Figure 65: The states selection approach according to the capacitor voltage              | 118        |

| Figure 66: The control block diagram of the CCSC with measuring of both upper and        | lower      |

| arm currents                                                                             | 119        |

| Figure 67: The step-up step-down generation of the reference signal                      | 120        |

| Table 1: The voltage rating of applications in different voltage range | 4  |

|------------------------------------------------------------------------|----|

| Table 2: The completed/planned UHV transmission lines in China         | 7  |

| Table 3: the component used in different types of multilevel converter | 25 |

| Table 4: Output of submodules regarding the switching states                            | 45   |

|-----------------------------------------------------------------------------------------|------|

| Table 5: Parameters of the PD-PWM/PS-PWM based MMC                                      | 46   |

| Table 6: Planning harmonic levels for 400V systems                                      | 53   |

| Table 7: Planning harmonic levels for 6.6kV, 11kV, and 20kV systems                     | 53   |

| Table 8: Planning harmonic levels for systems >20kV, < 145kV                            | 53   |

| Table 9: Planning harmonic levels for 275kV and 400kV systems                           | 54   |

| Table 10: The system parameters of the 40 level MMC                                     | 55   |

| Table 11: The comparison between the simulation and the grid code requirements          | 56   |

| Table 12: The range of the ideal sampling period with different number of submodules    | 65   |

| Table 13: The parameter used in the simulation to verify the proposed voltage balancing |      |

| approach                                                                                | 67   |

| Table 14: Parameters Used For Experimental Model                                        | 72   |

| Table 15: The parameters selected for the single-phase scaled down model                | 89   |

| Table 16: Parameters Used For Experimental Model                                        | 93   |

| Table 17: The channel selection code diagram                                            | .112 |

| Table 18: The PWM frequency list regarding the time register and the PWM register       | .116 |

| V <sub>out</sub> :       | converter output voltage                                   |

|--------------------------|------------------------------------------------------------|

| $V_{dc}$ :               | DC link voltage                                            |

| $V_{c\_up}$ :            | upper arm equivalent voltage                               |

| $V_{c_low}$ :            | lower arm equivalent voltage                               |

| $L_s$ :                  | arm inductance                                             |

| $I_{up}$ :               | upper arm current                                          |

| I <sub>low</sub> :       | lower arm current                                          |

| $e_j$ :                  | inner imaginary voltage                                    |

| I <sub>diff</sub> :      | differential current                                       |

| $V_{c\_up}^*$ :          | control signal for the upper arm                           |

| $V_{c\_low}^*$ :         | control signal for the lower arm                           |

| MI:                      | modulation index                                           |

| <i>ω</i> <sub>0</sub> :  | fundamental rotating speed                                 |

| $\varphi$ :              | phase angle                                                |

| $N_{c\_up1}N_{c\_upn}$ : | switching states of the submodule in the upper arm         |

| $V_{c\_up1}V_{c\_upn}$ : | capacitor voltages of the first submodule in the upper arm |

| $N_{c\_up1}N_{c\_upn}$ :        | switching states of the submodule in the low arm         |

|---------------------------------|----------------------------------------------------------|

| $V_{c\_up1}V_{c\_upn}$ :        | capacitor voltages of the first submodule in the low arm |

| $I_p$ :                         | output currents in upper arm                             |

| $I_n$ :                         | output currents in lower arm                             |

| C <sub>arm</sub> :              | arm capacitance                                          |

| $E_{cmax}$ :                    | rated converter power                                    |

| $P_s$ :                         | apparent power                                           |

| EP:                             | energy-power ratio                                       |

| $C_1 \ldots C_N$ :              | individual capacitance of each capacitor                 |

| <i>N</i> :                      | number of the submodule in each arm                      |

| <i>ɛ</i> :                      | capacitor voltage ripple                                 |

| C <sub>sub</sub> :              | capacitance of each capacitor                            |

| Cos $\varphi$ :                 | power factor                                             |

| <i>I</i> <sub>2<i>f</i></sub> : | maximum value of the circulating current                 |

| α:                              | fault current rise rate                                  |

| N <sub>on</sub> :               | number of the turned-on submodule                        |

| Pout:                           | output power                                             |

| $V_{dc}^*$ :                    | demanding voltage of capacitors                          |

| $i_{diff1}^*$ :                 | calculated different current                             |

| $V_{C_avg}$ :                   | average voltage of the capacitors                        |

| <i>S</i> <sub>1</sub> :         | the first switch in submodule                            |

| <i>S</i> <sub>2</sub> :         | the second switch in submodule                           |

| V <sub>sub</sub> :              | submodule reference voltage                              |

| <i>f</i> :                      | carrier frequency                                        |

| $\theta_1 \dots \theta_n$ :     | the switching angle of the submodules                    |

| <i>R</i> :                      | load resistance                                          |

| Ts:                             | sampling period                                          |

|                                 |                                                          |

## Chapter 1

# Introduction

#### **1.1 Introduction**

The three-phase transmission system has been used in energy transmission systems across different power grids since it was first introduced in the early 1870s. The mature technologies of the three-phase transmission systems compared to the single-phase transmission systems determined that the three-phase system was considered more attractive in the power transmission systems. However, the drawbacks such as relatively high distributed capacitance in the transmission lines exist in the three-phase system when considering the economy efficiency. The distributed capacitance can result in the increasing of the reactive power absorbed by the transmission lines for it needs to be charged to the voltage level during normal operation. Therefore, a large amount of transmission losses can be foreseen in long distance power transmission. It is predicted as high as 30-40% of the total losses per 1000km [1], whereas the High Voltage Direct Current (HVDC) transmission system only has around 3.5% transmission losses along the same distance. Because there are only two transmission lines in the HVDC transmission systems compared to the three-transmission lines in three-phase transmission system, and furthermore, the Direct current in the HVDC transmission lines only charges the distributed line capacitance when the system is activated hence the HVDC transmission system can have much lower transmission losses than the three-phase transmission system regarding the transmitting stage [2][3]. The initial investment for HVDC transmission lines is higher than conventional three-phase transmission system. Two major expenses of the original investment are the installations of AC filters and the converters [4]. They have always been the barriers to the further installation of HVDC transmission systems. In the past fifteen years, the global energy consumption has been increasing by 3% each year [5]. The growing demand for energy not only stimulates the spread of more energy networks but also requires the interconnection between different power grids. For example, in Europe, there are 23 HVDC transmission projects under construction and scheduled for completion before 2024 [6]. These systems, which employ subsea cables, are either connected to distant off-shore wind farms or used for interconnecting several countries with different fundamental frequencies. The higher installation cost for three-phase subsea cables and the high-power losses through the long distance subsea three-phase transmission lines determined that the threephase transmission system will not be the best option in these cases. On the other hand, the

recent rapid development of the power semiconductor switches, such as Insulated-Gate Bipolar Transistor (IGBT) and DC circuit breakers for high voltage applications [7], has made HVDC more attractive for high voltage applications. There is increasing interest in using Modular Multilevel Converter (MMC) based HVDC transmissions systems, considering the lower transmission losses and the installation costs compared to the three-phase transmission system over long distances. MMC based HVDC transmission topology has attracted much attention from researchers in recent years. However, compared to the well documented traditional three-phase transmission technologies, the research regarding MMC HVDC topology is still developing.

In the history of the development of the HVDC transmission system, the Line Commutated Converter (LCC) was initially employed in the HVDC transmission system. The switching device can be either uncontrollable (such as diode) or controllable (such as thyristor). However, because the power rating of the transmission site is getting higher recently and the significant improvement of the switching devices, the Voltage Source Converter (VSC) based HVDC transmission system appears to have a smaller site area and more cost efficient compared to the LCC based HVDC transmission system at the same power rating. The conventional Voltage Source Converter (VSC) based HVDC transmission system typically employs the two-level or three-level converters using thyristor valves, one of the disadvantages in this topology is a large amount of harmonics on the AC side. Therefore, the AC filters are required on the AC side of the converter to lower the high-frequency harmonics before connecting to the grids [8]. In the conventional HVDC transmission topology, the AC side filters can take up to half the space of the substation. The investment of the conventional transmission sites can be significant when using the two-level or three-level converters. In 2001, Prof. R. Marquardt suggested and patented a new structure for the multilevel converter, Modular Multilevel Converter (MMC), which is one of the most attractive candidates for HVDC transmission system [9]. The multilevel series connected structure and the identical submodules not only reduce the converter output harmonics on the AC side but also lower the difficulty of manufacturing. The multilevel structure also leads to the small voltage step across the submodules, which can result in the lower dv/dt across the components inside each submodule, and reducing the electromagnetic emission and the inrush current at given switching frequency. Therefore, by increasing the number of submodule can lower the size and requirement of the components in each submodule. Another benefit of using MMC is the lower converter output harmonics. When increasing the number of submodules in each arm, the converter output voltage steps are getting smaller. Once the number of submodules is sufficient,

2

the size of the AC harmonic filter is much smaller than the ones in conventional two-level or three-level converter topology, or the AC harmonic filter is not even necessary in some cases [10]. However, as a result of a large number of the submodules, the high initial investment is justified. One of the biggest problems regarding the MMC is the much greater components cost compared to the traditional two-level thyristor-based converter topology. The modular multilevel structure requires a large number of submodules connected in series in each arm to achieve the smaller voltage step changes, hence the lower converter harmonics. In commercial MMC HVDC system [11], the number of submodules in each arm can be up to 200, including the surplus submodules when there are one or more failure submodules [12]. This large number of submodules leads to high component costs even with the half-bridge MMC structure. The initial investment for the substation can be even higher with full-bridge MMC structure. Hence, author has investigated the potentials of lowering the component costs as well as improving the converter performance in different aspect, and provided the advanced voltage balancing control which can have better performance than the conventional voltage balancing control in different sampling frequency condition. In addition, the simplified circulating current suppressing control is also proposed and verified by both simulation and experimental results, showing strong control of the circulating current existing in the upper and lower arm of the MMC. The detailed results are presented in the following chapters and published in [13][14] as well.

#### 1.2 The development of the high voltage transmission system

It is commonly known in the industrial transmission applications that the higher voltage in the transmission lines, the lower current will be conducted through the transmission lines at the same power rating, therefore lowering the losses along the transmission lines. Base on that, the high voltage or even ultra-high voltage is always preferred in long distance transmission systems. The voltage ratings are presented in Table 1. In three-phase transmission systems, the transmission voltage can be boosted up easily by adding transformers between two networks, hence lowering the currents flowing through the transmission lines. However, the transmission losses caused by the aforementioned distributed capacitance can be large in long distance transmission. Therefore, researchers are seeking a more efficient way to further reduce the losses thus improving the efficiency of the overall network. Due to the need for clean energy, the demand for renewable energy such as wind farm, solar power system, and tide energy etc. are growing [16]. One of the drawbacks of using High Voltage Alternating Current (HVAC) transmission system to transfer the renewable energy is that, because the power generated by the renewable site is highly dependent on the weather condition, the renewable energy networks may not be as stable as traditional electricity generation methods [17]. In that case, the HVDC transmission system offers immunity to the disturbances according to the weather conditions, because the receiving end and the sending end frequencies are independent. Furthermore, the HVDC transmission system is more efficient than the HVAC transmission system when the transmission distance is long.

| Voltage rating      | Voltage range                     |

|---------------------|-----------------------------------|

| Lower voltage       | 100V – 1 kV                       |

| Medium voltage      | 1 kV – 35 kV                      |

| High voltage        | 35 kV – 230 kV                    |

| Extra-high voltage  | 245 kV and above                  |

| Ultra-high voltage* | Over 1000 kV (AC), or 800 kV (DC) |

Table 1: The voltage rating of applications in different voltage range

\*: It is not defined in the IEC 60038, but is commonly recognized as ultra-high-voltage above that voltage range [15].

Usually, the renewable energy site is far away from the load centre, hundreds or thousands kilometers away. To reduce the electricity losses and costs, the DC transmission lines are preferred when the transmission distance is long, and sometimes it might be the only solution, for example, the distant offshore wind farm. However, due to the much higher initial investment for the substations, the HVDC transmission system is less competitive compared to the HVAC transmission system in less than 50 km – 100 km distance depending on the system configurations.

HVDC has a higher initial cost – the converter stations – but because the means of transmission (the overhead lines and the cables) are less expensive per kilometer with DC, there is a break-even distance.

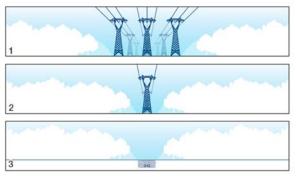

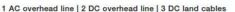

Figure 1: The transmission line setup of the HVAC/HVDC transmission systems, the investment cost along with the transmission distance.

Figure 1 demonstrates the structures of the HVAC/HVDC transmission systems. The number of the transmission lines required for HVDC transmission system is lower than the HVAC transmission system. The HVDC transmission system which employs the DC land cables can reduce the investment for the transmission towers, especially when the DC land cables are used to connect the offshore wind farms. The initial investment cost for the HVDC substations is much higher than the HVAC substations. However, when the transmission distance is increased, the difference between the initial investment of the HVDC and HVAC transmission system is getting smaller. There is a critical point where the costs for both HVDC and HVAC transmission systems are the same, and beyond that point the HVDC transmission system is more cost efficient than the HVAC transmission system. It can be seen in Figure 1 that the initial investment of the AC terminal is lower than the DC terminal. However, the line costs for the AC transmission lines are much higher compare to the DC transmission lines at the same distance. Therefore, the higher initial investment of the DC terminal can be justified by the lower costs of the lines compared to the AC system configurations. Once the distance beyond 150km (50km for subsea cables), the overall investment of the DC transmission system is lower than the AC transmission system. The offshore wind farms connected to the onshore site using subsea cables is considered the most cost efficient application for HVDC transmission system. The break-even distance can be as low as 30 km, which is highly competitive when installing the offshore wind farm [18].

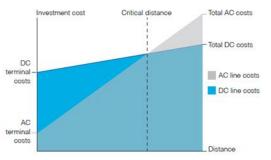

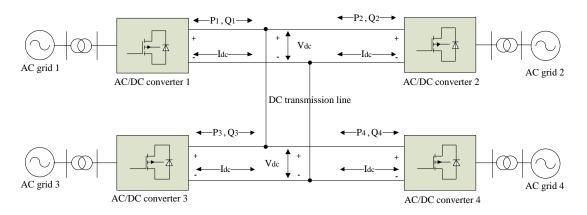

Since the energy consumption is increasing worldwide, the interconnections in different areas or between countries is necessary to bring down the cost. The unique feature of the HVDC transmission system is that it can connect two grids with different fundamental frequencies, and it can provide high immunity to the disturbances generated at one end as the other end is independent. This feature provides a robust system configuration for the multi-terminal connection, which promotes the development of the HVDC transmission projects in Europe [19][20]. In Figure 2, it shows the structure of a four-terminal HVDC transmission system. Because one of the most important factors when considering employ a HVDC transmission system is the distance between the sending end and the receiving end, therefore the HVDC transmission lines are preferred in large continents [21]. However, one of the barriers of realizing the HVDC transmission system is lack of effective fault-tolerant control method, compared to the commonly used half-bridge MMC, the full-bridge MMC based HVDC transmission system can block the DC fault but as the cost of increased investment for semiconductors and power losses [22]. The bi-directional current flowing design for the full-bridge structured MMC can block the DC fault current by adding appropriate control. Therefore, the popular converters employed in the HVDC transmission systems are investigated and the advantages and disadvantages are listed for guidance when selecting the appropriate converter.

Figure 2: The four-terminal configuration of the HVDC transmission system.

However, the development of the high/ultra-high voltage application never stopped with regard to the large power consumptions at present. M. Candas summarised the ultra-high voltage projects around the world in [160]. By increasing the transmitting voltage to over 800kv, the transmission losses through the long distance can be reduced significantly, which is very attractive when the power consumption center is highly concentrated in a small area and far from the power plants. Therefore, the State Grid Corporation of China (SGCC), the world's largest grid operator, has announced the plan to build 17 UHV transmission lines by 2017 and 27 UHV transmission lines to be constructed by 2020 [161]. Because of the ultra-high voltage ratings of these projects, it enables these transmission lines to transmit power though very long distance with minimal losses. The completed and planned UHV transmission lines in China are shown in Table 2. The power capacity for these transmission lines ranges from 5GW to 12GW. The extreme large power capacity of the transmission lines determined that even a small percentage of efficiency improvement could result in a large amount of power saving. In other words, problems such as computing stress or capacitor voltage deviations with respect to the control approaches could have greater impact on the performance of the UHV transmission lines compared to lower voltage applications.

| Name                                 | Туре  | Volt-<br>age<br>(KV) | Length (km) | Power<br>rating<br>(GW) | Year Com-<br>pleted/to be com-<br>pleted |

|--------------------------------------|-------|----------------------|-------------|-------------------------|------------------------------------------|

| Jindongnan–Nanyang–Jingmen           | UHVAC | 1000                 | 640         | 5                       | 2009                                     |

| Huainan–Zhejiang North–Shang-<br>hai | UHVAC | 1000                 | 2×649       | 8                       | 2013                                     |

| Zhejiang North - Fuzhou              | UHVAC | 1000                 | 2×603       | 6.8                     | 2014                                     |

| Xilingol League - Shandong           | UHVAC | 1000                 | 2×730       | 9                       | 2016                                     |

| Yunnan - Guangdong                   | UHVDC | ±800                 | 1373        | 5                       | 2009                                     |

| Xiangjiaba–Shanghai                  | UHVDC | ±800                 | 1907        | 6.4                     | 2010                                     |

| Jinping – Sunan                      | UHVDC | ±800                 | 2059        | 7.2                     | 2012                                     |

| Nuozadu - Guangdong                  | UHVDC | ±800                 | 1413        | 5                       | 2013                                     |

| Hami – Zhengzhou                     | UHVDC | ±800                 | 2192        | 8                       | 2014                                     |

| Xiluodu - Zhejiang West              | UHVDC | ±800                 | 1653        | 8                       | 2014                                     |

| Lingzhou - Shaoxing                  | UHVDC | ±800                 | 1720        | 8                       | 2016                                     |

| Shanxi North–Jiangsu                 | UHVDC | ±800                 | 1119        | 8                       | 2017                                     |

| Jiuquan–Hunan                        | UHVDC | ±800                 | 2383        | 8                       | 2017                                     |

| Xilingol League–Jiangsu              | UHVDC | ±800                 | 1620        | 10                      | 2017                                     |

| Shanghaimiao–Shandong                | UHVDC | ±800                 | 1238        | 10                      | 2017                                     |

| Zhundong–Wannan                      | UHVDC | ±1100                | 3400        | 12                      | 2018                                     |

Table 2: The completed/planned UHV transmission lines in China.

#### 1.2.1.Two-level or three-level VSC structure

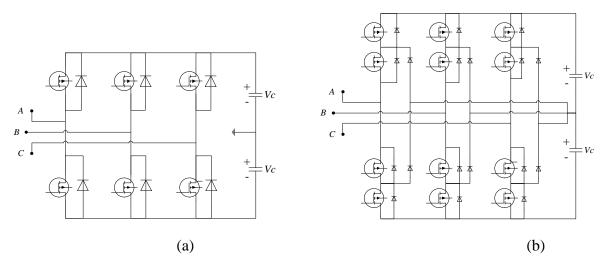

Because the simple structure and moderate controllability of the two-level and three-level converter, it was commonly used in industrial applications when it first came out in the early 1990s [23], hence it was first employed for HVDC transmission systems in the early stage of the development of the HVDC transmission lines. The two-level and three-level VSC structures were ideal converters for high-voltage applications when the first commercial HVDC transmission line was carried out in 1999 by ABB [24]. Since then, ABB has been developing the design and the structure of the HVDC transmission lines. In the following decades, the completed or incomplete HVDC transmission lines are using the two-level or three-level VSC stricter without exception until 2010 when the first MMC based HVDC transmission lines came out for commercial purpose, the Trans Bay project [11]. However, because of the restraints of the DC circuit breakers in high voltage applications, the development of the HVDC transmission lines has been slow until 2012 when ABB has developed the world's first HVDC DC circuit breaker [7]. The topologies of the two-level and three-level converters are shown in Figure 3. There are two DC link capacitors in both the two-level and three-level converters.

The converter output for the two-level converter shown can be either  $+V_{dc}$  or  $-V_{dc}$ , whereas the converter voltage output of the three-level converter includes the 0 states during normal operations. However, it can be observed that the structure of the three-level converter is more sophisticated than the two-level converter, and more components are required for the threelevel converter. Because of the large harmonics on the AC side of the converter, based on the two-level and three-level VSC, the multilevel converters were developed, such as diodeclamped converter [25] or flying capacitor converter [26]. However, compared to the MMC, the aforementioned multilevel converter suffers problems such as multiple dc supplies required and the increased control difficulties when the converter voltage levels are higher than five. In contrast, the voltage level of the MMC can easily increase to over 200 by inserting submodule without adding any dc supplies and the only difference of the control method between the low voltage level MMC and high voltage level MMC is the number of the carrier signals required in the PWM scheme.

Figure 3: The topology of the conventional (a) two-level converter (b) the three-level converter.

#### 1.2.2.Modular multilevel converter

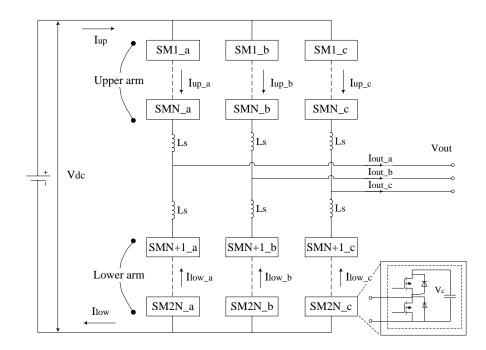

Nevertheless, when referring to the HVDC transmission system, the MMC based transmission line seems to be the only option for the long distance, low losses power transmission. Considering the highly modular submodules, low switching frequency, and low harmonic, MMC could still be one of the promising candidates for UHV transmission lines. The Trans Bay project has set a great example of implementing the MMC based transmission lines by stacking the modular submodules. Furthermore, one of the advantages of the MMC based transmission lines is the much lower harmonic and switching frequency due to the series-connected submodules. However, due to the physical limitations of the power switch and capacitor, the number of submodules could be large when implementing the UHV applications, thus increasing the initial investment for the construction of the substation. Because of the desirable features of the MMC in high voltage applications, the MMC based HVDC transmission systems are considered as one of the most attractive candidates for long distance power transmission. With the rapid development of the power electronic devices, the MMC based HVDC transmission line is one of the most attractive topologies for a distance transmission system. A typical three-phase MMC has been shown in Figure 4.

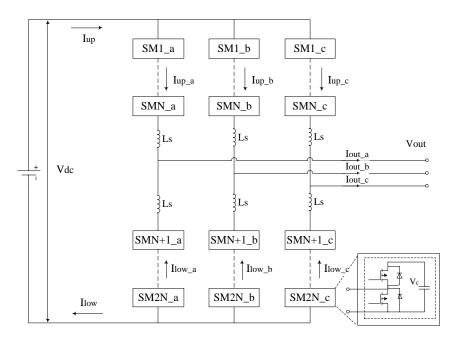

Figure 4: The typical structure of a three-phase MMC.

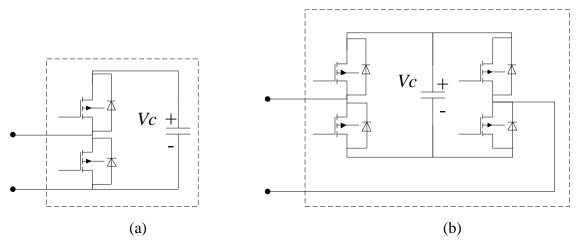

The modular structure of this converter determines that there are many submodules connected in series in both upper and lower arm. Each arm consists of several identical submodules in order to generate the desired output. The number of the submodule in upper and lower arm are the same. Depending on the structures of the submodules, the implementation of the MMC can have two different topologies as shown in Figure 5.

Figure 5: The submodule structure of the (a) half-bridge MMC (b) full-bridge MMC.

No matter how many power switches and capacitors are contained within one submodule, as demonstrated in Figure 5, all the submodules in both upper arm and lower arm are connected in series to integrate the converter output. This type of multilevel structure provides higher flexibility and lower control difficulty than conventional two-level or three-level VSC. The performance of the MMC based systems are improved in the following aspects:

## a. Lower switching frequency

Because of the series connections in each arm, the converter output voltage is generated by adding and reducing the number of connected submodules in MMC. Therefore, the switching frequency is dependent on the modulation method in the control approach. In the two-level and three-level converter, the Pulse Width Modulation (PWM) is used to generate control signals for the switches [8]. That can cause the frequent switching on and off actions to achieve low harmonic converter output. Nevertheless, in MMC, when the number of submodules is high, the commonly used modulation method is Nearest Level Modulation (NLM), which turns on and off the submodules according to the reference signals by rounding up to the nearest voltage level [27]. Because of the smaller voltage steps of the MMC than the two-level or three-level converter, the NLM approach not only lowers the switching frequency but also maintains the low converter output harmonics. However, the voltage balancing controls are required for the capacitors within all the submodules since they can have voltage deviations if left unattended. In [28], the impact of the control approach on switching frequencies is discussed, and it is shown that the switching frequency of each submodule can be operated less than 150Hz.

#### b. Low harmonic converter output

Because of the flexible structure of MMC itself, the number of submodules used in each arm does not compromise the control simplicity. With other types of multilevel converters,

10

such as the diode-clamp multilevel converter or flying capacitor converter, the control patterns can increase exponentially when the number of converter voltage levels is high [29][30]. To extend the benefits brought by increasing the number of submodules, such as the low converter output harmonics, low insulation requirements, etc. The number of submodules for each arm can be as many as 200 or even more. In this case, the converter output is approaching a sinusoidal waveform as increasing the number of submodules, leads to much fewer harmonics than the two or three voltage levels converters. Based on the simulation results, the minimum number of voltage level required to meet the grid code for a 6KV application is 40. However, the number can vary depending on the control approach applied. As a result of the lower AC side harmonics, the size of the AC side filter is reduced, or it is not necessary when the number of submodules is sufficient in each arm [31]-[33].

#### c. Low component requirement

The voltage distributed on each submodule is smaller than the two-level or three-level converter depending on how many submodules in one arm, which leads to the smaller voltage steps when turning on the submodules. In this case, the voltage differences at the two terminals of the power switches are also small hence reducing the stresses of the power switches in the submodules when the voltage level is high but also generates less electrical magnetic interferences due to the low switching frequency [34][35].

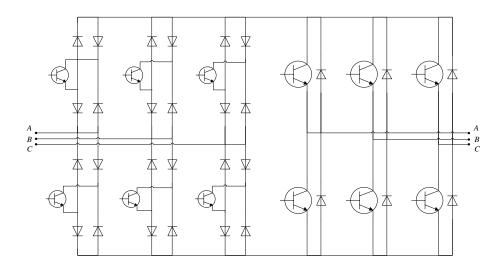

#### 1.2.3. Other potential converters

Depending on the application of the HVDC transmission lines, there are other types of converters that have the potential to be implemented in the HVDC transmission system. In Figure 6, the topology of a multilevel matrix converter is shown. There are many bi-directional power switches connected in each arm to achieve the AC-AC energy conversion. However, in the matrix converter, the power storage components, such as capacitors, are not necessary as stated in [36]-[38]. Because of the rapid development of the power switches, the cost and efficiency are both improved through the past a few years. These converters which are using a large number of power switches are becoming more and more competitive in high voltage applications. Despite the available converters for HVDC applications, the half-bridge structure MMC is widely accepted for its control simplicity and the fewer number of components used than the rest converters.

11

Figure 6: The topology of the matrix converter in a back-to-back application.

#### 1.3 Research background of the MMC

Because the power consumption is increasing over the past decades. It is critical to find a solution to the high losses and low efficiency of the traditional three-phase transmission system. In this case, the HVDC transmission system is the ideal choice for the distant and offshore power transmission. In this chapter, the construction costs for both AC transmission system and DC transmission system is analysed and the idea of critical distance is introduced to demonstrate the point where DC transmission line is more cost efficient than the AC transmission line. In addition, the commonly used types of converters are investigated in this chapter. The modular multilevel has shown a mature structure than the latest matrix converter and it also shows the higher flexibility and better performance than the traditional two-level or three-level converter used in HVDC transmission system. Therefore, the MMC based HVDC transmission system is the one of the most appropriate candidates for distant and low losses transmission system

#### 1.3.1.Mathematical representations of MMC

The mathematical representation of the MMC can precisely describe the behaviour of the MMC during the normal operation. However, the modelling methods of the MMC are different depending on which aspects of converter behaviour are of interest. Fundamentally, the models provide the voltage and current pattern of the converter according to the control approach. Some models are focusing on the switching losses and heat generation for converter efficiency assessment. Song and Liu created a mathematical model in [39] to describe the circuit interactions of the electrical quantities in the MMC. By simplifying to a simple key equation, this mathematical model focuses on the steady states of the MMC. The high-frequency

current components are extracted from the arm currents for voltage balancing control as suggested in [40] by Deng and Chen. However, the PWM method is limited to the Phase-Shifted PWM (PS-PWM) which can significantly increase the computation requirements when the number of submodules is large. To simplify the computation processes, the arm submodules are replaced by the equivalent controllable voltage sources in [41]. Inner voltages are introduced to represent the voltage changes across the submodules. This approach is preferred in the MMC control design when there are a large number of submodules in each arm. The lack of descriptions of the switching actions in this approach makes this modelling method inaccurate when the converter efficiency is of consideration. On the other hand, to describe the detailed model, the sensor delays are considered to control the current within the MMC arms [42]. Disturbances and harmonic compensation control can be injected into the reference signals to achieve the control of the positive, negative, and zero-phase-sequence converter currents control [43].

One of the problems when building the simulation model is that when the number of the submodules in each arm is increased, the computation requirement is also increased. Therefore, accurate and efficient modelling methods for multilevel level converters are required. An average-value-model of the 401-voltage level MMC based HVDC transmission system is given in [31]. The arm submodules are replaced by the controllable current sources to reduce the computation requirement as well as evaluating the converter performance. The Thévenin's equivalent equations for the converter part were given in [35] based on the predefined equations provided by manufacture. It does not require the exact equivalent model of the entire circuit. Therefore, the computation requirement is relatively low in this model. The comparisons among the leading approaches in modeling the MMC has been demonstrated in [44], an improved model is also presented to further improve the computational efficiency regarding the electromagnetic transient simulations. As stated in [44], while both average model and detailed equivalent model can offer great accuracy regarding the electrical-magnetic analysis, the detailed equivalent model is more accurate than the average in the same conditions and both of them are more accurate than the traditional detailed model. However, the electricalmagnetic interferences are not investigated in the simulation model. The MMC simulation model was designed and tested in MATLAB to validate the proposed control approaches.

#### 1.3.2. Control signal modulation method

The modulation methods for MMC are similar to the traditional modulation methods except that the number of the PWM carriers is more than that for two-level or three-level converters. When the number of submodules is large, the modulation complexity and the computation requirements of the control approach are greatly increased. The Space-Vector PWM (SV-PWM) was initially used to test the MMC [45]. Depending on the number of the submodules, the number of the switching states can be massive when the converter has more submodules than traditional two-level or three-level VSC based systems. The Phase-Shifted PWM (PS-PWM) and Phase-Disposition PWM (PD-PWM) are then employed to simplify the modulation processes. Their effectiveness is validated by both simulation and experimental results. The closed control loops are connected to the submodules to control the capacitor voltages [46]. This approach skips the capacitor voltage sorting, but at the cost of adding more control blocks. The capacitor voltage balancing approach based on the PD-PWM was suggested in [47][48]. However, the voltage sorting process and the monitoring of the arm currents and capacitor voltages are always the barriers of improving the MMC control approaches. In [40], the equations for the high-frequency current components in the arm currents were derived when the PS-PWM is used for modulation. The advantage of this approach is the measuring of the arm current is not necessary to control the capacitor voltages. On the other hand, it has the same problems regarding the computational stress as the conventional voltage balancing approaches when there are a large number of submodules in each arm., The Nearest Level Modulation (NLM) is proposed in [27] to cope with the increased voltage levels taking into account that the PWM effects are not significant as when the converter voltage level is low. The submodule numbers are determined by integrating the closest voltage according to the reference signals. However, the approximation of the NLM can generate many converter voltage harmonics when the number of submodules is insufficient. In [49], the switching states are simplified at the implementation stage of the NLM to shorten the necessary computation period. The comparisons between the Space Vector Pulse Width Modulation (SVPWM) and the NLM are presented in [53]. It has proven that the SVPWM can be equivalent to the NLM approach by selecting the appropriate redundant switching sequence. However, it is easier to modify the SVPWM switching pattern than the NLM to provide more flexibility to the system.

The converter output voltage harmonics exist no matter which PWM scheme is selected. Especially when the converter voltage level is low, the converter harmonics can be significant

14

depending on the number of the submodules. The Selective Harmonics Elimination (SHE) approach is proposed in [50][51] to minimize the converter output harmonics. However, the look-up table can be sophisticated even with only a low number of submodules connected. In [52], the converter output is increased from N+1 to 2N+1 by interleaving the carriers, which involves shifting the carriers by 180°. The interleaving technology can increase the voltage levels as well as reduce the converter output harmonics without adding more submodules. However, this modulation potentially increases the imbalanced voltage distributions on the arm inductors, hence increasing the power rating of the affected components.

#### 1.3.3.Selection of the arm inductor and submodule capacitor

The one of the major costs of the MMC based system is the cost for the submodules. Because of the modular structure of the MMC, each submodule contains the same number of switches and capacitors. The selection of the capacitor affects both the size and the cost of the converter [55] since the performance of the converter is determined by the capacity of the selected capacitors. Depending on the system requirements, the capacitance selections are focusing on these two factors: the capacitor voltage ripple and the maximum energy stored in the capacitors. The capacitor voltage ripple should be low to reduce the converter output harmonics, and on the other hand, it should be capable of transmitting the rated power from side to side. Besides that, the capacitors are selected considering the maximum capacitor voltage, voltage ripple, current ripple, and the submodule voltage capability of the converter [54]. Hence four equations are derived to suggest the upper and lower margins of the submodule capacitances. On the other hand, the capacitance can be determined based on the voltage ripple generated by the switching actions [9]. The maximum power storage in the submodules is another key factor should be taken into account. In order to illustrate the relationships between the converter rated power and the maximum power transmitted, the energy-power ratio was introduced in [56] to guide the selection of capacitor. The ratio between the power stored in the submodules and the power transferred through the MMC from 10 to 50 produces the best performance. On the other hand, because of the existence of the arm inductors, the resonances are investigated to determine the capacitance and inductance in [57]. The second and fourth harmonics of the arm currents are investigated, and the capacitance and inductance are selected in order to avoid the low-frequency resonances. Because of the low order harmonics generated by the series-connected capacitors and the inductors, the elimination of the resonant current existing in the arm currents can be another determining factor in the arm inductor selection. In [58], it presented the principles of selecting the arm inductances based on the equations for the circulating current at switching frequency when the circulating current suppression control is activated. The resonance current generated by the submodule capacitor and arm inductors are investigated in [56], the system parameters of the other nineteen different projects are presented to illustrate the resonance currents existing at the second and fourth harmonics. However, the arm inductors are also in charge of limiting the fault current whenever there are system failures. The equations for the arm inductance were derived in [59] based on the variation speed of the fault current which is related to the power switches. To further improve the selection of the arm inductance, the fault current limiting effect of the arm inductor and an Active Front-End (AFE) mode of the MMC were suggested in [57] to minimize the use of the passive components, hence reducing the size of the submodule capacitors and the arm inductors. However, in the AFE mode, the arm inductance was compensated by the AC side filter which may lead to the size increasing of the AC filter.

#### 1.3.4. The external control loop

The conventional VSC control loops are well developed, and it can be implemented in the MMC based HVDC transmission systems with little modifications. The AC side dynamics of the MMC based system was deduced in [60], theoretically approved the exterior control design of the traditional two-level VSC can be applied to the AC side of the MMC. Therefore, the active and reactive power decoupling control loops used for two-level VSC are eligible control methods for MMC. The output on the AC side of the MMC is integrated by turning on the submodules one by one according to the reference signals [61]. A large number of the submodules can provide high flexibility when there are one or more submodules failures. In [62], the redundant submodules are inserted into the arms to reduce the switching frequency and the capacitor voltage ripple, and the AC side voltage dynamics are also derived. The control of the AC side of the MMC can be achieved by decoupling the capacitor voltages with 10% redundancy submodules to simplify the switching processes and improve the computational efficiency [63]. As the extension of the MMC-based HVDC transmission lines, the direct power control can be applied to the MMC to enable the bi-directional power flowing through passive networks [64]. Besides the conventional outer VSC power control loop, the circulating currents are considered as the third variable to improve the performance of the MMC in the proposed control technology [65].

#### 1.3.5. The internal control loop

The internal control approach of the MMC is different from the traditional two-level or three-level VSC because of the series-connected submodules. Since the capacitors in the submodules can have voltage differences even with voltage balancing controls, they can cause circulating currents to flow in the arms. Therefore, the capacitor voltage balancing and the circulating current suppression are primary control loops for the internal control of the MMC.

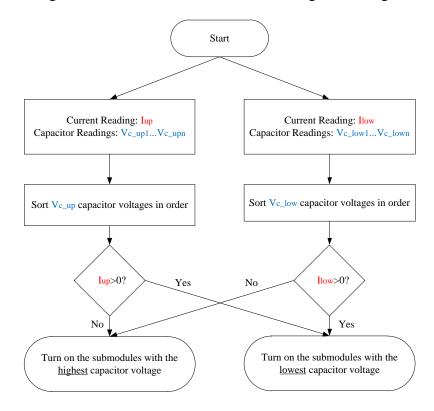

Depending on the measurement of the arm currents, the voltage balancing control is developed on a different basis. One of the approaches is to measure the arm currents of both upper and lower arms, and determine the turn-on and turn-off states of each submodule depending on the arm current directions. In [47], the arm currents are measured to predict the charging and discharging states of the affected submodules to improve the switching patterns. A double-fundamental frequency disturbance is injected into the reference signals to minimize the converter output harmonics. On the other hand, because the capacitor voltages are transferred to the control unit and processed according to the arm current directions, they can have a great impact on the switching frequency of each submodule, hence affecting the converter performance [67]. Therefore, the switching frequency can be reduced by inserting the submodule on and off states as the third variable [68]. This method can be implemented in arm current measurement based voltage balancing control to minimize the switching frequency [69][70]. In [71], the discrete mathematical model is derived, and the cost functions are pre-defined to balance the capacitor voltage. Due to its computational difficulty and the measuring redundancy, the following approaches are proposed to simplify the control process. In conventional voltage balancing control approach, the arm currents are always measured to ensure the balanced voltage distribution among the capacitors. However, it is possible to skip the arm current measuring process by improving the voltage balancing methods, such as the following voltage balancing methods. The DC voltage distribution can be controlled by adding control loops to every submodule, the capacitor voltage variations are restricted within the certain range by the control loops [46]. Because the extra control loops are required for every submodule, the implementation costs can be significant when there are many submodules. The equations for the high-frequency components of the arm currents based on the switching actions were derived in [40] to balance the capacitor voltages. The submodule voltages are controlled according to the power variations caused by the high-frequency current components. The capacitor voltages can be controlled by the energy balancing control from the power transmitting aspect as derived in [72][73]. The differential currents of the positive, negative, and zero sequences at

fundamental and twice-fundamental frequencies can be decoupled to regulate the energy distribution in both upper and lower arms [72]. The DC voltage and the AC side output currents can be measured to estimate the energy distribution among the submodules in the converter to fit different load conditions [73].

The circulating current is one of the side effects caused by the imbalanced DC voltage distributions. Because there are submodules connected in series, the imbalanced DC voltage distributions can generate currents flowing from upper arm to lower arm or from one phase to another phase. It can increase the RMS current ratings of the affected components and increase the switching losses. In [74], it describes the generation of the circulating current based on the instantaneous power flowing and suggests that the circulating current is proportional to the capacitor voltage differences. Therefore, it can be suppressed by decoupling the differential current to generate the corresponding control signals to compensate the capacitor voltage difference. The circulating current model of the MMC was proposed in [75] and it proved that the upper and lower arm controls are independent of each other and hence the communications between these two controls are not required. The paper also showed that the circulating current consists of the Direct current and the phase-to-phase average currents. However, the circulating current suppression methods can be different based on the different arm current decoupling methods. In [76]-[79], the circulating current suppression is focused on eliminating the alternating current by regulating the Direct current components in the circulating current. In [76], repetitive controllers are inserted into the suppression controller to improve the converter immunity to current harmonics and increase the efficiency of the controller. The alternating current components of the circulating current can be decoupled and the corresponding controllers can be designed to reduce the even order harmonics by tuning at the even order frequencies [77][78]. In [79], it improves the circulating currents suppression control under unbalanced grid conditions and further guaranteed the feasibility of this approach in different circumstances. In [80], it proposes the direct circulating current suppression method incorporating the half-delayed operation cycle to suppress the even order harmonics existing in the circulating currents, the results demonstrated the fast responses regarding system dynamics. In [81], it develops the quasi-proportional controller focusing on eliminating the second-order harmonics existing in the circulating currents, which combines the benefits of the AC circulating current suppression and the circulating current decoupling methods. In addition to the approaches of regulating the circulating current to the DC components, the circulating current was decoupled to extract the elements of the circulating current at the specific frequency [82][83]. In [82], it has derived the steady state model of the MMC to describe the circulating

current and the performance of the converter affected by inserting the submodule according to the sinusoidal reference signals. The resonant frequency in the steady state model indicated that the circulating current contains a large component of the AC currents at the twice fundamental frequency. In [83], the circulating current suppression method was designed based on the rotating frame of the arm currents at the fundamental frequency. The suppressing signals are generated and applied to the upper and lower arm separately because the controls of the upper and lower arm are independent of each other as described in [75]. In [84], it applies the proposed approach in [83] to a 71-level MMC model, and further investigated the performance of the system with the aforementioned approach.

#### 1.3.6. The converter efficiency and performance under fault conditions

A large number of submodules results in the lower switching frequency than the traditional two-level or three-level converters. However, due to the voltage balancing and the circulating current controls, the switching states of each submodule are difficult to track when the system is in operation. In [85], it derives the equations representing the on-state losses for the MMC based on different system capacities. The temperature coefficients of the power switches are presented using curve fitting to calculate the losses. The mathematical analysis of the MMC regarding both conduction losses and the switching losses is presented in [86], and the results are compared to the MATLAB equivalent model. The results are promising in regard to the conduction losses but not the switching losses. The loss calculation is linked to the junction temperature of the switch directly thus affecting the overall system designs. To precisely describe the losses in different frequency ranges, the accurate system model was derived based on the approximate calculation tools provided by the manufacturers [87]. The duty ratio of each submodule is considered and the switching temperature is estimated according to the theoretical maximum switching frequency.

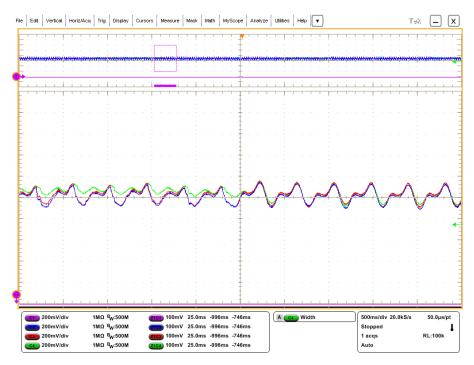

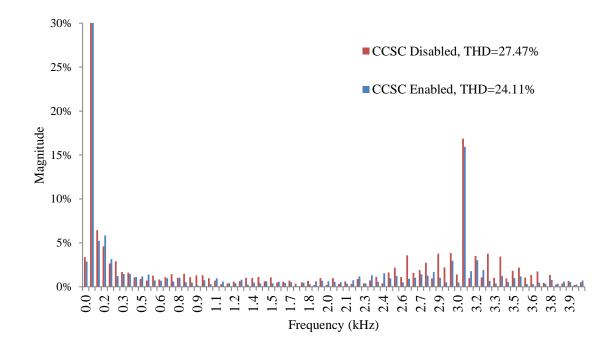

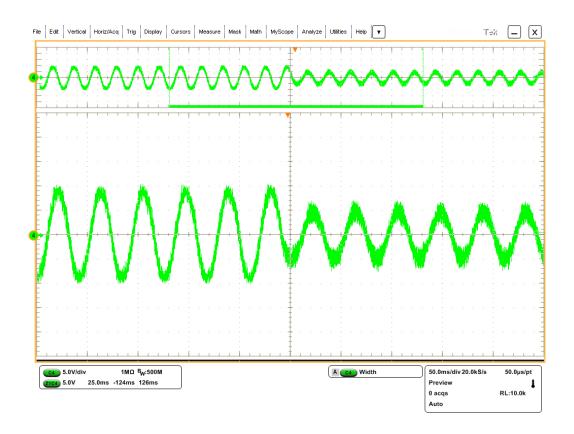

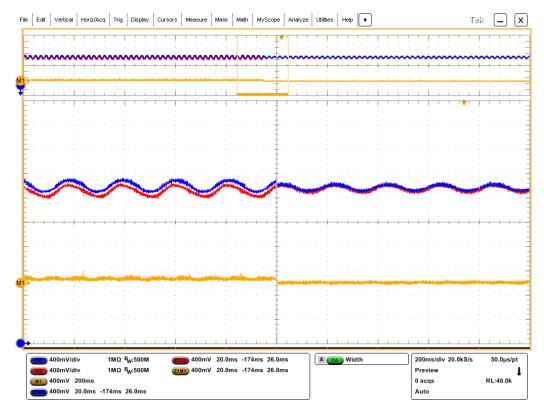

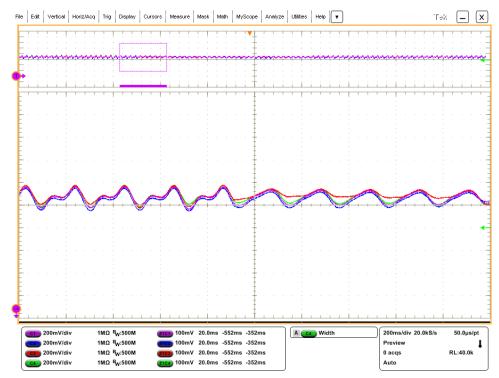

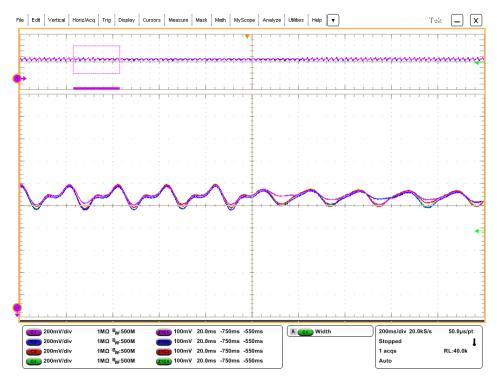

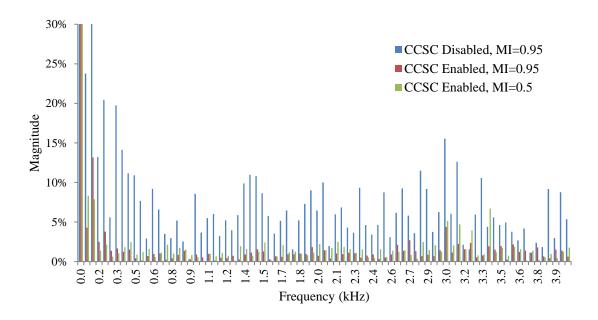

Because of the unfavourable conditions of using the average DC circuit breakers in the HVDC transmission systems [88]-[90], ABB managed to develop the first applicable HVDC DC circuit breaker in 2012. In [91], the line-to-line and line-to-ground faults are investigated and the transient electromagnetic transient of characteristics of the MMC was analysed. The simulation results indicated that the MMC-based HVDC systems have better controllability than the conventional VSC-HVDC systems. The fault-tolerant operation with redundant submodules was proposed in [92] when the failures are detected inside the submodules. The proposed method was carried out based on the PSCAD model and proven to maintain a constant power transfer when the number of faulty submodule exceeds the total number of redundant