# Current Fed Multilevel Converters for High Current Power Applications

Bakri Hassan

A thesis submitted for the degree of Doctor of Philosophy April, 2016

School of Electrical, Electronic and Computer Engineering

> Newcastle University United Kingdom

### Abstract

The majority of the worldwide installed power inverters today are voltage source inverters followed by current source inverters where the concluding decision lies with the performance of the applications besides the usual economic reasons. Recent active development in the current source inverter areas has seen the emerging of various generalized multilevel current source inverter topologies analogous to the existing multilevel voltage source inverter families. To date, the multilevel current source inverter families have been classified principally by the physical appearance of their basic structures and also by the number of current sources employed. The existing multilevel current source inverter topologies are unpopular for present applications due to reasons such as big sizes, high control complexity and low reliability; which circumstances are often associated to massive component counts and multiple requirements of current sources. Therefore, this research has been focused on the single-phase single-source generalized multilevel current source inverter for this apparent advantage; where this thesis proposed a novel generalized multilevel current-source inverter topology with the lowest component utilization while employing just a single current source. In addition, the proposed topology can conveniently achieved dc current balance with a simple low frequency switching strategy for the five- and nine-level current outputs. From comparison analysis, the proposed topology has significantly less number of components employed compared to the nearest topology, which implies low implementation cost. The experimental results verify the characteristics and performances of the proposed topology acquired by computer simulations.

i

## **Dedication**

To my late father, my mother and my family

### Acknowledgement

First and foremost, my most sincere appreciation goes to my supervisor, Prof. Volker Pickert for his guidance, encouragement, and relentlessly giving support and ideas to make this research successful. I am also very grateful to Dr. Bashar Zahawi as the co-supervisor for many valuable lessons.

Many thanks are due to everyone involves in this project either directly or indirectly. My special credit to the ministry of education, Malaysia and also to my employer the University Malaysia Pahang (UMP) for the financial support; as without their funding this work would not have happened.

My greatest gratitude to my family; my wife and our children for their continuous and undivided supports and loves during our toughest period along the journey towards PhD. Special thanks also to my mother, brothers and sisters for their du'a and endless morale support.

Last but not least, thank you to friends and colleagues in EECE NU and FKEE UMP in particular, the staffs and students of UG Lab and SuPER Lab for being helpful and supportive.

Alhamdulillah.

## Table of Contents

| Abstra  | acti                                                     |

|---------|----------------------------------------------------------|

| Dedica  | ationii                                                  |

| Ackno   | wledgementiii                                            |

| Table   | of Contents iv                                           |

| List of | <sup>2</sup> Figuresix                                   |

| List of | Tables xiii                                              |

| List of | Abbreviations xiv                                        |

| CHAP    | TER 1 1                                                  |

| An Ov   | verview of Multilevel Inverters1                         |

| 1.1     | Introduction 1                                           |

| 1.2     | Objectives and possible contributions to knowledge       |

| 1.3     | Thesis structure                                         |

| 1.4     | Publication work 10                                      |

| СНАР    | TER 2 11                                                 |

| Multil  | evel Converter: Topologies and Operations11              |

| 2.1     | Introduction                                             |

| 2.2     | Harmonic Minimization in MCSI                            |

| 2.3     | Harmonics                                                |

| 2.4     | Classification of converters for high-power applications |

| 2.5  | Multile  | vel Voltage Source Inverter                           | . 20 |

|------|----------|-------------------------------------------------------|------|

|      | 2.5.1    | Diode-Clamped Inverter                                | . 21 |

|      | 2.5.2    | Capacitor-Clamped Inverter                            | . 23 |

|      | 2.5.3    | Cascaded Multi-Cell Inverter                          | . 26 |

| 2.6  | Classic  | al Current Source Inverter                            | . 27 |

|      | 2.6.1    | Load-commutated inverter (LCI)                        | . 27 |

|      | 2.6.2    | PWM-CSI inverter                                      | . 29 |

| 2.7  | Introdu  | ction to MCSI                                         | . 30 |

|      | 2.7.1    | MCSI Topology: Principles of Design                   | . 31 |

|      | 2.7.2    | Duality Transformation                                | . 32 |

|      | 2.7.3    | Current-Multilevel (CML) Cells                        | . 33 |

| 2.8  | General  | lized MCSI Structures                                 | . 36 |

|      | 2.8.1    | Topology I (Antunes et al, 1999)                      | . 36 |

|      | 2.8.2    | Topology II (Bao et al, 2006)                         | . 43 |

|      | 2.8.3    | Topology III (Xiong et al, 2004)                      | . 47 |

|      | 2.8.4    | Topology IV (Suroso et al, 2010)                      | . 51 |

| 2.9  | Topolo   | gy Comparisons                                        | . 55 |

| 3.0  | Summa    | ury                                                   | . 60 |

| CHA  | PTER 3   |                                                       | . 62 |

| Curr | ent-Sour | ce Inverter Control for High- and Low-Load Conditions | . 62 |

| 3.1  | MCSI (   | Control Strategy                                      | . 63 |

|      | 3.1.1    | Fundamental frequency Switching Strategy              | . 63 |

|      | 3.1.2    | PWM Control Strategy                                  | . 65 |

| 3.2  | Propose  | ed MCSI Control Strategy                              | . 67 |

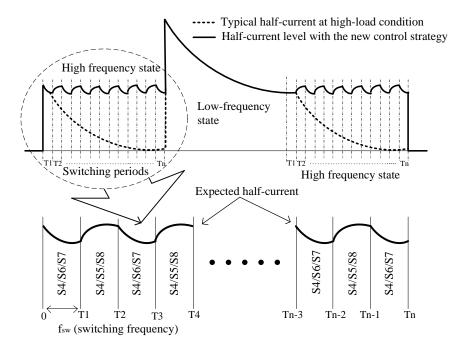

| 3.3  | Simulat  | tion Results                                          | . 72 |

|      |          |                                                       |      |

| 3.4  |          | toty investigation                                    | . 77 |

| CHAI                                                   | PTER 4                                                                         |                                                |                          |

|--------------------------------------------------------|--------------------------------------------------------------------------------|------------------------------------------------|--------------------------|

| Novel                                                  | Multile                                                                        | evel Current Source Inverter Topology          |                          |

| 4.1                                                    | Novel                                                                          | Generalized MCSI Topology                      |                          |

| 4.2                                                    | Operati                                                                        | ion of MCSI                                    |                          |

|                                                        | 4.2.1                                                                          | Five-Level MCSI                                |                          |

|                                                        | 4.2.2                                                                          | Nine-Level MCSI                                |                          |

| 4.3                                                    | Compu                                                                          | iter Simulations                               |                          |

|                                                        | 4.3.1                                                                          | Harmonic Minimization                          |                          |

|                                                        | 4.3.2                                                                          | Novel five-level CSI                           |                          |

|                                                        | 4.3.3                                                                          | Novel nine-level CSI                           |                          |

|                                                        | 4.3.4                                                                          | Total harmonic distortion                      |                          |

| 4.4                                                    | Perform                                                                        | nance comparison                               |                          |

| 4.5                                                    | Summa                                                                          | ary                                            |                          |

|                                                        |                                                                                |                                                |                          |

| CHAI                                                   | PTER 5                                                                         |                                                |                          |

|                                                        |                                                                                | Arrangements, Results and Discussions          |                          |

|                                                        | rimental                                                                       |                                                | 107                      |

| Exper                                                  | r <b>imental</b><br>Genera                                                     | Arrangements, Results and Discussions          | <b>107</b><br>108        |

| <b>Expe</b><br>5.1                                     | rimental<br>Genera<br>IGBT c                                                   | l <b>Arrangements, Results and Discussions</b> | 107<br>108<br>110        |

| <b>Exper</b><br>5.1<br>5.2                             | rimental<br>Genera<br>IGBT o<br>CSI po                                         | l <b>Arrangements, Results and Discussions</b> | 107<br>108<br>110<br>111 |

| Exper<br>5.1<br>5.2<br>5.3                             | rimental<br>Genera<br>IGBT c<br>CSI po<br>Contro                               | Arrangements, Results and Discussions          |                          |

| Exper<br>5.1<br>5.2<br>5.3<br>5.4                      | rimental<br>Genera<br>IGBT o<br>CSI po<br>Contro<br>Design                     | Arrangements, Results and Discussions          |                          |

| Exper<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5               | rimental<br>Genera<br>IGBT o<br>CSI po<br>Contro<br>Design<br>Experin          | Arrangements, Results and Discussions          |                          |

| Exper<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7 | rimental<br>Genera<br>IGBT o<br>CSI po<br>Contro<br>Design<br>Experin<br>Summa | Arrangements, Results and Discussions          |                          |

| 6.1                                                                                        | Conclusion                                                                                    | 123                                                                                                   |

|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| 6.2                                                                                        | Contributions to knowledge                                                                    | 123                                                                                                   |

|                                                                                            | 6.2.1 Other contributions:                                                                    | 124                                                                                                   |

| 6.3                                                                                        | Further works                                                                                 | 125                                                                                                   |

| Appe                                                                                       | ndix A                                                                                        | 126                                                                                                   |

| Simul                                                                                      | ink Model                                                                                     | 126                                                                                                   |

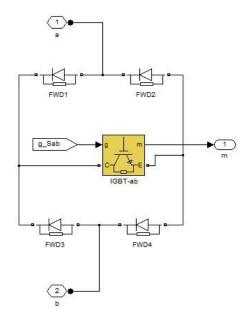

| A.1 IO                                                                                     | GBT Block                                                                                     | 126                                                                                                   |

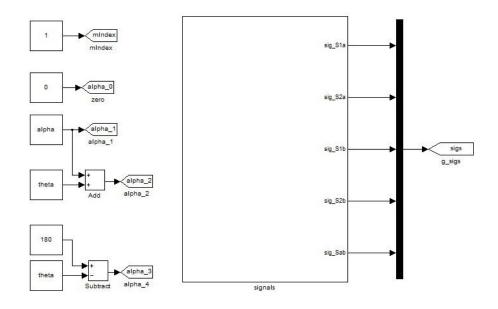

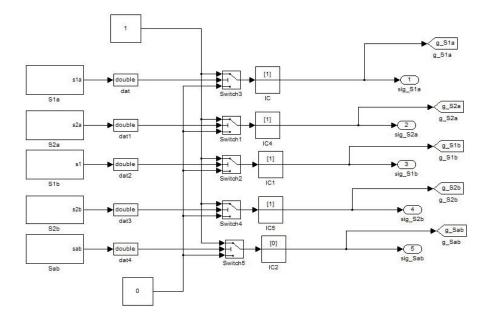

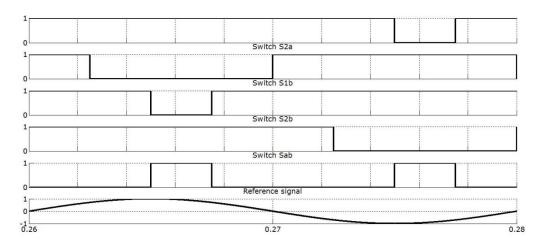

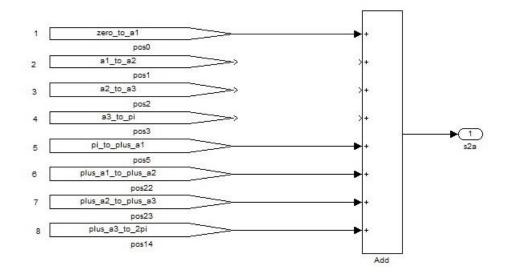

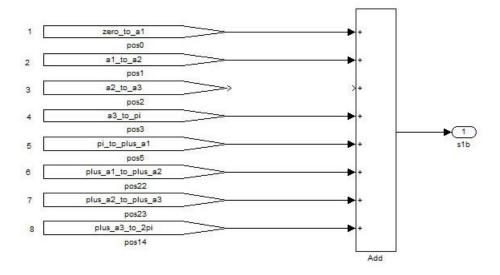

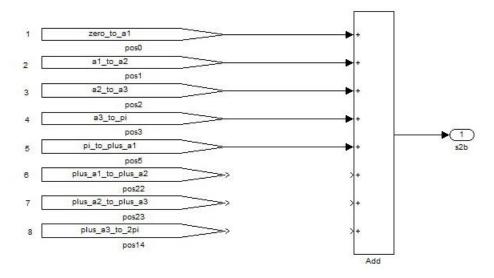

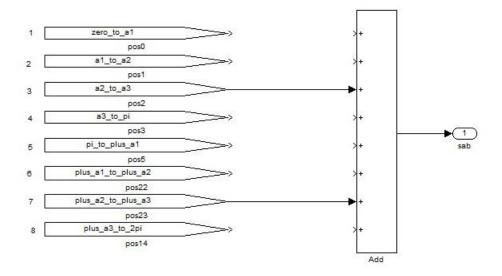

| A.2 G                                                                                      | ate Signal Block                                                                              | 128                                                                                                   |

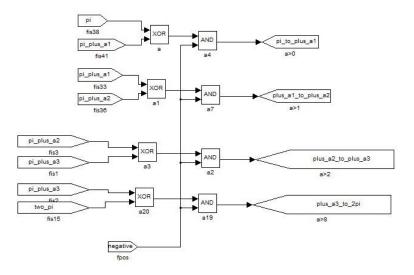

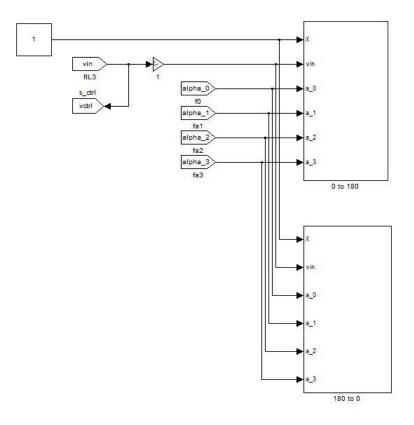

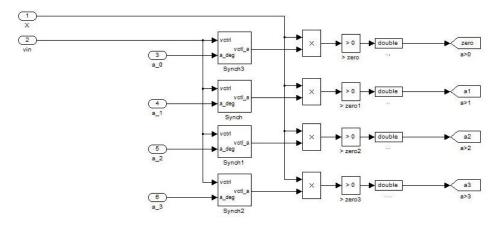

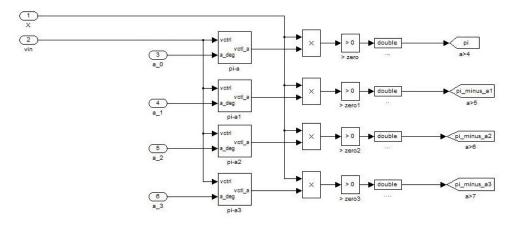

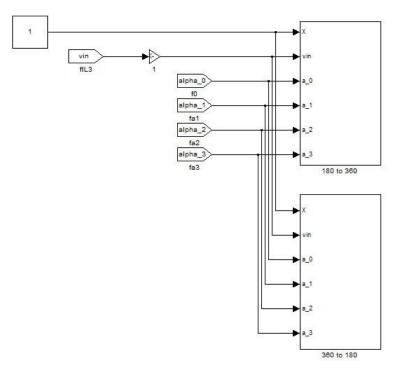

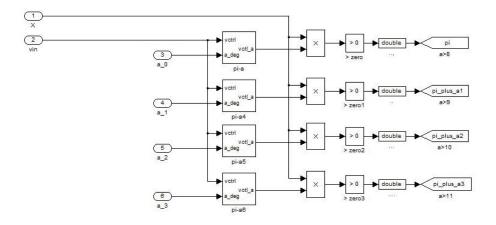

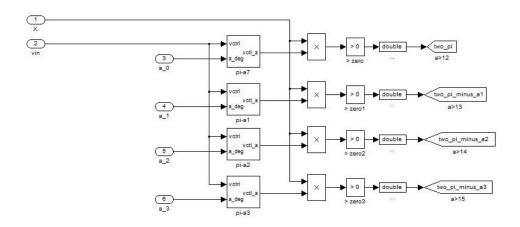

|                                                                                            | A.2.1 Control Signals Development                                                             | 130                                                                                                   |

|                                                                                            | A.2.2 Variable Switching Angles (Positive Cycle)                                              | 131                                                                                                   |

|                                                                                            | A.2.3 Variable Switching Angles (Negative Cycle)                                              | 133                                                                                                   |

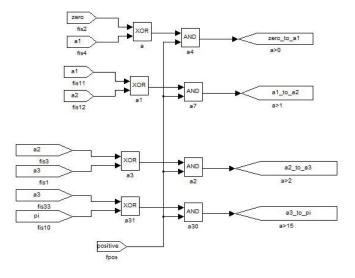

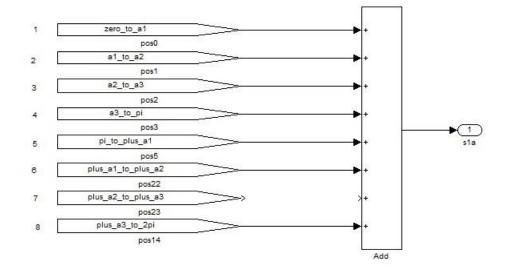

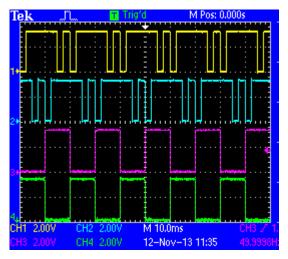

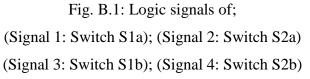

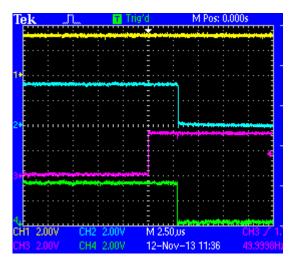

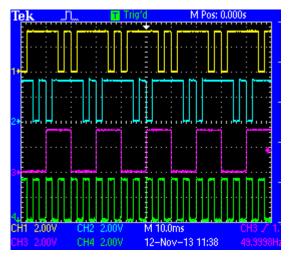

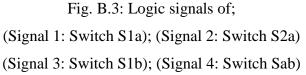

| A.3 L                                                                                      | ogic signals                                                                                  | 134                                                                                                   |

|                                                                                            |                                                                                               |                                                                                                       |

| Appe                                                                                       | ndix B                                                                                        | 138                                                                                                   |

|                                                                                            | ndix B                                                                                        |                                                                                                       |

| FPGA                                                                                       |                                                                                               | 138                                                                                                   |

| FPGA<br>B.1 V                                                                              | A Programming                                                                                 | <b>138</b><br>138                                                                                     |

| <b>FPG</b> <i>A</i><br>B.1 V<br>B.2 C                                                      | A <b>Programming</b><br>HDL Programming                                                       | <b>138</b><br>138<br>144                                                                              |

| FPGA<br>B.1 V<br>B.2 Ca<br>Appen                                                           | A Programming<br>HDL Programming                                                              | <ol> <li>138</li> <li>138</li> <li>144</li> <li>146</li> </ol>                                        |

| FPGA<br>B.1 V<br>B.2 C<br>Apper<br>Exper                                                   | A Programming<br>HDL Programming<br>aptured Signals<br>ndix C                                 | <ol> <li>138</li> <li>138</li> <li>144</li> <li>146</li> <li>146</li> </ol>                           |

| FPGA<br>B.1 V<br>B.2 C<br>Apper<br>Exper<br>C.1 In                                         | A Programming<br>HDL Programming<br>aptured Signals<br>ndix C<br>rimental Components          | <ul> <li>138</li> <li>138</li> <li>144</li> <li>146</li> <li>146</li> <li>146</li> </ul>              |

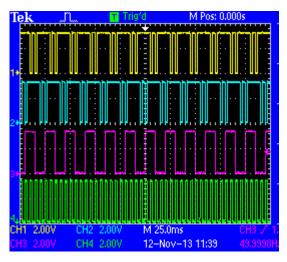

| <b>FPG</b> <i>A</i><br>B.1 V<br>B.2 C<br><b>Apper</b><br><b>Exper</b><br>C.1 In<br>C.2 G   | A Programming HDL Programming aptured Signals ndix C rimental Components everter Test Circuit | <ul> <li>138</li> <li>138</li> <li>144</li> <li>146</li> <li>146</li> <li>147</li> </ul>              |

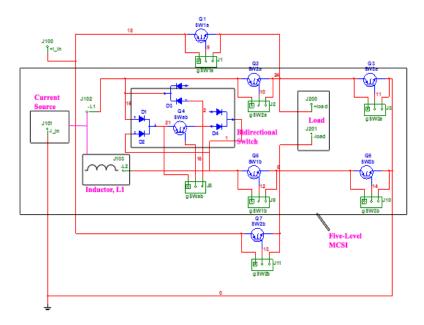

| <b>FPGA</b><br>B.1 V<br>B.2 C<br><b>Apper</b><br><b>Exper</b><br>C.1 In<br>C.2 G<br>C.3 IC | A Programming<br>HDL Programming                                                              | <ul> <li>138</li> <li>138</li> <li>144</li> <li>146</li> <li>146</li> <li>147</li> <li>150</li> </ul> |

| REFERENCES               | . 154 |

|--------------------------|-------|

| C.10 Current Probe       | . 153 |

| C.9 Digital Oscilloscope | . 153 |

| C.8 DC Power Supply      | . 152 |

| C.7 Main Power Supply    | . 152 |

| C.6 DC Contactor         | . 151 |

## List of Figures

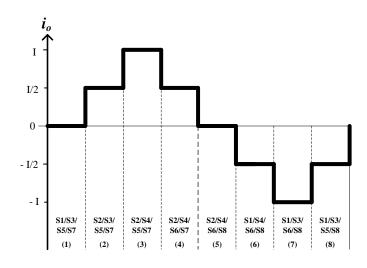

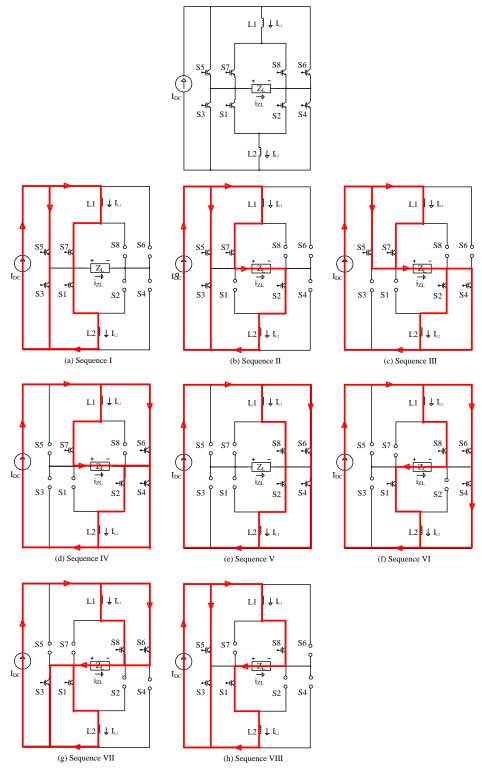

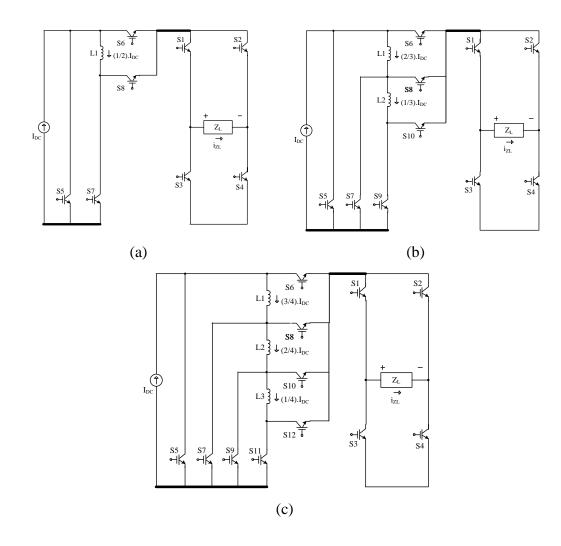

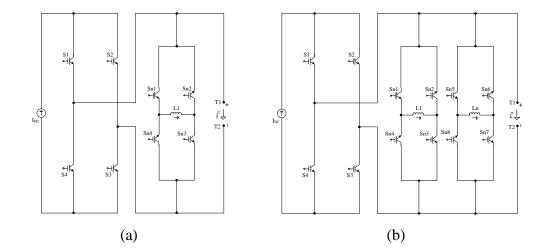

| Fig.2 - 26: Generalized structure of the topology III                                 |

|---------------------------------------------------------------------------------------|

| Fig.2 - 27: Topology III (a) 5-level inverter circuit (b) 7-level inverter circuit 40 |

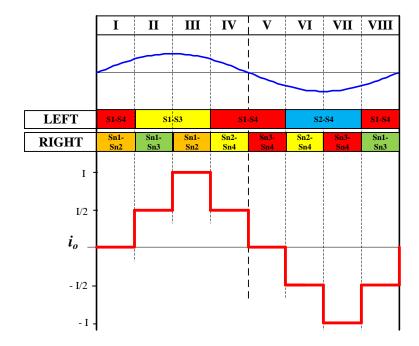

| Fig.2 - 28: Five-level switching sequence                                             |

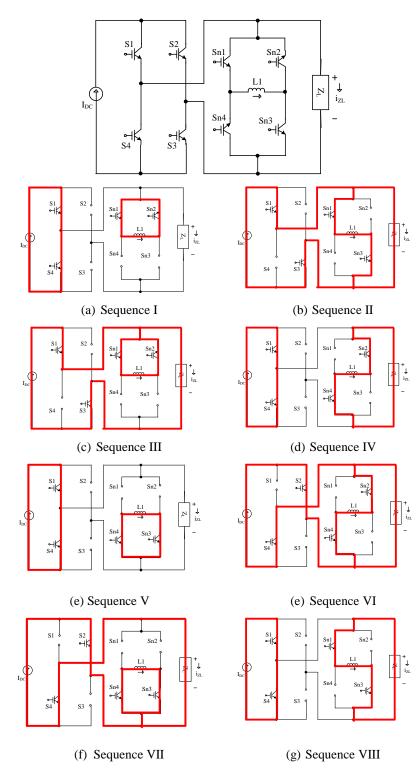

| Fig.2 - 29: Single-phase five-level inverter circuit and its corresponding switching  |

| sequences (a)-(h)                                                                     |

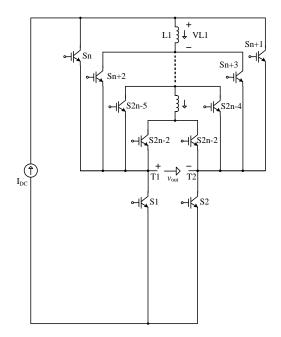

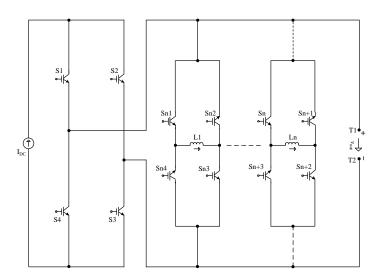

| Fig.2 - 30: The generalized structure of the Topology IV                              |

| Fig.2 - 31: Topology IV (a) 5-level inverter circuit (b) 9-level inverter circuit 52  |

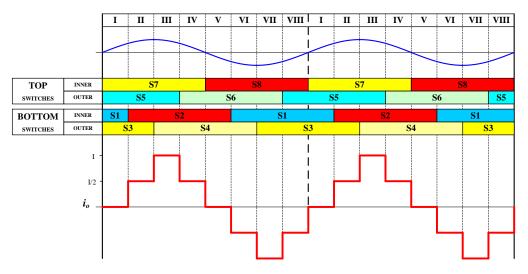

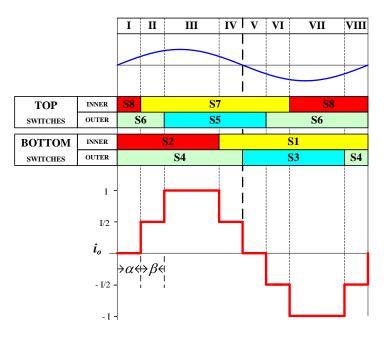

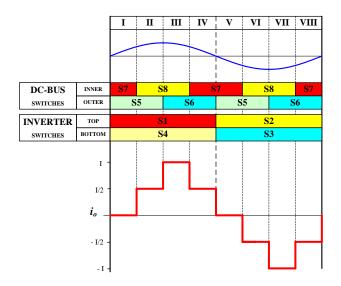

| Fig.2 - 32: Sequence                                                                  |

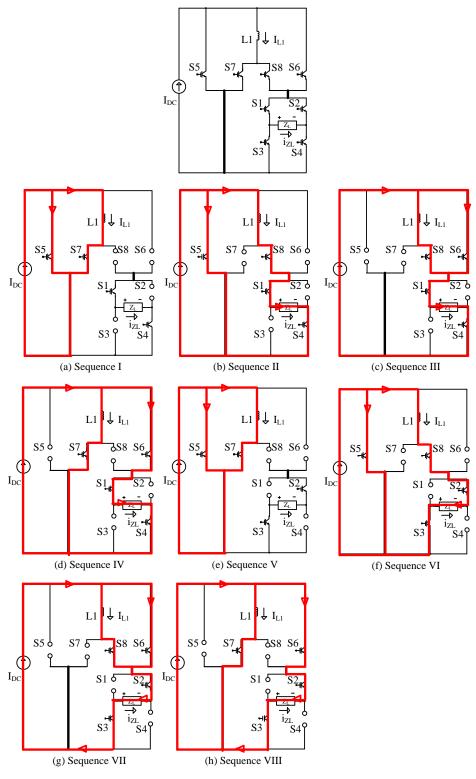

| Fig.2 - 33: Single-phase five-level inverter circuit and its corresponding switching  |

| sequences (a)-(h)                                                                     |

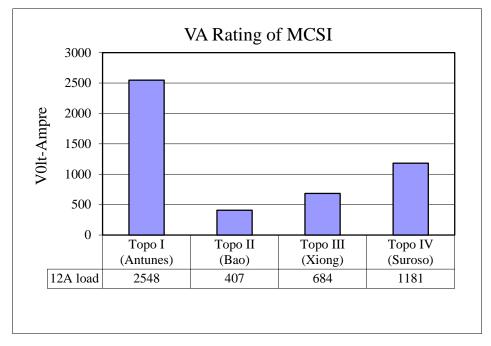

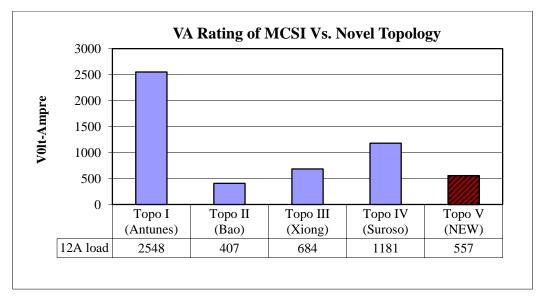

| Fig.2 - 34: Volt-Ampere (VA) comparison                                               |

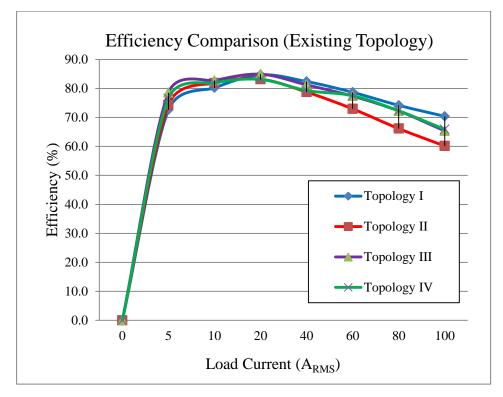

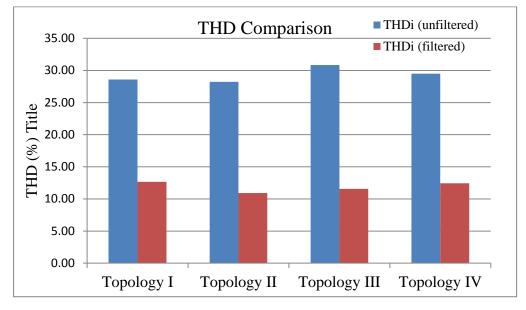

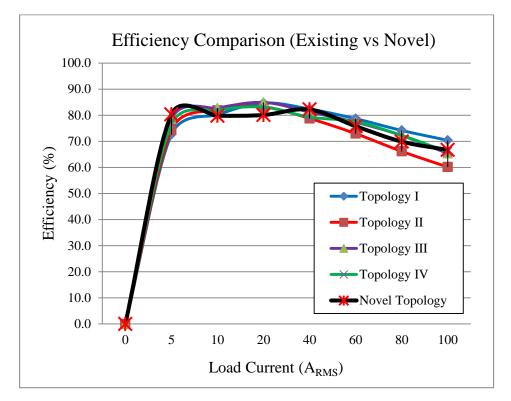

| Fig.2 - 35: Efficiency vs. Load Current                                               |

| Fig.2 - 36: THD and Distortion Factor                                                 |

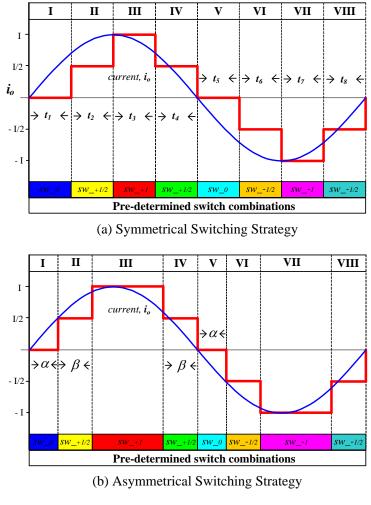

| Fig.3 - 1: Low frequency switching                                                    |

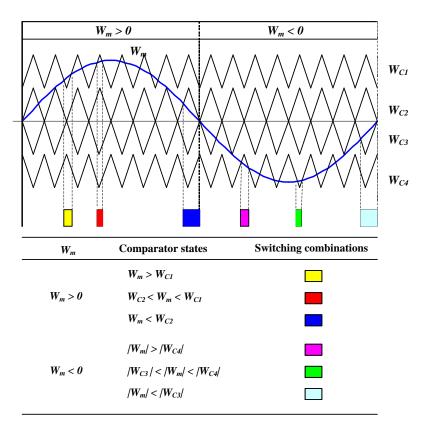

| Fig.3 - 2: POD-PWM control                                                            |

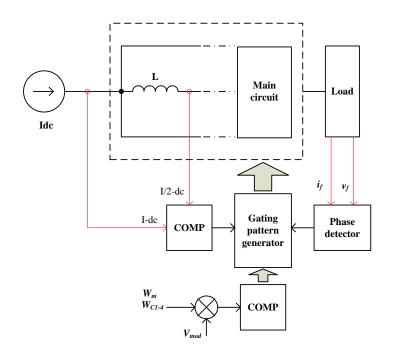

| Fig.3 - 3: Simplified overall control diagram                                         |

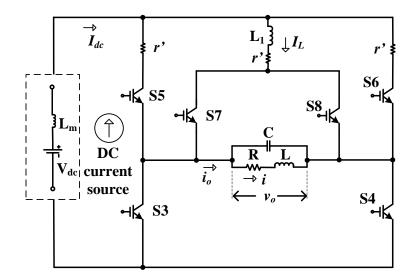

| Fig.3 - 4: Single-phase five-level CSI                                                |

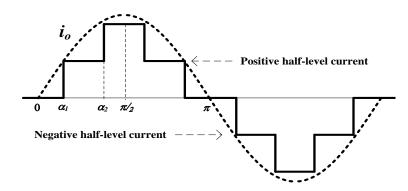

| Fig.3 - 5: Quarter wave symmetrical five-level output current                         |

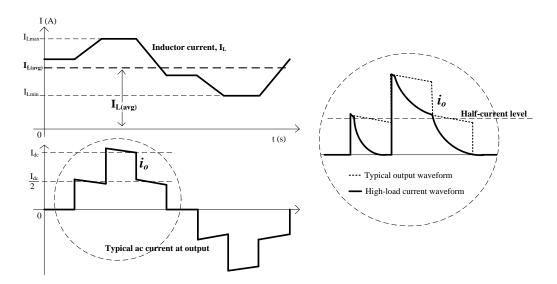

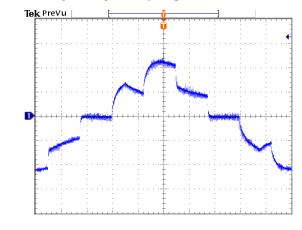

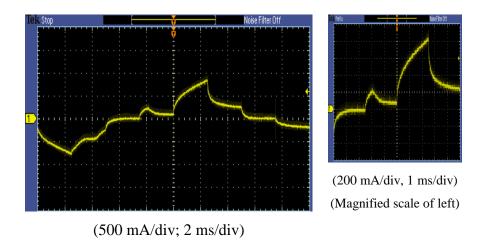

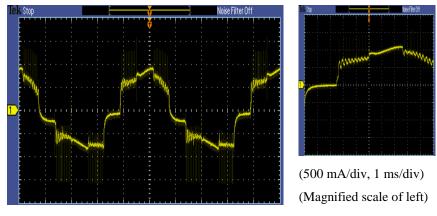

| Fig.3 -6: Typical average inductor current (top, left); the respective five-level     |

| output current waveform (bottom, left) and its comparison to the high-load current    |

| condition (as highlighted on the right)                                               |

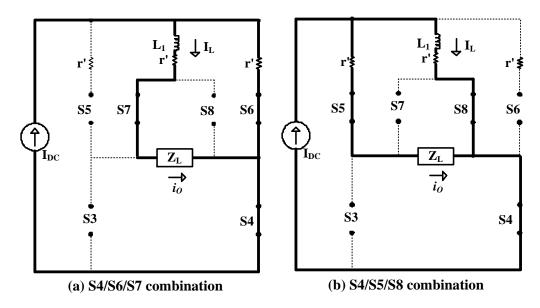

| Fig.3 - 7: Half-current redundant switching states                                    |

| Fig.3 - 8: Proposed RS-PWM control strategy                                           |

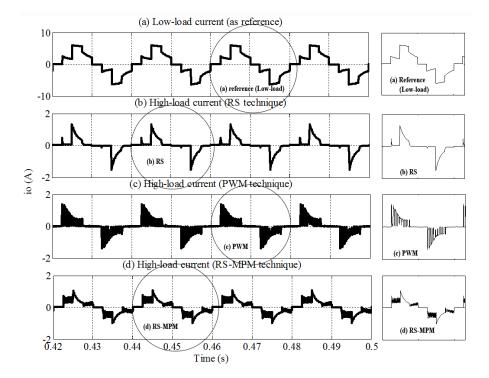

| Fig.3 - 9: Output current waveforms; high resistive load (from the top: ideal, RS,    |

| PWM and RS-PWM)73                                                                     |

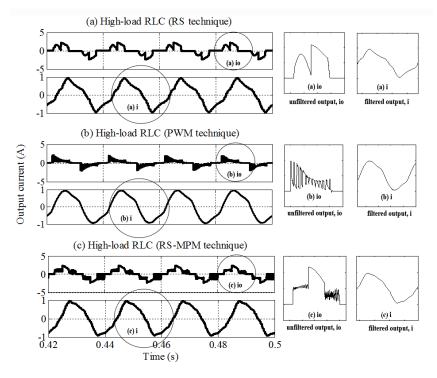

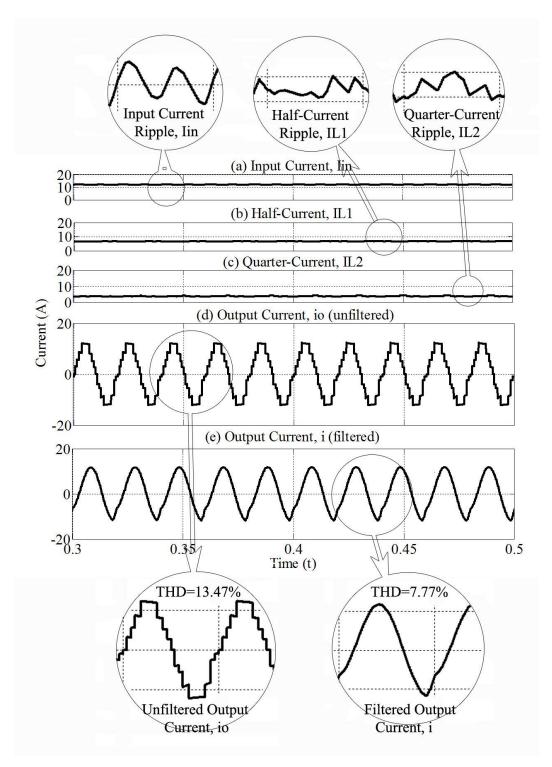

| Fig.3 - 10: Output current waveforms ( $i_0 \& i$ ); high RLC load74                  |

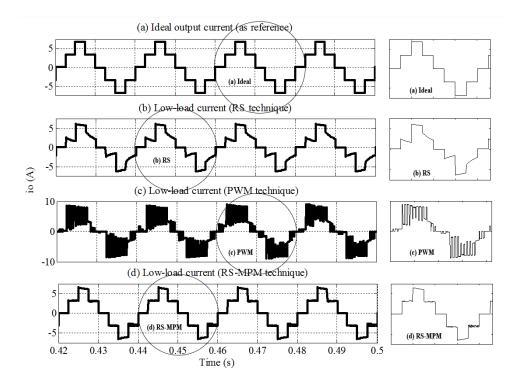

| Fig.3 - 11: Output current waveforms; light resistive load75                          |

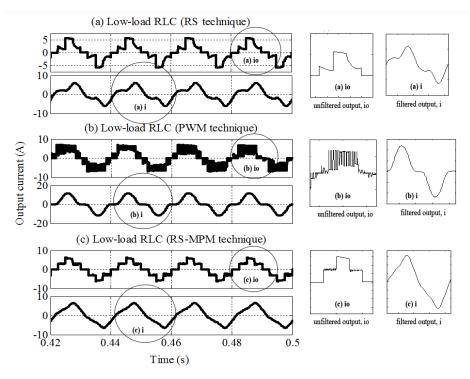

| Fig.3 - 12: Output current waveforms ( $i_0 \& i$ ); light RLC load                   |

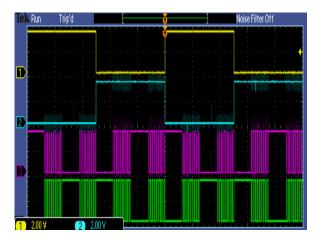

| Fig.3 - 13: FPGA gate signals of (top to bottom: S3, S4, S5, and S6)78                |

| Fig.3 - 14: Typical five-level output current at low-load (with RS technique)70       |

| Fig.3 - 15: Five-level output current at high-load condition (with RS technique) 79   |

|                                                                                       |

| Fig.3 - 16: Improved output current at high-load condition (with RS-PWM)71           |

|--------------------------------------------------------------------------------------|

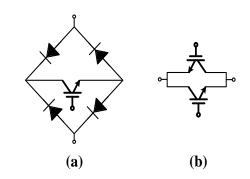

| Fig.4 - 1: (a) 1-IGBT with 4-diodes (b) 2-IGBTs in parallel                          |

| Fig.4 - 2: The proposed novel generalized topology                                   |

| Fig.4 - 3: (a) The novel 5-level CSI (b) The novel 9-level CSI                       |

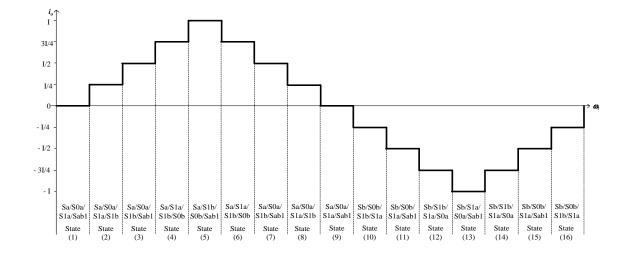

| Fig.4 - 4: Five-level CSI switching sequence                                         |

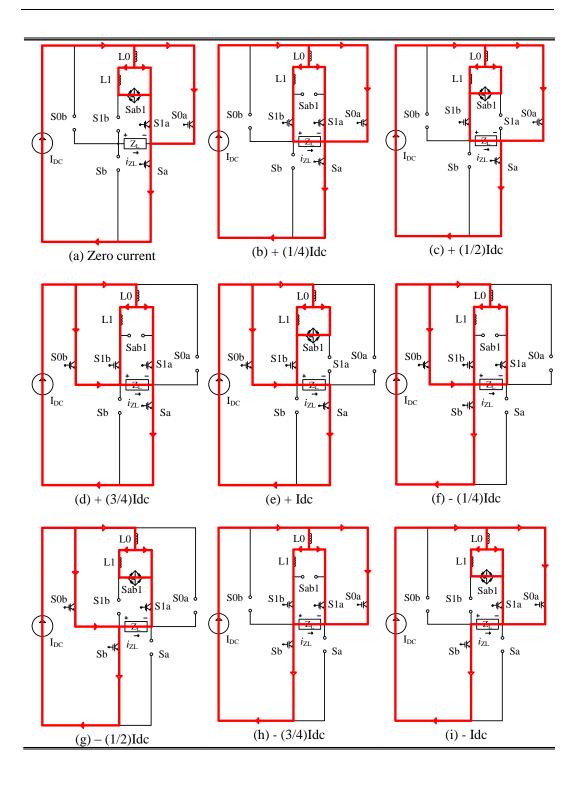

| Fig.4 - 5: Load current path of the five-level CSI                                   |

| Fig.4 - 6: Nine-level CSI switching sequence                                         |

| Fig.4 - 7: Load current path of the nine-level CSI                                   |

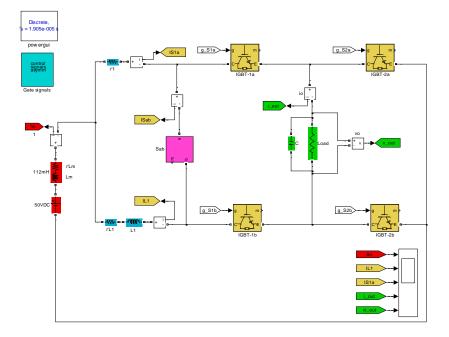

| Fig.4 - 8: Matlab/Simulink model of the novel five-level CSI                         |

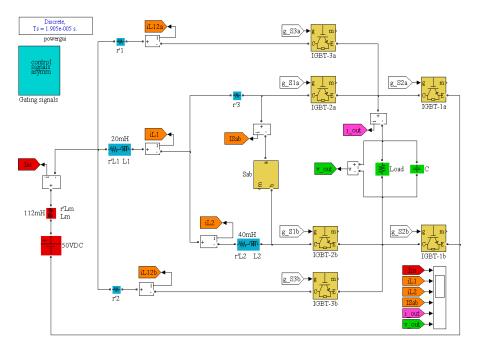

| Fig.4 - 9: Matlab/Simulink model of the novel nine-level CSI                         |

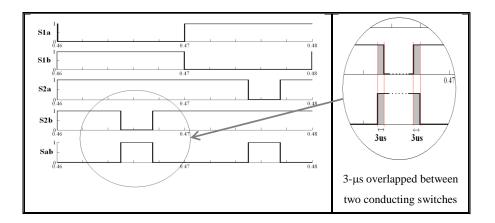

| Fig.4 - 10: Five-level CSI gate signals with overlapping periods highlighted93       |

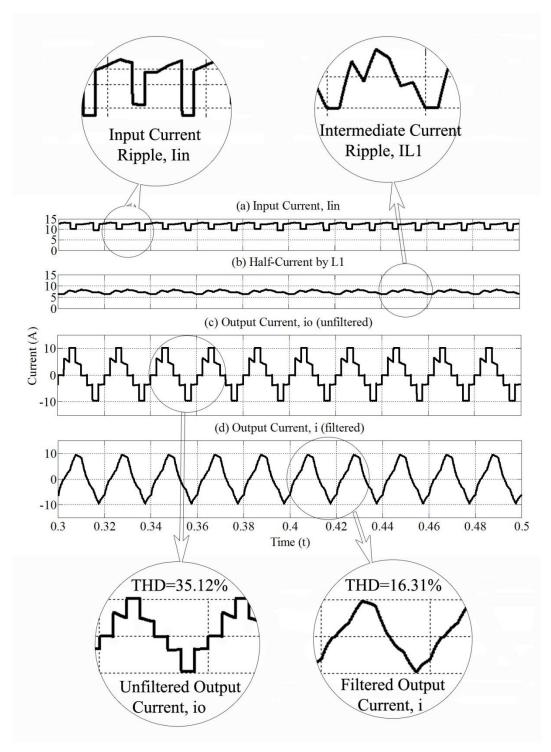

| Fig.4 - 11: Five-Level CSI with equal switching angles                               |

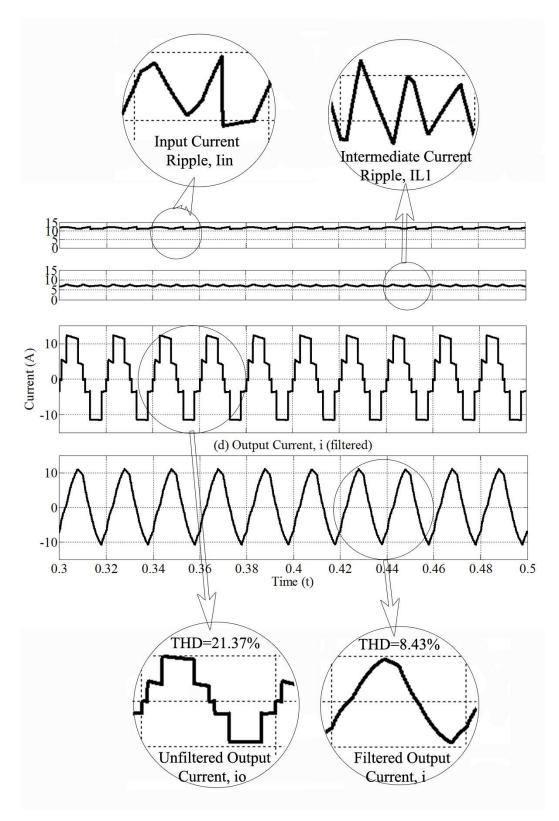

| Fig.4 - 12: Five-level CSI with selected switching angles                            |

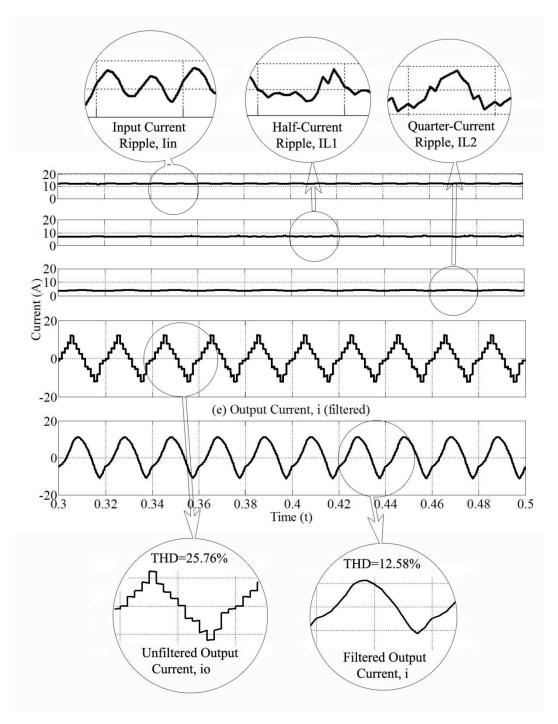

| Fig.4 - 13: Nine-level CSI with equal switching angles                               |

| Fig.4 - 14: Nine-level CSI with variable switching angles, $\theta$ (THD= 10.7 %) 92 |

| Fig.4 - 15: Current harmonic contents of the novel topology after filtering          |

| Fig.4 - 16: VA rating of novel topology                                              |

| Fig.4 - 17: Efficiency vs. Load current of novel topology                            |

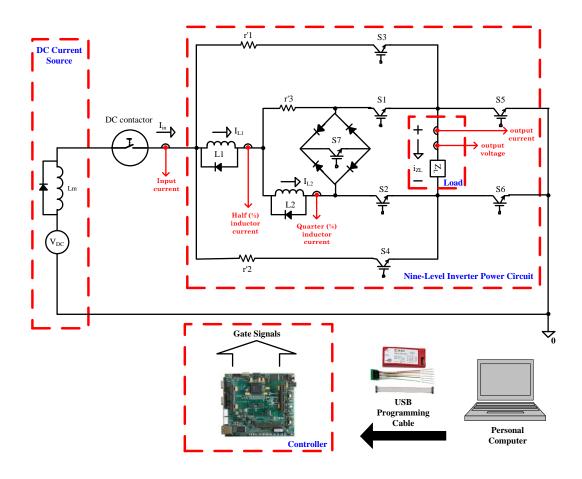

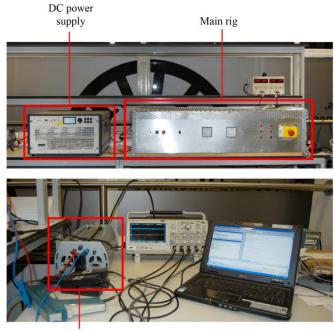

| Fig.5 - 1: General experimental layout 109                                           |

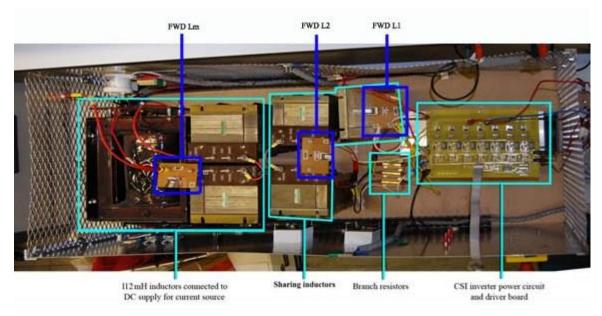

| Fig.5 - 2: Actual experimental test rig 109                                          |

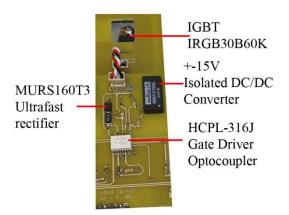

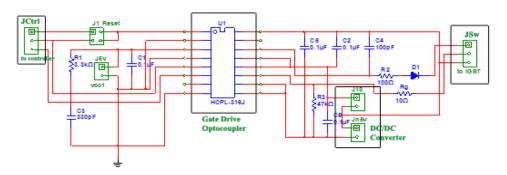

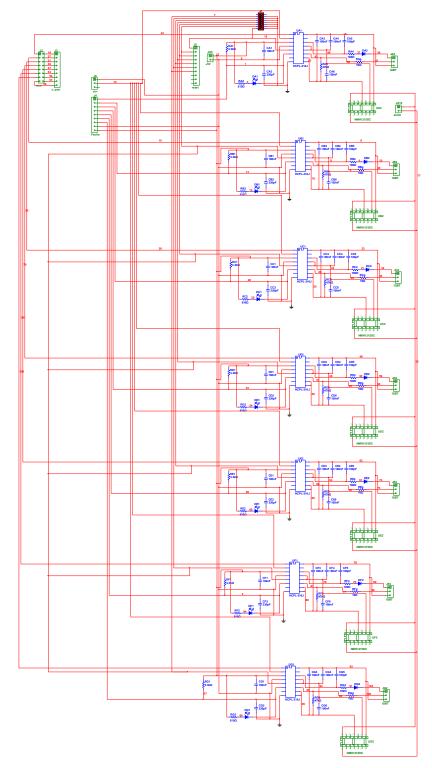

| Fig.5 - 3: IGBT driver circuit and the power circuit 110                             |

| Fig.5 - 4: Single 316J driver circuit and IGBT 100                                   |

| Fig.5 - 5: CSI power board                                                           |

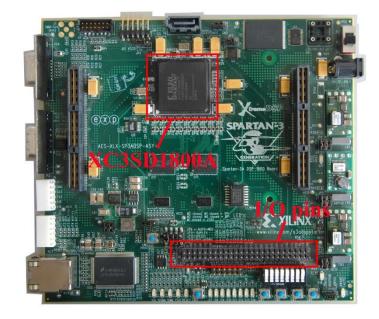

| Fig.5 - 6: Spartan 3-A DSP 1800A development board 102                               |

| Fig.5 - 7: Complete MCSI experimental arrangement set-up 103                         |

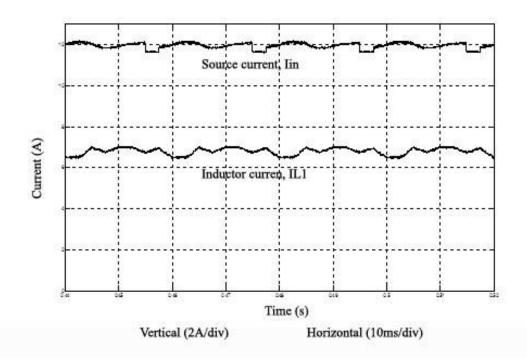

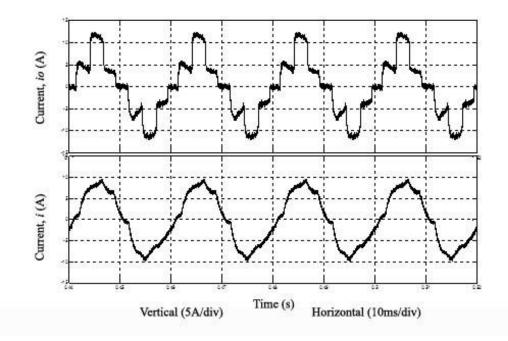

| Fig.5 - 8: The source current and inductor current waveforms 104                     |

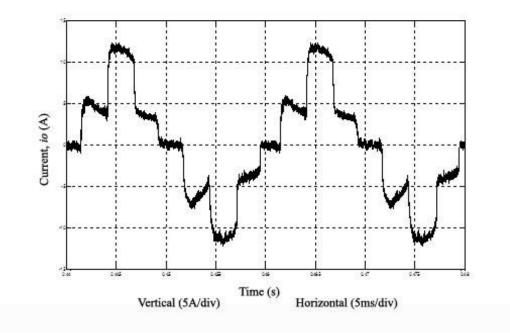

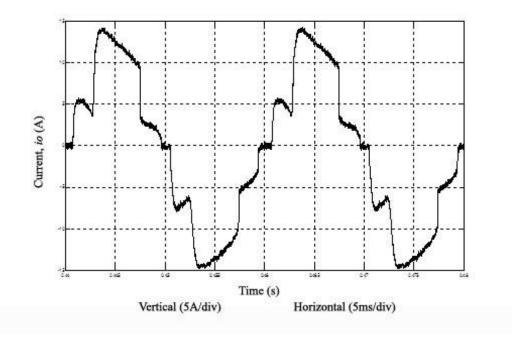

| Fig.5 - 9: The five-level output current waveform                                    |

| Fig.5 - 10: The output current before and after filtering 116                        |

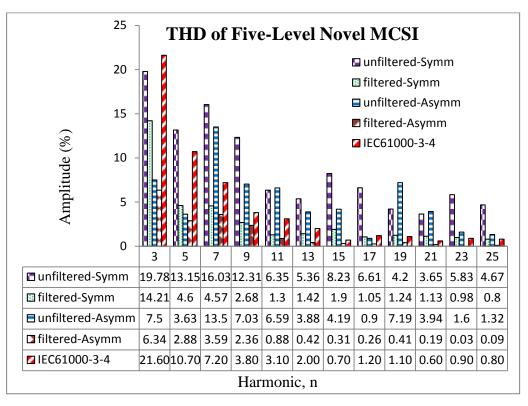

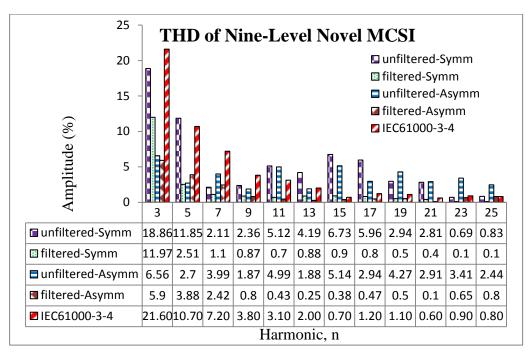

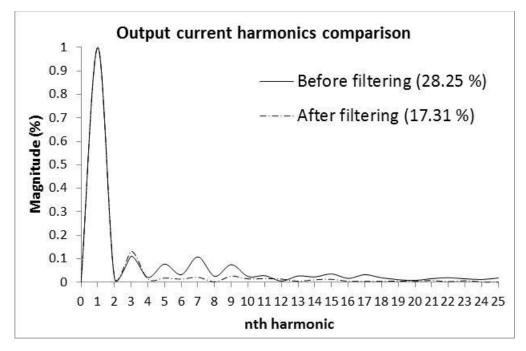

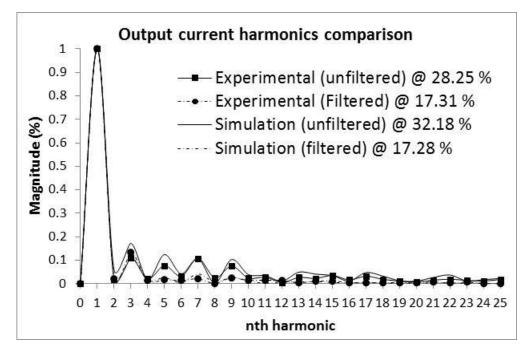

| Fig.5 - 11: Harmonics comparison before and after filtering 117                      |

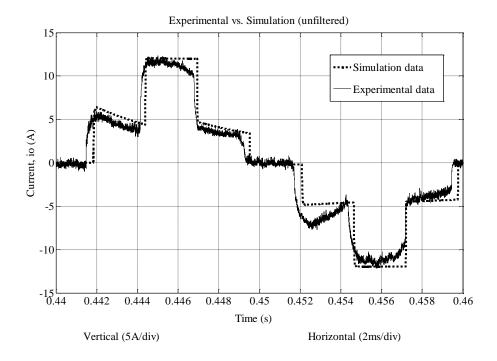

| Fig.5 - 12: Experimental vs. simulation (unfiltered waveforms) 118                   |

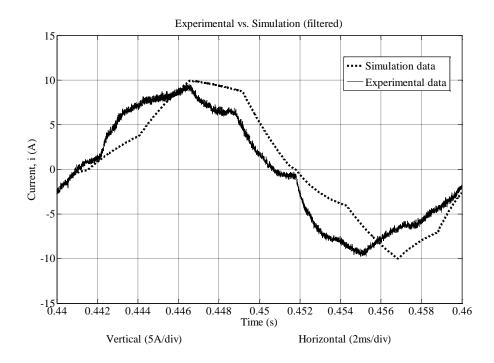

| Fig.5 - 13: Experimental vs. simulation (filtered waveforms) 118                     |

|                                                                                      |

- Fig.5 14: Harmonics comparisons experimental and simulation...... 119

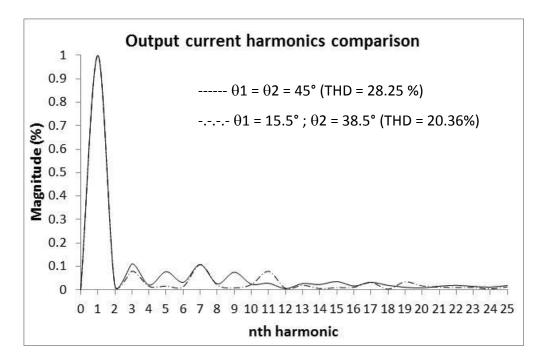

- Fig.5 15: The five-level output current with different switching angles ...... 120

- Fig.5 16: Harmonic contents improved at specific switching angles,  $\theta$  ...... 120

## List of Tables

| Table 2 - 1: Five-level switch combinations for Topology I             | 31  |

|------------------------------------------------------------------------|-----|

| Table 2 - 2: Structural comparison for five-level CSI                  | 55  |

| Table 2 - 3: Simulation parameters                                     | 50  |

| Table 3 - 1: Switching combinations of the single-phase five-level CSI | 60  |

| Table 3 - 2: Current THD comparison by methods of control              |     |

| Table 4 - 1: Comparison of number of components                        | 85  |

| Table 4 - 2: Simulation set of parameters 1                            |     |

| Table 4 - 3: Simulation set of parameters 2                            |     |

| Table 5 - 1: IGBT switches and diodes of the CSI power board           | 111 |

| Table 5 - 2: Summary of the key features of the Spartan-3A             | 113 |

## List of Abbreviations

| CML     | Current Multilevel Cell                                |  |  |

|---------|--------------------------------------------------------|--|--|

| CSI     | Current Source Inverter                                |  |  |

| DF      | Distortion Factor                                      |  |  |

| DPF     | Displacement Power Factor                              |  |  |

| IGBT    | Insulated-Gate Bipolar Transistor                      |  |  |

| IGCT    | Integrated Gate-Commutated Transistor                  |  |  |

| GTO     | Gate Turn-Off Thyristor                                |  |  |

| LCI     | Load Compensated Inverter                              |  |  |

| LFM     | Low Frequency Modulation                               |  |  |

| MCSI    | Multilevel Current Source Inverter                     |  |  |

| MVSI    | Multilevel Voltage Source Inverter                     |  |  |

| OHSW    | Optimized Harmonic Stepped-Waveform                    |  |  |

| PF      | Power Factor                                           |  |  |

| POD-PWM | Phase Opposition Disposition - Pulse Width Modulation  |  |  |

| PWM     | Pulse Width Modulation                                 |  |  |

| PWM-CSI | Pulse Width Modulation – Current Source Inverter       |  |  |

| RMS     | Root-Mean-Square                                       |  |  |

| RS      | Redundant Switching                                    |  |  |

| RS-MPM  | Redundant Switching – Multi-Pulse Modulation           |  |  |

| SCR     | Silicon-Controlled Rectifier                           |  |  |

| SHE     | Selected Harmonic Elimination                          |  |  |

| SHE-PWM | Selected Harmonic Elimination – Pulse Width Modulation |  |  |

| SPWM    | Synchronized Pulse-Width Modulation                    |  |  |

| THD     | Total Harmonic Distortion                              |  |  |

| TPF     | Total/True Power Factor                                |  |  |

| VSI     | Voltage Source Inverter                                |  |  |

### **CHAPTER 1**

### An Overview of Multilevel Inverters

#### 1.1 Introduction

In the last decades, inverters have found many usages in different power segments from low to medium to high power applications whether simply as domestic DC to AC converters or as medium to high power converters in AC drives. The advancement in modern industrial machines with various AC power requirements and the growth of the renewable energy sources as alternatives to fossil fuels which naturally produce useful DC power boost the research and development activities in the field of inverter technology. Though in general inverters basically converters that convert DC power to AC power, their circuits are not uncomplicated; where, multiple research fields can be explored such as the development of power semiconductors, methods of switching and controls, inverter topologies, or industrial converter applications.

Fundamentally, as shown in Fig. 1-1, there are two types of inverters existed; the voltage source inverter (VSI) and the current source inverter (CSI). In general, an inverter that exploits the input voltage while producing controlled output voltage is classified as the VSI whereas an inverter that exploits the input current while producing controlled output current is classified as the CSI. The VSI is the more mature and proven technology where it has been successfully implemented in industry for decades [1-5]. While the 2-Level VSI has found applications in many conventional industrial machines; the multilevel VSIs are more recent and established in industry due to its advantages in particular able to generate multilevel stepped-waveform with reduced harmonic distortion, able to reach higher voltage operation, and higher modularity [3, 6]. On the other hand, the CSI load-commutated inverters (LCI) are among the earliest inverters used for variable speed drives [7, 8] before slowly being replaced by the pulse-width modulation (PWM) CSI mostly in induction motor drives.

Quite recently, similar to the VSIs, multilevel CSIs are gaining attention in new research activities [9, 10]. While both types of inverter have substantial differences topologically, they do share the same working principles. Thus, in general, common control methods and common power semiconductor switches used for VSI can also be applied to CSI with some modifications [11].

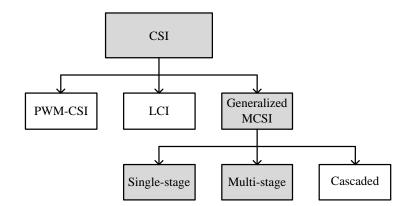

Fig.1 - 1: General Classification of Inverters

Today the majority of the worldwide installed power inverters are voltage source inverters (VSI) followed by current source inverters (CSI). Current source inverters are available as industrial drives [7, 12-15], and have also been connected to wind power and solar power generators [16] and fuel cell systems [17, 18]. Comparison between VSIs and CSIs have been reported many times [19-22] concluding that the decision lies with the performance of the application. Both inverters, however, face the same challenges; generally they have to be small, light and low cost and technically they have to operate at high efficiencies, produce low harmonics, are simple to control and must be reliable. For high voltage and high current application this has led to the introduction of multi-level topologies, first for VSIs like the diode-clamped, flying capacitor and cascaded topologies [23-25] and later to CSIs [7, 26-28]. With the

dominating VSI market research into multi-level current source inverters (MCSI) has been limited. The reason for the lag of interest is, beside the dominance of the VSI in the market, the large component count that is required to build MCSI in particular for a level higher than five i.e. an existing nine-level CSI requires three inductors and twelve power switches. This number goes up rapidly when upgrading the inverter to even higher level of currents. For example a seventeen-level CSI can have seven inductors and twenty power switches.

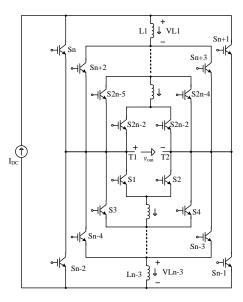

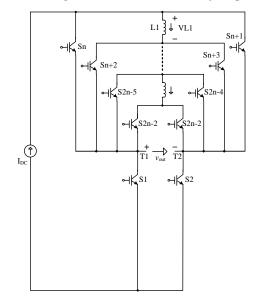

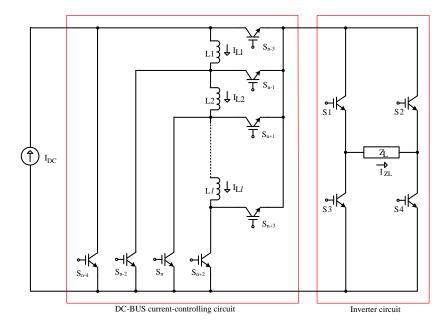

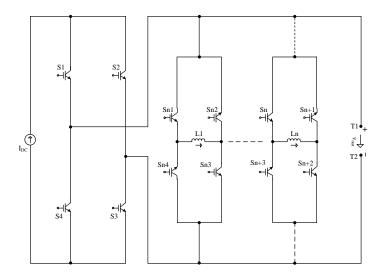

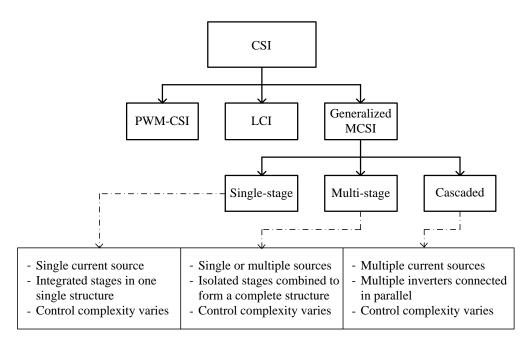

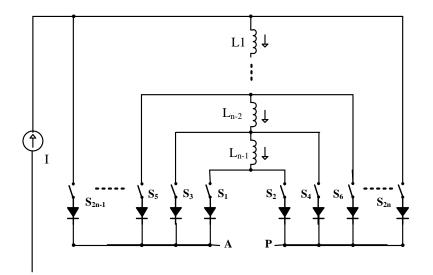

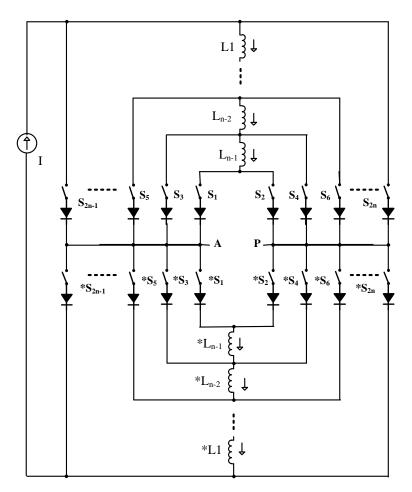

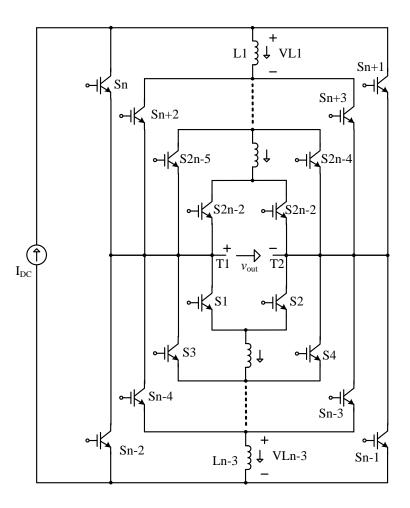

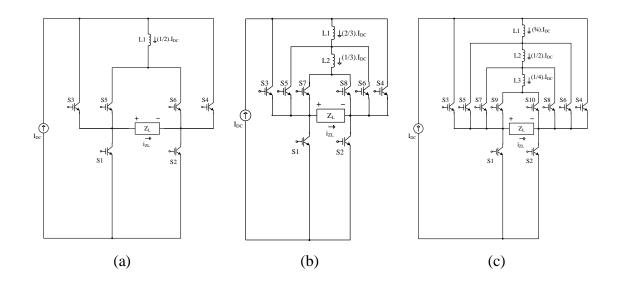

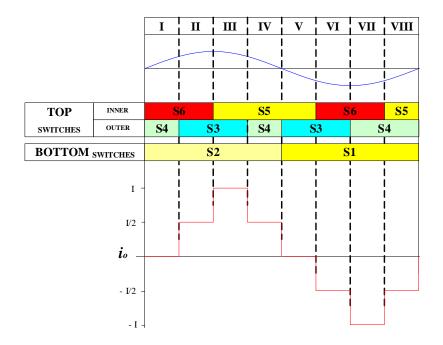

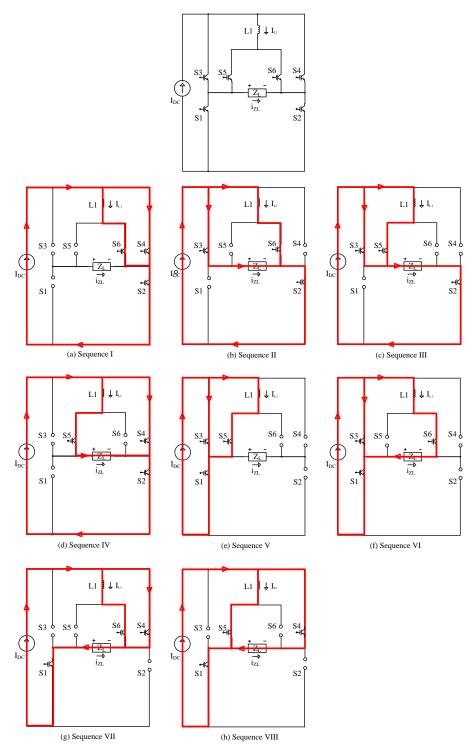

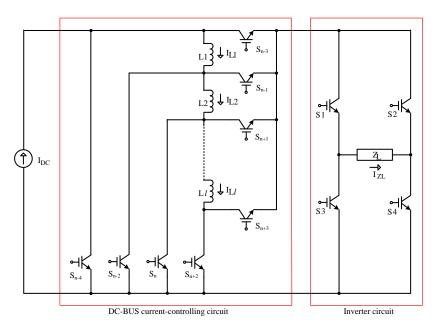

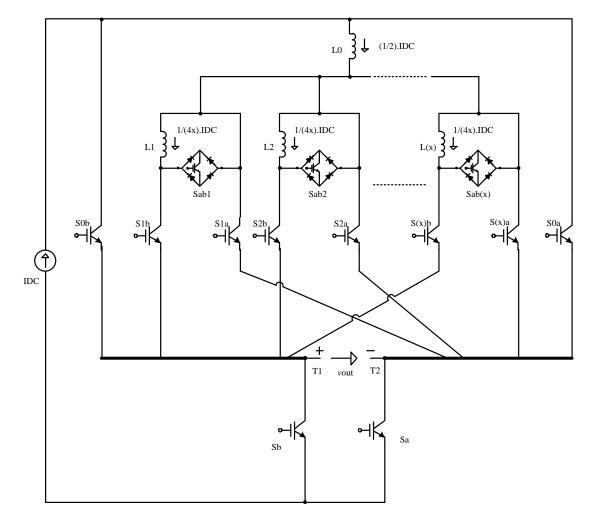

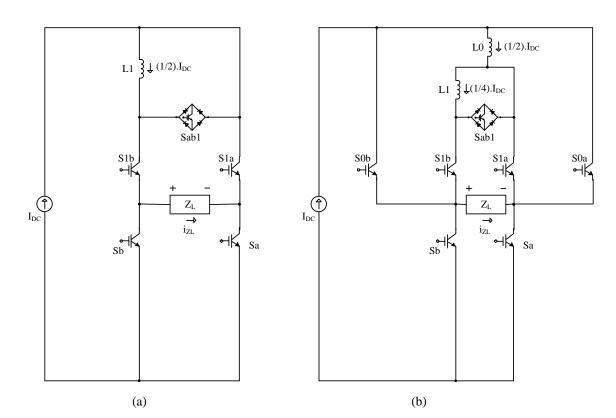

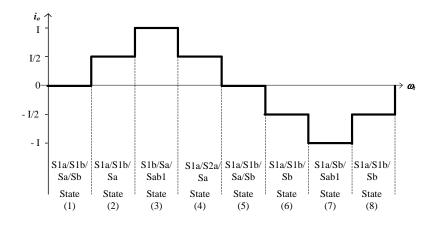

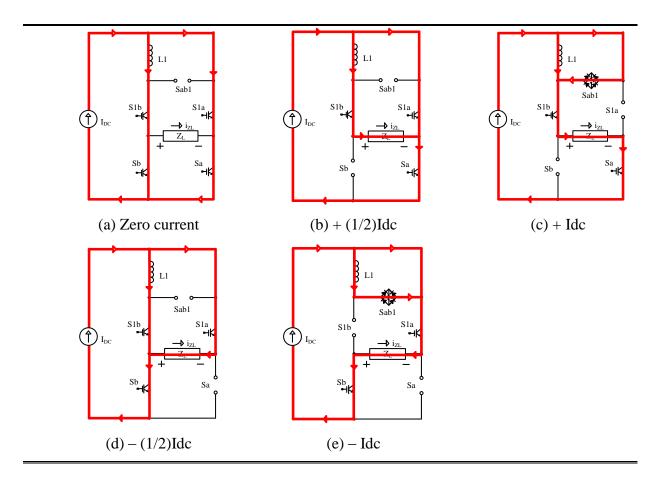

Recent active development of MCSI has seen the emergence of generalized multilevel CSI topologies besides the existing classical LCI and PWM-CSI topologies. However, since none specific multilevel CSI family has been universally established, their classifications are author oriented. For example, a generic multilevel CSI shown in Fig.1-2 uses a single current source where inductors acting as current sources to ensure equal current division among switches. The switches and inductors are integrated in one single structure. It was reported that the output current harmonics minimization and inductor current balance are achieved without the use of high-frequency modulation or closed-loop control [10]. A modified version of the MCSI as shown in Fig. 1-2 is represented by Fig. 1-3 [29]. It can be seen that the current returning paths of the former circuit have been simplified to only two switches. Thus the latter has achieved reduced number of components in a circuit though it should be highlighted that the returning switches must be in much higher ratings than the rest of the switches. In Fig.1-4 [30], although the generic topology also employs a single current source; however, the structure is classified based on the two isolated stages of the DC-bus current-controlling stage and the current-inverting stage. Similar to previous circuits, the inductors acting as the current sources to ensure equal current division among switches while the switch-combinations and also the switching sequences are manipulated to achieve the inductor current balance. Another classification as depicted in Fig. 1-5 [31] is based on two basic main circuits: H-bridge-based and commonemitter-based topologies. Similar to the circuit in Fig. 1-4, it is built with a single current source but multiple stages. While the first stage is to invert the source current into dual polarity, the second stage is to developed stepped-current waveform where

inductors are used to ensure equal current division among switches. The circuit operations will be discussed further in the next Chapter 2.

Fig.1 - 2: The generalized structure of Topology I

Fig.1 - 3: The generalized structure of Topology II

Fig.1 - 4: Generalized structure of Topology III

Fig.1 - 5: Generalized structure of Topology IV

Based on the discussions, the CSI cluster is revised in Fig. 1-6 where the Generalized MCSI is divided into single-stage, multi-stage and cascaded topology. The single-stage generalized MCSI is supplied with a single current-source before being split by sharing inductors and methodically forwarded to the load all in one integrated structure. On the contrary, the multiple-stage converter has two-or more isolated stages

that in combination forms a complete structure of a converter where these converters may have a single-or multiple current sources. The final category is the cascaded structure where multiple inverters are connected in parallel; therefore multiple current sources are expected. The control complexity for each category varies; relatively indicated by the converter size and the number of component in used.

Fig.1 - 6: General Classification of CSI converters

There have been few solutions proposed to reduce the converter size by either introducing new control algorithms [29, 32] or new topologies [10, 30]. For example [29] deploys PWM closed-loop control to sense and balance the intermediate currents through inductors in order to reduce inductor losses allowing smaller inductor designs. This technique however, comes with the expense of an increased complexity. Modification work proposed in [33] on the other hand reduces the total component count but is lagging to control inductor currents at high loads. New topologies as proposed in [34, 35] however fall under the multi-stage category; where multiple current sources are required.

The duality between the flying capacitor MVSI and MCSI was shown in [26]. In theory the flying capacitor MVSI can have an infinity number of capacitors to generate an infinity number of voltage levels. Therefore the flying capacitor topology is termed as a generalized topology. A generalized topology is also referring to a group of inverter whose structure is general to its own class. The same concept applies to the MCSI topologies proposed in [10] which in the following Chapter 2 is called Topology I and is shown in Fig.2-15 where each individual current in each inductor is added to achieve the desired load current as oppose to the flying capacitor where each voltage across each capacitor is added to achieve the desired output voltage. This topology together with few others as in [29, 30, 34] are categorized as generalized MCSI topologies since their principal circuit structures are general to their own cluster which in theory, can be expanded to an infinite level of current. Unfortunately, so far hardware demonstration was always reported on the smallest level which is five [29, 30, 36-38]. There are few publications describing non-experimental work on seven or higher level inverters [33, 39]; nevertheless no detail explanation was given regarding control issues, efficiencies at load variations and current harmonics which are the main drivers in high voltage / high current applications. For example the MCSI controller must guarantee continuous current flow in the inductors to avoid voltage spikes across the switching power devices. The controller must also minimize the inductor current ripple to reduce inductor losses and finally the switches must be controlled in such a way that the average voltage across each inductor is zero in order to avoid saturation of the inductor.

In order to make MCSI more attractive for power conversion the number of components must come down dramatically in particular at high current levels. A reduction in the number of inductors will increase the efficiency and a reduction in the number of switching devices will reduce control complexity. In this research, a novel MCSI is proposed that has a minimum number of inductors and power switches for any output-current level. This causes significant reduction in volume and size of the new inverter, thus allowing the new circuit to be more competitive compared to

existing MCSIs. Furthermore, reduced switching devices simplify the control algorithm, therefore prompting that the novel inverter can become more reliable.

#### 1.2 *Objectives and possible contributions to knowledge*

This research is primarily aimed to explore the basic construction of the generalized MCSI topologies and the focus is to overcome the shortcomings in the existing topologies by proposing a novel inverter topology with improved performance. Investigations on the operation characteristics of novel topologies of multilevel current-source inverter systems in typical high-current applications are carried out. The operation of these novel multilevel topologies will be analysed, modelled and experimentally verified to assess their impact on drive performance and supply distortion levels. In carrying out the experiments, lists of possible contributions to knowledge are highlighted:

- Comprehensive study of multilevel current source inverter topologies;

- Evaluate and compare the existing generalized MCSI topologies in terms of structure and performances;

- Design an improved control strategy for an MCSI under high-load as well as low-load conditions;

- Design a novel MCSI topology that overcomes current shortcomings in existing topologies;

- Evaluate the performance of the novel MCSI by computer simulation and practical experiment;

- Compare the simulation and experimental results obtained from the novel inverter for design verification.

#### 1.3 Thesis structure

Based on the flow of the possible contributions, this thesis is divided into six chapters. **Chapter 1** provides general discussions of multilevel inverters and the generalized CSI topologies as well as the motivation and objectives behind this research.

**Chapter 2** presents the general multilevel converters topologies and operations. Both classical voltage source inverter and current source inverter topologies are briefly discussed. The voltage source inverter to current source inverter duality theory is extended to the principle designs of multilevel current source inverter. Finally, carefully selected existing multilevel current source inverter topologies are discussed in reasonable details.

**Chapter 3** discusses the methods of controlling the multilevel current source inverters. It was shown that the existing methods are primarily aimed at low-load operations; therefore an improved control method that is efficient for both high- and low-load operations has been developed. The proposed method is validated via simulation as well as experimentally.

**Chapter 4** explains the proposed novel multilevel current source inverter topology. The structure and operational characteristics of the proposed inverter is discussed in detail. Computer simulations are performed to validate the theoretical assessment.

**Chapter 5** discusses the experimental arrangement of the research, circuit and controller as well as the associated experimental parameters and experimental results. In this chapter also, the developed MCSI topology is validated experimentally.

Chapter 6 presents the conclusions and also the current and future work plans.

#### *1.4 Publication work*

[1] **B. Hassan**, V. Pickert and B. Zahawi, "Performance Comparison of singlephase current-fed inverters," in Power Electronics, Machines and Drives (PEMD 2010), Proceedings of the 2010-5th IET on, 2010.

[2] **B. Hassan**, V. Pickert and B. Zahawi, "Control of five-level single-phase current-source inverters operating at high- and low-load conditions," in Power Electronics and Applications (EPE 2011), Proceedings of the 2011-14th European Conference on, 2011, pp. 1-9.

### CHAPTER 2

# Multilevel Converter: Topologies and Operations

Multilevel converters were designed in particular to overcome the voltage and current limitations of semiconductor devices for medium- and high-power applications where switching devices are connected in series or parallel to achieve increased power ratings [26, 28, 40]. Recently, multilevel converters have also become popular in low-power applications because of their reduced EMI effects compared to two-level inverters [9]. Although multilevel converters can be constructed either as voltage-source inverter (VSI) or current-source inverter (CSI), nowadays there are more VSIs in operation than CSIs mainly because of cost. This chapter starts by reviewing the classical converter hierarchy in a typical high-power drives application leading to the main research interest, the multilevel current source inverter (MCSI). The three (3) main groups of MCSI, as discussed in chapter 1, are elaborated where four existing single-source MCSI topologies are presented in detail, compared and summarized. Some details of the Simulink models used in the simulations are presented in Appendix A.

#### 2.1 Introduction

The invention of the multilevel converters in 1980 by Nabae et al [41] has encouraged research activities into transformer-less based investigations for highpower high-voltage electric drives because the multilevel converter topologies have the advantage of increased power rating, where they have been proven to be reliable and robust in some high power applications. They are also able to generate near sinusoidal voltages with only fundamental frequency switching or have almost no electromagnetic interference and common-mode voltage [41]. These advantages, however, are offered at the expense of extra complexities either structurally or by the switching strategies.

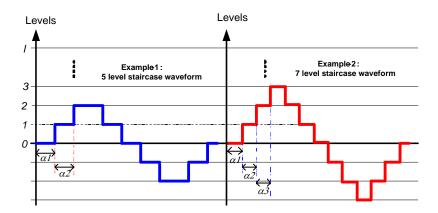

In numerous literatures, the term multilevel starts at the level of three, though definitions may vary either by applications or by author [6]. In this thesis, the definition of the number of levels is self-explained by the illustrations in Fig.2-1, where if l is simply the number of level on positive y-axis, then the number of levels, n for a typical staircase waveform can be mathematically determined by:

Converter output level,

$$n = 2l + 1$$

(2-1)

Fig.2 - 1: Converter output level determination

Generally, a higher number of level gives a better output total harmonic distortion (THD). Thus, in theory the output THD should be zero when the number of levels reaches infinity. Practically, however, the possible number of levels is bounded by various factors such as the voltage/current imbalance problems, voltage/current clamping requirements, circuit layout and packaging constraints, complexity of the controller, and also the maintenance costs [27]. These factors occurred depending on the applied topology. In multilevel topologies, the magnitude of harmonic distortion can be attuned by controlling the conducting angles;  $\alpha 1$ ,  $\alpha 2$  and  $\alpha 3$  (Fig.2-1) to create asymmetrical staircase waveform where specific low order harmonics can be eliminated. This method of control has been commonly practised in selective harmonic eliminated (SHE) modulation technique [6].

#### 2.2 Harmonic Minimization in MCSI

In Fig. 2-1, the parameters  $\alpha_1$ ,  $\alpha_2$  and  $\alpha_3$  are the firing angles which must be greater than zero and smaller than  $\pi/2$ . These angles can be chosen arbitrarily as long as they produce multilevel waveform as desired, or can be carefully selected for harmonic control in order to reduce THD. Nevertheless, by choosing the firing angles strategically, multiple harmonic orders can be completely eliminated and thus eliminating the need for filtering equipment required for that particular orders.

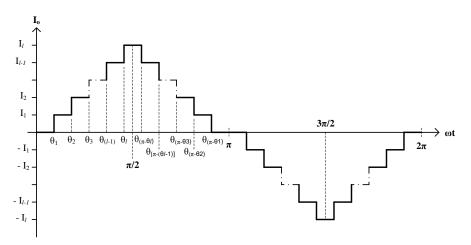

Fig.2 - 2: Output current waveform of a general single-source MCSI

Theoretically, the waveform of the load current of an MCSI, as shown in Fig. 2-2 is periodic and has the same symmetry as a sine wave. The figure illustrates a generalized output-current waveform of a single-source MCSI that consists of switching angles,  $\theta_1$ ,  $\theta_2$ ,  $\theta_{3,...}$ ,  $\theta_{(l-1)}$  and  $\theta_l$  in each quarter cycle. The maximum current level equals to  $I_l$  whereas the current of the intermediate levels are the fractions of this maximum current. The number of current fractions determines the complexity of the circuit whereby it identifies the number of current branches involved. This also reflects to the number of power switches and inductors that are required in order to divide the maximum current into current fragments. Like any other periodic function, this waveform can be expressed as a Fourier series which is a summation of sinusoids with frequencies that are integer multiples of the function's fundamental frequency. In general, the Fourier series of a periodic function  $f(\omega t)$  with fundamental frequency f can be expressed as [42];

$$f(\omega t) = a_0 + \sum_{m=1}^{\infty} [a_n \cos(m\omega t) + b_n \sin(m\omega t)]$$

(2-2)

where *m* is the harmonic order;  $a_0$  is the average value of the function;  $a_n$  and  $b_n$  are the coefficients of the series. The coefficients can be computed as follows;

$$a_o = \frac{1}{T} \int_0^T f(\omega t) \, d(\omega t) \tag{2-3a}$$

$$a_n = \frac{2}{T} \int_0^T f(\omega t) \cos(m\omega t) d(\omega t)$$

(2-3b)

$$b_n = \frac{2}{T} \int_0^T f(\omega t) \sin(m\omega t) d(\omega t)$$

(2-3c)

By referring to Fig 2-2, it can be noticed that the current waveform is both odd and half-wave symmetries. This would simplify its Fourier series equation to;

$$a_o = 0 \tag{2-4a}$$

$$a_n = 0 \tag{2-4b}$$

$$b_n = \frac{2}{\pi} \int_0^{\pi} I_o(\omega t) \sin(m\omega t) d(\omega t)$$

(2-4c)

It is also assumed that the periodic waveform has quarter-wave symmetry, therefore;

$$b_n = \frac{2}{\pi/2} \int_0^{\pi/2} I_o(\omega t) \sin(n\omega t) d(\omega t)$$

(2-5a)

$$b_n = \begin{cases} \frac{4}{\pi} \int_0^{\pi/2} I_o(\omega t) \sin(m\omega t) d(\omega t); & m = odd \\ 0; & m = even \end{cases}$$

(2-5b)

and the resulting Fourier series of the figure in Fig 2-2 is;

$$I_o(\omega t) = \sum_{m=1}^{\infty} b_n \sin(m\omega t)$$

(2-6a)

Let  $\omega t = \theta$ , hence

$$I_o(\theta) = \sum_{m=1}^{\infty} b_n \sin(m\theta)$$

(2-6b)

From Eqn. (2-5b) and (2-6a), therefore, the Fourier series of the current waveform in Fig 2-2 can be expressed as;

$$I_o(\omega t) = \sum_{m=odd}^{\infty} \frac{4I_0}{m\pi} \left( \sum_{k=1}^{l} \cos(m\theta_k) \right) \sin(m\omega t)$$

(2-7)

Where  $\theta_k$  is the switching angles which satisfy the condition  $\theta_1, \theta_2, ..., \theta_l < \frac{\pi}{2}$ ;

I<sub>0</sub> is the amplitude of dc current

*l* is the current-level on the positive x-axis

The amplitude of all odd harmonic components including the fundamental are given by;

$$h(m) = \frac{4I_0}{m\pi} \sum_{k=1}^{l} \cos(m\theta_k)$$

(2-8)

Which switching angles of the waveform can be adjusted to get the lowest THD in the output current as;

$$h(m) = \frac{4I_0}{m\pi} \left[ \cos\theta_1 + \cos\theta_2 + \cos\theta_3 + \dots + \cos\theta_{(l-1)} + \cos\theta_l \right]$$

(2-9)

The fundamental component amplitude depends on the modulation index, M which is the ratio of the modulating signal amplitude to the carrier signal amplitude;

$$M = \frac{l_1}{l_{max}} \tag{2-10}$$

Where  $I_1$  is the fundamental component of the output current

Imax is the maximum output current

Therefore, for the fundamental output current, the general harmonic equation can be determined by;

$$\frac{4I_0}{\pi} \left[ \cos\theta_1 + \cos\theta_2 + \cos\theta_3 + \dots + \cos\theta_{(l-1)} + \cos\theta_l \right] = I_1$$

(2-11a)

Which can be rewritten as;

$$\left[\cos\theta_1 + \cos\theta_2 + \cos\theta_3 + \dots + \cos\theta_{(l-1)} + \cos\theta_l\right] = M$$

(2-11b)

Whereas desired harmonics for elimination i.e. the  $3^{rd}$ ,  $5^{th}$  and  $7^{th}$  harmonics (although not limited to), can be determined by;

$$\left[\cos 3\theta_1 + \cos 3\theta_2 + \cos 3\theta_3 + \dots + \cos 3\theta_{(l-1)} + \cos 3\theta_l\right] = 0 \qquad (2-12a)$$

$$\left[\cos 5\theta_1 + \cos 5\theta_2 + \cos 5\theta_3 + \dots + \cos 5\theta_{(l-1)} + \cos 5\theta_l\right] = 0 \qquad (2-12b)$$

$$\left[\cos 7\theta_1 + \cos 7\theta_2 + \cos 7\theta_3 + \ldots + \cos 7\theta_{(l-1)} + \cos 7\theta_l\right] = 0 \qquad (2-12c)$$

While equation (2-11) guarantees the desired fundamental component, equation (2-12) are used to eliminate the selected harmonics i.e. the 3<sup>rd</sup>, 5<sup>th</sup>, and 7<sup>th</sup> although not limited to these specific orders. The number of certain harmonic orders that can be eliminated depends on the number of switching angles,  $\theta_k$ . As an example, for the 5-level current waveform, two switching angles involved; therefore, one selected harmonics can be eliminated. Similarly, for the 9-level

current waveform, four switching angles involved; therefore, three selected harmonics can be eliminated.

Although these angles can be computed numerically, this is by no means uncomplicated due to nonlinear and transcendental characteristics of the equations. In fact, this is one of the most difficult tasks associated with the SHE technique. Several solving methods were developed for the optimized harmonic switching angles in multilevel inverters as reported in [26, 42-46] and the Table 2-1 has presented some examples of the solved angles for the 3<sup>rd</sup>, 5<sup>th</sup> and 7<sup>th</sup> harmonics elimination by two different methods, namely the Newton-Raphson method (N-R) and the genetic algorithm based optimization method (GA) for a nine-level step-waveform [26, 42, 45]. It can be noticed that the resulted angles of the different schemes varies even though the standard step-waveform and the same modulation index are employed. Therefore, it is best to justify that these angles are only best to be used as references only since in practical hardly any two waveforms will be perfectly equivalent. Yet, it is beyond the scope of this thesis either to prove the effectiveness of any of these methods or to develop an appropriate new solving method for any particular waveform. Nevertheless, this has been recommended for future research in Chapter 6. On the other hand, it is in the interest of the thesis to demonstrate that the low order harmonics and the THD of the MCSI output current waveform can be improved with switching angle manipulation.

| Mod. Index |            | Angle (Degree) |           |

|------------|------------|----------------|-----------|

| Mod. Index |            | N-R Method     | GA Method |

|            | $\theta_1$ | 27.40          | 22.76     |

| 0.8        | $\theta_2$ | 51.60          | 34.42     |

| 0.8        | $\theta_3$ | 73.90          | 46.17     |

|            | $\theta_4$ | 81.40          | 58.03     |

|            | $\theta_1$ | 5.25           | 5.79      |

| 0.85       | $\theta_2$ | 28.10          | 17.38     |

| 0.83       | $\theta_3$ | 46.40          | 37.61     |

|            | $\theta_4$ | 84.09          | 55.74     |

Table 2 - 1: Switching angles for different modulation index and solving methods

#### 2.3 Harmonics

In general, the total harmonic distortion (THD) can be determined by [47];

$$THD_{\%fundamental} = \left(\frac{I_{rms(distortion)}}{I_{fundamental}}\right) \times 100$$

(2-13)

Where  $I_{rms(distortion)}$  is the rms value of harmonic current without the fundamental current.

*I*<sub>fundamental</sub> is the fundamental current.

The rms current of an ac waveform can be calculated by [48];

$$I_{rms} = \sqrt{\frac{1}{T} \int_0^T i_{ac}^2 dt}$$

(2-14)

Where *T* is the time period.

The ac current waveform,  $i_{ac}$  in steady states is the sum of its Fourier components (assuming zero dc component) as [49];

$$i_{ac}(t) = i_{1ac}(t) + \sum_{h \neq 1} i_{hac}(t)$$

(2-15)

Where  $i_{1ac}$  is the fundamental component and  $i_{hac}$  is the component at the *h* harmonic frequency. By substituting for  $i_{ac}$  from eqn. 2-15 into eqn. 2-14;

$$I_{ac(rms)} = \sqrt{I_{1ac(rms)}^{2} + \sum_{h \neq 1} I_{hac(rms)}^{2}}$$

(2-16)

The rms or the "root-mean-square" summation of current is used to determine the current whenever more than one current frequency exists. It is basically the total effective load current which contains both the fundamental and harmonics. This allows for individual calculations of the rms values of the actual waveform which can be approximated by (assuming zero dc components);

$$I_{rms} = \sqrt{I_{rms}^2(1) + I_{rms}^2(2) + \ldots + I_{rms}^2(n)}$$

(2-17)

Where  $I_{rms}(1)$  is the fundamental current ( $I_{fundamental}$ )

$I_{rms}(2)$  to  $I_{rms}(n)$  are the harmonic components ( $I_{rms(distortion)}$ )

Thus, the values of  $I_{rms}$  from eqn. 2-17 can be substituted into eqn. 2-13 to get the percentage of THD of the waveform.

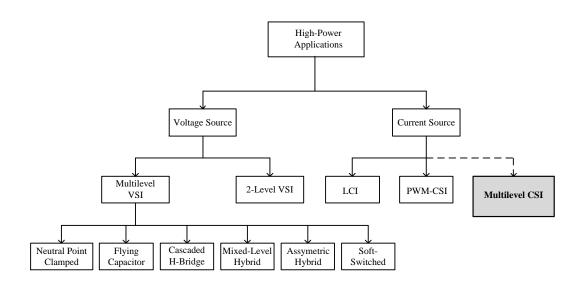

#### 2.4 Classification of converters for high-power applications

In high power applications, typically the inverters used can be classified into voltage source inverter (VSI) and current source inverter (CSI) as illustrates in Fig.2-3 [9]. VSIs are used to define the output voltages while CSIs are used to define the output currents. For multilevel topologies, the VSI has advantages such as the reduction in voltage dv/dt harmonics, electromagnetic interferences and filter size [41]. Popular MVSI topologies are the diode-clamped inverter (or neutral-point clamped), capacitor-clamped (or flying capacitor), and cascaded multi-cell with separate dc sources. These converters are commercially available and commonly found in the medium-to-high power applications of merely few megawatts to hundreds of megawatts i.e. petrochemical industry and cement industry [3]. There are other less-popular topologies such as the mixed-level hybrid inverter, the asymmetric hybrid inverter and the soft-switched inverter [6]. These are mostly available in the lower power range and subjected to on-going

research. On the contrary, even though CSI technology has been widely accepted in the industry, many of CSIs are designed for specific applications; and frequently for large ac drive [50, 51]. Previously, CSI can be divided into two classical topologies; one is called the load-commutated inverters (LCI) which utilize SCR as their switching devices, and second is the PWM-CSIs that often use either symmetrical GTOs or IGCTs devices. However, only recently new family of topology emerges; the generalized multilevel current source inverter (MCSI) which generates the output currents in multilevel forms. Although currently still at research stage, the MCSI has the potential to be used in high power applications due its ability to divide the total input current among the employed switches unlike the traditional CSI that are normally parallel-connected in order to produce multilevel waveforms with the help of inductor-links to smoothen the sharing-current outputs [26, 52].

Fig.2 - 3: Classification of converters for high-power applications

#### 2.5 Multilevel Voltage Source Inverter

The new emerging family of MCSI partly has been the result of the general viewpoint that CSI is the dual of a VSI imparts the essential step in the

construction of MCSI topologies via the duality principle [51]. By theory; two dual circuits share similar properties, thus the knowledge obtained from one topology can be applied to its dual circuit directly. Therefore, sufficient understanding of the renowned MVSI families such as the diode-clamped, flying capacitors and the cascaded H-bridge inverters are crucial.

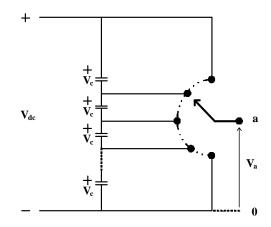

To simplify the idea, the MVSI simply can be viewed as voltage synthesizer where the main output voltage waveform is synthesized from different levels of smaller output voltages. Fig.2-4 shows a schematic diagram of a single-phase inverter with multiple numbers of capacitors to illustrate the basis of multilevel inverter operation. The different voltage levels are represented by the capacitors whereas the ideal switch with multiple poles represents the action of power semiconductor switches. It can be seen that a number of output voltage levels can be synthesized by controlling to where the switch pole is connected to a portion of the capacitors. Similarly, for a negative output voltage, the reference node, 0 is moved to the opposite end of the capacitor string. These are the basic principles surrounding the setup of MVSI as will be discussed next.

Fig.2 - 4: Multilevel inverter fundamental

### 2.5.1 Diode-Clamped Inverter

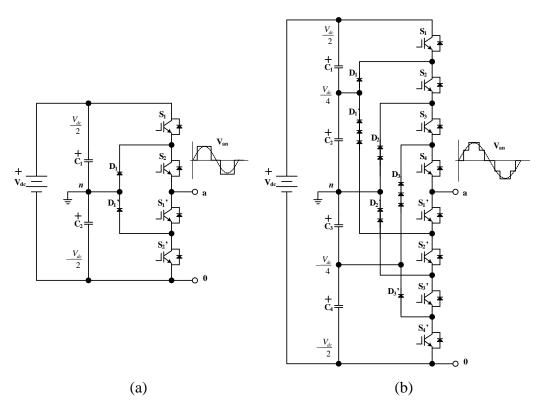

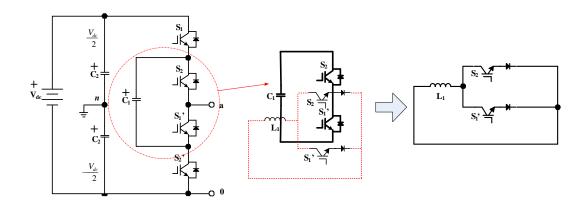

The diode-clamped inverter employs capacitors in series to split up the DC bus voltage into a set of voltage levels. Fig.2-5 shows the diode-clamped inverter

configurations for three-level and five-level voltage outputs. In order to produce an *n*-level phase voltage, a diode clamped converter needs (*n*-1) capacitors on the DC bus. From Fig. 2-5(a) it can be seen that for the three-level output, two capacitors are required whereby each capacitor carries  $\pm Vdc/2$  across them. As for the five-level output, four capacitors are required where the voltage across each capacitor is  $\pm Vdc/4$ . Knowing the voltage and polarity of each capacitor, the staircase output voltage can be easily synthesized by manipulating the switching combinations.

For a three-level diode-clamped inverter as shown in Fig.2-5(a), the dc-bus voltage is divided into two half values,  $V_{dc}/2$  by two series-connected capacitors  $C_1$  and  $C_2$ . The middle point, *n* between the two capacitors is defined as the neutral point. Therefore, the output voltage  $v_{an}$  has three levels; (1)  $v_{an} = +V_{dc}/2$  when switches  $S_1$  and  $S_2$  are turned on, (2)  $v_{an} = -V_{dc}/2$  when switches  $S_1$ ' and  $S_2$ ' are turned on, (3)  $v_{an} = 0$  when switches  $S_2$  and  $S_2$ ' are turned on.

Fig.2 - 5: Diode-clamped inverter (a) three-level (b) five-level

For a five-level diode-clamped inverter as shown in Fig.2-5(b), the dc-bus voltage is divided into four quarter values,  $V_{dc}/4$  by four series-connected capacitors  $C_1$ ,  $C_2$ ,  $C_3$ , and  $C_4$ . The point, *n* between capacitor  $C_2$  and  $C_3$  is defined as the neutral point. Therefore, the output voltage  $v_{an}$  has five levels; (1)  $v_{an} = +V_{dc}/2$  when all upper switches  $S_1$ - $S_4$  are turned on, (2)  $v_{an} = +V_{dc}/4$  when three upper switches  $S_2$ - $S_4$  and one lower switch  $S_1$ ' are turned on, (3)  $v_{an} = 0$  when two upper switches ( $S_2$  and  $S_4$ ) and two lower switches ( $S_1$ ' and  $S_2$ ') are turned on, (4)  $v_{an} = -V_{dc}/4$ when one upper switch  $S_4$  and three lower switches  $S_1$ '- $S_3$ ' are turned on. (5)  $v_{an} =$  $-V_{dc}/2$  when all lower switches  $S_1$ '- $S_4$ ' are turned on.

### 2.5.2 Capacitor-Clamped Inverter

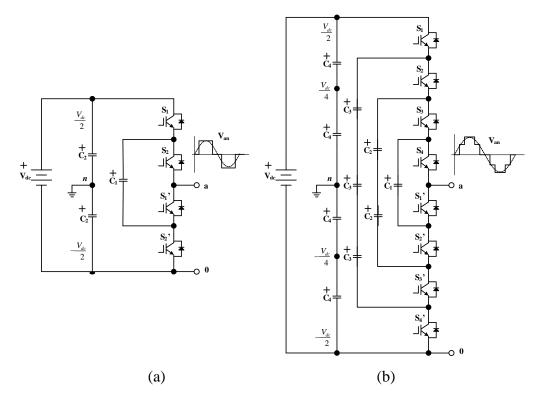

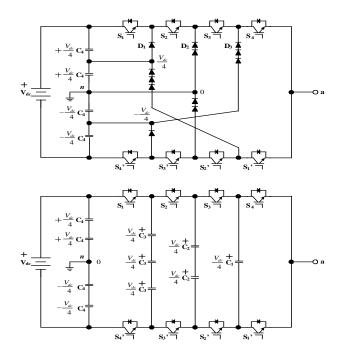

Fig.2-6 illustrates the capacitor-clamped inverter or the flying-capacitor inverter configurations for the three-level and five-level voltage outputs. It can be seen that, although the number of capacitors used to generate an n-level staircase output voltage is equal to (n-1) or equivalent to the requirement of the previous topology; however, this topology also requires a number of supplementary capacitors to be clamped in between switches. To better appreciate these differences, the five-level inverter circuits for both topologies are re-drawn in Fig.2-7. By looking at the capacitor-clamped inverter circuit in Fig.2-7, the figure has clearly shown that the supplementary capacitors are formed in a ladder structure such that every capacitor branch carries different value of voltages which allows mathematical exploitation of the output voltage. Knowing the different voltage value between branches and using the point n as the common reference, the staircase output voltage waveform can be obtained by manipulating the switching combinations.

Fig.2 - 6: Capacitor-clamped inverter (a) three-level (b) five-level

*Fig.2 - 7: Re-drawn figures of the (top) five-level diode-clamped inverter and (bottom) capacitor-clamped inverter*

As the example, for a three-level capacitor-clamped inverter as shown in Fig.2-6(a), similar to the diode-clamped topology, the dc-bus voltage is divided into two half values,  $V_{dc}/2$  by two series-connected equivalent capacitors  $C_2$ . The middle point, *n* between the  $C_2$  is defined as the neutral point. Therefore, the output voltage  $v_{an}$  has three levels; (1)  $v_{an} = +V_{dc}/2$  when switches  $S_1$  and  $S_2$  are turned on, (2)  $v_{an} = -V_{dc}/2$  when switches  $S_1$ ' and  $S_2$ ' are turned on, (3)  $v_{an} = 0$  when either switches ( $S_1$  and  $S_1$ ') or ( $S_2$  and  $S_2$ ') are turned on. The clamping capacitor  $C_1$  is charged when ( $S_1$  and  $S_1$ ') are turned on, and is discharged when ( $S_2$  and  $S_2$ ') are turned on.

The five-level capacitor-clamped inverter shown in Fig.2-6(b) has more flexibility than a diode-clamped inverter. The dc-bus voltage is divided into four quarter values,  $V_{dc}/4$  by four series-connected equivalent capacitors C<sub>4</sub>. The middle point, *n* between capacitor C<sub>4</sub> is defined as the neutral point. Therefore, by manipulating switch combinations similar to the diode-clamped topology, the output voltage  $v_{an}$  also has five levels but with more possible combinations;

(1)  $v_{an} = +V_{dc}/2$  when all upper switches S<sub>1</sub>-S<sub>4</sub> are turned on,

(2)  $v_{an} = -V_{dc}/2$  when all lower switches  $S_1'-S_4'$  are turned on.

(3)  $v_{an} = +V_{dc}/4$  has three possible combinations:

(a)  $S_1, S_2, S_3, S_4$ ' are on, where  $(v_{an} = +V_{dc}/2 - V_{dc}/4 = +V_{dc}/4)$

(a)  $S_2, S_3, S_4, S_4$ ' are on, where  $(v_{an} = +3V_{dc}/4 - V_{dc}/2 = +V_{dc}/4)$

(a)  $S_1, S_3, S_4, S_3$  are on, where  $(v_{an} = +V_{dc}/2 - 3V_{dc}/4 + V_{dc}/2 = +V_{dc}/4)$

(4)  $v_{an} = -V_{dc}/4$  has three possible combinations:

- (a)  $S_1, S_1', S_2', S_3'$  are on, where  $(v_{an} = +V_{dc}/2 3V_{dc}/4 = -V_{dc}/4)$

- (a)  $S_4, S_2, S_3, S_4$  are on, where  $(v_{an} = +V_{dc}/4 V_{dc}/2 = -V_{dc}/4)$

- (a)  $S_3, S_1', S_3', S_4'$  are on, where  $(v_{an} = +V_{dc}/2 V_{dc}/4 V_{dc}/2 = -V_{dc}/4)$

(5)  $v_{an} = 0$  has six possible combinations:

(a)  $S_1, S_2, S_1', S_2'$  (b)  $S_3, S_4, S_3', S_4'$  (c)  $S_1, S_3, S_1', S_3'$ (d)  $S_1, S_4, S_2', S_3'$  (e)  $S_2, S_4, S_2', S_4'$  (f)  $S_2, S_3, S_1', S_4'$

### 2.5.3 Cascaded Multi-Cell Inverter

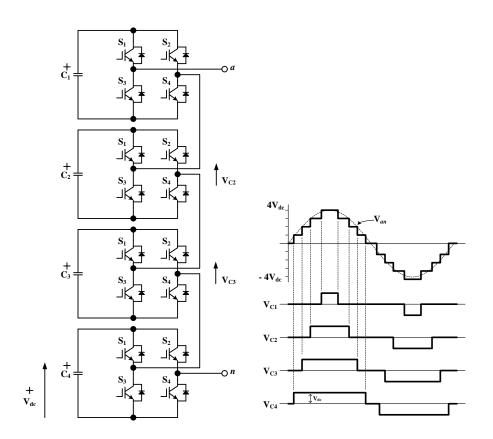

The cascaded multi-cell inverter practically consists of many identical singlephase H-bridge converters connected in a string where each of the bridge is separately supplied with a DC voltage sources. Fig.2-8 illustrates the nine-level cascading multi-cell inverter with its corresponding waveform. For each H-bridge converter, three different voltage outputs, +Vdc, -Vdc and zero can be generated through different combinations of the four switches. By connecting the bridges in series, the AC voltage output generated is such that the synthesized voltage waveform is the sum of the individual converter outputs (Fig.2-8). The staircase output voltage waveform again can be generated by manipulating the appropriate switch combinations. For this topology, the output voltage levels can be determined by (n = 2N+1), where N is the number of DC voltage sources.

Fig.2 - 8: Cascaded inverter with corresponding output waveform

#### 2.6 Classical Current Source Inverter

It has been reported that amongst the advantages of CSI topologies include: (1) short-circuit protection, where the output current is limited by the dc-bus current; (2) low output voltage *dv/dt*, which resulted from the output capacitor filtering effect; (3) high converter reliability, due to the unidirectional nature of the switches and the inherent short-circuit protection; and (4) instantaneous and continuous regenerative capabilities [53-56]. These features, in addition to the availability of large reverse blocking devices such as GTOs or IGCTs make the CSI-based drive attractive in medium to high power applications. Despite the above advantages, research development in CSI is far behind that of VSI. This can be justified simply by comparing the number of available literatures from both topologies. Over the last decade approximately six thousand (6000) papers and journals have been published on VSIs in IEEE Library whereas only three thousand and five hundred (3500) papers and journals have been published on CSIs.

### 2.6.1 Load-commutated inverter (LCI)

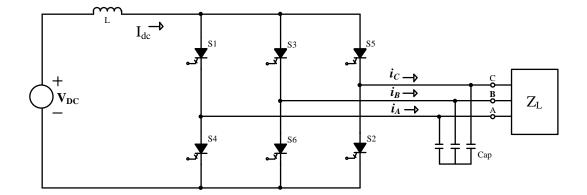

The SCR-based LCI is one of the earliest inverters developed for variable-speed drives. A three-phase LCI has three parallel poles; representing by two seriesconnected SCRs per-pole which in total requires six SCRs. As shown in Fig.2-9, the SCR or thyristor switches are numbered according to their firing sequence whereas the commutating elements, capacitors between the phase legs and series diodes are intentionally excluded for simplification. A nearly constant current, Idc is sourced by connecting a large inductor between the input dc voltage source, Vdc and the inverter components; thus creating a current-source inverter circuit. When a thyristor is fired, it immediately commutes the conducting thyristor of the same group (upper and lower groups) i.e. when S1 and S2 are conducting, the input current Idc will flow through (S1- phase A load– phase C load- S2) and back to the input source. The idealized waveforms of the input and output currents are shown in Fig.2-10 [57]. It can be seen that each thyristor conducts for a 120 degree interval. Since a thyristor is a load commutated device, these inverters have to be made to operate at leading power factor.

Fig.2 - 9: Schematic of a classical SCR-based CSI

While popular, SCR-based CSI is most commonly used for the low cost solution since higher power rated thyristors are easily available [58]. A major disadvantage of this topology is the limited control strategies applicable since a thyristor cannot be switched off from the gate drive circuit. Therefore, the most common control technique applied is the six-step switched control [59] although this controller is known for generating large amount of harmonics in the load voltage and load current. These harmonics can be reduced by connecting the output filter capacitors as illustrated in the Fig.2-9. Another approach to minimise the current and voltage harmonics in CSI is the application of PWM control which can be achieved easily by replacing the thyristor switches with gate turn-off devices such as the GTO or IGCT switches. This would allow turn-off capability and result in the extension of operation to loads with wider power factor and even pulse width modulation (PWM) capability [60].

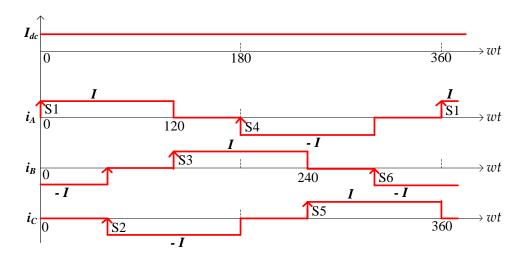

Fig.2 - 10: Three-phase SCR-based CSI typical current waveforms

# 2.6.2 PWM-CSI inverter

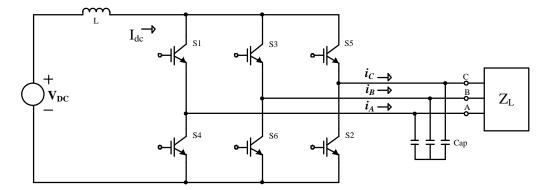

The CSI using IGBT switches is shown in Fig.2-11. In the figure, the series diodes are excluded for simplicity. The waveforms of currents  $i_A$ ,  $i_B$  and  $i_C$  are the same as those shown in Fig.2-10 except that the switches S1-S6 can be turned on and off by the gate voltages or gate currents of the devices. Various modulation techniques therefore can be applied in order to improve the output current harmonics including trapezoidal pulse width modulation (TPWM), selective harmonics elimination (SHE), and space vector modulation (SVM) [61, 62]. Whilst, the capacitor bank purposes are to assist the commutation process during switchover of current between devices by providing temporary load current, to filter out current harmonics then generate a sinusoidal load current, and to reduce voltage spikes.

Essentially in CSI, all switching devices must be able to withstand equally both forward and reverse blocking voltage, thus symmetrical switching devices are often preferred. In cases where unsymmetrical devices are used, series diodes are necessary to protect the switches from reverse voltage. This practice has however, not just increased the cost, but also the complexity and conduction losses [59]. Another disadvantage of PWM control is that it degrades the converter efficiency due to high switching losses.

Fig.2 - 11: Schematic of a CSI using IGBT switches

Despite the drawbacks, PWM-CSI inverters are continuously explored by many researchers for new or improved control algorithms [63-65] and topologies [66-68]. Apparently its ruggedness and reliability in general outweigh its disadvantages. Recent development in multilevel current source inverters (MCSI) which present several advantages regarding total harmonic distortion and stress on inductors and switches are progressively published. Several MCSI topologies have been developed and presented in the literature [29, 32, 34, 36, 39, 69, 70]. The next chapter will explain the different types of MCSI topologies in existent.

### 2.7 Introduction to MCSI

The CSI has certain performance advantages especially in the medium-voltage drive applications such as simple converter structures, low switch count, low switching  $\delta v/\delta t$ , and reliable over-current/short-circuit protection; however, its major disadvantages are the poor dynamic performance due to the use of dc chokes which limits the rate of dc current changes [61] and higher power losses in comparison to its dual, the voltage source inverters (VSI). In the past, the VSI designs have been proven to be more efficient, have higher reliability with faster dynamic response in the industrial markets [71]; therefore more investigations are carried out in this area. Amongst significant accomplishment is the introduction of multi-level voltage source inverters (MVSI) which have been installed in a range

of medium-to-high power applications such as in the retrofitted medium power drives [3] and high voltage dc transmission (HVDC) systems [72].

Just recently, since the availability of modern gate turn-off switching devices at increasing power levels, significant interest in the MCSI topologies have emerged. A number of new MCSI topologies have been developed. However, unlike the classical CSI topologies as previously discussed, these new topologies have different structure as well as characteristics to both classical CSIs that they fall into a new sub-category to the existing CSI family as illustrated in Fig.2-12. Comprehensive description of the figure has been previously discussed in chapter 1 (Fig.1-6). Many of these new topologies are developed as the equivalent to the MVSI topologies based on duality principles[11, 73-75].

Fig.2 - 12: Generalized MCSI under CSI classification

#### 2.7.1 MCSI Topology: Principles of Design

Generally, the classical CSI-based multilevel topologies are designed based on parallel-connection of multiple CSI circuits or cascaded MCSI. These can be either LCI-parallel with-LCI [76], PWM\_CSI-parallel with-PWM\_CSI [77], or LCI-parallel with-PWM\_CSI (or hybrid topology) [78, 79]. The new emerging generalized MCSI topologies can be either of single-stage structure [10, 29], multi-stage structure [30, 34, 80] or cascaded structure [39].

#### 2.7.2 Duality Transformation

The general viewpoint that CSI is the dual of a VSI imparts the essential step in the construction of MCSI topologies via the duality principle. The principle has been widely used in the development and understanding of power electronic converter topologies in both planar and non-planar [59] circuits. By theory; two dual circuits share similar properties, thus the knowledge obtained from one topology can be applied to its dual circuit directly. Eventually, sufficient understanding has been gained from well-known MVSI families such as the diode-clamped, flying capacitors and the cascaded H-bridge inverters where for these topologies, their MCSI duals have been progressively developed.

Fig.2 - 13: Duality principle transformation

Dual circuits can be developed by constructing the duals for like-to-like elements. For example in Fig.2-13, the capacitor in capacitor-clamped VSI is replaced with an inductor for CSI. The orientation of passive elements is not important for the duals; however the switches and diodes must be oriented precisely. Fig.2-13 also illustrates this conversion where parallel diodes are replaced by series and inverted diodes whilst power switches in series are replaced by switches in parallel with inverted switching functions. Recently, the subject matter of duality principle and related issues of constructing MCSI topologies from their MVSI equivalent has been extensively discussed [26, 37, 38, 52, 74, 81]; nevertheless, a common agreement has been realized that all direct duals are dysfunctional

circuits where intuitive modifications are necessary before the dual converters become viable. There are numbers of new MCSI families, of both single-phase [82] and three-phase [36-38] topologies that have been originally derived by this theory and successfully experimented. Certainly these circuits are indebted to the duality principle for the insight.

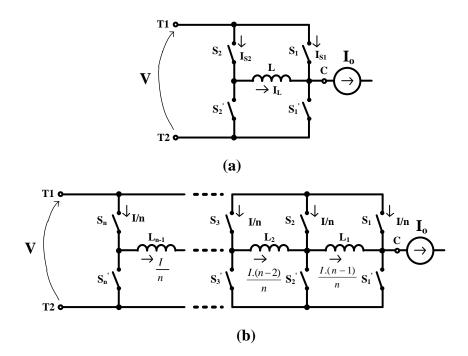

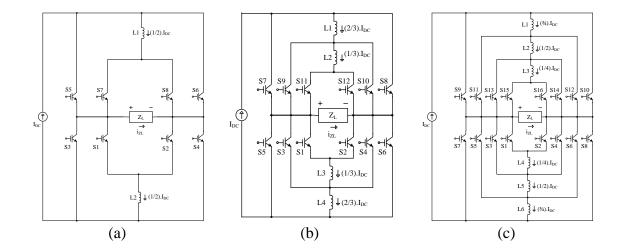

### 2.7.3 Current-Multilevel (CML) Cells

Prior to CML cell discovery, the concept of multilevel has been exclusively used in MVSIs where the total input voltage among a number of employed PWM cells are divided to provide a number of smaller voltage sources. However, the introduction of the generic CML cell (Fig.2-14) which allows current sharing via small balance inductors has instigated the feasibility of MCSI implementation [27]. The concept of CML has been originated from the proposed parallel association of PWM cells as an alternative to the series association of cells in generic multilevel voltage cell in order to increase the power capability of the anticipated converters [50, 69, 83]. The configuration, as shown in Fig.2-14a consists of multi cells arrangement of two complementary PWM switches per-cell (S1/S1' and S2/S2'), a voltage source between point T1 and T2 and also a current source at point C connected by means of balance inductors. The inductor is assumed to be in continuous conduction mode with negligible ripple and has a specific and fixed current level i.e. (I/n) current, where n equals the total number of complementary switches (Fig.2-14b). It is shown that it is possible for PWM cells to share the total current of a converter using inductors as pathways as long as the current is continuously conducting with negligible ripple about a fixed current value.

Fig.2 - 14: The original generic cell; (a) single-cell (b) multiple-cells