# ACTIVE CURRENT SHARING CONTROL SCHEMES FOR PARALLEL CONNECTED AC/DC/AC CONVERTERS

BASSIM M.H. JASSIM

A thesis submitted for the degree of Doctor of Philosophy

2014

School of Electrical and Electronic Engineering

Newcastle University

United Kingdom

#### **Declaration**

# I declare that the thesis entitled "ACTIVE CURRENT SHARING CONTROL SCHEMES FOR PARALLEL CONNECTED AC/DC/AC CONVERTERS"

is the results of my own research except as cited in the references.

The thesis has not been accepted for any degree and is not concurrent submitted in candidature of any other degree.

#### Abstract

The parallel operation of voltage fed converters can be used in many applications, such as aircraft, aerospace, and wind turbines, to increase the current handling capability, system efficiency, flexibility, and reliability through providing redundancy. Also, the maintenance of low power parallel connected units is lower than one high power unit. Significant performance improvement can be attained with parallel converters employing interleaving techniques where small passive components can be used due to harmonic cancellation.

In spite of the advantages offered by parallel connected converters, the circulating current problem is still a major concern. The term circulating current describes the uneven current sharing between the units. This circulating current leads to: current distortion, unbalanced operation, which possibly damages the converters, and a reduction in overall system performance. Therefore, current sharing control methods become necessary to limit the circulating current in a parallel connected converter system.

The work in this thesis proposes four active current sharing control schemes for two equally rated, directly paralleled, AC/DC/AC converters. The first scheme is referred to as a "time sharing approach," and it divides the operation time between the converters. Accordingly, in the scheme inter-module reactors become unnecessary, as these are normally employed at the output of each converter. However, this approach can only be used with a limited number of parallel connected units. To avoid this limitation, three other current sharing control schemes are proposed. Moreover, these three schemes can be adopted with any pulse width modulation (PWM) strategy and can be easily extended to three or more parallel connected units since they employ a modular architecture.

The proposed current sharing control methods are employed in two applications: a current controller for three-phase RL load and an open loop *V/f* speed control for a three-phase induction motor. The performance of the proposed methods is verified in both transient and steady state conditions using numerical simulation and experimental testing.

# **Dedication**

To Hidden Imam Mahdi (A.S), may God hasten his reappearance

#### Acknowledgements

First of all, I am extremely thankful to the Ministry of Higher Education and Scientific Research of Iraq, for awarding me a scholarship for my PhD studies.

I would like to express my sincere gratitude to my supervisors, Dr. Bashar Zahawi and Dr. Dave Atkinson, for their guidance and support. I consider myself extremely lucky to have had an opportunity to work under their supervision.

I would like to take this opportunity to express my deep appreciation to the faculty members of the Electrical Engineering Department in Baghdad University for their encouragement and assistance, especially Tagreed M. Ali, Sulaiman M. Abbas, Dr. Sadiq Jassim, Ahmed Mohsen, Dr. Jafer Alwash, Enas Ibrahim, and Thamir Mousa.

A special acknowledgement must also go to all of my colleagues in Power Electronics, Drives and Machines Research Group for their valued friendship and help during my time at Newcastle University. I also need to show my appreciation of the staff of the electronic, electrical, and mechanical workshops for their support.

I am also thankful to my parents, brothers, sisters, and my dearest nephew Taqi for their support throughout my PhD. Last but not least, I offer my special appreciation to my wife, who without her support and best wishes, I would not have come to the end of my study.

| Abstra  | ct      |                                                                    | 11    |

|---------|---------|--------------------------------------------------------------------|-------|

| Dedica  | tion .  |                                                                    | iii   |

| Acknov  | wled    | gements                                                            | iv    |

| Table ( | of Co   | ntents                                                             | v     |

| List of | Figu    | res                                                                | xi    |

| List of | Tabl    | es                                                                 | xxiii |

| List of | Abb     | reviations                                                         | xxiv  |

| Chapte  | er 1. ] | Introduction                                                       | 1     |

| 1.1     | Mo      | otivation and objective                                            | 1     |

| 1.2     | The     | esis contributions                                                 | 2     |

| 1.3     | The     | esis outline                                                       | 3     |

| 1.4     | Lis     | t of publications                                                  | 4     |

| Chapte  | er 2. ] | Background and Literature Review                                   | 5     |

| 2.1     | Vo      | Itage Source Inverter                                              | 5     |

| 2.2     | Fur     | ndamentals of Symmetrical Components                               | 5     |

| 2.3     | Cla     | rk and Park Transform                                              | 7     |

| 2.4     | Pul     | se Width Modulation Strategies                                     | 9     |

| 2.4     | 4.1     | Sinusoidal pulse width modulation                                  | 12    |

| 2.4     | 4.2     | Space vector pulse width modulation                                | 14    |

| 2.4     | 4.3     | Discontinuous pulse width modulation                               | 19    |

| 2.5     | Cu      | rrent Control Techniques for a Three-Phase Voltage Source Inverter | 23    |

| 2.3     | 5.1     | Linear current controllers                                         | 24    |

| 2.3     | 5.2     | Hysteresis current control                                         | 26    |

| 2.6     | Par     | rallel Operation                                                   | 26    |

| 2  | 2.7        | Circulating Current and Cross Current: Definitions and Generation                                                                          | 28             |

|----|------------|--------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 2  | 2.8        | Interleaving Techniques                                                                                                                    | 32             |

| 2  | 2.9        | Review of Control Methods for Parallel Connected Three-Phase Converters.                                                                   | 35             |

| Ch | apte       | 3. Proposed Methods                                                                                                                        | 39             |

| 3  | 3.1        | Time Sharing Approach                                                                                                                      | 39             |

| 3  | 3.2        | Average Current Sharing Control Scheme                                                                                                     | 40             |

|    | 3.2        | 1 Current sharing regulation analysis                                                                                                      | 41             |

|    | 3.2        | 2 Design of PI controller gains                                                                                                            | <del>1</del> 6 |

| 3  | 3.3        | Independent Current Sharing Control                                                                                                        | 49             |

|    | 3.3        | 1 Current sharing regulation analysis                                                                                                      | 50             |

| 3  | 3.4        | Impedance Emulation Current Sharing Control Scheme                                                                                         | 53             |

| 3  | 3.5        | Summary                                                                                                                                    | 55             |

| Ch | apte       | 4. Simulation Results                                                                                                                      | 57             |

| 4  | l.1        | Simulation of the PWM Strategies                                                                                                           | 57             |

|    | 4.1        | 1 SVPWM SIMULINK model                                                                                                                     | 57             |

|    | 4.1        | 2 DPWM SIMULINK model                                                                                                                      | 53             |

| 4  | 1.2        | Time Sharing Approach                                                                                                                      | 57             |

|    | 4.2        | 1 Simulation results of time sharing approach                                                                                              | 71             |

| 4  | 1.3        | Average Current Sharing Control Scheme                                                                                                     | 76             |

|    | 4.3<br>син | Parallel connected converter current-controller based on the average rent sharing control scheme                                           | 76             |

|    | 4.3<br>par | 2 Open loop V/f control for three-phase induction motor supplied from allel converters based on the average current sharing control method | 83             |

| 4  | 1.4        | Independent Current Sharing Control Scheme                                                                                                 | 89             |

|    | 4.4<br>cur | 1 Parallel connected converter current-controller based on independent rent sharing control method                                         | 89             |

|    | 4.4        | 2 Open loop V/f control for three-phase induction motor supplied from                                                                      |                |

|    | pai        | allel converters based on independent current sharing control scheme                                                                       | 92             |

|     | 4.4.3     | Independent current sharing control strategy applied to three units     | .95 |

|-----|-----------|-------------------------------------------------------------------------|-----|

| 4.  | 5 Imp     | pedance Emulation Current Sharing Control Scheme                        | .97 |

|     | 4.5.1     | Simulation results of parallel connected converter current controller   |     |

|     | based o   | n an impedance emulation current sharing approach                       | .97 |

|     | 4.5.2     | Simulation results for open loop V/f control for three-phase induction  |     |

|     | motor s   | upplied from parallel connected converters based on impedance emulation | on  |

|     | current   | sharing control scheme1                                                 | 101 |

| 4.  | 6 Inte    | erleaving Impacts on System Performance                                 | 103 |

|     | 4.6.1     | Combined current                                                        | 103 |

|     | 4.6.2     | Inter-module circulating current                                        | 106 |

|     | 4.6.3     | Common mode voltage                                                     | 107 |

| 4.  | 7 Sun     | nmary1                                                                  | 110 |

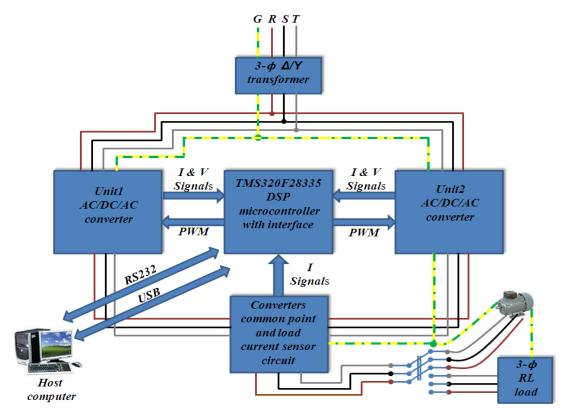

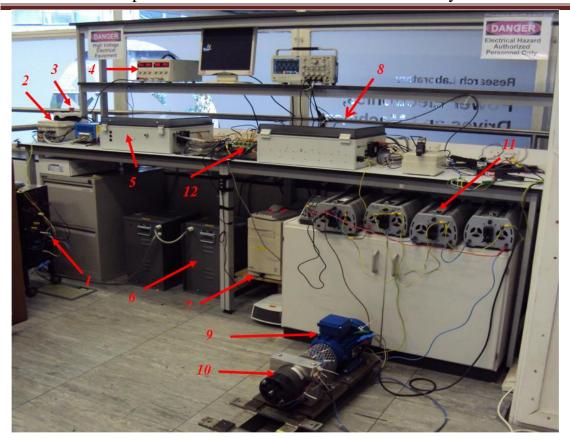

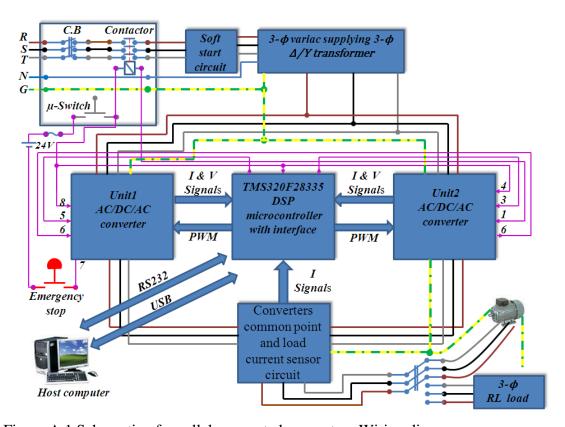

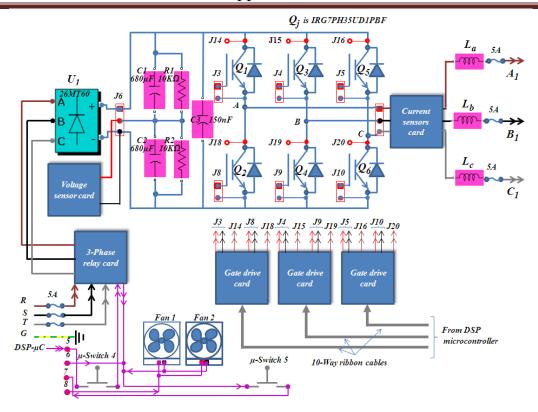

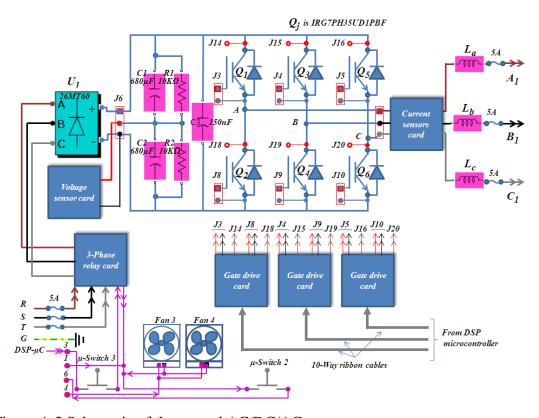

| Cha | pter 5. I | Development of Parallel-Connected Converters System                     | 112 |

| 5.  | 1 Sys     | tem Overview1                                                           | 112 |

|     | 5.1.1     | System requirements                                                     | 112 |

|     | 5.1.2     | System structure                                                        | 113 |

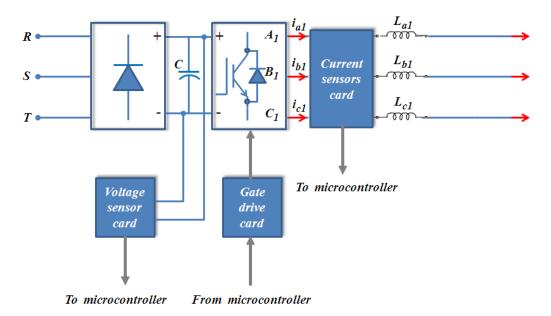

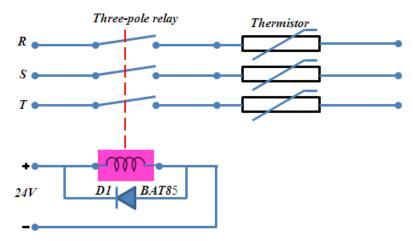

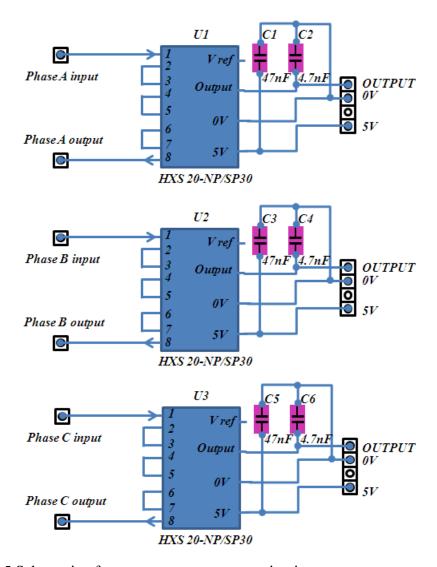

| 5.  | 2 Har     | dware Implementation1                                                   | 115 |

|     | 5.2.1     | AC/DC/AC converter unit                                                 | 115 |

|     | 5.2.2     | General purpose power interface board for the Texas Instrument®         |     |

|     | TMS320    | OF28335 DSP microcontroller                                             | 120 |

|     | 5.2.3     | Test load                                                               | 124 |

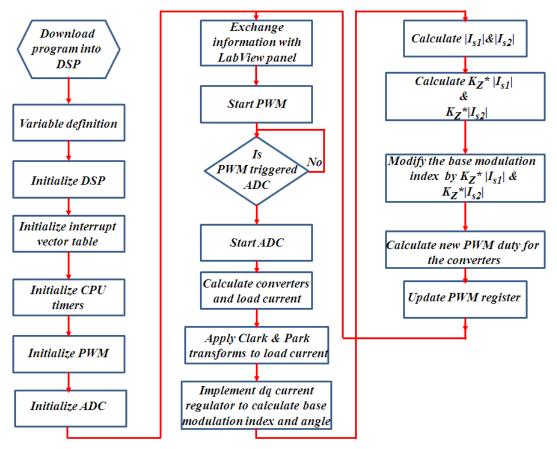

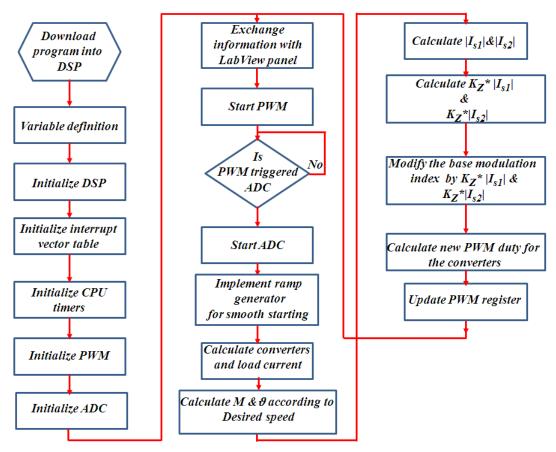

| 5.  | 3 Imp     | plementation of control algorithms                                      | 124 |

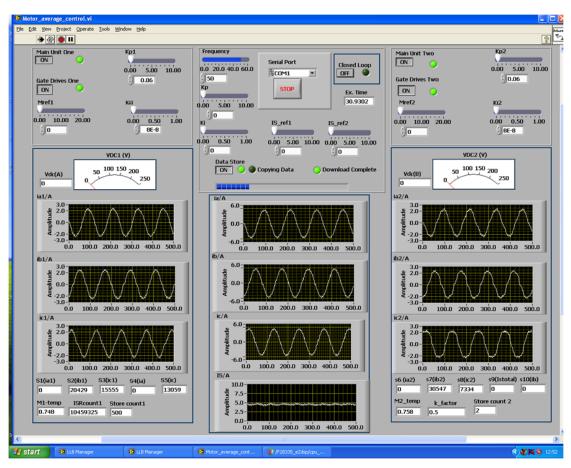

|     | 5.3.1     | LabView <sup>TM</sup> environment                                       | 125 |

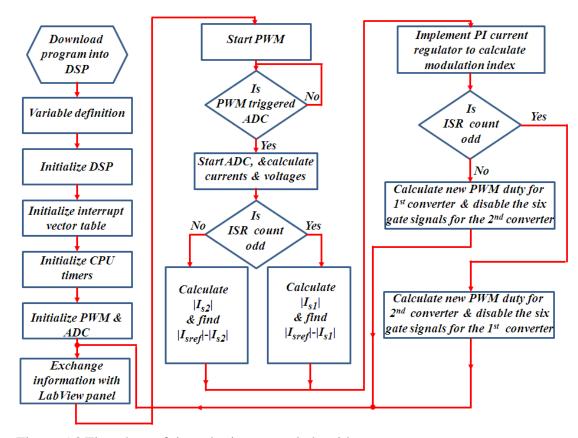

|     | 5.3.2     | Algorithm of time sharing control scheme                                | 126 |

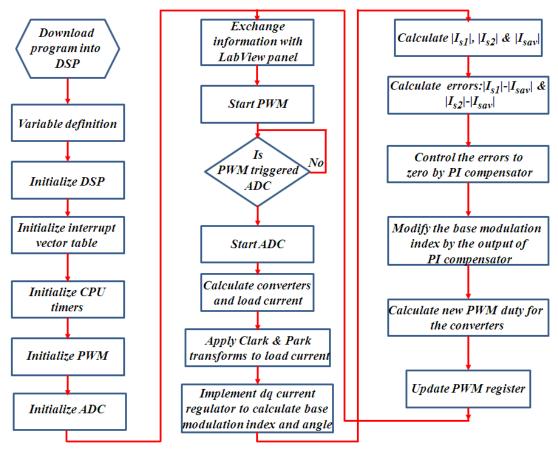

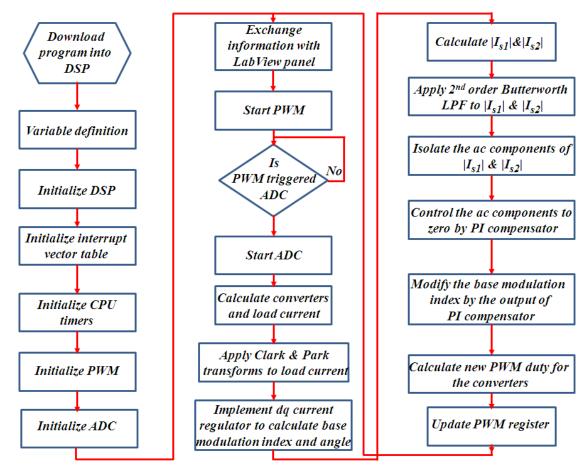

|     | 5.3.3     | Algorithm of average current sharing control scheme in a current        |     |

|     | controll  | ler application1                                                        | 128 |

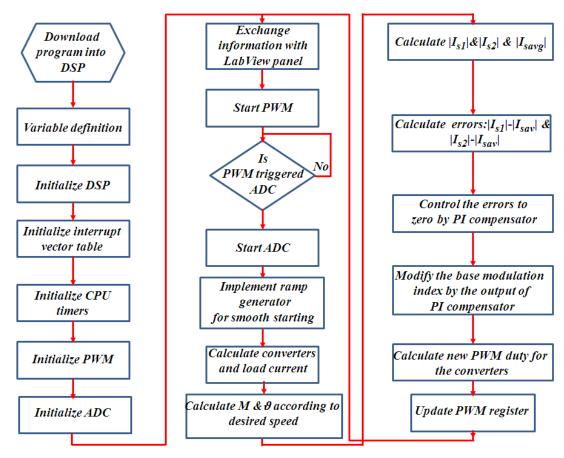

|     | 5.3.4     | Algorithm of open loop V/f control for three-phase induction motor      |     |

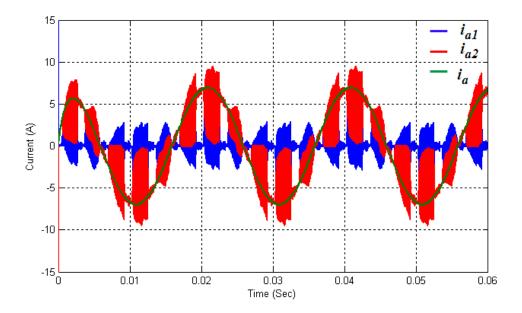

|     | supplied  | d from parallel converters based on the average current sharing control |     |

|     | scheme    |                                                                         | 129 |

|   | 5.    | 3.5     | Algorithm for independent current sharing control scheme in a current  |     |

|---|-------|---------|------------------------------------------------------------------------|-----|

|   | co    | ntroll  | ler application                                                        | 130 |

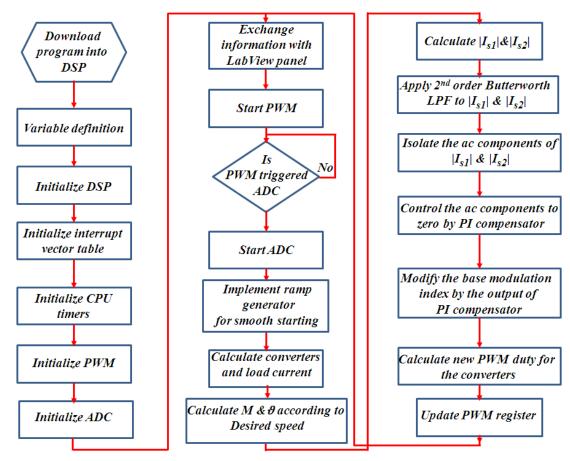

|   | 5     | 3.6     | Algorithm for open loop V/f control for three-phase induction motor    |     |

|   | su    | pplie   | d from parallel converters based on independent current sharing contro | l   |

|   | SC    | heme    |                                                                        | 131 |

|   | 5.4   | Me      | asurement equipment                                                    | 132 |

|   | 5.5   | Sur     | nmary of the test rig system development                               | 132 |

| C | hapte | er 6. l | Experimental Verification of Control Algorithms                        | 134 |

|   | 6.1   | Tes     | sting of PWM Strategies                                                | 134 |

|   | 6.2   | Tes     | sting of Time Sharing Approach                                         | 136 |

|   | 6.3   | Tes     | sting Average Current Sharing Control Scheme                           | 138 |

|   | 6.    | 3.1     | Current controller for the three-phase RL load                         | 138 |

|   | 6.    | 3.2     | Open loop V/f control for a three-phase induction motor                | 144 |

|   | 6.4   | Tes     | sting Independent Current Sharing Control Scheme                       | 148 |

|   | 6.    | 4.1     | Current controller for the three-phase RL load                         | 148 |

|   | 6.    | 4.2     | Open loop V/f control for the three-phase induction motor              | 151 |

|   | 6.5   | Tes     | sting of Impedance Emulation Current Sharing Control Scheme            | 153 |

|   | 6.    | 5.1     | Current controller for the three-phase RL load                         | 153 |

|   | 6.    | 5.2     | Open loop V/f control for the three-phase induction motor              | 155 |

|   | 6.6   | Inte    | erleaving Impact on System Performance                                 | 157 |

|   | 6.    | 6.1     | Combined current                                                       | 158 |

|   | 6.    | 6.2     | Inter-module circulating current                                       | 160 |

|   | 6.    | 6.3     | Common-mode voltage                                                    | 161 |

|   | 6.7   | Sur     | nmary                                                                  | 163 |

| C | hapte | er 7. ( | Conclusions and Future Work                                            | 167 |

|   | 7.1   | Coı     | nclusions                                                              | 167 |

|   | 7.2   | Fut     | ure work                                                               | 169 |

| R | efere | nces    |                                                                        | 170 |

| Append      | dix A                                                                   | 181      |

|-------------|-------------------------------------------------------------------------|----------|

| A.1         | Parallel Converters Wiring Diagrams                                     | 181      |

| A.2         | Algorithm of Impedance Emulation Current Sharing Control                | 185      |

| Append      | dix B. Simulation Results                                               | 187      |

| B.1         | Interleaving Impacts on System Performance When DPWM2 is Ado            | pted 187 |

| В           | 1.1 Combined current                                                    | 187      |

| В           | 1.2 Circulating current                                                 | 189      |

| Figur       | re B.5 Circulating current spectra for interleaved converters using DPW | VM2 at   |

| M=0.        | .9                                                                      | 189      |

| В           | 1.3 Common mode voltage                                                 | 190      |

| Append      | dix C. SVPWM Strategy Experimental Results                              | 192      |

| C.1         | Testing Average Current Sharing Control                                 | 192      |

| C.1.1       | Current controller for three-phase RL load                              | 192      |

| <i>C.</i> . | 1.2 Open loop V/f control for a three-phase induction motor             | 195      |

| C.2         | Testing Independent Current Sharing Control                             | 197      |

| C.2         | 2.1 Current controller for a three-phase RL load                        | 197      |

| C.3         | Testing Impedance Current Sharing Control                               | 199      |

| C           | 3.1 Current controller for a three-phase RL load                        | 199      |

| C.4         | Interleaving Impacts on System Performance                              | 200      |

| C.4         | 4.1 Combined current                                                    | 200      |

| C.4         | 4.2 Inter-module circulating current                                    | 201      |

| C.4         | 4.3 Common-mode voltage                                                 | 202      |

| Append      | dix D. DPWM2 Strategy Experimental Results                              | 204      |

| D.1         | Average Current Sharing Control Results                                 | 204      |

| <i>D</i>    | 1.1 Current controller for a three-phase RL load                        | 204      |

| D.2         | Independent Current Sharing Control Results                             | 207      |

| D           | 2.1 Current controller for a three-phase RL load                        | 207      |

| D.3         | Interleaving Impacts on System Performance                              | 208      |

| D.3.1 | Combined current                 | 208 |

|-------|----------------------------------|-----|

| D.3.2 | Inter-module circulating current | 210 |

| D.3.3 | Common-mode voltage              | 212 |

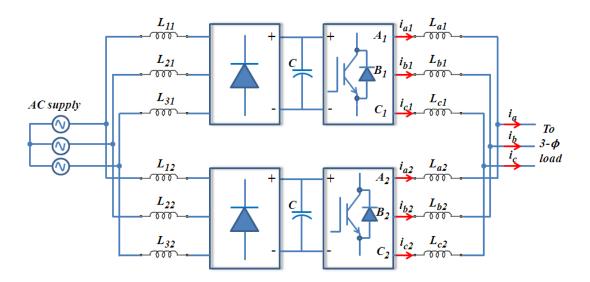

| Figure 1. 1 Parallel AC/DC/AC converters with a separate non-isolated DC link         | 2                  |

|---------------------------------------------------------------------------------------|--------------------|

| Figure 2.1 Three-phase voltage source inverter topology.                              | 5                  |

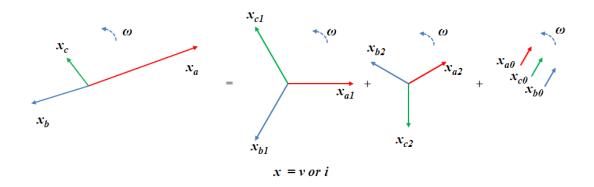

| Figure 2.2 Three-phase voltage source inverter topology                               | 6                  |

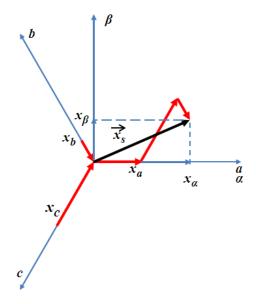

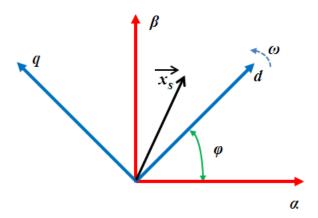

| Figure 2.3 Space vector in $\alpha\beta$ plane.                                       | 7                  |

| Figure 2.4 dq rotating frame of reference.                                            | 8                  |

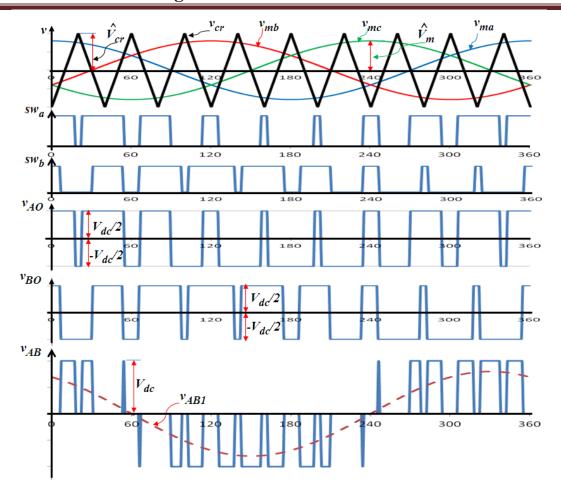

| Figure 2.5 Sinusoidal pulse-width modulation (SPWM)                                   | 11                 |

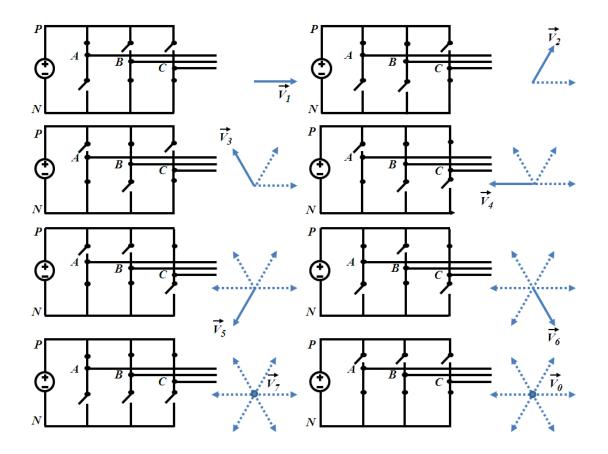

| Figure 2.6 Eight possible phase leg switch combinations for VSI.                      | 14                 |

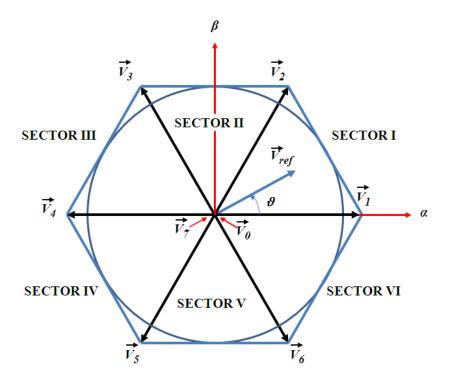

| Figure 2.7 Possible space vectors.                                                    | 16                 |

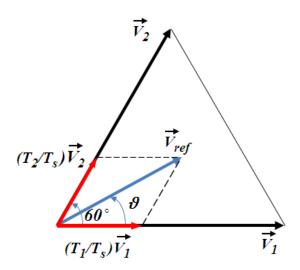

| Figure 2.8 Creation of the reference voltage vector in sector I                       | 16                 |

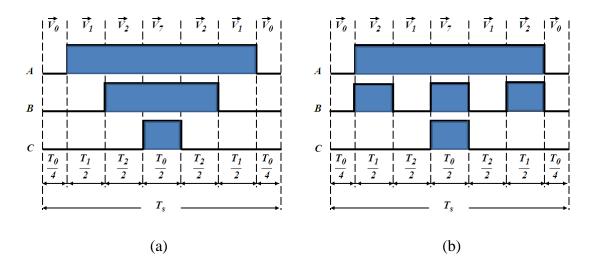

| Figure 2.9 Seven-segment switching sequence for reference voltage in sector I:        | 19                 |

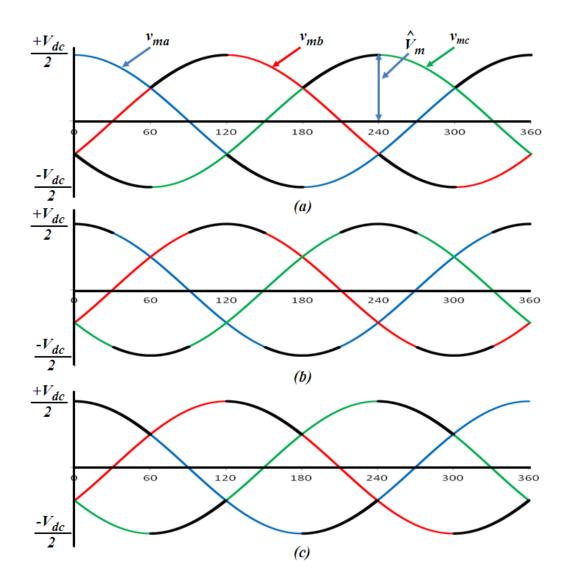

| Figure 2.10 Non-switching periods for discontinuous PWM: (a) DPWM0, (b) DPW           | WM1,               |

| (c) DPWM2                                                                             | 21                 |

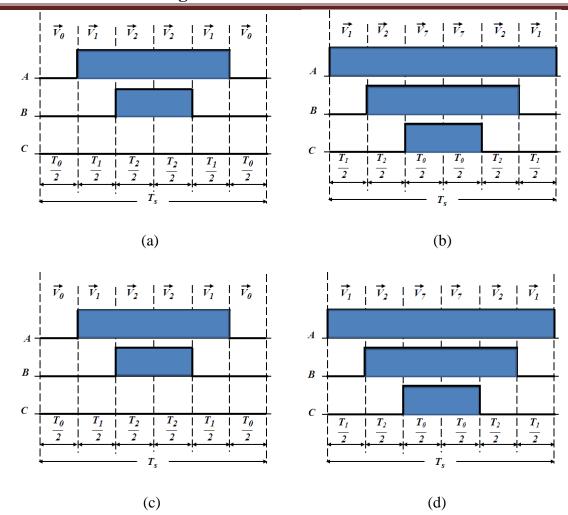

| Figure 2.11 Switching sequence for reference voltage in sector I: (a) DPWM0.          |                    |

| (b)Leading $30^{\circ}$ for DPWM1 (c) Trailing $30^{\circ}$ for DPWM1 (d)DPWM2        | 22                 |

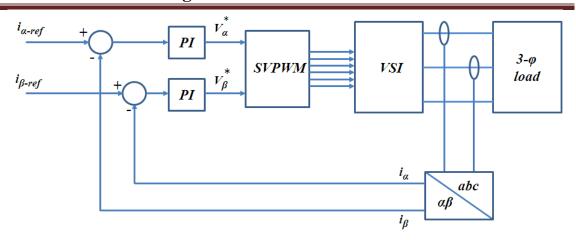

| Figure 2.12 A stationary frame PI current regulator                                   | 25                 |

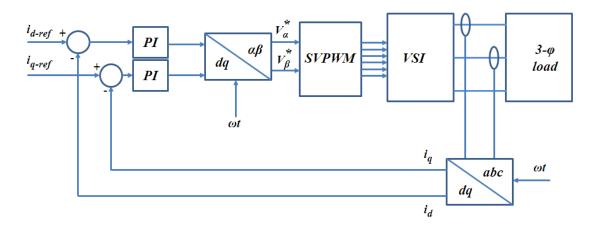

| Figure 2.13 A synchronous frame PI dq current regulator                               | 25                 |

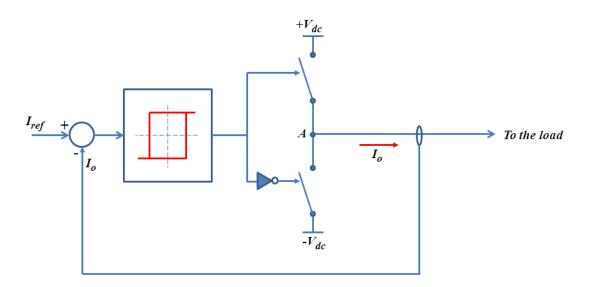

| Figure 2.14 Hysteresis current control (phase A)                                      | 26                 |

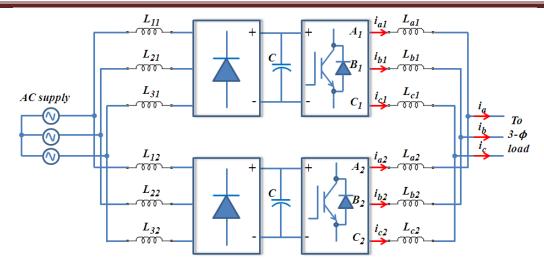

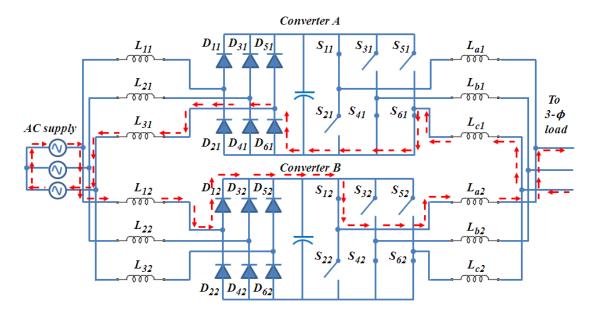

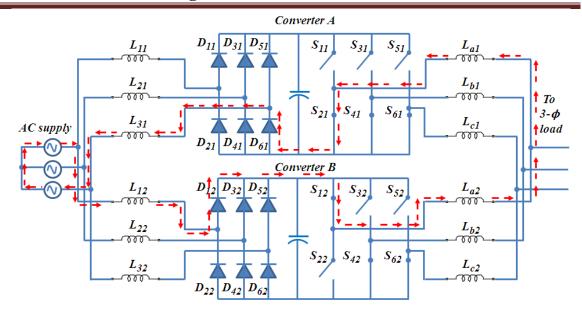

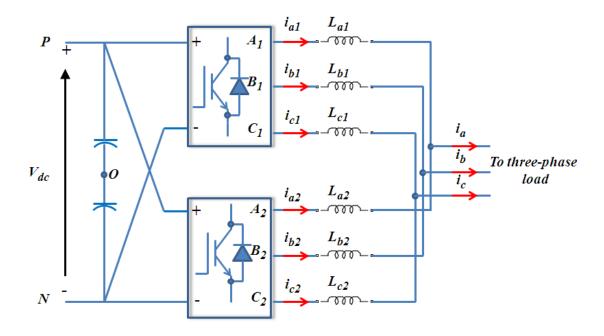

| Figure 2.15 Directly paralleled AC/DC/AC converters.                                  | 29                 |

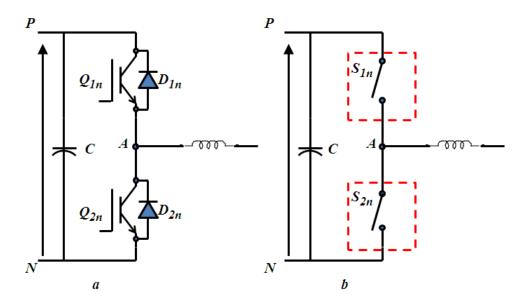

| Figure 2.16 Phase leg of an inverter: (a) Actual switching device (b) Single-pole s   | ingle-             |

| throw representation                                                                  | 29                 |

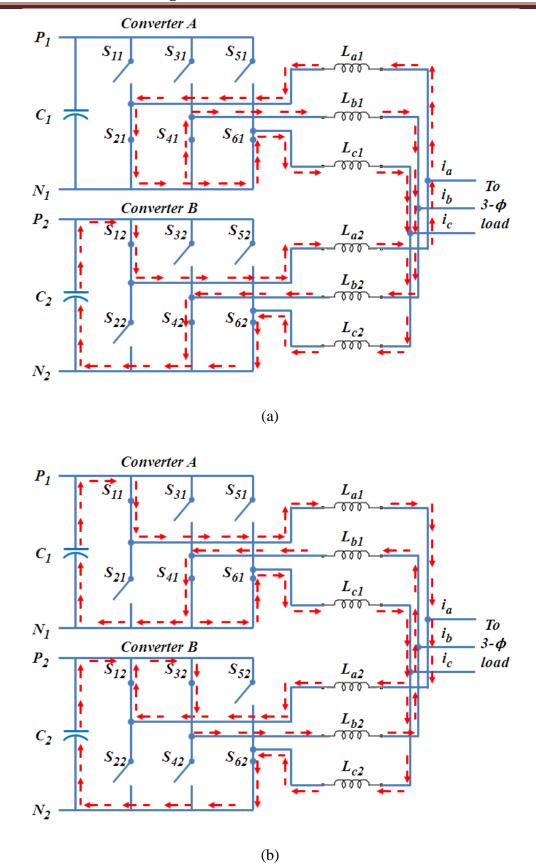

| Figure 2.17 Cross current paths (a) The 1st converter in zero switching state and the | ne 2 <sup>nd</sup> |

| in active switching state (b)The two converters are in active switching states        | 30                 |

| Figure 2.18 Intrinsic circulating current path when the two converters have the same  | ne                 |

| switching states                                                                      | 31                 |

| Figure 2.19 Circulating current path when the 1st converter in zero switching state   | and                |

| the 2 <sup>nd</sup> in active switching state                                         | 32                 |

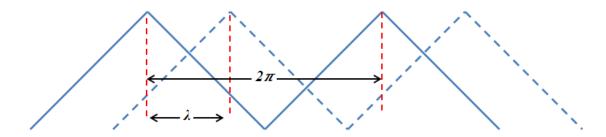

| Figure 2.20 Definition of interleaving angle ( $\lambda$ )                            | 32                 |

| Figure 2.21 Parallel connected VSCs                                                   | 33                 |

| Figure 3.1 Directly paralleled AC/DC/AC converters                                    | 39                 |

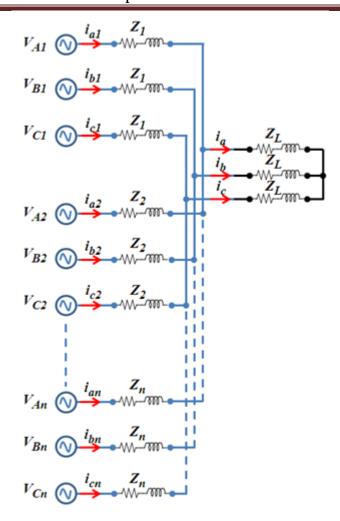

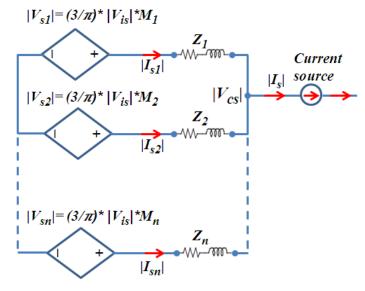

| Figure 3.2 Equivalent circuit for n-three-phase inverters connected in parallel       | 42                 |

| Figure 3.3 Equivalent circuit for n-three-phase inverters connected in parallel using |      |

|---------------------------------------------------------------------------------------|------|

| space vector magnitude representation                                                 | .42  |

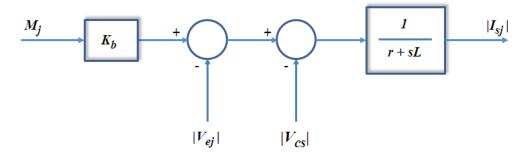

| Figure 3.4 Block diagram of three-phase inverter using space vector magnitude         |      |

| representation                                                                        | .43  |

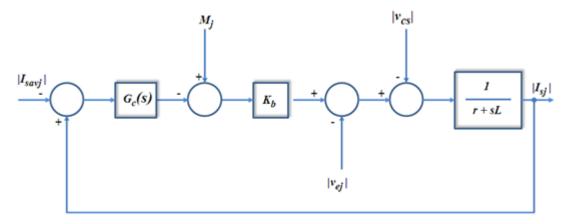

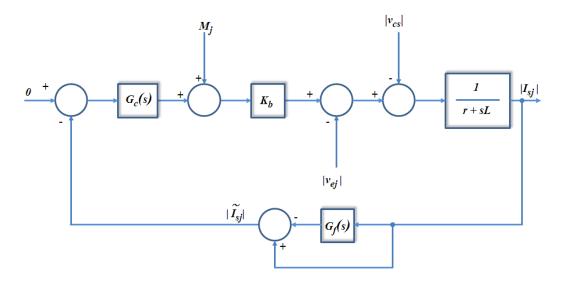

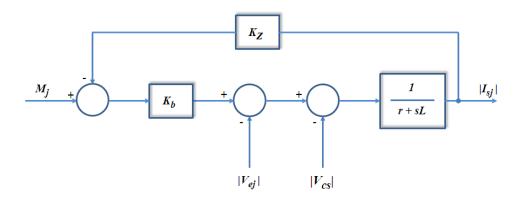

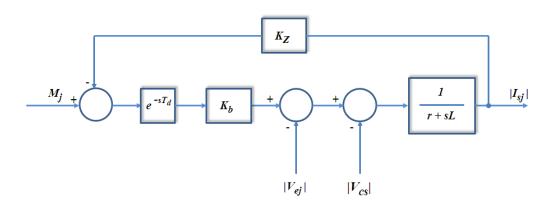

| Figure 3.5 Block diagram of three-phase inverter with average current control         | .45  |

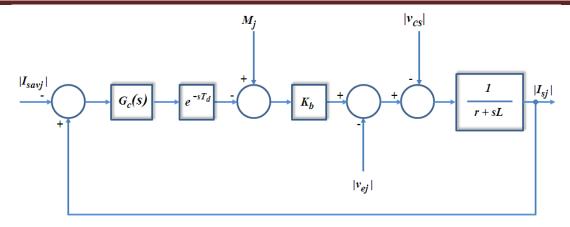

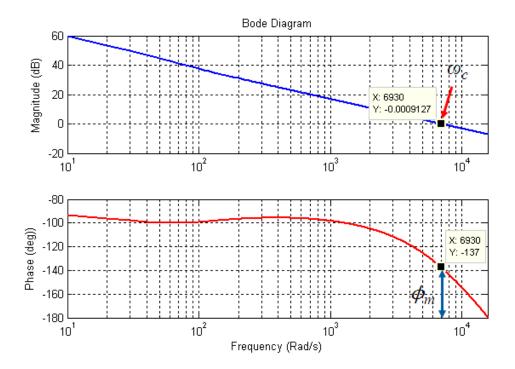

| Figure 3.6 Control diagram of three-phase inverter with delay effect                  | .47  |

| Figure 3.7 Magnitude and phase Bode plot of open loop forward path considering del    | lay  |

| effect Kp=0.06, Ki=4.2                                                                | .49  |

| Figure 3.8 Block diagram of three-phase inverter with independent current sharing     |      |

| control                                                                               | .50  |

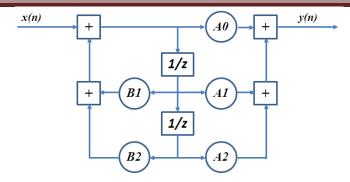

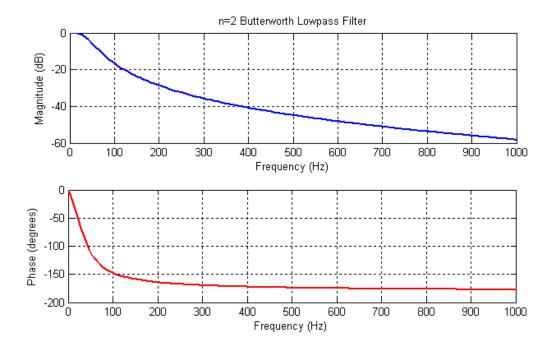

| Figure 3.9 Second order Butterworth LPF structure                                     | .53  |

| Figure 3.10 Second order Butterworth LPF frequency response                           | .53  |

| Figure 3.11 Block diagram of three-phase inverter with impedance emulation current    |      |

| sharing control                                                                       | .54  |

| Figure 3.12 Three-phase voltage source converter model considering delay effect       | .54  |

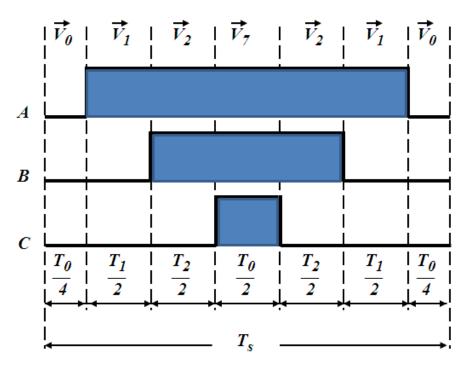

| Figure 4.1 Seven segments switching sequence for reference voltage in sector I        | .58  |

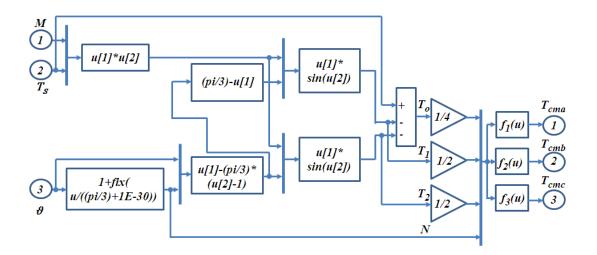

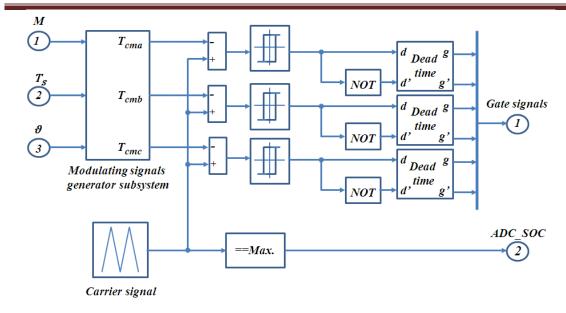

| Figure 4.2 Modulating signals generator                                               | .59  |

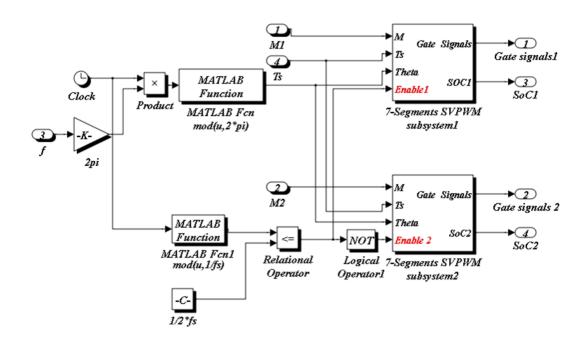

| Figure 4.3 Seven segment SVPWM SIMULINK model                                         | .60  |

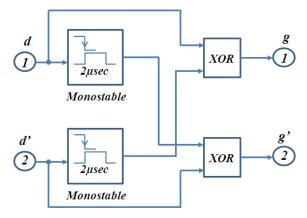

| Figure 4.4 Dead time SIMULINK model                                                   | .60  |

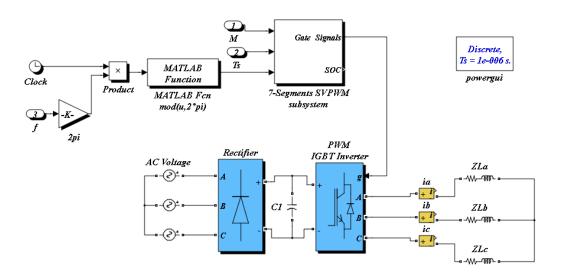

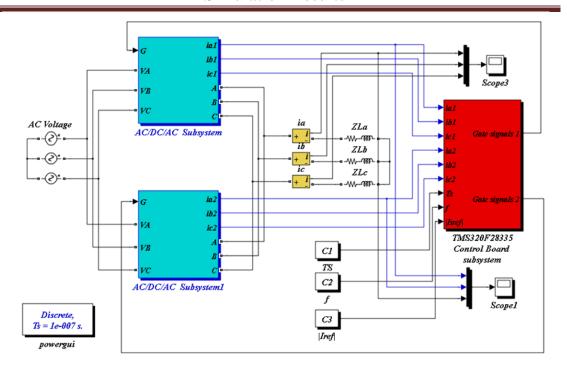

| Figure 4.5 SIMULINK model for three-phase AC/DC/AC converter                          | .61  |

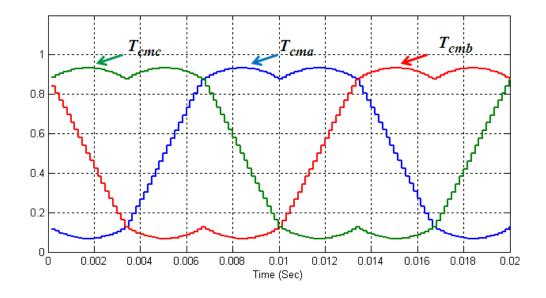

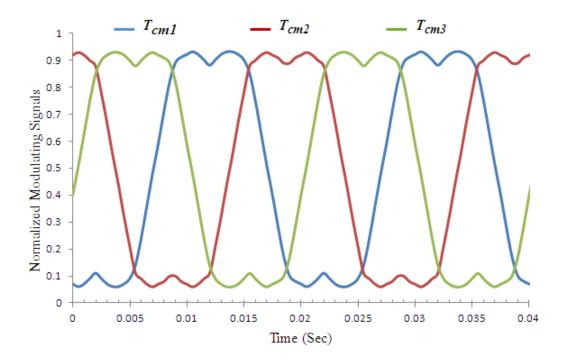

| Figure 4.6 Modulating signals for SVPWM strategy                                      | .62  |

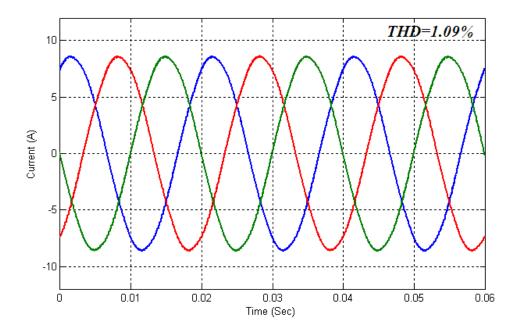

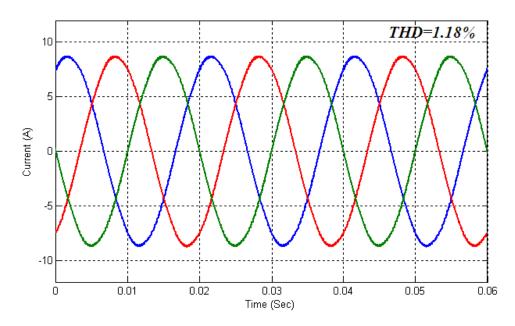

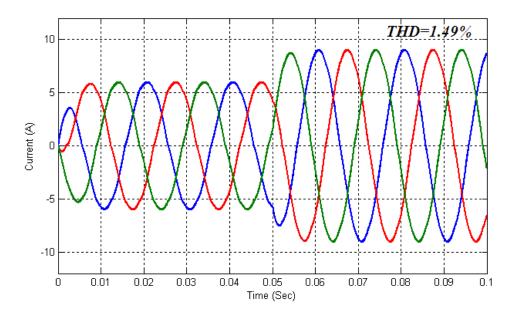

| Figure 4.7 Three-phase load current waveforms for SVPWM strategy                      | .62  |

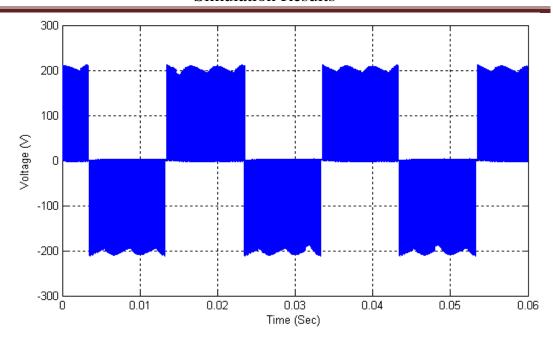

| Figure 4.8 Load line voltage based on SVPWM strategy                                  | .63  |

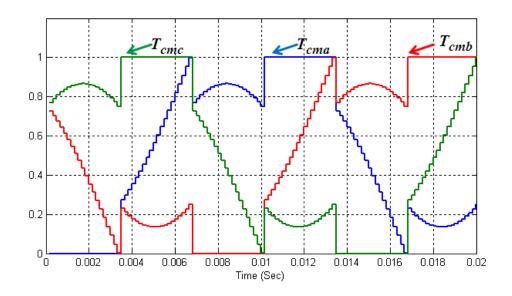

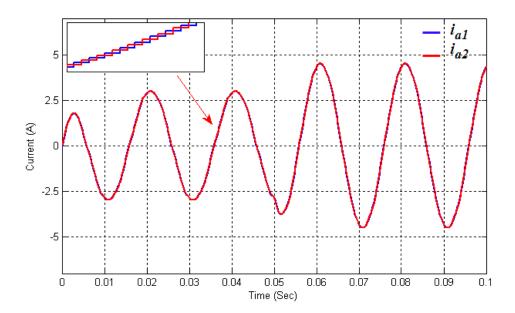

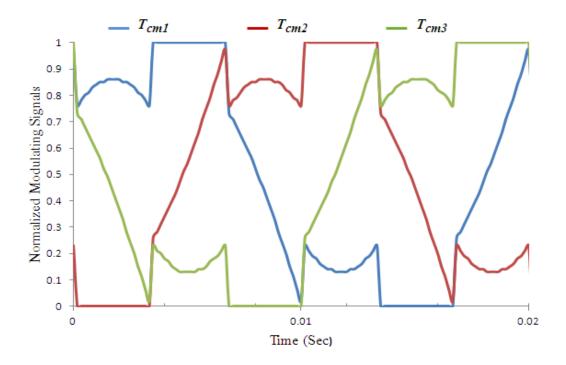

| Figure 4.9 DPWM2 normalised modulating signals                                        | .64  |

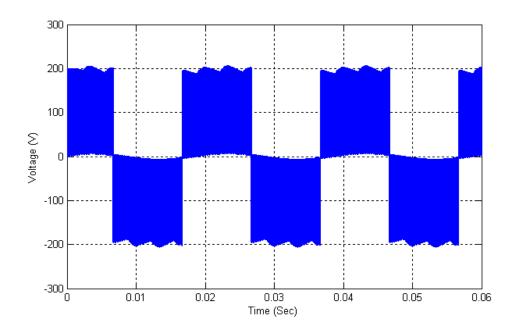

| Figure 4.10 Load line voltage based on DPWM2 strategy                                 | .64  |

| Figure 4.11 Three-phase load current waveforms with DPWM2 strategy                    | .65  |

| Figure 4.12 Load current and collector to emitter voltage waveforms with DPWM2        |      |

| strategy                                                                              | .65  |

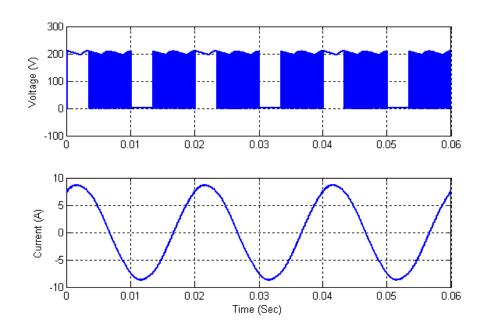

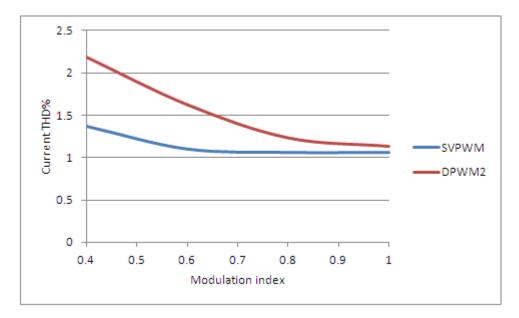

| Figure 4.13 Current THD for SVPWM and DPWM2 strategies.                               | .66  |

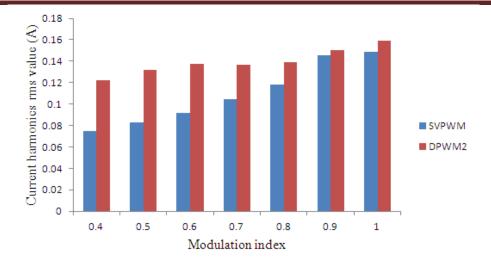

| Figure 4.14 RMS value of harmonic current components for SVPWM and DPWM2              |      |

| strategies                                                                            | .67  |

| Figure 4.15 SIMULINK model of parallel connected three-phase AC/DC/AC convert         | ters |

| controlled by time sharing approach                                                   | .69  |

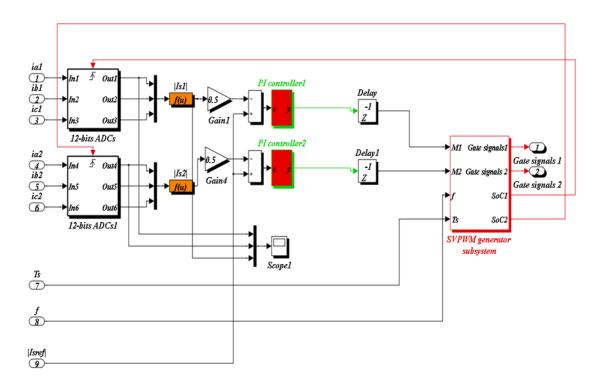

| Figure 4.16 SIMULINK model of a control board subsystem                               | .69  |

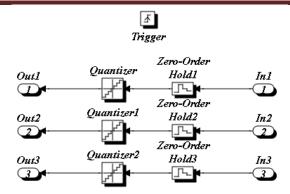

| Figure 4.17 ADC SIMULINK model                                                          |

|-----------------------------------------------------------------------------------------|

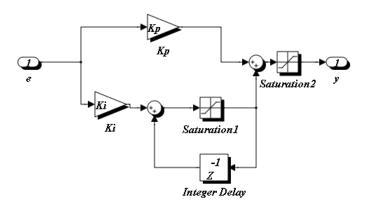

| Figure 4.18 Discrete PI compensator SIMULINK model70                                    |

| Figure 4.19 SIMULINK of SVPWM generator subsystem                                       |

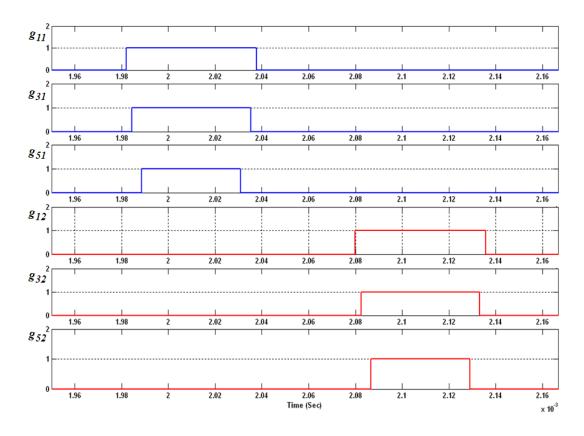

| Figure 4.20 IGBTs gate signals when time sharing is adopted72                           |

| Figure 4.21 Three-phase load current during transient and steady states                 |

| Figure 4.22 Converter current with identical parameters using time sharing approach .73 |

| Figure 4.23 Converter current space vector magnitude for identical parameters using     |

| time sharing approach74                                                                 |

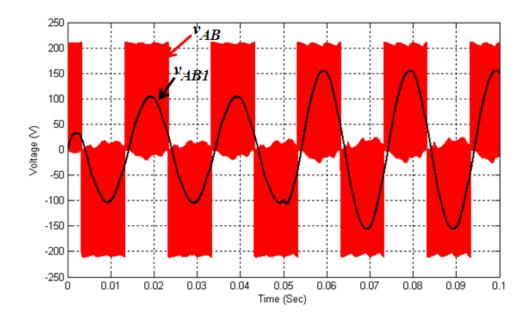

| Figure 4.24 Load voltage and its fundamental component using time sharing approach      |

| 74                                                                                      |

| Figure 4.25 Converter currents with different parameters using time sharing approach 75 |

| Figure 4.26 Converter current with the different dead time and physical parameters      |

| when time sharing is not adopted at M=0.65 for both converters76                        |

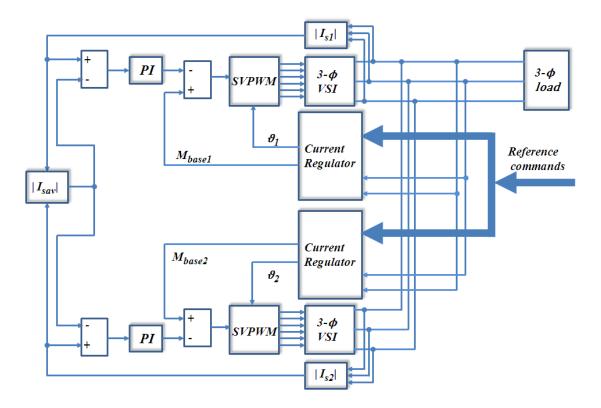

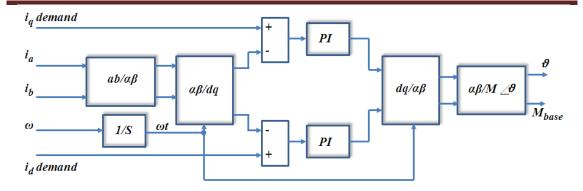

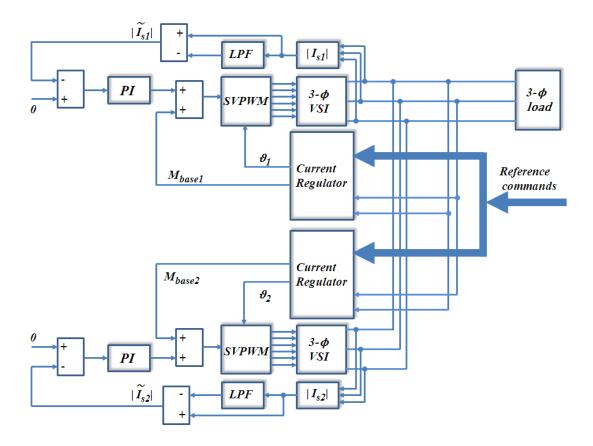

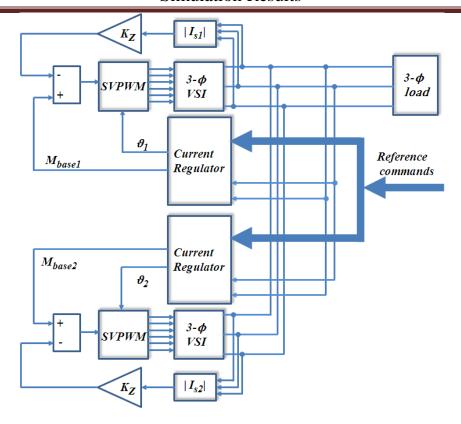

| Figure 4.27 Block diagram of parallel connected AC/DC/AC converter current              |

| controller based on average current sharing control                                     |

| Figure 4.28 Current regulator block diagram                                             |

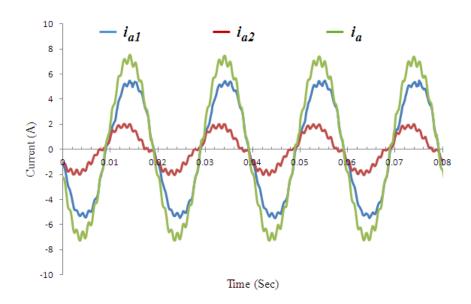

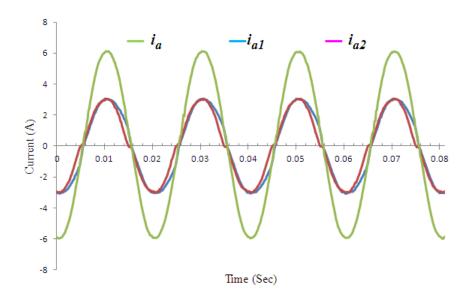

| Figure 4.29 Load and converters current waveforms without current sharing control 79    |

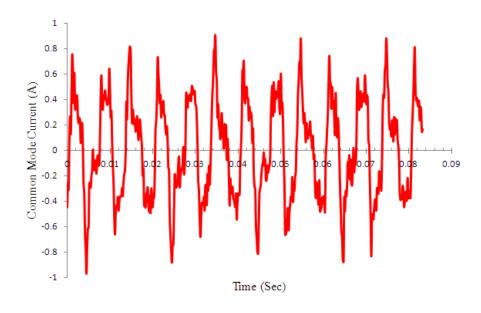

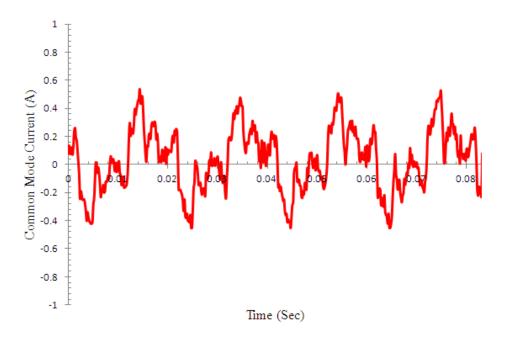

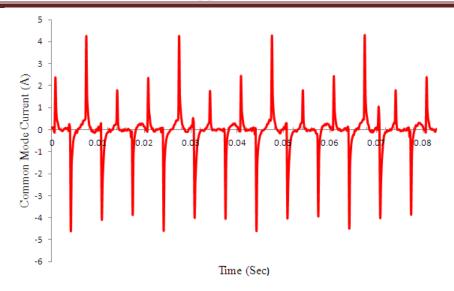

| Figure 4.30 Common mode circulating current waveform without current sharing            |

| control80                                                                               |

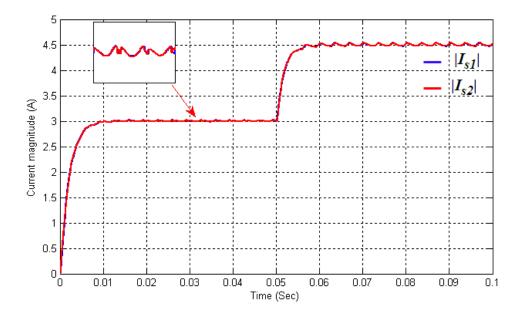

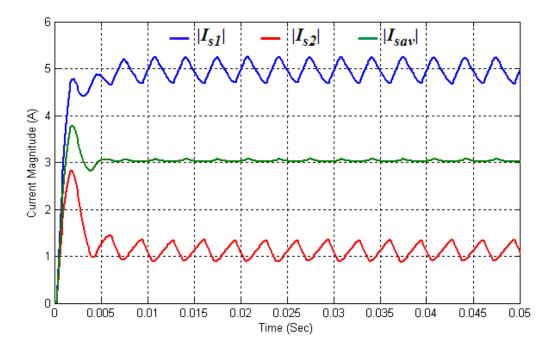

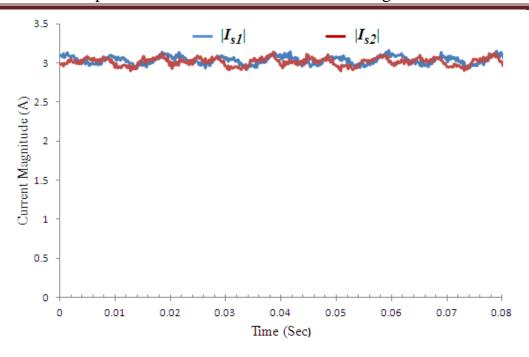

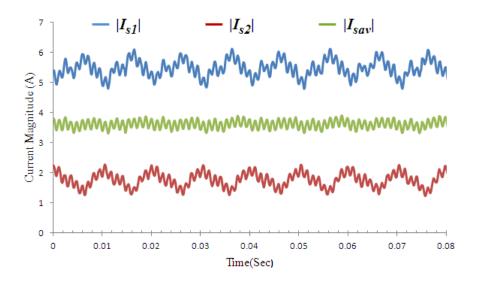

| Figure 4.31 Converter current space vector magnitude waveforms without current          |

| sharing control80                                                                       |

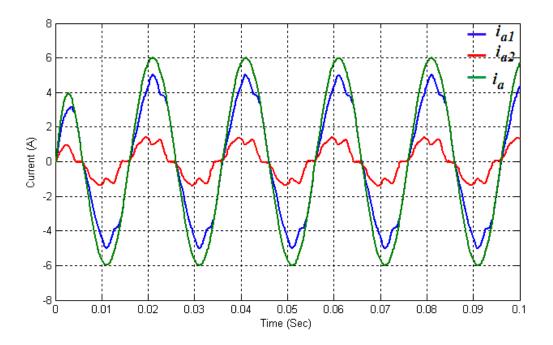

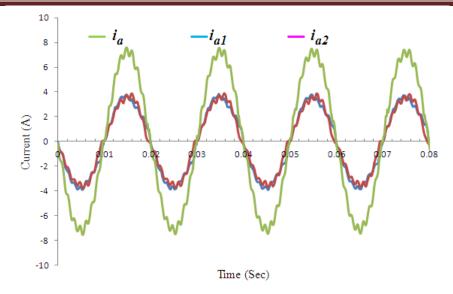

| Figure 4.32 Load and converter current waveforms with average current sharing control   |

| scheme81                                                                                |

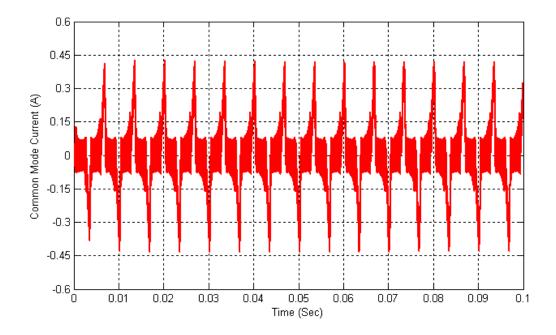

| Figure 4.33 Common mode circulating current waveform with average current sharing       |

| control scheme81                                                                        |

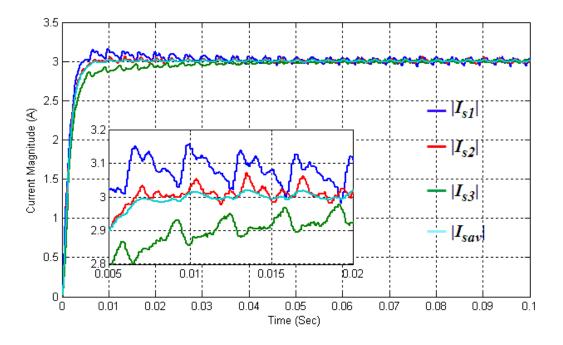

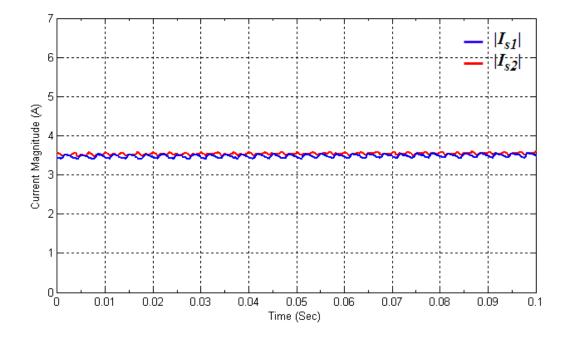

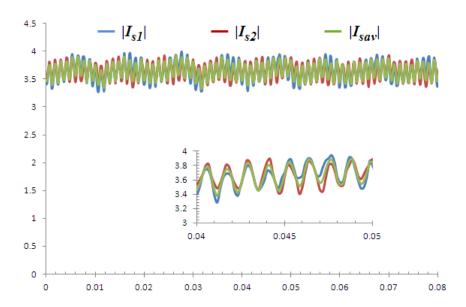

| Figure 4.34 Converter current space vector magnitude waveforms with average current     |

| sharing control scheme                                                                  |

| Figure 4.35 Converters and load current waveforms during step change in the desired     |

| current82                                                                               |

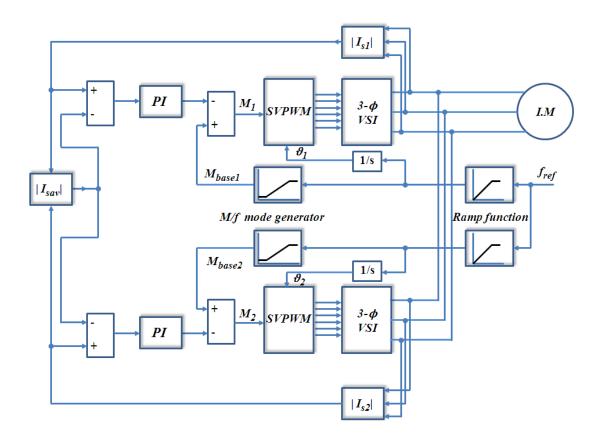

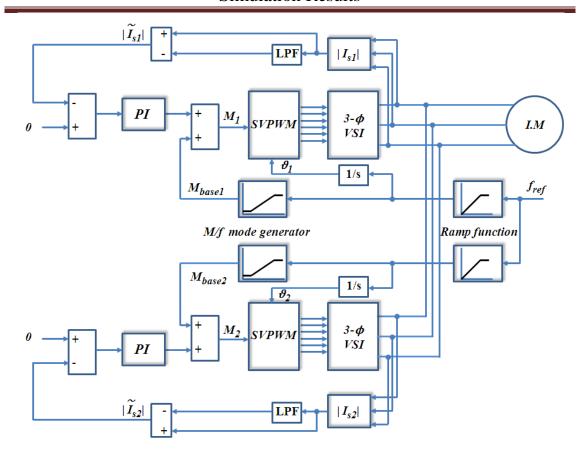

| Figure 4.36 Block diagram of open loop V/f for three-phase induction motor based on     |

| the average current sharing control scheme                                              |

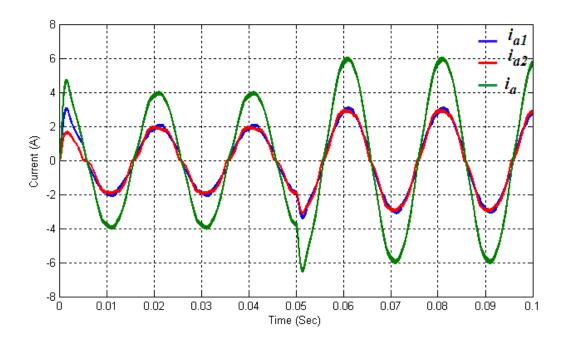

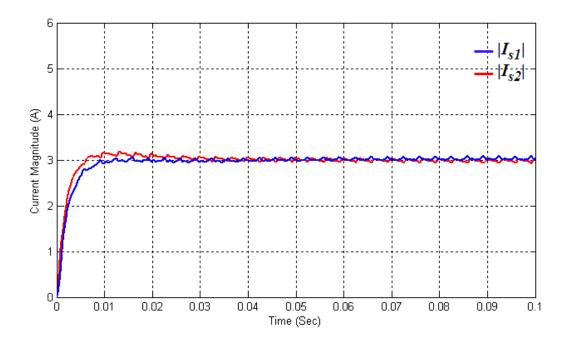

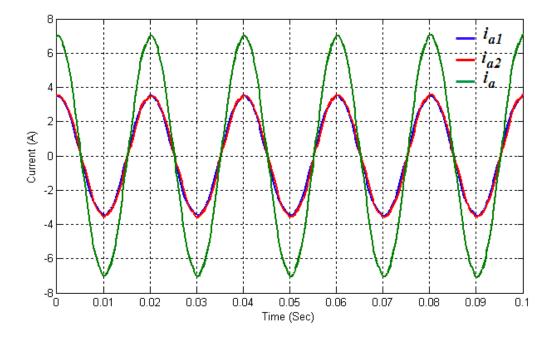

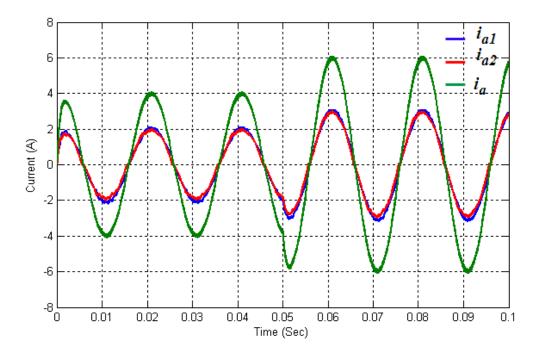

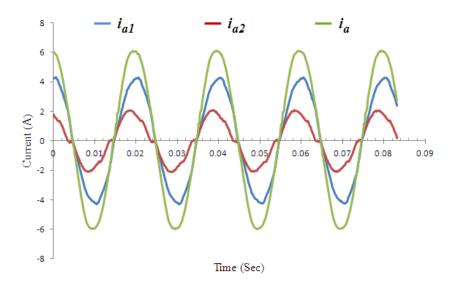

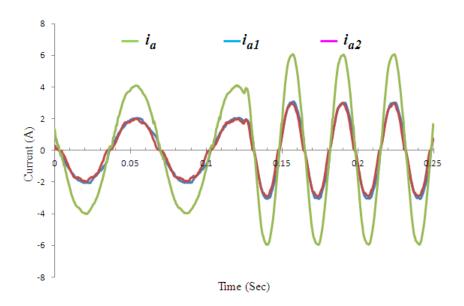

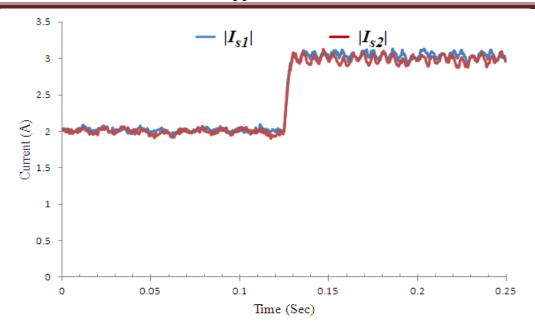

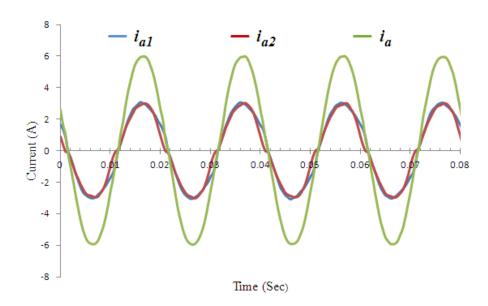

| Figure 4.37 Motor and converter current waveforms with average current sharing          |

| control method at 50Hz85                                                                |

| Figure 4.38 Three converter current waveforms without current sharing control86         |

| Figure 4.39 Three converters common mode current waveforms without current sharing      |

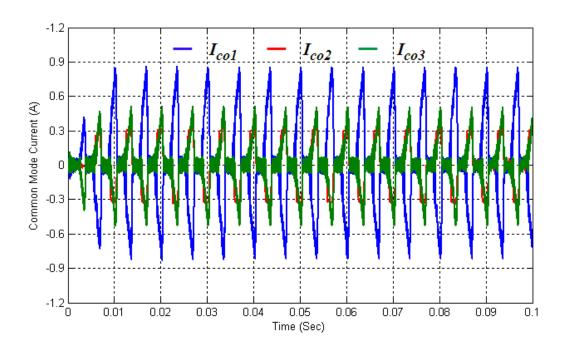

|-----------------------------------------------------------------------------------------|

| control86                                                                               |

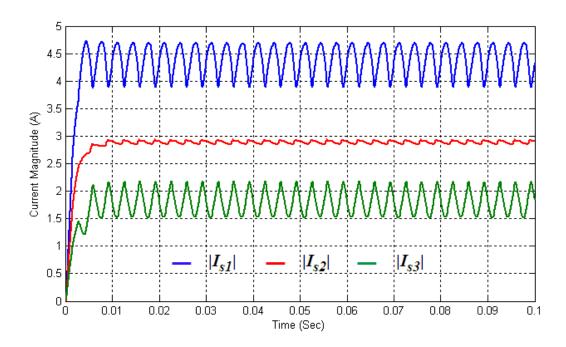

| Figure 4.40 Three converter current space vector magnitude waveforms without current    |

| sharing control                                                                         |

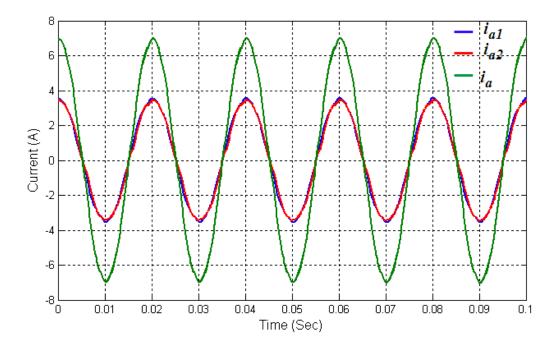

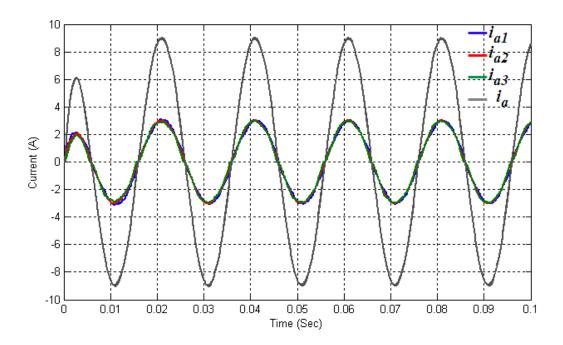

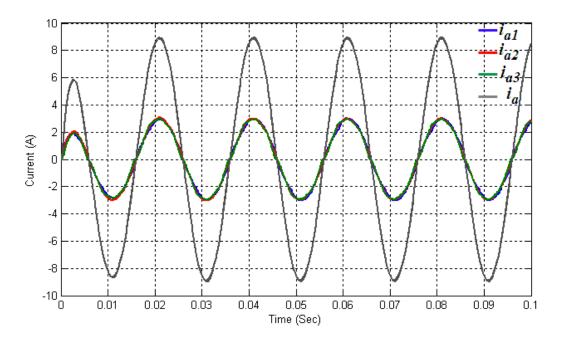

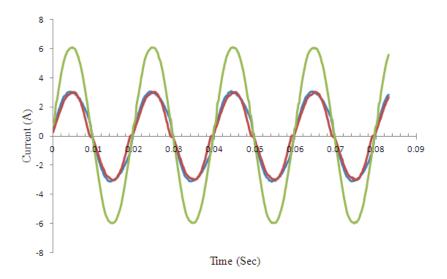

| Figure 4.41 Three converter current waveforms with average current sharing control87    |

| Figure 4.42 Three converter common mode current waveforms with average current          |

| sharing control                                                                         |

| Figure 4.43 Three converter current space vector magnitude waveforms with average       |

| current sharing control                                                                 |

| Figure 4.44 Block diagram of parallel connected AC/DC/AC converter current              |

| controller based on independent current sharing control90                               |

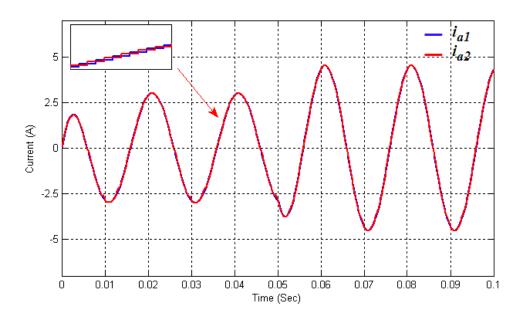

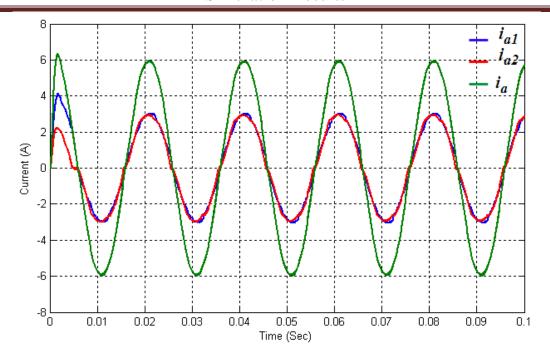

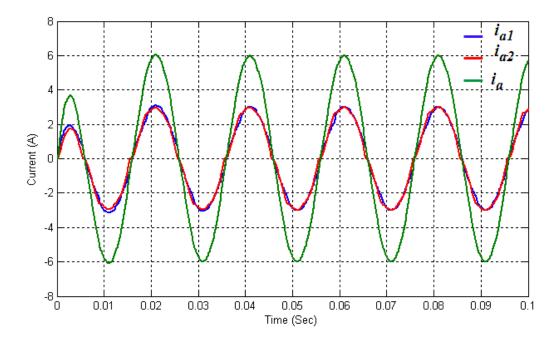

| Figure 4.45 Load and converter current waveforms with independent current sharing       |

| control method91                                                                        |

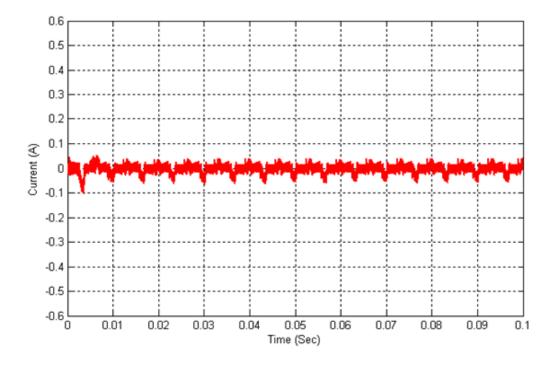

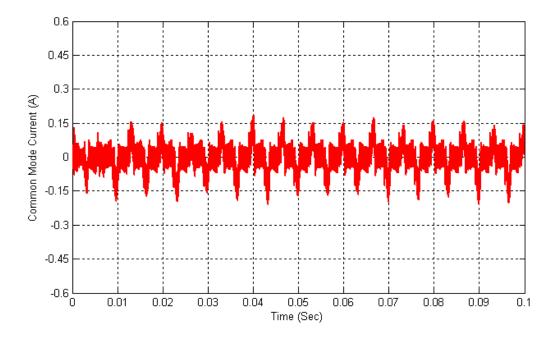

| Figure 4.46 Common mode circulating current waveform with independent current           |

| sharing control method                                                                  |

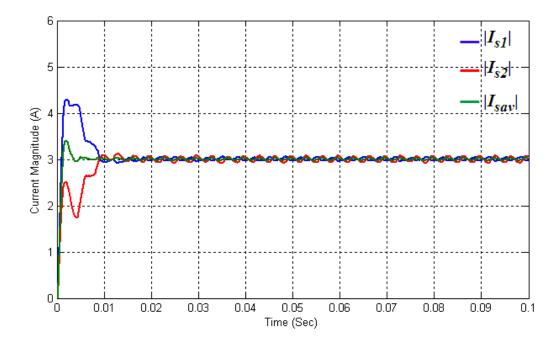

| Figure 4.47 Converter current space vector magnitude waveforms with independent         |

| current sharing control method                                                          |

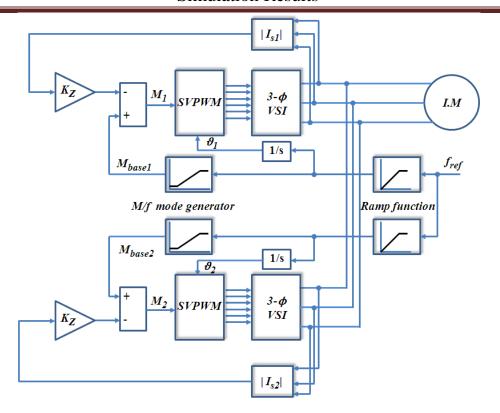

| Figure 4.48 Block diagram of open loop V/f for three-phase induction motor based on     |

| independent current sharing control method                                              |

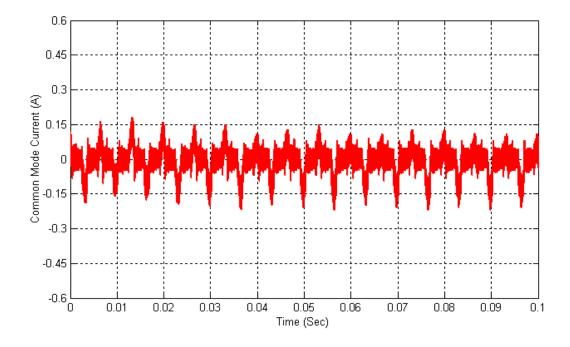

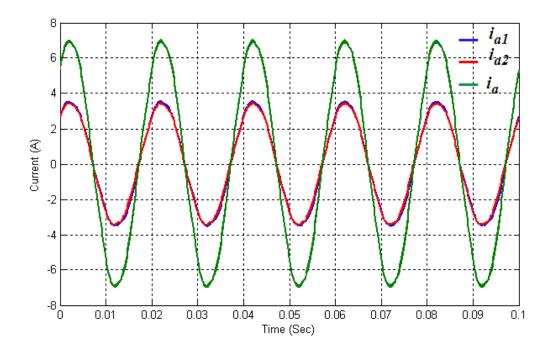

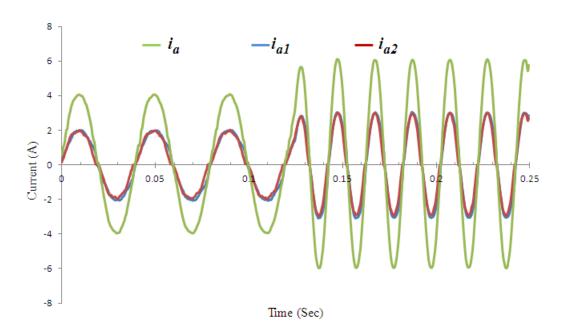

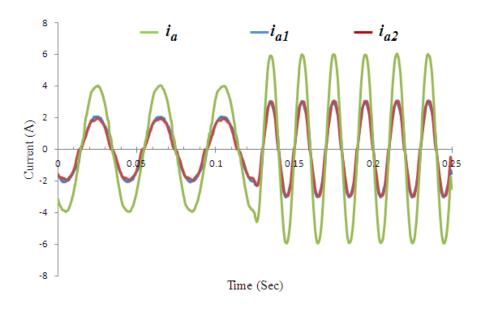

| Figure 4.49 Motor and converter current waveforms with independent current sharing      |

| control strategy94                                                                      |

| Figure 4.50 Common mode circulating current waveform with independent current           |

| sharing control strategy in open loop V/f control for three-phase induction motor94     |

| Figure 4.51 Converter current space vector magnitude waveforms for open loop V/f        |

| control for three-phase induction motor based on independent sharing control strategy95 |

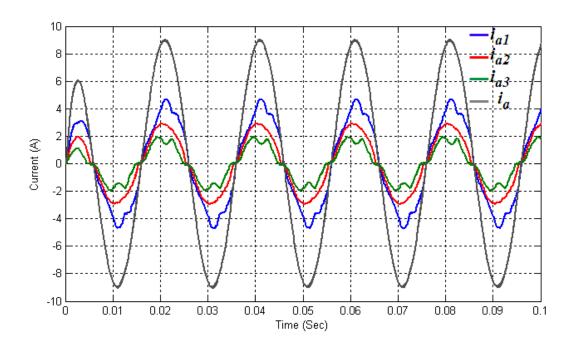

| Figure 4.52 Three converters current waveforms with independent current sharing         |

| control strategy96                                                                      |

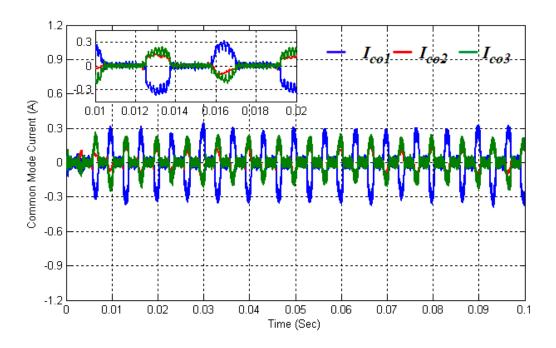

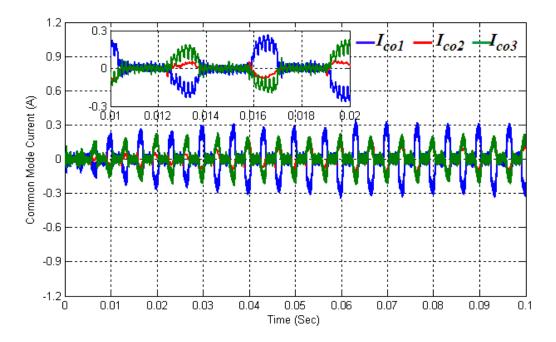

| Figure 4.53 Three converter common mode current waveforms with independent              |

| current sharing control strategy96                                                      |

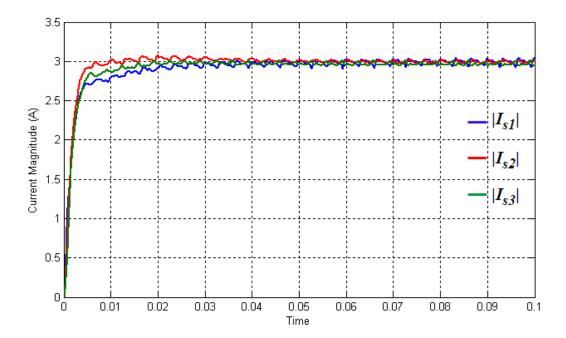

| Figure 4.54 Three converter current space vector magnitude waveforms with               |

| independent current sharing control strategy                                            |

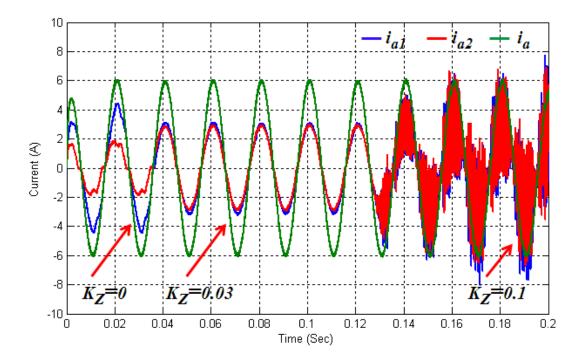

| Figure 4.55 Block diagram of impedance emulation current sharing control scheme99       |

| Figure 4.56 Load and converter current waveforms with different impedance emulation     |

| factor                                                                                  |

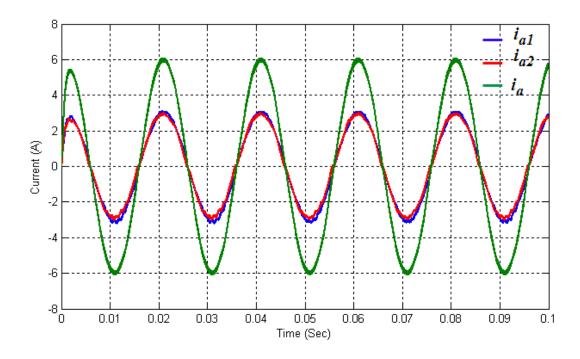

| Figure 4.57 Load and converter current waveforms with impedance emulation current   |

|-------------------------------------------------------------------------------------|

| sharing control strategy                                                            |

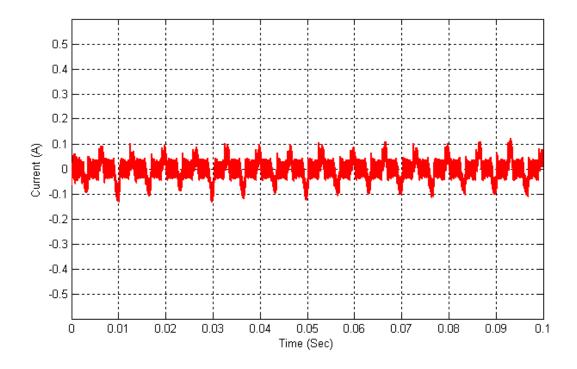

| Figure 4.58 Common mode circulating current with impedance emulation current        |

| sharing control strategy                                                            |

| Figure 4.59 Load and converter current waveforms with impedance emulation current   |

| sharing control strategy during transient condition                                 |

| Figure 4.60 Block diagram of an open loop V/f for three-phase induction motor based |

| on impedance emulation current sharing control strategy                             |

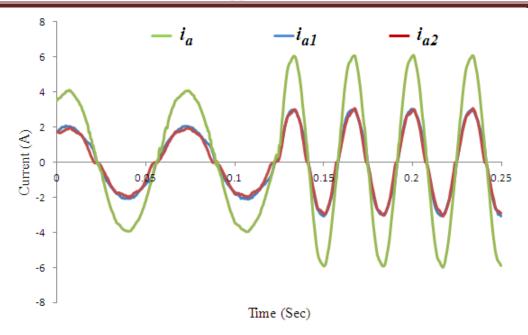

| Figure 4.61 Load and converter current waveforms with impedance emulation current   |

| sharing control strategy                                                            |

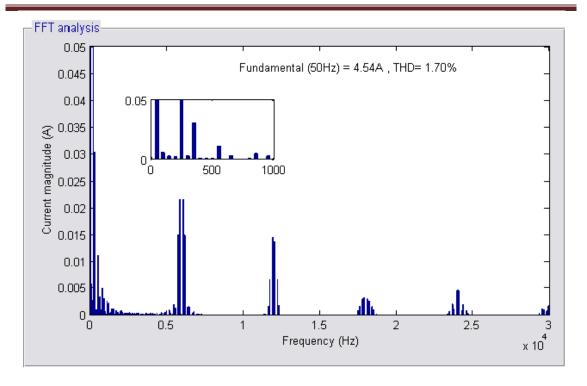

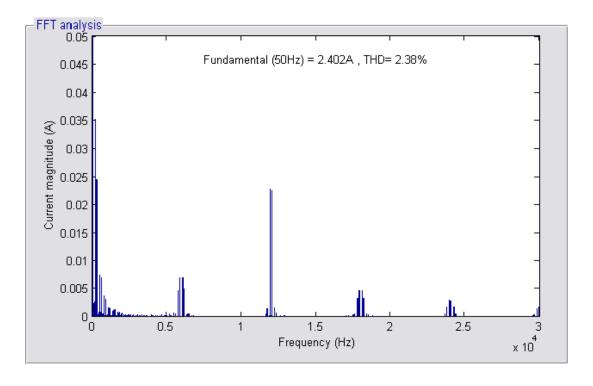

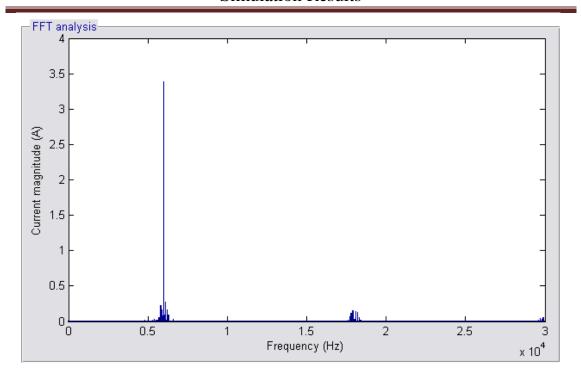

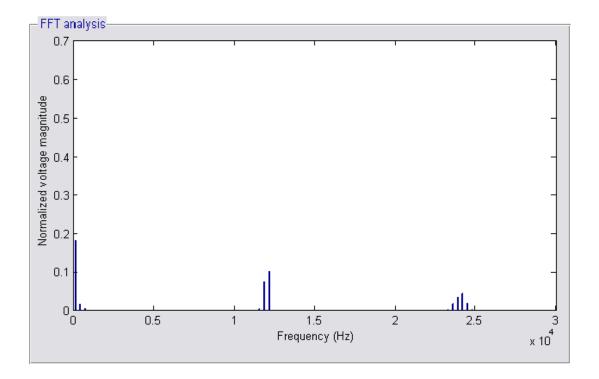

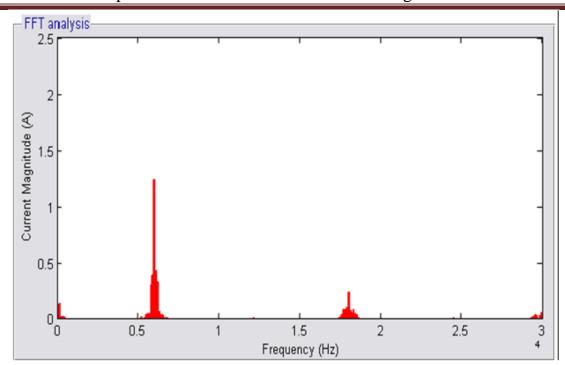

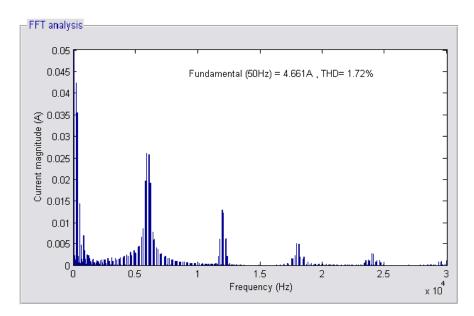

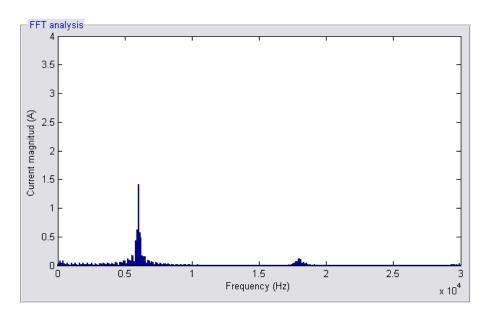

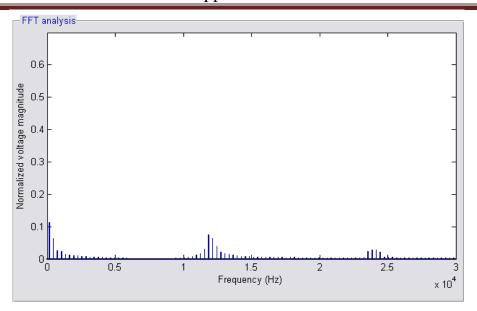

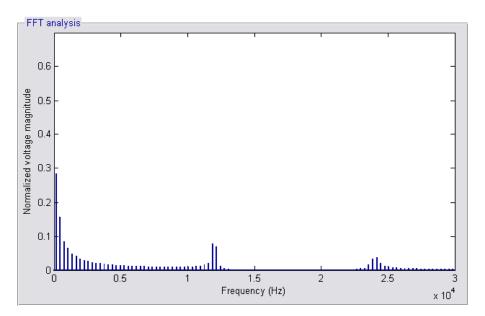

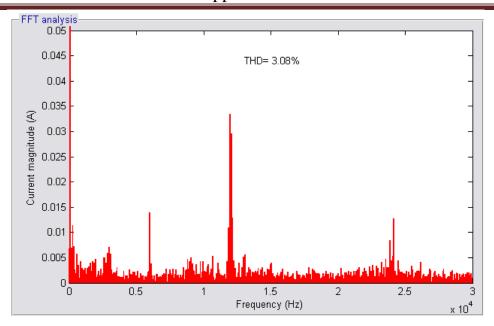

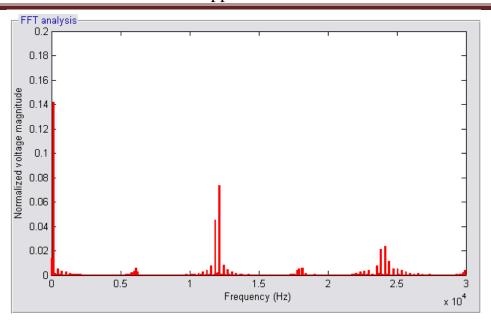

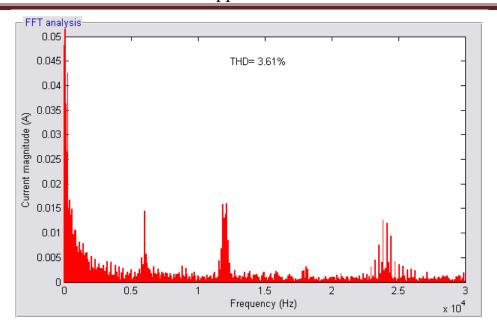

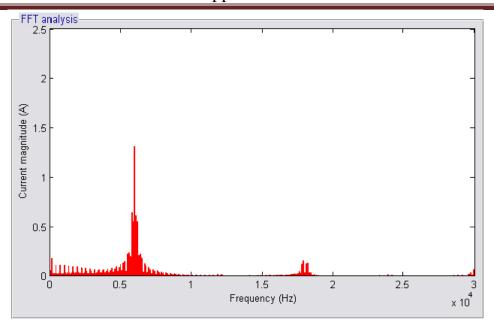

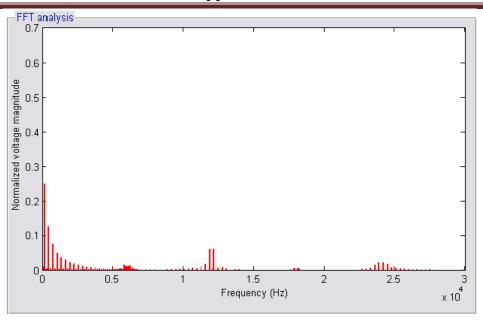

| Figure 4.62 Combined output current spectra for non-interleaved converters using    |

| SVPWM at M=0.9                                                                      |

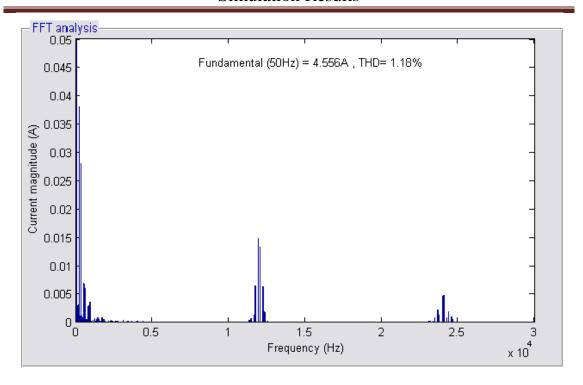

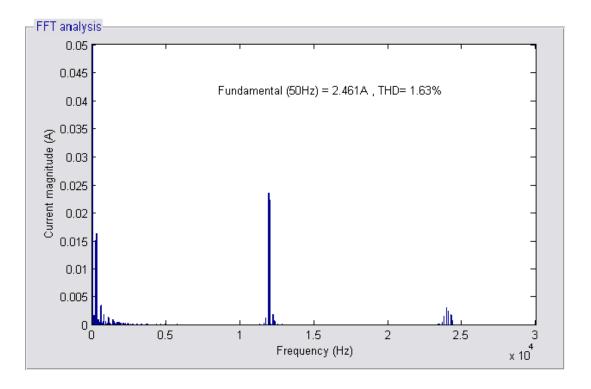

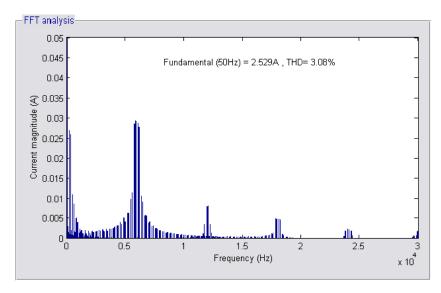

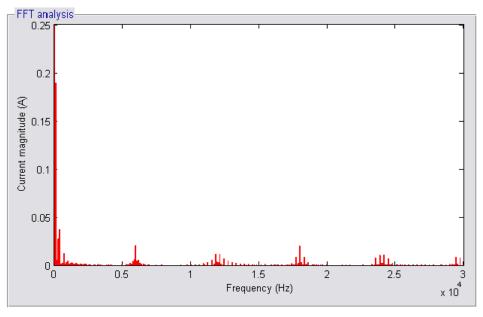

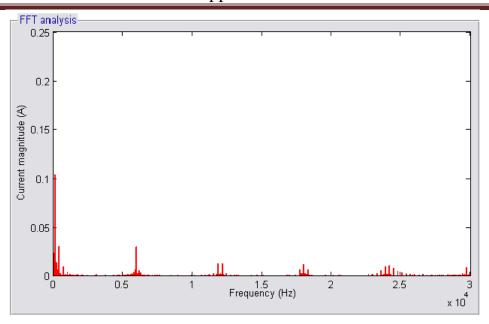

| Figure 4.63 Combined output current spectra for non-interleaved converters using    |

| SVPWM at M=0.5                                                                      |

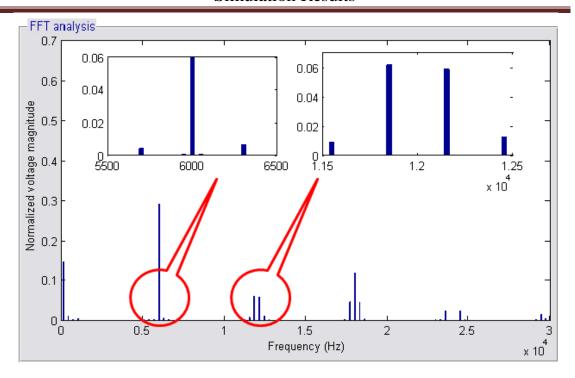

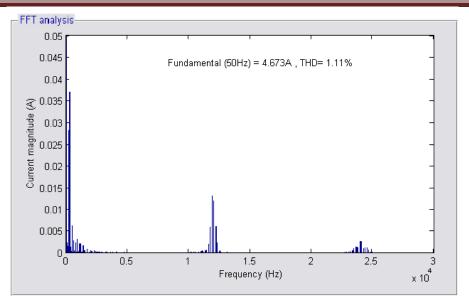

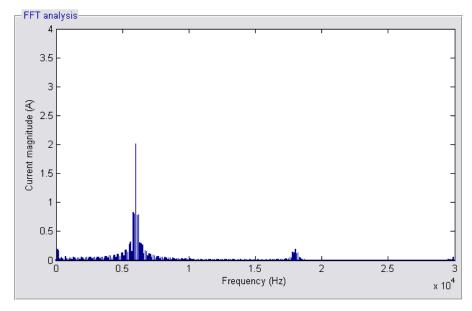

| Figure 4.64 Combined output current spectra for interleaved converters using SVPWM  |

| at M=0.9                                                                            |

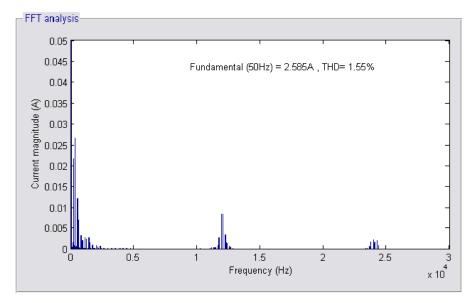

| Figure 4.65 Combined output current spectra for interleaved converters using SVPWM  |

| at M=0.5                                                                            |

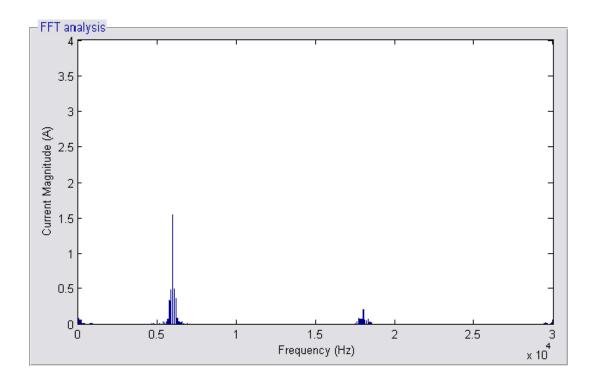

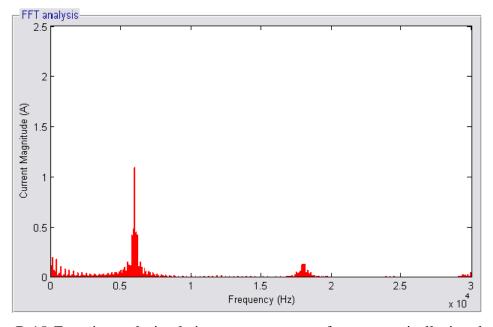

| Figure 4.66 Circulating current spectra for interleaved converters using SVPWM at   |

| M=0.9106                                                                            |

| Figure 4.67 Circulating current spectra for interleaved converters using SVPWM at   |

| M=0.5                                                                               |

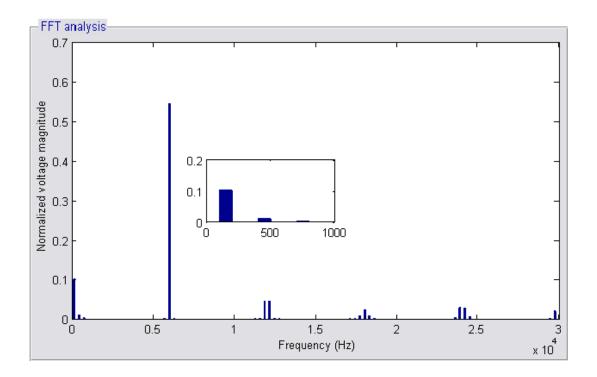

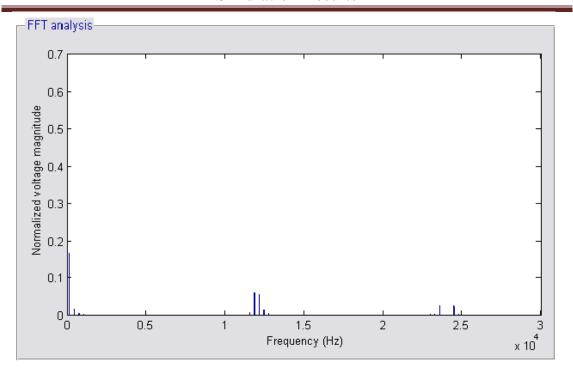

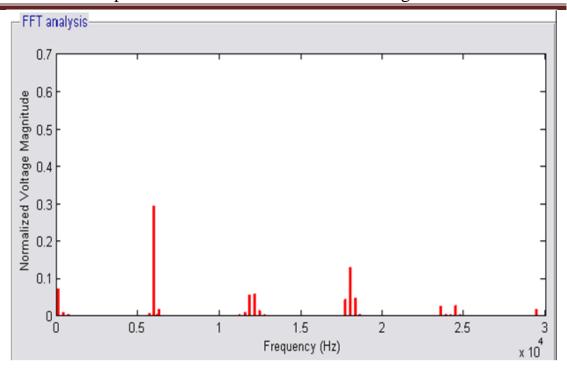

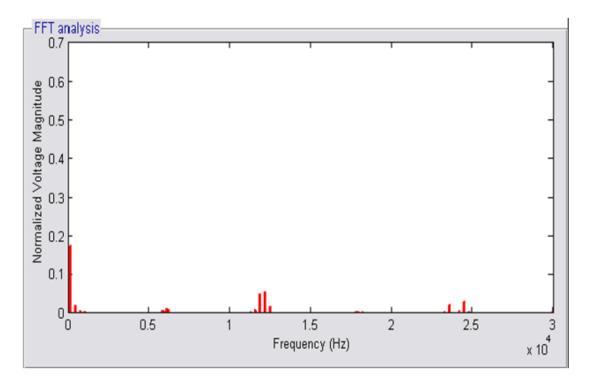

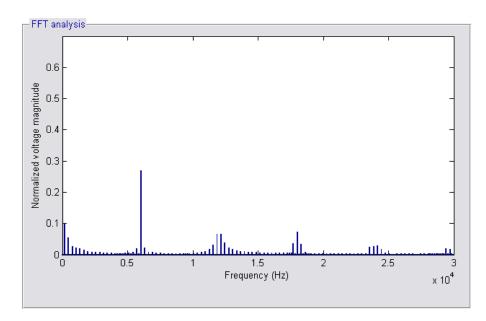

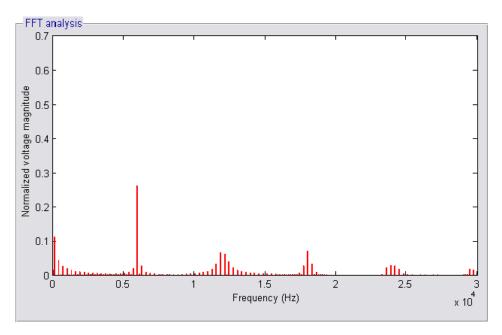

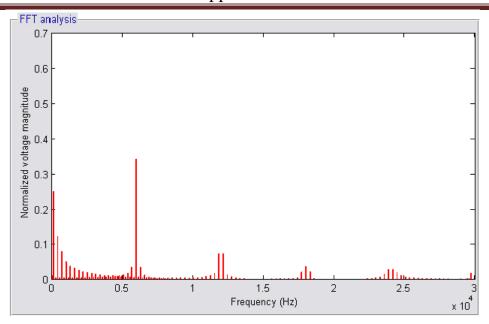

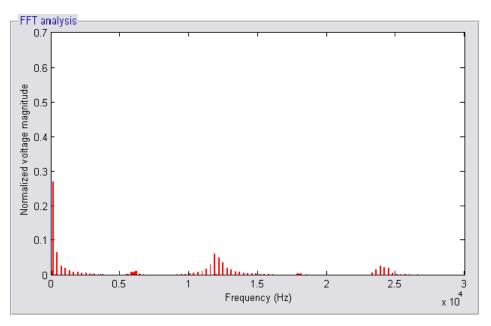

| Figure 4.68 Spectra of common-mode voltage for non-interleaved converters with      |

| SVPWM at M=0.9                                                                      |

| Figure 4.69 Spectra of common-mode voltage for non-interleaved converters with      |

| SVPWM at M=0.5                                                                      |

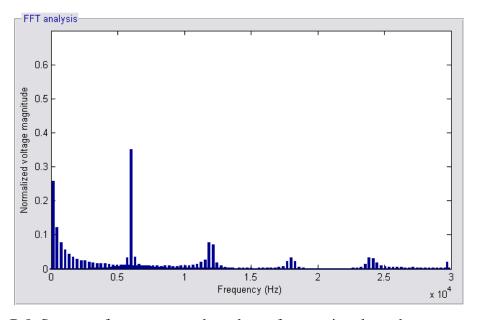

| Figure 4.70 Spectra of common-mode voltage for symmetrically interleaved converters |

| with SVPWM at M=0.9                                                                 |

| Figure 4.71 Spectra of common-mode voltage for symmetrically interleaved converters |

| with SVPWM at M=0.5                                                                 |

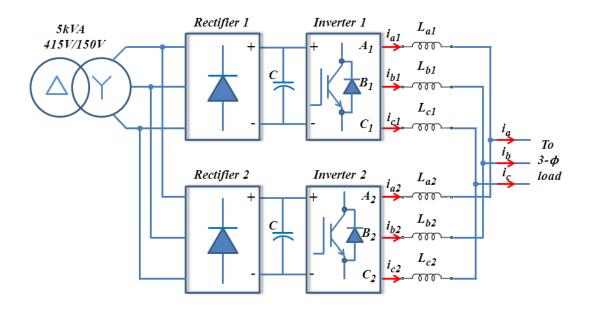

| Figure 5.1 Parallel AC/DC/AC converters system structure                            |

| Figure 5.2 AC/DC/AC converter structure                                             |

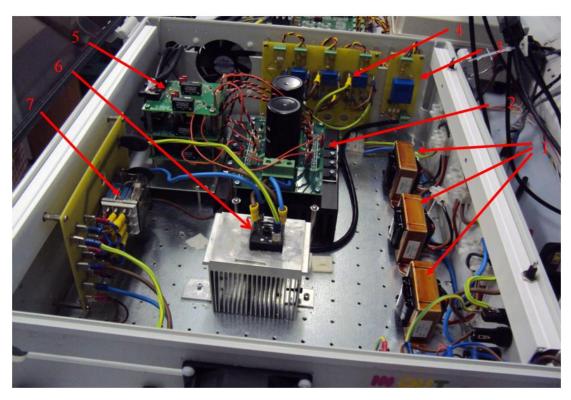

| Figure 5.3 Parallel converters system test rig                                      |

| Figure 5.4 Hardware structure of the AC/DC/AC converter                             |

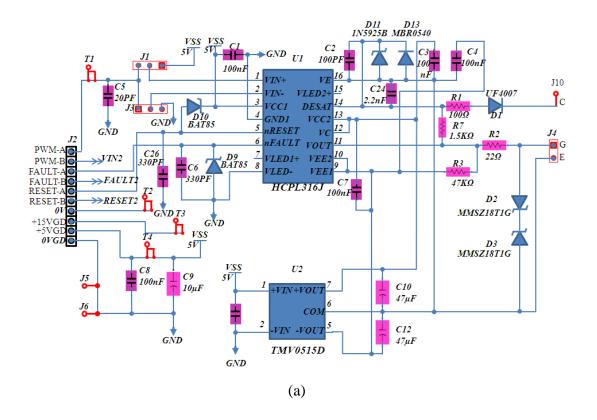

| Figure 5.5 Dual gate drive circuit schematic diagram (a) For Top IGBT (b) For bottom                                                                                                                                                                                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IGBT                                                                                                                                                                                                                                                                                                 |

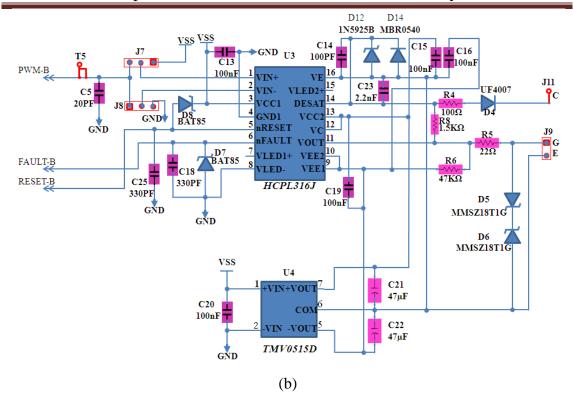

| Figure 5.6 General interface board with the Texas Instrument® TMS320F28335 DSP                                                                                                                                                                                                                       |

| microcontroller                                                                                                                                                                                                                                                                                      |

| Figure 5.7 LabView <sup>TM</sup> control and monitoring panel                                                                                                                                                                                                                                        |

| Figure 5.8 Flowchart of time sharing control algorithm                                                                                                                                                                                                                                               |

| Figure 5.9 Flowchart of average current sharing control algorithm employed in a current                                                                                                                                                                                                              |

| controller application                                                                                                                                                                                                                                                                               |

| Figure 5.10 Flowchart of average current sharing control algorithm employed in open                                                                                                                                                                                                                  |

| loop <i>V/f</i> control                                                                                                                                                                                                                                                                              |

| Figure 5.11 Flowchart of independent current sharing control employed in a current                                                                                                                                                                                                                   |

| controller application                                                                                                                                                                                                                                                                               |

| Figure 5.12 Flowchart of independent current sharing control algorithm employed in                                                                                                                                                                                                                   |

| open loop <i>V/f</i> control                                                                                                                                                                                                                                                                         |

| Figure 6.1 Experimental SVPWM modulating signals                                                                                                                                                                                                                                                     |

| Figure 6.2 Experimental DPWM2 modulating signals                                                                                                                                                                                                                                                     |

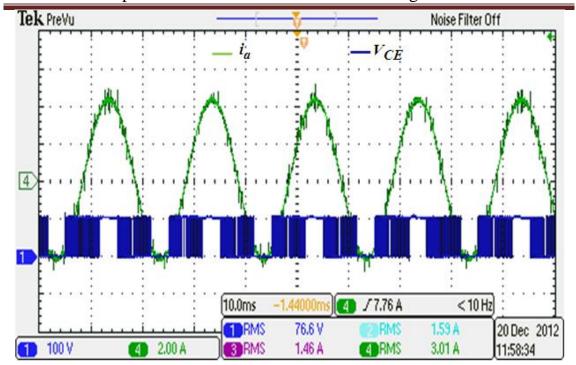

| Figure 6.3 Experimental load current and IGBT collector to emitter voltage (2A/div;                                                                                                                                                                                                                  |

| 100V/div; 10msec/div)                                                                                                                                                                                                                                                                                |

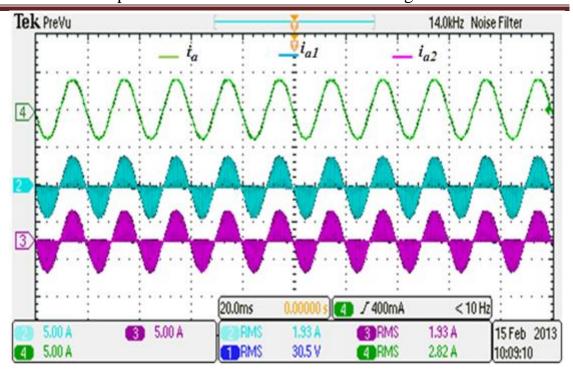

| Figure 6.4 Experimental steady state converter and load currents with time sharing                                                                                                                                                                                                                   |

| approach (5A/div; 20msec/div)                                                                                                                                                                                                                                                                        |

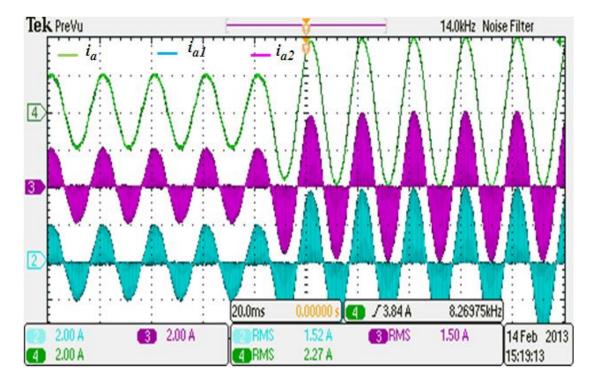

| Figure 6.5 Transient converter and load currents with time sharing approach (2A/div;                                                                                                                                                                                                                 |

| 20msec/div)                                                                                                                                                                                                                                                                                          |

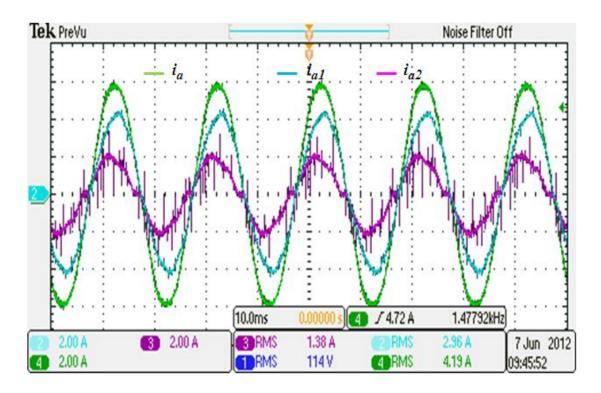

| Figure 6.6 Experimental converter and load current waveforms without sharing control                                                                                                                                                                                                                 |

| at 50Hz (2A/div; 10msec/div)                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                      |

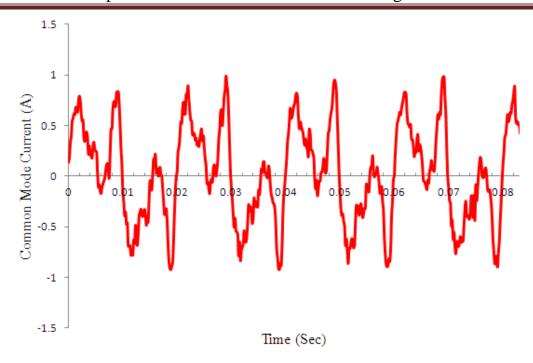

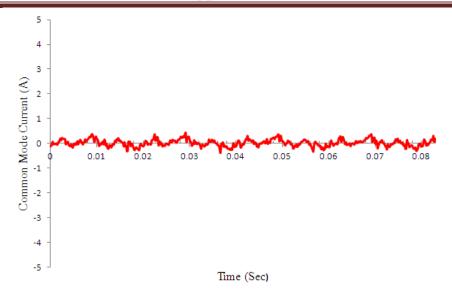

| Figure 6.7 Experimental common-mode circulating current without sharing control139                                                                                                                                                                                                                   |

| Figure 6.7 Experimental common-mode circulating current without sharing control139                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                      |

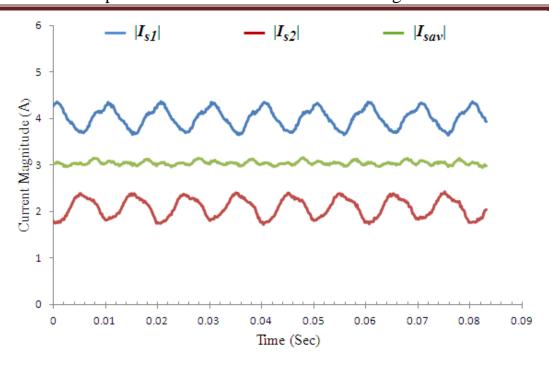

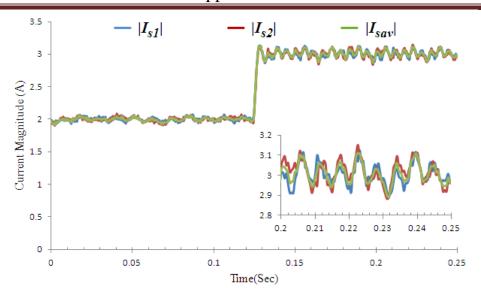

| Figure 6.7 Experimental common-mode circulating current without sharing control139 Figure 6.8 Experimental current space vector magnitudes without sharing control140                                                                                                                                |

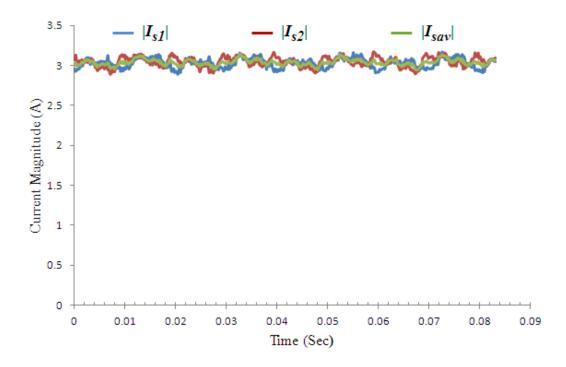

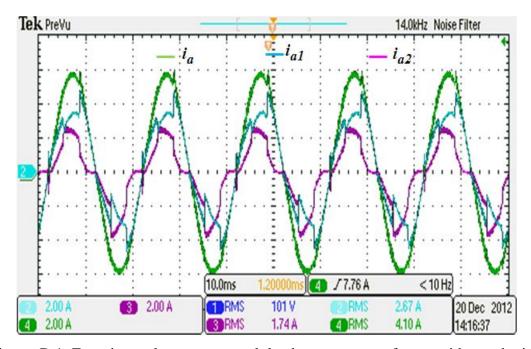

| Figure 6.7 Experimental common-mode circulating current without sharing control139 Figure 6.8 Experimental current space vector magnitudes without sharing control140 Figure 6.9 Experimental converter and load current waveforms with average current                                              |

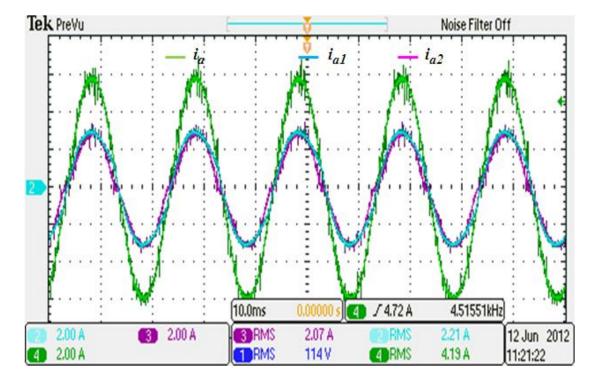

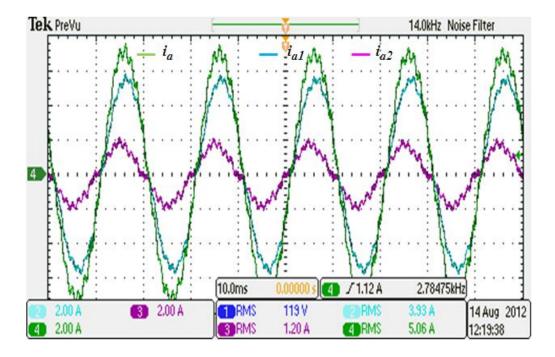

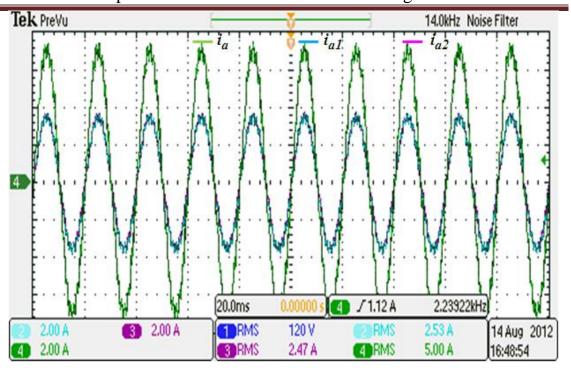

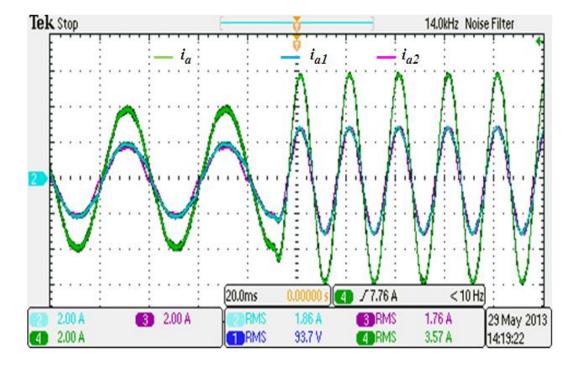

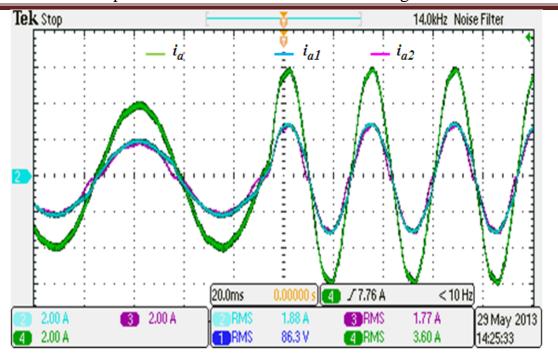

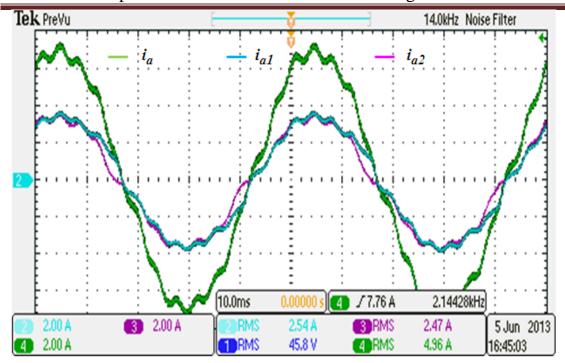

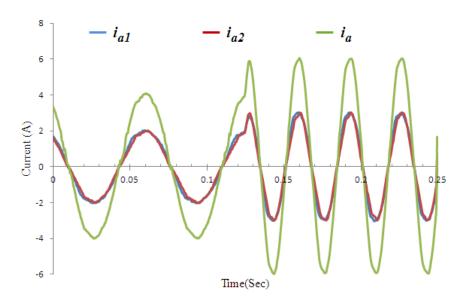

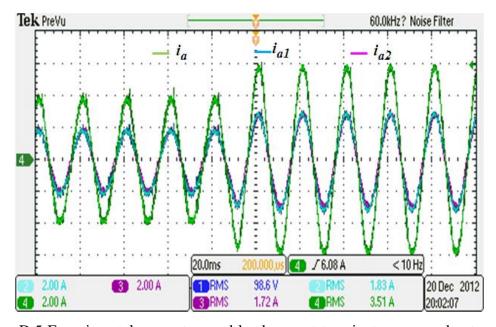

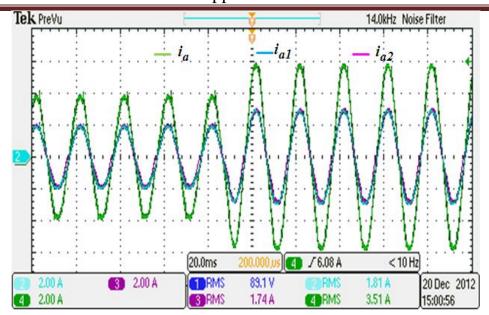

| Figure 6.7 Experimental common-mode circulating current without sharing control139 Figure 6.8 Experimental current space vector magnitudes without sharing control140 Figure 6.9 Experimental converter and load current waveforms with average current sharing control at 50Hz (2A/div; 10msec/div) |

| Figure 6.7 Experimental common-mode circulating current without sharing control139 Figure 6.8 Experimental current space vector magnitudes without sharing control140 Figure 6.9 Experimental converter and load current waveforms with average current sharing control at 50Hz (2A/div; 10msec/div) |

| Figure 6.7 Experimental common-mode circulating current without sharing control139 Figure 6.8 Experimental current space vector magnitudes without sharing control140 Figure 6.9 Experimental converter and load current waveforms with average current sharing control at 50Hz (2A/div; 10msec/div) |

| Figure 6.7 Experimental common-mode circulating current without sharing control139 Figure 6.8 Experimental current space vector magnitudes without sharing control140 Figure 6.9 Experimental converter and load current waveforms with average current sharing control at 50Hz (2A/div; 10msec/div) |

| Figure 6.13 Transient response due to step change in the desired current magnitude and  |

|-----------------------------------------------------------------------------------------|

| frequency from 25Hz to 50Hz (2A/div; 10msec/div)                                        |

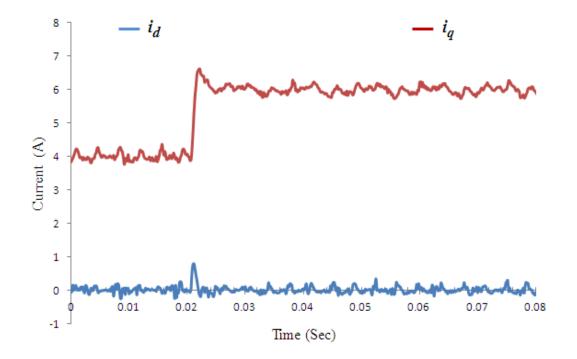

| Figure 6.14 Direct and quadrature axes load current due to a step change in the desired |

| quadrature axis current                                                                 |

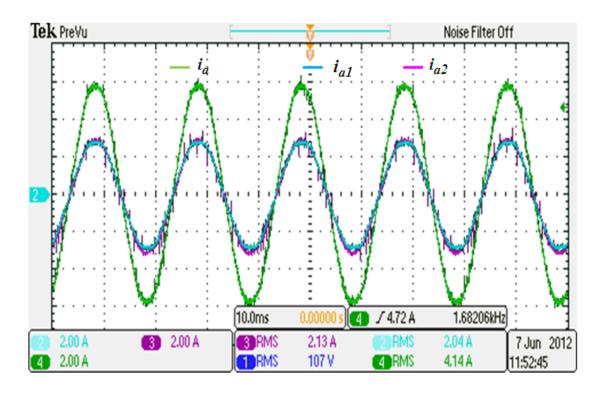

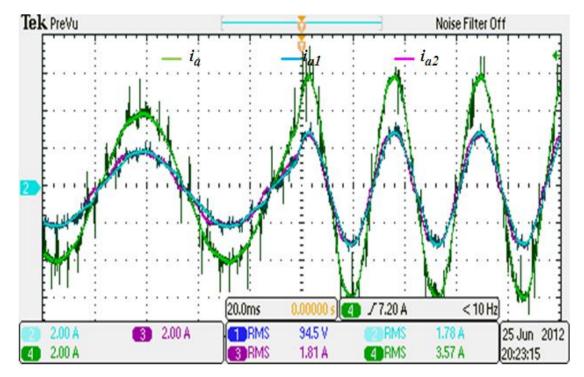

| Figure 6.15 Experimental converter and motor current waveforms without sharing          |

| control when the desired frequency is 50Hz (2A/div; 10msec/div)144                      |

| Figure 6.16 Experimental common-mode circulating current without sharing control        |

| when the desired frequency is 50Hz                                                      |

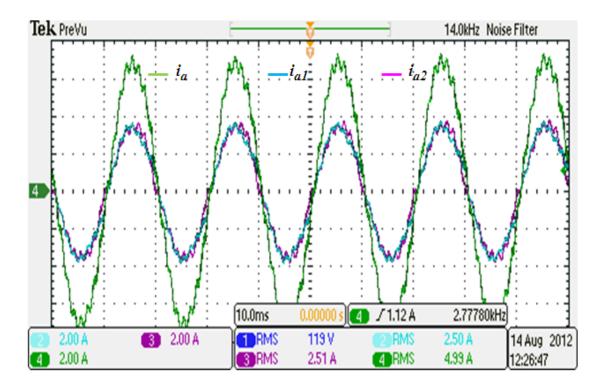

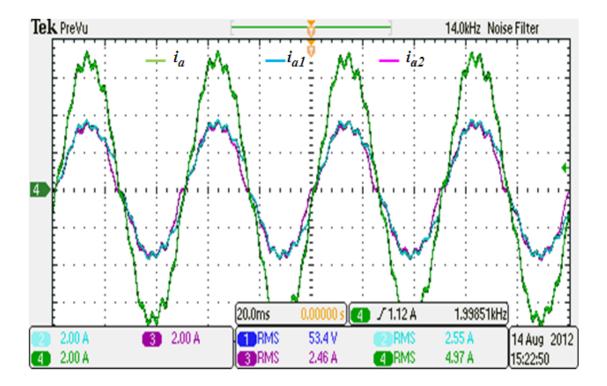

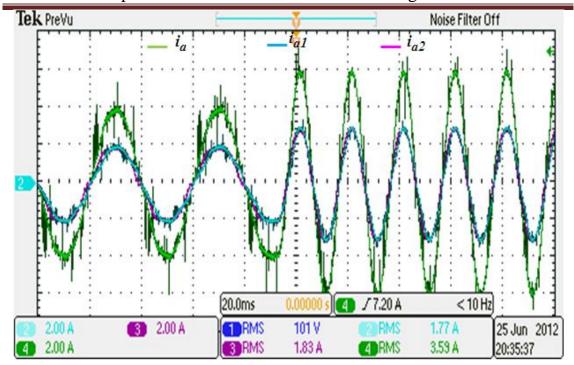

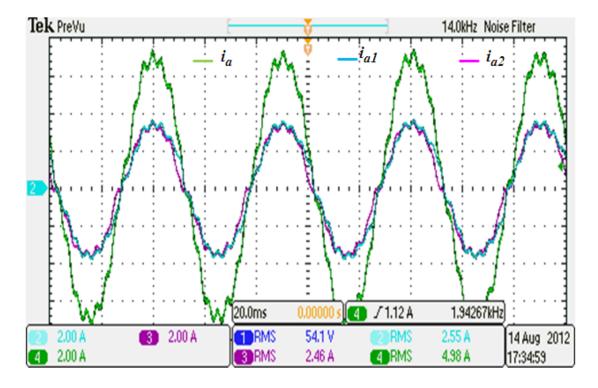

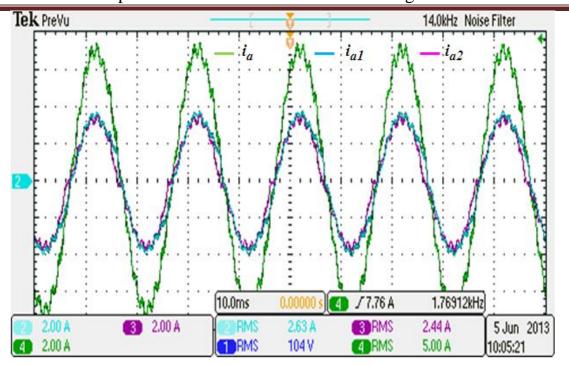

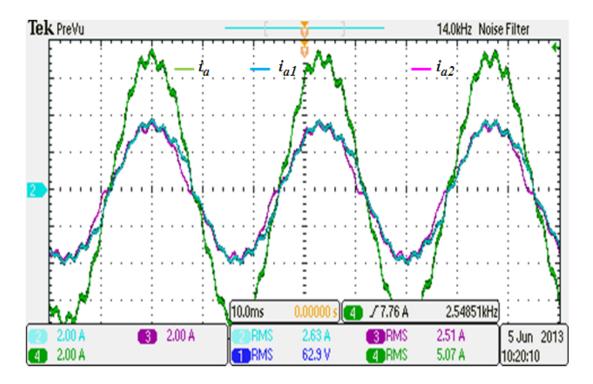

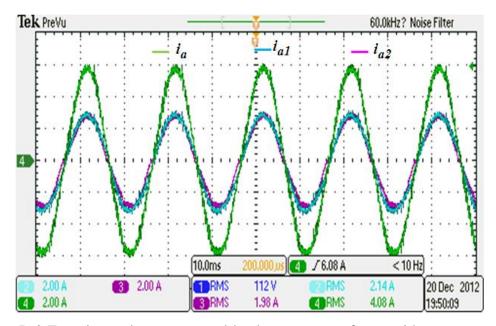

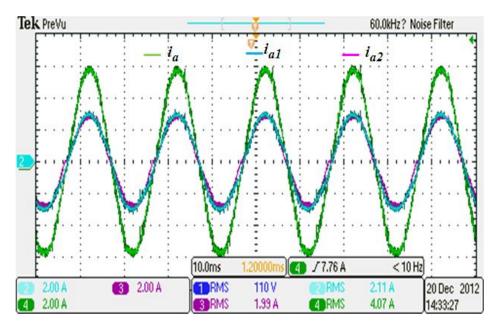

| Figure 6.17 Experimental converter and motor current waveforms with average current     |

| sharing control when the desired frequency is 50Hz (2A/div; 10msec/div)145              |

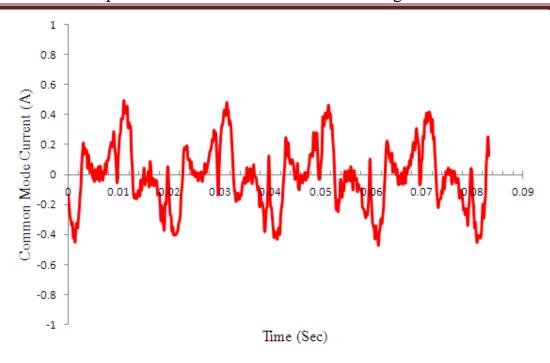

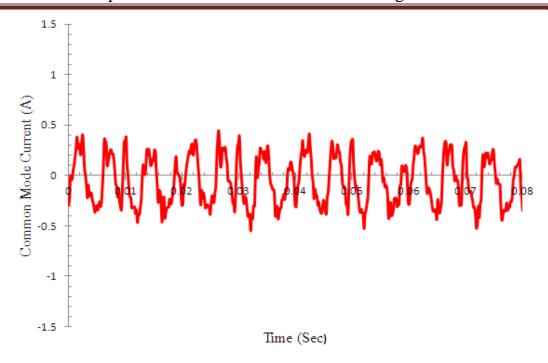

| Figure 6.18 Experimental common-mode circulating current with sharing control when      |

| the desired frequency is 50Hz146                                                        |

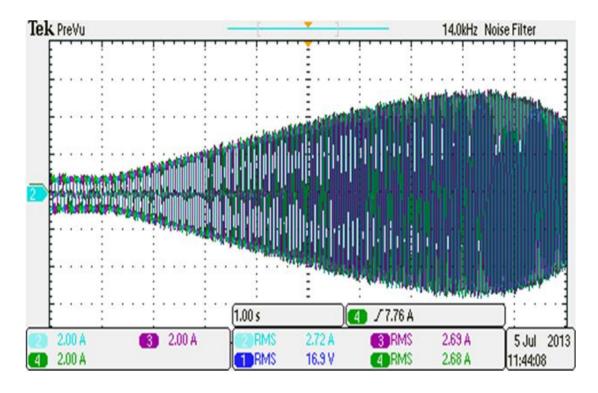

| Figure 6.19 Three-phase motor current during soft starting (2A/div; 1sec/div)146        |

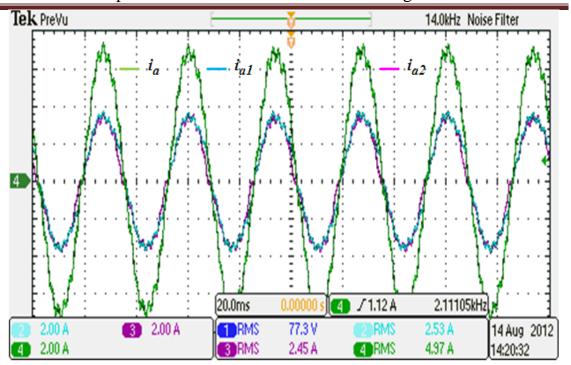

| Figure 6.20 Experimental converter and motor current waveforms with average current     |

| sharing control when the desired frequency is 20Hz (2A/div; 20msec/div)147              |

| Figure 6.21 Experimental converter and motor current waveforms with average current     |

| sharing control when the desired frequency is 30Hz (2A/div; 20msec/div)148              |

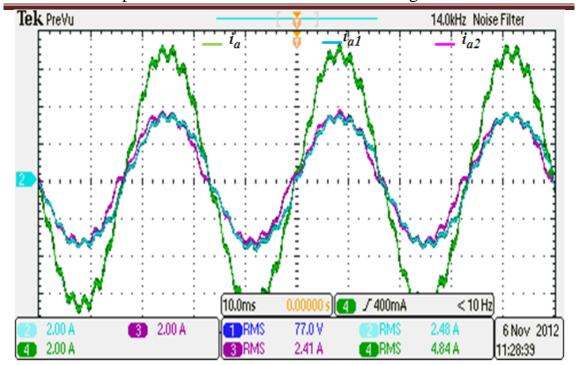

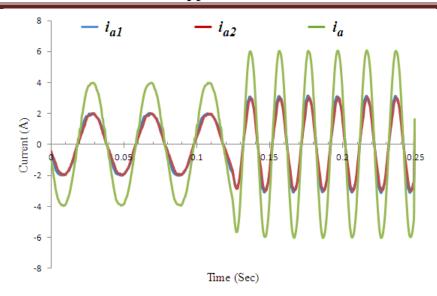

| Figure 6.22 Experimental converter and load current waveforms with independent          |

| (2A/div; 10msec/div)current sharing control when the desired frequency is 50Hz149       |

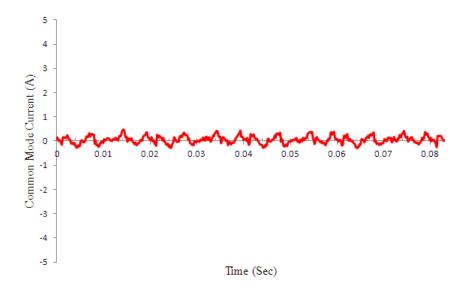

| Figure 6.23 Experimental common mode circulating current with independent sharing       |

| control at 50Hz149                                                                      |

| Figure 6.24 Current space vector magnitudes with independent sharing control at 50Hz    |

|                                                                                         |

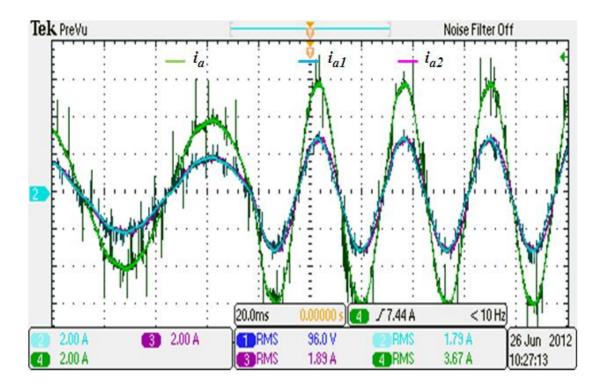

| Figure 6.25 Experimental converter and load current transient response due to a step    |

| change in the desired current magnitude from 4A to 6A and frequency from 15Hz to        |

| 30Hz (2A/div; 20msec/div)                                                               |

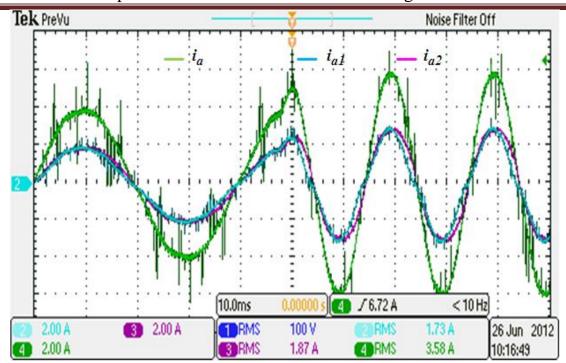

| Figure 6.26 Experimental converter and load current transient response due to a step    |

| change in the desired current magnitude from 4A to 6A and frequency from 25Hz to        |

| 50Hz (2A/div; 20msec/div)                                                               |

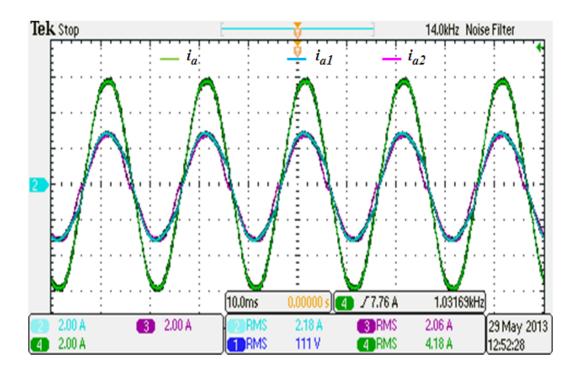

| Figure 6.27 Experimental converter and motor current waveforms with independent         |

| current sharing control when the desired frequency is 50Hz (2A/div; 20msec/div)152      |

| Figure 6.28 Experimental converter and motor current waveforms with independent         |

| current sharing control when the desired frequency is 20Hz (2A/div; 20msec/div)152      |

| Figure 6.29 Experimental converter and motor current waveforms with independent        |

|----------------------------------------------------------------------------------------|

| current sharing control when the desired frequency is 30Hz (2A/div; 10msec/div)153     |

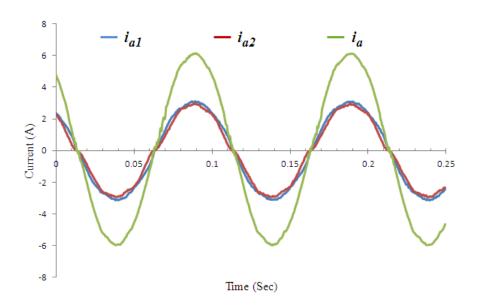

| Figure 6.30 Experimental converter and load current waveforms with resistance          |

| emulation current sharing control when the desired frequency is 50Hz (2A/div;          |

| 10msec/div)                                                                            |

| Figure 6.31 Transient response due to a step change in load current and frequency from |

| 25Hz to 50Hz (2A/div; 20msec/div)                                                      |

| Figure 6.32 Transient response due to a step change in load current and frequency from |

| 15Hz to 30Hz (2A/div; 20msec/div)                                                      |

| Figure 6.33 Experimental converter and motor current waveforms with sharing control    |

| when the desired frequency is 50Hz (2A/div; 10msec/div)                                |

| Figure 6.34 Experimental converter and motor current waveforms with sharing control    |

| when the desired frequency is 30Hz (2A/div; 10msec/div)                                |

| Figure 6.35 Experimental converter and motor current waveforms with sharing control    |

| when the desired frequency is 20Hz (2A/div; 10msec/div)                                |

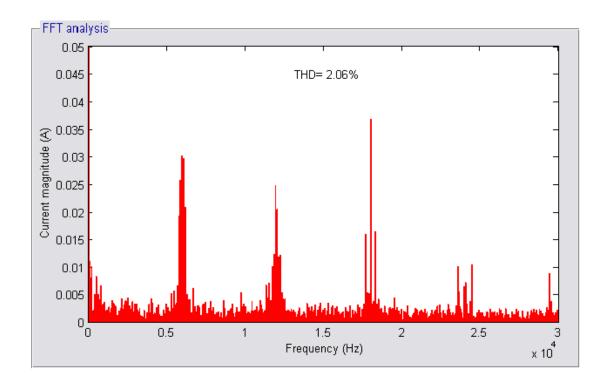

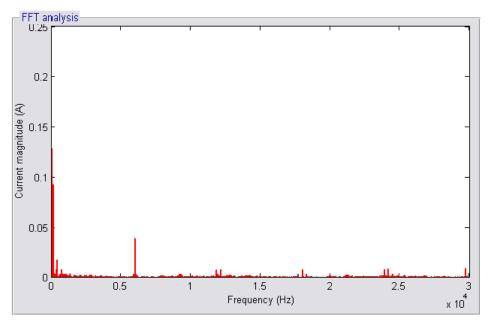

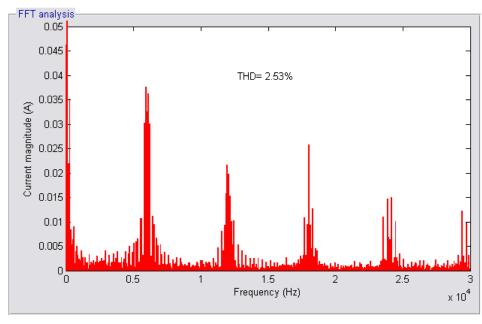

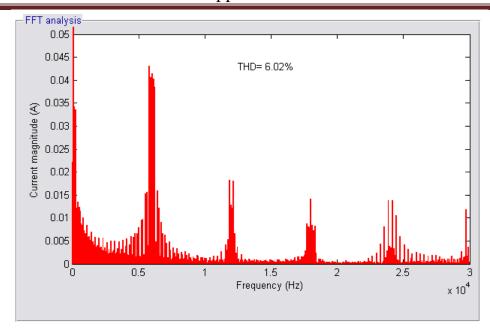

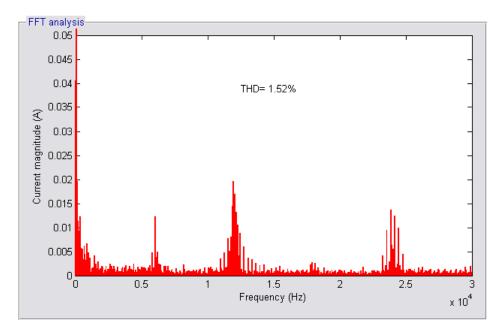

| Figure 6.36 Experimental combined output current spectra for non-interleaved           |

| converters using SVPWM at M=0.9                                                        |

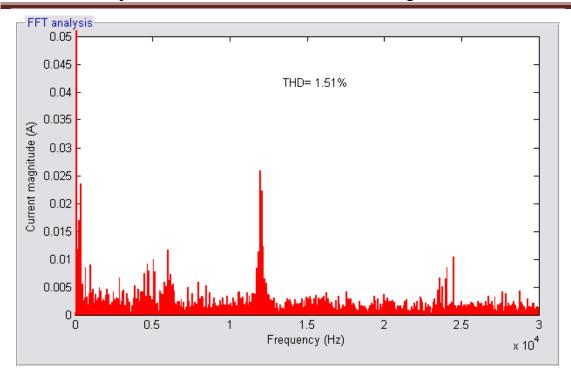

| Figure 6.37 Experimental combined output current spectra for symmetrically             |

| interleaved converters using SVPWM at M=0.9                                            |

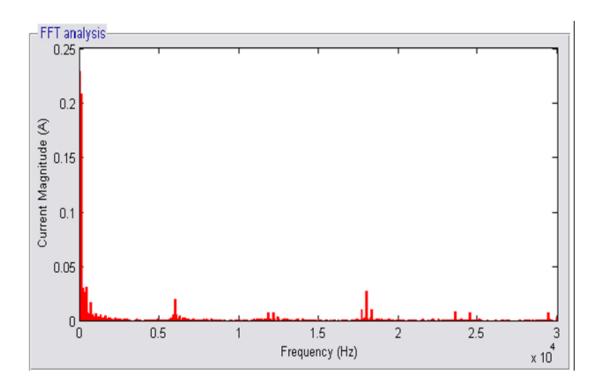

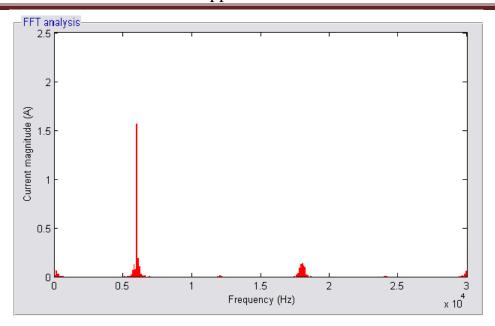

| Figure 6.38 Experimental circulating current spectra for non-interleaved converters    |

| using SVPWM at M=0.9160                                                                |

| Figure 6.39 Experimental circulating current spectra for symmetrically interleaved     |

| converters using SVPWM at M=0.9                                                        |

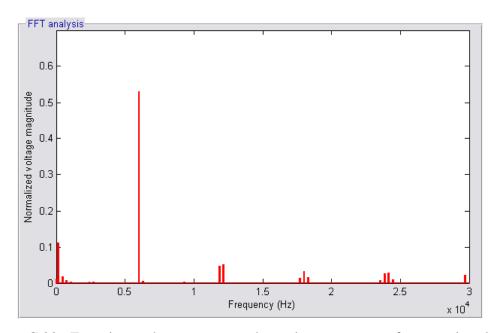

| Figure 6.40 Experimental common-mode voltage spectra for non-interleaved converters    |

| using SVPWM at M=0.9162                                                                |

| Figure 6.41 Experimental common-mode voltage spectra for symmetrically interleaved     |

| converters using SVPWM at M=0.9                                                        |

| Figure A.1 Schematic of parallel-connected converters-Wiring diagram                   |

| Figure A.2 Schematic of the first AC/DC/AC converter                                   |

| Figure A.3 Schematic of the second AC/DC/AC converter                                  |

| Figure A.4 Schematic of 3-phase rely card                                              |

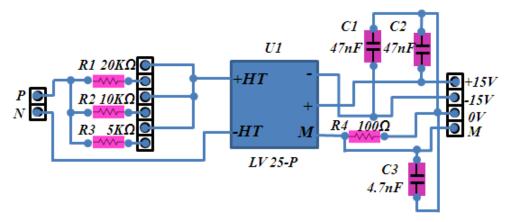

| Figure A.5 Schematic of converter current sensor circuit                               |

| Figure A.6 Schematic of converter voltage sensor circuit                               |

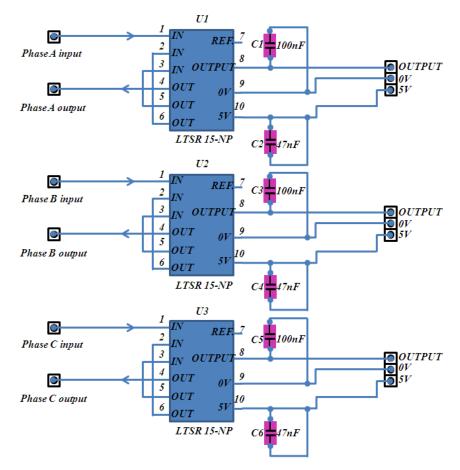

| Figure A 7 Schematic of load current sensor circuit 184                                |

| Figure B.1 Combined current spectra for non-interleaved converters using DPWM2 at       |

|-----------------------------------------------------------------------------------------|

| M=0.9                                                                                   |

| Figure B.2 Combined current spectra for non-interleaved converters using DPWM2 at       |

| M=0.5                                                                                   |

| Figure B.3 Combined current spectra for symmetrically interleaved converters using      |

| DPWM2 at M=0.9                                                                          |

| Figure B.4 Combined current spectra for symmetrically interleaved converters using      |

| DPWM2 at M=0.5                                                                          |

| Figure B.5 Circulating current spectra for interleaved converters using DPWM2 at        |

| M=0.9                                                                                   |

| Figure B.6 Circulating current spectra for interleaved converters using DPWM2 at        |

| M=0.5                                                                                   |

| Figure B.7 Spectra of common-mode voltage for non-interleaved converters with           |

| DPWM2 at M=0.9                                                                          |

| Figure B.8 Spectra of common-mode voltage for non-interleaved converters with           |

| DPWM2 at M=0.5                                                                          |

| Figure B.9 Spectra of common-mode voltage for symmetrically interleaved converters      |

| with DPWM2 at M=0.9                                                                     |

| Figure B.10 Spectra of common-mode voltage for symmetrically interleaved converters     |

| with DPWM2 at M=0.5                                                                     |

| Figure C.1 Experimental converter and load current waveforms without sharing control    |

|                                                                                         |

| Figure C.2 Experimental converter and load current waveforms with average current       |

| sharing control at 50Hz                                                                 |

| Figure C.3 Experimental current space vector magnitude transient response due to a step |

| change in the desired current magnitude and frequency from 15Hz to $30\text{Hz}193$     |

| Figure C.4 Experimental converter and load current transient response due to a step     |

| change in the desired current $$ magnitude and frequency from 15Hz to 30Hz193 $$        |

| Figure C.5 Experimental converter and load current transient response due to a step     |

| change in the desired current magnitude and frequency from 25Hz to $50\text{Hz}194$     |

| Figure C.6 Experimental converter and load current waveforms with average current       |

| sharing control at 10Hz                                                                 |

| Figure C.7 Experimental converter and motor current waveforms without sharing           |

| control when the desired frequency is 50Hz                                              |

| Figure C.8 Experimental current space vector magnitudes without sharing control at    |

|---------------------------------------------------------------------------------------|

| 50Hz                                                                                  |

| Figure C.9 Experimental converter and motor current waveforms with average196         |

| Figure C.10 Experimental current space vector magnitudes with average current sharing |

| control at 50Hz                                                                       |

| Figure C.11 Experimental converter and load current waveforms with independent        |

| current sharing control when the desired frequency is 50Hz197                         |

| Figure C.12 Experiment converter and load current transient response due to step      |

| change in the desired current magnitude from 4A to 6A and frequency from 15Hz to      |

| 30Hz                                                                                  |

| Figure C.13 Experimental current space vector magnitude transient response due to a   |

| step change in the desired current magnitude and frequency from 15Hz to 30Hz 198      |

| Figure C.14 Experiment converters and load current transient response due to a step   |

| change in the desired current magnitude from 4A to 6A and frequency from 25Hz to      |

| 50Hz                                                                                  |

| Figure C.15 Experimental converter and load current waveforms with impedance          |

| emulation current sharing control when the desired frequency is 50Hz199               |

| Figure C.16 Experiment converters and load current transient response due to a step   |

| change in the desired current magnitude from 4A to 6A and frequency from 25Hz to      |

| 50Hz                                                                                  |

| Figure C.17 Experiment converters and load current transient response due to a step   |

| change in the desired current magnitude from 4A to 6A and frequency from 15Hz to      |

| 30Hz                                                                                  |

| Figure C.18 Experimental combined current spectra for non-interleaved converters      |

| using SVPWM at M=0.5                                                                  |

| Figure C.19 Experimental combined current spectra for symmetrically interleaved       |

| converters using SVPWM at M=0.5                                                       |

| Figure C.20 Experimental circulating current spectra for non-interleaved converters   |

| using SVPWM at M=0.5201                                                               |

| Figure C.21 Experimental circulating current spectra for symmetrically interleaved    |

| converters using SVPWM at M=0.5                                                       |

| Figure C.22 Experimental common-mode voltage spectra for non-interleaved converters   |

| using SVPWM at M=0.5                                                                  |

| Figure C.23 Experimental common-mode voltage spectra for symmetrically interleaved    |

|---------------------------------------------------------------------------------------|

| converters using SVPWM at M=0.5                                                       |

| Figure D.1 Experimental converter and load current waveforms without sharing control  |

| at 50Hz (2A/div; 10msec/div)                                                          |

| Figure D.2 Experimental common-mode circulating current without sharing control .205  |

| Figure D.3 Experimental converter and load current waveforms with average current     |

| sharing control at 50Hz (2A/div; 10msec/div)205                                       |

| Figure D.4 Experimental common-mode circulating current with average current          |

| sharing control                                                                       |

| Figure D.5 Experimental converters and load current transient response due to a step  |

| change in the desired current magnitude (2A/div; 20msec/div)                          |

| Figure D.6 Experimental converter and load current waveforms with independent         |

| current sharing control at 50Hz (2A/div; 10msec/div)                                  |

| Figure D.7 Experimental common mode circulating current with independent sharing      |

| control at 50Hz207                                                                    |

| Figure D.8 Experiment converters and load current transient response due to a step    |

| change in the desired current magnitude (2A/div; 20msec/div)                          |

| Figure D.9 Experimental combined current spectra for non-interleaved converters using |

| DPWM2 at M=0.9                                                                        |

| Figure D.10 Experimental combined current spectra for non-interleaved converters      |

| using DPWM2 at M=0.5209                                                               |

| Figure D.11 Experimental combined current spectra for symmetrically interleaved       |

| converters using DPWM2 at M=0.9                                                       |

| Figure D.12 Experimental combined current spectra for symmetrically interleaved       |

| converters using DPWM2 at M=0.5                                                       |

| Figure D.13 Experimental circulating current spectra for non-interleaved converters   |

| using DPWM2 at M=0.9210                                                               |

| Figure D.14 Experimental circulating current spectra for non-interleaved converters   |

| using DPWM2 at M=0.5211                                                               |

| Figure D.15 Experimental circulating current spectra for symmetrically interleaved    |

| converters using DPWM2 at M=0.9                                                       |

| Figure D.16 Experimental circulating current spectra for symmetrically interleaved    |

| converters using DPWM2 at M=0.5                                                       |

| Figure D.17 Experimental common-mode voltage spectra for non-interleaved co | onverters |

|-----------------------------------------------------------------------------|-----------|

| using DPWM2 at M=0.9                                                        | 212       |

| Figure D.18 Experimental common-mode voltage spectra for non-interleaved co | onverters |

| using DPWM2 at M=0.5                                                        | 213       |

| Figure D.19 Experimental common-mode voltage spectra for symmetrically inte | erleaved  |

| converters using DPWM2 at M=0.9                                             | 213       |

| Figure D.20 Experimental common-mode voltage spectra for symmetrically into | erleaved  |

| converters using DPWM2 at M=0.5                                             | 214       |

# List of Tables

# **List of Tables**

| Table 2.1 The eight possible states and their output voltages                       |

|-------------------------------------------------------------------------------------|

| Table 2.2 Switching sequences for different sectors                                 |

| Table 2.3 DPWM switching sequences for different sectors                            |

| Table 4.1 Switching points for modulating signals calculation                       |

| Table 4.2 AC/DC/AC converter parameters                                             |

| Table 4.3 DPWM2 switching point calculations                                        |

| Table 4.4 Converters parameters with time sharing scheme                            |

| Table 4.5 Three-phase induction motor parameters                                    |

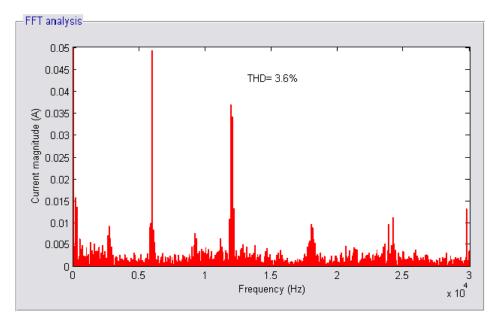

| Table 4.6 Combined output current THD for different PWM strategies103               |

| Table 5.1 AC/DC/AC converter ratings                                                |

| Table 6.1 Experimental THD for different modulation index values and PWM strategies |

|                                                                                     |

| Table 6.2 Simulated and experimental current imbalance ration for SVPWM strategy    |

|                                                                                     |

| Table 6.3 Simulated and experimental combined output current THD for different      |

| modulation index values and PWM strategies                                          |

| Table 6.4 Simulated and experimental common-mode voltage magnitude of the 6 kHz     |

| harmonic component                                                                  |

| Table 6.5 Summary of current sharing control schemes features                       |

#### **List of Abbreviations**

AC Alternating current

ADC Analogue to digital converter

CCS Code composer studio

CFC Converter flux based control

CM Common mode

DC Direct current

DM Differential mode

DPWM Discontinuous pulse width modulation

DSP Digital signal processor

EMI Electromagnetic interference

ESR Equivalent series resistor

FET Field effect transistor

FFT Fast Fourier transforms

FIR Finite impulse response

GUI Graphical user interface

IGBT Insulated gate bipolar transistor

IIR Infinite impulse response

LPF Low pass filter

PC Personal computer

PCC Point of common coupling

PI Proportional integral

PR Proportional resonance

PV Photovoltaic

PWM Pulse width modulation/modulated

RMS Root mean square

SMS Sliding mode frequency shift

SPWM Sinusoidal pulse width modulation

SVM Space vector modulation

SVPWM Space vector pulse width modulation

THD Total harmonic distortion

# List of Abbreviations

| UPS  | Uninterruptible power system      |

|------|-----------------------------------|

| VSC  | Voltage source converter          |

| VSI  | Voltage source inverter           |

| ZSCC | Zero sequence circulating current |

#### **Chapter 1. Introduction**

#### 1.1 Motivation and objective

Although there has been a considerable increase in the power rating of power semiconductor devices, these devices have either technical or economic limitations. They often have inadequate switching characteristics, or are too expensive due to being manufactured in low quantities. Power ratings can be increased by series or parallel connections. Series connections can be used to increase voltage blocking capability while a parallel connection can be utilised to increase the current handling capability. Both series and parallel connections can be implemented at the semiconductor devices level or power converter level, which is the most common approach [1].

Unlike a single converter, parallel converters provide many advantages such as increased reliability through redundancy. This is essential in some applications such as aerospace, wind turbine, or UPS for main frame computers and servers. Parallel converters can also have a virtually indefinite output power level, as any number of parallel converters can be selected according to the system power requirement. Furthermore, a significant performance improvement can be obtained by employing interleaving techniques. This allows smaller passive components to be used due to harmonic cancellation [2, 3].

The connection of parallel converters started with DC/DC converters [4, 5]. More recently, these have been used in three-phase power conversion as the need for an additional transformer became redundant through the development of active control strategies [6]. Parallel-connected, three-phase converters may be used for megawatt-level wind turbines [7-9], variable speed pump-storage power stations [10, 11], active power filters [12], grid-connected photovoltaic systems [13] and uninterruptible power system (UPS) inverters [14, 15].

Despite improvements in power level, system reliability, efficiency and flexibility [9], parallel-operating converters can suffer from unequal current-sharing between the units. The term circulating current is frequently used to describe the uneven current-sharing between the units. This circulating current can lead to current distortion, unbalanced operation, saturation in inductors and a decline in overall system performance.

#### Introduction

In three-phase power conversion, circulating currents flow between parallel-connected converters unless they have uniform modulation [16]. The reference waveforms and the carrier waveforms should have exactly the same amplitude, phase and frequency in order to prevent the flow of circulating currents. The physical parameters of the system and the dead time between the upper and lower switching signals in each leg should also be the same, which is not possible in a practical system. Consequently, practical methods are necessary to limit the circulating currents in such a system.

Although much work has been carried out to investigate active current-sharing techniques [17], designing a modular circulating current controller with a minimum size of passive components and an uncomplicated control algorithm is still the target of many studies.

The main objective of this work is to investigate a modular active current-sharing control for two parallel-connected converters which can be easily extended to more than two units. Two AC/DC/AC converters with a separate but not isolated DC link, as is shown in Fig.1.1, will be considered in this work.

Figure 1. 1 Parallel AC/DC/AC converters with a separate non-isolated DC link.

#### 1.2 Thesis contributions

The main contributions of this thesis are the development of four active current-sharing control systems as listed below:

#### Introduction

- ➤ Development of a modular active current-sharing control for parallel- connected converters such that only one set of information is shared between the converters and only one proportional-integral (PI) controller is utilised by each converter

- Development of modular current sharing control where there is no need to share any information between the parallel-connected converters and only one PI controller is used with each converter

- ➤ Development of a modular current-sharing control with no PI controller and where there is no need to share any information between the parallel-connected converters

- ➤ Development of a pulse width modulation (PWM) strategy that can be used for parallel-connected converters such that the current-sharing reactors will be redundant

- ➤ Investigation of the effect of interleaving when employed on a parallel converter structure.

- Experimental validation for all the systems mentioned above.

#### 1.3 Thesis outline

The main contents of the chapters can be summarised as follows:

Chapter 2 presents the background of the two-level, three-phase voltage source converter. It explains the commonly used PWM strategies such as sinusoidal pulse width modulation (SPWM), space vector pulse width modulation (SVPWM), and discontinuous pulse width modulation (DPWM). Some of the general current control strategies are presented like hysteresis current control, stationary frame and synchronous frame PI current regulator. The circulating current definition and generation mechanism for the parallel-connected converters considered in this work are also described. A brief description of the interleaving technique and its effect on the performance of parallel-connected converter systems will be given. Finally, a review of the previous work on active current-sharing control methods is presented and discussed. Chapter 3 describes the proposed control methods that provide equal current-sharing to the parallel-connected converter. Current-sharing analysis and compensator design will be presented for the suggested current-sharing control schemes.

Chapter 4 introduces different applications for the proposed methods such as a current controller for the parallel-connected converters supplying an inductive load and an open loop voltage to frequency (V/f) control for three-phase induction motor. The

#### Introduction

MATLAB/SIMSULINK® models for the PWM strategies and the suggested control methods will be demonstrated along with the simulation results. This will include the PWM strategies and the current-sharing behaviour for parallel-connected converters during transient and steady state conditions. These results include the case where the system is considered to be a current controller and when *V/f* control is utilised to control a three-phase induction motor. Further results show how interleaving affects the harmonic performance of the output current, circulating current between the converters, and the common mode voltage. In addition, this chapter will clarify the effect of the modulation index on the system performance.

Chapter 5 deals with the design and implementation of two parallel-connected converters. The hardware and software design aspects of the system are described, including the selection of passive and active components. Also, the necessary equipment, measurement, protection circuits and interfacing with the Texas Instrument® TMS320F28335 digital signal processing (DSP) microcontroller will be discussed. The National Instruments LabView<sup>TM</sup> platform used for monitoring and control will also be described.

Chapter 6 presents experimental results to verify the proposed methods when the parallel converters are used as a current controller for a three-phase inductive load. Further practical results will be demonstrated when the parallel converters are used for the open loop V/f control of a three-phase induction motor. Symmetrical interleaving is employed to validate the interleaving effects on the output current, common-mode voltage and circulating current between the parallel-connected converters.

Chapter 7 summarises the main conclusions and suggestions for future work.

#### 1.4 List of publications

- B. M. H. Jassim, B. Zahawi, and D. Atkinson, "Simple control method for parallel connected three-phase PWM converters", 6th IET International Conference in Power Electronics, Machines and Drives (PEMD 2012)

- B. M. H. Jassim, B. Zahawi, and D. Atkinson, "Modular Current Sharing Control Scheme for Parallel Connected Converters"; IEEE Transactions on Industrial Electronics; (submitted for reviewing)

#### **Chapter 2. Background and Literature Review**

#### 2.1 Voltage Source Inverter

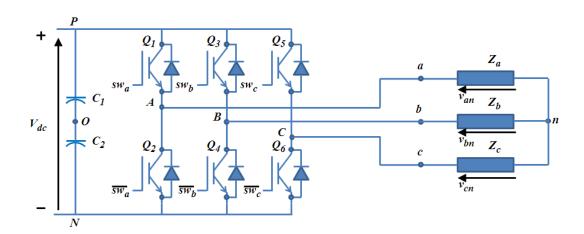

The main purpose of the voltage source inverter (VSI) is to convert a fixed DC voltage to a variable magnitude, variable frequency AC voltage. Figure 2.1 shows the basic topology of a two- level voltage source inverter. The converter consists of three phase legs connected in parallel with the DC voltage source. Each phase leg has two series connected switches (e.g. IGBT or FET), with anti-parallel diodes. Capacitors  $C_I$  and  $C_2$  should be large enough to filter the voltage ripple and provide a low impedance path for the high frequency ripple currents generated from the inverter stage [18]. The midpoint o is the reference (ground) for all the voltages and the connection from point n (neutral of the star connected load) to the midpoint o is not required when a balanced three phase currents are supplied to the load. Also, P and N are the positive and negative DC bus voltages respectively, with respect to the midpoint o. The voltage source inverter could be connected to any passive or active three-phase load.

Figure 2.1 Three-phase voltage source inverter topology

#### 2.2 Fundamentals of Symmetrical Components