# Asynchronous Techniques for New Generation Variation-Tolerant FPGA

## **Hock Soon Low**

A Thesis Submitted for the Degree of Doctor of Philosophy

at Newcastle University

School of Electrical and Electronic Engineering Faculty of Science, Agriculture & Engineering

October 2015

Asynchronous Techniques for New Generation Variation-Tolerant FPGA  $\ensuremath{\mathbb{C}}$

Hock Soon Low, Newcastle, October, 2015

### Abstract

This practical scenario thesis presents a for asynchronous logic implementation that would benefit the modern Field-Programmable Gate Arrays (FPGAs) technology in improving reliability. A method based on Asynchronously-Assisted Logic (AAL) blocks is proposed here in order to provide the right degree of variation tolerance, preserve as much of the traditional FPGAs structure as possible, and make use of asynchrony only when necessary or beneficial for functionality. The newly proposed AAL extra underlying hard-blocks that support asynchronous introduces interaction only when needed and at minimum overhead. This has the potential to avoid the obstacles to the progress of asynchronous designs, particularly in terms of area and power overheads. The proposed approach provides a solution that is complementary to existing variation tolerance techniques such as the late-binding technique, but improves the reliability of the system as well as reducing the design's margin headroom when implemented on programmable logic devices (PLDs) or FPGAs. The proposed method suggests the deployment of configurable AAL blocks to reinforce only the variation-critical paths (VCPs) with the help of variation maps, rather than re-mapping and re-routing. The layout level results for this method's worst case increase in the CLB's overall size only of 6.3%. The proposed strategy retains the structure of the global interconnect resources that occupy the lion's share of the modern FPGA's soft fabric, and yet permits the dual-rail

completion-detection (DR-CD) protocol without the need to globally double the interconnect resources. Simulation results of global and interconnect voltage variations demonstrate the robustness of the method.

## Acknowledgements

First of all, I would like express my profound thanks for my supervisors Prof Alex Yakovlev for his support through the course of my studies. His wisdom and vision were invaluable source of inspiration for me.

I would also like to express my gratitude to Dr Delong Shang and Dr Fei Xia for their guidance and advice throughout my PhD.

I am also grateful to colleagues and friends in the Microelectronics System Design research group at Newcastle University for their assistance and inspiring working atmosphere. Dr Danil Sokolov, Dr XueFu Zhang, Dr Maxim Rykunov, Dr James Docherty, Dr Graeme Coapes, Dr Nizar Dahir and Dr Ra'ed Aldujaily and Dr Ghaith Tarawneh. They made my PhD journey more enjoyable.

Finally, I wish to thanks my family for their love and unwavering support through the duration of my studies.

# CONTENTS

| CONTENTSvi                                        |

|---------------------------------------------------|

| FIGURESxi                                         |

| TABLES                                            |

| 1 Introduction1                                   |

| 1.1 Motivation and Objective1                     |

| 1.2 Overview of Chapters5                         |

| 1.3 Contributions                                 |

| 1.4 Publications7                                 |

| Chapter 2. Background9                            |

| 2.1 Introduction9                                 |

| 2.2 Introduction to FPGA Technology10             |

| 2.2.1 Moore's Law and Configuration Cells13       |

| 2.2.2 Programmable Memory14                       |

| 2.2.3 Modern FPGA Fabric16                        |

| 2.2.4 Software and Hardware Programmable Devices: |

| 2.2.5 Difference between the FPGA and ASIC19      |

| 2.2.6 Summary of Evolution22                      |

| 2.2.7 Fundamental Structure of the FPGA23         |

| 2.2.8 Logic Block24                               |

| 2.2.9 Routing Structure                           |

| 2.3 Introduction to Variation27                   |

| 2.4 Classification of Variability                 |

| 2.5 Process Variation Sources                           | 30 |

|---------------------------------------------------------|----|

| 2.5.1 Tool-Related Variation                            | 31 |

| 2.5.2 Intrinsic Variation                               | 32 |

| 2.6 Environmental Variation                             | 33 |

| 2.6.1 Temperature Variation                             | 33 |

| 2.7 Temporal Variation – Ageing Related                 | 38 |

| 2.8 Sensing and Characterisation                        | 39 |

| 2.8.1 Off-chip Sensing                                  | 40 |

| 2.8.2 On-chip Sensing                                   | 41 |

| 2.8.3 Soft Sensing in FPGA                              | 43 |

| 2.9 Conventional Variation Tolerance in FPGAs           | 44 |

| 2.9.1 STA and SSTA                                      | 44 |

| 2.9.2 Optimisation of Structural Parameters             | 46 |

| 2.9.3 Transistor Sizing                                 |    |

| 2.9.4 Asynchronous Techniques                           | 47 |

| 2.10 Variation Aware and Late Binding Techniques        |    |

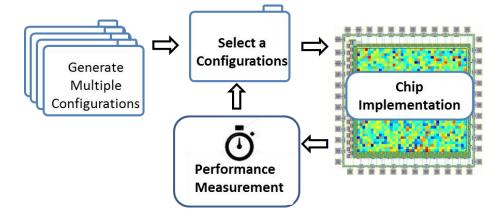

| 2.10.1 Yield Improvement Through Multiple-Configuration | 49 |

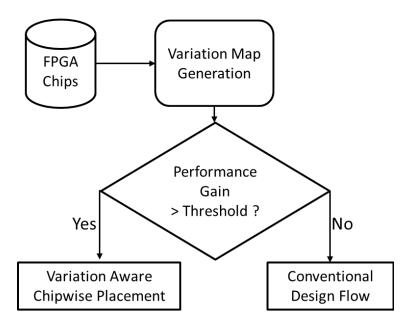

| 2.10.2 Variation Aware Modelling                        | 50 |

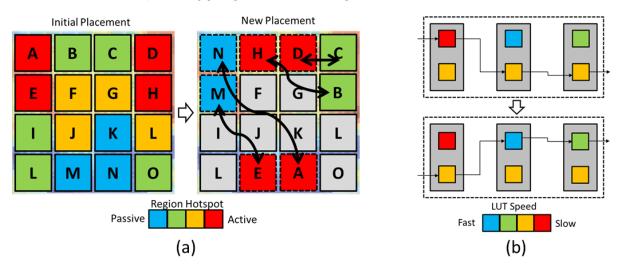

| 2.10.3 Relocation, Remapping and Rerouting              | 52 |

| 2.11 Summary                                            | 53 |

| Chapter 3. Existing Asynchronous Techniques in FPGA     | 58 |

| 3.1 Introduction                                        | 58 |

| 3.2 Principles of Asynchronous Design                   | 59 |

| 3.3 Bundle Data Design                                  |    |

| 3.3.1 Single-Rail Bundle-Data (SR-BD)                               | 61    |

|---------------------------------------------------------------------|-------|

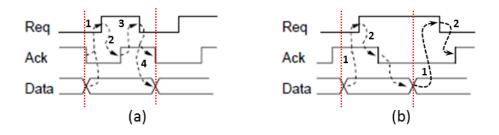

| 3.3.2 4-Phase and 2-Phase Bundle-Data Handshaking                   | 62    |

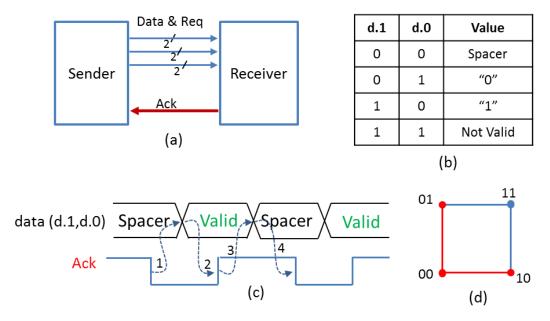

| 3.4 Delay-Insensitive Encoding                                      | 65    |

| 3.4.1 4-Phase Dual-Rail Handshaking                                 | 66    |

| 3.4.2 Completion Detection (CD) Circuit                             | 68    |

| 3.4.3 2-Phase Dual-Rail Protocol                                    | 69    |

| 3.5 Asynchronous Circuit Classification:                            | 70    |

| 3.5.1 Speed–Independent (SI)                                        | 71    |

| 3.5.2 Delay-Insensitive (DI)                                        | 72    |

| 3.5.3 Quasi-Delay-Insensitive (QDI)                                 | 72    |

| 3.6 Reconfigurable Asynchronous Architectures                       | 73    |

| 3.6.1 Type 1: Bundle Data and Timing Assumption Architectures       | 74    |

| 3.6.2 Type 2: High Performance Architecture                         | 77    |

| 3.6.3 Type 3: Communication Efficiency (2-Phase Dual-Rail or LEDF   | R)79  |

| 3.6.4 Type 4: Hierarchical and Coarse Grain Reconfigurable Archited | cture |

|                                                                     | 82    |

| 3.6.5 Other Asynchronous Style FPGAs                                | 86    |

| 3.7 Summary                                                         | 89    |

| Chapter 4. Distributed Control Asynchronous FPGA Architecture       | 93    |

| 4.1 Introduction                                                    | 93    |

| 4.2 Asynchronous Wrapper                                            | 94    |

| 4.3 Top Level Overview of the Architecture                          | 96    |

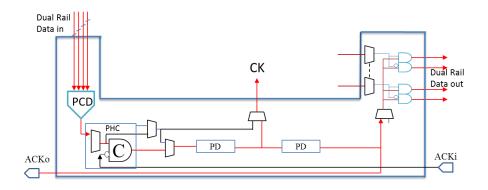

| 4.4 Asynchronous Wrapper Structure                                  | 98    |

| 4.4.1 Programmable Completion Detection (PCD)                       | 101   |

| 4.4.2 Switch Box (SW) Circuit                            | 102 |

|----------------------------------------------------------|-----|

| 4.4.3 Programmable Delay (PD) Unit                       | 103 |

| 4.4.4 Single-Rail to Dual-Rail Conversion Circuit (CONV) | 104 |

| 4.5 Area, Power and Speed Performance                    | 105 |

| 4.5.1 Area Overhead Calculation                          | 105 |

| 4.5.2 Power Comparison                                   | 106 |

| 4.5.3 Throughput Performance                             | 111 |

| 4.6 Variability Evaluation                               | 112 |

| 4.6.1 PLE Characterisation with Variable Vdd             | 112 |

| 4.6.2 Corner Analysis for PVT Variation                  | 115 |

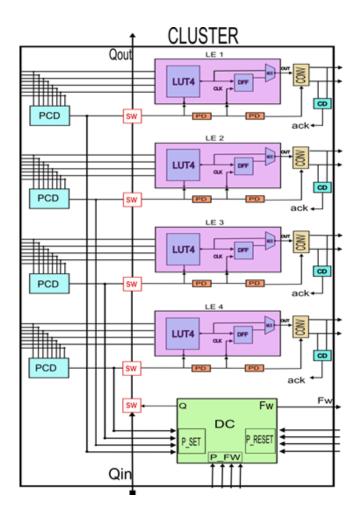

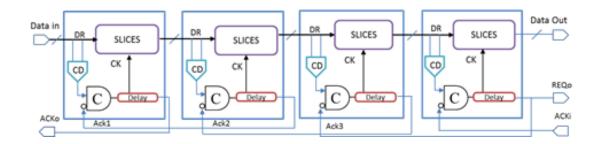

| 4.7 Logic Cluster Design                                 | 117 |

| 4.7.1 Distributed Control with David Cell                | 119 |

| 4.7.2 David Cell Control Transition Flow                 | 122 |

| 4.7.3 Implementation Case Study                          | 124 |

| 4.7.4 Design Flow                                        | 127 |

| 4.8 Summary                                              | 131 |

| Chapter 5. Asynchronously Assisted Logic (AAL) Scheme    | 134 |

| 5.1 Introduction                                         | 134 |

| 5.2 Architecture Overview                                | 135 |

| 5.3 AAL Architecture Implementation                      | 137 |

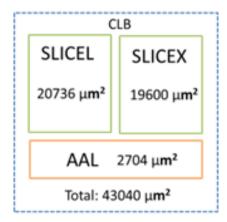

| 5.4 Area Overhead Calculation                            | 138 |

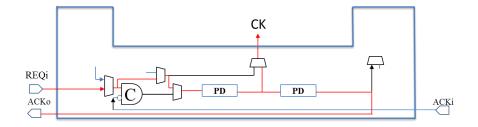

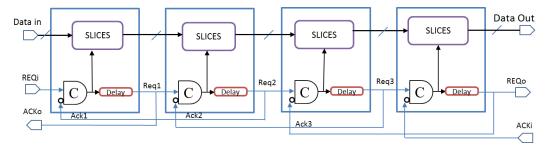

| 5.5 Multi-Style Handshaking Support                      | 140 |

| 5.6 Proposed Variation Aware Design Flow                 | 144 |

| 5.7 Throughput and Operation Energy Study                | 145 |

| 5.7.1 Short Critical Path                                        | 146   |

|------------------------------------------------------------------|-------|

| 5.7.2 Long Critical Path                                         | 148   |

| 5.8 Variability Study                                            | 150   |

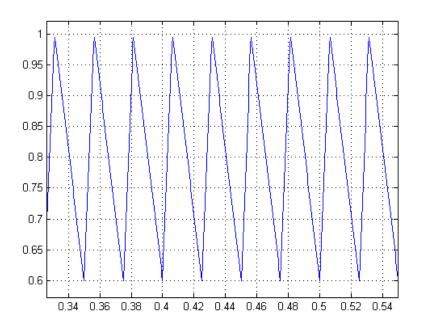

| 5.8.1 Global Variability Simulation                              | 151   |

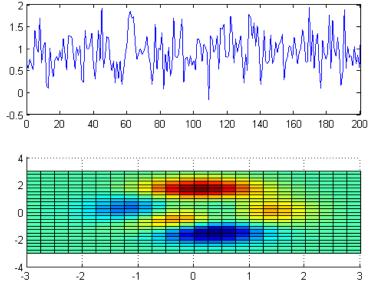

| 5.8.2 Interconnects Variability Simulation                       | 153   |

| 5.9 System Design on AAL structure                               | 155   |

| 5.9.1 Handshaking Support for Data Flow Structures               | 155   |

| 5.9.2 Booth Multiplier Case Study                                | 157   |

| 5.10 Summary                                                     | 160   |

| Chapter 6. Conclusion                                            | 162   |

| 6.1 Summary of Thesis                                            | 162   |

| 6.2 Future Work                                                  | 165   |

| 6.1.1 Variation Aware Design Flow with Consolidated Variation Ma | p.165 |

| 6.1.2 GALS Scheme Support                                        | 165   |

| 6.1.3 Silicon Implementation                                     | 166   |

| Appendix A: Abbreviations                                        | 168   |

| Appendix B: AAL Implementation                                   | 171   |

| Appendix C: Input Vector for Candence                            | 172   |

| Appendix D: Sawtooth Vdd Generation                              | 173   |

| Appendix E: Variation Map Generation                             | 174   |

| Bibliography                                                     | 175   |

## FIGURES

| Figure 1: Design margin barriers to efficiency1                                                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2: Asynchronous handshaking overhead and elastic margin's headroom                                                                                                    |

| Figure 3: Theoretical graph of relative cost of elasticity and handshaking protocols                                                                                         |

| Figure 4: (a) PLA with programmable OR plane; (b) PAL with fixed OR plane<br>[9]                                                                                             |

| Figure 5: (a) Look-Up Table (LUT) Structure, (b) 6-Transistors SRAM Cell. 13                                                                                                 |

| Figure 6: Modern FPGA fabric with Hard-block18                                                                                                                               |

| Figure 7: Basic FPGA and ASIC design flow[17]20                                                                                                                              |

| Figure 8: Key technology comparison vectors                                                                                                                                  |

| Figure 9: Basic logic implementation on the primary logic cell: (a) logic<br>diagram of a 1-bit adder; (b) truth-table for SUM; (c) logic mapping on a<br>lookup-table (LUT) |

| Figure 10: Hierarchy view of FPGA structure: (a) Island style structure, (b)<br>Two slices in a CLB, (c) Basic LC structure26                                                |

| Figure 11: Routing resources structure27                                                                                                                                     |

| Figure 12: Spatial and temporal variation classification                                                                                                                     |

| Figure 13: Subdivisions of process variation                                                                                                                                 |

| Figure 14: Line edge roughness at 90nm and 22nm technology [23]33                                                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 15: Classification of sources of environmental variation                                                                                                                           |

| Figure 16: Inverse path delay characteristics at lower voltage level with                                                                                                                 |

| increase in temperature [29]35                                                                                                                                                            |

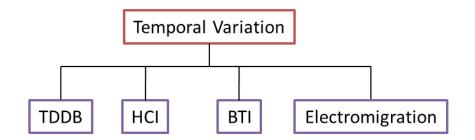

| Figure 17: Ageing related temporal variation                                                                                                                                              |

| Figure 18: Corner analysis with STA tools                                                                                                                                                 |

| Figure 19: Multiple reconfiguration strategy flow49                                                                                                                                       |

| Figure 20: Variation aware chipwise placement design flow [72]51                                                                                                                          |

| Figure 21: (a) Region relocation, (b) Path reconfiguration52                                                                                                                              |

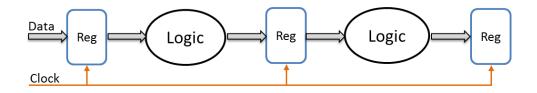

| Figure 22: Synchronous clocking system                                                                                                                                                    |

|                                                                                                                                                                                           |

| Figure 23: Abstract view of Asynchronous Circuit                                                                                                                                          |

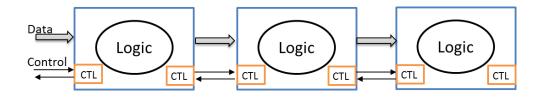

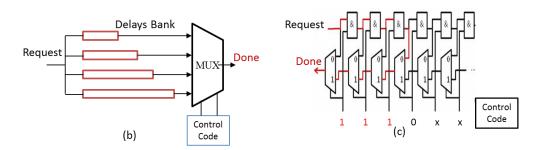

| Figure 24: (a) Abstract view of delay matching bundle-data approach; (b)                                                                                                                  |

| Figure 24: (a) Abstract view of delay matching bundle-data approach; (b) example of programmable delays bank. (c) AND gate and muxes fine tune                                            |

| Figure 24: (a) Abstract view of delay matching bundle-data approach; (b)                                                                                                                  |

| Figure 24: (a) Abstract view of delay matching bundle-data approach; (b) example of programmable delays bank. (c) AND gate and muxes fine tune                                            |

| <ul> <li>Figure 24: (a) Abstract view of delay matching bundle-data approach; (b) example of programmable delays bank. (c) AND gate and muxes fine tune programmable delay [82]</li></ul> |

| Figure 24: (a) Abstract view of delay matching bundle-data approach; (b)<br>example of programmable delays bank. (c) AND gate and muxes fine tune<br>programmable delay [82]              |

| <ul> <li>Figure 24: (a) Abstract view of delay matching bundle-data approach; (b) example of programmable delays bank. (c) AND gate and muxes fine tune programmable delay [82]</li></ul> |

| Figure 24: (a) Abstract view of delay matching bundle-data approach; (b)<br>example of programmable delays bank. (c) AND gate and muxes fine tune<br>programmable delay [82]              |

| Figure 24: (a) Abstract view of delay matching bundle-data approach; (b)<br>example of programmable delays bank. (c) AND gate and muxes fine tune<br>programmable delay [82]              |

| Figure 29: Case study of delay model circuit classification71                                    |

|--------------------------------------------------------------------------------------------------|

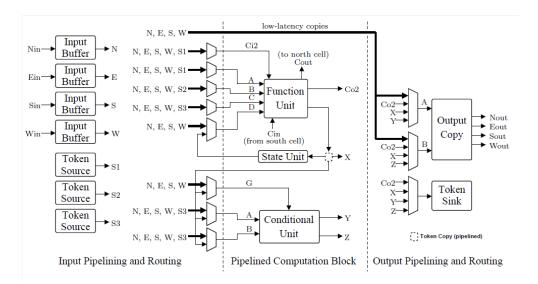

| Figure 30: MONTAGE functional unit (configured as C-Muller gate)75                               |

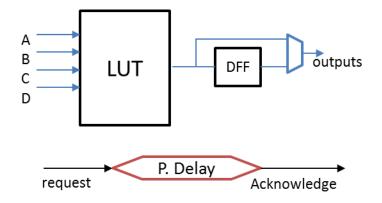

| Figure 31: PGA-STC functional block with programmable delay element76                            |

| Figure 32: PAPA architecture logic block [98]77                                                  |

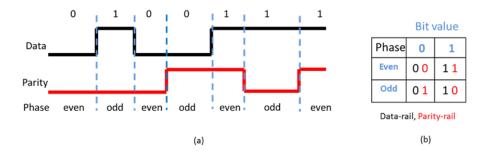

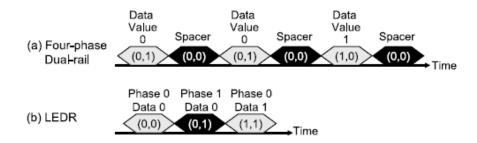

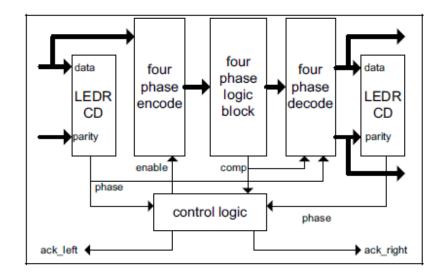

| Figure 33: 4P-DR and LEDR communication80                                                        |

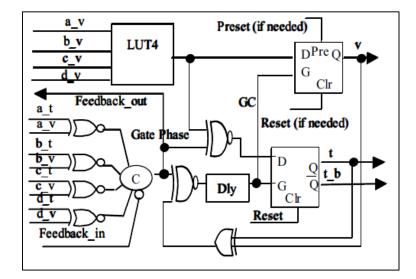

| Figure 34: LUT4-based phased logic gate [115]81                                                  |

| Figure 35: More complex LEDR protocol converter [117]82                                          |

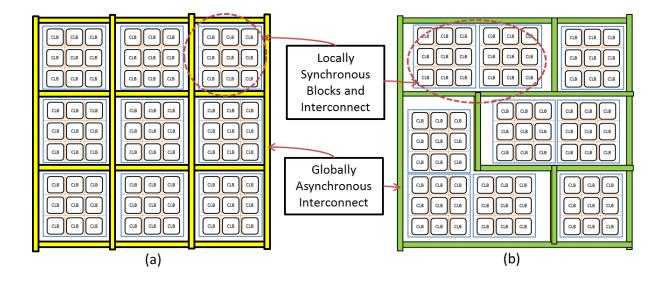

| Figure 36: GALS in FPGA: (a) Homogeneous; (b) Heterogeneous83                                    |

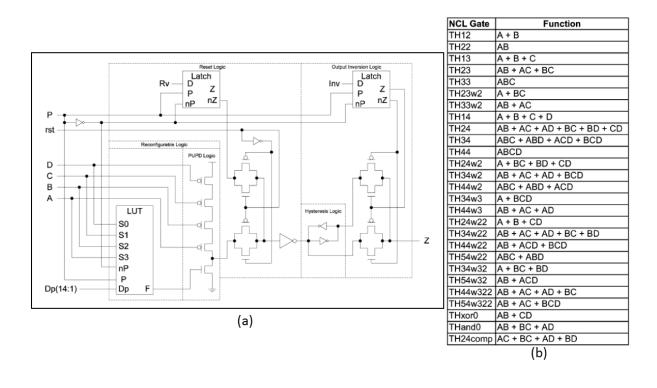

| Figure 37: (a) Basic reconfigurable NCL LE; (b) 27 fundamental NCL gates [127]                   |

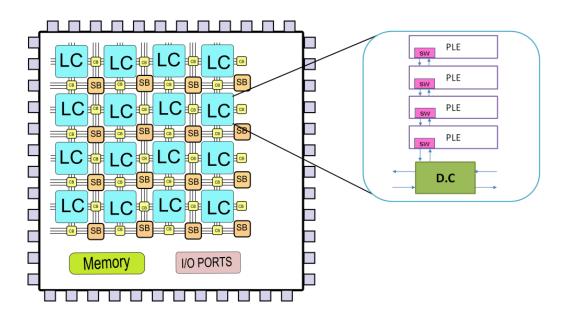

| Figure 38: Island style architecture96                                                           |

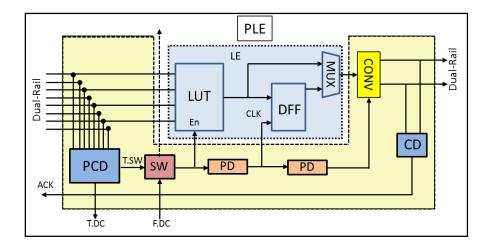

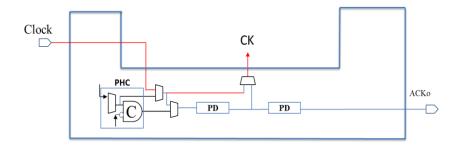

| Figure 39: Wrapper based programmable logic element (PLE)                                        |

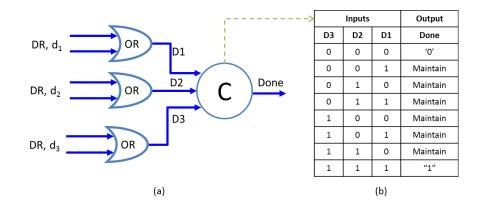

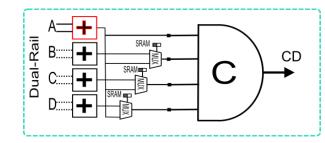

| Figure 40: Programmable completion detection                                                     |

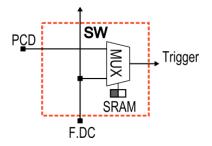

| Figure 41: SW box circuit103                                                                     |

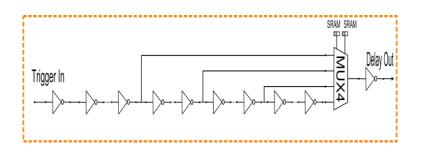

| Figure 42: Programmable delay circuit103                                                         |

| Figure 43: Dual-rail conversion or DEMUX circuit                                                 |

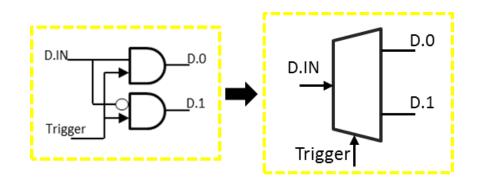

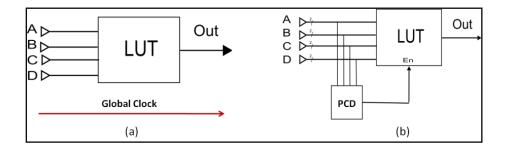

| Figure 44: (a) Synchronous LUT; and (b) PCD asynchronous LUT107                                  |

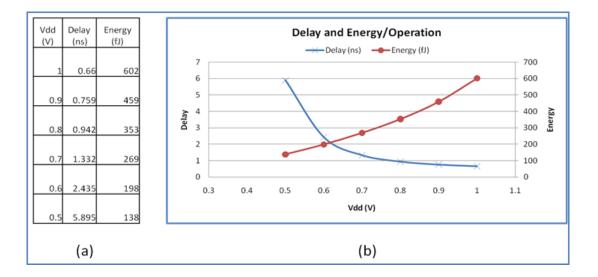

| Figure 45: Operation power: (a) synchronous LUT with timing clock; (b) asynchronous LUT with PCD |

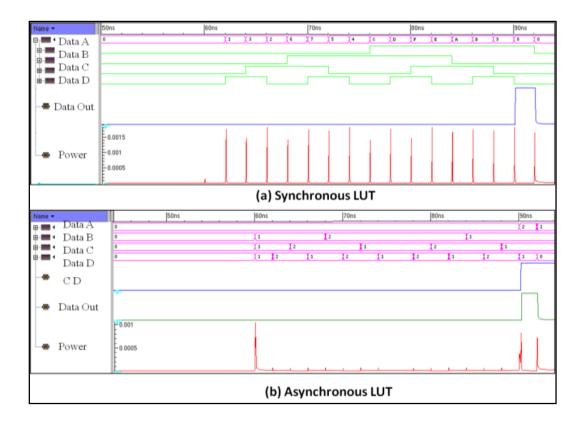

| Figure 46: Delay and operational energy at below nominal Vdd level: (a)            |

|------------------------------------------------------------------------------------|

| results table; (b) delay and energy plot over Vdd113                               |

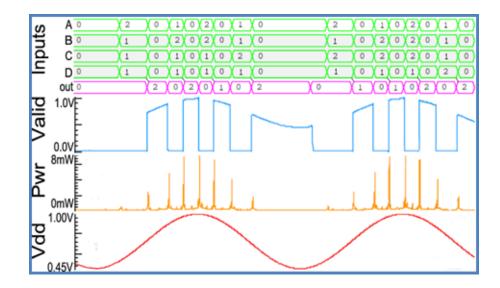

| Figure 47: PLE working under variable Vdd115                                       |

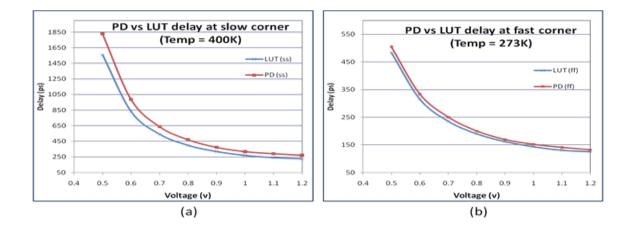

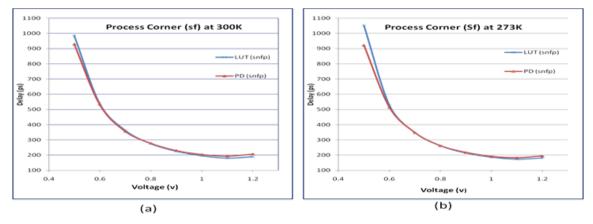

| Figure 48: PD and LUT delay successfully bundling: (a) Slow corner                 |

| (temperature=400K). (b) Fast corner (temperature=273K)117                          |

| Figure 49: Cross over at (sf): corner (a) Temperature=300K. (b)                    |

| Temperature=273K117                                                                |

| Figure 50: Logic cluster with DC119                                                |

| Figure 51: (a) Basic David cell Structure; (b) DC for distributed control; (c) set |

| and reset logic boxes for DC implementations121                                    |

| Figure 52: Data flow transition example with DCs                                   |

| Figure 53: Four bit full Adder example125                                          |

| Figure 54: System design flow129                                                   |

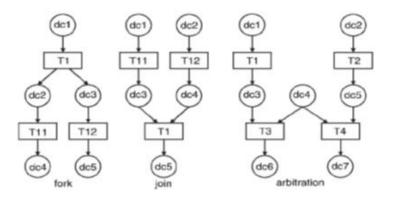

| Figure 55: Petri net models of control elements                                    |

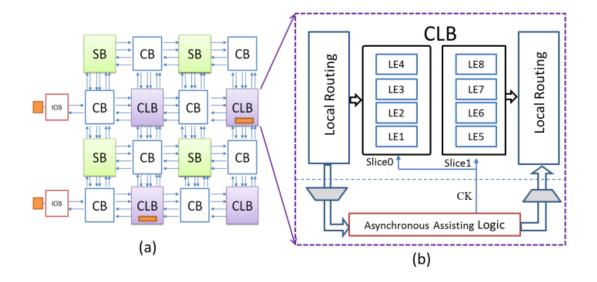

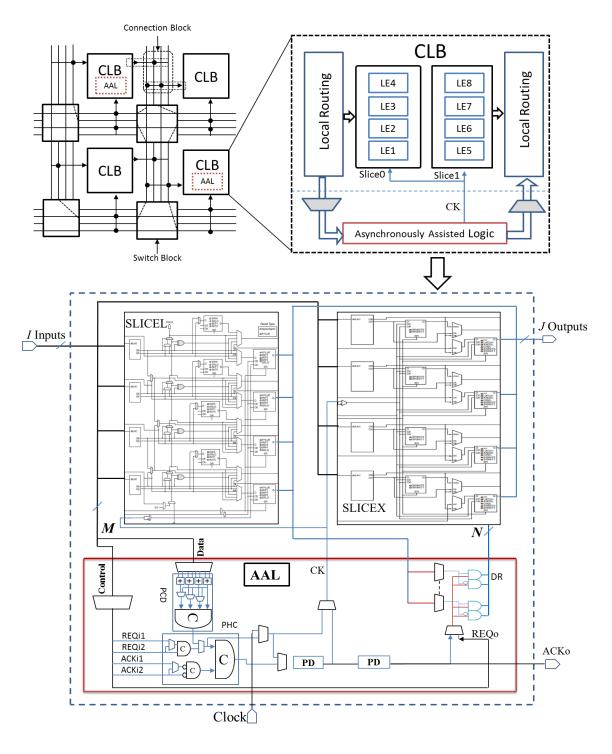

| Figure 56: Architecture overview: (a) Island style architecture, (b) AAL           |

| within a CLB                                                                       |

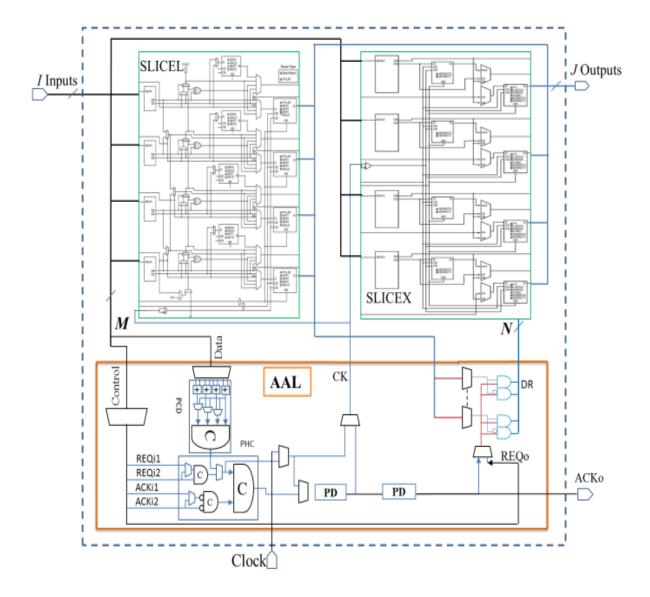

| Figure 57: AAL plugin to Xilinx's CLB with SLICEL & SCLICEX                        |

| Figure 58 Area calculation of CLB with AAL                                         |

| Figure 59: Dual-Rail Completion-Detection (DR-CD) resources141                     |

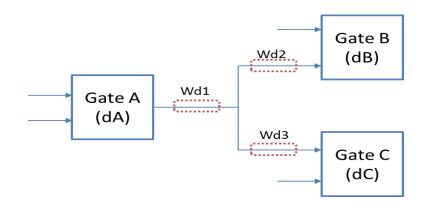

| Figure 60: Four Stages implementation of DR-CD circuit                             |

| Figure 61: Single-Rail Bundle-Data (SR-BD) resources143                      |

|------------------------------------------------------------------------------|

| Figure 62 Four Stages implementation of SR-BD circuit143                     |

| Figure 63: Clock triggers switching144                                       |

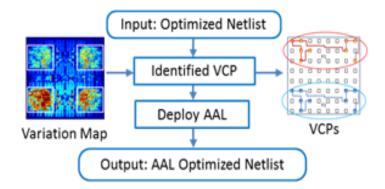

| Figure 64: Design flow based on variation map145                             |

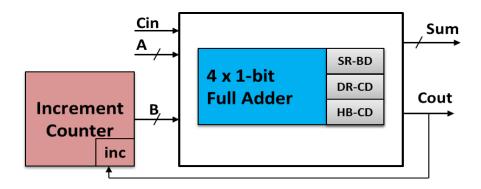

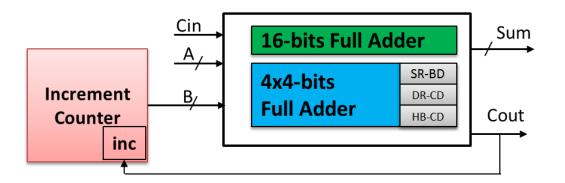

| Figure 65: Test setup for 4RCA147                                            |

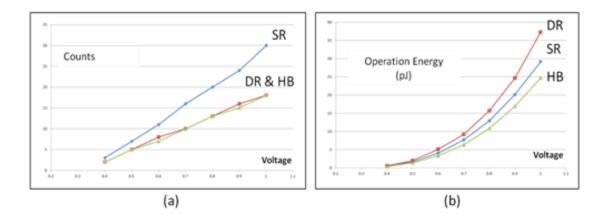

| Figure 66: Throughput and energy comparison (Voltage sweep, 0.4 - 1.0v), (a) |

| Throughput (Counts), (b) Operation Energy (pJ)148                            |

| Figure 67: Test setup for 16RCA and 4x4RCA149                                |

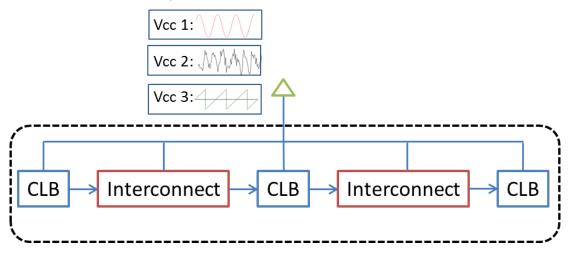

| Figure 68: Global Vdd variation simulation setup151                          |

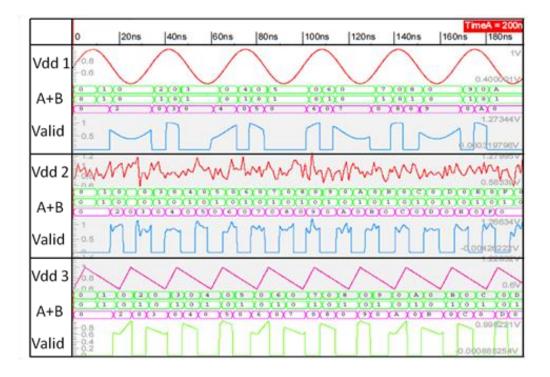

| Figure 69: Correct operation under various viable voltage supplies           |

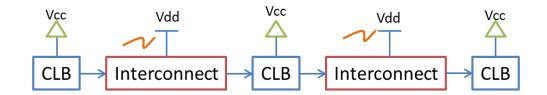

| Figure 70: Mixed constant Vcc on CLB and variable Vdd on interconnect        |

| simulation153                                                                |

| Figure 71: Interconnect variation simulation results155                      |

| Figure 72: Block diagram of Booth multiplier158                              |

| Figure 73 : Petri-net representation of booth multiplier control flow158     |

| Figure 74: Simplified SR-BD handshaking diagram for Booth multiplier158      |

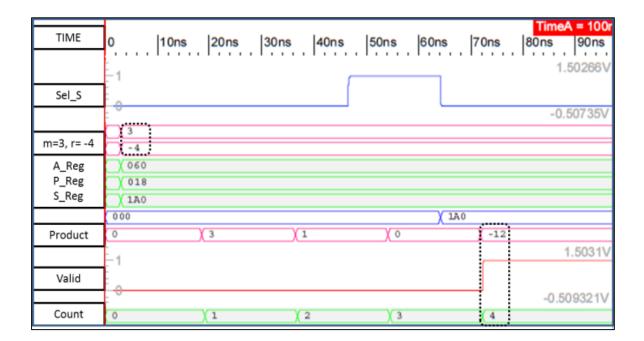

| Figure 75: Simulation waveform of Booth multiplier implementations 159       |

## TABLES

| Table 1: Key configurable cells technology comparison[9].    16 |

|-----------------------------------------------------------------|

| Table 2: Summary of asynchronous FPGAs    73                    |

| Table 3: Choice of architecture structure.    97                |

| Table 4: Dual-rail code-words.    101                           |

| Table 5: PLE size in terms of number of transistors.       105  |

| Table 6: Power and energy comparison.    110                    |

| Table 7: Throughput comparisons of various architectures111     |

| Table 8: Overhead of various asynchronous schemes               |

| Table 9: Comparison result for short path (4RCA).    147        |

| Table 10: Throughput and energy performance149                  |

| Table 11: Data flow control elements.    156                    |

## 1 Introduction

### 1.1 Motivation and Objective

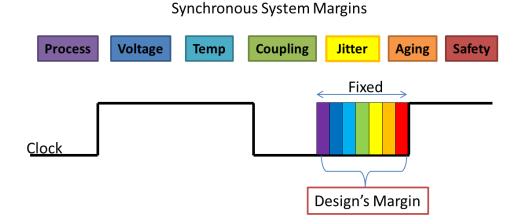

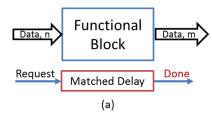

The effects of variability have become increasingly significant as a result of the scaling of technology. Static and dynamic variations affect the reliability of integrated circuits. Conservative approaches to increases the timing-margin/guard-band across the whole chip is imprudent and degrades performance. Figure 1 shows that excessive design margins to guarantee correct circuit operation over fix periods for both spatial and temporal variations are wasteful and reduced the circuit's efficiency in a synchronous system [1, 2]. (Note: the scale of the margins in Figure 1 and Figure 2 are for illustration only and may not scale accordingly).

#### Figure 1: Design margin barriers to efficiency.

FPGAs may be more affected compared to Application-specific integrated circuit (ASIC) because the circuit mapping and critical path vary depending on

user design in post-fabrication [3]. Therefore various traditional variation tolerance techniques proposed for ASICs may not be directly applicable. Yet, due to its configurability, the FPGA presents a unique opportunity to address variability and reliability challenges [4, 5].

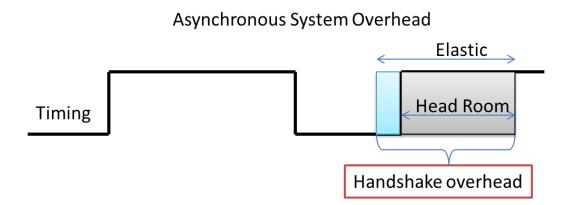

Asynchronous designs are highly tolerant to voltage and delay changes, and have been shown to be very robust in the present of variations [6, 7]. This also gives the potential for efficiency improvements in the margin headroom as shown in Figure 2. Therefore, applying asynchronous logic to FPGAs is an attractive idea.

# Figure 2: Asynchronous handshaking overhead and elastic margin's headroom.

However, there are three major challenges in applying asynchrony in balancing between the handshaking overhead and level of tolerances, as illustrated in Figure 2. These challenges are as follows:

i. Asynchronous circuits are more difficult to design and test compare to synchronous ones because of the wide variety of possible signalling

protocols and a broad spectrum of the degree of delay insensitivity from bounded-delay to fully delay insensitive (DI). Partly because of this, asynchronous designs suffer from a lack of automatic design tools, especially those combining all possible techniques in a single suite. These issues have impeded the progress of asynchronous techniques in the FPGA, because the latter is intrinsically less customizable.

- Asynchronous circuit is normally higher in area and power overheads due to the extra circuitry needed for handshaking. This depends on the delay assumption made or the protocols used. For example, converting all of the communication to dual-rail will double the interconnect resources. This is not acceptable, since interconnects occupy the lion's share of the fabric.

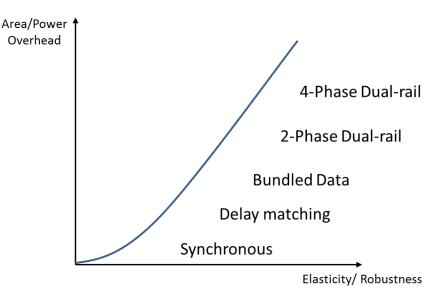

- iii. Depending on the timing assumptions made or handshaking protocols used, asynchronous logic can provide a range of improvements in power and speed/throughput efficiency in addition to its robustness toward variability. For instance, a single-rail delay-matching (SR-DM) protocol is more efficient in terms of power and area but more susceptible to variation compared to the 4-phase dual-rail (4P-DR) scheme which is more robust to variation but may require higher power and area as shown in theoretical graph in Figure 3 – relative cost of elasticity and handshaking protocols. Similar project of cost of elasticity using different asynchronous tools also presented in [8].

# Figure 3: Theoretical graph of relative cost of elasticity and handshaking protocols.

Therefore the objective of this thesis is centred on strategies which can maximise the variation tolerance benefit and keep the overhead at a balance. The challenges mentioned above are addressed using the following approaches:

- i. A wrapper-based asynchronous logic approach to communication and the preservation of the LUT-based computation block of modern FPGA architecture. This allows the re-use of the major part of the design tool flow, particularly the logic packing and mapping. It seeks to achieve *delay insensitive (DI)* in the large for long inter-cluster wires and *speed independence (SI)* in the small within clusters.

- ii. Characterising the performance of the most popularly used handshaking protocols that are tailored for reconfigurable logics. The power, throughput, area and robustness are determined of protocols

such as 4-phase dual-rail (4P-DR), 2-phase dual-rail (2P-DR), and bundled-data (BD).

iii. A strategy to balance the use of asynchrony to tolerate the effects of variations and the minimization of the area and power overheads.

### 1.2 Overview of Chapters

Chapter 2 gives an introduction to the development of programmable logic devices (PLDs) and their evolution into today's modern FPGA architectures. The continued scaling of CMOS technology enables the development of many advanced technologies. However the associated challenges include increasing variability problems in the manufacturing process as well as the effects of degradation effects over time. The second part of the chapter classifies the sources of variability and reviews its impact on FPGA structure as well existing techniques which attempt to reduce the impact.

Chapter 3 presents a literature review of the use of asynchronous approaches. The fundamental theory and terminology of asynchronous design are also briefly introduced here to serve as a basis for further understanding of the following chapters.

Chapter 4 describes the distributed control architecture which retains the computational block of the traditional FPGA un-touched (single-rail) and proposes the asynchronous wrapper and David's cell control around it. The

5

Chapter 1: Introduction

result achieves a balance between the desire to use asynchrony for tolerate the effects of variations and retention of the major part of the current design flow.

Chapter 5 presents new concepts for addressing the overhead challenges with an on-demand strategy. This approach suggests the deployment of asynchronous logic only on variation-critical paths (VCPs) by leveraging the mature techniques in obtaining variation maps. The proposed integration of asynchronously assisted logic (AAL) with state of the art FPGA architecture involves a minimal increase in overhead. Furthermore, the AAL supports the use of multi-style asynchronous logic implementation to allow the exploration of asynchrony at different levels of variation.

Chapter 6 summarises the techniques presented and describes the outlook for future developments.

## **1.3 Contributions**

- Classification of sources of the variability and its impact on FPGA architecture (chapter 2)

- Survey of asynchronous reconfiguration architectures based on the protocols and delay assumption used (Chapter 3)

- A detailed circuit realization at components level for the asynchronous wrapper using the distributed control approach for asynchronous components (Chapter 4)

6

- The proposal of a novel AAL architecture that applied Asynchrony only on the VCPs for the balancing of resource overhead and variation tolerance (Chapter 5)

- Summaries the work and proposed techniques for advancement.

(Chapter 6)

### **1.4 Publications**

The following papers have been published during the course of this work:

H. S. Low, D. Shang, F. Xia, and A. Yakovlev, "Variation tolerant asynchronous FPGA", poster presented at the 19th ACM/SIGDA International Symposium on Field-Programmable Gate Arrays (FPGA 2011) conference, Monterey, California, pp 282, 2011.

H. S. Low, D. Shang, F. Xia, and A. Yakovlev, "Variation tolerant AFPGA architecture", presented at the 17th IEEE International Symposium Asynchronous Circuits and Systems (ASYNC 2011), Ithaca, NY, pp 77–86, 2011.

X. Zhang, D. Shang, F. Xia, H. S. Low, and A. Yakovlev, "A hybrid power delivery method for asynchronous loads in energy harvesting systems", in *IEEE 10th International New Circuits and Systems (NEWCAS 2012)* conference, Montreal, Canada, pp 413-416, 2012.

H. S. Low, D. Shang, F. Xia, and A. Yakovlev, "Asynchronously Assisted FPGA for Variability", poster presented at the *Field Programmable Logic and Applications (FPL 2014)* conference, Munich, Germany, 2014.

## Chapter 2. Background

#### 2.1 Introduction

Field-programmable Gate Arrays (FPGAs) have become a popular technology for implementing digital electronic systems today due to their reconfigurability nature and short design cycle. Continued technology scaling enables more and more features to be implemented in a same size form-factor. However, similar to other VLSI design, many new challenges emerged due to the continued scaling of CMOS process technology. Variability and reliability have become growing issues in the nanometre scale region.

In order to understand the impact of variation on FPGA architecture, this chapter first provides an overview of FPGA technology and its development in recent years. Variation can be from many sources due to imperfection of manufacturing process, environmental changes or ageing effect resulting in correlated and random behaviour. This chapter also serves to clarify the terms by classification of the variability sources and technique commonly used to characterise them. On-chip, off-chip and soft-sensing classification techniques will be reviewed.

With the understanding of the variability through the characterisation techniques available from industry as well as academic research, improvements of performance and yield can be achieved through variation aware techniques that are unique for reconfigurable architectures such as

9

FPGA. The remainder of the chapter is structured into the following subsections:

- i. Introduction to FPGA Technology

- ii. Classification of Variability Sources

- iii. Sensing and Characterisation Techniques

- iv. Variation-tolerant and Yield Improvement Techniques

#### 2.2 Introduction to FPGA Technology

The FPGA is a hardware programmable device whose function can be defined after fabrication. The concept of the reconfigurable logic device was introduced in the electronic system design market in 1980s. The reason for the initial development of reconfigurable devices was mainly to ease the challenges faced by the traditional board-level design with standard components that increased in number with circuit complexity and size. The amount of components and layers of printed circuit boards (PCBs) grew drastically and thus the chance interconnection errors occurring increased together with the pressure on create a small form factor to fit the components into the enclosure.

Fuelled by the fast-moving market and evolving standards and rising of mask development costs in the manufacturing applications-specific integrated circuits (ASIC), the concept of the programmable logic device (PLD) that would allow its functionality to be restructured was born and has served the basis for more advance in PLDs.

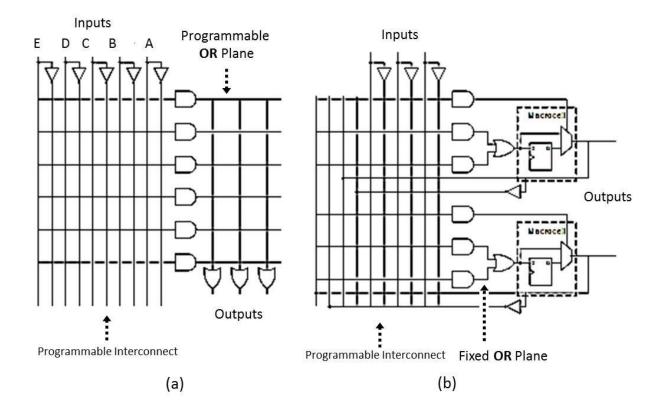

The programmable logic array (PLA) was one of the earliest types of PLD. Figure 4 (a) shows a typical structure of a PLA consisting of a matrix of programmable AND-gates and OR-gates in a plane used to implement the minimised standard forms of Boolean expressions, which are sum-of-products functions.

Figure 4: (a) PLA with programmable OR plane; (b) PAL with fixed OR plane [9].

With the realization that even with a fixed OR plane, the system would still be sufficient for logic implementation as a PLA, interconnect optimised programmable array logic (PAL) structures were introduced in 1978 [10], trademarked by Monolithic Memories, Inc. (MMI). As illustrated in Figure 4 (b), the architecture was evolved with the removal of the programmable ORplane and the introduction of new macro-cells that contained registers and multiplier for optional combinational or sequential logic implementation. The concept of the PAL was then extended to offer more complex logic functionality, and was later succeeded in the market by a new family called complex PLDs (CPLDs).

Although the level of logic complexity has increased, yet the main market for CPLDs was still not able to go far beyond a glue-logic within large systems. FPGA architecture based on the Look-Up Table (LUT) then emerged, which offered more features rich solutions.

#### 2.2.1 Moore's Law and Configuration Cells

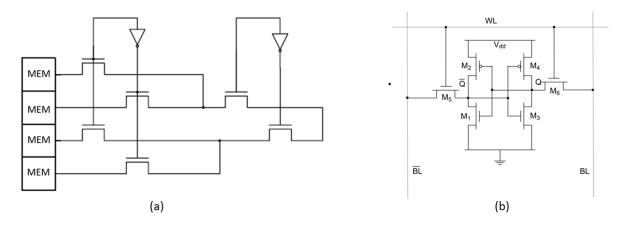

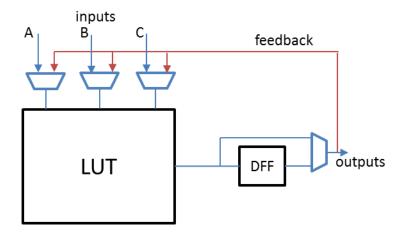

Figure 5: (a) Look-Up Table (LUT) Structure, (b) 6-Transistors SRAM Cell.

Gordon Moore, co-founder of Intel, forecast in his 1965 paper, "Cramming more components onto integrated circuits" [11] that the cost of transistors in a silicon chip would continue to fall with every advance of technology every two years or so, and later the prediction turned into a self-fulfilling prophecy. The doubling of numbers of transistors every 18 months following Moore's Law has stimulated drastic growth in the electronics industry. The doubling of transistor number at a rapid rate has also meant reductions in the cost per transistor with every new generation of smaller transistors. This benefited the advances in FPGA technology in the market in the mid-1980s. This is because the LUT-based FPGA, as in Figure 5 (a), used static-random-access-memory (SRAM) as the basis of the architecture and the typical SRAM circuit requires six transistors, as shown in Figure 5 (b), which means the configuration memory cell comes with a high overhead. However, with the growth indicated by Moore's Law, up to this point this has led the industry to exploit transistors which are almost free, especially in programmable hardware devices. This validated the area and cost overhead issue on SRAM-based FPGA.

#### 2.2.2 Programmable Memory

Programmable memory or the configuration cells are the underlying technology for hardware configurability. Earlier PLD devices used programmable read-only memory (PROM) where the programming could only be done once and was irreversible; namely the on-time-programmable (OTP) memory. Anti-fuse memory type, which is one, is more beneficial in terms of lower area, resistance and capacitance compared to others. Because it is a nonvolatile memory, this means that the system can work instantly at power-up in contrast to SRAM. In addition, the prime advantage of the anti-fuse PLD and the FPGA are their susceptibility to faults in environment with heightened radiation. In particular, the Actel/Microsemi [12] PLDs dominated the military and aerospace markets for over fifteen years [13]. However, the main disadvantage of anti-fuse FPGAs is that it requires specialised manufacturing and programming mechanism. This make it not in-system programmable as opposed to SRAM, which can fit well within the standard CMOS manufacturing process, the anti-fuse technology cannot scale and advance at the same rate as CMOS devices, making it far behind the process geometry in many generation in comparison.

14

An alternative Non-volatile memory that supports multiple re-write cycles and is convenient for in-system programming is the EEPROM (electrically erasable programmable read-only-memory) or flash memory. Technically this is a type of EEPROM but offers higher speed when writing large amounts of data compared to non-flash EEPROM memory. In addition, flash memory also offers fast read access times similar to DRAM (dynamic RAM) but slower than SRAM. The key advantages of flash based FPGA over SRAM are its low power requirement, non-volatility and it is also more secure and reliable for IP (intellectual property) protection purposes from a security standpoint as no extra external configuration memory required upon start since SRAM is volatile and cannot hold the data at power lost. However, the disadvantages of flash memory are its limited write cycle and the fact that specific manufacturing processes are used which differ from standard CMOS technology.

SRAM is the most popular type of memory used in today's FPGAs for two primary reasons. First, it offers the unlimited in-system programming and second the standard CMOS process technology is used and therefore, it benefits from the advances of the latest scaling of CMOS technology. However, continuous technology scaling may also have adverse impacts, which are discuss later in this chapter.

Unlike flash-based non-volatile devices, the volatile SRAM-based FPGA cannot hold its configuration without power source. Therefore, a dedicated

15

programming circuity and sequence is needed to load the configuration bits at every system power-up. This also means that SRAM-based FPGA has a leadtime at power-up before live operation and requires extra board-level nonvolatile components, which increase the overall cost. Since the configuration data are stored externally, this also opens up the potential for IP protection issues, although alternative encryption solutions may eliminate this. A summary and comparison of these three main types of memory are show in Table 1.

| Memory Type           | Anti-fuse             | Flash                   | SRAM          |

|-----------------------|-----------------------|-------------------------|---------------|

| Features              |                       |                         |               |

| Non-Volatile          | Yes                   | Yes                     | No            |

| Reconfigurable Cycle  | one-time              | Limited                 | Unlimited     |

| Area (element size)   | Low                   | Moderate                | High          |

| In-System programing  | No                    | Yes                     | Yes           |

| Manufacturing Process | Anti-fuse custom      | Flash process           | Standard CMOS |

| Speed                 | Fast read, slow write | Fast read, slow rewrite | Fast          |

Table 1: Key configurable cells technology comparison[9].

#### 2.2.3 Modern FPGA Fabric

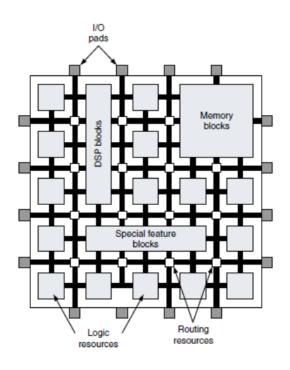

The tradition basic FPGA architecture consisting only of reconfigurable logic, an interconnect block and the input/output (I/O) pad is call *s*oft fabric. Today's state-of-the-art PFGAs are packed with over a million LUTs. Also more and more hard blocks have been included in the package to improve computation performance, including the digital-signal-processing (DSP) block, distributed memory, high-speed communication links, and an advanced clock management system together with mixed signal analogue functionality. This has made the architecture increasingly heterogeneous as illustrated in Figure 6. In hybrid structures, combinations of hard and soft microprocessor cores are also included. With the advances in FPGA technology, the use of mature intellectual property (IP) and computer-added-design tools (CAD) have also facilitated the emergence of user customisable system-on-chip (SoC) FPGAs that provide significant benefits for embedded system implementation. Chapter 2 Background: FPGA Technology and Variation Sources

Figure 6: Modern FPGA fabric with Hard-block

#### 2.2.4 Software and Hardware Programmable Devices:

Compared to general-purpose microcontrollers and microprocessors (µPs), FPGA-based circuit implementation is typically much faster. This is because in the FPGA, It is not necessary for the controller to move the data around between the data memory and working register in order to perform logic operations or in the context terms, the sequential fetch-decode-execute loop of The soft-computation. classic examples of software-programmable architectures are Von Neumann and Harvard processors. Instead, the underlying computation in FPGA is hardware-based. All of the possible combinations of output from a set of inputs is pre-calculated with Boolean algebra expression in a truth table and Karnaugh map and stored in the LUTs. The arrival of inputs will essentially become the address pointer to the specific memory location of the LUT; therefore, complex and multiple iteration computations can be avoided and results can be obtained almost instantly. Similar techniques have also been used in microcontrollers to achieve the fast computation of complex calculations by using the "not-to-compute-all" technique or, in other words prefetching or pre-calculating and storing all possible results on LUTs[14]. This technique is very effective and commonly used in embedded system design to decrease computation time. In the FPGA, LUT techniques are exploited intensively across the whole architecture.

#### 2.2.5 Difference between the FPGA and ASIC

The application-specific integrated circuit (ASIC) is a general term for fully customised designs. The main benefit of a device that is fully custom-designed is its smaller form factor from its manufacturing specifications and lower cost for high volume production. Whereas the FPGA is a hardware programmable device that its functionality can be configure by the end user after fabrication, which explains the term "field-programmable". The key advantages of the FPGA over ASIC are the low non-recurring engineering cost, which support rapid prototyping and fast-time-to-market. However, the disadvantage is that the FPGA may not be suitable for most electronic system design specifications because FPGAs are used for general purposes and therefore the logic density of the chip is multiple folds below that of the ASIC design. This translates into higher power consumption, higher cost and slower speed performance compared to equivalent systems implemented with ASIC. However, due to the advancement of CMOS processes and the introduction of more "hardened" blocks such as multipliers and accumulators, the performance gap between FPGAs and ASICs is gradually becoming smaller [15, 16].

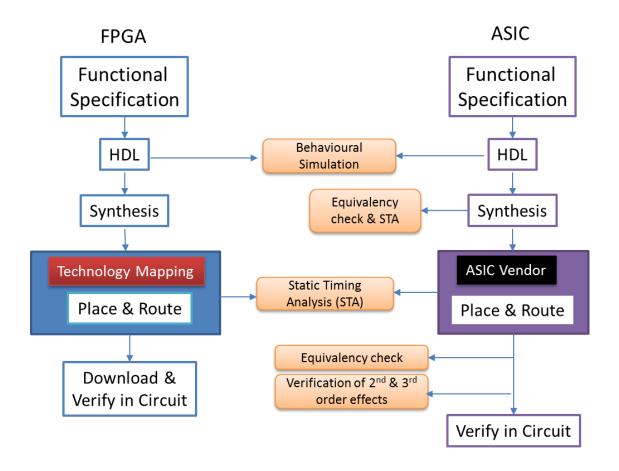

#### Figure 7: Basic FPGA and ASIC design flow[17].

The design of ASICs and FPGAs, however, shares a very similar tools flow. This is especially true for the upper part of the design flow, from functional specification normally in HDL (hardware description language) to logic synthesis and optimisation and later placement and routing. The difference in placing and routing at this point between the two flows is that the logic has to be packed and clustered into a fixed prefabricated structure on the FPGA and the routing resources to join them together, whereas the placement and routing on the ASIC are free. These similarities between the two flows are shown in Figure 7. Thus, historically, a main application of the FPGA was primarily used for ASIC prototyping or function verification before committing costly manufacturing processes. Due to the levelling of performance, competitive cost and 'harden core' enhancement, FPGAs now move beyond their historical use and are becoming the core technology platform for applications such as high speed signal processing, industrial control, communication network data network switching and high frequency financial trading and computation accelerators.

#### 2.2.6 Summary of Evolution

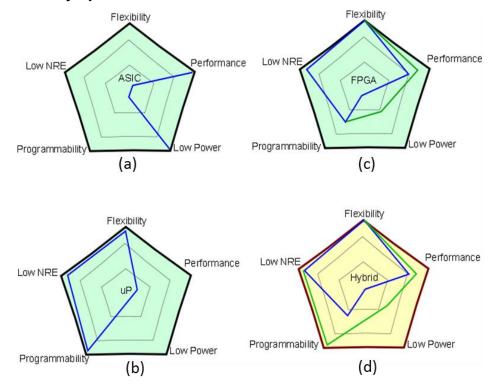

Figure 8: Key technology comparison vectors.

This section summaries the different between FPGA and two other key technologies for electronic system design, the microprocessor ( $\mu$ P) and ASIC. In Figure 8 (a), the main drives for the ASIC approach are mainly toward ultimate higher speed and lower power performance. However, the NRE costs for custom design, layout, fabrication and packaging are high. The mask for the silicon process is itself extremely expensive with a limited lifespan. However, in mass production runs this is still more cost-effective. From the reconfigurable software perspective, the standard processor architecture is more flexible in term of hardware configuration (such as I/O pin configuration), low non-recursive engineering costs and firmware programmability. However,

the downsides are that it is high in operating system overheads and compiler inefficiency, and there may also be a performance reduction due to the indirect relationship between the hardware and the software on the processor [18], as shown in Figure 8 (b).

Programmable devices or the FPGA architecture fit in between the other two design approaches and offer the greatest hardware configuration flexibility and higher performance compared to general processor approaches as well as lower NRE costs compared to the ASIC. In recent and past decade, advances in research and on the FPGA has been largely focused on improving the speed performance and optimising power consumption, as illustrated in the green line in Figure 8 (c). Given the benefit for both application-specificity and flexibility in a larger system, modern FPGAs are now also blending more and more application-specific hard-blocks with their traditional soft-fabric forming new hybrid architectures. The motivation for and benefit from the hybrid structures are also illustrated in the green line in the yellow pentagon at the bottom left of Figure 8 (d).

#### 2.2.7 Fundamental Structure of the FPGA

This section explains the underlying building block of the FPGA soft-fabric architecture and the terms associates with it from the most basic primary elements to the hierarchy which is build up.

## 2.2.8 Logic Block

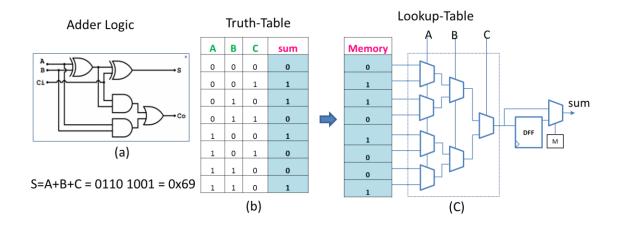

The basic building block in a FPGA comprises a lookup-table (LUT), a register (DFF) and a multiplexer (MUX), as shown in Figure 10(c). It is normally called a logic cell (LC) in Xilinx, while the equivalent from Altera is called the logic element (LE). For ease of explanation, Xilinx's terms will mainly be used in this thesis. Figure 9 demonstrates the primary concept of a simple logic implementation on a FPGA. This example demonstrates the implementation of basic logic circuit of a single bit adder in Figure 9 (a). The truth-table is first derived (Figure 9 (b)), this process is normally supported using a synthesis CAD tools. The synthesis processes basically computes each value of the logical expression of the circuit according to their functional arguments. In this example, the expression of sum = A + B + C = 0x69 is stored in the k-input size lookup-table or K-LUT as shown in Figure 9 (c). The memory size of the LUT is defined as  $2^k$  bits or 8 in this case for K = 3. Although the 4-LUT was once the more common structure, traditionally introduced because of area efficiency, it should be noted that modern FPGA structures are already built-in with 5 to 7 LUTs for better speed performance.

## Figure 9: Basic logic implementation on the primary logic cell: (a) logic diagram of a 1-bit adder; (b) truth-table for SUM; (c) logic mapping on a lookup-table (LUT).

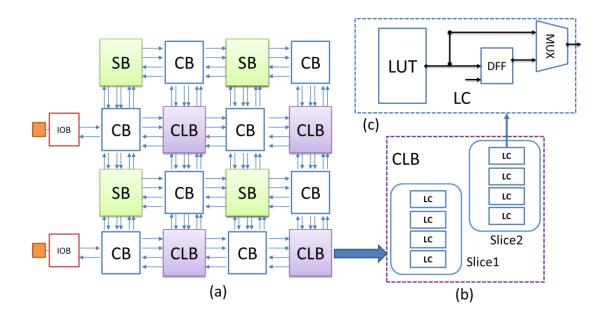

Figure 10 (a) shows a basic view of island-style FGA architecture. The cluster is the next level in the hierarchy of this architecture, consisting of a group of primary logic cells (LCs). In Altera, the terminology used is the logic array block (LAB); whereas deviating from Altera, Xilinx has another layer of hierarchy, a group of LCs called the SLICE and the two SLICEs constitute a Configurable Logic Block (CLB). The main idea for grouping LCs within a CLB is to avoid long global interconnects.

Figure 10: Hierarchy view of FPGA structure: (a) Island style structure, (b) Two slices in a CLB, (c) Basic LC structure.

## 2.2.9 Routing Structure

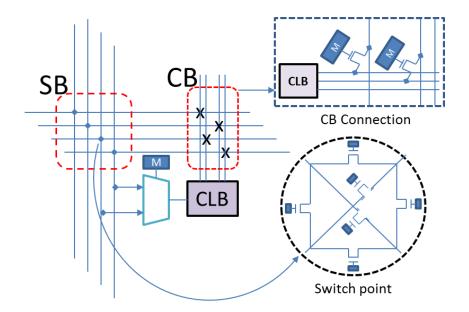

Surrounding the CLBs in the island style structure are the routing resources. The connection block (CB) links the inputs and outputs of CLBs with programmable switches. The interconnect grids are made of prefabricated wiring segments, and at each vertical and horizontal interaction of the wiring segments is a switching block (SB). The SB also consists of a set of switches that allows the possible routing of signals to the next intended CLB destination. For clarity of explanation, a simplified CB and SB block connected with only a few switches are shown in Figure 11.

Figure 11: Routing resources structure. **2.3 Introduction to Variation**

Variations have become more dominant with the continued scaling of the CMOS process. The complexity has increased, resulting in higher fabrication costs to achieve uniformity in die production. This limitation can result in random and spatially varying deviations from intended design parameters, and affecting speed, power and reliability. Conservative approaches to increase the operating timing margin across the whole chip to reduce the impact of parametric yield are imprudent and reduce performance, especially when the consideration is based on worst-case scenarios.

In addition to the physical parameter variation, dynamic environmental sources of variation such as temperature, or supply voltage changes during operation require engineers to employ more aggressive techniques. Similar to all other CMOS devices, FPGAs are no exception. In fact, the impact of variation could be more severe compared to ASICs, because the circuit mapping and critical path routing processes may result in any combination of worst and best case variability path or regions. This section provides a general description of sources of variation and discusses its impact on FPGA technology. Finally published variation tolerance techniques are reviewed.

# 2.4 Classification of Variability

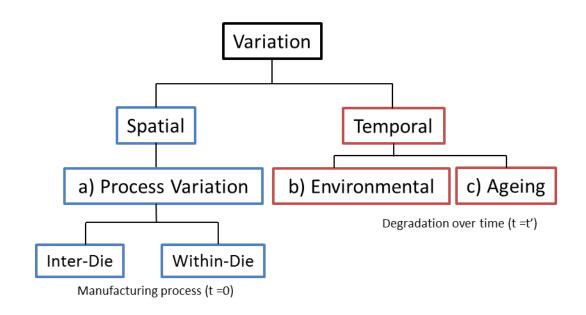

Sources of variation can be classified into two main categories. First, the imperfection during manufacturing and second operational environmental changes, degradation over time due to ageing and wear-out can all be broadly categorised as either spatial or temporal variations [19]. Figure 12 clarifies the classification of variation based mainly on timeline since the devices was manufactured. For spatial variation, the time assumption is constant (t=0s), and the changes of devices in the characteristics over time are therefore considered temporal (t = t').

#### Figure 12: Spatial and temporal variation classification.

- a) Process variation or the spatial variation mainly involves imperfection during the manufacturing process resulting in parametric deviation of transistor value between different die (inter-die) as well as variation within a same die (within-die/ Intra-die). Inter-die variation is a systematic type of variation which generally shows spatial correlation behaviour and normally results from varying MOS transistor dimensions in length or width (L/W), oxide thickness (TOX), and flatband condition [20] whereas line-edge-roughness (LER) or randomdopant fluctuations (RDFs) cause within-die variation with stochastic characteristic [21].

- b) Temporal variation, on another hand is due to changes in the characteristics of a device over its lifetime. Temporal variations can also be divided into two main branches, which are environmental and ageing,

where voltage and temperature variations can be classified as environmental.

c) Negative and positive bias-temperature instability (NBTI & PBTI), hotcarried-injection (HCI), time dependent dielectric breakdown (TDDB), and electromigration all fall into the Ageing category [22, 23].

# 2.5 Process Variation Sources

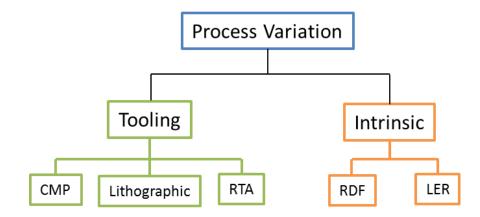

Figure 13 gives a summary of the key factors in process variations, which can be either systematic or statistical. Systematic variations are caused by imperfection in the mask and optical tooling mechanism and result in repetitive offset from chip-to-chip. Systematic variability is deterministic, and therefore can be estimated and improved using specific design techniques; however intrinsic variations are statistical and thus the impact cannot be reduced through improvements in the manufacturing process [24]. The following briefly explains and classifies them into two main categories of tooling-related and intrinsic variation.

Figure 13: Subdivisions of process variation.

#### 2.5.1 Tool-Related Variation

Optical lithography has been effectively used in fabrication for over thirty years. Due to technology scaling, optical lithographic are now in the subwavelength region where the feature sizes of the devices or transistors are now below the wavelength ( $\lambda$ ) of light. For example, the value of  $\lambda$  has remained at 193nm from 130nm to more recent 65-nm transistors [25]. Therefore, it has become extremely difficult to print the wafer exactly as intended on the layout [22]. Chemical mechanical polishing (CMP) is used for planarizing the metal interconnect layer between adjacent metal layers due to copper damascene process. Variations in interconnect thickness at post-CMP affect resistance and capacitance and result in variations in the delay in interconnects that may cause non-deterministic circuit behaviour both chip-to-chip and within a chip. In addition to CMP, rapid thermal annealing (RTA) and the stress liner effect from the fabrication process also induce variations in length and width parameters on the device [26].

## 2.5.2 Intrinsic Variation

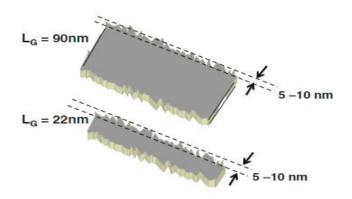

Beyond variations due to imperfect fabrication tools, some sources of variation are intrinsic to the technology involved. Two key sources of variation that are truly random in nature are random dopant fluctuation (RDF) and line-edge roughness (LER). RDF is variation resulting from variability in the concentration of the implanted impurity. RDF affects the transistor's channel region and alters its properties, particularly the device's voltage threshold. The impurity of atoms in modern process technology has a significant affect since the total number of dopants is decreasing drastically. Because of the limitations of lithography and etching tools, the resulting effect is line-edge roughness (LER). The impact of LER is less prominent for technology nodes above 90nm. However, in sub-50nm node, LER can critically affect the voltage threshold, since the ratio of roughness of the edges is becomes closer to the width of the transistor at the range of 5-10nm as illustrated in Figure 14.

Figure 14: Line edge roughness at 90nm and 22nm technology [23].

# 2.6 Environmental Variation

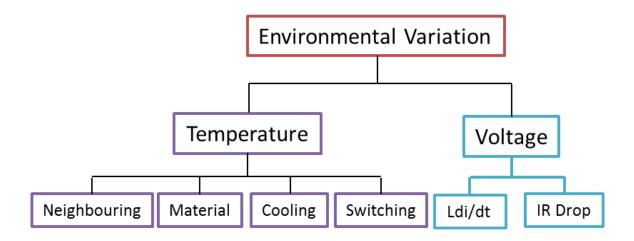

Temperature and supply voltage variations are categorised as environmental.

The performance of devices is strongly dictated by these conditions.

Figure 15: Classification of sources of environmental variation.

# 2.6.1 Temperature Variation

Several factors in addition to the ambient temperature affect the rise and dissipation of temperature within a chip. Regions of the chip with high activity and power consumption are normally associated with rises in temperature, or

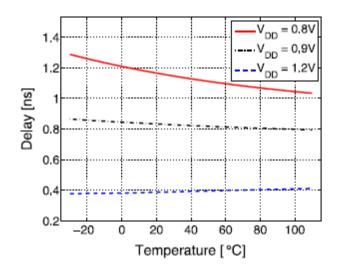

so called hot spots. This increase of heat in a localised area creates temperature variation across a chip. Time constants for temperature variation are normally in the range of milliseconds to seconds. Circuit normally decrease in speed with a rise of temperature due to reduced carrier mobility and increased interconnect resistance. Therefore keeping the temperature within a chip well regulated is necessary to maintain the performance of the circuits. Delays normally increase with increases in temperature. Towards lower geometries below 65nm and beyond at lower threshold voltage, the temperature variation has shown contrarian effects on cell delay [27]. Figure 16 show the characteristic of a typical circuit at nominal voltage, Vdd = 1.2V where the circuit gradually slows down with increasing temperature. However, at a level of Vdd below the nominal value, from 0.9V and 0.8V, the circuit exhibits the reverse characteristic [28]. Therefore, extra-care has to be taken, especially in the extent of sub-threshold to reduce operation power and strategy for energy efficiency improvement with DVFS.

# Figure 16: Inverse path delay characteristics at lower voltage level with increase in temperature [29].

Several factors that affect the temperature variation are listed as follow[23]:

- Neighbouring blocks power characteristic of the circuit switching activities and capacitive load around the location or within the same region will affect power consumption and heat generation.

- The thermal conductivity of material is closely related to power density. Heat generated in bulk CMOS device is dissipated through both the silicon substrate and the interconnecting wires. In SOIC (silicon-insulator) technology, however, heat dissipation occurs mainly along the wires and results in rapid heat increases in regions that consume a lot of energy. This disparity results in greater temperature gradients between hot and cold regions within a chip.

- Cooling efficiency of the packing or heat sink helps to improve the thermal profile. However, this issue exacerbated in the 3D (three-dimensional) stacking technology where circuits are sandwiched together. This means that it becomes more challenging to dissipate heat.

- Switching activity or the workload running on the system in a location or core can drastically increase the temperature in a specific region especially over a long period. In modern multi-core processor system or reconfigurable systems such as the FPGA, the workload may be distributed or inter-swap over time. This is however largely depending on the ability of the underlying support resources of the architecture for dynamic or partially dynamic reconfiguration. The strategy of periodically relocating the workload to different regions or cores will vary the thermal profile over time.

#### 2.6.2 Supply Voltage Variation

Supply voltage variations mainly result from voltage drop across resistive interconnect (IR-drop) and inductive (or di/dt) noise. The power distribution grid within a chip come with its inheriting parasitic resistance, and when a steady state current flows through, this cause IR-drop which can be derived from the basic Ohm's Law as  $\Delta V_{IR} = R_{grid} * i(t)$ . Meanwhile, fluctuations of

voltage due to the parasitic inductance, commonly referred to as the di/dt noise,  $(\Delta V_{\frac{di}{dt}} = L_{parasitic} * \frac{di}{dt})$ . These rapidly changing power noise effects normally have time constants in the range from nanoseconds to microseconds [29]. In summary, the characteristics of the circuit depend significantly on the operating voltage level. A drop of supply voltage affects both the grain and gate bias and the impact is reduced in a flow of current. One profound impact of this on circuit operation is that it does not just increase the delay in the critical path, but may make those near-critical paths that have not been optimised become critical.

Energy harvesting system that tends to provide variable power levels can also be considered as environmental variation. With the expansion of wireless sensor networks and looking toward to the wider scope of the Internet-of-Things (IoT), it is becoming more important to prolong and support existing battery-powered system [7, 30]. In certain applications, energy harvesters have completely replaced traditional batteries. Examples of commercial applications are the battery-less (infrared remote control) and (wireless wall switch) [31]. Energy harvester devices tend to provide dynamic power, and voltage levels may vary at run-time. The strategy to allow circuit working in wider operating range is therefore intentional [32-34]. The rationale for this kind of circuit is that energy should be used while it is abundant, which means that circuit can run at their optimum speeds. This is because the process of energy conversion and storing incurs extra circuit complexity that reduces its efficiency. The benefits of this kind of system able to operate under a wide range of operational voltage levels is maintaining circuit functional or at least part of the core features at a reduces rate while energy is scare and low [35-38].

# 2.7 Temporal Variation - Ageing Related

While environmental temporal variation such as changes in temperature and voltage add to the circuit marginalities, ageing-related temporal variation affects circuit performance gradually over a period. Key mechanisms contributing to such effects are TBBD, HCI and BTI [23], as shown in Figure 17.

## Figure 17: Ageing related temporal variation.

- Time-dependent dielectric breakdown (TDDB): The creation and joining of defects in the gate dielectric, causing gate dielectric breakdown.

- Hot carrier injection (HCI): Defects in the gate stack caused by highly energized carriers under large lateral (drain-to-source) electric fields cause shifts in the threshold voltage.

- Bias-temperature instability (BTI): The Capturing of holes (electrons) from the inverted channel in PFETs and NFETs by broken Si-H bonds, such as charge-trapping sites in high-K gate dielectrics (HfO2).

- Electromigration: is the transport of material caused by the gradual movement of the ions in a conductor due to the momentum transfer between conducting electrons and diffusing metal atoms.

# 2.8 Sensing and Characterisation

Sensing circuits play an important role in understanding and characterising the variability profiles of a particular batch or individual chip. The primary function of sensing circuits is twofold. First, to quantify between the deviated characteristic of a device and its ideal intended behaviour. Secondly, the onchip sensing circuits can be used for continued health monitoring to help provide adaptive refitting for environmental changes and temporal degradation. Less conservative guard banding can be achieved with the availability of characterisation information, which can mean timing yield improvements. Furthermore, with accurate sensing and characterisation, a detailed variation map can be generated. Utilising such information a controller can supplement the power of weakening regions and critical paths can be diverted. Therefore potential run-time malfunctions can be avoided. This section looks at several frequently used sensing and characterisation techniques that can be applied to ASIC and FPGA design.

## 2.8.1 Off-chip Sensing

Off-line sensing is a non-intrusive approach of characterisation without builtin sensors; external measurements equipment is used instead. The most straightforward characterisation technique traditionally used is to incorporate extra test pads for direct access of test probes that are able to inject stimulus signals containing multiple electrical parameters to the sections of the circuits [39]. Accurate current and voltage characteristics of the device can be obtained with this measure. However, such an approach is expensive with the number of test pads required especially with large circuit, the area overhead makes this not viable. Although, area optimisation techniques such as multiplexing the circuit in the array matrix format is possible [40], yet precision and complex analogue voltage-current measurement setup may still be needed. For modern multi millions gates FPGAs, this characterisation technique is almost impossible.

Optical imaging is another attractive non-invasive approach for chip variability characterisation without the need of embedded hard sensors. This technique is based on measurements of the deflective of the electromagnetic wave from the emitting source such as infrared to provide visual representation of the study. In [41], the optical imaging technique was successfully demonstrated to map systematic and random variability effect of microprocessor chip in 65nm technology. Static imaging camera was utilised in this approach to capture the light emission from off-state leakage current (LEOSLC). The authors suggest the recorded data that can be easily correlated to produce variation map and be successfully adapted for the evaluation and enhancement of the fabrication process as well as to develop countermeasure for the possible reliability issues.

Thermal and power characterisation using infrared imaging technique applied on FPGA is recently presented in [42]. In this work, run-time thermal characterisation is performed by capturing the emissions from the back of the chip. The result is the visualisation of operational thermal gradient and hot spot for the particular application mapped on FPGAs. Again, these off-chip techniques are attractive but require complex measurement equipment and procedures. In addition, due to the data being gathered externally, this makes the variation map correlation process less straightforward.

#### 2.8.2 On-chip Sensing

An alternative to the off-chip sensing are built-in hard sensors. The state of the art of multicore processors is normally equipped with multiple thermal sensors. Accurate sensing requires fine granularity of build-in sensors that is scattered across the chip and the question for the research has always been at what cost or overhead.

Sensing and characterisation based on Ring oscillator (RO) was presented in the past and recent years due to its simplicity in implementation either on-line or off-line [3, 43-49]. In [43], authors utilised the method to measure random

MOSFET threshold variations in voltages. Die-to-die variability measurements with ROs that is sensitive to parameter was proposed in [44]. In [46], authors proposed to create Path-based RO to measure and monitor the targeted critical path under process variation. RO was also presented as a temperature sensor as an alternative to analog sensing circuits. RO circuits may be convenient to deploy, yet this approach may increase the overall area of the circuit. In addition, the circuit itself is reactive to temperature and voltage fluctuation. The RO method unfortunately has also been remarked as a bad instrumentation technique for FPGA variability as it does not accurately represent the circuit path in FPGA designs. At high frequency oscillation, RO circuit itself generates heat, this consequently adds extra complexity and variability to the situation [50].

Increasing technology scaling in nanometer regions results in local random transistor parameter variations. The effects of such phenomena as random dopant fluctuations (RDF) and line edge roughness (LER) can dominate mismatch in neighbouring devices. Particularly in SRAM cells with high circuit density, mismatch can deteriorate the circuit functionality greatly. Current latch sense-amplifier (CLSA) for example in [51] is proposed to measure mismatch between two transistors. Since only a pair of transistors can be measured at any one time, this limits its usefulness. Extension from the basic mismatch sensor, array based characterisation is also presented in [52, 53]. Yet, the limitation of this method has been the low sensitivity due to device properties changing linearly with voltage threshold variation when the deviceunder-test (DUT) is biased in the saturation region.

#### 2.8.3 Soft Sensing in FPGA

Reconfigurable architectures such as FPGA give a unique opportunity for sensing and mitigating the effects of the variability using the generic built-in flexible resources rather the dedicated embedded sensing circuits. This is called "soft sensing" in this thesis. Modern FPGA architecture such as Altera's Stratix family and Xilinx's Virtex series are all equipped with a thermal sensor. However, a single sensor cannot sufficiently provide the temperature gradient of the chip. Never mind the ability to identify the maximum value or hot spots of the chip.

Ring oscillator (RO) is a commonly used technique due to its simplicity in implementation either on-line or off-line. Off-line RO is normally used for characterisation purposes such as variability of delay with the changes of temperatures [54]. Authors of [47, 54] proposed one of the earliest thermal soft sensing approach on reconfigurable computing architecture. Flexible RO-based thermal sensing replaced conventionally used analog sensor and its complex control circuit. Example of works in [3, 55] also used RO, instead of thermal, authors perform characterisation of FPGA process variation effect by measuring its component delay. On the other hand, to continuously monitor the health and provide adaptations to temporal effects [45, 46, 56], on-line soft sensing techniques can be beneficial. In [57], thermal soft sensing technique is proposed. This approach utilise an adder-accumulator multiplier to make the computation without the need of RO. Wong et al. [58-60] proposed novel characterisation techniques that enables accurate combinatorial delay measurement. This differs from the previous mentioned methods that used RO for latency measurement [3]. This work performs characterisation by stepping the system frequency gradually for error detection.

Leveraging the unique reconfigure structure of FPGA, extra-embedded analogue sensors can be avoided for PVT (process, voltage and temperature) characterisation. And this forms sound of the foundations for the work presented in this thesis. Furthermore, due the final application to be implemented on the FPGA is not known until it is fabricated, it is hard to predict where and how sensors should be distributed across the chip evenly. Therefore, soft sensing grants additional advantages for monitoring circuits, particularly in the use of on-chip hot spot tracking.

# 2.9 Conventional Variation Tolerance in FPGAs

#### 2.9.1 STA and SSTA

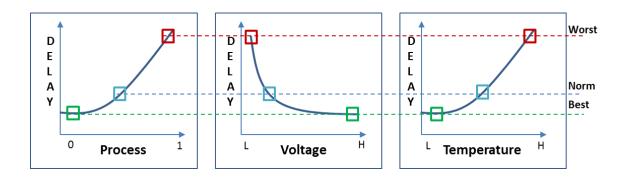

In Static Timing Analysis (STA), timing analysis is carried out in input independent manner, and purpose to determine the worst-case delay or critical path of the circuit over all possible input combinations. Therefore, STA approach often gives pessimistic timing estimation. Hence, this reduces the speed performance that could otherwise be much faster. Extensions of the STA are corner analysis, where worst-case and best-case scenarios for PVT variation can be presented. The best cases are defined as fastest processes at highest voltage level operating at the lowest temperature, and the worst case will be the opposite with a slow process at the lowest voltage and highest temperature. Examples of the effect of PVT on path delay are shown in Figure 18

#### Figure 18: Corner analysis with STA tools

Despite the conservative timing estimation on the critical paths, STA is not able to accurately model intrinsic variability that is random and stochastic. Under random parametric fluctuations, the shorter paths or near-critical paths that have not been optimised have the tendency to become critical.

Statistical static timing analysis (SSTA) tools aim to identify these statistically critical paths and minimize the chances of these paths becoming critical. However, the drawbacks of SSTA tools include the uniform strategies used across the whole chip and between different dies. Therefore, accurately modelling statistical variation from one die to another requires an accurate variation model value of mean ( $\mu$ ) and standard deviation ( $\sigma$ ). Also it is becoming difficult to produce statistical models for the larger systems with high random variation that are expected in future node technology, making the characterisation cost un-scalable to deal with the complexity of a system with increasing numbers of statistically critical paths [61].

#### 2.9.2 Optimisation of Structural Parameters

Structural parameter optimization is another proposed approach for mitigating FPGA variation, which focuses on traditional architectural parameters such as varying the value of N, the number of LUTs per CLB, and K, the number of inputs to a LUT [62]. However, study in [63] shows that varying the value of N and K value does not provide significant improvements over the variation concern [23].

#### 2.9.3 Transistor Sizing

Transistor sizing can be used in ASICs to optimize path delay and power performance. However, the process of transistor sizing for its width and length (W/L) at layout level for FPGAs requires a huge effort and will consumes significant amount of engineering time. Research into automated transistor sizing on FPGAs for area and speed trade-off [64] is also promising in exploring the use transistor sizing to mitigate the effect of variability on FPGA architecture. Yet, this technique is computational expansive and the variability-critical paths (VCPs) cannot easily predefined.

A recent project named the Programmable Analogue and Digital Array (PAnDA) architecture [24] represents a new approach to intrinsic variability, introducing reconfigurable transistor arrays at the analogue level. This approach allows low-level optimization during the post-fabrication stage and results in the recovery of the loss of performance yield introduced by stochastic variability. However, the extra configurability of the architecture also comes with a high area overhead.

#### 2.9.4 Asynchronous Techniques

Asynchronous designs are highly adaptive to changes in voltage and delay, providing robustness depending on the delay assumptions that are made [65]. The most robust class is delay-insensitive (DI), where circuits will operate correctly without any assumption of delay in either gates or wires. Circuits with carefully identified delay assumptions on isochronic wire are called quasidelay-insensitive (QDI) [66] or speed independent (SI) [67]. These circuits consider only the gate delay and neglect wire delay when ensuring circuit correctness.

There are many approaches or protocols for implementing asynchronous circuits. A taxonomy of potential protocol implementations is summarized in [65]. The choice of an asynchronous communication protocol affects the characteristics of circuit in term of implementation power, area, throughput and robustness.

In the past decade, different asynchronous FPGA architectures have been presented motivated mainly by the pursuit of low power and/or high-speed performance. These architectures can be classified into two main styles. The first relies heavily on timing assumptions to guarantee the correctness of the logic, and the second alters the traditional architecture at fine-grained level with the intensive use of state-holding memory components (such as Celements), which implies significant overheads in size and power [68, 69]. Details of asynchronous FPGA (AFPGA) designs are reviewed in Chapter 3.

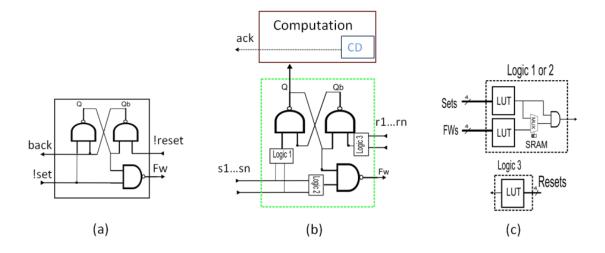

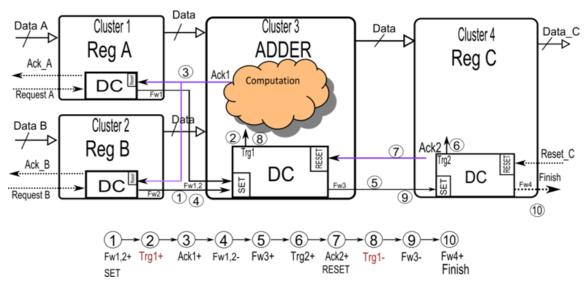

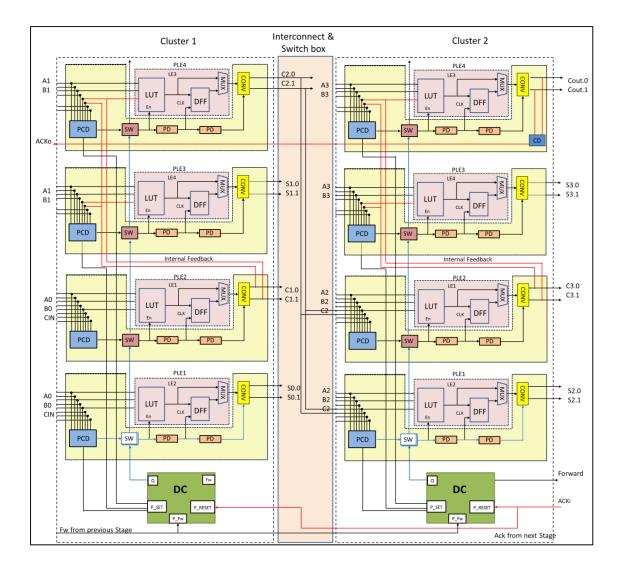

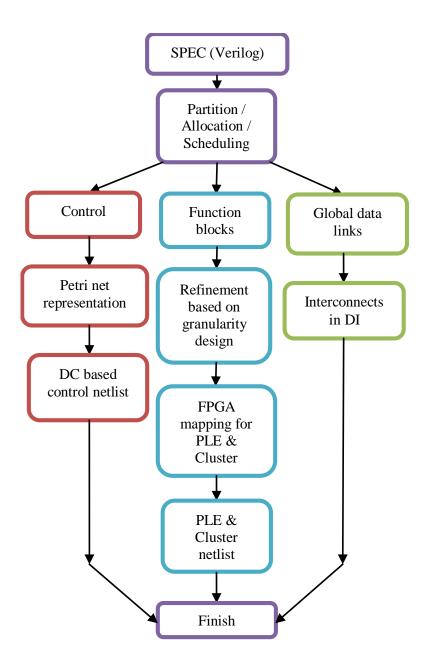

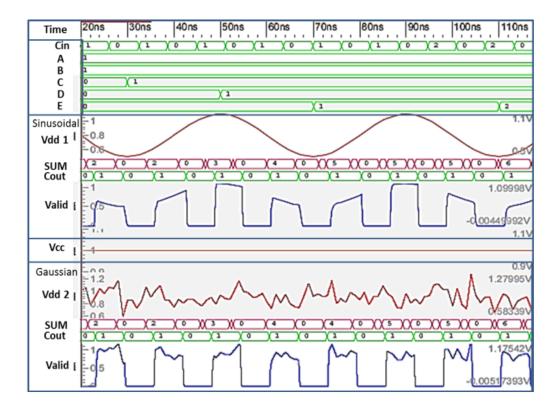

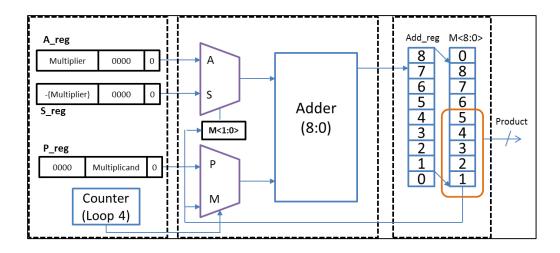

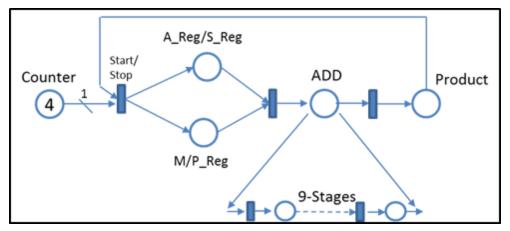

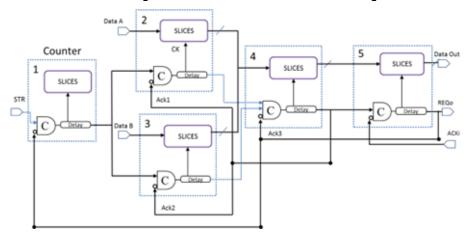

## 2.10 Variation Aware and Late Binding Techniques