# Soft Error Analysis and Mitigation In Circuits Involving C-Elements

A Thesis Presented to Newcastle University by

# NORHUZAIMIN BIN JULAI

In Partial Fulfilment

of the Requirement for the Degree of

Doctor of Philosophy in Electrical and Computer Engineering

School of Electrical, Electronic and Computer Engineering University of Newcastle

# CONTENTS

| Contents                  |         |                                        | iii   |

|---------------------------|---------|----------------------------------------|-------|

| List of Algorithms/Tables |         |                                        | vii   |

| List of Figures           |         |                                        | viii  |

| Abst                      | ract    |                                        | xviii |

| Glos                      | sary    |                                        | xix   |

| Ackr                      | nowledg | gement                                 | xxi   |

| Char                      | oter 1  | Introduction                           | 1     |

| 1.1                       | Motiva  | ation                                  | 1     |

| 1.2                       | Object  | ives                                   | 4     |

| 1.3                       | Thesis  | Overview                               | 5     |

| 1.4                       | Thesis  | Contributions                          | 6     |

| 1.5                       | Publica | ations                                 | 7     |

| Chap                      | oter 2  | Basics Concepts                        | 8     |

| 2.1                       | Radiat  | ion Effects in Digital Systems         | 8     |

|                           | 2.1.1   | Sources of Radiations                  | 8     |

|                           | 2.1.2   | The Effects of Radiation               | 10    |

|                           | 2.1.3   | Single Event Upset Modelling           | 13    |

| 2.2                       | Asyncl  | hronous Design                         | 16    |

|                           | 2.2.1   | Advantages of Asynchronous Design      | 16    |

|                           | 2.2.2   | C-element                              | 17    |

|                           | 2.2.3   | Classification of Asynchronous Circuit | 18    |

|                           | 2.2.4   | Asynchronous Circuit Implementation    | 19    |

| 2.3                       | Dual R  | ail Data                               | 21    |

|                           | 2.3.1   | Dual Rail Data Encoding                | 21    |

|                           | 2.3.2   | Handshake Protocols                    | 22    |

|     | 2.3.3   | Effect of SEU on Dual Rail Data                                                            | 25 |

|-----|---------|--------------------------------------------------------------------------------------------|----|

| 2.4 | Fault   | Folerant Latch                                                                             | 28 |

|     | 2.4.1   | Single Rail Fault Tolerant Latch                                                           | 28 |

|     | 2.4.2   | Dual Rail Fault Tolerant Latch                                                             | 32 |

| 2.5 | Factor  | s Affecting CMOS Performance                                                               | 34 |

|     | 2.5.1   | Voltage Supply                                                                             | 34 |

|     | 2.5.1   | Process Variations                                                                         | 34 |

|     | 2.5.2   | Temperature Variations                                                                     | 35 |

| 2.6 | CMOS    | S Power Dissipation                                                                        | 36 |

| Cha | pter 3  | Analysis of Single Event Upset on Different<br>Configurations of C- Elements               | 39 |

| 3.1 | Introd  | uction                                                                                     | 39 |

| 3.2 | Exper   | iments Setup and Work Flow                                                                 | 39 |

| 3.3 | Critica | al Charge Analysis for C-elements                                                          | 42 |

|     | 3.3.1   | Critical Charge Analysis for Single Rail with Inverter<br>Latch Configuration              | 44 |

|     | 3.3.2   | Critical Charge Analysis for Single Rail with Conventional Pull-Up Pull-Down Configuration | 50 |

|     | 3.3.3   | Critical Charge Analysis for Single Rail Symmetric<br>Implementation Configuration         | 55 |

|     | 3.3.4   | Critical Charge Analysis for Differential Logic and an Inverter Latch Configuration        | 60 |

| 3.4 |         | t Vulnerability Against Single Event Upset-Critical                                        | 65 |

| 3.5 | Concl   | usions                                                                                     | 70 |

| Cha | pter 4  | Error Rate Analysis of Different Configurations of C-<br>elements                          | 72 |

| 4.1 | Introd  | uction                                                                                     | 72 |

| 4.2 | Mathe   | matical Modelling of Soft Error                                                            | 73 |

| 4.3 | Propo   | sed Methods to Calculate Soft Error Rate                                                   | 80 |

| 4.4        | Result                     | And Analysis                                                                                | 84         |

|------------|----------------------------|---------------------------------------------------------------------------------------------|------------|

|            | 4.4.1                      | Error Rate for Single Rail with Inverter Latch Configuration                                | 84         |

|            | 4.4.2                      | Error Rate for Single Rail with Conventional Pull-Up<br>Pull-Down Configuration             | 94         |

|            | 4.4.3                      | Error Rate for Single Rail Symmetric Implementation<br>Configuration                        | 103        |

|            | 4.4.4                      | Error Rate for Differential Logic and an Inverter Latch<br>Configuration                    | 111        |

| 4.5        | Circui                     | t Vulnerability Against Single Event Upset -Error Rate                                      | 120        |

|            | 4.5.1                      | Error Rate Comparison                                                                       | 121        |

|            | 4.5.2                      | Sensitivity Analysis                                                                        | 122        |

| 4.6        | Concl                      | usions                                                                                      | 125        |

| Cha        | pter 5                     | Error Detection and Correction of Single Event Upset<br>Tolerant Latch for Single Rail Data | 127        |

| 5.1        | Introd                     | uction                                                                                      | 127        |

| 5.2        | Propos                     | sed Error Detection Latch                                                                   | 128        |

| 5.3        | Propos                     | sed Error Detection and Correction Latch                                                    | 139        |

| 5.4        | 1                          | mentation of Full Adder System by using Error Detection<br>prrection Latch                  | 152        |

| 5.5        | Concl                      | usions                                                                                      | 155        |

| Cha        | pter 6                     | Error Detection and Correction of Single Event Upset<br>Tolerant Latch for Dual Rail Data   | 156        |

| 6.1        | Introd                     | uction                                                                                      | 156        |

|            | muou                       |                                                                                             |            |

| 6.2        |                            | sed Error Detection for Dual Rail Data                                                      | 156        |

| 6.2<br>6.3 | Propos                     | sed Error Detection for Dual Rail Data                                                      | 156<br>166 |

|            | Propos<br>Propos<br>Propos |                                                                                             |            |

| Chaj | pter 7 The design of Asynchronous On-chip Communication<br>by using EDCD Proposed Latch | 187 |

|------|-----------------------------------------------------------------------------------------|-----|

| 7.1  | Introduction                                                                            | 187 |

| 7.2  | Asynchronous on-chip communication by using EDCD Latch                                  | 187 |

| 7.3  | Result and Simulation Employing EDCD Latch                                              | 193 |

| 7.4  | Conclusions                                                                             | 196 |

| Chaj | pter 8 Conclusions And Future Works                                                     | 197 |

| 8.1  | Conclusions                                                                             | 197 |

| 8.2  | Future Works                                                                            | 198 |

| App  | endixes                                                                                 | 200 |

| Refe | rences                                                                                  | 209 |

# List of Algorithms/Tables

| Table 1: Ground Level Soft Error Rates Measured by RAM                     | 2   |

|----------------------------------------------------------------------------|-----|

| Table 2: Dual Rail Encoding                                                | 21  |

| Method 4.1: Calculate the critical charge and normalized cross section     |     |

| of NMOS/PMOS with neutron                                                  | 80  |

| Method 4.2: Calculate charge, energy and rate of error with amplitude      |     |

| less than 380                                                              | 81  |

| Method 4.3: Calculate charge, energy and rate of error with amplitude      |     |

| more than 380                                                              | 82  |

| Method 4.4: Calculate error rate                                           | 83  |

| Table 4.1: Standard Deviation for the Process Corner-SIL                   | 86  |

| Table 4.2: Standard Deviation for the Process Corner-SC                    | 95  |

| Table 4.3: Standard Deviation for the Process Corner-SS                    | 104 |

| Table 4.4: Standard Deviation for the Process Corner-DIL                   | 113 |

| Table 5.1:Vulnerables nodes on converter                                   | 129 |

| Table 5.2: Vulnerable nodes on ED Latch                                    | 139 |

| Table 5.3: Vulnerable nodes on EDC Latch                                   | 149 |

| Table 5.4: Propagation Delay Between ED And EDC Latch                      | 151 |

| Table 5.5: Switching Power Between ED And EDC Latch                        | 152 |

| Table 5.6: Truth Table Full Adder                                          | 153 |

| Table 6.1: Vulnerable nodes on EDD Latch                                   | 165 |

| Table 6.2: Vulnerable nodes on EDCD Latch                                  | 177 |

| Table 6.3: Propagation Delay Comparison                                    | 178 |

| Table 6.4: Switching Power Comparison                                      | 179 |

| Table 6.5: Comparison of Different Latches                                 | 186 |

| Table 6.6: Comparison of Different Latches                                 | 186 |

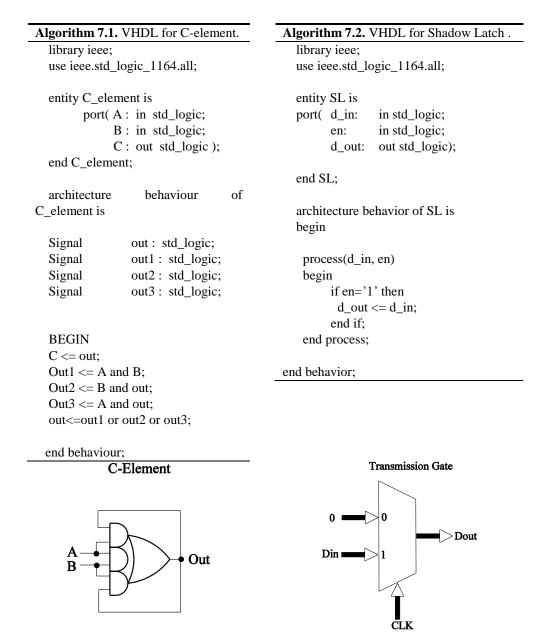

| Algorithm 7.1. VHDL for C-element                                          | 188 |

| Algorithm 7.2. VHDL for Shadow Latch                                       | 188 |

| Table 7.1: Code comparison in terms of wires, transition and capacity      | 190 |

| Table 7.2: Interface of dual rail to 3-6 and back to dual rail conversion. | 192 |

| Table 7.3: 3-6 and dual rail code.                                         | 193 |

| Table 1B: Interface of Adder System.                                       | 203 |

| Algorithm 1: Brent Kung 8-Bit Adder                                        | 207 |

# List of Figures

| Figure 1: The evolution of transistors with respect to year         | 1  |

|---------------------------------------------------------------------|----|

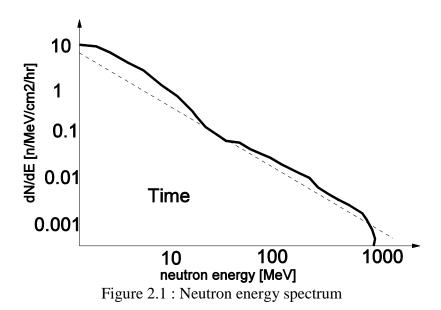

| Figure 2.1: Neutron energy spectrum                                 | 9  |

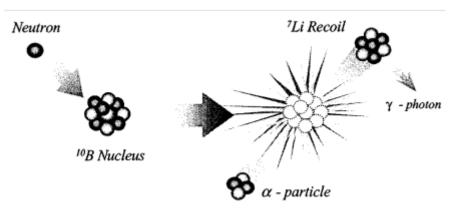

| Figure 2.2: Interaction of Boron and neutron                        | 10 |

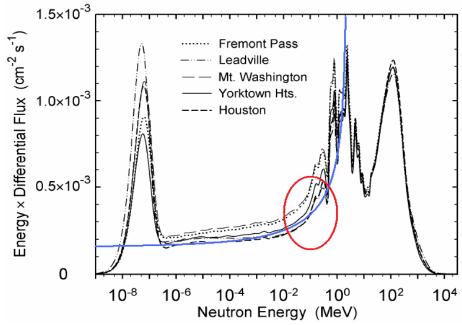

| Figure 2.3: Neutron spectrum below 1 MeV, including thermal-energy  | 10 |

| neutrons                                                            |    |

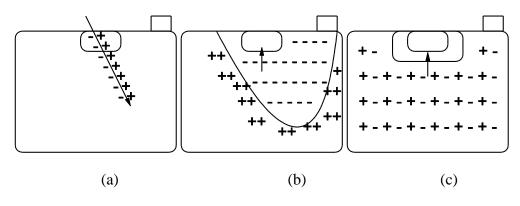

| Figure 2.4: SEU produced                                            | 11 |

| Figure 2.5: The drain current versus the gate voltage for MOSFET    | 13 |

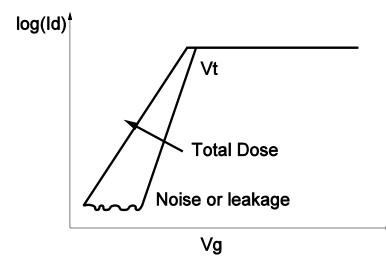

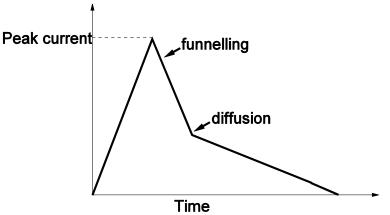

| Figure 2.6: Piece-wise linear function modelling for SEU            | 14 |

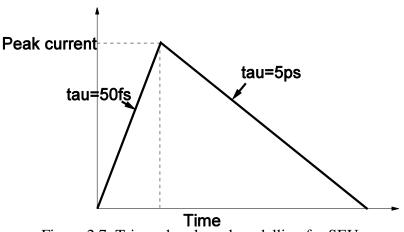

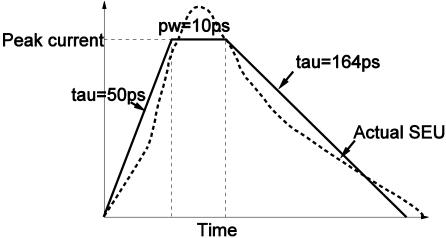

| Figure 2.7: Triangular-shaped modelling for SEU                     | 15 |

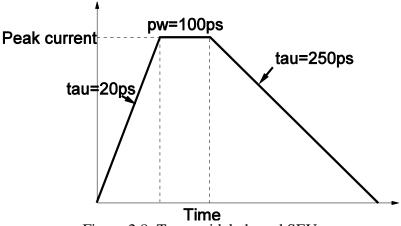

| Figure 2.8: Trapezoidal-shaped SEU                                  | 15 |

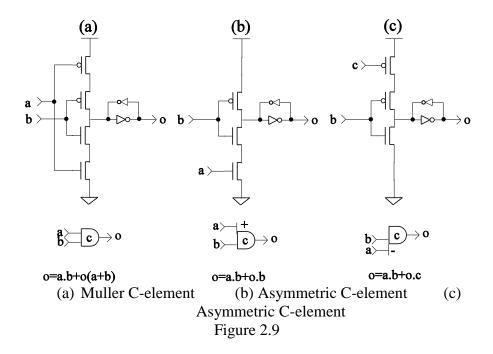

| Figure 2.9: (a) Muller C-element (b) Asymmetric C-element (c)       |    |

| Asymmetric C-element                                                | 18 |

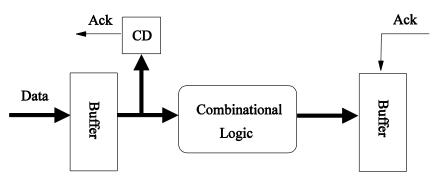

| Figure 2.10: Asynchronous buffer implementation                     | 19 |

| Figure 2.11: Asynchronous implementation                            | 20 |

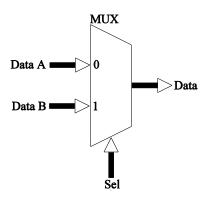

| Figure 2.12: Multiplexer                                            | 20 |

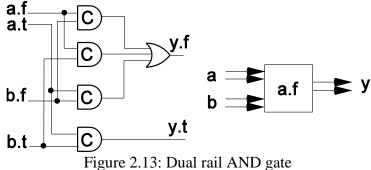

| Figure 2.13: Dual Rail And Gate                                     | 22 |

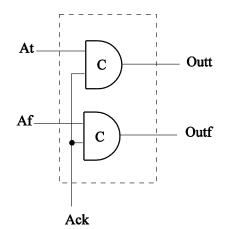

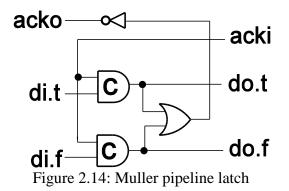

| Figure 2.14: Muller Pipeline Latch                                  | 22 |

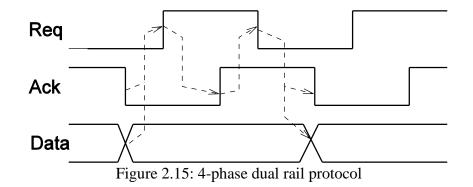

| Figure 2.15: 4-phase dual rail protocol                             | 23 |

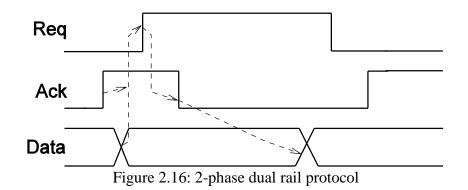

| Figure 2.16: 2-phase dual rail protocol                             | 23 |

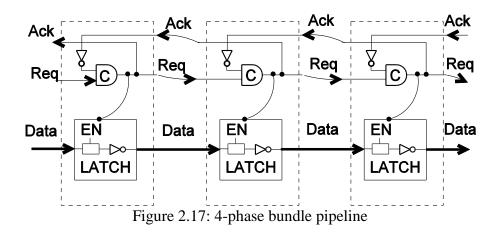

| Figure 2.17: 4-phase bundle pipeline                                | 24 |

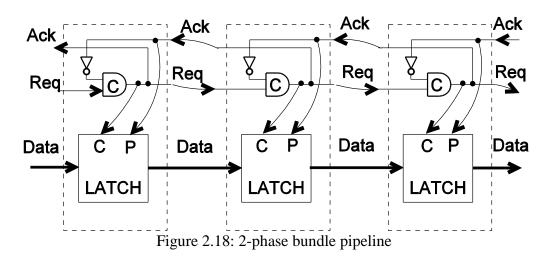

| Figure 2.18: 2-phase bundle pipeline                                | 24 |

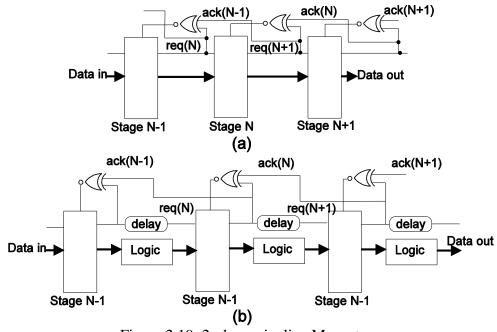

| Figure 2.19: 2-phase pipeline "Mousetrap"                           | 25 |

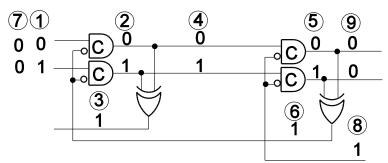

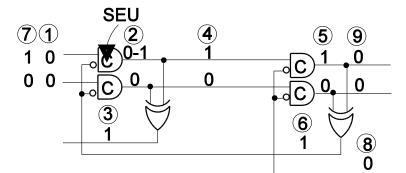

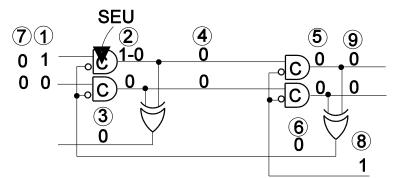

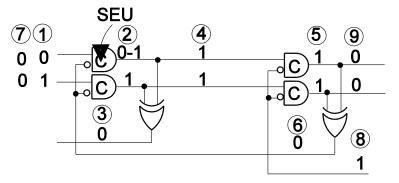

| Figure 2.20: Fault Free 1-bit Dual Rail                             | 26 |

| Figure 2.21: Case 1: 1-bit Dual Rail Pipeline                       | 27 |

| Figure 2.22: Case 2: 1-bit Dual Rail Pipeline                       | 27 |

| Figure 2.23: Case 3: 1-bit Dual Rail Pipeline                       | 28 |

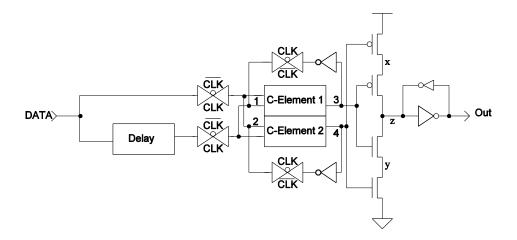

| Figure 2.24: FERST                                                  | 29 |

| Figure 2.25: SIN-LC                                                 | 30 |

| Figure 2.26: SIN-HR                                                 | 30 |

| Figure 2.27: SDT                                                    | 30 |

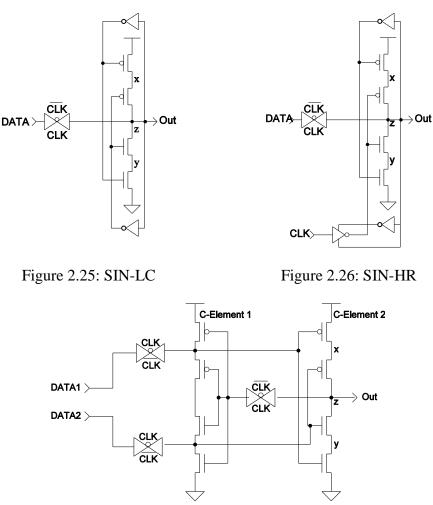

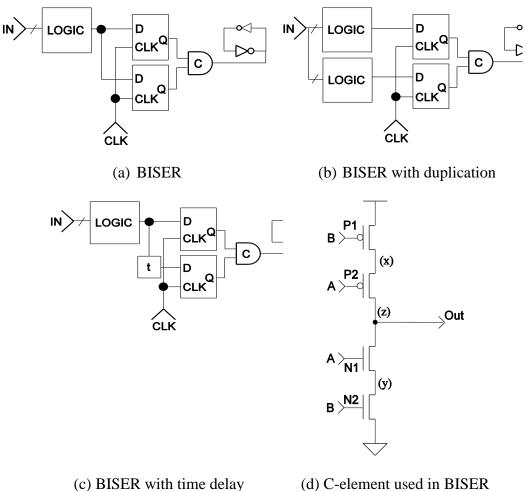

| Figure 2.28: (a) BISER (b) BISER with duplication (c) BISER with    |    |

| time delay (d) C-element used in BISER                              | 32 |

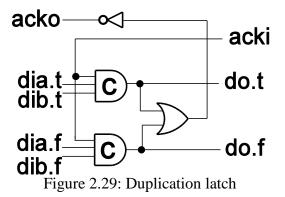

| Figure 2.29: Duplication Latch                                      | 32 |

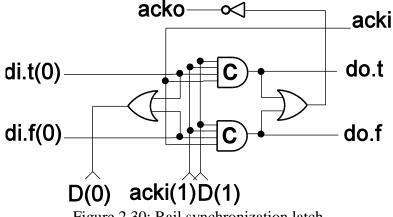

| Figure 2.30: Rail synchronization latch                             | 33 |

| Figure 3.1: SEU Current Modelling                                   | 40 |

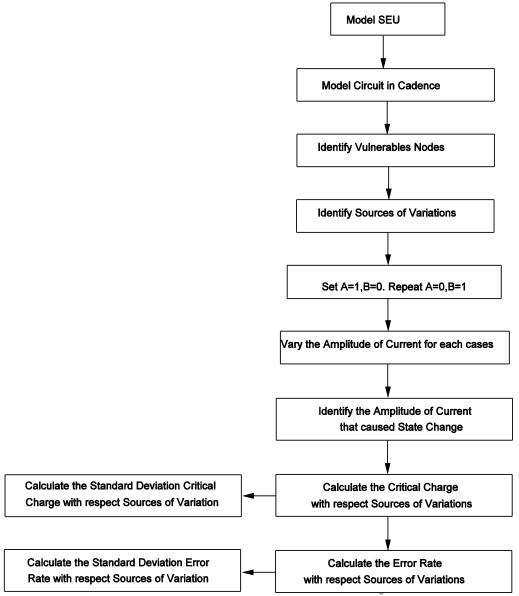

| Figure 3.2: Workflow of the experiments                             | 42 |

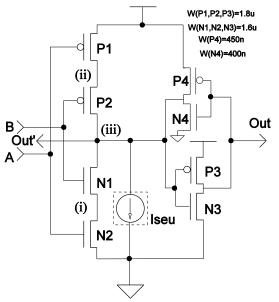

| Figure 3.3: SIL Configuration                                       | 44 |

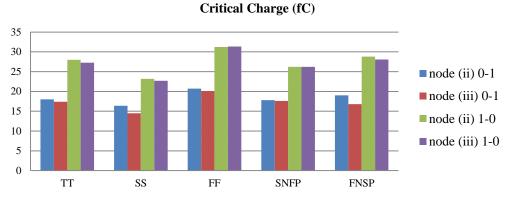

| Figure 3.4(a): Process Corner Variation for SIL configuration (A=1, | 46 |

| B=0)                                                                |    |

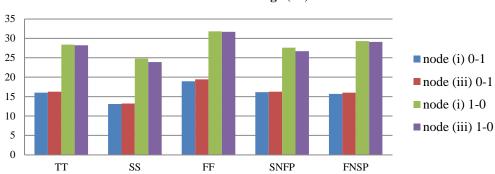

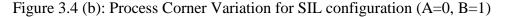

| Figure 3.4(b): Process Corner Variation for SIL configuration (A=0, | 46 |

| B=1)                                                                |    |

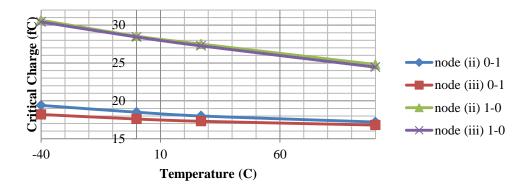

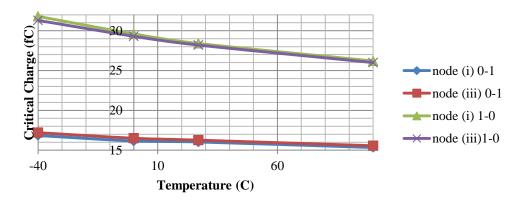

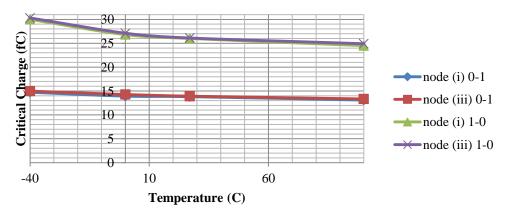

| Figure 3.5(a): Temperature Variation for SIL configuration (A=1,    | 47 |

| B=0)                                                                |    |

| Figure 3.5(b): Temperature Variation for SIL configuration (A=0,    | 47 |

| B=1)                                                                |    |

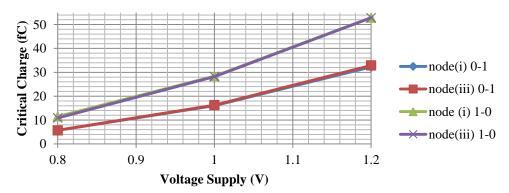

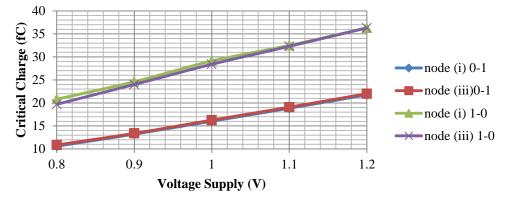

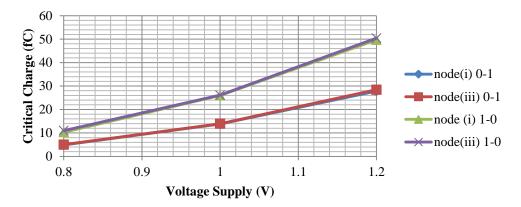

| Figure 3.6(a): Voltage and Size Scaling for SIL configuration (A=1, | 49 |

| B=0)                                                                |    |

| Figure 3.6(b): Voltage and Size Scaling for SIL configuration (A=0, | 49 |

| B=1)                                                                |    |

| Figure 3.7(a): Voltage Supply Scaling for SIL configuration (A=1,   | 50 |

| B=0)                                                                               |    |

|------------------------------------------------------------------------------------|----|

| B=1)                                                                               | 50 |

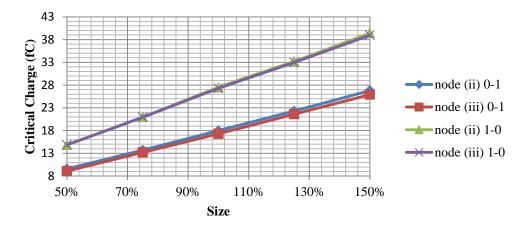

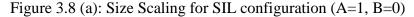

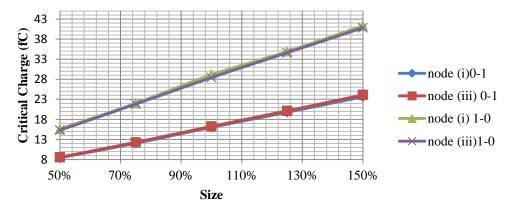

| Figure 3.8(a): Size Scaling for SIL configuration (A=1, 5<br>B=0)                  | 50 |

|                                                                                    | 51 |

| Figure 3.10(a): Process Corner Variation for SC configuration (A=1, 5              | 53 |

| B=0)                                                                               |    |

| Figure 3.10(b): Process Corner Variation for SC configuration (A=0, 5              | 53 |

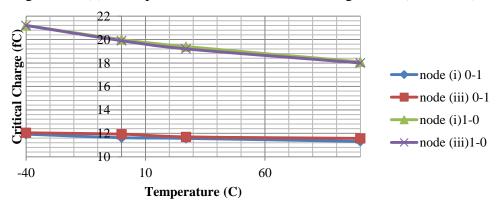

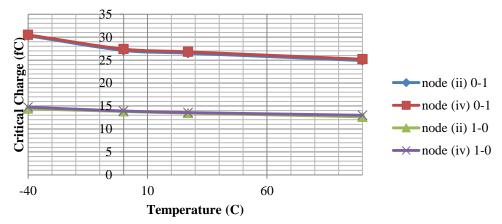

| B=1)<br>Figure 3.11(a): Temperature Variation for SC configuration (A=1, 5<br>B=0) | 53 |

|                                                                                    | 53 |

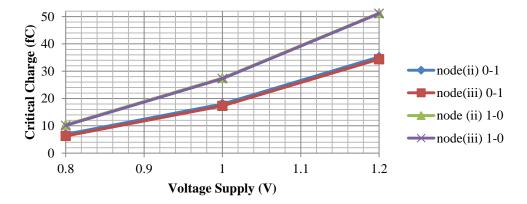

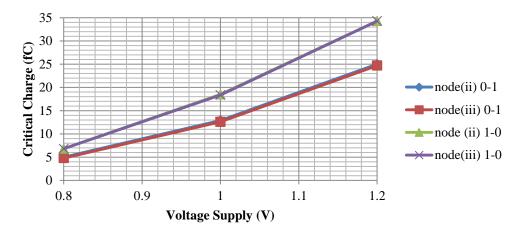

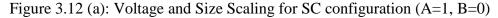

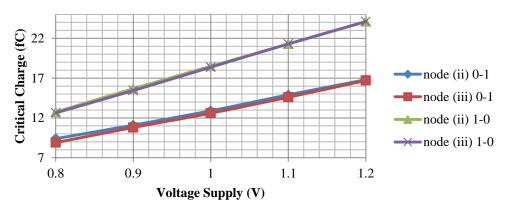

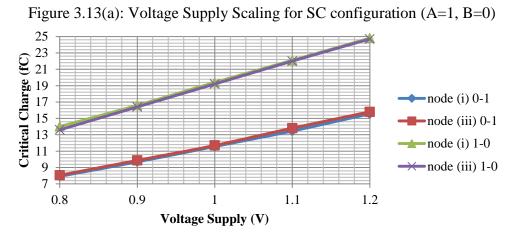

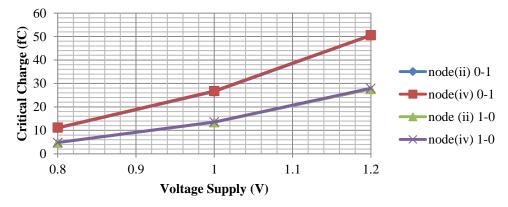

| Figure 3.12(a): Voltage and Size Scaling for SC configuration (A=1,                | 54 |

|                                                                                    | 54 |

|                                                                                    | 54 |

|                                                                                    | 54 |

| B=1)                                                                               |    |

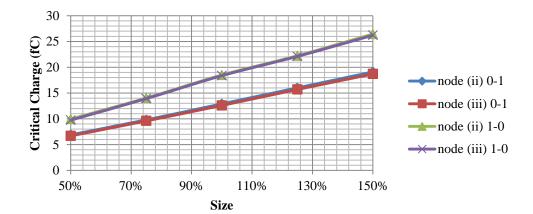

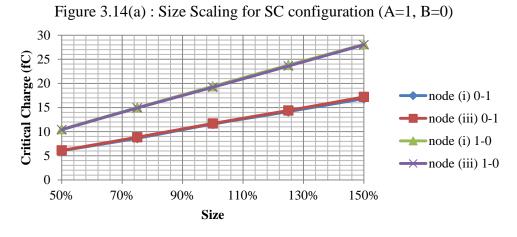

| B=0)                                                                               | 55 |

| Figure 3.14(b): Size Scaling for SC configuration (A=0, 5 B=1)                     | 55 |

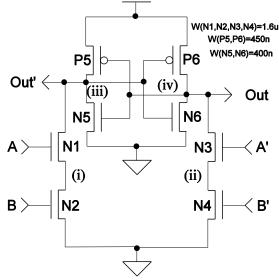

| Figure 3.15: SS configuration                                                      | 56 |

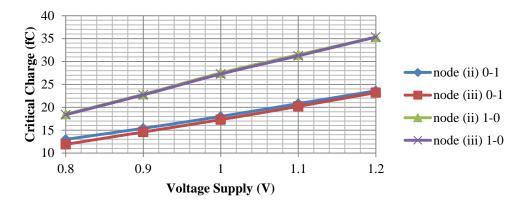

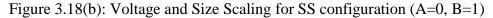

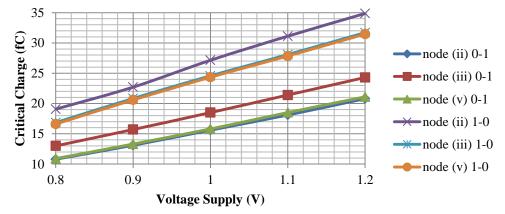

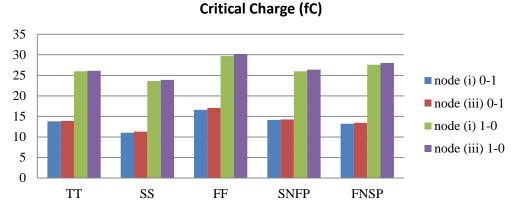

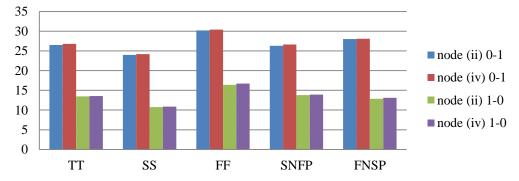

| 6 6                                                                                | 58 |

|                                                                                    | 58 |

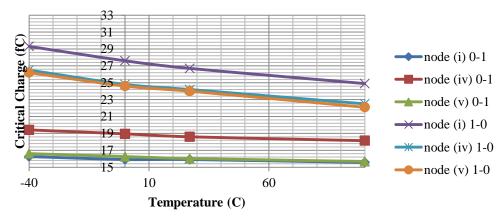

| Figure 3.17(a): Temperature Variation for SS configuration (A=1, 5                 | 58 |

|                                                                                    | 58 |

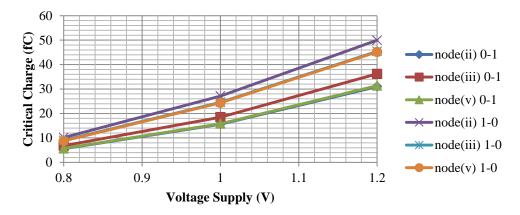

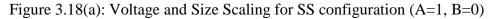

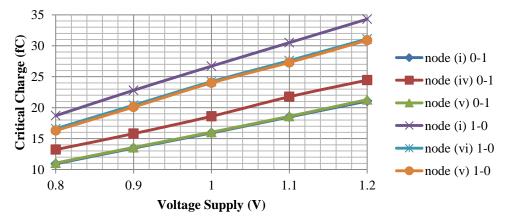

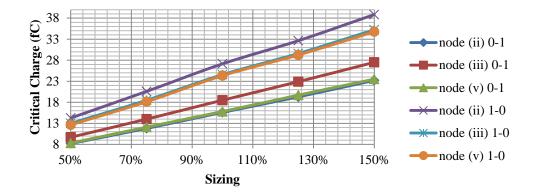

|                                                                                    | 59 |

|                                                                                    | 59 |

| B=1)<br>Figure 3.19(a): Voltage Supply Scaling for SS configuration (A=1, 5        | 59 |

| B=0)<br>Figure 3.19(b): Voltage Supply Scaling for SS configuration (A=0, 45       | 59 |

| B=1)                                                                               |    |

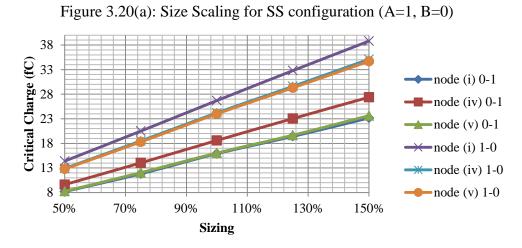

| Figure 3.20(a): Size Scaling for SS configuration (A=1, B=0)                       | 60 |

|                                                                                    | 60 |

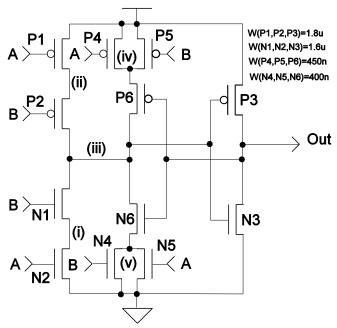

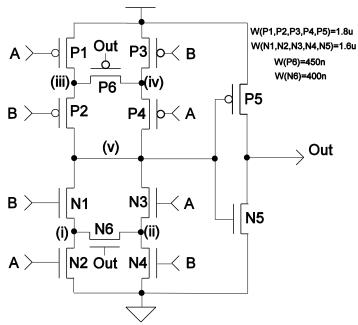

|                                                                                    | 61 |

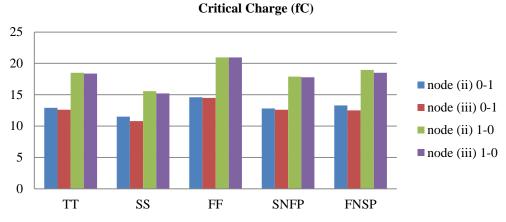

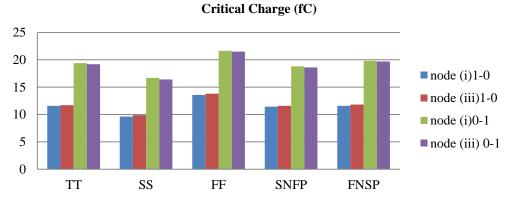

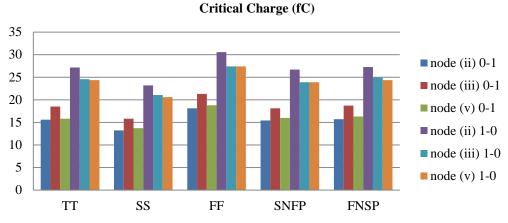

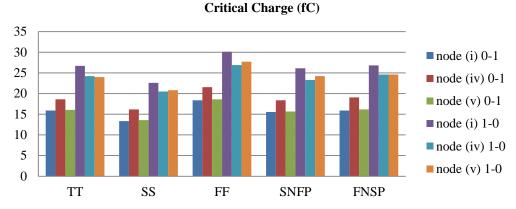

| Figure 3.22(a): Process Corner Variation for DIL configuration (A=1, 6<br>B=0)     | 63 |

|                                                                                    | 63 |

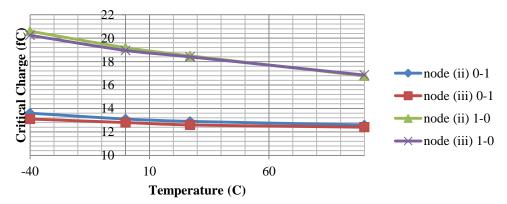

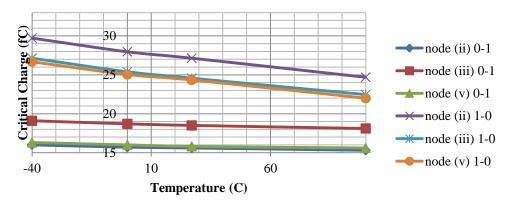

| ,                                                                                  | 63 |

| Figure 3.23(b): Temperature Variation for DIL configuration (A=0, $P=1$ )                                                                                                  | 63       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| B=1)<br>Figure 3.24(a): Voltage and Size Scaling for DIL configuration (A=1, B=0)                                                                                          | 64       |

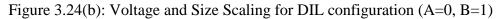

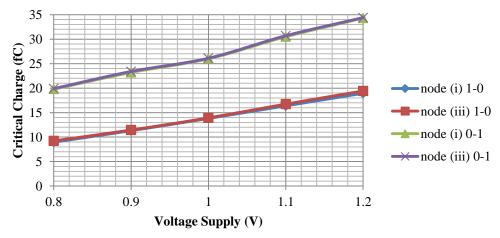

| Figure 3.24(b): Voltage and Size Scaling for DIL configuration (A=0, B=1)                                                                                                  | 64       |

| Figure 3.25(a): Voltage Supply Scaling for DIL configuration (A=1, B=0)                                                                                                    | 64       |

| Figure 3.25(b): Voltage Supply Scaling for DIL configuration (A=0, B=1)                                                                                                    | 64       |

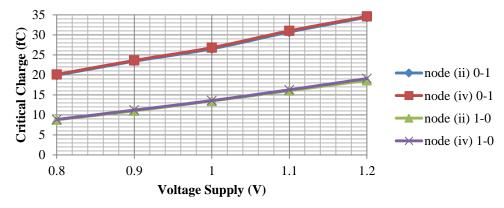

| Figure 3.26(a): Size Scaling for DIL configuration (A=1,                                                                                                                   | 65       |

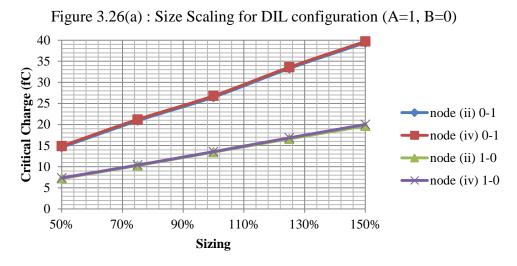

| B=0)<br>Figure 3.26(b): Size Scaling for DIL configuration (A=0,<br>B=1)                                                                                                   | 65       |

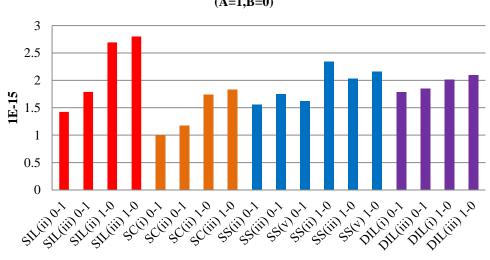

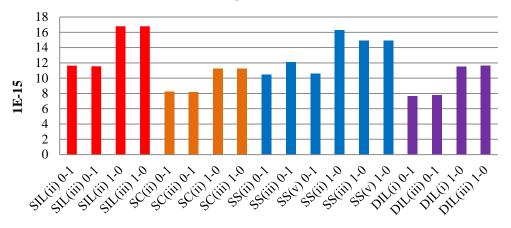

| Figure 3.27(a): Comparison of Standard Deviation with respect to Process Corner (A=1, B=0).                                                                                | 66       |

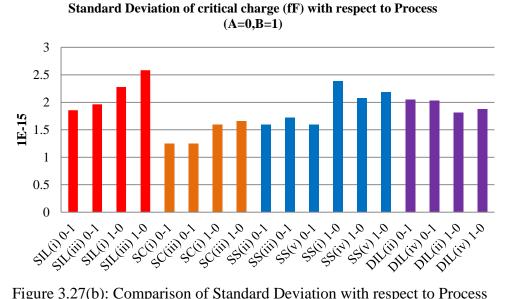

| Figure 3.27(b): Comparison of Standard Deviation with respect to Process Corner (A=0, B=1)                                                                                 | 67       |

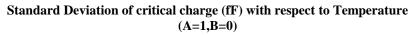

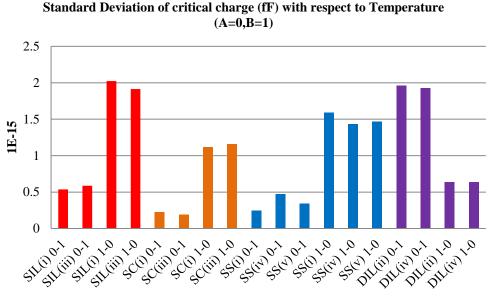

| Figure 3.28(a): Comparison of Standard Deviation with respect to Temperature (A=1, B=0)                                                                                    | 67       |

| Figure 3.28(b): Comparison of Standard Deviation with respect to Temperature (A=0, B=1)                                                                                    | 68       |

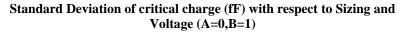

| Figure 3.29(a): Comparison of Standard Deviation with respect to Voltage and Scaling (A=1, B=0)                                                                            | 68       |

| Figure 3.29(b): Comparison of Standard Deviation with respect to Voltage and Scaling (A=0, B=1)                                                                            | 68       |

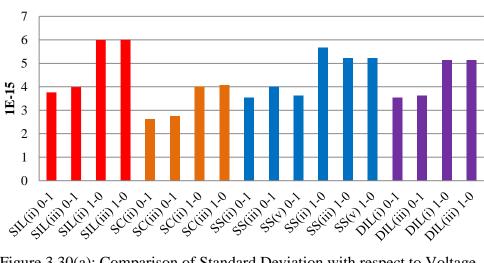

| Figure 3.30(a): Comparison of Standard Deviation with respect to Voltage Scaling (A=1, B=0)                                                                                | 69       |

| Figure 3.30(b): Comparison of Standard Deviation with respect to Voltage Scaling (A=0, B=1)                                                                                | 69       |

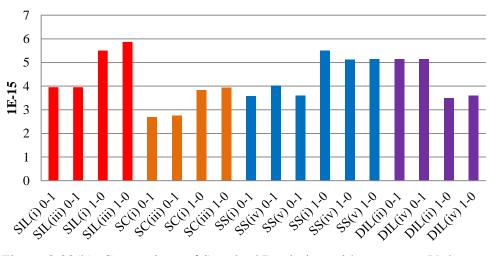

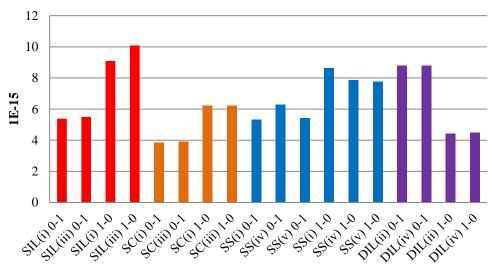

| Figure 3.31(a): Comparison of Standard Deviation with respect to Size Scaling (A=1, B=0).                                                                                  | 70       |

| Figure 3.31(b): Comparison of Standard Deviation with respect to Size Scaling (A=0, B=1).                                                                                  | 70       |

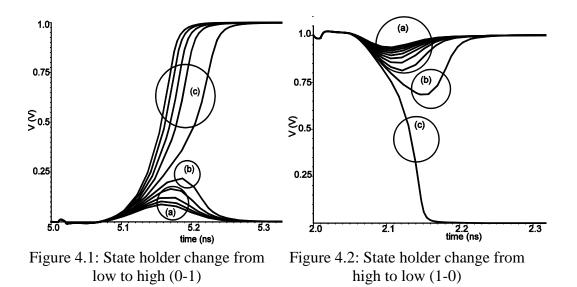

| Figure 4.1: State holder change from low to high (0-1)<br>Figure 4.2: State holder change from high to low (1-0)                                                           | 73<br>73 |

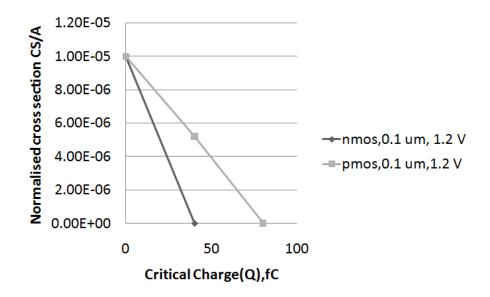

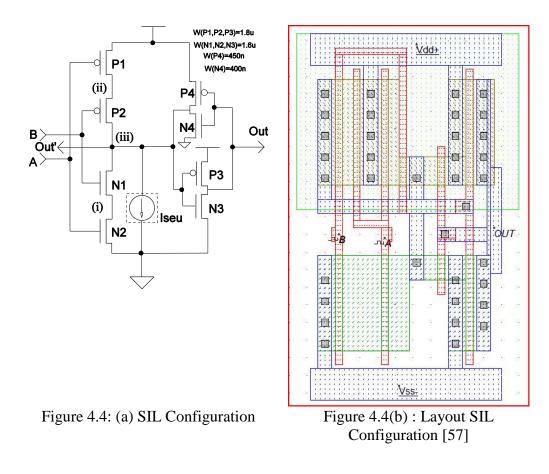

| Figure 4.3: Normalized atmospheric neutron cross section with the drain area<br>Figure 4.4: (a) SIL Configuration (b) Layout SIL Configuration                             | 77<br>85 |

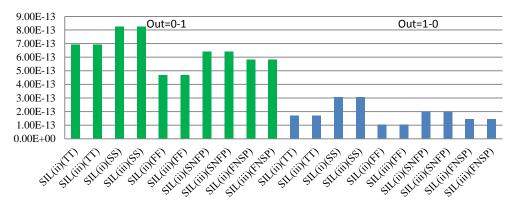

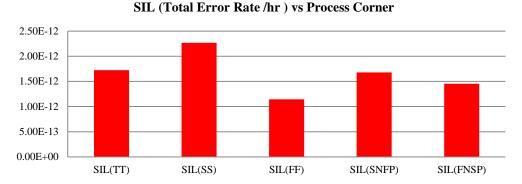

| Figure 4.4. (a) SIL Configuration (b) Layout SIL Configuration<br>Figure 4.5(a): Error rate due to neutron energy spectrum with respect<br>to Process Corner-SIL (A=1 B=0) | 85<br>86 |

| Figure 4.5(b): Error rate due to neutron energy spectrum with respect to Process Corner-SIL (A=0 B=1)                                                                      | 86       |

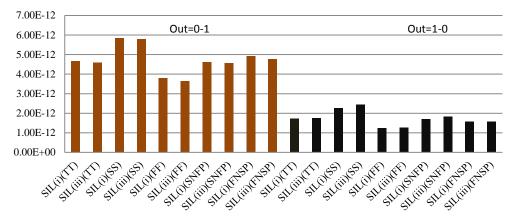

| Figure 4.6(a): Total Error rate due to neutron energy spectrum with respect to Process Corner-SI (A=1 B=0)                                                                 | 87       |

| Figure 4.6(b): Total Error rate due to neutron energy spectrum with respect to Process Corner-SIL (A=0 B=1)                                                                | 87       |

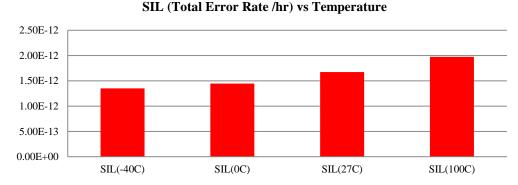

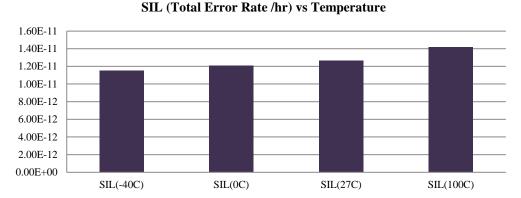

| Figure 4.7(a): Error rate due to neutron energy spectrum with respect to Temperature -SIL (A=1 B=0)                                                                        | 88       |

| Figure 4.7(b): Error rate due to neutron energy spectrum with respect to Temperature -SIL (A=0 B=1)                                                                        | 88       |

| Figure 4.8(a): Total Error rate due to neutron energy spectrum with                                                                                                        |          |

| respect to Temperature-SIL (A=1 B=0)                                                                                | 88         |

|---------------------------------------------------------------------------------------------------------------------|------------|

| Figure 4.8(b): Total Error rate due to neutron energy spectrum with                                                 | 00         |

| respect to Temperature-SIL (A=0 B=1)                                                                                | 89         |

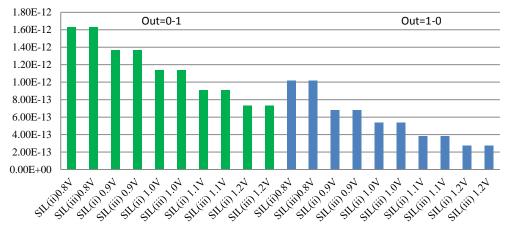

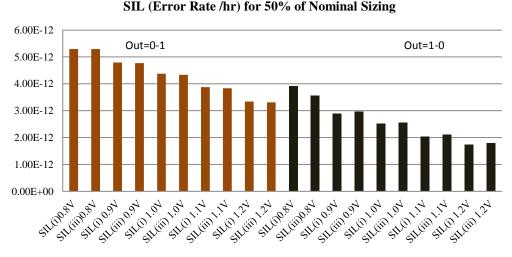

| Figure 4.9(a): Error rate due to neutron energy spectrum with respect                                               |            |

| to Voltage Supply for 50% SIL (A=1,B=0)                                                                             | 90         |

| Figure 4.9(b): Error rate due to neutron energy spectrum with respect                                               |            |

| to Voltage Supply for 50% SIL (A=0, B=1)                                                                            | 90         |

| Figure 4.10(a): Error rate due to neutron energy spectrum with respect                                              |            |

| to Voltage Supply for 100% SIL (A=1, B=0)                                                                           | 90         |

| Figure 4.10(b): Error rate due to neutron energy spectrum with respect                                              | 01         |

| to Voltage Supply for 100% SIL (A=0, B=1)                                                                           | 91         |

| Figure 4.11(a): Error rate due to neutron energy spectrum with respect to Voltage Supply for $150\%$ SU (A=1, B=0)  | 91         |

| to Voltage Supply for 150% SIL (A=1, B=0)<br>Figure 4.11(b): Error rate due to neutron energy spectrum with respect | 91         |

| to Voltage Supply for 150% SIL (A=0, B=1)                                                                           | 91         |

| Figure 4.12(a): Total error rate due to neutron energy spectrum with                                                | 71         |

| respect to Voltage Supply for SIL (A=1, B=0)                                                                        | 92         |

| Figure 4.12(b): Total error rate due to neutron energy spectrum with                                                |            |

| respect to Voltage Supply for SIL (A=0.B=1)                                                                         | 92         |

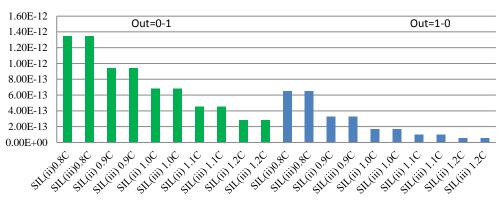

| Figure 4.13 (a): Standard Deviation of Error rate due to neutron                                                    |            |

| energy spectrum with respect to Process Corner, Temperature, Voltage                                                | 93         |

| and Size SIL(A=1,B=0).                                                                                              |            |

| Figure 4.13(b): Standard Deviation of Error rate due to neutron energy                                              |            |

| spectrum with respect to Process Corner, Temperature, Voltage and                                                   | 93         |

| Size SIL(A=0,B=1)                                                                                                   |            |

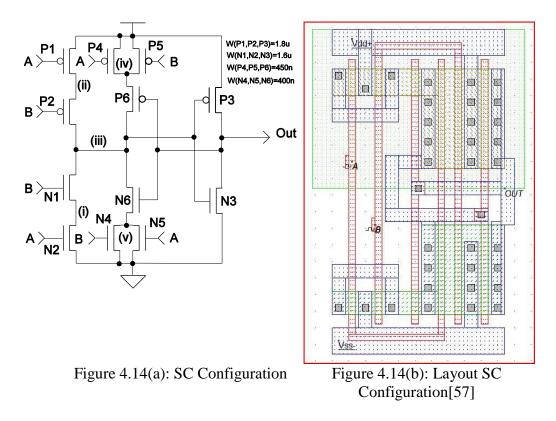

| Figure 4.14: (a) SC Configuration (b): Layout SC Configuration                                                      | 94         |

| Figure 4.15(a): Error rate due to neutron energy spectrum with respect                                              | o <b>r</b> |

| to Process Corner-SC (A=1 B=0)                                                                                      | 95         |

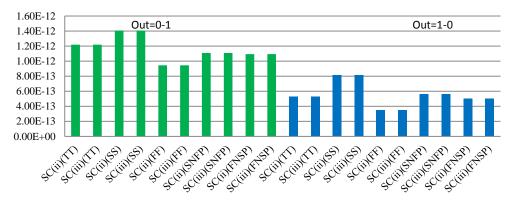

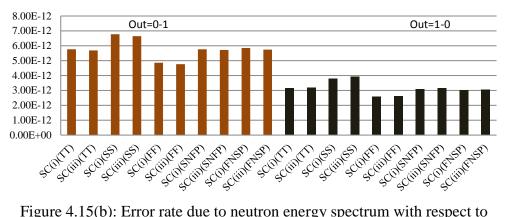

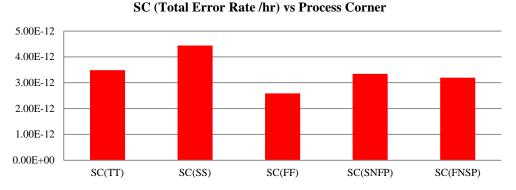

| Figure 4.15(b): Error rate due to neutron energy spectrum with respect $(A \cap B \cap A)$                          | 05         |

| to Process Corner-SC (A=0 B=1)                                                                                      | 95         |

| Figure 4.16(a): Total Error rate due to neutron energy spectrum with respect to Process Corner SC (A=1 B=0)         | 96         |

| Figure 4.16(b): Total Error rate due to neutron energy spectrum with                                                | 90         |

| respect to Process Corner SC (A=0 B=1)                                                                              | 96         |

| Figure 4.17(a): Error rate due to neutron energy spectrum with respect                                              | 70         |

| to Temperature SC (A=1 B=0)                                                                                         | 97         |

| Figure 4.17(b): Error rate due to neutron energy spectrum with respect                                              |            |

| to Temperature SC (A=0 B=1)                                                                                         | 97         |

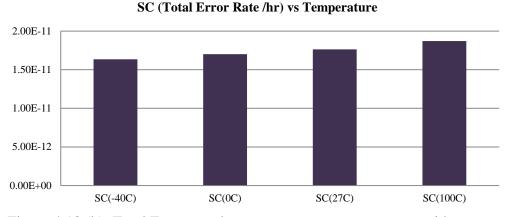

| Figure 4.18(a): Total Error rate due to neutron energy spectrum with                                                |            |

| respect to Temperature-SC (A=1 B=0)                                                                                 | 97         |

| Figure 4.18(b): Total Error rate due to neutron energy spectrum with                                                |            |

| respect to Temperature-SC (A=0 B=1)                                                                                 | 98         |

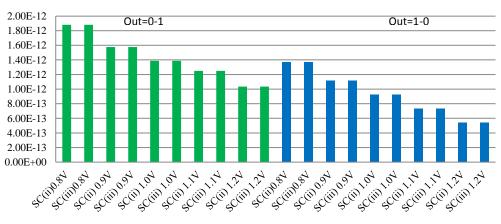

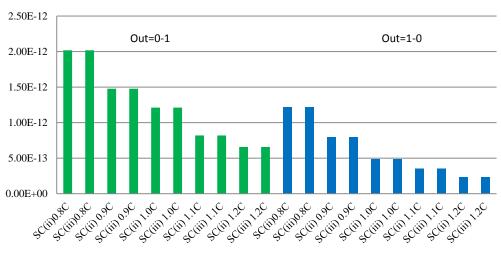

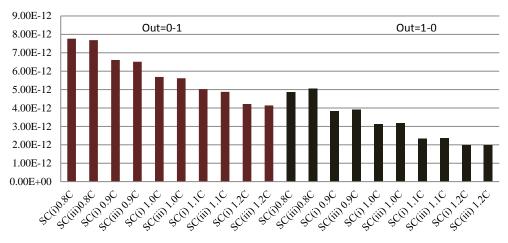

| Figure 4.19(a): Error rate due to neutron energy spectrum with respect                                              |            |

| to Voltage Supply for 50% SC (A=1, B=0)                                                                             | 99         |

| Figure 4.19(b): Error rate due to neutron energy spectrum with respect                                              |            |

| to Voltage Supply for 50% SC (A=0, B=1)                                                                             | 99         |

| Figure 4.20(a): Error rate due to neutron energy spectrum with respect to $V_{c}$ to $V_{c}$ to $P_{c}$ (A=1, P=0)  | 00         |

| to Voltage Supply for 100% SC (A=1, B=0)                                                                            | 99         |

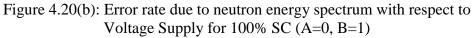

| Figure 4.20(b): Error rate due to neutron energy spectrum with respect to Voltage Supply for $100\%$ SC (A=0, B=1)  | 100        |

| to Voltage Supply for 100% SC (A=0, B=1)<br>Figure 4.21(a): Error rate due to neutron energy spectrum with respect  | 100        |

| to Voltage Supply for $150\%$ SC (A=1, B=0)                                                                         | 100        |

|                                                                                                                     | 100        |

| Figure (1.21(h): Error rate due to neutron energy energy with respect                                              |     |

|--------------------------------------------------------------------------------------------------------------------|-----|

| Figure 4.21(b): Error rate due to neutron energy spectrum with respect to Voltage Supply for 150% SC (A=0, B=1)    | 100 |

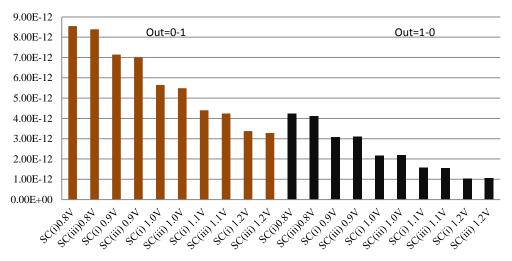

| Figure 4.22(a): Total error rate due to neutron energy spectrum with                                               | 100 |

| respect to Voltage Supply for SC (A=1, B=0)                                                                        | 101 |

| Figure 4.22(b): Total error rate due to neutron energy spectrum with                                               | 101 |

| respect to Voltage Supply for SC (A=0, B=1)                                                                        | 101 |

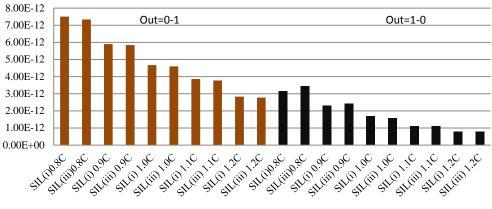

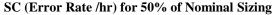

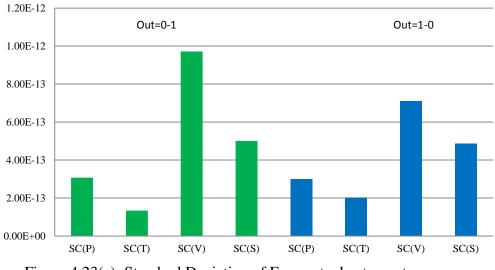

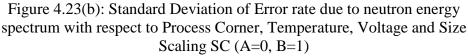

| Figure 4.23 (a): Standard Deviation of Error rate due to neutron                                                   | 101 |

| energy spectrum with respect to Process Corner, Temperature, Voltage                                               | 102 |

| and Size –SC (A=1, B=0)                                                                                            | 102 |

| Figure 4.23 (b): Standard Deviation of Error rate due to neutron                                                   |     |

| energy spectrum with respect to Process Corner, Temperature, Voltage                                               | 102 |

| and Size –SC(A=0, B=1)                                                                                             |     |

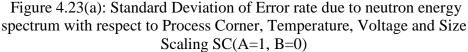

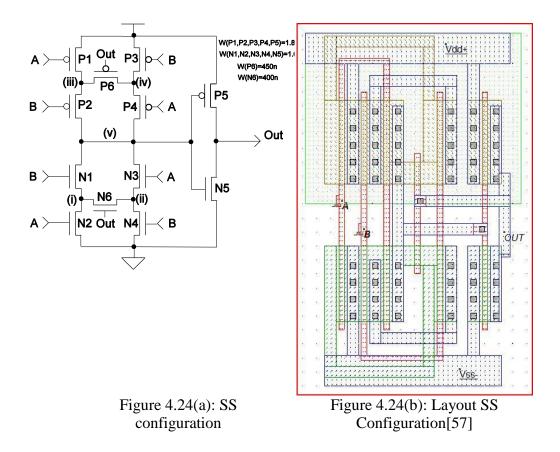

| Figure 4.24: (a) SS Configuration (b): Layout SS Configuration                                                     | 103 |

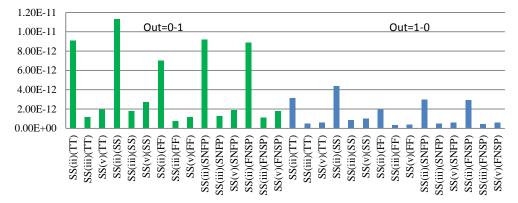

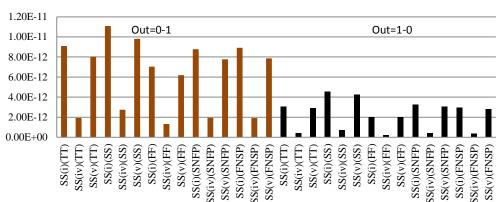

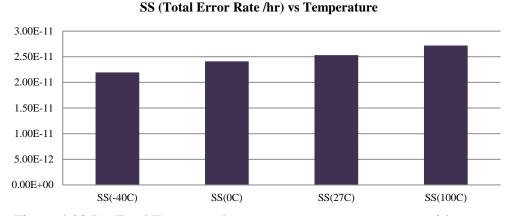

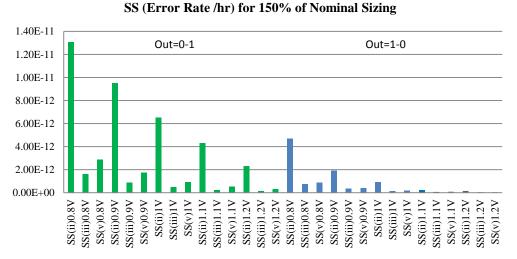

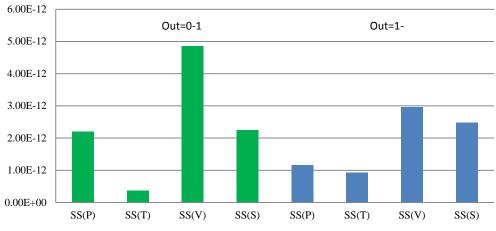

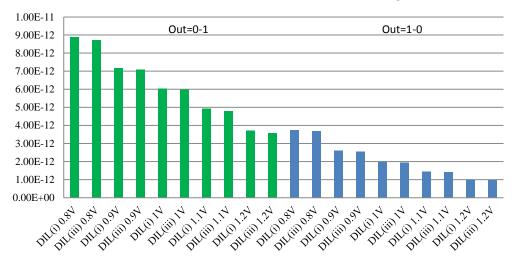

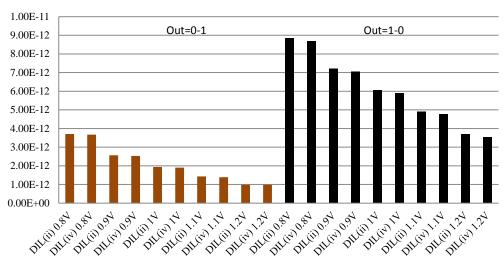

| Figure 4.25(a): Error rate due to neutron energy spectrum with respect                                             |     |

| to Process Corner-SS (A=1, B=0)                                                                                    | 104 |

| Figure 4.25(b): Error rate due to neutron energy spectrum with respect                                             |     |

| to Process Corner-SS (A=0, B=1)                                                                                    | 104 |

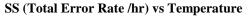

| Figure 4.26 (a): Total Error rate due to neutron energy spectrum with                                              |     |

| respect to Process Corner-SS (A=1, B=0)                                                                            | 105 |

| Figure 4.26(b): Total Error rate due to neutron energy spectrum with                                               |     |

| respect to Process Corner-SS (A=0, B=1)                                                                            | 105 |

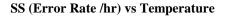

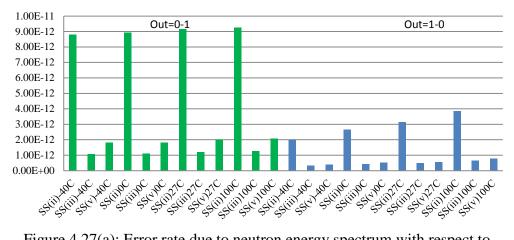

| Figure 4.27(a): Error rate due to neutron energy spectrum with respect                                             |     |

| to Temperature -SS (A=1, B=0)                                                                                      | 106 |

| Figure 4.27(b): Error rate due to neutron energy spectrum with respect                                             |     |

| to Temperature –SS (A=0, B=1)                                                                                      | 106 |

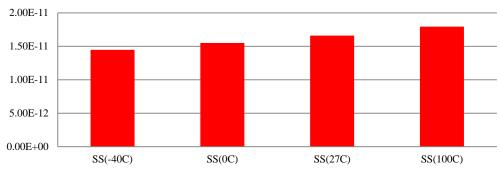

| Figure 4.28(a): Total Error rate due to neutron energy spectrum with                                               |     |

| respect to Temperature-SS(A=1 B=0)                                                                                 | 106 |

| Figure 4.28(b): Total Error rate due to neutron energy spectrum with                                               |     |

| respect to Temperature-SS (A=0, B=1)                                                                               | 107 |

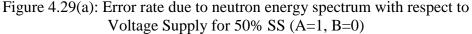

| Figure 4.29(a): Error rate due to neutron energy spectrum with respect                                             | 100 |

| to Voltage Supply for 50% SS (A=1, B=0)                                                                            | 108 |

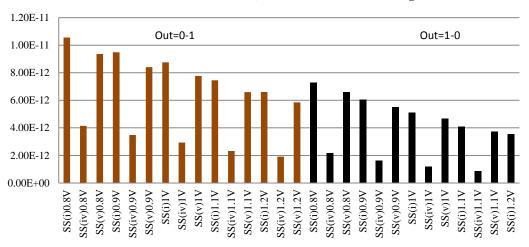

| Figure 4.29(b): Error rate due to neutron energy spectrum with respect                                             | 100 |

| to Voltage Supply for 50% SS (A=0, B=1)                                                                            | 108 |

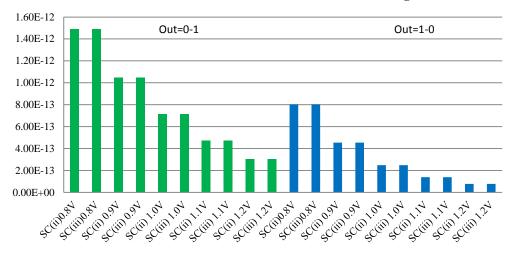

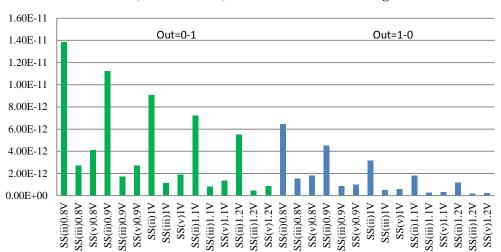

| Figure 4.30(a): Error rate due to neutron energy spectrum with respect to Voltage Supply for $100\%$ SS (A=1, B=0) | 100 |

| to Voltage Supply for 100% SS (A=1, B=0)                                                                           | 108 |

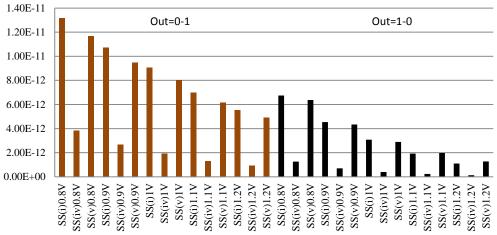

| Figure 4.30(b): Error rate due to neutron energy spectrum with respect to Voltage Supply for 100% SS (A=0, B=1)    | 109 |

| Figure 4.31(a): Error rate due to neutron energy spectrum with respect                                             | 109 |

| to Voltage Supply for 150% SS (A=1, B=0)                                                                           | 109 |

| Figure 4.31(b): Error rate due to neutron energy spectrum with respect                                             | 107 |

| to Voltage Supply for 150% SS (A=0, B=1)                                                                           | 109 |

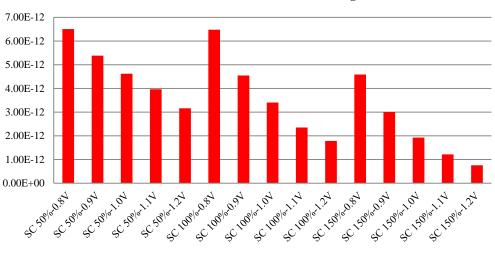

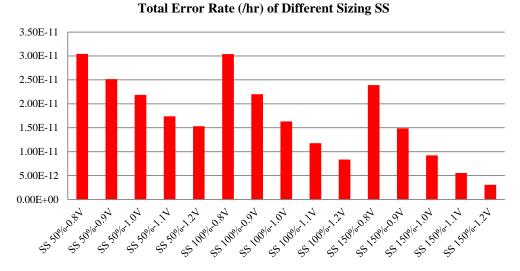

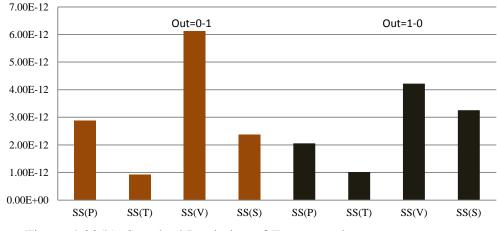

| Figure 4.32(a): Total error rate due to neutron energy spectrum with                                               | 107 |

| respect to Voltage Supply for SS (A=1, B=0)                                                                        | 110 |

| Figure 4.32(b): Total error rate due to neutron energy spectrum with                                               | 110 |

| respect to Voltage Supply for SS (A=0, B=1)                                                                        | 110 |

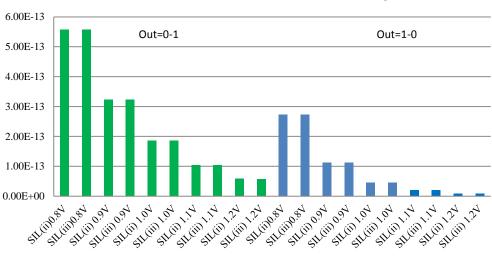

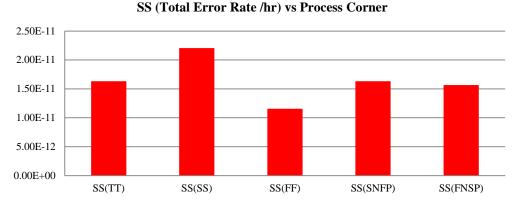

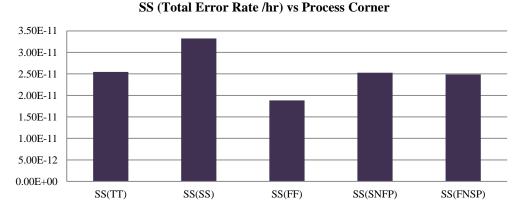

| Figure 4.33(a): Standard Deviation of Error rate due to neutron energy                                             | 110 |

| spectrum with respect to Process Corner, Temperature, Voltage and                                                  | 111 |

| Size SS(A=1, B=0)                                                                                                  | -   |

| Figure 4.33(b): Standard Deviation of Error rate due to neutron energy                                             |     |

| spectrum with respect to Process Corner, Temperature, Voltage and                                                  | 111 |

| Size SS(A=0, B=1)                                                                                                  |     |

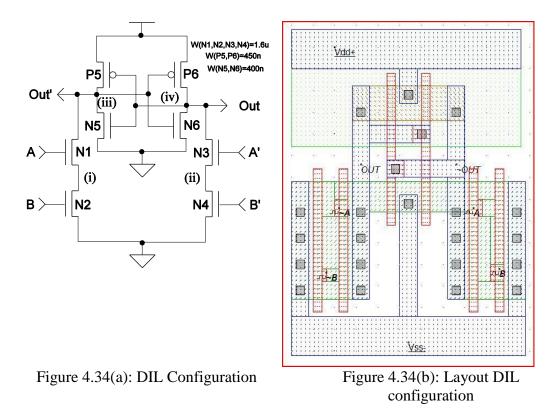

| Figure 4.34: DIL Configuration (b): Layout DIL Configuration                                                       | 112 |

| - · · · · · · ·                                                                                                    |     |

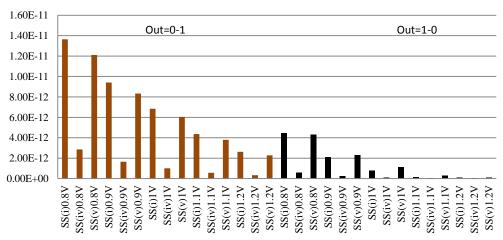

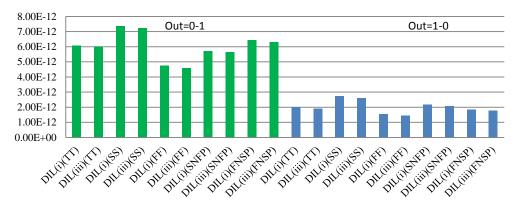

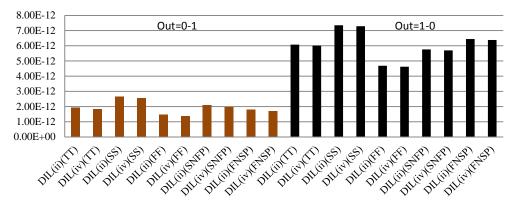

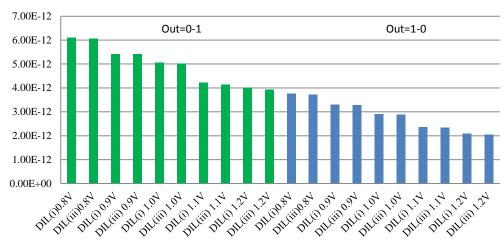

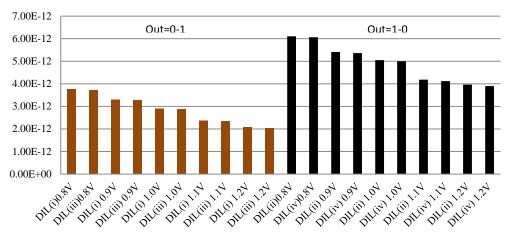

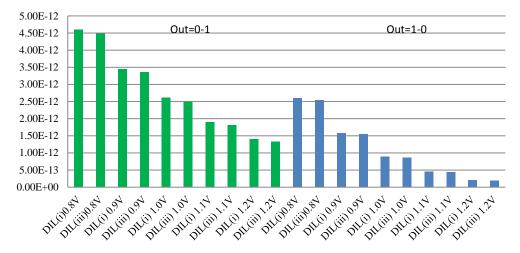

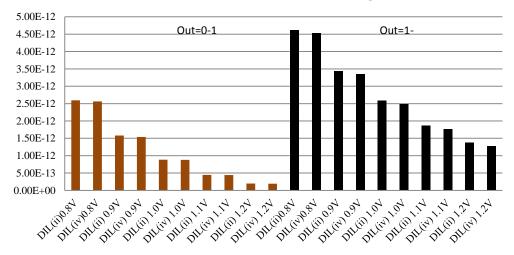

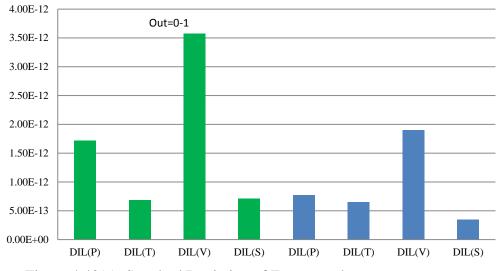

| Figure 4.35(a): Error rate due to neutron energy spectrum with respect to Process Corner-DIL (A=1, B=0)               | 113 |

|-----------------------------------------------------------------------------------------------------------------------|-----|

| Figure 4.35(b): Error rate due to neutron energy spectrum with respect                                                | 115 |

| to Process Corner-DIL(A=0, B=1)                                                                                       | 113 |

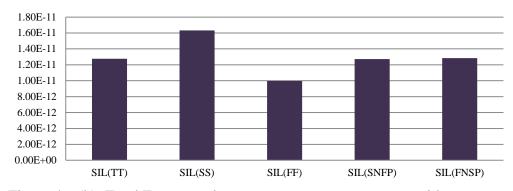

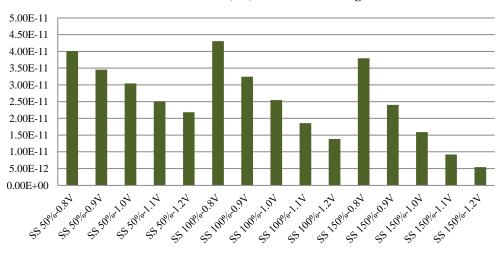

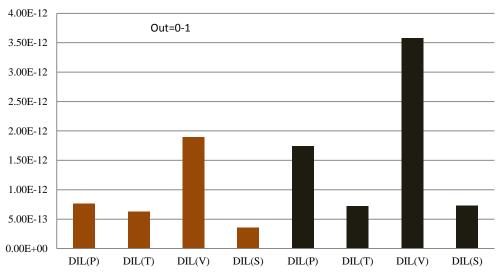

| Figure 4.36(a): Total Error rate due to neutron energy spectrum with                                                  |     |

| respect to Process Corner-DIL (A=1, B=0)                                                                              | 114 |

| Figure 4.36 (b): Total Error rate due to neutron energy spectrum with                                                 |     |

| respect to Process Corner-DIL (A=0, B=1)                                                                              | 114 |

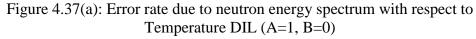

| Figure 4.37(a): Error rate due to neutron energy spectrum with respect $T$                                            | 117 |

| to Temperature -DIL (A=1, B=0)                                                                                        | 115 |

| Figure 4.37(b): Error rate due to neutron energy spectrum with respect to Temperature DII ( $A=0$ , $B=1$ )           | 115 |

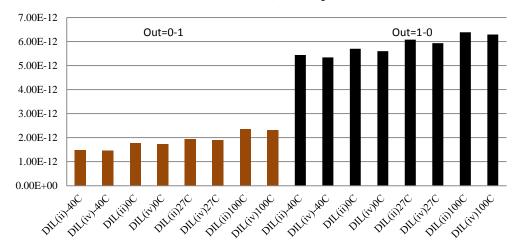

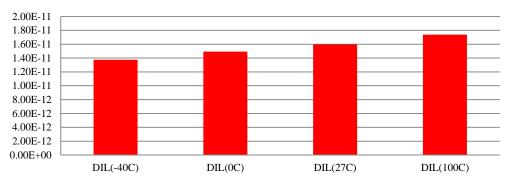

| to Temperature -DIL (A=0, B=1)<br>Figure 4.38(a): Total Error rate due to neutron energy spectrum with                | 115 |

| respect to Temperature-DIL (A=1, B=0)                                                                                 | 115 |

| Figure 4.38(b): Total Error rate due to neutron energy spectrum with                                                  | 115 |

| respect to Temperature-DIL (A=0 B=1)                                                                                  | 116 |

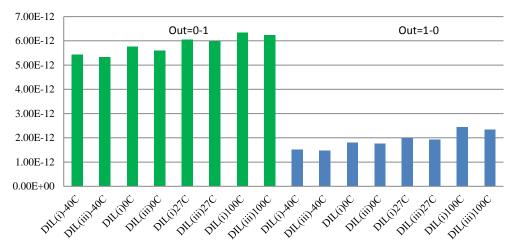

| Figure 4.39(a): Error rate due to neutron energy spectrum with respect                                                | 110 |

| to Voltage Supply for 50% DIL (A=1, B=0)                                                                              | 116 |

| Figure 4.39(b): Error rate due to neutron energy spectrum with respect                                                |     |

| to Voltage Supply for 50% DIL (A=0, B=1)                                                                              | 117 |

| Figure 4.40(a): Error rate due to neutron energy spectrum with respect                                                |     |

| to Voltage Supply for 100% DIL (A=1, B=0)                                                                             | 117 |

| Figure 4.40(b): Error rate due to neutron energy spectrum with respect                                                |     |

| to Voltage Supply for 100% DIL (A=0, B=1)                                                                             | 117 |

| Figure 4.41(a): Error rate due to neutron energy spectrum with respect                                                | 110 |

| to Voltage Supply for 150% DIL (A=1, B=0)                                                                             | 118 |

| Figure 4.41(b): Error rate due to neutron energy spectrum with respect to Valtage Superly for $150\%$ (DH (A=0, D=1)) | 110 |

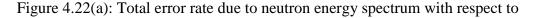

| to Voltage Supply for 150% DIL (A=0, B=1)<br>Figure 4.42(a): Total error rate due to neutron energy spectrum with     | 118 |

| respect to Voltage Supply for DIL (A=1, B=0)                                                                          | 118 |

| Figure 4.42(b): Total error rate due to neutron energy spectrum with                                                  | 110 |

| respect to Voltage Supply for DIL (A=0, B=1)                                                                          | 119 |

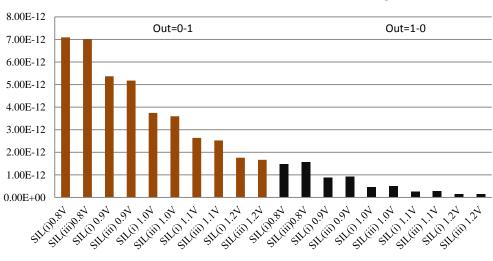

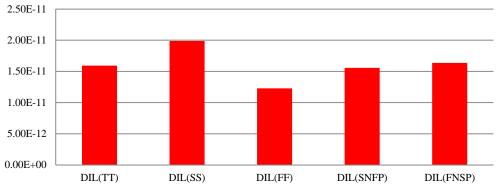

| Figure 4.43(a): Standard Deviation of Error rate due to neutron energy                                                |     |

| spectrum with respect to Process Corner, Temperature, Voltage and                                                     | 120 |

| Size DIL (A=1, B=0)                                                                                                   |     |

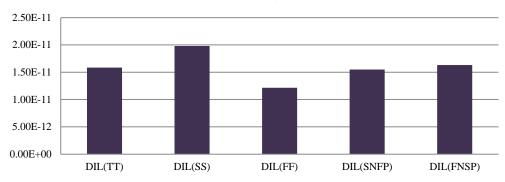

| Figure 4.43 (b): Standard Deviation of Error rate due to neutron                                                      |     |

| energy spectrum with respect to Process Corner, Temperature, Voltage                                                  | 120 |

| and Size DIL (A=0, B=1)                                                                                               |     |

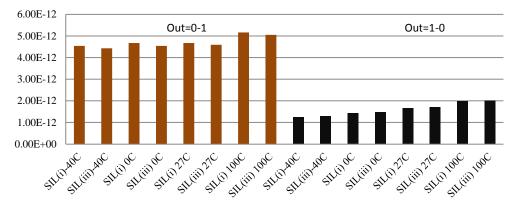

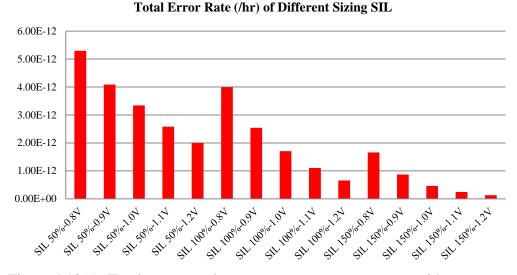

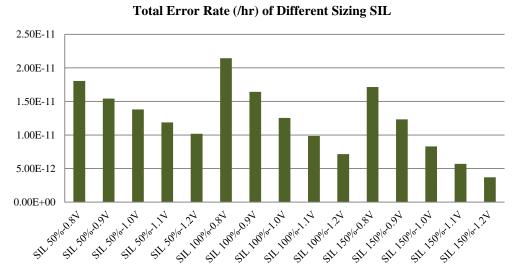

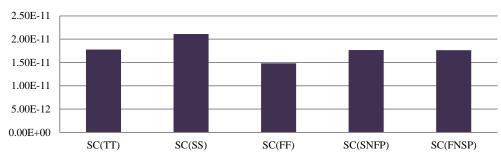

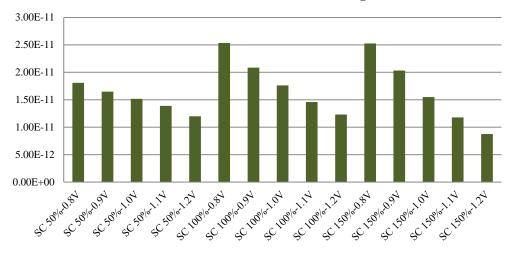

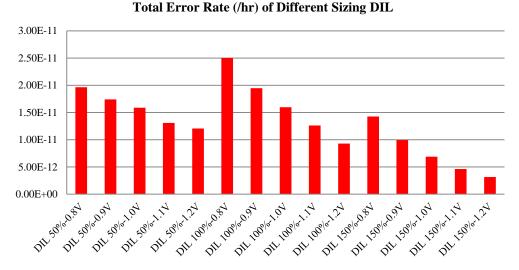

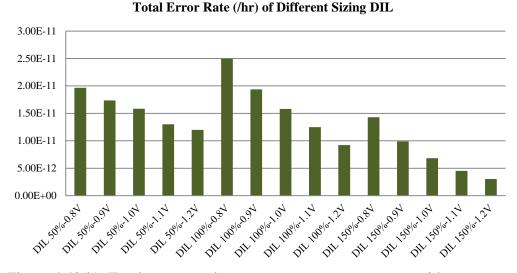

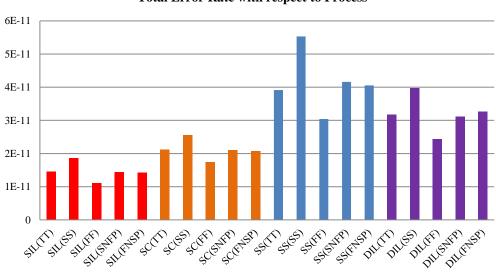

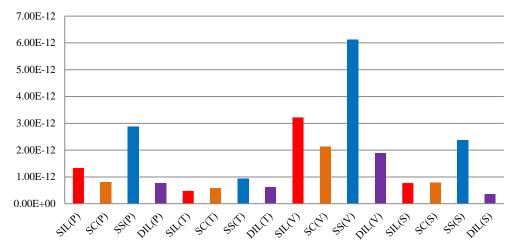

| Figure 4.44: Comparison of total error rate due to neutron energy                                                     |     |

| spectrum with respect to process at nominal sizing                                                                    | 121 |

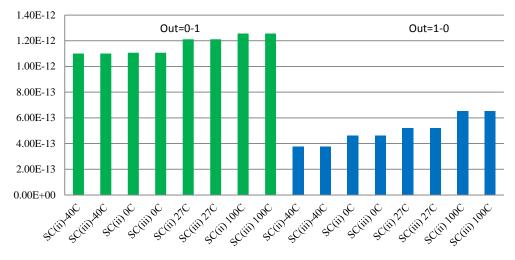

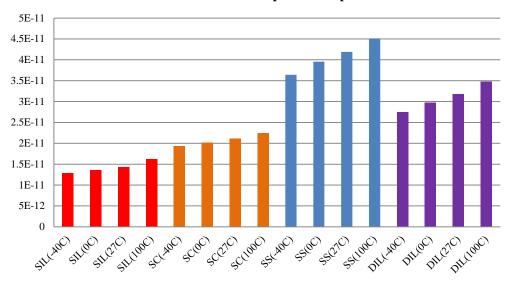

| Figure 4.45: Comparison of total error rate due to neutron energy                                                     | 100 |

| spectrum with respect to temperature at nominal sizing                                                                | 122 |

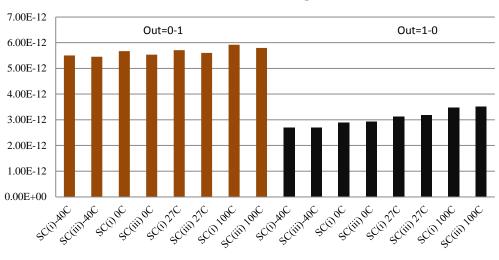

| Figure 4.46: Comparison of total error rate due to neutron energy                                                     | 122 |

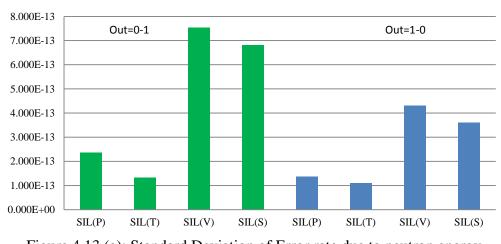

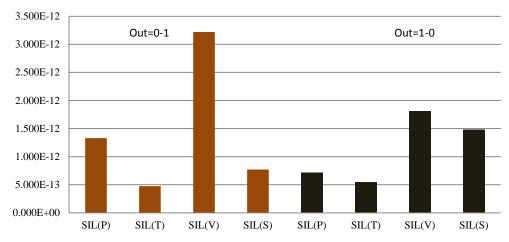

| spectrum with respect to voltage at nominal sizing<br>Figure 4.47(a): Standard deviation of error rate due to neutron | 122 |

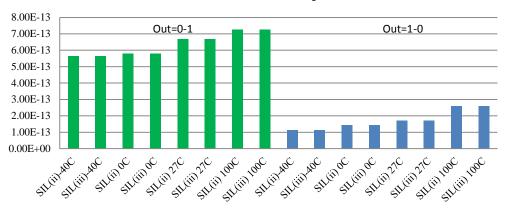

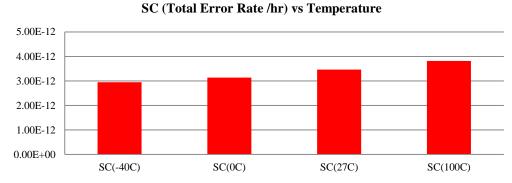

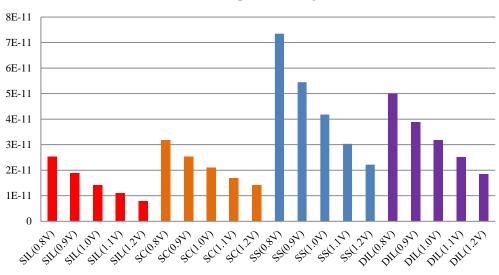

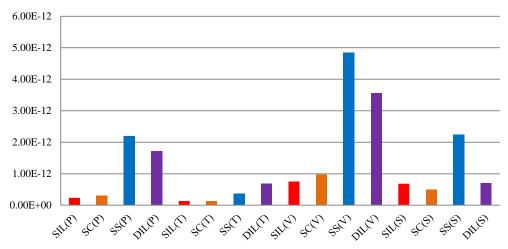

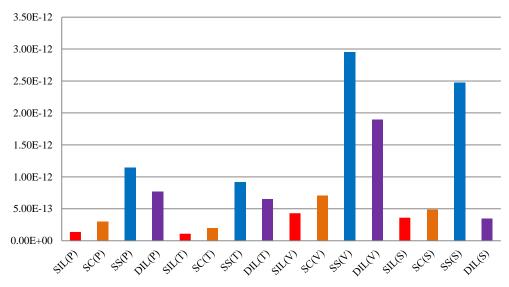

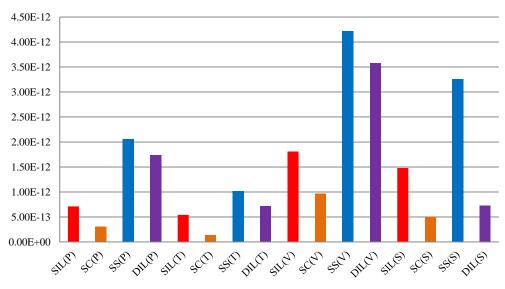

| spectrum energy for $0-1(A=1, B=0)$ .                                                                                 | 123 |

| Figure 4.47(b): Standard deviation of error rate due to neutron                                                       | 125 |

| spectrum energy for $1-0(A=1, B=0)$ .                                                                                 | 123 |

| Figure 4.48(a): Standard deviation of error rate due to neutron                                                       |     |

| spectrum energy for 0-1(A=0, B=1)                                                                                     | 124 |

| Figure 4.48(b): Standard deviation of error rate due to neutron                                                       |     |

| spectrum energy for 1-0(A=0, B=1)                                                                                     | 124 |

|                                                                                                                       |     |

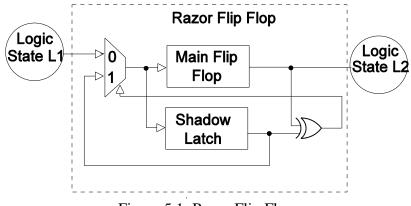

| Figure 5.1: Razor Flip Flop                                                                                                                       | 128 |

|---------------------------------------------------------------------------------------------------------------------------------------------------|-----|

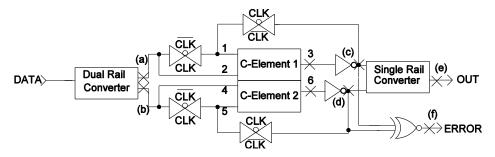

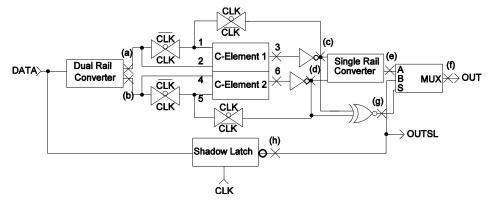

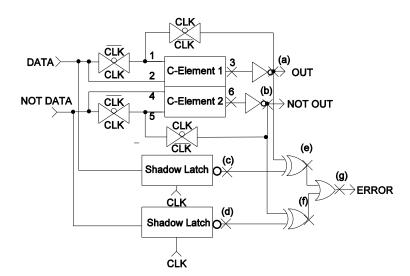

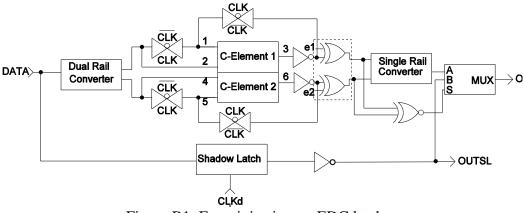

| Figure 5.2 : Proposed ED single rail latch                                                                                                        | 128 |

| Figure 5.3: Dual Rail Converter with vulnerable nodes                                                                                             | 129 |

| Figure 5.4 : Single Rail Converter with vulnerable nodes                                                                                          | 129 |

| Figure 5.5: Fault-free and Error Detected operation at the middle of                                                                              |     |

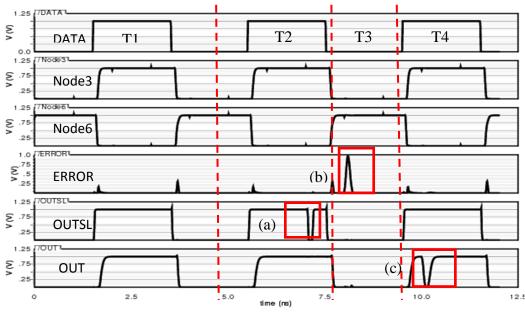

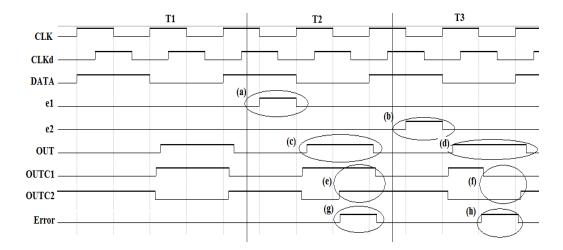

| the functional signal for ED Latch                                                                                                                | 131 |

| Figure 5.6: Fault-free and Error Detected operation at the edge of the                                                                            |     |

| functional signal for ED Latch                                                                                                                    | 131 |

| Figure 5.7: Statistical Variation of $V_{DD}$ +-20% of Nominal Value for                                                                          |     |

| Fault Free and Error Detected at the middle of functional signal for                                                                              | 132 |

| ED Latch                                                                                                                                          |     |

| Figure 5.8: Statistical Variation of $V_{DD}$ +-20% of Nominal Value for                                                                          |     |

| Fault Free and Error Detected at the edges of the functional signal for                                                                           | 133 |

| ED Latch                                                                                                                                          |     |

| Figure 5.9: Propagation delay of ED latch with respect to Process                                                                                 |     |

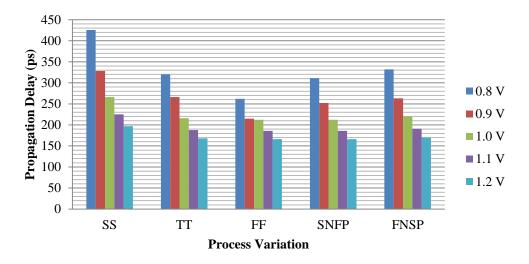

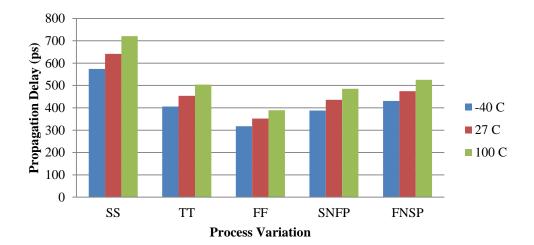

| Variation and Temperature                                                                                                                         | 134 |

| Figure 5.10: Propagation delay of ED latch with respect to Process                                                                                |     |

| Variation and Voltage Supply.                                                                                                                     | 135 |

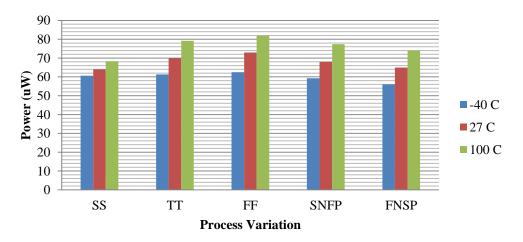

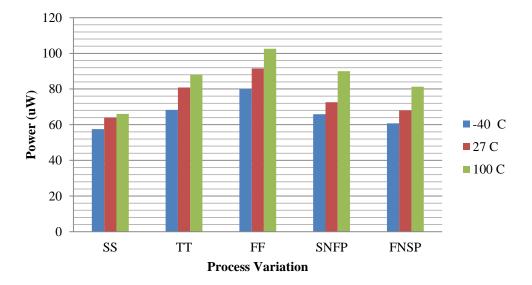

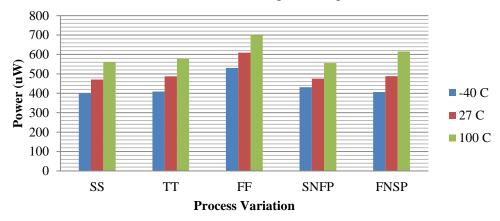

| Figure 5.11 Power Dissipation of ED latch with respect to Process                                                                                 |     |

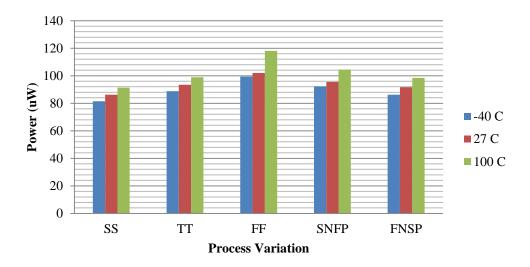

| Variation and Temperature.                                                                                                                        | 135 |

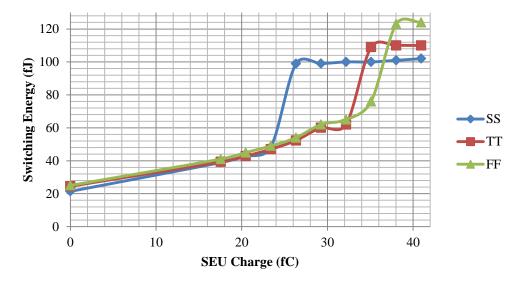

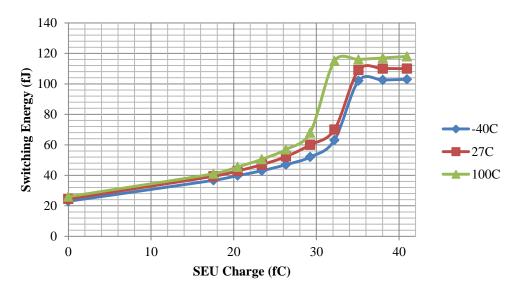

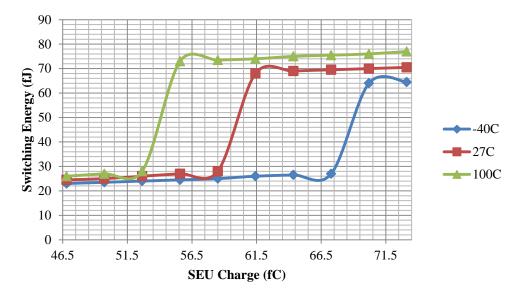

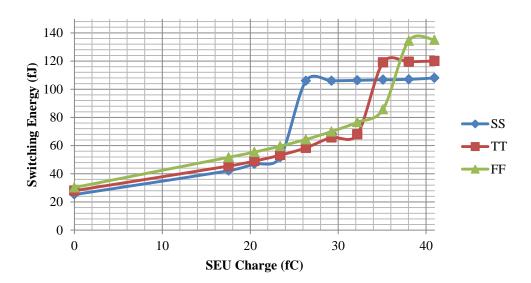

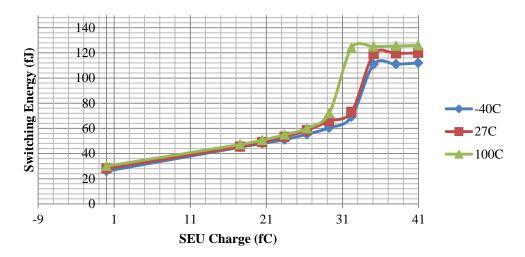

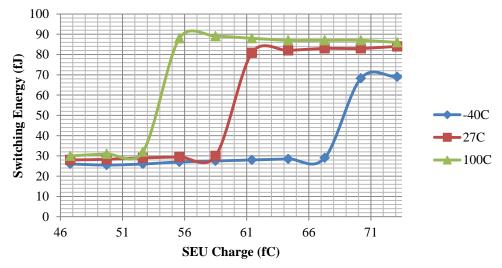

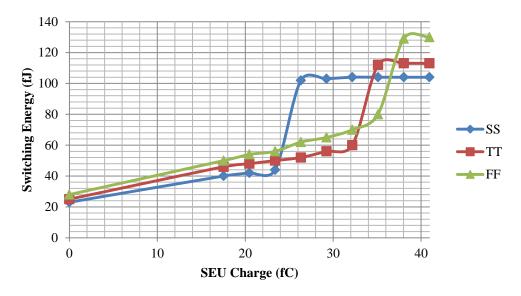

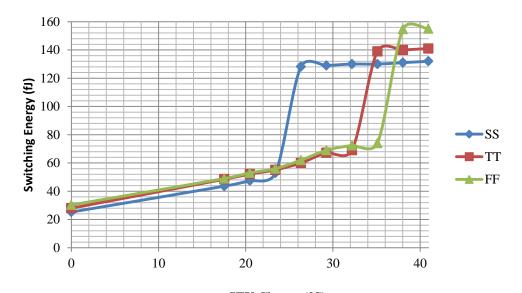

| Figure 5.12: Switching Energy for ED Latch (0-1 Change) with                                                                                      |     |

| Different Process.                                                                                                                                | 137 |

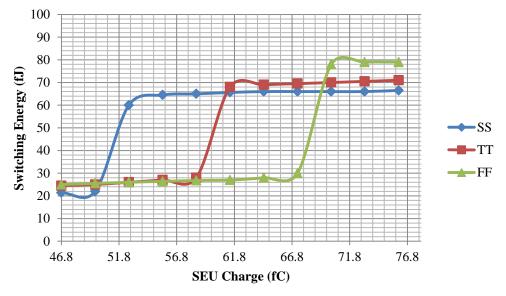

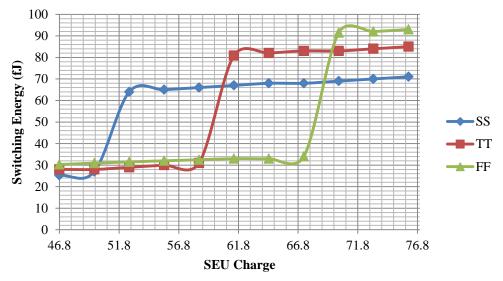

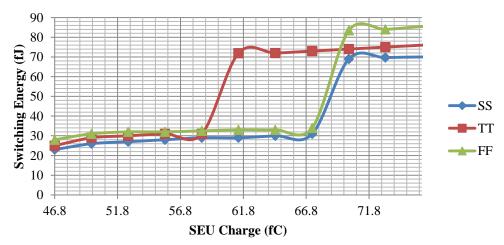

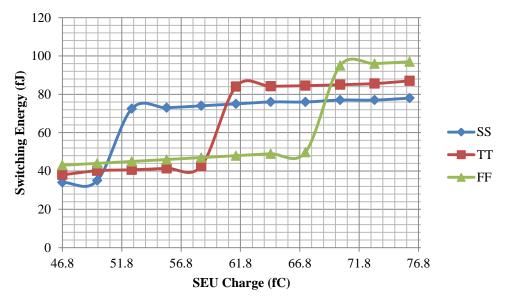

| Figure 5.13: Switching Energy for ED Latch (1-0 Change) with                                                                                      | 137 |

| Different Process                                                                                                                                 | 107 |

| Figure 5.14: Switching Energy for ED Latch (0-1 Change) with                                                                                      |     |

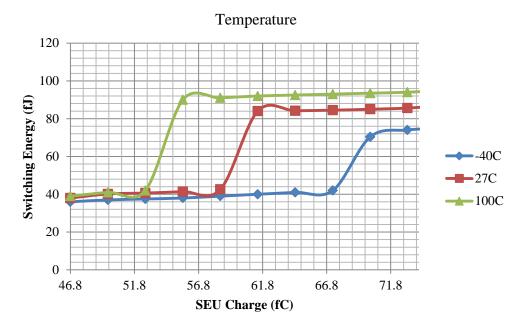

| Different Temperature.                                                                                                                            | 138 |

| Figure 5.15: Switching Energy for ED Latch (1-0 Change) with                                                                                      | 100 |

| Different Temperature.                                                                                                                            | 139 |

| Figure 5.16: ED Latch with vulnerable nodes                                                                                                       | 139 |

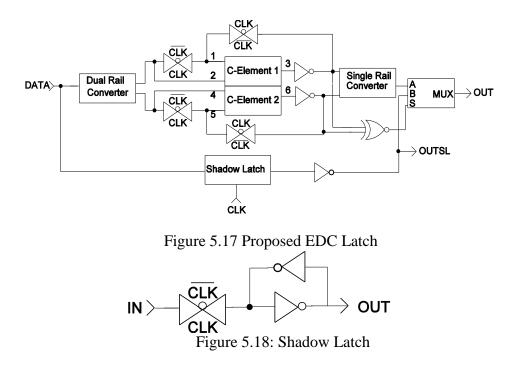

| Figure 5.17: Proposed EDC Latch                                                                                                                   | 140 |

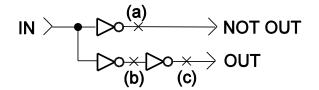

| Figure 5.18: Shadow Latch                                                                                                                         | 140 |

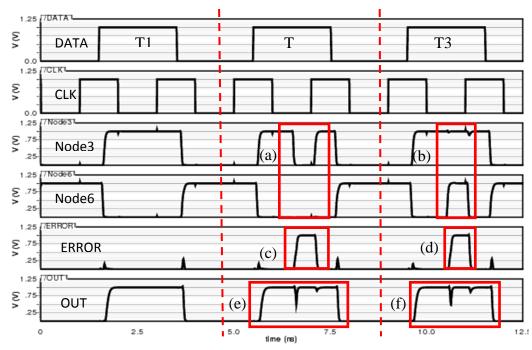

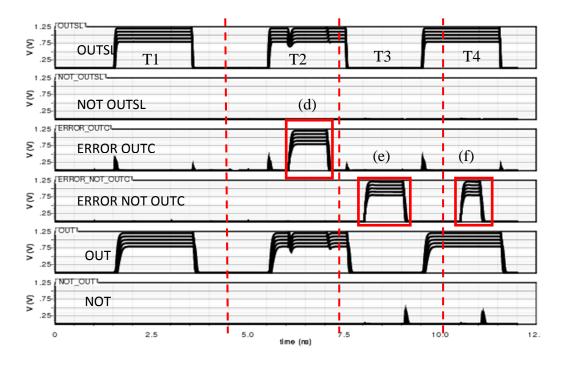

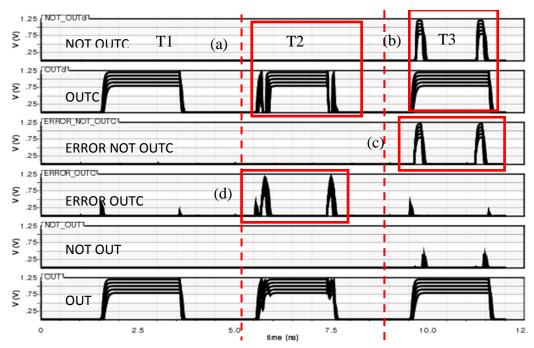

| Figure 5.19: Fault Free, Error Detected and Error Corrected at the                                                                                | 110 |

| center of the functional signal of for EDC Latch                                                                                                  | 142 |

| Figure 5.20: Fault Free, Error Detected and Error Corrected at the                                                                                | 112 |

| edge of the functional signal of for EDC Latch                                                                                                    | 143 |

| Figure 5.21: Statistical Variation of $V_{DD}$ +-20% of Nominal Value for                                                                         | 110 |

| Figure 5.21. Statistical valuation of $V_{DD}$ = 20% of Romman value for<br>Fault Free and Error Corrected at the middle of functional signal for | 144 |

| EDC Latch                                                                                                                                         | 111 |

| Figure 5.22: Statistical Variation of $V_{DD}$ +-20% of Nominal Value for                                                                         |     |

| Figure 3.22. Statistical variation of $v_{DD}$ = 20% of Romman value for<br>Fault Free and Error Corrected at the edge of functional signal for   | 144 |

| EDC Latch                                                                                                                                         | 144 |

| Figure 5.23: Propagation delay of EDC latch with respect to Process                                                                               |     |

| Variation and Temperature.                                                                                                                        | 145 |

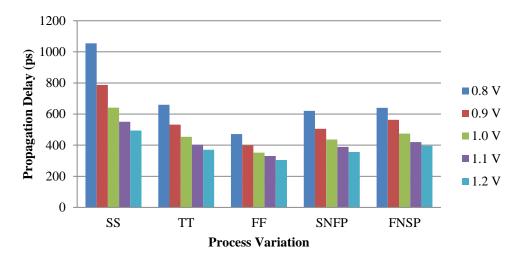

| Figure 5.24: Propagation delay of EDC latch with respect to Process                                                                               | 145 |

| Variation and Voltage Supply                                                                                                                      | 146 |

| Figure 5.25: Propagation delay of EDC latch with respect to Process                                                                               | 140 |

| Variation and Temperature                                                                                                                         | 146 |

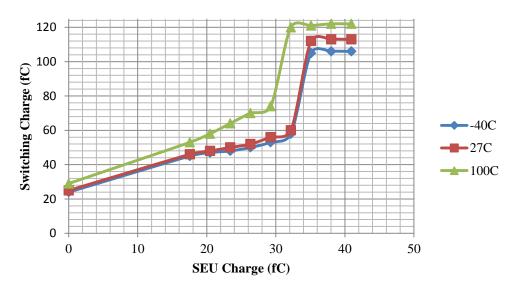

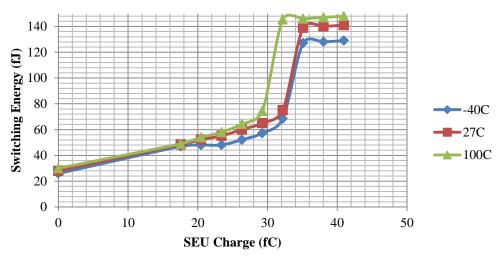

| Figure 5.26: Switching Energy for EDC Latch (0-1 Change) with                                                                                     | 140 |

| Different Process Variation                                                                                                                       | 147 |

| Figure 5.27: Switching Energy for EDC Latch (1-0 Change) with                                                                                     | 14/ |

| Different Process Variation                                                                                                                       | 147 |

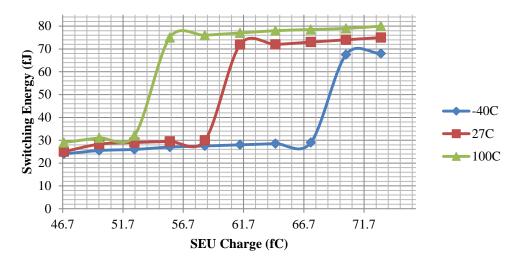

| Figure 5.28: Switching Energy for EDC Latch (0-1 Change) with                                                                                     | 14/ |

| rigure 5.20. Switching Energy for EDC Later (0-1 Change) with                                                                                     |     |

| Different Temperature                                                     | 148   |

|---------------------------------------------------------------------------|-------|

| Figure 5.29: Switching Energy for EDC Latch (1-0 Change) with             |       |

| Different Temperature                                                     | 148   |

| Figure 5.30: EDC Latch with vulnerable nodes                              | 149   |

| Figure 5.31: Dual Rail Converter with vulnerable nodes                    | 149   |

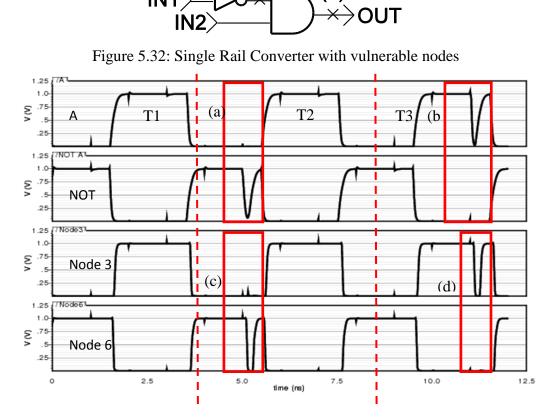

| Figure 5.32: Single Rail Converter with vulnerable nodes                  | 150   |

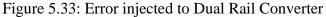

| Figure 5.33: Error injected to Dual Rail Converter                        | 150   |

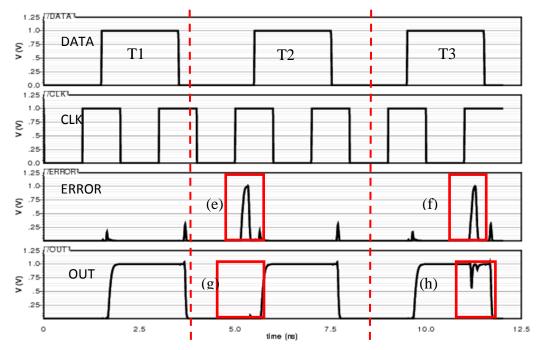

| Figure 5.34: Corrected error due to the injected error to Dual Rail       |       |

| Converter                                                                 | 151   |

| Figure 5.35: Error is injected to Shadow Latch, XNOR gate and Single      | 1 7 1 |

| Rail Converter.                                                           | 151   |

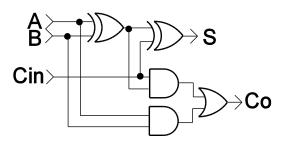

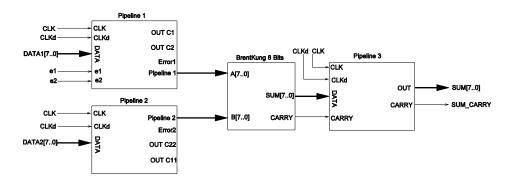

| Figure 5.36 : Full Adder Circuit.                                         | 152   |

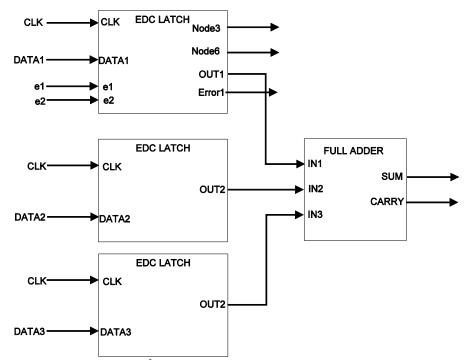

| Figure 5.37: Full Set-up of Adder System with EDC Latches                 | 153   |

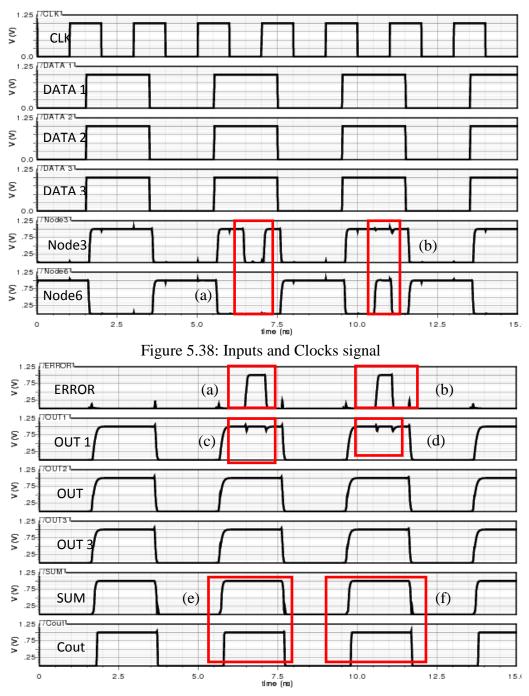

| Figure 5.38: Inputs and Clocks signal                                     | 154   |

| Figure 5.39: Output of C-elements, and Error Signal                       | 154   |

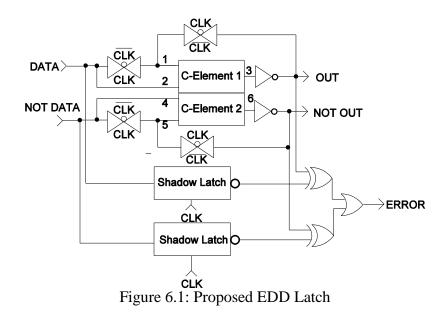

| Figure 6.1: Proposed EDD Latch                                            | 157   |

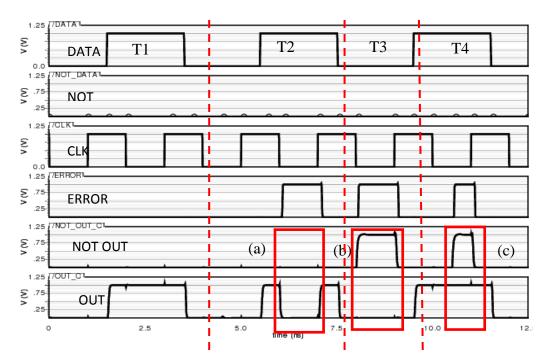

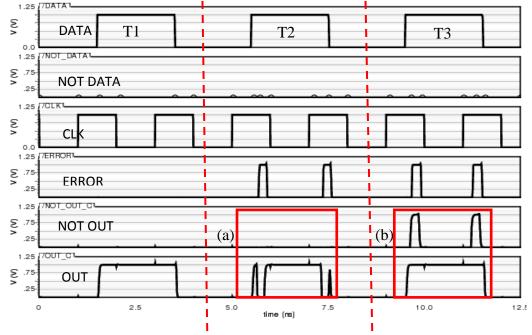

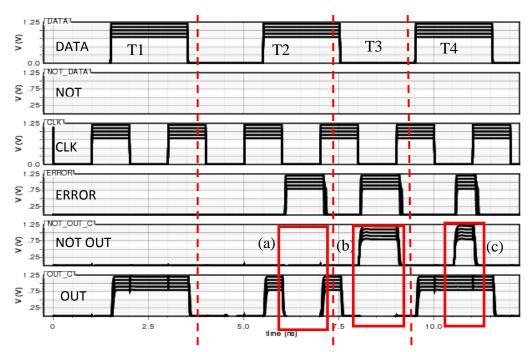

| Figure 6.2: Fault-free and Error Detected at the middle of the            |       |

| functional signal for EDD Latch                                           | 159   |

| Figure 6.3: Fault-free and Error Detected at the edge of the functional   |       |

| signal for EDD Latch                                                      | 159   |

| Figure 6.4: Statistical Variation of $V_{DD}$ +-20% of Nominal Value for  |       |

| Fault Free and Error Detected at the middle of the functional signal for  |       |

| EDD Latch                                                                 | 160   |

| Figure 6.5: Statistical Variation of $V_{DD}$ +-20% of Nominal Value for  |       |

| Fault Free and Error Detected at the edge of the functional signal for    |       |

| EDD Latch                                                                 | 160   |

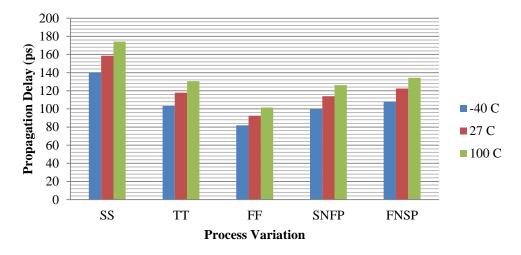

| Figure 6.6: Propagation delay of EDD latch with respect to Process        |       |

| Variation and Temperature                                                 | 161   |

| Figure 6.7: Propagation delay of EDD latch with respect to Process        |       |

| Variation and Voltage Supply                                              | 162   |

| Figure 6.8: Power Dissipation of EDD latch with respect to Process        |       |

| Variation and Temperature                                                 | 162   |

| Figure 6.9: Switching Energy for EDD Latch (0-1 Change) with              | 164   |

| different Process                                                         |       |

| Figure 6.10:Switching Energy for EDD Latch (1-0 Change) with              |       |

| Different Process                                                         | 164   |

| Figure 6.11: Switching Energy for EDD Latch (0-1 Change) with             |       |

| Different Temperature                                                     | 164   |

| Figure 6.12: Switching Energy for EDD Latch (1-0 Change) with             |       |

| Different Temperature                                                     | 165   |

| Figure 6.13: Vulnerable nodes on EDD Latch                                | 166   |

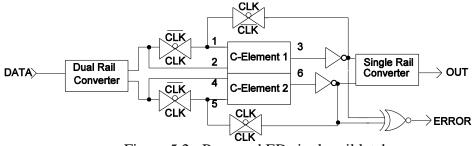

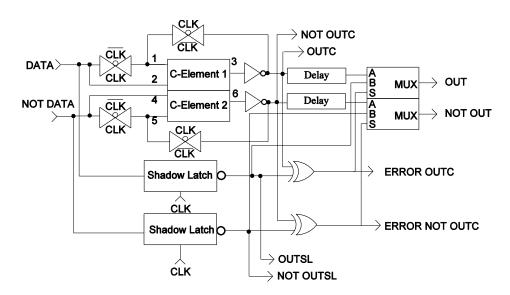

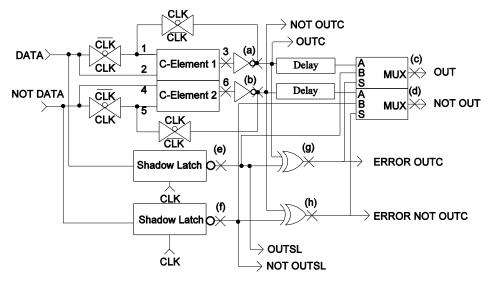

| Figure 6.14: Proposed EDCD Latch                                          | 166   |

| Figure 6.15: No delay inserted at the output of C-element                 | 167   |

| Figure 6.16: Correct delay inserted at the output of C-element            | 168   |

| Figure 6.17: Delay is longer than error signal pulse                      | 168   |

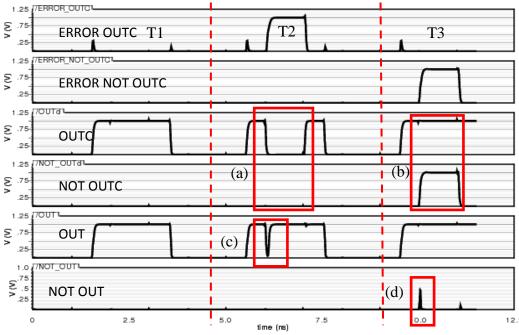

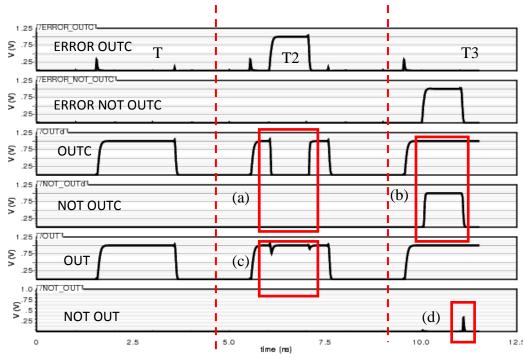

| Figure 6.18: Fault Free and Error Injected for EDCD                       |       |

| Latch                                                                     | 169   |

| Figure 6.19: Fault Free and Error Detected and Corrected at the           |       |

| middle of the functional signal                                           | 170   |

| Figure 6.20: Fault Free and Error Detected and Corrected at the edge      |       |

| of the functional signal                                                  | 171   |

| Figure 6.21: Statistical Variation of $V_{DD}$ +-20% of Nominal Value for |       |

| Fault Free, Error Injected at the middle of the functional signal for EDCD Latch                                                           | 171   |

|--------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Figure 6.22: Statistical Variation of $V_{DD}$ +-20% of Nominal Value for<br>Fault Free, Error Detected and Corrected at the middle of the | 172   |

| functional signal for EDCD Latch.                                                                                                          | 1/2   |

| Figure 6.23: Statistical Variation of $V_{DD}$ +-20% of Nominal Value for                                                                  |       |

| Fault Free, Error Detected and Corrected at the edge of the functional                                                                     | 170   |

| signal for EDCD Latch                                                                                                                      | 173   |

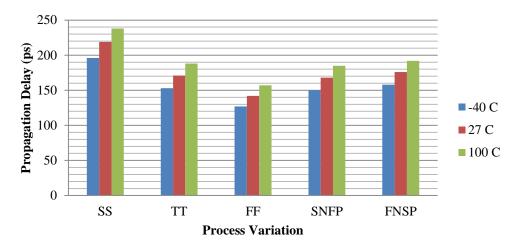

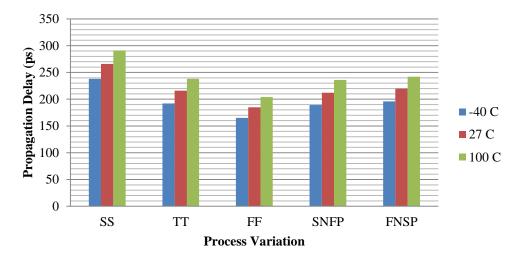

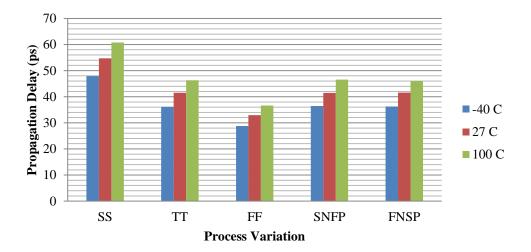

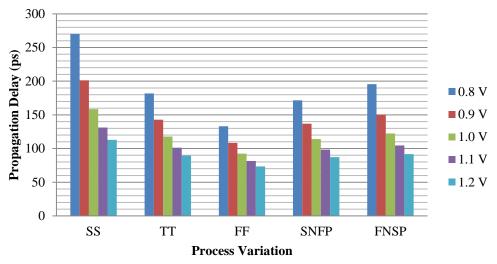

| Figure 6.24: Propagation delay of EDCD latch with respect to Process                                                                       | 174   |

| Variation and Temperature.                                                                                                                 | 174   |

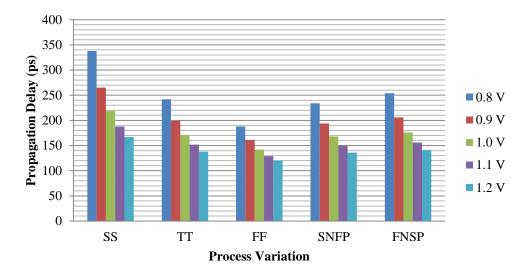

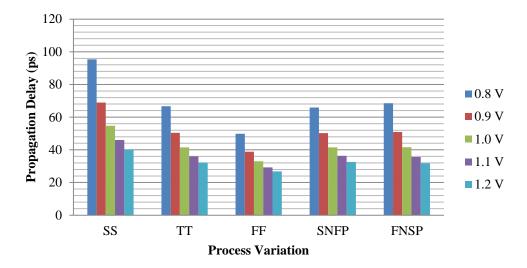

| Figure 6.25: Propagation delay of EDCD latch with respect to Process                                                                       | 174   |

| Variation and Voltage Supply.                                                                                                              | 174   |

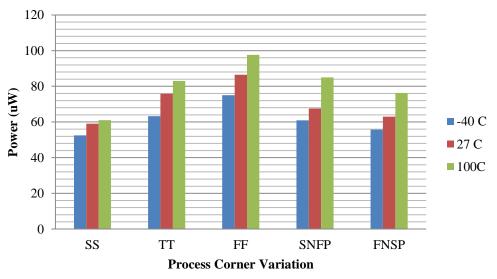

| Figure 6.26: Power Dissipation of EDCD latch with respect to Process                                                                       | 1.7.5 |

| Variation and Temperature.                                                                                                                 | 175   |

| Figure 6.27: Switching Energy for EDCD Latch (0-1 Change) with different Process.                                                          | 176   |

| Figure 6.28: Switching Energy for EDCD Latch (1-0 Change) with                                                                             |       |

| different Process                                                                                                                          | 176   |

| Figure 6.29: Switching Energy for EDCD Latch (0-1 Change) with                                                                             |       |

| Different Temperature.                                                                                                                     | 177   |

| Figure 6.30: Switching Energy for EDCD Latch (1-0 Change) with                                                                             |       |

| Different Temperature                                                                                                                      | 177   |

| Figure 6.31: Vulnerable nodes on EDCD latch                                                                                                | 178   |

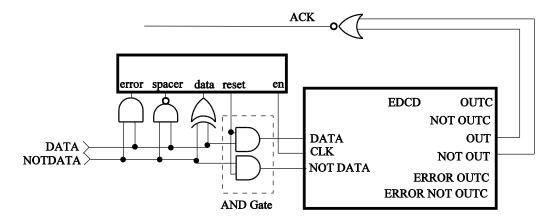

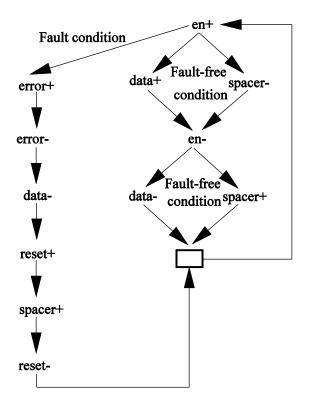

| Figure 6.32: Proposed EDCDT Latch                                                                                                          | 180   |

| Figure 6.33: Signal transition graph (STG)                                                                                                 | 180   |

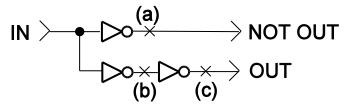

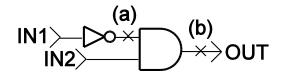

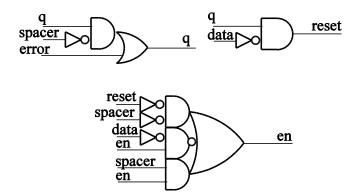

| Figure 6.34: Logic gates for the controller                                                                                                | 181   |

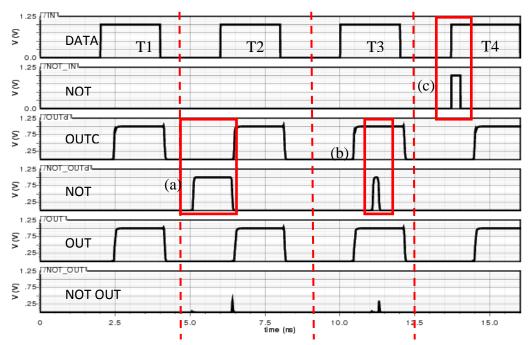

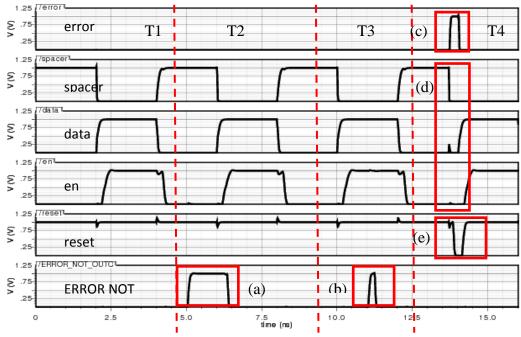

| Figure 6.35: Fault Free, Error Detected and Error Corrected for                                                                            |       |

| EDCDT Latch                                                                                                                                | 182   |

| Figure 6.36: Control Signal for EDCDT Latch                                                                                                | 182   |

| Figure 6.37: Statistical Variation of $V_{DD}$ +-20% of Nominal Value for                                                                  |       |

| Output of EDCDT Latch                                                                                                                      | 183   |

| Figure 6.38: Statistical Variation of $V_{DD}$ +-20% of Nominal Value for                                                                  |       |

| Control Signal of EDCDT Latch.                                                                                                             | 183   |

| Figure 6.39: Propagation delay of EDCDT latch with respect to                                                                              |       |

| Process Variation and Temperature                                                                                                          | 184   |

| Figure 6.40: Propagation delay of EDCDT latch with respect to                                                                              |       |

| Process Variation and Voltage Scaling                                                                                                      | 185   |

| Figure 6.41: Power Dissipation of EDCDT latch with respect to                                                                              |       |

| Process Variation and Temperature                                                                                                          | 185   |

| Figure 7.1: Synthesize C-element                                                                                                           | 188   |

| Figure 7.2: Synthesize Shadow Latch                                                                                                        | 188   |

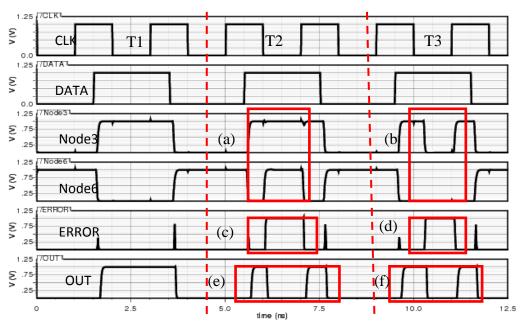

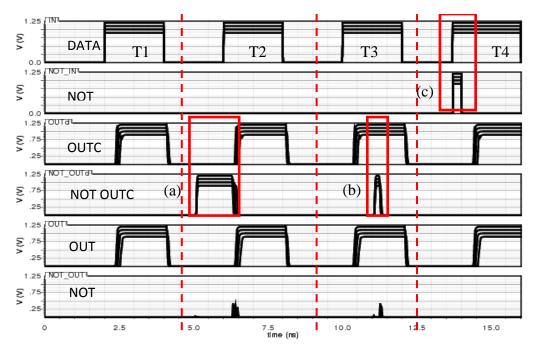

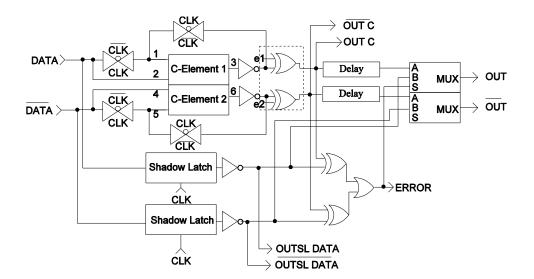

| Figure 7.3: Error injection on EDCD latch                                                                                                  | 189   |

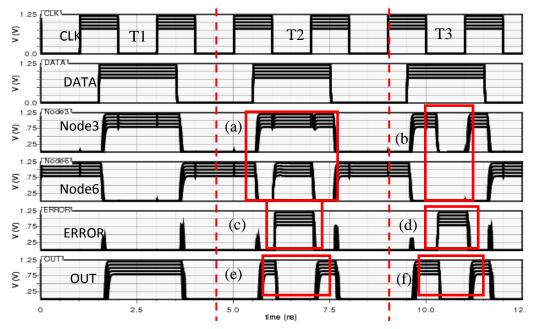

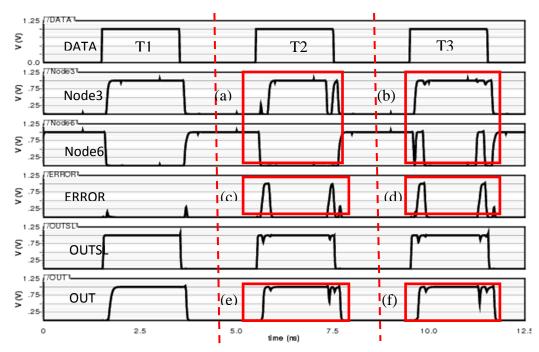

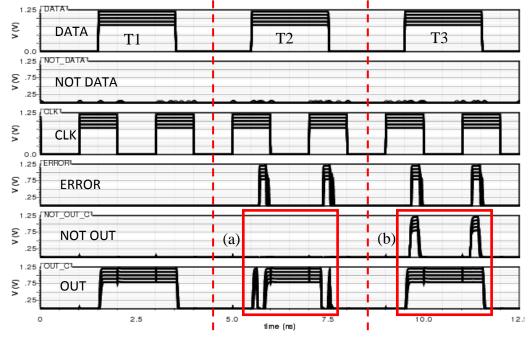

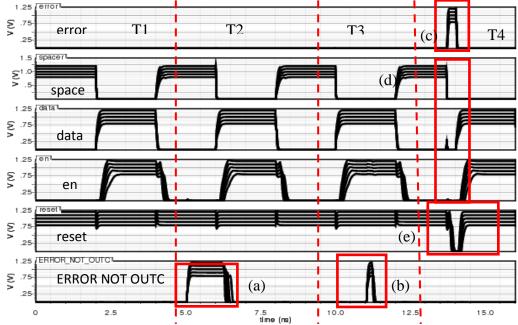

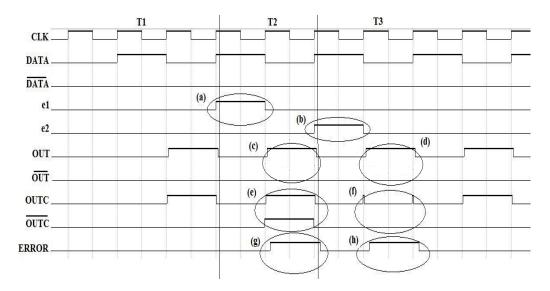

| Figure 7.4: Waveform simulation for fault free condition and error                                                                         |       |

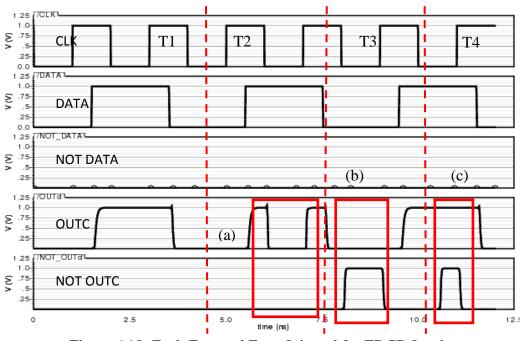

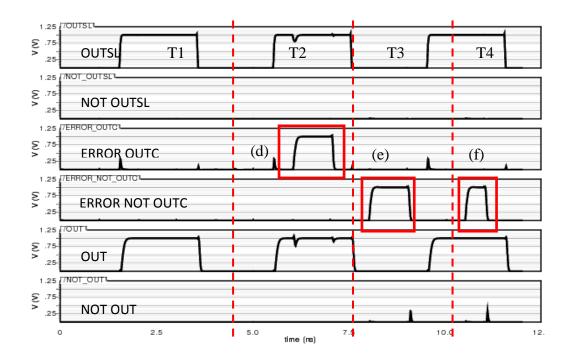

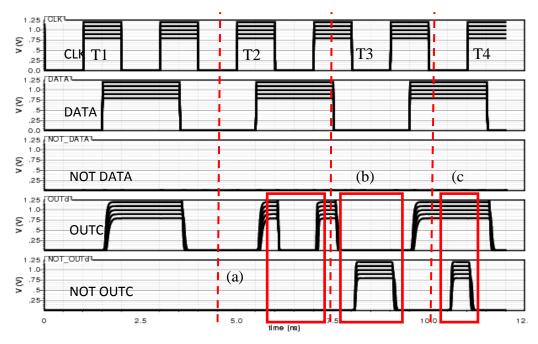

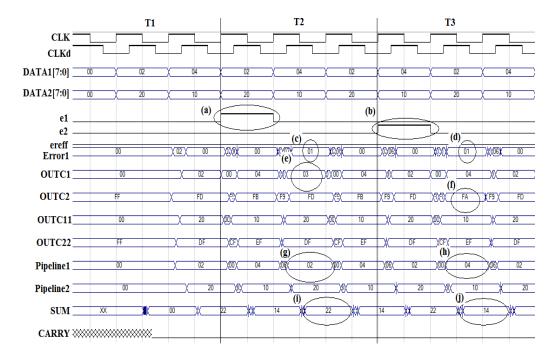

| injection on EDCD latch                                                                                                                    | 189   |

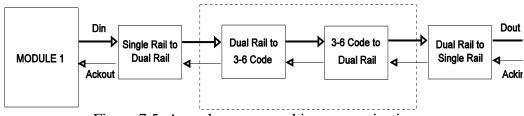

| Figure 7.5: Asynchronous on-chip communication                                                                                             | 190   |

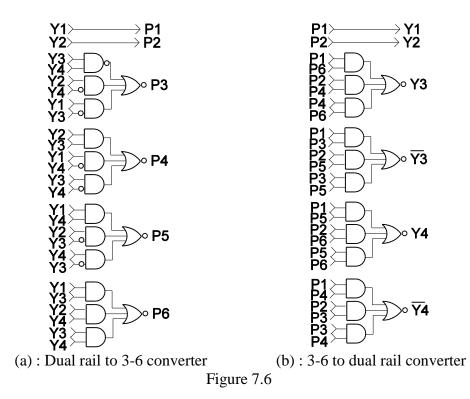

| Figure 7.6: (a) Dual rail to 3-6 converter (b) 3-6 to dual rail                                                                            |       |

| converter                                                                                                                                  | 191   |

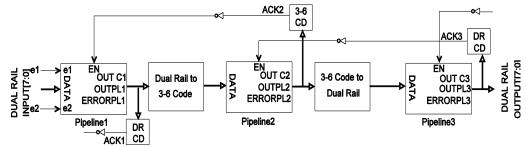

| Figure 7.7: Dual rail to 3-6 and back to dual rail conversion                                                                              | 192   |

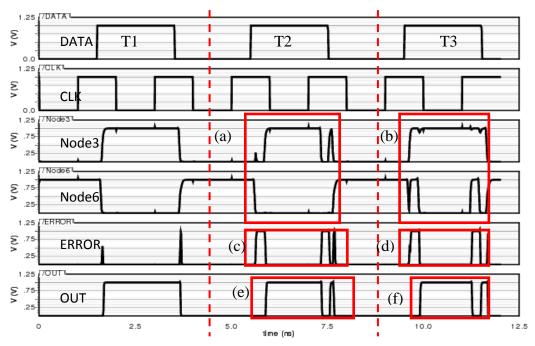

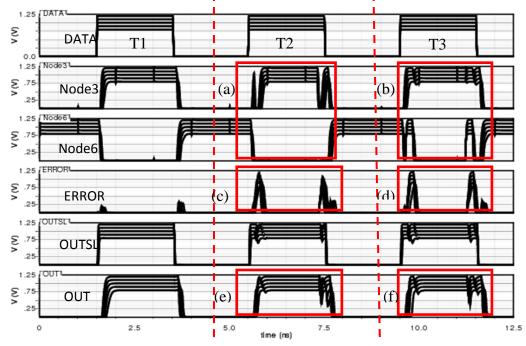

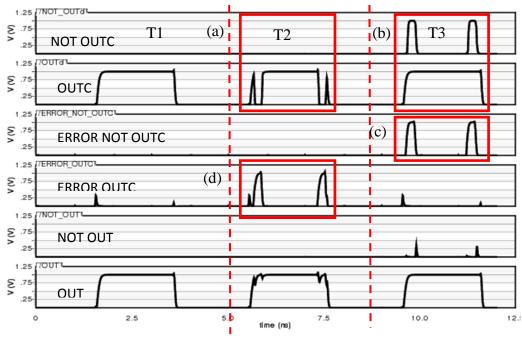

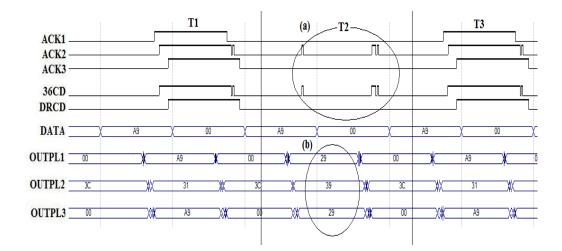

| Figure 7.8: Waveform simulation for fault free condition and error                                                                         |       |

| injection on dual rail latch that does not have error correction                                                                           |       |

| capability                                                                                                                                 | 194   |

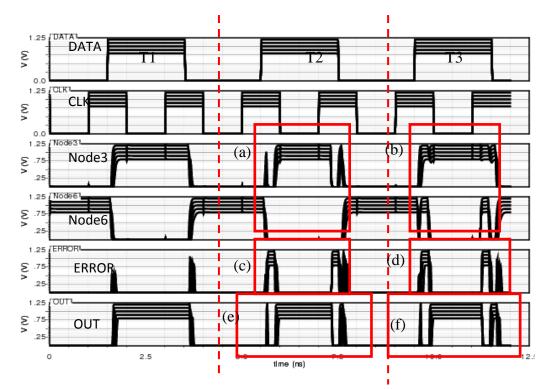

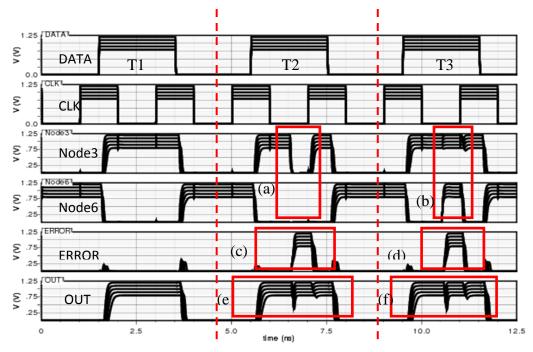

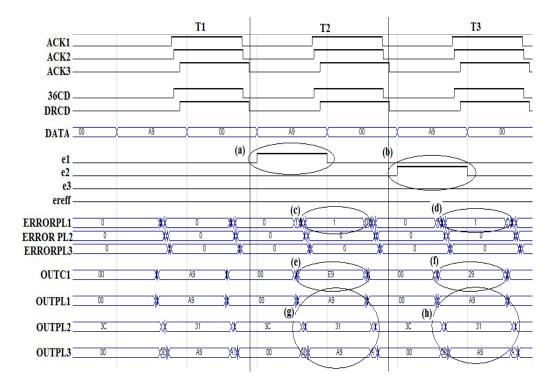

| Figure 7.9: Waveform simulation for fault free condition and error                                                                         |       |

| injection on EDCD latch                                           | 196 |

|-------------------------------------------------------------------|-----|

| Figure B1: Error injection on EDC latch                           | 201 |

| Figure B2: Waveform simulation for fault free condition and error |     |

| injection on EDC Latch                                            | 202 |

| Figure B3: Adder system employing EDC latches                     | 202 |

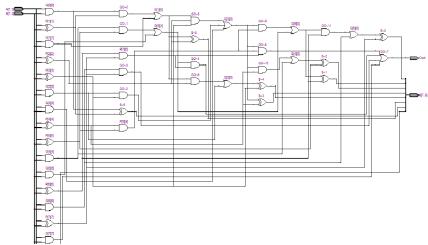

| Figure B4: The gate level view for 8-bit Brent-Kung adder         | 203 |

| Figure B5: Waveform simulation for fault free condition and error |     |

| injection on EDC Latch                                            | 205 |

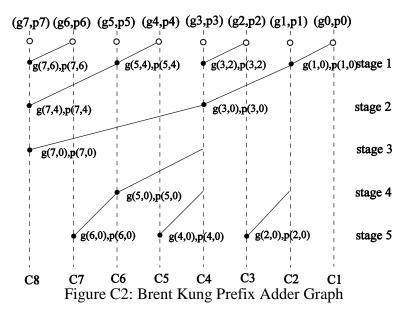

| Figure C1: Block diagram for basic Brent-Kung Adder               | 206 |

| Figure C2: Brent Kung Prefix Adder Graph                          | 206 |

## Abstract

A SEU or soft error is defined as a temporary error on digital electronics due to the effect of radiation. Such an error can cause system failure, e.g. a deadlock in an asynchronous system or production of incorrect outputs due to data corruption.

The first part of this thesis studies the impact of process variation, temperature, voltage and size scaling within the same process on the vulnerability of the nodes of C-element circuits. The objectives are to identify vulnerable to SEU nodes inside a C-element and to find the critical charge needed to flip the output from low to high (0-1) and high to low (1-0) on different implementations of C-elements.

In the second part, a framework to compute the SEU error rates is developed. The error rates of circuits are a trade-off between the size of the transistors and the total area of vulnerability. Comparisons of the vulnerability of different configurations of a C-element are made, and error rates are calculated.

The third part focuses on soft error mitigation for single and dual rail latches. The latches are able to detect and correct errors due to SEU. The functionalities of the solutions have been validated by simulation. A comprehensive analysis of the performance of the latches under variations of the process and temperature are presented.

The fourth part focuses on testing of the new latches. The objective is to design complex systems and incorporate both single rail and dual rail latches in the systems. Errors are injected in the latches and the functionality of the error correcting latches towards the SEU errors are observed at their outputs.

The framework to compute error rates and soft error mitigation developed in this thesis can be used by designers in predicting the occurrence of soft error and mitigating soft error in systems.

# Glossary

| CD                | Completion Detector                                                    |  |  |  |  |

|-------------------|------------------------------------------------------------------------|--|--|--|--|

| DI                | Delay Insensitive                                                      |  |  |  |  |

| DIL C-<br>element | Differential logic and an inverter latch C-element                     |  |  |  |  |

| DRAM              | Dynamic Random Access Memory                                           |  |  |  |  |

| ED                | Error Detection                                                        |  |  |  |  |

| EDC               | Error Detection and Correction                                         |  |  |  |  |

| EDCD              | Error detection and correction for dual rail data                      |  |  |  |  |

| EDCDT             | Error detection and correction with transient correction for dual rail |  |  |  |  |

| EDD               | Error detection for dual rail data                                     |  |  |  |  |

| FPGA              | Field Programmable Gate Array                                          |  |  |  |  |

| FF                | Fast NMOS and PMOS                                                     |  |  |  |  |

| FIT               | Failure-in Time                                                        |  |  |  |  |

| FNSP              | Fast NMOS and slow PMOS                                                |  |  |  |  |

| GALS              | Globally asynchronous locally synchronous                              |  |  |  |  |

| IC                | Integrated Circuit                                                     |  |  |  |  |

| LE                | Logic Element                                                          |  |  |  |  |

| MUX               | Multiplexer                                                            |  |  |  |  |

| QDI               | Quasi Delay Insensitive                                                |  |  |  |  |

| SC C-element      | Single rail with conventional pull-up pull-down C-element              |  |  |  |  |

| SEU               | Single Event Upset                                                     |  |  |  |  |

| SET               | Single Event Transient                                                 |  |  |  |  |

| SI                | Speed Independent                                                      |  |  |  |  |

| SIL C-<br>element | Single rail with feedback C-element                                    |  |  |  |  |

- SNFP Slow NMOS fast PMOS

- SRAM Static Random Access Memory

- SS Slow NMOS and PMOS

- SS C-element Single rail symmetric implementation C-element

- STG State Transition Graph

- TT Typical PMOS and NMOS

## Acknowledgements

I would like to thanks my supervisors Prof Alex Yakovlev and Dr Alex Bystrov for their guidance and supports throughout my studies. It is not possible to complete the project without their support

My wife, Lily Saidon and my two kids, Tisham and Ihsan have given their undivided support and time to me to complete my thesis.

### **Chapter 1. Introduction**

Chapter 1 presents the motivation behind the research, the objectives, a thesis overview, the thesis' contributions and publications.

#### **1.1 Motivation**

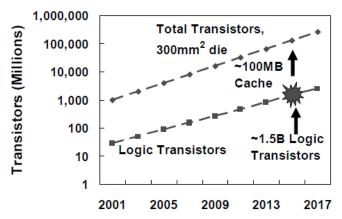

The demand for higher integration density and lower power consumption has lead to the scaling of transistor and voltage supply. Technology continues to improve in modern VLSI design with the number of transistors doubled every 18 months; this observation is known as Moore's law [1]. According to Figure 1 [2], assuming half of the die area of  $300 \text{ } mm^2$  is allocated for logic and the other half for cache memory, the number of transistors in logic and cache memory will reach 1.5 billion and 100 billion respectively by 2015. In 2001, the number of transistors in logic and cache memory were 50 million and 1 billion respectively. As transistors continue to shrink, their number of logic cells per chip. It becomes increasingly important to deal with reliability issues of such complex systems, which is the main focus of this thesis.

Figure 1: The evolution of transistors with respect to year

An important factor affecting reliability of systems is the phenomenon of a single event upset (SEU) in state holder components such as a memory cell, flip-flop or latch. NASA defines SEU as "*Radiation-induced errors in microelectronic circuits caused when charged particles (usually from the radiation belts or from cosmic rays) lose energy by ionizing the medium through which they pass, leaving behind a wake of electron-hole pairs"* [3]. SEU has been identified as a possible cause of data corruption. The term 'soft

error' refers to a temporary error that occurs as a result of particles (alpha particles from packaging or neutrons from the atmosphere) striking the silicon structures and causing the state to change from high to low or from low to high. This electrical effect happens due to the generated electron-hole pairs in the reverse-biased junction of the victim device.

Nowadays, the dimensions of transistors are very small, as the technology nodes of 90nm and below (down to 22nm at the time of completion of this thesis in 2013) became feasible. The drain current and the threshold voltage are reduced with voltage scaling. As a result, radiation induced soft errors in the combinational logic are gaining increasing attention and are expected to become as important as directly induced errors for state elements. The problem of SEU on transistors has been highlighted by the International Technology Roadmap for Semiconductors (ITRS), although the problem was ignored previously until the scaling of transistors had reached deep submicron technology. In a 2011 report, the ITRS listed SEU as one of the factors responsible for the decreased reliability of the device.

The severity of SEU toward high density memory devices can be illustrated on DRAM and SRAM, as they are important elements in an advanced IC. SRAM is less dense compared with DRAM since it is normally built from four or six transistors, whereas DRAM is built from a single transistor and a capacitor.

| Data                                                   | RAM  | RAM       | Avg FIT | #Diff | Range FIT | Average |  |  |

|--------------------------------------------------------|------|-----------|---------|-------|-----------|---------|--|--|

| By                                                     | Size | Type/Test | Rate    | Devs  | Rates     | Up/bit- |  |  |

|                                                        |      |           |         |       |           | hr      |  |  |

| IBM                                                    | 4M   | D/A       | 3500    | 5*    | 53-10300  | 8.9E-13 |  |  |

| IBM                                                    | 1M   | D/A       | 3300    | 2*    | 2500-4100 | 3.3E-12 |  |  |

| IBM                                                    | 1M   | D/F       | 325     | 2*    | 230-420   | 3.1E-13 |  |  |

| Mot                                                    | 256K | S/F       | 500     | 3     | 450-560   | 2E-12   |  |  |

| Mot                                                    | 1M   | S/F       | 2070    | 2     | 1330-2800 | 2.1E-12 |  |  |

| Mot                                                    | 4M   | S/F       | 5750    | 4     | 4500-8900 | 1.5E-12 |  |  |

| Table 1: Ground level soft error rates measured by RAM |      |           |         |       |           |         |  |  |

D-DRAM, S-SRAM, F-Field testing, A-Accelerated testing by using proton beam

From Table 1 [4] it can be observed that DRAM, which is tested using a proton beam, has an average FIT rate of 3300 for 1M and 3500 for 4M. Similarly, the average FIT rate for SRAM which has field testing is 2070 for 1M and 5750 for 4M. It is concluded that high density memories have higher error rates compared with low density memories due to transistor scaling.

Previously, soft errors were a concern for space applications, but now due to the increase in terrestial radiation, soft error affects everyone. The problems caused by single event upset can be illustrated by the examples below in the areas of security and finance: