# DESIGN OF ROBUST ASYNCHRONOUS RECONFIGURABLE CONTROLLERS FOR PARALLEL SYNCHRONIZATION USING EMBEDDED GRAPHS

JAMES SEBASTIAN GUIDO

Doctor of Philosophy(Ph.D.) School of Electrical, Electronic, and Computer Engineering Newcastle University

February 2015

# DECLARATION

I, James Sebastian Guido, confirm that this thesis and the work presented in it are my own achievement.

I have read and understand the penalties associated with plagiarism.

Newcastle, February 2015

James Sebastian Guido

James Sebastian Guido

Dedicated to the memory of my grandfather Joseph Nicholas Guido, who once found himself on a similar path to the one that I now walk. Though you left too early to share your insights with me, thanks for treading the ground first and making the trip feel less lonely.

April 5, 1923 - June 19, 1986

And to his brother, Carmelo Basil Guido, who was also walking the path as well, but had his trip cut short. I didn't know you, but I wish that I had.

May 10, 1915 - December 12, 1944

And to my grandmother Rosalia Anne Guido, who was always ready with words of encouragement and sage advice. You taught me to always look forward and not dwell too closely on the foibles and fallacies of the past, but rather to learn from them and make better decisions in the future. Thanks for being one of the major pillars in my life, and for helping to shape me into the man that I am today.

September 7, 1923 – December 1, 2014

Synchronization is a key System-on-Chip (SoC) design issue in modern technologies. As the number of operating points under consideration increases, specifications which are capable of altering key parameters such as the time available for synchronization and Mean Time Between Failures (MTBF) in response to input from the user/system become desirable. This thesis explores how a combination of parallelism and scheduling, referred to as wagging, can be utilized to construct schedulers for synchronizer designs which are capable of pooling the gain-bandwidth products of their composite devices, in order to satisfy this requirement.

In this work, we explore the ways in which the areas of graph theory and reconfigurable hardware design can be applied to generate both combinational and sequential scheduler designs, which satisfy the behavior requirement above. Further to this point, this work illustrates that such a scheduler is primarily comprised of an interrupt subsystem, and a reconfigurable token ring. This thesis explores how both of these components can be controlled in absence of a clock signal, as well as the design challenges inherent to each part.

The final noteworthy issue in this study is with regard to the flow control of data in a parallel synchronizer that incorporates a First-In First-Out (FIFO) buffer to decouple the reading and writing operations from each other. Such a structure incurs penalties if the data rates on both sides are not well matched. This work presents a method by which combinations of serial and parallel reading operations are used to minimize this mismatch.

#### **PUBLICATIONS**

Some ideas and figures have appeared previously in the following publications:

Guido, James Sebastian, and Alexandre Yakovlev. "Reconfigurable controllers for synchronization via wagging." In Proceedings of the 21st edition of the great lakes symposium on Great lakes symposium on VLSI, pp. 175-180. ACM, 2011.

Guido, James Sebastian, and Alexandre Yakovlev. "Design of Self-Timed Reconfigurable Controllers for Parallel Synchronization via Wagging." In IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 23(2):292-305, Feb. 2015 doi: 10.1109/TVLSI.2014.2306176

In my experience, finding design simplicity which copes with the demands of underlying complexity tends to yield the best rewards. I can also say that the quest for simplicity, is also usually anything but simple.

#### ACKNOWLEDGMENTS

It's been a lot of fun working at Newcastle University over the past few years. As my time here draws to a close, my thoughts turn to all of the people that have helped me over the years. First and foremost is my supervisor Alex Yakovlev, who helped me navigate from being a fresh out of college Masters student into a decent researcher. Ghaith Tarawneh assited me in developing a script which formed the front-end of my SPECTRE logical analysis experiments, and was generally beyond helpful during the course of my studies. Andrey Mokhov also deserves mention for his useful discussions which led to one optimization later in this thesis. Robin Emery also deserves mention, for reminding me to always try and see the big picture with regards to my work by asking me the all-important question "So what?"

On the more personal side of things, I'd like to thank my mother, Michaelanne, my father, James, my sister, Rochelle, and my niece and nephews, Magnus, Argyle, and Iona for being steadfast in their support. I'd also like to thank my good friend John Parry, for always being there to lend a sympathetic ear when times got rough or when things didn't quite go my way. More to that, I'd also like to thank his brother Richard, Anthony Pearson, and Thomas James for several years' worth of wonderful memories.

I could go on and on, but I'll always be the first to admit that I'm here because I had the encouragement and support of others. Thanks for making these some of the best years of my life.

# CONTENTS

| I              | PHD | THESI   | (S                                                           | 1  |

|----------------|-----|---------|--------------------------------------------------------------|----|

| 1 INTRODUCTION |     |         | CTION                                                        | 3  |

|                | 1.1 | Motiv   | ration                                                       | 3  |

|                | 1.2 |         | ibutions                                                     | 6  |

|                |     | 1.2.1   | Algorithms for Load Balancing in Token Rings via Distributed |    |

|                |     |         | Embedded Graphs                                              | 6  |

|                |     | 1.2.2   | Manipulation of Parallelism in a Self-Timed Reconfigurable   |    |

|                |     |         | Control Device via One-Hot Coding                            | 6  |

|                |     | 1.2.3   | Tolerance of Hard Faults in a Self-Timed Reconfigurable Con- |    |

|                |     |         | trol Device via Bypass Paths                                 | 7  |

|                |     | 1.2.4   | Flow Control in a FIFO Synchronizer based on Wagging         | 7  |

|                | 1.3 | Orgar   | nization of Thesis                                           | 7  |

| 2              | BAC | KGROU   | JND LITERATURE & MODELS                                      | 9  |

|                | 2.1 | Introd  | luction(Asynchronous Circuits)                               | 9  |

|                |     | 2.1.1   | Properties of Asynchronous Circuits                          | 9  |

|                |     | 2.1.2   | Asynchronous Control Circuits                                | 11 |

|                |     | 2.1.3   | Asynchronous Circuit Primitives                              | 12 |

|                | 2.2 | Petri I | Nets                                                         | 15 |

|                |     | 2.2.1   | Pre-sets and Post-sets                                       | 16 |

|                |     | 2.2.2   | Enabling and Firing                                          | 16 |

|                |     | 2.2.3   | Reachability                                                 | 17 |

|                |     | 2.2.4   | Other Petri Net Properties                                   | 17 |

|                | 2.3 | Signal  | l Transition Graphs                                          | 18 |

|                |     | 2.3.1   | Relation to Petri Nets                                       | 18 |

|                |     | 2.3.2   | State Graphs and Reachability Graphs                         | 19 |

|                |     | 2.3.3   | Complete State Coding                                        | 20 |

|                |     | 2.3.4   | Relative Timing in Signal Transition Graphs                  | 21 |

|                | 2.4 | Metas   | stability                                                    | 21 |

|                | 2.5 | Embe    | dded Cycle Graphs                                            | 24 |

|                |     | 2.5.1   | Basic Graph Definitions                                      | 24 |

|                |     | 2.5.2   | Applications of an Embedded Cycle Graph                      | 25 |

| 3              | OVE | RVIEW   | OF WAGGING SYNCHRONIZATION                                   | 27 |

|                | 3.1 | Introd  | luction(Synchronization Methods)                             | 27 |

|                |     | 3.1.1   | Synchronization Overview                                     | 27 |

|                |     | 3.1.2   | Cascaded Flip-Flop Synchronization                           | 28 |

|                |     | 3.1.3   | Mean-Time Between Failures in a Cascaded Flip-Flop Syn-      |    |

|                |     |         | chronizer                                                    | 29 |

|                |     | 3.1.4   | FIFO Synchronization                                         | 31 |

|                | 3.2 | Wagg    | ing Synchronization                                          | 33 |

|                |     | 3.2.1   | Two-way Wagging Buffer                                       | 35 |

|                |     | 3.2.2   | Wagging Synchronizer Concept                                 | 35 |

|   |            | 3.2.3          | Effect of Wagging on the Failure Rate of Cascaded Flip-Flop | - (      |

|---|------------|----------------|-------------------------------------------------------------|----------|

|   |            |                | Synchronizers                                               | 36       |

|   |            | 3.2.4          | Impact of Incorporating Reconfigurable Hardware Capabil-    | 0        |

|   |            |                | ity into a Wagging Synchronizer Design                      | 38       |

|   |            | 3.2.5          | Overheads of Incorporating Reconfigurable Hardware Capa-    |          |

|   |            |                | bility into a Wagging Synchronizer Design                   | 40       |

|   |            | 3.2.6          | Basic Operation of the Reconfigurable Control Device        | 41       |

|   | 3.3        | Topolo         | ogy of a Reconfigurable Token Ring                          | 43       |

|   |            | 3.3.1          | Cyclic Behavior of Token Rings                              | 43       |

|   |            | 3.3.2          | Sub-Optimal Distribution Algorithm Specification            | 46       |

|   |            | 3.3.3          | Optimal Distribution Algorithm Specification                | 48       |

|   | 3.4        | Token          | Ring Designs                                                | 51       |

|   |            | 3.4.1          | Ring Oscillators                                            | 52       |

|   |            | 3.4.2          | Fast David Cells                                            | 52       |

|   |            | 3.4.3          | Muller Pipeline                                             | 55       |

|   |            | 3.4.4          | Performance Comparison                                      | 56       |

|   |            | 3.4.5          | Distributed Token Ring Implementation                       | 57       |

| 4 | PAR        | ALLEL          | ISM IN A RECONFIGURABLE CONTROLLER FOR WAGGING              |          |

|   | SYN        | CHRON          | NIZATION                                                    | 63       |

|   | 4.1        | Introd         | uction (Arbitration & Reconfiguration)                      | 63       |

|   | 4.2        | Relate         | d Work (Overview of Arbitration)                            | 63       |

|   |            | 4.2.1          | The Mutual Exclusion Element (MUTEX)                        | 64       |

|   |            | 4.2.2          | Token Ring Arbiters                                         | 64       |

|   |            | 4.2.3          | Arbitration via Pausible Clocks                             | 65       |

|   |            | 4.2.4          | Relation to a Reconfigurable Control Device for a Wagging   |          |

|   |            |                | Synchronizer                                                | 66       |

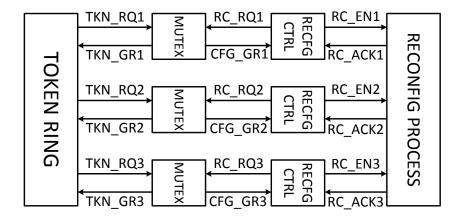

|   | 4.3        | Recon          | figuration Protocol                                         | 66       |

|   |            | 4.3.1          | Mathematical Foundations (Assumptions)                      | 69       |

|   | 4.4        | UCON           | If Threading                                                | 70       |

|   |            | 4.4.1          | Enforcing Firing Order in Cyclic Independent Loops          | 70       |

|   |            | 4.4.2          | Control of End Behavior in Cyclic Independent Loops         | 71       |

|   | 4.5        |                | Controller Design                                           | 71       |

|   | , ,        | 4.5.1          | Circuit Synthesis                                           | ,<br>72  |

|   |            | 4.5.2          | Performance Comparison                                      | 75       |

|   | 4.6        |                | it Data Merging in Reconfigurable Controller                | 77       |

|   |            |                | Circuit Synthesis & Results Analysis                        | 77       |

| 5 | ROB        |                | SS IN A RECONFIGURABLE CONTROLLER FOR WAGGING               | //       |

| J |            |                | SIZATION                                                    | 79       |

|   | 5.1        |                | uction (Principle of Exclusion)                             | 79<br>79 |

|   | 5.2        |                | Model Definitions                                           |          |

|   | 5.2        | 5.2.1          | Fault types                                                 | 79       |

|   | <b>-</b> 2 | _              | d Work (Johnson Counter)                                    | 79<br>80 |

|   | 5·3        |                | al Ring Networks (Algorithm Reinterpretation)               | 81       |

|   | 5.4        |                | Chordal Bypass Path Algorithm                               |          |

|   |            | 5.4.1          | ••                                                          | 82       |

|   |            | 5.4.2<br>LICON | Results Analysis                                            | 83       |

|   | 5.5        | UCUN           | ¶ Thread Forwarding                                         | 84       |

|    |      | 5.5.1  | Theoretical Overview (Why Forward?)                       | 85  |

|----|------|--------|-----------------------------------------------------------|-----|

|    |      | 5.5.2  | Applications to Robust Controller Design                  | 86  |

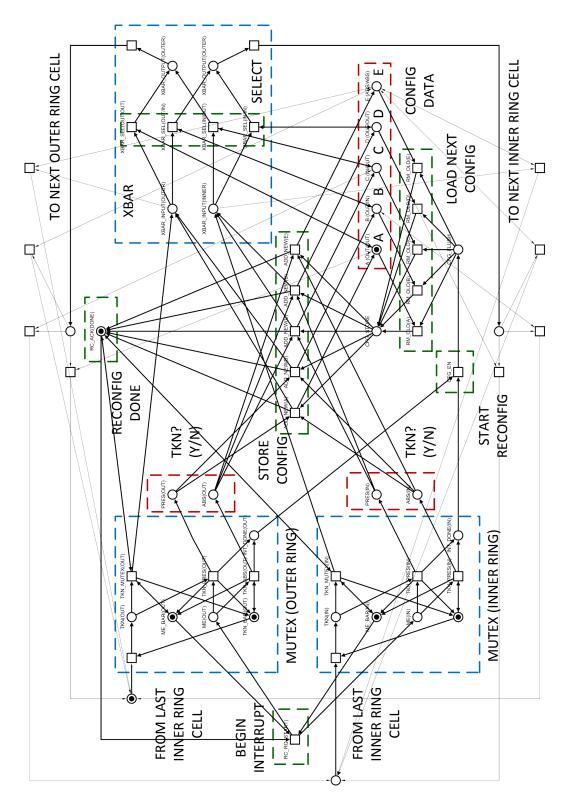

|    | 5.6  | Advar  | nced Controller Design (Hierarchy & Crossbar Plug-in)     | 86  |

|    |      | 5.6.1  | Theoretical Overview (System Hierarchy)                   | 86  |

|    |      | 5.6.2  | Derivation of the Petri Net (PN) Model                    | 88  |

|    |      | 5.6.3  | PN Model & Simulation                                     | 90  |

|    | 5.7  | Valida | ting Configurations via a Nearest Neighbor Checking Algo- |     |

|    |      | rithm  |                                                           | 92  |

|    |      | 5.7.1  | Validation Algorithm                                      | 92  |

| 6  | FLO  | w con  | TROL IN WAGGING SYNCHRONIZERS INCORPORATING FIFO          |     |

|    | BUF  | FERS   |                                                           | 95  |

|    | 6.1  | Introd | uction (Flow Control in FIFO Synchronizers)               | 95  |

|    | 6.2  | Relate | d Work (STARI)                                            | 95  |

|    |      | 6.2.1  | Applications to Wagging Synchronization                   | 96  |

|    | 6.3  | FIFO 7 | Testing Methodology                                       | 98  |

|    |      | 6.3.1  | Top-level Design Considerations                           | 98  |

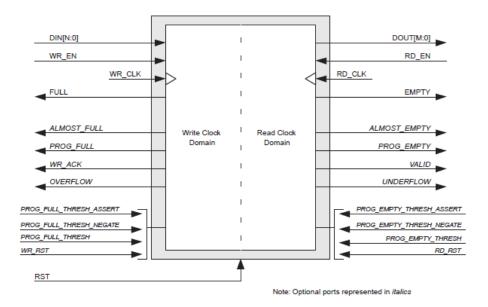

|    |      | 6.3.2  | FIFO I/O Considerations                                   | 100 |

|    | 6.4  | VHDI   | 1                                                         | 101 |

|    |      | 6.4.1  | O                                                         | 101 |

|    |      | 6.4.2  |                                                           | 101 |

|    |      | 6.4.3  | 0 00 0                                                    | 102 |

|    | 6.5  | VHDI   | Simulations                                               | 104 |

| 7  | CON  | ICLUSI | ONS                                                       | 109 |

|    | 7.1  | Main   | Contributions                                             | 109 |

|    | 7.2  | Future | e Work                                                    | 110 |

| II | API  | PENDIX |                                                           | 111 |

| Α  | APP  | ENDIX  |                                                           | 113 |

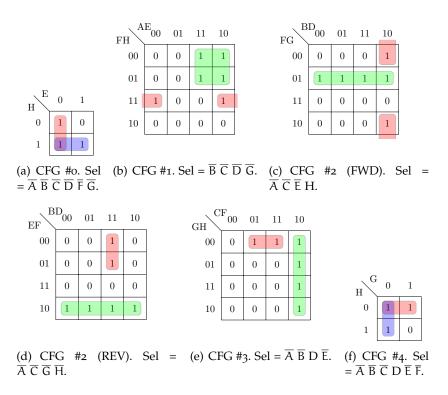

|    | A.1  |        | UX Boolean Logic Minimization                             |     |

|    | A.2  | CADE   | ENCE PWL Waveform Generation Example                      | 114 |

| ві | BLIO | GRAPH  | ·Y                                                        | 117 |

# LIST OF FIGURES

| Eiguno 1 1  | Cascadad Tura Flon Symphyonizar                                      |            |

|-------------|----------------------------------------------------------------------|------------|

| Figure 1.1  | Cascaded Two-Flop Synchronizer                                       | 4          |

| Figure 1.2  | Parallel Two-Flop Synchronizer                                       | 5          |

| Figure 2.1  | Behavioral representation of a D flip-flop                           | 13         |

| Figure 2.2  | Behavioral representation of a Muller C-Element (MCE)                | 13         |

| Figure 2.3  | Annotated Muller C-Element schematic with signal transi-             |            |

| P:          | tions representing 1 operating cycle                                 | 14         |

| Figure 2.4  | Annotated David Cell schematic with signal transitions rep-          |            |

| т.          | resenting 1 operating cycle                                          | 14         |

| Figure 2.5  | Petri Net Symbols                                                    | 15         |

| Figure 2.6  | Petri Net of a 3-cell token ring                                     | 16         |

| Figure 2.7  | Reachability Graph of a 3-cell token ring                            | 17         |

| Figure 2.8  | Annotated Signal Transition Graph (STG) of a 3-cell token ring       | 19         |

| Figure 2.9  | Annotated STG of a 3-cell token ring (CSC Conflict Resolved)         | 20         |

| Figure 2.10 | Abstract view of a butterfly curve. From [44]                        | 22         |

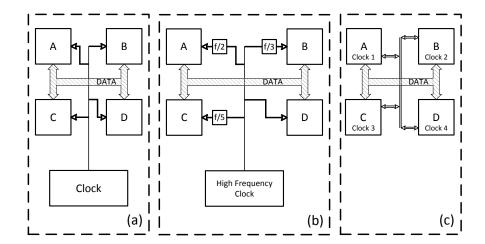

| Figure 3.1  | Overview of clocking methods: (a) Synchronous, (b) Ratio-            |            |

|             | nally related clocks, (c) Multiple clocks                            | 28         |

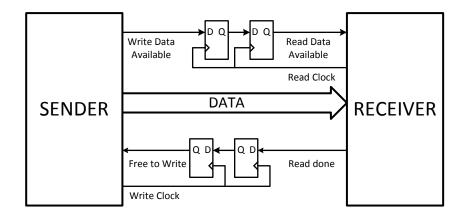

| Figure 3.2  | Synchronizing interface. From [44]                                   | 29         |

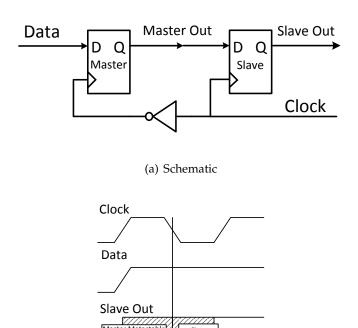

| Figure 3.3  | Cascaded flip-flop synchronizer                                      | 30         |

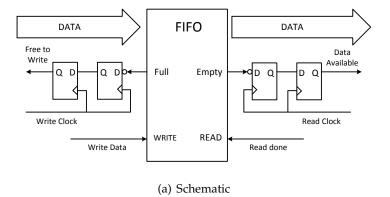

| Figure 3.4  | FIFO synchronizer. From [44]                                         | 32         |

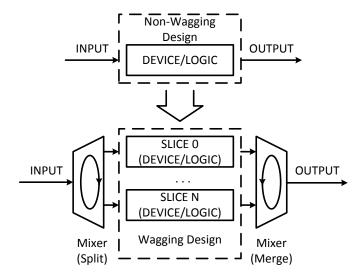

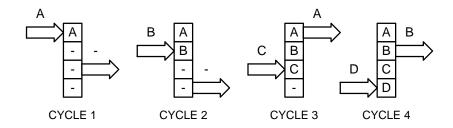

| Figure 3.5  | Conceptual diagram illustrating the wagging principle                | 33         |

| Figure 3.6  | Annotated diagram of a two-way wagging buffer                        | 34         |

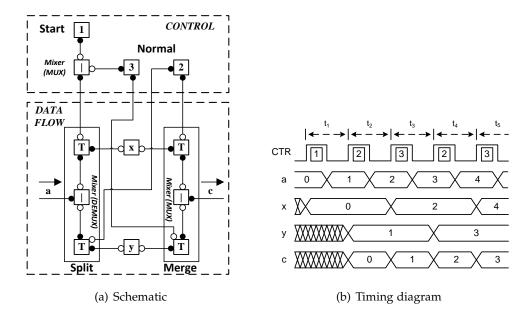

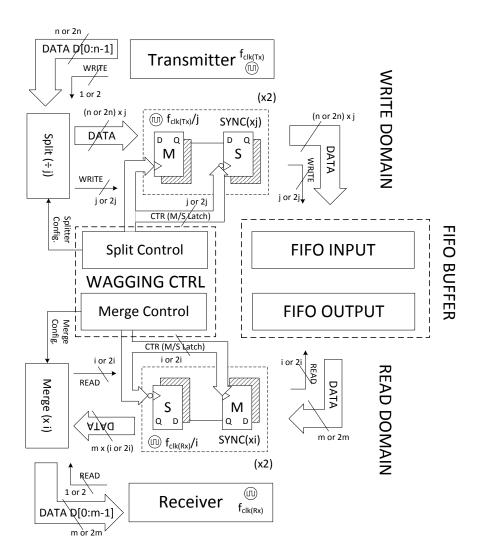

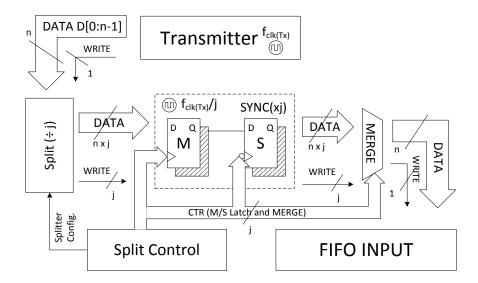

| Figure 3.7  | Block diagram of an N-wagging synchronizer                           | 37         |

| Figure 3.8  | Data flow from the transmitter end of a wagging synchro-             |            |

|             | nizer to the input of the FIFO in Fig. 3.7 with $j = 3$ and a        |            |

|             | 50% duty cycle                                                       | 38         |

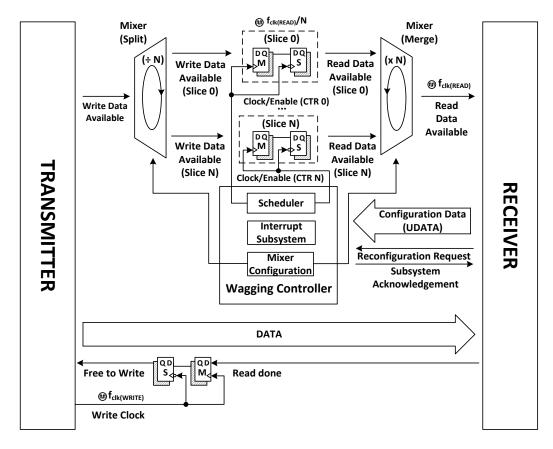

| Figure 3.9  | Block diagram of a reconfigurable controller suitable for a          |            |

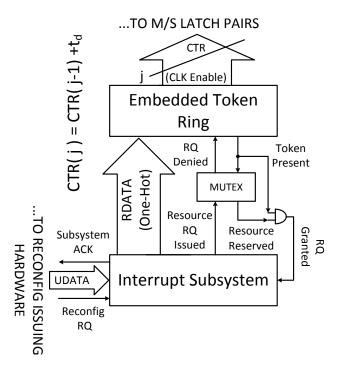

|             | wagging synchronizer                                                 | 42         |

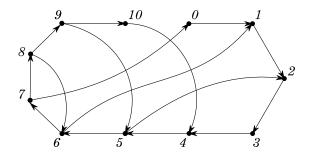

| Figure 3.10 | Cycle graphs of a token ring                                         | 44         |

| Figure 3.11 | Results of the sub-optimal distribution algorithm                    | 48         |

| Figure 3.12 | Optimized distributed feedback algorithm overview                    | 51         |

| Figure 3.13 | Ring oscillator with $n_{qate} = 5$ , and an active-low reset signal | 52         |

| Figure 3.14 | Annotated fast David Cell schematic with signal transitions          |            |

|             | representing 1 operating cycle                                       | 53         |

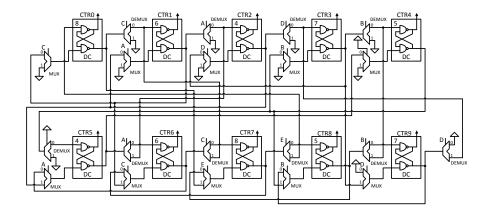

| Figure 3.15 | Four-way sequential token ring based on fast David Cells (DCs)       | 54         |

| Figure 3.16 | 4-way sequential token ring based on MCEs                            | 55         |

| Figure 3.17 | 8-way reconfigurable token ring implementation based on              |            |

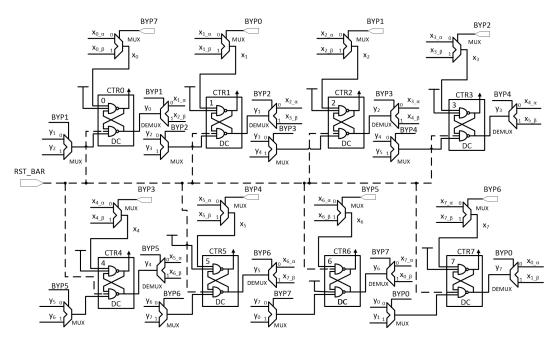

| 0 3 7       | sequential logic (5 possible configurations)                         | 58         |

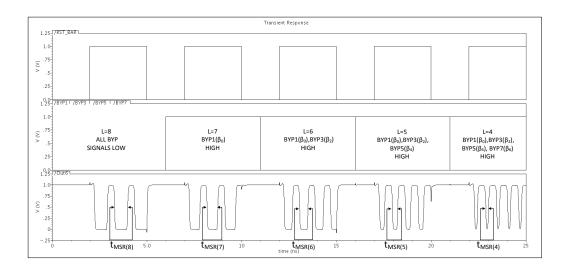

| Figure 3.18 | Transient response of the self-timed reconfigurable token            | <i>J</i> - |

| <i>G S</i>  | ring control circuit based on DCs illustrating the effect of         |            |

|             | increased parallelism on the time available for synchroniza-         |            |

|             | tion (path: CTR4)                                                    | 58         |

|             | uon (paul. CTN4)                                                     | 50         |

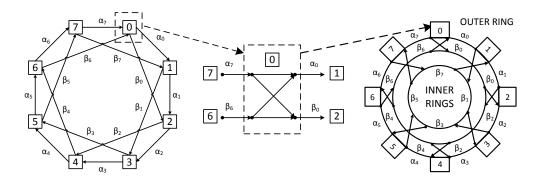

| Figure 3.19 | Distributed graph which models the behavior of the 8-way         |    |

|-------------|------------------------------------------------------------------|----|

|             | reconfigurable token ring circuit                                | 59 |

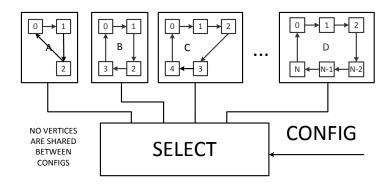

| Figure 3.20 | Basic reconfigurable control circuit based on hardware repli-    |    |

|             | cation and select signals                                        | 59 |

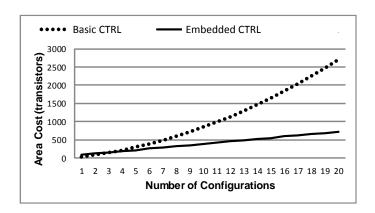

| Figure 3.21 | Area comparison of a self-timed reconfigurable token ring        |    |

|             | control circuit based on fast DCs. $(cycle_{(min)}(even) = 4)$ . | 60 |

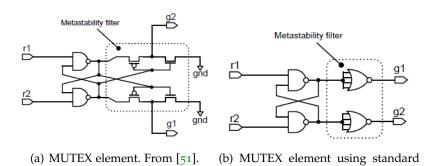

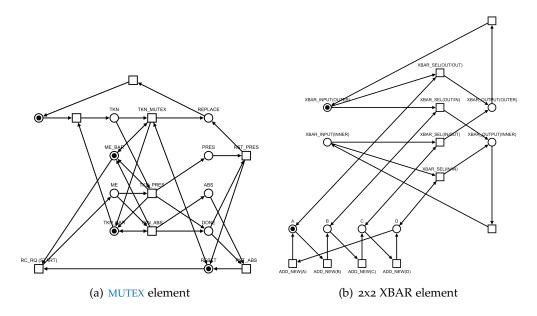

| Figure 4.1  | The mutual exclusion element                                     | 64 |

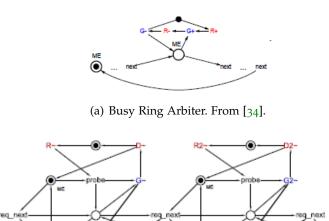

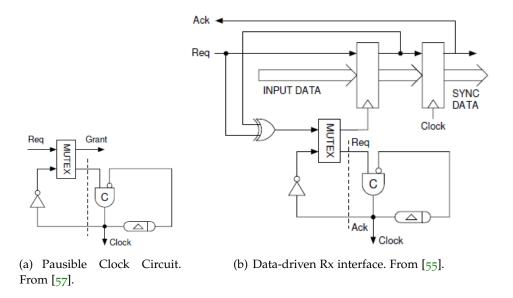

| Figure 4.2  | STGs of token ring arbiters                                      | 65 |

| Figure 4.3  | Pausible clock arbiter overview                                  | 66 |

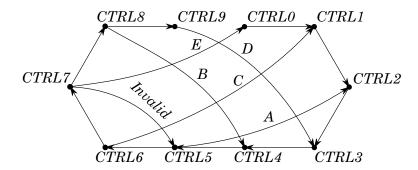

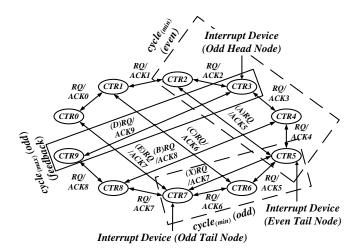

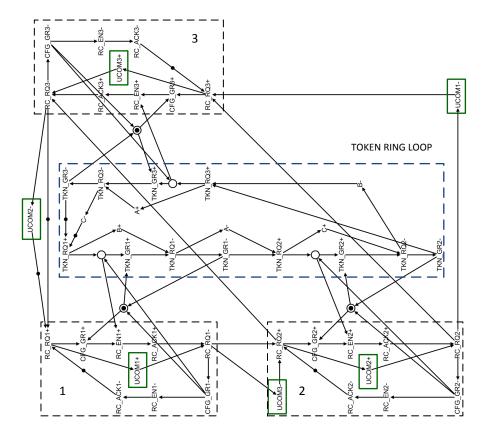

| Figure 4.4  | Behavior graph of an 8-way reconfigurable controller with        |    |

|             | several cycles                                                   | 67 |

| Figure 4.5  | Interrupt block diagram                                          | 67 |

| Figure 4.6  | Signal transition graph (FWD PATH)                               | 68 |

| Figure 4.7  | Signal transition graph (REV PATH)                               | 71 |

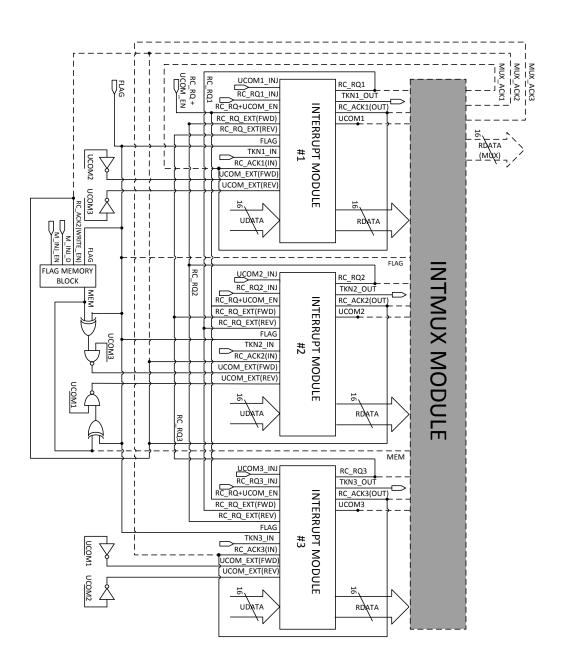

| Figure 4.8  | Top view of three 16-bit interrupt modules tied together via     |    |

|             | Unidirectional Communication (UCOM) threads. Solid lines         |    |

|             | represent the connectivity of the signal lines present in this   |    |

|             | section. Grayed out portions and dotted lines represent the      |    |

|             | connections and blocks which will be discussed in Section 4.6.   | 73 |

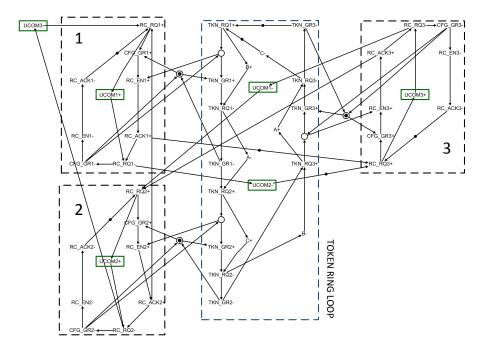

| Figure 4.9  | Internal view of an individual 16-bit interrupt module (i.e.     |    |

|             | module #1 in the example)                                        | 74 |

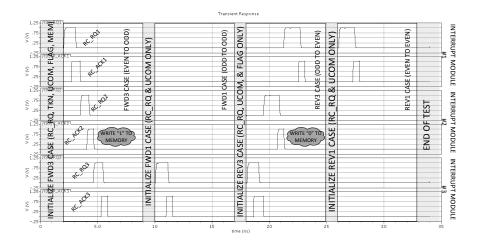

| Figure 4.10 | Transient response of the control signals for the subsystem      |    |

|             | of three interrupt devices, which demonstrates the firing be-    |    |

|             | havior of the design. Reconfiguration data, UCOM, FLAG,          |    |

|             | and MEM signals have been omitted                                | 75 |

| Figure 4.11 | INTMUX boolean logic minimization                                | 78 |

| Figure 5.1  | Eight-way ring network based on chordal bypass paths             | 81 |

| Figure 5.2  | Chordal Bypass Path Algorithm Overview                           | 82 |

| Figure 5.3  | Schematic of the self-timed reconfigurable token ring con-       |    |

|             | trol circuit based on DCs illustrating the effect of exclu-      |    |

|             | sion on the time available for synchronization in the system     |    |

|             | (path: CTR6)                                                     | 84 |

| Figure 5.4  | Transient response of the self-timed reconfigurable token        |    |

|             | ring control circuit based on DCs illustrating the effect of     |    |

|             | exclusion on the time available for synchronization in the       |    |

|             | system (path: CTR6)                                              | 85 |

| Figure 5.5  | Conceptual overview of the token ring based on chordal           |    |

|             | graphs                                                           | 87 |

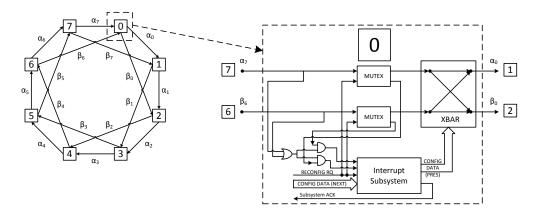

| Figure 5.6  | Overview of the reconfigurable interrupt an XBAR select at       |    |

|             | vertex o                                                         | 87 |

| Figure 5.7  | PN of building blocks for the reconfigurable control device      | 88 |

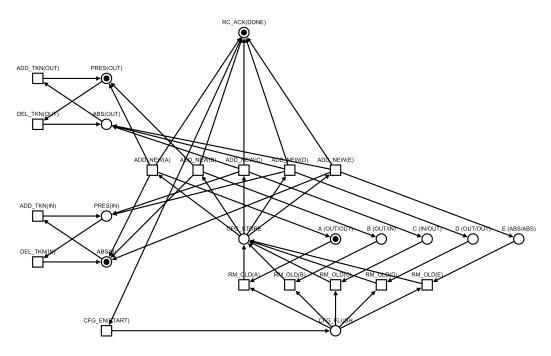

| Figure 5.8  | PN of the interrupt subsystem                                    | 90 |

| Figure 5.9  | PN representation of chordal reconfiguration protocol            | 91 |

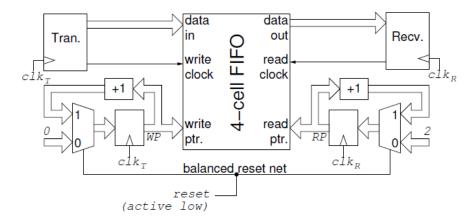

| Figure 6.1  | Four-cell STARI interface schematic. From [12]                   | 96 |

| Figure 6.2  | Data flow of a four-cell STARI interface, assuming that the      |    |

| -           | transmitter and receiver clocks are in phase. From [12]          | 96 |

| Figure 6.3  | Top view of a FIFO synchronizer incorporating wagging at                                              |     |  |  |  |

|-------------|-------------------------------------------------------------------------------------------------------|-----|--|--|--|

| _           | the transmitter and receiver                                                                          | 97  |  |  |  |

| Figure 6.4  | FIFO standard cell. From [82]                                                                         | 99  |  |  |  |

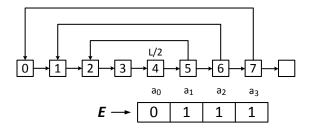

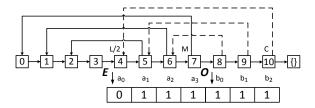

| Figure 6.5  | Serialized input from the transmitter to the input of the FIFO buffer                                 | 100 |  |  |  |

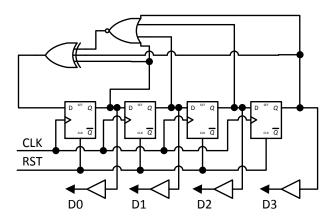

| Figure 6.6  | Four-bit Pseudorandom Binary Sequence (PRBS) generator.                                               |     |  |  |  |

| O           | Four-bit signature analyzer                                                                           |     |  |  |  |

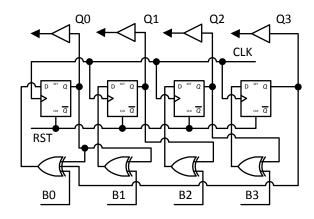

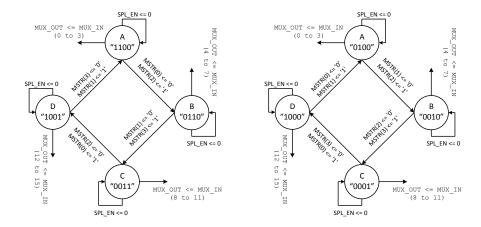

| Figure 6.7  | •                                                                                                     | 103 |  |  |  |

| Figure 6.8  | State machine for four-bit wagging control device                                                     |     |  |  |  |

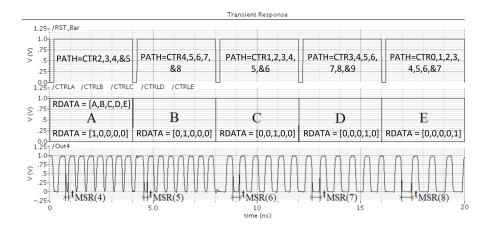

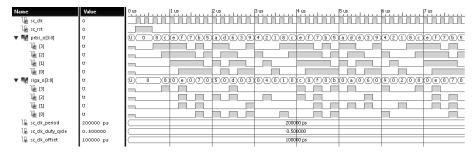

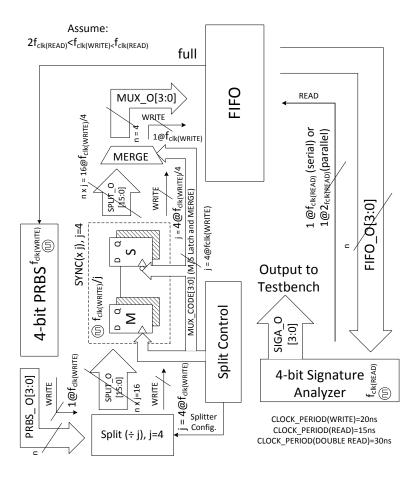

| Figure 6.9  | VHDL Experimental Setup                                                                               | 105 |  |  |  |

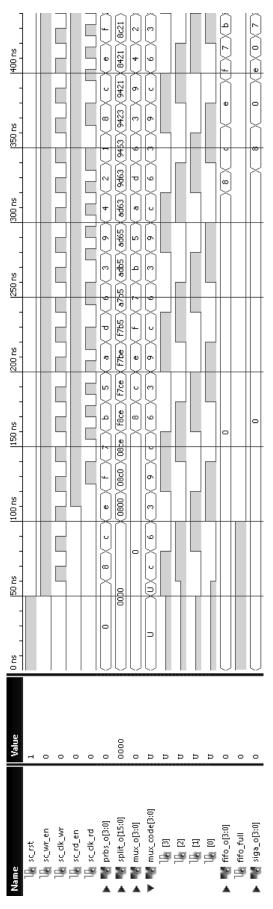

| Figure 6.10 | Transient response of the flow control in the complete self                                           |     |  |  |  |

|             | checking circuit                                                                                      | 106 |  |  |  |

| LIST OF TA  | ABLES                                                                                                 |     |  |  |  |

| Table 3.1   | MTBF of a Cascaded Two-Flop Synchronizer. From [2]                                                    | 29  |  |  |  |

| Table 3.2   | MTBF of a Fixed 3-Way Wagging Synchronizer. From [2]                                                  | 39  |  |  |  |

| Table 3.3   | Differences in the Cycle Lists of a Multi-cycle Token Ring                                            |     |  |  |  |

|             | with Distributed Edges vs. an Undistributed Ring (Maxi-                                               |     |  |  |  |

|             | mum Cycle Length = 8 Vertices)                                                                        | 45  |  |  |  |

| Table 3.4   | Differences in the Cycle Lists of Two Different Multi-cycle                                           | 13  |  |  |  |

| <i>3</i> I  | Token Rings Implementations with Distributed Edges (Max-                                              |     |  |  |  |

|             | imum Cycle Length = 8 Vertices)                                                                       | 50  |  |  |  |

| Table 3.5   | Average Power Consumption per Cell across Process Cor-                                                |     |  |  |  |

| 3 3         | ners at $V_{DD}$ = 1.0 V and $t_{cycle}$ = 1 ns (TN/TP)                                               | 57  |  |  |  |

| Table 3.6   | Average Time Available for Synchronization across Process                                             | 31  |  |  |  |

| J. c        | Corners at $t_{cycle} = 1$ ns $(TN/TP)$                                                               | 57  |  |  |  |

| Table 4.1   | Duration of the Active Region of the Interrupt Subsystem                                              | 37  |  |  |  |

| 14016 4.1   | for Different Configurable Modes at a TN-TP Corner with                                               |     |  |  |  |

|             | $V_{\rm DD}$ = 1.0 V                                                                                  | 75  |  |  |  |

| Table 4.2   | Average Power Consumption of the Active Region of the                                                 | 75  |  |  |  |

| 14010 4.2   | Interrupt Subsystem for Different Configurable Modes at a                                             |     |  |  |  |

|             | TN-TP Corner with $V_{DD} = 1.0 \text{ V} \dots \dots \dots \dots$                                    | 76  |  |  |  |

| Table = 1   | Variations in the Time Available for Synchronization in the                                           | 70  |  |  |  |

| Table 5.1   | Reconfigurable Token Ring Control across 3 Major Process                                              |     |  |  |  |

|             | Corners @ $V_{DD} = 1.0 \text{ V}$ and at a Temp = 27 °C                                              | Q 4 |  |  |  |

| Table = a   | <del>-</del>                                                                                          | 84  |  |  |  |

| Table 5.2   | Variations in the Time Available for Synchronization in the                                           |     |  |  |  |

|             | Reconfigurable Token Ring Control across Temperature Re-                                              | 0-  |  |  |  |

| Talala e -  | gions $@V_{DD} = 1.0 \text{ V}$ and a TN/TP Transistor Process $V_{DAB} = 1.0 \text{ Calcat Giarals}$ | 85  |  |  |  |

| Table 5.3   | XBAR Select Signals                                                                                   | 92  |  |  |  |

| Table 5.4   | Nearest Neighbor Checking Algorithm                                                                   | 93  |  |  |  |

| Table 6.1   | Read Sequence Generated by Equation 6.1 per Cycle, where                                              |     |  |  |  |

|             | i < j < 2i                                                                                            | 104 |  |  |  |

| Table 6.: | Effect of the Connectivity of the Serializing Multiplexer (MUX) on the Time Available for Synchronization in the Device 107 |  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------|--|

| LIST (    | OF ALGORITHMS                                                                                                               |  |

| Figure 1  | (Part 1)                                                                                                                    |  |

| LISTII    | NGS                                                                                                                         |  |

| Listing : | •                                                                                                                           |  |

| ACRO      | NYMS                                                                                                                        |  |

| CSC       | Complete State Code                                                                                                         |  |

| DC        | David Cell                                                                                                                  |  |

| DEMUX     | Demultiplexer                                                                                                               |  |

| FIFO      | First-In First-Out                                                                                                          |  |

| FPGA      | Field Programmable Gate Array                                                                                               |  |

| GALS      | Globally Asynchronous Locally Synchronous                                                                                   |  |

| LUT       | Look-Up Table                                                                                                               |  |

| MCE       | Muller C-Element                                                                                                            |  |

| MTBF      | Mean Time Between Failures                                                                                                  |  |

| MUTEX     | Mutual Exclusion Element                                                                                                    |  |

| MUX       | Multiplexer                                                                                                                 |  |

# XX ACRONYMS

NoC Network-on-Chip

PLL Phase-Locked Loop

PN Petri Net

PRBS Pseudorandom Binary Sequence

RG Reachability Graph

RO Ring Oscillator

RTC Relative Timing Constraint

SG State Graph

SoC System-on-Chip

STG Signal Transition Graph

TS Transition System

UCOM Unidirectional Communication

VHDL VHSIC Hardware Description Language

VCO Voltage Controlled Oscillator

VTC Voltage Transfer Characteristic

# Part I PHD THESIS

#### 1.1 MOTIVATION

Synchronization is a prominent issue in the design of modern digital systems. As the diversity of components, clock frequencies, and voltages on a chip increases, so does the importance of synchronization in order to reliably pass data across the regions of variation. Both the methodologies of Globally Asynchronous Locally Synchronous (GALS) signaling, and Network-on-Chips (NoCs) require synchronization. The former case requires the presence of an asynchronous wrapper in order to reliably pass data between two clock regions, which must then be synchronized at each end of the transfer [10]. While in the latter case, the interconnection network is shared between devices via the use of packets, and synchronization is necessary in order to perform the handshakes between the network and the system resources [7].

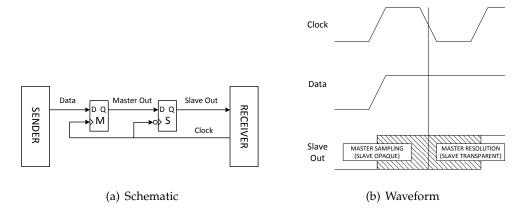

A common method for performing synchronization across two clock domains involves the use of a cascaded flip-flop synchronizer. Let us begin with a brief exploration of such a synchronizer, while highlighting the limitations and short-comings of the same to bring the primary issues discussed in this thesis into sharp relief. A basic two-flop synchronizer, as shown in Fig. 1.1(a), operates by using pair of flip-flops in a master-slave configuration to synchronize data items. A synchronization operation, as shown in 1.1(b) consists of two phases: sampling, and resolution.

During the sampling phase, when the *Clock* signal is high, the master latch samples *Data* items, while the slave latch remains opaque to changes. When the *Clock* signal transitions from high to low, the synchronizer enters the resolution phase, and master latch becomes opaque to changes, while the slave latch becomes transparent. During the resolution phase, the output signal from the master latch is pulled to either the supply voltage level or ground from an initial analog voltage level (i.e., it becomes a digital output signal). When the *Clock* signal transitions from low to high, the synchronizer re-enters the sampling phase and the output of the slave latch becomes opaque, thus retaining the resolved value from the previous sampling phase (i.e., it transmits the prior value from the master latch).

With the prior explanation in hand, we can now address the shortcomings of this design. When the *Data* input to the master latch changes state "sufficiently close" to the *Clock* transition marking the end of the sampling phase of the master latch, it results in longer than normal resolution times. If the output from the master latch does not resolve to a clear digital high or low before the end of the resolution phase (i.e., when the slave latch becomes opaque) the synchronization operation fails. The reliability of a two-flop synchronizer is thus directly related to the resolution time allotted to the synchronization operation, which is itself dependent on the duty cycle. Moreover, it will be shown in Chapters 2 and 3 of

Figure 1.1: Cascaded Two-Flop Synchronizer

this thesis that the relationship between the failure rate of the synchronizer and the time available for synchronization is exponential.

Because of the aforementioned relationship, the reliability of the synchronizer can be impacted by variations in the duty cycle of *Clock* signal. Of specific note are:

- 1. Variations in the delays of the CMOS transistors which comprise the *Clock* signal, due to process, voltage, and temperature dependencies.

- 2. Variations in the duty cycle due to the presence of multiple operating modes.

Typically, a cascaded flip-flop synchronizer is designed to meet the requirements of the worst-case operating mode only (i.e., the minimum time available for synchronization). In most cases, additional flip-flops are placed in series with the original two-flop master-slave latch pair to accomplish this. However, as additional flops are added, modelling the reliability characteristics of the synchronizer becomes more difficult [42].

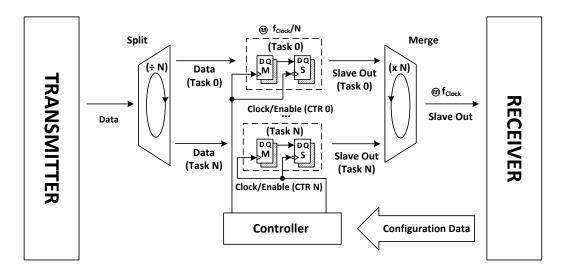

By integrating a combination of parallelism and task scheduling, known as wagging, into the design of a cascaded flip-flop synchronizer, as shown in Fig. 1.2, the worst case reliability requirements mentioned above can be met while using simpler two-flop equation models. Furthermore, if the parallelism and task scheduling in the cascaded flip-flop synchronizer of Fig. 1.2 can be altered by utilizing the practices of reconfigurable hardware design, the reliability characteristics of the synchronizer can be dynamically changed on an as needed basis via the use of control codes.

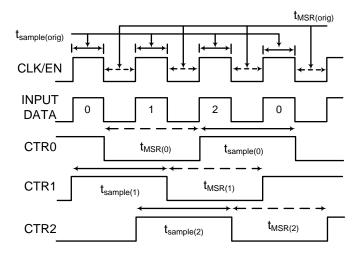

The parallel synchronizer of Fig. 1.2 operates by sharing the input data from the transmitter between the parallel master-slave flip-flop pairs, while the controller generates the Clock/Enable (CTR) signals used to schedule the sampling and resolution phases of each flip-flop pair. Resolved data items from the parallel master-slave flip-flop pairs are then merged back together and sent to the receiver. The tasks are shared evenly between master-slave flip-flop pairs, which results in an increase in the time available synchronization that is directly proportional to

Figure 1.2: Parallel Two-Flop Synchronizer

the number of parallel flip-flop pairs used, which will be discussed in greater detail during Chapter 3. When comparing the synchronizer design of Fig. 1.2 to that of Fig. 1.1, the trade-offs to are divided into two categories:

- 1. Delays due to additional hardware components along the datapath from the transmitter to the receiver.

- 2. Power and area overheads due to the control hardware, replicated master-slave latch pairs, and additional hardware components along the datapath.

Achieving the aforementioned design goals of reconfigurability and parallel synchronization requires that the issues of scalability, reliability, and fault tolerance be addressed within the context of the control hardware. Scalability issues, within this context, stem from the sharing of devices within a multi-mode reconfigurable controller. More specifically, it is necessary to maintain a limit on the maximum fan-in or fan-out of the control hardware regardless of the number of configurable modes available in the system. Reliability issues, within this context, refer to the protocols by which configurable modes are changed and functional correctness is guaranteed. Fault tolerance issues, within this context, concern how to route around faulty devices within the controller, which is useful as devices may be shared between more than one configurable mode. Additionally, if the transmitter and receiver are decoupled from each other via the use of a First-In First-Out (FIFO) buffer, as in prior literature by Chelcea, then data flow issues, such as data accumulation of starvation within the buffer, must also be considered as well [15].

With that in mind, the central aspects of this thesis will focus on the following issues:

- 1. Limitation of capacitive loading within the devices which comprise a multimode reconfigurable controller (Chapter 3).

- 2. Development of an asynchronous reconfiguration protocol which guarantees the functional correctness of the reconfigurable controller (Chapter 4).

- 3. Methods for excluding faulty components within the reconfigurable controller (Chapter 5).

- 4. Amelioration of data accumulation/starvation in parallel synchronizer incorporating a FIFO buffer (Chapter 6).

#### 1.2 CONTRIBUTIONS

This thesis presents and explores a framework for the design of reconfigurable control devices for parallel synchronizers through the use of distributed embedded graphs. Core to the work are the control of metastability within a parallel synchronizer through the application of one-hot codes, the issues of fault-tolerance within the parallel control structure via the use of bypass paths, as well as an of how the wagging paradigm affects the behavior of a FIFO synchronizer, and how to overcome the common pitfalls of data accumulation and reduced MTBF at higher clock frequencies.

It functions as a natural extension of work on parallel synchronization previously presented by Jex and Dike in 1995, Suk-Jin et. al in 2004, and work on wagging synchronization that was presented in 2010 by Alaskih [41] [43] [2]. Principle to this work are the following topics:

#### 1.2.1 Algorithms for Load Balancing in Token Rings via Distributed Embedded Graphs

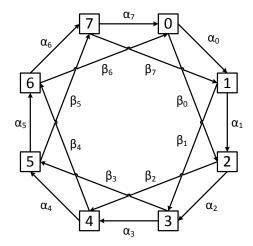

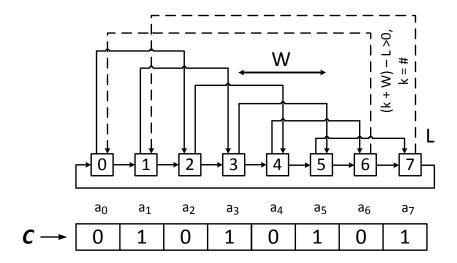

A basic algorithm for distributing the number of adjacent connections in an embedded cycle graph which models a multi-cycle token ring construct with several cycles is presented. Thereafter, It is optimized to improve the redundancy inherent to the graph and reduce overhead. Both the sub-optimal and optimized algorithms place concrete limitations on the maximum adjacency possible at a given vertex.

Such algorithms are useful in minimizing the capacitance and fan in/out of the connections of the resulting physical token ring implementation. As an example, embedded token rings based on ring oscillators, Muller pipelines, and David cells are simulated in UMC 90nm technology using CADENCE in Section 3.4. Abstract versions of the algorithms are also modeled in C++ in Section 3.3 [56] [21].

# 1.2.2 Manipulation of Parallelism in a Self-Timed Reconfigurable Control Device via One-Hot Coding

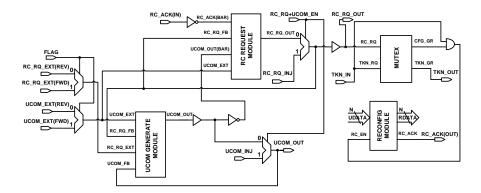

A design for a controller device is presented which is suitable for manipulating the parallelism contained within a token ring based on embedded graphs. Unidirectional Communication (UCOM) threading is shown to be useful in exerting control over asynchronous circuits based on a cyclic graph composed of independent loops, where the individual loops already possess Complete State Code (CSC). Merging of output data from multiple interrupt devices through the use of K-maps is shown to be essential in linking the interrupt devices together.

This method is useful in that it gives the designer direct control over the time available for synchronization inherent in a synchronizer composed of multiple parallel cascaded flip-flops at the cost of additional hardware. CADENCE simulations charting the performance of the control device across various process and temperature parameters in a UMC 90nm technology are used as a proof of concept.

# 1.2.3 Tolerance of Hard Faults in a Self-Timed Reconfigurable Control Device via Bypass Paths

The specification of the basic control device is modified by incorporating bypass paths into the underlying behavior graph. This allows faulty nodes to be excluded from the system, thereby facilitating recovery from hard faults at the cost of reduced performance. The concept of UCOM thread forwarding is introduced in order to ensure that the underlying Signal Transition Graph (STG) of the control device remains valid if a path is bypassed. The consistency of the graph is analyzed using a nearest neighbor checking algorithm and completion detection.

The utility of this method lies in overcoming the limitations of a Johnson counter, which tends to suffer either state-space locking in the case of stuck-at faults or unpredictable behavior in the case of intermittent hard faults [52]. This process is evaluated through simulations on both Petri Net (PN) and STG models of the system in Workcraft, as well as circuit simulations in CADENCE.

#### 1.2.4 Flow Control in a FIFO Synchronizer based on Wagging

A VHDL analysis of a FIFO synchronizer based on wagging is tested in Xilinx using automated test methods such as PRBS input vectors, and signature analysis. It is shown that while the MTBF can be manipulated via the use of shift register control signals, care must be taken when the parallel lines are serialized or the designer might not see the anticipated MTBF gains of the wagging method.

#### 1.3 ORGANIZATION OF THESIS

The thesis is organized as follows:

*Chapter 1* "Introduction." Describes the motivation, contributions, and organization in the thesis.

Chapter 2 "Background Literature & Models." Presents a review of the relevant theory on asynchronous circuits and metastable events. Discusses conceptual models useful in understanding the content of subsequent thesis chapters such as PNs, STGs, and embedded cycle graphs.

Chapter 3 "Overview of Wagging Synchronization." Presents a brief review of prior synchronization literature. Introduces the concept of synchronization via wagging, and discusses its effects on relevant synchronization parameters. Introduces the abstraction of a token ring, and compares various combinational and sequential circuit topologies suitable for the realization of the same. Applications of embedded cycle graphs to arbitrary token rings are also discussed, which focus

on the algorithms for the balanced distribution of edges in the ring construct.

Chapter 4 "Parallelism in a Reconfigurable Controller for Wagging Synchronization." Presents a brief review of the concepts of arbitration and reconfigurability, as it pertains within the context of a token ring based on embedded graphs. Defines a protocol for reconfiguration based on STGs which uses both interrupts and one-hot codes to control the parallelism in a reconfigurable controller device via the selection of valid embedded configurations within the behavior graph. Illustrates how UCOM threads can be used to control both the firing order and end behavior of independent interrupt devices. Addresses issues such as the reachability of different embedded specifications, the process by which the output data from separate interrupt devices is merged together, and the optimization of the one-hot control data via encoding to limit the number of input signal lines to a logarithmic growth function. A basic controller design is simulated across 5 process corners in a CADENCE UMC 90nm technology, and the results are presented as a proof of concept.

Chapter 5 "Robustness in a Reconfigurable Controller for Wagging Synchronization." Explores how the fault tolerance of the parallel controller device in Chapter 4 can be improved by excluding faulty nodes from the embedded behavior graph, as well as touching on the limitations of prior work regarding Johnson Counters. The STG of Chapter 4 is extended through the incorporation of bypass paths, which are necessary for the exclusion process. The concept of UCOM thread forwarding is defined, which is used to maintain the validity of the underlying STG in the presence of such bypass paths. A PN model is used to simulate the reconfiguration and selection process of the system via Workcraft. A nearest neighbor checking algorithm is also presented, which is used to validate the consistency of the cycle graph produced via reconfiguration and chordal bypass paths.

Chapter 6 "Flow Control in Wagging Synchronizers incorporating FIFO Buffers." Analyzes the flow control issues present in a wagging synchronizer which utilizes a FIFO to decouple read and write operations from each other. Introduces key design considerations in the FIFO synchronizer architecture. Discusses the VHSIC Hardware Description Language (VHDL) design flow and test bench used to simulate and verify the flow control algorithm in the chapter.

*Chapter* 7 "Conclusions." The work in the thesis is summarized, and future research directions are discussed.

### 2.1 INTRODUCTION (ASYNCHRONOUS CIRCUITS)

While the design and implementation of asynchronous circuits has been a topic of discourse for several years now and a complete overview is the subject of a textbook in and of itself, the work explored in the later body of this thesis is best served by providing a general overview of the main concepts which both motivate and underpin the concepts that will be discussed later, punctuated by a few well chosen examples. In the introductory section of this chapter the benefits, drawbacks, and differences between standard synchronous and asynchronous controller design are assessed. Major building blocks in asynchronous design used in the later portions of this thesis will also be presented. In Section 2.2, the theoretical concept of Petri nets will be presented with emphasis on how these nets can be used to model the behavior of asynchronous systems. Continuing onward, Section 2.3 will link the concept of a Petri net with that of a signal transition graph, which are used to further describe the internal workings of an asynchronous specification. Section 2.4 will discuss the concept of metastability, which is useful for describing the failure behavior of the synchonizer circuits covered in later chapters. Finally, Section 2.5 will cover the concept of an embedded cycle graph, which is a useful construct for handling the designs presented in the further chapters of this work.

#### **2.1.1** *Properties of Asynchronous Circuits*

Asynchronous circuits function in the absence of a global time reference which is a hallmark of standard synchronous circuit design. In synchronous circuit designs, glitches are allowed at all times during circuit operation excepting the times at which a clock transition occurs and all signals are assumed to be stable. Only knowledge of the final system state and the time allotted to complete its operation are required. By contrast, asynchronous circuits require knowledge of not only the final state of the system *but also the partial states as well*, in addition to a requirement that all transitions be glitch-free during the entire time continuum of its operation. For this reason, asynchronous designs do not generally enjoy the ubiquity of their synchronous counterparts. However, asynchronous circuits do possess certain advantageous properties which merit consideration.

**Modularity** From the perspective of the individual circuit, having a global clock simplifies the design process. However, this requirement becomes restrictive as the number of transistors on a chip increases. In a synchronous system, both the phase and frequency of the global clock are assumed to be known quantities. However, the arrival time of the clock observed by separate components in the system varies from one end of the chip to the other, due to both the spatial distance of the components from the distribution network itself, as well as differences in both the

passive interconnect and active device parameters [22]. This variance is referred to as the *clock skew* of the system, and it places constraints on both the maximum and minimum permissible operating frequency [29].

Because of the aforementioned timing constraints and the tightly interconnected relationship between the clock distribution network and intellectual property (IP) blocks present in a large scale synchronous designs, frequency scalability and reuse are not inherent features. Initiatives in previous years dealt with how to increase the plug and play characteristics of synchronous designs, such as creating standardized interfaces for Virtual Components [1]. By contrast, modularity is an inherent property of asynchronous circuits. Asynchronous blocks communicate with each other through protocols called *handshakes*, which will be discussed in more detail in subsection 2.1.2. No timing assumptions exist between the blocks, and as a consequence the asynchronous blocks can be frequency scaled and reused elsewhere without loss of functionality.

In more recent years, asynchronous design practices have been adapted in efforts to improve the modularity between synchronous designs. In one case, the modularity of System-on-Chip (SoC) designs can be improved by constructing the system with several different voltage/frequency islands (each with their own local clock) and then *synchronizing* the data items between regions using handshakes. While the topic of synchronization will be covered in Chapter 3, this principle forms the basis of the GALS signaling paradigm. GALS requires the presence of an asynchronous wrapper in order to reliably pass data between two clock regions, which must then be synchronized at each end of the transfer [14].

Continuing forward on the point above, there has also been a drive to partially decouple the component blocks in a SoC from the clock distribution network, as in the NoC paradigm [20]. For reference, a NoC routes transmitted data items as packets (called flits) along the wires of a homogeneous interconnection network, and carries out data transfers between the interconnection network and the local components using a network interface circuit. This network interface handles synchronization and flow control at the endpoints, while arbitration placed at regular intervals along the interconnection network handle the routing and flow control of flits across the chip [20].

Both of these examples serve to illustrate that modularity is a major design concern, and as stated above asynchronous circuits and design methods are well suited to handling it.

**Power** The advantageous power considerations which factor into circuits built from asynchronous designs can be broken down into two general categories.

The first category is tied to the discussion on modularity above. More specifically, in systems where no global clock exists and each locally clocked module communicates system-wide via asynchronous handshakes (i.e. GALS) there is also no global power consumption attributed to a system wide clock distribution network. The clock distribution network can have a significant impact on the global power consumption of a system. As an example, 33% of the system power in the Intel Itanium 2 processor was consumed by the clock distribution network back in 2002, which serves to highlight the statement above [59]. More recently in 2005,

this emphasis on power consumption led to the development of an asynchronous NoC which demonstrated reduced power consumption in the clock distribution network when compared against a synchronous design [7]. The only drawback is the additional complexity incurred as a result of utilizing asynchronous design methods [53].

The second power consideration is the reduced electromagnetic emissions of asynchronous designs. To clarify, the switching tranitions of control and data signals in a synchronous system are often correlated to the clock itself, which lead to draws in the supply current at the frequency of the clock signal and related harmonics [78], [18]. These harmonics impact the frequency domain characteristics of the system and can prove detrimental in applications where such characteristics must be precise [78]. As asynchronous designs are event-driven systems, no such harmonics are present which lead to reduced emissions in the frequency domain.

It is the former category that has garnered more attention in recent years though, with self-timed microprocessors like the ARM AMULET series becoming prevalent in low power designs where asynchronous processing is prevalent [31], [33], [32]. However, it should be noted that the dynamic power consumption savings incurred as a result of asynchronous design methods, must be weighted against the increased standby power consumption resulting from the increased complexity of asynchronous implementations.

Latency and Throughput The final distinctive property that separates logical circuits implemented using synchronous methods from their asynchronous counterparts is the difference between the global latency and throughput characteristics of each respective implementation. To clarify, the modeling the latency and throughput behavior of a synchronous design relies on computing the worst-case latency of the system, and attaching worst-case maximum (and sometimes minimum) frequency requirements to the finished product, thereby specifying where the design can be applied. Asynchronous designs, by contrast, only rely on the average-case latency between their components. Due to the aforementioned modularity property, as long as the asynchronous communication protocols connecting the modules together are satisfied functional correctness of the system is maintained. To be succinct, the latency and throughput of synchronous design is limited by the slowest component in the system, while an asynchronous design is limited by the average delay of all the components in the system at the cost of possibly unbounded circuit delays. Appropriately, the differences between latency and throughput of synchronous and asynchronous designs are mirrored in the control methodology discussed in the next subsection.

#### 2.1.2 Asynchronous Control Circuits

Conveying the distinctions between asynchronous control circuits and their synchronous counterparts, first requires a brief overview of the structural characteristics of a sequentials circuits composed using synchronous methods. The abstract model segregates the design into two parts, which are as follows:

- data path refers to the individual blocks within a system that perform manipulations and transformations on the data they receive. These blocks can either perform arithmetic operations (e.g., adders, multipliers), or communication and storage operations (e.g., muliplexers, registers).

- **control** refers to the signals that determine the data used by each block (e.g., multiplexer select signals), or the operations that each block performs (e.g. ALU operation codes).

In a synchronous design, the clock signal acts as a trigger for all of the control and data path operations that occur within a given clock period. As long as a final state is reached within a single clock cycle functional correctness is assured. From a control perspective, it can be said that the control within the system is centralized, and synchronization is implict across all blocks in the system. By contrast, in an asynchronous design control is distributed, as no global clock is present. Each block only synchronizes with its relevant neighbors, regardless of what other blocks in the system are doing. Because of this, the behavior of the entire system must be modeled with these concurrent executions in mind. The communication between neighboring blocks is accomplished via a handshaking protocol, which is composed of two parts:

- request refers to a signal issued from the environment to the input of a block indicating that data is ready at that device operation is requested.

- acknowledge refers to a signal issued from the output of a block to the environment indicating that the device has finished its operations and that the data results are stable.

The weaknesses of this control method stems from the increased number of data lines used to implement completion detection, as is the case with delay-insensitive coding styles such as a *dual rail* code [70]. Alternatively, the delay of individual lines can be adjusted to ensure that the propagation delay of signals lines in the system exceeds the worst case combinational operation of any given block [18]. The later method is less robust because of the additional timing assumptions that hinder the modularity and portability of the design. The only other pitfall is the requirement that the signals are free of *hazards* (i.e., deviations from specified circuit behavior).

#### 2.1.3 Asynchronous Circuit Primitives

Given the discussion above, we can now examine some of the fundamental sequential circuit primitives that will be used throughout the course of this work. Two major primitives common to asynchronous controller designs are readily apparent.

Figure 2.1: Behavioral representation of a D latch

Figure 2.2: Behavioral representation of a Muller C-Element (MCE)

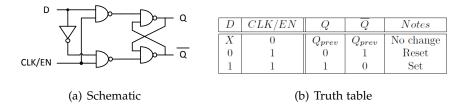

#### 2.1.3.1 Latches and Flip-flops

**Latches** A latch is defined as a level-sensitive circuit which is used to transmit and retain state information in a sequential process, as shown in Fig. 2.1(a). The state of the latch is altered when a differential voltage is applied to the inputs of the two cross-coupled NAND gates in the circuit. When the enable signal (CLK/EN) is high, the output signal of the latch (Q) follows the input signal (D). When the enable signal is low, the latch output retains its previous value. The truth table illustrating this process is shown in Fig. 2.1(b).

Flip-flops When two latches are placed in series, they form what is known as a *flip-flop*. The most prevalent example of a flip-flop is a D flip-flop (though others exist, such as the JK flip-flop), where the two latches forming the flip-flop are triggered on opposite edges of the clock in what is commonly known as a master-slave configuration [66]. Depending on how it is used it can either function as a data storage element, or as a synchronization element. In this work, we will focus on the latter application.

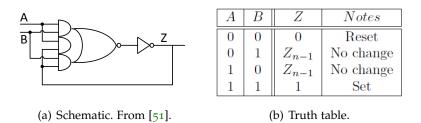

#### 2.1.3.2 Muller C-Elements

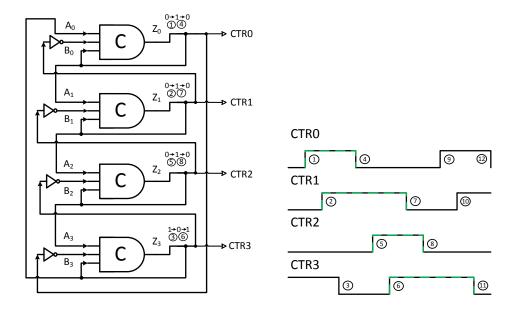

**Muller C-Element (MCE)** A MCE is a circuit that changes its state information only when all of its signal inputs (A, B, Z) are either logic high or logic low values, as in Fig. 2.2(a). All other input combinations result in the circuit outputting its last valid state. The truth table illustrating this process is shown in Fig. 2.2(b).

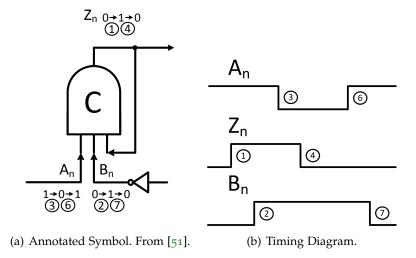

The operation of an individual cell is defined by both the output signal that the cell produces  $(Z_n)$ , and the input signals to the cell  $(A_n(Z_{n-1}), B_n(\overline{Z_{n+1}}))$  which are generated by adjoining MCEs. Fig. 2.3(a) depicts a schematic of an individual MCE, where the circled numbers in the figure represent the individual transitions generated internal to the cell, starting at transition 1. External signals generated by

Figure 2.3: Annotated Muller C-Element schematic with signal transitions representing 1 operating cycle

Figure 2.4: Annotated David Cell schematic with signal transitions representing 1 operating cycle

the adjoining MCEs are shown in Fig. 2.3(a), and also appear in the timing diagram of Fig. 2.3(b).

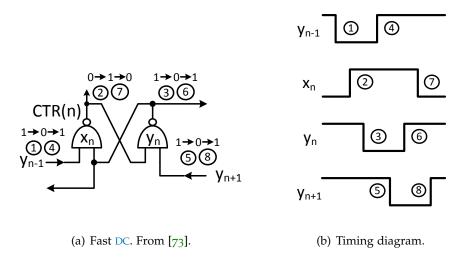

#### 2.1.3.3 David Cells

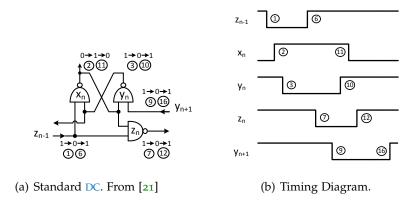

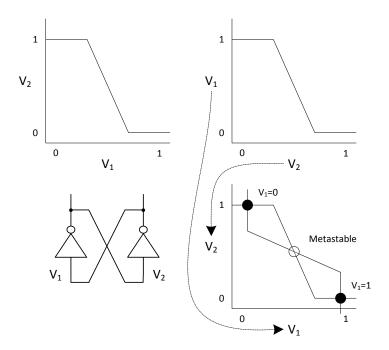

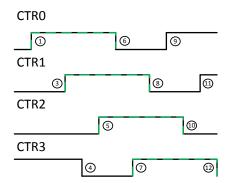

**David Cell (DC)** A DC, as shown in Fig. 2.4, can be thought of as a distributed circuit, where the state information or "token" is stored within the pair of complementary stable states formed by the cross-coupled NAND gates in the cell. If the CTR is high, then a token is present, and vice-versa if a token is absent.

The operation of an individual cell is defined by both the output signals that the cell produces  $(y_n, z_n)$ , and the input signals to the cell  $(z_{n-1}, y_{n+1})$  which are generated by adjoining DCs. Fig. 2.4(a) depicts a schematic of an individual DC, where the circled numbers in the figure represent the individual transitions generated internal to the cell, starting at transition 1. External signals generated by the adjoining DCs are shown in Fig. 2.4(a), and also appear in the timing diagram

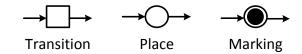

Figure 2.5: Petri Net Symbols

of Fig. 2.4(b). For reference purposes, in Fig. 2.4(a) these unmarked transitions are {4}, {5} for the previous DC in the token ring chain, and {8}, {13} for the next DC in the chain.

It should be noted that the "token" within the DC of Fig. 2.4(a) is atomic (i.e., the token is only "present" in a single cell at any given time). However, this does not have to be the case. In fact, the number of transitions which are required to complete the operation of an individual DC can be reduced if the atomicity of the token is violated and it is allowed to simultaneously exist in multiple DCs of the token ring. This concept has been referred to in prior literature as *token spreading* [73].

#### 2.2 PETRI NETS

Accurately modeling and specifying the behavioral characteristics of an asynchronous circuit is of vital importance to the design process of the same. In a traditional synchronous design, the behavior of the system is only analyzed around the rising and falling edges of a clock signal. The periodicity between the successive rising or successive falling edges of the clock signal is referred to as the *duty cycle* of the circuit. The inputs and outputs of the system are allowed to vary at any point in between these edges, but are assumed to resolve prior these evaluation points. By contrast, in an asynchronous design, the behavior of the system must be known for the entire time continuum of the duty cycle. As a consequence, the design of an asynchronous circuit is often more complex than the design process of any synchronous counterpart.

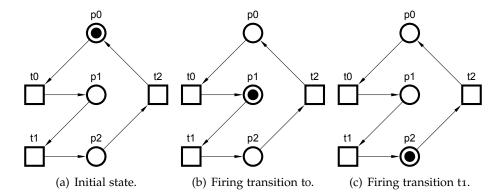

As a consequence of the design challenges listed above, the design flow needed to visualize the system as a whole is best done using a formal model known as a *Petri Net (PN)*. This model was originally developed by Carl Adam Petri in 1962, where he depicted the behavior of a system in terms of concurrent events, the causalities between these events (called transitions), and the dynamic state of the net itself (called markings) [63], [58], [62]. Where a traditional *finite state machine* (FSM) depicts the behavior of a synchronous digital circuit using a single global state (i.e., all actions take place on the rising or falling edge of a global clock signal), Petri Nets define the behavior of an asynchronous system as a composition of the local states in the system which alter themselves via synchronization and communication.

Let us define the symbols used in this formal model, which are depicted in Fig. 2.5. Informally, the *transitions* in the PN represent the events in an asynchronous system. *Places* can be thought of as the conditions necessary for these events to occur. If a place contains a *token* (i.e., if it is *enabled*) it is said to have a *marking*.

Figure 2.6: Petri Net of a 3-cell token ring

The global state of the asynchronous system is composed of all the marked places in the PN. With that in mind, the behavior of the PN can be thought of as a token game, where the markings change position (state) according to the enabling and firing rules in the net.

In the remainder of this Section, the formal definitions for the basic properties and behavior of a generic PN will be covered. Furthermore, the PN a 3-cell token ring, as shown in Fig. 2.6, will be used to provide additional insight.

**Definition 2.1** A Petri Net is a quadruple, PN = (P, T, F, m) where:

P is a finite set of places,

T is a finite set of transitions:  $(T \cap P = \emptyset)$ ,

F:  $(T \times P) \cup (P \times T) \rightarrow \mathbb{N}$  is a flow relation,

m:  $P \rightarrow \mathbb{N}$  is the marking (or state) of the net.

These nets are governed by a series of rules which will be shortly codified in the following subsections.

#### 2.2.1 Pre-sets and Post-sets

**Definition 2.2** The *pre-set* of a transition t, as denoted by  $\bullet$ t, is the set of places  $p \in \bullet t \subseteq P$  such that  $p \in \bullet t \Rightarrow F(p,t) > 0$ . Symmetrically, the pre-set of place p, denoted by  $\bullet p$ , is the set of transitions  $t \in \bullet p \subseteq T$  such that  $p \in \bullet t \Rightarrow F(t,p) > 0$ . Similarly, the *post-set* of a transition (or place) x, denoted  $x \bullet$ , is the set of all places (or transitions) y, such that  $y \in x \bullet \Rightarrow F(x,y) > 0$ .

Speaking less formally, the post-set of a transition corresponds to all of its output places, while the pre-set corresponds to all of its input places via similar arguments. As an example, in Fig. 2.6(a)  $\bullet$ p0 = t2, and p0 $\bullet$  = t0

### 2.2.2 Enabling and Firing

**Definition 2.3** A transition  $t \in T$  is *enabled* at marking  $m_1$  if for any place  $p \in \bullet t$ ,  $m_1(p) \ge F(p,t)$ . This enabled transition may produce a new marking,  $m_2$ , by *firing*

Figure 2.7: Reachability Graph of a 3-cell token ring

such that:

$$\forall p \in P : m_2(p) = m_1(p) - F(p,t) + F(t,p),$$

where + and - are defined component-wise, as denoted by  $\mathfrak{m}_1 \stackrel{t}{\to} \mathfrak{m}_2$  or  $\mathfrak{m}_1 \to \mathfrak{m}_2$ . Thus for each  $\mathfrak{p} \in \bullet t$ , firing t subtracts  $F(\mathfrak{p},t)$  tokens from  $\bullet t$ , and adds  $F(t,\mathfrak{p})$  tokens to  $t \bullet$  for each  $\mathfrak{p} \in t \bullet$ .

In the 3-cell token ring of Fig. 2.6(a), the only transition enabled in the Petri net is at t0 due to the presence of the token at place p0. After firing, the token marking is subtracted from place p0 and then added to place p1 using the flow relation specified above.

#### 2.2.3 Reachability

**Definition 2.4** The new marking  $m_2$ , produced from the firing of  $m_1$ , can enable further transitions. Consequently, we can now define sequences of transitions that are *reachable* from the firing of an initial marking, denoted  $m_0$ . These transition sequences are referred to as *traces*. The set of all markings reachable from marking m is denoted as [m]. The set of all markings reachable from the initial marking of the PN, denoted  $[m_0]$ , defines the *Reachability Graph* (*RG*) of the net, which consists of nodes corresponding to the reachable markings in the graph, and edges that correspond to the firing transitions between pairs of markings. Two nodes,  $m_i$  and  $m_j$ , in the graph are connected by an arc if  $m_i \rightarrow m_j$  holds.

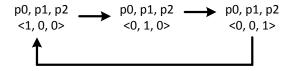

The RG of the 3-cell token ring depicted in the PN of Fig. 2.6, is illustrated in Fig. 2.7. The markings in the RG use vector encodings of the form  $\langle p0, p1, p2 \rangle$ . From the initial marking  $\langle 1, 0, 0 \rangle$  the RG is traversed as follows  $\langle 1, 0, 0 \rangle \xrightarrow{t0} \langle 0, 1, 0 \rangle \xrightarrow{t1} \langle 0, 0, 1 \rangle \xrightarrow{t2} \langle 1, 0, 0 \rangle$ . When t2 fires, the PN returns to its initial marking. However, as there are no concurrent paths in the original PN, this particular RG is only useful in a pedagogical capacity.

### 2.2.4 Other Petri Net Properties

#### **Boundedness**

The behavior of a circuit specification must to be finite. A PN is called *bounded* if the net only accumulates a finite number of tokens at any given place. If the number of tokens accumuated is equal to k, then the PN is called *k-bounded*. If k is

equal to 1 then the PN is called *safe*. Due to the binary nature of signal transitions in many digital circuits, 1-safe nets are the nets that are the most applicable to logical synthesis.

**Deadlocks** If a firing pattern results in a marking where no PN transitions are enabled, it is referred to as a *deadlock state*. If no such reachable markings exist, the PN is called *deadlock-free*.

#### 2.3 SIGNAL TRANSITION GRAPHS

While the description of a PN above yielded a basis for formal description of an asynchronous circuit, in the following sections another model for the description of an asynchronous circuit known as a Signal Transition Graph (STG) will be covered. While many of the same properties are shared between STGs and PNs, the following are of particular note [18]:

- 1. Rules for the enabling and firing of transitions.

- 2. Notions of reachable markings and traces.

- 3. Temporal relationships between transitions (i.e., choice, conflict, precedence, and concurrency).

However, the transitions in a STG are defined in terms of the rising and falling edges of a binary signal, rather than in terms of the presence or absence of a marking (token) in the pre-set or the post-set of a choice place of a PN. It is precisely this distinction that allows automated tools such as PETRIFY or Workcraft to derive complex gate equations necessary for logical synthesis from an asynchronous STG specification, but render them unable to do so when the same system is specified using a PN.[17] [18] [65]

First, Section 2.3.1. will provide a brief overview of the relationship between STGs and PNs, while Section 2.3.2 will provide a similar overview for State Graphs (SGs) and RGs. Next, Section 2.3.3. will cover the STG concept of CSCs. Finally, Section 2.3.4 will briefly touch on the concept of Relative Timing Constraints (RTCs).

#### 2.3.1 Relation to Petri Nets

**Definition 2.5** A *Signal Transition Graph* (*STG*) is a triple  $G = (PN, X, \lambda)$ , where:

- PN is a Petri net PN = (P, T, F, m),

- X is a finite set of binary signals, which generates a finite alphabet  $A^X = X \times \{+, -\}$  of signal transitions,

- $\lambda : T \to A^X$  is a labeling function.

Let us briefly unpack this definition. The first and third bullet points that indicate that the transitions, T, in the PN are replaced using the labeling function,  $\lambda$ . The second bullet point indicates that each transition in the old PN is split into a positive (rising edge, +) transition and negative (falling edge, -) transition.

Figure 2.8: Annotated STG of a 3-cell token ring

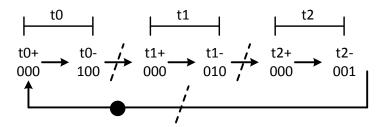

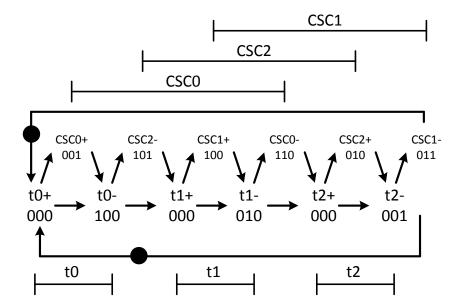

Highlighting the differences between STGs and PNs is best illustrated with a concrete example, and the annotated STG of Fig. 2.8 will serve in this capacity. As with the PN of Fig. 2.6, the STG will represent the a 3-cell token ring. The *initial marking* of the STG is indicated by the black dot on Fig. 2.8, while dotted lines represent *CSC conflicts* (i.e., points of identical state encoding).

#### 2.3.2 State Graphs and Reachability Graphs

A STG is also known as an interpreted PN, which is to say the transitions in the PN are labeled according to definition 2.5. Similarly, a SG is a RG with interpreted automata, which means that the markings and transitions in the RG have a 1-to-1 mapping with the (binary) states and events of a SG. To understand this relationship, we it must first note that a SG is defined by a Transition System (TS), rather than a Net like in a RG. A transition system is defined as follows [18]:

**Definition 2.6** A TS is a quadruple  $TS = (S, E, T, s_0)$ , where:

- S is a non-empty set of states,

- E is a set of events (E and S must be disjoint sets),

- T  $\subseteq$  S  $\times$  E  $\times$  S is a transition relation, and

- s<sub>0</sub> is an initial state.

Note: The elements of T are referred to as the transitions of TS, and will often be denoted by  $s \stackrel{e}{\to} s'$  instead of (s, e, s').

If S and E are finite, then the TS is finite. With the definition of a TS in hand, we can now formally define a State Graph [18]:

**Definition 2.7** A State Graph (SG) is a quadruple  $SG = (TS, X, \lambda_S, \lambda_E)$ , where:

- $TS = (S, E, T, s_0)$  is a transition system,

- $X = X_I \cup X_O$  is a set of binary signals  $X = x_1, x_2, ..., x_n$ ,

- $\lambda_S : S \to \{0,1\}^{|X|}$  is a state assignment function,

- $\lambda_E : E \to X \times \{+, -\}$  is an event assignment function.