# Electrical and Material Properties of Thin Film Perovskites

Daniel Joseph Robert Appleby

Doctor of Philosophy

May 2014

Submitted in partial fulfilment of the requirements for the degree of Doctor of Philosophy in Electrical and Electronic Engineering

"It doesn't make a difference how beautiful your guess is or how smart you are or what your name is. If it disagrees with experiment, it's wrong. That's all there is to it."

Richard P. Feynman

## Abstract

This thesis presents a study of negative capacitance in the robust perovskite  $BaTiO_3$ . Negative capacitance is an unstable state in ferroelectrics, which explains why there is a lack of experimental evidence in the literature. A positive capacitance in a series capacitor configuration allows stabilisation of negative capacitance. The key finding is the stabilisation of negative capacitance at room temperature in  $BaTiO_3$ .

Temperature constraints in back-end-of-line processing should be at 500 °C or below in order to avoid diffusion of dopants and to inhibit high resistivity silicide phases. Three deposition techniques, pulsed laser deposition, atomic layer deposition and sputter deposition are used to investigate the material and electrical properties of perovskites for back-end integration within this temperature constraint. SrTiO<sub>3</sub>, Ba<sub>0.8</sub>Sr<sub>0.2</sub>TiO<sub>3</sub> and BaTiO<sub>3</sub> are all explored as possible solutions for tunable capacitance under low temperature processing. Evidence is shown for SrTiO<sub>3</sub> displaying fully crystallised structures through pulsed laser deposition at 500 °C growth temperature.

A refined model of effective oxide thickness is used to calculate interfacial layers that impact metal-oxide-semiconductor capacitors. The model is applied to  $SrTiO_3$  metal-insulator-metal capacitors in terms of a dead layer. Calculation of the dead layer thickness, which has been previously unattainable using solely the series capacitance model, is carried out using the effective oxide thickness model. However, transmission electron microscopy images suggest that a physical layer of 'dead' material is abesnt in the capacitors. The results support the hypothesis of an intrinsic explanation to the dead layer phenomenon.

Finally, pulsed laser deposited  $BaTiO_3$  is explored in terms of ferroelectricity when integrated with Si using Pt/Ti/SiO<sub>2</sub>/Si substrates. Here, a mixed phase relationship is shown in the films of  $BaTiO_3$  in which the cubic phase, responsible for paraelectricity, dominates at room temperature. Increasing film thickness also correlates with higher remnant polarization in the films. The result confirms a size driven phase transition in thin film  $BaTiO_3$  which has previsouly been studied on perovskite free-standing films or nanoparticles.

## Acknowledgements

Firstly, I would like to thank my supervisor, Prof. Anthony O'Neill for giving me the opportunity to undertake this exciting research. His guidance and support throughout my studies has surely meant that I have completed my PhD to the very best of my abilities. I have been privileged to work under his supervision. I would also like to thank my second supervisor, Dr. Kelvin Kwa for all of his time and effort he invested in me along the journey of my PhD. We spent many an hour discussing ideas and working closely in the laboratory. I am deeply grateful.

I would like to take this opportunity to recognise our project collaborators at Imperial College London. In particular, Dr. Ullrich Hannemann, Tianle Wang, Dr. Bin Zou and Dr. Peter Petrov for their expertise and guidance on the PLD system. In addition, a special thank you to Prof. Neil Alford for his leadership and support at Imperial College, and ensuring we had the materials we required for completion of the studies. A further thank you must be given to the experts at Newcastle University whose help and advice was invaluable. They are Prof. Peter Cumpson and Dr. Anders Barlow for XPS, and Maggie White for XRD. Also, a thank you must be given to Dr. Budhika Mendis and Leon Bowen at Durham University for their time and knowledge on TEM. I must express sincere acknowledgements to EPSRC and Intel Ireland for the financial support they provided towards the project, for without them the work would not have been possible. Bernie Capraro from Intel Ireland deserves a special thank you for the additional time and mentoring he gave during my PhD, and also for the help he provided for extra sponsorship towards our Annual Research Conference 2013. A big thank you to all of my friends and colleagues I have met and had the pleasure to work with during my PhD. There are certainly too many to name, but without each and every one of you I know my time certainly would not have been as enjoyable as it has been. I do have to take time to particularly thank Nikhil Ponon, who started this journey with me. His knowledge, helpful discussions and friendship surely meant we both were able to drive the project towards a successful end.

One further thank you is reserved to a very close friend of mine, Nikodimos Lykos. His advice and friendship over the years contributed greatly to my successful academic career. The countless hours of revision together at Liverpool University are still fresh in my mind. Lastly, but most importantly, the biggest thank you to my parents Jill and Norman, and sister Holly. Without their never-ending love and support I would not be where I am today. I am forever grateful, and love them with all my heart.

# Contents

| Abstract                 | i    |

|--------------------------|------|

| Acknowledgements         | iii  |

| Contents                 | V    |

| Journals and Conferences | xi   |

| List of Figures          | xiii |

| List of Tables           | xxiv |

| Abbreviations            | XXV  |

#### Chapter 1

# Introduction, Research Aims and Hypotheses

| 1.1 Introduction                       | 1 |

|----------------------------------------|---|

| 1.2 Research Objectives and Hypotheses | 5 |

| 1.3 References                         | 9 |

#### Chapter 2

Ferroelectrics and their Incorporation into the Si Industry

| 2.1 Introduction                                          | 10 |

|-----------------------------------------------------------|----|

| 2.2 Ferroelectricity                                      | 15 |

| 2.2.1 Piezo/pyroelectricity and ferromagnetic comparisons | 15 |

| 2.2.2 Domains                                             | 17 |

| 2.2.3 Bulk and thin film ferroelectrics                   | 19 |

| 2.2.4 Dead layers                                         | 21 |

| 2.2.5 Perovskite ferroelectrics                           | 24 |

| 2.2.6 Electrostatics relating to capacitance              | 27 |

| 2.2.7 Landau's theory                                     |    |

| 2.2.8 Linear dielectrics                                  | 31 |

| 2.2.9 Non-linear dielectrics                              | 32 |

| 2.2.10 Temperature dependence                             |    |

| 2.3 Nanoelectronics and the Si Industry                   |    |

| 2.3.1 More Moore and scaling                              | 40 |

| 2.3.2 More than Moore                                     | 43 |

| 2.3.3 Low power applications                              | 45 |

| 2.3.4 Negative capacitance                                | 50 |

| 2.3.5 Tunnel FETs                                         | 53 |

| 2.3.6 Further applications and associated issues          | 55 |

| 2.4 Summary                                               | 58 |

| 2.5 References                                            | 60 |

# Thin Films, Characterisation and Fabrication

| 3.1 Introduction                                 | 64 |

|--------------------------------------------------|----|

| 3.2 Thin Film Capacitors and Materials           | 69 |

| 3.2.1 Insulator choice                           | 70 |

| 3.2.2 Electrode choice                           | 72 |

| 3.2.3 Substrate choice                           |    |

| 3.3 Electrical Characterisation                  |    |

| 3.3.1 Small-signal capacitance – voltage         |    |

| 3.3.2 Large-signal polarization – electric field | 80 |

| 3.3.3 Current - voltage                          | 81 |

| 3.4 Material Characterisation                    | 82 |

| 3.4.1 X-ray diffraction                          |    |

| 3.4.2 Atomic force microscopy                    | 83 |

| 3.4.3 Transmission electron microscopy           |    |

| 3.4.4 Raman spectroscopy                         | 86 |

| 3.4.5.X-ray photoelectron spectroscopy           |    |

| 3.5 Thin Film Deposition                         | 89 |

| 3.5.1 Atomic layer deposition                    |    |

| 3.5.2 Pulsed laser deposition                    | 91 |

| 3.5.3 Sputter deposition                         |    |

| 3.6 Summary                                      | 93 |

| 3.7 References                                   | 94 |

### Negative Capacitance in Ferroelectric Oxides at Room Temperature

| 4.1 Introduction             |     |

|------------------------------|-----|

| 4.2 Series Capacitance Model | 103 |

| 4.3 Experiment               | 115 |

| 4.4 Material Results         | 117 |

| 4.5 Electrical Results       | 121 |

| 4.6 Summary                  | 129 |

| 4.7 References               | 130 |

#### Chapter 5

## Low Temperature Growth of Perovskite Insulators for Tunable High-ĸ Applications

| 5.1 Introduction                                 |     |

|--------------------------------------------------|-----|

| 5.2 Experiment                                   |     |

| 5.3 Low Temperature Growth of SrTiO <sub>3</sub> |     |

| 5.3.1 Material properties                        |     |

| 5.3.2 Electrical properties                      | 149 |

| 5.4 Low Temperature Growth of Ba <sub>x</sub> Sr <sub>x-1</sub> TiO <sub>3</sub> | 161 |

|----------------------------------------------------------------------------------|-----|

| 5.4.1 Material properties                                                        | 161 |

| 5.4.2 Electrical properties                                                      | 163 |

| 5.5 Low Temperature Growth of BaTiO <sub>3</sub>                                 | 165 |

| 5.5.1 Material properties                                                        | 165 |

| 5.5.2 Electrical properties                                                      | 166 |

| 5.6 Summary and Conclusion                                                       | 169 |

| 5.7 References                                                                   | 172 |

## Ferroelectric and Tunable Perovskite Insulators for Integration with Si

| 6.1 Introduction                                      |     |

|-------------------------------------------------------|-----|

| 6.2 Experiment                                        |     |

| 6.3 The EOT Model                                     |     |

| 6.4 SrTiO <sub>3</sub> MIM Capacitors and Dead Layers |     |

| 6.4.1 Electrical characteristics                      | 190 |

| A. Permittivity                                       |     |

| B. Tunability                                         |     |

| 6.4.2 Material characteristics                        |     |

| 6.5 Mixed Phase BaTiO <sub>3</sub> MIM Capacitors     |     |

| 6.5.1 Results                                         |     |

| A. Electrical                                         |     |

| B. Material                |     |

|----------------------------|-----|

| 6.5.2 Discussion           |     |

| 6.6 Summary and Conclusion | 220 |

| 6.7 References             |     |

# Summary and Conclusion and Future Work

| 7.1 Summary and Conclusion |     |

|----------------------------|-----|

| 7.2 Future Work            | 232 |

| 7.3 References             | 238 |

## Journals and Conferences

**D. J. R. Appleby**, N. K. Ponon, K. S. K. Kwa, B. Zou, P. K. Petrov, T. Wang, N. M. Alford, and A. O'Neill, "Experimental observation of negative capacitance in ferroelectrics at room temperature," *Nano Letters* – Accepted June 2014, **DOI:** 10.1021/nl5017255 .

**D. J. R. Appleby**, N. K. Ponon, K. S. K. Kwa, U. Hannemann, P. K. Petrov, N. M. Alford, and A. O'Neill, "Ferroelectric properties in thin film barium titanate grown using pulsed laser deposition," *Journal of Applied Physics* – Submitted.

N. K. Ponon, **D. J. R. Appleby**, Erhan Arac, P. J. King, K. S. K. Kwa, and A. O'Neill, "Effect of deposition conditions and post deposition anneal on reactively sputtered titanium nitride thin films," *Thin Solid Films* – Submitted.

N. K. Ponon, **D. J. R. Appleby**, Erhan Arac, K. S. K. Kwa, J. P. Goss, U. Hannemann, P. K. Petrov, N. M. Alford, and A. O'Neill, "Impact of Crystalline Orientation on the Switching Field in Barium Titanate Using Piezoresponse Force Spectroscopy," *Advances in Scanning Probe Microscopy*, *MRS Proceedings*, 1652, 2014.

**D. J. R. Appleby**, N. K. Ponon, K. S. K. Kwa, B. Zou, T. Wang, and A. O'Neill, "Thin Film Barium Titanate for Nanoelectronic Applications," *Intel European Research and Innovation Conference*, 21-22 November 2013, Dublin, Ireland.

**D. J. R. Appleby**, N. K. Ponon, S. A. Mojarad, J. P. Goss, Z. Zhou, U. Hannemann, P. K. Petrov, K. S. K. Kwa, N. M. Alford, and A. O'Neill, "Low temperature fabrication of STO capacitors for integration with silicon," *E-MRS Spring Meeting*, 27-31 May 2013, Strasbourg, France.

S. A. Mojarad, J. P. Goss, K. S. K. Kwa, Z. Zhou, R. A. S. Al-Hamadany, **D. J. R. Appleby**, N. K. Ponon, and A. O'Neill, "Leakage current asymmetry and resistive switching behaviour of SrTiO<sub>3</sub>," *Applied Physics Letters*, 101, 173507 (2012).

N. K. Ponon, **D. J. R. Appleby**, S. A. Mojarad, K. S. K. Kwa, and A. O'Neill, "Ferroelectrics for nanoelectronics," *Intel European Research and Innovation Conference*, 3-4 October 2012, Dublin, Ireland.

S. A. Mojarad, K. S. K. Kwa, J. P. Goss, Z. Zhou, N. K. Ponon, **D. J. R. Appleby**, R. A. S. Al-Hamadany, and A. O'Neill, "A comprehensive study on the leakage current mechanisms of Pt/SrTiO<sub>3</sub>/Pt capacitor," *Journal of Applied Physics*, vol. 111, no. 1, p. 014503 (2012).

N. K. Ponon, **D. J. R. Appleby**, Z. Zhou, K. S. K. Kwa, and A. O'Neill, "Ferroelectrics for nanoelectronics," *Intel European Research and Innovation Conference*, 13-14 October 2011, Dublin, Ireland.

# List of Figures

#### Chapter 2

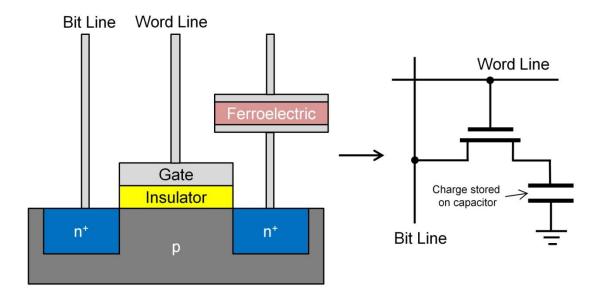

2.1: Schematic of the 1T/1C FRAM cell utilising ferroelectrics. Equivalent circuit shown as the transistor and capacitor connected to the word line and bit line, respectively.

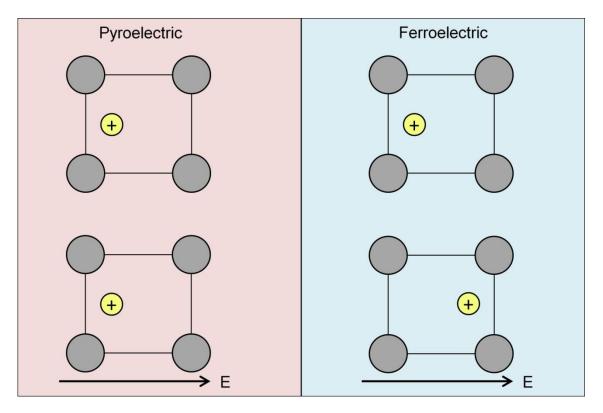

2.2: Pyroelectric and ferroelectric crystals are highlighted retaining their polar state. Application of an electric field switches the charge state in the ferroelectric, with the pyroelectric state remaining unchanged. Ferroelectrics are a subgroup of pyroelectricity (in addition to piezoelectricity) with this important switching characteristic.

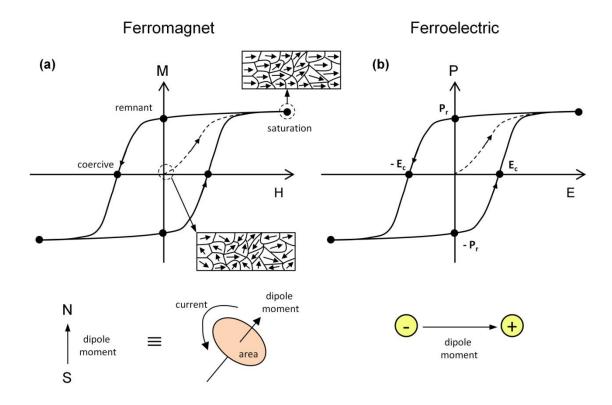

2.3: Illustration of the hysteretic nature of ferromagnetism (a) and ferroelectricity (b). As the field in each case is increased, the domains align through the force applied on the individual dipole moments, reaching saturation at high field. Removal of the field retains domain alignment, shown as a remnant polarization  $P_r$  for ferroelectrics. Reversal of the field switches the vector directions associated with the domains at the coercive point,  $E_c$  for the ferroelectric. Also shown is the magnetic and electric dipole moment, defining the properties in each case.

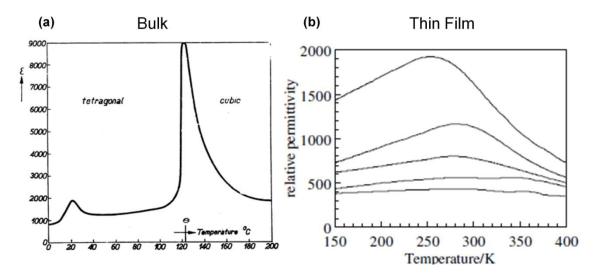

2.4: Permittivity response measured as a function of temperature in a bulk ferroelectric (a) [4] and thin films (b) [16]. The thin film maximum permittivity increases as a function of film thickness, starting from 175, 280, 340, 660 and 950 nm.

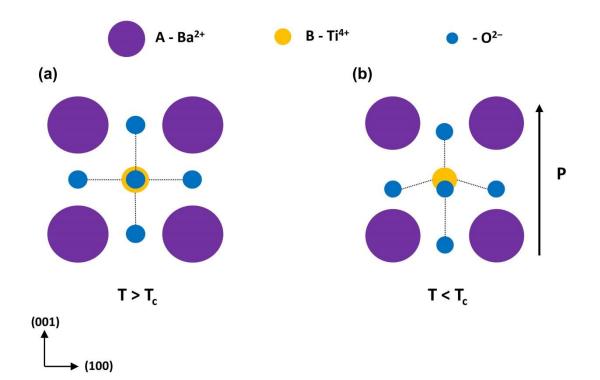

2.5: Schematic of the unit cell of a perovskite material  $BaTiO_3$ . The paraelectric phase is situated at temperatures above  $T_c$  where the unit cell is cubic (a). For the ferroelectric phase, temperatures lower than  $T_c$  induce a deformation along one of the axes and the unit cell is tetragonal, creating a permanent dipole with remnant polarization as shown (b).

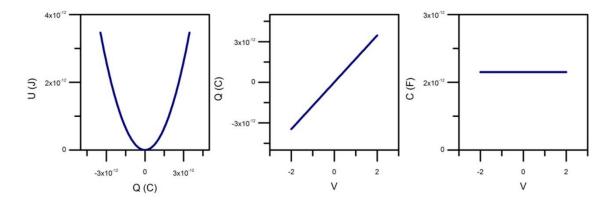

2.6: Energy stored by a  $SiO_2$  capacitor and its related QV and CV relationship derived from the energy function. Value of capacitance is for 50  $\mu$ m square electrodes and 50 nm thickness.

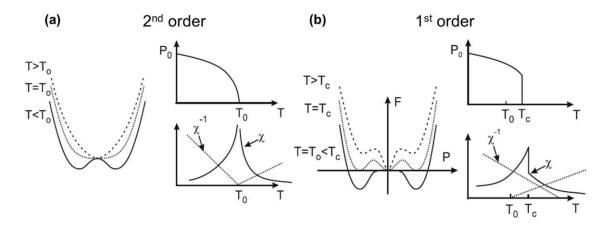

2.7: The impact on free energy, spontaneous polarization and dielectric susceptibility determined by the order of phase transition [34]. Second-order phase transition (a), first-order phase transition (b).

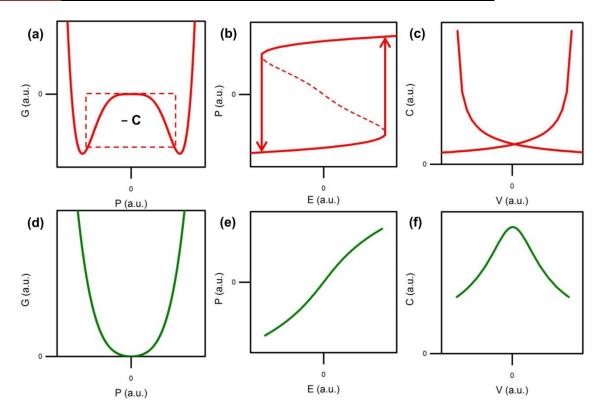

2.8: Simulated characteristics in BaTiO<sub>3</sub>, energy density (a), PE (b), CV (c) and in SrTiO<sub>3</sub>, energy density (d), PE (e), CV (f).

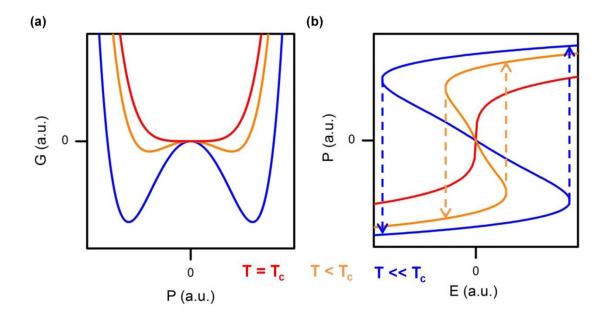

2.9: Simulated energy density (a) and related polarization as a function of electric field (b), at three temperatures, 100 K (T <<  $T_c$ ), 300 K (T <  $T_c$ ), 388 K (T =  $T_c$ ).

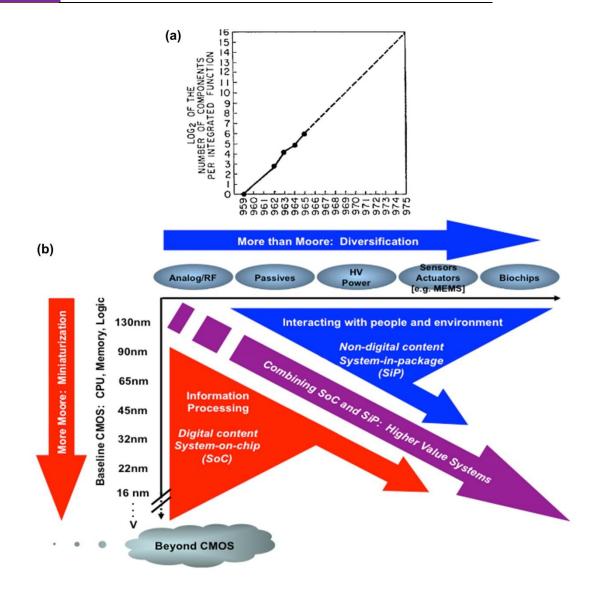

2.10: (a) The first account of Moore's law discussing the projection of the transistor as cramming more components onto an integrated circuit [42]. (b) An up-to-date view of the direction of the nanoelectronics industry featuring both scaling and diversification [43].

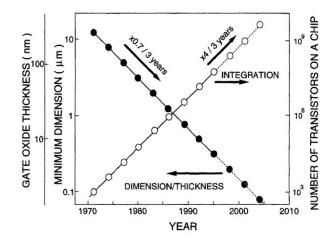

2.11: The historical trend of miniaturisation of the gate oxide thickness  $t_{ox}$  and gate length L. Also shown is the increase in the number of transistors on an IC into the modern day [47].

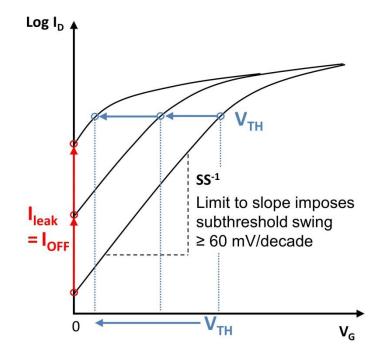

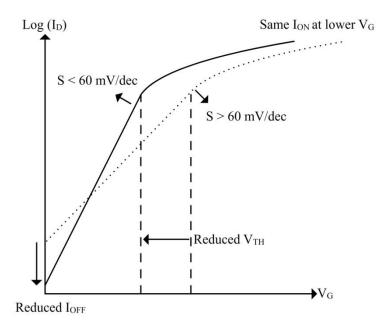

2.12: The subthreshold slope in a Si MOSFET. As the threshold voltage is reduced the leakage current in the off state is increased due to the limit of the slope.

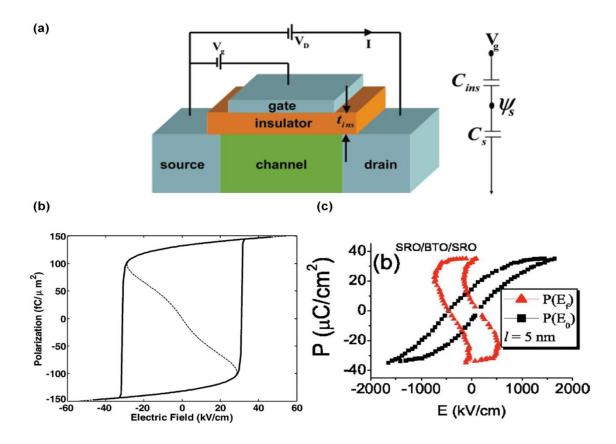

2.13: (a) Schematic of the MOSFET and its modelled series capacitance through the gate from equation 2.21 ( $C_{ins} = C_{ox}$ ) [10, 11]. (b) PE loop calculated from LD theory in comparison to that shown in figure 2.8 (b) showing a negative slope [10]. (c) 'Actual' PE loops, with field in the ferroelectric film  $E_f$  showing a negative slope [12].

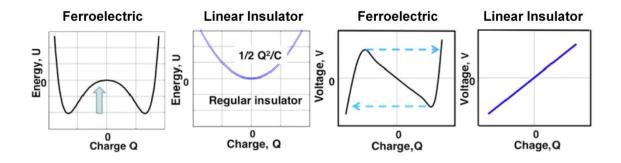

2.14: The energy functions in a ferroelectric and linear insulator and corresponding charge-voltage relationship [11].

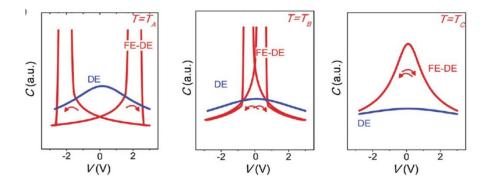

2.15: Simulations of capacitance from LD theory for a bilayer of  $Pb(Zr_{0.2}Ti_{0.8})O_3$  (FE) on  $SrTiO_3$  (DE) [54]. At temperatures  $T_A$  and  $T_B$  the instability of ferroelectric capacitance is shown (figure 2.8 (c)). However, at  $T_C$  the total capacitance of the bilayer is greater than the constituent positive layer.

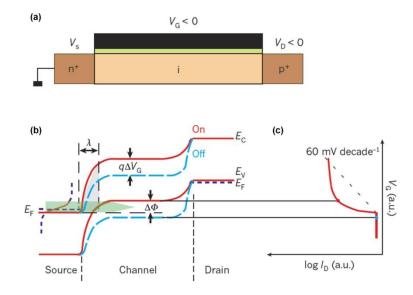

2.16: (a) A schematic of a TFET that is a gated p-i-n diode operating as a p - type transistor. Voltages of  $V_S$ ,  $V_G$ ,  $V_D$  are corresponding to standard MOSFETs but with different polarities. (b) Energy band diagram of the off (blue dash) and on (red line) state in the TFET.  $E_F$ ,  $E_C$ ,  $E_V$ , are the Fermi level, conduction and valence level, respectively. Applying a negative  $V_G$  allows the channel  $E_V$  to move above the source  $E_C$  to allow current to tunnel across the region shown by  $\Delta \Phi$ .  $\lambda$ represents tunnelling length. (c) The subthreshold slope is shown to be steeper for TFETs when compared to the linear dashed relationship for a MOSFET [56].

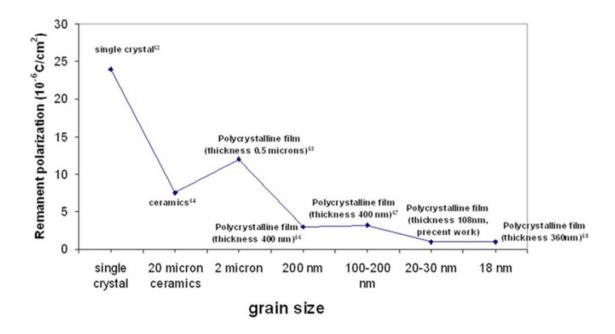

2.17: Remnant polarization in BaTiO<sub>3</sub> samples as a function of grain size [60].

#### Chapter 3

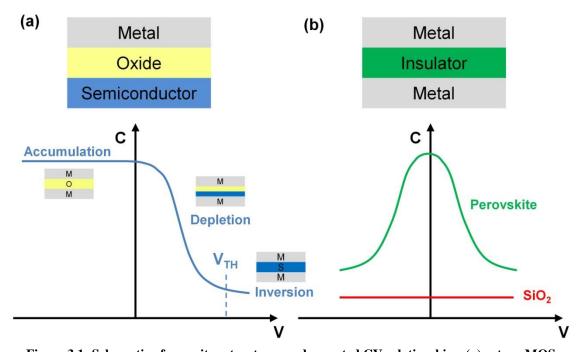

3.1: Schematic of capacitor structures and expected CV relationships. (a) p-type MOS capacitor with three operating regions of accumulation, where the oxide layer dominates; depletion, where the semiconductor capacitance acts in series with the oxide; inversion, where the semiconductor capacitance dominates due to largest depletion layer. This is for high frequency measurements where the inversion channel does not contribute to the capacitance. (b) MIM capacitor with either a linear (SiO<sub>2</sub>) or tunable (perovskite) insulator.

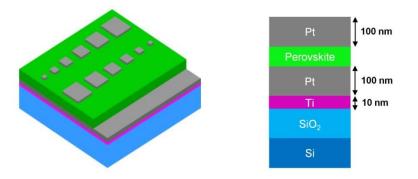

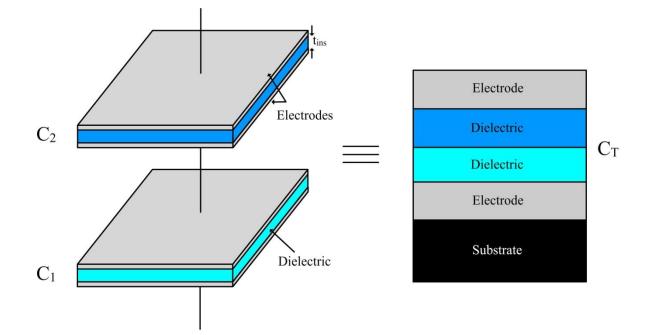

**3.2:** Schematic cross-section and full structure of the fabricated MIM capacitors. A thin section of the bottom Pt electrode is visible for contact with the probe.

**3.3:** Experimental setup for CV. (a) The probe station. (b) Image of the top and bottom electrodes on a MIM sample. (c) small-signal voltage applied to one device. (d) Example capacitance trend of a tunable perovskite.

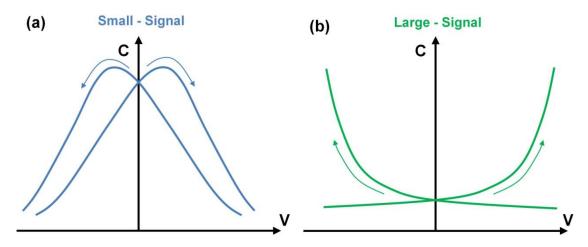

3.4: Capacitance trends measured using (a) a small - signal, (b) a large - signal.

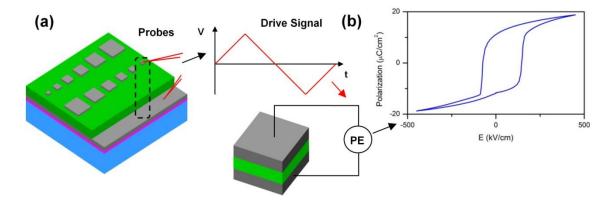

**3.5:** Experimental setup for PE. (a) Image of the top and bottom electrodes contacted by the probes with large-signal voltage applied to one device. (b) Example polarization response to an applied electric field in a ferroelectric.

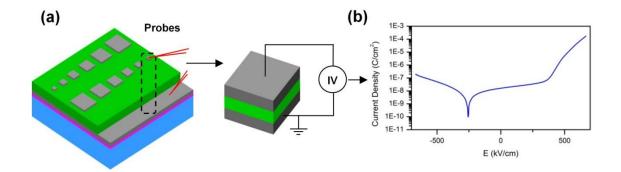

**3.6:** Experimental setup for IV. (a) Image of the top and bottom electrodes contacted by the probes with voltage applied to one device. (b) Example leakage current in a perovskite.

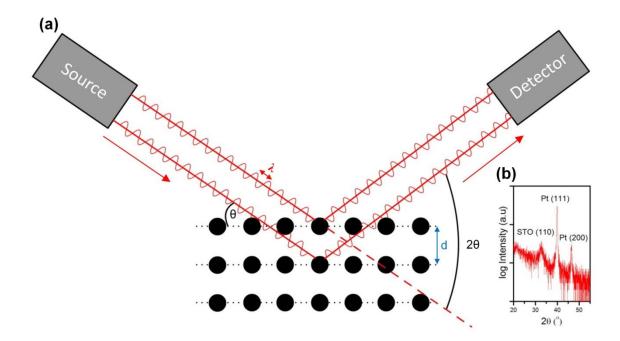

3.7: Experimental setup for XRD. (a) X-rays are incident onto a crystal plane and re-emitted from the atoms. The detector captures an interference pattern. (b) An example spectrum as the detector is moved about 20. Diffraction peaks are seen when constructive interference occurs as x-rays travel additional path lengths of  $n\lambda$ .

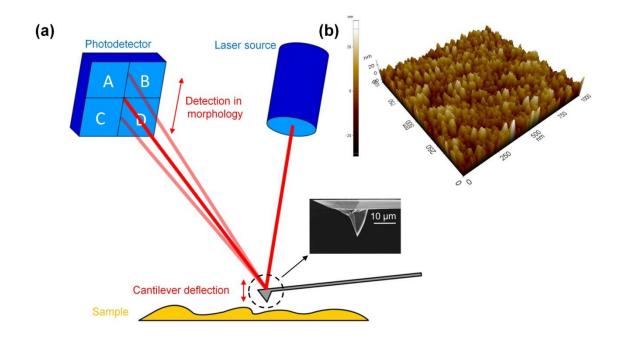

3.8: Illustration of the AFM experimentation. (a) A laser beam is directed towards the cantilever as it scans the surface of the sample. As the forces between the cantilever tip and sample surface interact the laser beam is deflected onto a photodiode. (b) Example surface scan using non-contact AFM.

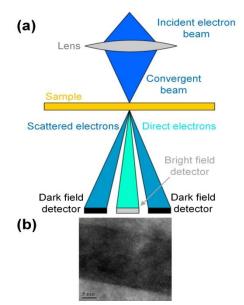

3.9: Illustration of the TEM experiment. (a) An incident beam is passed through a lens and electrons transmitted through the sample are interpreted as diffraction patterns or as an image. Bright field images use the direct electron beam, while dark field images are constructed from scattered electrons. (b) An example bright field image of a thin film.

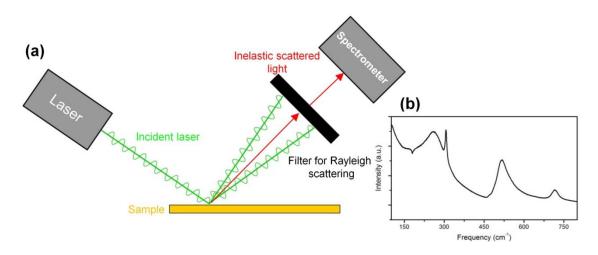

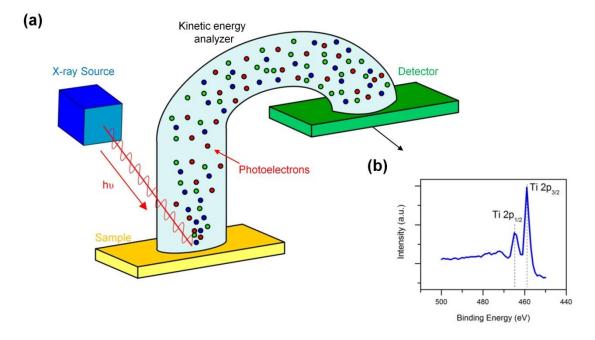

3.10: Illustration of the Raman spectroscopy setup. (a) Incident laser approaches sample and is reemitted into elastic and inelastic components. A Filter is used to remove any elastic scattered light and remaining contribution is detected by a spectrometer. (b) Example spectrum of  $BaTiO_3$ showing sharp peak at 300 cm<sup>-1</sup>. 3.11: Illustration of the XPS experimentation. (a) Incident x-rays promote electrons of different kinetic energies out of the sample under test. Detection occurs relating to the electron kinetic energy. (b) Example spectrum from the detector.

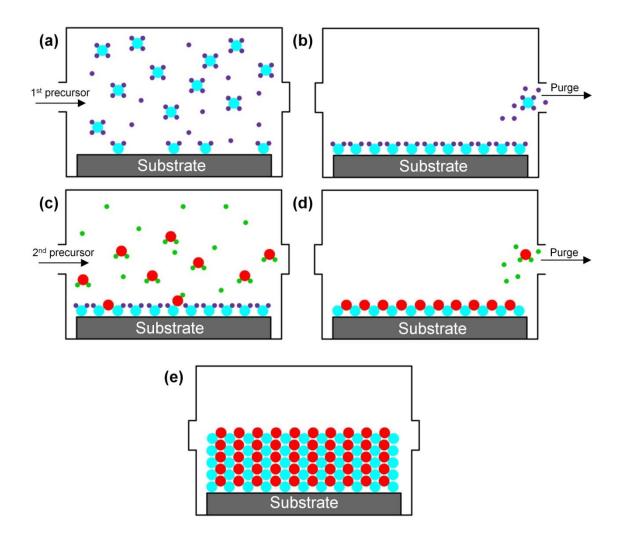

3.12: Schematic of the deposition process using ALD. (a) The initial precursor is introduced into the chamber. (b) Leftover precursor is purged from the chamber. (c) Second precursor is introduced into the chamber. (d) The chamber is purged of remaining precursor. (e) Steps (a) - (d) repeated until desired film thickness is grown.

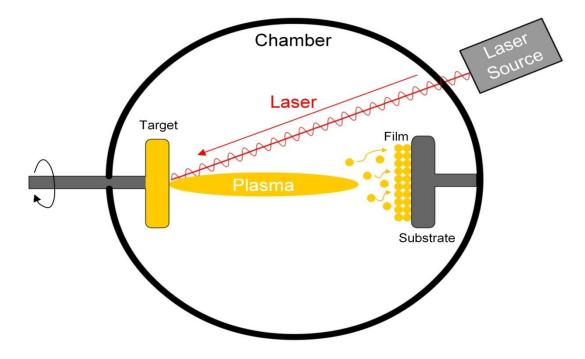

3.13: Schematic of the deposition process using PLD.

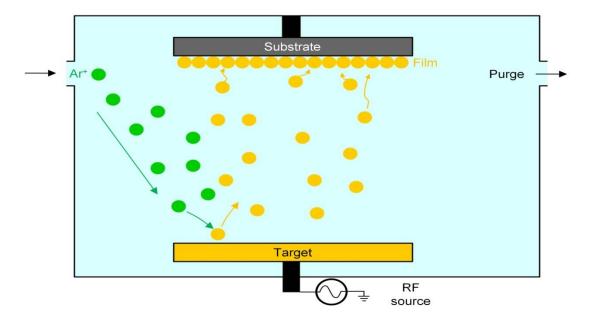

3.14: Schematic of the growth process using RF sputter deposition.

#### Chapter 4

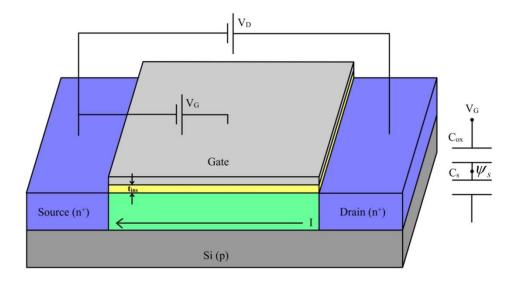

4.1: Illustration of a MOSFET under gate and drain bias voltage. Equivalent circuit shown as a series of the insulator and semiconductor capacitances with gate and surface potential.

4.2: Sketch of the subthreshold region in a MOSFET showing a steep < 60mV/dec and a standard > 60mV/dec slope.

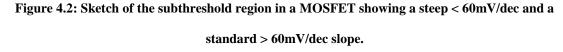

4.3: Polarization vs. electric field for  $BaTiO_3$  simulated using LD theory (equation 2.16). Negative capacitance region (red dashed negative slope) is situated around P = 0 and is not accessed due to instability. Material parameters were taken from reference 12.

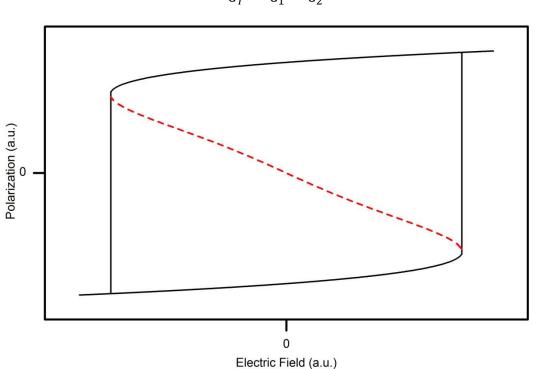

4.4: Series capacitance consisting of capacitors  $C_1$  and  $C_2$ . The equivalent MIM stack is shown as the total capacitance  $C_T$ .

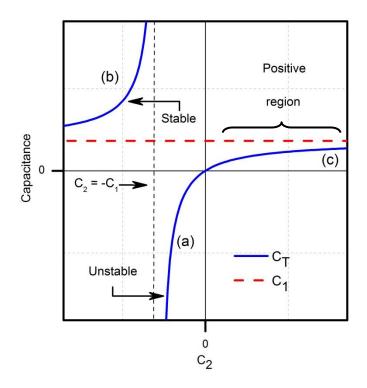

4.5: Series capacitances equation plotted as a function of capacitor  $C_2$ . When  $C_2$  is negative the total capacitance  $C_T$  is greater than  $C_1$ .

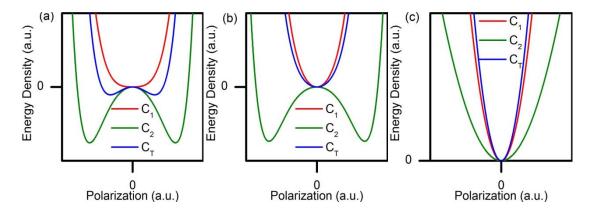

4.6: Simulated energy density at (a) 100 K, (b) 300 K, (c) 500 K. Shown is  $SrTiO_3$  as  $C_1$  at 25 nm,  $C_2$  BaTiO<sub>3</sub> at 50 nm and the bilayer capacitor  $C_T$  of  $SrTiO_3$  / BaTiO<sub>3</sub> at 25 nm / 50 nm.

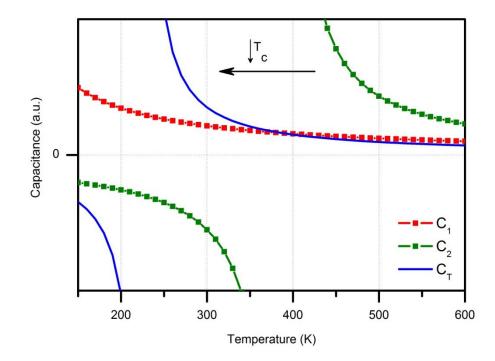

4.7: Capacitors  $C_1$ ,  $C_2$  and total capacitance  $C_T$  plotted as a function of temperature. At 300 K  $C_T$  is greater than  $C_1$  due to negative  $C_2$ .

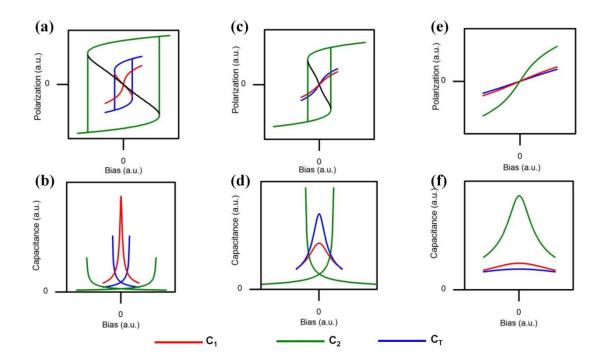

4.8: Simulated PV and CV at (a) (b) 100 K, (c) (d) 300 K, (e) (f) 500 K. Shown is the single  $SrTiO_3$  capacitor  $C_1$  at 25 nm, single  $BaTiO_3$  capacitor  $C_2$  at 50 nm, and the bilayer capacitor  $C_T$  of  $SrTiO_3$  /  $BaTiO_3$  at 25 nm / 50 nm.

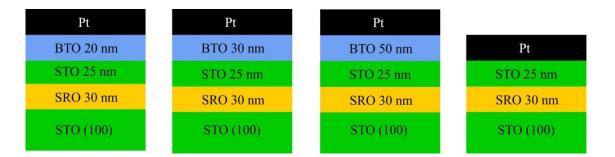

4.9: Schematic of the bilayers and test structure under investigation for negative capacitance.

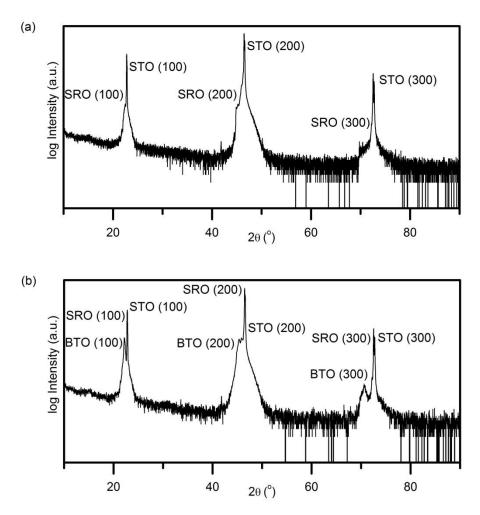

4.10: XRD spectra of (a) the single SrTiO<sub>3</sub> 25 nm and (b) bilayer SrTiO<sub>3</sub> / BaTiO<sub>3</sub> 25 nm / 50 nm capacitors.

4.11: XRD spectra of (a) the single  $SrTiO_3$  capacitor  $C_1$  (25 nm), (b) bilayer  $SrTiO_3$  /  $BaTiO_3$  (25 nm / 50 nm), (c) bilayer  $SrTiO_3$  /  $BaTiO_3$  (25 nm / 30 nm) and (d) bilayer  $SrTiO_3$  /  $BaTiO_3$  (25 nm / 20 nm) capacitors.

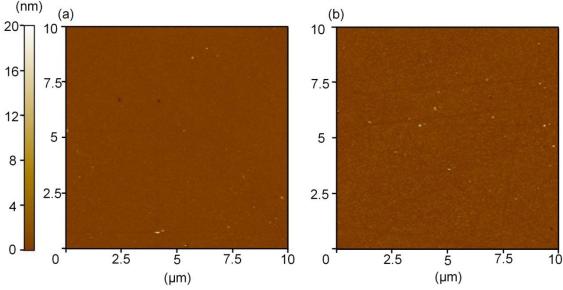

4.12: AFM topography images of the  $SrTiO_3$  (a) and  $SrTiO_3$  /  $BaTiO_3$  25 nm / 50 nm capacitors.

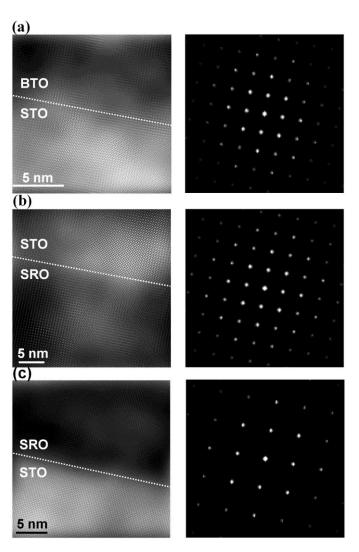

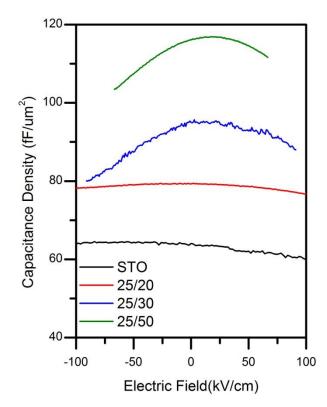

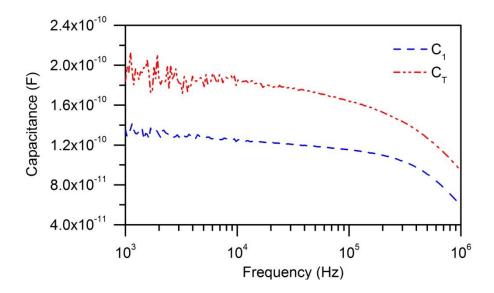

4.13: Bright field cross section of one the heterostructures under investigation at each interface. BaTiO<sub>3</sub>/SrTiO<sub>3</sub> film (a), SrTiO<sub>3</sub>/SrRuO<sub>3</sub> (b) and SrRuO<sub>3</sub>/SrTiO<sub>3</sub> (100) substrate (c). Dashed line shows interface between each thin film. Corresponding electron diffraction pattern is also shown indicating the single crystal nature. 4.14: Capacitance density measured in a single layer  $SrTiO_3$  capacitor at 25 nm thickness and three bilayer structures as a function of applied bias. The bilayers are combinations of  $SrTiO_3$  /  $BaTiO_3$  at 25 nm / 20 nm, 25 nm / 30 nm, 25 nm / 50 nm thicknesses.

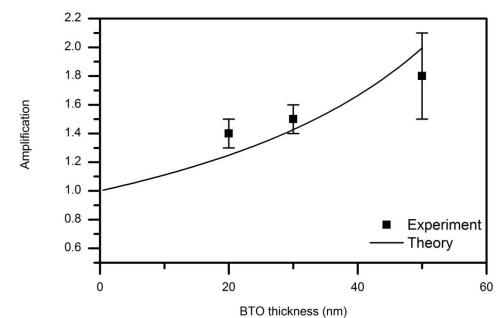

4.15: Amplification in each bilayer over the constituent  $SrTiO_3$  layer. Amplification is defined as  $C_T/C_1$ . Theory is simulated from equation 4.9 at room temperature, 25 °C.

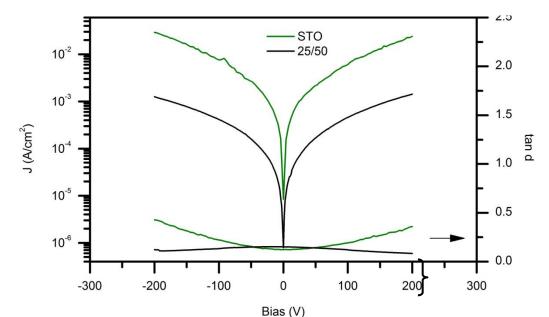

4.16: Current density and loss tangent as a function of applied bias in the 25 nm SrTiO<sub>3</sub> capacitor and the SrTiO<sub>3</sub> / BaTiO<sub>3</sub> 25 nm / 50 nm bilayer capacitor.

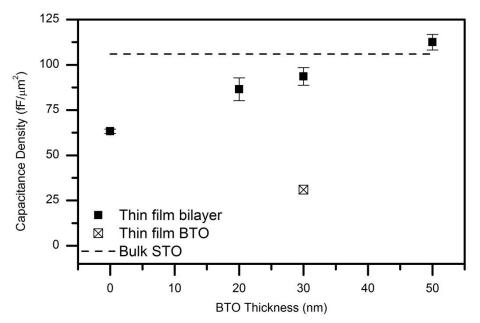

4.17: Capacitance density in the single 25 nm  $SrTiO_3$  capacitor and the three measured bilayers. At 30 nm an additional data point is shown representing the single  $BaTiO_3$  capacitor ( $C_2$ ) without a  $SrTiO_3$  layer. Theoretical capacitance density in single  $SrTiO_3$  capacitor is also shown.

4.18: Capacitance density measured at a function of frequency. The single 25 nm SrTiO<sub>3</sub> capacitor and 25 nm / 20 nm SrTiO<sub>3</sub> / BaTiO<sub>3</sub> bilayer are shown.

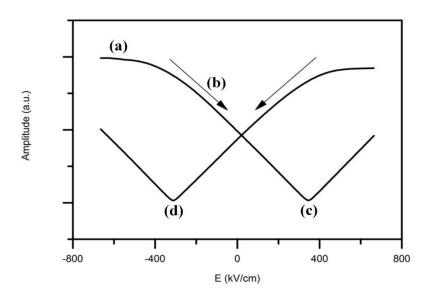

4.19: Amplitude of piezoresponse as a function of applied electric field. Arrows indicate the direction of applied electric field.

#### Chapter 5

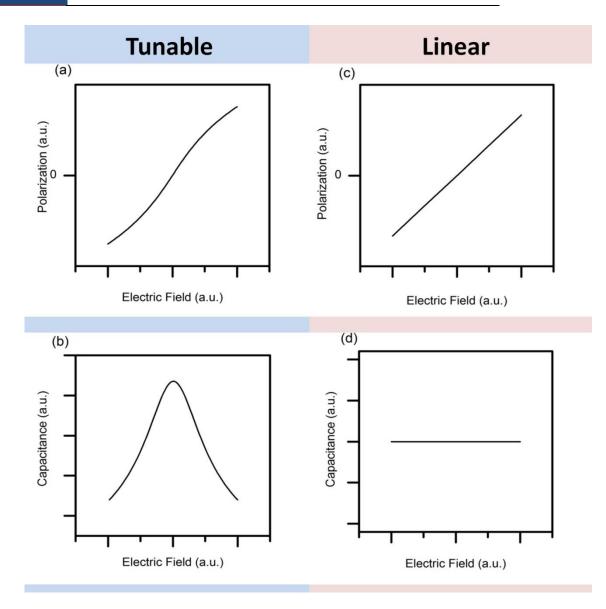

5.1: Polarization vs electric field curve for a tunable capacitor (a) and its corresponding tunable capacitance taken as dQ/dV (b). Linear polarization vs. bias for a typical dielectric (c) and corresponding bias independent capacitance (d).

5.2: XRD spectra of the STO films grown using PLD (a) at 500  $^{\circ}$ C and using ALD (b) and subsequent PDA at 500  $^{\circ}$ C.

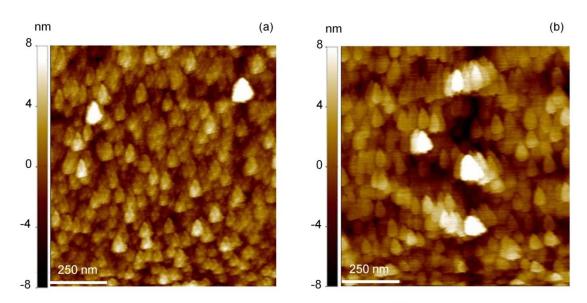

5.3: AFM images of the STO films grown using PLD at 500 °C (a), PLD at 700 °C (b) and using ALD at 250 °C and subsequently annealed using RTP for 120s in  $N_2$  at 600 °C (c).

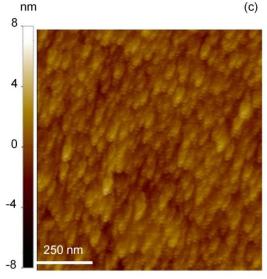

5.4: Bright-field TEM images of STO films grown using PLD at 500 °C. Cross-section of the STO thickness with example region shown for high resolution imaging (a), high resolution of the STO grains (b) and electron diffraction pattern (c). Also shown is the bright-field TEM image of STO grown at 700 °C indicated by the arrow. The schematic indicates the particular layer contrast in each image.

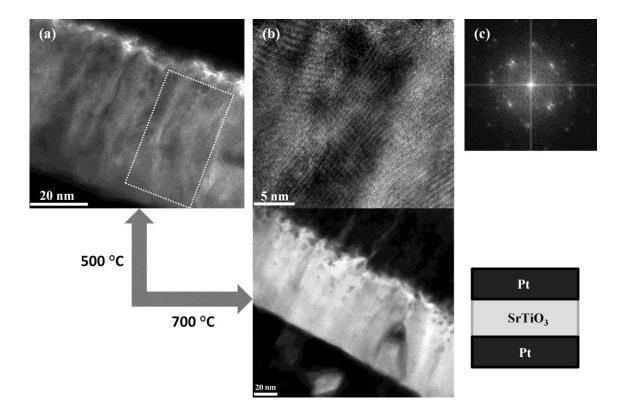

5.5: Bright-field TEM images of STO films grown using ALD and subsequently annealed at 600 °C. Cross-section of the STO thickness shown in (a) and high resolution image shown in (b). Inset is the electron diffraction pattern. Circled regions are nanocrystallites.

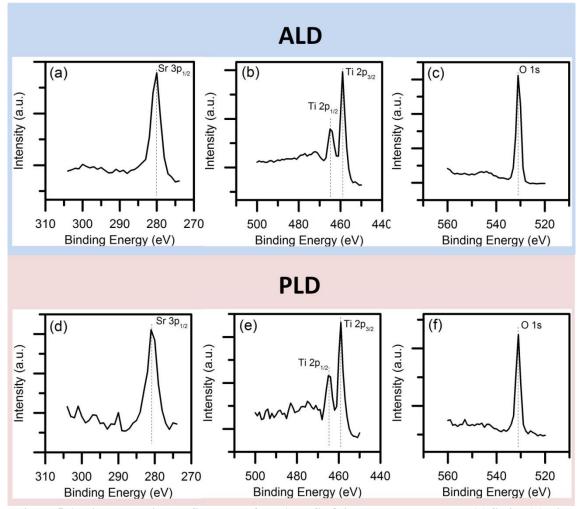

5.6: High resolution XPS spectra of the ALD STO in an as-grown phase: (a) Sr 3p, (b) Ti 2p, (c)

O 1s. XPS spectra of the PLD STO grown at 500 °C: (d) Sr 3p, (e) Ti 2p, (f) O 1s.

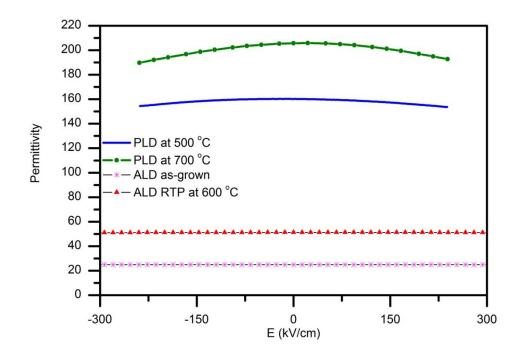

5.7: Permittivity measured in ALD and PLD SrTiO<sub>3</sub> films. The ALD film measured is as-grown and after RTP at 600 °C. The PLD film were grown at 500 °C and 700 °C.

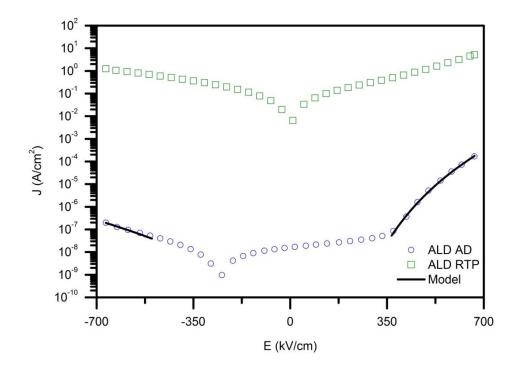

5.8: Leakage current density measured as a function of electric field in the SrTiO<sub>3</sub> film grown using ALD. The fitted model is described in [21].

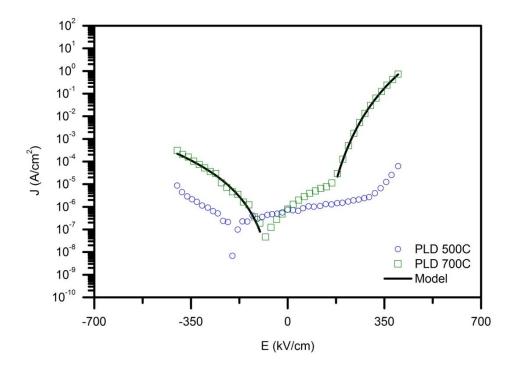

5.9: Leakage current density measured as a function of electric field in the SrTiO<sub>3</sub> films grown using PLD. The fitted model is described in [21].

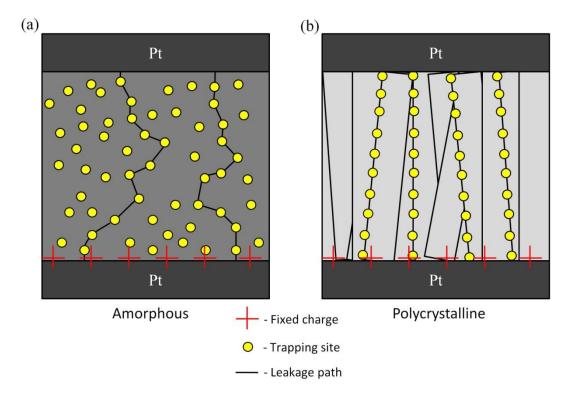

**5.10:** Schematic of leakage paths through trapping sites in the amorphous ALD film (a) and polycrystalline PLD film (b).

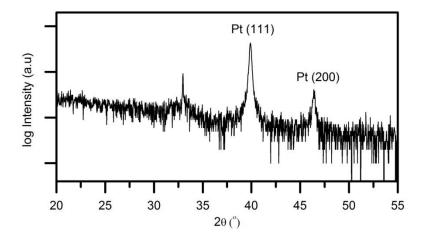

5.11: XRD spectrum of the BST film grown using PLD at 500 °C.

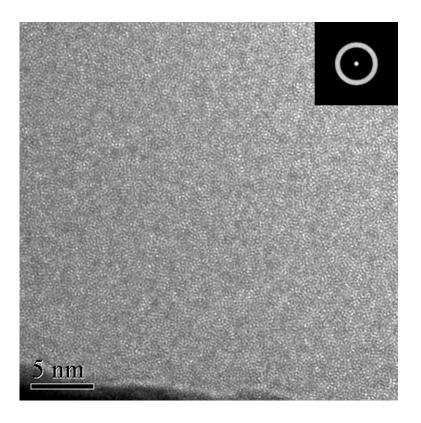

5.12: Bright-field TEM images of the BST film grown using PLD at 500 °C. Region shows high resolution region of BST. Inset shows the electron diffraction pattern.

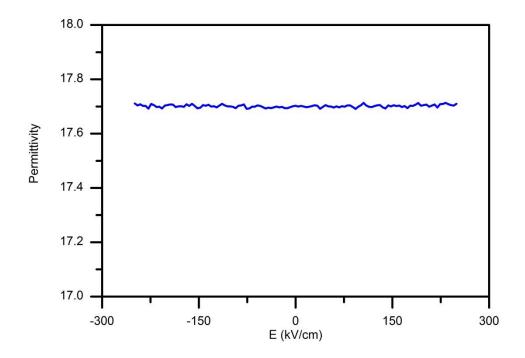

5.13: Permittivity measured in the Ba<sub>0.8</sub>Sr<sub>0.2</sub>TiO<sub>3</sub> film grown using PLD at 500 °C.

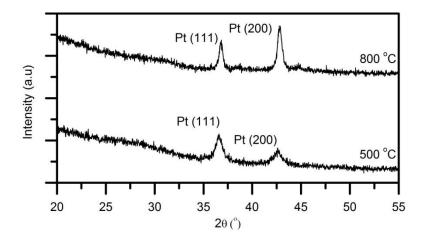

5.15: XRD spectra of BTO grown using sputter deposition at room temperature and post annealed at either 500 °C or 800 °C.

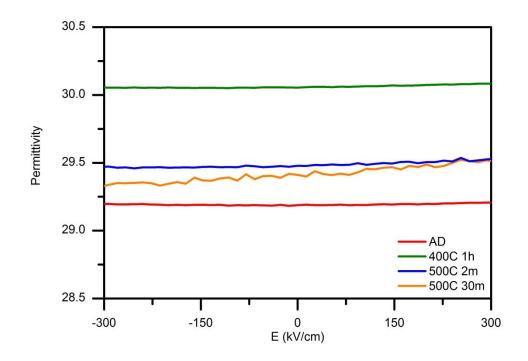

5.16: Permittivity measured in the sputter deposited BaTiO<sub>3</sub> film after different annealing schedules.

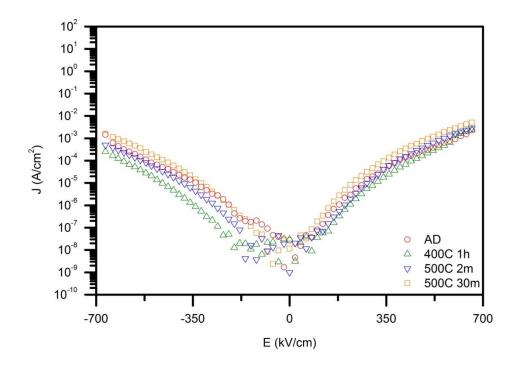

5.17: Leakage current density measured as a function of electric field in the sputter deposited BaTiO<sub>3</sub> film after different annealing schedules.

#### Chapter 6

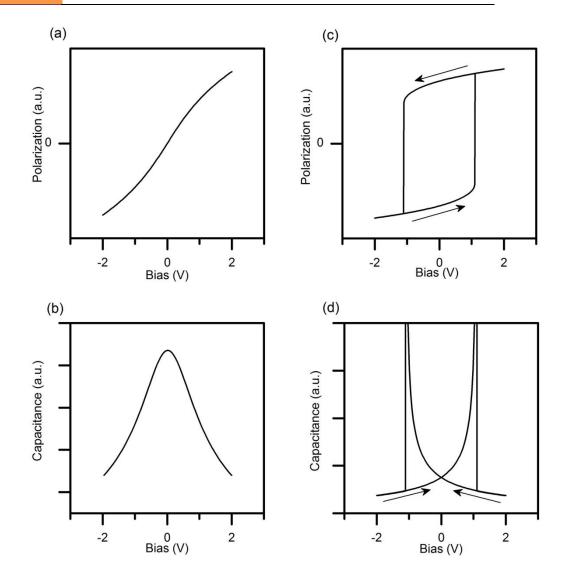

6.1: Polarization vs bias curve for a paraelectric capacitor (a) and its corresponding tunable capacitance taken as dQ/dV (b). Hysteretic polarization vs. bias for a ferroelectric (c) and corresponding capacitance, showing the instability at the switching field for this ideal case (d).

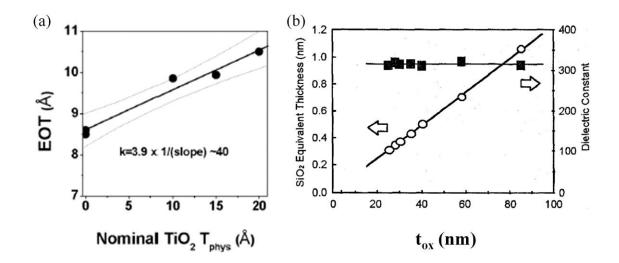

6.2: EOT vs. physical dielectric thickness t<sub>ox</sub>. Data is taken for (a) from ref. 31 and (b) ref. 49.

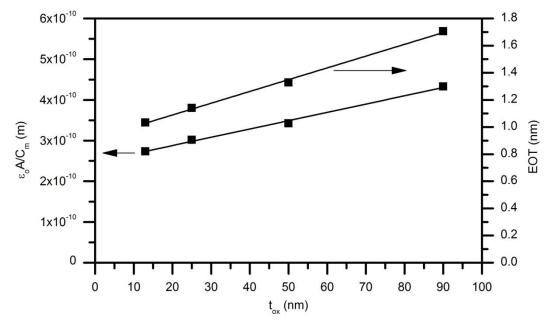

6.3: Series capacitance model and EOT vs. physical dielectric thickness, t<sub>ox</sub>. Measured data was on STO MIM capacitors deposited using PLD.

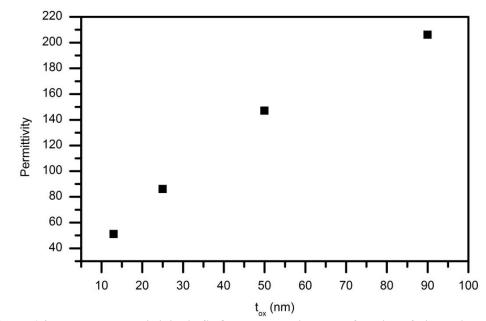

6.4: Measured permittivity in STO MIM capacitors as a function of dielectric thickness.

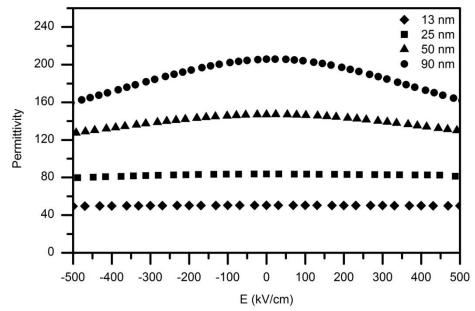

6.5: Measured permittivity in STO MIM capacitors as a function of applied electric field E and thickness of SrTiO<sub>3</sub>.

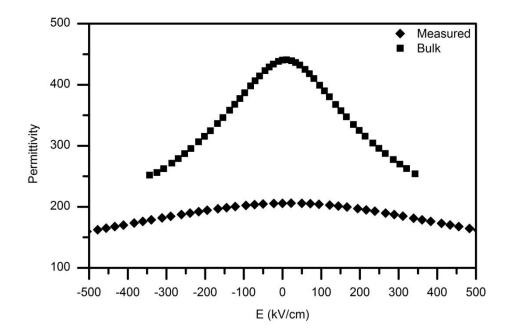

6.6: Bulk and measured permittivity vs. electric field in the 90 nm STO film, showing the influence of the interfacial layer capacitances.

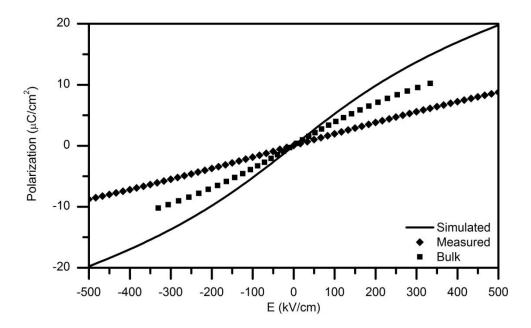

6.7: Bulk and measured permittivity vs. electric field in the 90 nm STO film, showing the influence of the interfacial layer capacitances.

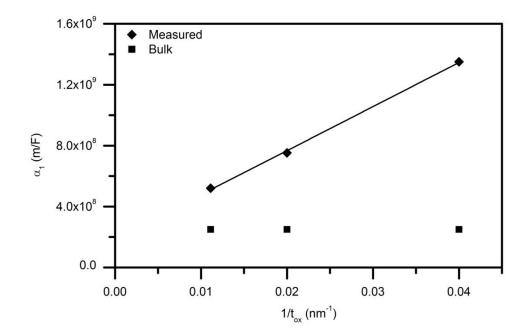

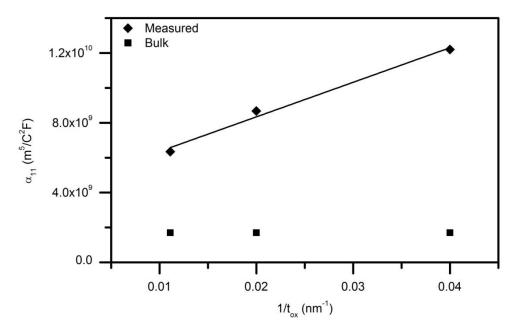

6.8: Linear dielectric stiffness coefficient extracted using a best fit of equation 6.16 in figure 6.7 of the measured polarization (diamond) and expected bulk value of linear coefficient using  $\alpha = 1/\epsilon$  (square).

6.9: Nonlinear dielectric stiffness coefficient extracted using a best fit of equation 6.16 in figure 6.7 of the measured polarization (diamond) and expected bulk value of nonlinear coefficient taken from ref. 62 (square).

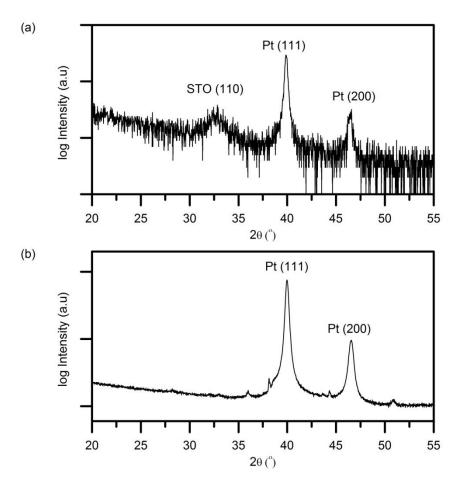

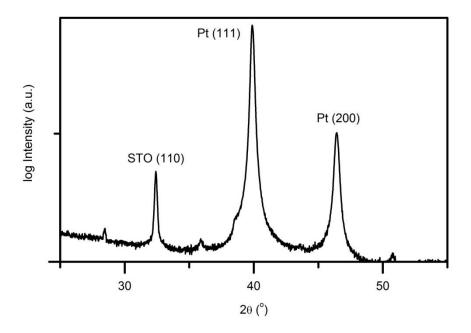

6.10: XRD spectrum of the 90 nm STO film. Peaks shown are attributed to the (110) perovskite phase for STO and (111), (200) of the Pt layer.

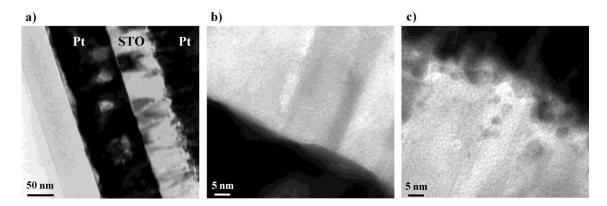

6.11: TEM a) 90 nm MIM capacitor. From the left of the image: Si/SiO<sub>2</sub>/Ti/Pt/STO/Pt. Dark contrasts are the facets of the individual growth columns of SrTiO<sub>3</sub>. b) Bottom Pt/ STO interface.

c) Top STO/Pt interface.

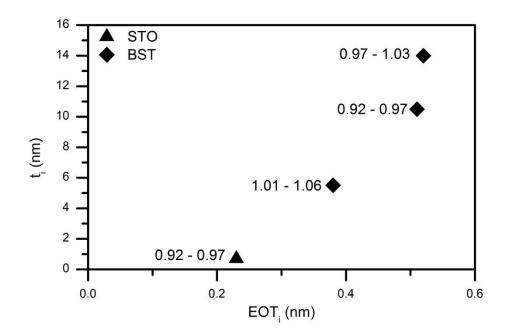

6.12: Extracted interface thickness as a function of interface  $EOT_i$  using equation 6.7 with data taken from ref. 24. Diamonds are  $Ba_xSr_{1-x}TiO_3$ , x=0.7 and triangle indicates STO. Numbers indicate elemental composition as Gr II/Ti ratio.

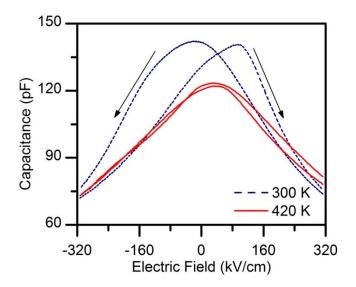

6.13: Capacitance-voltage measured on the Pt/BaTiO<sub>3</sub> (160 nm)/Pt capacitor at 300 K and 420 K. Electric field is taken as  $V/t_{ox}$ , where  $t_{ox}$  is the thickness of the BaTiO<sub>3</sub> film.

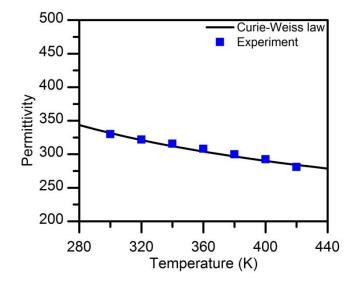

6.14: Permittivity measured on the  $Pt/BaTiO_3$  (160 nm)/Pt capacitor as a function of increasing temperature. Permittivity is extracted from the parallel-plate capacitor relationship. The Curie-Weiss law in equation 6.1 is fitted to the experimental data.

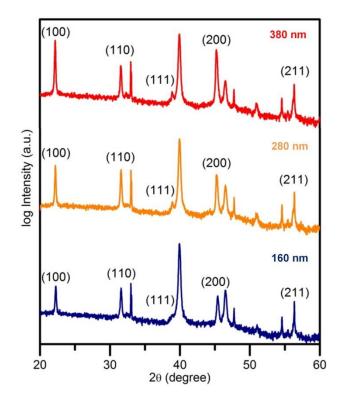

6.15: XRD spectra of the BTO films with varying film thickness. Orientations of BTO are labelled with remaining contributions originating from Si or Pt.

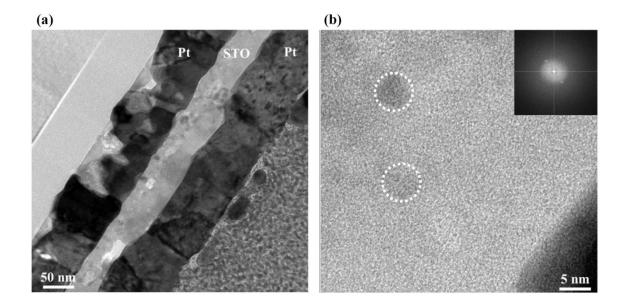

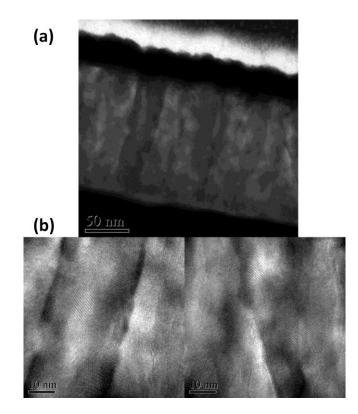

6.16: TEM imagine of the 160 nm thick BTO sample. (a) Image shows the cross section of the full film thickness situated between the dark contrasting Pt electrodes. (b) Images show high resolution TEM highlighting individual columns.

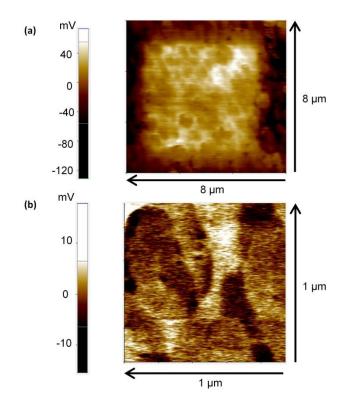

6.17: EFM image of polycrystalline BTO at 160 nm thick (a). BTO is non-uniformly polarized. High resolution scan shows that it is a mixture of polarizable and non-polarizable domains (b).

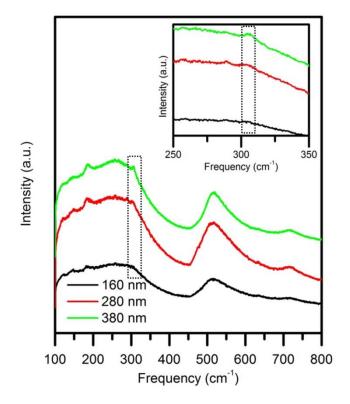

6.18: Raman spectra of polycrystalline BTO as a function of increasing thickness. Dashed region shows BTO has a reduced peak intensity around 300 cm<sup>-1</sup> indicating presence of both cubic and tetragonal phases. Inset highlights that the peak intensity at 300 cm<sup>-1</sup> increases with increasing film thickness.

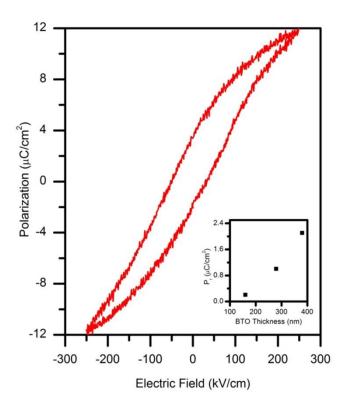

6.19: Large signal hysteresis measurements of the 380 nm thick BTO film. Inset shows the measured remnant polarization as a function of film thickness.

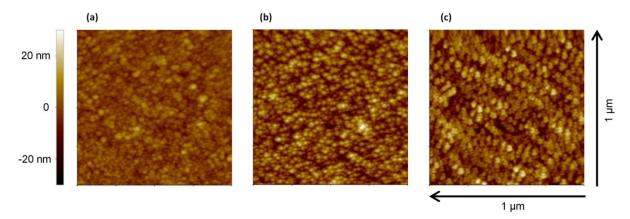

6.20: AFM topography scans of the 160 nm (a), 280 nm (b) and 380 nm (c) thick films.

#### Chapter 7

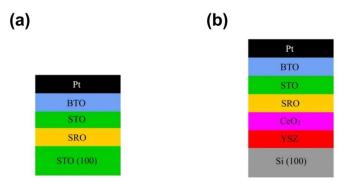

7.1: (a) Cross-section of the MIM bilayer from chapter 4. (b) The proposed bilayer with a Si substrate. An additional yttria-stabilised zirconia layer is incorporated into the design in order to epitaxially grow perovskite films on Si substrates [2].

# List of Tables

#### Chapter 2

2.1: Scaling rules for device miniaturisation to keep the electric field constant.

#### Chapter 3

3.1: Measured resistivity of the three electrodes used for the MIM capacitors. Values were calculated using 4 - probe sheet resistance measurements and known thicknesses of the films.

#### Chapter 5

5.1: The calculated atomic percentages of Sr, Ti, O, in the as-grown ALD film and PLD grown film at 500 °C. Values were extracted from the high resolution XPS spectra in figure 5.6.

5.2: The calculated barrier heights from the leakage current in the film grown using ALD from figure 5.8 and in the film grown using PLD at 700 °C from figure 5.9.

#### Chapter 6

6.1: Average permittivity, measured EOT and tunability across the 4 thicknesses of STO.

# Abbreviations

| AFM                        | Atomic Force Microscopy                                                                                        |

|----------------------------|----------------------------------------------------------------------------------------------------------------|

| ALD                        | Atomic Layer Deposition                                                                                        |

| BEOL                       | Back-End-Of-Line                                                                                               |

| BST                        | Barium Strontium Titanate                                                                                      |

| BTO                        | Barium Titanate                                                                                                |

| CMOS                       | Complementary Metal Oxide Semiconductor                                                                        |

| CV                         | Capacitance - Voltage                                                                                          |

| CVD                        | Chemical Vapour Deposition                                                                                     |

|                            |                                                                                                                |

| DC                         | Direct Current                                                                                                 |

| DC<br>DRAM                 | Direct Current<br>Dynamic Random Access Memory                                                                 |

|                            |                                                                                                                |

| DRAM                       | Dynamic Random Access Memory                                                                                   |

| DRAM<br>EFM                | Dynamic Random Access Memory<br>Electrostatic Force Microscopy                                                 |

| DRAM<br>EFM<br>FEOL        | Dynamic Random Access Memory<br>Electrostatic Force Microscopy<br>Front-End-Of-Line                            |

| DRAM<br>EFM<br>FEOL<br>FET | Dynamic Random Access Memory<br>Electrostatic Force Microscopy<br>Front-End-Of-Line<br>Field Effect Transistor |

| IV     | Current-Voltage                                   |

|--------|---------------------------------------------------|

| LD     | Landau-Devonshire                                 |

| MIM    | Metal-Insulator-Metal                             |

| MOS    | Metal Oxide Semiconductor                         |

| MOSFET | Metal Oxide Semiconductor Field Effect Transistor |

| PE     | Polarization – Electric Field                     |

| PFM    | Piezoresponse Force Microscopy                    |

| PLD    | Pulsed Laser Deposition                           |

| PV     | Polarization-Bias                                 |

| PVD    | Physical Vapour Deposition                        |

| PZT    | Lead Zirconate Titanate                           |

| QV     | Charge-Voltage                                    |

| RF     | Radio Frequency                                   |

| RT     | Room Temperature                                  |

| RTP    | Rapid Thermal Processing                          |

| SiP    | System-in-Package                                 |

| SoC    | System-on-Chip                                    |

| SRAM   | Static Random Access Memory                       |

| SRO    | Strontium Ruthenate                               |

| SS   | Subthreshold Swing               |

|------|----------------------------------|

| STO  | Strontium Titanate               |

| TEM  | Transmission Electron Microscopy |

| ULSI | Ultra Large Scale Integration    |

| XPS  | X-Ray Photoelectron Spectroscopy |

| XRD  | X-Ray Diffraction                |

| YSZ  | Yttria-Stabilised Zirconia       |

### Introduction, Research Aims and Hypotheses

#### **1.1 Introduction**

In the past six decades, metal oxide semiconductor field effect transistors (MOSFETs) have shrunk in order to supply the demand for ever increasing circuit speeds. With the introduction of complementary metal oxide semiconductor (CMOS) technology, and the scaling of the MOSFET channel length from 1  $\mu$ m to 22 nm, the CMOS industry is now into the nanoelectronics era. Transistor scaling is in adherence with Moore's law, who predicted that the number of transistors on a chip will double approximately every 18 - 24 months [1]. It is now commonplace to have upwards of billions of devices on a chip, which is at the heart of the expansion of the digital age. In the modern day, a shift has emerged where the pursuit of increasing the functionality of a circuit (more than Moore) is just as important as the scaling (more Moore).

As the MOSFET is scaled, in keeping with the more Moore agenda, the voltage supply, as well as the gate oxide thickness is also reduced [2]. A decreasing operating voltage may be beneficial for better power consumption, but problems arise when threshold voltages are too large, inhibiting the total drive current produced by the MOSFET. Furthermore, the gate oxide thickness, traditionally consisting of SiO<sub>2</sub>, became a major issue as it reached its fundamental level in the 1990s at dimensions < 2 nm [3]. At this length scale, quantum mechanical tunnelling becomes a major factor as charge stored on the gate of the MOSFET tunnels through the thin insulator.

The difficulty in fulfilling the more than Moore agenda arises due to the limited functionality of conventional materials such as  $SiO_2$ . Silica offers very little capacitance density due to its inherent low permittivity. In addition, its capacitance stays constant when the applied voltage increases.

For both scaling and increasing circuit functionality, the incorporation of new materials has been proposed and executed. Scaling was furthered by replacing the silica gate oxide with a high dielectric constant (high- $\kappa$ ) material [4]. In doing so, the gate capacitance is allowed to stay at high densities with thicker film dimensions. This acts to mitigate some of the quantum mechanical effects and reduce the overall leakage of charge. Capacitors are also vital components in many circuit applications, but are relatively large. High- $\kappa$  materials may also be used to offset any reduction in capacitance when the electrode area of these devices is reduced in the process of miniaturisation.

In order to achieve greater circuit functionality, materials with tunable capacitance are proposed [5]. This specific electrical characteristic of a material allows the capacitance to shift as a function of the applied voltage or electric field. Capacitance will be at a maximum at zero field, and decrease as the electric field across the insulator

is increased. The property is described through a voltage dependent permittivity, in contrast to that in silica which stays constant over the applied voltage. Applications of such a material are for hand held electronic components in microwave devices and tunable filters, among many others.

For both the aforementioned goals to increase circuit performance, perovskites offer both the high- $\kappa$ , tunable characteristics for more than Moore, and the possibility of utilising negative capacitance for the more Moore agenda. The permittivity achieved in perovskite material can be three orders of magnitude greater than that in conventional insulators, which may act to shrink the large capacitance elements of an integrated circuit. Its tunable permittivity is also of keen interest for the applications mentioned above. However, perovskite thin films are known to be affected by "dead layers" which inhibit the achieved permittivity at zero bias [6-8]. Thin film forms of perovskites may therefore be limited in terms of the quality of the deposited film.

Recently, negative capacitance has been proposed in thin film ferroelectrics [9, 10]. If a ferroelectric with negative capacitance can be placed into the gate stack of a MOSFET, the required gate voltage to switch the transistor on would be lowered. This is described due to a reduction in the subthreshold swing, in which a fundamental limitation of  $\geq$  60 mV/dec is currently required in order to increase the drain current by an order of magnitude. The MOSFET will then achieve the same value of drive current at lower voltages. In this regard, the overall power dissipation of the chip will be reduced, leading to greater transistor packing densities and furthering the more than Moore technology track. Negative capacitance may also lead to more powerful single core processors which previously generated too much heat, causing a necessity to move to multicore processors. However, experimental evidence of negative capacitance in barium titanate, particularly at room temperature, has never been observed. This is

critical if the material is to be used in current state-of-the-art transistors incorporated with Si.

#### **1.2 Research Objectives and Hypotheses**

The overall goal of this thesis is to investigate the characteristics of thin film perovskites for the nanoelectronics industry. Since Si is the workhorse material in most electronic devices, nanometer scale perovskite thin films grown on Si are an important advancement. A range of deposition techniques and growth parameters must be used and understood if the films are to be grown at a high standard. Use of a variety of characterisation techniques is also essential in order to assess the quality of the grown films. High quality perovskite thin films that offer a wide variety of characteristics is therefore a general aim of the thesis.

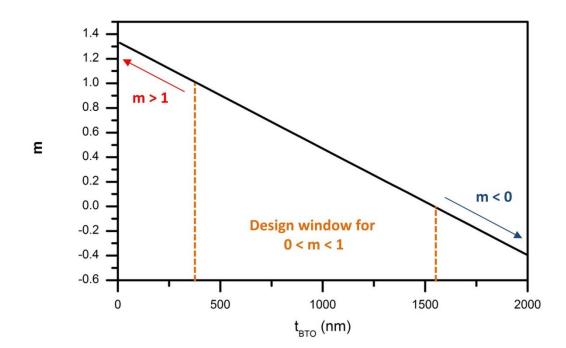

The key property of ferroelectric negative capacitance is investigated in thin film barium titanate, and a model is used to show its existence at room temperature. The model involves a series capacitance system of a positive and negative contribution, as negative capacitance under normal circumstances is unstable. It is shown that negative capacitance is stabilised, resulting in an overall enhancement of the total capacitance, which would never be observed in a standard series configuration of two positive capacitors. The model is developed using Landau theory for ferroelectrics, and guidelines for the designs are presented.

For high density capacitors integrated in the back-end of an integrated circuit, growth temperature is of critical importance. At a temperature exceeding 500 °C, high resistive silicide phases, such as NiSi<sub>2</sub>, can be created and disrupt circuit performance. As such, growing high quality ferroelectric thin films at 500 °C or below is a key issue if the films are to be incorporated with Si chips in the back-end-of-line. In contrast, front-end-of-line processes can be deposited at temperatures greater than 1000 °C, and is where a negative capacitive layer would be situated. There is a lack of evidence in the literature that addresses low temperature deposition of ferroelectric films, with the

#### Chapter 1 INTRODUCTION, RESEARCH AIMS AND HYPOTHESES

majority of studies focusing on high temperature growth. Investigation into the perovskites, strontium titanate, barium titanate and barium strontium titanate are shown using three different growth methods. The results indicate that growth technique, as well as thermal treatment with regards to annealing or temperature during growth, is important when film crystallisation is required. The results also show that the concentration of Ba impacts the crystallisation temperature considerably. In order to achieve thin films with high- $\kappa$  and tunable characteristics, strontium titanate grown at 500 °C using pulsed laser deposition (PLD) is the most successful technique applied.

Calculating the equivalent oxide thickness (EOT) is a well-known method for gauging the effectiveness of a high- $\kappa$  material, but problems may arise in the analysis if interfacial layers are apparent. It is shown that the standard equation for EOT is unsuitable if such an interfacial capacitance is in series with the desired insulator. The EOT model is developed to take into account any double layer capacitances that may arise in MOS gate stacks, and is shown to be suitable for calculating the thickness of the interfacial layer. The results are similar to that of dead layers affecting high- $\kappa$  perovskites, and the model is applied in order to calculate the actual thickness of dead layers acting upon strontium titanate capacitors integrated with Si. Further analysis is shown using high-resolution electron imaging of the metal-insulator-metal (MIM) interfaces. The tunable capacitance of the strontium titanate film is investigated in terms of the effective dead layers.

Finally, high temperature growth of barium titanate using PLD and integrated on Si substrates was investigated in terms of its retainable polarization and hysteresis. The ferroelectric properties of barium titanate integrated with Si substrates are important if the material is to be used as a negative capacitive layer. It was found that the achieved remnant polarization is minimal at the film thicknesses and temperatures studied. Further analysis using a range of electrical and material experiments supports a hypothesis of a mixed phase relationship in the polycrystalline barium titanate films, where a cubic phase is dominating. The cubic unit cell of a perovskite is responsible for the paraelectric phase, and as such lacks the ability to retain polarization. The inherent lack of polarization retention and switching negates the films to be used as a negative capacitance layer.

A summary of the main hypotheses of this thesis is presented below:

- Barium titanate displays effective negative capacitance. If the perovskite is stabilised in a series capacitance system, the total capacitance of the bilayer is larger than the constituent positive capacitance in the series.

- 2. Perovskite insulators may be crystallised at 500 °C for the purpose of back-end integrated circuitry.

- A physical layer of 'dead' material is evident in high-κ nanocapacitors. The dead layer will exhibit contrasting regions from the bulk of the perovskite in high resolution imaging.

- 4. Barium titanate films integrated with Si substrates achieve remnant polarization in the order of  $\ge 10 \ \mu\text{C/cm}^2$ .

- 5. A barium titanate thin film integrated with a Si substrate is affected by the size driven phase transition, which is known to impact bulk ferroelectric material.

The above hypotheses will be studied in chapters 4 through 6, and conclusions will be drawn in chapter 7.

Ferroelectrics are discussed in chapter 2, with particular attention placed upon Landau theory for the designs of negative capacitance stabilisation in bilayer structures. Chapter 3 will turn the attention to the fabrication methods and structures that were used in order to study thin film perovskites. The three main deposition techniques were sputter, pulsed laser and atomic layer deposition. The characterisation techniques are also explored.

In chapter 4 evidence for negative capacitance in barium titanate at room temperature is presented. It offers the first experimental observation of this phenomenon in barium titanate at room temperature.

Chapter 5 explores low temperature deposition of strontium and barium strontium titanate films grown using PLD for integration with Si. In addition, strontium titanate is investigated using atomic layer deposition and low temperature rapid thermal processing. Pure barium titanate is also discussed in terms of sputter deposition and post deposition annealing.

Chapter 6 studies the EOT of high- $\kappa$  films, which is developed to take into account any unwanted interfacial layers created in the thermal treatment of a capacitance structure. The model is then used to investigate dead layers in high- $\kappa$ perovskites, and a thickness is calculated for the dead layer. High temperature growth of barium titanate on Si substrates is investigated in terms of the displayed ferroelectricity. Finally, chapter 7 concludes and summarises the study, and suggests future work.

## **1.3 References**

- [1] G. E. Moore, "Cramming more components onto integrated circuits," *Electronics*, vol. 38, 1965.

- [2] Y. Taur, "CMOS design near the limit of scaling," *J. Res. & Dev.*, vol. 46, 2002.

- [3] T. Yuan, D. A. Buchanan, C. Wei, D. J. Frank, K. E. Ismail, L. Shih-Hsien, *et al.*, "CMOS scaling into the nanometer regime," *Proceedings of the IEEE*, vol. 85, pp. 486-504, 1997.

- [4] A. I. Kingon, J.-P. Maria, and S. K. Streiffer, "Alternative dielectrics to silicon dioxide for memory and logic devices," *Nature*, vol. 406, 2000.

- [5] A. K. Tagantsev, V. O. Sherman, K. F. Astafiev, J. Venkatesh, and N. Setter, "Ferroelectric Materials for Microwave Tunable Applications," *Journal of Electroceramics*, vol. 11, 2003.

- [6] K. C. Sekhar, *et al.*, "Thickness-dependent tunable characteristics of (Ba<sub>0.5</sub>Sr<sub>0.5</sub>)<sub>0.925</sub>K<sub>0.075</sub>TiO<sub>3</sub> thin films prepared by pulsed laser deposition," *Current Applied Physics*, 2011.

- [7] C. Basceris, S. K. Streiffer, A. I. Kingon, and R. Waser, "The dielectric response as a function of temperature and film thickness of fiber-textured (Ba,Sr)TiO<sub>3</sub> thin films grown by chemical vapor deposition," *J. Appl. Phys.* vol. 82, 1997.

- [8] L. J. Sinnamon, R. M. Bowman, J. M. Gregg, "Investigation of dead-layer thickness in SrRuO<sub>3</sub>/Ba<sub>0.5</sub>Sr<sub>0.5</sub>TiO<sub>3</sub>/Au thin-film capacitors," *Appl. Phys. Lett.* vol. 78, 2001.

- [9] S. Salahuddin, and S. Datta, "Use of Negative Capacitance to Provide Voltage Amplification for Low Power Nanoscale Devices," *Nano Lett.* vol. 8, 2008.

- [10] S. Salahuddin, and S. Datta, "Can the subthreshold swing in a classic FET be lowered below 60 mV/decade?," Proceedings of IEEE Electron Devices Meeting (IEDM), 2008.

## Chapter 2

# Ferroelectrics and their Incorporation into the Si Industry

## 2.1 Introduction

Well before the discovery of ferroelectrics, pyroelectric, and following this piezoelectric, material were known and understood [1]. Pyroelectricity is the phenomenon of a material to possess a temperature dependent spontaneous electric dipole moment, while piezoelectricity generates dipole moments under the application of strain. Following this in 1920, Valasek discovered the first ferroelectric known as Rochelle salt. The key property defining the ferroelectric material over both piezo and pyroelectricity is the ability to reverse the direction of the electric dipole moment with the application of an electric field [2]. However, ferroelectrics remained simply a curiosity for study until the discovery of the more robust perovskite oxide barium titanate (BaTiO<sub>3</sub>) in 1943 [3]. The simplified structure of this material allowed a

detailed understanding of ferroelectrics, which paved the way for its inclusion in the Si industry as  $BaTiO_3$  insulated capacitors.

A number of key studies were published on the uncommon properties of BaTiO<sub>3</sub>, some of which included connecting its crystal structure to the dielectric characteristics [4] and investigating the electric domains in the material [5]. Initially the electric domains were not well understood, which caused the ferroelectric properties to remain elusive until the 20th century due to zero net polarization in single crystals. Thus, it was not until the 1980s where the full scope of the material was realised; ferroelectrics were now being grown in thin film form for incorporation into semiconductor chips [6].

The main advantage of thin film ferroelectrics lie in the application of the voltage supplied from any hand held electronic device. A bulk ferroelectric of possible thickness 1 mm will require a 5 kV voltage supply to reach a specific switching field of E = 50 kV/cm, known as the coercive field. At this field the polarization is reversed and the dipoles align in the opposite direction. This required voltage is of course unsuitable for any of our modern day electronics. Thin film ferroelectrics with nanometer dimensions allow the coercive field to be attained at voltages used in modern integrated circuits. Therefore, ferroelectrics can now be incorporated into the nanoelectronics industry.

A substantial role for ferroelectrics, and in particular BaTiO<sub>3</sub>, is memory based applications, with a detailed text on ferroelectric memories published in 2000 [7]. While the topic of memory is rather in depth, the main feature of ferroelectrics for this application is its ability to retain a bulk electric polarisation, and therefore is best suited to non-volatile ferroelectric random access memory (FRAM).

1 transistor (1T) / 1 capacitor (1C) cell

Figure 2.1: Schematic of the 1T/1C FRAM cell utilising ferroelectrics. Equivalent circuit shown as the transistor and capacitor connected to the word line and bit line, respectively.

Figure 2.1 highlights a well-established use of ferroelectrics in FRAM: a 1 transistor (1T) / 1 capacitor (1C) cell. The operation is similar to dynamic RAM (DRAM); however in this instance the ferroelectric capacitor is charged and retains its polarity. The polarity of the ferroelectric capacitor represents the digital logic state 1 or 0 such that it does not need to be continuously refreshed between read or write cycles. A detailed study on the use for ferroelectrics for non-volatile memory is given in ref. 8.

In the modern day, ferroelectrics are being studied and investigated for a number of different applications. A 2007 review of the applications of modern ferroelectrics is given in [9]. Some of the highlighted directions for ferroelectric research in the study are: substrate/film interfaces, high strain states, magnetoelectrics, phased-array radars, electrocaloric cooling, among others, which are beyond the scope of this thesis. However, the relevance of the depth of research that ferroelectrics have attracted is underlined.

Further to the above mentioned applications,  $BaTiO_3$  has attracted attention due to its possible negative capacitance property. Salahuddin and Datta initially proposed the inclusion of a ferroelectric material with negative capacitance as a substitute into the gate stack of a MOSFET in order to reduce the subthreshold slope [10, 11]. Negative slopes in polarization-electric field hysteresis loops, indicating a negative capacitance property, were also shown in  $BaTiO_3$  [12]. The study highlights the likelihood of ferroelectric materials possessing a negative capacitance property. However, if  $BaTiO_3$  is to be used in a front-end transistor process for reducing the subthreshold slope, further experimental evidence is needed to support the negative capacitance hypothesis.

The subthreshold slope of a MOSFET is an important characteristic that describes the transition from its off to on state. A steeper slope shows that a lower voltage is required to saturate the transistor. However, using conventional insulators, and even high- $\kappa$  material, there is a fundamental lower limit on the gate voltage that is required in order to increase the current by an order of magnitude. This is commonly referred to as the subthreshold swing, and at its minimum is 60 mV/decade at room temperature. The use of negative capacitance may surmount this roadblock, and reach values < 60 mV/decade. A reduced subthreshold swing past the 'fundamental' limit enables the switching energy of the transistor to be lowered, in turn mitigating some of the self-heating issues attributed to modern state-of-the-art integrated circuits. Negative capacitance may, therefore, aid in the pursuit of greater packing densities on a chip, and prolonging the lifetime of Moore's law. Equal drive currents may also be obtained at smaller supply voltages, which is a key area of interest for an integrated circuit for low power applications and increasing battery life.

However, the necessity of thin films for the nanoelectronics industry does not come without limitations. Bulk forms of ferroelectrics differ substantially in their electrical and material properties when compared to a thin film counterpart. Reduced permittivity and retainable polarization is common in thin films, and chosen substrates will impose a microstructural change which is otherwise absent in powdered ferroelectric material.

The aim of this chapter is to describe ferroelectricity, particularly in a perovskite, and develop Landau theory in terms of the negative capacitance model. The differences between thin film and bulk forms of ferroelectrics are discussed, such as dead layers. A review of current state-of-the-art ferroelectric films is shown from the literature. Finally, an overview of the nanoelectronics industry is given.

## 2.2 Ferroelectricity

#### 2.2.1 Piezo/pyroelectricity and ferromagnetic comparisons

The name ferroelectric is a misnomer and does not indicate any iron in the material. It is derived from the similarities with ferromagnetism, which displays hysteretic properties due to its internal magnetic domains. A ferroelectric, therefore, displays electrical hysteresis, and domain structures consist of aligned electric dipole moments. This was first highlighted in Rochelle salt as displaying similar properties to magnetic hysteresis shown in the case of iron [2].

Ferroelectrics are both piezo and pyroelectric due to their polarization dependence on strain and temperature; however, the reverse is not true. A ferroelectric crystal should have two or more polar states in the absence of an electric field, and

Figure 2.2: Pyroelectric and ferroelectric crystals are highlighted retaining their polar state. Application of an electric field switches the charge state in the ferroelectric, with the pyroelectric state remaining unchanged. Ferroelectrics are a subgroup of pyroelectricity (in addition to piezoelectricity) with this important switching characteristic. have the ability to reverse between these states with the application of an electric field (figure 2.2). This is a key property that defines a material as ferroelectric and describes the reversible polarization in the material, where polarization is defined as a surface charge density.

The impact of switching polarization, P, with an applied electric field creating ferroelectric hysteresis, and also a comparison to a ferromagnetic hysteresis loop, is shown in figure 2.3. Also shown in the figure is the internal domain structure of the ferroelectric or magnetic material. A domain is defined as a uniform direction of either magnetic or electric moments in which the vectors associated with the dipoles are parallel. The internal magnetic domains consisting of the dipole moments in the ferromagnet are initially randomly oriented at zero magnetic field (figure 2.3 (a)). Applying an external magnetic field acts upon the domain structure within the material, shifting the dipoles towards alignment. As the individual domains begin to align, the magnetization increases and reaches saturation. Once the magnetic field is removed the ferromagnet retains a considerable amount of its magnetization as the domains do not revert back to their initial disordered state. If the magnetic field is reversed in direction, the magnetization is also reversed as the domains are ordered in opposite directions. The direct analogy to ferroelectricity is apparent in figure 2.3 (b), whose characteristic is showing the dependent nature of polarization on electric field. For the ferroelectric, an applied electric field acts upon electric dipole moments, whose alignment creates an electric domain. The resulting outcome is spontaneous polarization at the saturated point, and remnant polarization when the electric field is removed. The remnant polarization was described as representing the digital logic state 1 or 0 in figure 2.1. The remnant polarization  $P_r$  is reversed at a coercive field  $-E_c$  in a ferroelectric, and the retained polarization in this regard will be  $-P_r$  once the electric field is removed.

Figure 2.3: Illustration of the hysteretic nature of ferromagnetism (a) and ferroelectricity (b). As the field in each case is increased, the domains align through the force applied on the individual dipole moments, reaching saturation at high field. Removal of the field retains domain alignment, shown as a remnant polarization  $P_r$  for ferroelectrics. Reversal of the field switches the vector directions associated with the domains at the coercive point,  $E_c$  for the ferroelectric. Also shown is

the magnetic and electric dipole moment, defining the properties in each case.

#### 2.2.2 Domains

As described above, a domain in a ferroelectric crystal is a physical region with a uniform direction of electric dipole moments. For the case of BaTiO<sub>3</sub>, which is described in detail in the following section, the Ba<sup>2+</sup> and Ti<sup>4+</sup> ions are shifted towards neighbouring O<sup>6-</sup> ions. The relative shifting of the ions creates the electric dipoles within the crystal. A uniform domain would result if the Ba<sup>2+</sup> and Ti<sup>4+</sup> ions are displaced in equivalent directions toward the O<sup>6-</sup> ions. At the boundary of each domain are domain walls, following from the analogy to ferromagnetism. However, in the case of ferroelectrics, domain walls are sharp transitions in polarization direction spanning only 1 - 10 unit cells [13]. In the case of applying electric fields to switch polarization in a ferroelectric, the process can be regarded as the movement of domain walls, in turn reorienting the electric dipoles.

For a freestanding ferroelectric single crystal, where the surface bound polarization is not compensated by free charges on the plate of any electrode, an electric field will be induced anti-parallel to the polarization, known as a depolarizing field [1]. The energy resulting from this field can drive a shift in the domains in order to minimize the free energy of the system associated with the surface charges. The domain walls will reorient and the ensuing domains will be anti-parallel, which minimises the surface charges on the plane of the crystal. This process of free energy minimisation due to the induced depolarizing field can severely degrade ferroelectricity, and has been reported as one of the causes for dead layers in thin film capacitors [14]. Dead layers cause suppression of permittivity and reduced ferroelectricity in nanometer scale devices. Further discussion relating to dead layers is given in section 2.2.4. Even in the case of ferroelectric capacitors with electrodes, a lack of compensation of the surface polarization charge to the free charges on the electrode can lead to the creation of a depolarization field. Only in the case of a fully compensated bound polarization to free charge at the ferroelectric/electrode interface will the single domain state be energetically favourable [13]. Therefore, a keen interest of study is on electrode engineering in order to limit any depolarizing fields associated with degrading the ferroelectric properties.

#### 2.2.3 Bulk and thin film ferroelectrics

The application of ferroelectrics in the nanoelectronics industry demands that thin films are necessary. However, there are variations in the properties of thin film ferroelectrics over a bulk counterpart. Figure 2.4 encapsulates some of the key differences between bulk and thin film ferroelectrics in which the permittivity response versus temperature is shown [4, 16]. Figure 2.4 (a) describes a bulk ferroelectric crystal of BaTiO<sub>3</sub>, and a maximum peak in the permittivity is seen at approximately 120 °C, known as the Curie temperature. A description of permittivity decreasing as the temperature is increased past the Curie temperature is known as the Curie-Weiss law, given by

$$\chi = \frac{C}{T - T_c} \tag{2.1}$$

where  $\chi$  is the dielectric susceptibility, *T* is the operating temperature, *T<sub>c</sub>* and *C* is the Curie temperature and constant, respectively. The Curie temperature is typically just below a critical temperature [13], which delineates a phase transition in a perovskite crystal. Beneath the critical temperature the perovskite is tetragonal and retains

Figure 2.4: Permittivity response measured as a function of temperature in a bulk BaTiO<sub>3</sub> (a) (image taken from ref. 4) and thin film (Ba<sub>0.5</sub>Sr<sub>0.5</sub>)TiO<sub>3</sub> (b) (image taken from ref. 16). The thin film maximum permittivity increases as a function of film thickness, starting from 175, 280, 340, 660 and 950 nm.

spontaneous polarization. The spontaneous polarization can be reversed using an external electric field (figure 2.3). However, above the critical temperature, the crystal is cubic and no longer retains its bulk electric polarisation in the absence of an electric field. The properties of each perovskite crystal phase are discussed in detail in section 2.2.5.

For comparison, thin film permittivity response is given in figure 2.4 (b) for  $(Ba_{0.5}Sr_{0.5})TiO_3$ . The results show a lack in peak permittivity, which diminishes further with a decreasing film thickness. In addition, the highest achieved permittivity is lower than that shown in figure 2.4 (a). The smearing of the peak makes analysis on the phase transition of a ferroelectric difficult. The apparent shift also means that the Curie temperature shifts with film thickness. Chapter 6 explores detail of a mixed phase relationship in thin film BaTiO<sub>3</sub> with regards to a shift in the Curie temperature.

Further to electrical boundary conditions described in the previous section in terms of domain configurations, mechanical boundaries are also influential in thin film forms of ferroelectrics. For example, in a film which is mechanically clamped to a substrate, strain is developed depending on the lattice parameters and thermal expansion differences between the two materials. The energy associated with the strain can also cause a shift in domain formation from what is expected in a bulk, freestanding ferroelectric crystal. Certain substrates will produce different electrical properties due to the induced mechanical boundary conditions. It is therefore important to consider and address the impacts that a substrate has on the design of a ferroelectric capacitor. A detailed study given by Pertsev *et al.* shows the impact on the phase diagrams of BaTiO<sub>3</sub> as a function of the imposed misfit strain [15]. The work becomes relevant in the design of the negative capacitance structures in chapter 4.

#### 2.2.4 Dead layers

When the thickness of a thin insulating film decreases, its permittivity also decreases [14]. The phenomenon is not described when the standard equation for a single layer insulated capacitance is considered, and the reduction in permittivity has been expressed as a series capacitance configuration. The reason for this was originally thought to be due to a 'dead layer' at the insulator/electrode interface which acts in series with the bulk of the film. The electrical properties showing decreasing permittivity with film thickness is well described through the series capacitance model. However, it stipulates that a secondary material is present in the capacitor.

Previous studies have shown evidence of a distinct region of material that differs from the bulk of the insulator. Explanations to the origin of the secondary material were due to: inter-diffusion or reaction at interfaces [17], several nanometer layer at the interface due to diffusion of Pt [18], 3 nm thick fully strained region [19] and amorphous interfacial layer [20]. However, a range of other studies do not show any evidence of a physical or distinct dead layer [21 - 27].

Intrinsic influences leading to an explanation of the dead layer effect have also been explored, which explains why many studies have not shown evidence of a physical interfacial layer. A study by Black and Welser introduced the concept of a finite screening length in electrodes [28]. The electrons within the electrode are not arranged in an ideal delta function at the boundary of the electrode/insulator due to a combination of electron repulsion and their wave-like properties. The compensating charge then screens the bound polarization charge over a certain length within the electrode and, as a consequence, the applied electric field penetrates into the electrode. The penetrating electric field removes some of the voltage that would otherwise have been dropped across the insulator. In addition, the charge separation between the compensating and bound polarization charge inherently adds a capacitive contribution in series with the bulk expected capacitance of the insulating layer. The concept supports the series capacitance model that is shown to accurately describe the dead layer effect. Furthermore, a study in ref. 29 discusses the impact of Ti and O interdiffusion into the electrode and its resulting effect on the interfacial capacitive contribution to the series. The high polarizability of these ions can increase the achievable permittivity of the electrode, in turn increasing the capacitance of the electrode and reduce the dead layer effect. The result is a combination of an intrinsic case, resulting from the screening length of the compensating charge, with an extrinsic contribution from the diffusion of ions during deposition. Careful control of the thermal treatment of the capacitors during growth may inhibit some of the diffusion leading to dead layer effects.

A further intrinsic case that would be otherwise absent in electron microscopy imaging of the electrode/insulator interface is the depolarizing field. Depolarizing fields were previously discussed in section 2.2.2 in terms of free standing ferroelectric material without electrodes. If the compensating charge in the electrode does not fully screen the bound surface polarization charge of the insulator, an electric field is built across the insulator anti-parallel to the applied electric field. The result would be an overall reduction in the polarization of the insulator. Section 2.2.6 describes polarization and its proportionality with permittivity, however a reduction in polarization will lead to a reduction in the achieved permittivity in the insulating film. The overall result of depolarizing fields is that an insulator will show a suppressed permittivity, which is evident in thin films.

In either of the intrinsic cases, a reduction in film thickness increases the bulk capacitance. The increase in bulk capacitance when film thicknesses are now nanometer scale in length ensures that this capacitance is comparable to the fixed interfacial capacitance. The result has led to the widely reported decrease in permittivity as the film thickness reduces into the nanoscale. It was previously not observed in thicker films as this bulk capacitance was the much smaller contribution in the series capacitance configuration.

A study in ref. 14 shows the impact of both the screening length in electrodes and depolarizing fields in *ab initio* calculations, which results in a total capacitance density of 258 fF/um<sup>2</sup>, reduced from an expected 1600 fF/um<sup>2</sup> expected of the SrTiO<sub>3</sub> layer without the intrinsic dead layer influences. However, they propose that electrodes such as Pt should show minimal contributions to the finite screening lengths and depolarizing fields due to the high density of electrons in this metal. This is not the case in experimental studies with Pt used as the electrodes for high permittivity material [29, 30]. It is proposed that defects and inter-diffusion play an important role when using electrodes such as Pt [29]. Conducting oxide electrodes such as SrRuO<sub>3</sub> offer superior and ultra-flat epitaxial properties when used with other such materials (SrTiO<sub>3</sub>, BaTiO<sub>3</sub>, etc.) [14]. This will limit the interfacial capacitance contribution as the electrode/insulator interface approaches ideal infinitesimal thicknesses, and sharp boundaries between the insulating and conducting material are achieved. Chapter 6 explores dead layers in SrTiO<sub>3</sub> / Pt structures in a series capacitance model. A remodelled effective oxide thickness equation allows extraction of a dead layer thickness to investigate the origins of any physical dead material. Furthermore, chapter 4 shows high resolution electron imaging of epitaxial BaTiO<sub>3</sub> grown on SrRuO<sub>3</sub> electrodes where sharp interfaces are evident.

#### 2.2.5 Perovskite ferroelectrics

In the above description of ferroelectrics, the key property of the material is its ability to retain, and further reverse polarization with an electric field. Originally, this property was only seen in hydrogen bonded materials, and had little application due to their fragility. It was the discovery of the perovskite which changed what was thought possible with materials possessing ferroelectricity.

A perovskite is a material whose chemical formula is  $ABO_3$ , where the cations A sit on the corners of a unit cell and B is positioned in the centre, with remaining O anions surrounding B in an octahedral configuration. A range of different properties can be obtained depending on the composition of the ions in the perovskite; for example, metallic or insulating, Curie temperature tuning and many others.

Figure 2.5 shows schematically the perovskite of  $BaTiO_3$  in which A represents  $Ba^{2+}$ , and B  $Ti^{4+}$ . An important property of the perovskite is the ability to change in phase at the Curie temperature. As described in equation 2.1, above the Curie temperature the material is cubic, which is the structure of the high temperature paraelectric phase. In this cubic phase the lattice constant ratio of the perpendicular and in-plane parameters, c/a = 1. Due to the higher operating temperature, the increased thermal energy is enough to overcome the long-range Coulomb forces between the dipoles, ensuring the  $Ti^{4+}$  ion is positioned at the centre (figure 2.5 (a)). In this form, the unit cell is centrosymmetric and non-polar such that it does not display any polarization retention or reversal due to the higher symmetry state of the crystal. However, the paraelectric phase does display a non-linear polarization response to an applied electric field, with much higher permittivity over conventional high- $\kappa$  materials.

Figure 2.5: Schematic of the unit cell of a perovskite material BaTiO<sub>3</sub>. The paraelectric phase is situated at temperatures above  $T_c$  where the unit cell is cubic (a). For the ferroelectric phase, temperatures lower than  $T_c$  induces a deformation along one of the axes and the unit cell is tetragonal, creating a permanent dipole with remnant polarization as shown (b).