University of Newcastle upon Tyne School of Electrical and Electronic Engineering

## Design of Variation-Tolerant Synchronizers for Multiple Clock and Voltage Domains

By

### Mohammed Saleh Abdullah Alshaikh

A thesis submitted for the degree of Doctor of Philosophy (PhD) at Newcastle University

April 2014

## Abstract

Parametric variability increasingly affects the performance of electronic circuits as the fabrication technology has reached the level of 32nm and beyond. These parameters may include transistor Process parameters (such as threshold voltage), supply Voltage and Temperature (PVT), all of which could have a significant impact on the speed and power consumption of the circuit, particularly if the variations exceed the design margins. As systems are designed with more asynchronous protocols, there is a need for highly robust synchronizers and arbiters. These components are often used as interfaces between communication links of different timing domains as well as sampling devices for asynchronous inputs coming from external components. These applications have created a need for new robust designs of synchronizers and arbiters that can tolerate process, voltage and temperature variations.

The aim of this study was to investigate how synchronizers and arbiters should be designed to tolerate parametric variations. All investigations focused mainly on circuit-level and transistor level designs and were modeled and simulated in the UMC90nm CMOS technology process. Analog simulations were used to measure timing parameters and power consumption along with a "Monte Carlo" statistical analysis to account for process variations.

Two main components of synchronizers and arbiters were primarily investigated: flip-flop and mutual-exclusion element (MUTEX). Both components can violate the input timing conditions, setup and hold window times, which could cause metastability inside their bistable elements and possibly end in failures. The mean-time between failures is an important reliability feature of any synchronizer and depends exponentially on the metastability recovery time constant  $\tau$  and the delay through the synchronizer.

The MUTEX study focused on the classical circuit, in addition to a number of modifications at the circuit and transistor levels, to adjust the value  $\tau$  and its tolerance, based on increasing internal gain by adding current sources, reducing the capacitive loading, boosting the transconductance of the latch, compensating

the existing Miller capacitance, and adding asymmetry to maneuver the metastable point. The results showed that some circuits had little or almost no improvements, while five techniques showed significant improvements by reducing  $\tau$  and maintaining high tolerance.

Three design approaches are proposed to provide variation-tolerant synchronizers. First, the wagging synchronizer is proposed to significantly increase reliability over that of the conventional two flip-flop synchronizer. The robustness of the wagging technique can be enhanced by using robust  $\tau$  latches or adding one more cycle of synchronization. The second approach is the Metastability Auto-Detection and Correction (MADAC) latch which relies on swiftly detecting a metastable event and correcting it by enforcing the previously stored logic value. This technique significantly reduces the resolution time down from uncertain to certain time. Finally, a pseudo level-shifting handshake synchronization technique is proposed to transfer signals between Multiple-Voltage Multiple-Clock Domains (MVD/MCD) that do not require conventional level-shifters between the domains or multiple power supplies within each domain. This interface circuit uses a synchronous set and feedback reset protocol which provides level-shifting and synchronization of all signals between the domains, from a wide range of voltage-supplies and clock frequencies.

Overall, synchronizer circuits can tolerate variations to a greater extent by employing the wagging technique or using a MADAC latch, while MUTEX tolerance can suffice with small circuit modifications. Communication between MVD/MCD can be achieved by an asynchronous handshake with internal resetting protocols without a need for adding level-shifters.

ii

## Acknowledgments

At first, All thanks and gratitude to Allah the most graceful the most merciful.

"In the name of Allah, Most Gracious, Most Merciful. Praise be to Allah, the Cherisher and Sustainer of the worlds; Most Gracious, Most Merciful; Master of the Day of Judgment. Thee do we worship, and Thine aid we seek. Show us the straight way, The way of those on whom Thou hast bestowed Thy Grace, those whose (portion) is not wrath, and who go not astray." <sup>1</sup>

After that, I would like to express my deepest thanks to Prof. Alex Yakovlev. His advice, support and motivation kept me going forward throughout the years to finish my thesis. I would also want to say great thanks to Dr. Gordon Russell. His exceptional feedback and valuable comments have been a great value to me.

Also, I am grateful for the chance to work under the guidance of, full of inspiration and kindness, Prof. David Kinniment during my first year.

I want to thank all my friends and colleagues in the Microelectronics System Design group for their valuable discussions in many different occasions. I also want to thank all my friends, in the UK and Saudi Arabia, for their cheer and support.

In Saudi Arabia, I present my thanks to my mother, brothers and sisters for the encouragement and endless support. Especially, I would like to express a great love and thanks to my lovely wife, *Norah*, who kept standing by my side, encouraging, motivating and comforting me during health and sickness towards progressing over the years of my study and research, as well as sharing enthusiastically all my achievements. I am also grateful for my son '*Aziz*' who brings smile to us every day.

I would like to thank Umm Al-Qura University, Saudi Arabia, and the Saudi Cultural Bureau Attaché, in the Saudi Arabian Embassy in London, for providing me with the scholarship to finish my thesis.

<sup>1</sup> Surat Al-Fatihah, The Holy Quraan, Chapter 1, Verses 1:7.

## List of Publications

### **Conference Papers:**

- 1. M. Alshaikh, D. Kinniment, and A. Yakovlev. "A synchronizer design based on wagging." in Proceeding 2010 *IEEE 22nd International Conference on Microelectronics* (ICM 2010), Cairo, Egypt, Dec. 19-22, 2010, pp. 415-418.

- 2. M. Alshaikh, D. Kinniment, and A. Yakovlev. "On the trade-off between resolution time and delay times in bistable circuits." in Proceeding 2009 *IEEE International Conference on Electronics Circuits and Systems* (ICECS 2009), Yasmin Hammamet, Tunisia, 13-16 Dec 2009, pp. 355-358.

**Technical Reports:**

M. Alshaikh, D. Kinniment, and A. Yakovlev, "Robust Synchronization using the Wagging Technique." NCL-EECE-MSD-TR-2010-165, Microelectronic System Design Group, School of EECE, Newcastle University, December 2010.

Workshops:

4. M. Alshaikh, G. Russell, and A. Yakovlev. "Level-Shifting Handshake Synchronizers," accepted fresh ideas workshop in ASYNC 2014.

## List of Contents

| Abstra    | ct     |                                                           | i    |

|-----------|--------|-----------------------------------------------------------|------|

| Acknov    | vledg  | ments                                                     | iii  |

| List of l | Public | cations                                                   | iv   |

| List of l | Figure | 25                                                        | ix   |

| List of ' | Table  | S                                                         | xiii |

| Chapte    | er 1   | Introduction                                              | 1    |

| 1.1       | Тес    | chnology and Variability                                  | 1    |

| 1.1       | 1.1    | CMOS Transistor Scaling                                   |      |

| 1.1       | 1.2    | Sources of Variability                                    |      |

| 1.2       | Var    | riation-Tolerant Circuit and Microarchitecture Techniques | 9    |

| 1.2       | 2.1    | Adaptive Voltage Techniques                               | 9    |

| 1.2       | 2.2    | Error Detection and Recovery Circuits                     |      |

| 1.2       | 2.3    | Hardware Redundancy                                       |      |

| 1.2       | 2.4    | Asynchronous Circuits and Systems                         | 14   |

| 1.3       | The    | esis Motivations                                          | 15   |

| 1.4       | The    | esis Contributions                                        | 17   |

| 1.5       | The    | esis Organization                                         |      |

| Chapte    | er 2   | Background                                                | 20   |

| 2.1       | Ме     | tastability, Synchronizers and Arbiters                   |      |

| 2.1       | 1.1    | Metastability Behavior Analysis                           | 24   |

| 2.1       | 1.2    | Metastability Impact Mitigation                           |      |

| 2.1       | 1.3    | Synchronizers                                             |      |

| 2.1       | 1.4    | Arbiters                                                  | 41   |

| 2.2       | Syr    | nchronization Techniques in SoCs                          | 51   |

| 2.2       | 2.1    | Global Clock Technique                                    | 51   |

| 2.2       | 2.2    | Asynchronous Technique                                    | 52   |

| 2.2       | 2.3    | Multiple Clock Domain (MCD) Techniques                    | 52   |

| 2.2       | 2.4    | GALS Techniques                                           | 54   |

| 2.2       | 2.5    | Handshake Signaling                                       | 55   |

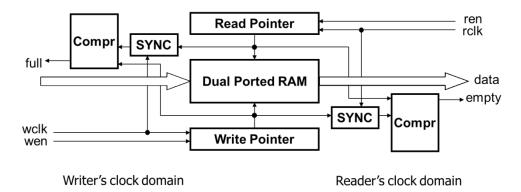

| 2.2    | 2.6  | FIFO                                                        |     |

|--------|------|-------------------------------------------------------------|-----|

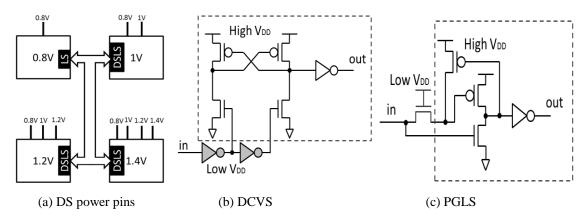

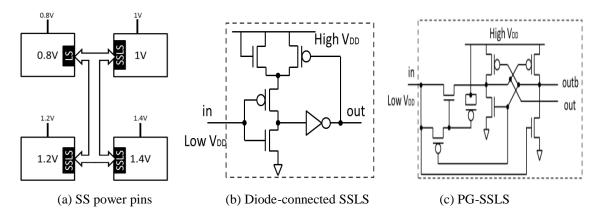

| 2.3    | Μι   | ıltiple Voltage Domain (MVD) in SoCs                        |     |

| 2.3    |      | Dynamic Voltage and Frequency Scaling (DVFS)                |     |

| 2.3    | 3.2  | Voltage Level-Shifters                                      |     |

| 2.3    | 3.3  | MVD and MCD Concerns                                        |     |

| 2.4    | Ch   | aracterizing Flip-Flops' Performance                        | 63  |

| 2.4    |      | Delay Time                                                  |     |

| 2.4    | ł.2  | Setup Time                                                  | 65  |

| 2.4    | ł.3  | Hold Time                                                   | 65  |

| 2.4    | ł.4  | Finding Setup and Hold Time                                 | 66  |

| 2.4    | ł.5  | Metastability Metrics                                       | 67  |

| 2.4    | ł.6  | Power and Energy                                            | 69  |

| 2.4    | ł.7  | Variability Analysis                                        | 70  |

| 2.5    | Su   | mmary                                                       | 73  |

| 3.1    | Fli  | p-Flop Design                                               |     |

| 0.4    |      |                                                             |     |

| 3.2    |      | p-Flop Results                                              |     |

| 3.3    |      | her Cell Examples                                           |     |

| 3.4    |      | liable Synchronizers                                        |     |

| 3.4    | ł.1  | Flip-Flop Synchronizer                                      |     |

| 3.4    | ł.2  | Wagging Synchronizer                                        |     |

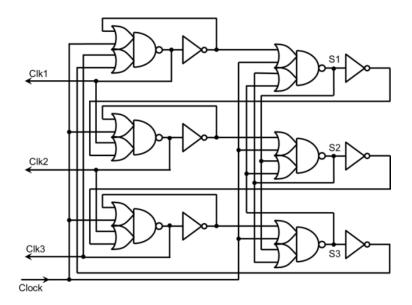

| 3.4    | ł.3  | Clocking Control Circuit (CCC)                              | 87  |

| 3.5    | Sy   | nchronizer Results                                          | 90  |

| 3.6    | Su   | mmary                                                       | 92  |

| Chapte | er 4 | Variation-Tolerant Arbiter Design                           | 93  |

| 4.1    | A    | Гуріcal MUTEX                                               | 93  |

| 4.1    |      | Analytical Approximation Model for Metastability in a MUTEX |     |

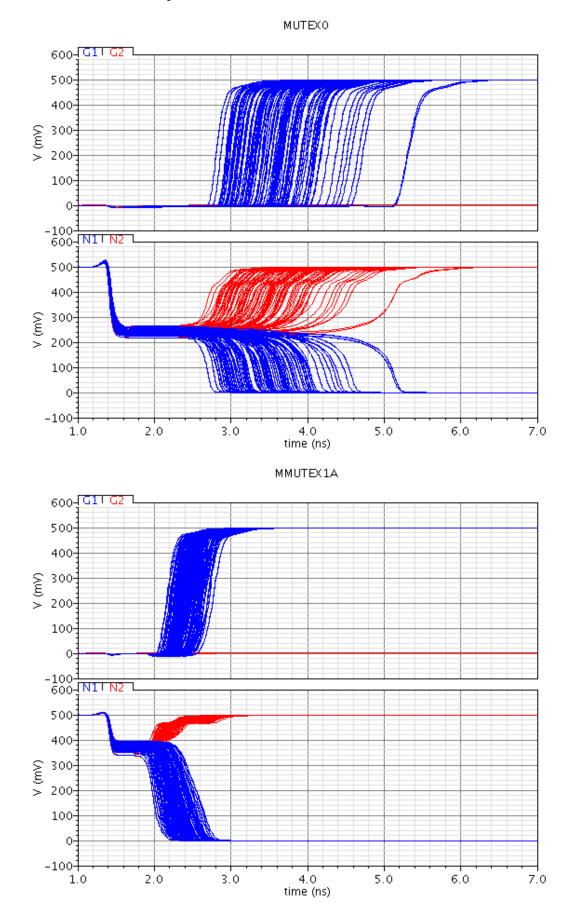

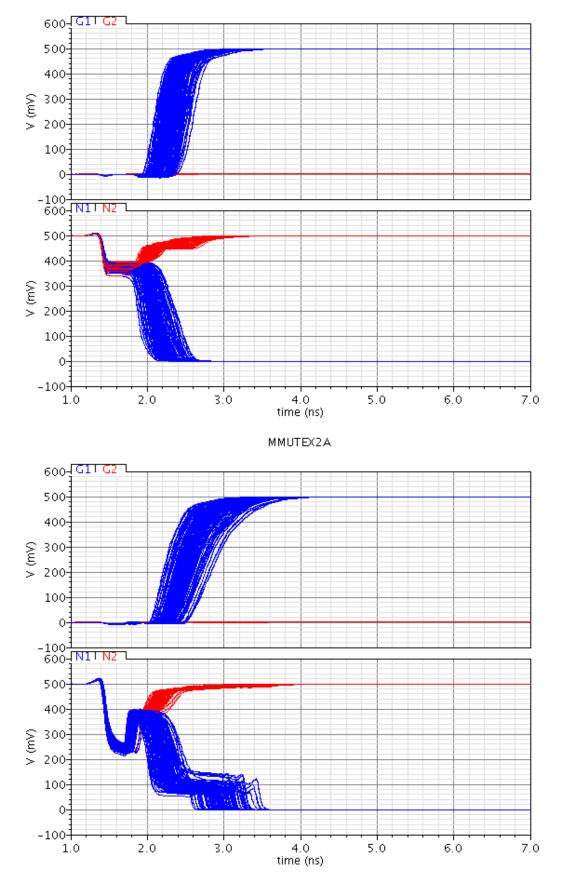

| 4.1    | .2   | Simulating a MUTEX                                          |     |

| 4.1    | .3   | Simulation Results of the Typical MUTEX                     | 100 |

| 4.2    | Im   | proving the MUTEX                                           |     |

| .2 I  | Improving the MUTEX                                 |  |

|-------|-----------------------------------------------------|--|

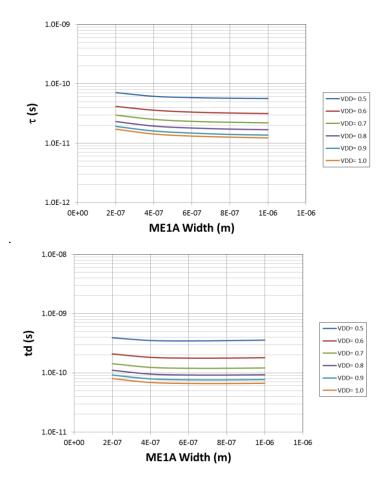

| 4.2.1 | M-MUTEX with current source (ME1A)                  |  |

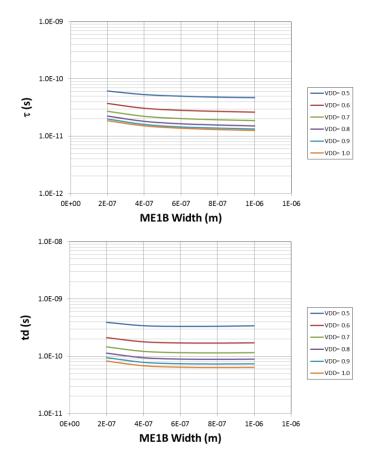

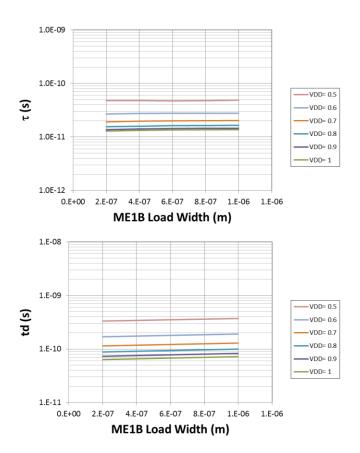

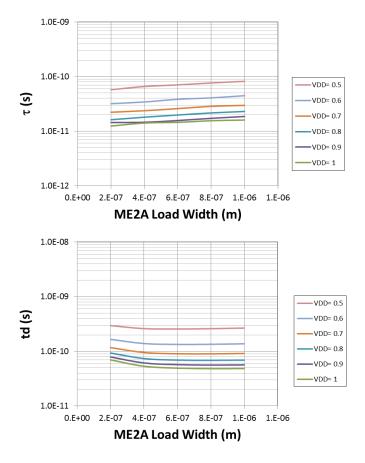

| 4.2.2 | M-MUTEX with current source and reduced load (ME1B) |  |

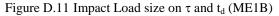

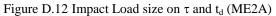

| 4.2.3 | M-MUTEX with $g_m$ Boosting                         |  |

| 4.2.4 | M-MUTEX with Cascode Feedback                       |  |

|       |                                                     |  |

| 4.2    | 2.5 M-MUTEX with Biased Choice                              | 110         |

|--------|-------------------------------------------------------------|-------------|

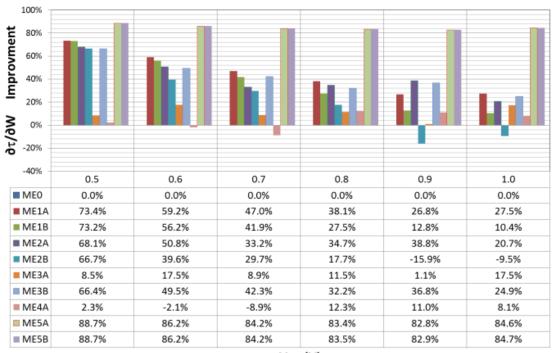

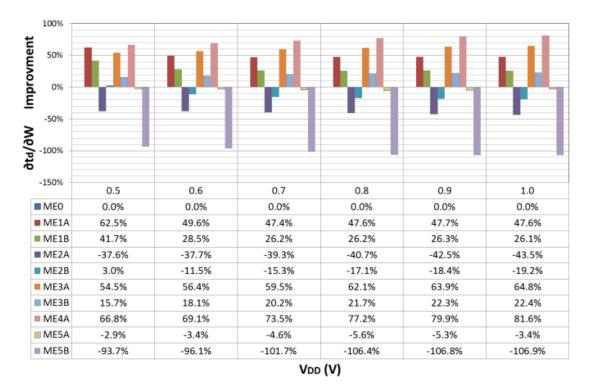

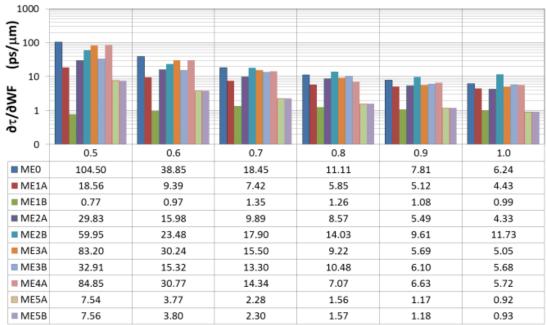

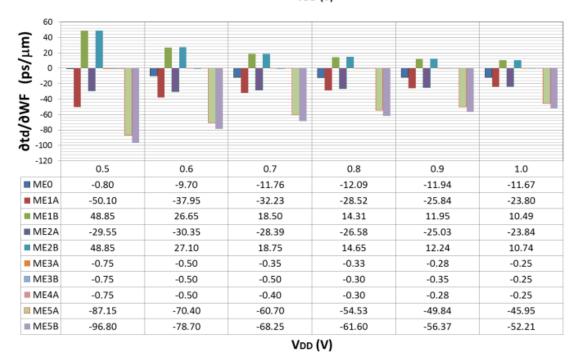

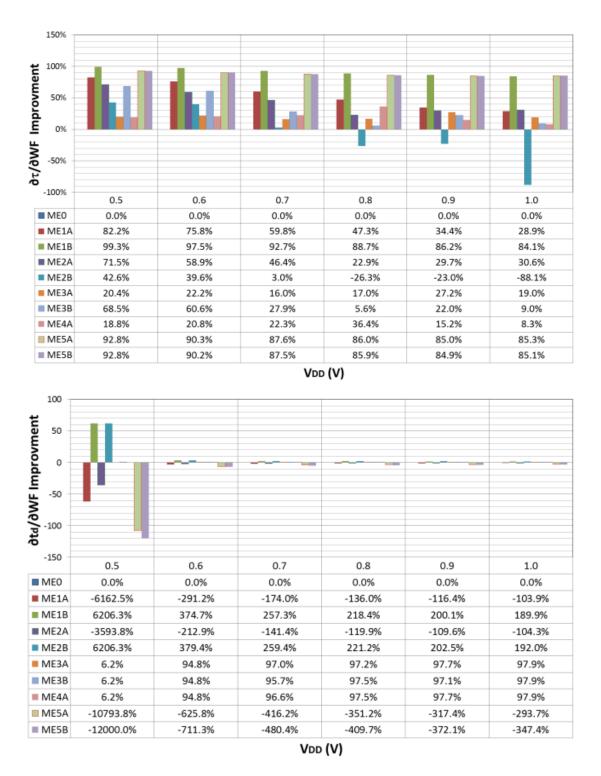

| 4.3    | Simulation Results                                          | 112         |

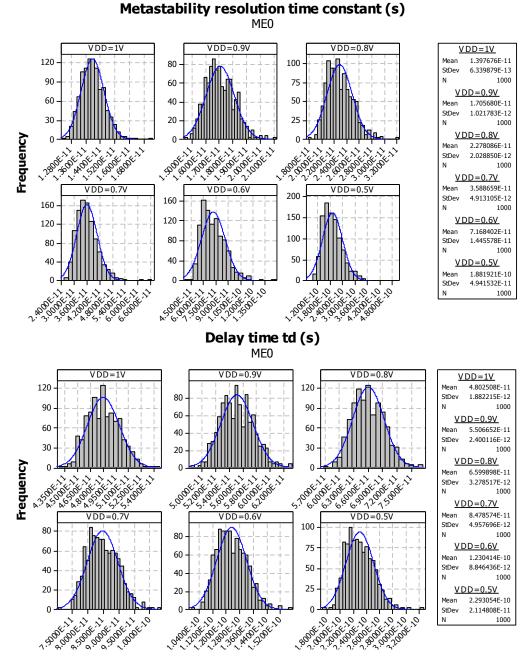

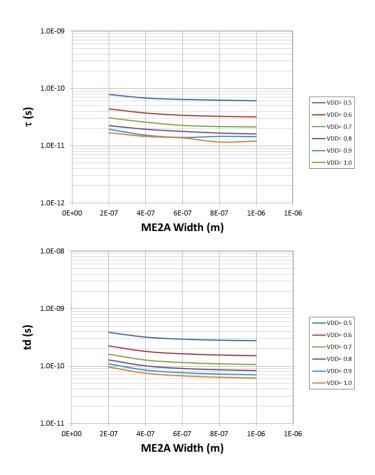

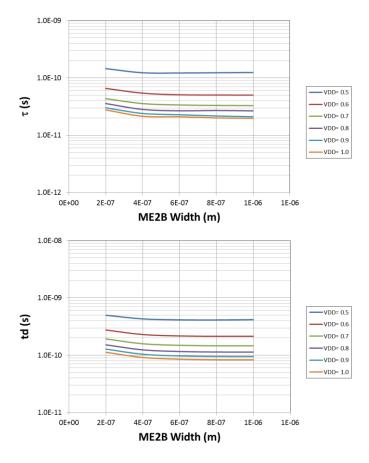

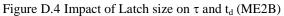

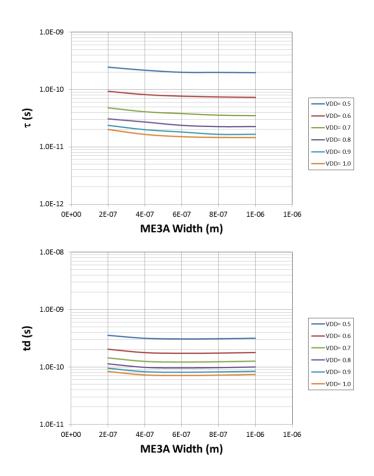

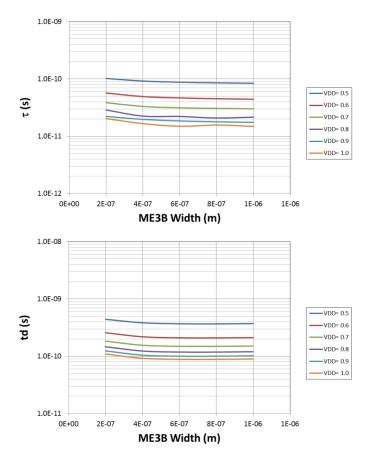

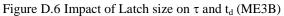

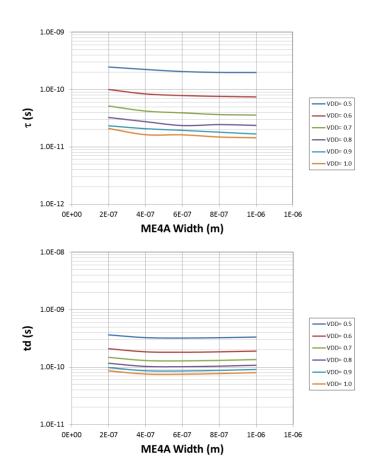

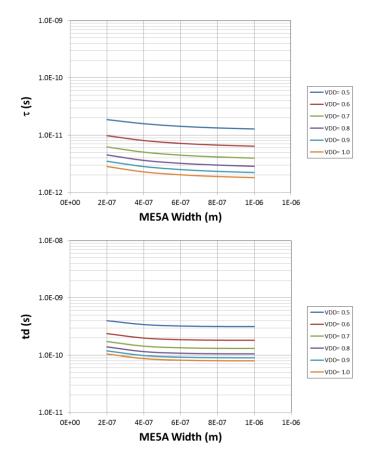

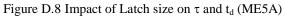

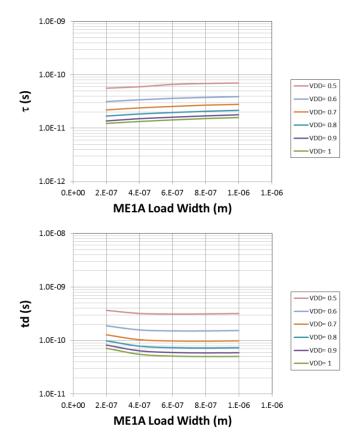

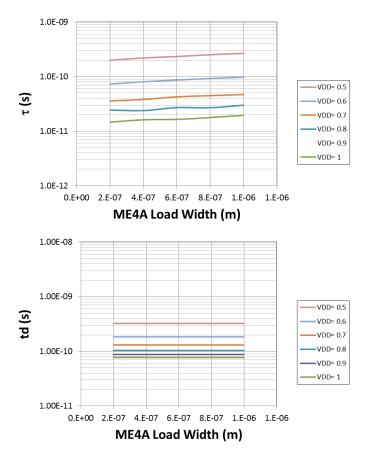

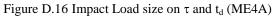

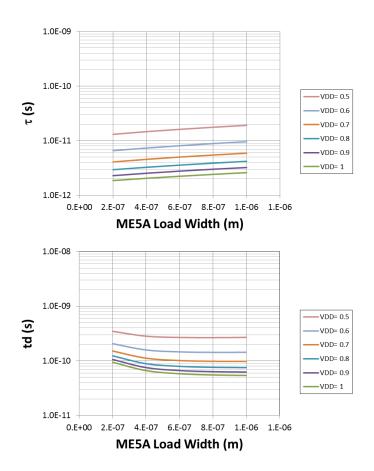

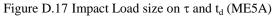

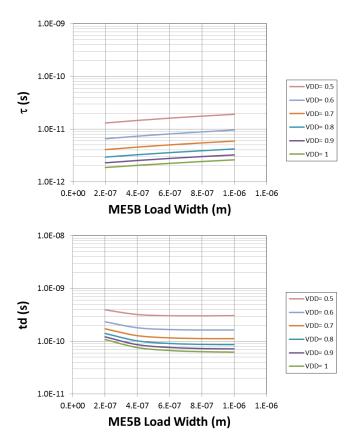

| 4.3    | Latch Sizing                                                |             |

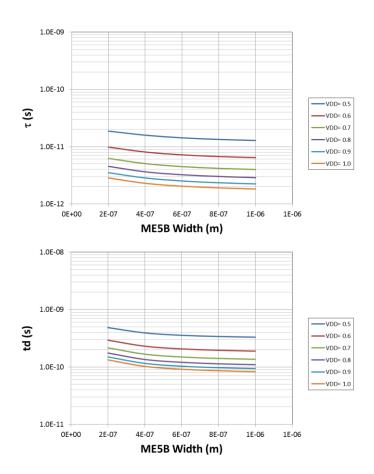

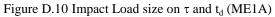

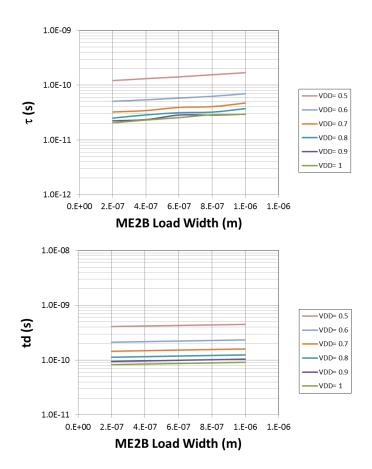

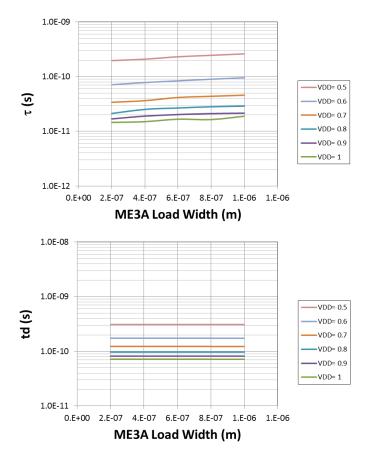

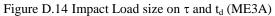

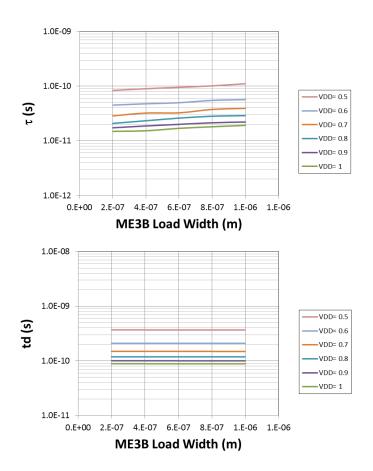

| 4.3    | 2.2 Load Sizing                                             |             |

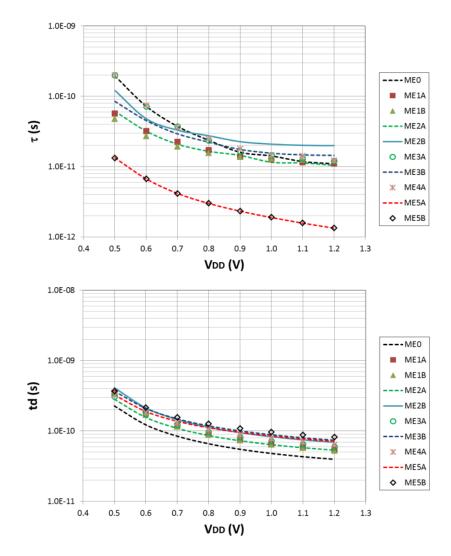

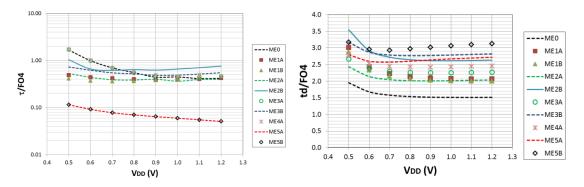

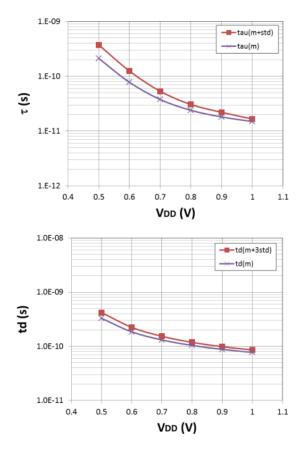

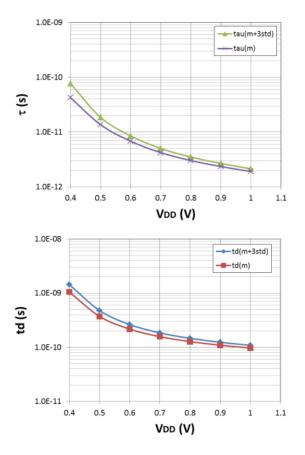

| 4.3    | 3.3 Voltage Supply Effect                                   | 116         |

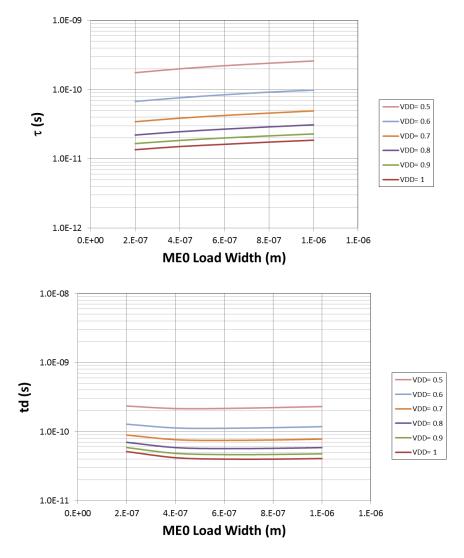

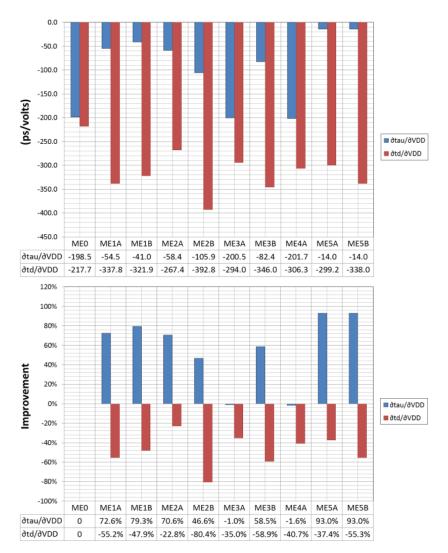

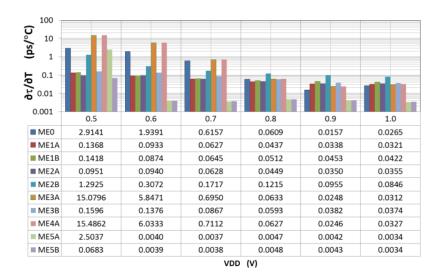

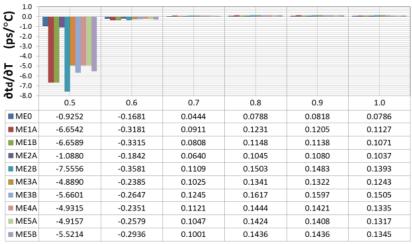

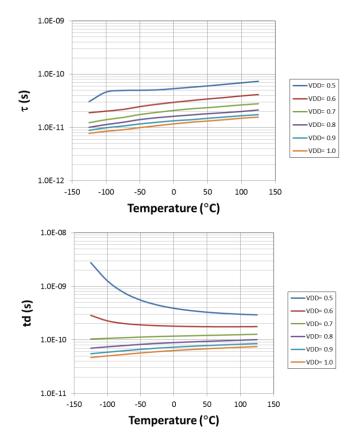

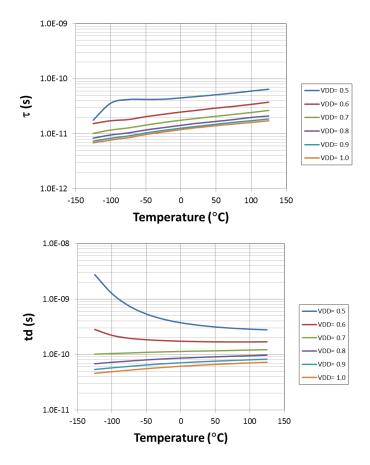

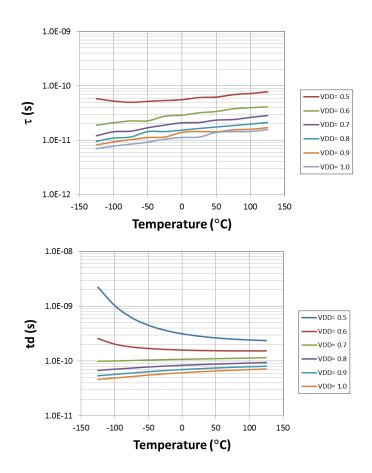

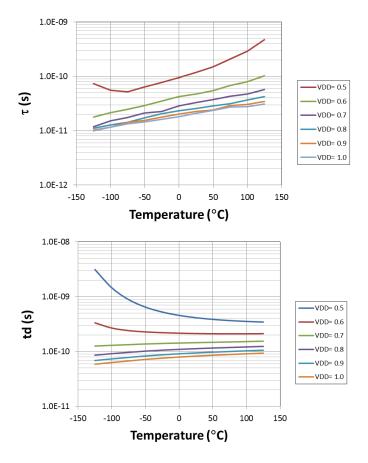

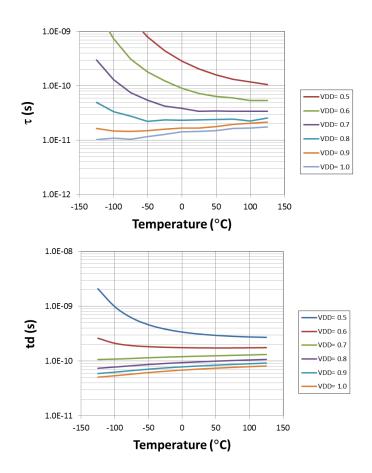

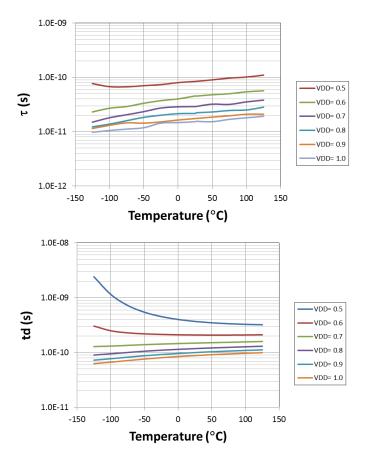

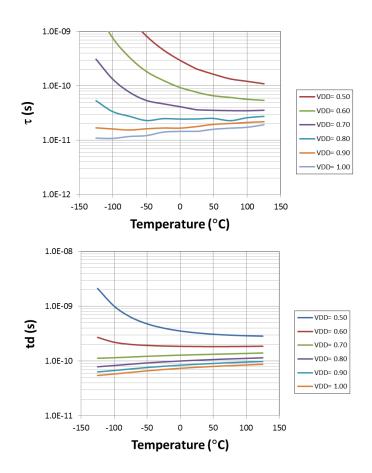

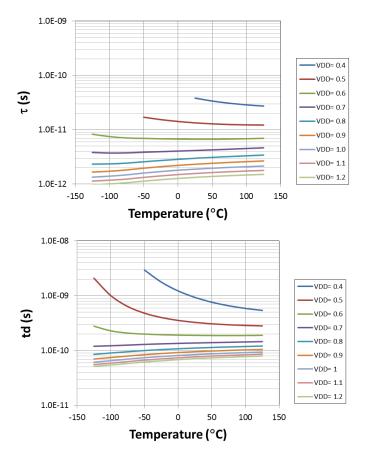

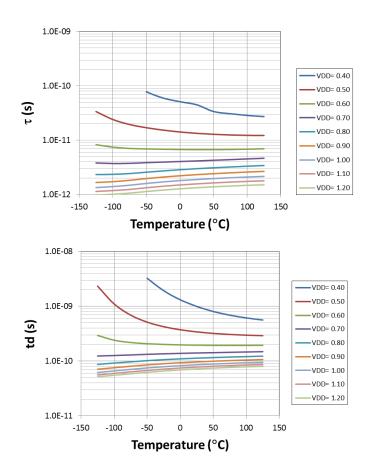

| 4.3    | 3.4 Temperature and Voltage Supply Effect                   |             |

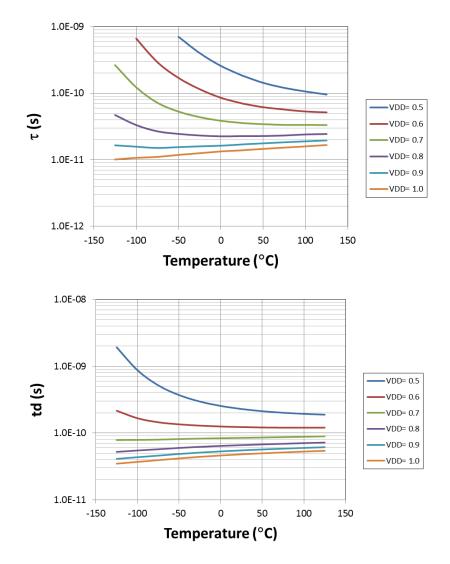

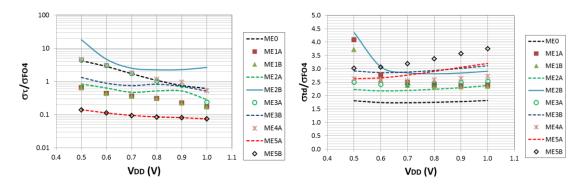

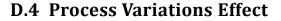

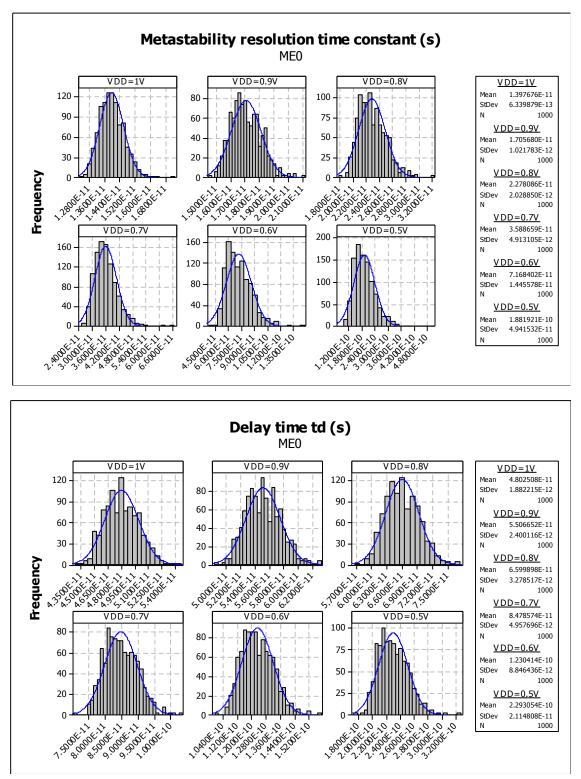

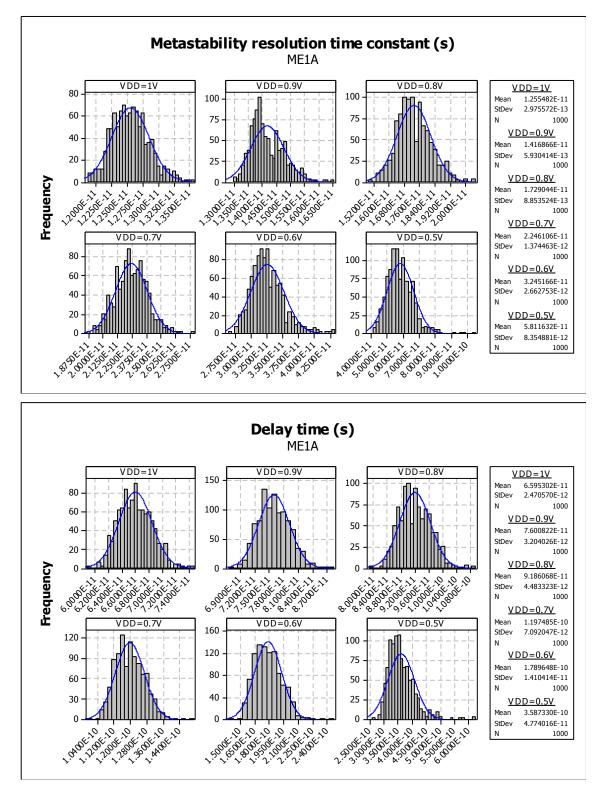

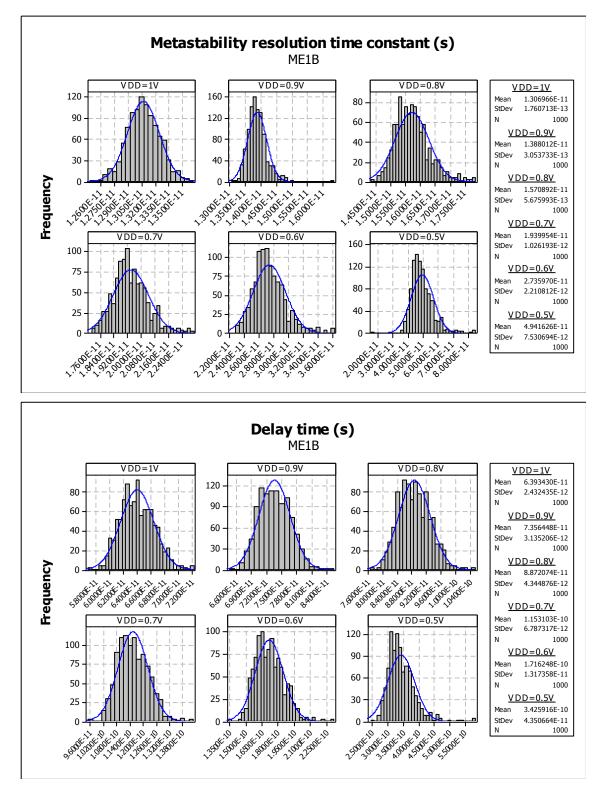

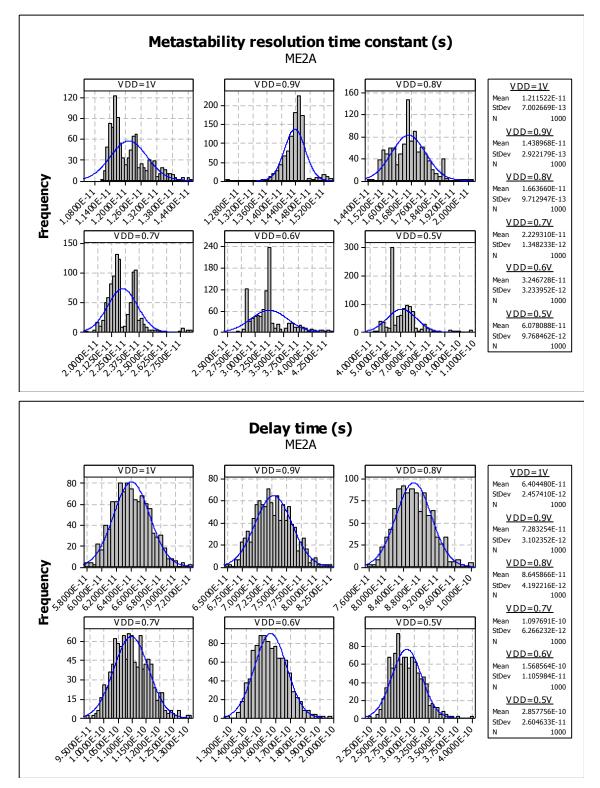

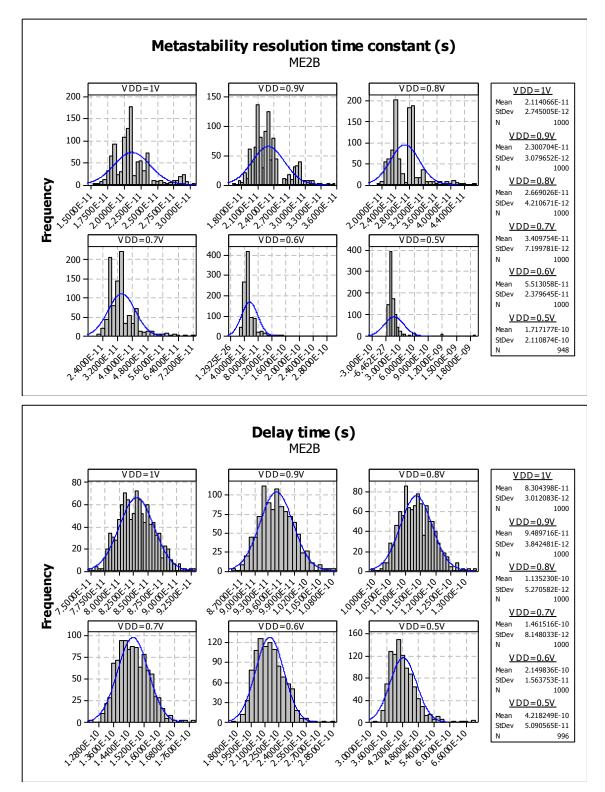

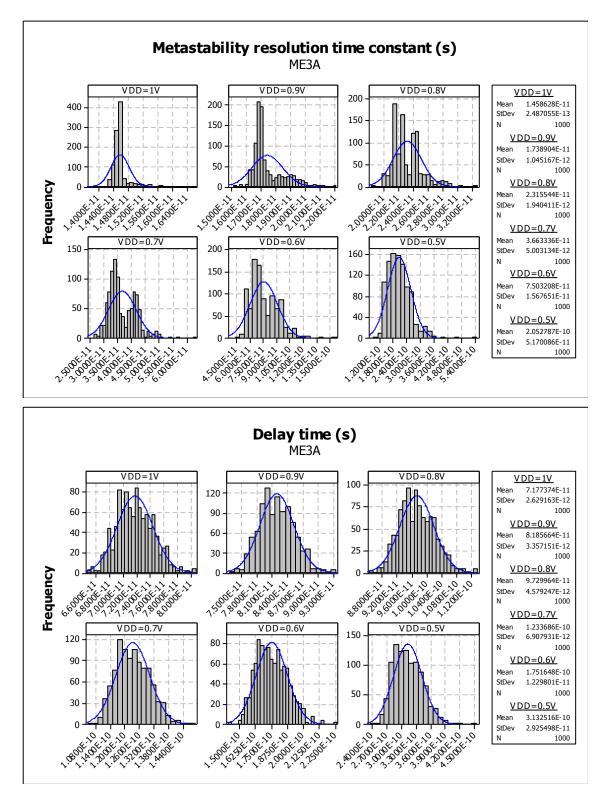

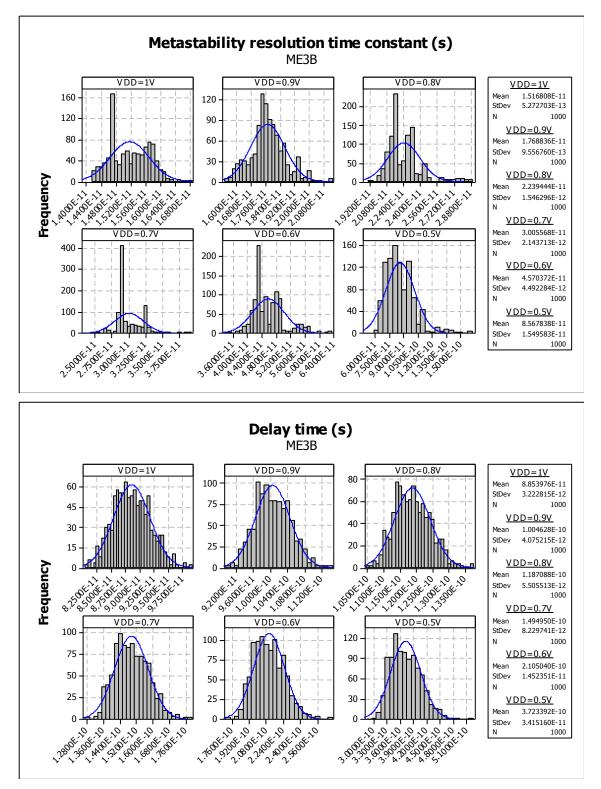

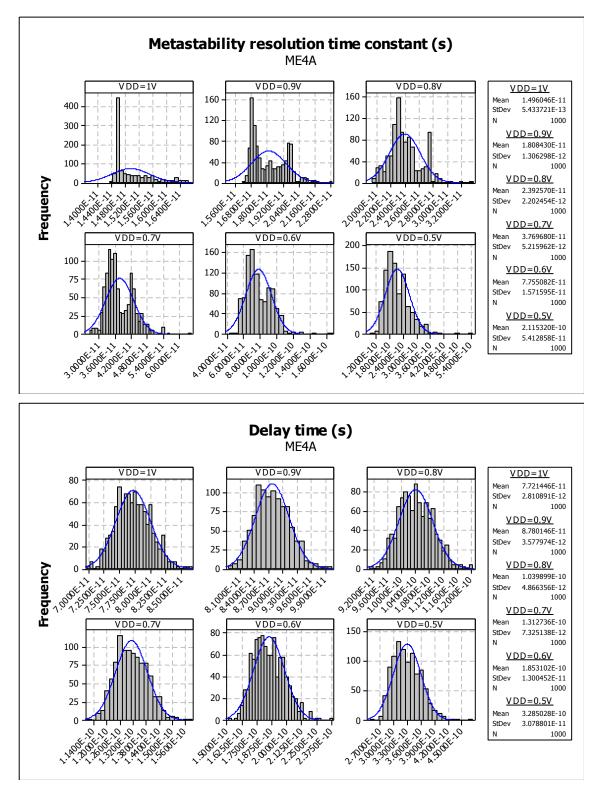

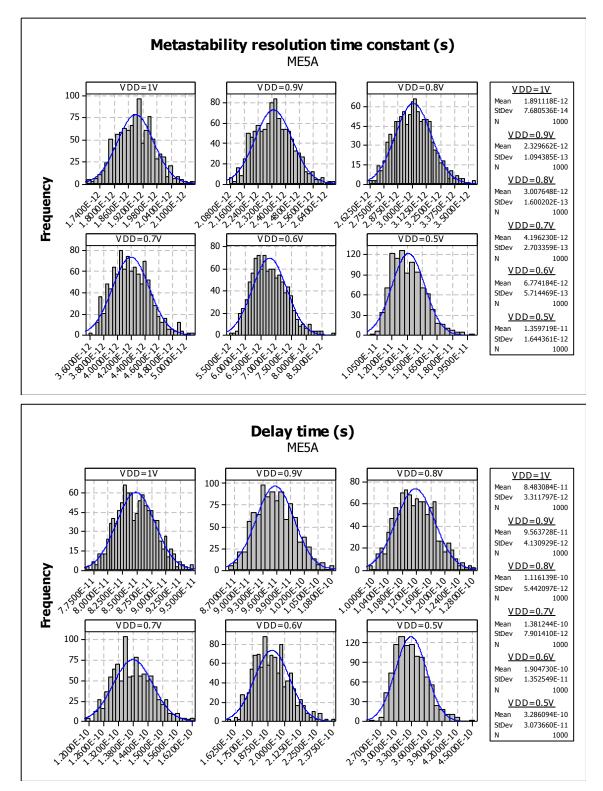

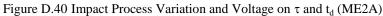

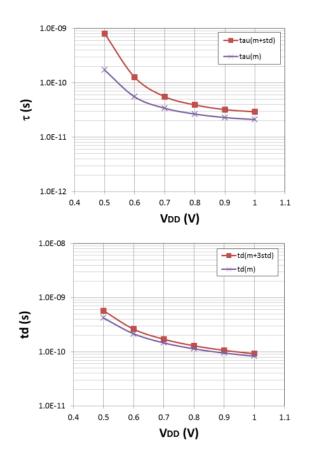

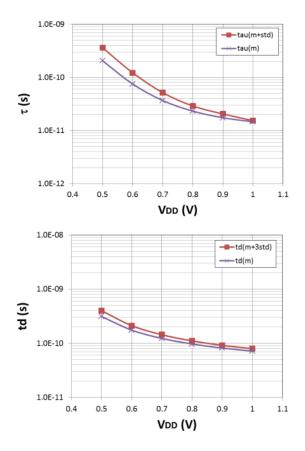

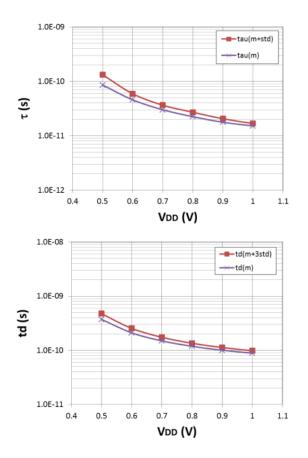

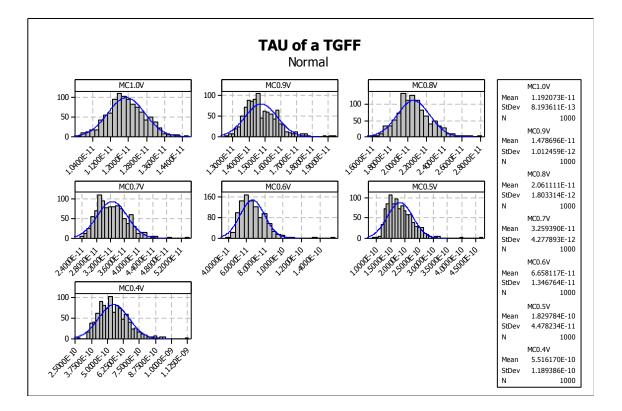

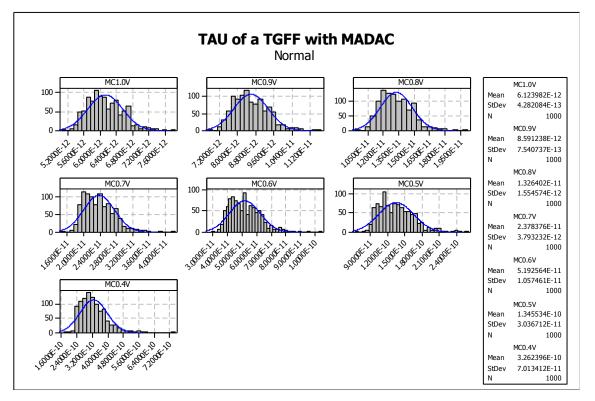

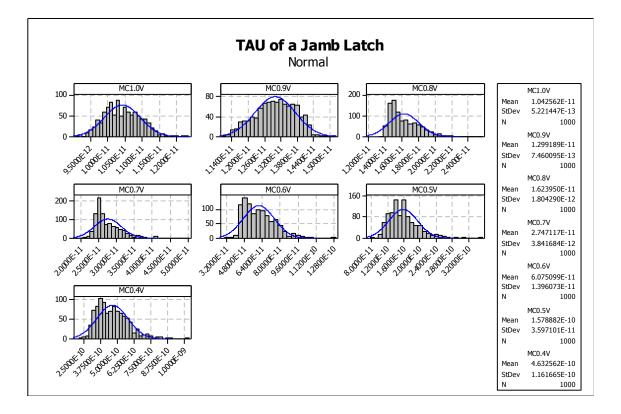

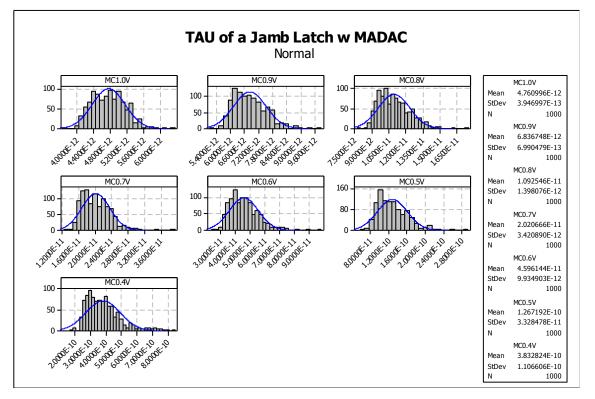

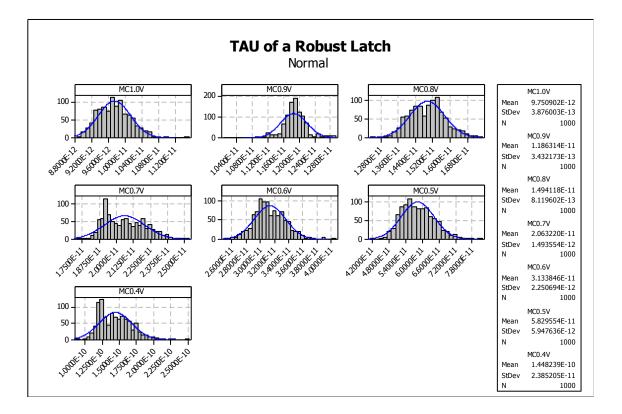

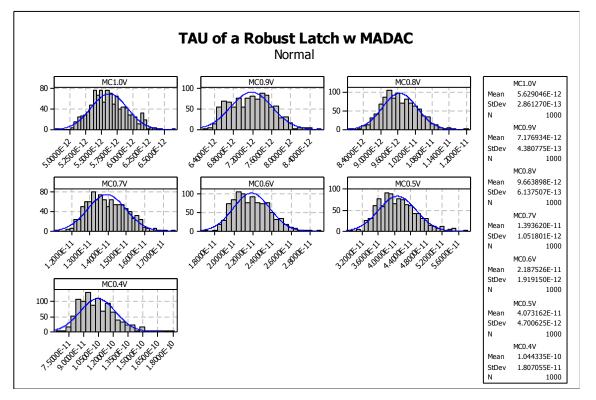

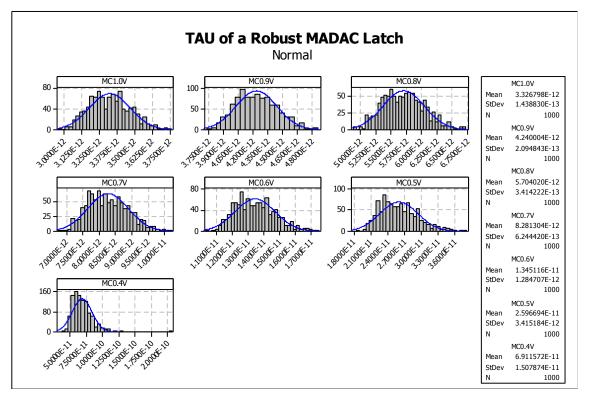

| 4.3    | 8.5 Process Variations and Voltage Effect                   |             |

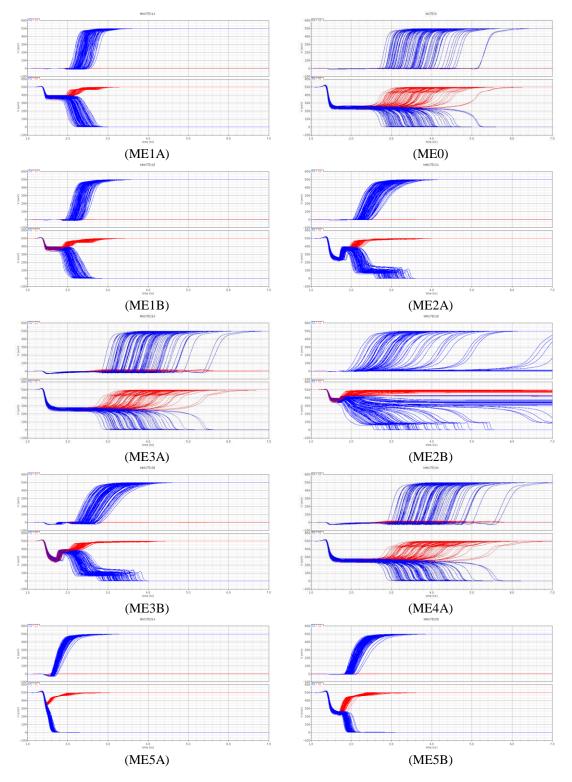

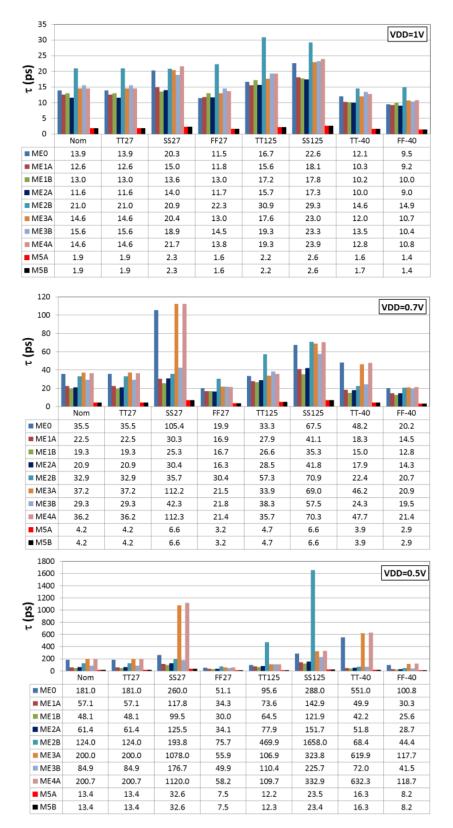

| 4.3    | 8.6 Process, Voltage and Temperature Corners Effect         |             |

| 4.4    | Summary                                                     |             |

| Chapte | r 5 Variation-Tolerant Synchronizer Design                  | 129         |

| 5.1    | Typical Synchronizer Circuits                               |             |

| 5.2    | Variation-Tolerant Wagging Synchronizer                     |             |

| 5.2    | Fast and Robust Wagging Synchronizer                        | 131         |

| 5.2    | 2.2 Wagging Synchronizer with Reconfigurable Resolution T   | ime132      |

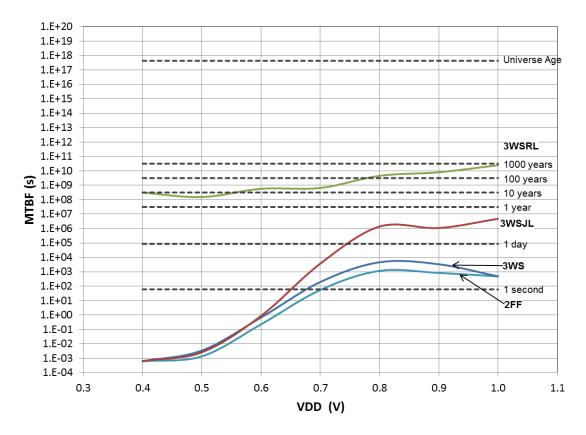

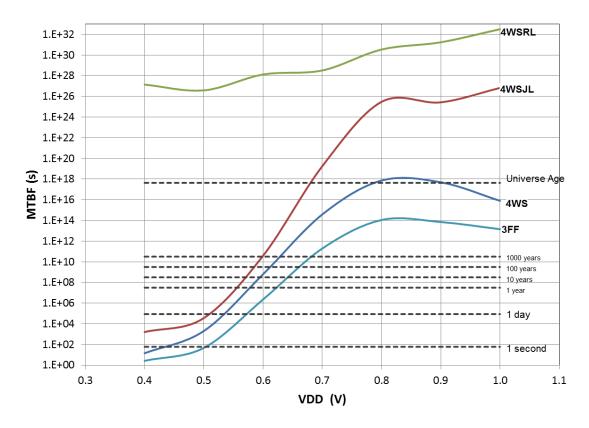

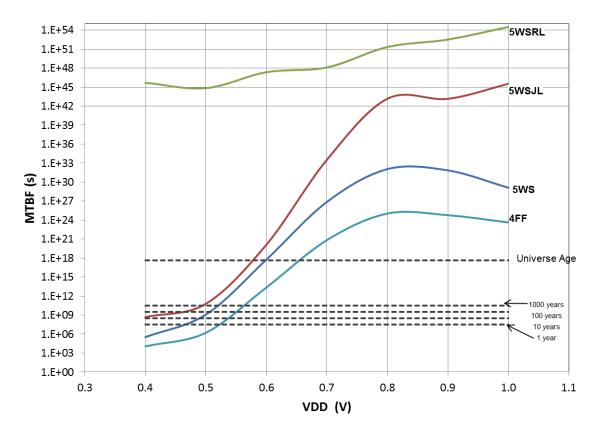

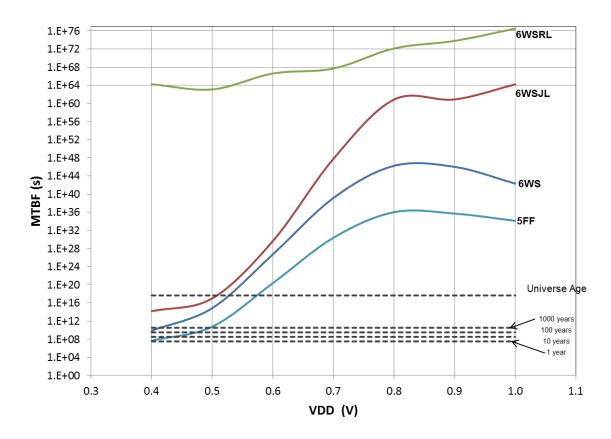

| 5.2    | MTBF Synchronizers Results                                  | 137         |

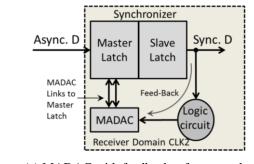

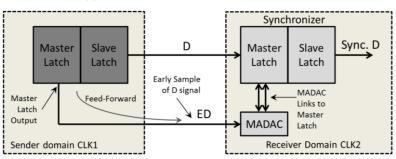

| 5.3    | Flop Synchronizer with Metastability Auto-Detection And Cor | rection140  |

| 5.3    | C-element MADAC                                             | 141         |

| 5.3    | 1                                                           |             |

| 5.3    | 8.3 Robust MADAC Latch (RML)                                | 143         |

| 5.4    | Single-Flop Synchronizers Results                           |             |

| 5.4    | .1 Impact of Supply Voltage Reduction                       | 145         |

| 5.4    | PVT Corners                                                 | 149         |

| 5.4    | 1                                                           |             |

| 5.5    | Summary                                                     |             |

| Chapte | r 6 Multiple Voltage Domain Synchronizers                   |             |

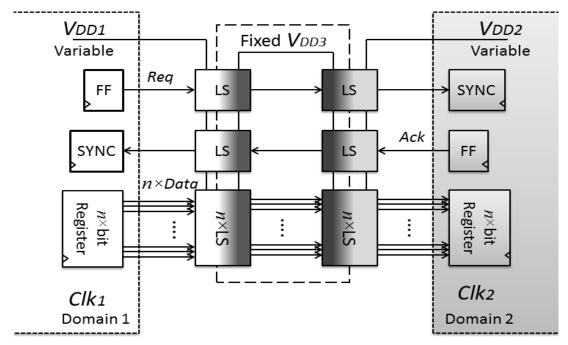

| 6.1    | Latch Level-Shifter                                         |             |

| 6.1    | .1 Dual-Supply Level-Shifting Latch                         |             |

| 6.1    | .2 Single-Supply Level-Shifting Latch                       |             |

| 6.1    | .3 Simulation Results                                       |             |

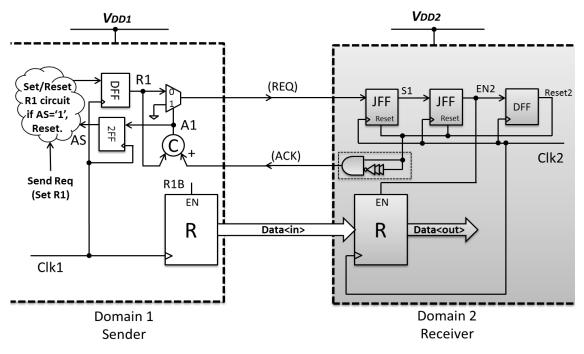

| 6.2    | Handshake Synchronization protocol for level-shifting       |             |

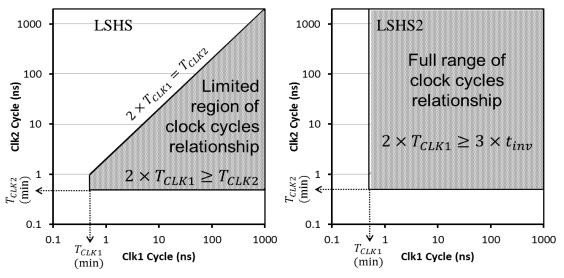

| 6.2    | 2.1 Pseudo Single-Supply Level-Shifting Handshake Synchro   | nization165 |

| 6.2    | 2.2 Pseudo LSHS2 for Wider Range of Clock Frequencies       |             |

| 6.3    | Bidirectional Level-Shifting Handshake Synchronization      | 174         |

| 6.4    | Summary                                                     |             |

| Chapter | 7    | Discussion, Conclusions and Future Work |     |

|---------|------|-----------------------------------------|-----|

| 7.1     | Disc | cussion                                 | 178 |

| 7.2     | Con  | clusions                                |     |

| 7.3     | Futi | ure Work                                |     |

|         |      |                                         |     |

| Append  | ix A | Lexicon Abbreviations                   |     |

| Append  | ix B | Symbols Annotation                      |     |

| Append  | ix C | UMC 90nm Model                          |     |

| Append  | ix D | MUTEX Circuits Simulation Results       |     |

| Append  | ix E | MADAC Technique Simulation Results      |     |

| Append  | ix F | LSHS 2 Simulations                      |     |

|         |      |                                         |     |

| Referen | ces. |                                         |     |

# List of Figures

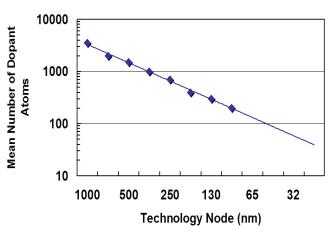

| Figure 1.1 Dopants levels [14]                                                 | 4  |

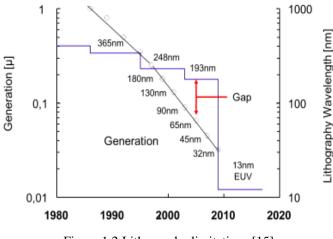

|--------------------------------------------------------------------------------|----|

| Figure 1.2 Lithography limitations [15]                                        | 5  |

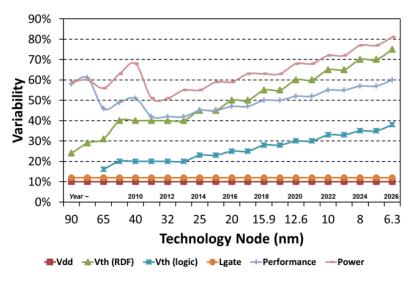

| Figure 1.3 ITRS design for manufacturability requirements [16]                 | 5  |

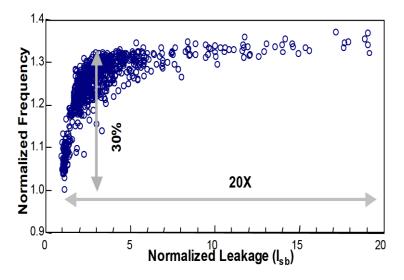

| Figure 1.4 Process variation impact frequency and leakage distribution [17]    | 6  |

| Figure 1.5 Supply voltage droop [22]                                           |    |

| Figure 1.6 Heat fluctuation across die [14]                                    | 8  |

| Figure 1.7 Alpha-particles striking substrate [4]                              | 9  |

| Figure 1.8 Error detection/recovery in flip-flop and latch circuits            | 12 |

| Figure 1.9 Triple-Modular-Redundancy technique                                 |    |

| Figure 1.10 ITRS asynchronous design requirements [16]                         | 14 |

| Figure 2.1 Data transition violation causes metastable output Q                |    |

| Figure 2.2 Metastability analogy to ball over a hill                           |    |

| Figure 2.3 Simulation waveforms of a latch going metastable                    | 23 |

| Figure 2.4 Cross-coupled inverters                                             |    |

| Figure 2.5 Intersecting point of voltage transfer characteristics of the latch | 25 |

| Figure 2.6 Symmetry and asymmetry between ratios of the two inverters          |    |

| Figure 2.7 Cross-coupled inverters parasitic capacitance and resistance        | 27 |

| Figure 2.8 Cross-coupled inverters linear amplifier model                      | 27 |

| Figure 2.9 Cross-coupled inverters transconductance model with Miller-effect   | 29 |

| Figure 2.10 Metastability detection in Razor FF [33]                           |    |

| Figure 2.11 Flip-flop with internal detection and correction feedback          |    |

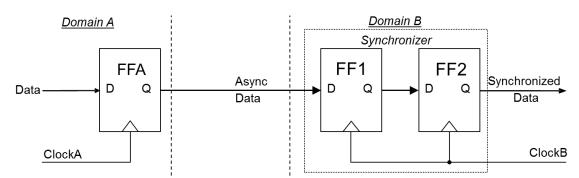

| Figure 2.5 A Two-Flip-Flop (2FF) synchronizer                                  |    |

| Figure 2.6 2FF synchronizer operation example                                  |    |

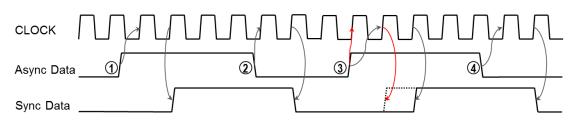

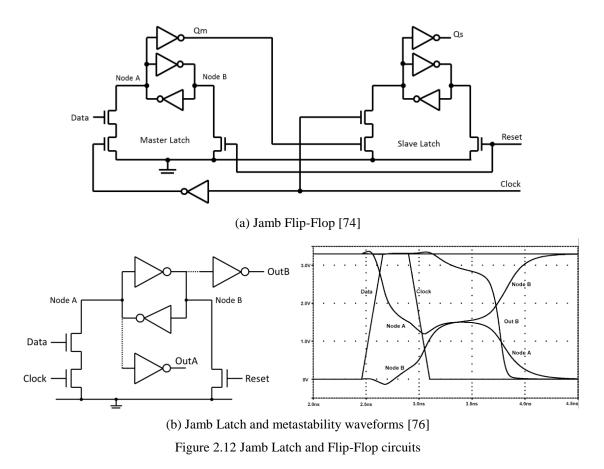

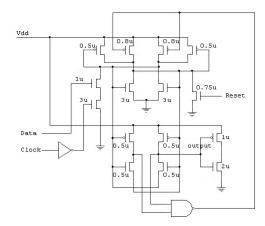

| Figure 2.12 Jamb Latch and Flip-Flop circuits                                  |    |

| Figure 2.13 A robust synchronizer [82]                                         |    |

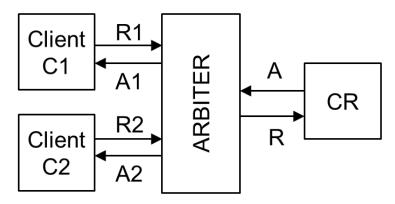

| Figure 2.14 Example of two-way arbiter                                         |    |

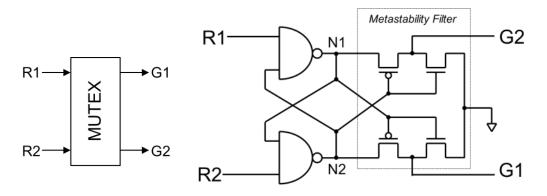

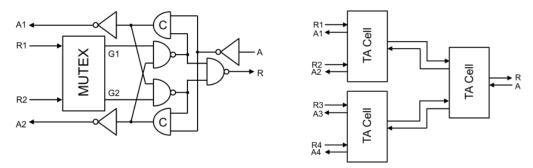

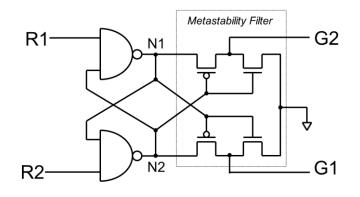

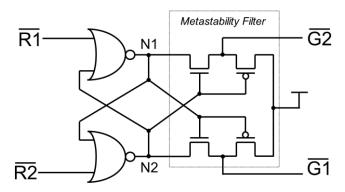

| Figure 2.15 MUTEX symbol and circuit                                           |    |

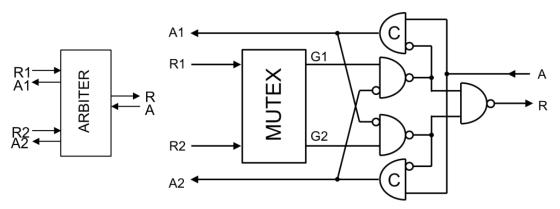

| Figure 2.16 MUTEX-based two-way arbiter                                        |    |

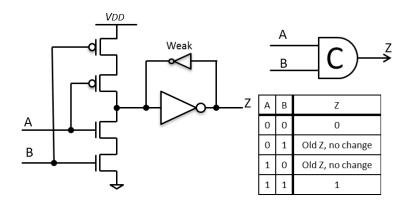

| Figure 2.17 C-element circuit                                                  |    |

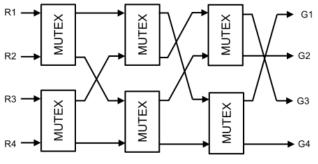

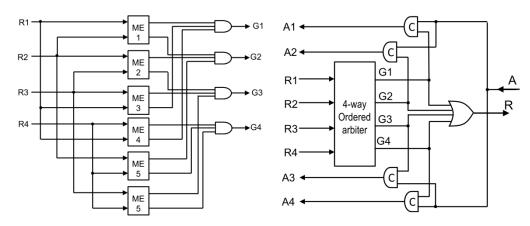

| Figure 2.18 Four-way mesh arbiter [50]                                         |    |

| Figure 2.19 Four-way tree arbiter [50]                                         |    |

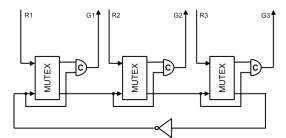

| Figure 2.20 Three-way busy ring arbiter [50]                                   |    |

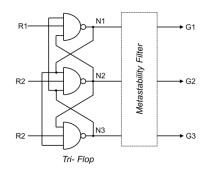

| Figure 2.21 Tri-flop arbiter [50]                                              |    |

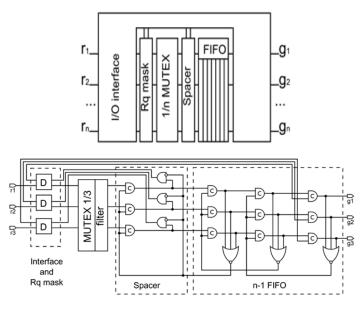

| Figure 2.22 Ordered FIFO arbiter [50, 99]                                      |    |

| Figure 2.23 Low-latency ordered arbiter [101]                                  | 50 |

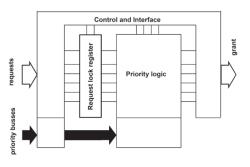

| Figure 2.24 Priority arbiter [50, 102]                                         | 51 |

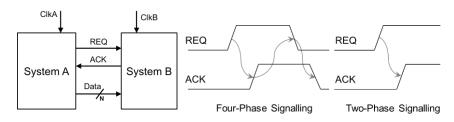

| Figure 2.25 Handshake signaling protocols                                      |    |

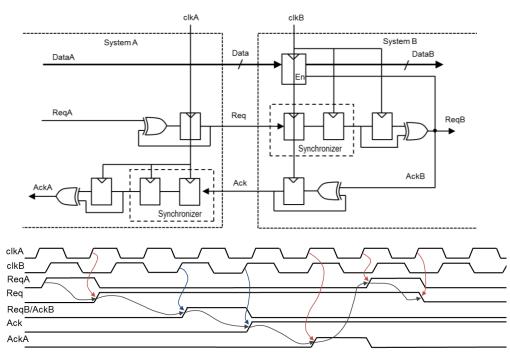

| Figure 2.26 Two-phase handshake synchronization [4]                            | 56 |

| Figure 2.27 FIFO synchronizer [70]                                             |    |

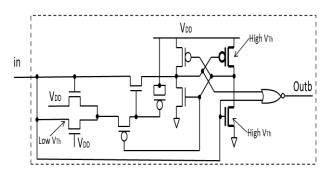

| Figure 2.28 Dual-Supply (DS) Level-Shifters (LS)                               |    |

| Figure 2.29 Single-Supply (SS) Level-Shifters (LS)                             |    |

| Figure 2.30 Example of bidirectional level-shifters [110]                      |    |

| Figure 2.31 Placement of Level Shifters [111]                                  |    |

| Figure 2.32 Handshake synchronization level-shifting requirements                                | 63  |

|--------------------------------------------------------------------------------------------------|-----|

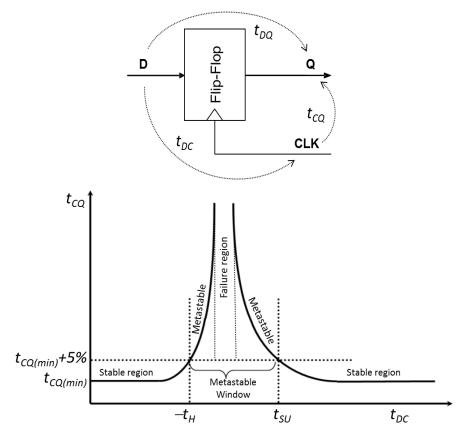

| Figure 2.33 Flip-flop timing characteristics                                                     | 64  |

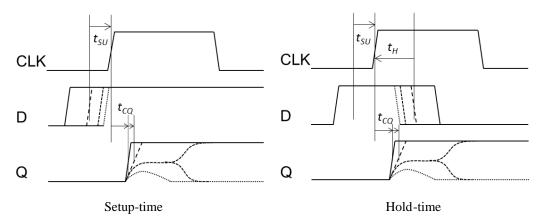

| Figure 2.34 Flip-flop setup-time and hold-time                                                   | 66  |

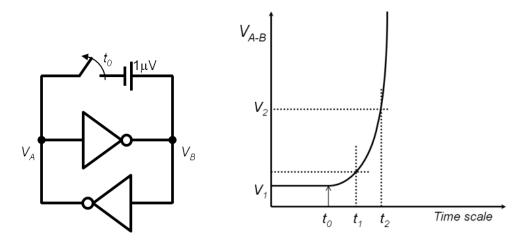

| Figure 2.35 Direct measurement of the metastability time constant                                | 69  |

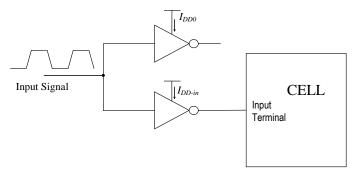

| Figure 2.36 Input driving power measurement                                                      | 70  |

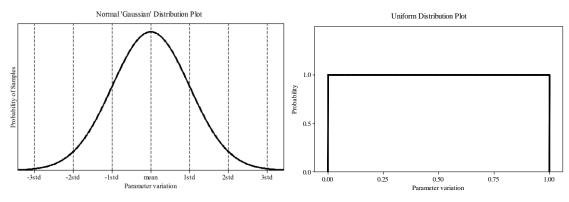

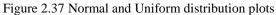

| Figure 2.37 Normal and Uniform distribution plots                                                | 71  |

| Figure 2.38 Cumulative normal distribution                                                       |     |

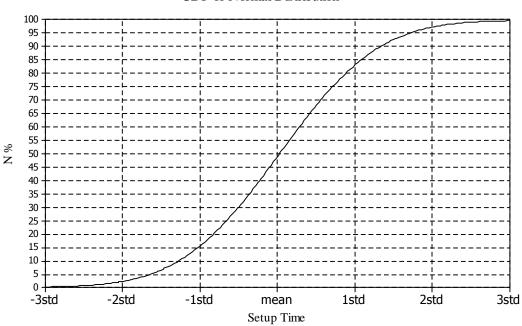

| Figure 3.1 Setup-time, hold-time and clock-to-Q time                                             | 74  |

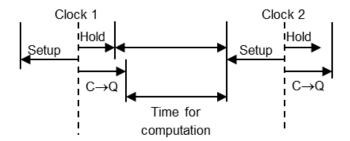

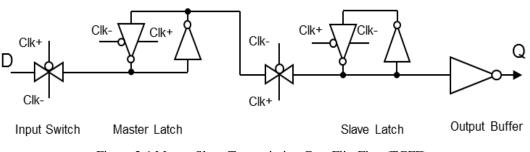

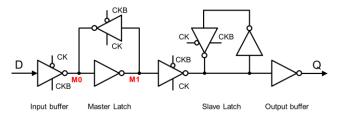

| Figure 3.2 Master Slave Edge Triggered D Flip-Flop (ETDFF)                                       | 76  |

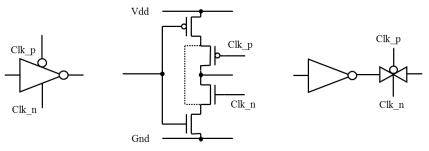

| Figure 3.3 Switched inverting buffers                                                            |     |

| Figure 3.4 Master Slave Transmission Gate Flip-Flop (TGFF)                                       | 76  |

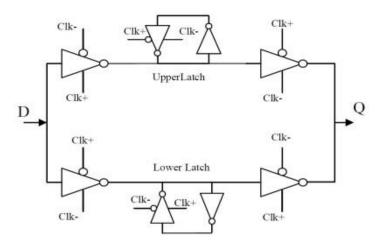

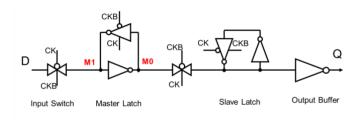

| Figure 3.5 Dual Edge Triggered Flip-Flop (DETFF).                                                |     |

| Figure 3.6 Jamb latch Synchronizer.                                                              |     |

| Figure 3.7 Robust Synchronizer with low buffer to latch ratio                                    |     |

| Figure 3.8 C-elements                                                                            |     |

| Figure 3.9 A 2FF pipeline synchronizer                                                           |     |

| Figure 3.10 A 3FF pipeline synchronizer                                                          |     |

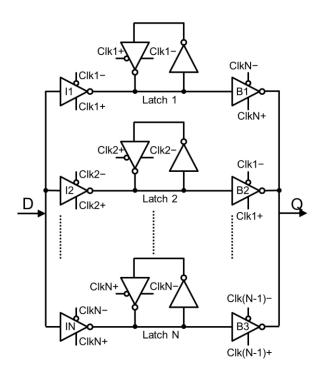

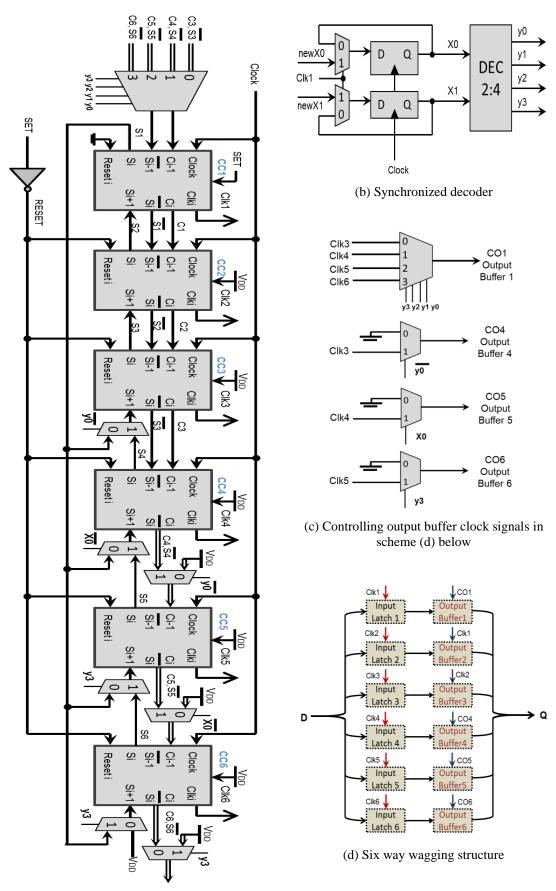

| Figure 3.11 Three-way wagging synchronizer                                                       |     |

| Figure 3.12 <i>N</i> way wagging synchronizer                                                    |     |

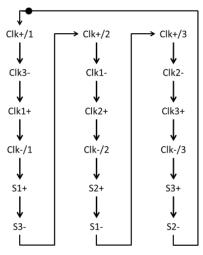

| Figure 3.13 STG for CCC                                                                          |     |

| Figure 3.14 The proposed Clocking Control Circuit (CCC)                                          |     |

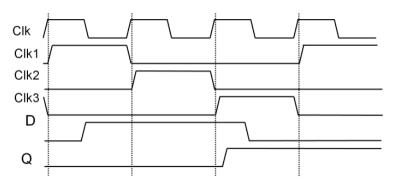

| Figure 3.15 Timing diagram of 3 clocking signals with the wagging synchronizer                   |     |

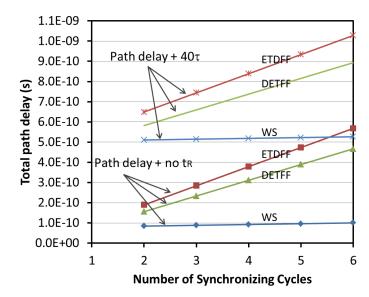

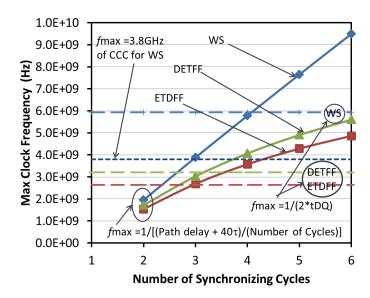

| Figure 3.16 Total path delay against the number of cycles                                        |     |

| Figure 3.17 Maximum clock frequency against the number of cycles                                 |     |

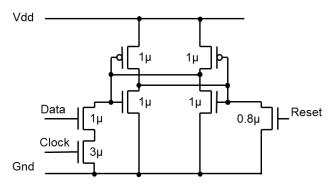

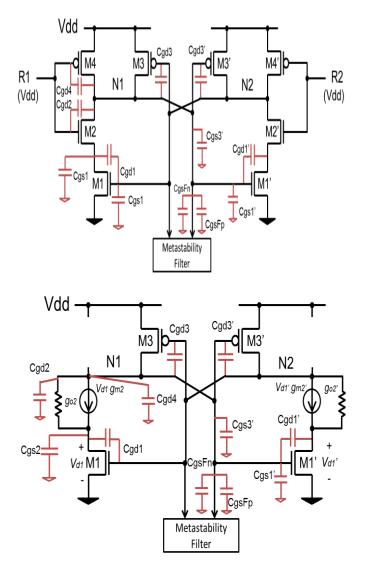

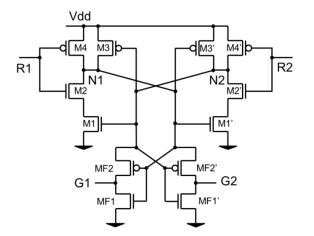

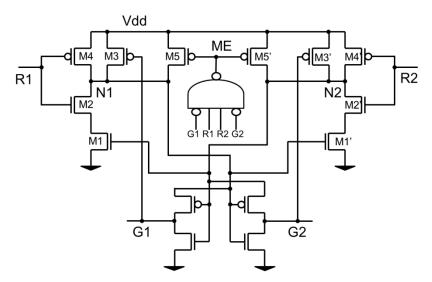

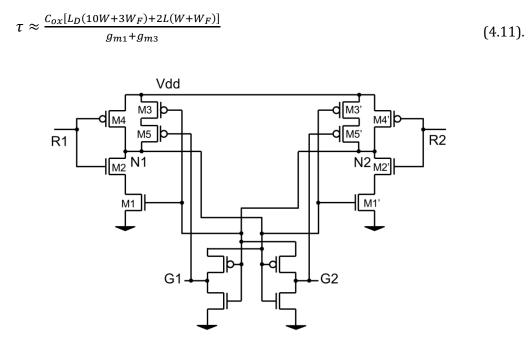

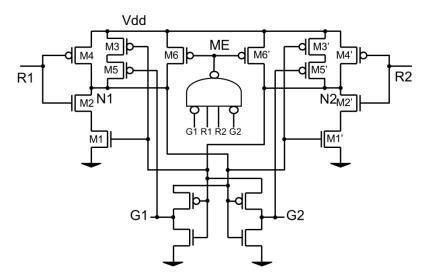

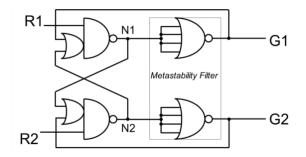

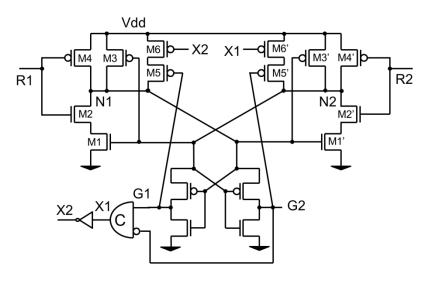

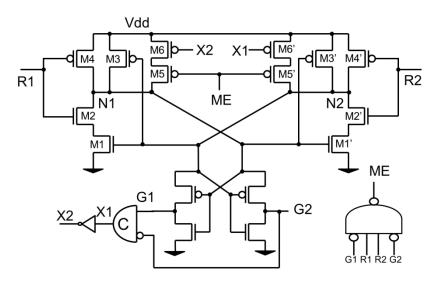

| Figure 4.1 Typical MUTEX circuits                                                                |     |

| Figure 4.2 Modelling of NAND gates during metastability                                          |     |

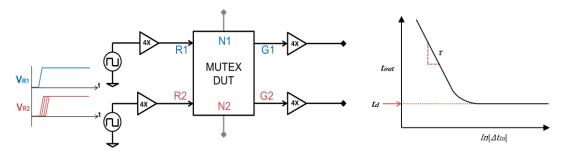

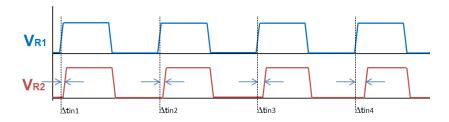

| Figure 4.3 Testing setup for simulating MUTEX performance                                        |     |

| Figure 4.4 Input-Output time curve                                                               |     |

| Figure 4.5 Input signals R1 and R2 to measure $\tau$ in one run                                  |     |

| Figure 4.6 Typical MUTEX transistor level under test                                             |     |

| Figure 4.7 Impact of Latch size ( <i>W</i> ) on $\tau$ and t <sub>d</sub> (ME0)                  |     |

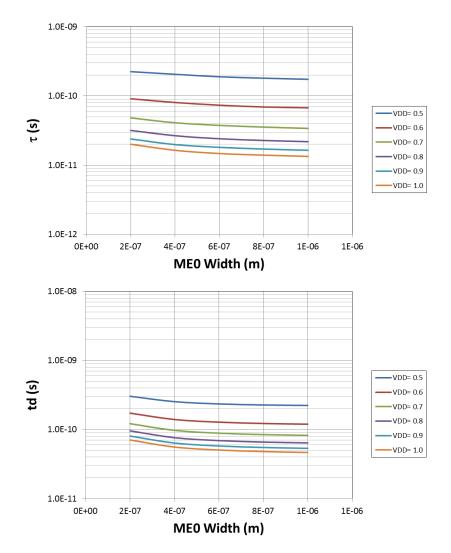

| Figure 4.8 Impact of load size ( $W_F$ ) on $\tau$ and $t_d$ (MEO)                               |     |

|                                                                                                  |     |

| Figure 4.9 Impact Voltage and Temperature on $\tau$ and $t_d$ (ME0)                              |     |

| Figure 4.10 Histograms of the impact Process Variation and Voltage on $\tau$ and $t_d$ (MEO)     |     |

| Figure 4.11 Impact of Process Variation and Voltage reduction on $\tau$ and t <sub>d</sub> (ME0) |     |

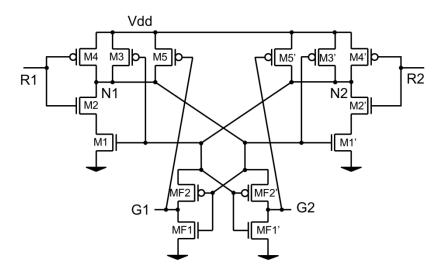

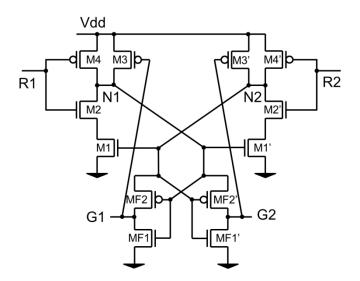

| Figure 4.12 M-MUTEX ME1A with current source biased by output feedback (ME1A)                    |     |

| Figure 4.13 M-MUTEX ME1B with current source and reduced load (ME1B)                             |     |

| Figure 4.14 M-MUTEX with <i>gm</i> boosting during metastability (ME2A)                          |     |

| Figure 4.15 M-MUTEX with <i>gm</i> boosting, current-source and reduced-load (ME2B)              |     |

| Figure 4.16 M-MUTEX with Cascode Feedback with feedback current source (ME3A)                    |     |

| Figure 4.17 M-MUTEX with Cascode and <i>gm</i> boosting (ME3B)                                   |     |

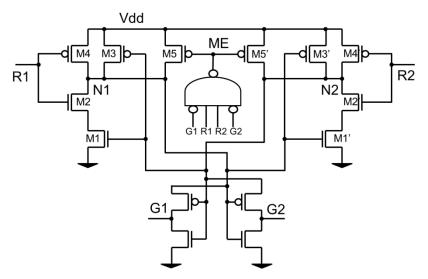

| Figure 4.18 OAI based MUTEX utilizing Cascode current source feedback (ME4A)                     |     |

| Figure 4.19 ME4A comprised of standard-cell OAI based                                            |     |

| Figure 4.20 M-MUTEX ME5A                                                                         |     |

| Figure 4.21 M-MUTEX ME5B                                                                         |     |

| Figure 4.22 Sensitivity of $\tau$ and $t_d$ to Latch width against $V_{DD}$                      |     |

| Figure 4.23 Improvement of sensitivity of $\tau$ and $t_d$ to latch width against $V_{DD}$       |     |

| Figure 4.24 Sensitivity of $\tau$ and $t_d$ to load width against $V_{DD}$                       | 115 |

| Figure 4.25 Improvement of sensitivity of $\tau$ and $t_d$ to load width against $V_{DD}$           | 116 |

|-----------------------------------------------------------------------------------------------------|-----|

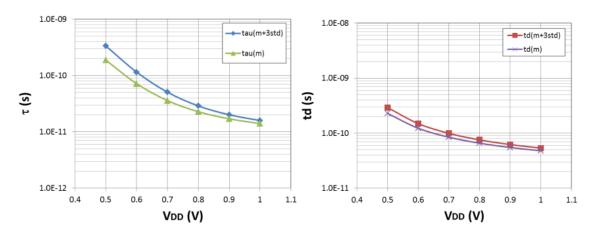

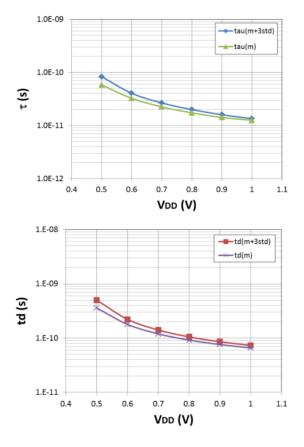

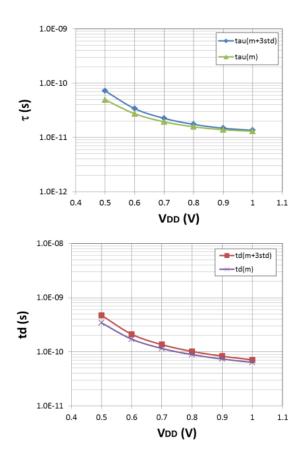

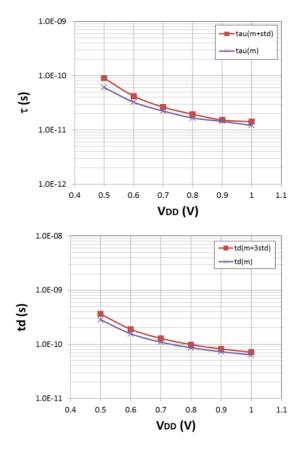

| Figure 4.26 Metastability time constant $\tau$ and delay time $t_d$ against $V_{DD}$                | 117 |

| Figure 4.27 Sensitivity $\tau$ and $t_d$ to $V_{DD}$ and Sensitivity Improvement                    | 118 |

| Figure 4.28 Ratio of $\tau$ and $t_d$ of all MUTEXes to FO4 delay of inverter against $V_{DD}$      | 118 |

| Figure 4.29 Sensitivity $\tau$ and $t_d$ to Temperature against $V_{DD}$                            | 119 |

| Figure 4.30 Sensitivity Improvement of $\tau$ and $t_d$ to temperature against $V_{DD}$             | 120 |

| Figure 4.31 Ratio of standard deviation of $\tau$ and $t_d$ to that of FO4 delay against $V_{DD}$   | 122 |

| Figure 4.32 Improvement of standard deviation of $\tau$ and $t_d$ to that of MEO against $V_{DD}$ . | 123 |

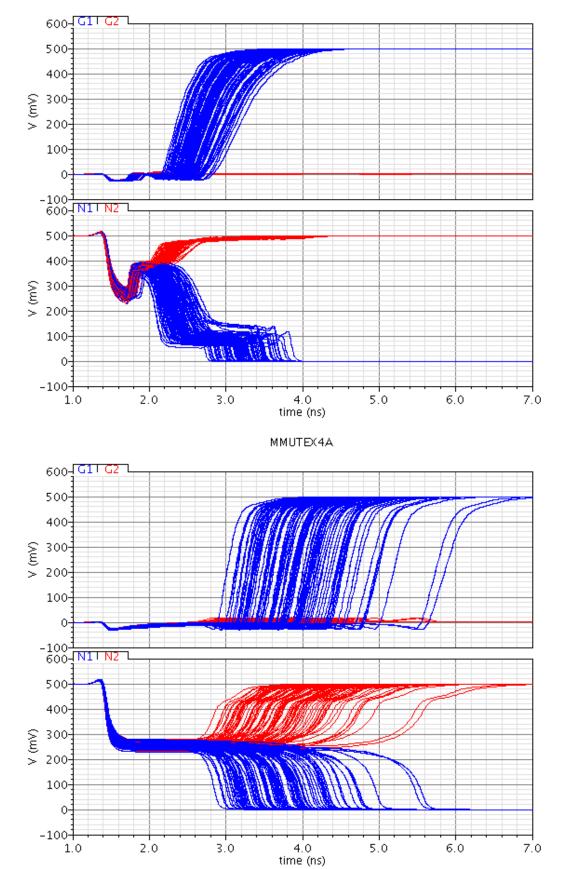

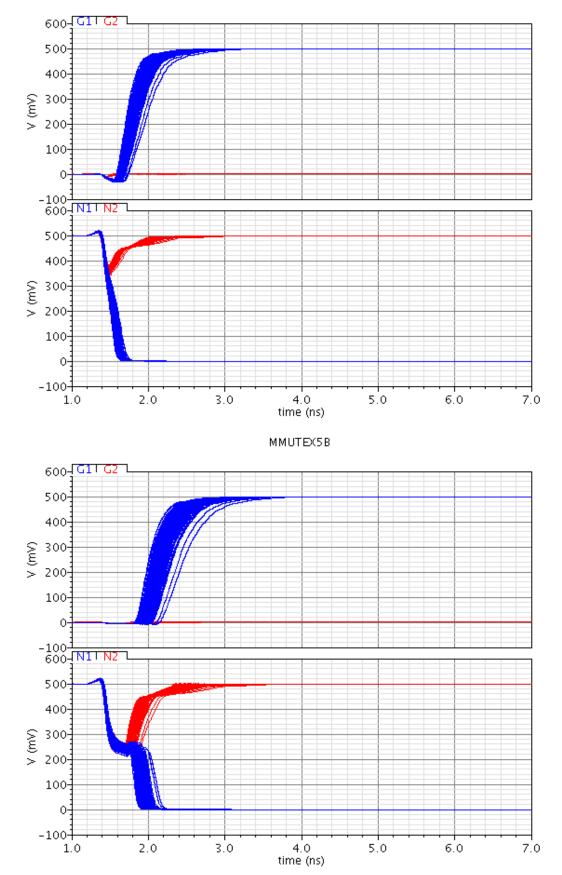

| Figure 4.33 Monte Carlo waveforms of metastability resolution at 0.5V                               | 124 |

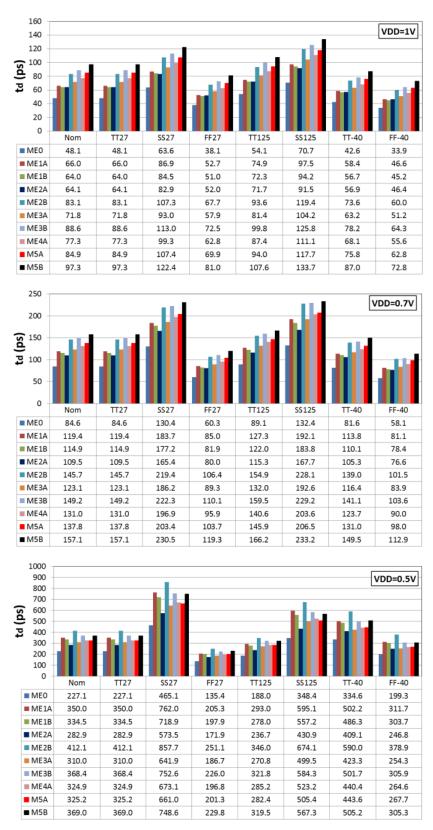

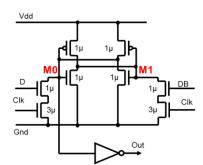

| Figure 4.34 PVT corners effect on τ                                                                 | 125 |

| Figure 4.35 PVT corners effect on t <sub>d</sub>                                                    |     |

| Figure 5.1 Latch and flip-flop circuits                                                             | 130 |

| Figure 5.2 Improved τ wagging synchronizer circuits                                                 |     |

| Figure 5.3 An asynchronous state cell to control a clocking signal                                  |     |

| Figure 5.4 Timing diagram of signals in one CCC                                                     |     |

| Figure 5.5 Reconfiguring CCC to produce clocking signals from three to six signals                  |     |

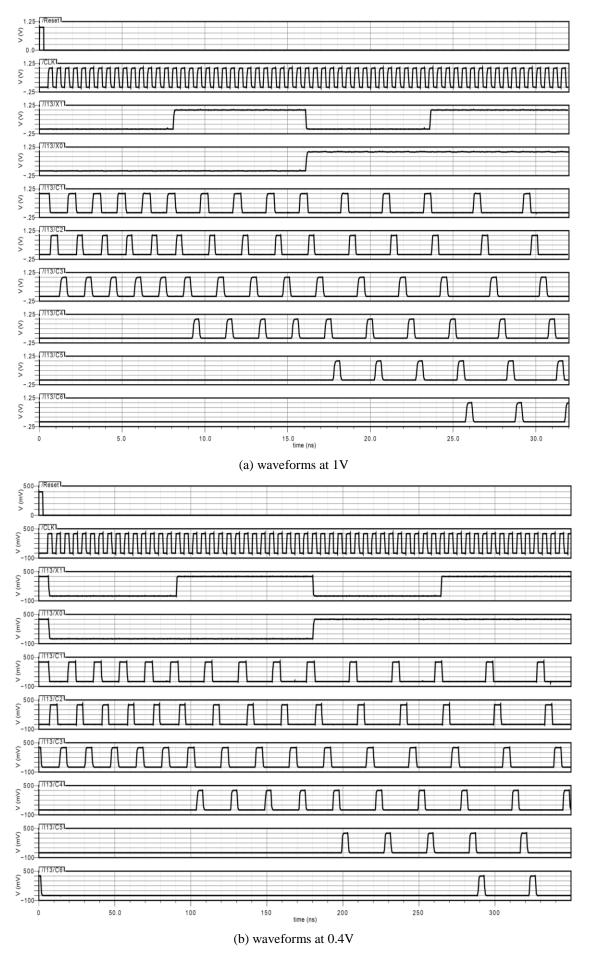

| Figure 5.6 Reconfigurable CCC operates at 1.0V and 0.4V                                             |     |

| Figure 5.7 MTBF of flip-flop and wagging synchronizers ( $f_d = f_{clk} = \max f_{clk}$ )           |     |

| Figure 5.8 MTBF of flip-flop and wagging synchronizers ( $f_d = f_{clk} = \max f_{clk}$ )           |     |

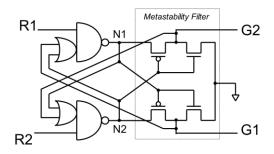

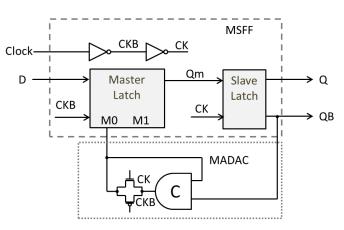

| Figure 5.9 MADAC technique                                                                          |     |

| Figure 5.10 C-element plus TG MADAC with feedback                                                   |     |

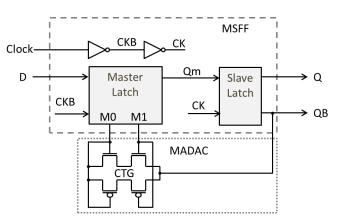

| Figure 5.11 CTG MADAC with feedback                                                                 |     |

| Figure 5.12 CTG MADAC with stable feedback                                                          |     |

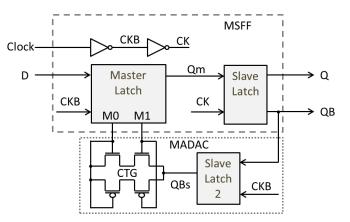

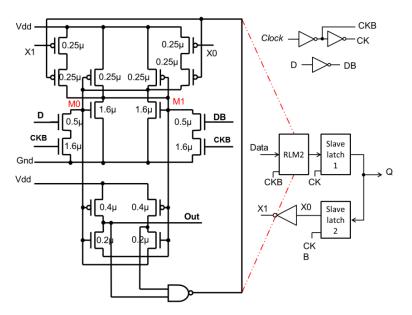

| Figure 5.13 Robust MADAC Latch (RML) circuit with feedback reference                                |     |

| Figure 5.14 Movement of the metastable point in RL and RML                                          |     |

| Figure 5.15 Device under test simulation setup                                                      |     |

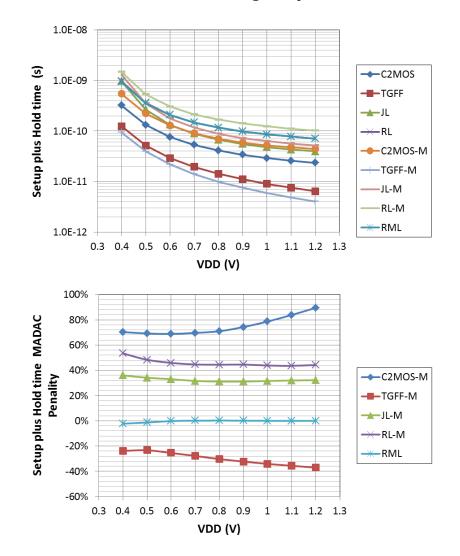

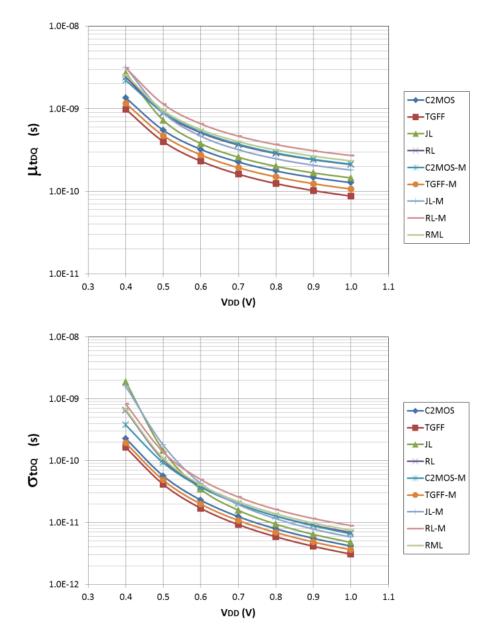

| Figure 5.16 Metastability time constant of flip-flops without and with MADAC                        |     |

| Figure 5.17 Data to Q delay time of flip-flops without and with MADAC                               |     |

| Figure 5.18 Setup and Hold 'window' time of flip-flops without and with MADAC                       |     |

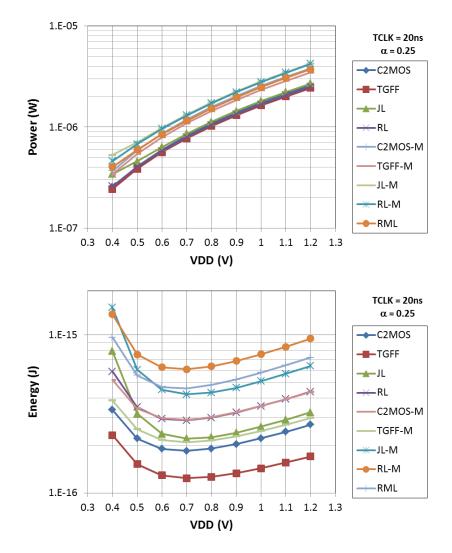

| Figure 5.19 Power and energy measurements                                                           |     |

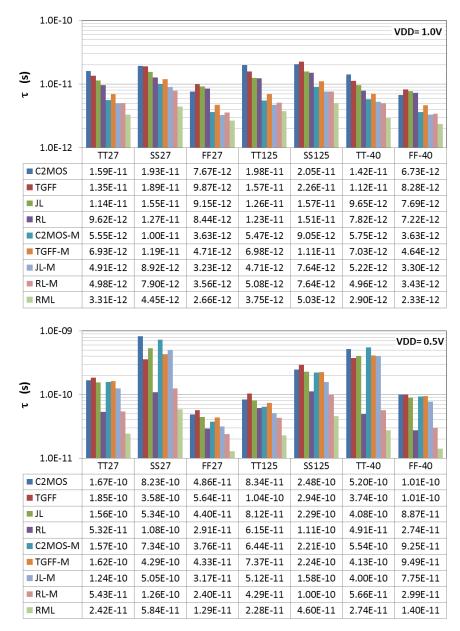

| Figure 5.20 τ response to PVT corners                                                               |     |

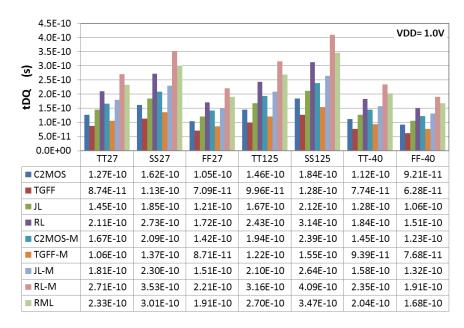

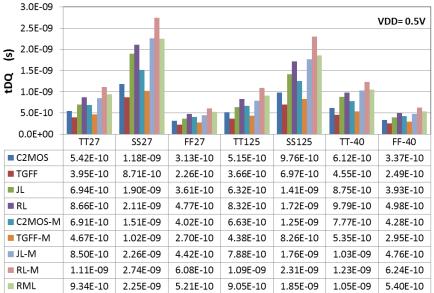

| Figure 5.21 D to Q delay time response to PVT corners                                               |     |

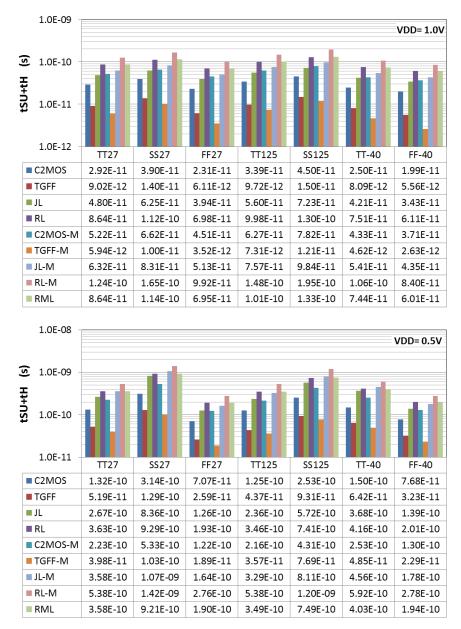

| Figure 5.22 Setup plus hold 'window' time response to PVT corners                                   |     |

| Figure 5.22 Secup plus notal window time response to $1.11$ corners                                 |     |

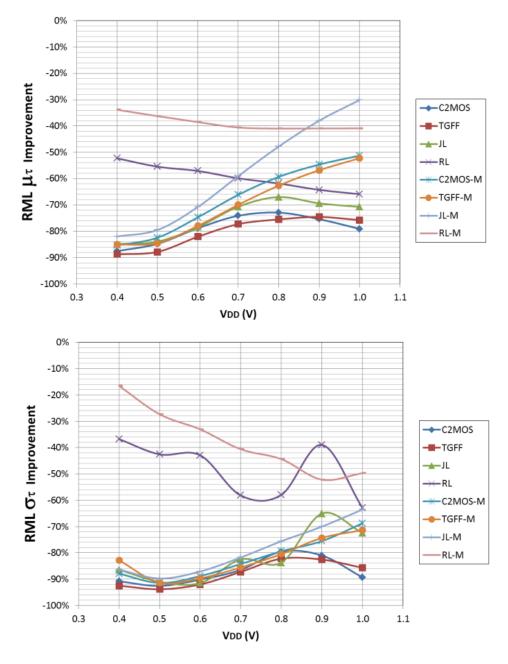

| Figure 5.24 Robust MADAC Latch Improvement of $\tau$ variability compared to others                 |     |

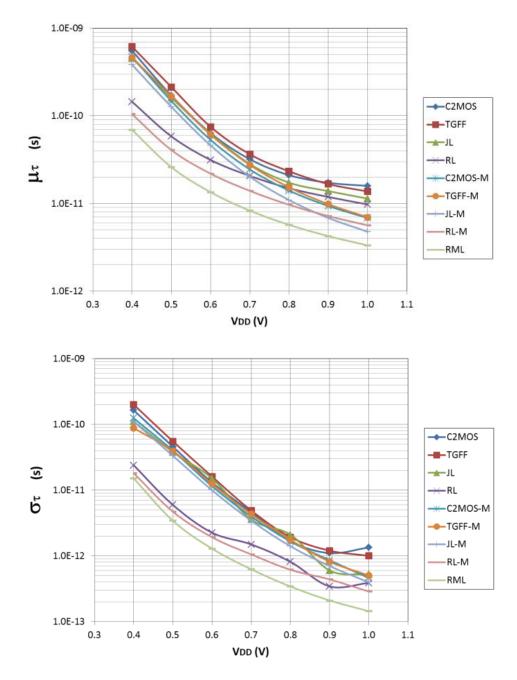

| Figure 5.25 Mean and standard-deviation of D to Q time                                              |     |

| Figure 5.26 Mean and standard-deviation of setup plus hold times                                    |     |

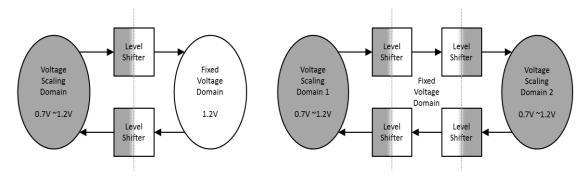

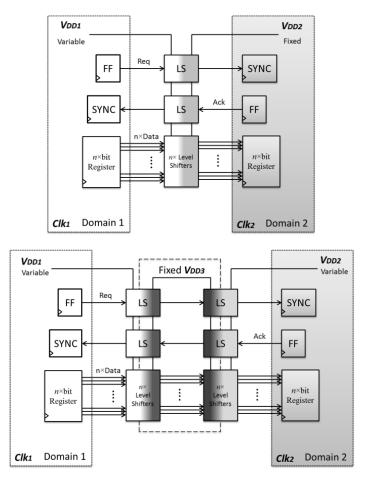

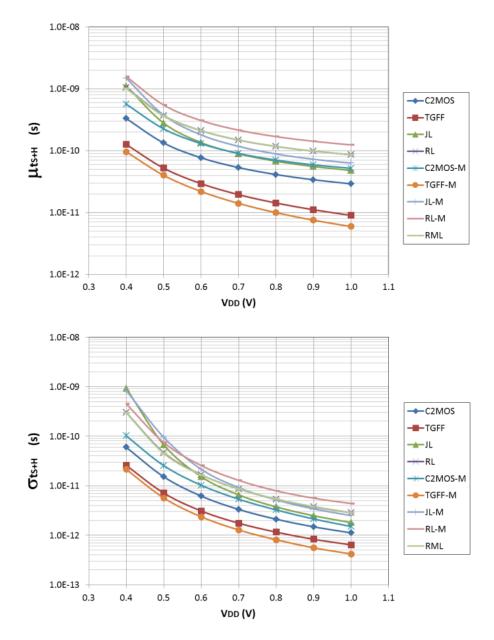

| Figure 6.1 Handshake between variable MVD/MCD domains                                               |     |

| Figure 6.2 Jamb Latch with differential input as a dual-supply level-shifter                        |     |

| Figure 6.3 Upshifting 0.7V to 1.1V in Jamb Latches                                                  |     |

| Figure 6.4 Jamb Latch flip-flop with reset as a single-supply level-shifter                         |     |

| Figure 6.5 Range of level-shifting at nominal corner                                                |     |

|                                                                                                     |     |

| Figure 6.6 Range of level-shifting at slow process corner and 120°C temperature                     |     |

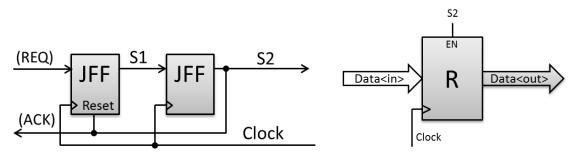

| Figure 6.7 Receiving LS synchronizer                                                                |     |

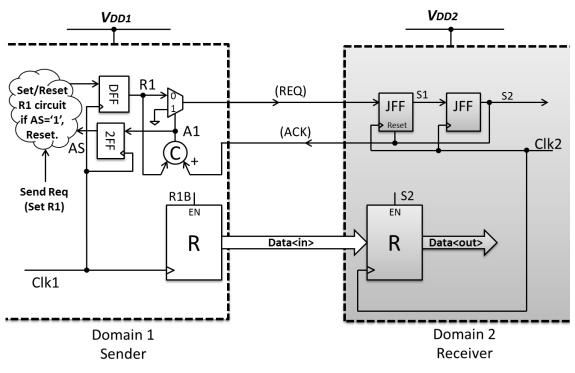

| Figure 6.8 Sender handshake circuit to send request and receive acknowledgment                      |     |

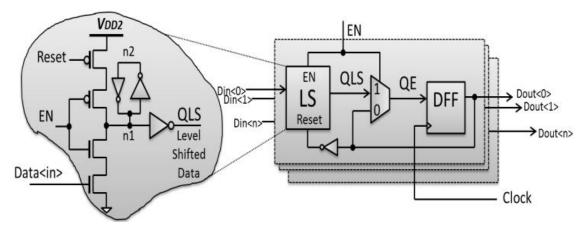

| Figure 6.9 Data-register with resettable input latch acting as a level-shifter                      |     |

| Figure 6.10 LSHS scheme                                                                             |     |

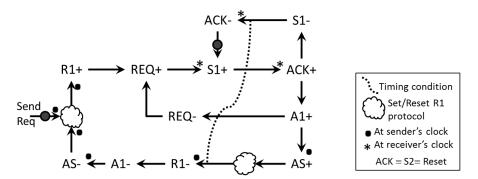

| Figure 6.11 Operation of LSHS STG diagram                                                           | 168 |

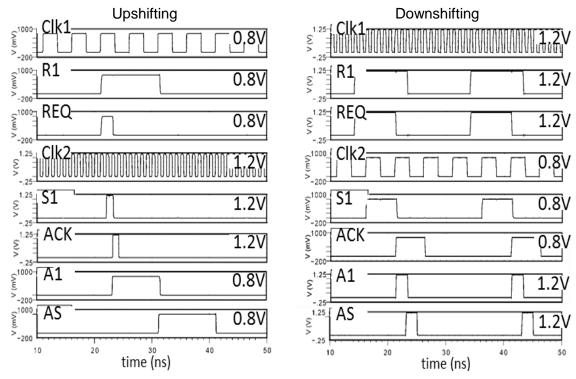

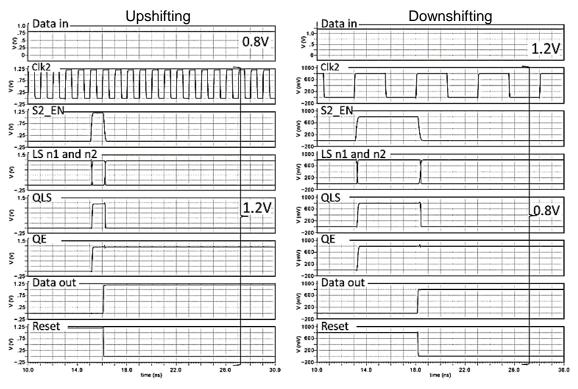

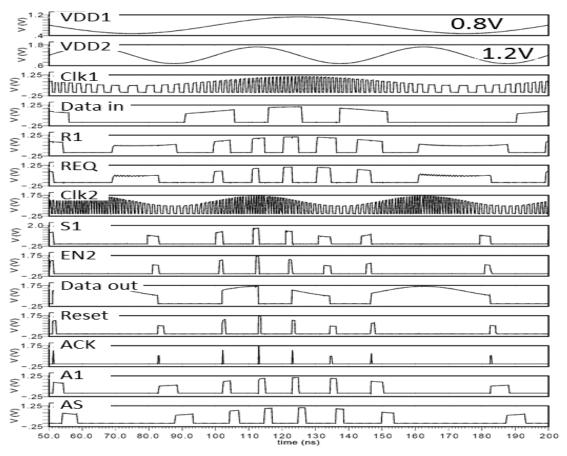

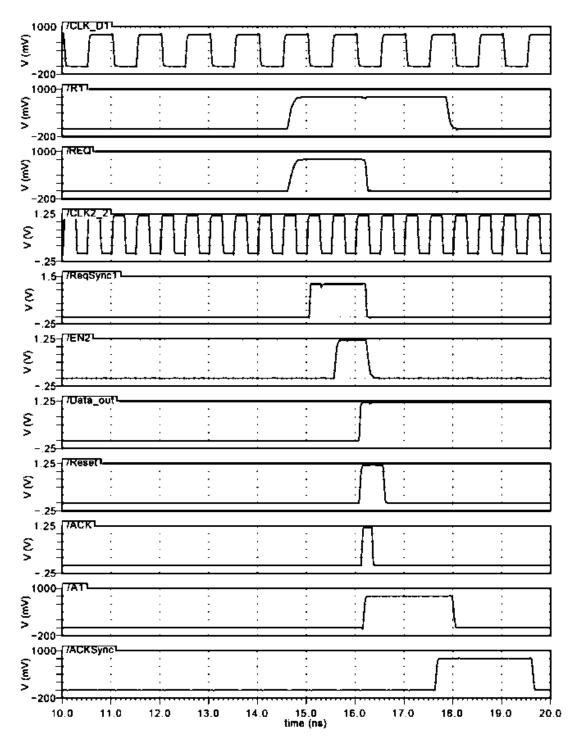

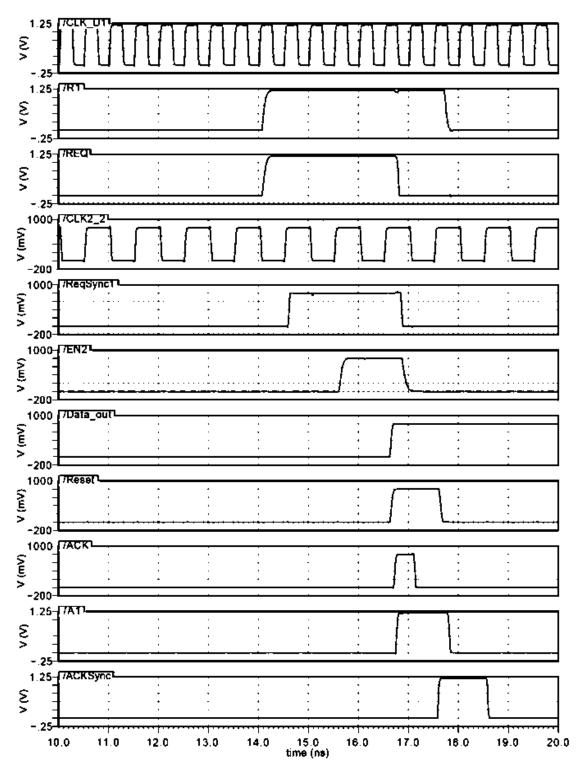

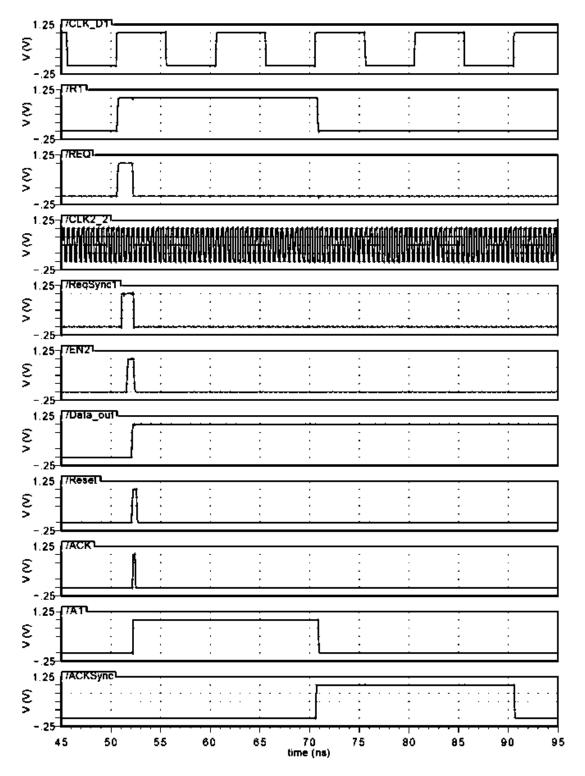

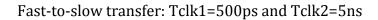

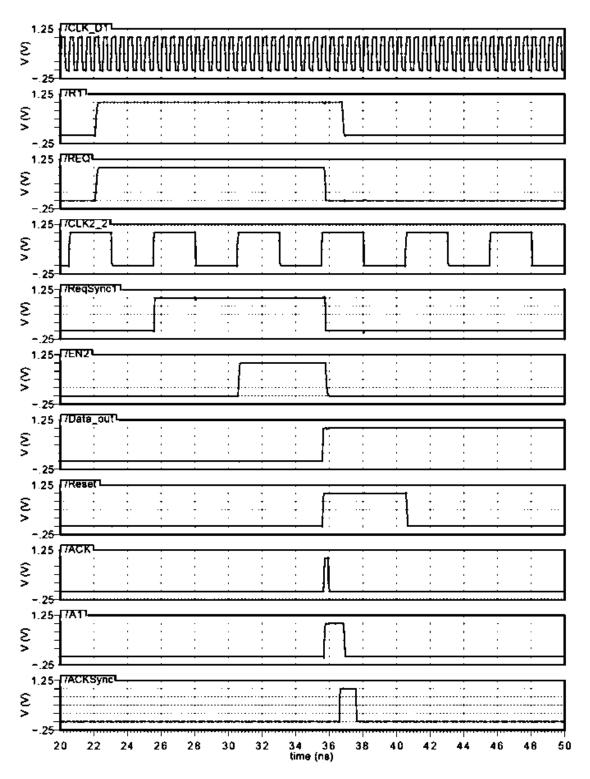

| Figure 6.12 LSHS interface waveforms                                       | 169 |

|----------------------------------------------------------------------------|-----|

| Figure 6.13 Data passing through the register at receiving end of the LSHS | 169 |

| Figure 6.14 Pseudo LSHS2 scheme                                            | 170 |

| Figure 6.15 Clocks cycles defined ranges for LSHS and LSHS2                | 171 |

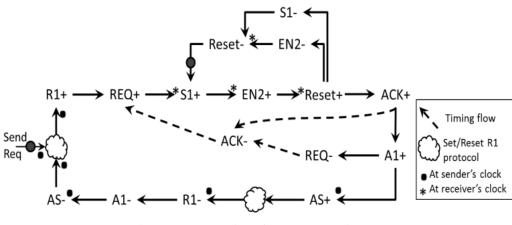

| Figure 6.16 Operation of LSHS2 STG diagram                                 | 171 |

| Figure 6.17 LSHS2 interface waveforms                                      | 172 |

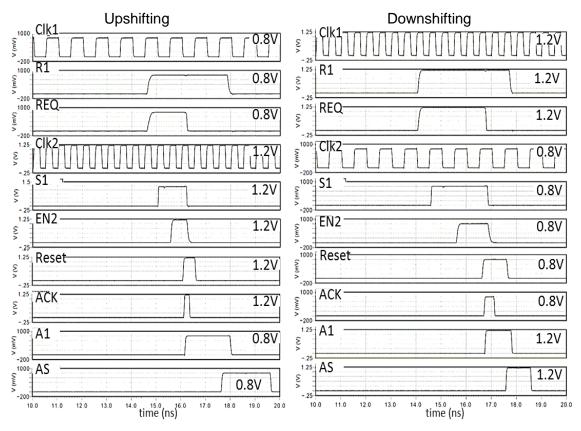

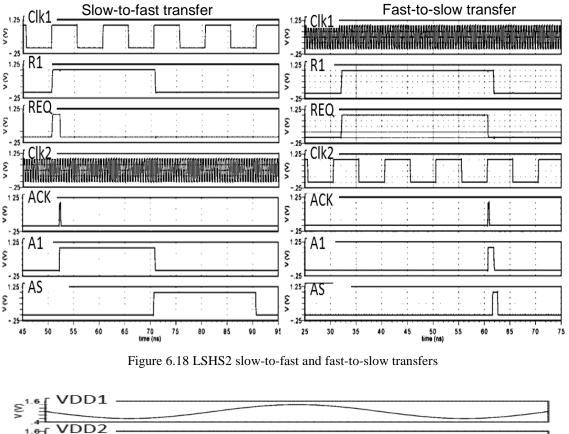

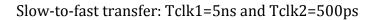

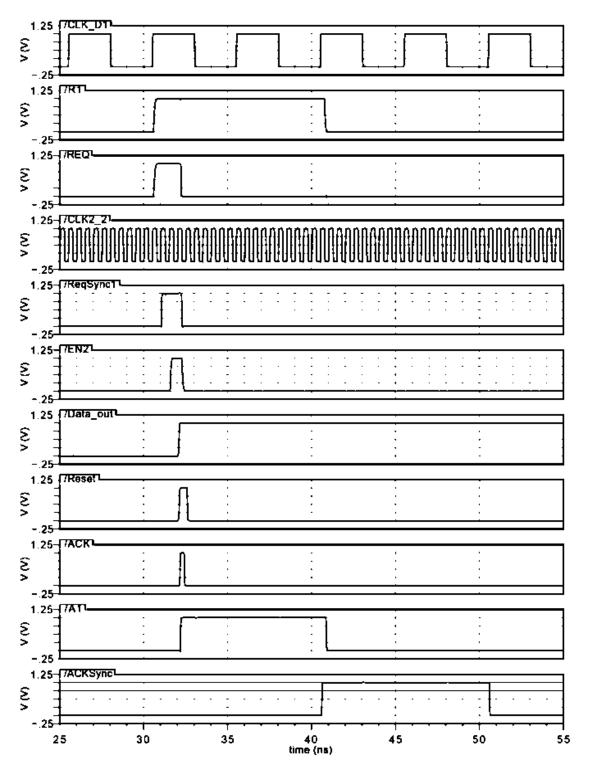

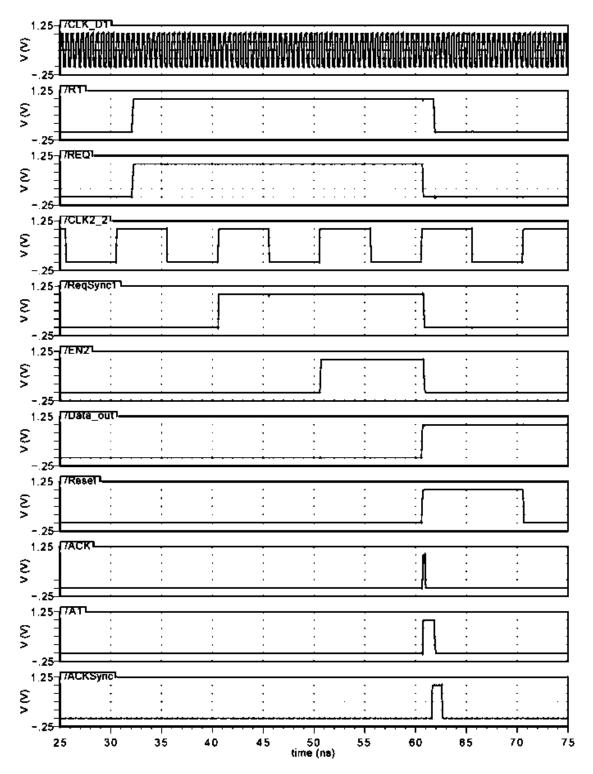

| Figure 6.18 LSHS2 slow-to-fast and fast-to-slow transfers                  | 173 |

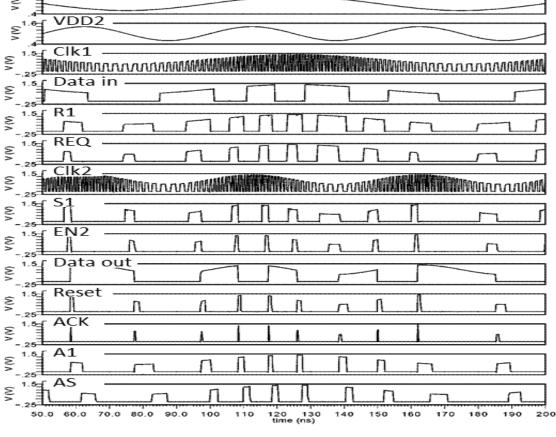

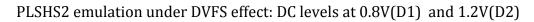

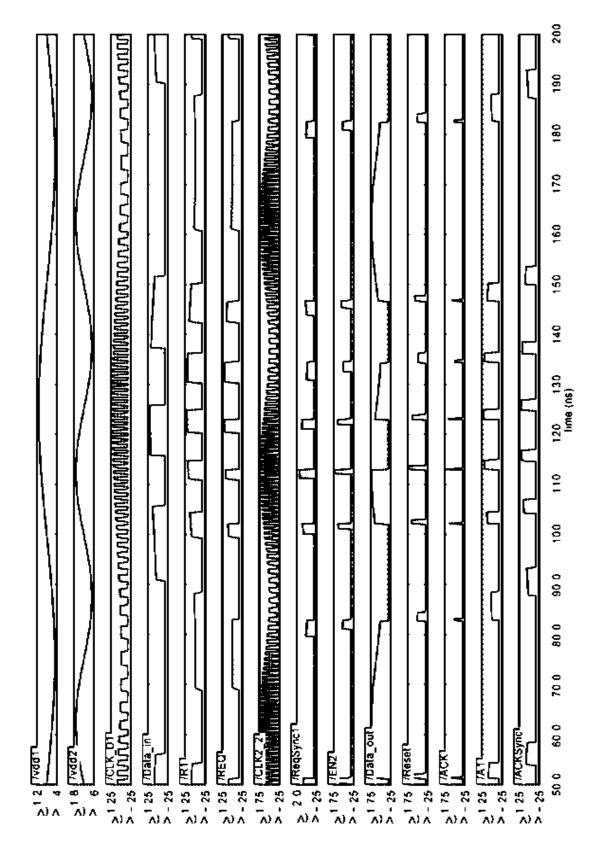

| Figure 6.19 LSHS2 emulation under DVFS effect: DC level at 1V              | 173 |

| Figure 6.20 LSHS2 emulation under DVFS effect with different DC levels     | 174 |

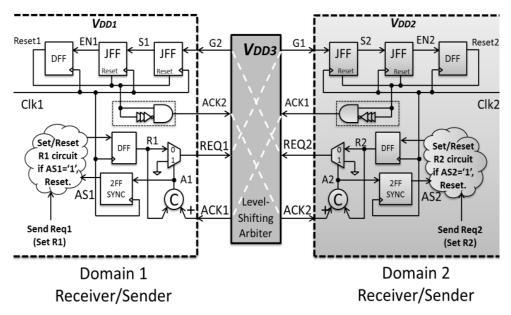

| Figure 6.21 Pseudo bidirectional LSHS scheme                               | 175 |

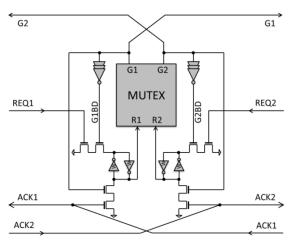

| Figure 6.22 Level-shifting arbiter                                         | 175 |

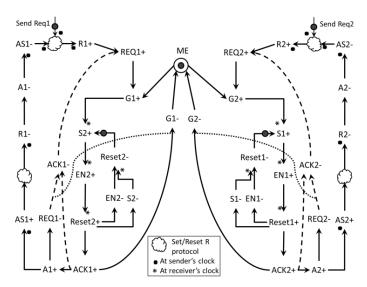

| Figure 6.23 STG diagram of the bidirectional LSHS                          | 176 |

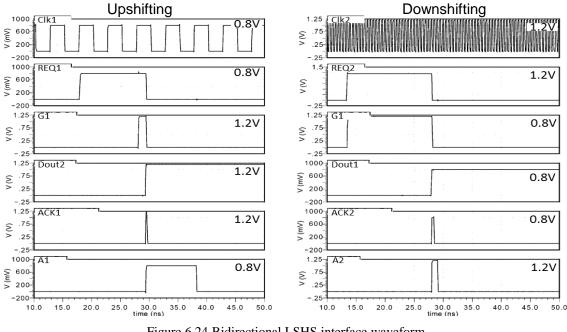

| Figure 6.24 Bidirectional LSHS interface waveform                          | 176 |

## List of Tables

| Table 1.1 Summary of scaling impact on CMOS transistor parameters [4]                | 2   |

|--------------------------------------------------------------------------------------|-----|

| Table 1.2 Scaling of UMC CMOS technology (logic/mixed-mode data) [6]                 | 3   |

| Table 3.1 Setup plus Clock to Q time                                                 | 79  |

| Table 3.2 Setup plus hold time                                                       | 79  |

| Table 3.3 Resolution time constant $	au$                                             | 79  |

| Table 3.4 Flip-Flop Comparison                                                       |     |

| Table 3.5 Comparing two flip-flop and wagging synchronizers                          | 90  |

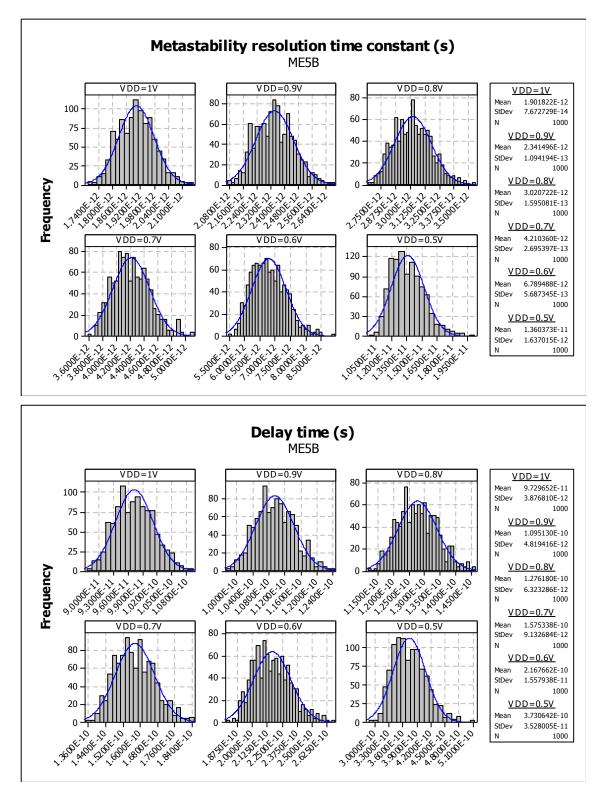

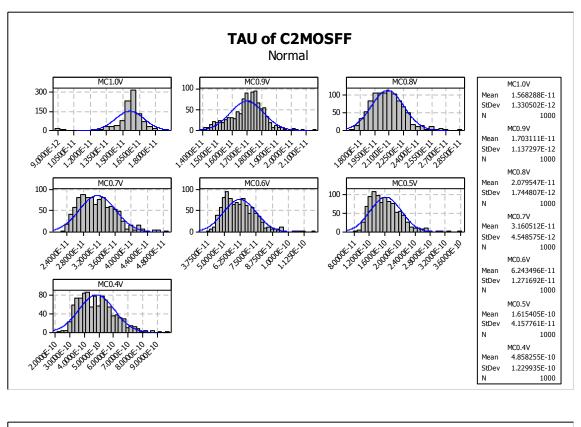

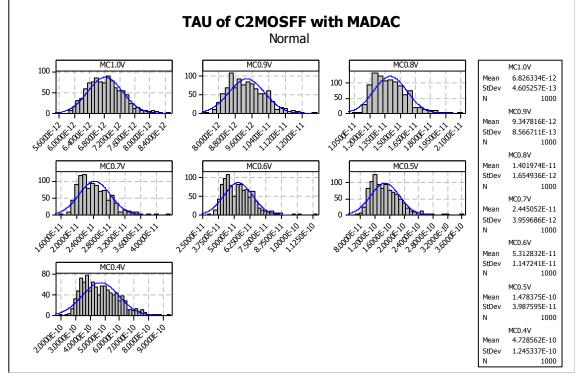

| Table 4.1 Response of $	au$ to ±3 $\sigma$ 1000 runs Monte Carlo process variation   | 121 |

| Table 4.2 Response of $t_d$ to $\pm 3\sigma$ 1000 runs Monte Carlo process variation | 122 |

| Table 5.1 6 way reconfigurable wagging synchronizer                                  | 133 |

| Table 5.2 Maximum main clock frequency to operate the clocking circuit               | 134 |

| Table 6.1 Level-Shifting Jamb Latch (LSJL) Flip-Flop                                 | 163 |

| Table 6.2 Level-Shifting Robust Latch (LSRL) Flip-Flop                               | 164 |

|                                                                                      |     |

## Chapter 1 Introduction

Increasing unpredictability and vulnerability to process, voltage and temperature variations in sub-nano CMOS process technologies suggests that current optimal designs in cell libraries must be reviewed and refined. Many VLSI systems and architectures are designed with more asynchronous cells, which need to be made more resilient to these variations. Cells which particularly affect the performance of systems on silicon include synchronizers and arbiters, which affect the latency between independently clocked processors and asynchronous systems, and register bits which require a time to set and hold data. These effects are expected to increase as technology nodes reach the level of 32nm and beyond [1].

In the subsequent sections of this chapter, the sources of variability and their impact on device parameters and circuit performance are surveyed. Thereafter, some of the techniques to reduce the effects of variability are reviewed. Then, the thesis motivation is stated, followed by the thesis main contributions, and finally the thesis organization.

### 1.1 Technology and Variability

In this section, the nature of scaling CMOS transistors' process technology nodes and their effects are discussed. Then, the common sources of performance variability of CMOS devices and circuits are reviewed, mainly in terms of process, voltage and temperature, as well as radiation.

#### 1.1.1 CMOS Transistor Scaling

The scaling down of transistor dimensions leads to reduction in cost and improvement in performance per unit transistor. Technology scaling main goals, for a logic gate, are to reduce its delay time, increase its density, and decrease its energy per switching operation [2]. At the present time, the scaling rate of the feature size is 0.7X of transistor dimensions per two to three years [1, 3, 4] corresponding to Moore's Law [4, 5]. The reduction of gate size showed a decrease

in the delay time by 30%, an increase of its density by two times and a reduction in the consumed energy per switching operation by 65%. This leads to an increase in clock frequency of 43% along with lowered power consumption by 50%. Over the years, since the start of integrated circuit technologies in the 1960s, the size of one transistor continued to shrink from a few microns down to tens of nanometers today, which kept leading to a greater integration capacity. Similarly, the amount of energy needed for charging and discharging capacitors is reduced due not only to the reduction in capacitor area but also the reduction in supply voltage down to 1V, as a result of that, the energy for writing or reading one data bit is decreased. Table 1.1 summarizes the impact of scaling on CMOS transistor parameters [4], where *S* is the scaling factor. Table 1.2 shows an example highlighting the scaling impact on transistor parameters of UMC CMOS process technology nodes from 250nm down to 65nm[6].

| Device parameters                          | Scaling effect |

|--------------------------------------------|----------------|

| Dimensions: L, W, t <sub>ox</sub>          | 1/S            |

| Voltages: $V_{DD}$ , $V_{THn}$ , $V_{THp}$ | 1/ <i>S</i>    |

| Doping concentration density               | S              |

| Drain Current: <i>I</i> <sub>DS</sub>      | 1/ <i>S</i>    |

| Conductance: $g_{out}$ and $g_m$           | 1              |

| Gate capacitance: <i>C</i> <sub>gate</sub> | 1/S            |

| Delay: <i>RC</i>                           | 1/ <i>S</i>    |

| Clock frequency                            | S              |

| Power and Area                             | $1/S^{2}$      |

| Energy                                     | $1/S^{3}$      |

Table 1.1 Summary of scaling impact on CMOS transistor parameters [4]

On the other hand, scaling down of global interconnect dimensions do not follow the scaling of local ones nor the transistor dimensions, which lowers the overall performance [2]. Basically, scaling wires results in the increase of the wire resistance per unit length by a factor of  $S^2$ , whereas, the wire capacitance per unit length is constant. Overall, the chip area should be halved every two consecutive technology nodes, however, as more transistors and functions are integrated on a single chip in recent designs, the need to increase the area of the chip is accompanied by an increase in global interconnect length and RC time constant.

| Technology node           | 250nm       | 180nm       | 130nm       | 90nm        | 65nm        |

|---------------------------|-------------|-------------|-------------|-------------|-------------|

| Substrate Type            | P-substrate | P-substrate | P-substrate | P-substrate | P-substrate |

| Poly Layers               | 1           | 1           | 1           | 2           | 1           |

| Metals Layers             | 5           | 6           | 8           | 9           | 10          |

| L <sub>min</sub> (µm)     | 0.24        | 0.18        | 0.12        | 0.08        | 0.06        |

| W <sub>min</sub> (μm)     | 0.3         | 0.24        | 0.16        | 0.12        | 0.08        |

| $T_{OXn}$ (nm)            |             | 7.0         | 2.63        | 2.25        | 2.05        |

| $V_{DD}$ Core (V)         | 2.5         | 1.8         | 1.2         | 1           | 1.0~1.2     |

| V <sub>ton</sub> NMOS (V) | 0.54        | 0.51        | 0.47        | 0.33        | 0.23        |

| V <sub>ton</sub> PMOS (V) | -0.58       | -0.5        | -0.42       | -0.277      | -0.19       |

| Core delay (ps/stage)*    | 40          | 27          | 19.6        | 10.6        | 6           |

Table 1.2 Scaling of UMC CMOS technology (logic/mixed-mode data) [6]

\* A stage accounts for one logic inverter gate delay in a ring oscillator without load.

#### 1.1.2 Sources of Variability

The performance of circuits is dictated by the characteristics of devices and interconnects and operating conditions. Parametric variability is any change in the design due to deviations in the chip's internal or external characterizing parameters. Variability in performance could be permanent or temporary [7-9]. Process variations cause permanent physical alterations to the wafer down to atomic level. On the other hand, deviation in supply voltage and surrounding temperature only impact on circuit operation briefly unless it exceeds a maximum value. Also, external radiation particles striking the transistor lattice could introduce temporary failures. Hence, these are considered temporary environmental variations. Variations also can be categorized as environmental or physical variations [7-9]. Environmental variations typically include changes in surrounding temperature and supply voltage. Physical parameters normally are independent of time and constitute the majority of process variations that occur during the manufacturing process.

In the following section the sources of process, supply voltage and temperature (PVT) variations, as well as radiation, together with their impact on the performance of CMOS circuits will be outlined.

#### 1.1.2.1 Process Variability

Manufacturing process imperfections, such as poor masking, are the main source

of process variations. These variations include any alteration in process parameters which characterize the behavior of passive and active devices. These parameters include transistor dimensions, threshold voltage, oxide-thickness and carrier mobility, as well as the capacitance and resistance of interconnects. Process variations can be grouped into two broad areas: spatial and temporal [7, 10, 11].

Spatial process variations are divided into two categories: die-to-die variations and within-die variations [7, 10, 11]. Die-to-die variations refer to the deviation from the chips' mean value and affect all devices in the same chip, they are sometimes referred to as inter-die variations. On the other hand, within-die variations (also known as intra-die variations) occur when there is a spatial deviation or mismatches across a single chip, they are mainly caused by random doping levels, and lithograph limitations, which therefore affect the certainty of device threshold voltage and mobility [12, 13].

The effects of fluctuation and randomness of doping in a device channel become more challenging with scaling of technology, because the number of dopant atoms in the channel of a transistor has reduced exponentially [14], as shown in Figure 1.1. Therefore, the total number and location of atoms in the device channel becomes highly significant in the deviation of the threshold voltage, and similarly in the source and drain, random dopants cause an irregular edge of the source and drain which adds variation to their resistance and capacitance. Moreover, the lithographic wavelength used to form transistor patterns below 250nm technology nodes has remained constant at 193nm [14, 15], as shown in Figure 1.2, which causes physical layout imperfections.

Figure 1.1 Dopants levels [14]

Figure 1.2 Lithography limitations [15]

Based on recent reports from the International Technology Roadmap for Semiconductors (ITRS) [16], the anticipated amount of variability in threshold voltage due to random doping variations is very large, and it could exceed 50% in 2018 technology nodes. The variability trend is plotted in Figure 1.3. In 2003, *Borkar et al.* [17] showed that normally distributed threshold voltage variations in microprocessor chips fabricated in 180nm CMOS logic technology caused frequency variations of 30% and leakage current variations of around 20 times, as shown in Figure 1.4. *Bowman et al.* [18] found that the number of critical paths increases as the variability increases and the maximum operating frequency also suffers as process variations increase with scaling.

Figure 1.3 ITRS design for manufacturability requirements [16]

There are some physical stress parameters that change rather slowly during the operational life of the chip and participate in the aging process of devices and interconnects [12]. Some stresses do not have a significant impact until a

catastrophic failure occurs, others can have a significant effect even in the early stages of degradation. These are considered temporal process variations and mainly include Negative Bias Temperature Instability (NBTI), Hot Electrons Injection (HCI) and electromigration [8, 9, 12, 19]. For example, NBTI could increase the threshold-voltage of a PMOS transistor by which it becomes slower, and HCI on the silicon-oxide gate of an NMOS transistor could increase its threshold-voltage, by which it becomes slower. The electromigration of metal interconnect could increase its propagation delays. This is caused by significant current densities and increased pressure of carrier collisions on metal atoms which causes a slow displacement of the metal interconnects.

Figure 1.4 Process variation impact frequency and leakage distribution [17]

HCI occurs, at device level, when an electron or a hole gains enough energy to overcome the potential barrier between silicon and oxide, thus becoming a hot carrier [8, 12, 19]. Hot carriers can degrade the dielectric material causing trap structures for electrons and holes, which increase leakage currents and alter threshold voltages prior to failing. It mostly impacts on NMOS transistors which become slower. From a circuit perspective, HCI occurs when both gate and drain voltages are significantly higher than the source voltage.

NBTI mostly affects PMOS devices, particularly during the device operation in the linear region. It is a result of the generation of silicon dangling bonds which form interface traps [8, 12, 19] and cause an increase in the absolute threshold voltage and a decrease in the drain current and transconductance and, as a result, a PMOS transistor becomes slower.

#### 1.1.2.2 Voltage Variability

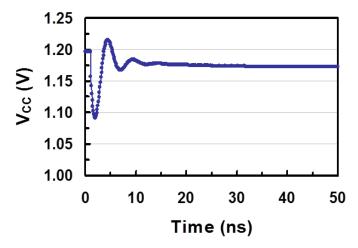

The supply voltage plays a fundamental factor in the design and analysis of integrated circuits. It determines the amount of current flowing through devices, the noise-margins of digital circuits and the power dissipation, it also limits the maximum switching frequency of a transistor. Therefore, any reduction in the supply voltage affects the circuit operational speed. Supply voltage fluctuations are generally a result of rapid variations in switching activity and poor power grid design, which causes a large amount of charge drawn from supply rail and results in an unbalanced dynamic power consumption across the chip and a droop in the supply voltage [17, 20, 21], as shown in Figure 1.5. A voltage droop is a small reduction in the supply voltage and grid distribution. These variations may result in slower speed and temperature hot spots.

Figure 1.5 Supply voltage droop [22]

#### **1.1.2.3 Temperature Variability**

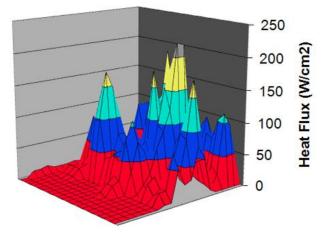

Variations in the surrounding temperature impacts on the operation of the circuits. Temperature variations may be influenced by the circuit during operation, and fluctuate across the chip as in Figure 1.6, depending on the circuit configuration, the switching frequency and power supply fluctuations, as well as the surrounding temperature, and whether it is provided with heat-sinks or not, as a result of hot spots may occur and the circuit's performance degraded [17, 20, 21]. This is because of the device and interconnects parameter dependence on temperature which decreases circuit performance. The empirical formulas, in Equation (1.1) below, show the effect of temperature on threshold voltage and mobility [4]. For instance, an increase in temperature causes a reduction in carrier mobility,

saturation mobility, threshold voltage and saturation current of transistors, whereas transistor sub-threshold leakage and interconnects resistance are significantly increased.

Figure 1.6 Heat fluctuation across die [14]

$$V_{TH}(T) = V_{TH}(T_0) \cdot \left(1 + TCV_{TH}(T - T_0)\right)$$

$$\mu(T) = \mu(T_0) \cdot (T_0/T)^{1.5}$$

(1.1).

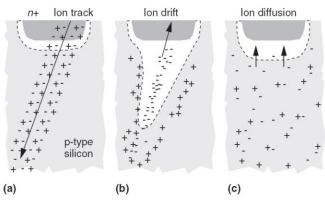

#### 1.1.2.4 Radiation particles

Soft errors are random transient errors in digital circuits caused by alpha particle radiation striking the substrate region in a device [4], as shown in Figure 1.7. They are emitted during the decay process of radioactive impurities in the packaging material. They are also induced by high-energy neutrons from cosmic rays. An alpha particle strike of a few nanoseconds creates a trail of hole-electron pairs in the substrate that could result in ion diffusion into the depletion region of a p-n junction collecting the charge. This charge is visible to the circuit as a current spike or a glitch and, if it exceeds a critical amount, may alter the state of the node causing a single event upset fault. This critical point decreases with technology scaling because it is dependent on the node capacitance and voltage as well as the circuit structure, increasing the probability of soft error failures. In order to reduce the probability of soft error failures, the critical nodes need to be high in capacitance and voltage.

Figure 1.7 Alpha-particles striking substrate [4]

### 1.2 Variation-Tolerant Circuit and Microarchitecture Techniques

Several techniques have been proposed to compensate for the impact of variability on performance and power. Most of them target particular problems, such as threshold voltage variation at device level, chip overheating, and timing variations. Several approaches combine two or more techniques to improve performance against variability. In the following sections, some of the variation reduction design techniques will be discussed.

#### 1.2.1 Adaptive Voltage Techniques

One of the serious problems of variability is the variations of the threshold voltages, which define device and circuit performance. To increase the number of accepted chips produced, several techniques were developed to improve the devices' performance by applying an appropriate body to source voltage to each die after fabrication to control both threshold voltage and leakage current, which helps reduce threshold voltage variations. The amount of voltage applied shifts the chip mean threshold voltage towards the target range of performance. The most commonly used of these techniques is to measure the variability in performance and leakage current of the chip with respect to the targeted tolerance, then apply a feedback body bias and then repeat measurements until the variability is mitigated. According to the literature [23-25], body bias is applied to all PMOS and NMOS transistors in a chip and can be forward, zero or reverse. The forward body bias increases the operating frequency, whereas applying a reverse body bias reduces the leakage current.

One of the earliest researchers [23] who adopted this technique towards die-to-die variations proposed the adaptive body bias technique to reduce the spread of

threshold voltage values for large number of die samples and to enhance their production yield. A different body bias was applied to different dies, that is, one body bias per die, depending on the difference between the target threshold voltage mean and that of the die. Their findings showed improvement in the threshold voltage variations between dies but also showed an increase in the within-die variations with channel length variations of 5%. Further research [24] considered an improved adaptive body bias technique to reduce die-to-die variations further, by finding the best PMOS and NMOS body bias combination for each die. Furthermore, improvements [24] on the previous technique [23] to compensate for within-die variations, where a unique body bias combination is applied to each circuit in the chip, increases the yield to three times of that of [23]. Both techniques showed improvement, but this improvement depends on the body bias voltage resolution, which may add to the complexity of the chip.

Another technique to reduce the variability of performance is known as adaptive supply voltage. Using this method, variations are reduced by decreasing the supply voltage of dies with high leakage current and increasing it for the ones with lower maximum frequency. The more the supply voltage resolution, the more effective is this technique. Both adaptive supply voltage and adaptive body bias can be combined together [25] to further reduce the impact of within-die variations and increase the yield. This enhanced technique showed a significant improvement in the number of accepted dies, which was nearly 98%. However, it consumes more area and increases the design complexity and power requirements [25].

In contrast, dynamic supply voltage variations have been an issue with increased switching activity and could not be solved using the adaptive supply voltage method. One known approach is adding on-die decoupling capacitors [26], which reduces the dynamic variations in the supply voltage. This improvement is dependent on the number of decoupling capacitors, but comes at the cost of area and increased gate oxide leakage in the sub-90nm technologies [17, 27]. An alternative method is to disable the power supply of clocked circuit blocks during idle stages, for example using sleep high-threshold-voltage transistors, which reduces the amount of excessive switching [27].

Temperature variations across the chip can strongly affect the chip's performance, since the material's electrical properties depend on temperature. To control the temperature on a chip, the throttling technique [17, 27] can be used to reduce both the operating frequency and the supply voltage when the chip's ambient temperature reaches its maximum limit, followed by a drop in power dissipation and then temperature. Adaptive body bias and supply voltage techniques can be combined together with internal thermal sensors at different points across the chip to control the temperature rise, as described by *Tschanz et. al.*[28]. Temperature and supply voltage readings are used to find the best combination of body bias, supply voltage and frequency by means of a look-up table, and then tune the circuit operation to reduce the operation temperature.

#### 1.2.2 Error Detection and Recovery Circuits

Microarchitecture techniques can be very effective in reducing the impact of dynamic variations. One traditional method is the error detection and correction scheme, which has been used commonly in different circuits and architectures. Most error detection techniques are based on checking output signals, while some techniques focus their attention on input signals. Any error has a number of different causes. Usually, transient errors are of concern during operation, in other words, they might occur during normal operation of the system. Some transient errors are caused by longer critical path delays resulting in timing errors, or logical errors. At circuit level, the common sources of transient errors could be as a result of PVT variations [21], timing violations causing a metastability failure [29], or alpha particle strikes causing soft error faults [4, 5, 30, 31].

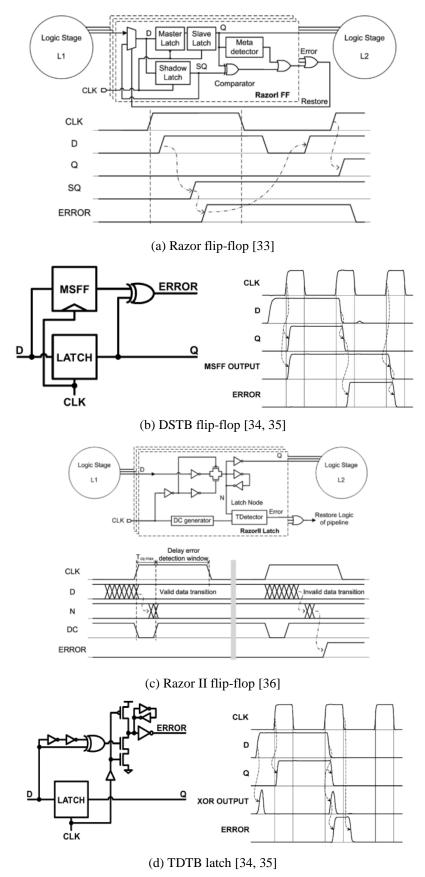

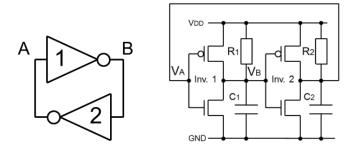

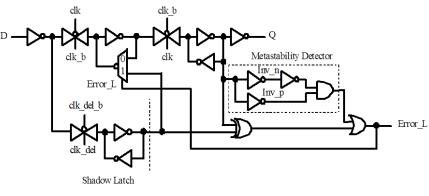

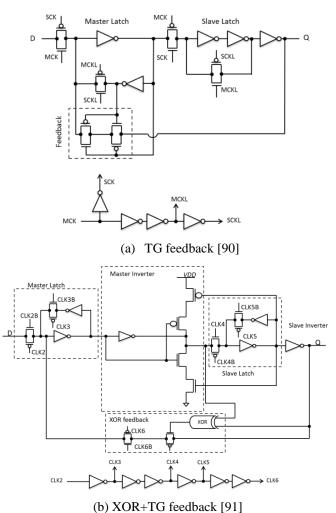

ARM proposed the Razor processor [32, 33] which utilizes timing error detection and correction techniques combined with dynamic voltage scaling and error rate monitoring techniques, to operate correctly at a critical supply voltage, that is, adequate under PVT variations. In general, the Razor flip-flop uses a datapath master-slave D flip-flop accompanied by a shadow latch and metastability and error detection circuits, as shown in Figure 1.8(a). Input data is sampled in the datapath flip-flop at the positive edge of the clock, and then sampled in the shadow latch at the negative edge of the clock. Then, the outputs of the flip-flop and latch are compared and if they differ, an error signal is produced to enable an error recovery mechanism to flush the pipeline. A similar technique was presented by Bowman [34, 35] known as the Double Sampling with Time Borrowing (DSTB) flipflop and comprised a datapath latch and shadow master-slave flip-flop with a comparison circuit to detect errors as shown in Figure 1.8(b). Its main advantages are design simplicity and removing metastability from the datapath.

Figure 1.8 Error detection/recovery in flip-flop and latch circuits

On the other hand, the early error detection technique, which is based on input transition detection, was presented in Razor II flip-flop [36] and Transition-Detection Time-Borrowing (TDTB) latch [34, 35], as shown in Figure 1.8(c) and Figure 1.8(d). Both techniques use a positive level-sensitive latch with a data input transition detector and clock detector. The transition detector senses any input data transition during the positive clock phase, and in the case of a flagged transition, the operating frequency is reduced and the instruction is replayed to correct the signal. Both techniques show an increased complexity compared to error detection being applied at the output.

Overall, novel error detection techniques along with adaptive techniques improved error rate as well as energy efficiency in the presence of different timing variations and faults. Transition detection techniques increase the design complexity, whereas output error detection techniques keep it simple.

### 1.2.3 Hardware Redundancy

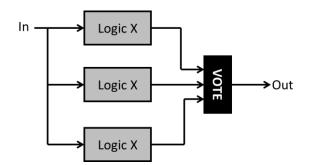

An alternative tactic to reduce the impact of soft errors is to add two more redundant circuits in parallel, followed by a majority voting circuit to produce the appropriate output, as shown in Figure 1.9. This technique is known as Triple-Modular-Redundancy (TMR) [4, 30]. In addition, adding one or more redundant paths within the cell itself can improve the robustness towards current spikes caused by alpha particle strikes, this is known as circuit-level hardening [30], for example radiation hardened flip-flops designs [4, 37] and soft-error tolerant memory cell designs [31, 38, 39].

Figure 1.9 Triple-Modular-Redundancy technique

A hardware redundancy technique can be implemented using two or more circuits in addition to monitoring and control circuits. The monitoring circuit tests all the circuits and decides which one has the best performance, for instance in terms of process variations, then enables the best circuit and disables the others. This technique was used in the synchronizer selection scheme in [40]. This technique improves the circuits' performance against permanent faults and aging process effects, but they have a negative impact on power and area overhead [30].

#### 1.2.4 Asynchronous Circuits and Systems

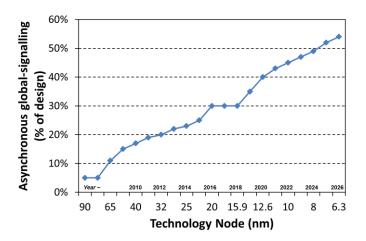

Asynchronous systems tend to have a unique advantage towards timing variations, as they require either more than one local clock or no clocks at all, which eliminates the problem of clock distribution and timing constraints, even with PVT variations spread across the chip [41, 42]. In addition, they would be the inevitable choice with the increase in intra-die variability against new technologies [21]. According to ITRS reports, the utilization of asynchronous global signaling on chip is expected to increase to 30% of the chip design by 2016 [16], as shown in Figure 1.10.

Figure 1.10 ITRS asynchronous design requirements [16]

Some approaches in the asynchronous world, such as Quasi-Delay Insensitive (QDI), which has no clocks and assumes delays only exist at isochronic forks, can actually tolerate timing variations and should never lead to failure [43] as well as consuming less dynamic energy.

Another approach called Globally-Asynchronous-and-Locally-Synchronous (GALS) [44], which is constructed from large synchronous blocks that communicate with each other using asynchronous interfaces, can eliminate the global clock distribution problem, even though they may have to face up to some inherited problems [43], for example, metastability operation in arbiters and synchronizers. The asynchronous links between the clocked regions require controlled handshake synchronization which leads to reduced maximum frequency and an increased

area overhead, especially under the limited availability of design tools [44-47]. The GALS architecture, in contrast with a global-synchronous architecture, can provide faster performance by at least 8% under within-die variations in gate length and thermal distribution [48]. These will be discussed further in Chapter 2.

#### **1.3 Thesis Motivations**

Integrated circuit scaling has some advantages and a few disadvantages; one of its disadvantages is the increase of parametric variability with every new technology node [16], which consequently reduces the chip production yield. These parameters may include transistor process parameters, supply voltage and temperature, which could have a huge impact on the circuit speed and power consumption if varied outside their design margins [17]. This effect is expected to continue to increase as the fabrication technology reaches the level of 32nm and beyond. Many VLSI system architectures, such as network-on-chip, are designed with more asynchronous circuits, which need to be more resilient to parametric variations.

Literature shows a number variation tolerant design techniques for parameters within different levels of abstraction. On the device level, there are some solutions to control variations in threshold voltage and leakage current by using adaptive body bias techniques [17, 23, 24, 45], and in a similar manner voltage supply variation can be improved with an adaptive supply voltage [17, 25-28, 45]. Others offered hardware redundancy on circuit level [4, 30], such as soft-error tolerant designs [31, 37-39]. Micro-architecture error detection and correction techniques, which are based on voltage scaling, timing errors detection and self-correction [34, 35], such as the Razor techniques [32, 33, 36, 49].

A System-on-Chip (SoC) cannot operate efficiently with a single global clock, due to parametric variations across the chip which makes the control of all the delays unlikely to be achieved. Asynchronous techniques, such as GALS [44], are the solution to SoCs [16, 21, 41, 42, 50]. Synchronizers and arbiters are special circuits commonly used in systems with multiple clock domains or clockless domains. A synchronizer is used to synchronize signals between Multiple-Clock Domains (MCD) while an arbiter selects between two requests. Their circuits are constructed based on one or more bistable elements, for example flip-flops, which

must receive stable input signals for a short specified window of time. Because synchronizers and arbiters may receive input signals with arrival times violating that specification, they are more susceptible to metastability problems [29, 41, 50, 51], which lead to apparently chaotic transient behavior that draws more current from the supply rail, and can result in an unpredictable state in the following stage.

The main objective of multiple voltage design is to reduce the overall power consumption, as well as to reduce the effects of process variations [52-54], by providing different voltage domains that are either constant or variable [55]. Sometimes, the reduction of voltage supply requires a reduced clock frequency as in the case of Dynamic Voltage and Frequency Scaling (DVFS), which creates an MCD challenge. Hence, there is a need to study the design of synchronizers placed between multiple voltage domains.

The aim of this thesis is to investigate how synchronizers and arbiters should be designed to tolerate parametric variations. All investigations focused mainly on circuit-level and transistor level designs and were modeled and simulated in the UMC90nm CMOS technology process [6]. Analog simulation was run using the Cadence Spectre Virtuoso [56] CAD tool to measure timing parameters and power consumption along with a "Monte Carlo" statistical analysis [57] to account for process variations.

Two main components of synchronizers and arbiters were primarily investigated: flip-flop and mutual-exclusion element (MUTEX). Both components can violate the input timing conditions, setup and hold window times, which could cause metastability inside their bistable elements and possibly end in failures. The mean-time between failures is an important reliability feature of any synchronizer and depends exponentially on the metastability recovery time constant  $\tau$  and the delay through the synchronizer. Both circuits were optimized to reduce the impact of metastability and tolerate process variations. Subsequently, proposed of circuit level-techniques were investigated to decrease these impacts. Lastly, synchronization schemes between multiple voltage and multiple clock domains were investigated.

16

### **1.4 Thesis Contributions**

In this thesis, a number of techniques have been proposed, to enhance the performance and robustness of synchronizers and arbiters. The study has focused on the impact of variations of PVT on the performance of circuits in terms of propagation delay time, metastability resolution time, power consumption. The contributions made to the state of the art in this area of research are outlined below:

- Analysis of the trade-off in Flip-Flops when used as registers or used in a synchronizer application. Flip-flops used to store a bit in a register have different requirements to flip-flops used in a synchronizer application. The data input must be held stable during the setup and until the Q output appears, these times determine the remaining part of the clock cycle available for computing. On the other hand, the data input can violate setup and hold times in a synchronizer, and the reliability of the synchronizer depends on the metastability recovery time constant. This work shows how these parameters can be traded off in a simple edge triggered D flip-flop and other cells. (Published IEEE ICECS 2009)

- The improvement of reliability and latency through the adoption of the Wagging synchronizer design. An alternative structure to the conventional two-flip-flop synchronizer is proposed based on the Wagging principle. The aim of the wagging synchronizer is to increase the time allowed for metastability to resolve, hence improve the synchronizer reliability. (Published IEEE ICM 2010).

- Modifications of the MUTEX circuit to improve the metastability resolution time and tolerance to the effects of process variation. The MUTEX study focused on the classical circuit, in addition to a number of modifications at the circuit and transistor levels, to adjust the value τ and its tolerance, based on increasing internal gain by adding current sources, reducing the capacitive loading, boosting the transconductance of the latch, compensating the existing Miller capacitance, and adding asymmetry to maneuver the metastable point. The results showed that some circuits had almost little or no improvements, while five techniques showed significant improvements by reducing τ and maintaining high tolerance.

- The design of robust and reconfigurable wagging synchronizer to improve reliability and latency tolerance to the effects of process variation. The robustness of the wagging technique can be enhanced by using robust  $\tau$  latches or adding one more cycle of synchronization by a reconfigurable circuit.

- The design of Metastability Auto-Detection and Correction (MADAC) latches that are able to detect and correct metastable events within the cell. This approach relies on swiftly detecting a metastable event and correcting it by enforcing the previously stored logic value. This technique significantly reduces the resolution time uncertainty.

- Finally, the design of pseudo Level-Shifting Handshake Synchronization (LSHS) techniques, which are able to operate between multiple-voltage multiple-clock domains that do not require conventional level-shifters between the domains or multiple power supplies within each domain. This interface circuit uses a synchronous set and feedback reset protocol which provides level-shifting and synchronization of all signals between the domains, from a wide range of voltage-supplies and clock frequencies.

### 1.5 Thesis Organization

The content of this thesis is organized in total seven chapters. Following the introduction:

In **Chapter 2**, a background study of the metastability behavior in bistable elements and synchronizers are presented. Followed by, studies of synchronizers and arbiters. Then, reviews of the synchronization techniques on-chip and the multiple voltage design are presented. At the end, the performance metrics of flip-flops and how to obtain them are defined.

In **Chapter 3**, the analysis of the trade-off in Flip-Flops when used as registers or used in a synchronizer application is discussed. Then, the wagging synchronizer design is described, accompanied by its results showing improvements of reliability and latency.

In **Chapter** 4, variation-tolerant arbiter design is presented. It focuses on modifications of the MUTEX circuit to improve the metastability resolution time

and tolerance to the effects of process variation design modification of the conventional. Then, simulation results, showing the impact of gate-size and load-size, as well as, PVT variations on  $\tau$  and delay time, are presented.

In **Chapter** 5, two variation tolerant design techniques for synchronizers are presented. First, the robust and reconfigurable wagging synchronizers to improve reliability and latency tolerance to the effects of process variation are presented. Then, the MADAC synchronizers that are able to detect and correct metastable events within the cell. Followed by simulation results of the MADAC against PVT variations on timing and power parameters are presented.

In **Chapter** 6, a multi-voltage synchronization technique is presented. First, the dual and single-supply level-shifting latch is discussed. Then, the LSHS approach, followed by a modified approach LSHS2 to adapt to wider clock cycles range, are presented. Then, a bidirectional LSHS approach is proposed.

Finally, **Chapter** 7 comprises the results discussion and thesis conclusions and outlines the future prospective research opportunities.

## Chapter 2 Background

The continued scaling of semiconductor technology creates the potential of SoC integration, that is, the integration of a complete electronic system, including interfaces to the outside world on a single die. An SoC consists of several mixed components with different implementation styles such as programmable processors, dedicated hardware to perform specific tasks, on-chip memories, input-output interfaces, and on-chip communication architecture that serves as the interconnection fabric for communication between these components.

This scaling of integrated circuits has been a challenging step in the industry to maintain an acceptable production yield. Chip scaling provides the opportunity to reduce area, cost and power consumption and improve speed. Yet, its drawbacks must be realized. Manufacturing variations can cause deterioration in the chip's performance and functionality and, consequently, in the production yield. Parameter variability is expected to increase with every new technology node and significantly increase the effects on circuit performance, in terms of power consumption and delay [1, 14, 45].

Multiple Systems-on-Chip are designed with more asynchronous circuits and techniques rather than synchronous ones to tolerate the variations at the transistor level. Some of these techniques use arbiters and synchronizer as the interface block between modules. Arbiters recognize the order of events, and synchronizers help to receive data from other synchronous or asynchronous domains. They have been used frequently in VLSI systems and architectures, such as GALS wrappers for a network-on-chip (NoC) [58-61] or network adapters and routers [61-64]; and they will be utilized even more in the future by the increase in asynchronous global signaling being exploited within a single SoC, which is predicted to double by 2016 [1].

In the subsequent sections of this chapter a background study of the metastability behavior along with the current synchronizer and arbiter circuits are discussed, as well as their design challenges. After that, different on-chip synchronization techniques are discussed including a single global-clock and multiple-clocks, asynchronous techniques, and GALS. Then, multiple-voltage domain approaches and concerns are discussed. At the end, the metrics for characterizing the performance, particularly of flip-flops, are defined.

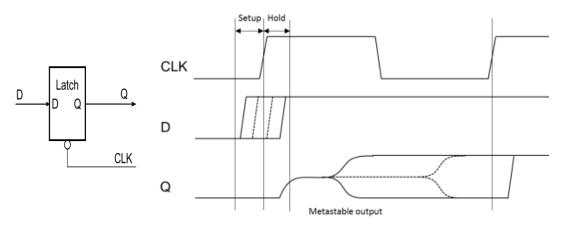

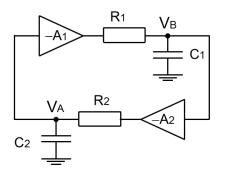

### 2.1 Metastability, Synchronizers and Arbiters

In a synchronous system, data signals always meet input timing requirements of flip-flops, because the relationship between data and clock is fixed; therefore, metastability does not occur. Nevertheless, in most multiple clock systems and asynchronous systems, input data regularly violates the setup and hold timing conditions of bistable elements, because input data, clock switching rates and phase relationship is inconsistent. This violation results in delayed output signals and possibly leads to metastable outputs, which add further delays to produce a valid and stable output value, logic '1' or logic '0'. Therefore, it is important to carefully analyze and design bistable elements prone to metastability for minimum metastability time without impacting on performance. Figure 2.1 shows the circuit diagram of a data latch and a timing diagram with clock, input data D and output value Q. The input data D transits within the setup and hold region around the clock rising-edge results in a metastable output Q, which may last a period of uncertain time.

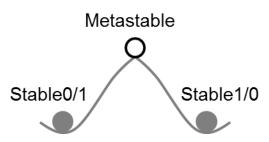

Metastability is a hazardous anomaly phenomenon that can take place in any bistable or sequential circuit; particularly, more often, in synchronizers and arbiters. It is known to be an unstable equilibrium voltage point between the valid voltage logic levels (0 and  $V_{DD}$ ) and usually around  $\frac{1}{2}V_{DD}$ . This voltage point is equivalent to the middle voltage which is the switching/inverting point of the gates comprising the bistable circuit. If the bistable circuit has a long feedback path, then metastability develops into an oscillation around the middle voltage, which was observed in some obsolete technologies, for example a set-reset latch comprised of TTL NAND gates [29] and CMOS NOR gates with buffered output either off chip [65] or on chip [66].

An analogy to a bistable latch is a ball transiting over a hill having two stable points at either side of the bottom of the hill and one metastable point at the top of the hill, as shown in Figure 2.2. If the ball transition force is not enough to cross the hill, then it will fall back to the bottom. However, if it is enough to cross the hill, the ball will fall to the other stable point, whereas if the force is only sufficient to reach the top of the hill, then the ball will stay still unless there is a disturbance in the environment due to wind for example.

Figure 2.1 Data transition violation causes metastable output Q

Figure 2.2 Metastability analogy to ball over a hill

The main cause of recurring metastable events is the conflict between incoming signals with the timing restrictions. Likewise, metastability may be initiated by the resolution in a preceding sequential stage violating the next stage's timing conditions, which is known as the back edge of the clock effect [50]. For example, if a master latch in a master-slave flip-flop exhibits metastability that holds the master latch a long time and resolves near the slave-latch timing condition at the back edge of the clock, this may initiate a new metastability event in the slave-latch needing more time to recover. Furthermore, metastability may be transferred between logic gates or from master latch to slave latch if not designed properly. Metastability may also occur due to a very short pulse gated clock or even a poorly timed clear or reset signal [50]. Moreover, on the occasion of a single event upset due to alpha particle strikes, a current spike could last a sufficiently long time to flip a cell or induce metastability.

However, this thesis only concentrates on metastable events that are caused by

asynchronous input signals from an asynchronous system or a differently clocked system because it is significantly the most frequent recurring cause of metastability, and it is considered one of the most difficult problems to deal with in synchronization.

In case of metastability at the output of a latch driving some logic stage, the subsequent logic stage will behave unpredictably, and some may interpret this invalid voltage level as a logic one while another as a logic zero. As a result, metastability may produce failures appearing as data being lost, corrupted or duplicated, which causes a system failure and in particular circumstances a system deadlock.

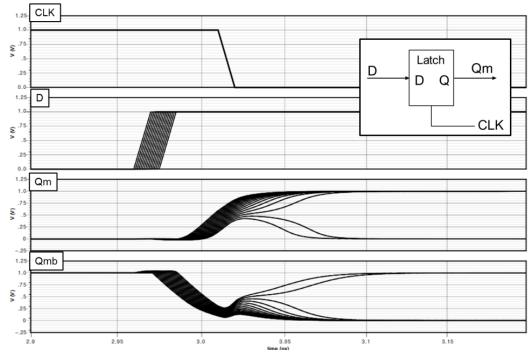

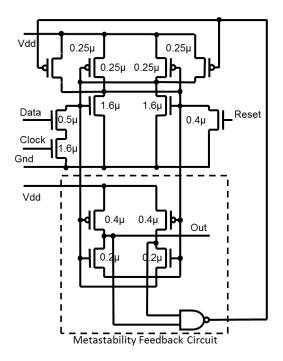

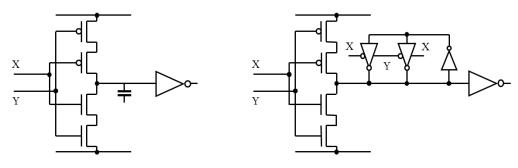

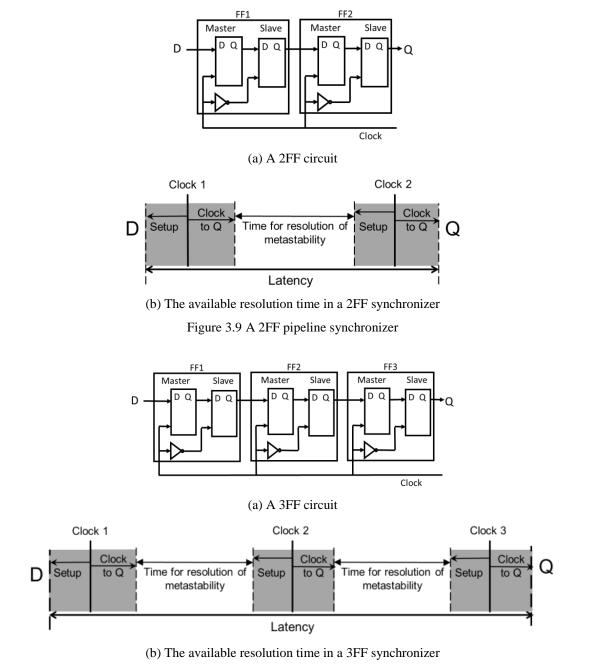

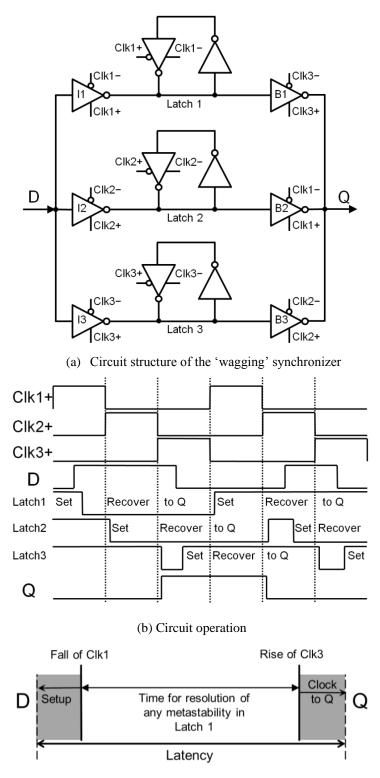

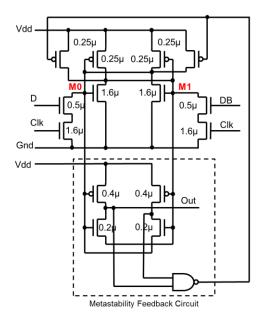

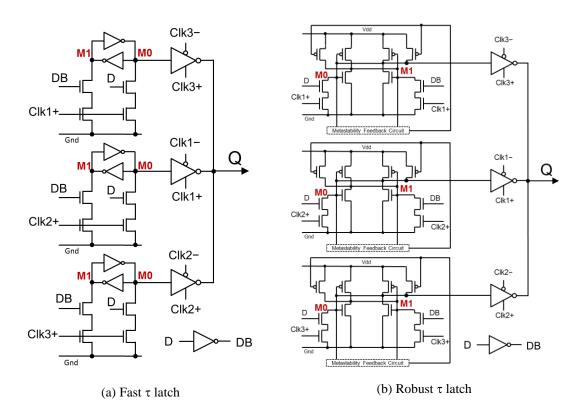

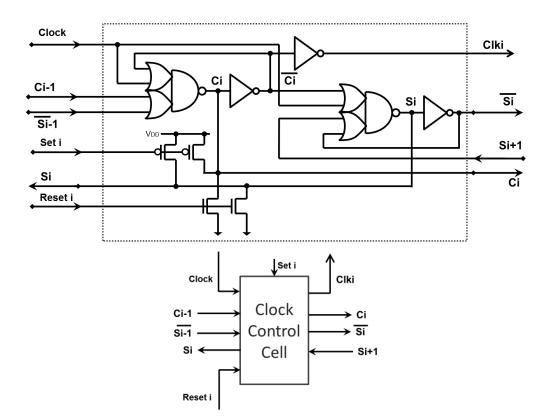

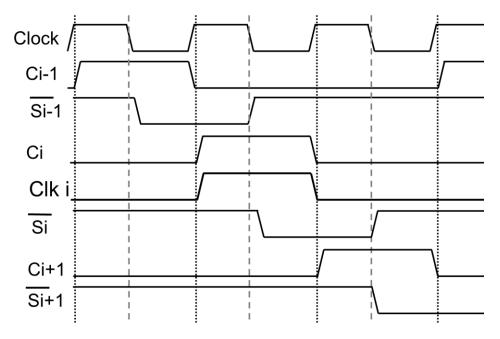

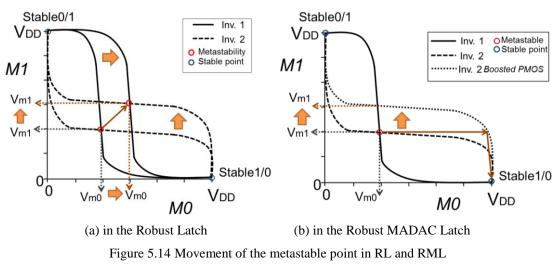

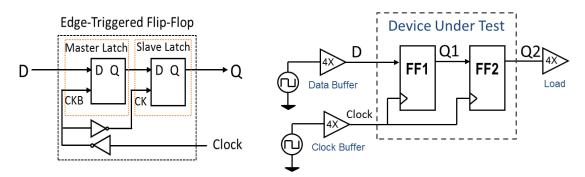

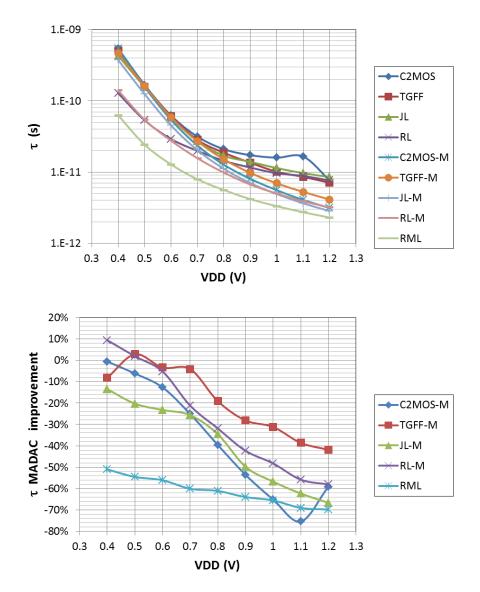

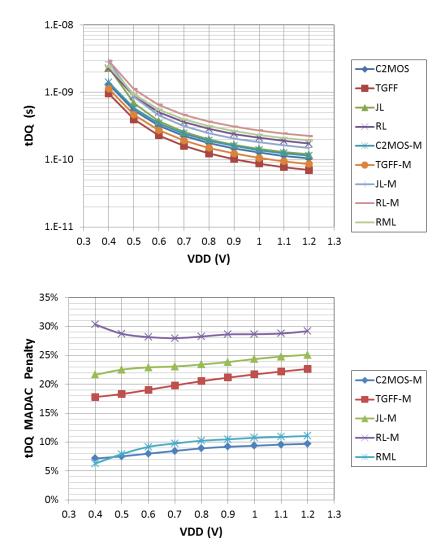

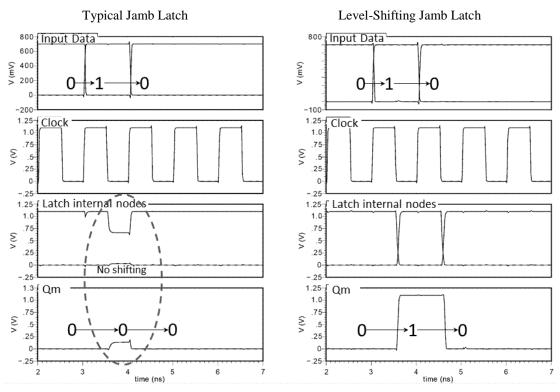

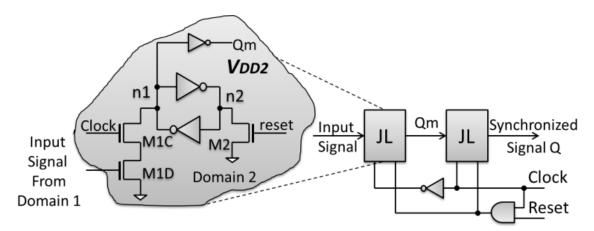

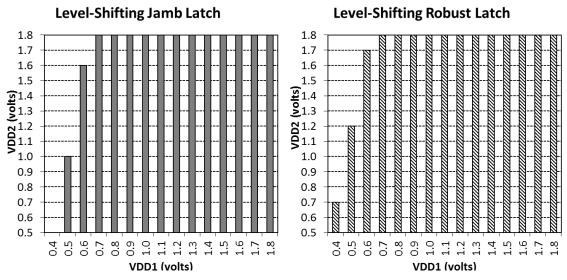

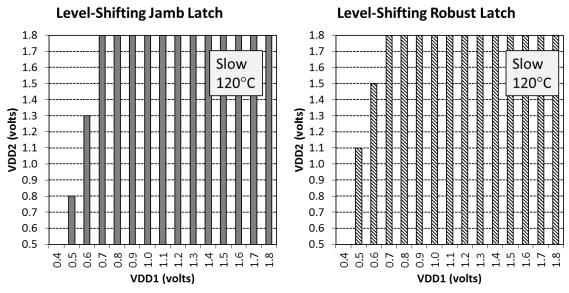

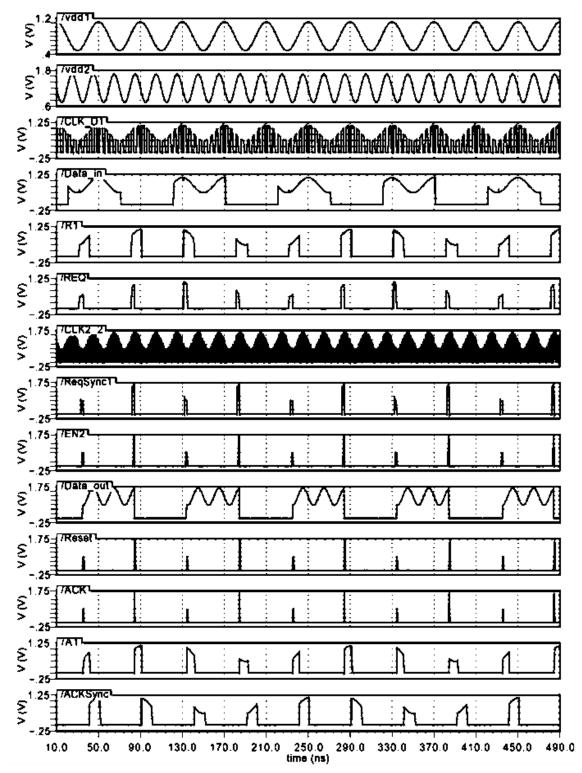

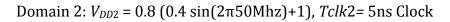

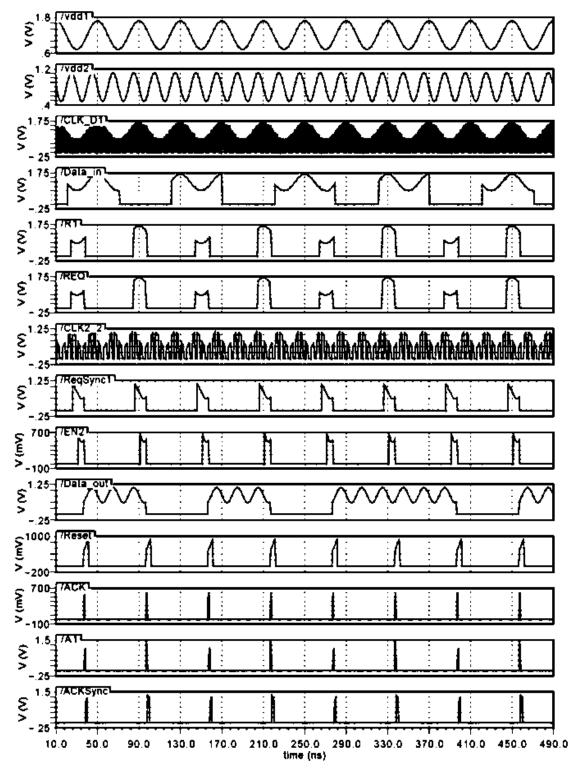

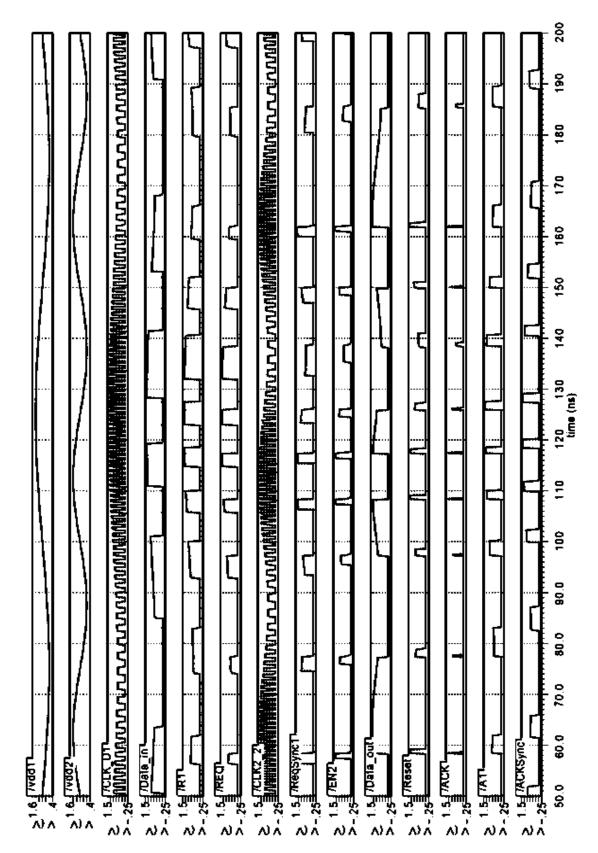

A simple latch circuit modeled in UMC 90nm process technology and simulated in SPICE-level. The latch simulation waveforms, shown in Figure 2.3, demonstrate the latch going metastable at different data arrival times, stepped at 1ps closer to the falling edge of the clock.