# Reduction of Variable Speed Drive IGBT Switching Loss, Utilising the IGBT Gate Drive, Without Increasing Radio Frequency Radiated Emissions

#### **Richard Samuel Gibson**

A Thesis Submitted for the Degree of Engineering Doctorate in Power Electronics

Machines and Drives

© August 2013

**Newcastle University**

School of Electrical, Electronic and Computer Engineering

#### **Abstract**

Radio frequency radiated emission from a variable speed drive must be limited below defined limits to avoid interference with electronic equipment. It is possible to comply with the international standards however, the current state of the art methods such as large gate drive resistance and output filters significantly reduce the efficiency or increase the cost of the products. It is known that the main source of emissions emanate from the switching transients associated with the output power semiconductors, however the exact mechanisms and specific sources are unknown. This thesis examines the interaction of power devices during the switching transient identifying features which can be controlled by a sophisticated gate drive design. Analysis of the frequency content of the signals is presented together with methods to minimise power losses while maintaining compliance with radiated emission standards. A research program has been undertaken to identify the sources responsible for radiated emissions and predict a figure of merit as an indication of compliance. Measuring radio frequency content on high voltage and current signals is difficult and several techniques to accurately achieve this are presented. Simple passive gate drive solutions which can be easily implemented are examined along with a discussion on more complicated optimised solutions.

#### Acknowledgements

This work has been funded by Control Techniques and the Engineering and Physical Science Research Council without which this project could not have been undertaken.

I would like to thank the support of everybody at Control Techniques in particular Tom Alexander and Bill Drury for the opportunity to undertake this doctorate and their encouragement and guidance throughout.

Special thanks are due to Colin Hargis for sharing his experience, expertise and guidance throughout the last four years. Also, to Matthew Armstrong for his encouragement and constructive feedback on the initial draft of my thesis; Volker Pickert and Alton Horsfall for challenging me on semiconductor physics; and Frank Heerdt for proofreading the final draft of my thesis.

Finally I would like to thank my parents for the support and encouragement they have shown throughout my career and for encouraging me into the engineering profession. I would like to thank my wife Sarah for her love, support and patience throughout my studies.

| ABSTI  | RACT    |                                                             | II   |

|--------|---------|-------------------------------------------------------------|------|

| ACKN   | OWLED   | DGEMENTS                                                    | III  |

| CONT   | ENTS    |                                                             | IV   |

| LIST C | F FIGU  | IRES                                                        | VIII |

| LIST C | F TABL  | ES                                                          | XIII |

| LIST C | F SYM   | BOLS                                                        | XIV  |

| LIST C | F ABBI  | REVIATIONS                                                  | XVI  |

| СНАР   | TER 1:  | INTRODUCTION                                                | 1    |

| 1.1    | . Pow   | VER LOSSES AND RADIATED EMISSIONS IN A VARIABLE SPEED DRIVE | 1    |

| 1.2    | . Овје  | ECTIVES OF THE WORK                                         | 4    |

| 1.3    | OVE     | RVIEW OF THE THESIS                                         | 5    |

| 1.4    | THE     | CONTRIBUTION TO KNOWLEDGE                                   | · 6  |

| 1.5    | Con     | IMERCIAL BENEFITS TO INDUSTRY                               | 6    |

| СНАР   | PTER 2: | KEY PRINCIPLES                                              | 8    |

| 2.1    | . Intr  | ODUCTION                                                    | 8    |

| 2.2    | Pow     | ver Semiconductor Physics                                   | 9    |

|        | 2.2.1   | Diodes                                                      | 9    |

|        | 2.2.2   | IGBT                                                        | 18   |

|        | 2.2.3   | Device Switching Characteristics                            | 26   |

| 2.3    | RAD     | IATED EMISSIONS SOURCES FROM A VSD                          | 36   |

|        | 2.3.1   | Emission Sources                                            | 36   |

|        | 2.3.2   | Power Cables                                                | 38   |

|        | 2.3.3   | Cable Capacitance                                           | 39   |

|        | 2.3.4   | Cable Inductance                                            | 43   |

|        | 2.3.5   | Braid Structure                                             | 44   |

|        | 2.3.6   | Cable Summary                                               | 46   |

| 2.4    | FREC    | QUENCY ANALYSIS                                             | 48   |

|        | 2.4.1   | Frequency Content in Switched Signals                       | 48   |

|        | 2.4.2   | Limit of Curve Shaping for Radiated Emissions               | 50   |

|        | 243     | Wavelet Transform                                           | 51   |

| 2.  | 5 Sumi  | MARY OF CHAPTER 2                                               | 55        |

|-----|---------|-----------------------------------------------------------------|-----------|

| СНА | PTER 3: | REVIEW OF GATE DRIVE CIRCUITS                                   | 57        |

| 3.  | 1 Intro | DDUCTION                                                        | 57        |

|     | 3.1.1   | Implementation of Gate Drive                                    | 57        |

| 3.  | 2 Inve  | RTER CONFIGURATION                                              | 59        |

|     | 3.2.1   | Single IGBT                                                     | 59        |

|     | 3.2.2   | Series IGBTs                                                    | 60        |

|     | 3.2.3   | Parallel IGBTs                                                  | 60        |

| 3.  | 3 DESIG | SN CONSIDERATIONS                                               | 62        |

|     | 3.3.1   | Gate Drive Power Supply                                         | 62        |

|     | 3.3.2   | Dead-Time Interlock                                             | 63        |

|     | 3.3.3   | Temperature Sensing                                             | 63        |

|     | 3.3.4   | Overvoltage Protection                                          | 63        |

|     | 3.3.5   | Over-Current Protection                                         | 64        |

|     | 3.3.6   | Switching Loss                                                  | 67        |

|     | 3.3.7   | Conduction Loss                                                 | 67        |

| 3.  | 4 Cont  | ROL OF SWITCHING TRANSIENTS                                     | 69        |

|     | 3.4.1   | Passive Gate Drive                                              | 69        |

|     | 3.4.2   | Active Gate Drive                                               | <i>75</i> |

|     | 3.4.3   | Reduction of EMI                                                | 87        |

| 3.  | 5 Ѕимі  | MARY OF CHAPTER 3                                               | 90        |

| СНА | PTER 4: | PRACTICAL MEASUREMENTS OF IGBT SWITCHING AND RADIATED EMISSIONS | 92        |

| 4.  | 1 INTRO | DDUCTION                                                        | 92        |

| 4.  | 2 Puls  | E TEST SETUP                                                    | 92        |

| 4.  | 3 MEA   | SURING EQUIPMENT                                                | 95        |

|     | 4.3.1   | Measuring Radio Frequency Content from Transient Signals        | 96        |

| 4.  | 4 Dc B  | us Bar Configuration                                            | 101       |

| 4.  | 5 Swit  | CHING LOSS MEASUREMENTS                                         | 109       |

|     | 4.5.1   | IGBT Parasitic Elements                                         | 111       |

|     | 4.5.2   | IGBT transconductance                                           | 112       |

|     | 4.5.3   | Intrinsic Time Delay in an IGBT                                 | 113       |

|     | 4.5.4   | Minimum Gate Resistance                                         | 115       |

| 4.  | 6 RADI  | ATED EMISSIONS MEASUREMENTS                                     | 116       |

|     | 4.6.1   | Open Area Test Site                                             | 116       |

|     | 4.6.2   | Gate Resistor Values                                            | 119       |

| 4.7   | Sum    | MARY OF CHAPTER 4                                            | 120           |

|-------|--------|--------------------------------------------------------------|---------------|

| СНАРТ | ΓER 5: | DETERMINATION OF KEY LINKAGES OF RADIATED EMISSIONS TO MEASU | JRED VOLTAGES |

| AND C | URREN  | NTS                                                          | 122           |

| 5.1   | INTR   | ODUCTION                                                     | 122           |

| 5.2   |        | TROL OF WAVELET MAGNITUDE TO INFLUENCE RADIATED EMISSIONS    |               |

|       | 5.2.1  | Switching Loss                                               |               |

|       | 5.2.2  | Isolated Peak Voltage Wavelet                                |               |

| 5     | 5.2.3  | Isolated Peak Current Wavelet                                |               |

| 5     | 5.2.4  | Switch Off Transient                                         |               |

| 5.3   | Radi   | ATED EMISSIONS APPARATUS                                     |               |

| 5     | 5.3.1  | Typical VSD Test Arrangement                                 | 138           |

| 5     | 5.3.2  | Simplified Test Setup                                        |               |

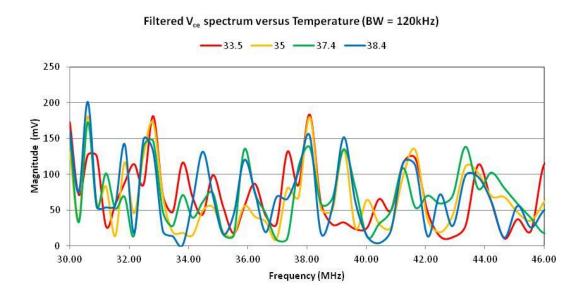

| 5.4   | Vari   | ABLES INFLUENCING RADIATED EMISSIONS MEASUREMENTS            | 143           |

| 5     | 5.4.1  | Signal Interference                                          | 143           |

| 5     | 5.4.2  | Azimuth                                                      | 145           |

| 5     | 5.4.3  | Temperature                                                  | 147           |

| 5.5   | IDEN   | TIFICATION AND INFLUENCE OF RADIATED EMISSIONS SOURCES       | 150           |

| 5     | 5.5.1  | Radiated Emissions Figure of Merit                           | 150           |

| 5     | 5.5.2  | Analysis of Electrical Signals                               | 150           |

| 5     | 5.5.3  | Emissions Sources and Gate Profiles                          | 151           |

| 5     | 5.5.4  | Minimum Rise/Fall Time                                       | 159           |

| 5.6   | Sum    | MARY OF CHAPTER 5                                            | 162           |

| СНАРТ | ΓER 6: | RADIATED EMISSIONS FROM A VARIABLE SPEED DRIVE               | 164           |

| 6.1   | INTR   | ODUCTION                                                     | 164           |

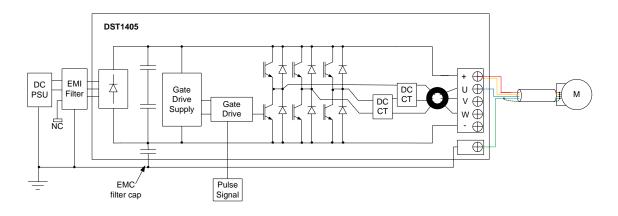

| 6.2   | THE    | COMMERCIAL VSD FOR EVALUATION                                | 164           |

| 6     | 5.2.1  | Modulation Strategy                                          | 164           |

| 6     | 5.2.2  | Switching Frequency                                          | 167           |

| 6     | 5.2.3  | Gate Drive                                                   | 168           |

| 6.3   | MEA    | SURING PROBES AND ANCILLARY HARDWARE                         | 170           |

| 6.4   | FIXE   | GATE RESISTOR VSD OPERATION                                  | 172           |

| 6.5   | Swit   | CHING ENERGY LOSS                                            | 178           |

| 6.6   | Radi   | ATED EMISSIONS PREDICTIONS                                   | 179           |

| 6     | 5.6.1  | Switch Off                                                   | 181           |

| 6     | 5.6.2  | Filter Components                                            | 183           |

| 6.7   | IMPL   | EMENTATION OF PASSIVE CIRCUITS TO INCREASE EFFICIENCY        | 186           |

| 6     | .7.1 Additional C <sub>ge</sub>                                   | 186 |

|-------|-------------------------------------------------------------------|-----|

| 6.8   | SWITCHED IMPEDANCE                                                | 188 |

| 6.9   | SIMPLE CONTROL OF WV <sub>CE_1</sub> WITH THRESHOLD HOLD CIRCUIT  | 190 |

| 6.10  | SUMMARY OF CHAPTER 6                                              | 192 |

| СНАРТ | ER 7: CONCLUSIONS                                                 | 194 |

| 7.1   | GENERAL OVERVIEW                                                  | 194 |

| 7.2   | FREQUENCY ANALYSIS                                                | 194 |

| 7.3   | Transient waveform shape                                          | 194 |

| 7.4   | GATE DRIVE SOLUTIONS                                              | 195 |

| 7.5   | MEASURING RF CONTENT IN ELECTRICAL SIGNALS                        | 195 |

| 7.6   | DOMINANT SOURCE OF RADIATED EMISSIONS                             | 196 |

| 7.7   | RADIATED EMISSIONS FROM A COMMERCIAL VSD                          | 196 |

| 7.8   | BENEFITS OF THE REDUCTION IN RE                                   | 197 |

| 7.9   | New Technology Devices                                            | 198 |

| 7.10  | RECOMMENDATIONS FOR FURTHER WORK                                  | 198 |

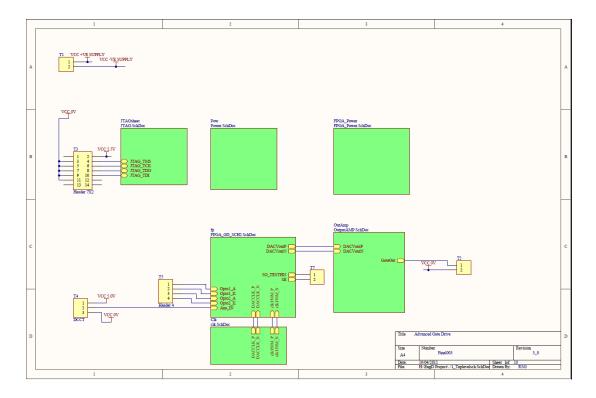

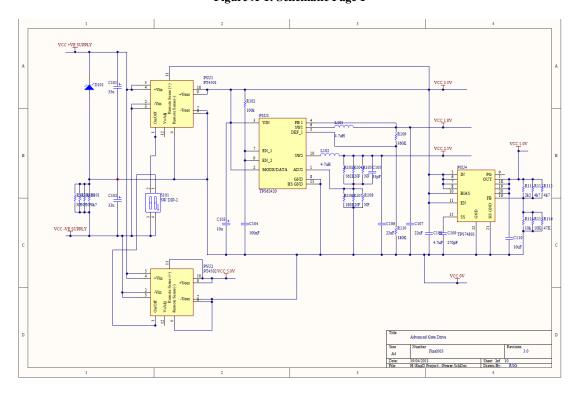

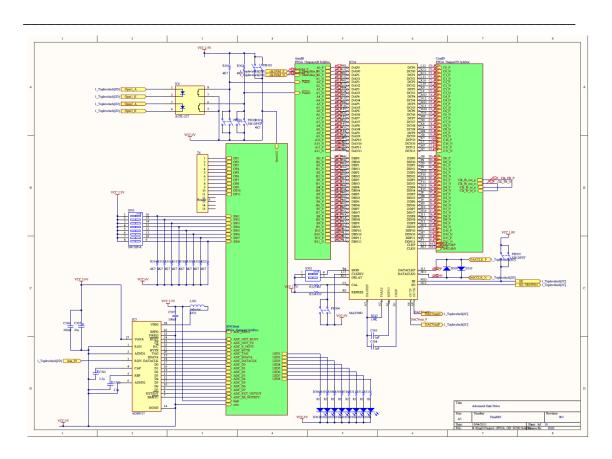

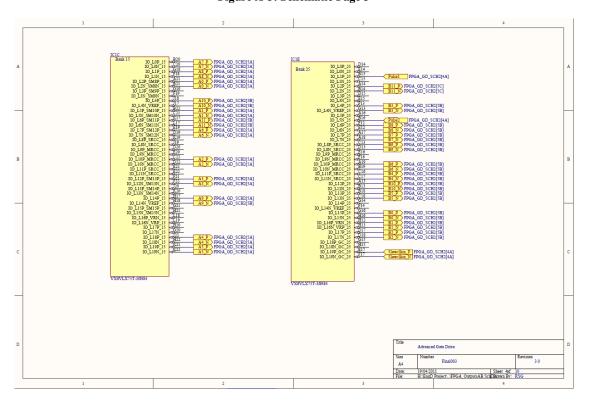

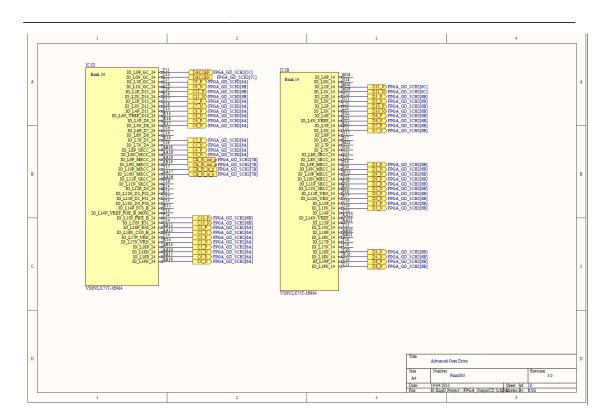

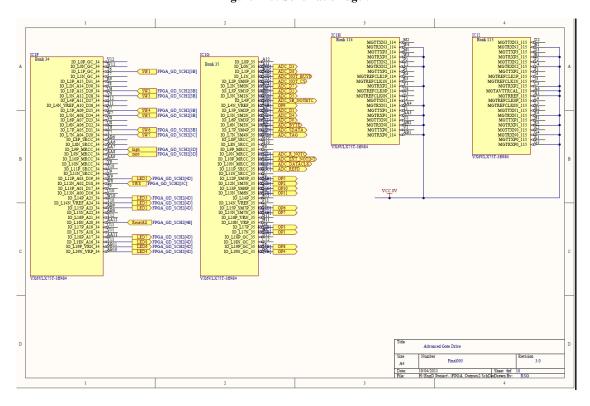

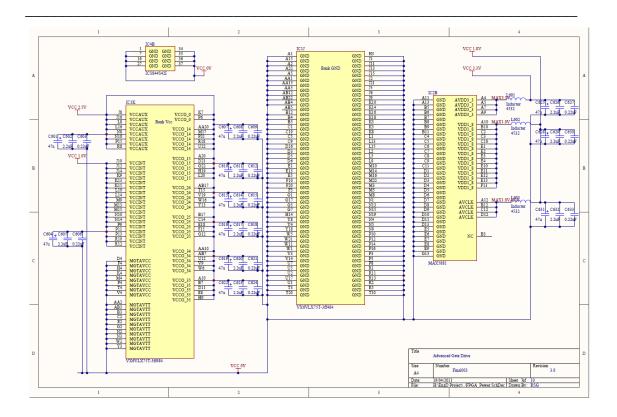

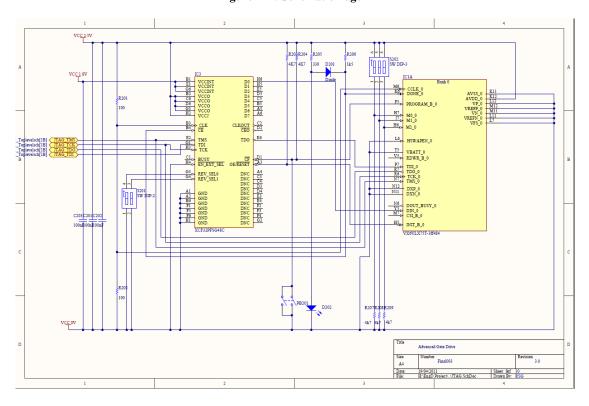

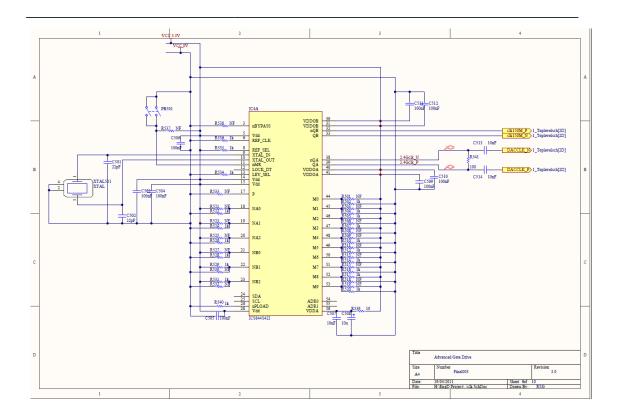

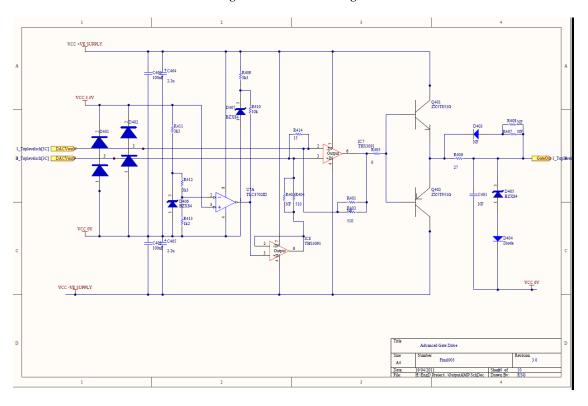

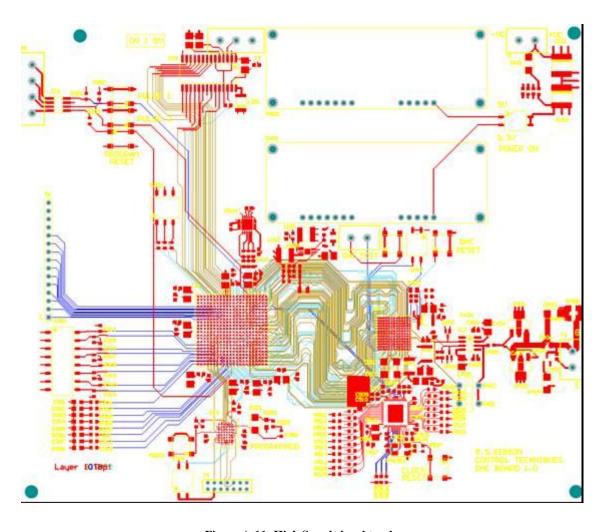

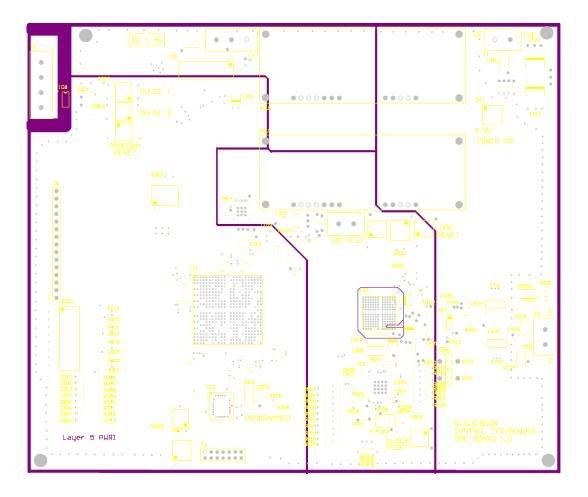

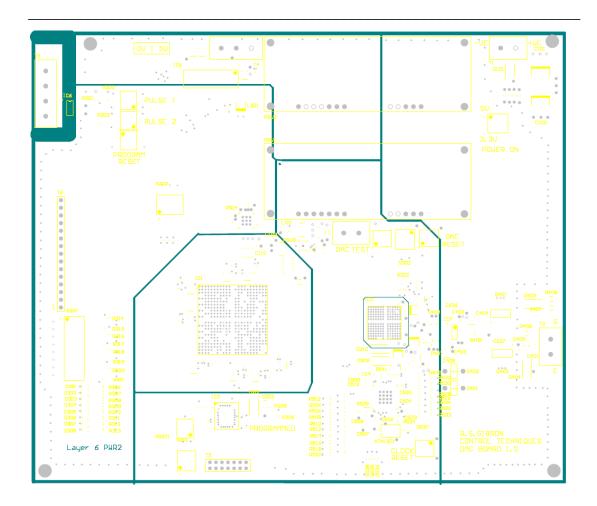

| APPEN | DIX A: 4 GHZ GATE DRIVE DESIGN                                    | 200 |

| A.1   | SCOPE                                                             | 200 |

| A.2   | SPECIFICATION AND KEY COMPONENTS                                  | 200 |

| A.3   | SCHEMATIC                                                         | 201 |

| A.4   | PCB                                                               | 207 |

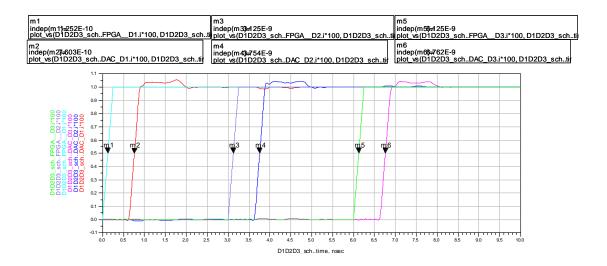

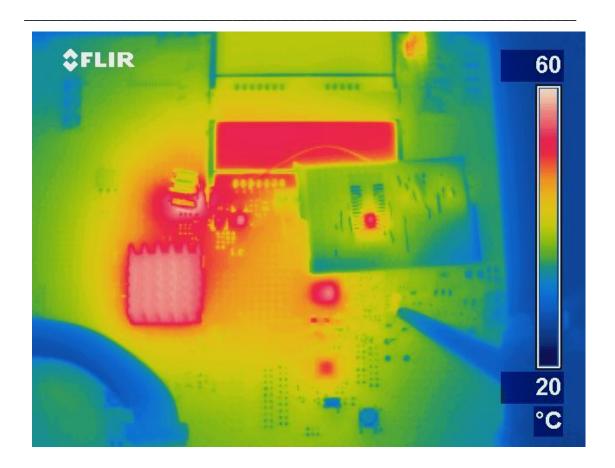

| A.5   | SIMULATION                                                        | 209 |

| A.6   | Measurement                                                       | 210 |

| A.7   | ASSEMBLED FPGA GATE DRIVE                                         | 212 |

| APPEN | DIX B: DERIVATION OF MINIMUM GATE RESISTOR                        | 213 |

| APPEN | DIX C: REFLECTED SIGNAL INTERFERENCE IN ANTENNA MEASUREMENTS      | 215 |

| APPEN | DIX D: SHAPED GATE TRANSIENTS AND RADIATED EMISSIONS MEASUREMENTS | 217 |

| APPEN | DIX E: TEMPERATURE RISE IN IGBT DIE FROM PULSE OF ENERGY LOSS     | 224 |

| LISTO | E REFERENCES                                                      | 225 |

| Figure 1-1: Block diagram representation of an ac-dc-ac VSD                                   | 2  |

|-----------------------------------------------------------------------------------------------|----|

| Figure 2-1: Structure of PIN diode a) Epitaxial diode; b) Diffused diode                      | 10 |

| Figure 2-2: Electric field profile for NPT (solid) and PT (dashed)                            | 12 |

| Figure 2-3: PIN diode band diagram and plasma concentration                                   | 13 |

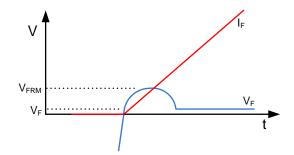

| Figure 2-4: Diode switch on waveform.                                                         | 15 |

| Figure 2-5: Soft Recovery PIN diode (softness factor S)                                       | 16 |

| Figure 2-6: PIN diode plasma concentration during snap-off for different types of diodes      | 17 |

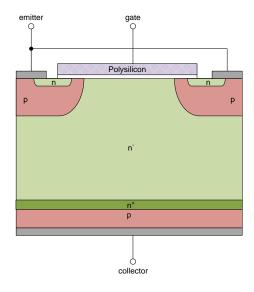

| Figure 2-7: Planar gate, Non-Punch Through IGBT structure                                     | 19 |

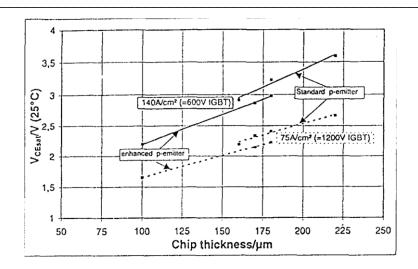

| Figure 2-8: Reduction in V <sub>ce</sub> with chip thickness [35]                             | 21 |

| Figure 2-9: Planar Gate, Punch Through IGBT structure                                         | 21 |

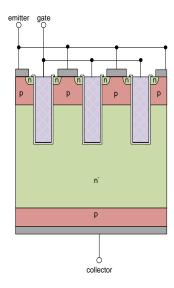

| Figure 2-10: Trench Gate, Non-Punch Through IGBT structure                                    | 23 |

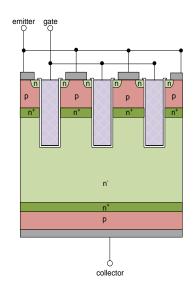

| Figure 2-11: Structure of CSTBT                                                               | 24 |

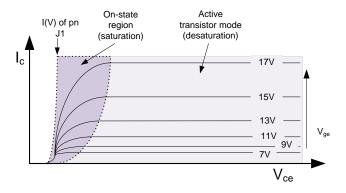

| Figure 2-12: IGBT forward characteristics                                                     | 25 |

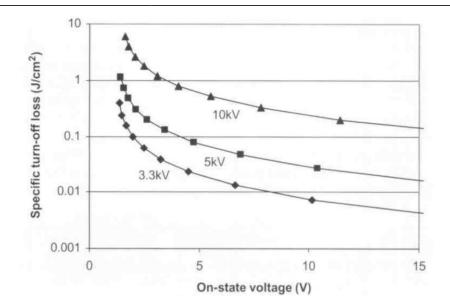

| Figure 2-13: Example curve illustrating trade off between switching and conduction loss [34]  | 26 |

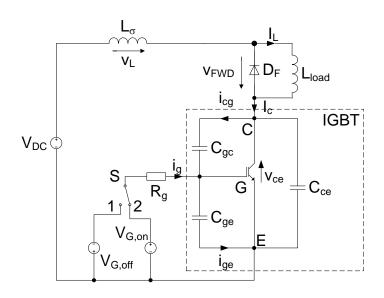

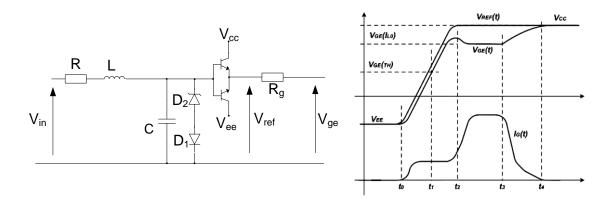

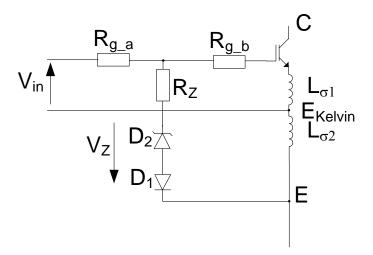

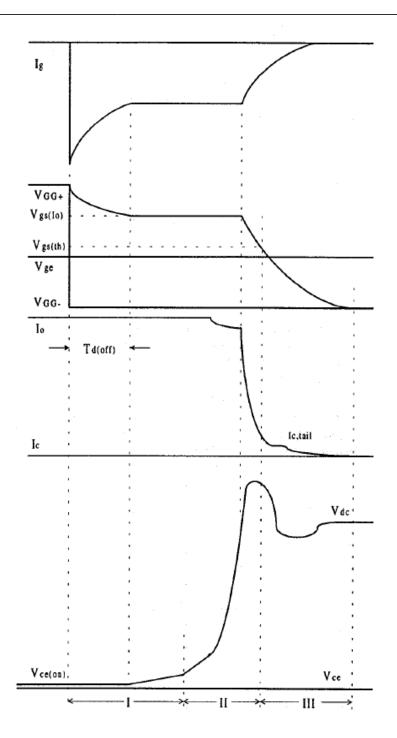

| Figure 2-14: IGBT pulse test circuit                                                          | 26 |

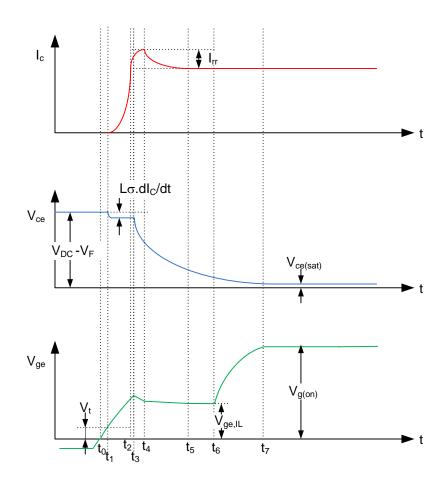

| Figure 2-15: IGBT switch-on waveforms with a bipolar diode                                    | 27 |

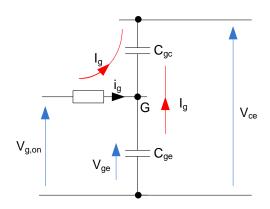

| Figure 2-16: Current flow in IGBT internal capacitance when $V_{ce}$ falls                    | 30 |

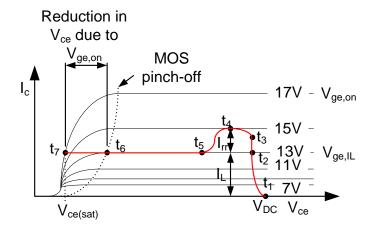

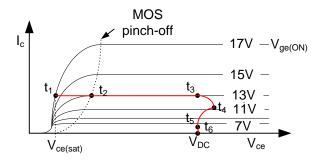

| Figure 2-17: I <sub>c</sub> (V <sub>ce</sub> ) characteristic curve for switch on.            | 32 |

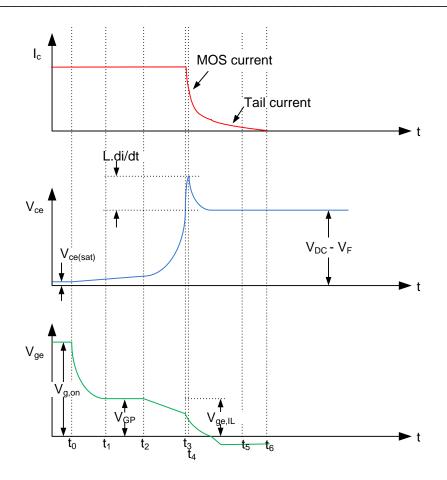

| Figure 2-18: IGBT switch-off waveforms with bipolar diode                                     | 33 |

| Figure 2-19: $I_c(V_{ce})$ characteristic curve for switch off                                | 35 |

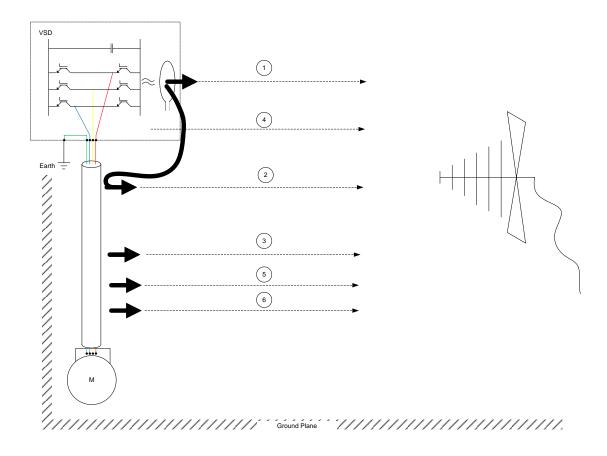

| Figure 2-20: Illustration of Emissions sources from VSD system                                | 38 |

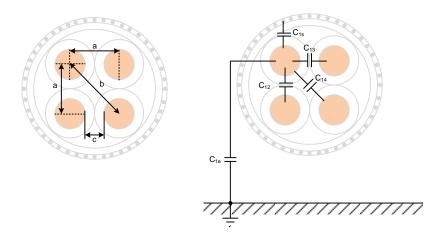

| Figure 2-21: Cross section of power cable identifying internal capacitances for one conductor | 39 |

| Figure 2-22: Cable capacitance to ground from a single conductor                              | 41 |

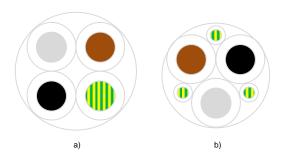

| Figure 2-23: Cable cross section a) 3 phase , 1 ground non-symmetrical b) 3 phase, 3 ground,  |    |

| symmetrical.                                                                                  | 44 |

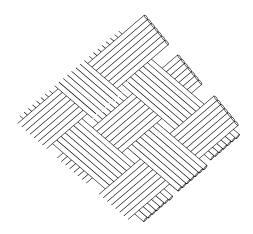

| Figure 2-24: Structure of Braid                                                               | 44 |

| Figure 2-25: Transfer Impedance of a Braided- wire shield [56]                                | 46 |

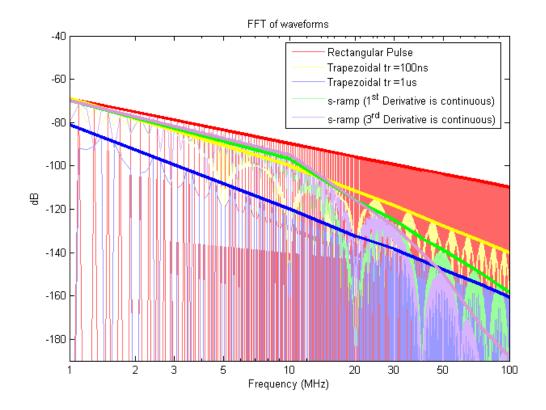

| Figure 2-26: Sample pulse trajectories                                                        | 49 |

| Figure 2-27: DFT of shaped pulse waveforms                                                    | 50 |

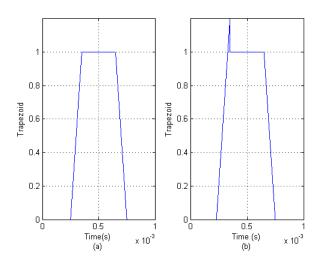

| Figure 2-28: a) Trapezoidal pulse with 10us rise time. b) Trapezoidal pulse with overshoot    | 52 |

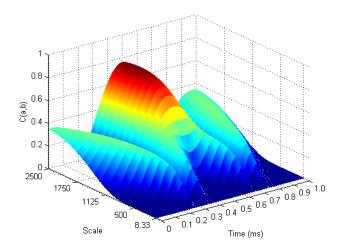

| Figure 2-29: Wavelet Transform of Trapezoidal pulse 1 kHz to 30 MHz                           | 53 |

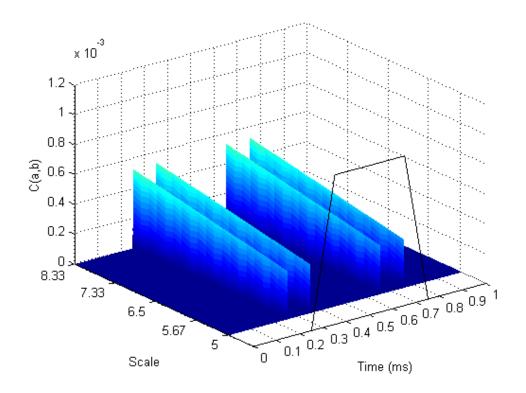

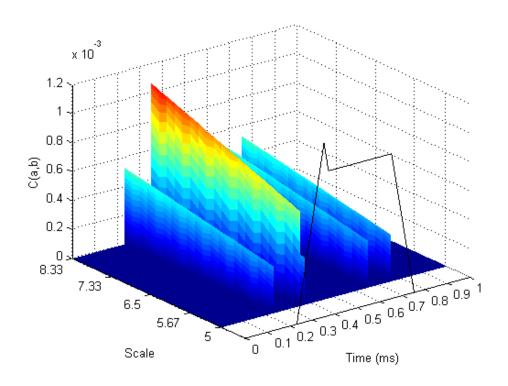

| Figure 2-30: Wavelet Transform of Trapezoidal pulse 30 MHz to 100 MHz                         | 54 |

| Figure 2-31: Wavelet Transform of Transzoidal pulse with overshoot 30 MHz to 100 MHz          | 54 |

|                                                                                                                      | _  |

|----------------------------------------------------------------------------------------------------------------------|----|

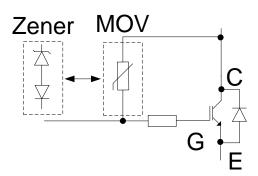

| Figure 3-1: Illustration of MOV or Zener used for overvoltage control                                                | 64 |

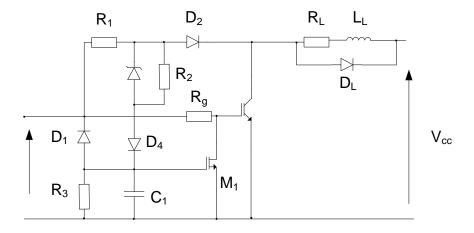

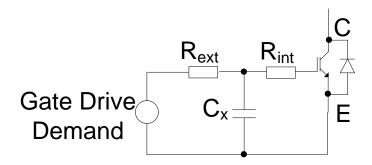

| Figure 3-2: Gate Drive offering protection against soft shorts for limits of SOA                                     | 66 |

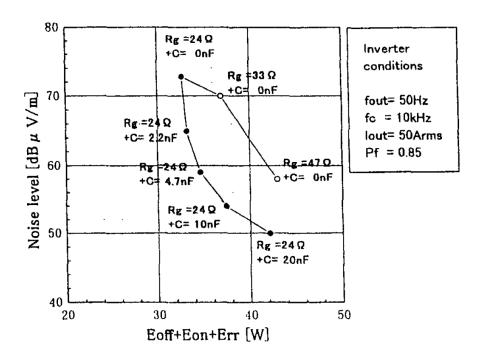

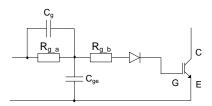

| Figure 3-3: a) CGD with Cge added; b) Change in switching loss and emissions with modified gate drive                |    |

| [87]                                                                                                                 | 70 |

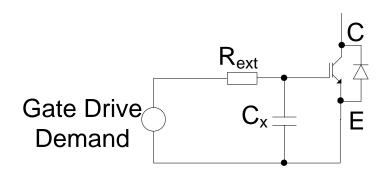

| Figure 3-4: T – Network and gate current waveforms.                                                                  | 71 |

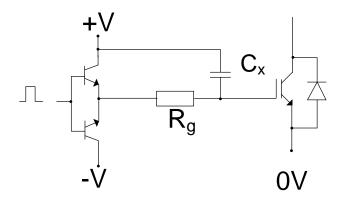

| Figure 3-5: Gate profile shaping using an RLC network [89]                                                           | 71 |

| Figure 3-6: Insertion of capacitor to improve stability of voltage transient.                                        | 73 |

| Figure 3-7: Pulse transformer in series with freewheeling diode for current measurement                              | 74 |

| Figure 3-8: dl/dt control using a Zener diode                                                                        | 74 |

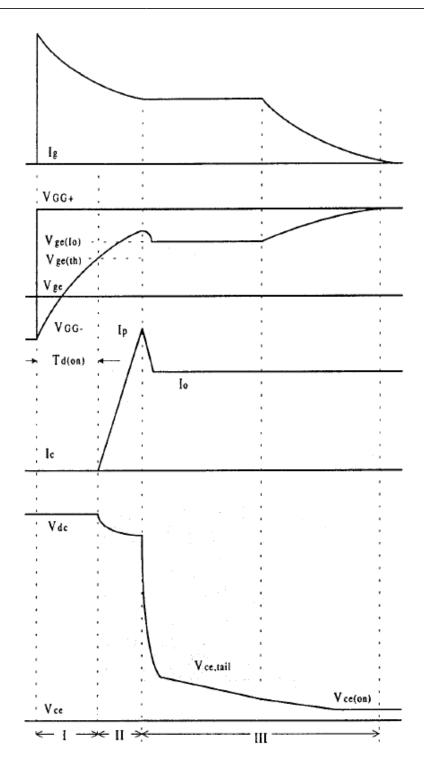

| Figure 3-9: Switch on waveforms [84]                                                                                 | 76 |

| Figure 3-10 : Switch off waveforms [84]                                                                              | 77 |

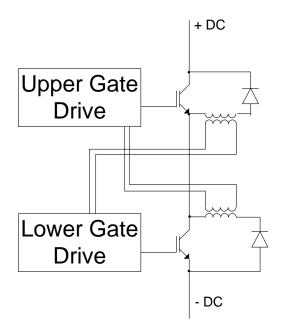

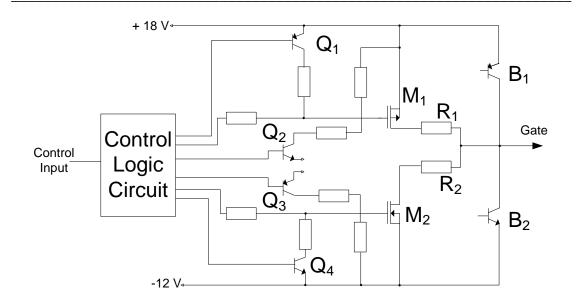

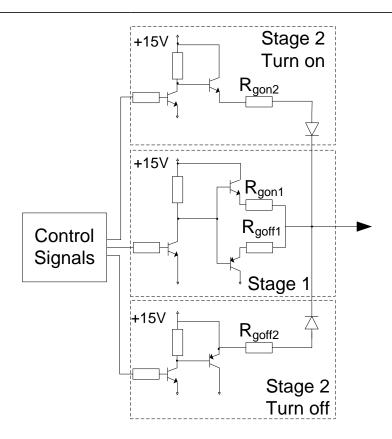

| Figure 3-11: Three stage gate drive                                                                                  | 78 |

| Figure 3-12: Switched resistance gate drive                                                                          | 81 |

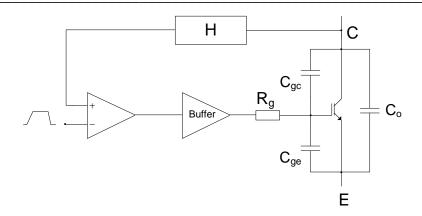

| Figure 3-13: Feedback gate drive circuit for dV/dt control                                                           | 82 |

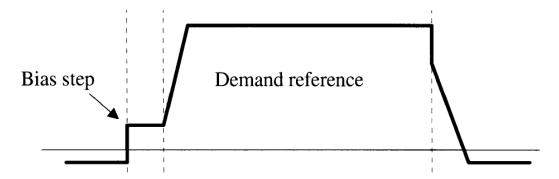

| Figure 3-14: Bias Step added to Voltage demand                                                                       | 82 |

| Figure 3-15: Gate drive schematic for control of conducted emissions                                                 | 84 |

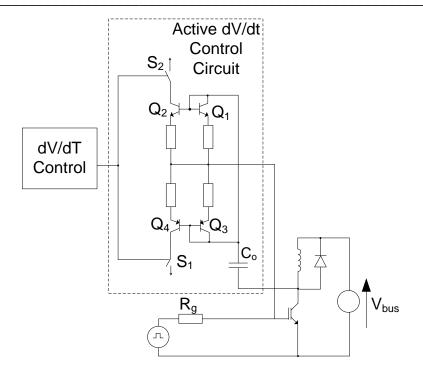

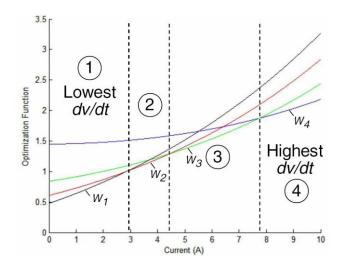

| Figure 3-16: Optimisation of four stage dV/dt control [101]                                                          | 84 |

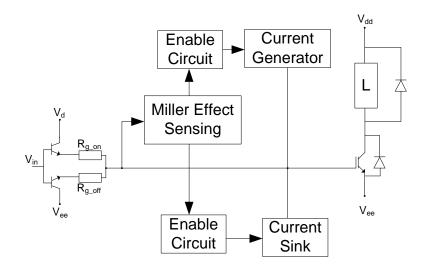

| Figure 3-17: Block diagram of high current gate drive.                                                               | 85 |

| Figure 3-18:Two stage switch off gate drive                                                                          | 87 |

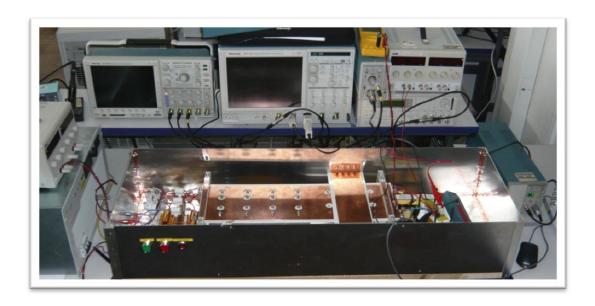

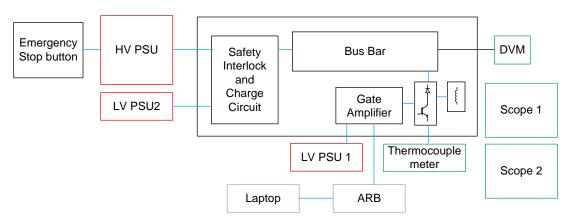

| Figure 4-1: Photograph of Pulse Test Rig                                                                             | 93 |

| Figure 4-2: Block Diagram of Pulse Test Rig                                                                          | 93 |

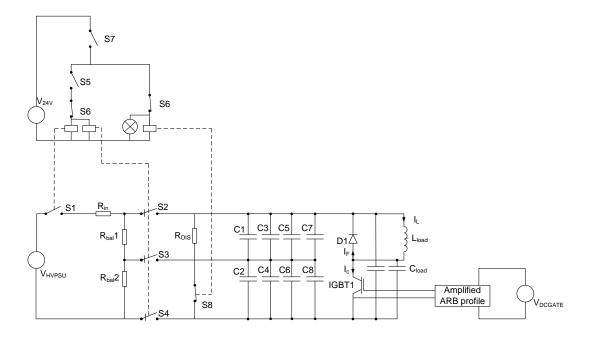

| Figure 4-3: Pulse Test schematic                                                                                     | 94 |

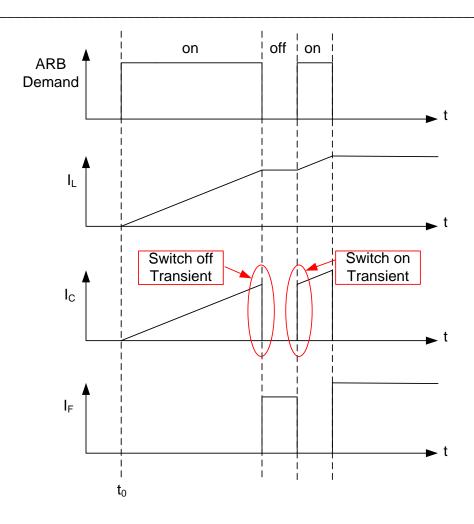

| Figure 4-4: Timing diagram to achieve desired current level                                                          | 95 |

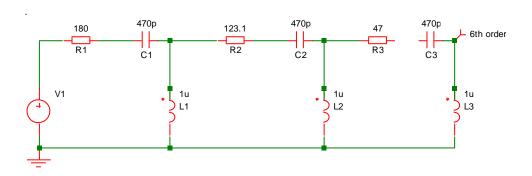

| Figure 4-5: Passive filter schematic                                                                                 | 97 |

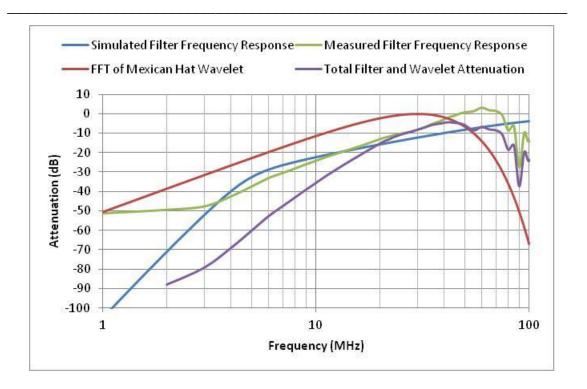

| Figure 4-6: Frequency Domain Filter and Wavelet Attenuation                                                          | 98 |

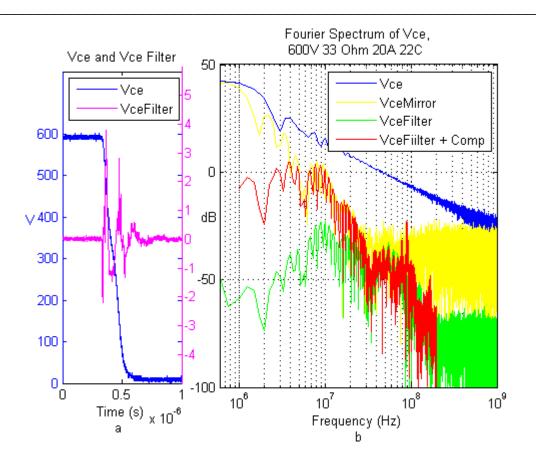

| Figure 4-7: a) Captured V <sub>ce</sub> and V <sub>ce</sub> filtered signals; b) Fourier analysis of voltage signals | 99 |

| Figure 4-8: Mexican Hat Wavelet Analysis (with pseudo frequency of 30 MHz) of $V_{ce}$ and $V_{ce}$ Filter 10        | 01 |

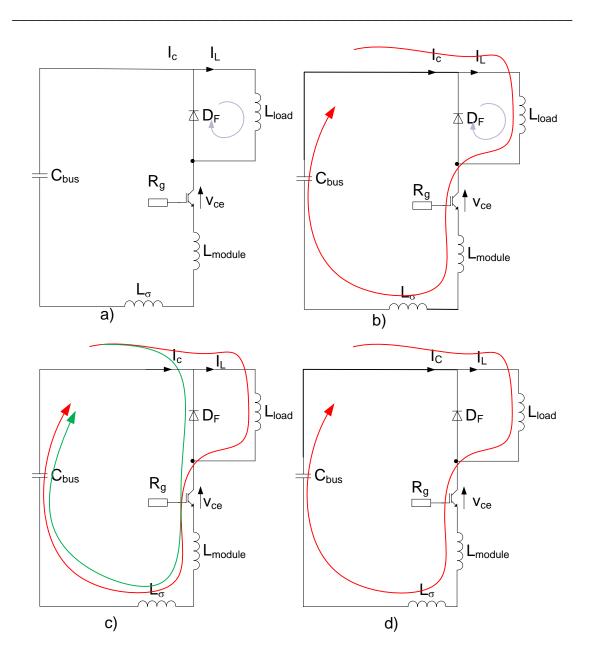

| Figure 4-9: Illustration of transient current path at switch on                                                      | 03 |

| Figure 4-10: Illustration of transient currents and induced voltage                                                  | 04 |

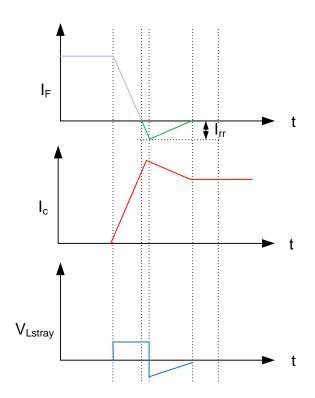

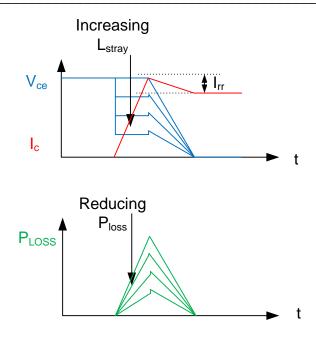

| Figure 4-11: Effect of switch on power loss with bus bar inductance                                                  | 05 |

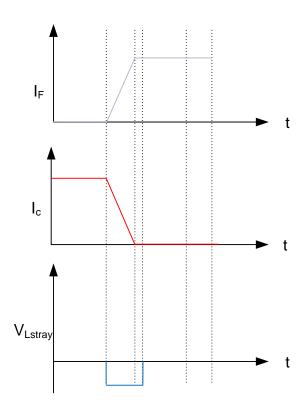

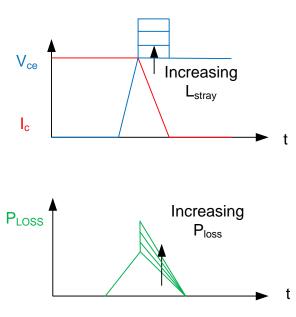

| Figure 4-12: Current transient during switch off                                                                     | 06 |

| Figure 4-13: Change in switch off loss with increasing bus bar inductance                                            | 06 |

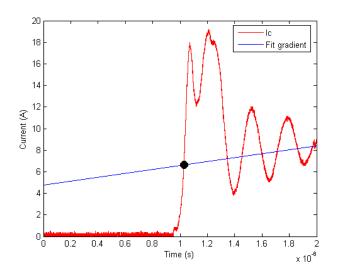

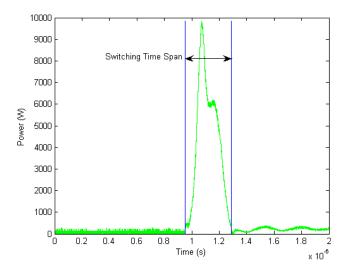

| Figure 4-14: Illustration of Ic at switch on                                                                         | 10 |

| Figure 4-15: Power loss calculation for a switch on event.                                                           | 10 |

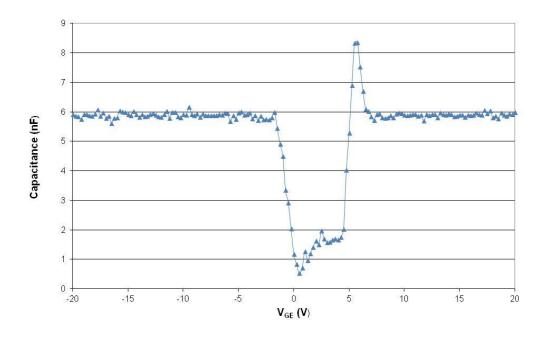

| Figure 4-16: IGBT gate capacitance versus gate voltage                                                               | 11 |

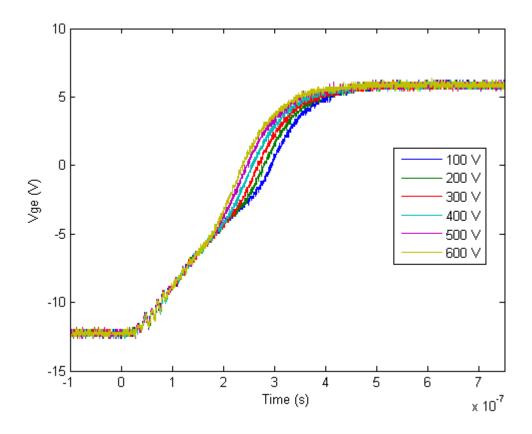

| Figure 4-17: Change in V <sub>ge</sub> with V <sub>ce</sub>                                                          | 12 |

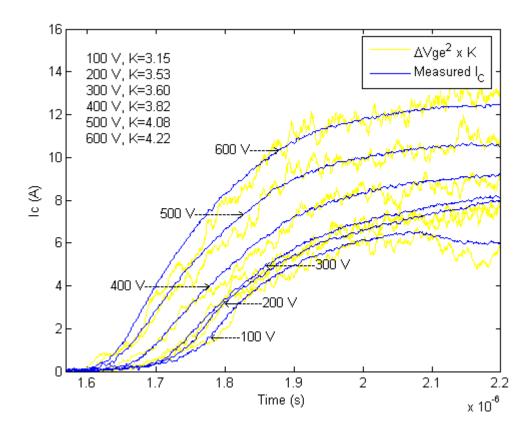

| Figure 4-18: Change in transconductance in practice                                                       | 113         |

|-----------------------------------------------------------------------------------------------------------|-------------|

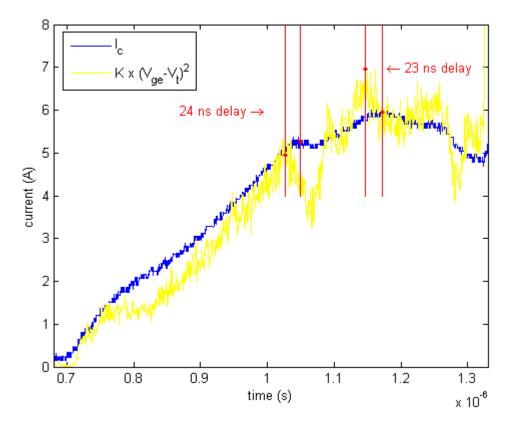

| Figure 4-19: Intrinsic IGBT Loop Delay for Collector Current                                              | 114         |

| Figure 4-20: Intrinsic IGBT Loop Delay for Collector Emitter Voltage                                      | 115         |

| Figure 4-21: Photograph of the OATS used                                                                  | 117         |

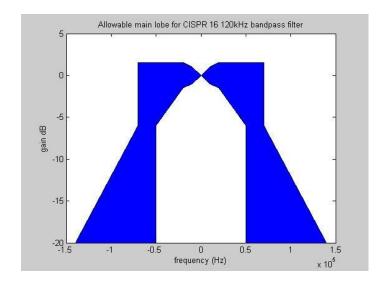

| Figure 4-22: CISPR16 pass band                                                                            | 118         |

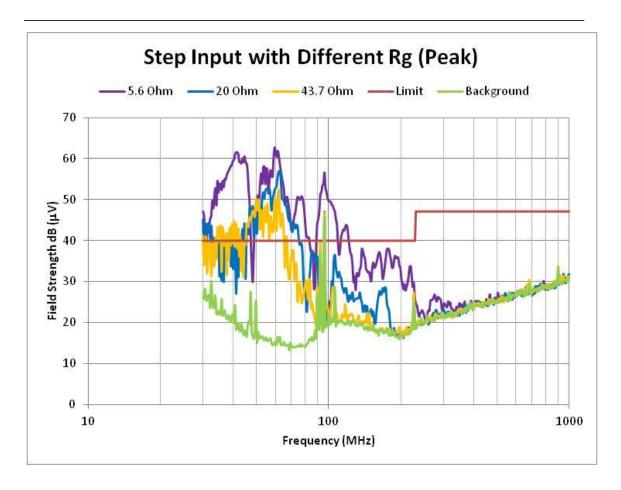

| Figure 4-23: Measured Radiated Emissions from step input.                                                 | 120         |

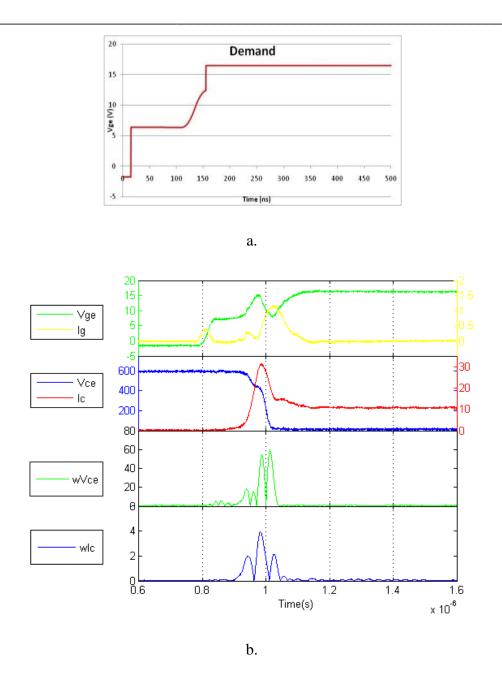

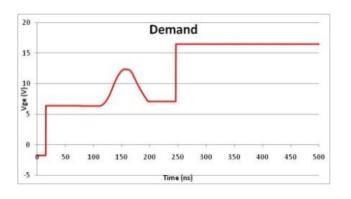

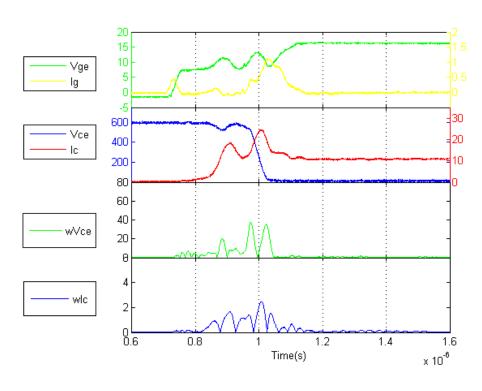

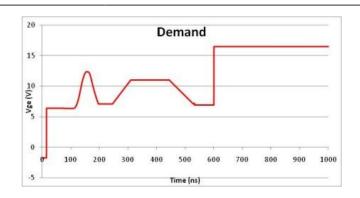

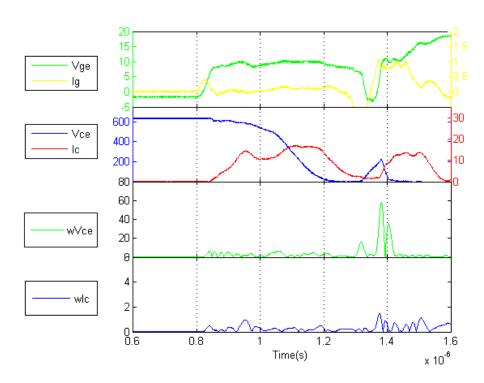

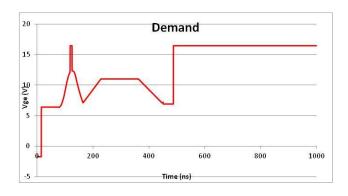

| Figure 5-1: a) V <sub>ge</sub> Demand; b) Voltage and current wavelet transform for step input            | 125         |

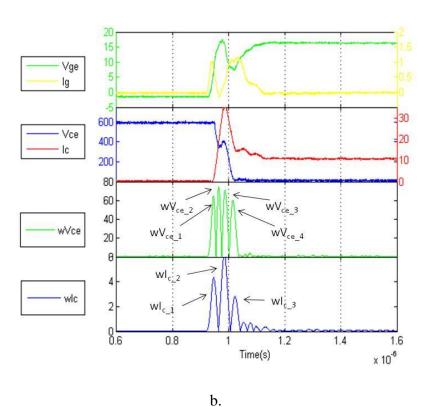

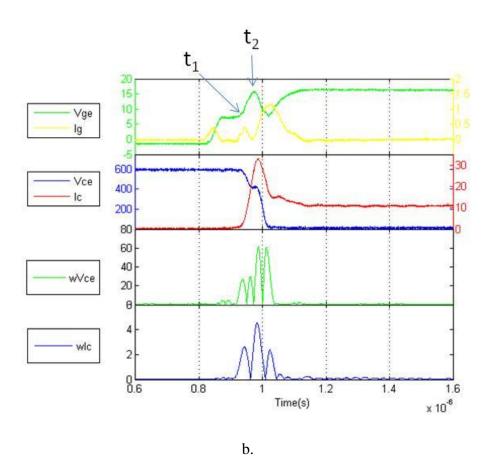

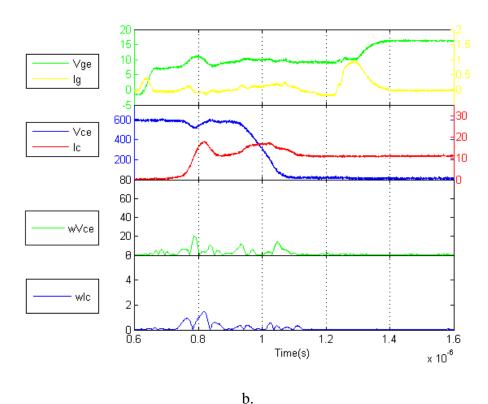

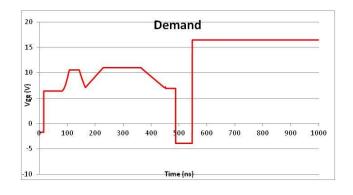

| Figure 5-2: a) $V_{ge}$ Demand; b) Voltage and current wavelet transform, held at $V_{t}$ for 85ns        | 127         |

| Figure 5-3: a) $V_{ge}$ Demand; b) Voltage and current wavelet transform, controlled slope of $V_{ge}$ to | o influence |

| I <sub>c</sub>                                                                                            | 129         |

| Figure 5-4: a) $V_{ge}$ Demand; b) Voltage and current wavelet transform, controlled slope of $V_{ge}$ to | o remove    |

| Q <sub>rs</sub>                                                                                           | 131         |

| Figure 5-5: a) $V_{ge}$ Demand; b) Voltage and current wavelet transform, controlled slope of $V_{ge}$ to | remove      |

| Q <sub>rf</sub>                                                                                           | 133         |

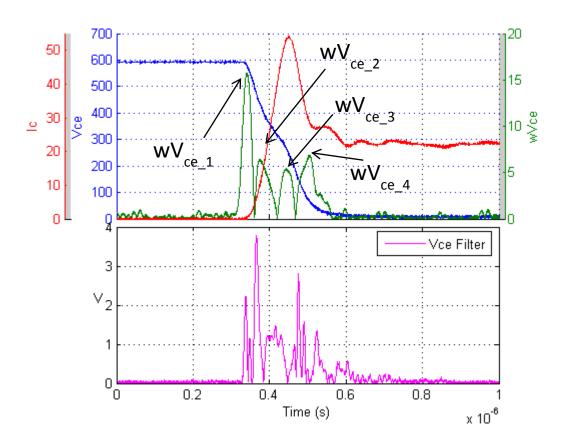

| Figure 5-6: Illustration of wV <sub>ce</sub> control                                                      | 135         |

| Figure 5-7: Illustration of wl <sub>c</sub> control                                                       | 136         |

| Figure 5-8: wV <sub>ce</sub> and wI <sub>c</sub> for switch off                                           | 137         |

| Figure 5-9: Typical setup schematic for testing VSD for radiated emissions on an OATS                     | 138         |

| Figure 5-10: Setup of pulse testing equipment for radiated emissions on an OATS                           | 140         |

| Figure 5-11: Continuous pulse train with fixed duty cycle to determine load current                       | 141         |

| Figure 5-12: a) Pulse test setup for radiated emissions, b) OATS.                                         | 142         |

| Figure 5-13: Radiated Emissions from power supply units without the IGBT switching                        | 143         |

| Figure 5-14: Signal path taken by radiated emission sources                                               | 144         |

| Figure 5-15: Azimuth pattern at select frequencies                                                        | 146         |

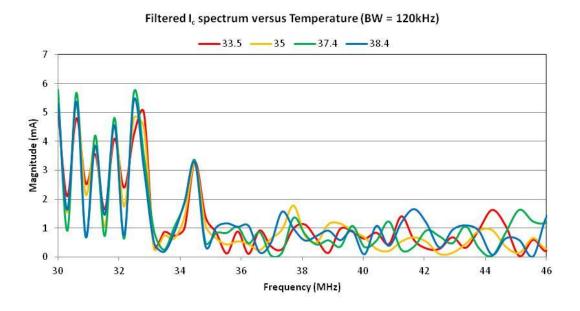

| Figure 5-16 : Measured Radiated Emissions spectrum change with temperature                                | 148         |

| Figure 5-17: Frequency spectrum of V <sub>ce</sub> change with temperature                                | 149         |

| Figure 5-18: Frequency spectrum of I <sub>c</sub> change with temperature                                 | 149         |

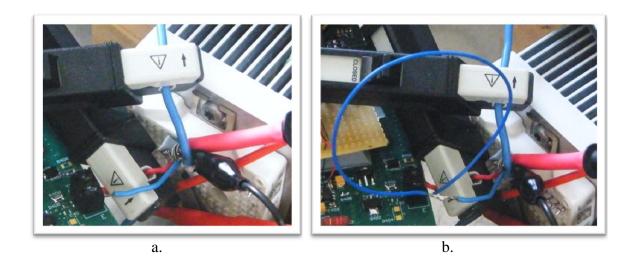

| Figure 5-19: a) Connection of FPGA gate drive PCB to IGBT, No Loop; b) connection with Loop               | inserted in |

| path                                                                                                      | 152         |

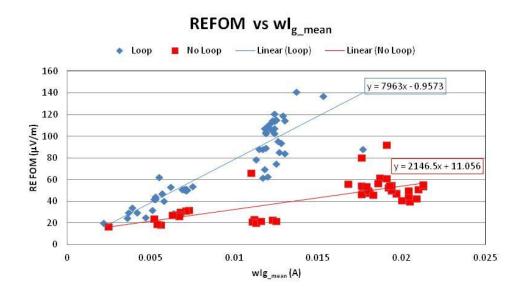

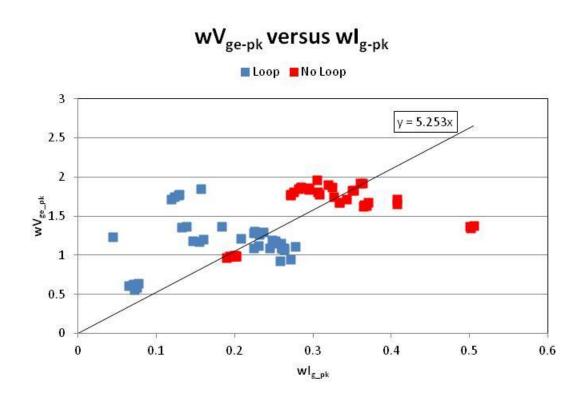

| Figure 5-20: Change in REFOM versus wl <sub>g_mean</sub>                                                  | 153         |

| Figure 5-21: Change in REFOM versus wV <sub>ge_mean</sub>                                                 | 154         |

| Figure 5-22: Change in gate circuit impedance Loop and No Loop                                            | 155         |

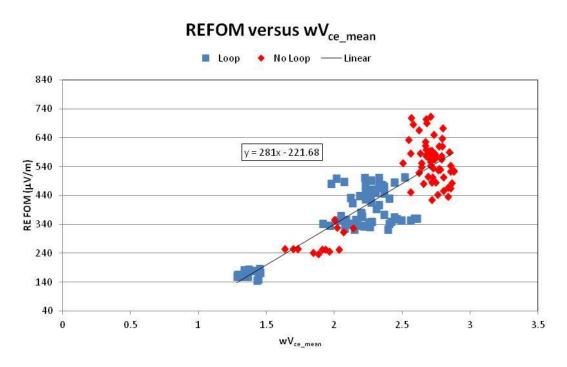

| Figure 5-23: REFOM versus wV <sub>ce_mean</sub>                                                           | 156         |

| Figure 5-24: REFOM versus wlc_mean                                                                        | 157         |

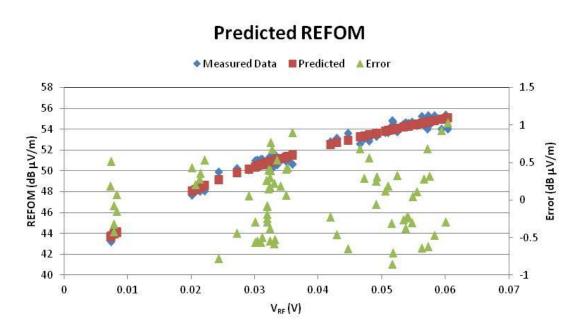

| Figure 5-25: REFOM versus V <sub>RF</sub>                                                                 | 158         |

| Figure 5-26: Predicted REFOM from V <sub>RF</sub> measurements                                            | 159         |

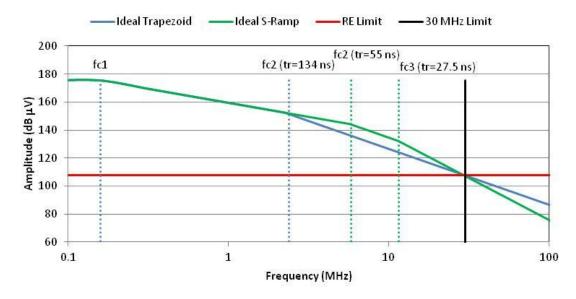

| Figure 5-27: Rise Time Limits based on Ideal Trapezoid and Ideal S-ramp                                                         | 161 |

|---------------------------------------------------------------------------------------------------------------------------------|-----|

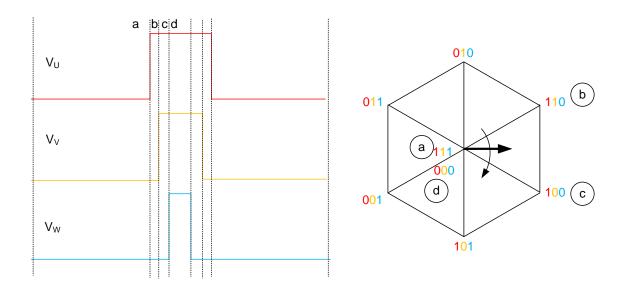

| Figure 6-1: Illustration of SVM                                                                                                 | 165 |

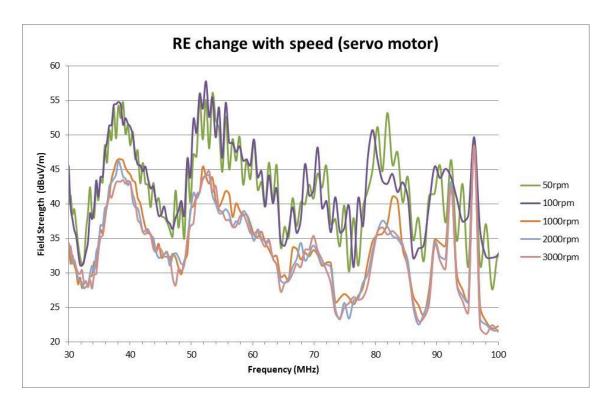

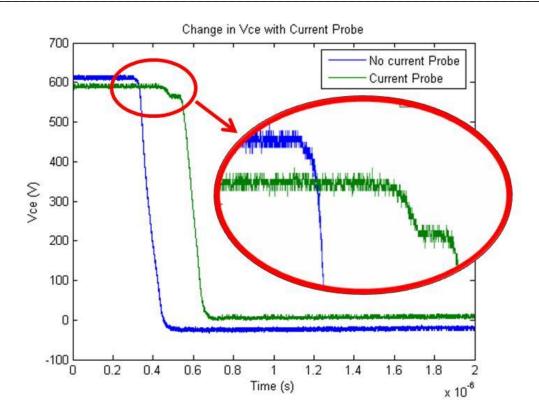

| Figure 6-2: Change in radiated emissions levels with change in motor rotational speed                                           | 166 |

| Figure 6-3: Change in radiated emission levels with output vector                                                               | 167 |

| Figure 6-4: Change of radiated emissions with switching frequency                                                               | 168 |

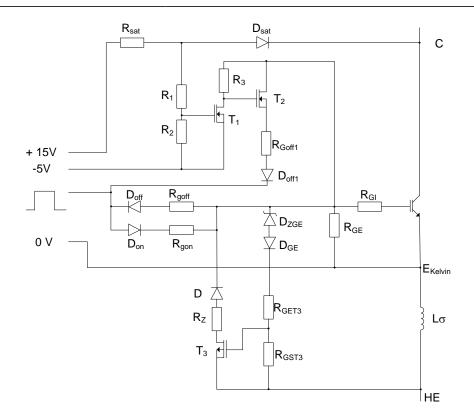

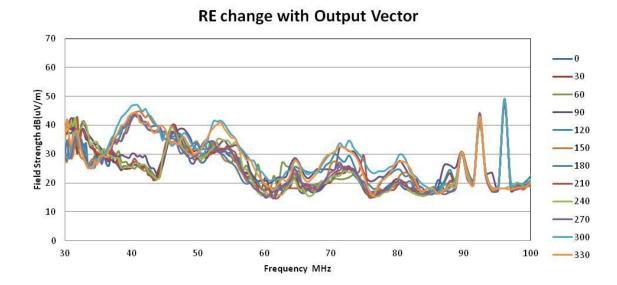

| Figure 6-5: DST1405 gate drive circuit.                                                                                         | 169 |

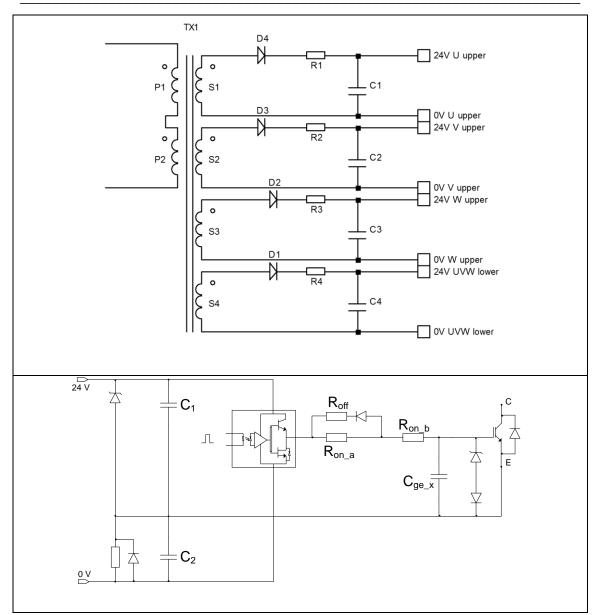

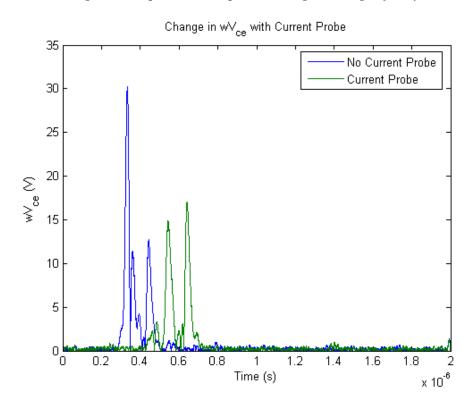

| Figure 6-6: Impact of current probe on voltage switching trajectory                                                             | 171 |

| Figure 6-7: wV <sub>ce</sub> for switch on transient with and without collector current probe                                   | 171 |

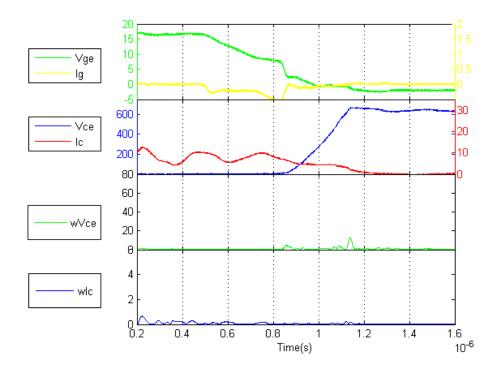

| Figure 6-8: VSD Pulse Test Setup.                                                                                               | 172 |

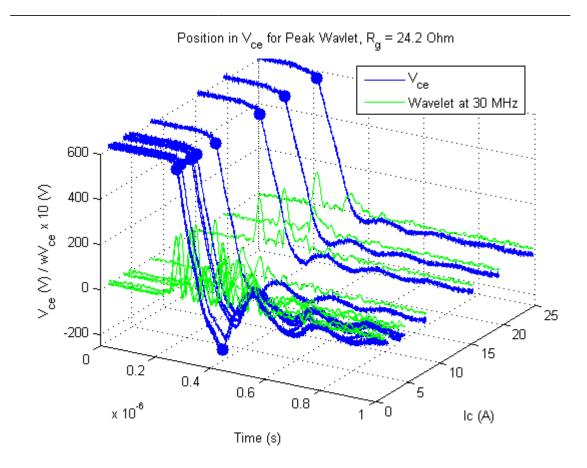

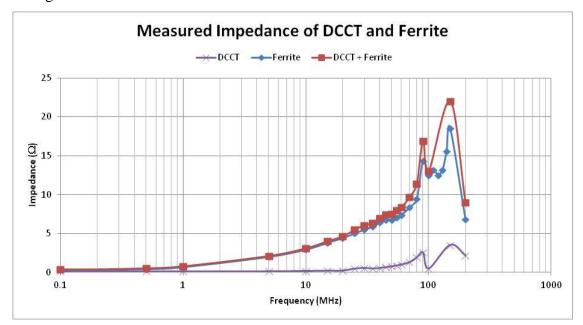

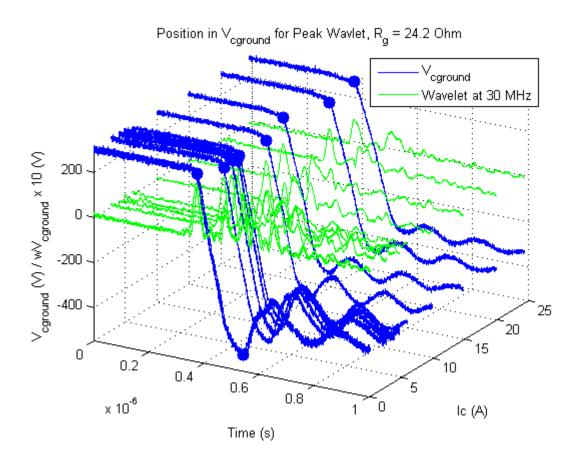

| Figure 6-9: Switch on transient and peak emissions for R $_{\rm g}$ = 24.2 $\Omega$                                             | 173 |

| Figure 6-10: Measured Impedance of Ferrite and DCCT                                                                             | 174 |

| Figure 6-11: Switch on transient and peak emissions for R $_{\!g}$ = 24.2 $\Omega$ measured to ground                           | 175 |

| Figure 6-12: Change in dV/dt with current                                                                                       | 176 |

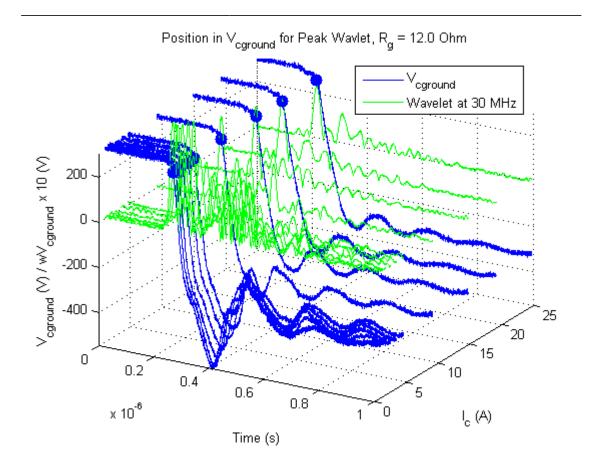

| Figure 6-13: Switch on transient and peak emissions for R $_{\!g}$ = 12 $\Omega$                                                | 177 |

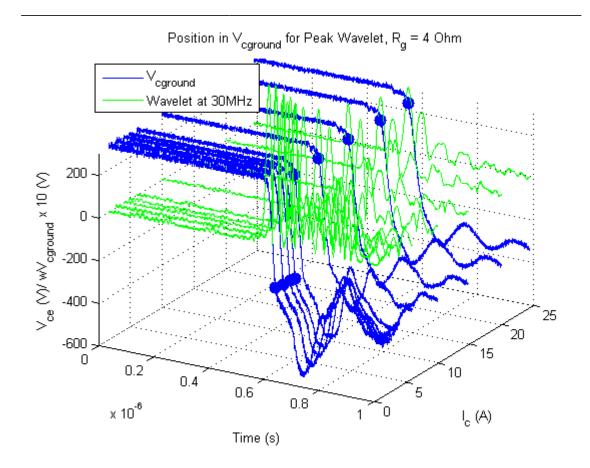

| Figure 6-14: Switch on transient and peak emissions for $R_g$ = 4 $\Omega$                                                      |     |

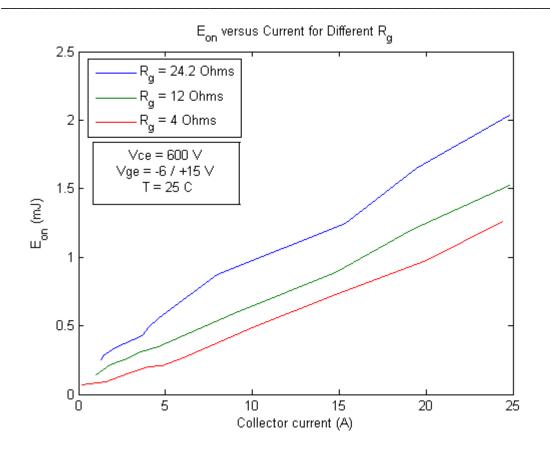

| Figure 6-15: E <sub>on</sub> for each of the above conditions                                                                   |     |

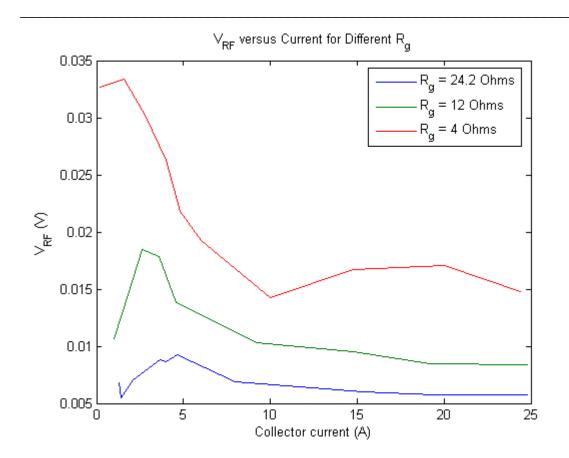

| Figure 6-16: change in V <sub>RF</sub> with current for different R <sub>g</sub>                                                | 180 |

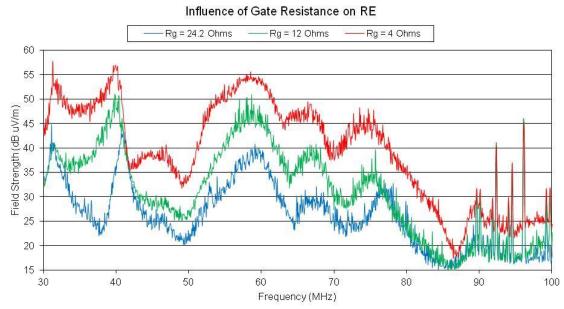

| Figure 6-17: Measured Radiated Emissions for different R <sub>g</sub> values                                                    | 181 |

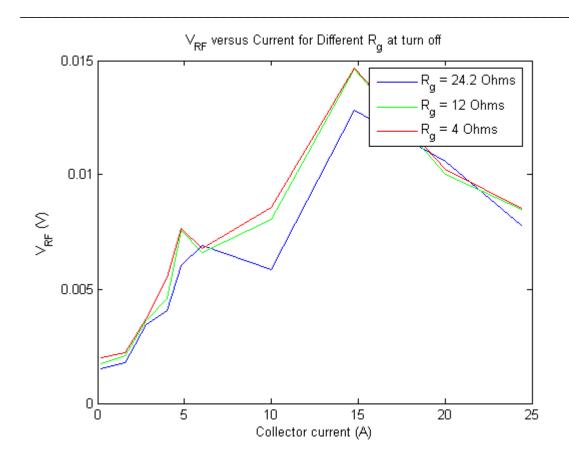

| Figure 6-18: change in V <sub>RF</sub> with current for different R <sub>g</sub> at switch off                                  |     |

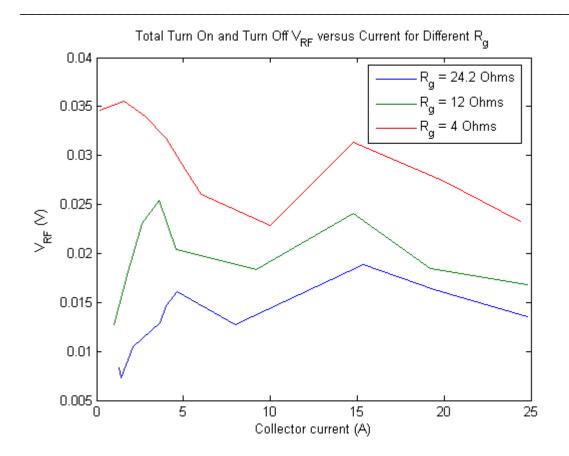

| Figure 6-19: change in $V_{RF}$ with current for different $R_g$ (sum of switch off and switch on)                              |     |

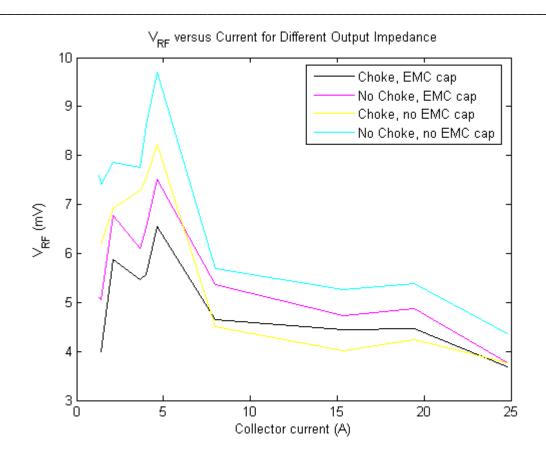

| Figure 6-20: Measured V <sub>RF</sub> with various combinations of filter components                                            | 184 |

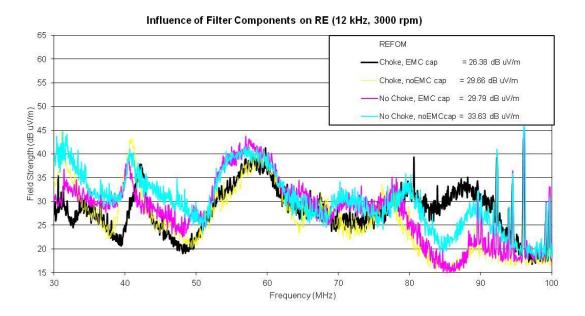

| Figure 6-21: Measured Radiated Emissions for VSD internal filter components at 100 rpm                                          | 185 |

| Figure 6-22: Measured Radiated Emissions for VSD internal filter components at 3000 rpm                                         | 185 |

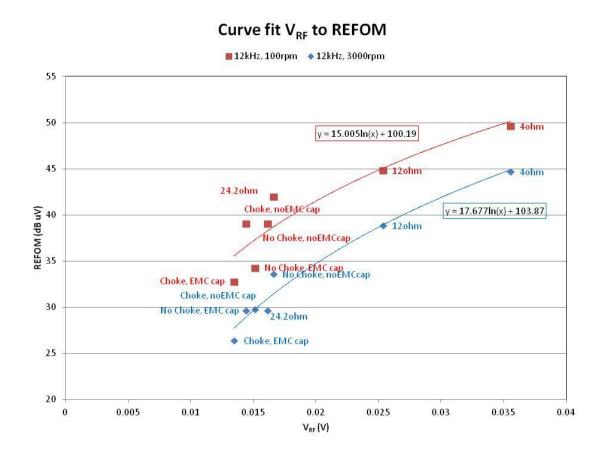

| Figure 6-23: DST1405 REFOM versus measured RF content in voltage                                                                | 186 |

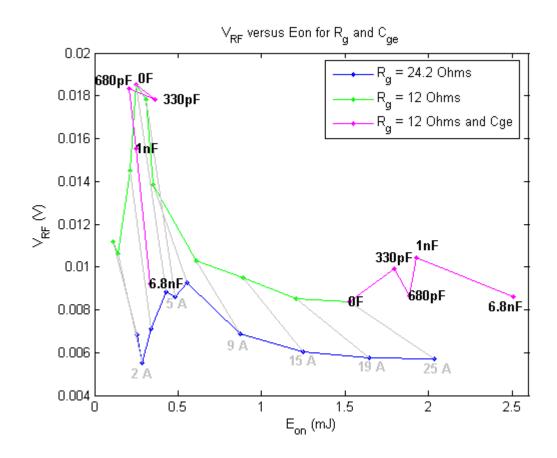

| Figure 6-24: Switch on loss versus V <sub>RF</sub> with external C <sub>ge</sub>                                                | 187 |

| Figure 6-25: Passive gate drive, parallel capacitor                                                                             | 188 |

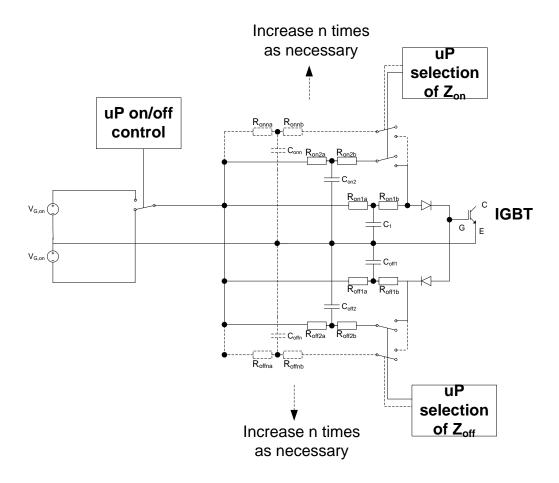

| Figure 6-26: Selectable Gate impedance                                                                                          | 189 |

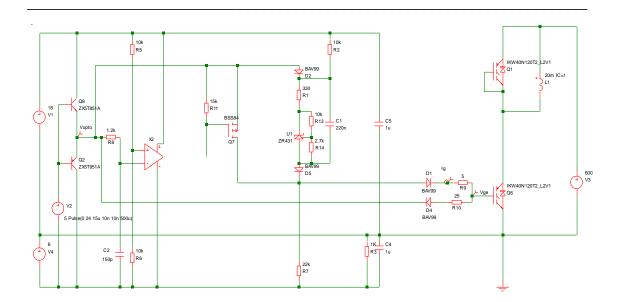

| Figure 6-27: Gate Threshold – Hold Circuit                                                                                      | 191 |

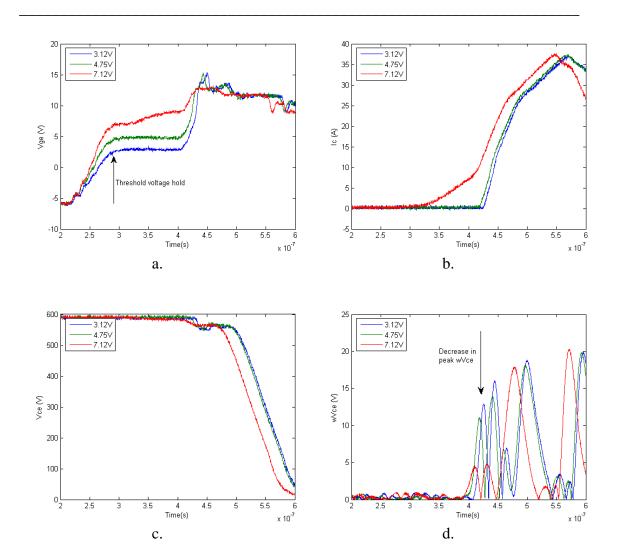

| Figure 6-28: Threshold hold transient waveforms a) V <sub>ge</sub> , b) I <sub>c</sub> , c)V <sub>ce</sub> , d)wV <sub>ce</sub> | 192 |

| Figure A-1: Schematic Page 1                                                                                                    | 202 |

| Figure A-2: Schematic Page 2                                                                                                    | 202 |

| Figure A-3: Schematic Page 3                                                                                                    | 203 |

| Figure A-4: Schematic Page 4                                                                                                    | 203 |

| Figure A-5: Schematic Page 5                                                                                                    | 204 |

| Figure A-6: Schematic Page 6                                                                                                    | 204 |

| Figure A-7: Schematic Page 7                                                                                                    | 205 |

| Figure A-8: Schematic Page 8                                              | 205 |

|---------------------------------------------------------------------------|-----|

| Figure A-9: Schematic Page 9                                              | 206 |

| Figure A-10: Schematic Page 10                                            | 206 |

| Figure A-11: High Speed signal tracks                                     | 207 |

| Figure A-12: PCB Power Layer 1                                            | 208 |

| Figure A-13: PCB Power layer 2                                            | 209 |

| Figure A-14: Delay time and crosstalk for Data line D1, D2 and D3         | 210 |

| Figure A-15: Thermal image of operation PCB.                              | 211 |

| Figure A-16: Photograph of FPGA gate drive with programmer.               | 212 |

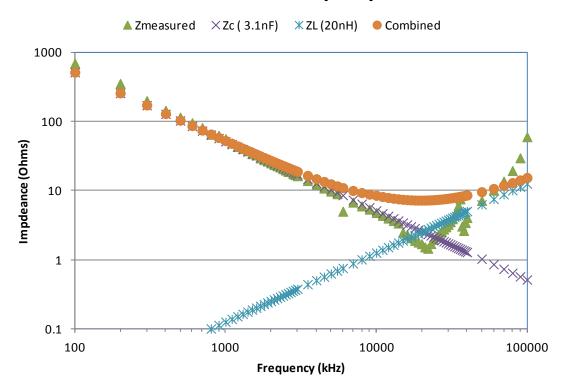

| Figure B-1: Curve fitting to estimate gate capacitance and inductance     | 214 |

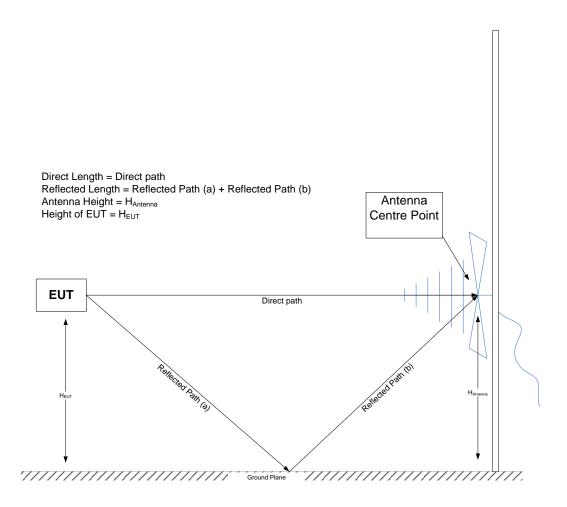

| Figure C-1: Illustration of direct and reflected radiated emissions paths | 215 |

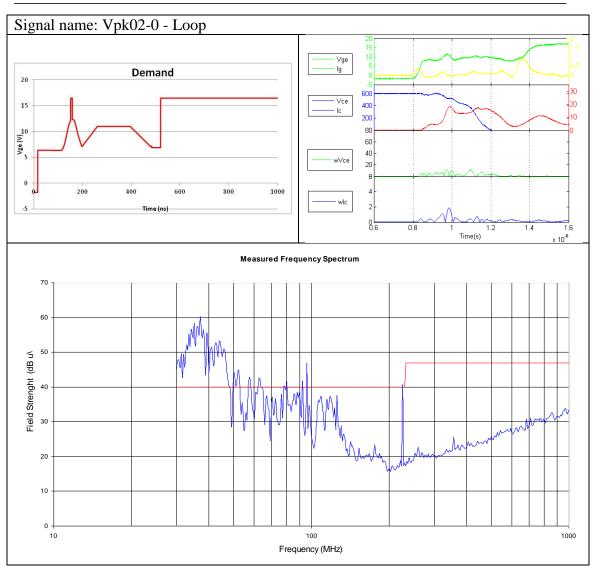

| Figure D-1: RE from signal Vpk02_0                                        | 218 |

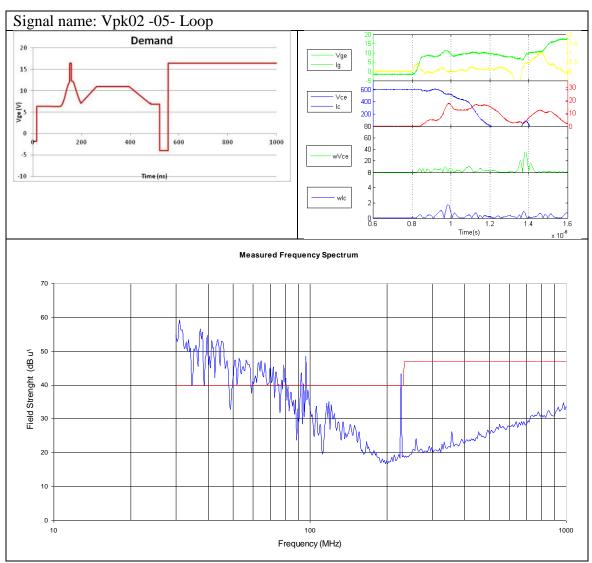

| Figure D-2: RE from signal Vpk02_05                                       | 219 |

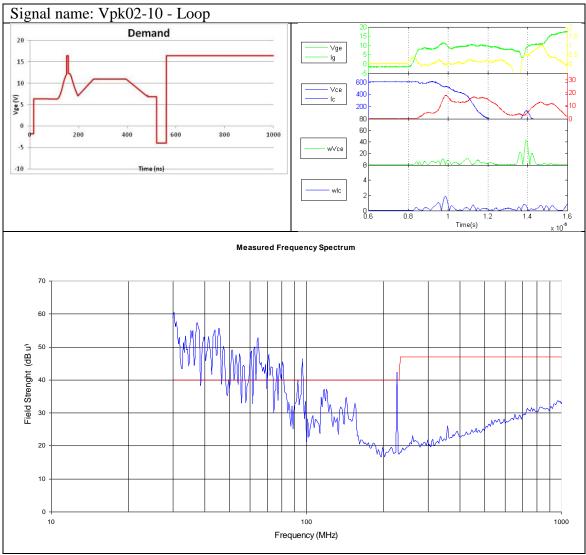

| Figure D-3: RE from signal Vpk02_10                                       | 220 |

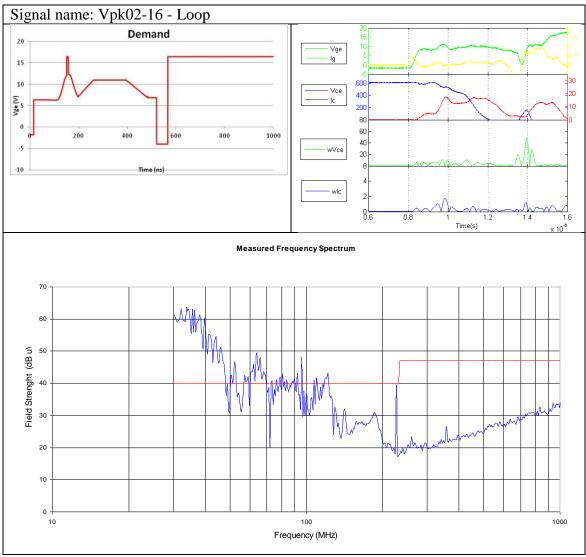

| Figure D-4: RE from signal Vpk02_16                                       | 221 |

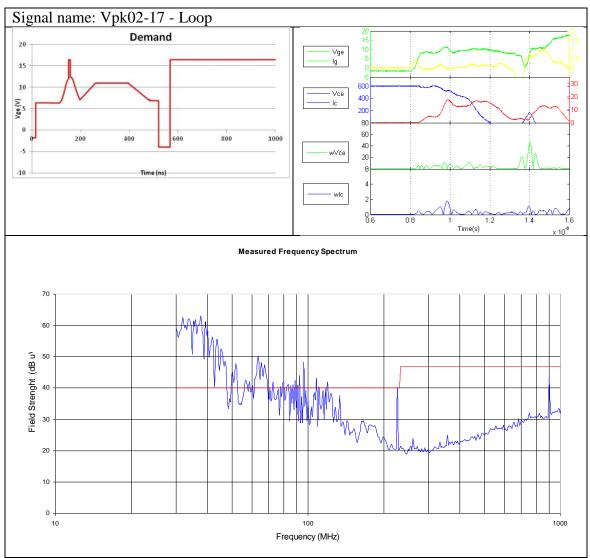

| Figure D-5: RE from signal Vpk02_17                                       | 222 |

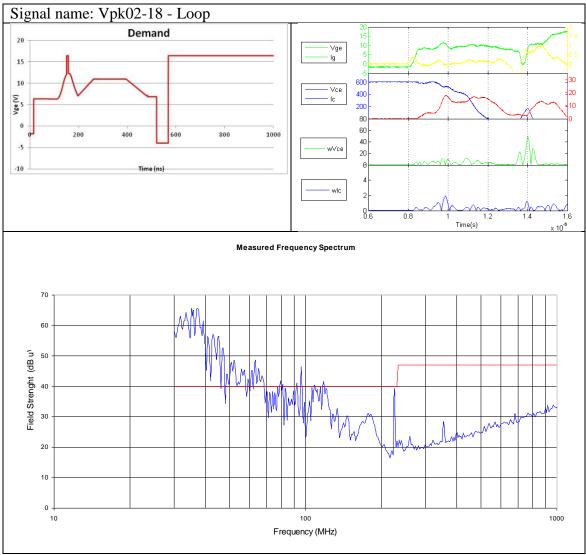

| Figure D-6: RE from signal Vpk02_18                                       | 223 |

## **List of Tables**

| Table 2-1: Calculated cable capacitance for a typical power cable             | 41    |

|-------------------------------------------------------------------------------|-------|

| Table 4-1: Example of Loss Reduction due to Bus Bar Inductance                | . 108 |

| Table 4-2: Radiated Emission Limits at 10 m                                   | . 116 |

| Table 5-1: Switch on Loss                                                     | . 134 |

| Table C-1: Signal transit time for various antenna heights                    | . 216 |

| Table C-2: Phase delay for different frequencies at different antenna heights | . 216 |

| Table C-3: Constants used to calculate the above tables                       | . 216 |

| Table E-1: Physical constants and dimensions of IGBT die                      | .224  |

| Table E-2: Temperature rise in Silicon for given energy pulse                 | 224   |

## **List of Symbols**

| Symbol               | Description                                                          |

|----------------------|----------------------------------------------------------------------|

| $C_{ox}$             | Oxide capacitance per unit area                                      |

| $C_{ge}$             | Gate emitter capacitance                                             |

| $C_{gc}$             | Gate collector capacitance                                           |

| D                    | Diffusion constant                                                   |

| $E_{C}$              | Conduction band minimum energy                                       |

| $E_{F}$              | Fermi level energy                                                   |

| $E_{on}$             | IGBT Turn on energy loss                                             |

| $E_{m}$              | Maximum electric field strength                                      |

| $E_{rr}$             | Reverse Recovery Energy                                              |

| $E_V$                | Valence band maximum energy                                          |

| $g_{fs}$             | Forward transconductance                                             |

| $I_c$                | Collector Current                                                    |

| $I_F$                | Diode forward current                                                |

| $I_g$                | Gate current                                                         |

| $I_{pk}$             | Peak current                                                         |

| $I_{rr}$             | Reverse recovery current                                             |

| k                    | Boltzmann's constant                                                 |

| $L_{ch}$             | Length of channel                                                    |

| $N_D$                | Donor ion concentration                                              |

| Q                    | Electron charge                                                      |

| $Q_{rf}$             | Diode depletion charge                                               |

| Qrr                  | Reverse recovery charge                                              |

| $Q_{rs}$             | Diode stored Charge                                                  |

| $R_g$                | Gate resistor                                                        |

| T                    | Temperature                                                          |

| $T_{d.on}$           | Turn on delay time                                                   |

| $V_a$                | Avalanche breakdown voltage                                          |

| $V_{bi}$             | Built in voltage (pn junction)                                       |

| $V_{ce}$             | Collector emitter voltage                                            |

| V <sub>ce,sat</sub>  | Collector emitter saturation voltage (when the device is turned on). |

| V <sub>contact</sub> | Voltage drop due to semiconductor / metal contact resistance         |

| $V_{DC}$             | DC bus voltage                                                       |

| $V_{\rm F}$          | Diode forward voltage                                                |

| $V_{FRM}$            | Repetitive peak forward voltage                                      |

| $V_{ge}$             | Gate emitter voltage                                                 |

| $V_{gatePSU}$        | Power supply voltage for gate drive                                  |

| $V_{GP}$             | Gate plateau voltage                                                 |

| $V_t$                | Threshold Voltage                                                    |

| W                    | Depletion width                                                      |

## List of Symbols

| Symbol                | Description                     |

|-----------------------|---------------------------------|

| $W_{n-}$              | Width of diode intrinsic region |

| $W_{ch}$              | Width of channel                |

| X                     | Electron affinity               |

| $\Phi_{\mathrm{m}}$   | Metal work function             |

| $\alpha_{pnp}$        | Gain of pnp transistor          |

| $\varepsilon_{\rm s}$ | Permittivity of semiconductor   |

| $\mu_n$               | Electron mobility               |

| τ                     | Carrier lifetime                |

#### **List of Abbreviations**

Abbreviations ac Alternating current AGD Active Gate Drive

ARB Arbitrary Waveform Generator

BJT Bipolar Junction Transistor

CE Conformité Européenne

CGD Conventional Gate Drive

CISPR Comité International Spécial des Perturbations Radioélectriques

CSTBT Carrier Stored Trench Gate Bipolar Transistor

DAC Digital to Analogue Converter

dc Direct current

DCCT Direct Current Current Transformer

DFT Discrete Fourier Transform

DIGBT Doubly Diffused Insulated Gate Bipolar Transistor

DVM Digital Volt Meter EM Electromagnetic

EMC Electromagnetic Compatibility

e.m.f Electromotive Force

EMI Electromagnetic Interference EUT Equipment Under Test

FPGA Field Programmable Gate Array FRED Fast Recovery Epitaxial Diodes

FS Field Stop

FWD Free Wheel Diode HF High Frequency

HV PSU High Voltage Power Supply

IC Integrated Circuit

IGBT Insulated Gate Bipolar Transistor IPM Intelligent Power Module

JFET Junction Field Effect Transistor

LF Low Frequency

MF Medium Frequency

MOSFET Metal Oxide Semiconductor Field Effect Transistor

MOV Metal Oxide Varistor

NPT Non Punch Through

OATS Open Area Test Site

PSU Power Supply Unit

PT Punch Through

QP Quasi Peak

RE Radiated Emissions

REFOM Radiated Emissions Figure of Merit

RF Radio Frequency R.M.S Root mean square

SMPS Switched Mode Power Supply

SOA Safe Operating Area

SOI Silicon on Insulator

SVM Space Vector Modulation

UHF Ultra High Frequency

VHF Very High Frequency

VSD Variable Speed Drive

#### **Chapter 1: Introduction**

## 1.1 Power Losses and Radiated Emissions in a Variable Speed Drive

Variable speed drives (VSD) in industrial applications are used to convert energy from a fixed frequency ac mains supply to a variable output frequency for speed control of an electrical machine. Over the last few decades, the increase in the performance of the power transistors used to control the flow of power have led to smaller, more efficient devices. Increases in microprocessor technology have allowed faster data processing improving the ability to execute complex control algorithms and improve the dynamic performance and precision of machine control. With increasing acceptance of human induced climate change, users of VSDs demand more efficient products to reduce their carbon footprint while maintaining an acceptable cost of equipment. While advances in individual components have contributed to the improvement in efficiency, the entire VSD system must be considered as a whole to leverage commercial and environmental benefits to the customer [1].

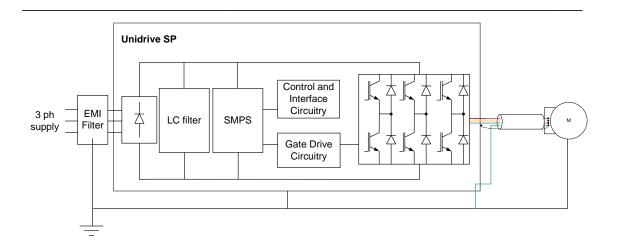

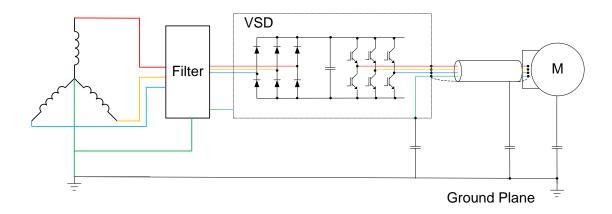

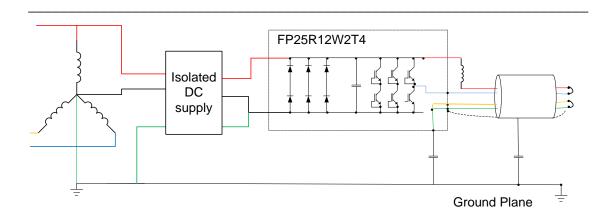

Control Techniques Unidrive SP<sup>™</sup> is a range of ac VSDs used for high performance industrial applications. The functional blocks within the VSD and system can be considered representative of a typical industrial VSD design and are illustrated in Figure 1-1. A three phase diode rectifier converts the sinusoidal mains voltages into a unipolar voltage which is then smoothed via the low pass LC filter to provide a smooth dc voltage. A switch mode power supply (SMPS) converts the rectified and smoothed dc voltage to appropriate voltage levels suitable for a microprocessor and digital control electronics. The control electronics provide the interface to the outside world receiving motion control demand signals and relaying confirmation of these operations. The full bridge output stage is also connected to the dc bus where switching signals, provided from the control circuitry and software, create switching patterns to shape the output voltages and currents to the motor. A cable containing three output phases, a safety earth and enclosed in a wire mesh shield connect the output of the VSD to a motor located at some application specific distance.

Figure 1-1: Block diagram representation of an ac-dc-ac VSD

There are several modulation techniques used to control the switches in the output bridge to achieve sinusoidal outputs with minimal distortion and the maximum possible root mean square (r.m.s.) voltage. For each case, when the required combination of insulated gate bipolar transistors (IGBTs) are switched on, the full dc bus voltage is applied to the terminals of the motor. The inductance of the motor windings causes the current to change at a relatively slow rate. When the desired current level has been achieved, the switches can be turned off. To achieve a high fidelity sinusoidal current waveform, the switching frequency of the IGBTs must be several multiples of the fundamental frequency of the output current. For the Unidrive  $SP^{TM}$ , the switching frequency can be selected from either: 3 kHz, 4 kHz, 6 kHz, 8 kHz or 12 kHz. During the transient switching action (for both on to off and off to on), the IGBTs momentarily support both the full output phase current and simultaneously the full dc bus voltage. Under these conditions, the power loss is very high and the resulting energy is dissipated as heat. When operating at the maximum switching frequency, there are 24000 pulses of energy loss per second for each IGBT and diode in the output bridge contributing up to 60% of the total energy loss of the VSD depending on operating conditions<sup>1</sup>. If the duration of each pulse can be minimised the total energy loss can be greatly reduced.

The switching action of these devices establishes electric and magnetic fields with spectrum extending into radio frequencies. These radio frequencies can interfere with

<sup>&</sup>lt;sup>1</sup> Based on SPMD1404 operating at 6 kHz switching frequency.

components and circuits within the product itself or can be transmitted from the product into the environment causing non-intentional interference with other products. With the increasing use of electronics in an industrial environment for control and monitoring purposes, it is important that products do not interfere with the performance of neighbouring equipment in an unexpected manner. International technical standards have been introduced to define the acceptable level of power supply disturbance and radio frequency emissions which a product can emit, to which other products must be immune [2, 3].

The radio frequency spectrum has been classified into bands for use with communication equipment. The allowable level of unintentional signals are protected by national laws based on technical standards [4] which may be interpreted for specific products and environments. At low frequencies (30 kHz to 300 kHz), medium frequencies (300 kHz to 3 MHz) and high frequency (3 MHz to 30 MHz), the national grid system of power cables can operate as efficient antennas transmitting noise in these frequency ranges into the atmosphere [5]. It is not practical to take measurement of an individual product's emissions broadcast in this manner, however standards provide a test method to determine the voltage disturbance applied to the cables from an individual product. These are referred to as conducted emissions and the limits are defined over a frequency range of 150 kHz to 30 MHz. EMI filters can be designed to contain the common and differential mode currents, in this frequency range, within the VSD system and prevent conduction onto the mains supply. While the filter design is complex requiring a detailed knowledge of material properties of ferrites and capacitors over wide operating ranges, there are known procedures to design such systems at an acceptable cost. Above 30 MHz, (very high frequency (VHF), 30 - 300 MHz, ultra high frequency (UHF) (300 MHz to 3 GHz)) structures within VSD system including cables become efficient antennas and can radiate signals directly into the surrounding environment. Generic standards applicable to a commercial VSD define an acceptable limit to these radiated emissions [4, 6].

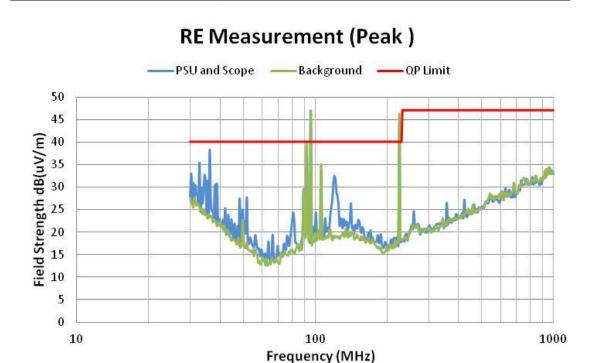

As part of a VSD development process, the product is tested for compliance with the standards to ensure suitability for CE (Conformité Européenne) marking allowing it to be placed for sale on the market in Europe. The VSD is installed in an open area test

site (OATS) in a manner representative of a customer installation with an electromagnetic interference (EMI) filter designed to suppress conducted emissions, communication cables and connections to a motor as described in the VSD installation manual. An antenna is located at a distance of 3 m from the equipment under test (EUT) and connected to a receiver. When the EUT is in its operating mode, the receiver software scans through the required frequency spectrum recording the measured electromagnetic field strength. When the VSD rotates a motor, a significant increase in broadband emissions above background noise can be measured over the range of 30 MHz to 100 MHz.

The current state of art method for reducing the measured emissions is to increase the switching time for the IGBTs by increasing the gate resistance or to add additional filters [7-9]. However, as described above, increasing the switching time results in an increase of power loss, reducing the system efficiency and the addition of filters adds cost and increases the physical size of the system.

It has been identified from work carried out at Control Techniques that different power semiconductor manufacturer's devices can have different levels of radio frequency (RF) emissions for the same switching period. From this observation, it can be deduced that the switching time may not be critical to the production of RF emissions but some less understood phenomenon.

#### 1.2 Objectives of the Work

The main objective of this work is to provide an understanding of the linkages between the operation of power switching devices and the measured radiated emissions. From this understanding, the sources of the radio frequency emissions should be identified in time. The role and influence of the gate drive in generating the radio frequency content should be examined together with research into published gate drive control methods. A method to quantify measured radiated emissions across a wide frequency range is required and a comparison of measured electrical signals to radiated emissions limits defined in international standards is needed. A possible solution to improve the trade off between switching loss and radiated emissions is required which can be extended to

include a method to assess the physical construction of a VSD for its ability to suppress radiated emissions.

#### 1.3 Overview of the Thesis

This thesis consists of seven chapters, the first, giving an introduction to the objectives of the research task and a brief outline of the contributions to knowledge and commercial benefits.

The research presented in chapter two gives background information to enable the reader to understand the problem in depth from several disciplines: power semiconductor physics; radio frequency engineering applied to a VSD system; and frequency analysis techniques for use at radio frequencies. The limitation to the control of radiated emissions in IGBT switching transients is presented.

In chapter three, a review of relevant published literature for gate driving techniques for IGBTs is researched. The merits of these solutions when applied to radiated emissions and variable speed drives is discussed and identifies a lack of specific material in this area.

Chapter four presents the practical application of the theory and determines the limits of common laboratory equipment for both measurement of radio frequency components within relatively high voltage and current switching signals. The impact of VSD construction with regards to its influence on the switching transients and hence radiated emissions is discussed.

Chapter five describes the evaluation of a simplified VSD system to determine the electrical sources responsible for the radio interference. Sophisticated hardware is developed to accurately control features in the switching transient at realistic operational speeds. The features of the switching signal responsible for the radiated emissions are identified and can be used to determine key parameters which can be controlled in a commercial product.

Chapter six describes how methods to measure and control radiated emissions in a simplified system can be applied to a more complex commercial VSD operating in an

industrial environment with the expected fluctuation in supply voltage, load current and temperature. The measurement techniques discussed in preceding chapters are implemented and evaluated to reduce the switch on energy loss while complying with international standards for radiated emissions.

Chapter seven summarises the work presented in this thesis giving conclusions. Further work is discussed regarding application of the techniques presented here to future semiconductor technologies such as wideband gap materials.

#### 1.4 The Contribution to Knowledge

Throughout the research programme undertaken for the degree of Engineering Doctorate, several techniques have been used and discoveries identified which have not been published previously.

#### In this thesis:

- the dominant source of radiated emissions is found to be the RF content within the collector emitter voltage during the IGBT switching transient. In a commercial VSD system, this finding is expanded to include the voltage transient measured between the output phase and ground connection.

- the peak broadband emissions have been identified to occur at four specific points on the voltage waveform. The location of the peak emission changes with load current and VSD construction.

- it is found that the RF content in the IGBT collector current does not contribute to the measured radiated emissions.

- the influence of the bus bar impedance on the IGBT switching trajectory has been identified and the potential opportunities to reduce the switching loss are discussed.

A patent for design of gate drive circuitry has been filed (September 2012):

• "Selectable impedance gate drive."

#### 1.5 Commercial Benefits to Industry

This research project carried out offers commercial benefits to industry by:

• Improving VSD gate drive design which can offer an increase in product efficiency, (a valuable benchmark versus competitors).

- The increase in efficiency will offer a reduction in product size, which will reduce component costs and environmental impact through reduction in transported mass.

- An improved dynamic performance offered by operation of a VSD at a higher switching frequency can improve process control offering further efficiencies in the manufacturing industries.

- A reduction in switching losses can offer a reduction in thermal cycling of IGBTs giving a reduction in thermal fatigue increasing the useful lifetime of VSDs.

- A radiated emissions figure of merit (REFOM) has been found which can be used in a laboratory to understand the radiated emissions sources from a product reducing product development time.

#### **Chapter 2: Key Principles**

#### 2.1 Introduction

This chapter describes the key principles which must be understood when considering the design of a gate drive circuit for low switching loss while considering the requirements for compliance to radiated emissions limits. The three main topics include:

- 1. Power Semiconductor Physics

- 2. Radiated Emission Sources

- 3. Frequency Analysis

The switching operation of an IGBT is far from ideal. The operation of the IGBT is highly dependent on the impedance of the gate drive circuitry, impedance of the power circuit, dc bus voltage, load current and temperature [1, 10-12]. To understand how these parameters effect the device operation, an understanding of the semiconductor physics for both the IGBT and diode is required. Developments in semiconductor technology have resulted in many competing technologies, each of which has benefits within a niche voltage or current rating. Section 2.2 will discuss the characteristics of IGBTs and diodes which are used in state of the art inverters. The theoretical design of the devices is discussed where they effect the electrical characteristics. The characteristics which can be influenced by gate drive circuit design, power circuit design and thermal performance where it relates to electrical characteristics and electromagnetic compatibility (EMC) are presented.

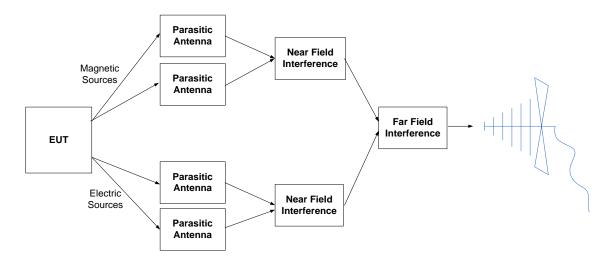

Research into electromagnetic (EM) field radiation has been extensive for many years since first described by Maxwell [13-15]. The majority of the research has focused on the use of EM waves for intentional transmission at specific frequencies where the impedance of cables, power supplies, antennas and the physical dimensions of antennas can be carefully designed to maximise their radiation efficiency [15-17]. The type of radio signals which radiate from a VSD are broadband in content and emanate from multiple sources, voltages and currents, and radiate in all directions [9]. Important information describing the potential radiated emission sources is presented in this chapter.

Radiated emissions are known to arise from the transient switching voltages and currents of the IGBTs [18]. The radio frequency content within these signals occurs for a short duration relative to the switching periods. Many published papers imply that an increase in switching time reduces the EMI emanating from a VSD [19, 20]. Analysis identifying the precise location in time of the radio frequency content and analytical methods to reduce the magnitude over the frequency range of interest is presented. The shape of a switching transient is considered for its radio frequency content.

#### 2.2 Power Semiconductor Physics

The majority of power semiconductor components are constructed from high quality silicon dies. Research has been carried out into the use of alternative materials which offer superior characteristics such as silicon carbide and gallium nitride however at premium prices [21, 22]. This section of the thesis will only consider devices which are currently available and used for mass market industrial VSDs. The devices considered operate over a voltage range 600V to 2kV with a current rating up to 1000A.

#### 2.2.1 Diodes

Diodes used in power electronics can be divided into two categories in terms of their semiconductor physics: the PIN diode and the Schottky diode. The PIN diode uses a pn junction to block reverse bias voltages. When conducting in the forwards direction, the current is carried across the pn junction by minority carriers (holes in the n-type material, electrons in the p-type material). The significance of this for power losses and for fast switching operation will be discussed in section 2.2.1.1. The Schottky diode losses increase with blocking voltage and is not normally used above 600 V when constructed from silicon. Power devices constructed from materials with higher avalanche voltages can utilise the Schottky diode construction up to higher voltages before the conduction losses prohibit this. These will not be discussed in detail in this thesis [21].

#### 2.2.1.1 PIN Diode Structure

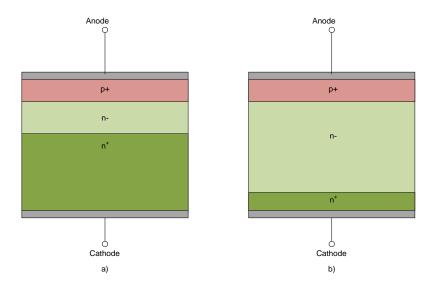

The silicon PIN diode is constructed with three distinct regions of doping. To enable electrical connections to the device, a layer of metal must be deposited on each end to form contacts (see Figure 2-1). The anode is heavily doped with acceptor ions to create

a p region which can create a low ohmic contact with the metal. This is important to reduce power loss when current flows through the device (the high doping concentration is denoted with "+"). For n-type material, the doping needs to be above  $10^{19}$  cm<sup>-3</sup> to achieve a low ohmic contact to the metallisation hence the inclusion of the n<sup>+</sup> region at the cathode [23]. Doping in the middle region of the diode is low (between  $10^{15}$  to  $10^{17}$  cm<sup>-3</sup>) to support a high electric field and is denoted with "-".

Figure 2-1: Structure of PIN diode a) Epitaxial diode; b) Diffused diode

The  $p^+n^-$  junction is responsible for supporting the reverse blocking voltage. The breakdown voltage can be increased by reducing the doping level in the  $n^-$  region (or drift layer). The avalanche breakdown voltage ( $V_a$ ) indicates the point where static avalanche initialises and can be determined from equation (2-1) [24].

$$V_a = 5.34 \times 10^{13} \cdot N_D \tag{2-1}$$

Where  $N_D$  is the doping concentration of donor ions in the n<sup>-</sup> region.

At avalanche, the electrons are accelerated by the electric field with sufficient energy to excite an electron from the valence band into the conduction band generating an electron / hole pair. The new electrons and holes are also accelerated by the electric field causing the process to repeat. The electrons and holes contribute to the leakage current, increasing power dissipation in the diode which can lead to thermal destruction of the device [25].

When the  $p^+n$  junction is in high injection (discussed in section 2.2.1.4), the doping in the low doped  $n^-$  region does not contribute significantly to the charge balance i.e. the processes are the same as if this region is undoped. For this reason it is referred to as intrinsic hence the "i" in PIN.

The PIN diode can be constructed by two different methods depending on the blocking voltage required [26]. For low blocking voltages, the n<sup>-</sup> region only needs to be a few µm thick and so can be grown epitaxially on n<sup>+</sup> substrate followed by a diffusion of acceptor ions to create the p<sup>+</sup> region. As the voltage requirements increase, it becomes more cost effective to begin with a n<sup>-</sup> substrate then diffuse both the p<sup>+</sup> and n<sup>+</sup> region at each end.

#### 2.2.1.2 Static Operation

#### 2.2.1.2.1 Reverse Blocking

The PIN diode operates under reverse bias using the depletion region set up by the pn junction to support high blocking voltages [24]. As the reverse voltage is increased, the depletion width increases. The maximum electric field  $E_{\rm m}$  in an abrupt pn junction is given by equation (2-2).

$$E_{m} = \sqrt{\frac{2qN_{D}V_{a}}{\varepsilon_{c}}} \tag{2-2}$$

where:

- q is the electron charge;

- $\varepsilon_s$  is the permittivity of the semiconductor.

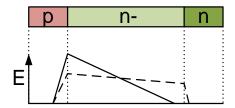

As the applied reverse voltage is increased, the depletion region expands and hence the region supporting the electric field also expands with a triangular characteristic. This is referred to as a Non-Punch Through (NPT) diode and the maximum depletion width (W) for the device occurs at the avalanche voltage which is given by equation (2-3).

$$W = \sqrt{\frac{2\varepsilon_s V_a}{q N_D}} \tag{2-3}$$

If the electric field reaches the n<sup>+</sup> region before falling to zero, it reduces rapidly due to the high doping concentration giving an approximately trapezoidal electric field (see Figure 2-2). This is referred to as a Punch Through diode (PT). This is not strictly the correct terminology as the field does not reach another doping type however the title has generally been accepted [26].

Figure 2-2: Electric field profile for NPT (solid) and PT (dashed)

In a PT device, the electric field strength can be reduced across the n<sup>-</sup> drift region to a level which will not cause avalanche in the n<sup>+</sup> region. The electric field strength can then reduce over a short distance in the n<sup>+</sup> region allowing PT devices to be thinner for a given blocking voltage hence giving a lower forward voltage. However, that can lead to unwanted characteristics such as a snappy behaviour when switching (see section 2.2.1.4.3) [27]. This n<sup>+</sup> layer is often referred to as the buffer layer or field stop layer.

In practice the breakdown voltage at the edge of the component is lower than deep within the silicon. There are various physical methods used to raise this voltage to the one dimensional (1D) theoretical condition. Details of these will not be discussed further however they should be considered when modelling the device behaviour [24].

Datasheet values for reverse blocking capability are often quoted at 25°C. It is important to note that the breakdown voltage reduces by 1.5 V/K as less additional energy is required to excite the electron to the conduction band [24].

#### 2.2.1.2.2 Forward Conduction

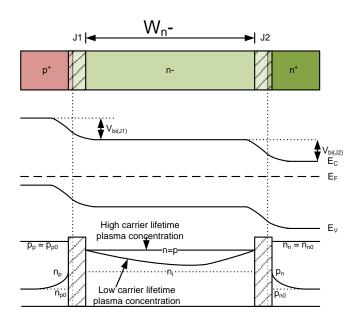

The PIN diode consists of two junctions (J1 and J2) that can be represented in an energy band diagram (Figure 2-3). Under forward bias conditions, holes are injected into the intrinsic region from the p<sup>+</sup> region and electrons are injected into the intrinsic region from the n<sup>+</sup> region. Assuming the junctions are ideal emitters (i.e. only holes cross J1 and only electrons cross J2) the holes and the electrons must recombine in the intrinsic region for current to flow.

Figure 2-3: PIN diode band diagram and plasma concentration

The concentration of the charge carriers (holes and electrons) will exceed the low doping concentration of the drift region giving a quasi neutral mix of charged particles which is referred to as plasma. The voltage drop across the device when forward bias is given by equation (2-4). It can be seen that the voltage drop across the n- region adds to the total forward voltage hence the requirement for a thin drift region, particularly at high voltages.

$$V_{F} = V_{contact} + V_{J1} + V_{J2} + V_{n-}$$

(2-4)

The forward voltage drop across the drift region  $(V_{n-})$  is given in equation (2-5) which shows the dependence on the carrier lifetime  $(\tau)$  and the width of the intrinsic region  $(W_{n-})$  as determined for the required blocking voltage, where  $\tau$  should be large to reduce

$V_{n-}$ . For a short carrier lifetime, the holes and electrons recombine after a short distance giving a catenary distribution.

$$V_{n-} = \frac{3\pi kT}{8q} e^{\frac{W_{n-}}{\sqrt{D\tau}}}$$

(2-5)

where:

- k is Boltzmann's constant

- T is the Temperature

- D is the diffusion constant for silicon

#### 2.2.1.3 PIN Diode Applications

For a VSD output bridge and SMPS applications, the conduction loss is an important factor and hence a high plasma concentration is required to reduce the resistance. However as the switching frequency increases, the switching losses both in the diode and IGBT or metal oxide semiconductor field effect transistor (MOSFET) tend to dominate. For these applications, the designed plasma concentration is a compromise between conduction loss and switching loss [11, 28, 29]. These diodes are often referred to as fast recovery epitaxial diodes (FRED). When switching these devices rapidly, there are other interesting characteristics which must be considered.

In an effort to reduce the plasma concentration, the carrier lifetime can be altered by irradiating a diode with high energy particles, proton and helium implantation or heavy metal diffusion such as platinum or gold [27, 30]. The plasma concentration can be shaped along the length of the diode by controlling the implantation energy to achieve the required depth of diffusion.

#### 2.2.1.4 PIN Diode Switching Characteristics

#### 2.2.1.4.1 Switch On

When the diode begins to switch on, the voltage across it must first increase to the repetitive peak forward voltage ( $V_{FRM}$ ) before falling to  $V_F$  (see Figure 2-4).  $V_{FRM}$  is a function of the rate of change of current (di/dt) and can be greater than 100 times  $V_F$  [26]. This voltage overshoot also adds to the voltage stress on the switching device

(IGBT) which is conducting the full load current during this instant. This voltage stress is in addition to the parasitic inductance voltage drops and can be difficult to measure from a module unless direct probing of the diode contacts can be achieved.

Figure 2-4: Diode switch on waveform.

When the diode becomes forward biased, the forward voltage has to overcome the resistance of the n<sup>-</sup> region while the plasma is forming. This voltage peak becomes more significant on high voltage components as the volume of plasma is larger [26].

#### 2.2.1.4.2 Switch Off

During switch off of the diode, the holes and electrons in the plasma recombine or are swept from both ends by a reverse recovery current ( $I_{rr}$ ). The diode can only begin to support the voltage when the plasma concentration reaches zero at one end of the negion allowing a depletion layer to form. The stored charge in the diode can be considered in two distinct regions which can be observed as the diode switches off. The total charge swept out by the reverse current is commonly referred to as reverse recovery charge ( $Q_{rr}$ ). The diode stored charge ( $Q_{rs}$ ) or excess plasma must be removed to the point where the depletion layer just forms. The charge that continues to be swept out of the diode to allow the depletion layer to expand is referred to as the diode depletion charge ( $Q_{rf}$ ) [11]. The rate of change of voltage (dV/dt) of the diode is determined by the concentration profile of  $Q_{rf}$  throughout the near region, the rate of recombination, and the rate at which the charge carriers are swept out by load current.

In Semikron publications [26, 27], reference is made to a softness factor to characterise the reverse recovery current of a diode (see Figure 2-5 and equation ( **2-6** )), however values for this softness factor are not published in their data sheets. This could be a

useful figure however, it would have to include a plot of softness factor versus di/dt and given for a range of temperatures and load currents for a circuit designer to be able to apply to new designs.

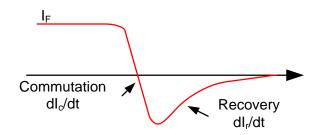

Figure 2-5: Soft Recovery PIN diode (softness factor S)

$$S = \frac{\left| -\frac{dI_c}{dt} | I = 0 \right|}{\left( \frac{dI_r}{dt} \right) \max}$$

(2-6)

A diode is considered to be a hard recovery diode if the rate of change of commutation current ( $dI_c/dt$ ) is less than half of the rate of change in recovery current ( $dI_r/dt$ ) otherwise it is referred to as a soft recovery diode. For a given stored charge the peak reverse recovery current ( $I_{rr}$ ) is proportional to di/dt.

#### 2.2.1.4.3 Snap-Off

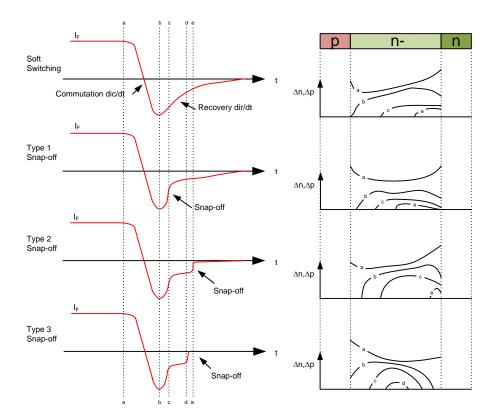

During switch off, it is possible to have very fast current transients during the reverse recovery period. This will depend on operating conditions and diode characteristics. The high current transients have been blamed for increasing electromagnetic emissions and so diodes should be designed to avoid operating in this area [31, 32]. This very fast recovery is referred to as snap-off and can result from three different conditions within the diode. The plasma and associated waveforms are illustrated in Figure 2-6.

There are three different positions in the recovery tail where snap-off can occur leading to a different characteristic waveform [11, 27]:

• **Type 1:** A shallow plasma in the middle of the n<sup>-</sup> region can give a snap-off soon after the peak reverse recovery current.

• **Type 2:** An insufficient thickness of the diode n<sup>-</sup> region may result in snap-off towards the end of the switch off period.

• **Type 3:** An excessively strong anode emitter and/or weak cathode emitter may lead to snap-off in the middle phase of the switch off process.

Figure 2-6: PIN diode plasma concentration during snap-off for different types of diodes

There are various operating condition which can increase the chance of snap-off [11]:

- The carrier lifetime hence plasma concentration is a function of temperature. At low temperature, the carrier lifetime is shorter hence the diode can become more snappy. This condition would typically be observed as type 1.

- At a low forward current, the plasma concentration is low resulting in snappy behaviour (type 2).

- At high dc bus voltage, the diode appears thinner because the depletion layer expands much faster increasing the risk of snap-off in the tail (type 3).

High di/dt extracts the excess charge rapidly. An initially low plasma concentration in the middle region will result in a snap off after the current peak (type 1).

#### 2.2.2 IGBT

The IGBT combines the high current and voltage capability of the bipolar junction transistor (BJT) with the high input impedance of the MOSFET in a single device. It has been assumed that a PIN diode has been used in the switching waveforms presented in this chapter unless otherwise stated.

#### 2.2.2.1 Device Structure

The structure of an IGBT can be split into two different regions, the gate region and the high power region. For the following description of the device structure and operation, the planar gate structure, Non-Punch Through technology is used. This is extended in section 2.2.2.2 to include specific features which are used to customise the device depending on the application.

The structure of the IGBT is shown in Figure 2-7. Areas which have characteristics similar to simpler devices have been indicated as these will aid the description of device operation. The n-channel MOSFET has been identified as the small area under the emitter contact and the polysilicon / oxide gate. The n region under the emitter is highly doped to give a good ohmic contact to the emitter terminal. This forms the source of the MOSFET. The surrounding p region, referred to as the p-base, is usually the substrate or body in a MOSFET device. The p-base region is also connected to the emitter terminal allowing the gate voltage to be referenced to the emitter creating a MOS junction. The application of a positive voltage to the polysilicon gate, relative to the p-base attracts electrons towards the gate which collect below the insulating oxide layer. When the concentration of free electrons in a very thin layer under the gate, is greater than the p-base doping concentration, this is called an inversion layer or channel.

The n<sup>-</sup> drift region forms the drain of the MOSFET. When the drain is positively biased relative to the source and the inversion layer has formed, a current of majority carriers (electrons) will flow along the channel into the drain.

emitter n-channel MOSFET Oxide laver Polysilicon JFET region due to depletion region from p-base J2 Parasitic thyristor pnp bipolar transisto J1 р collector

Figure 2-7: Planar gate, Non-Punch Through IGBT structure

The pnp transistor consists of the p layer at the IGBT collector, n drift layer and p-base layer connected to the IGBT emitter. From the semiconductor point of view, the terminals of this device have been labelled incorrectly. The emitter of the pnp transistor is actually the labelled as the collector of the IGBT and likewise for the pnp collector [11].

The JFET (junction field effect transistor) region is formed by adjacent cells in the drift region. The depletion layer around the p-base acts to pinch off the current flowing from the channel and increases the IGBT resistance. This effect increases as the cell density increases [11].

The npnp structure is often referred to as a parasitic thyristor. The thyristor is normally in its blocking condition and hence does not influence the device performance. The p-base region of the IGBT forms part of the gate which is shorted to its cathode via the IGBT emitter terminal and remains off. Under conditions with high current densities or fast transients, a voltage drop across the p region can occur causing the thyristor to latch on. The thyristor will remain in the conducting state until the voltage across the IGBT is reversed. In most hard switched IGBT applications, this voltage across the device will not be reversed hence the latched IGBT leads to thermal runaway and device destruction.

Unlike a MOSFET, there is no reverse conducting path through an IGBT due to the p layer at the collector. A separate freewheeling diode is always used in parallel to the IGBT for this purpose.

The IGBT structure as shown in Figure 2-7 is a single unit cell. This pattern is repeated many times throughout a single chip. The number of unit cells hence area of the chip is determined by the required current. The thickness of the device determines the blocking voltage in a similar manner to the PIN diode.

The planar gate structure is often referred to as a DIGBT. This is in reference to the construction techniques of double diffusing first the p-base followed by the n+ region to form the gate structure [33].

#### 2.2.2.2 Evolution of Device Structure

As IGBT technology and manufacturing capabilities have progressed, there have been several distinct changes to the device structures. This section will discuss these improvements, associated electrical characteristics and applications.

Competition between manufacturers has led to a proliferation of marketing terms to describe variants of IGBT structure [34]. The various names will be mentioned throughout this section.

#### Non-Punch-Through