# Fault Injection Testing of Software Implemented Fault Tolerance Mechanisms of Distributed Systems

Sha Tao

Ph.D. Thesis

October 1996

**University of Newcastle upon Tyne Department of Computing Science**

NEWCASTLE UNIVERSITY LIBRARY

096 51028 9

Thesis L5770

#### Abstract

One way of gaining confidence in the adequacy of fault tolerance mechanisms of a system is to test the system by injecting faults and see how the system performs under faulty conditions. This thesis investigates the issues of testing software-implemented fault tolerance mechanisms of distributed systems through fault injection.

A fault injection method has been developed. The method requires that the target software system be structured as a collection of objects interacting via messages. This enables easy insertion of fault injection objects into the target system to emulate incorrect behaviour of faulty processors by manipulating messages. This approach allows one to inject specific classes of faults while not requiring any significant changes to the target system. The method differs from the previous work in that it exploits an object oriented approach of software implementation to support the injection of specific classes of faults at the system level.

The proposed fault injection method has been applied to test software-implemented reliable node systems: a TMR (triple modular redundant) node and a fail-silent node. The nodes have integrated fault tolerance mechanisms and are expected to exhibit certain behaviour in the presence of a failure. The thesis describes how various such mechanisms (for example, clock synchronisation protocol, and atomic broadcast protocol) were tested. The testing revealed flaws in implementation that had not been discovered before, thereby demonstrating the usefulness of the method. Application of the approach to other distributed systems is also described in the thesis.

# Acknowledgements

First and foremost, I would like to thank my supervisor Professor Santosh Shrivastava for his constant support and constructive advice. I am grateful to Professor Shrivastava for his comments and criticisms on the preliminary drafts of the work.

I would also like to thank my colleagues Dr Paul Ezhilchelvan, Dr Neil Speirs, and Dr Francisco Brasileiro for the many fruitful discussions I had with them during the course of the work.

The support and encouragement offered by my family during my studies are also greatly acknowledged.

The work reported in this thesis was financially supported by grants from the CEC ESPRIT programme and the UK Engineering and Physical Sciences Research Council (EPSRC).

# **Table of Contents**

| Chapter 1 | Introduction                                                | 1  |

|-----------|-------------------------------------------------------------|----|

|           |                                                             |    |

| Chapter 2 | Fault Injection Techniques and Software Testing             | 5  |

| 2.1. Int  | roduction                                                   | 5  |

| 2.2. Sin  | nulated Fault Injection                                     | 7  |

| 2.3. Ha   | rdware-Implemented Fault Injection                          | 11 |

| 2.3.1     | 1. Pin Level Fault Injection                                | 11 |

| 2.3.2     | 2. Heavy-ion Radiation Injection                            | 15 |

| 2.3.3     | 3. Other Techniques of Hardware-Implemented Fault Injection | 17 |

| 2.4. So   | ftware-Implemented Fault Injection                          | 17 |

| 2.4.1     | 1. FIAT Fault Injection Tool                                | 18 |

| 2.4.2     | 2. FERRARI Fault Injection Tool                             | 20 |

| 2.4.3     | 3. SFI Fault Injection Tool                                 | 22 |

| 2.4.4     | 4. FINE Fault Injection Tool                                | 23 |

| 2.4.5     | 5. Simulation-Assisted Fault Injection                      | 26 |

| 2.4.6     | 6. Other Work on Software-Implemented Fault Injection       | 27 |

| 2.5. Fai  | ult Injection for Fault Removal                             | 28 |

| 2.5.1     | 1. Testing of Distributed Fault Tolerant Algorithms         | 28 |

| 2.5.2     | 2. Fault Tolerance Testing of AAS                           | 30 |

| 2.6. Ov   | verview of Software Testing Techniques                      | 33 |

| 2.6.      | 1. Structural Testing                                       | 33 |

| 2.6.2     | 2. Functional Testing                                       | 34 |

| 2.6.3. Random Testing                                            | 35 |

|------------------------------------------------------------------|----|

| 2.6.4. Equivalence Partitioning Testing                          | 35 |

| 2.6.5. Cause-effect Testing                                      | 36 |

| 2.6.6. Mutation Testing                                          | 38 |

| 2.6.7. Assertion Testing                                         | 39 |

| 2.6.8. Comments                                                  | 40 |

| 2.7. Fault Tolerance Testing Strategies                          | 41 |

| 2.7.1. Structural Testing                                        | 42 |

| 2.7.2. Functional Testing                                        | 44 |

| 2.8. Summary                                                     | 46 |

|                                                                  |    |

| Chapter 3 Focused Fault Injection Method                         | 50 |

| 3.1. Introduction                                                | 50 |

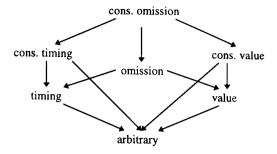

| 3.2. Modelling Faulty Behaviour                                  | 51 |

| 3.2.1. Simple Responses                                          | 52 |

| 3.2.2. Replicated Responses                                      | 53 |

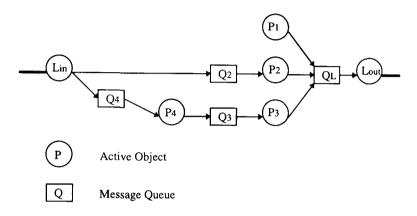

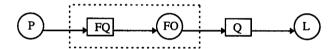

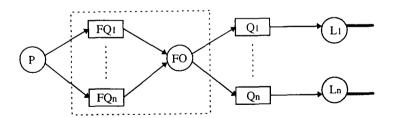

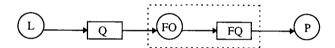

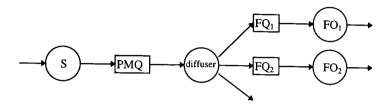

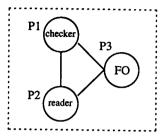

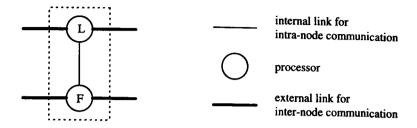

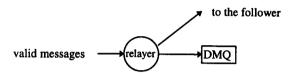

| 3.3. Software Structure Permitting Focused Fault Injection       | 55 |

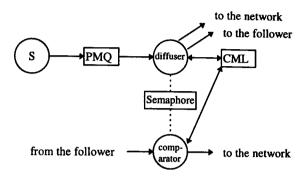

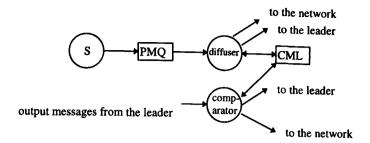

| 3.4. Injection of Replicated Responses                           | 59 |

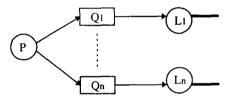

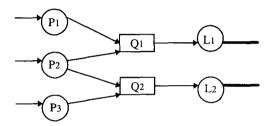

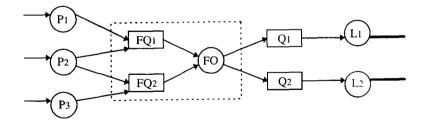

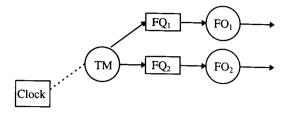

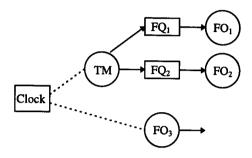

| 3.5. Injection of Multiple Processes                             | 61 |

| 3.6. Injection of Multiple Processors                            | 63 |

| 3.7. Ordering Arrivals of Erroneous Messages                     | 67 |

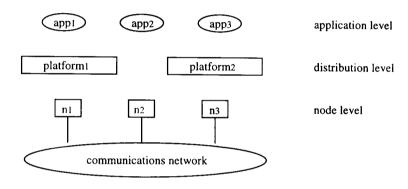

| 3.8. Software-Implemented Fault Tolerance in Distributed Systems | 70 |

| 3.8.1. Node Level Fault Tolerance                                | 70 |

| 3.8.2. Distribution Level Fault Tolerance                        | 71 |

| 3.8.3. Application Level Fault Tolerance                         | 72 |

| 3.9. Summary                                                     | 73 |

| Chapter 4 Focused Fault Injection on Voltan TMR Node    | 75  |

|---------------------------------------------------------|-----|

| 4.1. Introduction                                       | 75  |

| 4.2. Voltan TMR Node Architecture                       | 76  |

| 4.2.1. System Model and Assumptions                     | 77  |

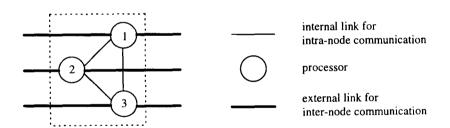

| 4.2.2. Node Software Architecture                       | 79  |

| 4.3. Implementation                                     | 81  |

| 4.3.1. Voting Module                                    | 83  |

| 4.3.2. Clock Synchronisation Module                     | 84  |

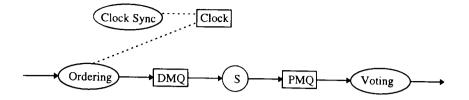

| 4.3.2.1. The Protocol                                   | 84  |

| 4.3.2.2. The Implementation                             | 89  |

| 4.3.3. Ordering Module                                  | 90  |

| 4.3.3.1. The Protocol                                   | 91  |

| 4.3.3.2. The Implementation                             | 95  |

| 4.3.4. Communications Layer                             | 96  |

| 4.4. Fault Injection Implementation                     | 97  |

| 4.5. Experiments and Results                            |     |

| 4.5.1. Voting Module                                    | 101 |

| 4.5.2. Clock Synchronisation Module                     | 105 |

| 4.5.3. Ordering Module                                  | 111 |

| 4.5.4. Comments                                         | 115 |

| 4.6. Summary                                            | 115 |

|                                                         |     |

| Chapter 5 Focused Fault Injection on A Fail-Silent Node | 117 |

| 5.1. Introduction                                       |     |

| 5.2. Fail-Silent Node Architecture                      |     |

| 5.2.1. System Model and Assumptions                                          | 119         |  |

|------------------------------------------------------------------------------|-------------|--|

| 5.2.2. Basic Node Architecture                                               | 120         |  |

| 5.2.3. Node Failure Semantics                                                | 121         |  |

| 5.2.4. The Symmetric Node Design                                             | 123         |  |

| 5.2.5. The Leader-Follower Node Design                                       | 125         |  |

| 5.3. Leader-Follower Node Implementation                                     | 128         |  |

| 5.3.1. Communications Layer                                                  | 130         |  |

| 5.3.2. Ordering Modules                                                      | 131         |  |

| 5.3.3. Comparison Modules                                                    | 133         |  |

| 5.4. Implementing Focused Fault Injection                                    | 13 <b>5</b> |  |

| 5.5. Experiments and Results                                                 | 137         |  |

| 5.5.1. Experimental Set-Up                                                   | 138         |  |

| 5.5.2. Comparison Module of Follower                                         | 140         |  |

| 5.5.3. Comparison Module of Leader                                           | 141         |  |

| 5.5.4. Time-Monitoring Mechanism of Follower                                 | 142         |  |

| 5.6. Summary                                                                 |             |  |

|                                                                              |             |  |

| Chapter 6 Applying Focused Fault Injection at Higher Levels of a Distributed |             |  |

| System                                                                       | 144         |  |

| 6.1. Introduction                                                            |             |  |

| 6.2. Distribution Level Fault Tolerance                                      | 146         |  |

| 6.2.1. Focused Fault Injection Scheme                                        | 146         |  |

| 6.2.2. The ISIS Example                                                      | 149         |  |

| 6.3. Application Level Fault Tolerance                                       |             |  |

| 6.3.1. The Manetho Example                                                   | 154         |  |

| 6.4 Summary                                                                  |             |  |

| Chapter 7 Conclusions          | 157 |

|--------------------------------|-----|

| 7.1. Contributions             | 157 |

| 7.2. Future Directions         | 159 |

| 7.2.1. Limitations of the Work | 159 |

| 7.2.2. Further Work            | 160 |

|                                |     |

| References                     | 163 |

# **Chapter 1: Introduction**

Very high reliability is required from computing systems that are used in life- and mission-critical applications. Enormous effort is put into the design and implementation of such systems. Various types of fault tolerance mechanisms are employed to achieve that required level of system reliability. A major problem related to the development of fault tolerant computing systems is their validation.

Fault tolerant systems must handle an 'extra class' of inputs, i.e., failure events, which they are designed to cope with. For systems intended for critical applications, failure probabilities in the range of 10<sup>-6</sup> to 10<sup>-10</sup> per hour are often specified [Wensl78]. It is simply not possible to take the conventional approach of running a system for long periods (so failure events do occur) to collect failure data for evaluating the reliability properties of a system. Other ways of system validation must be employed to examine the behaviour of the system in the presence of failures.

Fault injection based testing is recognised as an effective means of validating reliability properties of systems. It has been used to examine reliability mechanisms, such as error detection mechanisms, error recovery schemes, and other aspects of fault tolerance. Fault injection can also be used to study the behaviour of large systems under faulty conditions. Over the years, various fault injection tools and methods have been developed and implemented in both hardware and software.

Fault injection is the general term used to describe a wide range of activities which create the effects of fault occurrences. Especially, 'software-implemented fault injection' actually refers to software based approaches to the injection of errors (manifestations of faults).

This thesis describes a fault injection method that we have developed for testing software-implemented fault tolerance mechanisms of distributed systems. The method differs from the previous work in that it exploits an object oriented approach of software implementation to support the injection of specific classes of faults at the system level. The method requires that the target software system be structured as a collection of objects interacting via messages so that fault injection objects can be easily inserted into the target system to emulate incorrect behaviour of faulty processors by manipulating messages. This approach allows one to inject specific classes of faults without requiring any significant changes to the target system. The method has been applied to test the implementation of redundancy management protocols of a TMR (triple modular redundant) node and a fail-silent node.

The need for the injection of specific classes of faults at the system level is exemplified by the so called 'Byzantine Generals problem'. The problem refers to a situation in which a failed processor of a system exhibits 'two-faced' behaviour, telling one processor one thing and another processor a different thing, thereby 'confusing' the correct processors of the system. It is therefore necessary that the correct processors execute an 'agreement' protocol to prevent any disagreement about the disseminated information. Such Byzantine agreement protocols do exist. These protocols have been validated by formal correctness proofs. However, faults can still be introduced at the

implementation stage. Testing-based validation of the implementation is therefore required. Effective testing of software modules implementing these protocols can only be achieved by the injection of specific types of faults that can create required failure scenarios, such as 'two-faced' Generals. We show in chapter 3 how such software modules can be effectively tested using the method presented in the thesis.

The rest of the thesis is organised as follows.

Chapter 2 gives a survey of the existing work on fault injection. Various fault injection tools and methods and their applications are analysed. Their merits and shortcomings are discussed. A brief discussion on software testing techniques in general is also presented.

In chapter 3, we present our fault injection method. We first describe a fault model for distributed systems. Then we discuss in detail how the target software should be structured to support fault injection and how various failure scenarios can be created through fault injection. In this chapter we also discuss the various levels at which fault tolerance can be provided in a distributed system.

Chapter 4 describes the fault injection experiments conducted to test the soundness of the design and implementation of Voltan TMR node. The Voltan TMR node is implemented entirely in software using standard transputer hardware. A TMR node consists of three processors and is capable of masking the failure of a single processor through replicated processing. The key to the correct functioning of a TMR node is redundancy management. In a software-implemented TMR node, this is provided by the

implementation of redundancy management protocols which forms the 'hard-core' of system software of a node. The 'hard-core' must function correctly in the presence of a single failure for the node to be correct. We tested the 'hard-core' consisting of the voting, clock synchronisation and ordering modules of the Voltan TMR node software.

Our fault injection method has also been applied to test the fault tolerance mechanisms of a software-implemented fail-silent node. Unlike a TMR node which is designed to mask the failure of a single processor and continue to provide a required service, a fail-silent node is only required to exhibit certain fail-silence properties in the presence of a single processor failure. In chapter 5 we describe the fault injection experiments performed on a fail-silent node.

In chapter 6 we discuss the application of our fault injection method to distributed systems where fault tolerance is provided at distribution level or application level. In such systems, message exchanges among the processors of the system are often based upon the use of a set of primitives provided by the underlying communication layer. The target system modules have direct access to the primitives for sending and receiving messages, rather than make use of link handling objects as suggested in chapter 3. It is not possible to insert an injection object to intercept and manipulate output messages. In chapter 6 we describe how our fault injection method can be adapted to be used in the testing of such systems. Thus we show that our approach can be used to test a wide class of distributed computing systems.

Chapter 7 concludes the thesis. Limitations of our work are discussed and plans for future work are outlined.

# Chapter 2: Fault Injection Techniques and Software Testing

#### 2.1. Introduction

For systems intended for critical applications, failure probabilities in the range of 10<sup>-6</sup> to 10<sup>-10</sup> per hour [Wensl78] and system down times in the range of 3 to 156 seconds per year [Crist90] are often specified. It is simply not feasible to take the conventional approach of running a system for long periods (so failure events do occur) to collect failure data for evaluating the reliability properties of such systems. A more direct means of feeding the target system with a special category of inputs, i.e. failure events, through fault injection, is therefore required. Fault injection based experiments have increasingly been recognised as a very useful way of validating system reliability. Fault injection can be employed for two different objectives with regard to system reliability validation: fault forecasting and fault removal [Arlat91, Lapri92].

Fault forecasting is not about forecasting the occurrence of faults. It is about the impact of faults on the target system, that is, forecasting the *consequences of faults*. Fault forecasting handles issues such as the likelihood of a fault being detected, how long it takes to detect a fault, and how the target system would behave under the influence of faults, etc. Fault injection has been widely used to examine coverage and detection latency of various error detection mechanisms, and to study system behaviour under

faulty conditions.

Within the context of fault tolerant systems, fault removal deals with the uncovering of flaws and deficiencies in the design and implementation of fault tolerance mechanisms, to make sure that fault tolerance mechanisms do cope with the faults which they are designed to handle. In other words, fault removal is concerned with the removal of fault tolerance deficiency faults. In this sense, the process of fault tolerance testing for the objective of fault removal is similar to that of conventional software testing, only that the inputs are of a special category (faults).

The fault injection techniques and methods used in fault injection experiments for the two different objectives are quite different. In the experiments for fault forecasting, the essential requirement is to emulate the occurrence of faults in the real world as closely as possible. The techniques are usually geared towards supporting fault injection of random nature at low levels. While in the experiments for fault removal, the requirement is to be able to inject specific classes of faults so that the fault tolerance mechanisms under test can be checked adequately. Such experiments allow testers to find out whether the fault tolerance mechanisms can indeed tolerate the faults which they are supposed to tolerate.

There is a wide range of techniques which are used to implement fault injection for the purpose of fault forecasting at various stages of the development process of reliable systems. These techniques can be classified into three categories: simulated fault injection, hardware-implemented fault injection, and software-implemented fault injection. Simulated fault injection is typically employed at the design stage, so

that different architectural design ideas can be tested and evaluated, and potential reliability deficiencies can be identified. Hardware- and software-implemented fault injection approaches are suitable for prototype testing and evaluation; these direct approaches avoid the task of constructing complex simulation models. In sections 2.2 - 2.4 we will discuss and analyse the three categories of fault injection techniques.

In section 2.5 we will discuss some existing work on fault injection with the objective of fault removal. Such work is similar in nature to software testing, that is the aim is to test that a system does what it is expected to do. Section 2.6 gives an overview of software testing techniques in general. Section 2.7 presents a brief discussion on the issue of testing strategies that are used in fault tolerance testing. Section 2.8 summarises the chapter.

## 2.2. Simulated Fault Injection

Simulated fault injection is carried out by injecting faults into the simulation model of the target system under study. It constitutes an important means for performance and reliability evaluation [Iyer93]. Such evaluation is highly useful in comparing alternative design ideas and analysing reliability characteristics. Another obvious advantage of simulated fault injection over hardware/software-implemented fault injection is that there is no restriction in accessing internal parts of components of a processor, and very low level faults can be simulated (see below). Simulated fault injection has been used in evaluating fault tolerant processor architectures during the design stage.

Various levels of system abstraction can be considered for simulated fault injection. In

practice, three levels of abstraction are often used for injection based analysis. They are: transistor level, gate level, and function level.

A wide range of research work has been carried out concerning simulated fault injection at all three levels of system abstraction. Some of them deal mainly with simulation tools, while others concentrate on studying reliability characteristics of some specific systems.

Transistor level faults are simulated by changing the electric voltage and current inside a circuit, which is in fact a form of circuit simulation. FOCUS [Choi92] is a transistor level simulation tool, it adopts a *mixed-mode* approach of simulation. The non-faulty parts of the circuit are simulated at the logical level while the injected parts are simulated at the electrical (analogical) level. Logical level simulation of the non-faulty parts helps reduce the complexity of the simulation model while electrical level simulation of the faulty parts enables a more realistic emulation of real world faults.

FOCUS has been used to study error propagation within a microprocessor [Choi92]. In the study, a total of 2100 simulations was performed to obtain stable results. The study found: 71.9% of the faults injected never caused an error (a faulty signal has to be 'latched' to become an error); 16.4% of the faults injected caused errors that propagated to a pin of an IC chip; and 9.2% of the faults injected caused errors that propagated to the functional output of the microprocessor.

Gate level fault simulation adopts fault models at a higher level of system abstraction. It simulates logical faults, such as stuck-at-0, stuck-at-1, or inverted logic value faults. A

number of studies have used gate level fault simulation to analyse error propagation in IC chips and to characterise the impact of gate level faults on program behaviour. Lomelino [Lomel86] investigated error propagation from the gate level to the pin level. Czeck and Siewiorek [Czeck90] injected faults in a gate level simulation model of the IBM RT PC to investigate the impact of transient gate level faults on program behaviour.

Simulated fault injection can also be carried out at function level to study the reliability of complete computer systems or even distributed systems. In such simulations, components of the system of either hardware (e.g. cpu, memory) or software (e.g. workload) are modelled and their interaction considered.

DEPEND [Goswa90] is a typical example of a function level fault simulation environment. It takes an object oriented approach and provides a collection of objects representing hardware and software components of systems. Users can use these objects to build simulation models rapidly. DEPEND has been used to simulate the UNIX-based Tandem Integrity S2, a TMR node system [Jewet91]. Faults were injected into the simulation model of the system to evaluate the impact on the system MTBF (mean time between failure) by correlated errors, latent errors, memory scrubbing, and repair times [Goswa91]. The results show that correlated errors (i.e., errors affecting two or three processors) with no latency cause enormous degradation to the system MTBF. However, errors typically have latencies and when error latency is taken into account the reduction in the MTBF is not as pronounced. The results also show that there is no relationship between the size of error latency and the system MTBF. For systems designed to tolerate

single faults, repair time is a window of vulnerability. The study shows that reduced repair time improves the system MTBF as long as there are no correlated errors. Memory scrubbing, which is used to detect and remove memory errors, is found to be extremely effective at eliminating errors with large latencies.

Jenn et al [Jenn94, Rimen93] reported work on a simulated fault injection tool (MEFISTO) based on a widely used hardware description language (VHDL). The work differs from previous research work in this area in two aspects. Firstly, MEFISTO is based on VHDL [IEEE88], an existing hardware description language with a wide spectrum of applications. Target system simulation models written in VHDL can be injected directly. This removes the burden of having to learn a new simulation language and construct a simulation model in this language. Secondly, MEFISTO allows fault injection at multiple levels of abstraction. This feature is supported by VHDL's ability to describe both structure and behaviour of a target system. MEFISTO has been used to fault inject a processor. The main objective of the experiment is to analyse the impact of the choice of the injection method and the model description level on the error outcome.

Another example of function level fault simulation tool is React [Clark95]. React is specifically designed to assess reliability properties of multi-processor architectures. It can be used to study different fault tolerant architectures such as, N modular redundancy, duplication and comparison, and standby sparing.

Some of the network simulation tools, such as NEST [Dupuy90], which were not originally developed for fault simulation, can also be used to simulate node and link

failures to model faults in distributed systems.

## 2.3. Hardware-Implemented Fault Injection

Hardware-implemented fault injection is also known as physical fault injection and involves the physical introduction of faults into the target system either by applying voltage levels to the pins of IC chips, radiating IC chips with heavy ion, or some other forms of physical interference. Pin level fault injection changes the external behaviour of an IC chip by having some of its pins stuck-at-1, stuck-at-0, or inverted. Heavy ion radiation allows faults to be injected inside a chip and so changes the external behaviour of the chip in an indirect way. The behaviour of IC chips can also be modified through power disturbance or electro-magnetic interference.

## 2.3.1. Pin Level Fault Injection

Pin level fault injection is the most widely used hardware fault injection method. It is especially useful in evaluating error detection mechanisms for detection latency and coverage. There are two different techniques used for implementing pin level fault injection, known as *forcing* and *insertion* respectively.

With the forcing technique, probes are attached to the IC pins (injection points) directly. The current/voltage levels of the injected pins can then be altered to emulate erroneous logic values. Using the forcing technique, the fault types allowed are limited to stuck-at-0 and stuck-at-1.

The insertion technique requires some physical modification of the target

hardware. The selected IC chip is extracted from the circuit board and an extra piece of hardware, called *socket*, is then inserted between the IC chip and the circuit board. Through the socket, logic values of the pins can be manipulated. Apart from the stuckat-0 and stuck-at-1 fault types, more complex fault types, such as inverted faults where logic values are inverted (0 to 1, or 1 to 0) and open faults where pins are 'open' (disconnected), can also be injected. Most pin level fault injection tools use insertion technique.

For an early example of pin level fault injection method, see the papers by Decouty and Crouzet [Decou80, Crouz82]. The aim was to evaluate the coverage of error detection mechanisms attached to various modules of a self-checking microcomputer [Morei76]. Faults were injected into the target microcomputer and results were monitored through the use of a purpose-built tool. The tool consisted of a fault injector and a hardware monitor. The hardware monitor observed whether the errors caused by the injected faults were detected by the error detection mechanisms and whether erroneous outputs were emitted by the microcomputer. The study found error detection rates to be very high: 96% CPU errors, 99% ROM errors, and 99% RAM errors were detected. Another significant observation of the experiments was that no erroneous outputs were emitted by the microcomputer. In other words, either the microcomputer was stopped when an error was detected or the error didn't result in the microcomputer emitting erroneous outputs.

The fault recovery mechanism of the FTMP computer [Hopki78] was evaluated using pin level fault injection [Finel87]. The main objective was to collect data on fault

recovery times and establish their statistical distribution. This information is of vital importance for reliability estimation of the FTMP. The fault injection set-up has a hardware fault injector, interface hardware, and support software. Experiments were controlled from a host computer on which the support software was run. Fault injection instructions were issued from the host computer to the injector; the results were read by the FTMP itself and sent back to the host computer through the hardware interface. The results of the experiments were very interesting. While no single distribution of fault recovery times was shown to be the best fit for all the data sets, the exponential distribution, which is often assumed in reliability modelling, was a bad fit for all data sets.

The MESSALINE fault injection tool [Arlat89, Arlat90a, Arlat90b] developed at LAAS has been used to test both centralised and distributed target systems with reliability mechanisms through pin level fault injection. In the case of the centralised target system [Arlat90a], the target system was a subsystem of a computerised interlocking system for railway control applications. The mechanisms examined were a self-test program and the hardware error detection mechanism of the system. Stuck-at-1, stuck-at-0, and open faults were injected. The experiments showed that the test program was far more efficient in detecting errors than the hardware error detection mechanism.

In the second exercise [Arlat90a], the Multicast Communication System (MCS) of Delta-4 distributed system [Powel91] was examined. The MCS provides multicast services that are built using an atomic multicast protocol (AMP). The MCS is implemented within Network Attachment Controllers (NACs) which connect the host

machines of a distributed fault tolerant system to a local area network. The NACs have self-checking capabilities and are assumed to be fail-silent (i.e., they fail by stopping and becoming silent). Fault tolerance of the MCS depends on two levels of coverage: local coverage, provided the self-checking capabilities of the NACs, and distributed coverage provided by the defensive properties of the AMP. The defensive properties of the AMP refer to its ability to provide continued fault tolerance in the event that the fail-silence property of NACs is broken and erroneous messages are sent by NACs. The experimental results showed that 67.47% of the errors caused by injected faults were detected and the NAC was subsequently extracted from the network (become silent). The results also showed that 23.79% of the errors, though not detected, did not result in any erroneous behaviour of the MCS. This was due to the distributed fault tolerance coverage provided by the AMP. Thus, in 91.26% of the injections, the MCS was able to handle the error correctly.

In a more recent study, Madeira and Silva [Madei94] investigated the effectiveness of error detection mechanisms in guaranteeing fail-silent behaviour by using pin level fault injection. Two target computers, one Z80 based and the other 68000 based, were evaluated. A number of error detection mechanisms were tested in the contexts of the two computers. These error detection mechanisms check program control flow, memory access behaviour, and illegal instructions. The results showed that by using a combination of such error detection mechanisms, very high error detection rates could be achieved. The Z80 based computer achieved a combined error detection rate of 97.8%; while the 68000 based computer achieved 90.4%. As expected, not all undetected errors would cause a violation of fail-silence. The actual fail-silence

coverages achieved were higher than the error detection rates. The Z80 based computer achieved a fail-silence coverage of 99.6%; while the 68000 based computer achieved 98.1%.

Fault injection experiments were also conducted on the Z80 and 68000 based computers without any added error detection mechanism. The results were not surprising. 16.7% of errors caused by injected faults resulted in a fail-silence violation in the 68000 based computer; while 45.6% of such errors resulted in a fail-silence violation in the Z80 based computer.

Other examples of pin level fault injection include [Shin86] for measuring error detection latency and [Schue86] for rating the coverage of error detection mechanisms.

## 2.3.2. Heavy-ion Radiation Injection

Heavy-ion radiation of IC chips [Gunne89, Mirem92] allows faults to be injected within IC chips which is not possible with pin level fault injection. Another difference between pin level injection and heavy-ion radiation injection concerns the certainty of fault injection. With pin level fault injection, one has control over the faults being injected with regard to the types of faults and the location of injection. However, when a IC chip is radiated with heavy-ion, there is no such certainty of control. As a result, heavy-ion radiation based fault injection experiments are conducted in ways different from those of pin level fault injection. An experimental set-up consisting of two CPUs is normally required; one is subject to fault injection and the other acts as a reference. The two CPUs operate in synchrony using the same main clock and are connected to a

comparator. When a fault which actually causes an error is injected, it will be detected by the comparator and the output signals of both CPUs are recorded.

Heavy-ion radiation testing was used when a MC6809E microprocessor was fault injected to generate error data [Gunne89]. The error data were later used as input of programs which simulated error detection schemes suitable for a watchdog processor. A watchdog processor is a small processor that checks the behaviour of the main processor on the external bus [Mahmo88]. Each error detection scheme consisted of a number of individual error detection mechanisms for checking program control flow, memory access behaviour, and illegal instructions. All error detection mechanisms were individually evaluated and then a number of combinations (schemes) were also evaluated. The results showed that, while the individual error detection mechanisms typically have detection rates at around 25% - 60%, the error detection schemes have much higher coverage. The best scheme detected 79% of errors and 99% of the errors that caused execution to diverge were detected by the scheme.

Heavy-ion radiation has also been used to examine two software error detection techniques directly [Mirem92]. These two error detection techniques are known as Block Signature Self-Checking (BSSC) and Error Capturing Instructions (ECI), respectively [Mirem92]. They are intended for checking program control flow. In the experiments, the two error detection techniques were evaluated under different workloads and detection coverage and latency were measured.

# 2.3.3. Other Techniques of Hardware-Implemented Fault Injection

Other techniques of hardware-implemented fault injection include electro-magnetic interference [Leber93] and power supply disturbance [Damm86, Mirem92]. These techniques of fault injection are similar in nature to that of heavy-ion fault injection. They allow faults to be injected within IC chips but they suffer from the same lack of experimental control in terms of fault injection location and types of faults to be injected. However, electro-magnetic interference and power supply disturbance do emulate faults in the real world most closely.

## 2.4. Software-Implemented Fault Injection

Software-implemented fault injection introduces errors into the target system by software means. Compared with hardware-implemented fault injection, the software approach does not require special hardware equipment, therefore it offers reduced cost, more flexibility and better experimental control. With the software approach, high level fault injection becomes possible, which opens the way for effective testing of some software implemented fault tolerance mechanisms. For these reasons, software-implemented fault injection has become increasingly popular in recent years.

Software-implemented fault injection is typically carried out by changing memory content in either data or program code sections, changing register content, or triggering some built-in hardware error detection mechanism. The injection techniques used mostly involve modifying the memory image of processes at compile time. In this way, the program control flow can be altered and fault injection routines can be incorporated

into the target program which will later carry out fault injection work when the program is run.

# 2.4.1. FIAT Fault Injection Tool

Segall et al [Segal88] developed the FIAT fault injection environment for evaluating reliability properties of distributed real-time fault tolerant systems. FIAT works by manipulating the target software systems, known as *workloads*, at symbolic level (see the explanation in the following paragraph). A target software system is a collection of communicating processes, with each process consisting of a code segment and a data segment.

The target system is first analysed and the symbolic names (known as *attributes*) are extracted. These symbolic names identify individual processes, and code and data segments within individual processes of the target software system. Using the extracted symbolic names, the tester can express what faults are to be injected at what objects identified by the symbolic names. These fault injection intentions consisting of type of fault to inject and location of injection are expressed in the form of *fault classes*. A fault class is like an abstract data type. The tester specifies the characteristics of the faults to be injected in a fault class, and later the fault class will be used by the fault instance generator to generate a list of faults to be injected.

The fault classes provided by FIAT are:

• Memory fault;

- Register fault;

- Communication fault;

- Error detection mechanism triggering fault.

A number of program attachments are linked to the target system at link time. These program attachments monitor the target system, carry out actual fault injection, and report high level abnormal events. The specially linked target software systems are executed on Fault Injection Receptacle (FIRE) machines and the experiment is controlled from a Fault Injection Manager (FIM) machine. The FIREs and the FIM are connected by a local area network.

FIAT has been used to examine a real-time distributed checkpointing fault tolerant system [Segal88]. The target system consisted of two computational engines: the primary and the secondary. The primary, on receiving a request for real-time computation, informs the secondary of the request as well as the time for next interaction. The primary then executes the request. The secondary waits for the next interaction. If the next interaction has exceeded the time bounds (i.e., primary failure), the secondary then initiates a recovery action and becomes the primary. If the primary detects that no secondary exists (i.e., secondary failure), it creates a secondary. In the experiments, the primary was fault-injected to examine the failure detection coverage and detection latency of the secondary.

The FIAT fault injection environment demonstrated the viability of emulating hardware

faults through software-implemented fault injection.

## 2.4.2. FERRARI Fault Injection Tool

The FERRARI fault injection tool [Kanaw92] made improvements in software-implemented fault injection in terms of better controllability. It allows faults to be injected in specific physical locations instead of only those mapped by symbolic names. The time of fault injection during the execution of the target system can also be controlled. FERRARI can also inject transient faults which cause errors of limited durations.

In FERRARI, the target system is first analysed and executed. The purpose of this analysis and execution phase is to determine the starting address and size of the text (code) and data segments of the executable file, and to extract the execution behaviour of a fault free run, such as the execution time, the output, and the addresses used by the program. Fault injection instructions of a user are expressed through experiment parameters. These parameters include:

- Experiment modes (user specified or automatic selection of fault location, time and duration);

- Fault types (bit XOR, bit set, bit reset, byte set, or byte reset);

- Fault class (data, control flow, or user defined);

• Type of reliability measurements (coverage, or coverage and latency).

Using the results of the target system analysis and the experiment parameters provided by the user, the target system is modified and injection points (software traps) are set up. When the modified target system is run, it will be trapped at the injection points, where selected faults are injected.

FERRARI supports the injection of both transient faults (called transient errors in [Kanaw92]) and permanent faults. When the execution reaches a specified address, the program is trapped. For transient faults, a selected fault is injected and the current instruction is executed, and then the error caused by the injected fault is removed and the program is allowed to resume execution. For permanent faults, the error caused by the injected fault is not removed. The program is trapped for the next n instructions, where n is the duration of the fault.

In FERRARI, faults are modelled on bus line faults (both address line faults and data line faults) and faults in condition code flags, though the actual manipulations (fault injection) are applied to memory cells and registers. For example, an "address line fault while the processor is fetching an instruction" is said to have been injected when the processor is forced to fetch a different instruction. This is achieved by modifying the program counter. For transient faults, the modified program counter will be restored to its correct value after the execution of the incorrect instruction. While for permanent faults, the program counter will be modified repeatedly for several instructions, or the entire execution interval of the target application.

FERRARI has been implemented on a SUN SPARC station and used to measure the effectiveness of several redundancy based error detection techniques that were built into application programs [Kanaw92]. As the experimental results showed, most of the errors caused by injected faults were detected by the built-in error detection mechanisms of the SPARC system before the application level error detection techniques had a chance. However, most of the errors that slipped through the detection of the SPARC system were either detected by the application level detection techniques or caused a program crash.

## 2.4.3. SFI Fault Injection Tool

The Software Fault Injector (SFI) developed by Rosenberg and Shin [Rosen93] allows fault injection at various levels for different purposes. Low level faults can be injected to create memory errors and CPU failures (such as the failure of the adder or multiplier) for testing reliability mechanisms implemented on single nodes. Injection at message level facilitates the testing of distributed reliability mechanisms. Messages from the injected node can be omitted, delayed, or altered.

Compared with other software-implemented fault injection tools, SFI also offers better timing control. With SFI, faults can be injected as transient, intermittent, and permanent faults, and the timing parameters of all these types can be specified by the user. A transient fault is injected only once, at a given time after the start of an experiment run. An intermittent fault is injected repeatedly at the same location. For an intermittent fault, the tester can specify the distribution of the interval time between injections. The

interval time can be deterministic, with a set time between injections, or can follow an exponential distribution with a given mean. When the interval time between injections is small, the injected fault will behave like a permanent fault.

Three methods are employed in implementing fault injection in SFI. They are active injection, control flow alteration, and code replacement. Active injection is performed by a process that runs concurrently with the executing workload. Active injection is used to inject memory faults. Control flow alteration can be used to modify the functional behaviour of the system. It is used to inject communication faults. Code replacement can be used to emulate faults in areas which are otherwise not accessible, such as the adder or the multiplier of the processor.

SFI has been used to examine the effect of intermittent communication failures (message omissions) on the message delivery time between two adjacent nodes in the HARTS distributed real-time system [Shin91], and it has also been used to evaluate a number of routing algorithms for distributed systems by injecting omission faults in selected nodes.

## 2.4.4. FINE Fault Injection Tool

While most fault injection based studies concentrate on the final impact of faults on the target system with emphasis on latency and coverage issues, Kao et al [Kao93] looked into the issue of how errors propagate in a software system. A software tool for fault injection and monitoring (FINE) was developed and used to trace UNIX system behaviour under the influence of faults. FINE is made up of four major components

(fault injector, software monitor, workload generator, and controller) and some analysis utilities.

The fault injector supports the injection of both hardware faults and software faults. Since the application programs do not have the privilege to modify the kernel, the fault injector is implemented in two parts, client and server. The server part is implemented in the UNIX kernel. It provides an interface for the client part to specify the faults to be injected into the kernel.

The software monitor traces the execution flow (by using *probes*) and key variables of the kernel, and writes trace data to a file. The probes are inserted into most of the significant functions to keep track of the execution flow and arguments. The software instrumentation is embedded in the kernel to monitor system behaviour. While the functionality of the software monitor is implemented in the kernel, an interface (in the form of a system call) is provided so that a user program can specify the probes and key variables to trace.

The workload generator generates synthetic workload of system calls according to user specification. The controller specifies the fault for the fault injector, the key variables for the software monitor, and the workload specification for the workload generator; it then starts the experiment.

Both hardware faults and software faults (software bugs) can be injected with FINE. The hardware fault types are:

| • Memory faults;                                                                         |

|------------------------------------------------------------------------------------------|

| • CPU faults (register faults);                                                          |

| • Bus faults;                                                                            |

| • I/O faults.                                                                            |

| The software faults modelled in FINE are:                                                |

| • Initialisation faults;                                                                 |

| • Assignment faults;                                                                     |

| • Checking faults;                                                                       |

| • Function faults.                                                                       |

| Initialisation faults include uninitialised variables and wrongly initialised variables  |

| Assignment faults can be missing assignment or incorrect assignment. Checking faults     |

| include missing condition checks and incorrect condition checks. Function faults are     |

| those which involve multiple incorrect statements.                                       |

| Experiments on SunOS 4.1.2 were conducted to investigate error propagation and to        |

| evaluate the impact of various types of faults. Based on the results of the experiments  |

| error propagation models were built for both hardware and software faults. The           |

| experimental results also revealed that memory faults and software faults usually have a |

very long latency while bus faults and CPU faults tend to crash the system immediately.

# 2.4.5. Simulation-Assisted Fault Injection

Software-implemented fault injection is restricted to the parts of the target system that are accessible to software. Sub-instruction level faults, such as the omission of a micro-instruction in a RISC (Reduced Instruction Set Computer) processor can not be directly injected using conventional software-implemented fault injection methods. Guthoff and Volkmar [Gutho95] proposed a simulation-assisted software-implemented fault injection method.

Under this method, fault injection is carried out in three steps. In the first step, the target system starts off normally and then is interrupted when a fault is to be injected. In the second step, the state of the target system is transferred to the simulator and the resulting state after fault injection is calculated. In the final step, the resulting state is transferred back to the target system and execution is resumed. This method has been used to investigate the impact of the omission of a single micro-instruction on the behaviour of a Motorola MC88100 RISC processor. The experiments were carried out while the processor was running a benchmark program. The experiments revealed that the omission of a single micro-instruction can cause segmentation violation, bus error, and division by zero error. The detection latency of these errors by the processor's built-in error detection mechanisms was also measured.

This combined method offers the benefits of software-implemented fault injection while allows access to parts of the target system which are not accessible using conventional software approach. Because the portion of the target system which is simulated is only the part of the target system which is not accessible by software, the effort required for the construction of the simulation model is kept to a minimum.

# 2.4.6. Other Work on Software-Implemented Fault Injection

Software-implemented fault injection provides an important means for studying systems behaviour under faulty conditions. Chillarege and Iyer [Chill87] investigated error latency in systems by injecting memory faults in a VAX 11/780 system using data gathered through hardware instrumentation. The workload is that of a typical multi-user time-sharing system, which consisted of a variety of scientific and miscellaneous word and data processing applications. The study finds that the mean error latency in the memory containing the operating system varies by a factor of 10 to 1 (in hours) between the low and high workloads. The study also finds that most errors were discovered within a day of fault injection.

Chillarege and Bowen introduced the idea of failure acceleration, and studied the failure behaviours of a large commercial transaction processing system using memory fault injection [Chill89]. The work revealed: only 16% of faults actually cause a total loss of primary service; some errors do not affect short term system availability but would cause a catastrophic failure following a change in operating state, where a change of operating state refers to a substantial change in workload or a change in system configuration; some errors are potential candidates for repair before total failure.

Though the emphasis of the two papers has been on the methodology and design of such

experiments rather than on the fault injection techniques, it does show the value of software-implemented fault injection in such investigations.

#### 2.5. Fault Injection for Fault Removal

Unlike fault injection for the purpose of fault forecasting (i.e., issues of error latency, error detection coverage and error propagation, etc.), fault injection for the purpose of fault removal inevitably requires the injection of specific classes of faults in order to uncover flaws in the design/implementation of fault tolerance mechanisms. The issues of injecting specific classes of faults (also known as *deterministic fault injection* [Echtl91]) for the objective of fault removal have been looked at in a number of contexts.

## 2.5.1. Testing of Distributed Fault Tolerant Algorithms

The issue of fault injection based testing for the removal of design faults of distributed fault tolerant algorithms has been discussed in [Echtl91], and a *structural testing* approach suggested. It is observed that the distributed fault tolerant algorithm under test can be represented by a *structure graph*. The goal of structural testing is to feed the software implementation of the algorithm with carefully selected inputs so that some (or all) structural parts of the algorithm are executed and results (outputs) are monitored. It is hoped that design faults can be revealed through this execution.

For distributed fault tolerant algorithms, the inputs also include faults. In distributed systems, the behaviour of a faulty processor is exhibited by the erroneous messages the

faulty processor sends. So message level fault injection was adopted in [Echtl91] for the testing of distributed fault tolerant algorithms. The internal conditions of a faulty processor is of no significance for the distributed fault tolerant algorithm under test.

One important issue in structural testing is the selection of faults in order to cover certain structural parts of the algorithm. Echtle et al [Echtl91] suggested the use of a special heuristics which is based on the typical characteristics of distributed fault tolerant algorithms.

EFA [Echtl92], a distributed testbed system for testing the fault tolerance capabilities of distributed algorithms, was developed to support the implementation of deterministic fault injection. This distributed testbed system provides a number of facilities, including special communication primitives. These special communication primitives allow the transmission and receipt of messages to be intercepted and monitored. This provides the basis for deterministic fault injection. The intercepted messages can be manipulated in a number of ways. Injection of the following faults is supported:

- Falsification of message contents;

- Multiple transmission of messages;

- Falsification of message transmission times (delays);

- Re-ordering of message transmissions;

- Generating spontaneous messages;

# • Combinations of the fault types listed above.

The fault cases to be injected are expressed by the testers in the form of a program module which will be called by the testbed system software when the experiment is executed.

The distributed fault tolerant algorithms to be tested must be implemented using the special facilities provided by EFA. The main idea here is to modify messages in a manner that will force the algorithm under test to take specific execution paths. Distributed fault tolerant target systems implemented using the usual communication facilities provided by a communication subsystem can not be tested in this testbed. In other words, this testbed is for algorithms, not for implementations.

Avresky et al [Avres92] also investigated the issue of structural testing of fault tolerant algorithms through deterministic fault injection, and the Inter-Replica protocol (IRp) of Delta-4 distributed fault tolerant architecture [Powel91] was partially tested on a simulator. The IRp provides co-ordination functions necessary to handle communications between replicated application processes. A small part of the code implementing the IRp was tested on a simulator. The simulator simulated three stations (three replicas). Two faults were discovered: one was an implementation fault and the other was a protocol design fault.

# 2.5.2. Fault Tolerance Testing of AAS

The Advanced Automation System (AAS) is a distributed real-time system developed

for the US Federal Aviation Administration to provide future air traffic control services for the US [Avizi87, Benel89, Crist90]. It is a large and complex system with very high reliability requirements. To verify its reliability properties prior to commissioning, it becomes necessary to conduct a systematic testing of the fault tolerance capabilities of AAS at all levels through various forms of fault injection [Dilen91].

Fault tolerance in AAS is provided in a hierarchy of fault handling facilities, at both local level and distributed systems level. These fault handling facilities include error detection, error reporting, and error recovery. The AAS fault tolerance testing is intended for both reliability assessment (fault forecasting) and validation of fault tolerant software. As a result, two approaches were taken: specific testing and selective sample testing. With specific testing, specific error conditions are created to verify whether the system can operate correctly and cope with the expected failures. With selective sample testing, large numbers of faults of random nature are injected in the system under various operational conditions in order to identify any previously unknown failure modes and to establish a statistical basis for the evaluation of system reliability.

The method adopted in the AAS fault tolerance testing is to integrate the fault injection provisions into the AAS architecture. Each Ada (the AAS implementation language) program address space contains a fault injection subsystem which interprets and coordinates the execution of fault injection instructions in that address space. At the local level, the faults which can be injected include:

#### · Ada exceptions raised;

- Memory corruption;

- Timer manipulation;

- Processes delayed or terminated;

- Operating system failures.

At the distributed systems level, communication messages can be manipulated to emulate:

- Message loss;

- Message delay;

- Message corruption;

- Message duplication.

These fault injection capabilities allow a wide range of AAS modules to be tested for fault tolerance. A good example of how specific testing can help uncover software bugs is the testing of the implementation of a group membership protocol in AAS. After the initial analysis showed possible flaws in the implementation, a specific test case was constructed to test the software. The experiment revealed a missing piece of exception handling code.

Although the AAS fault tolerance testing mainly centres on specific testing for the

removal of fault tolerance deficiency faults, the fault injection capabilities developed are also used in selective sample testing for assessing system reliability.

# 2.6. Overview of Software Testing Techniques

The testing activities that occur during a software project can be classified into unit testing, integration testing and system and acceptance testing [Ince89]. Unit testing is the process of checking a program unit (subroutine or procedure) with test data. The main aim of unit testing is to ensure that a program unit meets its specification. Integration testing is the process of testing a partial version of the system while small chunks of the system are added. The aim is to ensure that the interface between the chunk that has been integrated and the system is correct. Finally, system and acceptance testing is conducted to ensure that a software system meets its system specification. System testing is carried out by the developers of the system while acceptance testing is carried out by the users though the aim of the testing and the techniques used are the same.

In this section we present an overview of some of the established software testing techniques and discuss their application in different testing activities.

#### 2.6.1. Structural Testing

Structural testing [Ince93] involves testing a program so that some structural metric is satisfied or a particular path is traversed. The latter is often referred to as path testing. Examples of program metric include percentage rate of statements or conditional

branches being executed. While in path testing, a program path can be any execution path from the beginning to the end of the program being tested.

The test data for structural testing can be generated by analysing the source code of the program. Whether particular parts of a program have been executed can be monitored by inserting software probes into the program under test.

Structural testing is normally employed during unit testing where specific structural metrics are set, for example, all statements are to be executed and 90% of conditional branches are to be traversed.

The advantage of structural testing is that test data can be derived systematically and test coverage measured. In the next section we will discuss structural testing further in the context of fault tolerance testing.

#### 2.6.2. Functional Testing

Functional testing is a testing technique where the specification of the program under test is used to derive test data and then the test data is used to check whether the program behaves as specified. In functional testing, the tester is not concerned with the internal structure of the program being tested.

The key issue here for the tester whose aim is to discover program defects is to select test data which have a high probability of exposing program defects. Effective selection of test data is dependent on the skills and experience of the tester but there are some structured techniques (see sub-sections 2.6.4 and 2.6.5) which can be used to guide the

selection.

Functional testing can be employed in unit testing, integration testing, and system testing.

# 2.6.3. Random Testing

Random testing is a technique of randomly generating test data. It involves identifying the input data space for a program and randomly generating test data inside that space.

Random testing is cheap to conduct in terms of tool support as all that required is some form of random number generator. Another advantage of random testing is that it is extremely good at producing data which a human tester would not think of. The main disadvantage of random testing is that for large programs the amount of data needs to be generated is prohibitively high. And this ensures that random testing can only be used for unit testing.

Due to the random nature of this approach to testing, it should only be employed as a useful adjunct to other testing techniques.

# 2.6.4. Equivalence Partitioning Testing

Equivalence partitioning [Somme92] is a test data selection technique whereby the input data is divided into classes (*equivalence partitions*) of common properties. A program should behave in a comparable way for all members of an equivalence partition.

The equivalence partitions may be identified by using design or functional specification and by the tester using experience to predict classes of input data which may lead to different execution paths. For example, a program processing temperatures may process temperature readings in different ranges (below zero, at zero, and above zero) differently. Then the input data space can be divided into three equivalence partitions. Test data will be selected from the three equivalence partitions.

This test data selection technique is useful during unit testing, integration testing, and system testing.

#### 2.6.5. Cause-effect Testing

Cause-effect testing [Ince93] is another test data selection technique. This technique involves examining the program output and analysing it to establish the relationship between input events (causes) and output events (effects). The main advantage of cause-effect testing is in that it is possible to consider combinations of events that occur in a test.

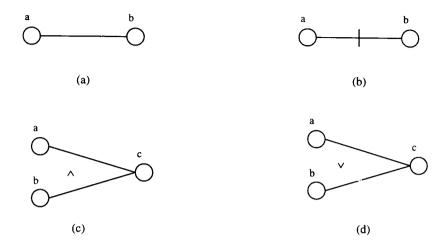

The basic elements of the cause-effect testing notation are shown in Fig. 2.1. On the left-hand side of the graphs are the causes which give rise to events in a system. Typical causes might be an operator typing a command, or a valve closing. On the right-hand side of the graphs are the events that occur because of causes, for example, an alarm being sounded, or an error message being displayed on a screen.

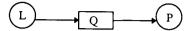

Fig. 2.1

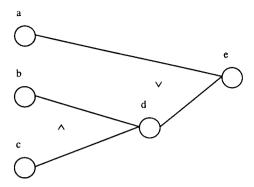

The first graph in Fig. 2.1 states that event b will occur when event a occurs. The second graph states that event b will occur when event a does not occur. The third graph states that event c will occur when events a and b occur, and the fourth graph states that event c will occur when event b occurs. A simple example cause-effect graph is shown in Fig. 2.2. The graph shows that event e will occur when either event a occurs or events b and c both occur.

Fig. 2.2

The cause-effect graph of a software system is derived from the functional specification of the system. This process involves a number of steps. First the system is partitioned into manageable chunks so that each chunk can be analysed on a piece of paper or on a computer screen. Then the causes and effects are identified. The cause-effect graph is then built up. The resulting graph is used to guide the selection of test data.

The cause-effect testing technique is mainly employed during system testing.

# 2.6.6. Mutation Testing

Mutation testing [Mathu94] is a technique which is used to examine the adequacy or effectiveness of test data. Once a series of tests have been conducted, a collection of test data will have accumulated. One important question a tester may ask is: is the test data used adequate in terms of test effectiveness? Mutation testing is a technique aimed at answering this question.

Mutation testing is based on creating mutants of a program. A mutant is a

modified version of the original program in which a small error is inserted. A typical error would be to replace an operator with a different one, for example, replacing an addition operator with a multiplication operator. A large number of such mutants are created, and are then executed using the test data which was employed in testing the original program. If the mutant gives a result which is different from the result of the test of the original program then the mutant is said to have been killed. This means that the test data is able to distinguish between the original program and the mutant.

The percentage rate of the mutants having been killed reflects the level of adequacy of the test data. If the tests of the mutants result in all the mutants being killed then the test data is adequate. However, if any mutants are still living after the tests then it is clear that the test data is incapable of exposing these bugs. Further test data will be required to kill off any living mutants.

Though mutation testing can be used during integration testing and system and acceptance testing, it is best employed during unit testing. This is mainly due to the fact that in general there are a massive number of mutants that can be created.

#### 2.6.7. Assertion Testing

An assertion is a predicate which relates the values of variables in a program and describes a condition which must be true during the execution of a program. Assertion testing [Ince93] is a technique which checks such properties of a program during execution. If a program is correct then such properties must hold during program execution. As a simple example, the following predicate is an assertion: a > b + c. It

states that during program execution variable a must be greater than the sum of variable b and variable c.

Assertions can be inserted into a program under test either by hand or by means of a software tool [Ince93]. Assertion testing can be employed during the whole testing process up to system testing.

It should be pointed out that assertion testing only checks certain properties of a program. Such properties must hold if the program is correct. However, such properties may still hold even if the program contains bugs. Hence assertion testing should only be used in addition to other testing techniques.

#### 2.6.8. Comments

In general there are two broad approaches to software testing: structural testing and functional testing [Somme92]. In the structural approach, the aim is to achieve certain structural metrics or to traverse a particular path in the testing. The selection of test data is clearly guided by this aim.

In the functional approach, the tester is not concerned with the internal structure of the program under test. The key issue here for the tester is to select test data which has a high probability of exposing program defects. In this section we have examined a number of test data selection techniques: random testing, equivalence partitioning, and cause-effect testing.

The adequacy or effectiveness of test data in terms of its defect revealing power can be

checked through mutation testing. The assertion testing technique is aimed at testing a program from a different perspective by checking certain run-time properties of a program which must be true if the program is correct.

In this section we only discussed generic software testing techniques which are generally independent of application domains. Some application domain specific testing techniques have also been proposed which take into account the characteristics of application. For example, the testing of telecommunications software [Avrit95], where the arrival distribution of input (telephone calls) is of great importance in revealing software defects.

# 2.7. Fault Tolerance Testing Strategies

When considering fault injection based testing for the purpose of removing fault tolerance deficiency faults, one is faced with two related issues: fault injection techniques and testing strategies. While fault injection techniques deal with the question of how to inject required faults effectively, testing strategies deal with the issue of what faults to inject in order to achieve an adequate test of the target system. In this chapter we have already described the techniques for fault injection, now we discuss the related issue of testing strategies.

As in conventional software testing, there are two broad testing strategies: structural testing and functional testing. In the structural approach, the idea is to select faults such that these faults will cause certain structural parts of the target software system to be executed. The overall aim is to inject a set of faults so that all parts of the target system

are executed at least once, with the hope that fault tolerance deficiency faults in the target system will be exposed once the system is fully exercised. Functional testing takes a more direct approach. Faults are injected to create specific failure scenarios to ascertain that the target system can indeed tolerate such faulty conditions. These two contrasting approaches are discussed and their merits and shortcomings are analysed in the following sub-sections.

# 2.7.1. Structural Testing

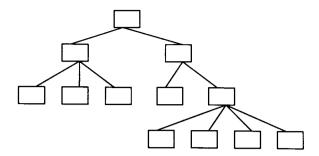

The first step in structural testing involves the construction of the *structure graph* [Echtl91] (or *execution tree* [Avres92]) of the program under test. The structure graph models a program by characterising it as forks leading to branches. A node in the structure graph represents a sequence of statements, while an edge represents a branch of a conditional statement. An example of a structure graph is shown in Fig. 2.3. When constructing the structure graph of a program, conditional loops are modelled as a chain of forks if the number of iterations is finite. With the structure graph of a program constructed, faults can be selected and injected in 'faulty' processor(s) with the aim of having the program running on correct processor(s) execute certain branch(es) of the structure graph.

Fig. 2.3 Program Structure Graph

The structural approach towards fault tolerance testing has the theoretical nicety of completeness, in the sense that a complete test of the target program can be carried out by covering all the branches of the structure graph. The level of testing granularity can also be determined according to the amount of resources allocated to the testing efforts. In a 'large grain' testing, the leaves of the structure graph may be large pieces of program that contain conditional statements; while in a 'fine grain' testing, the leaves may contain only sequential statements (non-conditional statements). Given enough resources, it is possible to have each and every one of the statements of the program covered (executed) in a complete test.

The structural approach has some serious problems. The first question one would ask is "what is the relationship between the correctness of a program under test and a complete coverage of its structure graph". Obviously achieving a complete coverage of the structure graph does not necessarily mean that a program is correct. The execution of a part of the structure graph may give correct results for some input data but incorrect results for some other input data. Another shortcoming with the structural approach has to do with the way the structure graph is generated. A structure graph is generated from

the design of the target software system to be tested. So if the design is incorrect then the structure graph, which is used as a reference framework for testing, may be incorrect as well. For example, if a branch of the structure graph is missing due to a system design fault (i.e. a certain failure scenario is not handled by the program), the bug would not be revealed by a testing based on structural coverage.

There are also some practical difficulties in implementing structural testing of fault tolerance. In order to cover the structure graph with a limited number of test runs, a mechanism for recording information regarding which parts of the graph have been covered will be needed. It was suggested in [Echtl91] that software implemented *probes* be planted in the program code to record the actual program flow. It might be feasible for testing fault tolerant algorithms implemented in a purpose-built testbed system with facilities supporting the use of probes, but it is likely to be difficult to plant probes in a target system implemented in its own environment. Structural testing is generally a tedious process and is not scaleable. Thus it is often impractical to conduct on complex target systems.

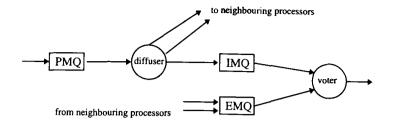

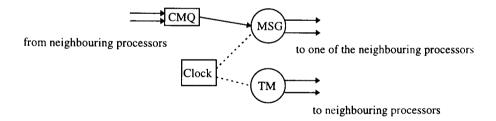

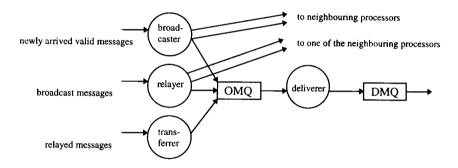

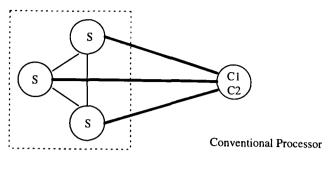

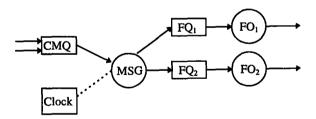

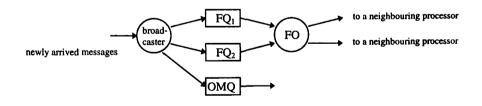

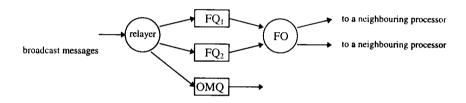

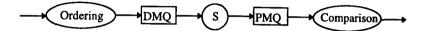

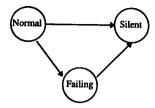

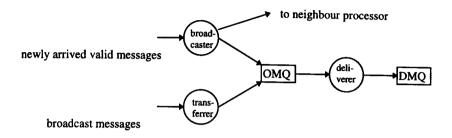

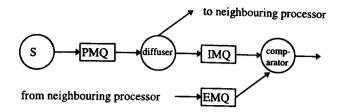

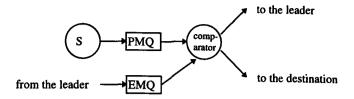

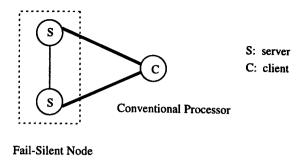

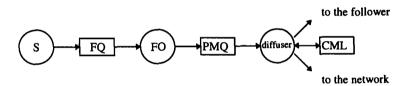

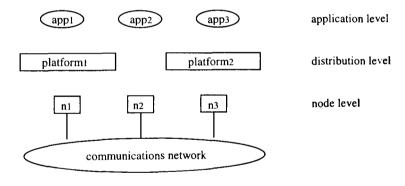

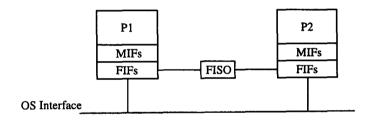

# 2.7.2. Functional Testing