# University of Newcastle upon Tyne Department of Computing Science

Verification and Synthesis of Asynchronous Control Circuits Using Petri Net Unfoldings.

> by Alexei Semenov

NEWCASTLE UNIVERSITY LIBRARY

097 52134 8

Thesis L6094

PhD thesis

July 1997

# BEST COPY

# AVAILABLE

Variable print quality

# Contents

| A | CKHO  | wiedgements                                | VIII |

|---|-------|--------------------------------------------|------|

| A | bstra | act                                        | ix   |

| 1 | Int   | roduction                                  | 1    |

|   | 1.1   | Motivation                                 | 2    |

|   | 1.2   | Design Cycle                               | 3    |

|   | 1.3   | Position and Contributions of This Work    | 4    |

|   | 1.4   | Organisation of Thesis                     | 5    |

| 2 | Pre   | vious and Related Work                     | 7    |

|   | 2.1   | Asynchronous Circuits Taxonomies           | 8    |

|   |       | 2.1.1 Delay taxonomy                       | 8    |

|   |       | 2.1.2 Protocol signalling taxonomy         | 8    |

|   | 2.2   | Design Methodologies                       | 10   |

|   |       | 2.2.1 Huffman Fundamental Mode Circuits    |      |

|   |       | 2.2.2 Delay-Insensitive Circuits           | 11   |

|   |       | 2.2.3 Speed-Independent Circuits           | 11   |

|   |       | 2.2.4 Micropipelines                       |      |

|   | 2.3   | Formal Models                              | 13   |

|   | 2.4   | Design of Speed-Independent Circuits       | 16   |

|   | 2.5   | Conclusions                                | 17   |

| 3 | Pet   | ri Nets and Related Formalisms             | 18   |

|   | 3.1   | Petri Nets                                 | 18   |

|   | 3.2   | Analysis of PN Behaviour by RG Methods     | 25   |

|   | 3.3   | Analysis of PN Behaviour by PN-unfolding   | 26   |

|   | 3.4   | Signal Transition Graphs                   | 32   |

|   | 3.5   | Analysis of STG Behaviour                  | 34   |

|   | 3.6   | Conclusions                                | 37   |

| 4 | Ana   | alysis of PN Models                        | 38   |

|   | 4.1   | Adapting Truncated PN-unfolding            | 38   |

|   | 4.2   | Avoiding Redundancy in PN-unfolding        | 40   |

|   |       | 4.2.1 Redundancy of Truncated PN-unfolding | 41   |

|   |       | 4.2.2 PN-unfolding Segment                 | 43   |

*CONTENTS* ii

|   | 4.3 | Performance Comparison of Algorithms                                   |

|---|-----|------------------------------------------------------------------------|

|   |     | 4.3.1 Ring Protocol                                                    |

|   |     | 4.3.2 Production Cell                                                  |

|   | 4.4 | Analysis of LPN Models                                                 |

|   |     | 4.4.1 Verification of LPN Models of Specifications                     |

|   |     | 4.4.2 Verification of LPN Models of Circuits                           |

|   | 4.5 | Experimental Results                                                   |

|   | 4.6 | Concluding Remarks                                                     |

| _ |     | 1 L ACTO 11                                                            |

| 5 |     | dlysis of STG models                                                   |

|   | 5.1 | Full State Graph                                                       |

|   | 5.2 | STG-unfolding Segment                                                  |

|   | 5.3 | Low-level System Analysis                                              |

|   |     | 5.3.1 Analysis of STG specifications                                   |

|   |     | 5.3.2 Analysis of asynchronous circuits                                |

|   | 5.4 | Conclusions                                                            |

| 6 | Syn | thesis from STG-unfolding 82                                           |

| U | 6.1 | Motivation                                                             |

|   | 6.2 | Implementation of SI Circuits                                          |

|   | 0.2 | 6.2.1 Basic Synthesis Concepts                                         |

|   |     | 6.2.2 ACGPS Implementation                                             |

|   |     | 6.2.3 ACGPEF Implementation                                            |

|   |     | 6.2.4 ACGPER Implementation                                            |

|   | 6.3 |                                                                        |

|   | 0.3 |                                                                        |

|   |     | -                                                                      |

|   |     | 6.3.2 STG-unfolding Slices                                             |

|   | 0.4 | 6.3.3 Concluding Remarks                                               |

|   | 6.4 | Exact Cover Implementation                                             |

|   |     | 6.4.1 ACGPS Implementation                                             |

|   |     | 6.4.2 ACGPEF Implementation                                            |

|   |     | 6.4.3 ACGPER Implementation                                            |

|   | 6.5 | Strategies for Deriving Approximated Covers                            |

|   |     | 6.5.1 Negative Set Approximation                                       |

|   |     | 6.5.2 Positive Set Cover Evaluation                                    |

|   |     | 6.5.3 Concluding Remarks                                               |

|   | 6.6 | Initial Cover Approximation                                            |

|   |     | 6.6.1 Partial Cut Cover Approximation                                  |

|   |     | 6.6.2 Finding $\mathcal{P}$ -set and $\mathcal{N}$ -set Approximations |

|   |     | 6.6.3 Correctness of Negative Set Approximation Strategy               |

|   | 6.7 | Cover Refinement                                                       |

|   | 6.8 | Experimental Results                                                   |

|   |     | 6.8.1 Practicality                                                     |

|   |     | 6.8.2 Feasibility                                                      |

|   | 6.9  | Conclusions                                      |

|---|------|--------------------------------------------------|

| 7 | App  | ications of PN-unfolding                         |

|   | 7.1  | Motivation for Contextual Net Unfolding          |

|   | 7.2  | Positive Contextual Nets                         |

|   |      | 7.2.1 Contextual Net Definition                  |

|   |      | 7.2.2 Role of Conflict Relation                  |

|   | 7.3  | Contextual Net Unfolding                         |

|   |      | 7.3.1 Basic Relations in Acyclic Contextual Nets |

|   |      | 7.3.2 Contextual Net Unfolding                   |

|   |      | 7.3.3 Contextual Net Unfolding Segment           |

|   | 7.4  | Application: Modelling a Communication Mechanism |

|   | 7.5  | Circuit Verification Results                     |

|   | 7.6  | Use of Unfolding for Variable Ordering           |

|   | 7.7  | Symbolic Traversal of Petri Net State Space      |

|   | 7.8  | Variable Ordering by Means of Unfolding          |

|   | 7.9  | Experimental Results                             |

|   | 7.10 | Conclusions                                      |

| 8 | Con  | lusions 14                                       |

|   | 8.1  | Summary                                          |

|   | 8.2  | Areas of Further Research                        |

# List of Figures

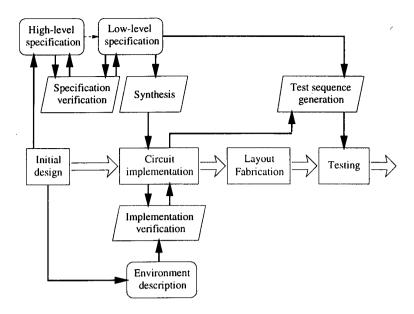

| 1.1  | Overall design process                                                                    | 3  |

|------|-------------------------------------------------------------------------------------------|----|

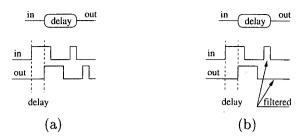

| 2.1  | Illustration of pure (a) and inertial (b) delay models                                    | 8  |

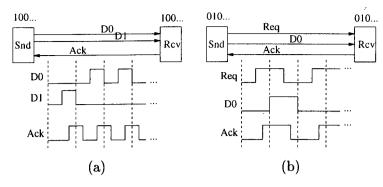

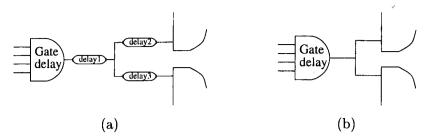

| 2.2  | Illustration of dual-rail (a) and bundled data (b) signalling                             | 9  |

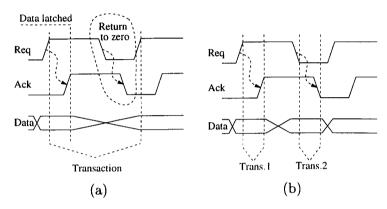

| 2.3  | Illustration of four-phase (a) and two-phase (b) protocols                                | 9  |

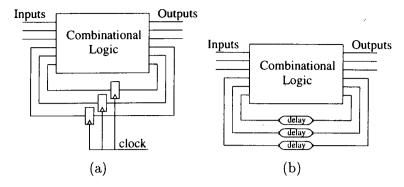

| 2.4  | Fundamental mode synchronous (a) and asynchronous (b) circuits                            | 10 |

| 2.5  | Illustration of Delay-Insensitive (a) and Speed-Independent (b) circuits                  | 11 |

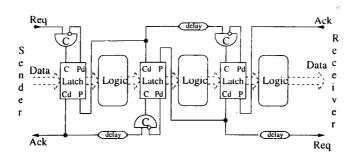

| 2.6  | Sutherland micropipelines                                                                 | 13 |

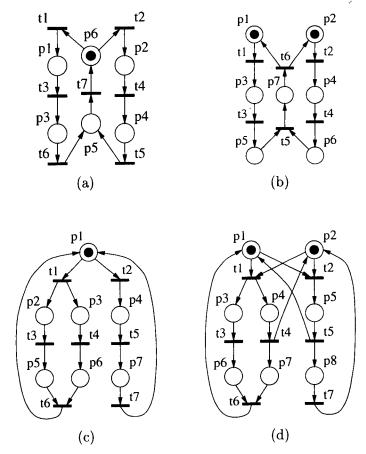

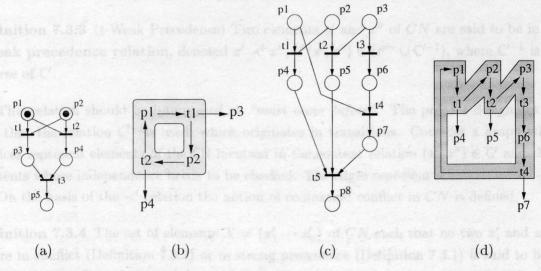

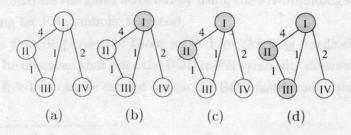

| 3.1  | Examples of different classes of PNs: (a) SMPN, (b) MGPN, (c) FCPN and                    |    |

|      | EFCPN (d)                                                                                 | 19 |

| 3.2  | Example of an RG of a PN                                                                  | 21 |

| 3.3  | Illustration of relations between transitions: (a) concurrent, (b) structural con-        |    |

|      | flict with concurrent transitions and (c) dynamic conflict                                | 22 |

| 3.4  | Illustration of UCPN                                                                      | 23 |

| 3.5  | Example of an LPN                                                                         | 23 |

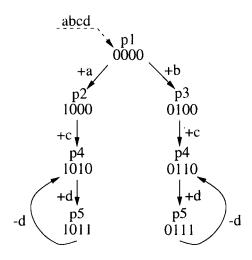

| 3.6  | Example of a ${\sf PN}$ (a) and a reduced ${\sf RG}$ (b) built using stubborn sets method | 25 |

| 3.7  | Example of a BDD representation of the RG in example from Figure $3.6(a)$                 | 26 |

| 3.8  | Algorithm for building PN-unfolding.                                                      | 28 |

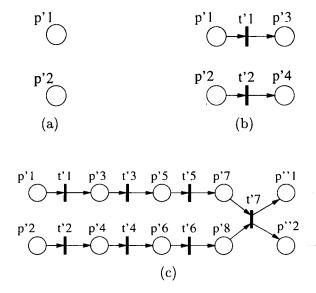

| 3.9  | Steps of the PN-unfolding algorithm (a) initialised $N'$ , (b) after adding two           |    |

|      | instances, (c) after adding one instance of each transition                               | 29 |

| 3.10 | Algorithm for truncated PN-unfolding.                                                     | 31 |

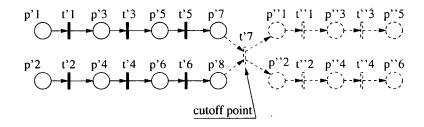

| 3.11 | The truncated unfolding for PN from Figure 3.6(a)                                         | 32 |

| 3.12 | Examples of a valid (a) and invalid (b) STGs                                              | 34 |

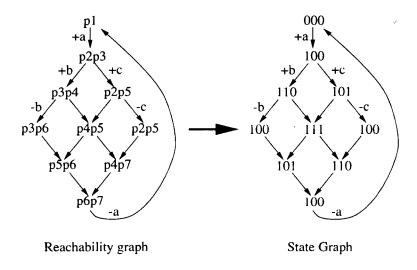

| 3.13 | Illustration of the RG and SG built for the STG example from Figure 3.12(a).              | 35 |

| 4.1  | Example of truncated (a) and modified truncated (b) PN-unfolding                          | 38 |

| 4.2  | Algorithm for modified truncated PN-unfolding.                                            | 39 |

| 4.3  | Example of truncated PN-unfolding redundancy                                              | 40 |

| 4.4  | Examples of truncated PN-unfolding growth                                                 | 41 |

| 4.5  | Illustration of FIFO transformation of an unsafe PN                                       | 42 |

| 4.6  | Example of a PN and its truncated PN-unfolding                                            | 43 |

| 4.7  | Parametrised algorithm for truncated PN-unfolding                                         | 45 |

| 4.8  | Example of a PN and its truncated PN-unfolding                                            | 46 |

| 4.9  | Truncated PN-unfolding with wrong cutoffs                                                 | 47 |

| 4.10 | Algorithm for pruning a truncated PN-unfolding.                                           | 48 |

LIST OF FIGURES

| 4.11 | Illustration of redundancy in a PN-unfolding segment                             | 9 |

|------|----------------------------------------------------------------------------------|---|

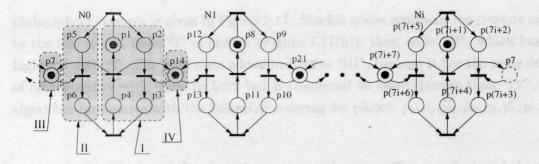

| 4.12 | Scalable example                                                                 | 0 |

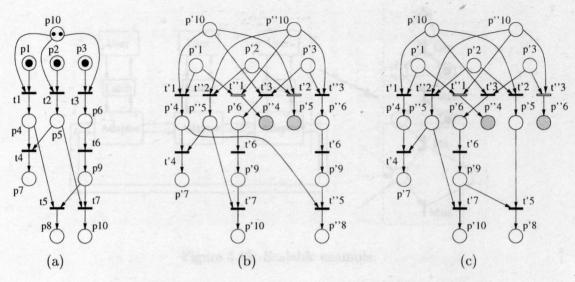

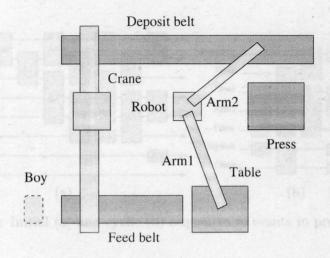

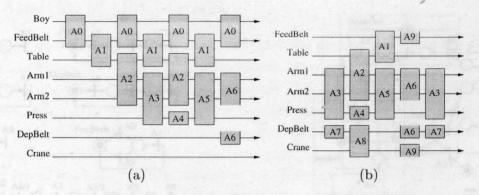

| 4.13 | Illustration of a production cell                                                | 2 |

| 4.14 | Initial (a) and cyclic (b) sequences of events in production cell 5              | 3 |

| 4.15 | PN fragments (a) and the complete PN model (b) for production cell 5             | 4 |

| 4.16 | Algorithms for verification of properties in PN-unfolding segment: (a) Liveness  |   |

|      | check, (b) Safeness check and (c) Persistency check                              | 6 |

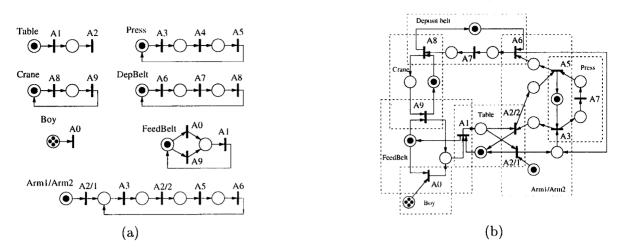

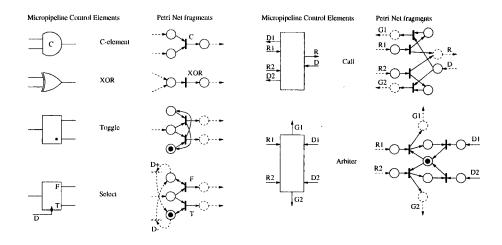

| 4.17 | Basic two-phase control elements and their LPN models                            | 9 |

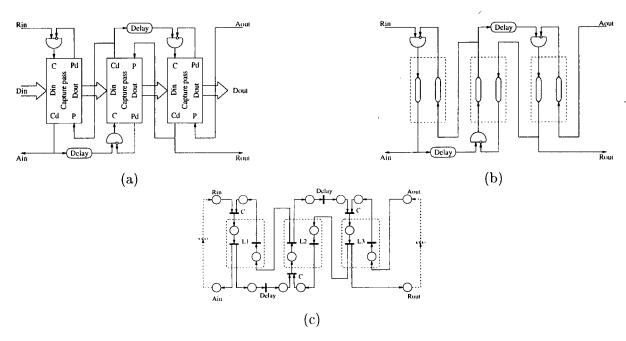

| 4.18 | Sutherland's micropipeline FIFO (a), its control circuitry (b) and its LPN model |   |

|      | (c)                                                                              | 0 |

| 4.19 | Illustration of a hazard of the gate's output                                    | 0 |

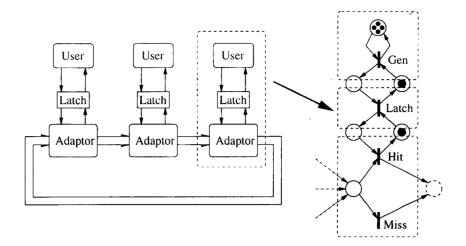

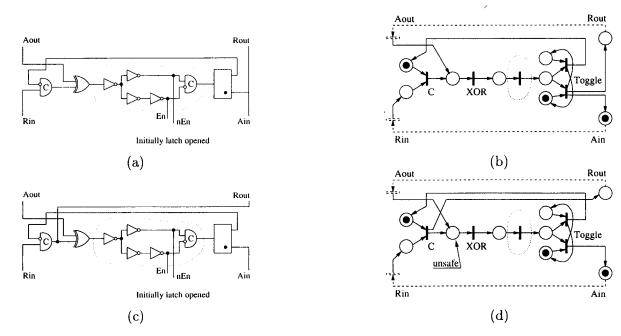

| 4.20 | Standard (a-b) and Fast Forward (c-d) pipeline with four-phase latch control . 6 | 1 |

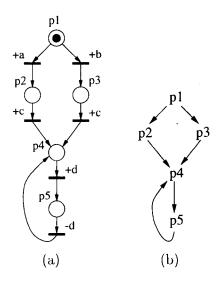

| 5.1  | An STG (a) and its corresponding RG (b)                                          | 5 |

| 5.2  | Algorithm for constructing an FSG from an STG 6                                  | 6 |

| 5.3  | An FSG constructed for the STG from Figure 5.1(a) 6                              | 7 |

| 5.4  | Example of an STG (a) and its RG (b) which is not covered by its FSG (c) 6       | 8 |

| 5.5  | Algorithm for obtaining STG-unfolding segment                                    | 3 |

| 5.6  | Examples of STG-unfolding segments                                               | 4 |

| 5.7  | Examples of a 3 input AND gate (a), Muller C-element (b) and ME-element (c). 78  | 8 |

| 5.8  | Four-phase micropipeline control circuit                                         | 9 |

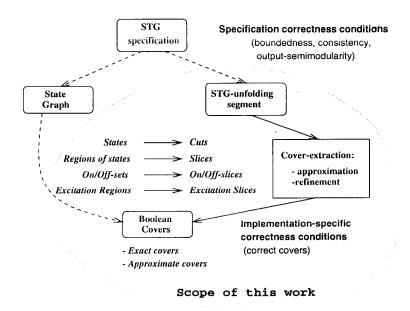

| 6.1  | Overview of synthesis issues discussed in the work                               | 3 |

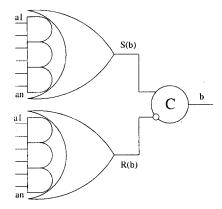

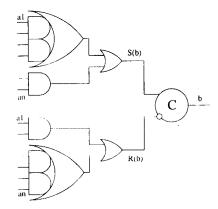

| 6.2  | Atomic complex gate architecture                                                 | 6 |

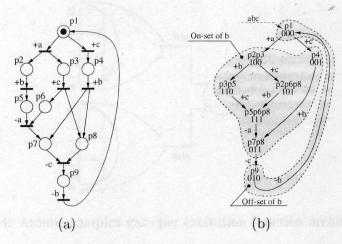

| 6.3  | Example of an STG (a) and its corresponding SG (b)                               | 7 |

| 6.4  | Atomic complex gate per excitation function architecture                         | 8 |

| 6.5  | Atomic complex gate per excitation region architecture                           | 9 |

| 6.6  | Illustration of cuts                                                             | 3 |

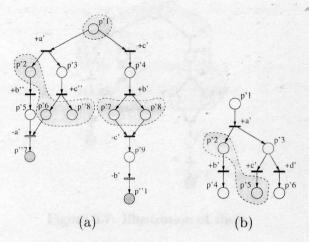

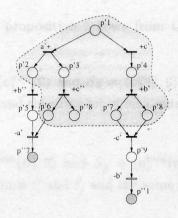

| 6.7  | Illustration of slices                                                           | 4 |

| 6.8  | An SG (a) and STG-segment (b) for the STG in Figure 6.3 97                       | 7 |

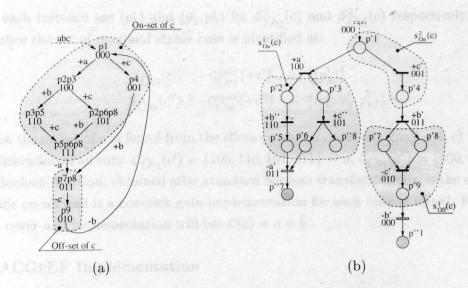

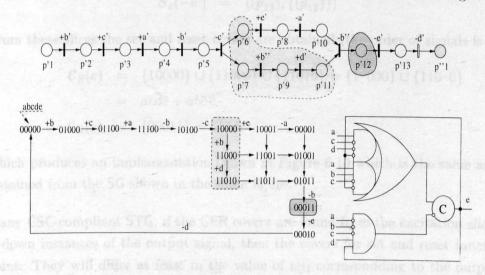

| 6.9  | Illustration of the Set cover calculation on STG-unfolding                       | 9 |

| 6.10 | Another example of the Set cover calculation on STG-unfolding 99                 | 9 |

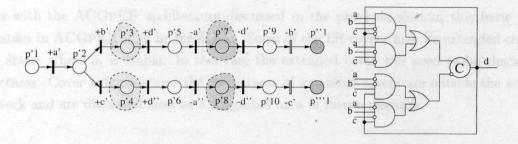

| 6.11 | Illustration of slices and cover calculation for ACGPER architecture 10          | 1 |

| 6.12 | Illustration of the Negative set approximation strategy                          | 3 |

| 6.13 | Procedure for the Negative set approximation strategy                            | 1 |

| 6.14 | Illustration of the Positive set evaluation strategy                             | 1 |

| 6.15 | Procedure for the Positive set cover evaluation strategy                         | 5 |

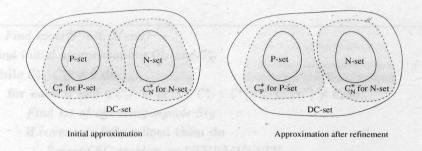

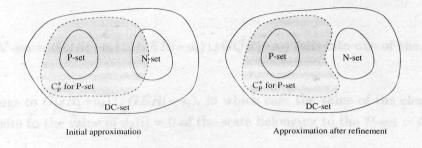

| 6.16 | Illustration of cover approximation for a place (a) and a slice (b) 108          | 3 |

|      | Procedure for refining cover approximations                                      |   |

| 6.18 | Illustration of cover approximation and refinement                               | 7 |

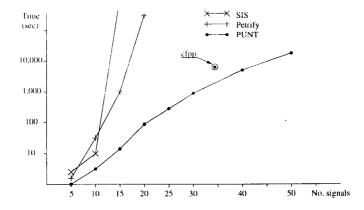

| 6.19 | Experimental results for Muller pipeline                                         | ) |

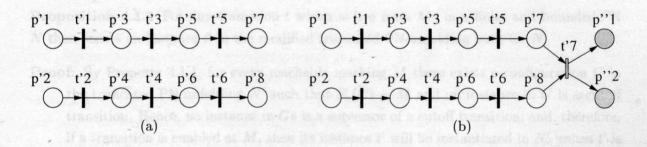

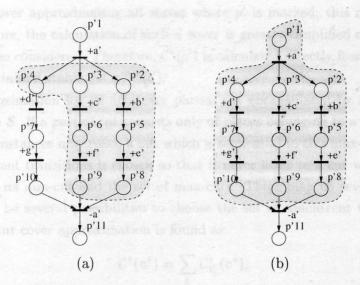

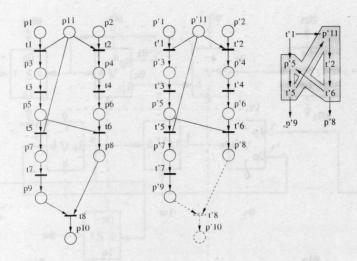

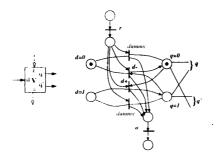

| 7.1  | Example of a Petri net with self-loops (a) and its unfolding according to the    |   |

|      | requirement of structural conflict (b)                                           | l |

LIST OF FIGURES vi

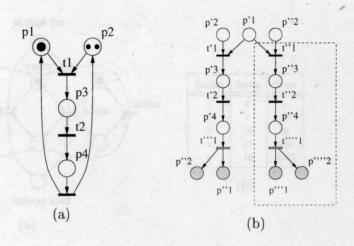

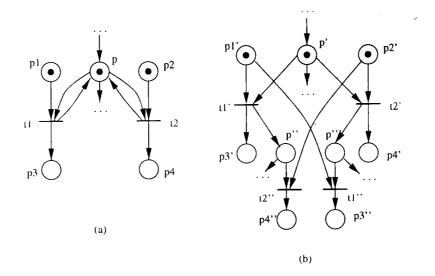

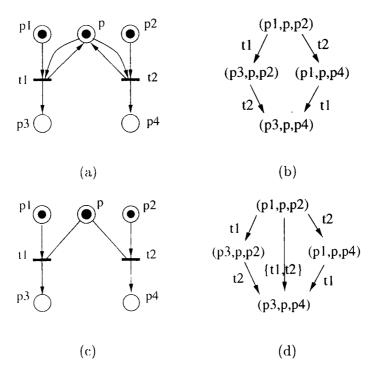

| 7.2  | Petri net with self-loops (a) with its step reachability graph (b) and contextual |

|------|-----------------------------------------------------------------------------------|

|      | net (c) with its step reachability graph (d)                                      |

| 7.3  | Conflict and semi-conflict                                                        |

| 7.4  | Examples of CNs (a),(c) which cannot be contextual occurrence nets and their      |

|      | corresponding graphs (b),(d) of must occur before relation                        |

| 7.5  | Algorithm for obtaining CN-unfolding segment                                      |

| 7.6  | Another example of a CN and its unfolding                                         |

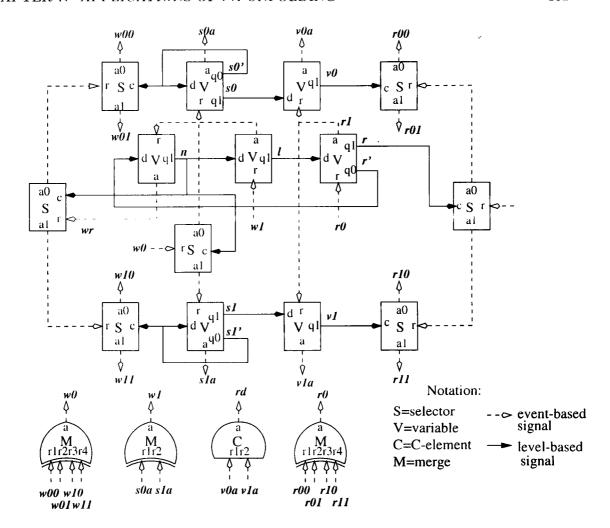

| 7.7  | Schematic for Simpson's communication mechanism                                   |

| 7.8  | Illustration of the Variable element                                              |

| 7.9  | Illustration of the benchmark circuit                                             |

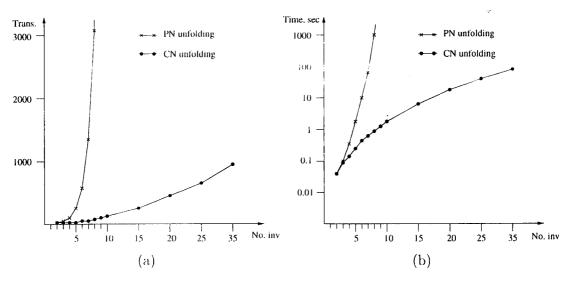

| 7.10 | Experimental results: (a) Size of the segment in transition instances; (b) Time   |

|      | taken                                                                             |

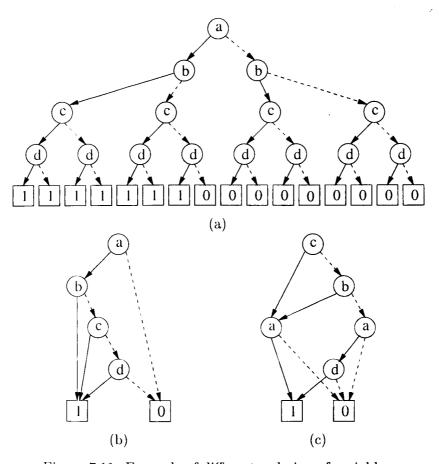

| 7.11 | Example of different ordering of variables                                        |

| 7.12 | Pseudo-code for construction of the BDD representation of the state space of a    |

|      | PN                                                                                |

| 7.13 | Example of a BDD                                                                  |

| 7.14 | Pseudo-code for clustering algorithm                                              |

| 7.15 | Dining philosophers benchmark                                                     |

| 7.16 | Pseudo-code for cluster ordering algorithm                                        |

| 7.17 | Steps of cluster ordering algorithm                                               |

# List of Tables

| 4.1 | Experimental results for the token ring protocol        |

|-----|---------------------------------------------------------|

| 4.2 | Experimental results for the production cell            |

| 4.3 | Experimental results for the Sutherland's pipeline 6    |

| 5.1 | Experimental results for the examples set of benchmarks |

| 5.2 | Experimental results for the No-USC set of benchmarks   |

| 5.3 | Experimental results of four-phase circuit verification |

| 6.1 | Experimental results for circuit synthesis              |

| 7.1 | Experimental results for PN symbolic traversal          |

| 7.2 | Experimental results (deadlock detection)               |

# Acknowledgements

I would like to express my gratitude to my supervisor, Alex Yakovlev, for introducing me to the exciting and challenging world of asynchronous circuit design. His enthusiasm and devotion to the asynchronous world kept me going from the very first day when I learned about the existence of asynchronous circuits till the very end. Special mentioning deserves his patience and on-going interest in discussing some of my theories (often not very good ones, in retrospect) and wholehearted participation in the development of most of my papers. He introduced me to top-class researchers in the asynchronous area, for which I am also thankful. He and his family (Maria and Greg) made my life in Newcastle a pleasant experience.

This work would have not been possible had I not met and discussed it with the "mediterranean" research group consisting of Luciano Lavagno, Jordi Cortadella, Enric Pastor, Oriol Roig and Marco Peña. Their comments helped me to develop and shape this work. A special thank you goes to the members of their families who's companies I enjoyed while visiting Berkeley and Barcelona.

Of course, this work would never be completed without constant support from my family and friends, patiently bearing my "coma-like" periods during which I was working towards numerous deadlines. I value greatly the moral input from Olga, Anton and Andrew who once again proved that friendship is indeed delay-insensitive. I would like to thank my officemates from B338, Martin Hesketh and Frode Sandnes for being such a wonderful company; my particular appreciation is to Rob Allen who, in addition, managed to read through the whole thesis.

Last, but not least, I would like to acknowledge financial help from the Research Committee of the University of Newcastle upon Tyne, which provided my Research Studentship grant, and the Committee of Vice-Chancellors and Presidents, which provided the Overseas Research Studentship Award.

### Abstract

Design of asynchronous control circuits has traditionally been associated with application of formal methods. Event-based models, such as Petri nets, provide a compact and easy to understand way of specifying asynchronous behaviour. However, analysis of their behavioural properties is often hindered by the problem of exponential growth of reachable state space. This work proposes a new method for analysis of asynchronous circuit models based on Petri nets. The new approach is called PN-unfolding segment. It extends and improves existing Petri nets unfolding approaches. In addition, this thesis proposes a new analysis technique for Signal Transition Graphs along with an efficient verification technique which is also based on the Petri net unfolding. The former is called Full State Graph, the latter - STG-unfolding segment. The boolean logic synthesis is an integral part of the asynchronous circuit design process. In many cases, even if the verification of an asynchronous circuit specification has been performed successfully, it is impossible to obtain its implementation using existing methods because they are based on the reachability analysis. A new approach is proposed here for automated synthesis of speed-independent circuits based on the STG-unfolding segment constructed during the verification of the circuit's specification. Finally, this work presents experimental results showing the need for the new Petri net unfolding techniques and confirming the advantages of application of partial order approach to analysis, verification and synthesis of asynchronous circuits.

# Chapter 1

## Introduction

Asynchronous (or self-timed) circuits and systems have attracted increasing attention from the research community in recent years. The inherent concurrency in their operation and the absence of the requirement for a pre-determined settling period, the clock cycle, means that these systems reflect more naturally the processes happening in real life.

By making the assumption of a synchronous mode of operation, designers can abstract from the problem of tracking of all intermediate states of the system. It can be safely assumed that the clock period is chosen to be long enough for the signals to settle to their new values. Any feedback is cut off to prevent the changing outputs from affecting the inputs. The arrival of a new clock pulse triggers the transition process to the next state of the system.

In an asynchronous circuit there is no such a "start-stop" mechanism. Any change of signals may cause a transition of the system into the next state. This makes asynchronous circuits harder to design. In addition, the majority of today's designers are used to creating systems and circuits in the synchronous domain.

Since asynchronous circuits are more complex to design, most of the design methodologies assume the use of some formal method. For some time this was an additional obstacle to adopting the self-timing concept. The need for formal verification in circuit design has now been widely recognised in the synchronous domain as well. This places asynchronous circuits on a par with their clocked counterparts.

The asynchronous community has demonstrated that it is possible to design fully functional circuits beyond trivial examples. Several microprocessors have been designed to date. Examples of microprocessor designs can be found in works reported by the Caltech [43], Titech [55] and Manchester [25, 24, 1] research groups. In Manchester, the AMULET group designed an instruction-level compatible asynchronous version of the ARM6 microprocessor whose performance characteristics are comparable to those of the synchronous one. In addition, Philips reported a design of an asynchronous error correction chip [6, 5] which demonstrated 80% savings in the power consumption.

In order to cater for the growing need and complexity of asynchronous circuit design, new methods need to be developed. The conventional approach to circuit verification and synthesis proves to be unable to deal with relatively large examples. The purpose of this work is to introduce a novel technique which will advance the applicability of formal methods. It also serves as the basis for further research.

#### 1.1 Motivation

The use of the asynchronous paradigm in circuit design has been argued to provide certain advantages in circuit performance. The most commonly cited are discussed below.

Average case performance The clock cycle of every synchronous circuit is determined by the longest propagation delay of the circuit. The rate of the clock signal must accommodate the settling times for the longest possible operation. Therefore, during a faster operation some of the parts of the circuit will stay idle while the clock signal is due to switch. To overcome this problem circuit designers need to come up with elaborate scheduling and re-timing schemes.

In an asynchronous circuit, every part works at its own pace. As soon as the data has been processed by one part, the next part is informed and may start working with the data. Thus the overall cycle time, i.e. the average time between the completion of two sequential operations, will be the average of the execution times of all operations.

Absence of clock skew The existence of a propagation delay in the wires of a chip means that the signal change may arrive at two ends of a forking wire at different times. This phenomenon is known as the *clock skew* problem. To guarantee that all operational blocks work synchronously the designer needs to make sure that the clock signal is received by each block at exactly the same time. However, with growing clock rates it becomes increasingly difficult to guarantee the absence of clock skew. In addition, clock wiring has been reported to take up to 60% of all wiring in the chip.

By choosing an asynchronous implementation the designer escapes the clock skew problem and the associated routing problem.

Low power consumption During the operation of a synchronous circuit the clock signal is propagated to every operational block of the circuit even if this block is not used in a particular computation at all. Thus the power is spent on driving the clocked inputs of the gates which do not perform any useful actions.

Each part of an asynchronous circuit operates only when signalled to commence the operation, after the data has been prepared on the inputs of this part. Therefore, until such a request is produced, this part of the circuit does not consume any power at all.

**High modularity** Synchronous circuits are subject to precise synchronisation between the modules comprising them. Redesigning of any module requires meeting heavy restrictions on the execution times to ensure the correct synchronisation.

Any part of an asynchronous circuit can be redesigned at will. The new module must, of course, conform to the same interface protocol as the module that is being replaced. However, the speed at which the new module operates is irrelevant allowing easy upgrading of asynchronous circuits.

Reduced EMI Electro-magnetic emission generated by synchronous circuits causes interference with other equipment. Much of this interference is attributed to the clock signal which produces a steady peak in the spectrum on the frequency at which the transistors are switched.

Figure 1.1: Overall design process.

The transistor switching frequency in an asynchronous circuit depends on the data which is being processed by the circuit. Thus the spectrum is smoother and the peak values are lower.

#### 1.2 Design Cycle

The work presented in this thesis follows a well established circuit design path. The overall design process is illustrated in Figure 1.1.

At the first stage of the design process a designer's idea is expressed as a high-level specification of the future circuit. This specification is then checked for correctness, i.e. that the specification behaves according to the designer's requirements.

At the next stage, the high-level description is transformed into a low-level specification of the circuit; this low-level specification now includes signals which will implement the circuit. At this stage the specification is again checked for correctness. This time the requirements also include conditions related to the binary nature of the circuit implementation.

Once verified, the specification is submitted to the synthesis procedure which produces a set of boolean functions, one for each output signal. The synthesis procedure deals with such things as optimisation of the boolean logic functions and the technology mapping (implementing the circuit using a particular type of gates).

If the synthesis procedure uses some formal method and is automated, then there is no need to verify the implementation. However, many designers still use ad hoc techniques to produce an implementation from a high-level "blackboard" specification. In this case, the implementation needs to be verified. To do so, the model of the implementation is composed with the model of the environment obtained from the initial specification. The composed model is then verified for correctness. This process is somewhat similar to the debugging process in software development.

The third stage deals with the actual physical production of the circuit. This stage includes placing and routing of the circuit elements on the actual silicon. A laid out circuit is sent to

the manufacturing process.

At the last stage, the manufactured circuits are tested for the absence of faults. The testing procedure usually targets faults which could be introduced during the manufacturing of the chip. In order to do so, test sequences are required which consist of the sequences of input changes along with the outputs' checkpoints. These are generated using the low-level specification and the implementation produced by the synthesis process.

The process outlined above has been widely accepted for the design of asynchronous circuits. It is common to employ some formal model, such as Petri nets or process algebras, in the asynchronous circuit design. A variety of analysis methods can be used for reasoning about the behavioural properties of circuit models. A growing body of current research is aimed at the efficient automation of the design process; this works forms a part of this research.

#### 1.3 Position and Contributions of This Work

The main objective of this work is to demonstrate the application of the partial order approach in the design of asynchronous circuits. Unlike the state graph approach, this method represents the concurrency of an asynchronous system in its true form. Thus in many cases the exponential state explosion, usually associated with the state graph approach, is avoided.

This work tackles three major problems in the asynchronous circuit design:

- Specification verification, where the general Petri net (PN) unfolding technique is adapted for the verification of PN and/or Signal Transition Graph (STG) models of the "would-be-circuits".

- Implementation verification, where a PN or STG model is constructed for an already designed circuit and then this model is verified along with the model of the circuit's environment.

- Boolean logic synthesis, where the boolean logic implementation is obtained from the STG-unfolding segment instead of constructing the state graph.

This work proposes an automated approach which takes a specification of an asynchronous circuit in the form of an STG, verifies the specification and, in the case of successful verification, produces an implementation in the form of boolean logic equations. If the specification failed to pass the verification stage, the offending behaviour is reported and the specification can be corrected. In addition, techniques proposed in this work can be used for verification of existing circuits. The main contributions of this work are as follows:

- The existing PN-unfolding method, suggested by McMillan, is examined and adapted for the verification of relations between transitions of the original PN. The problem of redundancy in the truncated PN-unfolding is approached. A new termination condition is suggested for a wide class of non-autoconcurrent PNs. This condition avoids construction of redundant copies of the transition instances in the unfolding, which results in gains in speed and size of the segment.

- New algorithms, based on the PN-unfolding segment method, are suggested for the verification of the behavioural properties of asynchronous circuits and systems. The

verification of these properties allows the designer to find errors in the design long before the implementation stage is reached.

- A new concept of the Full State Graph (FSG) is introduced, which adequately captures the behaviour of an arbitrary STG. A partial order based approach for the FSG analysis, called the STG-unfolding segment, is suggested. This method is an extension of the PN-unfolding segment approach to STG analysis and takes into account the signal interpretation of transitions in an STG.

- A new method for the automated synthesis of asynchronous circuits from STGs is suggested. This method identifies fragments of the STG-unfolding segment from which the boolean logic implementation is obtained for each signal. In addition, the new synthesis method employs an approximation technique which uses the structural information available from the segment.

- A new algorithm which applies the unfolding technique to contextual nets is proposed. This algorithm takes advantage of contextual dependency and demonstrates significant savings in time and space compared to the analysis of PN models of existing circuits.

- An algorithm is suggested for obtaining a better variable ordering for the analysis and synthesis methods which use Binary Decision Diagrams for the representation of state space.

Results obtained in the course of this research also contributed to works on verification of STGs [76, 77] and synthesis of speed-independent circuits from their STG specifications [80, 81]. In addition, the methods and approaches developed here were used to explore the analysis of timed models [78] and for the analysis of realistic examples of a microprocessor [75] and a communication mechanism [79].

This work leaves out such areas of the asynchronous circuit design process as testing and technology mapping. It does, however, lay the basis for future research in these areas and demonstrates that the partial order methods achieve results which compare favourably to those of existing powerful methods.

### 1.4 Organisation of Thesis

This thesis is organised as follows:

- Chapter 2 briefly outlines the research work done in the area of asynchronous circuit design.

- Chapter 3 introduces Petri nets (PNs) and describes methods for their analysis. This chapter also introduces Signal Transition Graphs (STGs) which are used for the specification of asynchronous circuits.

- Chapter 4 suggests a new method for the analysis of PNs based on McMillan's truncated unfolding. It presents a comparison between the original version of the PN-unfolding algorithms and the suggested experimental technique and illustrates the performance of

the approach on real life examples. The new method is also applied to the analysis of PN models of asynchronous circuits.

- Chapter 5 introduces the Full State Graph (FSG) and proposes the application of the new unfolding technique to the analysis of STGs. The suggested STG-unfolding segment analysis is applied to a set of existing benchmarks and its performance is discussed.

- Chapter 6 describes the application of the STG-unfolding segment to the synthesis of asynchronous circuits. The experimental results demonstrate that the new synthesis method extends the application of automated synthesis procedures.

- Chapter 7 illustrates how the application of the unfolding technique may assist in solving

other problems in asynchronous circuit design. The first problem is related to the

analysis of PNs with self-loops, which are often found in PN models of circuits, and deals

with Contextual nets; the second application of PN-unfolding deals with the variable

ordering for Binary Decision Diagrams.

- Chapter 8 concludes the thesis, summarising the results presented in this work and outlining the areas for future research.

# Chapter 2

## Previous and Related Work

The purpose of this chapter is to give a brief account of the work done to date on asynchronous circuit design.

An asynchronous circuit can be viewed as a set of gates interconnected with wires so that no two outputs can be connected together. Asynchronous circuits assume that there is no clock signal. However, the behaviour of the circuit components cannot be considered without taking the timing domain into account. Every event that takes place in the circuit can be characterised by the time it has taken and the place where this event occurred. In addition, several signalling protocols exist which ensure that the signal levels are interpreted correctly. The interpretation of the time domain and the signalling protocols lead to the two taxonomies that define existing design methodologies:

- Delay taxonomy, which defines the model chosen to represent the duration of every event occurring in the circuit; and

- Protocol taxonomy, which defines the method that is used to pass data from one part of the circuit to another.

Combinations of different types of delays and protocols produced a variety of different design methodologies for asynchronous circuits. Each methodology established certain requirements on the environment in which a circuit operates. It was soon realised that asynchronous circuits were too complex to be designed by hand. This called for the use of formal methods in asynchronous design.

The goal of formal methods application is, on one hand, to provide the designer with a somewhat unified way of describing the desired behaviour. On the other hand, formal methods allow reasoning about the global properties of the behaviour, e.g. establishing if a system ever reaches a certain state. An attempt to find a rarely encountered state by means of conventional simulation may take a long time and cannot be done with 100% certainty.

First this chapter examines the delay and the protocol taxonomies. The discussion about taxonomies is followed by a brief account of the existing methodologies and the formal models and methods used in asynchronous circuit design.

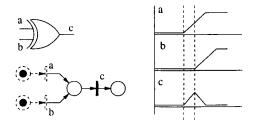

Figure 2.1: Illustration of pure (a) and inertial (b) delay models.

#### 2.1 Asynchronous Circuits Taxonomies

#### 2.1.1 Delay taxonomy

The delay taxonomy draws a distinction between different models of delays taking into account their duration and behaviour.

Bounded and unbounded delays One of the major properties of the delay is its duration. A delay is said to be bounded if its upper and lower bounds are known. Alternatively, a delay is called unbounded if its upper and lower bounds are unknown, however it is known that the delay is *finite* and positive.

Pure and inertial delays Another characteristic of the delay is its ability to propagate signals. A delay is called **pure** if a change of any length in the input signal causes a change on the output after a certain amount of time. A delay is called **inertial** if the changes in the input signals are not propagated if they are shorter than a certain length. The difference between these two delay models is illustrated in Figure 2.1. The pure delay element in Figure 2.1(a) simply delays the changes in the output signal, whereas the inertial delay element (Figure 2.1(b)) filters out short pulses but delays the the long ones.

**Delay cite** Any circuit can be viewed as a set of gates interconnected by wires. The cite of the delay in a circuit is crucial to the design methodology. A delay is called **gate delay** if it occurs inside a gate, reflecting the time taken to compute the output signal change. A delay is called **wire delay** if it happens in the wire and reflects the wire propagation times of the signals.

#### 2.1.2 Protocol signalling taxonomy

The protocol signalling taxonomy draws a distinction between the ways in which data is transferred from one part of the circuit to another.

Dual-rail and bundled data signalling The absence of the clock means that there is no way to fix a moment in time at which the signal level can be sampled. For example, registering a low level of some signal twice may mean two sequential 0s. Alternatively, it may be a 0 followed by a 1, but the second value was sampled too early, i.e. before the transition was completed.

Figure 2.2: Illustration of dual-rail (a) and bundled data (b) signalling.

Figure 2.3: Illustration of four-phase (a) and two-phase (b) protocols.

To ensure the correct data transmission between two parts of the system (a sender and a receiver) a dual-rail data signalling protocol was introduced, illustrated in Figure 2.2(a). Each bit uses two wires, e.g. D0 and D1 with the appropriate encoding using combinations of high an low levels of both wires. One combination, e.g. 01 (D1D0), represents a "0" and a complimentary one, 10, represents a "1". One of the combinations 00 or 11 is used as a spacer, a special symbol which separate sequential bits. The fourth combination is considered to be illegal and must never appear. A single wire is used in the reverse direction to indicate that the receiver has registered the changes on all data wires and is ready to accept the next piece of data.

A bundled data signalling protocol assumes that each data bit is represented by one wire, but there exists a pair of request and acknowledgement wires between the sender and the receiver. This protocol is illustrated in Figure 2.2(b). As soon as the sender sets the levels on the data wires, it sends a request signal. Upon receiving the request signal, the receiver processes the data on its inputs and returns an acknowledgement after which the system enters the next cycle. An important assumption in this protocol is that the propagation delay in the request wire must be greater than the longest delay in any of the data wires.

Four-phase and two-phase signalling This distinction comes from the fact that the signals have two levels. A four-phase signalling protocol assumes that only one edge (change of the signal from high to low or vice versa) indicates an occurrence of some event. Therefore,

Figure 2.4: Fundamental mode synchronous (a) and asynchronous (b) circuits.

there exists a sequence of changes in the signal levels, called the "return-to-zero" phase, when the signals are reset to their original levels. Since only one level of the signal represents an event, this protocol is also called *level signalling* protocol. This protocol is illustrated in Figure 2.3(a).

In the **two-phase** signalling protocol, every change in the signal level indicates an event. This protocol is illustrated in Figure 2.3(b). In this protocol there is no phase resetting the signals to their original levels.

#### 2.2 Design Methodologies

#### 2.2.1 Huffman Fundamental Mode Circuits

The operation of an asynchronous circuit in the Huffman fundamental mode [31] is similar to the operation of a circuit in the synchronous mode (see Figure 2.4(a)). The Huffman fundamental mode assumes that the circuit consists of a combinational logic block and a set of feedback wires. However, these circuits assume that a bounded delay element is inserted instead of the latches breaking the feedback wires (Figure 2.4(b)). The changes in the outputs appear at the inputs of the circuit separated in time, thus giving the necessary delay for settling of the signals inside the combinational logic block. Huffman fundamental mode circuits also require that only one input changes at a time.

The circuit is specified using a *Finite State Machine* (FSM) flow table [89] which is then binary encoded and implemented. The flow table specification is usually minimised to reduce the complexity of the encoding algorithms and to reduce the number of the variables needed to encode the states of the FSM.

The implementation in the Huffman mode must be free from critical races [90]. A race is a simultaneous change of more than one signal during a transition from one state of the system to another. A race is called **critical** if the behaviour of the circuit depends on the order in which the racing signals change.

The operation in the Huffman fundamental mode imposes very strict requirements on the implementation. A number of approaches were suggested to relax these restrictions. They are based on the observation that not all multiple changes in the input signals lead to critical races; hence the other two modes can be considered: multiple input change (MIC) mode, where several inputs can change at the same time; and unrestricted input change (UIC) mode,

Figure 2.5: Illustration of Delay-Insensitive (a) and Speed-Independent (b) circuits.

where no restrictions are imposed on the input changes whatsoever. However, designing MIC and UIC circuits proved to be complex. A solution was suggested in the form of the *burst mode* circuits [57] which assume that:

- the inputs can change in bursts (sets of simultaneously changing signals);

- no burst can be a subset of another burst.

Furthermore, the burst mode can be extended into the extended burst mode [104] which allows don't-cares on the inputs and condition signals. The former allows an input to choose non-deterministically whether or not its value changes in a particular burst. The latter introduces special signals whose levels determine possible advancements in the behaviour of the FSM. There exists a variety of other methodologies implementing fundamental mode circuits such as locally clocked [59, 60] and 3-D state machines [106, 105].

#### 2.2.2 Delay-Insensitive Circuits

Delay-Insensitive (DI) circuits assume that both gate and wire delays are unbounded. The general idea is shown in Figure 2.5(a). As a result of this assumption these circuits are the most robust implementation with respect to the delay changes. Indeed, a DI circuit is insensitive to the variations of the delay values due to the working conditions of the implementation. If a signal gets stuck permanently at a particular level, so called *stuck-at-fault*, then the circuit will stop functioning rather than producing a spurious result, i.e. it will fail safely.

Very few circuits can be designed so that they are completely DI. Therefore, a DI implementation is usually obtained from modules whose behaviour is considered to be DI on their interfaces.

An implementation is usually obtained from a specification in a high-level programming language such as Communicating Sequential Processes (CSP) [30] and CSP-like HDL [45], Tangram [4], trace theory expressions [20] or DI algebras [33]. The known examples of DI circuits include asynchronous microprocessors [43, 9] and Philips error correction chip [6, 5].

#### 2.2.3 Speed-Independent Circuits

The research into Speed-Independent (SI) circuits was pioneered by Muller [53]. SI circuits assume that the gate delay is unbounded whilst the wire delay is negligible with respect to the date delay. An illustration of the delay cite in an SI circuit is given in Figure 2.5(b). Muller introduced a formal model, called *State Transition Diagram* (STD), for representing

the behaviour of asynchronous circuits. Each state of an STD is a binary vector representing the signal values. States are connected by the arcs labelled with signal transitions (only one label per arc is allowed). A signal is said to be *stable* in a particular state if it is equal to the value computed by the corresponding logic function under the values given by the vector; otherwise it is called *excited*. Muller showed that the circuit's behaviour can be equivalently described using STDs.

Speed-independence is closely related to the notion of semi-modularity. A circuit is said to be **semi-modular** if every excited signal becomes stable due to the change of its value, i.e. the signal's excitation cannot be removed by another signal. Muller showed that any semi-modular circuit is speed-independent. The synthesis procedure for SI circuits takes an STD as the specification of the future circuit and produces an implementation in the form of boolean logic equations for the circuit's gates. Varshavsky *et. al.* [93] showed that any semi-modular STD can be implemented as an SI circuit using a restricted set of gates: n-input AND-OR-NOT gates (that are able to implement an arbitrary sum-of-product function) or 2-input NAND and 2-input NOR gates with the fanout limited to two gates. Recent works [3, 2] established the conditions for an SI implementation using n-input NAND gates and a Muller C-element.

Specifying an SI circuit in terms of an STD can sometimes be a problem due to the high degree of concurrency. A number of formal models were suggested to be used for specification of SI circuits, e.g. Trace theory [19], Change Diagrams [35] and Signal (Transition) Graphs [73, 13]. These models specify the behaviour in a compact form and then automatically verify and/or synthesise the SI implementation. A more detailed discussion of the existing methods is given in the next section.

Quasi Delay-Insensitive (QDI) circuits were suggested in [44] and assume the unbounded gate and wire delay models, however, they are enriched with isochronic forks. An isochronic fork is a forking wire where the difference between the delays of the branches is negligible. The isochronic fork definition does not require the delays between all destinations to be negligible. Thus it is possible to specify an isochronic fork in which the difference between the delays is negligible only for a subset of destinations. QDI circuits with this form of the isochronic fork are not equivalent to SI circuits. However, if all destinations are isochronic, which is usually the case, QDI circuits are equivalent to SI circuits if the wire delay is considered as a part of the gate delay generating the signal.

#### 2.2.4 Micropipelines

Micropipelines were suggested by I. Sutherland in [88]. The general idea is illustrated in Figure 2.6. The backbone of a micropipeline consists of Muller C-elements and Capture-Pass latches. The sender generates a request when the data is ready to be sent down the pipeline. The first stage is ready to accept new data if the previous piece of data has already been latched by the next stage. If ready, the first stage latches the new data and sends a signal acknowledging this latching to the sender. At the same time the first stage sends a request to the next stage to pass on the portion of data held in the latch. Each stage of the micropipeline operates in a similar way regarding the preceding stage as a sender. At the other end of the micropipeline the receiver accepts the arriving data and acknowledges every

Figure 2.6: Sutherland micropipelines.

portion. In addition, each stage may contain a combinational logic block which performs necessary computations on the data. The control circuitry of the micropipelines is delay insensitive. Introducing the data path requires careful compensation for the propagation time of the signals through the data wires and, where necessary, through the combinational logic.

Micropipelines use bundled data protocol with either two- or four-phase signalling. They have proved to be a powerful design methodology; well-known examples of the micropipelined systems include a FIFO controller [71] and the AMULET microprocessor [24, 23].

#### 2.3 Formal Models

The goal of this section is to give a brief overview of the formal methods employed in asynchronous circuit design methodologies. The motivation behind using formal models in circuit design is to ensure that the implementation is correct. In particular, the implementation must produce the required output signals in response to the input stimuli. Furthermore, an asynchronous circuit must operate without hazards. A hazard is an unspecified change of the signal, e.g. a spike. In synchronous design, a spike may occur during the settling period. This spike does not affect the correctness of the implementation but rather its power consumption. In an asynchronous circuit, there is no way to distinguish a spurious spike from a sequence of signal changes. Thus this spike may be registered by a gate and cause the circuit to malfunction. Interested readers are referred to [87, 41] for a thorough review of hazards.

State graph based models In the state graph based methods the specification is given in terms of a finite automaton describing all possible states of the system. If the system has many events that can happen concurrently, then the total number of states in the system may be prohibitively large.

The problem with the size of the specification comes from the fact that any set of concurrent events produces an exponential number of intermediate states, although the state reached at the end is always the same. The use of the burst mode FSM specifications allows a reduction in the size of the specification. In effect, a burst of input and/or output signals captures all interleavings which would be possible had these signals been allowed to change freely. The penalty paid for such a reduction is the requirement for the difference between the moments of signal changes in one burst to be negligible.

The state based models offer a direct route for obtaining the circuit implementations. The

states are encoded using binary codes and the truth tables are obtained in a straightforward manner.

Trace based models The trace theory was suggested for the automated verification of SI circuits by Dill [19]. The behaviour of each element of the circuit is described using the trace theory primitives. In addition, the desired behaviour is also specified in terms of trace theory. An element is said to *conform* to its specification if its observable behaviour is equivalent to that of its specification. This suggests the hierarchical verification where an element is substituted with its specification which is often much simpler. This method, however, is more applicable to the verification of the already designed circuits, i.e. the designer must take a trial and error approach if he wishes to implement a particular specification.

Ebergen [20] suggested an approach for the synthesis of DI circuits which is also based on trace theory. This approach uses a top-down design methodology. A future circuit is specified using the trace theory description of its input/output behaviour. The specification is verified for delay insensitivity. Alternatively the specification can be constructed using a restricted grammar which can only produce a DI circuit. Once a circuit is specified it is generated automatically using syntax-directed translation and a predefined table of the implementation primitives.

Josephs [34] takes a similar approach suggesting an algebraic solution to the synthesis of asynchronous circuits. Using a special DI algebra the specification is transformed to the level of the implementation primitives.

The trace based model provides a powerful approach to the automated synthesis of asynchronous circuits. The circuits are hazard free by construction. However, this model does not have provision for the verification of such important properties as a deadlock, i.e. a state from which no further advancement of the system can be made. In addition, implementations produced by a syntax-driven synthesis process are often far from optimal.

High-level description languages High-level description languages specify the system in a similar way to the conventional programming languages. Among the most well-known are Martin's [44] and Brunvand's [10, 8] compilation systems and van Berkel's Tangram language [7, 4]. Most of these methods are based on the theory of Communicating Sequential Processes [30] using a *channel* as the primary communication mechanism between subsystems.

Martin's compilation system used a CSP-like hardware description language whereas van Berkel suggested a completely new language. The approach is, however, similar. The system is specified as a composition of the communicating processes. Once the system is specified, each process is decomposed into simpler processes. At the low level, the communication and synchronisation commands are expanded into a four-phase handshake protocol. The final circuit is obtained after the re-shuffling of transitions and the insertion of state signals to eliminate the ambiguities.

Brunvand's approach is based on a subset of Occam. Similar to the techniques described above, the system is specified as a program. Each statement has a corresponding hardware primitive. The program is directly translated into a set of interconnected primitives. The resulting circuit is often very poor with respect to the area size and the performance. Similar to programming language compilers, this approach uses an optimisation to increase the

performance and the area results. The optimisation, called *peephole optimisation*, is based on detecting those parts of the circuit which can be safely substituted by an already optimised fragment with an equivalent behaviour.

Event based models The use of event-based models in asynchronous circuit design was prompted by the difficulties with the state space size for complex behaviours. Instead of the complete enumeration of all states of the system, an event-based formal model specifies events and relations between them. A suitable formal model for this was found in the form of Petri nets (PNs)<sup>1</sup> [65, 67]. PNs provide a simple graphical description of the system with an easy representation of concurrent events or a choice between alternative events. In addition, the set of reachable states can be obtained from a PN using a straightforward algorithm.

PNs do not make any assumptions about the time at which an event occurs. This makes them attractive for asynchronous circuit design. Patil [63] suggested a syntax directed method for the translation of PN specifications of asynchronous systems into implementations.

A number of works [51, 86, 54] use *I-nets* for the specification of asynchronous circuits. An I-net represents the interface behaviour of a circuit using events associated with its inputs and outputs. The initial state of the system is captured by the initial marking. After the specification is completed, an *Interface State Graph* (ISG) is built for this I-net which represents all reachable states of the system. After that an *Encoded Interface State Graph* (EISG) is constructed which takes into account the binary interpretation of the signals on the circuit's interface. The EISG is then used for the generation of truth tables and building an implementation either in the Huffman or burst mode.

Signal Transition Graphs (STGs) were suggested independently in [73] and [13] for the specification, verification and synthesis of self-timed circuits. An STG is a PN where each transition is labelled with a directed signal transition (up or down). An STG specification serves as a low-level description of the future circuit's behaviour. The synthesis process attempts to restore an STD from an STG by building the reachability graph representing the set of reachable state of the underlying PN, similar to I-nets. Each state of the obtained reachability graph is assigned with a binary code. Once the binary code assignment is completed the implementation is generated by deriving the truth tables.

A model closely related to the STG model, called *Change Diagrams* (CDs), was suggested in [35]. CDs have two distinctive features. Firstly, they have provision for non-repeatable events using disengagable arcs. Secondly, they allow OR-causality, i.e. they are able to model an event whose happening is induced by any of its causes. A set of algorithms for the verification and automated synthesis of SI circuits was suggested in [35]. A notable feature of these algorithms is that they use the unfolding process to reason about the properties of the specification. Unfortunately, CDs cannot model specifications with non-deterministic choice.

The methods discussed above are geared for the automated verification and generation of implementations from a PN-based specification. A number of works [47, 101] also examined the verification of the already designed circuits. These approaches usually build fragments of PNs for each gate which are then composed together according to the gate net list. The resulting PN is composed with the PN model of the environment and it is verified for errors

<sup>&</sup>lt;sup>1</sup>See next chapter for definitions from the Petri net theory.

in design and/or hazards.

#### 2.4 Design of Speed-Independent Circuits

SI circuits have a special place in the asynchronous circuit design. Operational conditions for SI circuits require less strict assumptions than those for fundamental mode circuits. The design process of a fundamental mode circuit is similar to the design process of a synchronous circuit. This, on one hand, makes it easier for a synchronous circuit designer to understand the new design methodology. On the other hand, an accurate delay estimation is required for the correct operation of the circuit. The delay estimation must take into account all possible conditions affecting the circuit. SI circuits are built to operate independently of the gate delay. Thus, if a circuit is SI, then this circuit will operate correctly under any environmental conditions that may affect the gate delay. This also makes SI circuits very robust to the manufacturing technology parameters. Therefore, an SI design can be ported to different technologies without major modifications.

SI circuits have a gate-level degree of granularity as opposed to the module level of DI circuits. Only a few elements can be designed to be DI at the gate level. The module-level granularity is very coarse and usually has a negative impact on the performance of a circuit. Furthermore, SI circuits can be built using standard gate libraries, and, therefore, existing layout tools can be used for their low-level design.

It has also been shown that SI circuits are self-checking with respect to stuck-at-faults on gate outputs. That is, if a fault occurs, a circuit would stop rather than produce incorrect or unspecified outputs. Using this property, it is easy to design an autonomous fault-correction mechanism. Thus, if a circuit fails, the fault-correction mechanism will detect the fault place and correct the fault by, for example, replacing the faulty module with a reserved one.

The SI circuit design supports easy decomposition. A complex design can be decomposed into smaller subsystems with a well defined set of interface signals. In many cases, the environment model for a subsystem, which includes only the interface signals, is much smaller than the model for the rest of the system. Thus each subsystem can be designed separately using tools which cannot cope with the whole system. Furthermore, any subsystem can be later re-designed at will without the need for re-design of the rest of the system.

From the very beginning the design of SI circuits was associated with formal methods. Formal verification methods, unlike traditional simulation, can provably show that the circuit's behaviour is correct, or produce a sequence of events leading to the erroneous behaviour.

Behaviours described by PNs have a striking resemblance to asynchronous systems. The fundamental notions of the states and transitions between the states are inherent in PNs. This has prompted their application in SI circuit design. The graphical representation of the behaviour in the form of a PN (or STG) is easier to understand by circuit designers than an algebraic or trace model. The body of existing PN research is enormous; many results from PN theory have been applied to SI circuit design.

#### 2.5 Conclusions

This chapter briefly outlined the main existing methodologies in the asynchronous circuit design. Examples of the reported designs include almost every conceivable combination of delay models, signalling protocols, formal models and their analysis methods. A number of works, e.g. [29, 41], provide a more extensive introduction and comparison of most common approaches. This chapter also described in more detail the pros and cons of SI circuit design which is the main subject of this work.

## Chapter 3

## Petri Nets and Related Formalisms

This chapter introduces Petri nets (PNs) and their related models, such as Labelled Petri nets (LPNs) and Signal Transition Graphs (STGs). Properties of the behaviour described by each formalism are defined and discussed. These properties are related to the properties of the correct behaviour of asynchronous circuits and systems. The existing methods for the behavioural analysis for each model are also outlined.

#### 3.1 Petri Nets

This section defines a Petri net and introduces the notation used throughout the thesis. Interested readers may wish to refer to Peterson [65] and Reisig [67] for more extensive introductions to Petri net theory.

**Definition 3.1.1** A Petri net (PN) is tuple  $N = \langle P, T, F \rangle$  where

- P is a set of places, and

- T is a set of transitions such that  $P \cap T = \emptyset$ ; and

- -F is a flow relation between places and transitions,  $F \subseteq P \times T \cup T \times P$ .

Both P and T are assumed to be finite unless stated otherwise.

Graphically, a PN is usually represented in the form of a graph with two types of vertices: circles, which correspond to places, and bars (or boxes), which correspond to transitions. The flow relation F is represented by directed edges (arcs) of the graph. A bi-directional arc is used sometimes as a shorthand for a pair of arcs going in the opposite directions between a particular pair of a place and a transition.

Each element  $x \in P \cup T$  of a PN N has a set of input elements (which are connected with x by the arcs going to x) and a set of output elements (which are connected with x by the arcs originating from x). These sets of PN are called *pre-set* and *post-set* of x respectively and are defined as follows:

**Definition 3.1.2** The sets  $\bullet x$  and  $x \bullet$  are called *pre-set and post-set* of  $x \in P \cup T$  respectively iff:

$$- \bullet x = \{ y \in P \cup T | (y, x) \in F \}$$

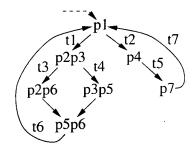

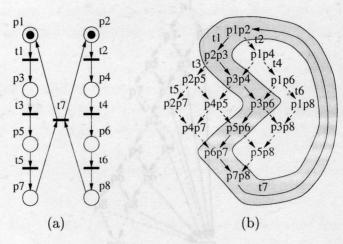

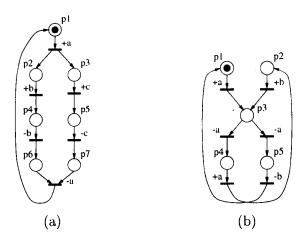

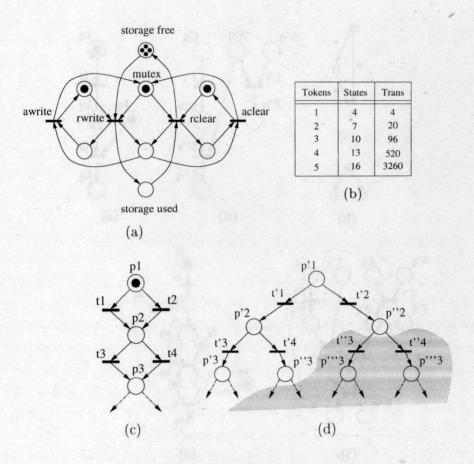

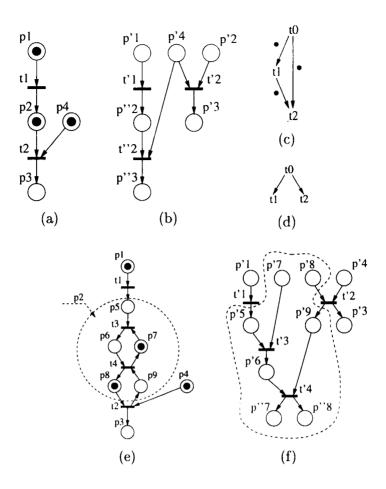

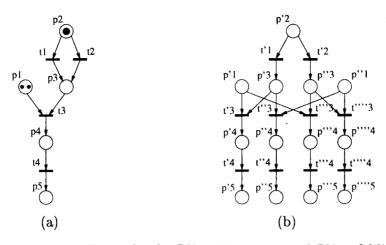

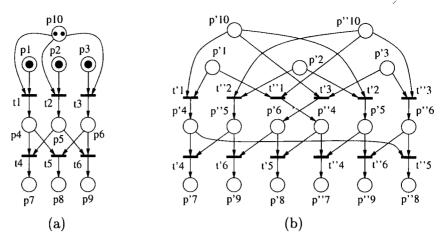

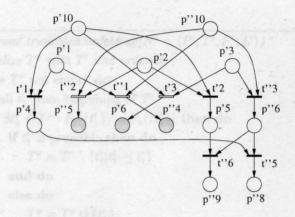

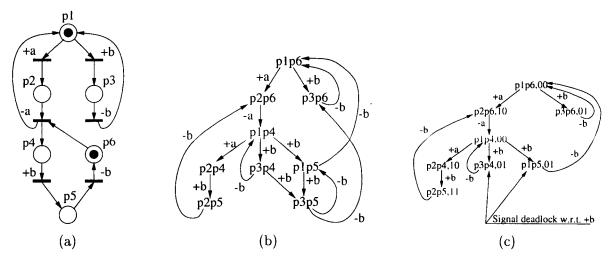

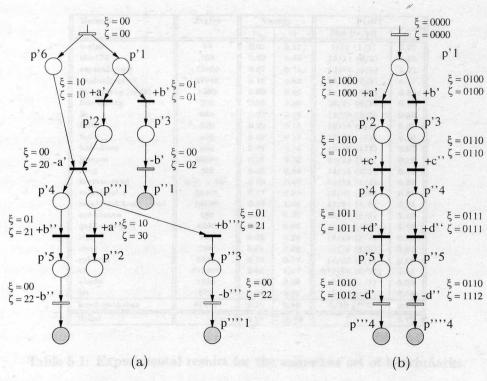

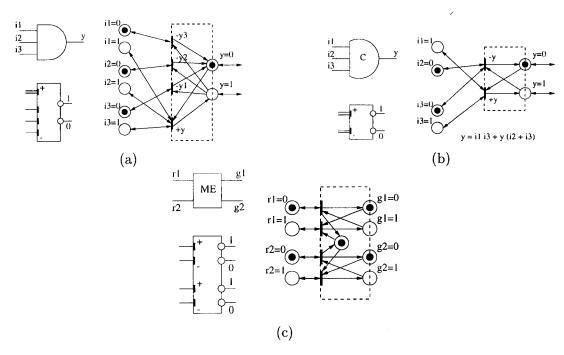

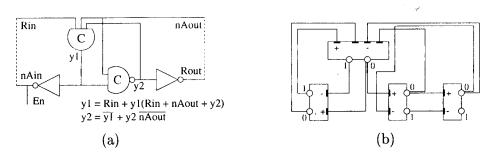

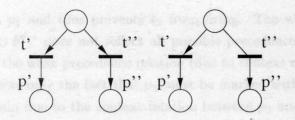

Figure 3.1: Examples of different classes of PNs: (a) SMPN, (b) MGPN, (c) FCPN and EFCPN (d).

$$-x \bullet = \{ y \in P \cup T | (x, y) \in F \}$$

The notation  $x_1 \bullet x_2$  means that  $x_1 \bullet \cap \bullet x_2 \neq \emptyset$ .

In what follows, it is assumed that  $\bullet t \neq \emptyset \neq t \bullet$ , for every transition  $t \in T$ .

Structural properties of PNs define structural classes of PNs; these classes are identified below.

**Definition 3.1.3** A state machine PN (SMPN) is a PN N such that  $\forall t_i \in T : |\bullet t_i| = 1$  and  $|t_i \bullet| = 1$ .

In other words, every transition in a SMPN has one input and one output place. An example of a SMPN is shown in Figure 3.1(a).

**Definition 3.1.4** A marked graph PN (MGPN) is a PN N such that  $\forall p_i \in P : |\bullet p_i| = 1$  and  $|p_i \bullet| = 1$ .

Each place in a MGPN may have at most one input and one output transition. An example of a MGPN is shown in Figure 3.1(b).

A place  $p_i$  such that  $|p_i \bullet| \ge 2$  is called a *conflict place* and the transitions that are in  $p_i \bullet$  are said to be in *structural conflict*. This is defined below:

**Definition 3.1.5** Two transitions  $t_i \in T$  and  $t_j \in T$  of a PN N are said to be in *structural conflict* iff  $\bullet t_i \cap \bullet t_j \neq \emptyset$ .

The structural conflict between two different transitions  $t_i$  and  $t_j$  is denoted as  $t_i \# t_j$ . No two transitions of MGPN can be in structural conflict.

**Definition 3.1.6** A free choice PN (FCPN) is a PN N such that for any  $p_i \in P$  with  $|p_i \bullet| \ge 2$  the following is true:  $\forall t_i \in p_i \bullet : |\bullet t_i| = 1$ .

**Definition 3.1.7** An extended free choice PN (EFCPN) is a PN N such that for any  $p_i \in P$  the following is true:  $\forall t_i, t_j \in p_i \bullet : \bullet t_i = \bullet t_j$ .

Any two conflicting transitions in FCPN have only one input place. EFCPNs are an extension of FCPNs allowing the conflicting transitions to have more than one input place but, at the same time, requiring that this set of input places is identical for these transitions. Examples of FCPN and EFCPN are shown in Figures 3.1(c) and 3.1(d) respectively.

In order to convey the dynamic properties of the system a notion of PN marking is used. A subset of places P may be marked which is denoted on the graph by placing tokens (thick black dots) into the places. Formally, a marking is defined below.

**Definition 3.1.8** A marking of a PN N is a multiset M defined on P, i.e. it is a function  $M: P \to \{0, 1, 2, \ldots\}$ .

**Definition 3.1.9** A transition  $t_i$  is said to be *enabled* at a marking M iff  $\bullet t_i \subseteq M$ .

A transition which does not have all of its input places marked at a marking M is said to be disabled at this marking. An enabled transition may fire, changing the current marking of the PN. The new marking is calculated as follows:

$$M' = M \setminus \bullet t_i + t_i \bullet$$

.

This rule is called the PN firing rule. The firing of a transition  $t_i$  is denoted as:

$$M \stackrel{t_i}{\rightarrow} M'$$

.

Thus a transition of a PN can be associated with some event and its input and output places with pre- and post-conditions. When all its pre-conditions are fulfilled, the event occurs (transition fires) changing the state of the system by setting its post-conditions to TRUE. A dynamic system is usually described by its structure and some initial state from which the system progresses. In terms of PNs this is defined as a marked PN.

**Definition 3.1.10** A marked PN is a tuple  $N = \langle P, T, F, M_0 \rangle$  where  $M_0$  is an initial marking of the PN N.

From now on any PN in this thesis will be treated as a marked PN unless stated otherwise. Transitions of a PN start firing from its initial marking  $M_0$  and their firing may continue while there exists at least one enabled transition. A sequence of transitions such that:  $\sigma = M_1 \stackrel{t_1}{\to} M_2 \stackrel{t_2}{\to} M_3 \cdots$  is called a firing sequence from  $M_1$ . Obviously a transition  $t_i$  may

Figure 3.2: Example of an RG of a PN.

be included several times in one firing sequence. Each firing of this transition is called an  $instance^1$ . Given a marking  $M_1$  and a sequence  $\sigma$  it is easy to restore all visited markings by firing the transitions in the order of their instances in  $\sigma$ .

**Definition 3.1.11** A marking  $M_m$  is said to be reachable in a PN N from  $M_1$  iff there exists at least one firing sequence  $\sigma = M_1 \stackrel{t_1}{\to} M_2 \stackrel{t_2}{\to} \cdots \stackrel{t_{m-1}}{\to} M_m$ .

This is also denoted as:  $M_1 \stackrel{\sigma}{\to} M_m$ .

The set of all makings which are reachable from  $M_0$  is called the *reachability set* of a PN N. It is defined formally as follows:

**Definition 3.1.12** The set  $R = \{M_i \mid \exists \sigma : M_0 \xrightarrow{\sigma} M_i\}$  of markings of a PN N is called the reachability set of N.

Often, the reachability set of a PN is represented as a directed graph where vertices are labelled with reachable markings and the edges are labelled with transitions which change one marking to another. This graph is often referred in the literature (e.g. [65]) as the reachability graph (RG). An example of the RG for the PN from Figure 3.1(c) is shown in Figure 3.2. In order to avoid cluttering in the figures from here on, obvious labels of arcs which represent the same transition from different markings will be omitted, e.g. arcs between  $(p_2, p_3)$  and  $(p_3, p_5)$  and between  $(p_2, p_6)$  and  $(p_5, p_6)$  correspond to the firing of transition  $t_4$ . These arcs are drawn parallel to each other. The initial marking is indicated by a broken arrow.

The dynamic behaviour of a PN allows some transitions i) to fire in parallel or ii) to prevent each other from firing. This is captured in the notions of i) concurrency and ii) (dynamic) conflict.

**Definition 3.1.13** Two transitions  $t_i$  and  $t_j$  of a PN N are said to be *concurrent* iff there exists a reachable marking M at which both transitions are enabled and M contains the multiset  $\bullet t_i$  and  $\bullet t_j$ ; i.e.  $\bullet t_i + \bullet t_j \subseteq M$ .

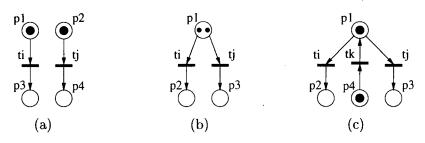

The fact that a particular marking M contains the sum of input places of both enabled transitions  $t_i$  and  $t_j$  means that transitions may fire *simultaneously* (as illustrated in Figure 3.3(a)) consuming tokens from their input places and producing tokens into their output places. Note that  $t_i$  and  $t_j$  may be in a structural conflict but they could still fire independently. If the number of tokens in the conflicting place(s) at M is sufficient for firing both

<sup>&</sup>lt;sup>1</sup>This notion will also be used later to refer to transitions and places in an unfolding of PN

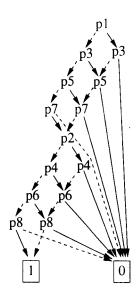

Figure 3.3: Illustration of relations between transitions: (a) concurrent, (b) structural conflict with concurrent transitions and (c) dynamic conflict.

$t_i$  and  $t_j$  simultaneously, then these two transitions are concurrent (see Figure 3.3(b)). Two concurrent transitions are denoted as:  $t_i||t_j$ .

The notion of concurrency can be further extended to represent the relation between places and places and transitions. Two places  $p_1$  and  $p_2$  of a PN are said to be concurrent if there exists a reachable marking M such that  $\{p_1, p_2\} \subseteq M$ , i.e.  $p_1$  and  $p_2$  can be simultaneously marked at some reachable marking M. Lastly, a place p is said to be concurrent to a transition t if there exists a reachable marking M such that  $\{p\} + \bullet t \subseteq M$ , i.e. token in place p remains untouched while transition t fires at M.

A special case is when  $\bullet t + \bullet t \subseteq M$ ; then transition t may fire simultaneously more than once. Such a transition is called **autoconcurrent**. For example, both  $t_i$  and  $t_j$  in Figure 3.3(b) are autoconcurrent.

**Definition 3.1.14** A PN N is said to be *non-autoconcurrent* if no transition is autoconcurrent at any reachable marking of N.

Non-autoconcurrency of events is one of the main requirements in asynchronous circuit specifications. Therefore, unless it is necessary to distinguish explicitly, all PNs in this work will be considered to be non-autoconcurrent.

**Definition 3.1.15** Transition  $t_i$  of a PN N is said to be in dynamic conflict with another transition  $t_j$  at a marking M iff both transitions are enabled at M and the firing of  $t_i$  disables  $t_j$ .

The notion of dynamic conflict is asymmetric, i.e. transition  $t_i$  may be disabling  $t_j$  whereas the firing of  $t_j$  does not disable  $t_i$ . A transition  $t_i$  in conflict with  $t_j$  is denoted as  $t_i \# t_j$ . If the dynamic conflict is symmetric then, abusing the notation, it is denoted as  $t_i \# t_j$ . A symmetric conflict is illustrated in Figure 3.3(c), transitions  $t_i$  and  $t_j$  are in conflict at the marking  $(p_1, p_4)$ . Furthermore,  $t_i$  and  $t_j$  may be in dynamic conflict at M but the firing of a third transition  $t_k$  may change the marking to M' at which  $t_i$  and  $t_j$  will be concurrent, e.g. transitions  $t_i$  and  $t_j$  at the marking  $(p_1, p_1)$  in Figure 3.3(c).

Recall the classification of PNs according to their structural properties. It follows from the definition of MGPN that no two transitions in a MGPN can be in dynamic or structural conflict. The notion of dynamic conflict is stronger than the notion of structural conflict. If two transitions are in dynamic conflict, then they are always in structural conflict. The notion of dynamic conflict is used to identify another class of PNs.

Figure 3.4: Illustration of UCPN.

Figure 3.5: Example of an LPN.

**Definition 3.1.16** A unique choice PN (UCPN) is a PN N such that for any two transitions  $t_i$  and  $t_j$  in dynamic conflict the following is true:  $\bullet t_i = \bullet t_j$ .

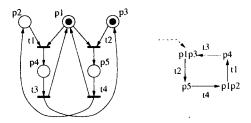

An example of a UCPN is shown in Figure 3.4 with its reachability graph on the right. As it can be seen, transitions  $t_1$  and  $t_2$  are never enabled together although they are in structural conflict.

Each transition in a PN is unique. However, it is often impossible to describe a system with only one transition corresponding to each action of the system. Therefore, the notion of a *Labelled PN* is introduced below.

**Definition 3.1.17** A Labelled PN (LPN) is a tuple  $N^L = \langle N, A, L \rangle$  where

- -N is a marked PN,

- A is a set of actions, and

- $-L: T \to A$  is a labelling function which associates each transition of the PN N with some action from A.

Henceforth, N will be used instead of  $N^L$  to represent an LPN unless it causes confusion.

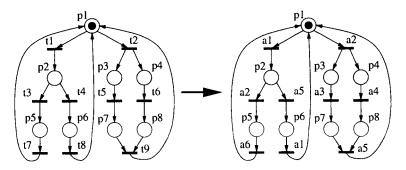

It is sometimes convenient to allow A to include a special action  $\gamma$  which is called *silent* action and does not cause any visible effect. An example of an LPN is given in Figure 3.5.

It is also possible to define the notions of concurrency and conflict between actions of an LPN.