# Architectural Soup:

A proposed very general purpose computer

## Ian Weaver

Ph.D. Thesis

University of Newcastle upon Tyne

September 1989

# BEST COPY

# AVAILABLE

Variable print quality

#### ABSTRACT

This thesis is concerned with architecture for long term general purpose computers. The work is based on current trends in machine architecture and technology. Projections from these generated "Architectural Soups". An Architectural Soup has the potential to emulate many different machine architectures. The characteristics of this class of machine are, three dimensional, simple cells and a simple communications topology, which can be reconfigured at a very low level. This thesis aims to show potential usefulness and viability of machines with such capability.

Methods of programming are considered, and important design issues are investigated. A specific implementation architecture is described and illustrated through simulation. An assessment is made of the architecture and of the simulator used. In addition, the implementation architecture is used as the basis for a VLSI design, which shows the simplicity of a Soup cell, and provides estimates of the possible number of cells in future machines.

#### ACKNOWLEDGEMENTS

Although this work is declared as mine, I am indebted to many people for their assistance and opinion. I particularly wish to acknowledge the considerable help and useful comments received from my supervisor, Richard Hopkins, and the members of my supervisory committee, Martin McLauchlan and Brian Randell.

I also wish to acknowledge support which has indirectly assisted, from Mike Brudenell, Shirley Craig, John Clowes, Pete Lee, Ian Scoins, all at BNFL, Andy, Bart, my family and Tree.

Funding was provided by the Science and Engineering Research Council.

# INDEX

| 1 | Introd  | uction                                                                                                  | 1              |

|---|---------|---------------------------------------------------------------------------------------------------------|----------------|

|   | 1.1     | INTRODUCTION                                                                                            | 1              |

|   | 1.2     | VON NEUMANN AND THE NEED FOR PARALLELISM                                                                | 3              |

|   | 1.3     | TRENDS IN ARCHITECTURE                                                                                  | 6              |

|   | 1.4     | TECHNOLOGICAL PROSPECTS                                                                                 | 12             |

|   | 1.5     | SOME MOTIVATIONS FOR LONG TERM GENERAL<br>PURPOSE ARCHITECTURE                                          | 14             |

|   |         | 1.5.1 A programmable array of nand gates                                                                | 16             |

|   | 1.6     | THE AIMS AND STRUCTURE OF THIS THESIS                                                                   | 17             |

|   |         |                                                                                                         |                |

| 2 | Archite | ectural Soup                                                                                            | 20             |

|   | 2.1     | INTRODUCTION                                                                                            | 20             |

|   | 2.2     | ARCHITECTURAL SOUP                                                                                      | 21             |

|   |         | 2.2.1 A basis architecture<br>2.2.2 Simulation and Emulation<br>2.2.3 Why this architecture is proposed | 22<br>24<br>25 |

|   | 2.3     | PROGRAMMING CONCERNS                                                                                    | 28             |

|   |         | 2.3.1 Machines with no dynamic reprogramming                                                            | 31             |

|   |         | capacity<br>2.3.2 Machines with dynamic reprogramming                                                   | 32             |

|   |         | capacity<br>2.3.3 Highly dynamic machines<br>2.3.4 Discussion of programming methods                    | 35<br>38       |

|   | 2.4     | SUMMARY                                                                                                 | 40             |

| 3 Directions for investigation                                                                                                                                                             | 43                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 3.1 INTRODUCTION                                                                                                                                                                           | 43                               |

| 3.2 THEORETICAL ASPECTS                                                                                                                                                                    | 44                               |

| 3.3 PROPERTIES OF SILICON-STYLE MATERIALS                                                                                                                                                  | 48                               |

| 3.4 SURFACES AND INTERFACE CONSIDERATIONS                                                                                                                                                  | 50                               |

| 3.5 THE INITIALISATION PROBLEM                                                                                                                                                             | 53                               |

| 3.6 SYNCHRONISATION ISSUES                                                                                                                                                                 | 55                               |

| 3.7 CONTROL CIRCUITRY REVISITED                                                                                                                                                            | 58                               |

| 3.8 FAULT TOLERANCE                                                                                                                                                                        | 60                               |

| 3.9 ALTERNATIVE TECHNOLOGY                                                                                                                                                                 | 63                               |

| <ul> <li>3.9.1 Optical computers</li> <li>3.9.2 Biological computers</li> <li>3.9.3 Embedded computers</li> <li>3.9.4 Interfacing dedicated architectures</li> <li>3.10 SUMMARY</li> </ul> | 64<br>65<br>67<br>68<br>69       |

| 4 On the implementation of an Architectural Soup                                                                                                                                           | 70                               |

| 4.1 MOTIVATIONS FOR A CHOICE OF ARCHITECTURE                                                                                                                                               | 70                               |

| 4.2 THE ARCHITECTURE                                                                                                                                                                       | 72                               |

| 4.2.1 General description<br>4.2.2 Function of the control unit<br>4.2.3 Logic<br>4.2.4 The multiplexor<br>4.2.5 The program register<br>4.2.6 The control unit revisited                  | 72<br>81<br>82<br>85<br>88<br>89 |

| 4.3 IS THIS AN ARCHITECTURAL SOUP?                                                                                                                                                         | 92                               |

| 4.4 ARCHITECTURE SUMMARY                                                                                                                                                                   | 93                               |

| 4.5 ARCHITECTURE ASSESSMENT                                                                                                                                                                | 95                               |

| 5 | Simulation work |                                                                                                                                                  | 101                             |

|---|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

|   | 5.1             | SIMULATION ENVIRONMENT                                                                                                                           | 102                             |

|   |                 | 5.1.1 Circuit description<br>5.1.2 Preprocessor<br>5.1.3 The Simulator<br>5.1.4 Graphical display of results                                     | 102<br>105<br>106<br>108        |

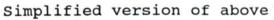

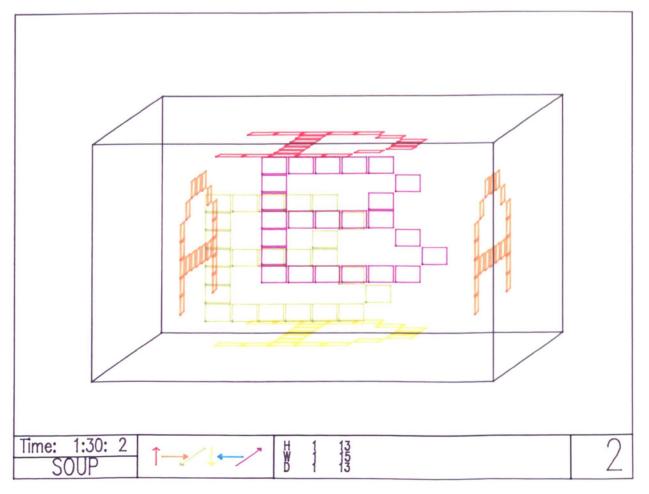

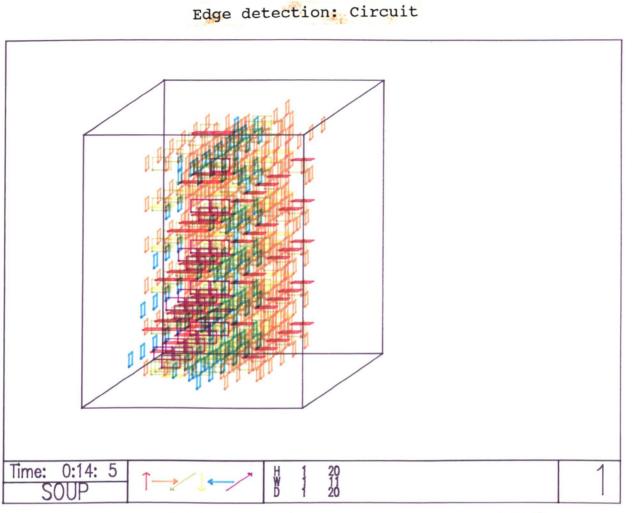

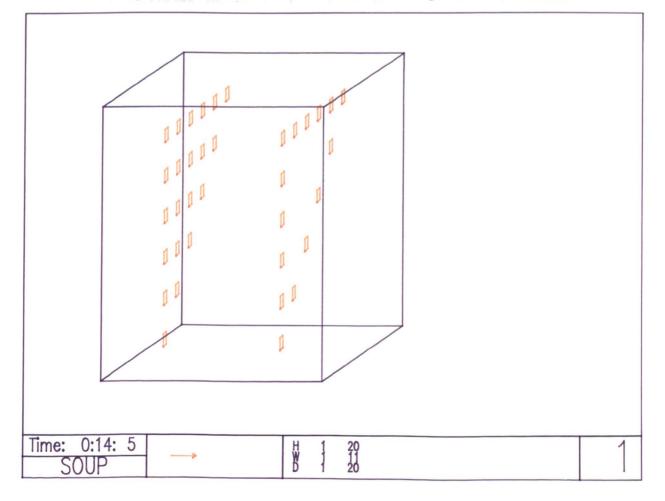

|   | 5.2             | PROGRAMMING EXAMPLES                                                                                                                             | 111                             |

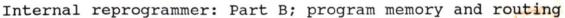

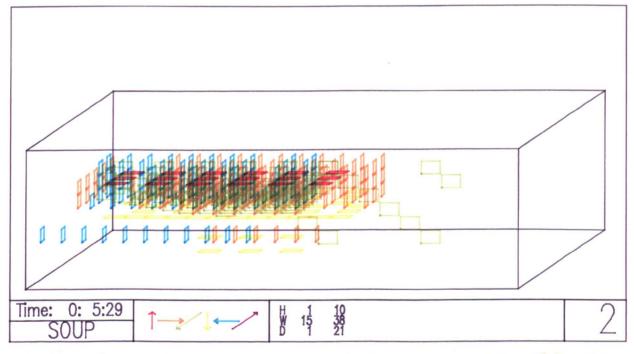

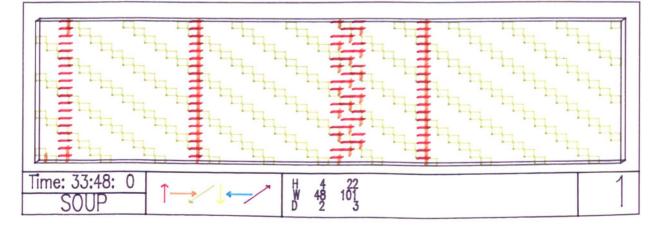

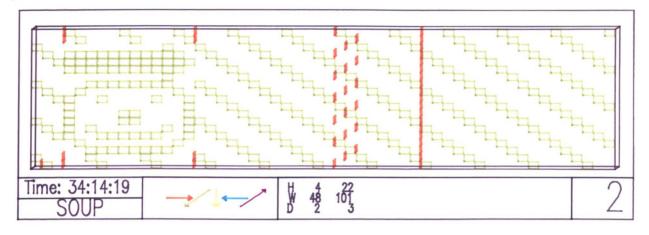

|   |                 | 5.2.1 An illustration of loading<br>5.2.2 Inverting wires<br>5.2.3 External reprogramming<br>5.2.4 Edge detection<br>5.2.5 Internal reprogrammer | 111<br>114<br>117<br>120<br>126 |

|   | 5.3             | AN ASSESSMENT OF THE SIMULATION ENVIRONMENT                                                                                                      | 133                             |

|   | 5.4             | AN ASSESSMENT OF THE ARCHITECTURE IN LIGHT OF SIMULATION                                                                                         | 136                             |

|   | 5.5             | SOME SUGGESTED FURTHER DESIGN AND SIMULATION WORK                                                                                                | 138                             |

|   | 5.6             | SUMMARY AND CONCLUSION                                                                                                                           | 143                             |

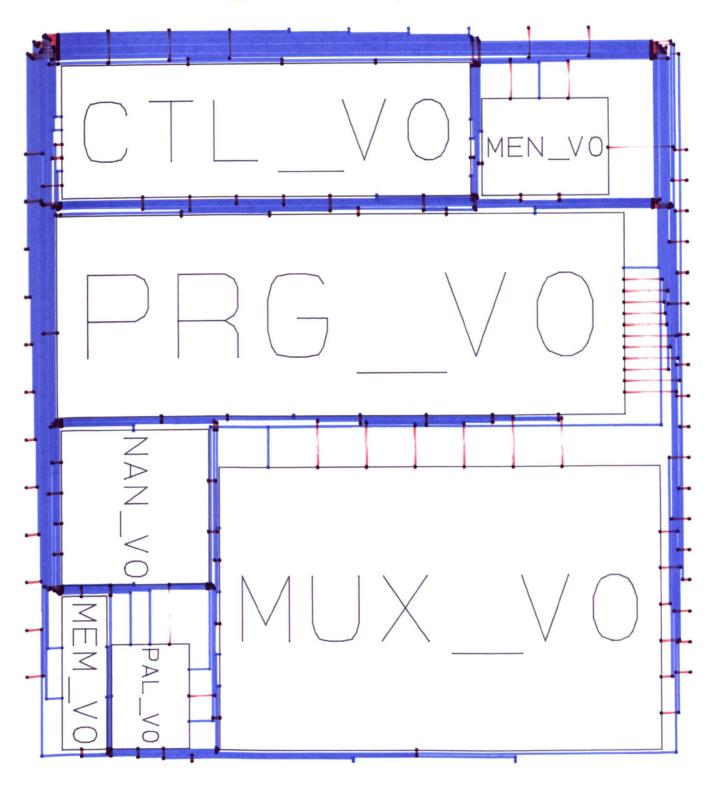

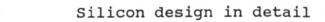

| 6 | On a V          | LSI implementation                                                                                                                               | 145                             |

|   | 6.1             | THE DESIGN                                                                                                                                       | 146                             |

|   |                 | 6.1.1 Design omissions                                                                                                                           | 150                             |

|   | 6.2             | A FURTHER ARCHITECTURAL ASSESSMENT                                                                                                               | 151                             |

|   | 6.3             | AREA ESTIMATES                                                                                                                                   | 152                             |

|   |                 | 6.3.1 Long term estimates from computer technology predictions                                                                                   | 154                             |

|   | 6.4             | SUMMARY AND CONCLUSION                                                                                                                           | 157                             |

•

| 7 | 7 Summary and conclusions | 159 |

|---|---------------------------|-----|

|   | 7.1 SUMMARY               | 159 |

|   | 7.2 FURTHER WORK          | 166 |

|   | 7.3 CONCLUDING REMARKS    | 168 |

# REFERENCES

#### APPENDIX

171

Chapter 1: Introduction

#### 1.1 INTRODUCTION

Any computer is ultimately bound by its physical size, the speed of light, the properties of the technology and the construction methods used to build it. Any other restrictions that a computer may have are due to the imposition of man-made architectural decisions.

Broadly speaking there is a spectrum of computer architecture, ranging between general purpose and dedicated purpose. The former is intended to be applicable to many different types of problem, whereas the latter is optimised for a specific class or classes of tasks. Dedicated purpose computers are usually easier to design as the use for which they are intended can be rigorously defined. This is not the case with general purpose machines. A key concept in the

generality of an architecture is the notion of its efficiency. The dedicated purpose computer is poor for general purpose use as its optimisation will normally prevent efficient solution of tasks other than those for which it was intended. Similarly, a general purpose computer is unlikely to be the optimum for any one particular task as it has not been optimised towards the task. The criterion for the 'ultimate' general purpose architecture, therefore, is the ability to emulate ALL possible dedicated purpose machines as EFFICIENTLY as possible.

There are often many approaches to solving the same problem. To give a specific example, in the area of image processing [ROS82] examines methods of utilising cellular computers for parallel processing of images at the region level. He expresses the need for a cellular computer with the ability to dynamically re-configure itself, in parallel. An alternative approach is taken by [FOU85], who illustrates the applicability of three-dimensional MIMD controlled processor structures such as pyramids and cubes. This is a different algorithm for the same problem. A general purpose machine should be good for both approaches, not biased in favour of either.

This chapter will examine current architecture and technology. Based on this, the suggestion will be made that a method by which a general purpose machine can perform such

emulation, without favouritism, is to be reconfigurable at a very low level. The remainder of this thesis is concerned with detailed examination of low level reconfigurability.

#### 1.2 VON NEUMANN AND THE NEED FOR PARALLELISM

A consequence of the Von Neumann architecture is that the small amount of silicon devoted to processing, usually only 2-3%, is kept very busy, whilst silicon devoted to memory is relatively idle [HIL85]. As machines get larger more opportunity will be lost due to the poor use made of the majority of silicon. Even in the higher utilised processing elements there is inefficient use of transistors. This wasted capacity can make machines with simple instruction sets faster than machines with comprehensive ones (see reduced instruction set computers [KAT84]).

The Von Neumann architecture is a poor candidate for the 'ultimate architecture' due to the Von Neumann bottleneck. Methods used to speed up Von Neumann machines include caching, pipelining, vector processing, and the interconnection of small numbers of machines. These computers ARE faster, but hard to program well. On

supercomputer architecture [DEN80] writes "Current architectures require intricate programming to obtain a fraction of their potential." Usually, the effective performance of supercomputers ranges between only 5 and 25 percent of peak performance [HWA87].

Hardware is inherently parallel [GOL85] so the available resource will be under-utilised as a consequence of imposing a sequential architecture upon it. Also, to efficiently emulate any particular dedicated purpose circuit, the emulator must be parallel. Consider neural computers. Here there is a requirement for large numbers of switches where each switch only performs a simple operation in order to alternate between two states [ABU87]. In this case a high degree of parallelism and inter-connectivity seem of more importance than the speed of the individual switching actions. It is likely that future machines will be highly parallel [MEA80]. The present trend is pushing the granularity of parallelism down [HWA87].

To illustrate trade-offs between sequential and parallel architectures consider two computers, both efficiently implemented, using similar technology and the same amount of silicon real-estate. One machine is Von Neumann architecture and the other is highly parallel with simple processing elements. The Von Neumann machine will be appropriate for sequential algorithms. However, it is unlikely to be as

appropriate as the parallel machine for highly parallel tasks requiring simple processing operations. The efficiency of a parallel machine for parallel tasks will depend on how well the tasks map on to the machines particular architecture. For sequential tasks the parallel machine is unlikely to be as efficient. The simplicity of each processing element will make execution of the task on an individual element complex. The sequentiality of the task will make efficient utilisation of the majority of the processing elements difficult, and if feasible at all, the speed of solution will be restricted by the communications overhead between the elements.

Arguably, any computer which has a fixed architecture must be biased in favour of the algorithms which map well on to it. (Thus no computer is truly general purpose.) The more dynamic the architecture the more general it will be, provided any overheads incurred in control and communication are not large. In order to have an architecture which is good for both parallel and serial problems, I propose examination of a machine with the simplest possible underlying architecture. This could be dynamically programmed to emulate other architectures. The thesis aims to show the viability of the principle of such machines. From the outset it is clear that control and communication overheads could be large, so such machines might never be of practical use. The thesis will examine these overheads and

illustrate some trade-off benefits which can be incurred as a result of high flexibility. This thesis also aims to give insight into the capability and flexibility possible in future general purpose machines. It is hoped that such examination will give insight into future design considerations.

#### 1.3 TRENDS IN ARCHITECTURE

Current trends in architecture were examined, in particular, machines which were not Von Neumann architecture. Distinction was made between technology improvement and architectural improvement. These factors are often related. On a basic level, improved technology can permit more complex architectures, an example being a decrease in feature size, permitting faster components and higher density. An example of architectural improvement is parallel as opposed to sequential. Technological improvements can be estimated long term by examining the theoretical capabilities of materials and assuming all production difficulties will be overcome. (For a discussion of the maximum theoretical capabilities of silicon see [MEA80].) Architectural innovation is harder to predict, but by

combining the assumptions of capability of future technology and examining the trends in current architecture it should be possible to obtain indications of the architecture of future machines.

There are many alternatives to pure Von Neumann architecture, for example, Illiac IV [SL071], Burroughs Scientific Processor [ST077], Cray-1 [BAS77] [K0Z80], Massively Parallel Processor [FUN77] [BAT80], Cyber 205 [KOZ80], Apiary Network Architecture [HEW80], Systolic Arrays [MEA80] [MOO86], Heterogeneous Element Processor [SMI81], NYU Ultracomputer [GOT82], Configurable Highly Parallel computer [SNY82], data-flow and reduction machines [DEN80] [TRE82], Cray X-MP-2 [CHE83], Erlangen Multiprocessor System [FRI83], Semantic Network Array Processor [MOL84], Reduced Instruction Set Computers [KAT84], Geometric Arithmetic Parallel Processor [DAV84], the Connection Machine [HIL85] [KUN86] [HIL87], INMOS Transputer [INM85], CLIP [FOU85], Hypercubes [KUN86], and the Encore Multimax [ENC86] [LEE87]. Much of the following work is based on an examination of these architectures and on a recent survey reviewing the 'state of the art' in supercomputer architecture ([HWA87]).

Generally speaking there are two approaches to parallelism. Firstly, to have a small number  $(O(10^{1}))$  of very powerful processors, as in the Cray, and secondly, to have a large

number  $(O(10^2) - O(10^5))$  of simple processors, as in the Connection Machine or array processors. In both of these approaches there is a high degree of regularity in processing units, the individual processors within a machine usually have similar (if not identical) function and a similar communications topology. [HEW80] identifies this as a need for both homogeneity and isotropy in an architecture in order to simplify software so that complicated optimisations do not need to be performed. (Homogeneity being each processing unit appearing the same in order that there are no distinguished locations. For isotropy there are no distinguished directions.) Considering the first approach of small numbers of powerful processors, closer examination reveals more similarity with the second approach. The powerful processors are typically speeded up using pipelines and vector processing units. If each section in a pipeline and each element of a vector processor is counted as a separate processor then each of these large processing elements can be considered to be a number of smaller elements grouped together. A difference between these two approaches to parallelism is in the degree of regularity. The systems which comprise of large numbers of simple processors are more regular.

Five basic architectural trends can be identified amongst multiprocessor systems which have large numbers of simple processing elements. Firstly the number of processing

elements is increasing. Secondly the processors have progressively simpler functions. Thirdly processors are tending towards a multiple instruction stream and multiple data stream (MIMD) architecture ([AND87]) with each processor capable of processing instructions and data independently of other processors in the machine. There are designs now for MIMD parallel machines comprising of thousands of autonomous processing elements such as the NYU Ultracomputer [GOT82]. Fourthly, having a larger number of processing elements is enforcing a simple regular communications topology between elements. The trend is towards a near neighbour mesh, although there are practical restrictions as the building of a large mesh will generate complex interconnection wiring if many circuit boards are required. Alternative interprocessor communication schemes in supercomputers can be seen in [HWA87], and a taxonomy of schemes is given in [LIP87]. The near-neighbour mesh is particularly popular in Wafer Scale Integration for the interconnection of physically adjacent processors, for example work see [JES86]. The mesh permits exploitation of locality, but data movement is often limited to adjacent processing elements [SNY82]. One consequence is that distribution of data to a large number of elements may require significant time. The last trend identified is that memory is becoming more incorporated into each individual processing element. This is because communications bottlenecks are common when using a large global memory. In

a typical computer more than 90 percent of silicon is devoted to memory [HIL87]. Distribution of the addressing of this memory amongst a number of processors permits faster access and a higher degree of parallelism. Doubling the amount of silicon afforded to the processors does not significantly effect the total amount of silicon required for the machine since the percentage currently afforded to processors is small in comparison with the percentage afforded to memory. It should be possible for future machines to have an increased degree of processing power without significantly effecting memory capacity.

An additional issue highlighted through examination of architecture, concerns the difficulty of designing optimal circuits. Switching theory provides formal methods for minimising the number of gates required. Unfortunately this does not necessarily give best solutions as the topological properties of the circuit interconnections must also be considered. Designs requiring more gates but having simpler more regular interconnection topology are often faster [MEA80]. "As switching components become smaller and less expensive, we begin to notice that most of our costs are in wires, most of our space is filled by wires, and most of our time is spent transmitting from one end of the wire to the other." [HIL85]. Even in the simple communication topology of the NYU ultracomputer most of the machine volume is occupied by the communications network and its assembly is

seen as being the dominant cost [GOT82]. One of the problems in the architecture of parallel computers is in the choice of processor communication scheme [RUZ86]. For example, the "workers" in an "Apiary" [HEW80] do not share any physical memory but communicate by packet-switching message passing. Passing messages of arbitrary sizes and performing complex operations on these messages demand powerful node processors [HWA87]. For some tasks the penalty paid for such large processors may be prohibitive. However, flexibility is needed in the communications network in order to enable formation of a large number of processing elements in a pattern best suited to the problem at hand [HIL87]. It will be difficult to obtain such flexibility with simpler communication processors.

Some issues in the architecture of the processors, memory and communications schemes have been illustrated. The section which follows will investigate future technology to identify forms of architecture which may be favoured.

#### 1.4 TECHNOLOGICAL PROSPECTS

New strategies for interconnection and architecture will have to be devised to cope with the problems of size reduction [BAT88]. "In the foreseeable future, short-channel effects and the non-statistical behaviour of devices spanning only a few tens or hundreds of silicon atoms will require a drastic rethinking of the basic device technology underlying most of present-day circuit integration." [NUD85]. Trends in technology suggest future machines will be much larger in terms of numbers of active devices possible. The complexity of the DESIGN problem will necessitate machines being constructed in a highly repetitive manner from very simple atomic structures [BER85]. Uniformity is of major importance in VLSI [SNY82]. The difficulty is that "seen from the software user, these same machines must show a different face: they are dynamic information structures which can be arbitrarily modified in order to adapt them to the immense diversity of sequential and parallel software" [BER85]. The architecture therefore needs to be simple and repetitive but capable of performing complex tasks.

The component density permissible on a chip is increasing but fundamental limits are being approached [NUD85]. Perhaps within a decade reductions in feature size will run up

against the limits of circuit technology [BAT88]. Once the limit has been reached then increasing the number of components on a chip will require that the chips are physically larger. Research in this area includes work on Wafer Scale Integration [JES86] and three-dimensional computers such as [PRE83] [GRI84] [NUD85]. An attempt at a three-dimensional computer can be seen in [NUD85] where silicon wafers are stacked on each other. Although connectivity between the wafers is poor this research suggests that forms of three dimensional technology will be available within the foreseeable future. [NUD85] predicted that it would be possible to produce a working version of his three-dimensional cellular machine by approximately 1990. Chip layering of 20-30 layers is apparently feasible with existing technology [GRI84] [NUD85] [POR87]. The anticipated benefits of three-dimensional silicon circuits are, easier more systematic wire routing, shorter wires, and as a consequence more compact circuits [ROS83]. ([ROS83] demonstrates dramatic efficiency improvements in circuit realisations over those attainable in two dimensions.)

An important manufacturing characteristic of cellular three-dimensional computers is the potential for low cost fabrication. The construction of conventional computers involves many processes that are time-serial. Assembly of cellular three-dimensional machines could be more parallel [GRI84]. There are still many problems to be surmounted,

such as power distribution (heat) and the creation of an apparently fault-free medium, but the trends suggest that these problems can eventually be overcome for general purpose architecture. The design of large DEDICATED three-dimensional structures will be more complex than current VLSI design, in order to take advantage of three dimensional connectivity, because dedicated architectures are likely to be irregular. Even with current design tools, the production of a two-dimensional chip is an extremely time consuming process due to the complexity of the electrical factors. This design complexity again suggests the need for simple regular architecture.

1.5 SOME MOTIVATIONS FOR LONG TERM GENERAL PURPOSE ARCHITECTURE

It has been suggested that future technology is likely to be three-dimensional and that general purpose architectures imposed upon this technology will be parallel. Trends in architecture, compounded with the three-dimensional construction complications, suggest that the machine will have a large number of simple processing elements. Each element will contain its own small memory and will only be

capable of direct communication with immediate neighbours. Software and hardware arguments have suggested the system needs to be simple and regular in order to facilitate design. Increased technological complications suggest that the design of any irregular architecture, such as a dedicated architecture for such technology, could be significantly more complex.

It was seen in section 1.2 that flexibility is required in the size of the architecture's processing elements in order to obtain high utilisation. Flexibility is required in memory organisation to permit parallel access, if required, and fast sequential access when parallel access is not. Flexibility is required in the communications network in order to permit reconfiguration of the memory and processing elements towards the task in hand, however, the elements of the communications system should be simple. The reconfiguration control of a large communications system consisting of many small communications elements will be a complex task. This will be augmented, because only simple processing and memory elements are available within the machine for such control. In the event of a machine being designed which has the flexibility suggested above, the ability to control the architecture will therefore be of crucial importance.

1.5.1 A programmable array of nand gates

It is theoretically possible to design a machine comprising a regular programmable array of NAND gates. Conceptually, ignoring temporal issues, the nand gates can be organised to make any functional circuit required. The processing element of a machine can be provided through arbitrary interconnection of two input nand gates which can generate all of the Boolean functions of two variables [GIB83]. A simple memory element can be created via the interconnection of two nand gates to form an SR flip-flop [GIB83]. Communication can be provided by chains of gates with the unconnected input held high to make gates act as inverters.

By programming an array of gates it should be possible to create processing elements, memory and communication paths where they are required, to create architectures which fit the application algorithms. The problem with this solution is that there are still many design decisions to be made. For example, the size (numbers of inputs and outputs) and interconnection topology of the individual nand gates will influence the interconnection possibilities, and hence favour different architectures. The control of the interconnection of the gates will be of paramount importance. There are many possibilities. For example, the architecture could be programmed via a mesh of busses which

are externally programmed in a similar manner to the way memory is addressed, with connections being made or broken depending on the conditions at the bus intersections. Long busses will be slow. An alternative is that topologies could permit a cell to be programmed by examining the state of the cells surrounding it, raising the possibility of internal reprogramming. A penalty is that cell complexity would increase in order to perform this examination. The benefits of internal reprogramming and local communication must be considered against the simplicity of a global bus system.

The notion of a mass of programmable nand gates can be used to conceptualise the possibilities of a machine with limited architectural restriction. The implementation possibilities are large and there are still many architectural decisions which need to be made. This thesis will examine areas requiring such decisions.

#### 1.6 THE AIMS AND STRUCTURE OF THIS THESIS

This chapter has examined trends in computer architecture. It has made the distinction between dedicated purpose and general purpose machines, problems with current

architectures have been stated, and long term predictions for future computers made. This thesis will examine some possible architectures for general purpose computers in the very long term based on these predictions.

Chapter 2 proposes a type of parallel architecture based on the projections made in chapter 1. Components of the architecture are, simple, homogeneous and general purpose. The possible capabilities of such machines will be discussed and similarities with some existing ideas and architectures are identified.

Chapter 3 details implementation issues. A broad set of topics are examined, as factors which now require little consideration will become more important in future architecture. A consequence of this broadness is that individual topics are not considered in depth.

Chapter 4 discusses a specific design, meeting the considerations discussed in the previous chapters. The machine discussed is symmetrical in three-dimensions, hence, cannot be built with current technology.

Chapter 5 illustrates this design through simulation. Experience with programming and simulation of a three-dimensional computer and directions for further experimental work is given.

Chapter 6 presents a VLSI design for one processing element of the architecture illustrated, to show the design's simplicity, and the simplicity of the architecture. The design is then utilised to obtain a projection for the possible number of processing elements in a future realisation.

The final chapter presents a summary and makes concluding remarks on the validity of work done, with direction for further work.

#### Chapter 2: Architectural Soup

#### 2.1 INTRODUCTION

Computational problems frequently have many methods of solution. For any rigorously specified problem that may be solved by computer there will be optimal electronic circuits. The closer the architecture of a computer to a 'minimum solution circuit' the faster the solution can be found. 'Architectural Soup' is a proposed type of computer with the capability to be reconfigured at a very low level to, it is hoped, efficiently emulate such circuits. (The term Architectural Soup is derived from the myriad of potential architectures available from within the machine.)

When considered at a low level, computers consist of processing elements, memory and wires. Consider a machine with simple cells, which may be dynamically reconfigured to provide these components as required. Such a machine should

be able to imitate the function of any feasible computer, however, there will be differences in the speed of individual components and in the size limitation of the machine.

This chapter will define Architectural Soups. The architecture of such machines will be shown to be an extension of the trends identified in chapter 1. This is followed by an examination of the possible capabilities and limitations of such machines should fabrication become feasible.

### 2.2 ARCHITECTURAL SOUP

Architectural Soup is a class of architectures as opposed to any single architecture. There are many possibilities for machines with simple processing elements which have the capability to emulate other machines. In order to define the class, a basis architecture will be defined. Membership of the class is determined by assessment of a candidate machines ability to emulate this basis architecture.

#### 2.2.1 A basis architecture

Consider a three dimensional machine consisting of a very large number of simple cells. For example 100x100x100 cells is small. (Estimates for the total number of cells in a future machine will be made in chapter 6.) The cells must exhibit the properties of homogeneity and isotropy in that they have identical function and that orientation is of no concern. (Discontinuity problems at the surface of the machine will be examined in Section 3.4 .) The technology of the machine must be sufficiently stable and the architecture be such that the actions of all cells are controllable and deterministic so that repetition of the same operation from the same starting state will yield the same result. The basis is not defined as having a global clock to aid in these control issues as Soup cells could also function asynchronously. (Synchronisation issues will be considered in Section 3.6.)

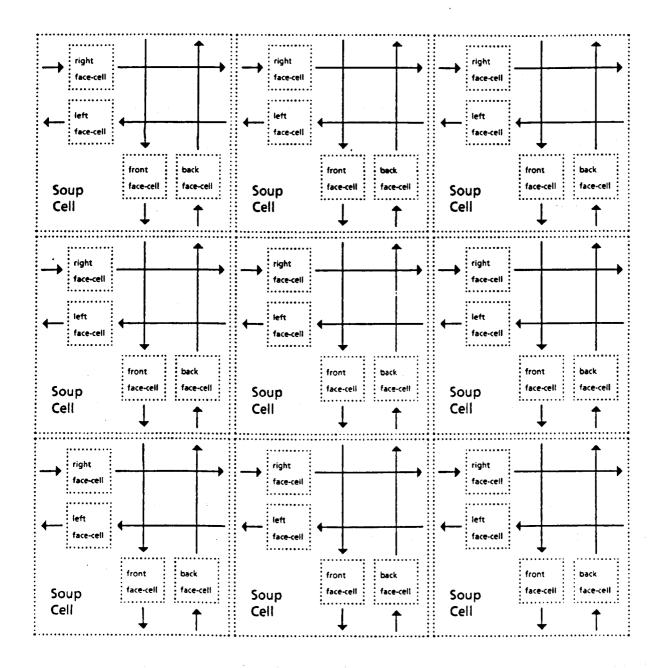

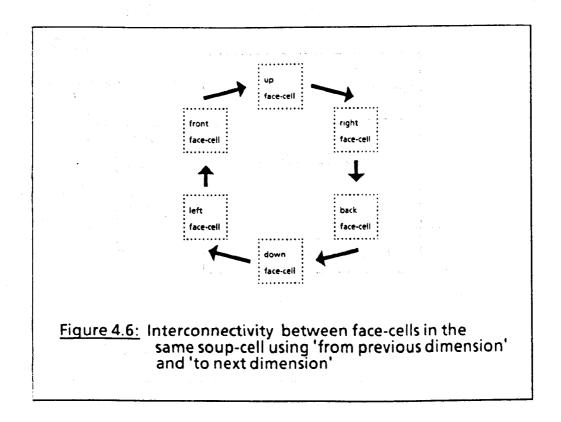

Cells in this basis architecture are cubic. Each has six immediate neighbours, left, right, back, front, up and down. Up and down are included in order to utilise three dimensional space, as opposed to two dimensional. Cells are abutted in a three dimensional complete near-neighbour mesh. Communication is with immediate neighbours only, via a one

bit wide input and a one bit wide output to each abutting neighbour.

The functionality of cells is provided by programming the required primitives between the six inputs and six outputs of a cell. The method by which this programming could be performed will be discussed later in this chapter. The functional primitives required in each cell are a wire, a one bit memory and a simple processing element. The wire -It should be possible to program the interconnection between ANY input to and ANY output from, the cell. An additional desirable characteristic of the wire function is that there should be no noticeable degradation over a path through the machine which consists of many such wire functions. The memory - A memory primitive has two inputs and one output. When the control input is signaled, the value on the data input is stored in the memory. The processing element - This can be provided by a two input nand gate, two input nand gates can be interconnected in order to provide all the possible functions of two Boolean variables [PRO87] and hence all functions of N Boolean variables. In order for the machine to be isotropic, it must be possible to place nand gates, memory elements and wires between any inputs and outputs of a Soup cell. In addition to these functional primitives, the Boolean constants 1 and 0 are required. It must therefore be possible to program any output of a cell to generate these constants.

## 2.2.2 Simulation and Emulation

Many machines will be capable of simulating the basis Architectural Soup but in order to emulate it they will require simple cells and a simple communication topology. Based on the dictionary definition [OED33] the difference between a simulation and an emulation, in this case, is that an emulation is much closer to the true speed of the target architecture. An emulator would require a very direct correspondence to the elements and connections in the basis. It will require large numbers of simple processing elements, a highly distributed memory, and the capacity for fast local communication. Consider a simulation of the functionality of the basis machine on current Von Neumann machines. This would not be a Soup as the quality of emulation would be poor. Consider a machine identical to the basis, with the exception that each cell has only one nand gate which is positioned between left and right inputs and the front output. Such a machine would be able to emulate the basis architecture by programming a group of these cells to act similarly to one basis cell. This provides routing such that nand gates 'appear' to have the ability to be connected in every feasible orientation. As the number of cells in such a group will be small this architecture would consequently be an Architectural Soup.

### 2.2.3 Why this architecture is proposed

Taking into consideration the requirements and trends established in chapter 1, the first architectural requirement of a Soup is that the number of processing elements must be large. This should be fulfilled as a consequence of the simplicity of the Soup's cells and communication topology. It should be remembered that the simplest cells do not necessarily give the most space efficient architecture, due to the amount of control circuitry required. Cells which have more complex function but require less control may permit a denser packing. Cells with functions simpler than memory, nand gates and wires could be considered, for example, the interconnection of several cells to form a single nand gate. A possible benefit of this would be to achieve higher cell density. Control of such an architecture, however, is likely to require more control circuitry, and be a prohibitively complex task.

A second trend identified was that a machines individual cells have very simple functions. The cells in a Soup have simplicity which, in fact, renders them incapable of meaningful computation on their own. With such simplicity there would be little purpose in every cell of the machine performing the same function at the same time. It is suggested that such a machine must require both a multiple

instruction stream and a multiple data stream, that is to say the third trend.

The fourth trend suggests that the communication system in the basis has a near-neighbour mesh topology. By Soup definition, any machine capable of emulating the basis will require a topology close to the near-neighbour mesh, otherwise the quality of emulation will be poor. (Due to the simplicity of the cells and topology, circuit switching techniques will likely be used as opposed to packet ' switching.)

The final trend identified was that of memory being incorporated with each processing element. In the above architecture there is a one bit memory for each one bit nand gate processing element. This represents maximum memory/processor interleaving.

This style of architecture appears to be an appropriate candidate for three-dimensional technology. Cells are simple and identical so permitting a simple design. For example, a small area consisting of a few cells of the machine can be designed in detail and used to make generalisations for a larger machine based on simple repetition. As the active devices are in a regular lattice, modelling of this architecture is simplified. One of the major problems with three dimensional machines is heat generation. The ability

to model heat generated in a lattice of cells will simplify this complex aspect of design. Considering manufacturing characteristics, it has been mentioned in section 1.4 that manufacture of a three-dimensional machine could be simplified by using parallelism in the manufacturing processes. A regular array of simple processing elements will make the Soup a candidate for such parallelism.

The flexibility aspects, identified in chapter 1, must also be considered as motivations for general purpose architecture. The simplicity of the Soup's cells are such that the machine can be programmed so that processing elements, memory and wire, are configured as required. This provides the potential for flexibility in processing, in the memory and also in communication. An important consequence of this is that, theoretically, a machine with the above capabilities could be efficient at executing both parallel and serial algorithms. As the architecture is highly parallel, it should be possible to reconfigure the machine in order to emulate a variety of parallel architectures. This could include any future alternative machine architectures which follow the trends outlined. In addition, due to the simplicity of the cells, it should still be possible to reconfigure the machine to emulate serial architectures. Penalties for this flexibility will be, the amount of control hardware required, the overhead of any

unused elements within each cell when it is programmed, and the delay incurred in programming the control circuitry.

#### 2.3 PROGRAMMING CONCERNS

It has been shown that an Architectural Soup follows projections of machine trends. Consideration will now be given to the means by which such a machine could be programmed. It is proposed that it will be possible to program at this low level because machine trends imply this style of architecture. The programming of the architecture can be viewed from two standpoints, firstly as being at a level just above that of silicon chip design, and secondly at a level below machine code programming.

Consider the view of programming being similar to silicon design. It can be argued that we are not yet highly skilled at programming in this manner. However, programmers of the Soup will be less concerned with electrical factors, such as power distribution, than a silicon designer, as these will have been considered before the machine was manufactured. Programming a Soup can be viewed as nearer semi-custom VLSI design than full-custom. (For a description of semi-custom

design see [HIC83].) A two dimensional realisation of a Soup could perhaps be conceptualised as a surface of gate-array chips which have a dynamically programmable metal layer.

[GOL85] states that integrated circuit design is currently in a phase similar to that of software design thirty years ago when the first compilers became available. The target domain for silicon compilation is complex, but as the possible number of features available on a chip increases, designers are more concerned with aspects of size than of obtaining high utilisation in the previously limited area of silicon real-estate. As a consequence the tools used by silicon designers are now tending towards software methods [DAL84]. A silicon compiler described by [KEL85] can automatically generate self-timed circuits from a behavioural description. (A behavioural description specifies the input/output mapping, as opposed to the explicit physical structure of the architecture.) Algorithms are viewed by the compiler as having two dimensions , which are mapped directly onto the two dimensions available on planar chips. One dimension is used for the flow of data through the algorithm, the other for parallelism. This suggests that it should be possible to produce a compiler for Soup architecture, especially given the increased flexibility of a third dimension.

Alternatively, the programming of a Soup could be viewed as programming at a level below machine code. Considering this approach, programmers are no longer concerned with writing programs at the machine code level. It is assumed, in the majority of cases, that compilers will generate efficient code. For a suitable machine code it should be possible to generate circuits which implement equivalent function. A compiler could then specify which circuit primitives were required as opposed to producing a machine code. A problem of such a system will be synchronisation. Timing difficulties exceed all other design problems by "an order of magnitude" [KOE86]. [KOE86] goes on to state that the self-timed approach is capable of tackling not only the problems of timing, but also design complexity and testing. A penalty of the approach is increased circuitry.

A Soup can be seen to be more software dependent when compared to existing machines since the underlying hardware has, effectively, had less structure imposed upon it. It follows that some of the properties sought in hardware design will also become sought in software design. For example, simple regular structures may be preferred in circuit generation as repetition is likely to be simple. A speculation is that compilers may become more concerned with environmental issues, such as heat generation. Heat in silicon is primarily generated from the active devices as opposed to wires [ROS83]. Synchronisation protocols may,

therefore, have an additional requirement of slowing down circuits switching frequently, so as to prevent excessive heat production.

Considering both standpoints, programming a Soup in some form does appear feasible. This will be at a level in between that of machine code and silicon design.

Methods of programming will now be considered. The manner by which a machine is to be programmed will influence the manner in which it is controlled. The following discussion is simplified, further issues will be considered in chapters 3, 4 and 5.

2.3.1 Machines with no dynamic reprogramming capacity

Consider first a machine which can only be programmed when switched on. This type of machine has no capacity for dynamic reprogramming of its architecture. Assuming the machine is in a receptive starting state, it is possible to consider specifying an architecture by using a high level language similar in form to a VLSI description. This description can be algorithmically decomposed to generate the necessary programs for each individual cell of the Soup. Once the Soup has been programmed, the users perform

applications programming on the emulated machine. This architecture has similarities with the properties of static microcode, that is, remaining the same for a period of time but having capacity to change if required. (Microprogramming is used to implement control of a processor in a "systematic and flexible" manner [HAY78]. It is intended to permit tailoring of a computer to a particular problem, or type of problem, by providing a closer interface to the underlying architecture [ECK79]. It is argued that the extra delay from the circuitry required to implement the microcode is offset by the improvements in speed gained from achieving a better utilisation of the underlying resources [ECK79].) A benefit of this capability in Soup architecture is that a general purpose off-the-shelf hardware unit can be purchased and tailored, using software methods, towards the particular environment in which it is to be used.

2.3.2 Machines with dynamic reprogramming capacity

If a Soup has the capability for its architecture to be changed dynamically, there is the possibility for individual applications or programs selecting a favoured architecture from a set of standard architectures, which can be loaded as required. The user programming language could permit specification of the required architecture or give hints as

to which architecture might be preferred, leaving the final choice to the compiler. The compiler could then generate code optimised towards the chosen architecture. If a Soup permits more rapid dynamic change then changing architectures during execution could be considered. This would benefit tasks where the amount of parallelism varies depending on previous results. The complexity of performing such transformations is likely to be large, requiring an overhead of circuitry to detect when the change is required. A benefit would be that the Soup architecture need show little favouritism towards individual application languages as it could restructure itself in a short period of time to favour others. This is similar to the properties of a dynamically changeable microcode. For example, a microcode capable of changing its function during execution depending on how the algorithm is executing. The speed benefits need to be greater than the complexity of the programming task and the speed at which the microcode can be changed. Little attention has been paid to microcode with such dynamic properties to-date. Such properties will be more complex to control. Also, microcode has been predominately used on Von Neumann architecture machines. As the architecture of the underlying machine remains essentially Von Neumann there is little benefit to be gained from dynamic change. An important difference gained by use of a Soup is that a much higher percentage of the architecture could be changed so such dynamic flexibility may be beneficial.

For the programming methods discussed, there is a trade-off between time spent generating and loading the initial architecture and time spent running the application on it. For example, an algorithm can be implemented as a regular lattice of identical processing elements or alternatively as an irregular lattice of several different elements. The initialisation time saved by regular design could offset any benefit from the irregular case being closer to a minimum solution circuit.

A particular issue which arises from an ability to change architecture is that, historically, there has been a need for software developed for old computers to be supported by new models. Given that the architecture of a machine could be specified and compiled into programs for the Soup, the Soup would then be able to emulate any architecture (if it had appropriate peripherals) and hence execute old software, although there will likely be considerable speed reductions. This is called upward compatibility. As there is the physical three-dimensional restriction on the building of any future computer and a Soup has such low level emulation capacity, it would be able to emulate any FUTURE machine architecture (including other Soups). It will therefore have the ability to execute software for FUTURE machines for silicon style technology. I term this anomaly 'downward compatibility. Obvious problems would arise in the possible size and speed of the machine but previously it has been

more important that software can be executed (in acceptable time) rather than that it executes well. Software would gain in portability since it could execute on more machines. For example, applications could incorporate a specification of the required architecture in some form of standardised specification language. It is important to remember that it is the specification, rather than the 'circuit programs', which can be transferred from one machine to another. It will not necessarily be possible to transfer circuits since any difference in feature size or material technology between machines will effect timing considerations. For example, in a silicon design a component may no longer function if it is scaled down [MEA80].

# 2.3.3 Highly dynamic machines

If a Soup has a highly dynamic architecture then reprogramming of applications architectures from within the machine can be considered. This would permit dynamic creation of dedicated architectures. An example of work done in dynamic switching can be seen in [POR87] where the switching of arrays, both in form and structure, during the course of computation, is considered. [POR87] states that "Such capabilities are desirable to cope with the computational demands of multi-stage algorithms.". (For a

discussion of highly parallel dynamic systems see [HIL85].) A simple example relevant to a Soup is that an addition operation specified in a program can be compiled into an adder circuit no larger than required, with the appropriate synchronisation to neighbouring circuits. A more complex example would be a dynamic stack which claimed and released Soup cells as required. This introduces two requirements on the Soup architecture, the ability to identify free circuit space and the ability of a circuit to replicate itself into this free space. Many additional problems will result from having such flexibility in Soup architecture. For example, difficulty in deciding which circuits to use (a problem encountered in optimising compilers), although the cost of performing these decisions could be reduced by extraction of parallelism. The issues involved in this flexibility are comparable with those of tailoring microcode to provide the specifically required function, and also of the microcode modifying itself during execution depending on previous actions taken.

An application where such dynamism might prove useful is neural computing. Similar features which can be identified when considering a neural computer and a Soup architecture are the requirements for fine grain computation with massive parallelism, the potentially very high communication bandwidth, and a distributed and self-organising control mechanism [HWA87]. In particular it is possible for a neural

computer to program itself [ABU87]. The ability for a machine to modify its architecture from within, it is proposed, will be of major importance.

Work on dynamic reconfiguration can be seen in Cellular Automata theory [COD68] [PRE84] [WOL86]. One of the original purposes for the study of Cellular Automata was to determine how computers could be made to reproduce themselves [PRE84]. An automaton is similar to a Soup in that it consists of a near neighbour mesh of identical processing elements. Such machines are identified as having the ability to, in theory, compute all computable functions, to reconfigure other parts of the cellular space, to reproduce itself in any quiescent, accessible and sufficiently large region of the space, and to emulate other Automaton. It is stated that "If an economical realisation can be found, Cellular Automata provide the capability of extending the computing power of a system in small or large increments and of reorganising these increments to suit various special needs". [COD68]. (The Connection Machine is described as a realisation of a Cellular Automaton [HIL85] [KUN86] [HIL87]. One important similarity with a Soup is that any single cell within the Connection Machine is incapable of meaningful computation on its own, groups of cells are connected together to form "active data-structures".) A difference between an Automaton and a Soup is that cells in Automaton are defined as synchronised to a global clock. An Automaton is one

realisation of a Soup. A Soup could emulate an Automaton and hence possesses similar capabilities. However, there could be other realisations of a Soup where cells are not synchronised to a global clock.

# 2.3.4 Discussion of programming methods

Several programming methods with varying degrees of dynamism have now been considered. It is important that an Architectural Soup which can only be programmed once at switch-on, can be used in a similar fashion to a machine which can be dynamically programmed, by configuring the machine to emulate the dynamically reconfigurable Soup architecture. This ability to emulate other architectures is a crucial factor when defining a machine as a Soup. There will be emulation penalty, but this is offset by the frequency of use of dynamism. Dynamism must be frequently used, or there will be little benefit gained from an architecture which has this capacity. The additional control would make circuits which do not require such dynamic changes run slowly.

It has been shown that there is a range of possible dynamism within the program control circuitry. There are many possibilities for Architectural Soup architectures, the

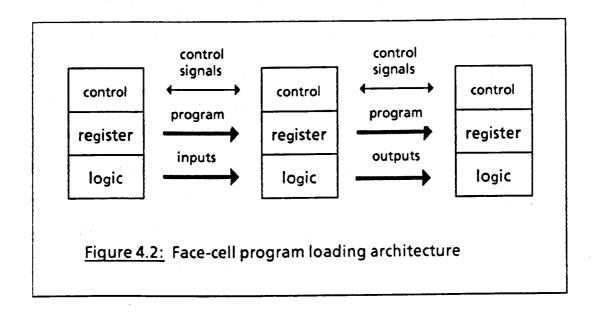

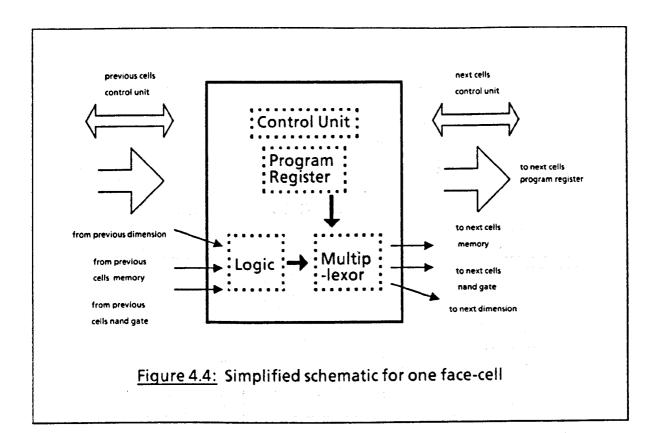

common factor being their ability to emulate each other. A major issue appears to be the binding time of the architecture. The method of programming which can be employed is affected by the quantity of architecture specified at time of manufacture, the quantity at switch on, and the quantity which can be dynamically changed. The speed of change will be important in deciding the relative merits of any dynamic reconfiguration. For a system which does not change dynamically, a global transmission system such as a mesh of global busses which are controlled externally, would suffice to force cells into the required configurations. However, as the trends in chapter 1 suggest that communication will only be local, a global bus is unlikely to be a good solution. Alternatively, it can be considered that a cell (or group of cells) has the capability to force a neighbouring cell into a required configuration, with new circuits only being loaded into the external cells of the machine. Such a system will be illustrated in chapter 4. A third possibility is that a cell switches itself, depending on past events and its environment, such as in Cellular Automata. However, this was thought unlikely to be of practical use for machines with such simple cells, as the circuitry required for this function would likely be complex.

•

#### 2.4 SUMMARY

In Chapter 1 the projection of technology trends supported a prediction that future technology will permit large three-dimensional arrays of transistors. A proposed style of architecture for such technology is the Architectural Soup. The main properties of this architecture are that it is highly parallel, simple and regular. An Architectural Soup could be used for particular tasks by configuring itself at a very low level to emulate a good architecture on which to solve the problem. The assessment of the quality of this emulation is difficult as it is technology dependent. It can be argued that as machine trends are leading towards this style of architecture, it is likely that emulations will be reasonable. Provided that the Soup is sufficiently large it could, theoretically, be programmed to emulate directly (more so than current computers) any existing or future computer. The emulation would be slower than machines that have been emulated, due to the overheads of set up and control that will be required for a machine with simple cells. It is argued that this is offset by the flexibility benefits.

The technological design of three-dimensional systems will be more complex than current machines. With the increased importance of factors such as heat and non-statistical

behaviour, it may be that in practice it will ONLY be possible to design a system which is simple and regular. The simplicity of a Soup's basic cells would simplify hardware design. For example, it is easier to model a regular system. Regularity simplifies production, for example, there is capacity for a high degree of parallelism to be employed in manufacture. As software becomes more responsible for concerns which were previously architectural considerations, the properties sought in hardware design will become more important in software design. Software designs possessing simple regular structure will be favoured, and it is possible that software may become concerned with factors such as heat.

In section 2.2 it was shown that it is possible to conceive an architecture which is efficient for both parallel and sequential code. The run-time efficiency is dependent on the control over-head required. The following chapter will illustrate implementation issues in more detail, to assess factors requiring control, and illustrate complexities of the future design problem. A specific example of an architecture with a capacity for internal reprogramming will be illustrated in chapter 4.

As the control overhead for Architectural Soup machines is likely to be high it is thought unreasonable to design a computer with cells at the gate level other than for the

interest aspect of examining a machine with such flexibility. However as current trends project to this style of architecture, architectures with only slightly more complex cells than the machines described here are likely to be practical.

.

### Chapter 3: Directions of investigation

# 3.1 INTRODUCTION

This chapter is concerned with implementation issues. Due to the diversity of topics which need to be considered when designing a machine it is not possible to perform a thorough investigation into all design issues. It is therefore intended to present an overview of possible directions and issues for investigation, in particular, to illustrate factors which are likely to be of increasing importance in future machines. The factors which will be examined are, theoretical considerations, material properties, surfaces and interface considerations, initialisation problems, synchronisation, control circuitry, fault tolerance and some alternative technology to silicon style machines.

# 3.2 THEORETICAL ASPECTS

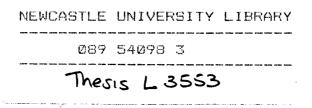

Restrictions on the architectural form of a machine can be established from examination of relevant mathematical theory. Consider the manner in which the cells of the machine can be interconnected. This will effect the number of neighbours which can abut an individual cell. The physical interconnection architectures which are possible can be determined by examining the theories of compacting solids, for example work see [TOT64] [LOE76] [MAN82]. The number of regular polyhedra which compact together to fill an area of three dimensional space is finite. Some examples of such space-filling polyhedra are shown in Figure 3.1. Consider one cell of an Architectural Soup as being one such polyhedron. The manner by which these polyhedra abut will determine the number of immediate neighbours a cell has and hence limit the interconnection topologies that are possible between cells. (The theoretical topologies possible would, in practice, be restricted to those permitted by the properties of the material and limitations of construction technologies. In particular some materials may not favour a simple cubic design, such as in the basis.)

There is a trade-off of functionality between cells and functionality within them. The functions available within a cell will effect the number of neighbours that a cell should

have. For example, if a cell has a complex processing element or a large memory it may justify a complex communications topology. When considering routing, there are many possibilities available from within a Soup cell. Each cell in the basis architecture, as described in chapter 2, has six inputs and six outputs. For isotropy, it was stipulated that it be possible to connect every input to every output. This is an exhaustive method of routing and so likely to be more complex than is required. Such a system will need extensive control to select the required combinations from the large number of wiring possibilities available. It should also be noted that with this system, the cost of increasing the number of neighbours will be relatively high due to a combinatorial explosion in the complexity of the cell. This suggests that a small number of neighbours will be a major design aim for an exhaustive approach to inter-cell routing.

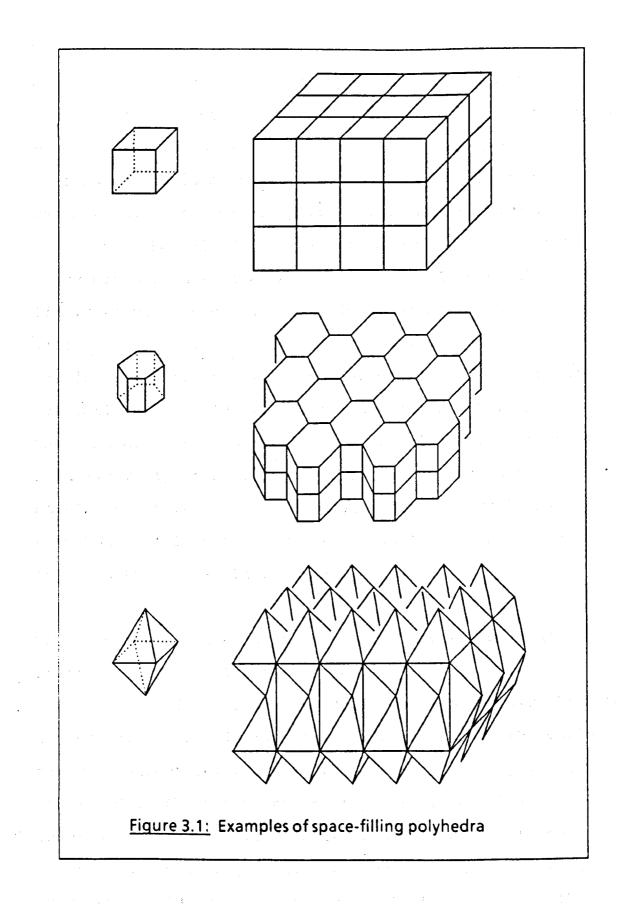

The opposite of an exhaustive routing set is the minimum routing set. This utilises the smallest number of connections which permit communication from any direction to any other. One possibility for cells similar to the cubic basis architecture, would be to have each input primarily connected to the output on the opposite face, while incorporating the ability to redirect the output to one other face, as in Figure 3.2. For example the input to the left face would primarily be routed to the output on the

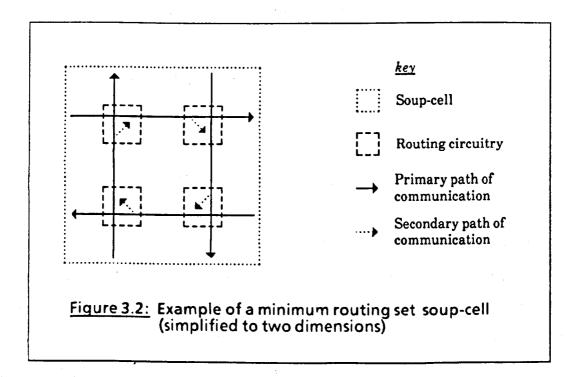

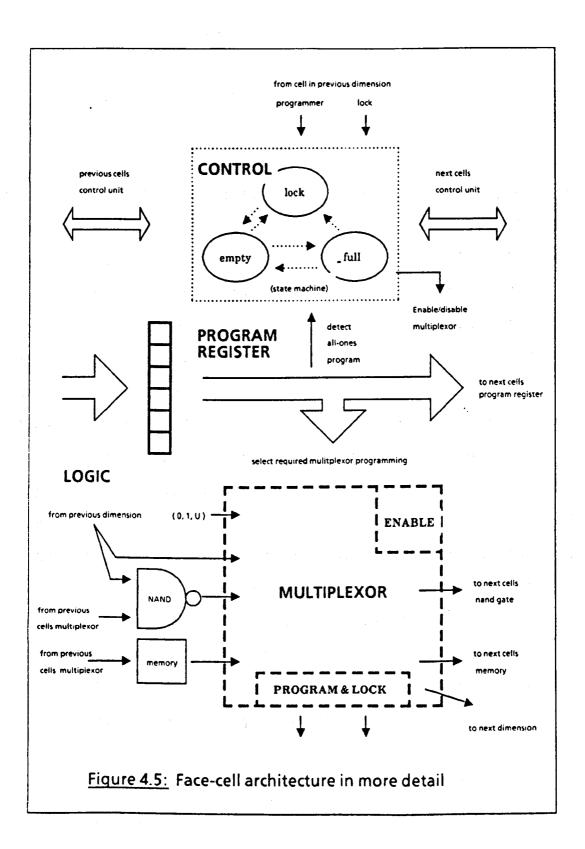

right face, but it would also be possible to direct this output to the front face if required. If cells remain orthogonal then information can still be routed from any direction to any other, by connecting together several adjacent cells to route signals to the required direction. Such a routing system would increase linearly in complexity with the number of neighbours that a cell has, so permitting a higher number of neighbours before the complexity of routing control becomes prohibitive. A penalty with a minimum routing set, however, is that where several cells may be required, only one is required with the exhaustive approach. An architecture based on a minimum routing set is illustrated in chapter 4. This architecture was chosen for its simplicity.

### 3.3 PROPERTIES OF SILICON-STYLE MATERIALS

Design of silicon at approaching minimum feature size is complex. For a detailed analysis of the properties of silicon and the complexity involved see [MEA80] [CAR80] [CHI82] [LIN82] [GIB83]. This design problem will be exacerbated by the increased complexity possible with three dimensional circuits. For example, higher connectivity would permit smaller more densely packed components [PRE83] [ROS83]. This shortening of wires in circuits will potentially make components faster. However, this will also increase other design problems, such as the amount of heat generated. The scale of features in cells will effect the manner in which they are implemented. For example, as VLSI feature size reduces, the relative time cost of wiring increases over the cost of the switching components [MEA80]. The distinction between switching states becomes blurred due to current leakage and imperfections [BAT88]. Smaller active circuits have a reduced drive capability [NUD85]. These factors suggest that the smallest possible cell size will not necessarily be the best. Considering manufacturing aspects, the smaller the feature the tighter the controls needed and the lower the yield. Not all problems will increase in building a large three-dimensional machine. For example, a simplification of the power distribution problems found in Wafer Scale Integration, unlike in current silicon

chips, is that there is no requirement for high power driving circuitry needed for communication between several chips within a wafer [GRI84].

The complexity of manufacturing three dimensional devices will influence the resultant architecture. For example, if it is as easy to use three dimensions as it is to use two dimensions then cubic or spherical machines can be considered. However, if utilisation of the third dimension is difficult then machines will essentially be only a small number of surface layers, such as the computer described in [NUD85] which consists of the interconnection of a few two-dimensional wafers.

Section 2.2.2 illustrated the ability to model part of the machine and make generalisations, due to the regularity of the architecture. The design of a Soup should be simpler than designing three-dimensional machines which are based on existing architectures, due to the simplicity of the Soup cells and the regularity of the inter-cell architecture. A consequence of the simplicity is that it will be easier to design and accurately model the electrical considerations of an individual cell. Once this has been performed, interaction in a regular group of such cells could be examined and generalisations made for a larger machine based on repetition. This would be a difficult task for complex

and irregular architectures as such generalisation can not be made.

### 3.4 SURFACES AND INTERFACE CONSIDERATIONS

The surface area of a Soup is a factor in interface considerations as it is the point from which communication will occur. The ratio of surface area to volume is important. A thin film of material provides a higher surface area to Soup cell ratio than a sphere which has a low ratio. The optimum ratio will be determined by the speed of the Soup cells and the input/output requirements. (For insight into possible capability of future input and output devices see work on highly parallel optical stores such as [ABU87] or [HUT87].) If the permissible input/output speed is a restricting factor this may limit the maximum useful size of the Soup. This problem is compounded in larger Soups as the average communication path from Soup-cells to peripherals interfaced to the surface will also increase. Input/output intensive tasks may, as a result, take longer to execute.

The surface of a material is particularly important for controlling the materials behaviour and properties [JAS77].

For example, the abrupt termination of a crystal lattice at the surface must result in a unique arrangement of the surface atoms. The surface of a machine is most prone to unpredictable external factors such as electrical interference. The surface will also be required to dissipate heat. These factors suggest that one of the most important areas of the machine (input/output) is also likely to be the most unstable if designed in the same manner as the cells in the remainder of the machine. It is therefore suggested that cells in the proximity of the surface will require a different design from those cells at greater depth. This will introduce a programming irregularity. Irregularity may be acceptable, given that a programming irregularity at the edge of the machine is inevitable due to the discontinuity of material. In systolic arrays this problem is solved by routing the outputs from one side of the machine back into the inputs on the opposite side. Examples of rings and torus architectures performing this function can be seen in [MEA80] [MOO86] [POR87]. However, this is unlikely to be a feasible solution for an Architectural Soup due to the large communication distance between cells on opposite sides of the machine relative to the distance between adjacent cells within the machine. An alternative is that the architecture can to an extent be folded to reduce this communication distance. For example consider a cubic Soup. The left and right surfaces of the machine could be folded together to form a ring, and the top and bottom surfaces could be folded

to obtain a doughnut shape. (It is not possible to join the front of this Soup to the back as these are now the internal and external sides of the doughnut.) Such a machine is likely to be hard to manufacture due to its irregularity, and similarly hard to interface to and program. For these reasons the cubic machine is favoured. If it were required, a small 'doughnut architecture' machine could be emulated on a large cubic Soup. '

Compatibility of a Soup with the machines it is required to communicate with will be an important factor. It is possible that communication with the outside world may suggest a communication mechanism for Soup cells in the proximity of the surface. This may influence the communication topology of all cells within the machine in order to maintain regularity. For example, a fundamental problem with input/output devices is metastability [MEA80] [KOE86]. This necessitates determination of whether an intermediate signal is of a high or low value. One method of tackling metastability problems is to use asynchronous communication protocols, the result being that occurrences of metastability only cause the system to slow down temporarily [KOE86]. If such an interface scheme were adopted it may be desirable to make the remaining cells within the Soup communicate using asynchronous protocols.

#### 3.5 THE INITIALISATION PROBLEM

The initialisation problem concerns transformation of a machine from an initial random state into a known and useful state. For Soups the initialisation problem can be subdivided at a cell level. Firstly, a cell must acknowledge that it does not contain a valid program, and secondly, it must accept the required program. Considering the first problem, cells could be designed which assume an empty state when the machine is switched on by using the initial power characteristics. An alternative is that a cell could be forced into an empty state by the cell's neighbour(s), and once in the empty state the cell could force a neighbour (or any neighbours) which are not in an empty state similarly. Cells on the surface of the machine could be forced into a suitable state to start this process - it should not be complex to generate programs consisting of all ones or all zeros in the machines surface cells, by connecting every surface cell's program input to all high or all low input signals as appropriate. The architecture of the machine could be such that a cell receiving an all-ones or all-zeros program will send a similar message to its neighbours and then place itself in the empty state ready to receive the appropriate initial programming. After a period of time all of the cells in the machine should be in the empty state. The time taken for initialisation will depend upon either

the speed at which cells can be reprogrammed or the speed of input to the Soup. A system based on this will be described in chapter 4.

There will be problems with such a start up system. For example, in a machine which can program itself internally there will be a risk of some initial random state, such that the machine will start reprogramming itself. This programming may be resistant to any start up circuitry, for example, if it can reprogram itself faster than the initialisation circuitry can clear it. It must be ensured, therefore, that the machine is unable to arrange itself into a random state such that it cannot be initialised. Similarly, there is the possibility of accidentally generating an all-ones signal in one cell during execution (for example as a result of external interference) which could result in a reprogramming of the entire machine. Another initial problem would be if a Soup cells initial random state is an illegal electrical state such that the cell does not function as expected. Avoidance of this unintended function (as with all circuits) will require special attention when cells are designed.

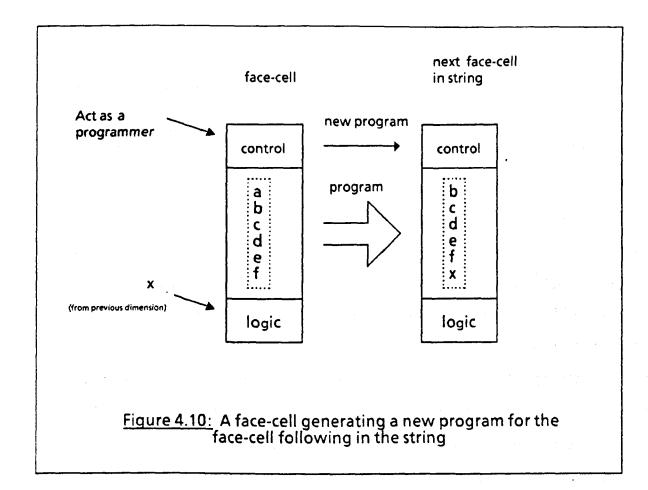

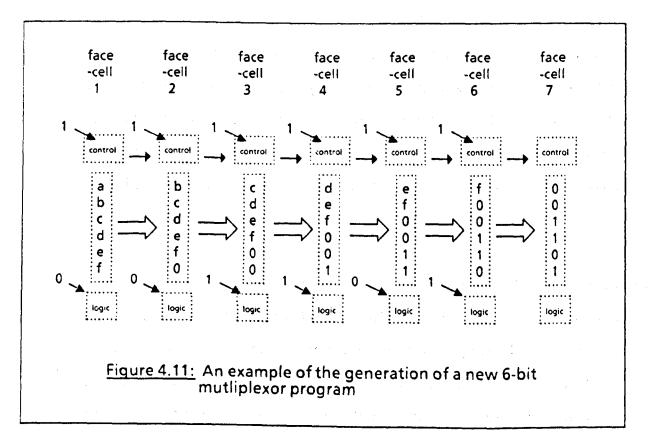

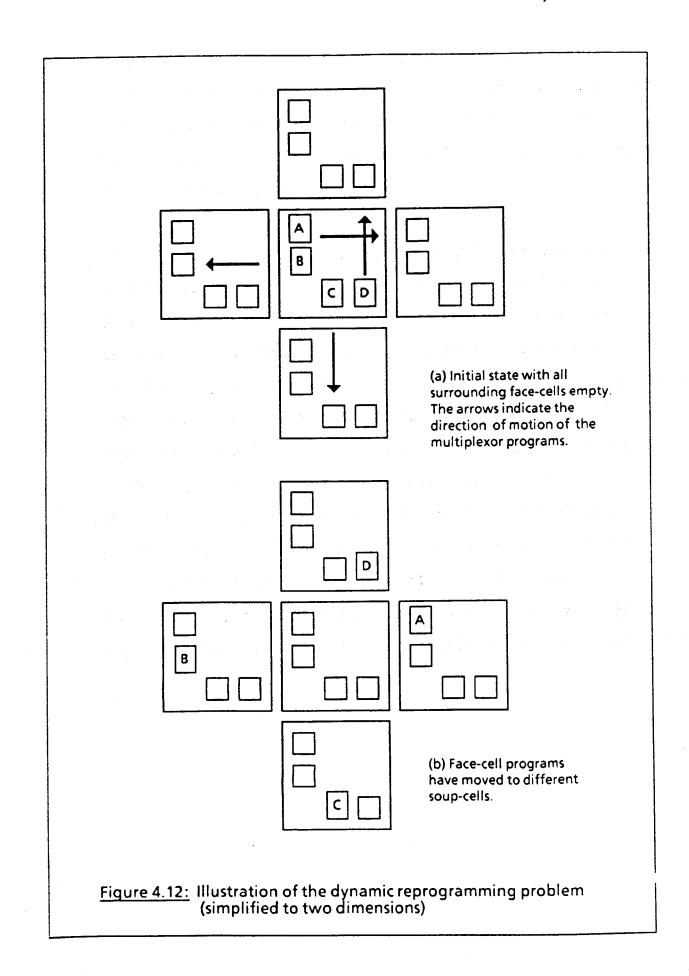

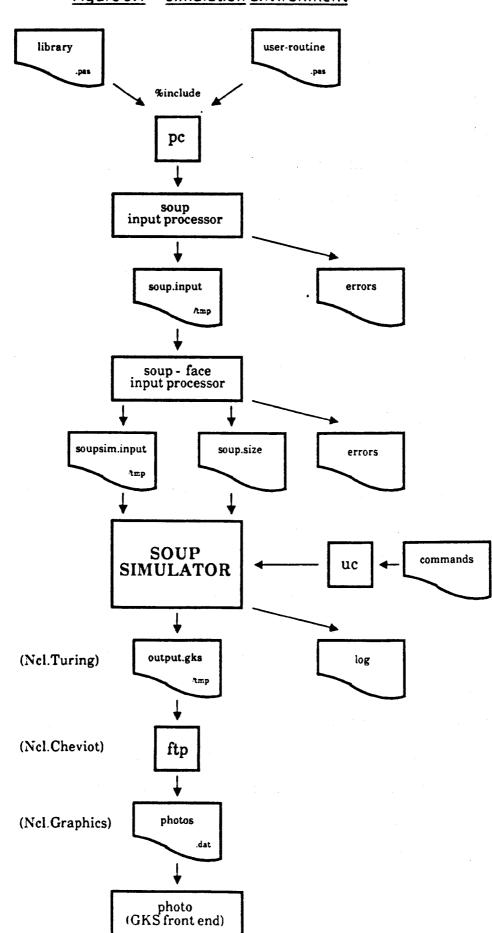

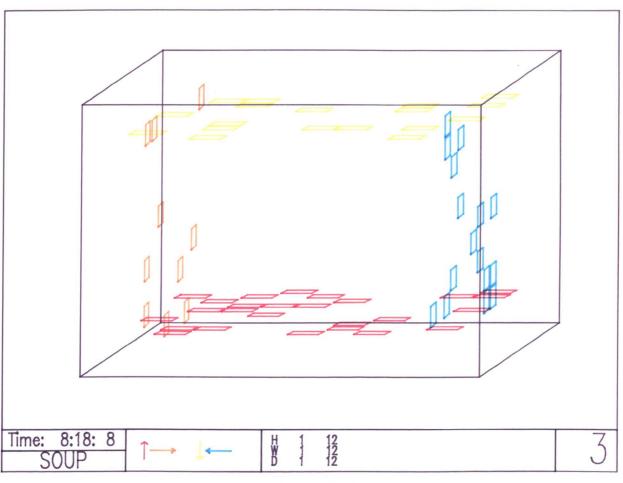

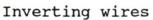

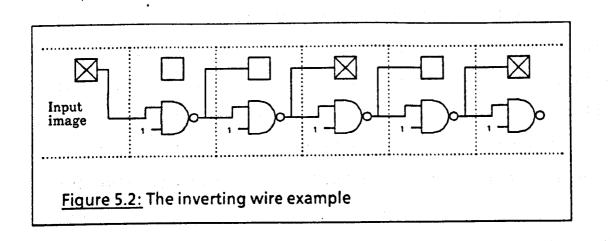

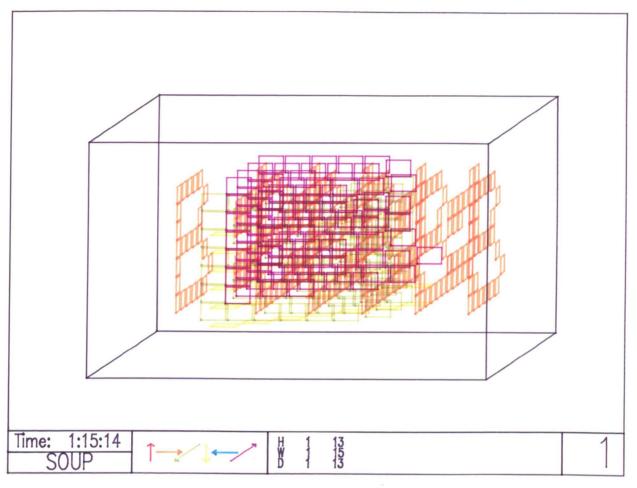

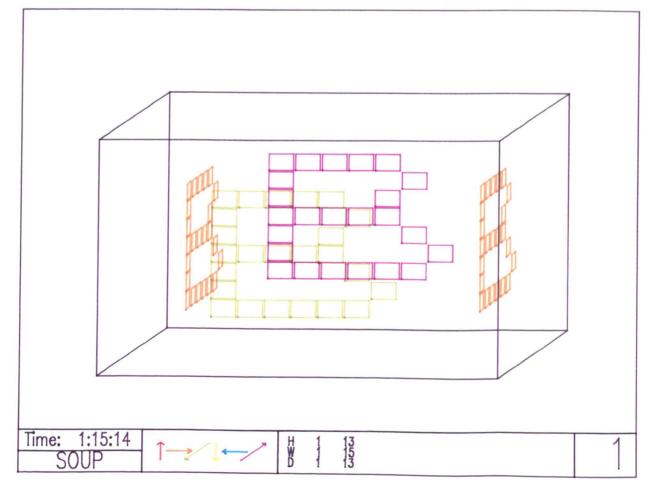

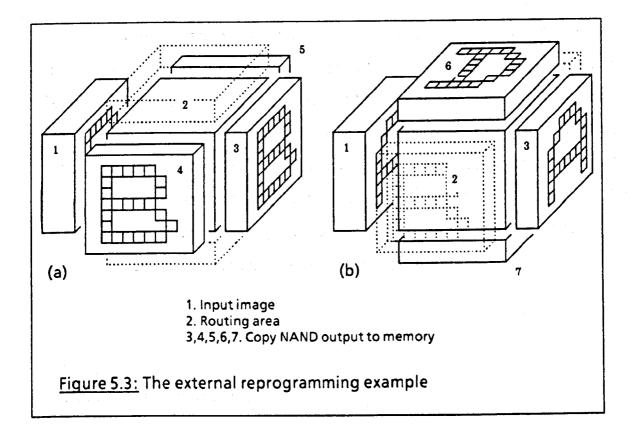

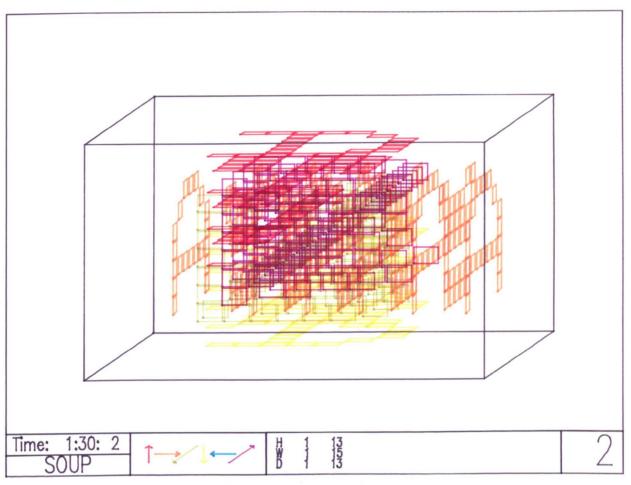

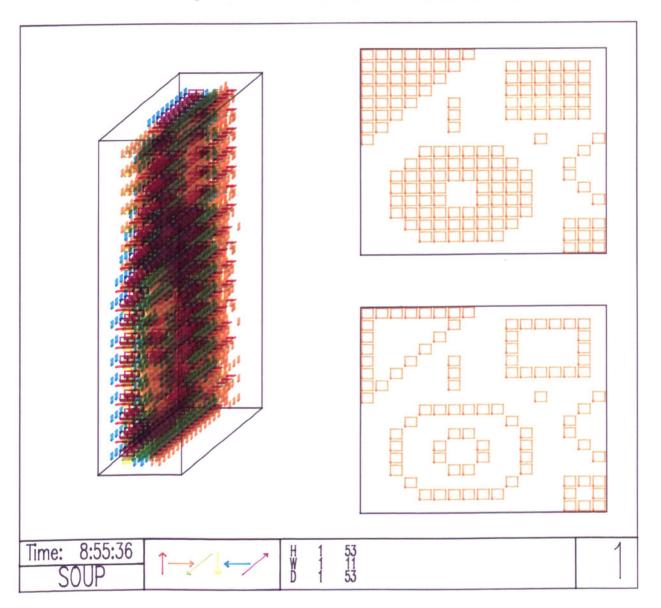

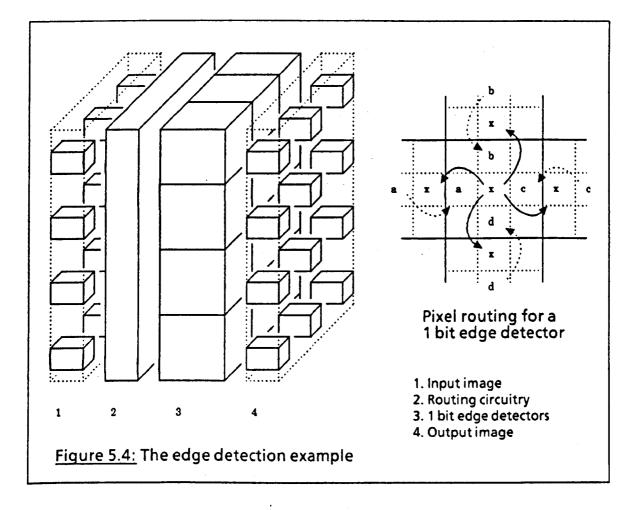

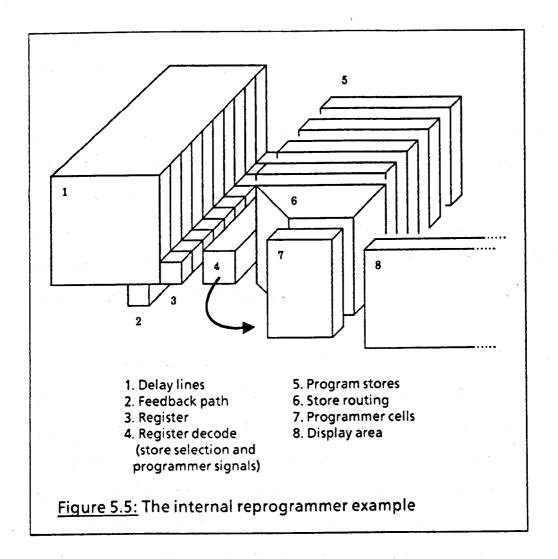

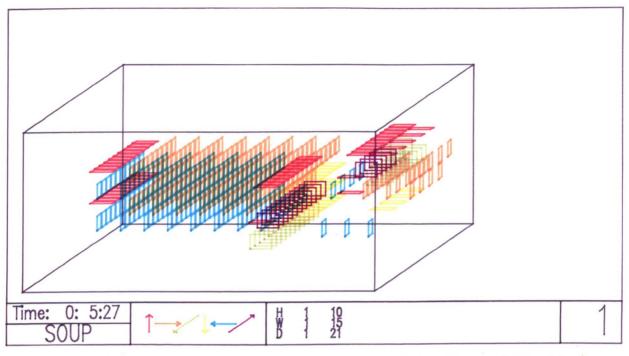

### 3.6 SYNCHRONISATION ISSUES