# Constructing Fail-Controlled Nodes for Distributed Systems: A Software Approach

### Francisco Vilar Brasileiro

NEWCASTLE UNIVERSITY LIBRARY

094 51557 9

Ph.D. Thesis

**University of Newcastle upon Tyne Computing Science Department**

### **Abstract**

Designing and implementing distributed systems which continue to provide specified services in the presence of processing site and communication failures is a difficult task. To facilitate their development, distributed systems have been built assuming that their underlying hardware components are *fail—controlled*, i.e. present a well defined failure mode. However, if conventional hardware cannot provide the assumed failure mode, there is a need to build processing sites or *nodes*, and communication infra–structure that present the fail—controlled behaviour assumed.

Coupling a number of redundant processors within a replicated node is a well known way of constructing fail—controlled nodes. Computation is replicated and executed simultaneously at each processor, and by employing suitable validation techniques to the outputs generated by processors (e.g. majority voting, comparison), outputs from faulty processors can be prevented from appearing at the application level.

One way of constructing replicated nodes is by introducing hardwired mechanisms to couple replicated processors with specialised validation hardware circuits. Processors are tightly synchronised at the clock cycle level, and have their outputs validated by a reliable validation hardware. Another approach is to use software mechanisms to perform synchronisation of processors and validation of the outputs. The main advantage of hardware based nodes is the minimum performance overhead incurred. However, the introduction of special circuits may increase the complexity of the design tremendously. Further, every new microprocessor architecture requires considerable redesign overhead. Software based nodes do not present these problems, on the other hand, they introduce much bigger performance overheads to the system.

In this thesis we investigate alternative ways of constructing efficient fail—controlled, soft-ware based replicated nodes. In particular, we present much more efficient order protocols, which are necessary for the implementation of these nodes. Our protocols, unlike others published to date, do not require processors' physical clocks to be explicitly synchronised. The main contribution of this thesis is the precise definition of the semantics of a software based *fail—silent* node, along with its efficient design, implementation and performance evaluation.

## Acknowledgements

"Mais foi tanto dos vaquêro qui rênô no meu sertão, qui cantano um dia intêro num menajo todos não."

Excerpt from História de Vaqueiros by Elomar.

There are many people who, in one way or another, have helped me during the time this work has been developed, and to whom I shall be forever grateful.

First of all, I would like to thank my supervisor, Dr. Neil Speirs, for the many technical discussions we have had over the past three and a half years and for his comments on earlier drafts of this thesis. A special dept of gratitude is due to Dr. Paul Ezhilchelvan, who gave me invaluable guidance for the work on *order protocols*. I am also grateful for Paul's careful reading of some important parts of this thesis. Further, I would like to express my gratitude to Professor Santosh Shrivastava for his constructive criticisms and continuous stimulus throughout the development of this work. It is my pleasure to acknowledge that part of the work on *fail-silent nodes* was developed in collaboration with Dr. Speirs, Dr. Ezhilchelvan and Professor Shrivastava.

Further thanks go to Sha Tao, Steve Caughey and David Black – fellow members of the Voltan project; and to the staff of the Computing Science Department of Newcastle University; particularly to Shirley Craig, for the tremendous work she does as the Department's librarian.

I am indebted to my colleagues at the Systems and Computing Department of the Federal University of Paraíba (DSC/UFPb) for coping with the extra workload during my absence. I can only hope that in the years to come we will all profit from my experience at Newcastle University.

I should not forget to thank the support and encouragement I have received from my family and friends in Brazil, and from the many new friends I have made whilst in Newcastle. Thanks very much folks!

Last, but not least, I am sincerely grateful to the Federal University of Paraíba which has provided me with institutional support, and to the Brazilian National Research Council (CNPq/Brasil) for their financial support (grant number 201601/91–5).

## **Table of Contents**

| Ackno<br>Table o<br>List of | wledgements ii of Contents iii Figures vii Tables ix |

|-----------------------------|------------------------------------------------------|

| 1. Int                      | roduction 1                                          |

| 1.1.                        | Designing Dependable Computer Systems                |

| 1.2.                        | Fault Tolerance in Distributed Systems               |

|                             | 1.2.1. Constructing Fail–Controlled Nodes            |

| 1.3.                        | Thesis Structure 9                                   |

| 2. De <sub>l</sub>          | pendable Computer Systems                            |

| 2.1.                        | Introduction                                         |

| 2.2.                        | Designing Fault-Tolerant Computer Systems            |

|                             | 2.2.1. Specific Purpose Systems                      |

|                             | 2.2.1.1. Highly–Available Systems                    |

|                             | 2.2.1.2. Long–Life Systems                           |

|                             | 2.2.1.3. Safety–Critical Systems                     |

|                             | 2.2.2. General Purpose Systems                       |

|                             | 2.2.2.1. Mainframes                                  |

|                             | 2.2.2.2. Parallel and Distributed Systems            |

| 2.3.                        | Concluding Remarks                                   |

| 3. Fa  | il-Controlled Replicated Nodes for Distributed Systems . 31 |

|--------|-------------------------------------------------------------|

| 3.1.   | Introduction                                                |

| 3.2.   | Constructing Fail-Controlled Replicated Nodes               |

|        | 3.2.1. Hard Nodes                                           |

|        | 3.2.2. Soft Nodes                                           |

|        | 3.2.3. Hard Nodes versus Soft Nodes                         |

| 3.3.   | Voltan Architecture                                         |

|        | 3.3.1. System Model and Assumptions                         |

|        | 3.3.2. Node Architecture                                    |

| 3.4.   | Concluding Remarks                                          |

| 4. Soi | ft Failure–Masking Nodes 62                                 |

| 4.1.   | Introduction                                                |

| 4.2.   | Reference Design                                            |

|        | 4.2.1. Standard Voter Protocol                              |

|        | 4.2.2. Order Protocol with Synchronised Clocks              |

| 4.3.   | Efficient Order Protocols                                   |

|        | 4.3.1. A Protocol without Explicit Clock Synchronisation    |

|        | 4.3.1.1. Protocol Description                               |

|        | 4.3.1.2. Protocol Correctness                               |

|        | 4.3.1.3. Protocol Performance                               |

|        | 4.3.1.4. Finite Upper Bound on $\pi$                        |

|        | 4.3.2. Reducing the Protocol Stability Delay for TMR nodes  |

|        | 4.3.2.1. Protocol Description                               |

|        | 4.3.2.2. Protocol Correctness                               |

|        | 4.3.2.3. Protocol Performance                               |

|    |      | 4.3.3. An <i>Early–Order</i> Protocol for Nodes with <i>fifo</i> Internal Channels 92 |

|----|------|---------------------------------------------------------------------------------------|

|    |      | 4.3.3.1. Protocol Description                                                         |

|    |      | 4.3.3.2. Protocol Correctness                                                         |

|    |      | 4.3.3.3. Protocol Performance                                                         |

|    | 4.4. | Node Overhead Analysis                                                                |

|    |      | 4.4.1. Voting Overhead                                                                |

|    |      | 4.4.2. Ordering Overhead                                                              |

|    |      | 4.4.2.1. Stability Delay                                                              |

|    |      | 4.4.2.2. Intra–Node Message Traffic                                                   |

|    | 4.5. | Concluding Remarks                                                                    |

| 5. | Sof  | t Fail-Silent Nodes 109                                                               |

|    | 5.1. | Introduction                                                                          |

|    | 5.2. | Reference Design                                                                      |

|    |      | 5.2.1. Comparison Protocol                                                            |

|    |      | 5.2.2. Order Protocol with Synchronised Clocks                                        |

|    | 5.3. | Efficient Order Protocols                                                             |

|    |      | 5.3.1. Improving the Synchronised Clock Protocol                                      |

|    |      | 5.3.2. Order Protocol with Logical Clocks                                             |

|    |      | 5.3.3. Asymmetric Order Protocol                                                      |

|    | 5.4. | Comparison Protocols                                                                  |

|    | 5.5. | Node Overhead Analysis                                                                |

|    | 5.6. | Concluding Remarks                                                                    |

| 6. | Im   | plementation and Performance Evaluation of Soft                                       |

|    | Rej  | olicated Nodes                                                                        |

|    | 6.1. | Introduction                                                                          |

| 6.2.   | Implementation Details                                                | 0 |

|--------|-----------------------------------------------------------------------|---|

|        | 6.2.1. System Services                                                | 1 |

|        | 6.2.2. Communication Layer                                            | 5 |

|        | 6.2.3. Replication Layer                                              | 6 |

| 6.3.   | Performance Evaluation                                                | 9 |

|        | 6.3.1. Nodes Description                                              | 9 |

|        | 6.3.2. Experiments Description and Evaluation                         | 1 |

| 6.4.   | Concluding Remarks                                                    | 3 |

| 7. Red | configurable Replicated Nodes 160                                     | 6 |

| 7.1.   | Introduction 166                                                      | 6 |

| 7.2.   | Reconfigurable Fault-Tolerant Systems 16                              | 7 |

| 7.3.   | Constructing Reconfigurable Replicated Nodes                          | 8 |

|        | 7.3.1. Constructing Reconfigurable Nodes from Fail–Safe Components 18 | 1 |

|        | 7.3.2. Improving Node Performance via Reconfiguration                 | 4 |

| 7.4.   | Concluding Remarks                                                    | 6 |

| 8. Co  | nclusions                                                             | 7 |

| 8.1.   | Discussion                                                            | 7 |

| 8.2.   | Directions for Further Research                                       | 2 |

| 8.3.   | Concluding Remarks                                                    | 3 |

| Appei  | ndix A: Correctness Proof of Order Protocols 195                      | 5 |

| A.1.   | System Assumptions, Definitions and Notations                         | 5 |

| A.2.   | Proof of Correctness of the Protocol of Section 4.3.1                 | 7 |

| A.3.   | Proof of Correctness of the Protocol of Section 4.3.2                 | 2 |

| A.4.   | Proof of Correctness of the protocol of Section 4.3.3                 | 5 |

| Refer  | ences                                                                 | 1 |

## **List of Figures**

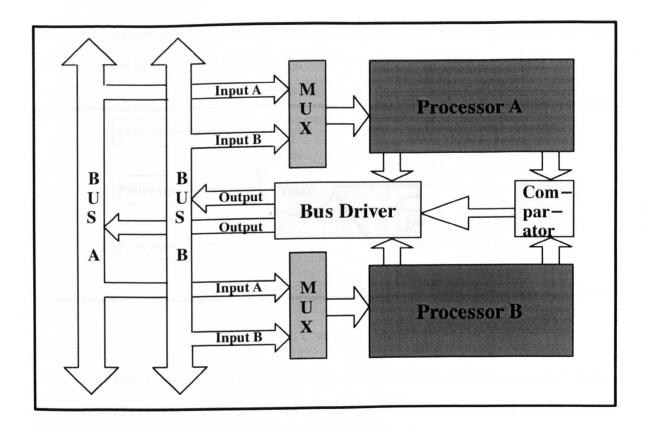

| Figure 3–1:  | Stratus fail–silent node                                          | 39 |

|--------------|-------------------------------------------------------------------|----|

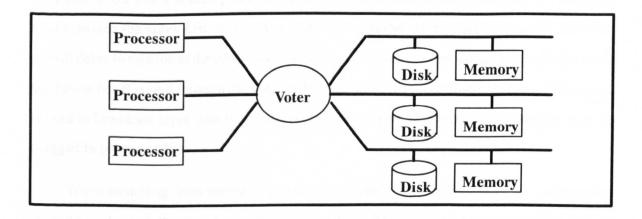

| Figure 3–2:  | C.vmp configuration                                               | 40 |

| Figure 3–3:  | C.vmp voter multiplexing circuit                                  | 40 |

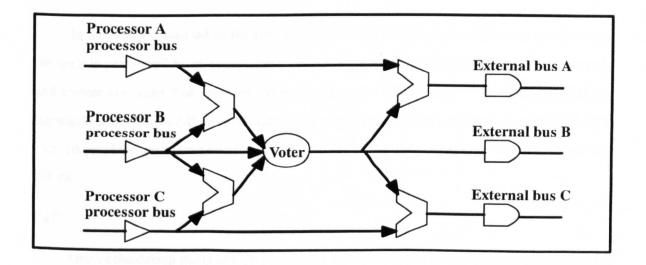

| Figure 3–4:  | FTP input dissemination circuit                                   | 42 |

| Figure 3–5:  | SIFT architecture                                                 | 45 |

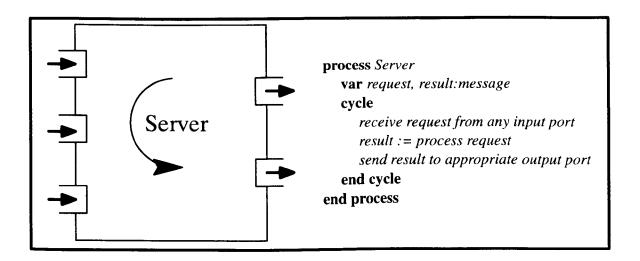

| Figure 3–6:  | Unreplicated 'server'                                             | 51 |

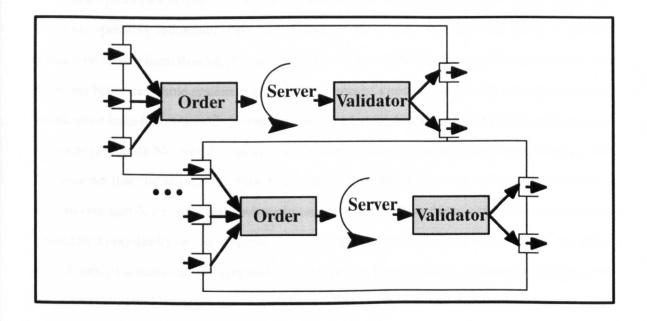

| Figure 3–7:  | Replicated 'server'                                               | 52 |

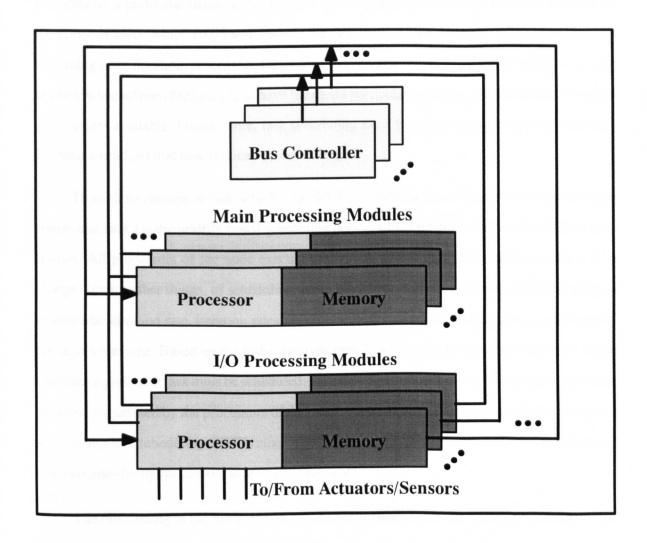

| Figure 3–8:  | Voltan node                                                       | 56 |

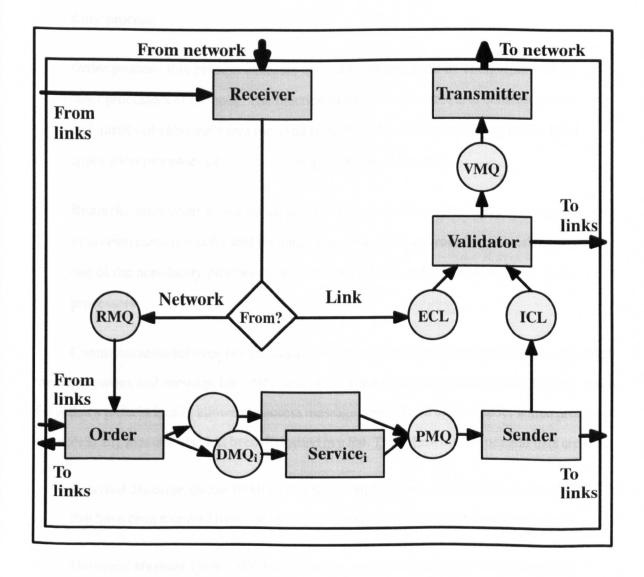

| Figure 3–9:  | Receiver process                                                  | 58 |

| Figure 3–10: | Sender process                                                    | 59 |

| Figure 3–11: | Transmitter process                                               | 59 |

| Figure 4–1:  | Voter process                                                     | 64 |

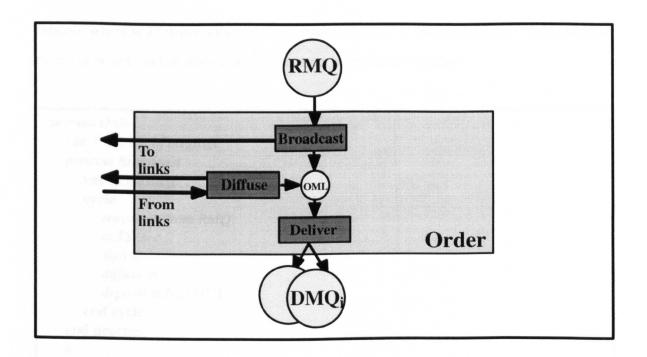

| Figure 4–2:  | Order process structure                                           | 67 |

| Figure 4–3:  | Order process for reference design                                | 68 |

| Figure 4–4:  | Send primitive                                                    | 73 |

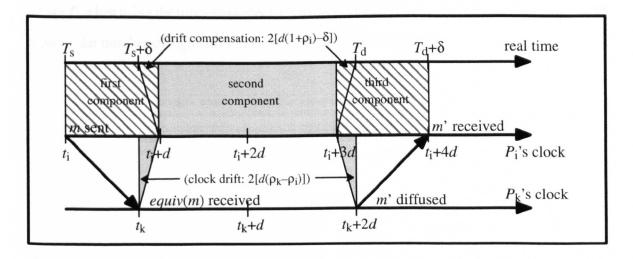

| Figure 4–5:  | Compensating the difference between the drift of clocks in an NMR | 75 |

| Figure 4–6:  | Time diagram for timeliness check C1                              | 77 |

| Figure 4–7:  | Update process for an order protocol based on logical clocks      | 79 |

| Figure 4–8:  | Order process for an order protocol based on logical clocks       | 80 |

| Figure 4–9:  | Broadcast process for an order protocol based on logical clocks   | 81 |

| Figure 4–10: | Diffuse process for an order protocol based on logical clocks     | 81 |

| Figure 4–11: | Deliver process for an order protocol based on logical clocks     | 82 |

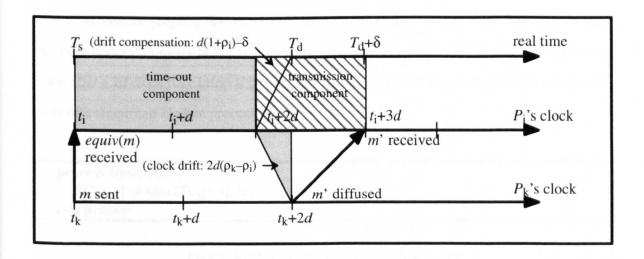

| Figure 4–12: | Compensating the difference between the drift of clocks in a TMR  | 87 |

| Figure 4–13: | Update process for TMR nodes                                      | 88 |

| Figure 4–14: | Broadcast process for TMR nodes                                   | 89 |

| Figure 4–15: | Diffuse process for TMR nodes                                     | 89 |

| Figure 4–16: | Update process for early—order protocol                           | 97 |

| Figure 4–17: | Broadcast process for early–order protocol                                          | 97 |

|--------------|-------------------------------------------------------------------------------------|----|

| Figure 4–18: | Diffuse process for early–order protocol                                            | 98 |

| Figure 4–19: | Deliver process for early-order protocol                                            | 98 |

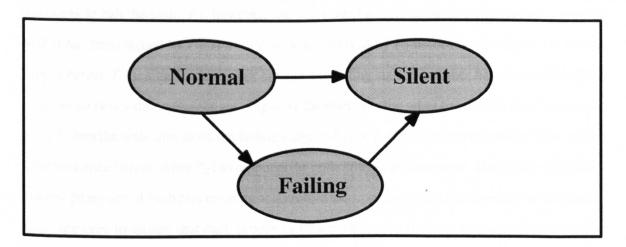

| Figure 5–1:  | State transitions in a fail-silent node                                             | 10 |

| Figure 5–2:  | Comparator process                                                                  | 14 |

| Figure 5–3:  | Order process for synchronised clock based order protocol 1                         | 16 |

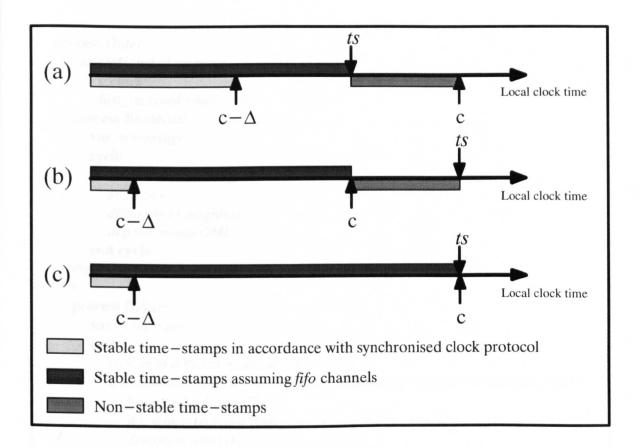

| Figure 5–4:  | Stability intervals                                                                 | 19 |

| Figure 5–5:  | Order process for synchronised clock based order protocol with <i>fifo</i> channels | 20 |

| Figure 5–6:  | Order process for logical clock based order protocol                                | 23 |

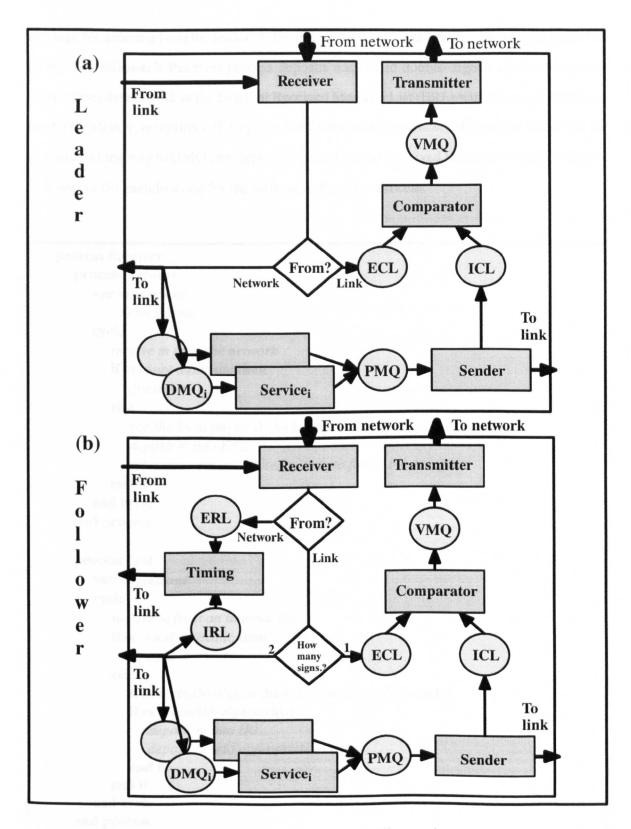

| Figure 5–7:  | Asymmetric fail–silent node                                                         | 26 |

| Figure 5–8:  | Follower's Receiver process 1                                                       | 27 |

| Figure 5–9:  | Timing process                                                                      | 28 |

| Figure 5–10: | Leader's Receiver process                                                           | 29 |

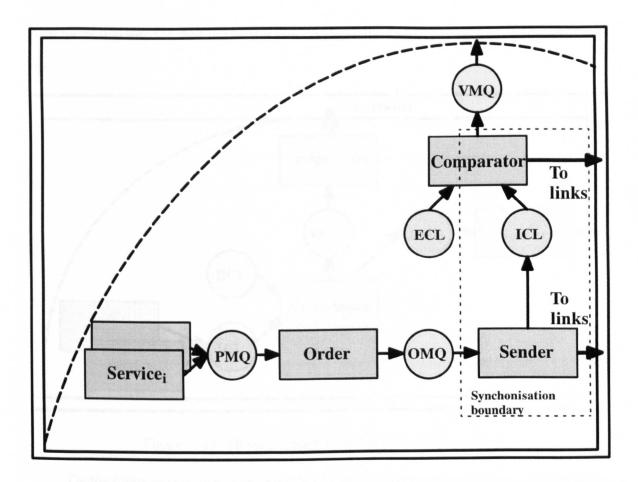

| Figure 5–11: | Extended Voltan fail-silent node 1                                                  | 33 |

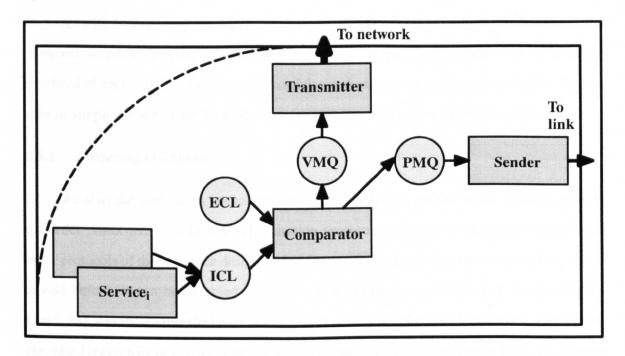

| Figure 5–12: | Message comparison for follower processors                                          | 34 |

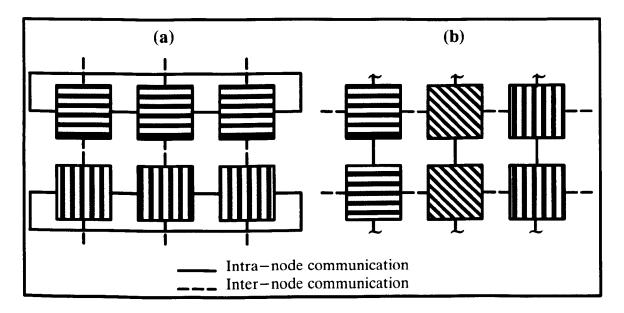

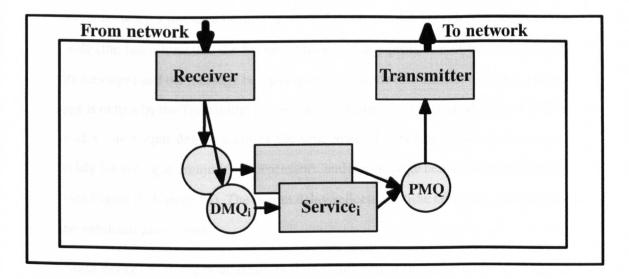

| Figure 6–1:  | Structuring replicated nodes on a six-transputer network                            | 40 |

| Figure 6–2:  | The Active_Object class                                                             | 41 |

| Figure 6–3:  | Active object derived class (Producer)                                              | 42 |

| Figure 6–4:  | Active object derived class (Consumer)                                              | 43 |

| Figure 6–5:  | Connecting active objects                                                           | 43 |

| Figure 6–6:  | Interface of Queue and List classes                                                 | 44 |

| Figure 6–7:  | Interface of Message_Block class 1                                                  | 45 |

| Figure 6–8:  | Sender process for a two-processor fail-silent node                                 | 47 |

| Figure 6–9:  | Sender process for a TMR node                                                       | 48 |

| Figure 6–10: | Unreplicated node model                                                             | 51 |

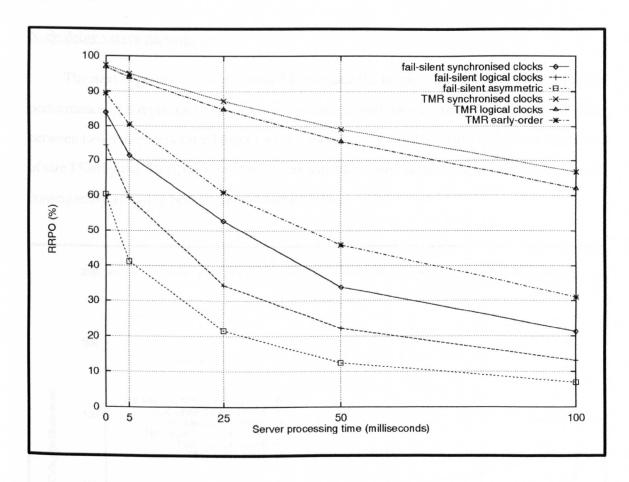

| Figure 6–11: | RRPO versus server processing time                                                  | 58 |

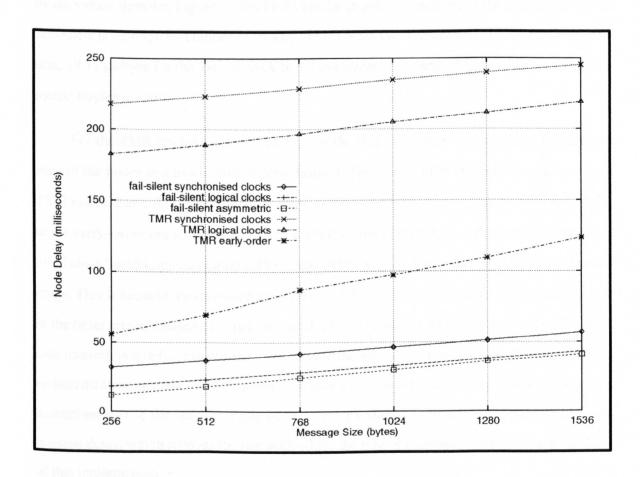

| Figure 6–12: | Node delay versus message size                                                      | 59 |

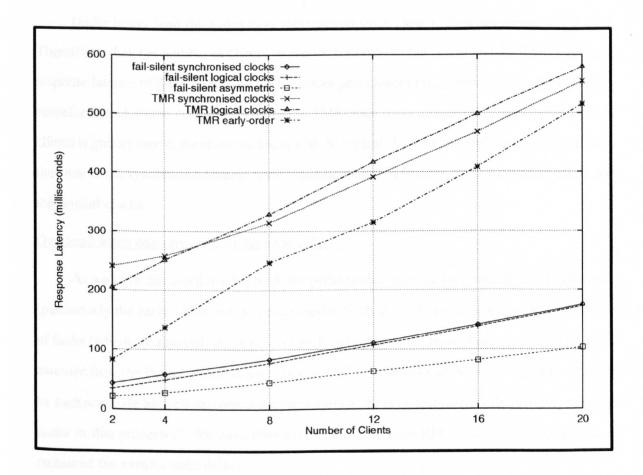

| Figure 6–13: | Node delay versus number of clients                                                 | 61 |

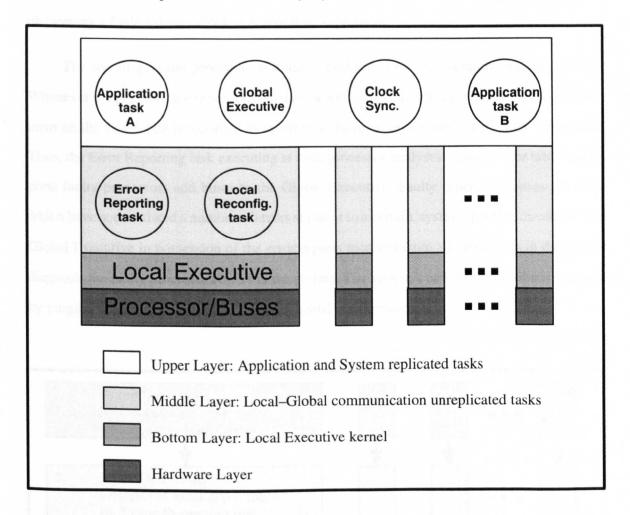

| Figure 7–1:  | Operating system structure of the SIFT system                                       | 68 |

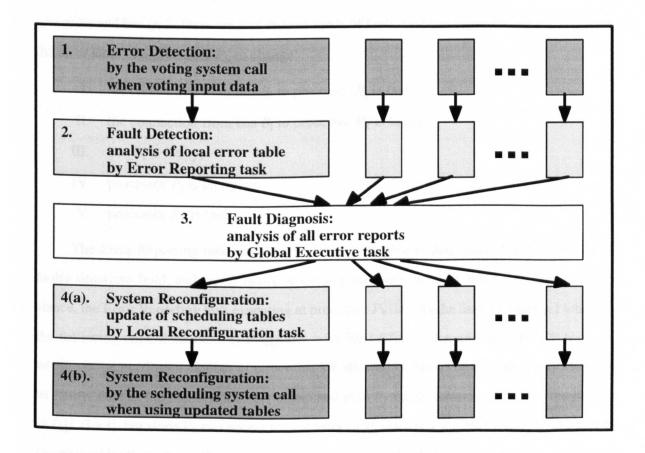

| Figure 7–2:  | Reconfiguration phases                                                              | 69 |

| Figure 7–3:  | Software architecture of the QuadFTP architecture                                   | 73 |

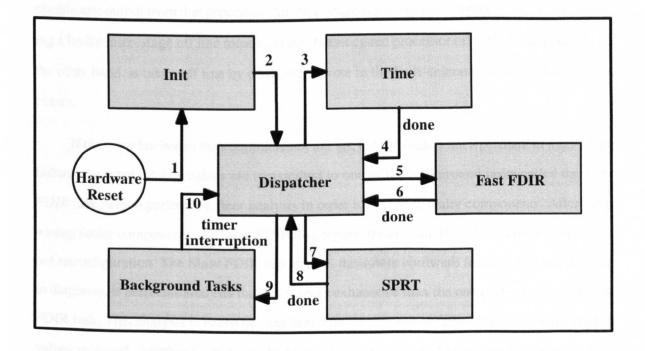

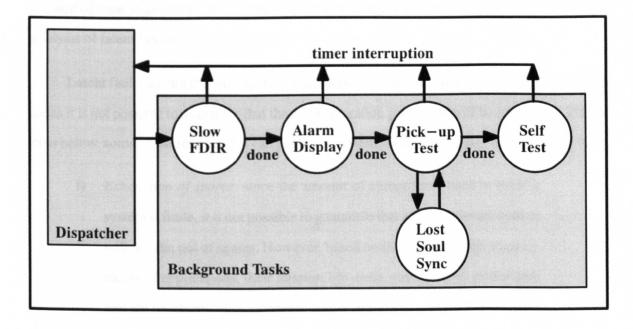

| Figure 7–4:  | Background tasks of the QuadFTP architecture                                        | 76 |

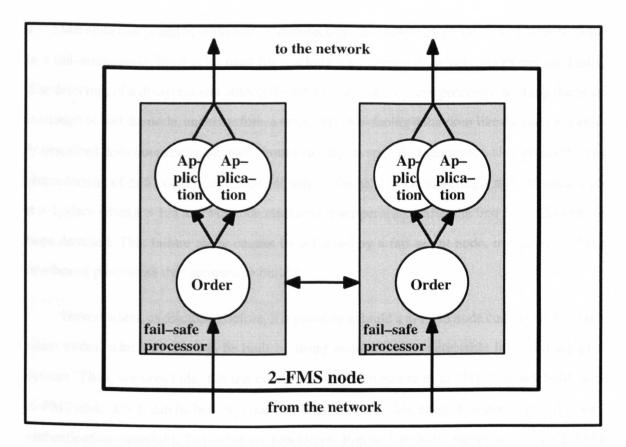

| Figure 7–5:  | Using a pair of fail-safe processors to construct a 2-FMS node 1                    | 82 |

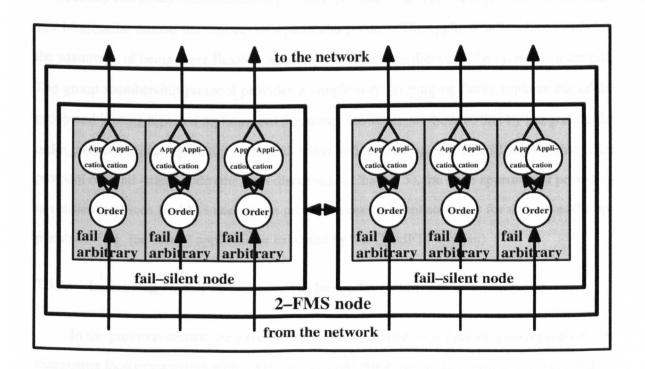

| Figure 7–6:  | Using fail—arbitrary processors to construct FMS nodes                              | 83 |

## **List of Tables**

| Table 2–1: | Common error detection mechanisms for a mainframe                         | 24  |

|------------|---------------------------------------------------------------------------|-----|

| Table 6–1: | Performance overhead for a client–server application on fail–silent nodes | 153 |

| Table 6–2: | Performance overhead for a client–server application on TMR nodes         | 156 |

| Table 6–3: | Response latency and RRPO for a client–server application                 | 157 |

| Table 6–4: | Performance overhead for TMR nodes containing a crashed processor         | 163 |

| Table 7–1: | Local fault diagnosis                                                     | 171 |

## Chapter 1 Introduction

Since their invention, computer systems have been designed to tolerate faults that may occur on their components. Nevertheless, the reasons that have made computer system designers introduce mechanisms for fault tolerance into their designs have changed considerably throughout the years. Changes in the objectives and amount of fault tolerance mechanisms added to computer systems have been driven mainly by two factors: i) the evolution of the technology of components; and ii) the introduction of new applications with new specification requirements to be met.

High failure rates of components such as relays and vacuum tubes, used to build the first generation computers in the nineteen forties and early fifties, made fault tolerance an overwhelming concern to the designers of those systems. However, the rapid evolution of components technology (e.g. transistors/core), which marked the beginning of the second generation of computers, was responsible for a change in the direction of the evolution of fault–tolerant computer systems. The reliability of components was considered to be sufficiently high for the requirements of existing applications, hence the need for any built–in fault tolerance mechanisms was not sensibly felt [Avizienis 78]. Throughout the nineteen sixties and seventies, the specification requirements of applications began to influence the design of fault–tolerant computer systems. Applications such as control of life–support hospital equipment, flight control on commercial airlines, control systems of high–speed trains, safety processes monitoring in industrial installations, launch of vehicles for space exploration projects, electronic telephone switching control and satellite support systems, on which computer failure could place human life in danger or

cause heavy economic penalties, demanded a degree of *dependability*<sup>1</sup> [Laprie 89] which could not be met by existent computer systems. Thus, parallel to the development of general purpose computers, highly dependable specific purpose computer systems started to be developed [Hopkins et al. 78, Ihara et al. 78, Katsuki et al. 78, Rennels 78, Siewiorek et al. 78a, Siewiorek et al. 78b, Toy 78, Wensley et al. 78]. In the past sixteen years, mainly due to the ever increasing number of applications whose specifications incorporate dependability requirements, an increasing number of dependable computer systems have been designed and implemented [FTCS 71–94]. Recently, with the development of parallel and distributed computer systems, dependability has become a major concern not only in the design of specific purpose computer systems, but also in the design of general purpose ones.

### 1.1. Designing Dependable Computer Systems

Fault avoidance and fault tolerance are two complementary approaches for improving the dependability of a computer system. In the first approach, the aim is to avoid the presence of faults in the system. Fault avoidance techniques are mainly concerned with the manufacturing process of the system, and the environmental conditions to which the system is exposed. The utilisation of conservative design methodologies and high quality components in the manufacturing process can considerably reduce the probabilities that the system will fail. Further, when the system is operative, a close control over environmental variables such as temperature, power supply fluctuation and human interference, can reduce even more the probabilities of a fault. Unfortunately,

<sup>1.</sup> Dependability as defined in [Laprie 89] is "that property of a computing system which allows reliance to be justifiably placed on the services it delivers." It can also be understood as a global concept that encloses a number of attributes such as reliability, availability, maintainability, safety, integrity and security. Each of these can be seen as a different perception of the same concept. For instance, in the context of the control system of a nuclear power plant, where a computer failure could cause devastating social and economic losses, dependability is better associated with system reliability, whilst in the context of an electronic telephone switching control system, where failures which cause the system to become unavailable for a long period of time are unacceptable, dependability is better associated with system availability.

extensive use of high quality components can impact the cost of the system immensely. Also, for some computer systems, it is not possible to successfully control or even anticipate the operating environment of the system. These two constraints reduce the feasibility of using fault avoidance techniques as the only means of providing dependability for a large number of systems.

For a more general class of systems, a more flexible approach is to forecast possible faults, and to introduce redundancy into the system in such a way that anticipated faults can be tolerated. The goal of fault tolerance techniques is therefore to guarantee that the system provides its service, with the required dependability, despite the occurrence of faults. Faults are tolerated mainly by the introduction of redundant components that can take over the functionality of faulty ones. Redundancy can also be introduced in the time domain, where faults are tolerated via redundant computation on non–redundant components (e.g. mechanisms for tolerating transient faults [Kopetz et al. 90]).

Design decisions on which fault avoidance techniques to use and which fault tolerance mechanisms to introduce into a computer system, so that it delivers its service with the required degree of dependability, are subject to cost considerations. It is necessary to weigh the cost of using such techniques and mechanisms against the cost of system malfunction, where system malfunction is normally translated as incorrect computation and/or system downtime. As will be seen in Chapter 2, the purpose of a dependable computer system is an important factor when deciding which techniques and mechanisms are appropriate. The more information that is available about the applications, the more accurate is the choice of techniques and mechanisms to be utilised. Thus, one can state that designing dependable, specific purpose systems, where the characteristics of the applications are likely to be known in advance, allows the evaluation of the dependability cost/benefit relation of the system in a much simpler and more precise fashion than when evaluating the same relation for a general purpose architecture, where little is known about the comportment of applications.

In this research we present ways of providing dependable distributed systems with a fault-tolerant processing infra-structure on top of which they can be more easily implemented. Hence, in the next chapter, when discussing the design of various dependable computer systems described in the literature, and studying how fault avoidance techniques and fault tolerance mechan-

isms have been used to implement such systems, we pay special attention to the case of dependable general purpose distributed systems.

### 1.2. Fault Tolerance in Distributed Systems

There are many reasons for the success of distributed computer systems. With the current development level of microprocessor and communication technologies, a distributed computer system composed of a collection of processing sites interconnected by a high–speed network can offer a much better price/performance relation than a traditional centralised mainframe. In some cases, a distributed system can even out–perform a mainframe, and becomes the only feasible solution for applications which require high degree of performance. Also, applications which involve spatially separated machines possess inherent distributed characteristics which can be captured more easily when those applications are to be developed within the framework of a distributed system. Finally, a carefully designed distributed system can potentially be more dependable than a centralised one. To achieve greater dependability, the failure of an isolated processing site, or a network connection, should have small impact, if any, on the operation of the system as a whole.

Of course, distributed systems have also got their drawbacks. The difficulty in designing and programming those systems can be regarded as one of their main problems. Ideally, programming a distributed system should be no more difficult than programming a traditional centralised computer system. This notion is reflected in the following definition of a distributed system from [Tanembaum 92]: "A distributed system is one that runs on a collection of machines that do not have shared memory, yet looks to its users like a single computer."

Aiming to achieve this desirable level of transparency, new programming paradigms such as *remote procedure call* [Birrell–Nelson 84], *atomic transaction* [Lampson 81] and *group communication* [Birman et al. 91] have been proposed. Fault tolerance is one of the many issues that must be faced when designing such programming concepts. Supported by these new programming paradigms, a number of distributed systems, ranging from distributed operating systems [Kopetz–Merker 85, Accetta et al. 86, Mullender et al. 90] to distributed programming toolkits

[Shrivastava 89, Birman et al. 91], have been developed. All these systems incorporate, to a great or a lesser extent, the notion of fault tolerance.

Experiences in constructing distributed systems which continue to provide specified services in the presence of processing site and communication failures, have shown that designing and implementing such systems is a difficult task. In a perfect world, one would like to construct a distributed system using hardware components which are guaranteed to be either failure—free or to have well defined failure modes. However, all hardware components must fail eventually, possibly in an unpredictable manner. A sensible approach, taken by the designers of a considerable number of dependable distributed systems reported in the literature (e.g. [Bartlett 81, Kopetz—Merker 85, Shrivastava 89, Powell 92, Birman et al. 91]), is to build their systems assuming that the underlying hardware components of a distributed system are *fail—controlled* [Laprie 89], i.e. present a well defined failure mode, and then build processing sites or *nodes* and communication infra–structure that do indeed present the fail—controlled behaviour assumed.

The complexity of the fault tolerance mechanisms implemented at an upper software level of a dependable distributed system reflects the assumptions made upon the underlying hardware where the software is going to be executed. Many dependable systems reported in the literature have been built under the assumption that they execute on nodes that fail safely [Laprie 89], i.e. a faulty node will halt, rather than perform an unspecified transition. Nodes with this failure semantics are referred as *fail–safe nodes*. *Fail–stop nodes* [Schlichting–Schneider 83, Schneider 84] and *fail–silent nodes* [Bernstein 88, Shrivastava et al. 91, Shrivastava et al. 92, Webber–Beirne 91, Brasileiro et al. 92, Reisinger–Steininger 93] are two representatives of this class of fail–controlled nodes. Other systems assume that nodes are failure–free, hence they must execute on nodes that are able to guarantee proper functioning for the entire duration of the mission of the applications in question. *Failure–masking nodes* [Hopkins et al. 78, Wensley et al. 78, Siewio-rek et al. 78a, Smith 84, Lala 86, Theuretzbacher 86, Shrivastava et al. 91, Shrivastava et al. 92, Powell 92, Speirs et al. 93] form another class of fail–controlled nodes, which are able to mask failures and therefore deliver proper service with arbitrary high probability.

On the other hand, the assumption of which failure semantics to use for the underlying hardware depends not only on the hardware characteristics itself, but also, among other para-

meters, on the dependability requirements and the mission lifetime of the applications to be executed. If conventional hardware cannot provide, with sufficiently high probability, the failure semantics assumed (for the duration of the mission of the applications they are executing), there is a need to construct nodes which guarantee the required failure semantics. It has been observed that 'off—the—shelf' processors do fail in an arbitrary way [Lala 86, Harper et al. 88]. Furthermore, for an increasing number of applications, the probability with which conventional processors fail in an arbitrary way is high enough to rule out their utilisation as fail—controlled underlying nodes for dependable computer systems.

In this thesis we present ways of using 'off-the-shelf' processors to construct nodes with different fail-controlled behaviour. We discuss the design of both failure-masking nodes (Chapter 4) and fail-silent nodes (Chapters 5), together with their implementation and performance analysis (Chapter 6). Then, in Chapter 7, we discuss the design of reconfigurable fail-controlled nodes which possess characteristics of both failure-masking and fail-silent nodes.

### 1.2.1. Constructing Fail-Controlled Nodes

Constructing a fail—controlled node from components that can fail in an arbitrary way involves necessarily the introduction of redundant components. One way to do this is by adding to the design self—checking logic such as error detection codes, watch-dog timers, power supply monitors, temperature monitors, etc. A problem with this approach is that achieving high error detection coverage is normally difficult. Furthermore, there is an interval of time between the occurrence of a failure and its detection by a checking circuit, during which the node can potentially present an undesirable behaviour.

Both the degree of error detection coverage and the length of the detection delay depend on the amount of redundancy introduced in the form of checking circuits. A great amount of redundant components reduces the detection delay, and increases error detection coverage, but at the same time increases the complexity and the cost of the node. In [Reisinger–Steininger 93] a fail—controlled node based on the introduction of self—checking logic is presented, whose error detection coverage is estimated to be better than 99% [Kopetz et al. 90]. The choice of the amount

and the kind of self-checking mechanisms introduced in that node is simplified by taking advantage of an a priori knowledge of specific characteristics of the system.

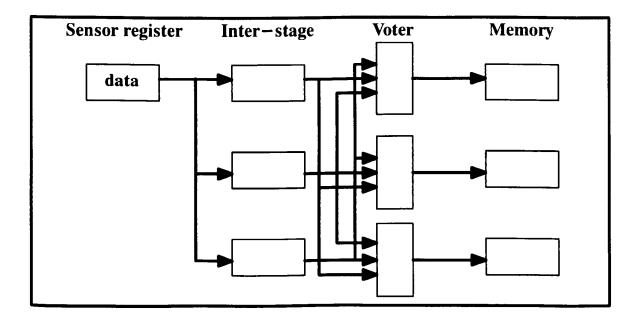

Another approach is to couple redundant processors within a *replicated node*. A fail—controlled replicated node is composed of a number of processors which fail independently. Computation is replicated and executed simultaneously at each processor. By employing a suitable validation technique to the outputs generated by the replicated processors (e.g. majority voting, comparison), outputs from faulty processors can be prevented from appearing at the application level. Error detection coverage in a replicated node is extremely high, since it depends exclusively on the design of a simple validation mechanism. Further, if the communication mechanisms of the system ensures that information is validated before being used at the upper application level, then damage is confined to the lower node level even when there is a substantial delay in the detection of errors.

Distributed applications are normally structured as a set of tasks executing in parallel, which do not share memory, and communicate only via messages exchange. Thus, replicated nodes can provide an attractive solution for the problem of constructing fail—controlled nodes for dependable distributed systems. A number of ways of constructing replicated nodes have been reported in the literature [Hopkins et al. 78, Toy 78, Smith 84, Lala 86, Bernstein 88, Webber—Beirne 91]. Those nodes are based on hardwired mechanisms to couple replicated processors with specialised validation hardware circuits (e.g. comparator, voter). Processors are tightly synchronised at the clock cycle level, and have their outputs validated at appropriate times by a reliable validation hardware. Another strategy, pioneered by the designers of the SIFT system [Wensley et al. 78], is to implement fail—controlled replicated nodes by using software mechanisms to perform both synchronisation of redundant processors and validation of the outputs of the node. Later in this thesis we discuss in more detail how replicated nodes following each of these approaches have been designed and implemented.

The main advantages of the hardware based nodes are the minimum performance overhead incurred, and the small impact that the architecture imposes on the software design process. However, there are also some problems with this approach. Firstly, individual processors must be built in such a way that they have a deterministic behaviour at each clock cycle. This can rule out the

utilisation of 'off-the-shelf' processors, whose reliability is normally higher than specially designed processors [Siewiorek-Swarz 92]. Secondly, the introduction of special circuits such as reliable comparator/voter and synchronisation mechanisms increases the complexity of the design, which at an extreme can result in a decrease in the overall node reliability. Finally, every new microprocessor architecture requires a considerable redesign overhead.

The advantages of the software based nodes are very much the converse of the drawbacks discussed above. The absence of tight synchronism allows the utilisation of 'off—the—shelf' processors. Further, by employing different types of processors within a node, there is a possibility that a measure of tolerance against design faults in processors can be obtained, without recourse to any specialised hardware assistance. Another advantage is that software protocols are much more flexible than their hardware counterparts. Also, the fact that the redundancy management protocols are implemented in software, allows the design of the underlying hardware to be made much simpler and possible to scale. Finally, technology upgrades appear to be easy, as the principles behind the protocols do not change, and software protocols can be ported relatively easily to any type of processor (including those expected to be available in the future).

Unfortunately, these advantages do not come for free. The synchronisation strategy of software based nodes normally imposes rules in the way that applications must be programmed, which might increase the complexity and/or introduce limitations on the development of applications. Furthermore, the extra overhead in performance imposed by the execution of the redundancy management protocols can be substantial. The first problem is less critical within the framework of some of the solutions presented in the literature [Schneider 84, Schneider 90, Shrivastava et al. 91, Shrivastava et al. 92]. There is however, a major concern over the performance overhead incurred by the redundancy management protocols. In SIFT, for instance, the overhead associated with redundancy management can consume as much as 80% of the processor throughput [Palumbo–Butler 85].

Hybrid solutions, which incorporate both tight synchronisation and software synchronisation mechanisms, have been proposed to reduce this overhead. MAFT [Kieckhafer et al. 88], FTP-AP [Lala-Alger 88] and Delta-4 [Powell 92] are hybrid architectures which share the same general structure. These architectures are structured around a tight synchronised hard core, on

top of which conventional processors are replicated. The tight synchronised hard core is responsible for executing management functions, whilst application processes are executed at the upper level replicated processors. The extra computational power delivered by the replicated processors increases the throughput of the system, and provides all the advantages of the software synchronisation approach; however, the underlying hard core re–introduces the problems associated with tight synchronisation.

The work in this thesis investigates alternative ways of constructing efficient fail—controlled replicated nodes based solely on the utilisation of 'off—the—shelf' processors (which can fail in an arbitrary way, although restricted by authentication capabilities [Strong et al. 90]) and software protocols to control system redundancy, without recourse to any specialised hardware. In particular, we present much more efficient order protocols, which are necessary for the implementation of both failure—masking and fail—silent nodes. The precise definition of the semantics of a software based fail—silent node, along with its efficient design, implementation and performance evaluation, are the main contributions of this thesis. Other contributions are:

- i) design and implementation of efficient protocols for the construction of software based failure-masking nodes;

- performance evaluation of software based fail—controlled nodes, which indicates the feasibility of the utilisation of such nodes in a wide range of applications; and

- before stopping nodes composed solely of conventional processors, without recourse to specialised hardware. (This proves false a conjecture in [Shrivastava et al. 91], which argued the impossibility of constructing such nodes.)

#### 1.3. Thesis Structure

The remainder of this thesis is structured as follows. In Chapter 2 we study several fault-tolerant computer systems, emphasising the impact of the purpose of the system on the decision

of the amount and kind of fault tolerance mechanisms used to provide systems with their required dependability. We show how the design of fault-tolerant distributed systems can be simplified, by assuming that the underlying processing and communication hardware possesses a well defined failure mode. Then, in Chapter 3, we discuss how replicated nodes can be used as a means of providing fail—controlled behaviour for the underlying processing hardware of a distributed computer system. We analyse how redundant processors are used, and how redundancy is controlled, in order to build nodes with different fail—controlled behaviour. Then, we compare the hardware and software based approaches to the control of redundancy when constructing fail—controlled nodes, highlighting the advantages and drawbacks of each approach. Finally, a general model for the construction of software based fail—controlled nodes is presented.

The model presented in Chapter 3 indicates that the key issues to be tackled when designing a software based replicated node are the provision of efficient protocols for ordering the messages to be input by the node, and for validating the messages to be output by the node. In Chapter 4, the design of failure—masking nodes is presented. Order protocols are studied in detail. [Shrivastava et al. 92] presents a software based failure—masking node, which incorporates an order protocol based on having the replicated clocks of the node synchronised within a known bound. We present new order protocols that do not need physical clocks to be explicitly synchronised. We also take into account the characteristics of the nodes we are constructing to present order protocols which are more efficient than the ones reported in the literature. The protocols presented are then applied to the important case of a Triple Modular Redundant (TMR) node, where the performance of the order protocols can be further improved. The correctness proof of the protocols is sketched, and their performance is analysed. An extended correctness proof of the protocols presented can be found in Appendix A.

[Shrivastava et al. 92] also indicates how a software based fail—silent node can be derived from the failure—masking node presented in that paper. In Chapter 5 we show that the reduced redundancy of fail—silent nodes introduces additional complications, particularly in the validation protocol (a comparison protocol), which, if not treated with due care, can lead the node to present an unpredictable behaviour. We then define the precise semantics of a software based fail—silent node [Brasileiro et al. 92]. A two—processor fail—silent node is the cheapest fail—con-

trolled node that can be constructed using 'off-the-shelf' replicated processors, thus we concentrate on the design of a two-processor fail-silent node, and introduce two new order protocols for this node. Based on the insights gained whilst developing order protocols, we have designed a comparison protocol that guarantees, with efficiency, the correct semantics of a fail-silent node. The chapter is concluded with a discussion of this comparison protocol.

Chapter 6 is devoted to the discussion of the implementations of three-processor failure-masking nodes (TMR nodes) and two-processor fail-silent nodes. Several versions of the nodes have been implemented using the different protocols presented in Chapter 4 and Chapter 5. A set of experimental distributed applications was executed using the fail-controlled nodes as platform, and the performance figures obtained for each implementation were analysed. The results indicate the feasibility of using the nodes implemented for a wide class of applications.

Fail—silent nodes take the conservative approach of stopping as soon as a failure is detected. On the other hand, failure–masking nodes are designed to survive a bounded number of failures. However, this masking property can also hide the fact that failures have occurred and have reduced the fault tolerance capabilities of the node. When the masking capabilities of the node have been totally degraded, a further failure can lead to catastrophic results. Thus, it is desirable to design a fail-controlled node which could incorporate the safety property of fail-silent nodes, as well as the survivability property of failure-masking nodes. In [Shrivastava et al. 91] the notion of a failure-masking before stopping node (FMS node) is presented. Such a node should be able to mask a number of failures up to a point where a further failure would potentially have catastrophic effects. At this point the node should fail safely, thus avoiding the potential catastrophic effects of a further failure. In [Shrivastava et al. 91] the authors conjecture that it is not possible to build such nodes from 'off-the-shelf' processors, which can potentially fail in an arbitrary way. In Chapter 7 we discuss reconfigurable replicated nodes. We study how dependable systems reported in the literature have incorporated reconfiguration as a means to improve system dependability. We then show that the conjecture in [Shrivastava et al. 91] is false, by presenting the design of an FMS node composed merely of 'off-the-shelf' processors, without recourse to any specialised hardware. Finally, in Chapter 8, we present our conclusions and directions for further research.

## Chapter 2 Dependable Computer Systems

### 2.1. Introduction

Fault avoidance and fault tolerance are the two complementary approaches that can be taken in order to provide a computer system with the ability of dependably delivering its specified service. Fault avoidance techniques try to minimise the probability with which faults manifest themselves within the system. On the other hand, the goal of fault tolerance is to guarantee that the system provides its service with the required dependability, despite the occurrence of faults.

Fault avoidance techniques are mainly concerned with the manufacturing process of the system, and the environment conditions to which the system is exposed. During the manufacturing process, the dependability of the system is increased by means of conservative design methodologies and the utilisation of high quality components. When the system is operative, close control must be exercised over environment variables such as temperature, power supply fluctuation and human interference, so that failure rates can be kept extremely low.

The basic principle of fault tolerance is the introduction of redundancy into the system. Redundancy can be introduced in either time or resources. For instance, a processor which tolerates transient faults by simply computing the same operation several times in succession (e.g. [Kopetz et al. 90]) is an example of fault tolerance attained through time redundancy. On the other hand, a system that tolerates faults occurring on a bus by having a duplicated bus configuration (e.g. [Bartlett 81]) is an example of fault tolerance achieved by means of resource redundancy.

Extensive use of high quality components has an immense impact on system cost. Furthermore, since most of the time designers cannot control or even anticipate the operating environment of the system, fault avoidance alone is not suitable for attaining the dependability requirements of a large number of computer systems. Thus, in the discussion to follow, we concentrate on fault tolerance mechanisms, rather than fault avoidance techniques, as the main means of achieving dependability for a more general class of systems.

### 2.2. Designing Fault-Tolerant Computer Systems

A computer system is composed of a number of components which are bounded together, and interact in a well defined way to provide a specified service. The behaviour of a component can be specified as a function of its internal state, the state transitions that it should perform, and possible outputs that it should produce in response to specified input stimuli. A component failure occurs when the behaviour of the component first deviates from its specification. A failure, therefore, can be attributed to either an erroneous transition, or to a sequence of valid transitions initiated from an erroneous state. In both cases the system has experienced the manifestation of a fault [Laprie 89]. To summarise, there is a cause/effect relationship that is represented by the chain fault-error-failure, and can be interpreted in the following way: the manifestation of a fault can give rise to errors in the internal state of a component, which can lead to the failure of the component. The ultimate intent of fault tolerance is to prevent failures in internal components causing the system to fail in delivering its service. A fault-tolerant computer system is designed to tolerate a finite and bounded number of failures that its components may suffer. Hence, fault-tolerant systems must provide mechanisms to deal with both faults and errors, so that a finite number of failures of the components of the system do not cause the system to deviate from its specified behaviour.

In [Lee-Anderson 90] four constituent phases of fault tolerance are identified. The first three phases – error detection, damage confinement and assessment, and error recovery – are related to error treatment mechanisms, whilst the last phase is related to fault treatment mechanisms, and encompasses fault diagnosis and location, system repair, and continued system service. It is worth noting that there is no strict order on the execution of actions associated with each of

the phases listed above, furthermore, in many fault-tolerant systems it is not always possible to match a particular mechanism with a particular phase. Nevertheless the discussion of each phase in isolation is useful to indicate to the reader how fault-tolerant computer systems are structured.

- i) Error detection: fault-tolerant systems must first learn of the manifestation of faults before attempting to tolerate any fault it is designed to tolerate. Hence, fault tolerance mechanisms are usually triggered by the detection of errors in the internal state of the system. This implies that error detection mechanisms are a crucial issue in the design of many fault-tolerant system. Replication, timing checks, reversal checks and coding, form the set of most popular techniques to implement error detection mechanisms (see [Lee-Anderson 90] for more details on these techniques).

- ii) Damage confinement and assessment: error detection mechanisms try to attain the maximum possible coverage of error detection. There is however a detection latency delay, which corresponds to the interval of time since the manifestation of a fault until the detection of an error caused by that fault, during which, damage can be spread throughout the system. The longer the detection latency, the greater the possibility and the extent of damage proliferation. Therefore, although error detection mechanisms are capable of identifying the manifestation of a fault, they cannot guarantee that all of the unwanted consequences of a fault are detected. It is necessary to adopt strategies for damage assessment, before any error recovery can take place. Damage is normally spread via the flow of information (data and control signals), therefore damage assessment must be based on assumptions about the structure of the system. In order to have damage proliferation minimised, the system must be structured in such a way that the flow of information is well defined and controlled.

- iii) Error recovery: mechanisms for error detection and damage confinement do not change the system in any way. Thus, these mechanisms alone

do not allow systems to actually tolerate faults and their consequences. Hence, there is a need to introduce active mechanisms which modify the system after an error is detected, such that the system is still able to deliver its service despite the manifestation of faults. Mechanisms to implement error recovery are concerned with the elimination of errors in the system state. The basic idea behind error recovery is to transform an erroneous state of the system into a valid one, from which the system can continue to provide its service. There are two basic strategies to implement error recovery mechanisms, namely *forward error recovery* and *backward error recovery*. Forward error recovery tries to undo the damage introduced by a fault into the system state, so that after recovery the system state is the same as it would have been had the manifestation of a fault not happened. Contrarily, backward error recovery mechanisms are based on the restoration of the state of the system to a previously known valid state.

assessment and error recovery mechanisms have the objective of ensuring that any error introduced to the system due to the manifestation of a fault is removed. This prevents the immediate danger of a failure. However, this may not be enough to ensure dependability, since those mechanisms only deal with the symptoms produced by the manifestation of a fault, rather than with the source of the fault. Therefore, although in some situations error treatment mechanisms can cope successfully with faults (e.g. when the recovery mechanisms are powerful enough to deal with recurring faults; or the future operation of the system avoids the fault; or the fault is transient), in many other situations the recurrence of a fault can cause the system to fail. This happens either because the fault becomes more and more serious, or because the recovery operations demand so much work to be carried out, that the system is unable to deliver

its proper service. Fault treatment mechanisms try to eradicate faults from the system so that its service can be sustained, despite the manifestation of faults. Fault location, components repair and system reconfiguration are the main procedures associated with fault treatment.

Design decisions on the amount and type of fault tolerance mechanisms to introduce into a fault-tolerant system are subject to cost considerations. It is necessary to weigh the cost of these mechanisms against the cost of system malfunction, where system malfunction is translated as incorrect computation and/or system downtime. In conventional mainframe systems, where only a small number of applications have dependability requirements, the introduction of fault tolerance mechanisms is seldom cost effective. These systems normally rely on simple fault avoidance techniques and only a very limited amount of fault tolerance mechanisms to increase their dependability. On the other hand, in many safety-critical systems for instance, incorrect computation can lead to immense social and/or economical penalties, therefore these systems normally incorporate a great deal of fault tolerance mechanisms. Moreover, as will be shown later in this chapter, the actual mechanisms used by different systems vary considerably, depending on the requirements of the applications executing on each particular system.

In this way, the purpose of a fault-tolerant computer system dictates the amount and the goals of fault tolerance that must be introduced, such that the system can provide application programs with the degree of dependability they require. Also, the more information that is available about the applications, the more accurate is the choice of which fault tolerance mechanisms to use. In other words, designing specific purpose fault-tolerant systems, where the characteristics of the applications are likely to be known in advance, allows the evaluation of the cost/benefit relation associated with fault tolerance to be carried out in a much simpler and more precise fashion than when evaluating the same relation for a general purpose fault-tolerant architecture, where little is known about the comportment of applications.

Next we discuss the design of various fault-tolerant computer systems described in the literature, and study how fault tolerance mechanisms have been used to implement both specific and general purpose fault-tolerant systems.

### 2.2.1. Specific Purpose Systems

Specific purpose fault-tolerant computer systems have been designed to cope with a diversity of applications such as spacecraft control [Rennels 78, Larman 83], commercial aircraft flight control systems [Hopkins et al. 78, Wensley et al. 78], process monitoring in industrial installations [Siewiorek et al. 78a, Siewiorek et al. 78b, Smith 84, Kopetz-Merker 85, Lala 86], telephone electronic switching systems [Toy 78, Toy-Gallaher 83], on-line transaction processing [Bartlett 81, Bernstein 88, Webber-Beirne 91] and many others. It is possible, however, to divide these systems into three distinct categories, each one possessing well defined goals.

The first category is composed of those systems whose applications require system's down-time to be kept to a minimum, although a certain degree of incorrect operation is acceptable. For instance, a typical requirement for a telephone electronic switching control system is that system's downtime do not exceed 2 hours during a period of 40 years of system's operation, though the interruption of a small number of on—going calls can be accepted. Those systems are therefore classified as *highly—available* systems.

On the other hand, *long-life* systems form another category of system, whose applications can sustain longer periods of downtime, provided that the system eventually delivers its correct service. A main requirement of long-life applications is that they must survive their mission life-time without the need of system maintenance. Unmanned spacecrafts control and submarine prospecting, are examples of long-life applications where maintenance is either impossible or too expensive, and where the correctness of the service delivered is crucial, although intervals of unavailableness (e.g. due to system reconfiguration) are acceptable.

Safety-critical systems comprise the last category of special purpose systems. Safety-critical applications require that the system deliver its correct service with high degree of reliability, since the effect of a malfunction can be catastrophic. A great many safety-critical systems are associated with real-time applications, therefore, for those systems, recovery must be achieved with little, if any, degradation on system performance. Commercial aircraft flight control, rail-way switching control and industrial processes monitoring are examples of applications whose requirements can only be met by safety-critical fault-tolerant computer systems.

### 2.2.1.1. Highly-Available Systems

This class of systems is represented mainly by telephone electronic switching control systems and on—line transaction processing systems such as airlines reservations and bank accounting. Those systems are normally structured around a basic error detection mechanism at the processing unit, which can be realised either by self—checking logic based mechanisms or duplication and matching mechanisms. Following the detection of an error, indicated by an interruption for instance, the processing unit is disabled. Error recovery is attained by a variety of mechanisms which differ considerably from system to system. On the other hand, continued service is generally achieved via the use of standby spares. Since there are no strict requirements on the timeliness with which the service is provided, a performance decrease whilst recovery and reconfiguration are executed is acceptable; therefore, there is no need to keep spare modules in close synchronism.

One of the first highly-available systems to be developed was the AT&T ESS family of telephone electronic switching control systems [Toy 78]. These systems were first introduced in 1965, and since then, three generations have been built. The differences between each generation is very much a function of the advances on the technology of components, and the variations on system goal. The 3B20D architecture [Toy-Gallaher 83] for instance, was designed for a broad range of AT&T applications, and marked the beginning of the third generation of ESS highly-available systems.

The 3B20D is a duplex processor architecture with extensive use of self-checking hard-ware to detect errors. The promptness of error detection guaranteed by the massive utilisation of self-checking logic minimises the possibility of damage proliferation. At each time, only one processor is operational, however, special fault-tolerant memory update circuits are used to guarantee that write operations are executed simultaneously in both memories. If an error is detected, a switch circuit is activated, which transfers control from the faulty processor to the spare, making the latter operational. Since the processors are not executing in synchronism, an initiation sequence to load the on-board data of the processor (e.g. registers) with correct information is required, so that service is continued properly. Additional fault tolerance mechanisms include the

use of 4 parity bits for the 32-bit data paths, error correction codes for memory units, mirrored disk units equipped with self-correcting cyclic redundant code and a timing check (sanity check) for processing units, which cause automatic reset of operational processors in the event of time-out expiration (correct operational processors are designed to reset the timing check at predefined intervals of time).

A similar design is found on the Tandem family of NonStop highly-available systems [Bartlett 81]. These systems are targeted to on-line transactions processing (OLTP) applications. Fault confinement is achieved through the use of a loose synchronised multicomputer, where individual computers are connected to a dual bus system through carefully designed bus interfaces. The interface to the bus incorporates self-checking logic, and is implemented in such a way that a faulty computer cannot inject spurious signals into the bus through the interface. Processing units also use self-checking logic to detect errors. Recovery is implemented via backward error recovery mechanisms which restore valid states previously saved in well defined checkpoints. Application processes are duplicated and executed at two different computers. One of the processes in the pair is assigned to be active, whilst the spare process receives periodic checkpoints from the active process. If the spare process detects the failure of its active copy, then service is resumed from the last checkpoint saved.

Two other highly–available systems providing support for OLTP applications followed Tandem's NonStop systems. The Stratus architecture [Webber–Beirne 91] is a loosely coupled multicomputer system. Each Stratus system consists of up to 32 modules connected via a proprietary inter–module link. Each module is formed by a number of processing, memory and I/O channel units, connected via a reliable bus. Each processing unit is composed of two conventional processors which are driven by a common clocking source. The two processors execute in *lock–step* and have their output compared by a reliable comparison circuit. This first level of duplexing provides error detection. Once a mismatch is detected by the comparison mechanism, the faulty processing unit is disabled, resulting in no more signals being output to the bus. Two processing units are then coupled together in tight synchronism to provide continued service despite the failure of one of the processing units.

The Sequoia system [Bernstein 88], on the other hand, is a tightly coupled multiprocessor system. Duplicated processing elements (PEs), duplicated I/O elements (IOEs) and memory elements (ME) are connected by a duplicated bus through master/slave bus interfaces. PEs and IOEs execute in lock—step, accomplishing error detection in the usual duplication and matching way, via a special comparator circuit at the bus interfaces. Once a mismatch is detected, the faulty PE is isolated from the system (a similar mechanism is used for the IOEs). MEs incorporate a powerful error correction mechanism based on an extended Hamming SEC—DEC code [Siewio-rek—Swarz 92], which is also able to tolerate failures of the encode/decode circuit itself. Error recovery is attained through software protocols based on process pairs and checkpoints, similar to those used in the Tandem architecture. Mirrored disks are used to provide fault—tolerant I/O operations to the file system.

### 2.2.1.2. Long-Life Systems

A typical long-life system is encountered in space exploration missions. In those applications it is common to have most of the useful collection of data being realised near the end of the system's mission, thus it is imperative to have the system operative at that stage. Since component repair is not easily accomplished remotely, the duration of the mission dictates the amount of spare units with which the system must be equipped, so that it will survive the mission lifetime. It is important to notice that the designers of such systems must take into account all aspects of the system, and not only the computational part. In a spacecraft for instance, the craft structure, weight, power supply sources and data communication channels are other aspects where reliability constraints must also be imposed.

The Galileo spacecraft [Larman 83], for instance, has been designed to perform a two stage mission to collect data from Jupiter. The spacecraft is composed of an orbiter vehicle and a probe vehicle. The first part of the mission initiates when the spacecraft is around 150 days away from Jupiter, and consists of the release of the probe vehicle into Jupiter's atmosphere. The orbiter vehicle then starts acquiring data from the probe. In the second part of the mission, the orbiter vehicle goes into orbit about Jupiter for a period of 20 months, during which it explores the sur-

rounding space environment and stores data for future analysis. (The same data is also transmitted to the Earth base.)

The basic mechanism for fault tolerance in the Galileo spacecraft is the use of duplicated modules equipped with extensive self-checking logic. The main processing unit is actively redundant, i.e. processing is carried out on both processors, executing in tight synchronism. Once a failure is detected (via the self checking logic), the faulty module is isolated, whilst the functioning module can continue operation without disruption of the system service.

Characteristics of the application software are used to implement reasonableness checks. Also, parity checks are heavily used, as well as periodic diagnostic checks. Due to the unknown, and possibly hostile, characteristics of the environment, persistent checks based on retries are carried out consistently. A component is only considered to have failed if a failure is observed throughout a predefined interval of time, or alternatively, after a predefined number of unsuccessful retries have been attempted. There is also the possibility of a remote intervention of the maintenance personal at the Earth base to deal with unanticipated conditions.

System operation is divided into critical and non—critical operations. If an error is detected whilst the system is executing a non—critical operation then the operation in hand is aborted. The system is then placed into a safe state with minimum power consumption and thermal stability. (This includes internal temperature control, as well as the use of shades to protect external equipment from sun rays.) Finally recovery is attempted. Most of the cases recovery consists of simply retrying the erroneous operation, or skipping to the next operation. Detection of errors during the execution of critical operations is performed in a different way. The active redundancy of the processing unit guarantees the provision of services after the failure of one of the processors. Recovery from a second failure is attained through rollback techniques followed by retry.

### 2.2.1.3. Safety-Critical Systems

The strict time requirements of most safety-critical applications demand that fault tolerance must be attained with no disruption of system service. Hence, safety-critical systems are generally built with failure-masking mechanisms. A classical example of this kind of systems is the C.vmp system [Siewiorek et al. 78a, Siewiorek et al. 78b]. It consists of a triplicated as-

sembling of conventional processors executing in lock—step, and a hardware voting mechanism which controls access to a replicated bus. All information retrieved (stored) from (into) memory is voted, and the reliable voting mechanism masks the failure of one processor and one memory module. In fact, since the voting is performed in a bit—by—bit fashion, there are more combinations of faulty components that can be tolerated. For instance, if memory is organised in such a way that every bit of a particular word is stored in a different chip, the system can tolerate the simultaneous failure of memory chips in the three computers, provided that failures in different computers do not affect the same bit of a particular word.

Among the first safety—critical architectures to be implemented were FTMP, from the C.S. Draper Laboratory [Hopkins et al. 78], and SIFT, developed by the SRI Laboratory [Wensley et al. 78]. Their design goals are very similar – both were designed to be used by commercial transport aircraft, nevertheless, their designers have followed two very distinct approaches. Both FTMP and SIFT are multiprocessors of arbitrary size. Processing modules are organised in triads to perform tripled redundant functions and mask the failure of one processor. The basic difference between the two systems is on the way the replicated computation performed by each of the processors forming a triad is synchronised, and the way replicated outputs are voted, so that failures can be masked.

In FTMP voting is achieved via a hardware circuit which implements a reliable voted access to the bus. Processors forming a triad must therefore execute in lock–step. A fault–tolerant clock synchronisation algorithm implemented by a hardware circuit provides a common time frame for the processors forming a triad. On the other hand, in SIFT processors do not need to maintain tight synchronism, further, voting is achieved via a software mechanism. Each processor in a triad is able to read (but not write) the memory of the other processors and vote on relevant information deposit in predefined locations. Processes need only maintain a loose synchronism, which allows the executive software to guarantee that information upon which voting is performed is available at the required time at each correct processor. SIFT voting mechanism is highly dependent on the cyclic nature of SIFT's application programs. Loose synchronisation is attained through a software fault–tolerant clock synchronization protocol based on message exchange. The voting mechanism in both systems is able to detect a faulty processor. If a failure

is detected then reconfiguration is performed to restore the failure–masking property of the system. (In FTMP there are 14 processors, which are arranged in 4 triads, leaving 2 processors as spares.) The interval of time between error detection and system reconfiguration is short, reducing the probability of the manifestation of a subsequent non–maskable fault, whilst reconfiguration is being performed.

Other examples of safety-critical systems are the 'fly-by-wire' system control of the airbuses A320, A330 and A340 [Brière-Traverse 93]. These systems have very rigourous requirements in terms of both reliability and availability. Their design is based on special processing nodes, which are composed of two separate processing channels. One of the processing channels is responsible for executing the system functions, whilst the other is responsible for monitoring the correct operation of the former. Each channel, including its design and software, is completely independent from the other. These nodes are replicated in order to achieve the required availability. Spare nodes are kept in close synchronism with the active nodes, so that reconfiguration is realised with almost no delay. Flight control computers must be especially robust, thus, their design incorporate protection against over-voltages, under-voltages, electromagnetic aggressions and indirect effects of lightning.

### 2.2.2. General Purpose Systems

The variety of applications that can be executed on general purpose computer systems rules out the utilisation of application attributes in order to choose the appropriate fault tolerance mechanisms to be used. Therefore, designers must be much more careful when introducing fault tolerance mechanisms into general purpose computer systems. Ideally, applications should be able to receive dependable services on an application–by–application basis, so that an application that does not require any degree of dependability would not incur any extra penalty, either in performance or in system cost, whilst at the same time other applications with dependability requirements would be able to co–exist, receiving dependable services, and with an overhead corresponding to their dependability demands.

The difficulty in achieving this idealised scenario has lead to less ambitious, compromising solutions. Traditional mainframes, for instance, possess only a restricted number of built-in fault

tolerance mechanisms, and indeed represent the minimal standard to which any fault-tolerant system should aspire. On the other hand, the natural replication of resources found in parallel, and distributed systems can be exploited to provide much better solutions to applications with dependability requirements, raising only a limited overhead to the remaining applications not requiring dependable services.

Next, we analyse fault tolerance mechanisms used by several general purpose fault-tolerant systems described in the literature.

### 2.2.2.1. Mainframes

Unlike the systems presented before, mainframes such as the VAX 8600 from DEC and the 3090 from IBM, primarily use fault avoidance techniques to attain better reliability levels. Fault avoidance techniques, as discussed before, try to avoid system failure, hence they are mainly concerned with the manufacturing process of the system, and the environmental conditions to which the system is exposed. Thus, most mainframes are constructed with high quality, low intrinsic failure components, and must operate in a friendly and well controlled environment, where power fluctuations are avoided, and temperature is kept within specified limits. Apart from this, only a small number of fault tolerance mechanisms are introduced.

A mainframe can be divided into three main sections: central processor unit, memory (possibly divided into main memory and cache memory) and I/O channels. Since each section has its own attributes, fault tolerance mechanisms added to the system vary in accordance with the section where they are inserted. Table 2–1 below summarises the most common error detection mechanisms used in each section of a mainframe.

| Mainframe section | Error detection mechanism                                                            |  |

|-------------------|--------------------------------------------------------------------------------------|--|

| main memory       | double–error–detection code on data;<br>parity on addresses and control              |  |

| cache memory      | parity on data, address and control                                                  |  |

| central processor | parity on data paths and control store;<br>duplication and matching on control logic |  |

| I/O processors    | parity on data and control                                                           |  |

Table 2–1: Common error detection mechanisms for a mainframe

The design goal is to tolerate transient faults, hence the extensive use of coding. The basic recovery mechanisms is retry after the detection of an error. If an error has been caused by a transient fault, a small number of retries inter–spaced by a predefined delay is sufficient to bring the system back to normal operation. Memory units are generally equipped with error correction codes for data.