# EMBEDDED DYNAMIC PROGRAMMING NETWORKS FOR NETWORKS-ON-CHIP

RA'ED AL-DUJAILY

A Thesis Submitted for the Degree of Doctor of Philosophy at Newcastle University

School of Electrical, Electronic & Computer Engineering

Faculty of Science, Agriculture & Engineering

March 2013

Relentless technology downscaling and recent technological advancements in three dimensional integrated circuit (3D-IC) provide a promising prospect to realize heterogeneous system-on-chip (SoC) and homogeneous chip multiprocessor (CMP) based on the networks-onchip (NoCs) paradigm with augmented scalability, modularity and performance. In many cases in such systems, scheduling and managing communication resources are the major design and implementation challenges instead of the computing resources. Past research efforts were mainly focused on complex design-time or simple heuristic run-time approaches to deal with the on-chip network resource management with only local or partial information about the network. This could yield poor communication resource utilizations and amortize the benefits of the emerging technologies and design methods. Thus, the provision for efficient run-time resource management in large-scale on-chip systems becomes critical. This thesis proposes a design methodology for a novel run-time resource management infrastructure that can be realized efficiently using a distributed architecture, which closely couples with the distributed NoC infrastructure. The proposed infrastructure exploits the global information and status of the network to optimize and manage the on-chip communication resources at run-time.

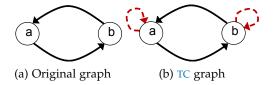

There are four major contributions in this thesis. First, it presents a novel deadlock detection method that utilizes run-time transitive closure (TC) computation to discover the existence of deadlock-equivalence sets, which imply loops of requests in NoCs. This detection scheme, TC-network, guarantees the discovery of all true-deadlocks without false alarms in contrast to state-of-the-art approximation and heuristic approaches. Second, it investigates the advantages of implementing future on-chip systems using three dimensional (3D) integration and presents the design, fabrication and testing results of a TC-network implemented in a fully stacked three-layer 3D architecture using a through-silicon via (TSV) complementary metal-oxide semiconductor (CMOS) technology. Testing results demonstrate the effectiveness of such a TC-network for deadlock detection with minimal computational delay in a large-scale network. Third, it introduces an adaptive strategy to effectively diffuse heat throughout the three dimensional network-on-chip (3D-NoC) geometry. This strategy employs a dynamic programming technique to select and optimize the direction of data manoeuvre in NoC. It leads to a tool, which is based on the accurate HotSpot thermal model and SystemC cycle accurate model, to simulate the thermal system and evaluate the proposed approach. Fourth, it

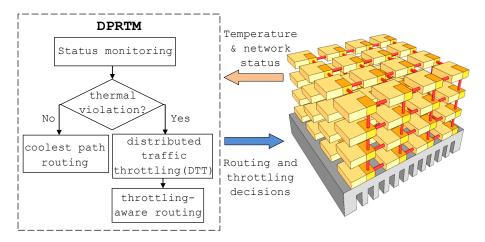

presents a new dynamic programming-based run-time thermal management (DPRTM) system, including reactive and proactive schemes, to effectively diffuse heat throughout NoC-based CMPs by routing packets through the coolest paths, when the temperature does not exceed chip's thermal limit. When the thermal limit is exceeded, throttling is employed to mitigate heat in the chip and DPRTM changes its course to avoid throttled paths and to minimize the impact of throttling on chip performance.

This thesis enables a new avenue to explore a novel run-time resource management infrastructure for NoCs, in which new methodologies and concepts are proposed to enhance the on-chip networks for future large-scale 3D integration.

# DECLARATION

| I hereby declare that this thesis is my<br>has not been submitted anywhere for<br>of information have been used, they h | any award. Where other sources |

|-------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| Newcastle Upon Tyne, March 2013                                                                                         |                                |

|                                                                                                                         | RA'ED AL-DUJAILY               |

# CERTIFICATE OF APPROVAL

| I confirm that, to the best of my knowledge, this thesis is from the |

|----------------------------------------------------------------------|

| student's own work and effort, and all other sources of information  |

| used have been acknowledged. This thesis has been submitted with     |

| my approval.                                                         |

| Newcastle Upon Tyne, March 2013 |               |

|---------------------------------|---------------|

|                                 |               |

|                                 | ALEX YAKOVLEV |

# Referred journal publications

R. Al-Dujaily, N. Dahir, T. Mak, F. Xia, A. Yakovlev, "Dynamic Programming-based Runtime Thermal Management (DPRTM): An On-line Thermal Control Strategy for 3D-NoC Systems", ACM Transactions on Design Automation of Electronic Systems, (submitted), pp. 1 - 28, 2012.

- 2. **R. Al-Dujaily**, T. Mak, K. P. Lam, F. Xia, A. Yakovlev, C. S. Poon, "Dynamic thermal optimization in three dimensional networks-on-chip", *The Computer Journal*, (in press), pp. 1 15, 2012.

- 3. **R. Al-Dujaily**, T. Mak, F. Xia, A. Yakovlev, M. Palesi, "Embedded transitive-closure network for run-time deadlock detection in networks-on-chip", *IEEE Transactions on Parallel and Distributed Systems*, vol. 23, no. 7, pp. 1205 1215, 2012.

- 4. T. Mak, **R. Al-Dujaily**, K. Zhou, K. P. Lam, Y. Meng, A. Yakovlev, C. S. Poon, "Dynamic programming networks for large-scale 3D chip integration", *IEEE Circuits and Systems Magazine*, vol. 11, no. 3, pp. 51 62, 2011.

Conference, workshop and forum publications:

- 1. **R. Al-Dujaily**, T. Mak, F. Xia, A. Yakovlev, K. P. Lam and C. S. Poon, "Dynamic Thermal Optimization in 3-D NoC", DATE 2012 workshop in: Design, Automation and Test of 3D-ICs, 2012, pp. 1 2.

- 2. **R. Al-Dujaily**, T. Mak, K. Zhou, K. P. Lam, Y. Meng, A. Yakovlev, C. S. Poon, "On-chip dynamic programming networks using 3D-TSV integration", Embedded Computer Systems (SAMOS), 2011 International Conference on, July, pp. 318 325.

- 3. **R. Al-Dujaily**, T. Mak, F. Xia, A. Yakovlev, "Run-Time Resources Management for 3D Networks-on-Chip based Systems," UK Electronics Forum (UKEF 2011), Manchester, 4-5 July, 2011, pp. 1 7.

- 4. C. S. Poon, T. Mak, **R. Al-Dujaily**, K. Zhou, and K. P. Lam, "Onchip dynamic programming networks design in TSV-based 3D stacking technology," In GOMAC Tech. Conference Session 10 on 3D-IC, 19-22 March, 2011.

- R. Al-Dujaily, T. Mak, F. Xia, A. Yakovlev and M. Palesi, "Runtime deadlock detection in networks-on-chip using coupled transitive closure networks," Design, Automation Test in Europe Conference Exhibition (DATE), 2011, March, pp. 497 502 (BEST PAPER AWARD).

- 6. **R. Al-Dujaily**, T. Mak, F. Xia, and A. Yakovlev, "A Methodology for Deadlock Detector Minimization in Interconnection Network," UK Electronics Forum (UKEF 2010), Newcastle, July, 2010, pp. 1 6.

- 7. **R. Al-Dujaily**, L. Dai, F. Xia, D. Shang and A. Yakovlev, "NoC Monitoring Infrastructure: A supervisory and Control Services" in the 21st UK Asynchronous Forum, Bristol, 14-15th September, 2009, pp. 1 6.

"There is no capital more useful than intellect and wisdom, and there is no indigence more injurious than ignorance and unawareness."

Ali ibn Abi Talib

#### ACKNOWLEDGMENTS

The research presented in this thesis was carried out under the supervision of Prof. Alex Yakovlev, Dr Terrence Mak and Dr Fei Xia of Newcastle University. I wish to express my profound thanks to them for their support, inspiration, editorial control and counsel throughout the course of my studies.

I am grateful to the Iraqi Ministry of Higher Education and Scientific Research (MOHESR) for funding my PhD study through their Scholarship Programme and also wish to express my gratitude to the Iraqi Cultural Attaché in London.

I would like to thank Dr Maurizio Palesi for his help and advices in modifying the NoC simulator used in this thesis. We had joint paper publications.

I would like to thank my thesis examination committee (Professor Kees Goossens and Dr Albert Koelmans) for their support in this endeavour.

I am grateful to the members of the Microelectronics System Design group at Newcastle University for assisting me in my study. Many thanks go to my friends and colleagues — Nizar Dahir, Ghaith Tarawneh, Maxim Rykunov, Reza Ramezani and Petros Missailidis — for numerous inspiring discussions, productive criticism, endless support, and for simply being very pleasant company.

I would also like to acknowledge MIT Lincoln Laboratory (MIT-LL) for providing access to the MIT-LL 3D circuit integration technology which used to fabricate the 3D-IC presented in Chapter 4.

Last but not least, I wish to thank my family for their continuous support and motivation throughout the duration of my studies.

# CONTENTS

| I | Τŀ  | nesis Chapters                            | 1  |

|---|-----|-------------------------------------------|----|

| 1 | INT | RODUCTION                                 | 2  |

|   | 1.1 | Motivation and Objective                  | 2  |

|   | 1.2 | Structure of the Thesis                   | 4  |

|   | 1.3 | Statement of Originality                  | 5  |

| 2 | ВАС | KGROUND AND LITERATURE REVIEW             | 8  |

|   | 2.1 | Introduction                              | 8  |

|   | 2.2 | Networks-on-Chip (NoCs)                   | 9  |

|   | 2.3 | Components of NoCs                        | 9  |

|   |     | 2.3.1 Router                              | 10 |

|   |     | 2.3.2 Link                                | 11 |

|   |     | 2.3.3 Network Interface                   | 12 |

|   |     | 2.3.4 Intellectual Property Core          | 12 |

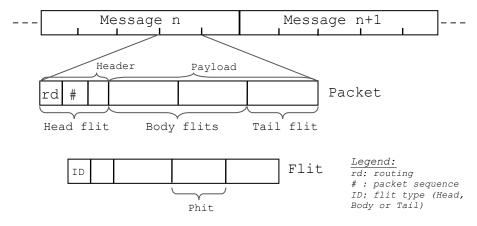

|   | 2.4 | NoCs Flow Control                         | 13 |

|   |     | 2.4.1 Message-Based Flow Control          | 14 |

|   |     | 2.4.2 Packet-Based Flow Control           | 14 |

|   |     | 2.4.3 Flit-Based Flow Control             | 15 |

|   | 2.5 | Routing Algorithms                        | 16 |

|   |     | 2.5.1 Deterministic                       | 16 |

|   |     | 2.5.2 Oblivious                           | 16 |

|   |     | 2.5.3 Adaptive                            | 17 |

|   |     | 2.5.4 Minimal vs Non-minimal              | 17 |

|   | 2.6 | Deadlock and Livelock                     | 17 |

|   |     | 2.6.1 Deadlock                            | 17 |

|   |     | 2.6.2 Livelock                            | 22 |

|   | 2.7 | NoCs and the Emerging Technologies        | 22 |

|   | •   | 2.7.1 Three Dimensional Integration       | 22 |

|   |     | 2.7.2 On-Chip Optical Interconnect        | 25 |

|   |     | 2.7.3 On-Chip Wireless RF Interconnect    | 25 |

|   | 2.8 | Networks-on-Chip: A Review                | 25 |

|   |     | 2.8.1 The Emergence of NoCs               | 26 |

|   |     | 2.8.2 Routing Algorithms and Flow Control | 27 |

|   |     | 2.8.3 Different Architecture Philosophy   | 29 |

| 3 | RUN | J-TIME DEADLOCK DETECTION                 | 38 |

| J | 3.1 | Introduction                              | 38 |

|   | 3.2 | Related Work                              | 41 |

|   | 3.3 | Methodology for Deadlock Detection        | 42 |

|   | 5.5 | 3.3.1 Background and Assumptions          | 42 |

|   |      | 3.3.2 Equivalence Set Criterion for Deadlock       | 43             |

|---|------|----------------------------------------------------|----------------|

|   |      | 3.3.3 Equivalence Set Computational Complexity     | 46             |

|   | 3.4  | Transitive Closure (TC) Network Architecture       | 48             |

|   |      | 3.4.1 TC Computation with TC-networks              | 48             |

|   |      | 3.4.2 Coupling TC-network to NoC                   | 50             |

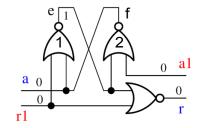

|   |      | 3.4.3 Hardware Implementation                      | 54             |

|   | 3.5  | Results and Discussion                             | 58             |

|   |      | 3.5.1 Evaluation Methodology                       | 58             |

|   |      | 3.5.2 Evaluation Results                           | 59             |

|   | 3.6  | Deadlock Recovery System                           | 71             |

|   |      | 3.6.1 End-to-End Recovery Protocol                 | 71             |

|   |      | 3.6.2 Deadlock Recovery System: Evaluation Results | 75             |

|   | 3.7  | Summary and Conclusions                            | 77             |

|   | 20.1 | NOCS BASED TSV INTEGRATION                         | 80             |

| 4 |      | Introduction                                       | 80             |

|   | 4.1  | Advantages of 3D-NoCs over 2D-NoCs                 | 81             |

|   | 4.2  |                                                    | 81             |

|   |      |                                                    |                |

|   |      |                                                    | 8 <sub>5</sub> |

|   | 4.2  | 4.2.3 Deadlocks Formation Rate                     | 88             |

|   | 4.3  |                                                    |                |

|   |      |                                                    | 89             |

|   |      |                                                    | 89             |

|   | 4.4  | 4.3.3 Testing the 3D-IC chip                       | 90             |

|   | 4.4  |                                                    | 93             |

|   |      |                                                    | 93             |

|   | 4 5  | 4.4.2 TC-network for Deadlock Detection            | 93             |

|   | 4.5  | Summary and Conclusions                            | 94             |

| 5 | RUN  | N-TIME THERMAL ADAPTATION IN 3D-NOCS               | 97             |

|   | 5.1  | Introduction                                       | 97             |

|   | 5.2  | Related Work                                       | 98             |

|   | 5.3  | Methodology for Run-Time Thermal Adaptation        | 99             |

|   |      | 5.3.1 Dynamic Programming                          | 99             |

|   |      | 5.3.2 Coolest Path as Shortest Path                | 100            |

|   |      | 5.3.3 Dynamic Programming Network                  | 102            |

|   |      | 5.3.4 Coupling DP-network with 3D-NoC              | 103            |

|   |      | 5.3.5 NoC Routing with DP-network                  | 103            |

|   |      | 5.3.6 DP-network Convergence Time and Complexity   | 104            |

|   | 5.4  | On-Chip Communication, Power and Thermal Models    | 106            |

|   |      | 5.4.1 Communication Model                          | 106            |

|   |      | 5.4.2 Area and Power Model                         | 106            |

|   |      | 5.4.3 Thermal Model                                | 106            |

|   |      | 5.4.4 Tool Chain for Dynamic Thermal Optimization  |                |

|   |      | 9                                                  | 110            |

|   | 5.5  | Results and Discussion                             | 111            |

|   |      | 5.5.1 Evaluation Methodology                       | 111            |

|   |      |                                                    |                |

|     |      | 5.5.2  | Evaluation Results                       | 112 |

|-----|------|--------|------------------------------------------|-----|

|     | 5.6  | Summ   | ary and Conclusions                      | 123 |

| 6   | RUN  | -TIME  | THERMAL MANAGEMENT FOR 3D-NOCS           | 124 |

|     | 6.1  |        | uction                                   | 124 |

|     | 6.2  |        | d Work                                   | 126 |

|     | 6.3  | Dynar  | nic Programming Run-time Thermal Manage- |     |

|     |      | ment ( | (DPRTM)                                  | 127 |

|     |      | 6.3.1  | System Overview                          | 127 |

|     |      | 6.3.2  | Path Cost Computation                    | 128 |

|     |      | 6.3.3  | Coupling DPRTM with 3D-NoC               | 129 |

|     |      | 6.3.4  | Throttling Techniques                    | 130 |

|     |      | 6.3.5  | NoC Routing in the DPRTM                 | 131 |

|     |      | 6.3.6  | DPRTM Deadlock Freedom                   | 132 |

|     | 6.4  | Hardy  | vare Implementation                      | 132 |

|     | 6.5  | Result | s and Discussion                         | 135 |

|     |      | 6.5.1  | Evaluation Methodology                   | 135 |

|     |      | 6.5.2  | Proactive Routing Evaluation Results     | 135 |

|     |      | 6.5.3  | Reactive Routing Evaluation Results      | 141 |

|     |      | 6.5.4  | DPRTM Evaluation Results                 | 142 |

|     |      | 6.5.5  | Area and Power Estimation                | 146 |

|     | 6.6  | Summ   | ary and Conclusions                      | 148 |

| 7   | CON  | CLUSIO | ONS AND FUTURE WORK                      | 150 |

| -   | 7.1  | Summ   | nary and Conclusions                     | 150 |

|     | 7.2  |        | e Work                                   | 152 |

|     | •    |        |                                          |     |

| П   | Th   | esis A | ppendices                                | 155 |

| A   | FABI | RICATE | ED 3D CHIP SUPPLEMENTARY MATERIALS       | 156 |

| В   | тнг  | RMAT.  | MATERIAL PARAMETERS                      | 161 |

| -   |      |        |                                          | 201 |

| Ш   | Th   | esis B | ibliography                              | 163 |

| віі | BLIO | GRAPH  | Y                                        | 164 |

# LIST OF FIGURES

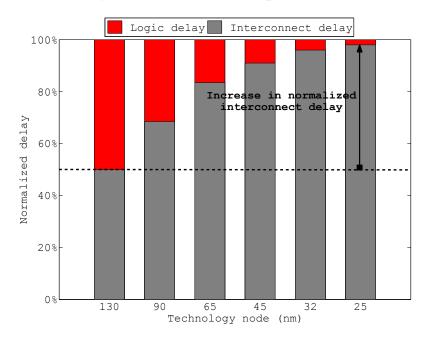

| Figure 1.1 | The trend of logic delay and interconnect delay with technology scaling (source data: International     |    |

|------------|---------------------------------------------------------------------------------------------------------|----|

|            | Technology Roadmap for Semiconductors (ITRS)                                                            |    |

|            | [3])                                                                                                    | 3  |

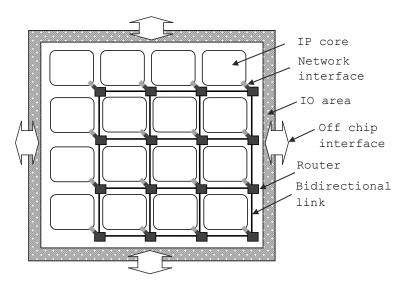

| Figure 2.1 | General network-on-chip (NoC) structure                                                                 | 10 |

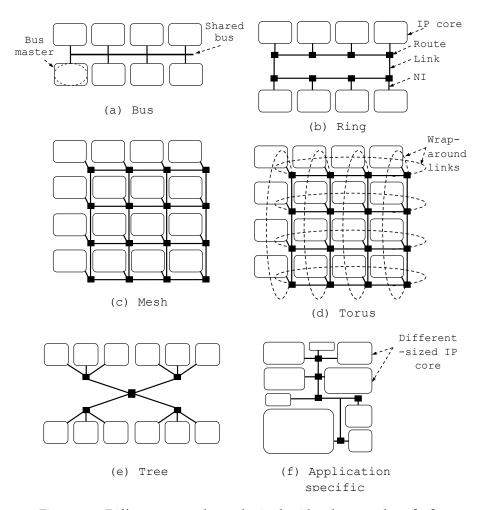

| Figure 2.2 | Different network topologies beside a bus topol-                                                        |    |

|            | ogy [36]                                                                                                | 11 |

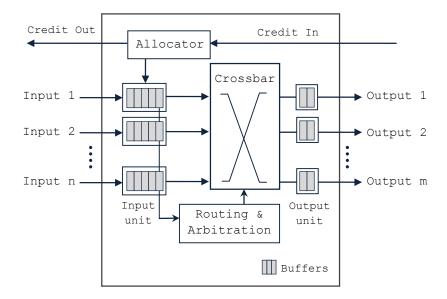

| Figure 2.3 | A typical network-on-chip (NoC) router microar-                                                         |    |

|            | chitecture [92]                                                                                         | 12 |

| Figure 2.4 | An illustration of message segmentation to pack-                                                        |    |

|            | ets, flits and phits. These different granularities                                                     |    |

|            | of data representation are directly associated                                                          |    |

|            | with the resource allocation of different flow                                                          |    |

|            | control technique [52]                                                                                  | 13 |

| Figure 2.5 | A deadlock cycle in a two dimensional (2D) mesh                                                         |    |

|            | network                                                                                                 | 18 |

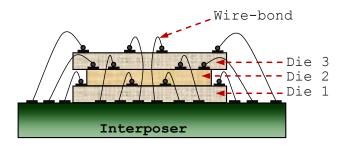

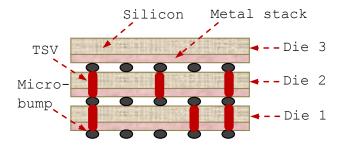

| Figure 2.6 | Different vertical interconnect technologies: an                                                        |    |

|            | illustration                                                                                            | 23 |

| Figure 2.7 | The possible eight turns in 2D mesh beside the                                                          |    |

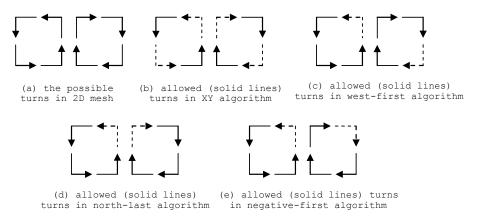

|            | allowed turns in different routing algorithms [65]                                                      | 27 |

| Figure 3.1 | Four packets in a 2D network are waiting for one                                                        |    |

|            | another and forming a deadlock configuration.                                                           | 39 |

| Figure 3.2 | Graphical representation of Example 1                                                                   | 45 |

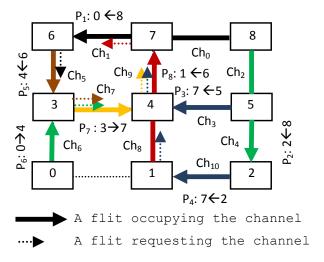

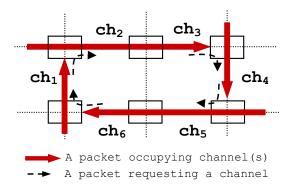

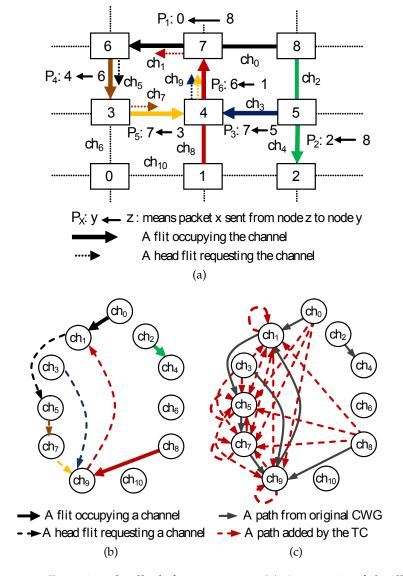

| Figure 3.3 | Detecting deadlock from a two dimensional network                                                       | <- |

|            | on-chip (2D-NoC): (a) A scenario of deadlock for-                                                       |    |

|            | mation; (b) the channel wait-for graph (CWG)                                                            |    |

|            | of the network; (c) the TC of the CWG, the set of                                                       |    |

|            | channels {ch <sub>1</sub> , ch <sub>5</sub> , ch <sub>7</sub> , ch <sub>9</sub> } satisfy the deadlock- |    |

|            | equivalence set (DES) definition (Eq.3.1)                                                               | 46 |

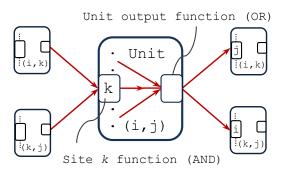

| Figure 3.4 | Unit interconnection in a general TC-network                                                            |    |

|            | where $1 \le i, j, k \le n; k \ne i, j$ [101]. The output                                               |    |

|            | of Unit (i,j) will be the input of other units ac-                                                      |    |

|            | cording to the problem network structure. At                                                            |    |

|            | each unit, there are h sites, which corresponds                                                         |    |

|            | to the total number of neighbouring nodes of i,                                                         |    |

|            | to carry out the inference operations as defined                                                        |    |

| T.         | in the site function                                                                                    | 49 |

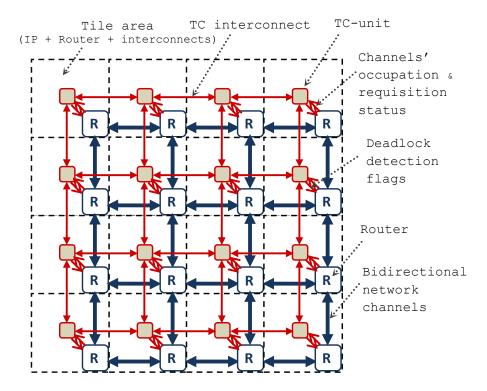

| Figure 3.5 | A TC-network coupled to a 2D mesh NoC                                                                   | 51 |

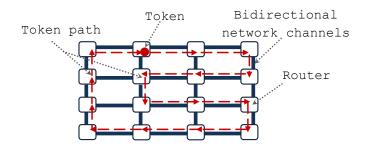

| Figure 3.6 | A Hamiltonian cycle [22] for a token ring distri-                                                       |    |

|            |                                                                                                         |    |

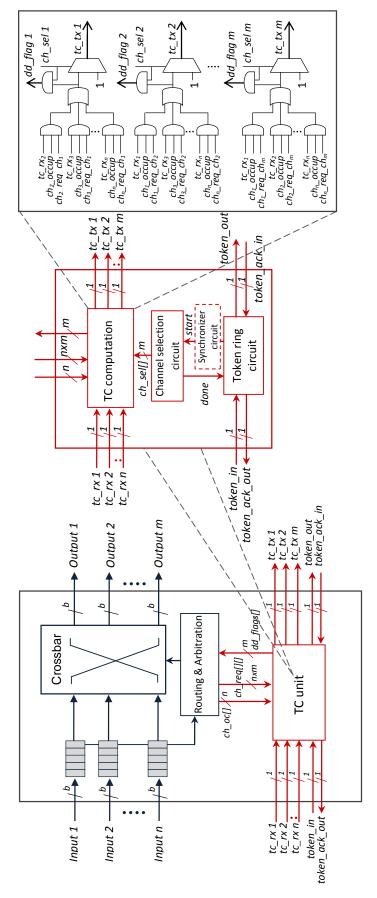

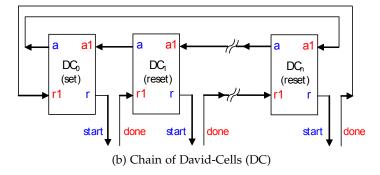

| Figure 3.7   | Schematic of the router. (Left) Top-level view. (Middle) Block implementing the TC-unit. (Right)                                                    | -6         |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Figure 3.8   | Block implementing the TC-computation An example of token-ring protocol implementation                                                              | 56<br>57   |

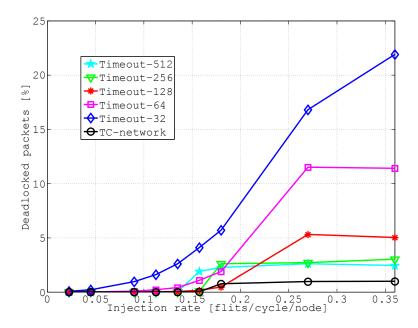

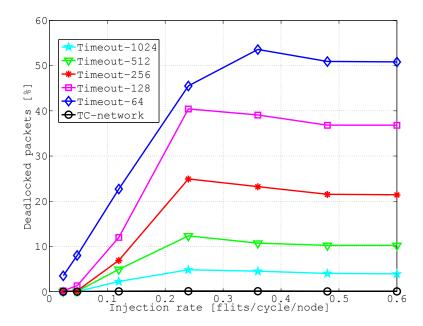

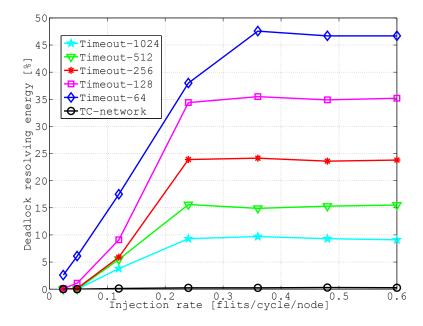

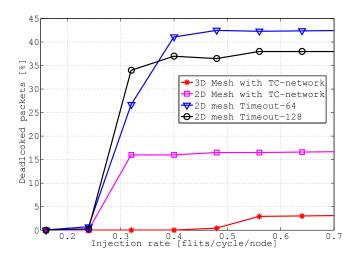

| Figure 3.9   | Percentage of detected deadlocked packets to the total received packets using the TC-network and the timeout mechanism under <i>uniform</i> traffic |            |

| т.           | scenario                                                                                                                                            | 59         |

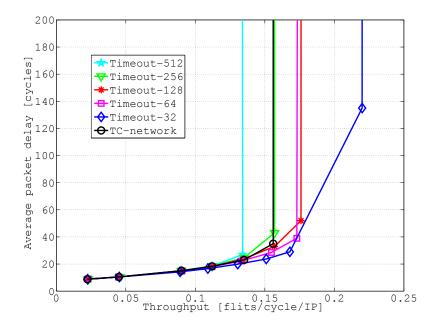

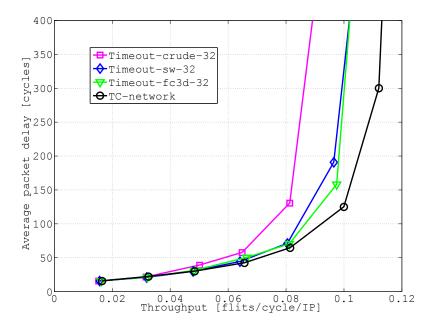

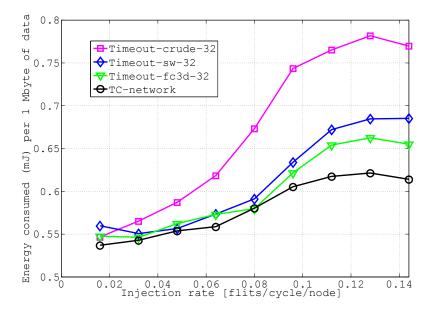

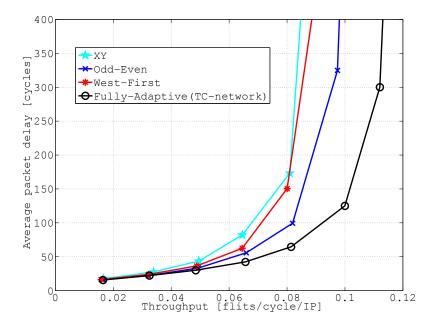

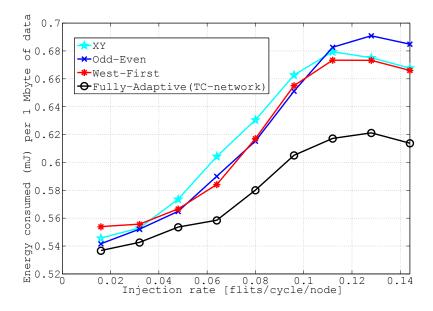

| Figure 3.10  | Performance of the TC-network and the timeout mechanism under <i>uniform</i> traffic scenario with                                                  | ( -        |

| Eigung o aa  | different injection rates                                                                                                                           | 60         |

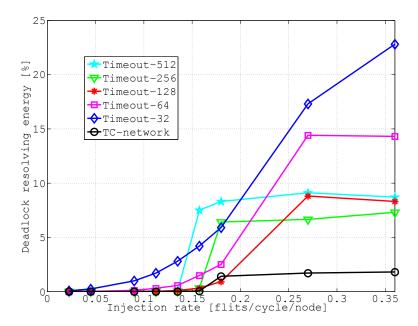

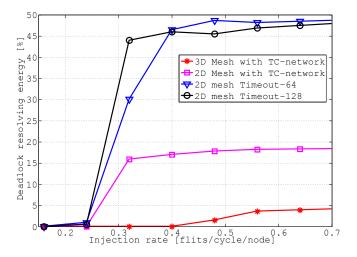

| Figure 3.11  | Percentage of total energy consumed to resolve detected deadlocks to the total NoC energy under                                                     | 61         |

| Figure 3.12  | uniform traffic scenario                                                                                                                            | 01         |

| 11guic 3.12  | the total received packets using the TC-network and the timeout mechanism under <i>bit-reversed</i>                                                 |            |

|              | traffic scenario                                                                                                                                    | 62         |

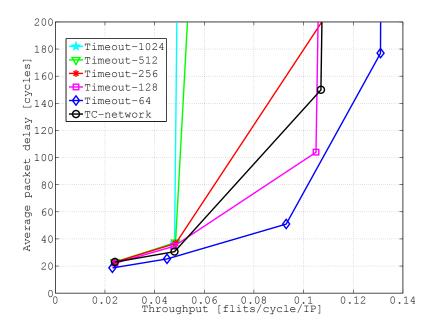

| Figure 3.13  | Performance of the TC-network and the time-                                                                                                         | -          |

| 1180110 3113 | out mechanism under <i>bit-reversed</i> traffic scenario                                                                                            |            |

|              | with different injection rates                                                                                                                      | 63         |

| Figure 3.14  | Percentage of total energy consumed to resolve                                                                                                      | )          |

| 0 0 1        | detected deadlocks to the total NoC energy under                                                                                                    | (-         |

| Eiguno o a = | bit-reversed traffic scenario                                                                                                                       | 63         |

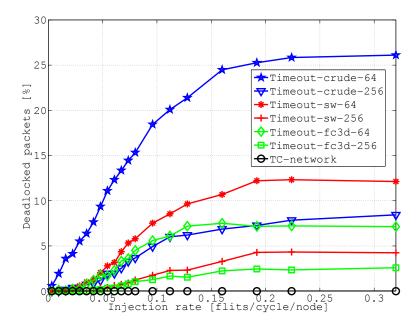

| Figure 3.15  | Percentage of detected deadlocked packets to the total received packets using different methods                                                     |            |

| F: (         | under multi-media system (MMS)                                                                                                                      | 65         |

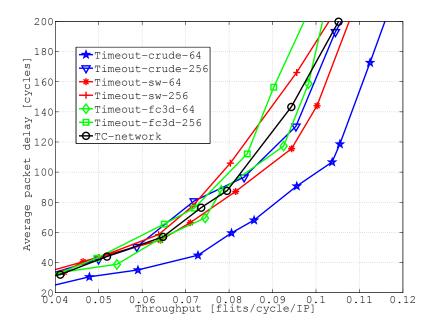

| Figure 3.16  | Performance of the TC-network and the timeout mechanism under MMS with different injection                                                          |            |

| F:           | rates                                                                                                                                               | 66         |

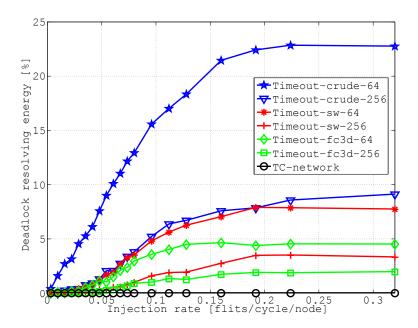

| Figure 3.17  | Percentage of energy consumed to resolve detected deadlocks (retransmission) to the total                                                           |            |

|              | NoC energy (transmission + retransmission) un-                                                                                                      |            |

| Eigung a 40  | der MMS                                                                                                                                             | 67         |

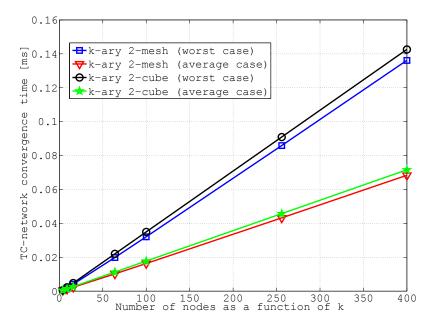

| Figure 3.18  | TC-network convergence time for different network topologies and sizes                                                                              | 71         |

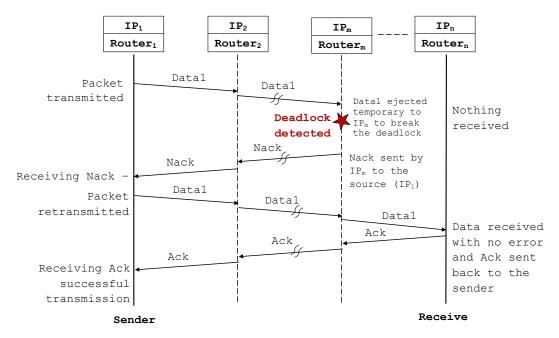

| Figure 3.19  | Transmission scenario 1, which illustrates how                                                                                                      | •          |

| 0 3 7        | to resolve the deadlock if it forms part of the data packet                                                                                         | 72         |

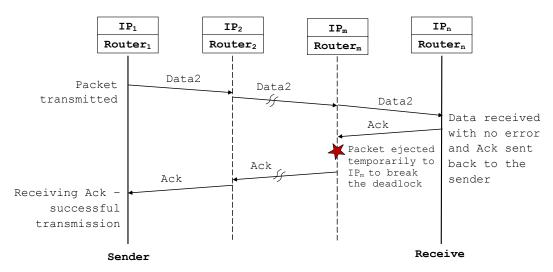

| Figure 3.20  | Transmission scenario 2, which illustrates how                                                                                                      | ′          |

| 0 0          | to resolve the deadlock if it forms part of the <i>Ack</i>                                                                                          |            |

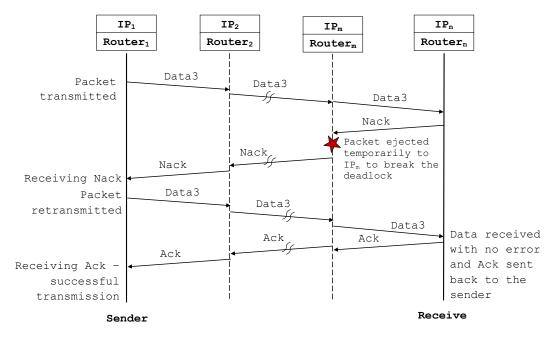

| Figure 3.21  | packet                                                                                                                                              | <b>7</b> 3 |

| 11guit 3.21  | to resolve the deadlock if it forms part of the                                                                                                     |            |

|              | Nack packet                                                                                                                                         | 74         |

| Figure 3.22 | Evaluation of deadlock recovery system with <i>shuffle</i> traffic distribution and different deadlock                                                             |          |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Figure 3.23 | detection techniques                                                                                                                                               | 77       |

| Figure 3.24 | using different deadlock detection techniques  Performance evaluation of deadlock recovery and deadlock avoidance systems with <i>shuffle</i> traffic distribution | 78<br>79 |

| Figure 3.25 | Energy required to drain 1 Mbyte of data in deadlock recovery and deadlock avoidance systems for <i>shuffle</i> traffic                                            | 79       |

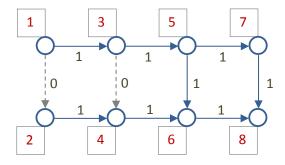

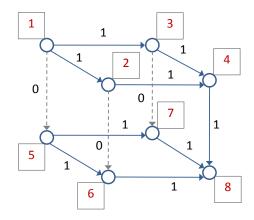

| Figure 4.1  | Eight nodes NoC interconnected in 2D                                                                                                                               | 83       |

| Figure 4.2  | Eight nodes NoC interconnected in 3D                                                                                                                               | 84       |

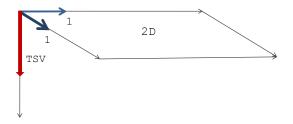

| Figure 4.3  | TSV unit length modelling in three dimensional                                                                                                                     |          |

| 0 13        | networks-on-chip (3D-NoCs) compared to planar                                                                                                                      |          |

|             | 3D-NoCs links                                                                                                                                                      | 8        |

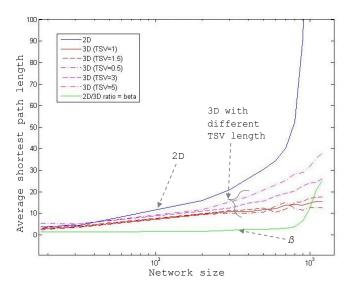

| Figure 4.4  | Average shortest path lengths versus grid size                                                                                                                     | _        |

| 0 11        | (log)                                                                                                                                                              | 8        |

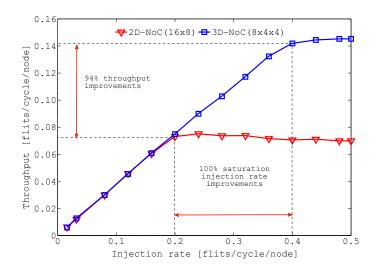

| Figure 4.5  | Throughput and saturation injection rate (IR)                                                                                                                      | _        |

| 0 13        | improvements of 3D-NoCs over two dimensional                                                                                                                       |          |

|             | networks-on-chip (2D-NoCs) for 128 nodes con-                                                                                                                      |          |

|             | nected as mesh $(16 \times 8 \text{ and } 8 \times 4 \times 4)$                                                                                                    | 86       |

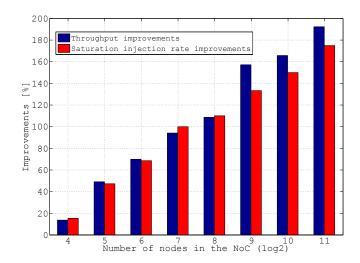

| Figure 4.6  | Throughput and saturation IR improvements of                                                                                                                       |          |

|             | 3D-NoCs over 2D-NoCs for different network grid                                                                                                                    |          |

|             | size                                                                                                                                                               | 86       |

| Figure 4.7  | Percentage of detected deadlocks for 64 nodes                                                                                                                      |          |

| 0 17        | NoC configured as 2D mesh and 3D mesh with                                                                                                                         |          |

|             | fully adaptive routing algorithm                                                                                                                                   | 87       |

| Figure 4.8  | Percentage of energy consumed to resolve de-                                                                                                                       | •        |

|             | tected deadlocks to the total energy for NoC con-                                                                                                                  |          |

|             | figured as 2D mesh and 3D mesh with fully adap-                                                                                                                    |          |

|             | tive routing algorithm                                                                                                                                             | 87       |

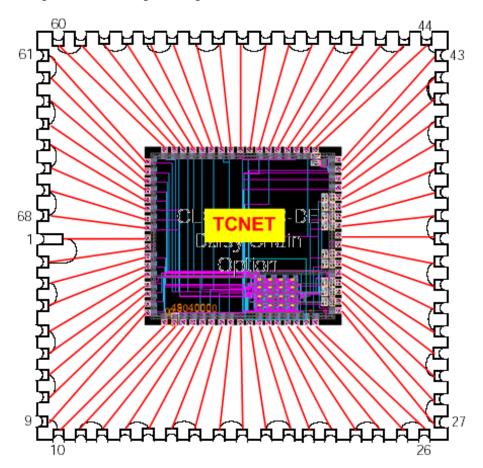

| Figure 4.9  | 3D stacked chip layout shows the input/output                                                                                                                      |          |

|             | pins map                                                                                                                                                           | 88       |

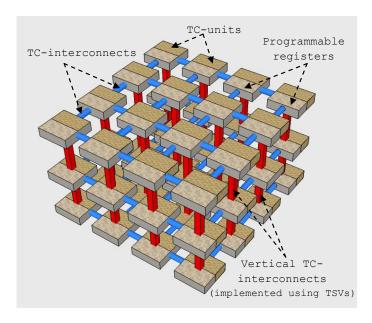

| Figure 4.10 | 3D layout shows the topology of the implemented                                                                                                                    |          |

|             | chip                                                                                                                                                               | 89       |

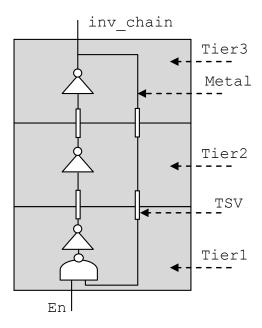

| Figure 4.11 | Schematic of 3D ring oscillator implemented on-<br>chip                                                                                                            | 90       |

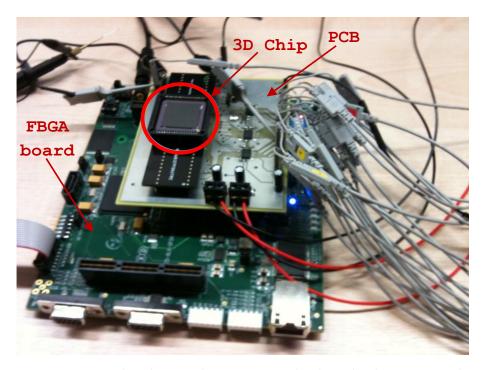

| Figure 4.12 | Snapshot showing the setup to test the chip. The                                                                                                                   | J.       |

| 7·2-        | chip is mounted in a special socket on top of                                                                                                                      |          |

|             | a printed circuit board (PCB) then interfaced to                                                                                                                   |          |

|             | the field-programmable gate array (FPGA) board                                                                                                                     |          |

|             | using a SAM interface                                                                                                                                              | 91       |

|             | aong a orner manuacci                                                                                                                                              | 7        |

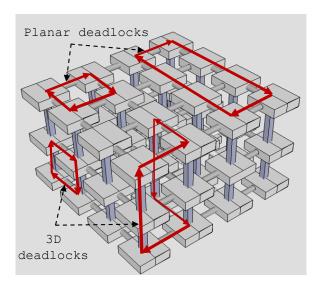

| Figure 4.13  | Examples of planar deadlock and 3D deadlock configurations with different sizes in the 3-tiers |     |

|--------------|------------------------------------------------------------------------------------------------|-----|

|              | chip                                                                                           | 0.3 |

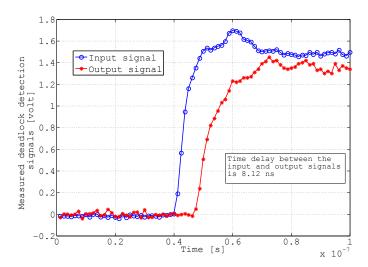

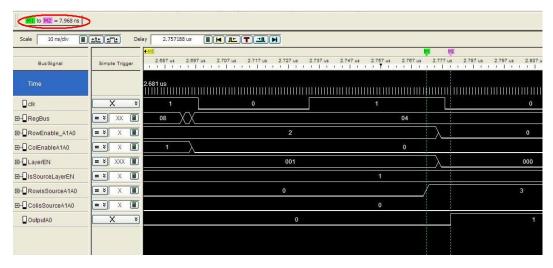

| Figure 4.14  | The start of TC computation and the deadlock                                                   | 92  |

| 0 1 1        | detection signals                                                                              | 92  |

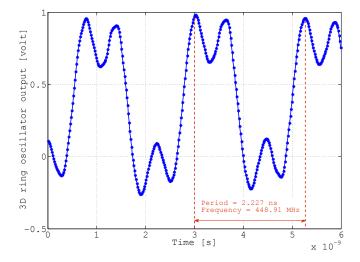

| Figure 4.15  | Ring oscillator output captured showing an os-                                                 | 9-  |

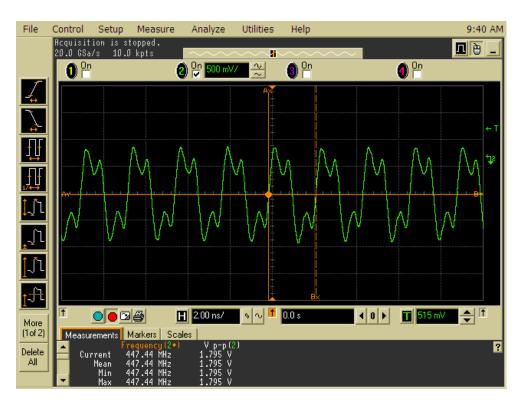

| 118410 4.17  | cillation of 448.91 MHz                                                                        | 93  |

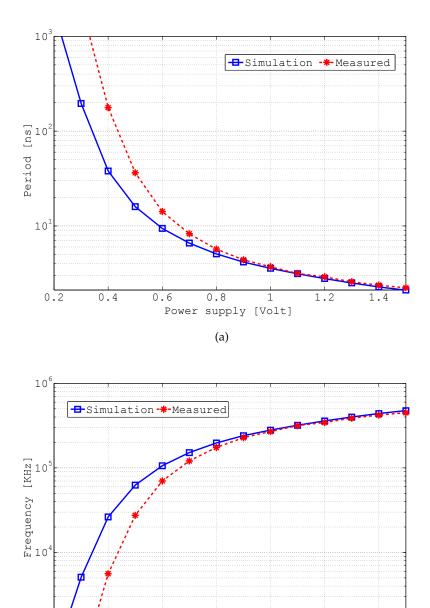

| Figure 4.16  | (a) Frequency (log); (b) period (log) of the 3D-IC                                             | 93  |

| 11guie 4.10  |                                                                                                |     |

|              | ring oscillator operation with different power supply values                                   | 0.  |

| Eigene 4 4 = | 11 5                                                                                           | 95  |

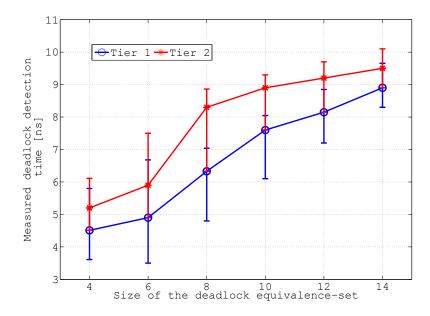

| Figure 4.17  | The time delay to detect different-sized dead-                                                 |     |

|              | locks in tier 1 and 2 in the 3D-NoC chip (error bars                                           |     |

|              | represent the maximum and minimum measure-                                                     |     |

| T. 0         | ments)                                                                                         | 96  |

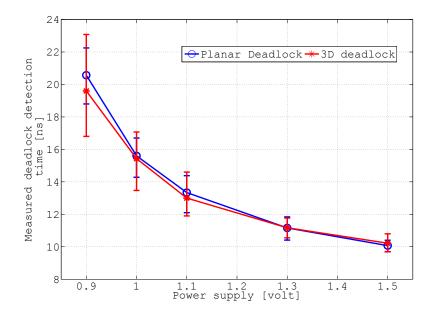

| Figure 4.18  | Deadlock detection delay with scaling down the                                                 |     |

|              | power supply voltage (error bars represent the                                                 |     |

|              | maximum and minimum measurements)                                                              | 96  |

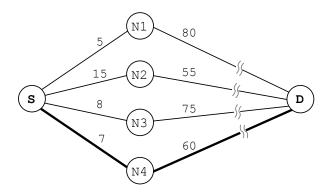

| Figure 5.1   | The shortest path in a weighted graph (bold line                                               |     |

|              | from S to D). It is clear this problem exhibits                                                |     |

|              | optimal substructure; a straight line indicates a                                              |     |

|              | single edge; a broken line indicates a shortest                                                |     |

|              | path between the two nodes it connects (other                                                  |     |

|              | nodes on these paths are not shown)                                                            | 101 |

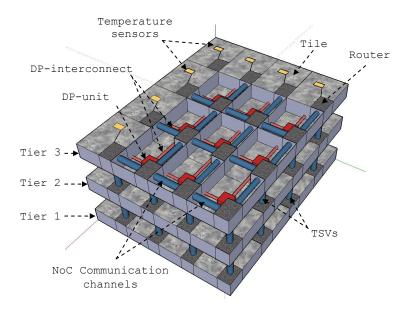

| Figure 5.2   | A dynamic programming (DP)-network coupled                                                     |     |

|              | to a 3D mesh NoC, drawing not to scale                                                         | 104 |

| Figure 5.3   | The floorplan of the Intel 80-tiles chip fabricated                                            |     |

| 0            | at 65nm technology.                                                                            | 107 |

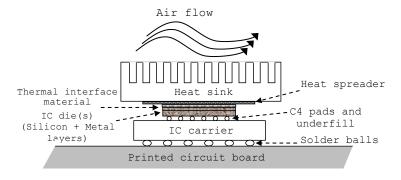

| Figure 5.4   | Side view of a typical integrated circuit (IC) pack-                                           |     |

| 0 0 ,        | age installed on a PCB showing the constituent                                                 |     |

|              | layers [84]                                                                                    | 108 |

| Figure 5.5   | Dynamic compact model illustration: (a) resistance                                             |     |

| 0.00         | capacitance (RC) model for Figure 5.4; (b) RC                                                  |     |

|              | model for an example die with two architec-                                                    |     |

|              | tural units (u1 & u2) and their connection to                                                  |     |

|              | the upper and lower layers; (c) RC model for the                                               |     |

|              | heat-spreader layer, illustrating the four cardinal                                            |     |

|              | direction's lateral heat transfer paths                                                        | 100 |

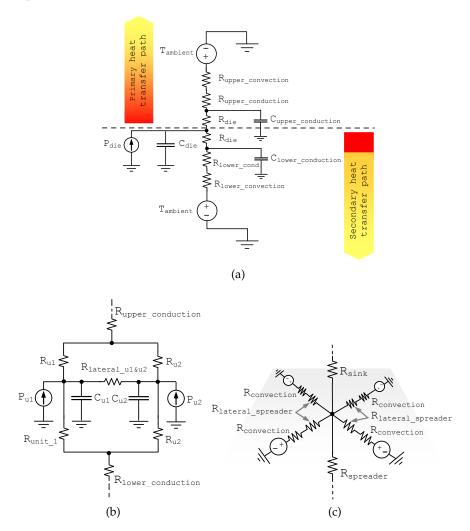

| Figure = 6   | Automated flow of the proposed tool for dy-                                                    | 109 |

| Figure 5.6   | 1 1                                                                                            | 111 |

| Eigene       | namic thermal optimization for 3D-NoCs                                                         | 111 |

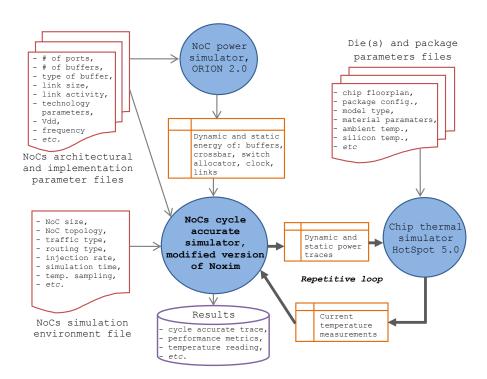

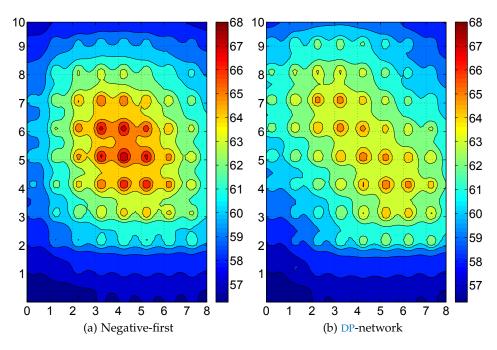

| Figure 5.7   | Temperature distribution of the 80-tiles chip sub-                                             |     |

| Г' 0         | jected to <i>transpose</i> traffic scenario                                                    | 113 |

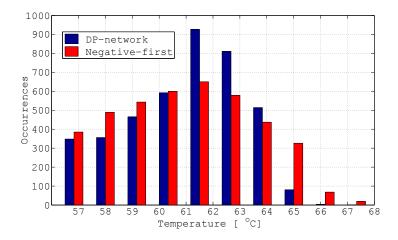

| Figure 5.8   | Temperature occurrences over the 80-tiles chip                                                 |     |

| г.           | with <i>transpose</i> traffic scenario                                                         | 113 |

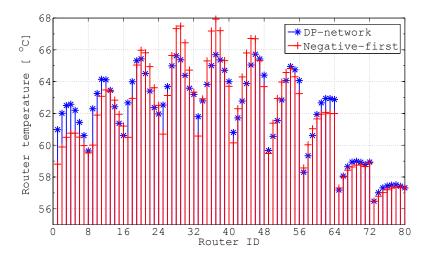

| Figure 5.9   | Maximum steady state temperature distribution                                                  |     |

|              | of the 80-tiles chip subjected to <i>transpose</i> traffic                                     |     |

|              | scenario                                                                                       | 114 |

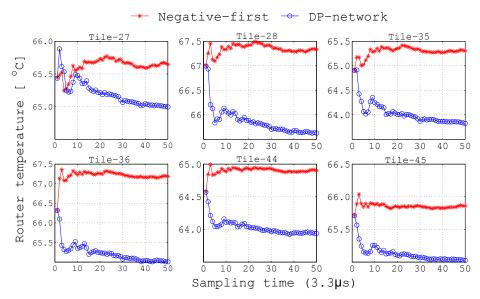

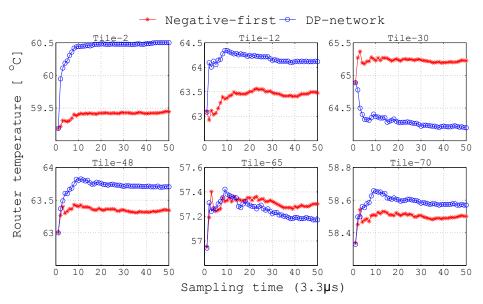

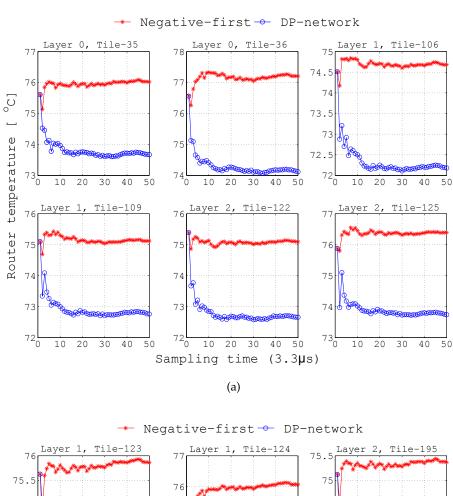

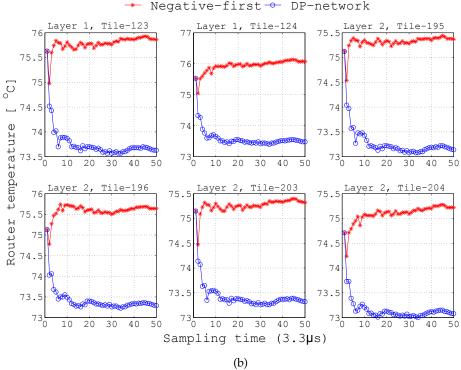

| Figure 5.10 | Temperature variation over time for a selection of tiles interconnected as $8 \times 10$ <sub>2D</sub> mesh NoC |      |

|-------------|-----------------------------------------------------------------------------------------------------------------|------|

|             | and subjected to <i>transpose</i> traffic                                                                       | 115  |

| Figure 5.11 | Temperature distribution of the simulated $8 \times$                                                            |      |

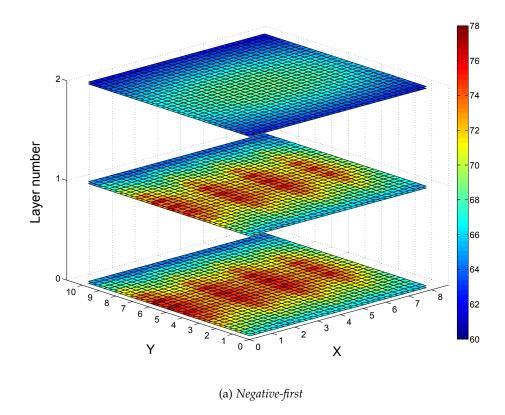

|             | $10 \times 3$ 3D NoC subjected to <i>butterfly</i> traffic scenario                                             | 0117 |

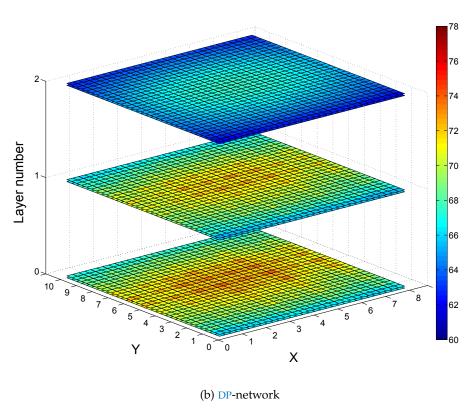

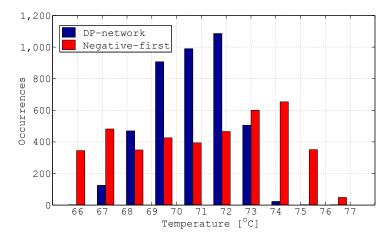

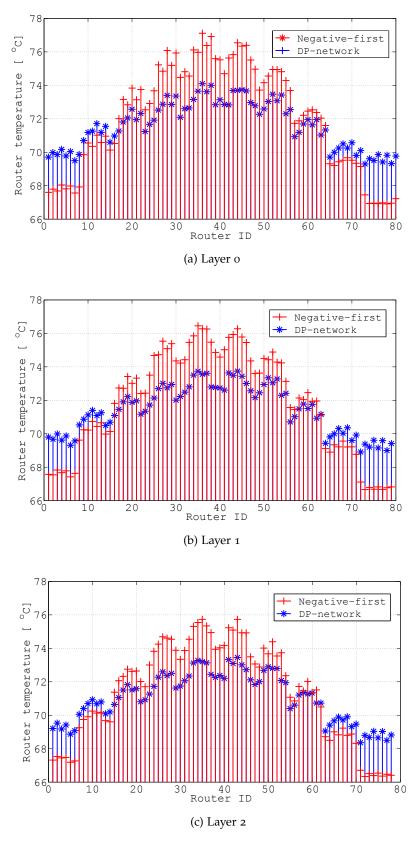

| Figure 5.12 | Temperature distribution over the 240-tiles chip                                                                |      |

|             | with <i>butterfly</i> traffic scenario                                                                          | 118  |

| Figure 5.13 | Maximum temperature distribution over the 240-                                                                  |      |

| Diama = .   | tiles chip                                                                                                      | 119  |

| Figure 5.14 | Temperature change over time for a selection of tiles under <i>butterfly</i> traffic                            | 120  |

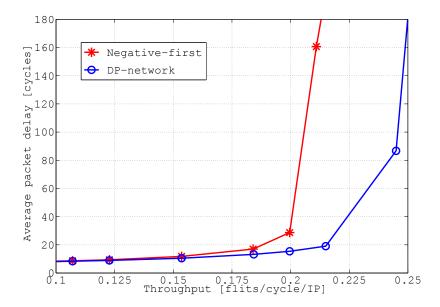

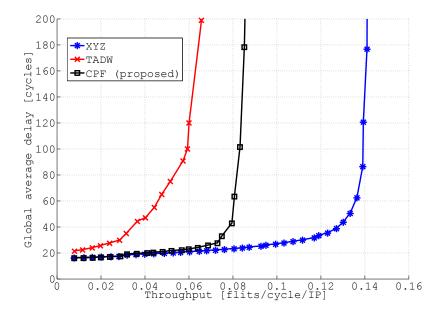

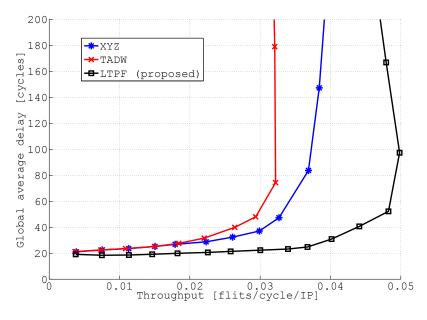

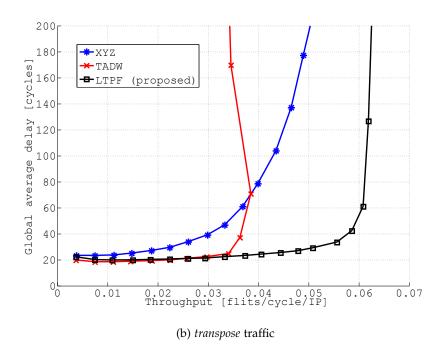

| Figure 5.15 | NoC performance (Average delay versus Through-                                                                  |      |

|             | put) for <i>transpose</i> traffic                                                                               | 121  |

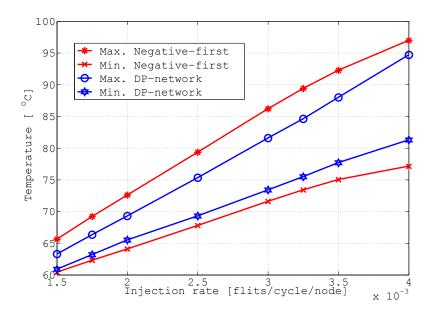

| Figure 5.16 | Maximum (max.) & minimum (min.) tempera-                                                                        |      |

|             | ture for the hottest layer under transpose traffic.                                                             | 121  |

| Figure 6.1  | The proposed dynamic programming-based run-                                                                     |      |

|             | time thermal management (DPRTM) for NoCs                                                                        | 128  |

| Figure 6.2  | Illustration of the routing paths in <b>DPRTM</b> system.                                                       | .129 |

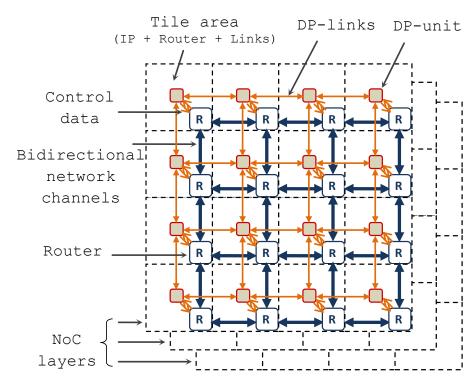

| Figure 6.3  | DP-network coupled to a 3D mesh NoC                                                                             | 130  |

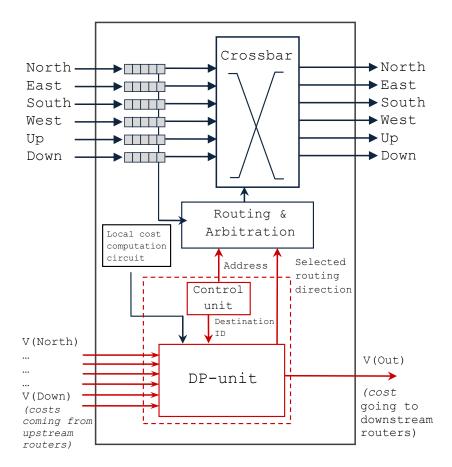

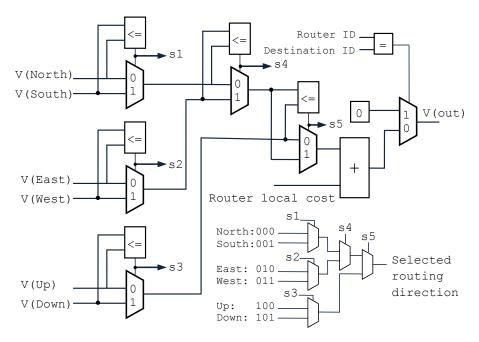

| Figure 6.4  | Schematic design of 3D mesh NoC router with a                                                                   |      |

| _           | DP-network. The computation unit is integrated                                                                  |      |

|             | to the local router to enable dynamic thermal-                                                                  |      |

|             | aware routing. The DP computational unit inter-                                                                 |      |

|             | connects with other DP-units locating at adjacent                                                               |      |

|             | tiles                                                                                                           | 134  |

| Figure 6.5  | Realization of the DP computational unit                                                                        | 135  |

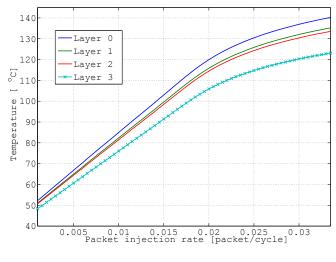

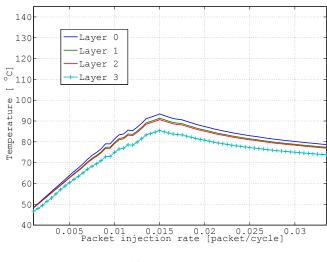

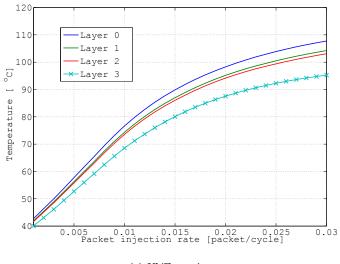

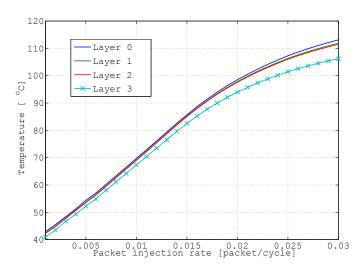

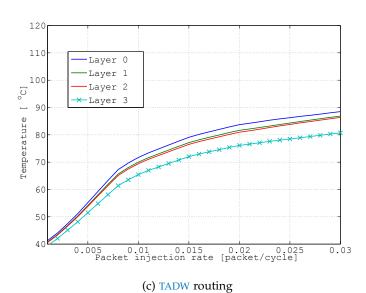

| Figure 6.6  | Maximum temperature of each layer for different                                                                 |      |

|             | routing algorithms under uniform traffic distri-                                                                |      |

|             | bution                                                                                                          | 137  |

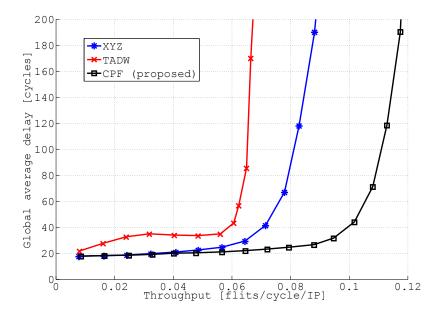

| Figure 6.7  | NoC performance results for different routing                                                                   |      |

|             | algorithms under <i>uniform</i> traffic distribution                                                            | 138  |

| Figure 6.8  | Maximum temperature of each layer for different                                                                 |      |

| _           | routing algorithms under transpose traffic scenario                                                             | .140 |

| Figure 6.9  | NoC performance results for different routing                                                                   |      |

| _           | algorithms under transpose traffic scenario                                                                     | 141  |

| Figure 6.10 | Performance results for different routing algo-                                                                 |      |

|             | rithms under fixed throttled routers concentrated                                                               |      |

|             | in the centre of the NoC                                                                                        | 143  |

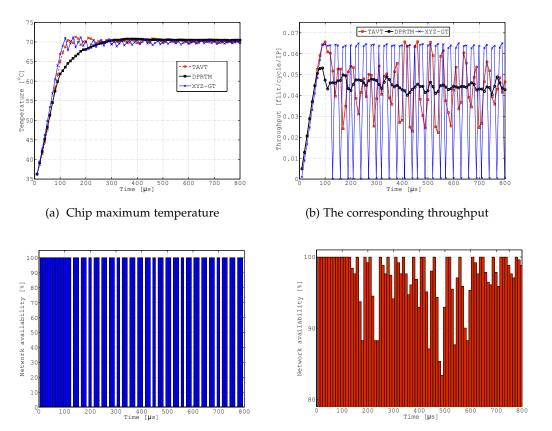

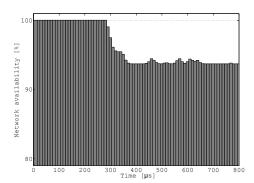

| Figure 6.11 | The results of temperature regulation for a ther-                                                               |      |

| -           | mal limit of 70 °C for different run-time thermal                                                               |      |

|             | management (RTM) methods                                                                                        | 145  |

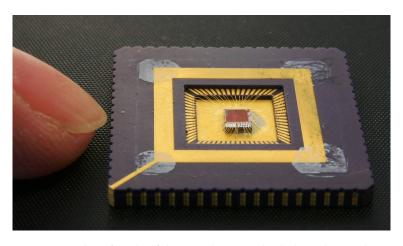

| Figure A.1  | Snapshot for the fabricated 3D stacked three-                                                                   |      |

| -           | layer chip in the package after removing the top                                                                |      |

|             | cover                                                                                                           | 156  |

|             |                                                                                                                 | _    |

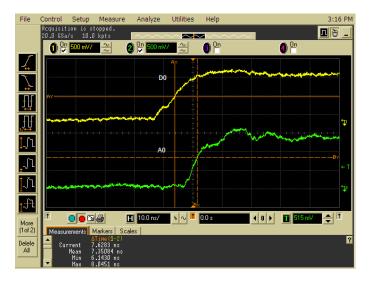

| Figure A.2 | Snapshot from the digital signal analyzer showing the start of TC computation and the deadlock                                                           |            |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

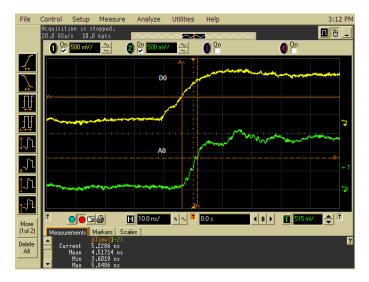

| Figure A.3 | detection signal (detection time equal to 7.9 ns)<br>Oscilloscope capture showing deadlock detec-                                                        | 156        |

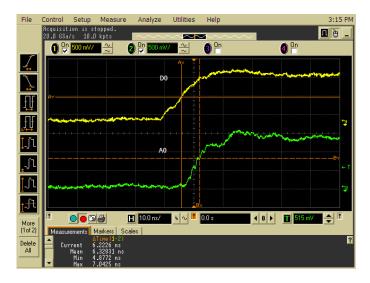

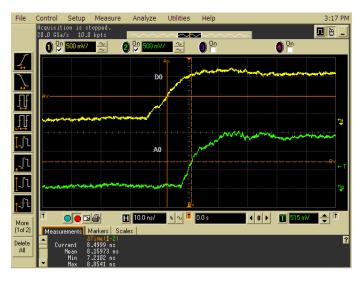

| Figure A.4 | tion (loop size 4)                                                                                                                                       | 158        |

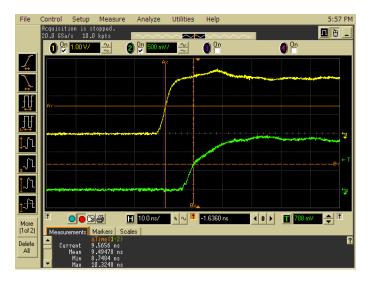

| Figure A.5 | tion (loop size 6)                                                                                                                                       | 158        |

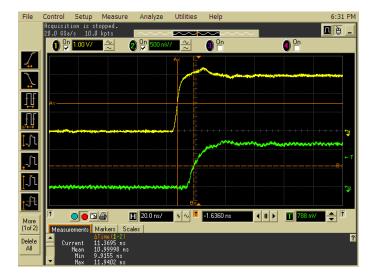

| Figure A.6 | tion (loop size 8)                                                                                                                                       | 158        |

| Figure A.7 | Oscilloscope capture showing deadlock detection (loop size 12)                                                                                           | 159<br>159 |

| Figure A.8 | Oscilloscope capture showing deadlock detection(loop size 14)                                                                                            | 159        |

| Figure A.9 | Oscilloscope capture showing the output of the through layers (3D-IC) ring oscillator                                                                    | 160        |

| Table 2.1  | Deadlock handling strategies in packet-switching networks: a comparison                                                                                  | 21         |

| Table 2.1  |                                                                                                                                                          | 21         |

| Table 2.2  | Different vertical interconnect technologies: a comparison                                                                                               | 24         |

| Table 2.3  | Different approaches to implement the on-chip networks                                                                                                   | 34         |

| Table 2.4  | Main featurtes and differences among the avilable on-chip networks simulators                                                                            | 36         |

| Table 3.1  | DES analysis of a TC-network for different network topologies                                                                                            | 50         |

| Table 3.2  | TC-network improvement compared to timing based methods for different threshold values and traffic scenarios                                             | 6.         |

| Table 3.3  | Energy consumption ( <i>mJ</i> ) to drain 2 Mbytes of multi-media system data for different network                                                      | 64         |

| Table 3.4  | loads and different deadlock detection methods<br>Area and power contributions of the TC-unit and<br>different timeout circuits to the total router area | 68         |

| Table 3.5  | and power                                                                                                                                                | 70         |

|            | percentage of total energy consumed to resolve<br>them under <i>shuffle</i> traffic scenario with different<br>deadlock detection schemes                | 76         |

| Table 5.:         | Performance metrics, maximum and minimum steady state temperature measurements (in C°) for different network traffic with and without DP-network                            | 22       |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Table 6.:         | Achievable performance metrics for different routing algorithms with different thermal limits                                                                               |          |

| Table 6.2         | routing algorithms with different thermal limits                                                                                                                            | 8        |

| Table 6.3         | under <i>transpose</i> traffic                                                                                                                                              | 9        |

| Table 6.2         | for both RTM methods under <i>uniform</i> traffic 14 The resulting network availability and the corresponding throughput different thermal limits                           | 4        |

| Table 6.          | for both RTM methods under <i>transpose</i> traffic 14 Router plus DP-unit area and power synthesiza-                                                                       |          |

| Table 6.6         | r                                                                                                                                                                           |          |

| Table A. Table B. | chip                                                                                                                                                                        | 57       |

|                   | the thermal simulation                                                                                                                                                      | )2       |

|                   |                                                                                                                                                                             |          |

| LIST C            | OF ALGORITHMS                                                                                                                                                               |          |

| 3.1               | Pseudo code to check the existence of a DES using TC computation                                                                                                            | 17       |

| 3.2               | D 1 1 (1 1)                                                                                                                                                                 | 17<br>53 |

| 4.1               | Floyd-Warshall algorithm to compute all-pairs shortest-paths from a directed weighted graph 9                                                                               | 32       |

| 5.1               | Pseudo code of the proposed dynamic thermal optimization routing using DP-network                                                                                           | )5       |

| 6.1<br>6.2        | Decide throttling level $TR_n(t)$ of the current node $n_c$ . 13 Pseudo code for computing the routing directions performed by each DP-unit of the proposed DPRTM system 13 |          |

### **ACRONYMS**

2D two dimensional

2D-NoC two dimensional network-on-chip

2D-NoCs two dimensional networks-on-chip

3D three dimensional

<sub>3</sub>D-IC three dimensional integrated circuit

3D-NoC three dimensional network-on-chip

3D-NoCs three dimensional networks-on-chip

ASIC application-specific integrated circuit

ASL application specific logic

AXI advanced extensible interface

BES best-effort service

CMOS complementary metal-oxide semiconductor

CMP chip multiprocessor

CPF coolest path-first

LTPF least throttled paths-first

CPU central processing unit

CRC cyclic redundancy check

CWG channel wait-for graph

DW-XYZ downward XYZ

DC David cell

DES deadlock-equivalence set

DMEM data memory

DOR dimension-ordered routing

DP dynamic programming

DPRTM dynamic programming-based run-time thermal management

DSP digital signal processing

DT distributed-throttling

DVFS dynamic voltage and frequency scaling

FIFO first in, first out

FPGA field-programmable gate array

GALS globally asynchronous locally synchronous

GS guaranteed service

GT global-throttling

I/O input/output

IC integrated circuit

ID identification

IMEM instruction memory

IP intellectual properties

IR injection rate

ITRS International Technology Roadmap for Semiconductors

LP linear programming

MEMS micro-electro-mechanical systems

MMS multi-media system

MIC many integrated core

MIPS microprocessor without interlocked pipeline stages

MPEG moving picture experts group

MPSoC multiprocessor system-on-chip

NI network interface

NMOS n-type metal-oxide-semiconductor logic

NoCs networks-on-chip

NoC network-on-chip

OCP open core protocol

OS operating system

PCB printed circuit board

PDA personal digital assistant

PIR packet injection rate

PMOS p-type metal-oxide-semiconductor logic

PTM predictive technology model

PVT process-voltage-temperature

QoS quality of service

RC resistance-capacitance

RLC resistance-inductance-capacitance

RF radio frequency

RO ring oscillator

RTL register transfer language

RTM run-time thermal management

SCC single-chip cloud computer

SoC system-on-chip

SRAM static random-access memory

TADW traffic-aware downward

TAVT thermal-aware vertical throttling

TC transitive closure

TDM time-division multiplexing

TSV through-silicon via

ATtAT average-throughput to average-availability

VC virtual channel

VLSI very large scale integration

VT vertical-throttling

XYZ-GT XYZ with global-throttling

# Part I Thesis Chapters

#### 1.1 MOTIVATION AND OBJECTIVE

The continuing advances in technology scaling over the past decades have led to important improvements in the portability, size and performance of electronic products, but with some real communication challenges. Increases in design complexity, system-wide synchronisation issues, larger process-voltage-temperature (PVT) variation, increased vulnerability to errors and increases in the global interconnect delay are all examples of the design challenges. These challenges led the very large scale integration (VLSI) designers to adopt a communication centric design with a systematic and structured approach to communicate in system-on-chip (SoC). This can be achieved through modularity, plug-and-play, intellectual properties (IP) core reuse and standard interfaces (e.g., open core protocol (OCP) and advanced extensible interface (AXI)) with hybrid synchronous and asynchronous schemes (i.e., globally asynchronous locally synchronous (GALS) systems).

The networks-on-chip (NoCs) became the choice of communication paradigm for SoCs and chip multiprocessors (CMPs) design to tackle many of the challenges associated with technology scaling. NoCs play an important role by providing a scalable, flexible and power efficient solution to integrate tens of IP cores in a single chip. For example, Intel 80-tile teraFLOPS [157] and Tilera 64-tile TILEPro [10] are multicore processor chips built on top of network-on-chip (NoC) communication fabric. Migrating from on-chip point-to-point and bus-based communication schemes to network schemes opens doors for research topics such as network topology selection, application mapping, data routing algorithms, fault-tolerant routing, quality of service (QoS), monitoring, debugging, etc. Some of these, such as topology selection and application mapping, can be tackled at design-time; while others, like adaptive routing and fault-tolerant routing algorithms, require design and run-time awareness.

In addition, shrinking feature size to the deep submicron technologies enables smaller and denser IP core design and thus allows increasing the number of cores integrated in a single chip. In terms of delay, however, scaling favours logics and short interconnects more than global interconnects for a constant die size, as shown in Figure 1.1. Therefore, data (messages or packets) transmitted using planar NoC with a large number of cores will suffer from bigger delay because of the increase of hop count and the global interconnects delay. The advent of the multi-level integrated circuit (IC) using three di-

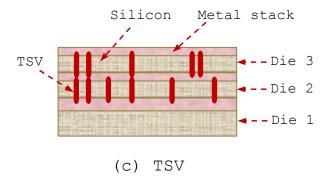

mensional (3D) VLSI [135, 63, 106] opens a new prospect for design of on-chip networks by providing a new dimension to exploit novel geometric integration of silicon dies. A variety of vertical cross-die interconnection techniques are being developed [58]. In particular, the through-silicon via (TSV) [144, 20, 95] of three dimensional integrated circuit (3D-IC) connecting multiple die/wafer layers in a single chip provides opportunities to increase the integration capacity and also reduces the lengths of global interconnects. However, increases in yield and heat mitigation are major issues facing the 3D integration advancements. In particular, thermal issues are exacerbated by the advent of 3D integration. This will worsen the figures reported in [148] which state that over 50% of electronic product failures can be accounted for by thermal issues and hotspot formations.

Figure 1.1: The trend of logic delay and interconnect delay with technology scaling (source data: ITRS [3]).

Moreover, on-chip system complexity grows significantly with continued increasing transistor density caused by aggressive technology scaling and the additional tightly coupled physical layers imposed by 3D integration. Therefore communication resources management in such complex systems becomes a major challenge. Examples of pervasive NoCs services that might require run-time management are dynamic packets routing, thermal diffusion, thermal management, fault-tolerant routing, managing the voltage and frequency islands, etc. This thesis argues that in-depth understanding of the NoC architecture is of vital importance to enable the designer to exploit the underlying architecture and find new efficient solutions for such challenges. The primary objective of this thesis is the exploration of

innovative methods that maximize the on-chip networks performance while complying to some design constraints.

This thesis also argues that with such an increase in the on-chip system complexity, design time methods may not be able to fully utilize the underlying hardware resources to dynamically adapt to the traffic, power and thermal constraints. The thesis aims to propose a design methodology that advocates the use of a run-time management infrastructure that can be realized using a distributed architecture which closely couples with the NoC infrastructure. This infrastructure can be defined and built to produce run-time solutions for different NoC based systems challenges. The work investigates several NoCs challenges, in particular: runtime deadlock detection, optimized thermal-aware routing and thermal-management of complex 3D multi-core systems. It can be extended using a similar methodology to tackle other run-time issues such as fault-tolerant routing, managing and optimizing the voltage and frequency islands.

#### 1.2 STRUCTURE OF THE THESIS

The thesis is organised into seven chapters, as follows:

Chapter 2 provides on-chip network theory, architecture design and modelling to enable the reader to understand the motivation and the choices made in the subsequent chapters. It also reviews the emerging technologies that promise profound change in on-chip communication architecture. In addition, different methodologies and techniques for designing NoCs from various leading research groups and VLSI companies are reviewed.

Chapter 3 studies deadlock detection and recovery in networks-onchip, as opposed to deadlock avoidance. It presents a new deadlock detection method that utilizes run-time transitive closure computation to discover the existence of deadlock-equivalence sets which imply loops of requests in NoCs. A distributed transitive closure (TC)-network architecture, which couples with the NoC architecture, is also presented to realize the detection mechanism efficiently. The parallel computation and network convergence properties of the TC network are discussed. Evaluation results using a cycle-accurate simulator and synthesis tools are presented. Detailed hardware realization architectures and schematics are offered.

Chapter 4 quantifies the advantages of using three dimensional networks-on-chip (3D-NoCs) compared to two dimensional networks-on-chip (2D-NoCs), using different design measures for different network sizes. Specifically, the average shortest paths length, network performance and deadlock formation rate are studied for 3D-NoCs

and 2D-NoCs. Moreover, the chapter presents the design and the chip fabrication results of the proposed 3D TC-network used for run-time deadlock detection. The prototype consisted of three tiers stacked in a single chip and interconnected using TSV technology.

Chapter 5 studies thermal variations and hotspot formations in the three dimensional network-on-chip (3D-NoC) stacked chip. It introduces an adaptive strategy to effectively diffuse heat throughout the 3D geometry. This strategy employs a dynamic programming network to select and optimize the direction of data manoeuvre in a NoC. This led to developing a tool chain, which is based on the accurate *HotSpot* thermal model and *SystemC* cycle accurate model, to simulate the thermal system and evaluate the proposed approach. Evaluation results using the developed tool chain are presented.

Chapter 6 proposes an adaptive, collaborative dynamic programming-based run-time thermal management (DPRTM) system for NoCs. It manages the routing workload dynamically to achieve thermal mitigation and control. Reactive and proactive schemes are interchanging to optimize the routing pathways depending on the critical temperature thresholds and the traffic developments. When the thermal limit is violated, DPRTM responds by throttling the routers where violation took place. The proposed DPRTM is evaluated and compared with other run-time thermal management (RTM) systems in terms of adaptation efficiency and thermal regulation.

Chapter 7 summarises the contributions of this thesis and directions for future work are identified.

# 1.3 STATEMENT OF ORIGINALITY

I have published a large amount of the work in this thesis in conference proceedings and journals. The materials have been explained in four major divisions, which are covered in separate chapters. Each chapter has an introductory section and related work section. The introduction in each chapter describes the rationale and contributions in further detail, while the related work sections present and discuss works pertinent to the issues addressed in the chapter. The main contributions of this thesis are listed as follows:

Proposing a novel deadlock detection method that utilizes runtime transitive closure computation to discover the existence of deadlock-equivalence sets in NoCs. This detection scheme guarantees the discovery of all true-deadlocks without false alarms, in contrast with state-of-the-art approximation and heuristic approaches. A distributed TC-network architecture, which cou-

ples with the NoC architecture, is also presented to realize the detection mechanism efficiently [14].

- Introducing a deadlock-equivalence set criterion for detecting loops of packet requests and presenting a new deadlock detection scheme to discover the existence of deadlock-equivalence sets based on TC computation. Detailed hardware realization architectures and schematics are presented. The proposed method is rigorously evaluated using a cycle-accurate simulator and synthesis tools to demonstrate the effectiveness of the TC-network based detection method compared to the time-out mechanism. Experimental results confirm the merits and the effectiveness of the proposed method. It drastically outperforms timing-based deadlock detection mechanisms by eliminating false detections and, thus, reduces energy wastage in retransmission for various traffic scenarios including real-world application [19].

- Quantifying the effectiveness of using 3D-NoCs compared to 2D-NoCs using different design measures for different network sizes. The average shortest paths length, network performance (throughput and saturation injection rate) and deadlock formation rate all show a considerable improvement when adopting 3D-NoCs compared to 2D-NoCs [15].

- Introducing the design of TC-network architecture and its implementation, using three-layer 3D-IC. The vertical inter-unit communication is achieved by means of TSV. The three-layer chip prototype is fabricated using 150nm complementary metal-oxide semiconductor (CMOS) technology. Prototype testing results demonstrated the TC-network is effective and detects deadlock rapidly in a NoC platform [115, 116].

- Proposing a new adaptive strategy to effectively diffuse heat throughout the 3D geometry. This strategy employs a dynamic programming network to select and optimize the direction of data manoeuvre in a NoCs. This led to developing a tool chain, which is based on the accurate *HotSpot* thermal model and *SystemC* cycle accurate model, to simulate the thermal system and evaluate the proposed approach. The evaluation results demonstrated that the proposed approach can significantly diffuse the hotspots from a 3D geometry and maximum temperature can be reduced by 4°C [18, 17].

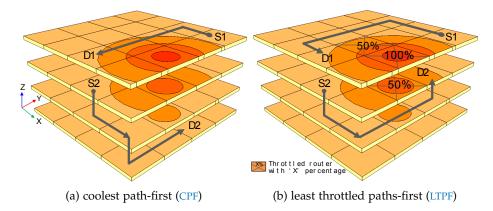

- Proposing a novel adaptive, collaborative dynamic programming-based thermal management system for NoC (DPRTM). The system manages the routing workload dynamically to achieve thermal mitigation and control. Routing in DPRTM adapts in two modes: coolest path-first (CPF) and least throttled paths-first (LTPF). The first mode is active while the chip works within the thermal limit

and aims to diffuse heat from the 3D chip geometry and prevent thermal hotspots for as long as possible. When the thermal limit is violated, DPRTM responds by throttling the routers where violation takes place. This action introduces irregularity in terms of communication performance in the network. Thus, DPRTM adapts to this irregularity by changing its routing strategy to give priority to the least throttled paths in order to minimize the performance impact of throttling. Since the proposed routing adaptation strategy is resilient to any throttling taking place, a distribute clock throttling strategy is employed in the DPRTM. The proposed DPRTM is rigorously evaluated and the results show that it overcomes other RTM systems in terms of adaptation efficiency and thermal regulation. Results show that DPRTM achieves up to 33% improvement in throughput compared to other RTM systems for 3D-NoC under the same thermal constraints [16].

#### 2.1 INTRODUCTION

In recent years, there has been an increasing interest in designing and developing SoC and CMP in order to deliver new levels of performance under strong time-to-market pressure while also achieving cuts in system costs. This requires the use of appropriate design methodologies, including incorporating a proper on-chip communication fabric to interconnect existing components in a plug-and-play manner. SoC is a single chip IC that integrates heterogeneous components, e.g., general purpose microprocessors, digital signal processing (DSP), memories (static random-access memory (SRAM), Flash), application specific logic (ASL) and any other IP cores, in order to provide feasible solutions to a variety of design problems. On the other hand, a CMP IC consists of several homogeneous processor blocks to build a high performance processor. In recent years, industry chip vendors demonstrate an increasing concentration in multi-core products by releasing new processors with greater core counts. The state-of-the-art communication models to interconnect these SoC's and CMP's building blocks (IP cores) are either point-to-point or bus-based schemes [33].

However, the latest advancements in VLSI circuit design have heightened the need for different on-chip communication architecture to handle the increasingly large number of IP cores integrated in a single silicon chip. There is also an increased demand in bandwidth requirements of the on-chip communication fabrics to match the increase on the integrated IP cores and thus assist high core utilization. Moreover, technology downscaling at the deep submicron level decreases logic (transistors) delays but increases interconnect delays, in particular the global interconnect [76]. Global interconnects are used to transmit data across a chip. Therefore, it is becoming increasingly difficult to rely on the state-of-the-art on-chip communication schemes to fulfil different system requirements in terms of scalability, modularity, parallelism and synchronization while still complying with the time-to-market pressure. Thus provision for a communication-centric approach to design complex SoCs becomes vital [133, 126].

Recently, NoC emerged as a new on-chip communication paradigm to alleviate the limitations of the point-to-point and bus-based interconnection schemes. This chapter briefly introduces the basic concepts and theory behind the NoC paradigm in order that the reader can understand the motivation and the choices made in the context of this work. In the literature, there are prominent research efforts devoted to

addressing different on-chip network challenges and also a considerable number of different architectures have been proposed. A review for a variety of NoC architectures are presented and discussed in this chapter. The contributions of this chapter are as follows:

- Providing basic concept and theory behind the NoC's architecture, components, flow control, deadlock and livelock (Section 2.3 to 2.6)

- Reviewing NoC emerging technologies like three dimensional integration, optical interconnect and wireless interconnect (Section 2.7).

- Presenting a comprehensive survey of various NoC architecture and routing algorithms proposed by a number of leading research groups and VLSI design companies (Section 2.8).

- Surveying and presenting the different features of the available NoC simulator platforms

#### 2.2 NETWORKS-ON-CHIP (NOCS)

NoC emerged as a new on-chip communication paradigm for SoC and CMP design. This new paradigm transmits packets between onchip cores through a network of interconnected routers (a.k.a. switch) instead of using the classical point-to-point and bus-based interconnection, see Figure 2.1. NoC provides a scalable, flexible, high performance and power efficient solution to integrate hundreds of IP cores in a single silicon chip like SoC and CMP. Each of the IP cores can be an implementation of processor cores, memory modules, DSP blocks and embedded reconfiguration modules that consist of millions of transistors [141, 78]. In essence, NoCs are similar to interconnection networks for parallel computers with multiple processors. However, in the latter each IP is an individual chip and the communication takes place at the printed board level that integrated them. Whereas in NoC, all the components are integrated in a single chip and this make NoC design challenging under tighter area and power constraints. The past decade has seen rapid advances in the NoC field through an abundance of research papers [55, 133, 68, 35, 103], books [130, 90, 42, 36] and successful implementation projects [157, 59, 10].

# 2.3 COMPONENTS OF NOCS

An on-chip interconnection network consist of a router at every node, connected to neighbour via interconnects (on-chip wiring) and a network interface (NI) to bind each IP core to a router. The NoC main components (router, link and NI) are interconnected with IP cores to form a SoC or CMP. However, NoC has also been widely used as an

Figure 2.1: General network-on-chip (NoC) structure

abbreviation to include all on-chip networks [92]. The four on-chip components are commonly called 'Tile' in a tile-based chip design approach, where one tile is designed and then replicated to perform a complex on-chip system. The chip is divided into tiles, each with an IP core, NI, router and links.

The layout pattern of interconnections of all on-chip components is called network topology. Many topologies exist in the literature to constitute SoCs, the simplest being the shared bus and ring. Figure 2.2 shows different NoCs topologies along with the classical shared bus; some of these are general purpose and one is application specific. The selection of the appropriate topology will follow SoC and CMP design constraints such as performance, area, power, locality of traffic and quality of service. There follows a brief description of each of the on-chip components:

#### 2.3.1 *Router*