# IMPROVING FAULT TOLERANT DRIVES FOR AEROSPACE APPLICATIONS

Andrew Wechsler

A thesis submitted for the degree of Engineering Doctorate

January, 2013

School of Electrical and Electronic Engineering

Newcastle University

United Kingdom

### Preface

This thesis is submitted as part of the Engineering Doctorate (EngD) degree.

The EngD differs slightly from the traditional Philosophy Doctorate (PhD) in the sense that it is more a portfolio of work undertaken at industry. The Engineering and Physical Sciences Research Council (EPSRC) describes the Engineering Doctorate as:

"A four-year programme that combines PhD-level research projects with taught courses, and students spend about 75% of their time working directly with a company"

In the first year of the EngD, various modules from MSc and MBA programs are undertaken. The remaining 3 years focuses on the main body of research, in collaboration with the industrial sponsor.

The work undertaken in this thesis was done at Newcastle University with Goodrich Actuation Systems (part of Goodrich Aerospace, now United Technologies) as the industrial sponsor.

### Abstract

The aerospace industry is moving towards the more electric aeroplane where traditional hydraulic systems are being replaced with electrical systems. Electrical technology offers some strong advantages compared to hydraulic technology including; cost, efficiency, power on demand and relative ease of maintenance. As with most new technologies, a major disadvantage is its limited reliability history. A lot of research in the aerospace field therefore focuses on improving fault tolerant electrical systems.

Work done in this thesis builds on an existing fault tolerant drive, developed by Newcastle University and Goodrich Actuation Systems as part of the ELGEAR (Electrical Landing Gear) project. The purpose of this work is to continue improving the drive's fault tolerant features; especially in areas where the drive is most vulnerable.

The first part of this thesis focuses on improving the overall system reliability by monitoring the health of the dc-link capacitors in the fault tolerant drive. The implemented estimation technique makes use of voltage and current sensors which are already in place for protection and control purposes. The novel aspect of the proposed technique relates to monitoring capacitors in real time whilst the motor is operational. No external interferences, such as injected signals or special operation of the drive, are required. The condition monitoring system is independent of torque and speed, and hence independent of a variation in load. The work was validated using analytical methods, simulation, low voltage experimentation and high voltage implementation on the ELGEAR drive.

The second part of this thesis focuses on single shorted turn faults, in fault tolerant permanent magnet (PM) motors. Despite the motor being able to withstand a wide range of faults, the single shorted turn fault remains a difficult fault to detect and handle. The problem arises from the magnets on the spinning rotor that cannot be 'turned off' at will. This thesis investigates the severity of the faulted current in a shorted turn and how it varies depending on the turn's location in the stator slot. The severity of the fault is studied using 2D finite element analysis and practical implementation on the ELGEAR rig. Finally, recommendations are proposed for improving the ELGEAR motor for future fault tolerant designs.

### Contents

| Preface        |                                             | ii    |

|----------------|---------------------------------------------|-------|

| Abstract       |                                             | iii   |

| List of figure | es                                          | xii   |

| List of tables | S                                           | xvii  |

| Acknowledg     | gements                                     | xviii |

| List of symb   | ols and acronyms                            | xix   |

|                |                                             |       |

| Chapter 1 -    | General Introduction                        | 1     |

| 1.1 Pri        | nciples of fault tolerance                  | 1     |

| 1.2 Co         | ntribution to knowledge                     | 2     |

| 1.3 Eve        | olving aircraft technology                  | 3     |

| 1.3.1          | The more electric aeroplane                 | 3     |

| 1.4 Fau        | It tolerant drives in aircraft              | 6     |

| 1.4.1          | Overview                                    | 6     |

| 1.4.2          | Redundant power generation and distribution | 7     |

| 1.4.3          | Fault tree                                  | 8     |

| 1.4.4          | Type of failures                            | 9     |

| 1.5 Ger        | neral research on reliability and failures  | 10    |

| 1.5.1          | Dormant failures                            | 10    |

| 1.5.2          | The ELGEAR fault tolerant drive             | 12    |

| 1.6 Ter        | minology and nomenclature                   | 12    |

| 1.6.1          | Motor drive electronics (MDE)               | 12    |

| 1.6.2          | Condition monitoring nomenclature           | 13    |

| 1.6.3          | Fault tolerant permanent magnet (PM) motor  | 14    |

|                |                                             |       |

| 1.    | 6.4    | Metallised polypropylene film (MPPF) capacitors          | 14 |

|-------|--------|----------------------------------------------------------|----|

| 1.    | 6.5    | dsPIC (digital signal peripheral interface controller)   | 14 |

| 1.7   | Res    | search objectives                                        | 14 |

| 1.8   | The    | esis overview                                            | 15 |

|       |        |                                                          |    |

| Chapt | er 2 - | Condition Monitoring Literature                          | 17 |

| 2.1   | Intr   | roduction                                                | 17 |

| 2.2   | Gei    | neral reliability assessment of capacitors               | 17 |

| 2.    | 2.1    | Electrolytic capacitors                                  | 17 |

| 2.    | 2.2    | Metallised polypropylene film (MPPF) capacitors          | 19 |

| 2.    | 2.3    | MPPF parallel operation                                  |    |

| 2.3   | Det    | tailed study of MPPF capacitors                          |    |

| 2.    | 3.1    | Failure modes of MPPF capacitors                         |    |

| 2.    | 3.2    | Construction of MPPF capacitors                          |    |

| 2.    | 3.3    | Self healing property                                    |    |

| 2.    | 3.4    | MPPF literature summary                                  | 25 |

| 2.4   | Co     | ndition monitoring literature                            |    |

| 2.    | 4.1    | Offline monitoring systems – by removal of the capacitor |    |

| 2.    | 4.2    | Online monitoring systems – keeping the circuit intact   | 27 |

| 2.    | 4.3    | Conclusion                                               |    |

|       |        |                                                          |    |

| Chapt | er 3 - | Proposed Monitoring Design                               |    |

| 3.1   | Intr   | roduction                                                |    |

| 3.2   | Ma     | tlab Simulink                                            |    |

| 3.    | 2.1    | The motor                                                |    |

| 3.    | 2.2    | The controller                                           |    |

| 3.    | 2.3    | The inverter                                             |    |

| 3.2.4   | The dc-link                                          | 35 |

|---------|------------------------------------------------------|----|

| 3.2.5   | Capacitor calculation                                | 36 |

| 3.3 Pro | oposed dc-link capacitor condition monitoring system | 36 |

| 3.3.1   | Required sensors                                     | 39 |

| 3.3.2   | Design of a dc-link input filter for ELGEAR          | 40 |

| 3.3.3   | Zero voltage state monitoring                        | 41 |

| 3.3.4   | Zero voltage state current calculation               | 42 |

| 3.4 Si  | mulating the proposed condition monitoring system    | 43 |

| 3.4.1   | Drive simulation                                     | 43 |

| 3.4.2   | Capacitor open circuit fault simulation              | 45 |

| 3.5 Ha  | urdware layout                                       | 47 |

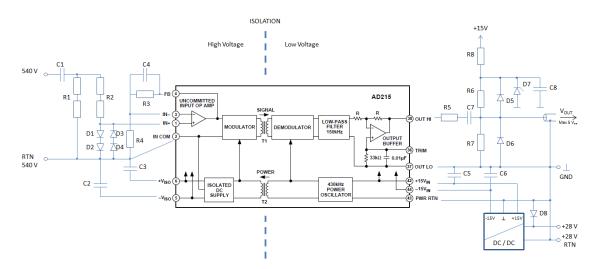

| 3.6 De  | esigning the voltage monitor                         | 48 |

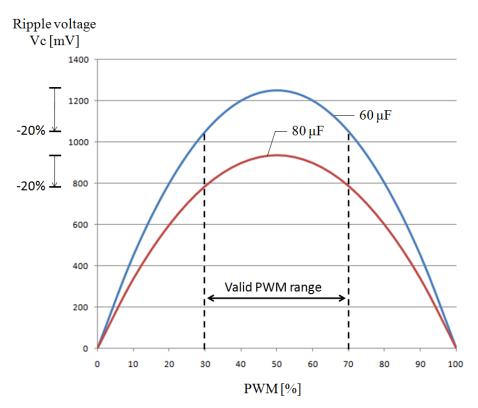

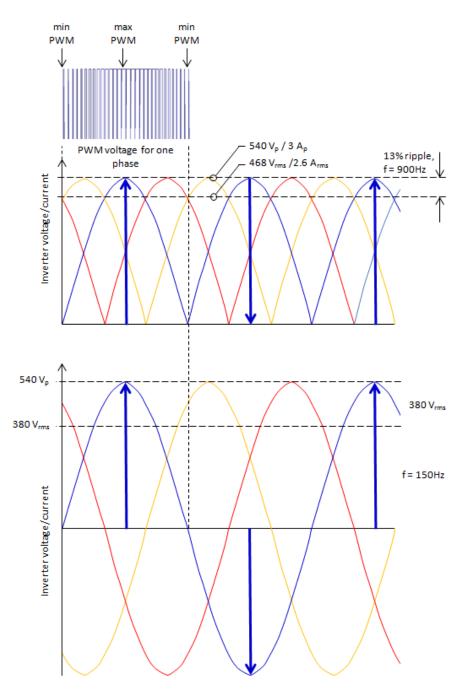

| 3.6.1   | Ripple voltage vs. PWM ratio                         | 48 |

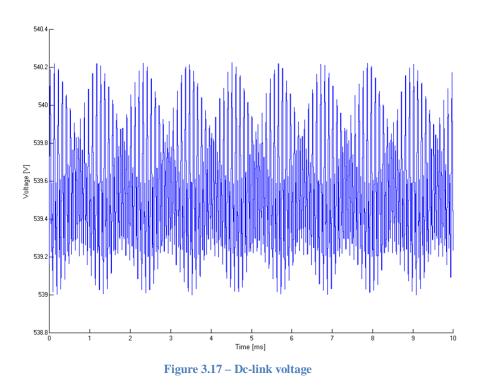

| 3.6.2   | Ripple voltage                                       | 51 |

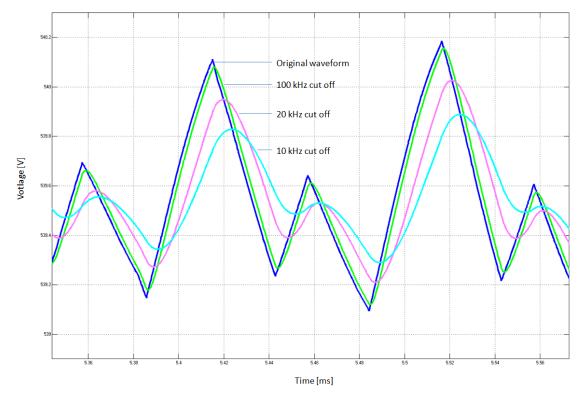

| 3.6.3   | Lower frequency dc-link voltage ripple component     | 52 |

| 3.6.4   | Cut off frequency                                    | 53 |

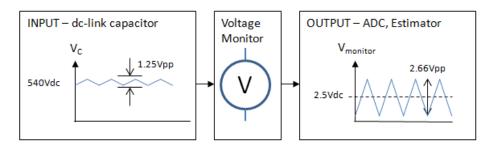

| 3.6.5   | Voltage monitoring hardware for ELGEAR               | 54 |

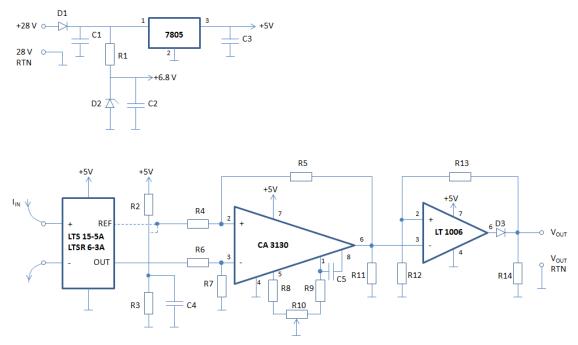

| 3.7 De  | esigning the current monitor                         | 57 |

| 3.8 Ti  | ming                                                 | 60 |

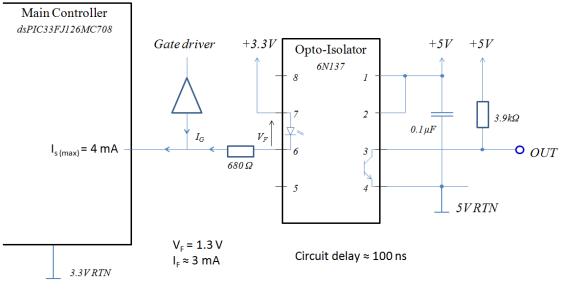

| 3.8.1   | IGBT opto-isolator                                   | 60 |

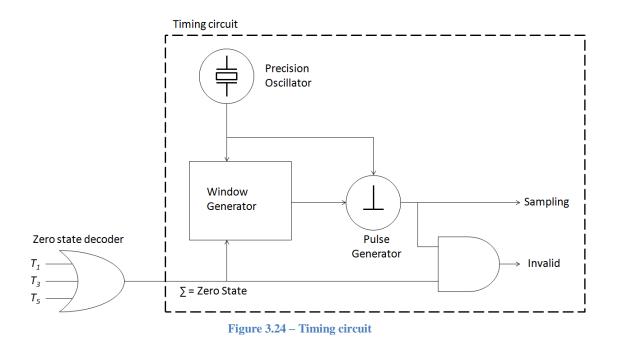

| 3.8.2   | Timing circuit design                                | 61 |

| 3.8.3   | Timing accuracy                                      | 62 |

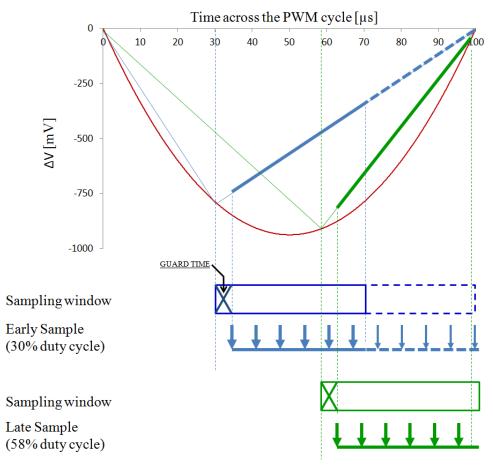

| 3.8.4   | Valid sampling example                               | 63 |

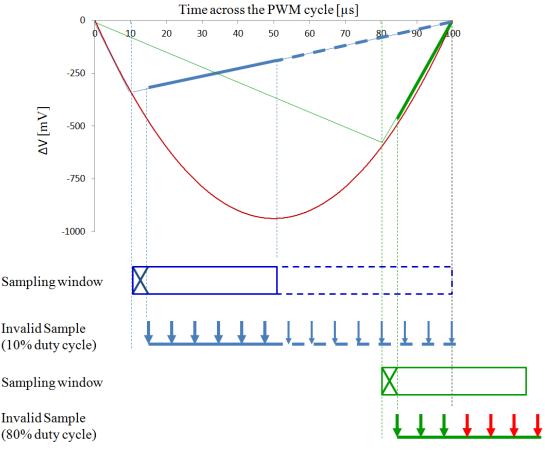

| 3.8.5   | Invalid sampling example                             | 64 |

| 3.9 Es  | timator                                              | 64 |

| 3.10    | Temperature dependence                               | 65 |

| 3.10.1  | Voltage monitor                                      | 65 |

| 3.10.2 | Current monitor                | . 66 |

|--------|--------------------------------|------|

| 3.10.3 | Overall temperature variation  | . 66 |

| 3.11 0 | Conclusions                    | . 66 |

| 3.11.1 | Comparison with the literature | . 66 |

| 3.11.2 | Proposed monitoring design     | . 67 |

|        |                                |      |

| Chapte | er 4 - Low Voltage Experimentation   | 68 |

|--------|--------------------------------------|----|

| 4.1    | Introduction                         | 68 |

| 4.2    | Principle of operation               | 68 |

| 4.3    | Low voltage vs. the high voltage rig | 70 |

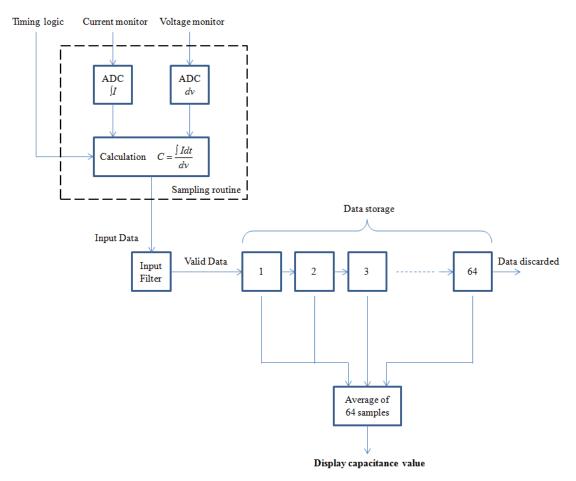

| 4.4    | Low voltage result                   | 71 |

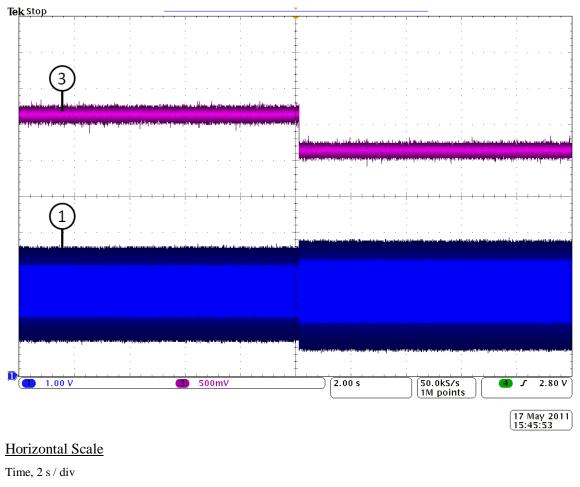

| 4.5    | Capacitor switch out                 | 72 |

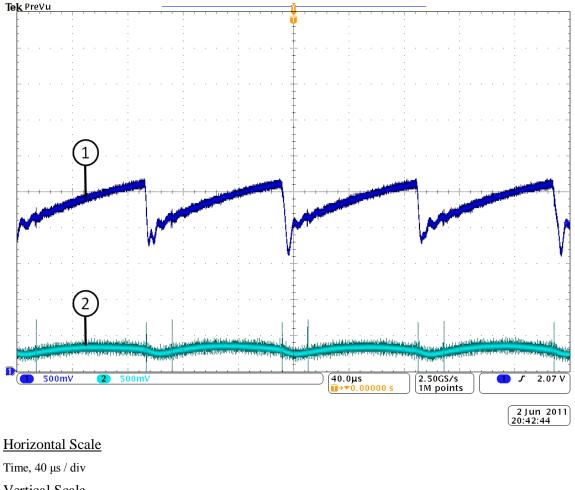

| 4.6    | Duty ratio modulation                | 74 |

| 4.7    | Conclusion                           | 75 |

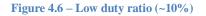

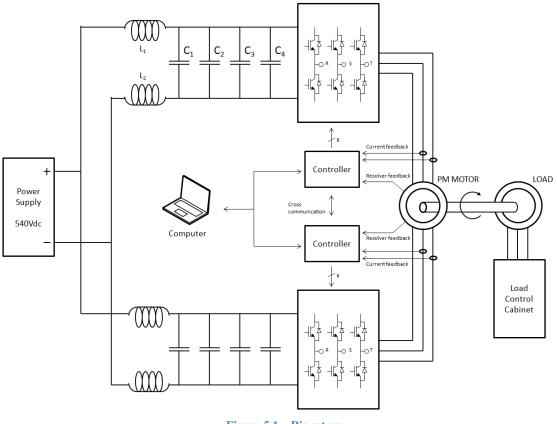

| Chapter | Chapter 5 - High Voltage Experimentation |                           |    |

|---------|------------------------------------------|---------------------------|----|

| 5.1     | Intr                                     | oduction                  | 77 |

| 5.2     | Hig                                      | h voltage test rig        | 77 |

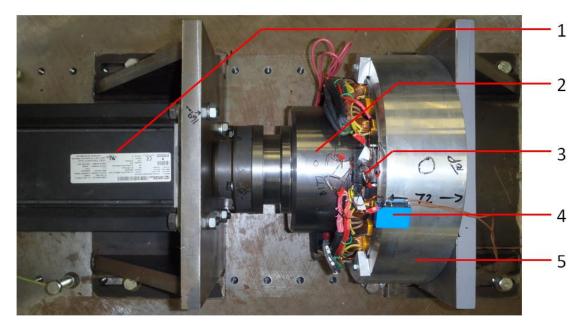

| 5.2     | .1                                       | Pictures                  | 78 |

| 5.2     | .2                                       | Power supply              | 81 |

| 5.2     | .3                                       | Drive                     | 81 |

| 5.2     | .4                                       | Master computer           | 83 |

| 5.2     | .5                                       | PM motor and load         | 83 |

| 5.3     | Exp                                      | perimental set up         | 84 |

| 5.4     | Cap                                      | pacitor fault simulation  | 84 |

| 5.4     | .1                                       | Switching method          | 85 |

| 5.4     | .2                                       | Capacitor fault switching | 85 |

|         |                                          |                           |    |

| 5.4  | 1.3  | Safety issues                                               | . 86 |

|------|------|-------------------------------------------------------------|------|

| 5.5  | Hig  | gh voltage nominal operation (80 μF)                        | . 87 |

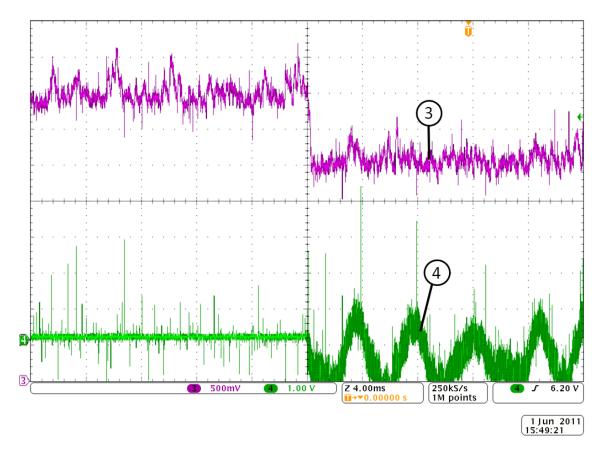

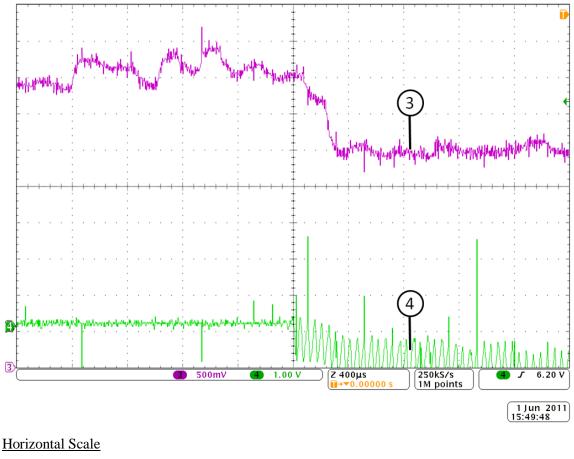

| 5.6  | Caj  | pacitor switch out (80 µF to 60 µF)                         | . 88 |

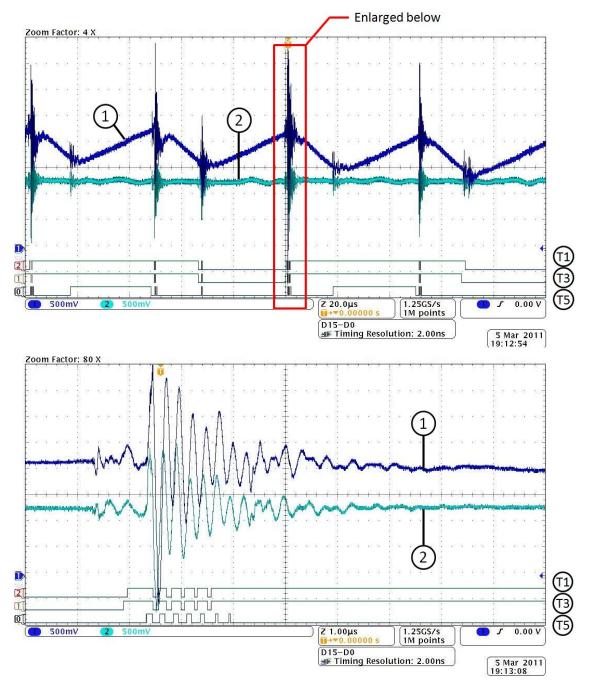

| 5.7  | Filt | tering techniques                                           | . 90 |

| 5.7  | 7.1  | No filter                                                   | . 90 |

| 5.7  | 2.2  | Introducing a data filter                                   | . 91 |

| 5.8  | Sta  | tistical analysis and accuracy                              | . 93 |

| 5.9  | Hig  | gh voltage experimental evaluation of capacitance estimator | . 95 |

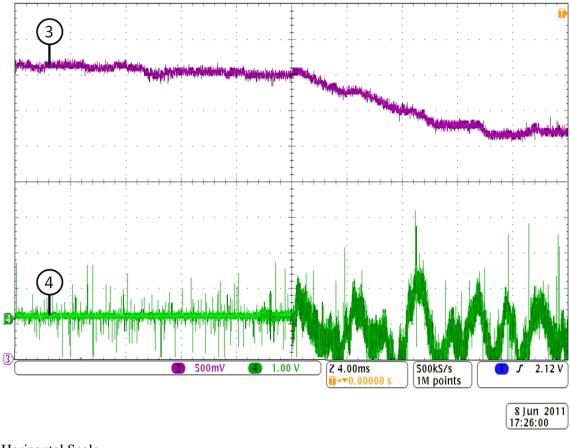

| 5.9  | 9.1  | Minimising IGBT switching noise                             | . 95 |

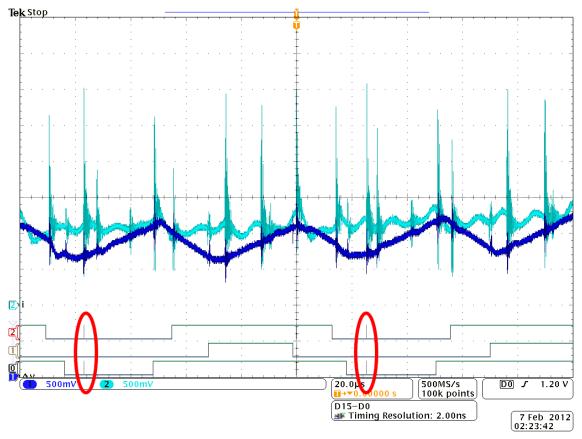

| 5.9  | 9.2  | Issues involving two drives in operation                    | . 97 |

| 5.9  | 9.3  | Concept vs. flight model                                    | . 98 |

| 5.10 | (    | Conclusion                                                  | . 99 |

| Chapte | er 6 - Faults in Permanent Magnet Motors       |  |

|--------|------------------------------------------------|--|

| 6.1    | Introduction                                   |  |

| 6.2    | The development of the fault tolerant PM motor |  |

| 6.3    | Variety of fault tolerant PM motors and drives |  |

| 6.3    | 3.1 Multiphase topologies                      |  |

| 6.3    | 3.2 Multilane topologies                       |  |

| 6.3    | 3.3 Other topologies                           |  |

| 6.3    | 3.4 Literature conclusion                      |  |

| 6.4    | The fault tolerant ELGEAR motor                |  |

| 6.5    | Possible faults on the PM motor                |  |

| 6.5    | 5.1 Winding open circuit fault                 |  |

| 6.5    | 5.2 Phase terminal short circuit fault         |  |

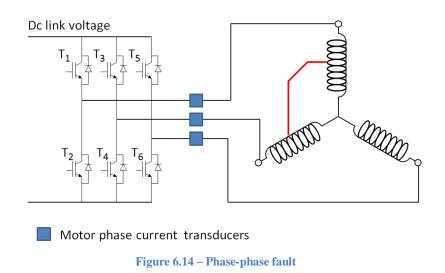

| 6.5    | 5.3 Phase-phase terminal fault                 |  |

| 6.5    | 5.4 Inter-turn, phase-phase fault              |  |

|        | 1111                                           |  |

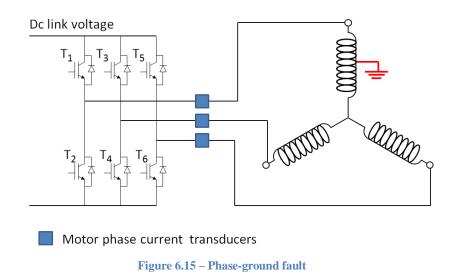

| 6.5.5 | Phase-ground fault | 116 |

|-------|--------------------|-----|

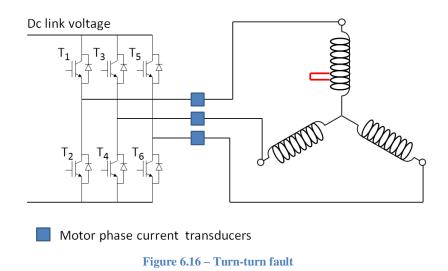

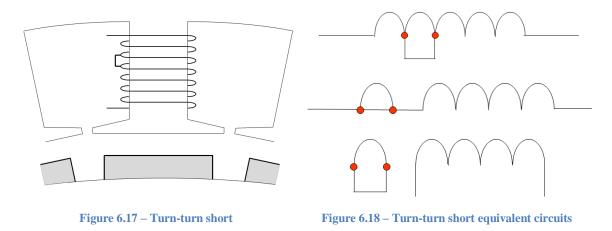

| 6.5.6 | Turn-turn faults   | 116 |

| 6.6 C | onclusion          |     |

| Chapter | 7 - Terminal and Turn-Turn Fault Analysis 120                 |

|---------|---------------------------------------------------------------|

| 7.1     | Introduction                                                  |

| 7.2     | Terminal short circuits                                       |

| 7.2.    | 1 Types of terminal short circuits                            |

| 7.2.    | 2 Remedial action                                             |

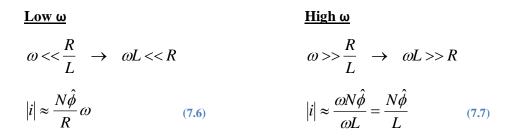

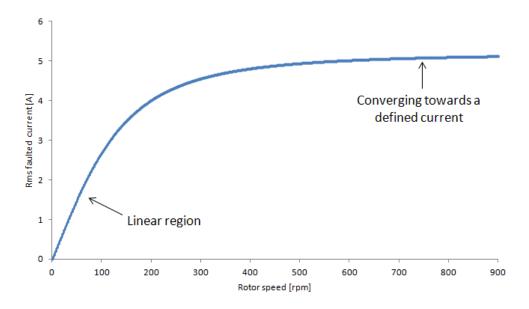

| 7.2.    | 3 Mathematical analysis                                       |

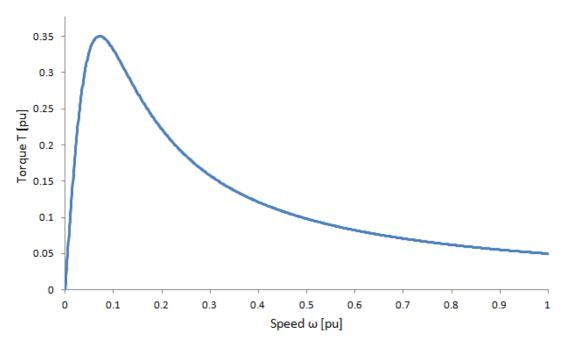

| 7.2.4   | 4 Drag Torque                                                 |

| 7.2.    | 5 Definition of rated current                                 |

| 7.3     | Turn-turn faults                                              |

| 7.3.    | 1 Causes of turn-turn faults                                  |

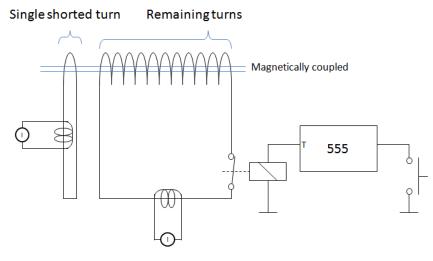

| 7.3.    | 2 The single shorted turn                                     |

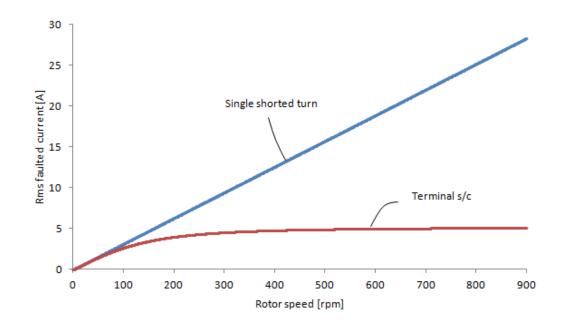

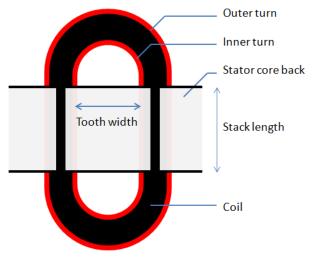

| 7.3.    | 3 Severity of the single shorted turn                         |

| 7.3.4   | 4 Consequences of shorted turn faults                         |

| 7.4     | Resistance of coils                                           |

| 7.5     | Heating                                                       |

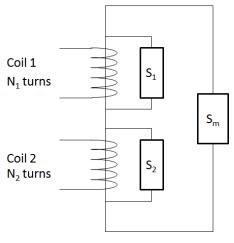

| 7.6     | Relationship between the individual turns and remaining turns |

| 7.6.    | 1 Remedial action of turn-turn faults                         |

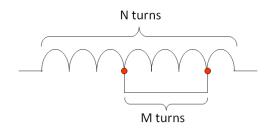

| 7.6.    | 2 The transformer model                                       |

| 7.6.    | 3 Mutual inductance                                           |

| 7.7     | Conclusion138                                                 |

| Chapter | <b>8</b> - Simulation | 139 |

|---------|-----------------------|-----|

| 8.1     | Introduction          | 139 |

| 8.2    | Tur    | rn resistance and inductance properties                      | 140 |

|--------|--------|--------------------------------------------------------------|-----|

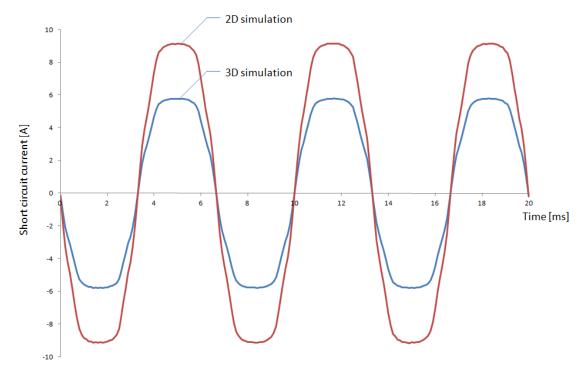

| 8.3    | Ter    | minal short circuit                                          | 141 |

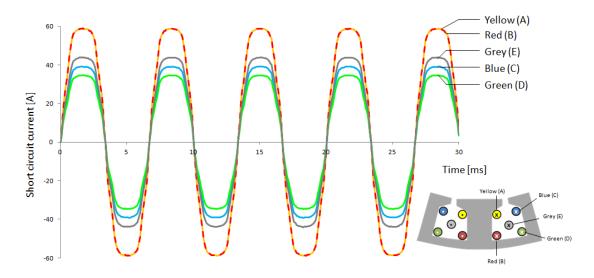

| 8.4    | Sin    | gle shorted turn                                             | 142 |

| 8.4    | 4.1    | Actual resistance per turn                                   | 142 |

| 8.4    | 4.2    | Heating per turn                                             | 143 |

| 8.4    | 4.3    | Average resistance per turn                                  | 143 |

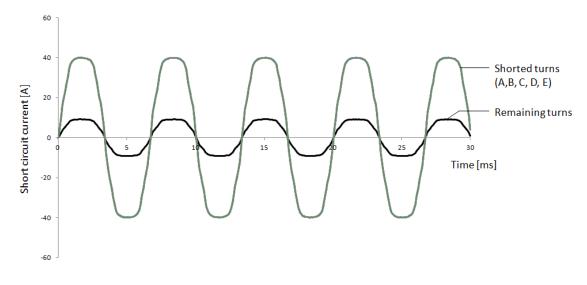

| 8.5    | Rer    | medial action – terminal short circuit                       | 144 |

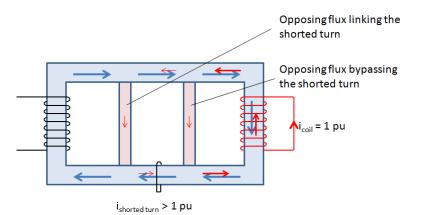

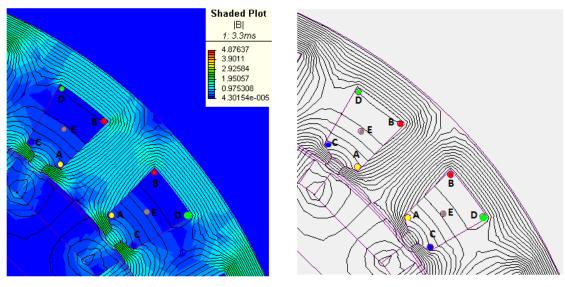

| 8.5    | 5.1    | Flux analysis                                                | 144 |

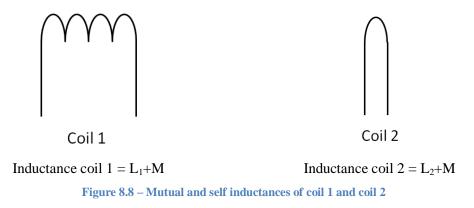

| 8.5    | 5.2    | Self and mutual inductances                                  | 147 |

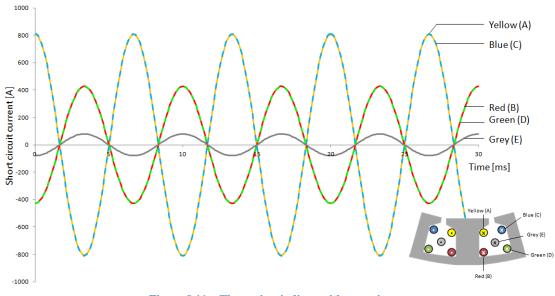

| 8.5    | 5.3    | Calculated fault current                                     | 148 |

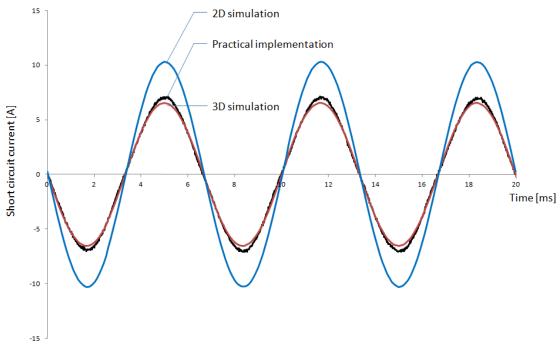

| 8.5    | 5.4    | Simulation and mathematical results                          | 149 |

| 8.5    | 5.5    | MagNet versus Matlab                                         | 151 |

| 8.6    | Ter    | minal short circuit – ignoring resistance                    | 151 |

| 8.6    | 5.1    | The effect of leakage inductance                             | 152 |

| 8.6    | 5.2    | Positive and negative leakage inductance for different turns | 155 |

| 8.7    | Cor    | nclusion                                                     | 156 |

|        |        |                                                              |     |

| Chapte | er 9 - | Practical Implementation                                     | 158 |

| 9.1    | Intr   | roduction                                                    | 158 |

| 9.2    | Set    | up                                                           | 158 |

| 9.2    | 2.1    | The ELGEAR rig                                               | 158 |

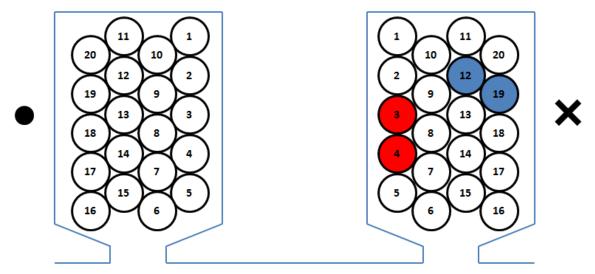

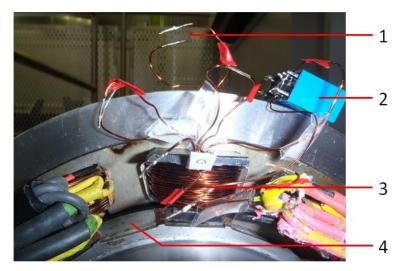

| 9.2    | 2.2    | Shorted turns                                                | 160 |

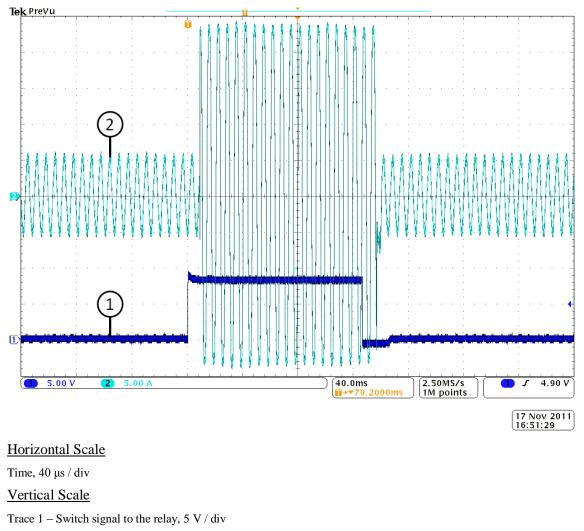

| 9.2    | 2.3    | Measurement                                                  | 160 |

| 9.3    | Ter    | minal short circuit on one coil                              | 162 |

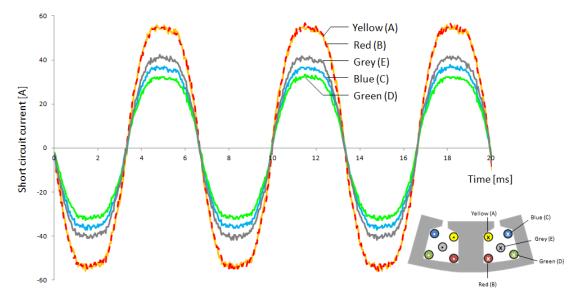

| 9.4    | Sin    | gle shorted turn (remaining portion of coil open-circuit)    | 164 |

| 9.4    | 4.1    | Comparison to the literature                                 | 166 |

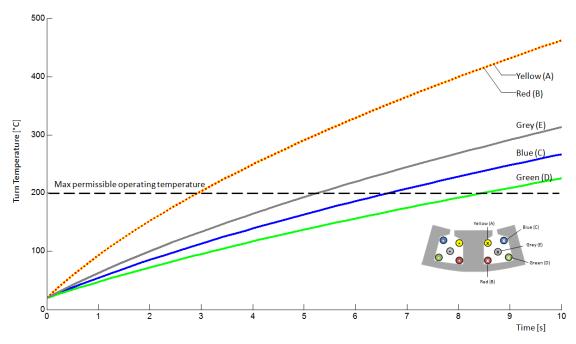

| 9.4    | 4.2    | Heating                                                      | 166 |

|        |        |                                                              |     |

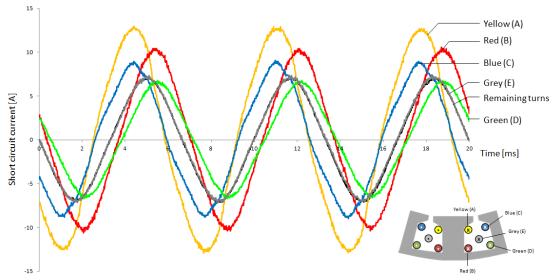

| 9.5     | 9.5 Single shorted turn with remedial action        |  |  |

|---------|-----------------------------------------------------|--|--|

| 9.5     | .1 Simulation vs. practical implementation          |  |  |

| 9.5     | .2 Analysis of the suppressed currents              |  |  |

| 9.6     | Improvements – limiting the current                 |  |  |

| 9.6     | .1 Varying the slot reactance                       |  |  |

| 9.6     | .2 Increasing the coil's diameter                   |  |  |

| 9.6     | .3 Cone shaped diameter of the coil                 |  |  |

| 9.6     | .4 Using two coils of different material            |  |  |

| 9.6     | .5 Twisting the coil                                |  |  |

| 9.7     | Conclusion                                          |  |  |

|         |                                                     |  |  |

| Chapter | r 10 - General Conclusion                           |  |  |

| 10.1    | Capacitor monitoring                                |  |  |

| 10.2    | Turn-turn faults                                    |  |  |

| 10.3    | Review of objectives & contribution to knowledge178 |  |  |

| 10.4 | Future work | . 179 |

|------|-------------|-------|

|      |             |       |

| Appendix   |     |

|------------|-----|

|            | 104 |

| References |     |

# List of figures

| Figure 1.1 – Development of power generation on an aeroplane [6] (chart updated using   |

|-----------------------------------------------------------------------------------------|

| [5])4                                                                                   |

| Figure 1.2 – Electrical Backup Hydraulic Actuator mounted on an Airbus A380 rudder 6    |

| Figure 1.3 – Electrical Hydraulic Actuator mounted on an Airbus A380 aileron            |

| Figure 1.4 – Simplified overview of the various systems on board an aeroplane           |

| Figure 1.5 – Fault tree                                                                 |

| Figure 1.6 – Single-point failure example when the power supply fails 10                |

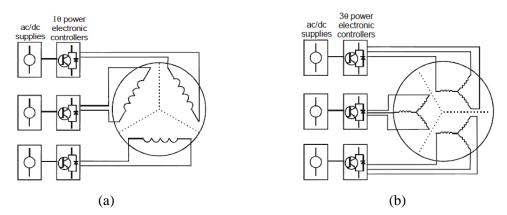

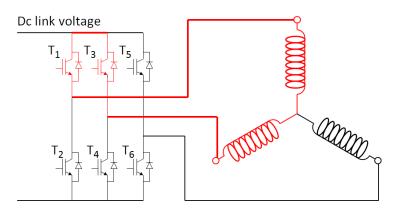

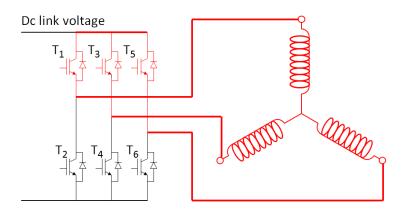

| Figure 1.7 – Fault tolerant motor drive electronics                                     |

| Figure 1.8 – Motor drive                                                                |

| Figure 1.9 – Condition monitoring block diagram14                                       |

| Figure 2.1 – Failure distribution of various electrical components [23]                 |

| Figure 2.2 – Failure distribution of power components in power electronic circuits [24] |

|                                                                                         |

| Figure 2.3 – Haylock's dc-link capacitor configuration                                  |

| Figure 2.4 – Typical failure rate characteristic in MPPF capacitors [29] 21             |

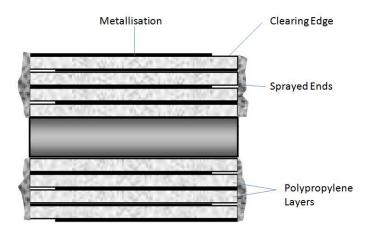

| Figure 2.5 – Capacitor cross section of a typical MPPF capacitor [31]                   |

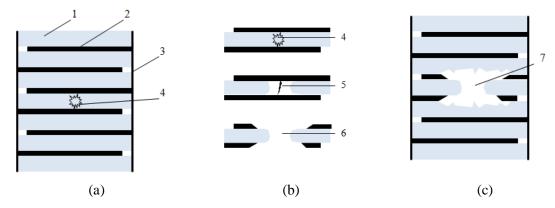

| Figure 2.6 – Segmented construction of electrodes                                       |

| Figure 2.7 – Self healing principle according to [29] and [35]                          |

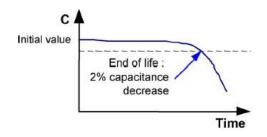

| Figure 2.8 – Typical end of life behaviour of the MPPF capacitor [32]                   |

| Figure 2.9 – Proposed condition monitoring by Aeloiza et al. [38]                       |

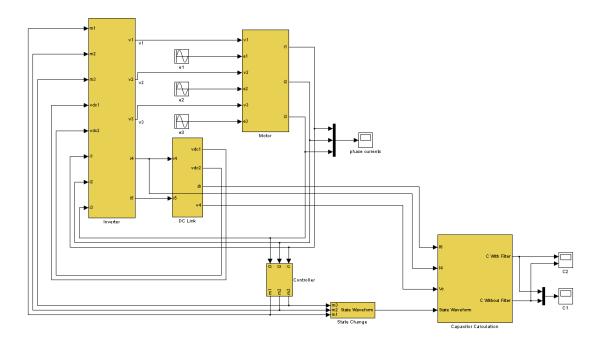

| Figure 3.1 – Diagram layout of the Matlab Simulink model                                |

| Figure 3.2 – Overall Matlab Simulink of the motor drive                                 |

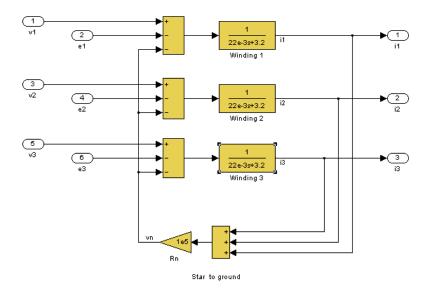

| Figure 3.3 – Motor sub-system                                                           |

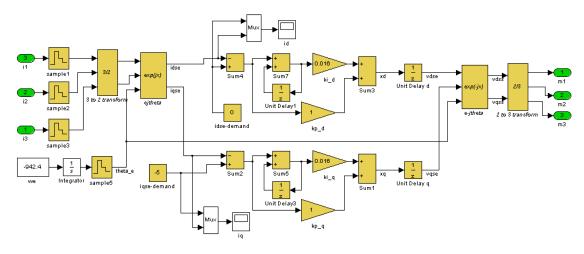

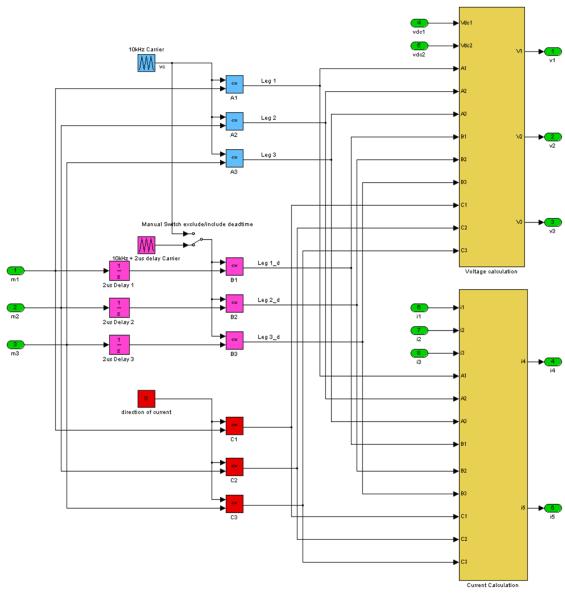

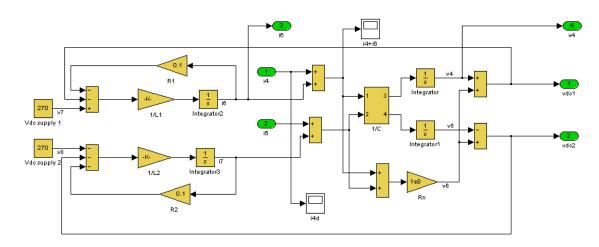

| Figure 3.4 – Controller sub-system                                                      |

| Figure 3.5 – Inverter internal structure                                                |

| Figure 3.6 – Dc-link internal structure                                                 |

| Figure 3.7 – Motor Drive Electronics according to Matlab Simulink                       |

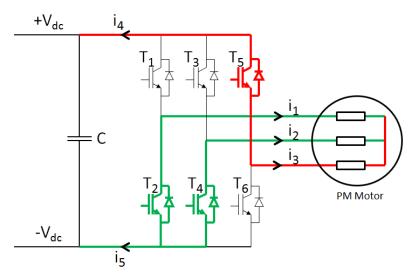

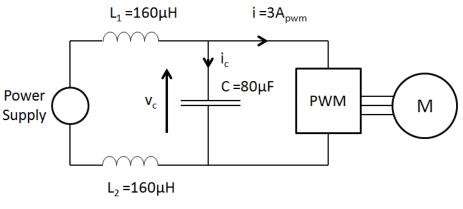

| Figure $3.8 - Example$ of current flow for a given state when T2, T4 and T5 are on 38   |

| Figure 3.9 – Dc-link capacitor equivalent currents 40                                   |

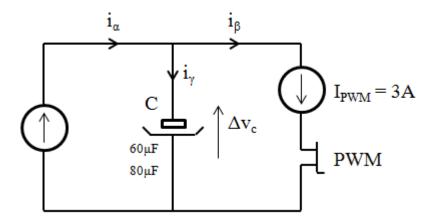

| Figure 3.10 – During zero voltage state sampling, $i_4 = 0$                             |

| Figure $3.11 - Dc$ -link capacitor equivalent currents, where the drive is modelled as one                                         |   |

|------------------------------------------------------------------------------------------------------------------------------------|---|

| phase @ 10 kHz                                                                                                                     | 3 |

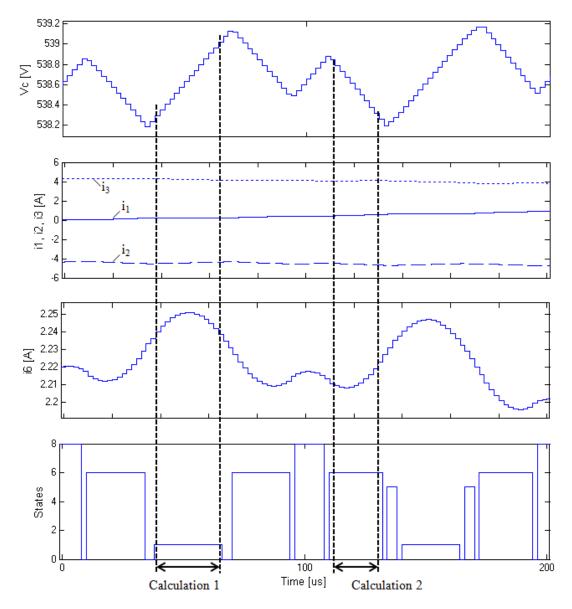

| Figure $3.12 - \text{Snap}$ shot in time of v <sub>c</sub> , i <sub>c</sub> , i <sub>1</sub> -i <sub>4</sub> and transistor states | 4 |

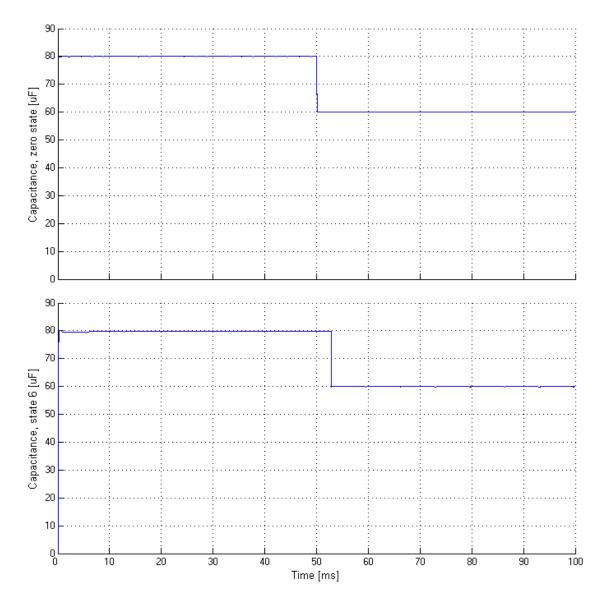

| Figure 3.13 – Result of the monitoring simulation. Top graph, monitoring on the zero                                               |   |

| voltage state. Bottom graph, monitoring on state 6. Capacitor change programmed to                                                 |   |

| switch from 80µF to 60µF at t=50ms                                                                                                 | 6 |

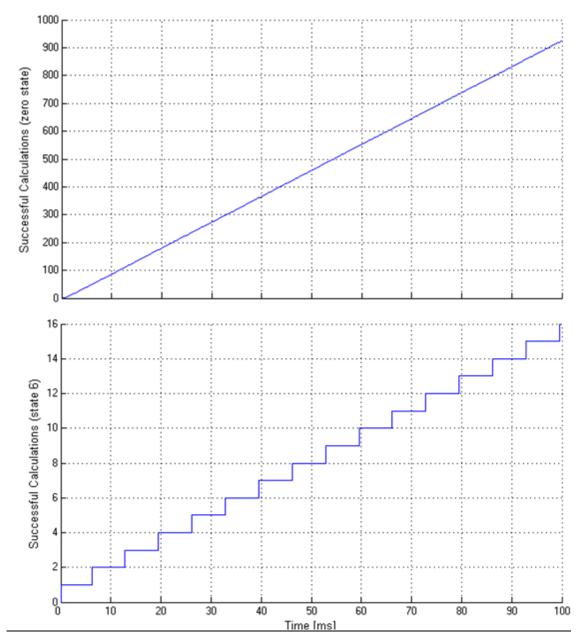

| Figure 3.14 – Number of successful calculations for the zero voltage state (top) and                                               |   |

| state 6 (bottom)                                                                                                                   | 7 |

| Figure 3.15 – Design overview                                                                                                      | 8 |

| Figure 3.16 – Ripple voltage vs. PWM duty ratio                                                                                    | 1 |

| Figure 3.17 – Dc-link voltage                                                                                                      | 2 |

| Figure 3.18 – Reconstruction of the ripple on the dc-link capacitor                                                                | 3 |

| Figure 3.19 – Comparison of different cut off frequencies for the voltage monitor 54                                               | 4 |

| Figure $3.20 - Voltage$ monitoring adaptation, $60 \ \mu F$ capacitor example                                                      | 5 |

| Figure 3.21 – Voltage monitoring circuit diagram                                                                                   | 6 |

| Figure 3.22 – Current monitor circuit diagram                                                                                      | 9 |

| Figure 3.23 – Opto-isolator circuit for one IGBT signal                                                                            | 1 |

| Figure 3.24 – Timing circuit                                                                                                       | 2 |

| Figure 3.25 – Timing circuit diagram, valid samples                                                                                | 3 |

| Figure 3.26 – Timing circuit diagram, invalid samples                                                                              | 4 |

| Figure 4.1 – Low voltage test circuit                                                                                              | 9 |

| Figure 4.2 – Low voltage experimental unit                                                                                         | 9 |

| Figure 4.3 – Low voltage test result, ~50% duty ratio                                                                              | 2 |

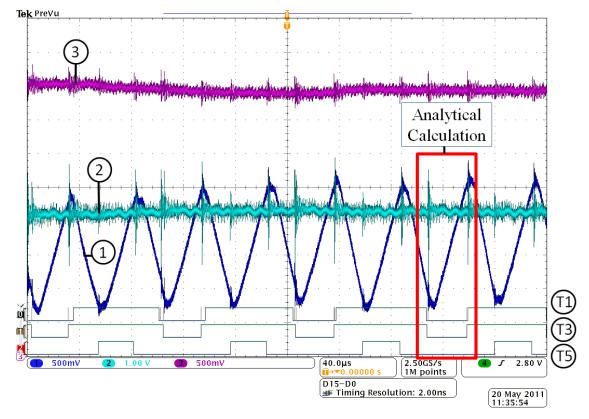

| Figure 4.4 – Capacitor switch out transient                                                                                        | 3 |

| Figure 4.5 – High duty ratio (~90%)                                                                                                | 4 |

| Figure 4.6 – Low duty ratio (~10%)                                                                                                 | 5 |

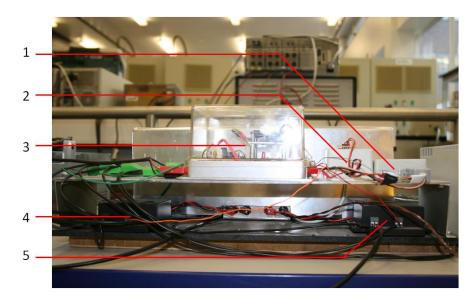

| Figure 5.1 – Rig set up                                                                                                            | 8 |

| Figure 5.2 – Set up of the rig                                                                                                     | 8 |

| Figure 5.3 – High voltage section of the rig                                                                                       | 9 |

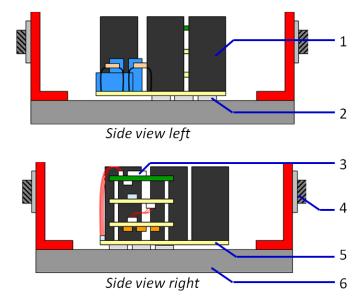

| Figure 5.4 – Motor drive electronics modules                                                                                       | 0 |

| Figure 5.5 – Capacitor monitoring equipment                                                                                        | 1 |

| Figure 5.6 – Test rig details                                                                                                      | 2 |

| Figure 5.7 – Side view drawing of the MDE module                                                                                   | 3 |

| Figure 5.8 – High voltage experimental set up (one drive only)                             |

|--------------------------------------------------------------------------------------------|

| Figure 5.9 – Capacitor connection detail                                                   |

| Figure 5.10 – High voltage experiment                                                      |

| Figure 5.11 – Capacitor switch out (zoomed out), no filtering of data                      |

| Figure 5.12 – Capacitor switch out (zoomed in), no filtering of data                       |

| Figure 5.13 – The implemented filter                                                       |

| Figure 5.14 – Results after filtering                                                      |

| Figure 5.15 – Switching noise on the IGBTs96                                               |

| Figure 5.16 – Two drives operational, the red circle highlights the switching noise        |

| induced by the mirroring inverter                                                          |

| Figure 5.17 – Problematic dc-link layout due to narrow gates in the flooded planes 99      |

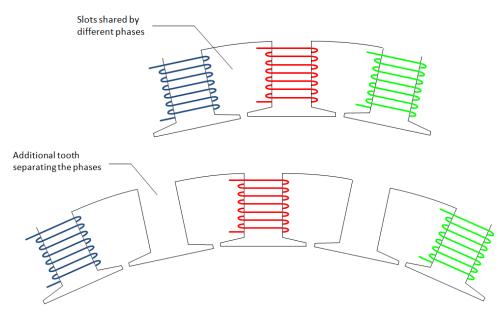

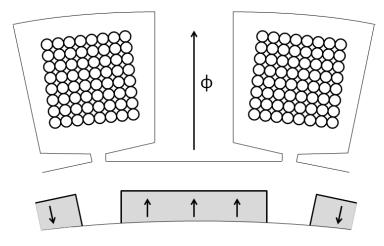

| Figure $6.1 - \text{Top}$ diagram shows the conventional method when phases share the same |

| slot. The bottom diagram shows the additional tooth incorporated in machine design to      |

| physically isolate the phases                                                              |

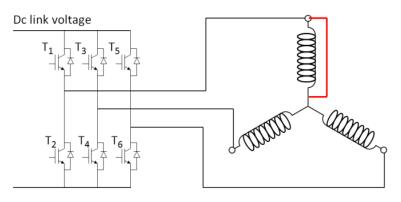

| Figure 6.2 – Star point connected with terminal short                                      |

| Figure 6.3 – Individual H-bridge connection 103                                            |

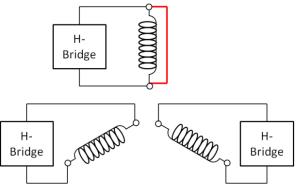

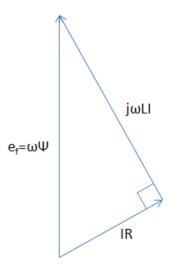

| Figure 6.4 – Phasor diagram of a terminal shorted winding 104                              |

| Figure 6.5 – Different suggested motor configurations for 3-lane systems [9, 51] 105       |

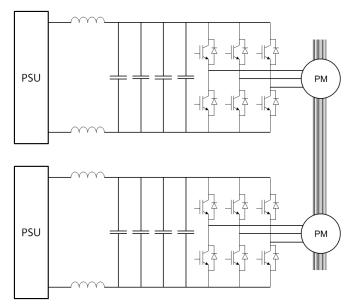

| Figure 6.6 – Dual lane 3 phase motor drive unit 108                                        |

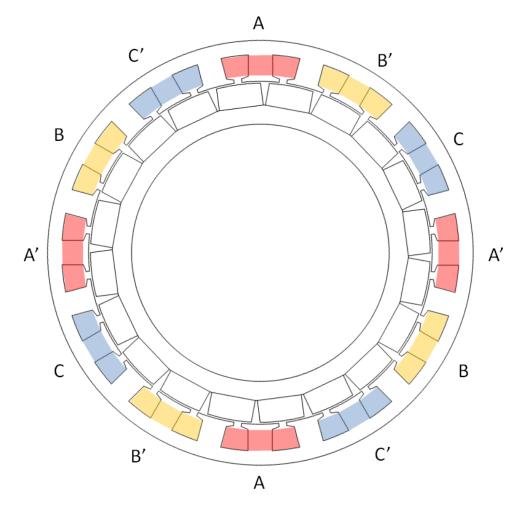

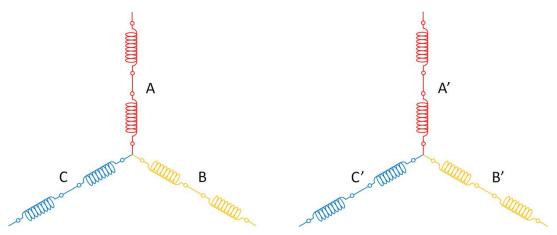

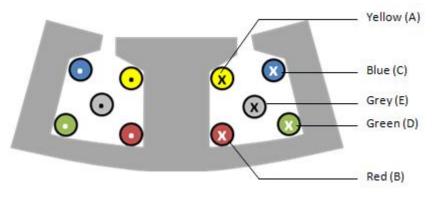

| Figure 6.7 – Phase layout on the stator                                                    |

| Figure 6.8 – Electrical layout of the phases                                               |

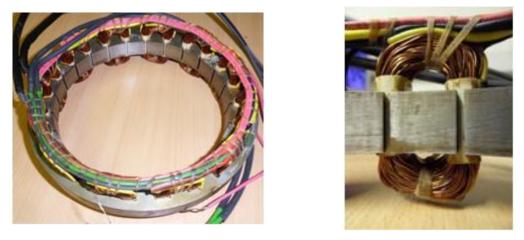

| Figure 6.9 – Left, a picture of the ELGEAR stator. Right, a picture of a single coil 110   |

| Figure 6.10 – Picture of the ELGEAR rotor                                                  |

| Figure 6.11 – Winding open circuit fault                                                   |

| Figure 6.12 – Terminal short circuit fault                                                 |

| Figure 6.13 – Phase-phase short                                                            |

| Figure 6.14 – Phase-phase fault                                                            |

| Figure 6.15 – Phase-ground fault                                                           |

| Figure 6.16 – Turn-turn fault                                                              |

| Figure 6.17 – Turn-turn short                                                              |

| Figure 6.18 – Turn-turn short equivalent circuits                                          |

| Figure 7.1 – Phase-phase short                                                             |

| Figure 7.2 – 3 Phase terminal short                                                        |

| Figure 7.3 – Cross section, one coil                                                 | 122   |

|--------------------------------------------------------------------------------------|-------|

| Figure 7.4 – Electrical equivalent diagram, one coil                                 | 123   |

| Figure 7.5 – Terminal shorted electrical equivalent diagram                          | 123   |

| Figure 7.6 – Faulted current vs speed (terminal short circuit)                       | 124   |

| Figure 7.7 – Drag torque vs Speed                                                    | 126   |

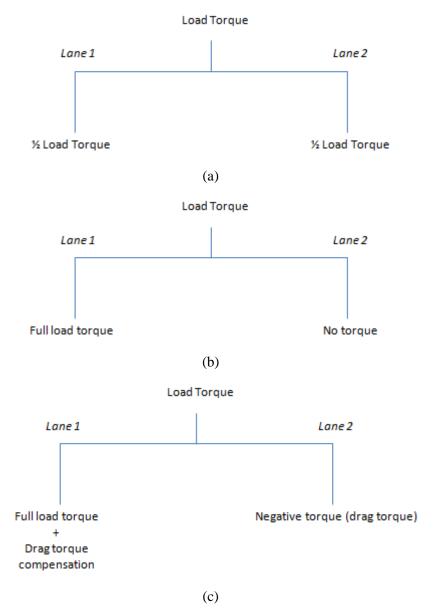

| Figure 7.8 – Various torque sharing scenarios of both a dual lane                    | 127   |

| Figure 7.9 – Shorted coil of M turns within a winding of N turns                     | 128   |

| Figure 7.10 – Two scenarios of adjacent winding shorts                               | 128   |

| Figure 7.11 – Terminal fault, electrical equivalent                                  | 130   |

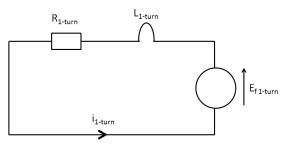

| Figure 7.12 – Turn-turn fault electrical equivalent                                  | 130   |

| Figure 7.13 – Terminal fault vs single shorted turn                                  | 131   |

| Figure 7.14 – Stator coil, side view                                                 | 132   |

| Figure 7.15 – 5 different locations in the stator slot                               | 133   |

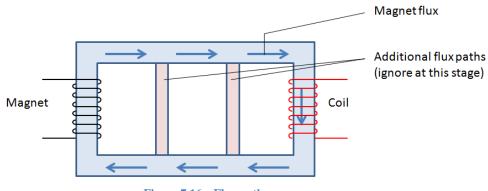

| Figure 7.16 – Flux paths                                                             | 136   |

| Figure 7.17 – Shorted turn                                                           | 137   |

| Figure 7.18 – Flux paths, terminal short                                             | 137   |

| Figure 7.19 – Flux paths, terminal short with a shorted turn                         | 138   |

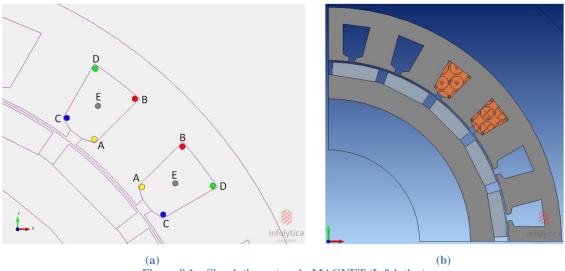

| Figure 8.1 – Simulation set up in MAGNET (Infolytica)                                | 140   |

| Figure 8.2 – Terminal short circuit                                                  | 141   |

| Figure 8.3 – Single shorted turn (actual resistance)                                 | 142   |

| Figure 8.4 – Single shorted turn (average resistance)                                | 144   |

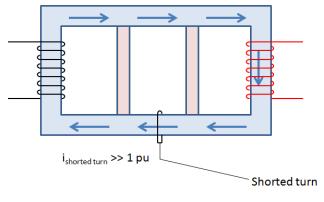

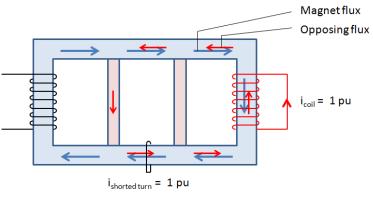

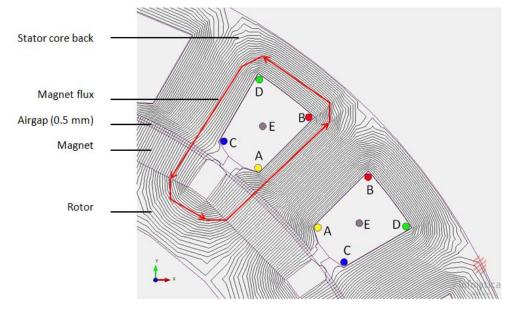

| Figure 8.5 – Magnet flux component only                                              | 145   |

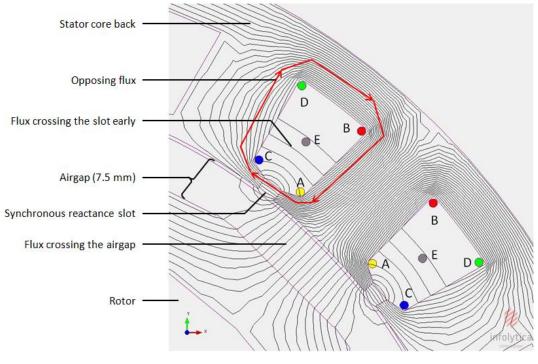

| Figure 8.6 – Opposing flux only                                                      | 145   |

| Figure 8.7 – Resulting flux in the motor (magnet flux and opposing flux superimped   | osed) |

|                                                                                      | 146   |

| Figure 8.8 – Mutual and self inductances of coil 1 and coil 2                        | 147   |

| Figure 8.9 – by MagNet – Fault current in the single shorted turn with remedial act  | tion  |

|                                                                                      | 150   |

| Figure 8.10 – by Matlab – Fault current in the single shorted turn with remedial act | tion  |

|                                                                                      | 150   |

| Figure 8.11 – Theoretic windings with no resistance                                  | 152   |

| Figure 8.12 – Reluctance paths in coils                                              | 152   |

| Figure 9.1 – Set up of the ELGEAR rig for the investigation of single turn faults (top   |     |

|------------------------------------------------------------------------------------------|-----|

| view) 1                                                                                  | 159 |

| Figure 9.2 – Coil rewound with 5 single shorted turns positioned in the slot 1           | 159 |

| Figure 9.3 – Faulted current 1                                                           | 61  |

| Figure 9.4 – Shorted turn current 1                                                      | 62  |

| Figure 9.5 – Terminal shorted coil on ELGEAR rig 1                                       | 163 |

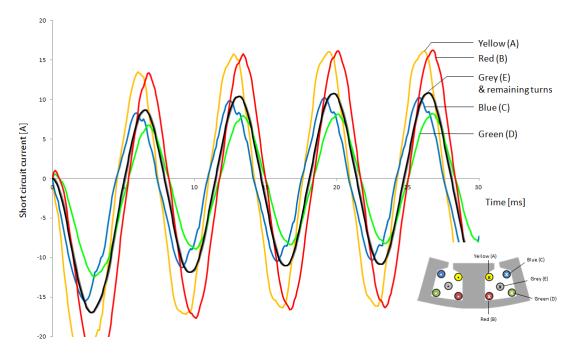

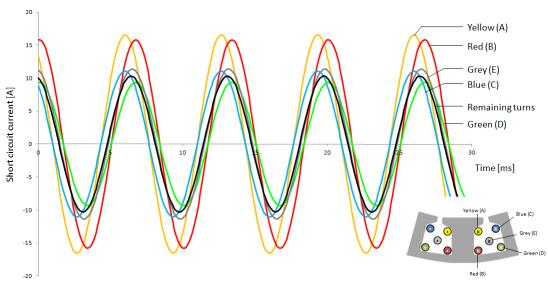

| Figure 9.6 – Shorted turn currents 1                                                     | 165 |

| Figure 9.7 – Heating of a single shorted turn 1                                          | 168 |

| Figure 9.8 – Measured single shorted turn current, with remedial action 1                | 169 |

| Figure 9.9 – Simulation results of the single shorted turn current, with remedial action | 1   |

| (figure copied from Figure 8.10 page 149) 1                                              | 169 |

| Figure 9.10 – Regions where single shorted turns are likely to have the largest current  | īS  |

|                                                                                          | 171 |

| Figure 9.11 – Expected currents exceeding 1 pu in a single shorted turn with remedial    | ł   |

| action1                                                                                  | 171 |

| Figure 9.12 – Increase in the coil's diameter closer to the slot opening (side view) 1   | 172 |

| Figure 9.13 – Increase of the coils diameter close to the slot opening (top view) 1      | 172 |

| Figure 9.14 - Two series connected coil windings with two different type of materials    | \$  |

|                                                                                          | 173 |

| Figure 9.15 – Twisting the coil to allow the turns to occupy different positions within  |     |

| the stator slot 1                                                                        | 174 |

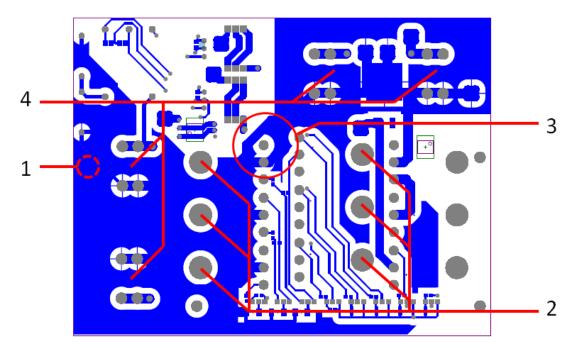

| Figure A.1 – PCB Layout top layer 1                                                      | 180 |

| Figure A.2 – PCB Layout bottom layer 1                                                   | 181 |

| Figure A.3 – Capacitor layout 1                                                          | 181 |

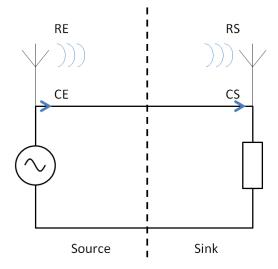

| Figure B.1 – Electromagnetic interference disciplines 1                                  | 182 |

## List of tables

| Table 1.1 – Failure cases                                                                 |

|-------------------------------------------------------------------------------------------|

| Table 3.1– Currents of $i_4$ related to its transistor state                              |

| Table 3.2 – Approximate analytical calculation of the capacitance       45                |

| Table 3.3 – Discharge voltages of the capacitor depending on the PWM duty ratio.          |

| Highlighted columns indicate maximum ripple voltage50                                     |

| Table 3.4 – Specification of the voltage monitoring circuit                               |

| Table 3.5 – List of components, voltage monitor                                           |

| Table 3.6 – Current monitor specification                                                 |

| Table 3.7 – List of components, current monitor                                           |

| Table 3.8 – Components in the current monitor varying most with temperature               |

| Table 5.1 – Statistical analysis with one drive operational       94                      |

| Table 5.2 – Statistical analysis with two drives operational       94                     |

| Table 6.1 – ELGEAR motor parameters                                                       |

| Table 6.2 – Design characteristics of the ELGEAR motor       112                          |

| Table 7.1 – Turn-turn fault possibilities                                                 |

| Table 7.2 – Resistance for each turn                                                      |

| Table 8.1 – Turn resistive and inductive properties    141                                |

| Table 8.2 – Per-unit faulted currents    143                                              |

| Table 8.3 – Temperature increase                                                          |

| Table 8.4 – Self and mutual inductances of every coil or turn (2D simulation) 148         |

| Table 8.5 – Per-unit faulted currents    151                                              |

| Table 8.6 – imaginary component of the s/c current, based on the self and mutual          |

| inductances                                                                               |

| Table 9.1 – Turn's given length/resistance and actual length/resistance                   |

| Table 9.2 – Simulation and practical comparison of the remaining turns' properties 164    |

| Table 9.3 – Single shorted turn per-unit current, simulation vs. practical implementation |

|                                                                                           |

| Table 9.4 – Single shorted turn per-unit current, with remedial action       169          |

## Acknowledgements

The author would like to thank EPRSC and Goodrich Aerospace (now United Technologies) for their financial support.

Foremost, my utmost thanks to Dr. David Atkinson and Prof. Barrie Mecrow who supervised my projects and provided first class technical support and guidance. I benefitted from their vast knowledge and know-how in machines and drives. I would also like to thank my industrial supervisor Dr. Maamar Benarous's who provided me with valuable technical support during the time I worked at the Goodrich Aerospace site.

I would like to thank Dr. John Bennett for his efforts in getting me started in the project, and providing me with technical support on the practical side of things throughout. All in all my study at Newcastle University was a very enjoyable and entertaining thanks to many of my friends and colleagues in the UG-lab (especially Min Zhang, Maher Algreer, Chris Morton, Kamyar Mehran).

I could not have done the engineering doctorate without support from my parents Frederic and Olivia as well as my sister Connie-Rose. My family have provided me with a huge amount of support and perseverance throughout the doctorate scheme. Special credit should be given to my father Frederic who helped me by providing me with technical support and ideas using his vast amount of experience of the industrial world.

# List of symbols and acronyms

### List of symbols

| A        | Availability of a system or cross sectional area |

|----------|--------------------------------------------------|

| С        | Specific heat capacity                           |

| С        | Capacitance                                      |

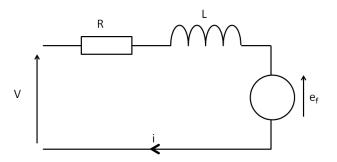

| $e_f$    | Electro-motive force                             |

| f        | Frequency                                        |

| i        | Current                                          |

| $i_C$    | Capacitor current                                |

| J        | Current density                                  |

| j        | Imaginary component                              |

| l        | Length                                           |

| L        | Inductance                                       |

| $L_m$    | Mutual inductance                                |

| Ν        | Number of turns in a coil                        |

| R        | Resistance                                       |

| Т        | Torque or temperature                            |

| t        | Time                                             |

| V        | Voltage                                          |

| $V_C$    | Capacitor voltage                                |

| $V_{dc}$ | Dc bus voltage                                   |

| $V_{pp}$ | Peak to peak voltage                             |

| $X_C$    | Capacitor reactance                              |

| $X_L$    | Inductor reactance                               |

| ϑ        | (rotor) Angle or temperature                     |

| ρ        | Density or resistivity                           |

| σ        | Conductivity                                     |

| $\phi$   | Flux                                             |

| Ψ        | Flux linkage                                     |

| ω        | Angular frequency                                |

|          |                                                  |

#### List of Acronyms

| AC     | Alternative current                            |  |

|--------|------------------------------------------------|--|

| ADC    | Analogue to digital converter                  |  |

| CE     | Conducted emissions                            |  |

| CMRR   | Common mode rejection ratio                    |  |

| CS     | Conducted susceptibility                       |  |

| DAC    | Digital to analogue converter                  |  |

| DC     | Direct current                                 |  |

| dsPIC  | Digital signal peripheral interface controller |  |

| ELGEAR | Electrical landing gear                        |  |

| EMC    | Electromagnetic compatibility                  |  |

| EMF    | Electro-motive force                           |  |

| EMI    | Electromagnetic interference                   |  |

| ESL    | Equivalent series inductance                   |  |

| ESR    | Equivalent series resistance                   |  |

| IGBT   | Insulated gate bipolar transistor              |  |

| LED    | Light emitting diode                           |  |

| MDE    | Motor drive electronics                        |  |

| MMF    | Magneto-motive force                           |  |

| MPPF   | Metallised polypropylene film                  |  |

| MTTF   | Mean time to failure                           |  |

| MTTR   | Mean time to repair                            |  |

| PCB    | Printed circuit board                          |  |

| PE     | Protective earth                               |  |

| PLL    | Phase locked loop                              |  |

| PM     | Permanent magnet                               |  |

| ppm    | Parts per million                              |  |

| pu     | Per-unit                                       |  |

| PWM    | Pulse width modulation                         |  |

| RE     | Radiated emissions                             |  |

| RLC    | Resistor inductor capacitor                    |  |

| rms    | Root mean square                               |  |

| RS     | Radiated susceptibility                        |  |

| SRM    | Switch reluctance motor                        |  |

|        |                                                |  |

### **General Introduction**

### Chapter 1

#### **1.1 Principles of fault tolerance**

In everyday life we are often faced with the situation where a failure in an electronic device causes the device to malfunction or not to function at all. Causes of such failures may be traced to improper handling of the product, component failure, tear and wear etc. In most cases the disruption caused by the failed product is not too severe, and the product is usually replaced sooner or later (or not at all!).

In some cases however, a fault causing disruption in a system is simply not an option. Failure of such systems could lead to hazardous situations, financial losses, serious environmental consequences, human injury or even death. Examples include the military, telecommunication industry, banking sectors, nuclear industry and the aerospace industry [1]. In these vulnerable situations, fault tolerant systems are employed to significantly increase the system's reliability and availability.

The definition of a fault tolerant system is well described by White and Miles in [2]:

"A fault in a component or subsystem does not cause the overall system to malfunction"

A fault tolerant system is essentially a carefully designed system that is resilient to single-point failures. In the event of a fault, the system would still continue to function but this might be at limited or reduced capacity (depending on the specification for post fault operation).

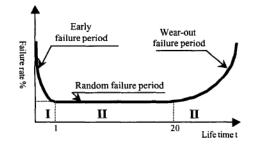

Using statistical means, an important aspect of reliability can be analysed. Fault tolerance is typically evaluated through component history or life testing statistics. It is expressed as mean time to failure (MTTF). This variable indicates the typical time span until a component is likely to fail. The duration of a system being offline is defined by the mean time to repair (MTTR). Using both MTTF and MTTR, the availability A of a system can be calculated, shown in equation (1.1) [2].

$$A = \frac{MTTF}{MTTF + MTTR}$$

(1.1)

White and Miles also describe the four principle points which have to be taken into account when designing a fault tolerant system. These are:

- Redundancy The ability for a system to continue operating after a fault. This

can be achieved by having an entire backup system that starts operating when

the primary system is offline. Another form of redundancy includes partitioning,

where the system is divided in failure groups. This way, vulnerable sections of

the system can be designed to provide additional redundancy.

- 2. Fault isolation Preventing the fault from propagating to healthy parts of the system.

- Fault detection and annunciation Ensuring a fault gets reported to maintenance, thus avoiding dormant failures or systems losing their redundancy.

- Online repair In some applications, systems are continuously operating and can therefore not be switched off for maintenance. Repairs have to take place whilst the system is running, also known as hot swapping.

Another factor to consider is that more redundancies in a system leads to a lower MTTF due to the increase of the number of components, and thus a higher probability for a component to fail. When a system is properly designed – incorporating effective redundancy switching – it considerably reduces the chance of a catastrophic failure. However, a significantly higher maintenance capacity is required as explained by Argile in [3].

#### **1.2 Contribution to knowledge**

This section outlines areas of work that have not been published before, or not covered in detail in the current literature.

• Work done in this thesis has resulted in a journal paper publication:

#### Condition Monitoring of DC-Link Capacitors in Aerospace Drives

This paper appears in: IEEE Transactions on Industry Applications Date of Publication: Nov.-Dec. 2012 Author(s): Wechsler, A. School of Electrical & Electronic Engineering, Newcastle University, Newcastle upon Tyne, UK Mecrow, B.C. ; Atkinson, D.J. ; Bennett, J.W. ; Benarous, M. Volume: 48, Issue: 6 Page(s): 1866 - 1874 Product Type: Journals & Magazines

- Development and application of a novel online condition monitoring technique of dc-link capacitors in aerospace drives, by experimental and simulated verification.

- Examination of fault tolerant PM machine design parameters that influence the severity of turn-turn faults during fault and post fault operation.

- Experimental and simulated verification of the presence of negative leakage inductance in faulted turns of fault tolerant PM machines

#### **1.3 Evolving aircraft technology**

The fault tolerant drive described in this thesis is for the aerospace application. This section aims to provide a general background on the development of electrical systems on aircraft.

#### **1.3.1** The more electric aeroplane

Hydraulically powered systems have been present on aircraft since the dawn of aviation. During the 1940's it was decided that future aircraft flight systems – mainly actuators – should be based on hydraulic technology and not electrical [4]. At the time aircraft simply did not have sufficient electrical power generation capacity to support electrical systems.

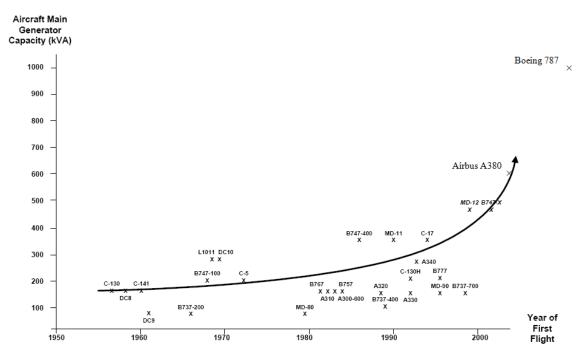

This situation changed in the 1980's (see Figure 1.1) where an increasing demand of electrical technology in combination of advancement in engine power and power electronic systems played a key role to introducing electrical systems on aircraft on a larger scale. Since then, aircraft were equipped with ever more electrical power consuming systems such as in-flight entertainment, multiple radar systems, navigation, flight data processors etc. As a consequence, aircraft must have an appropriate electrical infrastructure including ac power generation, power distribution, rectification and filtering [5-7].

Potential improvements are highlighted in the *All Electric Aircraft* by Cronin [8]. Electrical systems pose many advantages over hydraulic systems:

- Power on demand. Hydraulic systems require constantly pressurised systems, even when on stand-by where nominal power is consumed to maintain pressure. In contrast, electrical systems only consume power when operating.

- Ease of maintenance. Although the actual routine maintenance may not be any different, hydraulic fluids are more difficult to maintain. In contrast, electrical systems can be relatively easily replaced using appropriate interconnections. Furthermore electrical systems have wider possibilities for diagnoses.

- Reduction in weight. This point can be argued, since some electrical concept systems are actually heavier than their hydraulic counterparts. On the other hand, taking continuous progression into account it should be possible to significantly reduce the weight of many electrical components.

Figure 1.1 – Development of power generation on an aeroplane [6] (chart updated using [5])

Nevertheless, the aerospace industry is very cautious and reluctant to introducing new technologies due its limited reliability history. This has especially been the case for flight critical systems where reliability is top priority. In flaps and slats for example, a mean failure rate of under  $10^{-9}$  per hour is required, which corresponds to a failure every 100,000 years of continuous operation. By comparison, industrial electrical machines typically have a failure rate of  $2 \times 10^{-5}$  failures per hour [9].

Today, the aerospace industry is moving towards the concept of the *more electric aircraft*, rather than the *all electric aircraft*. This essentially highlights the direction of

aerospace research towards hybrid technologies. Some mechanical and hydraulic components may be completely replaced (e.g. fly-by-wire in Airbus aircraft), other systems will simply operate in parallel in the form of an active redundancy or as auxiliary units.

Examples of electrical systems can be found in the new Boeing 787 Dreamliner, which has a generating capacity of 1000 kVA (250 kVA per engine) [5] incorporating many electrical systems including electric braking in the undercarriage wheels. Electrical equipment is also replacing pneumatic technology on the future Boeing 747-8 aircraft. Rolls-Royce is currently developing bleedless engines, suggesting that electrical compressors are now a more efficient way obtaining air [10].

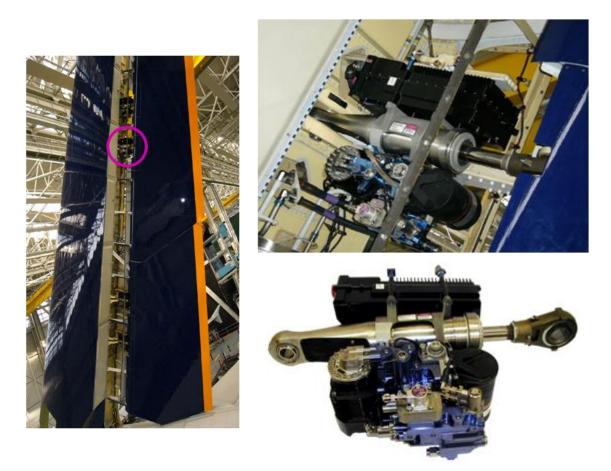

The Airbus A380 (with a generating capacity of 600 kVA, 150 kVA per engine) [5] incorporates a number of electrical systems, examples include:

- Electrostatic hydraulic backup actuators (EHBA) where the technology is still predominantly hydraulic but is backed up by an electrically powered actuator. One of such components can be found in the aircraft's rudder (Figure 1.2).

- Electrostatic hydraulic actuator (EHA) Similar to the above, but operates as an active unit, under normal circumstances. It can be found in the aircraft's ailerons (Figure 1.3).

- Other electrical or hybrid systems can be found on the aircraft's spoilers and elevators.

Figure 1.2 – Electrical Backup Hydraulic Actuator mounted on an Airbus A380 rudder

Figure 1.3 – Electrical Hydraulic Actuator mounted on an Airbus A380 aileron

#### 1.4 Fault tolerant drives in aircraft

#### 1.4.1 Overview

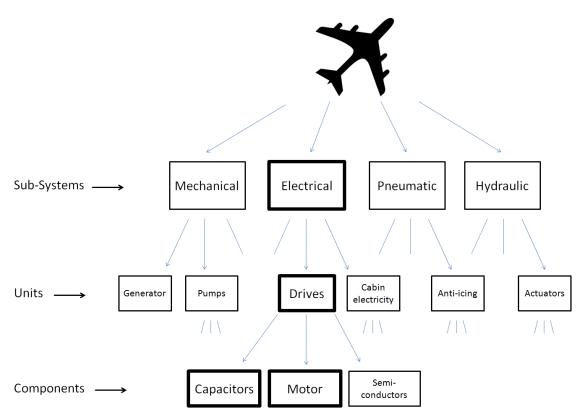

Today's aeroplanes incorporate various technologies that all have to be qualified for fault tolerant operation. There are a variety of systems on board an aeroplane as shown in Figure 1.4. The figure shows a simplified breakdown of the different technologies used which are further broken down in separate units consisting of components.

Figure 1.4 – Simplified overview of the various systems on board an aeroplane

The subsystems' power mostly originates from the engine. Mechanical power is extracted from the engine shaft and is distributed to hydraulic pumps, electrical generators, etc. Pneumatic power is obtained using a bleeding compressor in the engines that in turn is used to start up engines, maintain cabin pressure, power instrumentation and de-icing equipment. Hydraulic power is used to drive most actuators on an aeroplane, although some actuators are already replaced by electrical systems [11, 12].

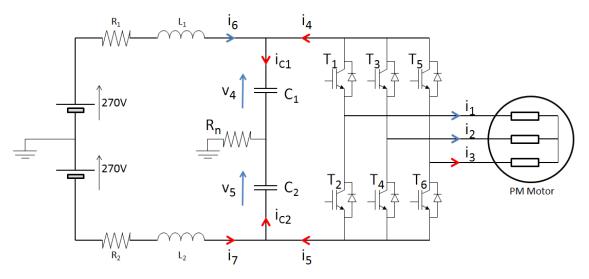

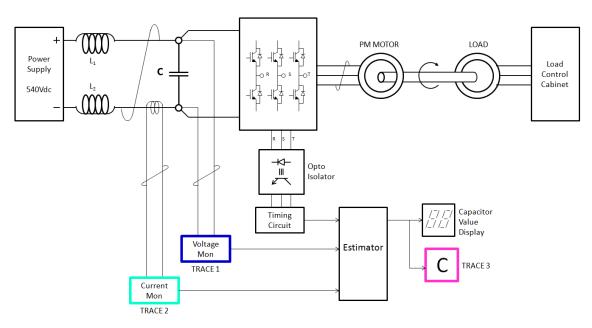

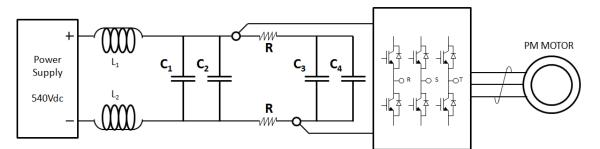

An electric drive can be broken down in to the dc-link capacitor, inverter (including semi-conductors), controller and the motor. This thesis specifically focuses on the fault tolerant issues related to dc-link capacitors and permanent magnet (PM) motor design in aerospace drives.

#### 1.4.2 Redundant power generation and distribution

In an aircraft, electrical power is generated by the engines. For redundancy reasons, there are typically two separate power sources originating from two or more engines. The ac generator output is then rectified to a symmetric dc voltage of +270V and -270V.

Another separately generated, redundant power source produces a dc supply voltage of 28V. This independent low voltage and low noise supply is dedicated to aliment instrumentation such as navigation, communications digital processors etc. Single instruments are often wired-or to both nominal and active redundant low-power supplies by use of diodes; a very simple and reliable method.

All aircraft dc power is transported to various electrical systems on an aircraft through a dedicated set of power lines known as a 'bus'. Bus architecture implies that all users are connected in parallel. This approach clearly becomes a reliability issue since any user on the bus may disturb other users either by short-circuiting the power lines or producing excessive noise. Table 1.1 lists these errors under 'fault propagation'. In order to avoid mutual interference, all electrical systems connected to the power bus have to conform to strict electromagnetic compatibility (EMC) regulations, outlined by the DO-160F standard in [13].

One of the topics covered in the DO-160F standard is associated with the amount of ripple or noise a system is allowed to generate. Over-current protection towards the power bus is also specified. For motor drive electronics, filters have to be introduced to suppress the switching noise of the inverter, and any spikes from being transmitted back onto the power bus. Usually power filters consisting of inductors and capacitors are introduced. Under the DO-160F standard, section 16.7.7.2 for 270 V equipment it states:

"For equipment of the same type that draws a combined total power between 1kW and 10kW, the peak to peak value of the individual equipment's line current ripple shall not exceed 0.140 times of the individual equipment's maximum load dc current draw."

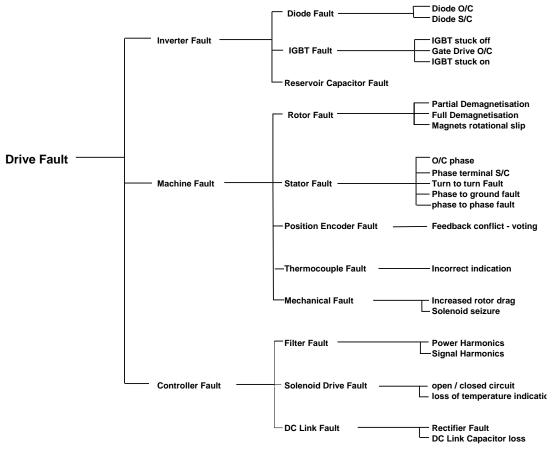

#### 1.4.3 Fault tree

The fault tree in Figure 1.5 is used to highlight all the potential hardware faults that may occur in an electric drive and its corresponding consequences. For example, a diode in the inverter may fail open or short circuit, or a thermocouple fault would provide a wrong feedback value. All of these failures must be taken in to account and as aforementioned, none of these failures are allowed to cause the overall system to malfunction.

8

Figure 1.5 – Fault tree

The failures investigated in this thesis focuses on dc-link (or reservoir) capacitor faults, found under inverter fault, and the turn-turn fault found under machine stator fault.

#### 1.4.4 Type of failures

Failure analysis is a broad topic as there are many different type of scenarios related to the type(s) of failure that could occur. From a failure handling point of view, there are various different type of failure cases as shown in Table 1.1.

| Case | Failure Type         | Means to avoid                               |

|------|----------------------|----------------------------------------------|

| 1    | Single-point Failure | Hot redundancy                               |

|      |                      | Redundancy switching                         |

| 2    | Systematic Failure   | Failure supervision & preventive maintenance |

| 3    | Fault Propagation    | Localised protection                         |

| 4    | Multi-point Failure  | Out of scope                                 |

#### Table 1.1 – Failure cases

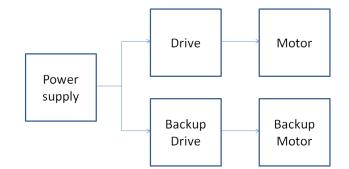

Single-point failures are failures that result in the shutdown of an entire system which must be avoided in fault tolerant systems. An example of a single-point failure is shown in Figure 1.6. The redundancy topology in this particular case is incorrectly designed as the power supply is vulnerable to single-point failures. A failure in the power supply will cause the entire system to shut down. Using appropriate redundancy by ensuring fault tolerance across the entire system (i.e. the addition of a back up supply) reduces the likelihood of such failures.

Figure 1.6 – Single-point failure example when the power supply fails

A systematic failure occurs when a device or component fails without it being repaired. A reason may be that the fault is not detected or by negligence. As a result, components or subsystems may lose their redundancy. For example, if the drive in Figure 1.6 fails, the backup drive will now be vulnerable to single-point failures. The failure of the drive must therefore be detected and repaired swiftly.

Fault propagation could occur if a fault is not isolated properly. For example, if a fault develops in a motor consequently causing excessive heating, the thermal fault may propagate to other parts of the (healthy) system.

Multi-point failures are more complicated. They independently arise simultaneously (e.g. when the drive and the backup motor fail at the same time for different reasons in Figure 1.6). The probability of this failure occurring is much lower than the other three failures, and will not be covered in this thesis.

#### 1.5 General research on reliability and failures

#### **1.5.1** Dormant failures

In this thesis the systematic failure will be investigated for dc-link capacitors. Dc-link capacitors are inherently less reliable than other power electronic components (as will

be covered later on). They are therefore placed in a circuit, considering sufficient redundancy. However, when a capacitor fault is left undetected, it could lead to a systematic failure.

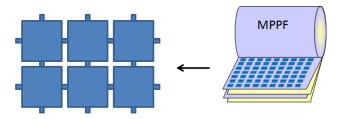

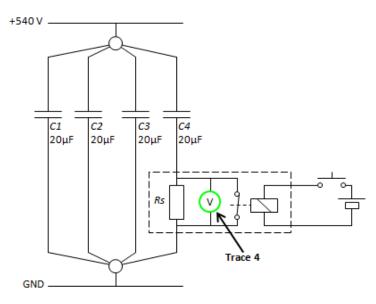

Other than the degradation and limited lifetime of capacitors, there is another important reason as to why it is desirable to monitor dc-link capacitors – to avoid dormant failures (a form of systematic failure). In general it is not strictly mandatory to have multiple parallel connected dc-link capacitors, but there are various advantages in doing so. Firstly capacitors are generally bulky components, and having multiple capacitors as opposed to a single bulky component may have advantages for compact design. Secondly, capacitors are inherently less reliable than other power electronic components (as will be covered later on the thesis). By placing capacitors in parallel, an open circuit capacitor failure would therefore not necessary constitute to a total dc-link failure.

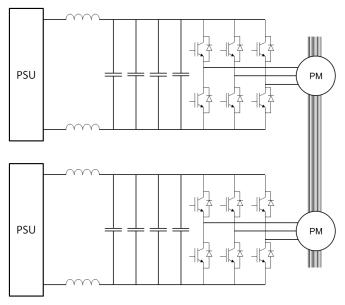

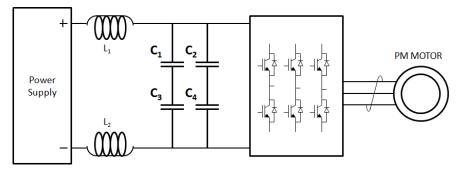

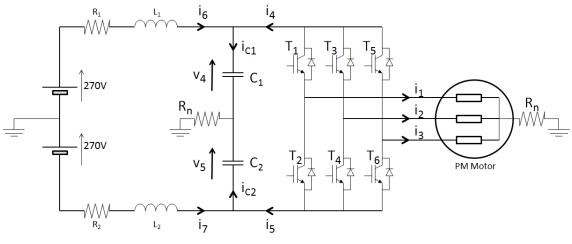

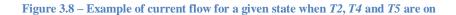

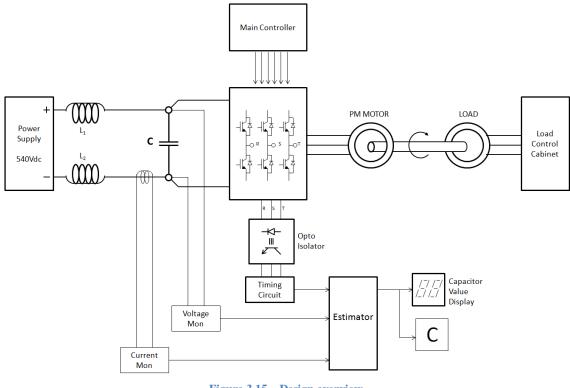

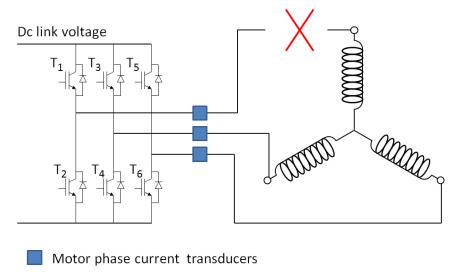

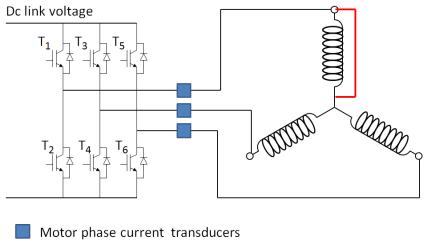

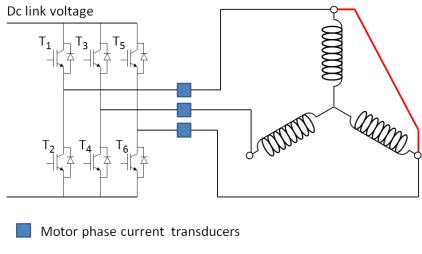

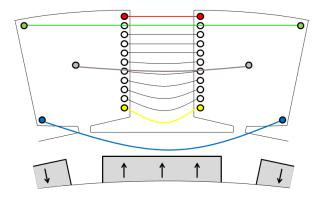

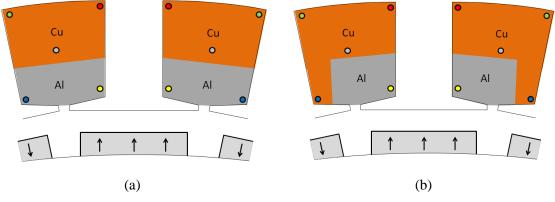

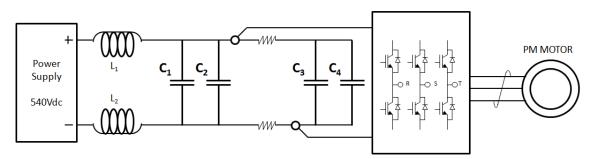

The diagram in Figure 1.7 shows that there are four capacitors in parallel per drive forming a redundancy of  $4 \times 20 \ \mu\text{F}$  equal to an 80  $\mu\text{F}$  capacitance. If a single capacitor fails open circuit, the remaining capacitors will still ensure the drive is operational because the total capacitance is 4/3 overrated by design to guarantee the full performance.

Figure 1.7 – Fault tolerant motor drive electronics

However, when a capacitor open-circuit failure occurs, the total capacitance on the dclink reduces. This will cause an increased stress on the remaining capacitors as the ripple currents and voltages increase as a result. When the faulted capacitor is left undetected, other capacitors in the dc-link could fail which would defeat the purpose of having multiple parallel capacitors. This effect is known as a dormant failure. Consequently, it is important to detect when a failure occurs in each of the capacitors, so the component can be replaced as soon as possible.

#### **1.5.2** The ELGEAR fault tolerant drive

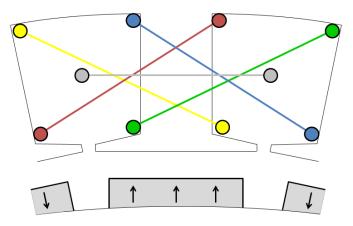

The motor used for this project is designed by Goodrich Actuation Systems and Newcastle University for the Electric Landing GEAR (ELGEAR) project [14]. The project was requested by Airbus to develop a concept electrical landing gear. The architecture of the fault tolerant drive used in the ELGEAR project is found in Figure 1.7. The figure shows a duplex fault tolerant 3 phase motor drive. Each drive is powered by a separate power supply unit, from two independent power sources on an aircraft [13]. Each drive also contains its own dc-link filter (two inductors and four capacitors), inverter (6 IGBTs) and a dual 3 phase fault tolerant PM motor.

Both drives are mirrored in operation to maintain redundancy across the entire drive system. The drives are continuously in operation and share the load torque under nominal conditions (active/active redundancy). Each drive is designed to maintain the fully rated torque in case its counterpart drive is out of operation. The only common fragment in the system is the mechanical actuator axle. The mechanical analysis of the axle is beyond the scope of this thesis; it is assumed that the axle is designed to meet the aerospace reliability requirements as it may constitute to a single-point failure.

#### 1.6 Terminology and nomenclature

#### **1.6.1** Motor drive electronics (MDE)

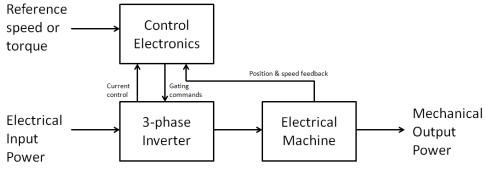

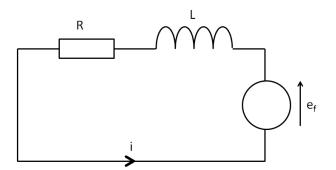

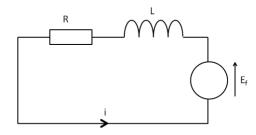

The motor drive electronics referred to in this thesis is depicted in Figure 1.8. This thesis also refers to a fault tolerant drive which is based on the same principle but is slightly modified to resist or accommodate various faults.

#### 3-Phase inverter

Three high power silicon bridges (IGBT technology) will commutate the three phases of an electrical machine. The standard aerospace bus voltage is  $\pm 270$  V dc which is used by the bridges to produce the required phase voltage of 380V rms [13].

#### Control electronics

The control electronics subassembly contains all necessary functions to operate the inverter bridges in a desired manner. As the electronics work on an independent low voltage supply, the commanding interfaces to the inverter bridges are optically isolated. External inputs to control electronics are the desired motor speed and torque values which are compared with the motor sensors feedback.

#### Electrical machine

Finally, the output of the inverter bridge is connected to a 3-phase permanent magnet synchronous machine. The machine is equipped with a dedicated set of measurement sensors to provide information on motor torque and speed to the control electronics.

#### **1.6.2** Condition monitoring nomenclature

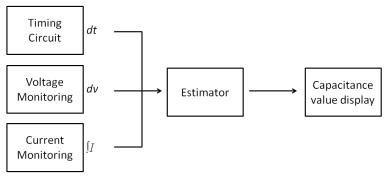

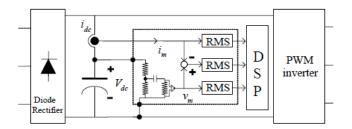

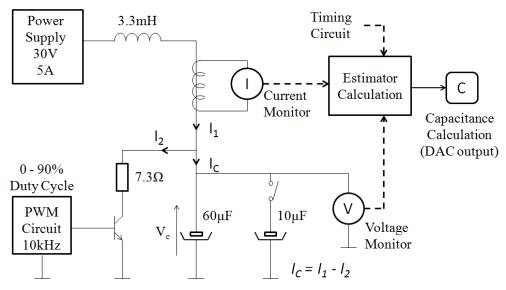

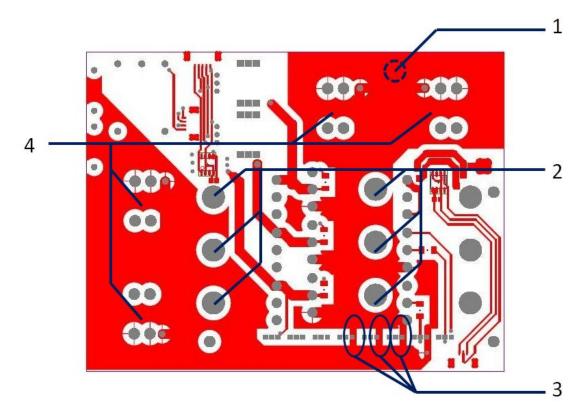

In this thesis, a there are some specific terms which refer to the implemented dc-link capacitor monitoring system. The calculations carried out to determine the capacitance value is referred as the "estimator". The estimator is of dsPIC technology (digital signal peripheral interface controller) and processes data originating from three modules, namely: the "timing circuit", "voltage monitor" and "current monitor" (see Figure 1.9). Each module specialises in obtaining and transferring the appropriate signals to the estimator whilst maintaining high voltage isolation.

Figure 1.9 – Condition monitoring block diagram

#### 1.6.3 Fault tolerant permanent magnet (PM) motor

The fault tolerant PM machine refers to a permanent magnet motor that is configured to resist or accommodate various faults. The motor design options ranges from a single overrated motor to multiple active and/or passive motors for redundancy purposes.

The motor used in this thesis is a 3-phase, fault tolerant, dual lane, interior rotor, permanent magnet motor. The term dual lane refers to a topology where two separate power supplies, drives and motors are used to drive the same shaft, or output torque as Figure 1.7 shows on page 11.

#### 1.6.4 Metallised polypropylene film (MPPF) capacitors

This refers to the type of capacitor predominantly used as reservoir capacitors on aerospace drives. Although much larger in size, the capacitor is preferred to electrolytic technology due to its more fault tolerant nature.

#### **1.6.5** *dsPIC* (*digital signal peripheral interface controller*)

This refers to the type of digital processor used in the control electronics. The microcontroller is a digital signal peripheral interface controller manufactured by the company Microchip. The type of controller is a specialized design for motor control applications.

#### **1.7 Research objectives**

The targets for the engineering doctorate are listed below:

- To analyse the mode of failure of dc-link capacitors in fault tolerant drives for the aerospace application.

- To develop a technique to monitor the dc-link capacitors and inform the user if an open-circuit dc-link capacitor failure were to take place.

- To investigate the impact and consequences of a turn-turn failure upon the fault tolerant ELGEAR motor.

- To provide recommendations for future fault tolerant motor designs to improve the resilience to turn-turn failures, both during fault and post fault operation.

#### **1.8 Thesis overview**

This thesis consists of two projects related to fault tolerant systems in the aerospace application. The first part of the thesis describes condition monitoring of dc-link capacitors in aerospace drives (chapters 2-5). The second part of the thesis describes an analytical study on shorted turn failures in fault tolerant permanent magnet motors (chapters 6-9). Finally, a general conclusion can be found in chapter 10, concluding the work and addressing the targets and the scope outlined in the introduction. A brief description of each chapter is provided below:

Chapter 1 contains a general introduction covering some of the more common terminology used in this thesis. The chapter provides an introduction to fault tolerant electrical systems for the aerospace application and focuses on typical fault tolerant architectures currently discussed in the literature.

Chapter 2 is a literature review covering the failure mode of MPPF capacitors and existing condition monitoring techniques in drives.

Chapter 3 introduces the proposed, novel, condition monitoring technique for dc-link capacitors. Using simulation software (Matlab Simulink), the design parameters are defined and applied for the ELGEAR project. Details of how the estimation technique will monitor the condition of dc-link capacitors, as well as its design can be found in this chapter.

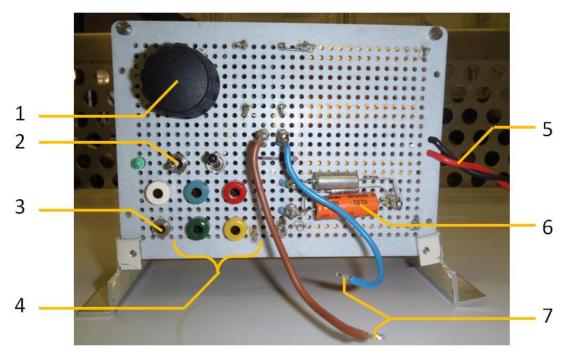

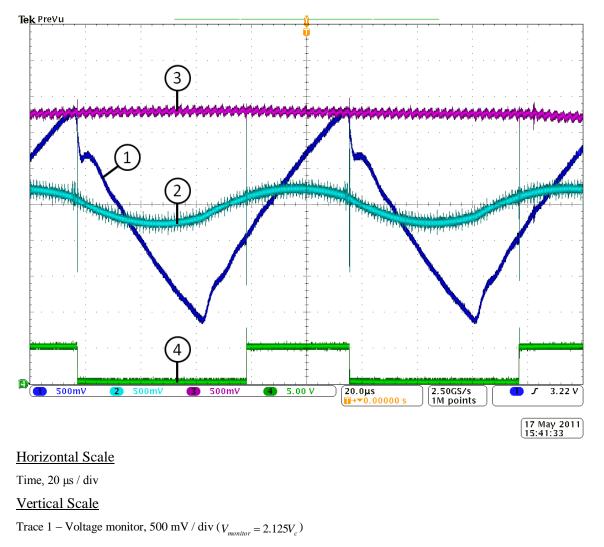

Chapter 4 presents a low voltage experimentation of the proposed condition monitoring technique. This experimentation is an intermediate step before high voltage implementation. This step allows the proposed technique to be examined experimentally in a reduced noise environment where the individual components of the acquisition chain can be tested and calibrated.

Chapter 5 presents the high voltage experimentation of the condition monitoring system on a representative aerospace test rig. The limits of the proposed system are discussed in

15

terms of the accuracy of the data, as well as the response time of a potential capacitor fault.

Chapter 6 describes the physics and the severity of turn-turn faults in fault tolerant PM motors. The chapter consists of an introduction to fault tolerant PM motors, covering the development, variety of topologies in the literature as well as the various faults the motor can accommodate. The chapter continues by describing the type of fault tolerant PM motor used in this project (the ELGEAR motor).

Chapter 7 focuses on the impact and severity of turn-turn faults on the ELGEAR motor. The terminal fault is also covered since it is similar to the turn-turn fault. A detailed theoretical analysis of the faults is provided, where the origin and the remedial actions are discussed.

Chapter 8 analyses the terminal and single shorted turn fault using 2D finite element analysis simulation (MagNet by Infolytica). The parameters that influence the fault, such as resistance and inductance are analysed in detail, and results of the faulted current for various number of turns in the slot are plotted and discussed.

Chapter 9 follows up by introducing the faults on a high voltage test rig (ELGEAR). A comparison is drawn between the practical and simulation results, and the severity of the faults are analysed. The chapter concludes by recommending improvements to the motor for future fault tolerant design.

Chapter 10 is the general conclusion of the thesis, where both the condition monitoring and turn-turn faults are covered. The conclusion also refers to targets and objectives set in the introduction of the thesis.

# Condition Monitoring Literature Chapter 2

# **2.1 Introduction**

This chapter commences with an assessment related to the general reliability of dc-link capacitors in drives. This is followed by a detailed study of the MPPF capacitor, where its failure modes are studied.

The chapter then focuses on condition monitoring techniques of capacitors. A literature review covers a wide range of existing monitoring techniques and proposals. It analyses both the reliability and availability of online and offline monitoring systems and how these could be applied to the aerospace application.

The chapter continues with a proposed, novel, online condition monitoring system of dc-link capacitors in aerospace drives. MPPF capacitors are the preferred technology used for the dc-link in aerospace drives. MPPF capacitors are more resilient to aerospace environments where changes to pressure, humidity and temperature play an important role upon the capacitor's health. It should be stressed that the condition monitoring system would work for other capacitor technologies as well and is thus not limited to MPPF technology.

# 2.2 General reliability assessment of capacitors

In order to monitor the condition of capacitors, it is important to understand why and how they fail. There are many factors that influence the failure of capacitors including:

- How the capacitor is handled and operated

- The quality of manufacturing and installation

- The environmental factors in which the capacitor operates

# 2.2.1 Electrolytic capacitors

In most power converter applications, the electrolytic capacitor is the popular choice for dc-link filtering. Electrolytic technology allows a high capacitance per volume and relatively low production costs [15-17]. Despite these advantages, electrolytic capacitors do have a vast number of disadvantages:

- Sensitivity to temperature variations as the electrolyte shows a significant dependence on temperature. According to Amaral et al. in [18], the capacitance typically varies from -40% to +5% for a temperature from -40°C to 105°C respectively. This significant change is due to the electrolyte solution having properties of conductivity and viscosity which varies quite significantly over temperature. Furthermore, the electrolyte solution is prone to a faster evaporation at higher temperatures, effectively reducing its operating life time. Induced self-heating can be observed when a high ripple current heats up the capacitor due to equivalent series resistance (ESR) losses [19, 20].

- Reduced operational bandwidth. Since it takes a finite period of time for the dipoles in the oxide dielectric of the capacitor to become orientated, the reduced capacitance is reduced at higher frequencies. This phenomenon is known as polarisation [20].

- Short shelf life. The electrolytic capacitor suffers from increased levels of DC leakage current when stored for more than 5 to 10 years. Additionally during the capacitor's lifetime reforming has to take place if not being exposed to a voltage for a certain period of time. Reforming is a process when the capacitor is slowly recharged at a low voltage to allow proper polarisation of the electrolyte. The length of time when reforming should take place depends on the capacitor and should be provided in the manufacturer's datasheet [15, 21, 22].

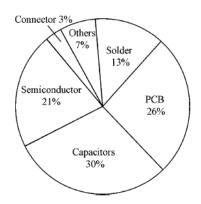

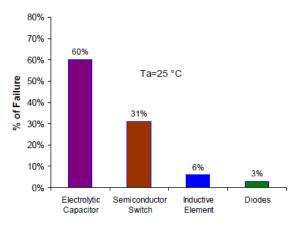

The above disadvantages add to the overall low reliability of the electrolytic capacitor. Figure 2.1 is a survey of the causes of failure in an electrical system. The survey is based on over 200 products, from 80 companies [23]. Figure 2.2 shows a separate statistical analysis by [24], based on the military handbook [25]. Clearly, (electrolytic) capacitors are responsible for most breakdowns in power electronic circuits.

Figure 2.1 – Failure distribution of various electrical components [23]

Figure 2.2 – Failure distribution of power components in power electronic circuits [24]

The most unreliable part of the capacitor is the electrolyte itself. Since it is a liquid based technology it is prone to faster evaporation and hence, faster deterioration in hostile environments – such as the aerospace environment, where variations in air pressure, temperature and humidity are extreme. As a result, the electrolytic capacitor is unsuitable for aerospace applications.

#### 2.2.2 Metallised polypropylene film (MPPF) capacitors

MPPF capacitors have become an acceptable substitute to electrolytic capacitors for the aerospace and fault-tolerant application. This is mainly due to their low ESR, good filtering bandwidth as well as its unique self healing property. Moreover, MPPF capacitors are metal based and are therefore more resilient to environmental changes. Compared to electrolytic technology, MPPF capacitors offer the following advantages:

- High peak and rms current capabilities

- Not polarised

- Solid metal based technology

- More robust (able to withstand up to twice the rated voltage for short periods of time)

- Able to withstand a wide temperature range

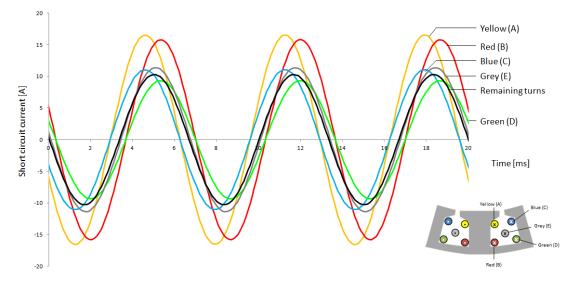

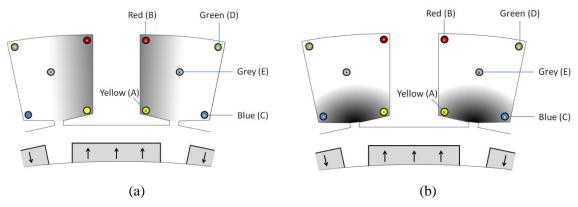

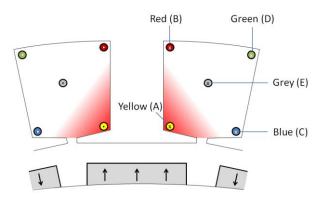

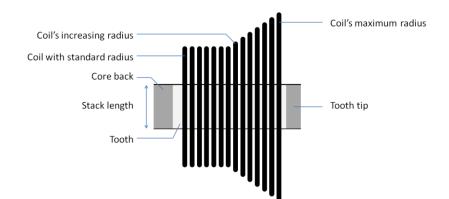

- High reliability (long lifetime, and long shelf life)