# Investigation of High Bandwidth Biodevices for Transcutaneous Wireless Telemetry

By

Gehad. A. Elamare

Thesis submitted for the degree of Doctor of Philosophy in Engineering

School of Electrical, Electronic and Computer Engineering

University of Newcastle upon Tyne

United Kingdom

## Abstract of the Dissertation

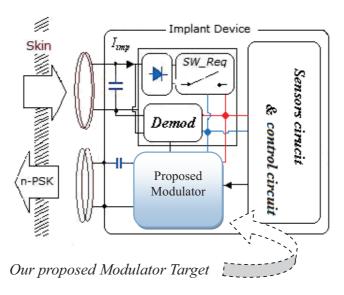

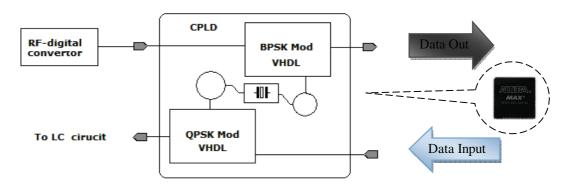

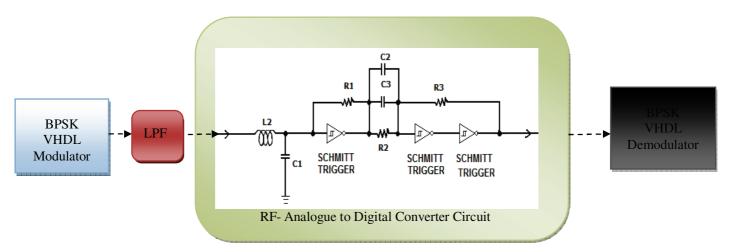

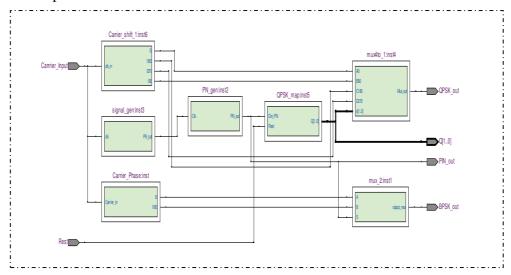

**IODEVICE** implants for telemetry are increasingly applied today in various areas applications. There are many examples such as; telemedicine, biotelemetry, health care, treatments for chronic diseases, epilepsy and blindness, all of which are using a wireless infrastructure environment. They use microelectronics technology for diagnostics or monitoring signals such as Electroencephalography or Electromyography. Conceptually the biodevices are defined as one of these technologies combined with transcutaneous wireless implant telemetry (TWIT). A wireless inductive coupling link is a common way for transferring the RF power and data, to communicate between a reader and a battery-less implant. Demand for higher data rate for the acquisition data returned from the body is increasing, and requires an efficient modulator to achieve high transfer rate and low power consumption. In such applications, Quadrature Phase Shift Keying (QPSK) modulation has advantages over other schemes, and double the symbol rate with respect to Binary Phase Shift Keying (BPSK) over the same spectrum band. In contrast to analogue modulators for generating QPSK signals, where the circuit complexity and power dissipation are unsuitable for medical purposes, a digital approach has advantages. Eventually a simple design can be achieved by mixing the hardware and software to minimize size and power consumption for implantable telemetry applications. This work proposes a new approach to digital modulator techniques, applied to transcutaneous implantable telemetry applications; inherently increasing the data rate and simplifying the hardware design. A novel design for a QPSK VHDL modulator to convey a high data rate is demonstrated. Essentially, CPLD/FPGA technology is used to generate hardware from VHDL code, and implement the device which performs the modulation. This improves the data transmission rate between the reader and biodevice. This type of modulator provides digital synthesis and the flexibility to reconfigure and upgrade with the two most often languages used being VHDL and Verilog (IEEE Standard) being used as hardware structure description languages. The second objective of this thesis is to improve the wireless coupling power (WCP). An efficient power amplifier was developed and a new algorithm developed for auto-power control design at the reader unit, which monitors the implant device and keeps the device working within the safety regulation power limits (SAR).

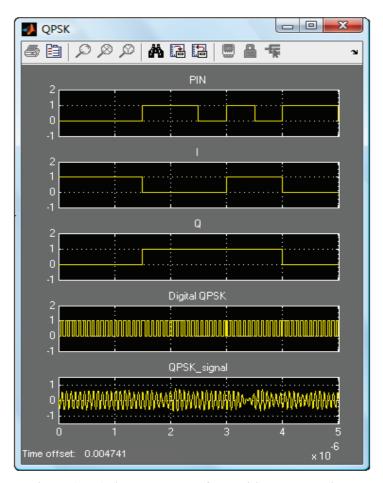

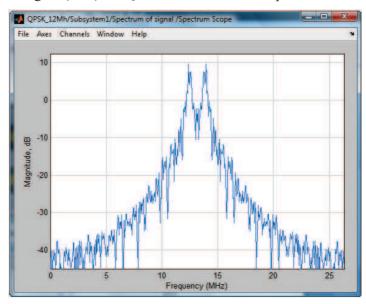

The proposed system design has also been modeled and simulated with MATLAB/Simulink to validate the modulator and examine the performance of the proposed modulator in relation to its specifications.

# Acknowledgement

First and foremost, I would like to express my appreciation to my supervisor, Dr. Graeme

Chester, for help and guidance during my studies. He has always been willing to help, explain and discuss any matters with me over the past three years. I would also thank my second supervisor, *Mr. Jeffrey Neasham*, for his helpful explanations, and guidance in the experimental setup, and practical discussion. I am intensely indebted to many people who made my time in the EECE School, at the electronics Lab use the design Tools and taught me how to use the Measurement equipments. Namely, Mr. Brian

Smith, Mr Stephen Robson, Mr. Darren Mackie, Mr. Jack Noble, Mr. Jeffrey Warren, and Mr. Graham Ewart, the Staff of ITC for their support during my study. Ultimately, the staff of Mechanical workshop for their support and helpful during my PhD.

Second, I acknowledge with thanks the support provided by the scholarship from the Higher Education Ministry in Libya to study and complete my degree .I must thank friends in H.E.M in Libya, the UK regional section, and also all the staff in Libyan Cultural Affairs in the Libyan Bureau in UK, I am specially indebted to thanks of all my colleagues in the general post telecommunication company, and the higher professional electronics institute. I would like to thanks Newcastle University for its support and good facilities to study. Finally, I would like to dedicate this work to my wife, my parent and family for the extraordinary sacrifices and their constant encouragement through of my study and emotional support whenever needed during my time at Newcastle University. Finally, I thank my friends for the support they have given me in so many ways.

PhdThesis 2010

# TABLE OF CONTENS

| Abstract Acknowledgments Table of Contents                                                                                                                                                                                                                            | I<br>II<br>III                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| Chapter I                                                                                                                                                                                                                                                             |                                              |

| 1. Introduction                                                                                                                                                                                                                                                       | 1                                            |

| 1.1 Biodevices Technology                                                                                                                                                                                                                                             | 2                                            |

| 1.2 Implant Technology for Medical Applications 1.2.1 Implant Cochlear Technology. 1.2.2 Intraocular (Retinal) Implant. 1.2.3 Brain Implant Device. 1.2.4 Pacemaker Device. 1.2.5 Wireless Capsule Endoscopy                                                          | 4<br>5<br>6<br>7<br>8<br>9                   |

| 1.3 Media Absorption, Side Effect and Technology Limitations                                                                                                                                                                                                          | 10                                           |

| 1.3.1 Skin Tissue Attenuation 1.3.2 Electromagnetic interference 1.3.3 ISM Band Frequency for Medical Applications 1.4 Acquisition Neural signals. 1.5 Medical Telemetry Chips and applications 1.6 Chapter Summery 1.7 Motivation of Thesis 1.8 Thesis Organization. | 11<br>13<br>14<br>15<br>17<br>18<br>21<br>21 |

| Chapter II                                                                                                                                                                                                                                                            |                                              |

| 2. Background and Literature Review                                                                                                                                                                                                                                   | 25                                           |

| 2.1 Implantable devices modulation schemes                                                                                                                                                                                                                            | 25                                           |

| 2.1 Analogue Modulation Background                                                                                                                                                                                                                                    | 26                                           |

| 2.1.1 Introduction to Analogue Modulation                                                                                                                                                                                                                             | 26                                           |

| PhdThesis                                                                                                                                                                                                                                                             | 2010                                         |

#### **TABLE OF CONTENS**

| 2.2 Background of Principle Digital Modulation         | 27 |

|--------------------------------------------------------|----|

| 2.2.1 Introduction to digital modulation               | 27 |

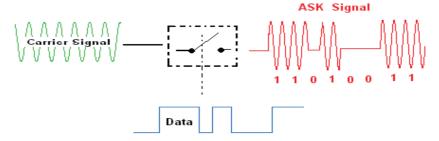

| 2.2.2 ASK Modulation background                        | 28 |

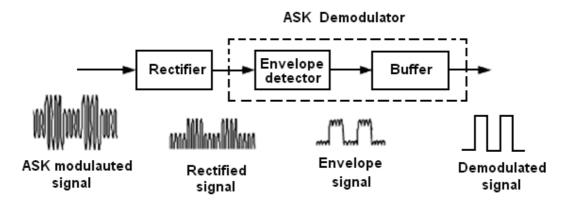

| 2.2.3 ASK Demodulation Technique                       | 30 |

| 2.3 Principle of n-PSK modulation                      | 31 |

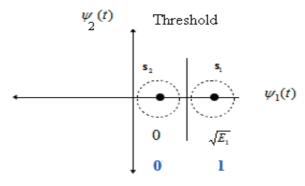

| 2.3.1 Binary Phase Shift Keying                        | 31 |

| 2.3.2 Demodulation of BPSK                             | 33 |

| 2.3.3 Qaudrtuer Phase Shift Keying                     | 36 |

| 2.3.4 Demodulation of QPSK                             | 41 |

| 2.4 Quadrature Signals Generation Techniques           | 43 |

| 2.4.1 Direct Digital Synthesizer (DDS)                 | 43 |

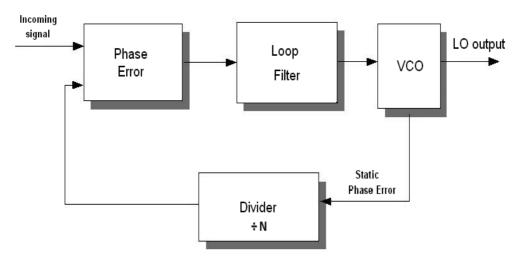

| 2.4.2 PLL (Voltage control Oscillator)                 | 44 |

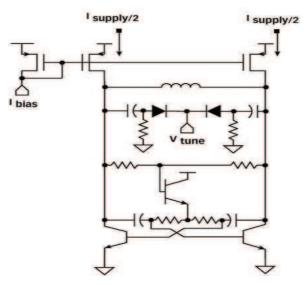

| 2.4.3 LC VCO tuning oscillator                         | 45 |

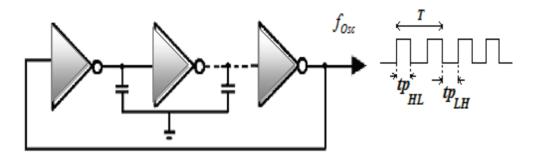

| 2.4.4 Ring Oscillator                                  | 46 |

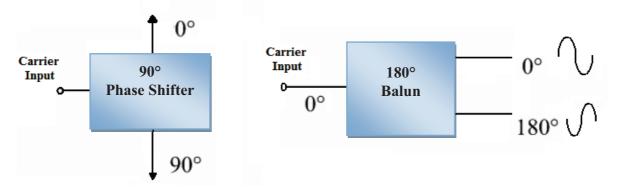

| 2.5 Quadrature Phase Shifter and Mixers                | 47 |

| 2.5.1 Types of Phase shifter                           | 47 |

| 2.5.1.1 Balance phase shifter                          | 47 |

| 2.5.1.2 RC-CR                                          | 48 |

| 2.5.1.3 RC- polyphase network                          | 49 |

| 2.5.1.4 Active Balun                                   | 50 |

| 2.5.1.5 CG-CS Active Balun                             | 52 |

| 2.6 Modulator Mixers                                   | 52 |

| 2.6.1 Active modulator mixres                          | 53 |

| 2.7 Summary of Modulation Schemes Topologies           | 54 |

| Chapter III                                            |    |

|                                                        |    |

| 3. Inductive Coupling link, Power Amplifier and        |    |

| Transmit circuit Inductive Coupling Link               | 56 |

| 3.1 Theory and Background for inductive coupling link  | 56 |

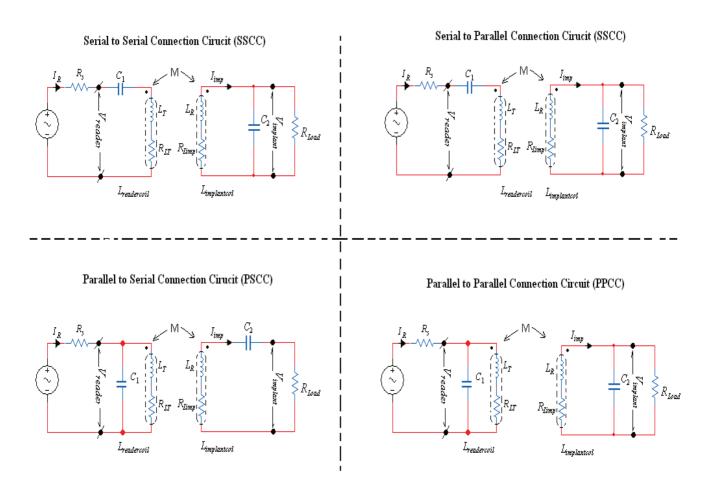

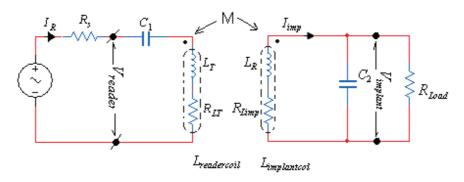

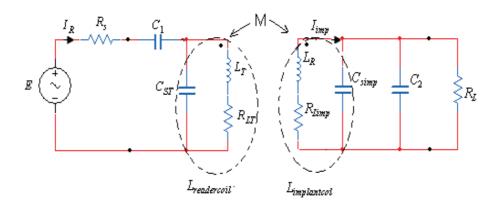

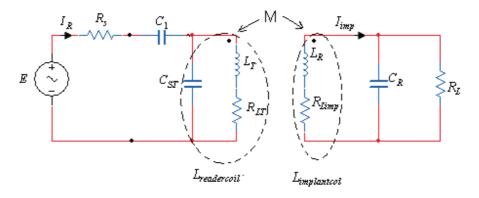

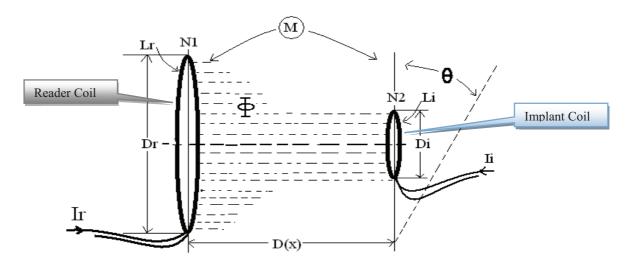

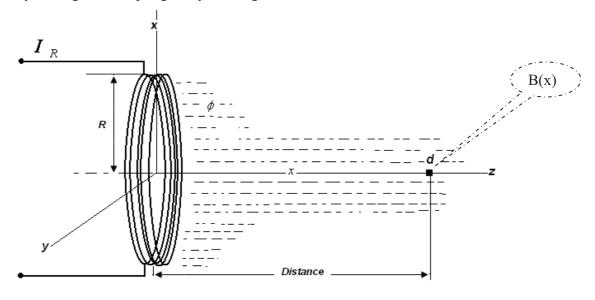

| 3.1.1 Theoretical Derivations                          | 58 |

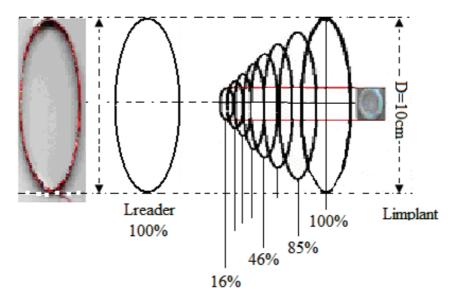

| 3.1.2 Hypothetical Methods simulation and measurements | 67 |

|                                                        |    |

PhdThesis 2010

#### TABLE OF CONTENS

|     | 3.1.3                                                                                                          | Inductive Coupling Link Efficiency                                                                                                                                                                                                                                                                                                                                                           | 71                                                                               |

|-----|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

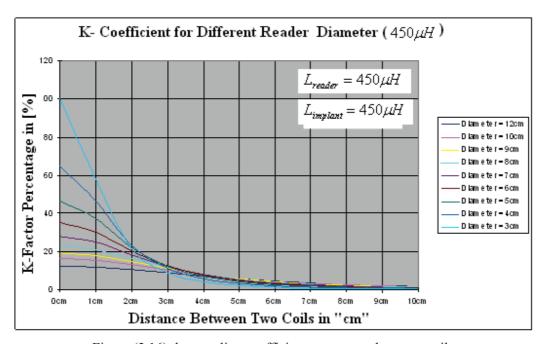

|     | 3.1.3.1                                                                                                        | Mutual and Coupling Coefficient for inductive link                                                                                                                                                                                                                                                                                                                                           | 71                                                                               |

|     | 3.1.3.2                                                                                                        | Lab Characterization measurements for mutual coupling                                                                                                                                                                                                                                                                                                                                        | 74                                                                               |

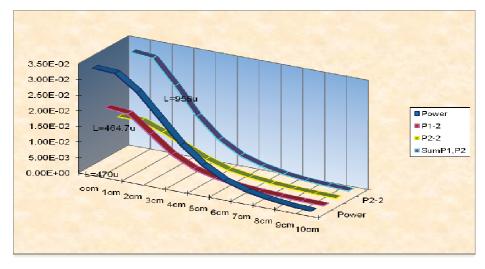

|     | 3.1.3.3                                                                                                        | Lab Measurements for Wireless Received Power                                                                                                                                                                                                                                                                                                                                                 | 75                                                                               |

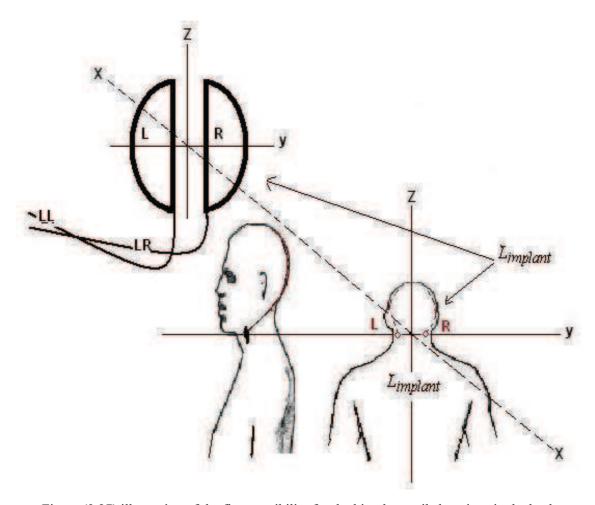

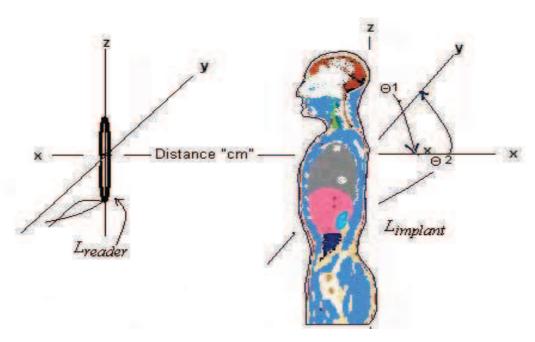

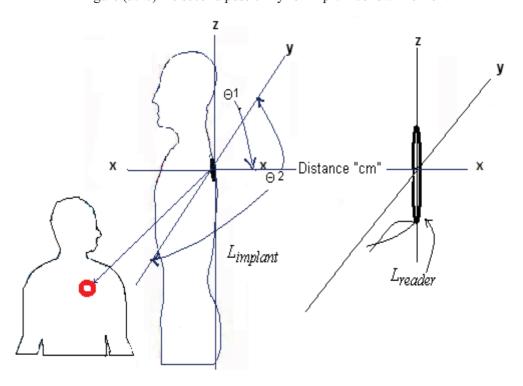

|     | 3.1.4                                                                                                          | Misalignment Investigation for Inductive Link                                                                                                                                                                                                                                                                                                                                                | 77                                                                               |

|     | 3.1.4.1                                                                                                        | Misalignment Analysis and Lab measurements                                                                                                                                                                                                                                                                                                                                                   | 78                                                                               |

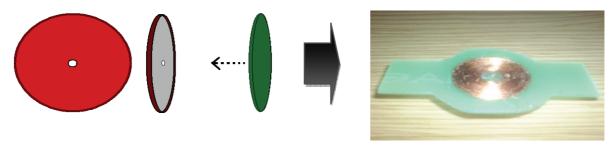

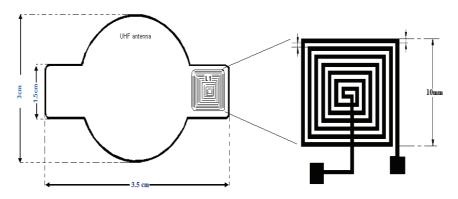

|     | 3.1.5                                                                                                          | Implant Coils Surgical Investigation                                                                                                                                                                                                                                                                                                                                                         | 80                                                                               |

|     | 3.1.6                                                                                                          | Conclusion of the inductive coupling Link                                                                                                                                                                                                                                                                                                                                                    | 83                                                                               |

| 3.2 | Power A                                                                                                        | mplifiers                                                                                                                                                                                                                                                                                                                                                                                    | 84                                                                               |

|     | 3.2.1                                                                                                          | Introduction to Power Amplifiers                                                                                                                                                                                                                                                                                                                                                             | 84                                                                               |

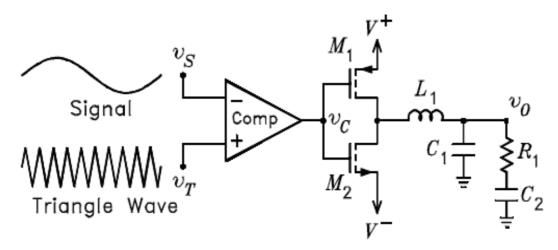

|     | 3.2.2                                                                                                          | Class <b>E</b> Power Amplifier theory simulation and design                                                                                                                                                                                                                                                                                                                                  | 85                                                                               |

|     | 3.2.3                                                                                                          | Class <b>F</b> Power Amplifier theory design and simulation                                                                                                                                                                                                                                                                                                                                  | 89                                                                               |

|     | 3.2.4                                                                                                          | Automatic frequency control for class F power amplifier                                                                                                                                                                                                                                                                                                                                      | 91                                                                               |

|     | 3.2.5                                                                                                          | Simulation and Lab measurements for Power Amplifiers                                                                                                                                                                                                                                                                                                                                         | 94                                                                               |

|     | 3.2.6                                                                                                          | Comparing measurement results for power amplifiers                                                                                                                                                                                                                                                                                                                                           | 98                                                                               |

|     | 3.2.7                                                                                                          | Summary of Power Amplifiers                                                                                                                                                                                                                                                                                                                                                                  | 99                                                                               |

| 3.3 | Implant F                                                                                                      | Received Power Simulation and Measurements                                                                                                                                                                                                                                                                                                                                                   | 100                                                                              |

|     | 2 2 4                                                                                                          | DE DC Descived Dever Investigation                                                                                                                                                                                                                                                                                                                                                           | 400                                                                              |

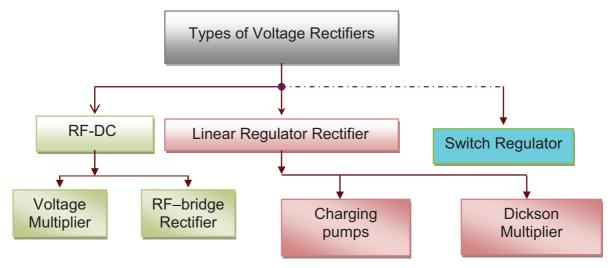

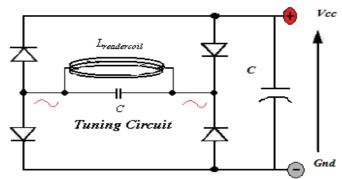

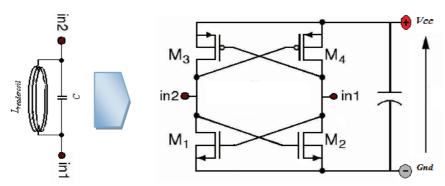

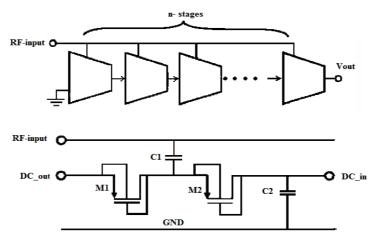

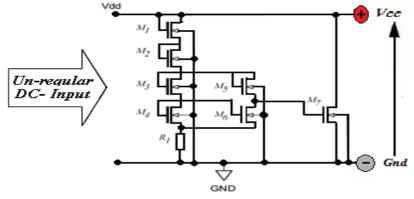

|     | 3.3.1                                                                                                          | RF–DC Received Power Investigation                                                                                                                                                                                                                                                                                                                                                           | 100                                                                              |

|     | 3.3.1                                                                                                          | Voltage Multiplier                                                                                                                                                                                                                                                                                                                                                                           | 100                                                                              |

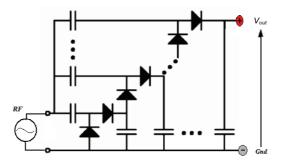

|     |                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                              | 101                                                                              |

|     | 3.3.2                                                                                                          | Voltage Multiplier                                                                                                                                                                                                                                                                                                                                                                           | 101<br>102                                                                       |

|     | 3.3.2<br>3.3.3                                                                                                 | Voltage Multiplier Schottky Diode Rectifier                                                                                                                                                                                                                                                                                                                                                  | 101<br>102                                                                       |

|     | 3.3.2<br>3.3.3<br>3.3.4                                                                                        | Voltage Multiplier                                                                                                                                                                                                                                                                                                                                                                           | 101<br>102<br>103                                                                |

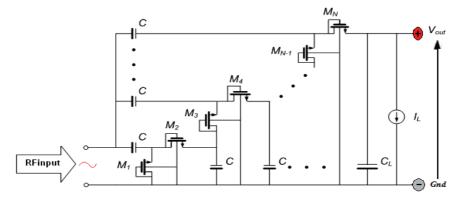

|     | 3.3.2<br>3.3.3<br>3.3.4<br>3.3.5                                                                               | Voltage Multiplier Schottky Diode Rectifier RF-DC-CMOS Bridge Rectifiers. Dickson Charge Pump                                                                                                                                                                                                                                                                                                | 101<br>102<br>103<br>103                                                         |

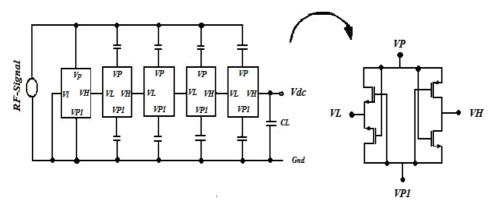

|     | 3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>3.3.6                                                                      | Voltage Multiplier                                                                                                                                                                                                                                                                                                                                                                           | 101<br>102<br>103<br>103<br>104                                                  |

|     | 3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>3.3.6<br>3.3.7<br>3.3.8<br>3.3.9                                           | Voltage Multiplier                                                                                                                                                                                                                                                                                                                                                                           | 101<br>102<br>103<br>103<br>104<br>105                                           |

|     | 3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>3.3.6<br>3.3.7<br>3.3.8<br>3.3.9<br>3.3.10                                 | Voltage Multiplier                                                                                                                                                                                                                                                                                                                                                                           | 101<br>102<br>103<br>103<br>104<br>105<br>105<br>107<br>108                      |

|     | 3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>3.3.6<br>3.3.7<br>3.3.8<br>3.3.9<br>3.3.10<br>3.3.11                       | Voltage Multiplier                                                                                                                                                                                                                                                                                                                                                                           | 101<br>102<br>103<br>103<br>104<br>105<br>105<br>107<br>108<br>111               |

|     | 3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>3.3.6<br>3.3.7<br>3.3.8<br>3.3.9<br>3.3.10<br>3.3.11                       | Voltage Multiplier                                                                                                                                                                                                                                                                                                                                                                           | 101<br>102<br>103<br>103<br>104<br>105<br>105<br>107<br>108<br>111               |

| 3.4 | 3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>3.3.6<br>3.3.7<br>3.3.8<br>3.3.9<br>3.3.10<br>3.3.11<br>3.3.12             | Voltage Multiplier                                                                                                                                                                                                                                                                                                                                                                           | 101<br>102<br>103<br>103<br>104<br>105<br>105<br>107<br>108<br>111               |

| 3.4 | 3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>3.3.6<br>3.3.7<br>3.3.8<br>3.3.9<br>3.3.10<br>3.3.11<br>3.3.12             | Voltage Multiplier                                                                                                                                                                                                                                                                                                                                                                           | 101<br>102<br>103<br>103<br>104<br>105<br>105<br>107<br>108<br>111<br>112        |

| 3.4 | 3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>3.3.6<br>3.3.7<br>3.3.8<br>3.3.9<br>3.3.10<br>3.3.11<br>3.3.12<br>Low Freq | Voltage Multiplier                                                                                                                                                                                                                                                                                                                                                                           | 101<br>102<br>103<br>103<br>104<br>105<br>105<br>107<br>108<br>111<br>112        |

| 3.4 | 3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>3.3.6<br>3.3.7<br>3.3.8<br>3.3.9<br>3.3.10<br>3.3.11<br>3.3.12<br>Low Freq | Voltage Multiplier Schottky Diode Rectifier RF-DC-CMOS Bridge Rectifiers. Dickson Charge Pump Voltage Regulator. Charging Pump voltage convertor Dc-Dc switches converter Switch Regulator Simulation of the RF-DC rectifiers Experimental Lab measurements Results. Summary of receiving power rectifying  uency Using Inductive Coupling Topology  LSK Modulation Investigation and design | 101<br>102<br>103<br>103<br>104<br>105<br>107<br>108<br>111<br>112<br><b>113</b> |

PhdtThesis 2010

#### **TABLE OF CONTENTS**

# **Chapter IV**

| 4.   | Proposed VHDL Modulators Synthesis and Evaluation      | 117               |

|------|--------------------------------------------------------|-------------------|

| 4    | 4. Biomedical Transmission Background                  | 117               |

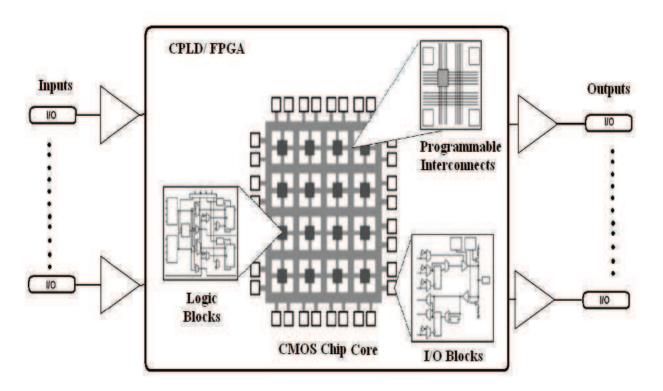

| 4.1  | The Biomedical Applications Using FPGA/CPLD Technology | 118               |

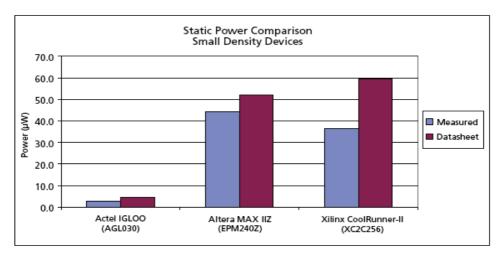

| 4.2  | Investigation of the Low power device                  | . 119             |

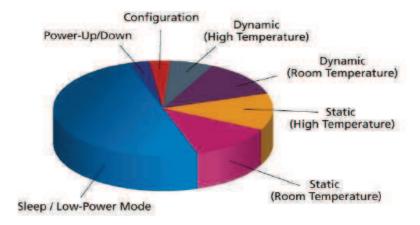

| 4.3  | Dynamic Power Calculation for FPGA/CPLD                | 120               |

|      | 4.3.1 Configration of CPLD and FPGAs devices           |                   |

| 4.4  | BPSK –VHDL Direct Digital Modulator                    | 123               |

|      | 4.4.1 Modulator Methodology Design                     | 126<br>126        |

| 4.5  | QPSK –VHDL Direct Digital Modulator                    | 129               |

|      | 4.5.1 Module Method Design                             | 133<br>133<br>135 |

| 4.6. | 8PSK Modulator Digital                                 | 139               |

|      | 4.6.1 Module Method Design                             | 139<br>140        |

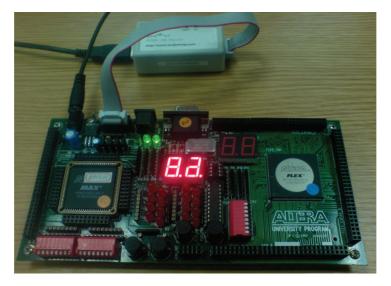

| 4.7  | Experimental Lab Measurements for VHDL Modulators      | 144               |

|      | 4.7.1 BPSK Modulator                                   | 144<br>146<br>148 |

| 4.8  | Filters Investigation for Medical Purpose              | 149               |

|      | 4.8.1 LP Filter Design and Simulation                  | 151<br>153        |

PhdThesis 2010

#### **TABLE OF CONTENTS**

PhdThesis

| 4.8.3 Filter Lab Measrements Results                    |

|---------------------------------------------------------|

| 4.8 Summary and Results                                 |

| Chapter V                                               |

| 5. Biodevices System Overview                           |

| 5.1 Biodevices System and Experimental Lab Measurements |

| 5.1.1 Downlink Reader Unit                              |

| 5.1.1.1 Lab Measurements for ASK modulator              |

| 6.0 Conclusion Thesis Results and Future Work           |

| 6.1 Down-Up Link System                                 |

| 6.2 Suggestion for Future work                          |

| List of Abbreviation and Symbols                        |

| References                                              |

| References                                              |

| Appendixes                                              |

| Appendixes                                              |

2010

# Chapter

1

# Introduction

## Chapter I

emiconductor chips are used today not only in communication or control systems, but also in our bodies, for diagnostic or monitoring signals, such as electroencephalograph (EEG), and electrooculography (EOG). They are used to understand electrical brain activity, with the nervous system behavior, and process it within implant circuitry [44] [46] [47] and [68] [75]. Generally, the investigation of the brain function has been targeted by many researchers and universities in the past and this century [114]. The human brain maintains over 14- billion nerve cells; 9-billion of these are distributed over 64 sections in the brain [210]. These bulk networks are being investigated by researchers and neuroscientists who have began to use bundles of tiny wire cables and multi electrode arrays, for monitoring and analysis of the many neurons in the brain, which are essential to understand the neural substrates of many physiological and pathological brain diseases, such as epilepsy and paralysis. The transcutaneous wireless telemetry implant is one of these technology solutions applied in biomedical applications, used to avoid a susceptible path to infection in the body and reliability problems. This eliminates the needs for tethering wires or implantable batteries [45] [50]. The research is continuing to develop many different types of electronic biomedical devices which may give prosthetics for treatments of a range of other wide ailments, such as blindness, quadriplegia, epilepsy and Parkinson's diseases [161]. On the other hand, these electronic devices are used especially in biomedical applications. These characteristics are imperative because the devices are difficult to access and the consequences are serious if the devices malfunction or fail, which requires knowledge of material behaviour and media. This chapter gives an overview of biomedical device topologies that are used in medical treatment in hospitals, clinical, telemedicine, and healthcare. Finally, there is a summary of the applications of transcutaneous biodevices, which are based on wireless infrastructure and a study of most of the applications for the magnetic field applied to the human body.

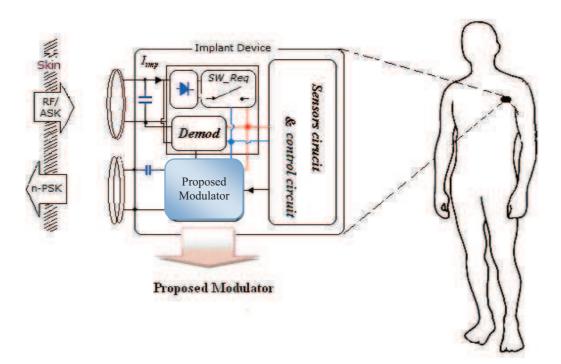

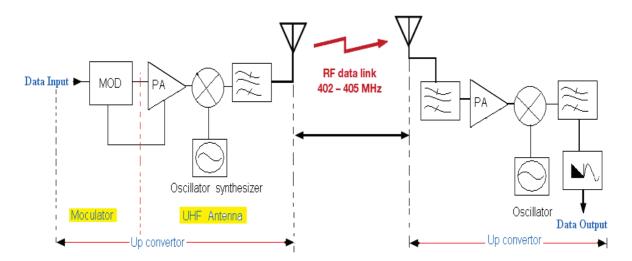

#### 1.1 Biodevices Technology

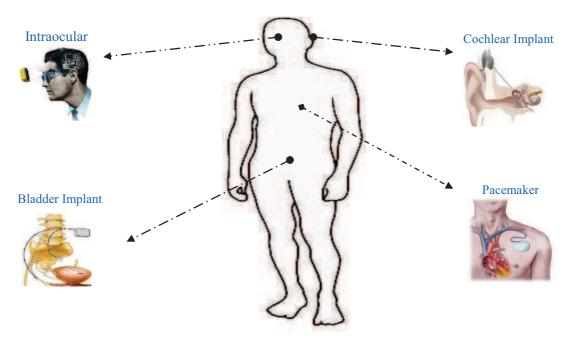

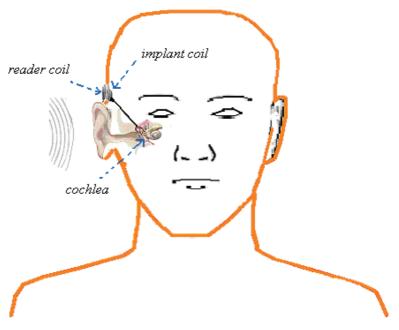

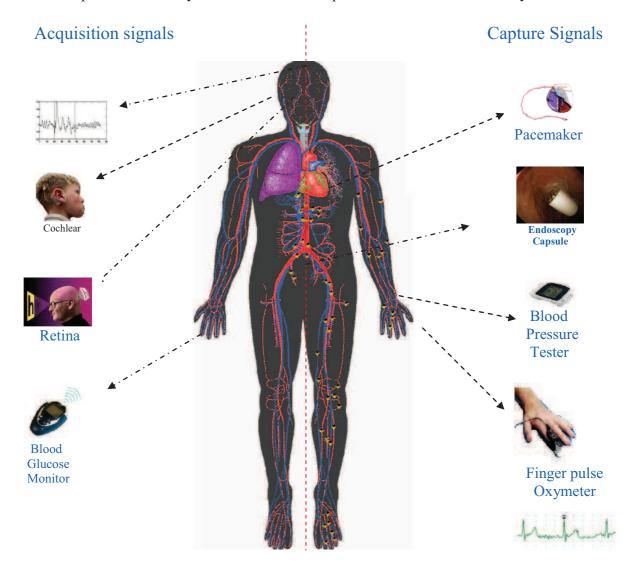

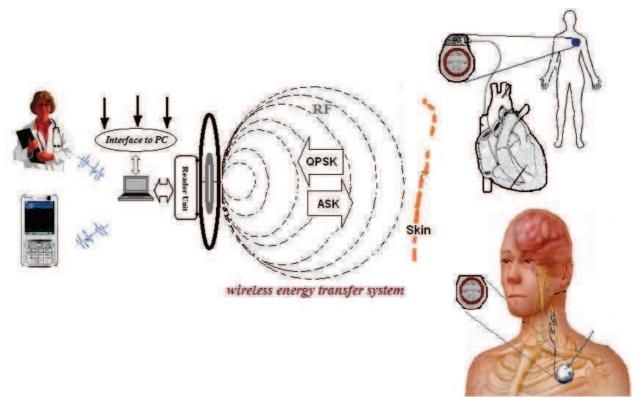

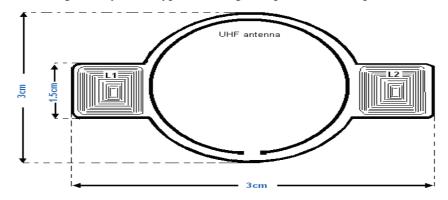

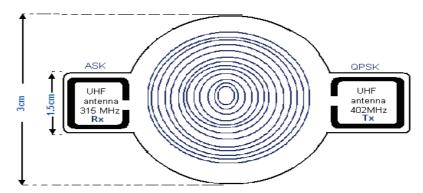

Biomedical devices technology has been recently used for medical applications in the human body, by monitoring or recording many signals such as electrocardiogram (EKG), electroretinogram (EKG), and electromyography (EMG) [154] and [164]. Many research groups at institutes and universities are focusing on biomedical circuit devices. Predominantly these are to understand disorders of brain behaviour and processing it within the implant circuitry. These biodevices may solve many biomedical disorders, such as epilepsy and Parkinson's disease, which are caused by many factors. Typically, a wireless biomedical device consists of two parts, a reader that transfers a power RF signal, when the biomedical electronics device is swallowed or surgically implanted in a subject/patient, and can control the device from outside the body through an inductive coupling downlink, using a variety of modulated energy forms like electromagnetic energy [137]. On the other hand, the implantable device can communicate with exterior world by up-link, whether over inductive wireless coupling or UHF links to transmit the acquired data from the body [100] [96]. General examples of applications for the human body are shown in Figure (1.0).

Figure (1.0) Implant technology applications in the human body

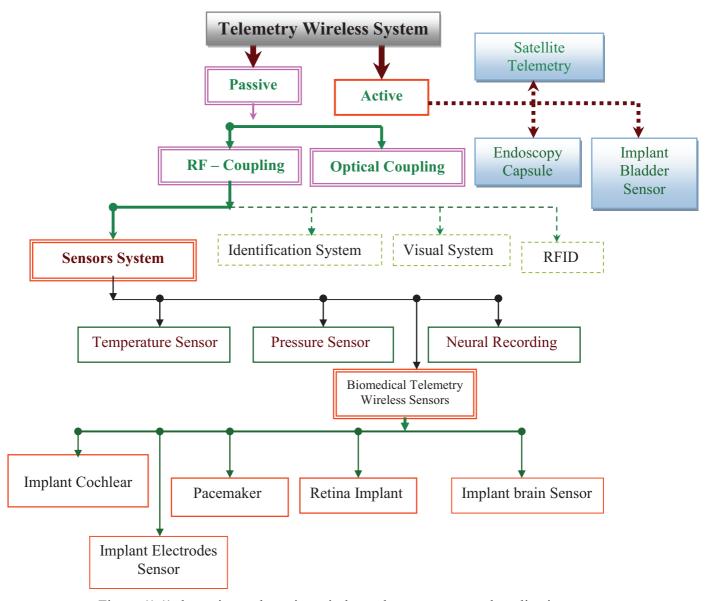

Conceptually, most biodevices are bi-directional systems which transmit RF signal carriers when they are swallowed or surgically implanted in a subject/ patient. They can communicate with biological or physiological parameters which are transferred through different medium types between two locations including air space, water and biological tissue (blood, fat, bone, etc) [43],[48]. The classification types of most common Passive/Active wireless telemetry applications and purposes are illustrated in Figure (1.1) [151] [193].

Figure (1.1) the active and passive wireless telemetry types and applications

#### **1.2** Implantable Technologies For Medical Applications

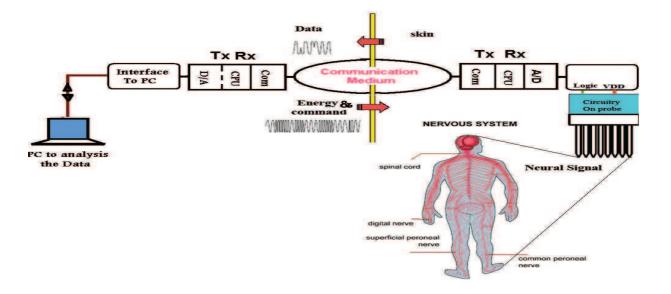

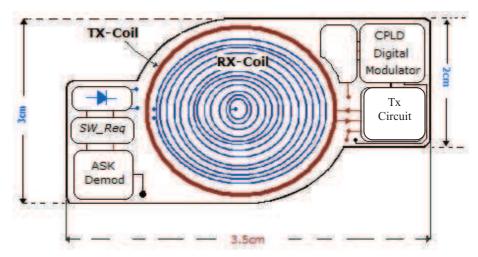

Implant technology has developed via further investigation and studies on human diseases in combination with work on electronic circuits. One of these technologies which is now used wireless implantable sensors; this new technology application is derived from the transcutaneous implant telemetry devices inside the body. It has been recently used for medical applications in the human body; one of these application examples is rehabilitation for replacing the damaged organs by biomechanical electronic devices to do the same function [154] [155] [159] and [160]. Almost all conventional wireless telemetry has limited applications, and this chapter describes most of the applications topology using inductive coupling as based in our work, whilst chapter three covers the background and design of the inductive coupling link and data over a magnetic link. The basic system consists of a bi-directional data transmission channel through the skin tissue of the patient. The data acquired from the matrices of sensors are converted into digital form modulated signal and retransmitted into a reader unit for analysis and processing (Up-link) [82] [105] and [175]. The general bio-communication architecture system for collecting data from the nervous system is described in Figure (1.2) as an example based on the work in the this thesis.

Figure (1.2) the bio-communications system architecture

#### **1.2.1** Implant Cochlear Technology

Cochlear technology uses wireless coupling coils through human tissue, with the interior implant inside the head of a patient, and the exterior part outside the body [67] [148]. The exterior part picks up the sound from around a microphone, amplifies it and manipulates this sound by a speech processor, and then retransmits it through the inductive coupling. However, the interior coil is implanted surgically, and placed to get the optimum coupling with the exterior coil. The modulated RF signal offers the DC-source for the implant electronic circuits, and the electronics used in the implant cochlear device need to be of low power consumption and high reliability [109]. When the demodulated data are converted into electrical signals for the cochlear nerve, the electrical pulses are sent to the brain. The brain analyses these electrical pulses as received information, which enable the patient to understand and respond to sound, and can enable disabled patients to hear. Generally, the principle of cochlear implant technique has been shown in Figure (1.3). Typically the acoustic band frequency for humans is between 300~ 3400 Hz, the transferred data through the coils are low rate, which is a few kbps [70] [144]. This kind of technology overlaps with the work presented here because of the inductive coupling link, for the implant coil design.

Figure (1.3) the cochlear implantable coil

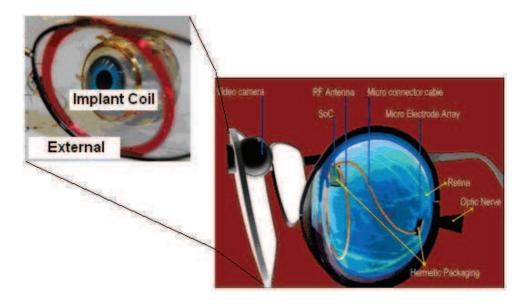

#### 1.2.2 Intraocular (Retinal) Implant

One of the main growth areas in application research is retinal implant or Bionic eye technology, to help blind patients or retinal disease sufferers with their sight, and help people get a sense of their surroundings. This technique replaces and strengthens the damaged optic nerve (ganglion cells). It provides light and image to the brain's vision system for normal processing [112] [76]. The RF antenna foe inductive coupling is used to communicate with the exterior part reader, which supplies the implant with the required DC power, and transfers the image data from the video camera. Moreover, a tiny implant coil on the surface of the eye receives the wireless signals from an external camera, which the patient wears on a pair of spectacles that contain a camera, transmitter and wearable computer to process the signal from the camera. The camera stimulates the normal eye which converts the view into an electrical image signal modulated to transfer over wireless coupling link into the implant coupling inside the eye. Light and image signals are received through a pair of coils and received by an array of electrodes surgically implanted on the retina. The array delivers electrical signals to the nerve cells in the eye, mimicking the role of light-sensitive cells lost in degenerative retinal disease. The general architecture of a retina implant is shown in Figure (1.4).

Figure (1.4) Principle architecture of the retinal implant device [198]

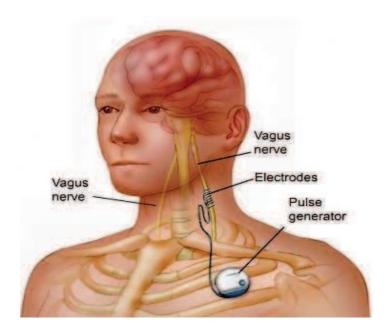

#### 1.2.3 Brain Implant Device

Brain-stimulation devices for treating depression have faced unexpected setbacks, to help millions of people who fail to respond to antidepressant drugs. The brain pacemaker device is implanted in the chest of a patient, with leads that send electrical impulses into parts of the brain. They have already been approved to treat movement disorders such as epilepsy, and Parkinson's disease tremors and depressed patients have improved significantly [117] [175]. Figure (1.5) shows the brain stimulator pacemaker construction for the patient, surrounding the vagus nerve [218]. In particular, children suffering from dystonias can benefit from brain pacemaker surgery. However, a brain pacemaker implantation is only advised in cases when the aforementioned drugs and combinations thereof do not lead to satisfactory treatment results and in patients less than 70 years of age. Additionally, the brain device is powered with a long life battery. One of the development solutions introduces a wireless power coupling technology to avoid additional regular surgical operations to replace the old battery, and which may cause the malfunction of the device when the battery is replaced. The wireless technique offers full control for the device and improves the performance, and gives more flexibility for the patient remotely.

Figure (1.5) the brain pacemaker implant device [218]

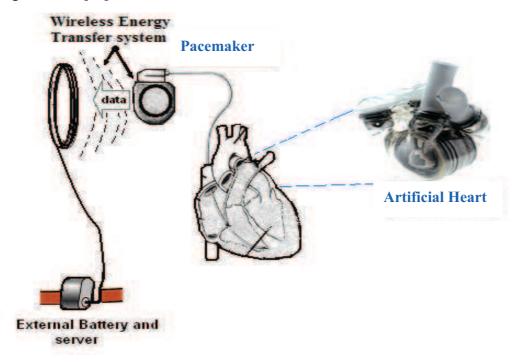

#### **1.2.4** Pacemaker Device

In recent years there has been a high rate of surgery for artificial heart implants and cardiac pacemakers for monitoring and controlling irregular heart rhythms, especially for babies and the elderly. A newly developed artificial heart is called the intelligent smart artificial heart, created in order to realize the safe treatment and effective control for patients [154]. However, wireless inductive coupling can be used to communicate between the pacemaker and artificial heart using a wearable reader outside the patient [159] [160]. This avoids the surgical procedure for replacing the battery. Typically it provides the energy and control data, gathering back data from the implant pacemaker device. We demonstrate in Figure (1.6) the wireless application for a pacemaker or artificial heart. The new technology using Bluetooth can provide a simple interface with the patient, where the information can be accessed by mobile phone or interface with a web network to connect them to the Hospital or clinic. Obviously, electrical magnetic interference (EMI) may be one of the main effective causes, and could be a defect of the highly sensitive devices, which work in, near or interface with magnetic environment field such as RFID magnetic area [72].

Figure (1.6) the wireless communication for artificial pacemaker device

#### **1.2.5** Wireless Capsule Endoscopy

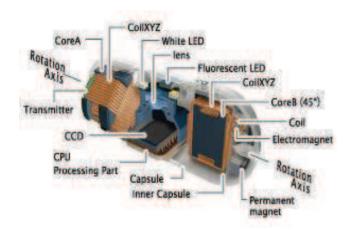

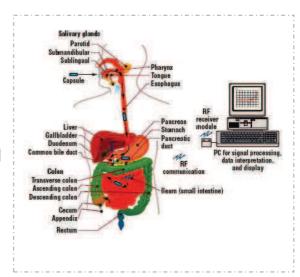

The wireless capsule endoscopy (WCE) is based in a vitamin size pill which captures the images of the digestive tract, while it is transported passively by peristalsis. The device consists of an image sensor, an illumination module, a radio frequency transmitter and a battery [203] [157]. The architecture diagram of a capsule endoscope is shown in Figure (1.7). The WCE is used to perform a painless diagnosis inside the gastrointestinal tract. The test requires a patient to ingest, after a one night fast, the WCE, which is carried by peristalsis through the digestive area. During the transit the pill takes images from the CCD camera system, which are transmitted to an antenna placed outside the patient's body. The second generation of WCE uses magnetic fields generated for controlling the capsule from outside the body in certain directions [76]. The received electromagnetic energy is converted into a power supply for the capsule that is capable of localizing the device and determining the location of the pill inside the patient's body. Figure (1.8) describes the movement of the capsule inside the patient body, which communicates with wireless transmission to the PC.

Figure (1.7) the Architecture of Endoscopy Capsule [203]

Figure (1.8) the Endoscopy System [76]

## 1.3 Media Absorption Side Effects and Technology Limitations

Generally, there are an increased number of wireless applications, with most of the biomedical devices being augmented by the wireless environment techniques. The biomedical electronics devices use inductive magnetic communication for controlling or monitoring the acquisition back data from the patient. The magnetic flux that crosses the patient's skin is coupled with the implant coil inside the body. The body attenuates the magnetic field, which is dependent on the frequency used for coupling [143]. Table (1.0) illustrates the electrical properties of the body at ISM frequency [201], and the occupational exposure level of the electrical and magnetic fields varying with time are shown in Table (1.1) [211].

| Table $(1.0)$ the E | Electrical data | of biological | tissue used at | 402MHz [ | 201] |

|---------------------|-----------------|---------------|----------------|----------|------|

|                     |                 |               |                |          |      |

| Biological Tissue | Permittivity ( $\varepsilon_r$ ) | Conductivity $\sigma(s/m)$ | Mass Density $\rho(g/cm^3)$ |

|-------------------|----------------------------------|----------------------------|-----------------------------|

| Brain             | 49.7                             | 0.59                       | 1.04                        |

| Skin              | 46.7                             | 0.69                       | 1.01                        |

| Fat               | 11.6                             | 0.08                       | 0.92                        |

| Blood             | 64.2                             | 1.35                       | 1.06                        |

| Bone              | 13.1                             | 0.09                       | 1.81                        |

| Muscle            | 58.8                             | 0.84                       | 1.04                        |

Table (1.1) Permitted level of exposure for electric and magnetic fields over frequency [211]

| Frequency range | E-field strength $(V m^{-1})$ | H- field strength $(A m^{-1})$ | <b>B-field</b> $(\mu T)$ | Equivalent plane wave power density $S_{eq}(Wm^{-2})$ |

|-----------------|-------------------------------|--------------------------------|--------------------------|-------------------------------------------------------|

| up to 1 Hz      | _                             | $1.63 \times 10^{5}$           | $2 \times 10^{5}$        | _                                                     |

| 1-8 Hz          | 20,000                        | $1.63 \times 10^{5}/f^{2}$     | $2 \times 10^{5} f^{2}$  | _                                                     |

| 8-25 Hz         | 20,000                        | $2 \times 10^4/f$              | $2.5 \times 10^4/f$      | _                                                     |

| 0.025-0.82 kHz  | 500/f                         | 20/f                           | 25/f                     | _                                                     |

| 0.82-65 kHz     | 610                           | 24.4                           | 30.7                     | _                                                     |

| 0.065-1 MHz     | 610                           | 1.6/f                          | 2.0/f                    | _                                                     |

| 1-10 MHz        | 610/f                         | 1.6/f                          | 2.0/f                    | _                                                     |

| 10-400 MHz      | 61                            | 0.16                           | 0.2                      | 10                                                    |

| 400-2,000 MHz   | $3f^{1/2}$                    | $0.008f^{1/2}$                 | $0.01f^{1/2}$            | fi40                                                  |

| 2-300 GHz       | 137                           | 0.36                           | 0.45                     | 50                                                    |

#### **1.3.1** Skin Tissue Attenuation

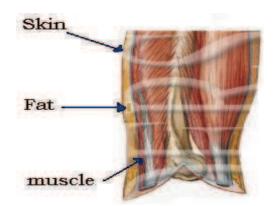

One of the objectives of this thesis is to investigate the body skin attenuation for electromagnetic fields. Most of the studies for electromagnetic radiation exposure of the biological tissue cover the mobile phone radiation effects for a human body. The interactions of the radio frequencies are not specific to a certain frequency; the exposure field is characterised by the frequency, intensity and polarization. For microwave radiation it is essential to compute the absorption rate (SAR) for high EMF power [211]. At low frequency working in biomedical device applications, the RF EMF generated by the transmitter coil toward the human body, received by a small loop coil as implant part, is less than a few Watts. In practice, the area where the type of coil is located at the external layer of the skin is the critical place to be considered for reduced attenuation. However, the body tissue layers affect the absorption of electrical and magnetic energy. A generic body model is defined consisting of planar layers of skin, fat and muscle tissue. Fat tissue has very low water content and therefore a significantly lower permittivity and conductivity ( $\varepsilon_r$  = 5.5,  $\sigma$ = 0.05S/ m), whereas muscle tissue has permittivity and conductivity of ( $\varepsilon_r$  = 55.0  $\sigma$ = 0.95S/m) [72]. The skin tissue varies from 0.4mm to 2.6mm thick. These values include the epidermis and dermis and cover an age range from newborn to 60 years. On other the hand the fat layer thickness takes into account all possible effects due to impedance matching in the body layers. The layered body tissue is shown in Figure (1.9). The main factors affecting the attenuation for electromagnetic signal through the patient skin can be expressed in equation (1.1) [210].

$$\alpha = \sqrt[\omega]{\frac{\mu\varepsilon}{2}} \left[ \sqrt{1 + \left(\frac{\sigma}{\omega\varepsilon}\right)^2} - 1 \right]$$

(1.1)

where:

- $(\omega)$  is the angular frequency

- (ε) is the permittivity

- $(\sigma)$  is the conductivity

- $(\mu)$  is the Permeability

Figure (1.9) Different layers for the skin [209]

It clear that the greatest effect of RF energy as a result of exposure to electromagnetic fields at relatively low levels (below 10 mW/cm<sup>2</sup>), is on the eye and the gonads. Those are particularly susceptible to heat, and have been extensively investigated [139]. The radiation at frequencies above 800 MHz can produce injury to the eye and this type of injury depends on the frequency, and millimeter waves can produce keratitis. Cataracts develop after a sufficiently long exposure to power densities above 100mW/cm<sup>2</sup>. The biological effects are related to the intensities of the fields within the living body, not to the external intensity of an exposure field. The internal fields are a complex function of exposure conditions and other parameters. The internal fields are frequently described in terms of the Specific Absorption Rate (SAR), which expresses the rate of energy absorption (e.g., at a given location, or averaged over the whole body) and is proportional to the square of the internal electric field intensity. The proportionality constant depends on the electrical properties of the tissue. The average SAR for a whole body, far-field (far away from the radiator) exposure depends on the field frequency, intensity, direction, subject-to-source configuration, subject's size and shape, and presence of other objects. Particularly with metal objects in the immediate vicinity, increased absorption occurs in various places inside the body, resulting in so-called "hotspots". For human beings maximum energy absorption take place between 30 and 100 MHz, depending on the body size and the environment [174]. For an average man isolated from ground the frequency of the maximum absorption is about 80 MHz. However, for the SAR the important parameters are absorbed energy in the area where the type of antenna is located, the outer layer of the skin current distribution and the distance between reader transmit coils and the receiver coils, in near field radiation of transcutaneous wireless coupling. The SAR is usually averaged either over the whole body or over a small sample volume typically (1g or 10g of tissue) and has units of Watts per kilogram. It can be calculated from the electrical field within the tissue as defined in the equation [219]:

$$SAR = \frac{\sigma |E^2|}{2\rho} \quad \left[\frac{W}{kg}\right] \tag{1.2}$$

where:

- (E) is the Electrical field strength

- $(\sigma)$  is the conductivity of tissue

- ( ho ) is the sample of mass density of tissue

#### **1.3.2** Electromagnetic Interference (EMI)

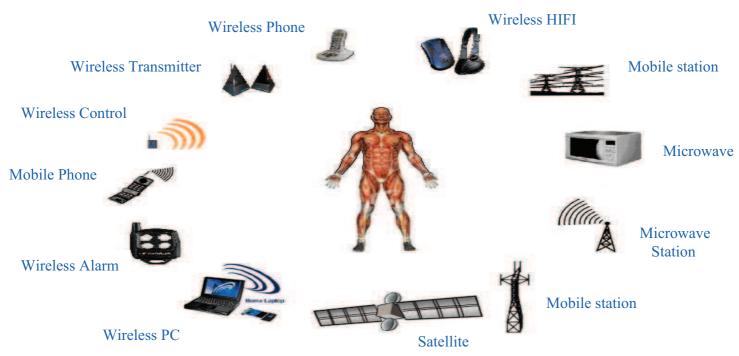

The electromagnetic inductive coupling link has been used in biomedical applications, and the implant device coil can receive any transmit signals around it. That could cause the device to malfunction, if it is resonant at the same received frequency [72] [115]. Hence, it is difficult to shield the inductive coupling, which is an open transformer, to protect the implant microelectronics device from undesirable magnetic fields. It is required to develop a suitable solution to minimize the risk for the patients. Typically, the low frequency field induces currents in the human body that can have an effect on the sensory, nerve and muscle cells. The greater field strength, the more pronounced the effects [217] [196]. On the other hand, the high frequency fields heat the human body, and the degree of the absorption of electromagnetic waves is a function of the frequency and intensity of the field and the type of tissue. The organs with lesser blood flow are the most endangered, e.g. the eyes. In contrast, the heart and brain are better at handling heat due to their better blood flow [187]. However, the strength of field decreases at increasing distance from the source of radiation. In addition, the electrical charges absorbed by the body (static charge) could cause malfunction of electronic devices. Figure (1.10) demonstrates the most common sources around the patient which could cause effects.

Figure (1.10) the most common EMI interfaced into the human body

#### **1.3.3** ISM Band Frequency For Medical Applications

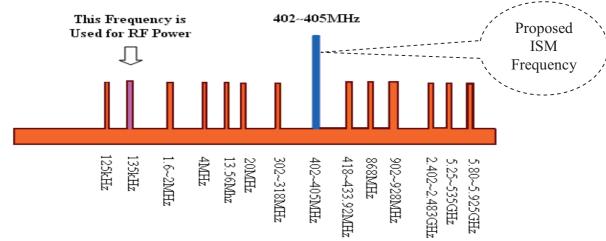

The implant biomedical system is under rapid development for many applications. There are demands for a higher data rate over the wireless environment that requires a high bandwidth and high frequency carrier. A new unlicensed Industrial Scientific and Medical "ISM" frequency band (402~405 MHz) was recently reserved for medical implant communication system by the FCC Federal Communication Commission, and recommended by ITU-R [192] [210]. This band seems attractive providing low body absorption at these frequencies comparing to other frequencies. Figure (1.11) demonstrates the most common frequencies covered in biomedical wireless applications. However, the frequency for transcutaneous telemetry devices rises up into the microwave band, which is shared with other wireless applications. Typically other applications use the microwave frequency band (2.45 GHz-5.8GHz), for example the satellite telemetry for animal tracking and microwave tomography for medical image analysis, and widely used devices such as RFID, Bluetooth, car alarms, microwave ovens and wireless home phones, which are operated at 2.45GHz, may cause interference effects for various implant devices. Disadvantages of using the microwave frequency in the human body, concern certain frequencies which have biological effects such as thermal damage or overheating of the blood or tissue [139]. Conversely, the chosen carrier frequency is most important for designing the electronic implant system, for less interference; our chosen frequency was 135 kHz as RF power carrier frequency in our application, whilst our target frequency is 402MHz for the implant device.

Figure (1.11) ISM frequency bands used for medical applications

#### 1.4 Acquisition of Neural Signals

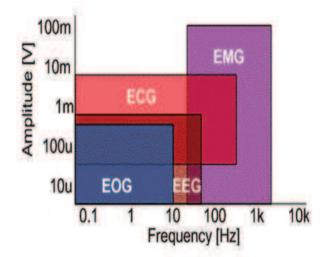

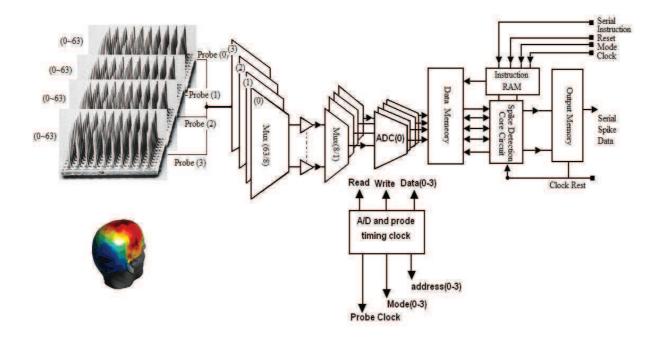

To acquire and record neural signals, such as Electroencephalography (EEG) or electromyography (EMG), to assist understanding of the brain behaviour signals, requires processing of signals within active integrated electronic implant circuitry [114]. The EMG has an amplitude of only 1mV so to detect it an amplifier is needed and filtering is required for the noise or electromagnetic interference. Generally, the noise is generated by many common applications such as power lines, fluorescent lights, computer and monitors, and that is added and amplified with the EEG signal will often swamps the EEG signal [105] [140]. Figure (1.12) demonstrates the frequencies with respect to amplitude for different acquisition signals from the body. The Utah microelectrode array captures the respond commands signals from neuron cells, processing and coding this information and re-transmitted to the reader unit or interface PC. Eventually Utah electrodes are brought out to a small printed circuit board with multiplexer brought out to a micro tech connector [44] [150] and [151]. The architecture of the Utah microelectrodes arrays (UEA) is demonstrated in Figure (1.13). The UEA total is (10 x 10) array of 100 platinum-tipped silicon extra cellular electrodes, and amplifies the neural signal from each electrode. This data is digitized and transmitted over an RF link mounted on the chip [168] [137] and [161]. It is necessary to increase the conveyed bit rate, and reduce the effects of the interference or increase signal to noise ratio (S/N), where the neural signal is less than  $500\mu V$ .

Figure (1.12) the frequencies and amplitudes of body signals

Finally, samples of signals captured by Utah microelectrodes are presented in Figure (1.14).

Figure (1.13) the architecture of Utah microelectrodes array [151]

Figure (1.14) Captured signals from Utah microelectrodes [196]

#### **1.5** Biomedical Telemetry Chips and Applications

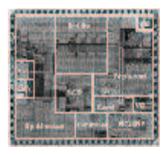

In recent years, many researchers have developed different packages of miniature implantable devices. To study the complex neurons involved in scientific phenomena such as cochlear disease, epilepsy, and aggressive behaviour, it is necessary to observe the electrophysiological activity in real time. Figure (1.15) shows the prototype samples of fabricated chips for medical purposes, and there are different chips for medical solutions such as blood pressure sensors, bladder sensor, and cochlear implant, retina and sphincter sensor [156]. However, there are many medical instruments that use electronic devices, such as insulin pumps and breathing activity monitor. There are still many biodevices under investigation for improving the power efficiency and coupling link and using different schemes for maximizing the data rate with low noise and minimum size. The second research point is the interface technology with the medical device and networks or appropriate adapters such as PC or mobile phones. This gives to the patient the flexibility to use the devices remotely. Figure (1.16) shows the biomedical device interfaces for communication and flexibility of technology for patient use [48] [49] [177].

Figure (1.15) the layout of different medical chips [49]

Figure (1.16) the medical care interface communication

#### **1.6** Chapter Summary

This chapter has shown an introductory summary of the recent and previous study cases and researchers working on biomedical implant telemetry devices applications. Briefly, it describes the disorders and ailments of the human body such as epilepsy, paralysis, Parkinson's disease, and nervous system disorders. It has briefly summarized the key design elements of most of the design factors for electronic implant devices that are commonly used in wireless communication. The Table below (1.2) shows the main comparison parameters between data rate and communication distance, for different biomedical applications. They use different modulation schemes over the wireless coupled link and different RF carrier frequencies. The term near field communication is used when signals are inductively coupled between reader and implant for data transmission. However, demand for a higher data rate for the acquisition data returned from the body is increasing, and requires an efficient modulation technique for achieving a high transfer rate and low power consumption. These are the main challenge factors in implant devices, and are therefore our goal in this work. For example, the human voice band is between 300~3400 kHz; obviously it does not require a high RF frequency for manipulation. However, visual implants such as retinal implants or wireless endoscopy capsules, which work with image data and control signals transmitted in real time, deal with high speed data for transfer over a magnetic communication link. These types of technology may need a high rate modulator to encode the huge amount of information.

Table (1.2) summary of the published research for implant devices

| TX- Carrier    | Data encoding | Data -   | Comm.  | Publication | Publication |

|----------------|---------------|----------|--------|-------------|-------------|

| Frequency      | Modulation    | Rate     | Range  | Year        | References  |

| 125 to135 kHz  | FSK           | 4kbps    | 20cm   | 2002        | [201]       |

| 1.6-2MHz       | FSK           | 1.2kbps  | 3.5cm  | 2005        | [179]       |

| 4 MHz          | ASK&PWAM      | 60kbps   | 2.8cm  | 2004        | [128]       |

| 13.56MHz       | BPSK          | 1.12Mbps | 1.5cm  | 2005        | [135]       |

| 2MHz           | ASK           | 8bps     | 0.6cm  | 2005        | [150]       |

| 27MHz          | FM            | 9bps     | 1-2cm  | 1998        | [45]        |

| 402-405MHz     | FSK           | 20kbps   | 1-2cm  | 2005        | [145]       |

| 868 to 928 MHz | FM            | Low rate | 91cm   | 2005        | [151]       |

| 3.2 GHz        | FM            | Low rate | 2.5 cm | 1995        | [204]       |

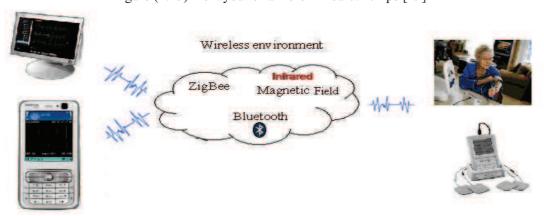

The previous table (1.2) compares the main research approaches for implant devices design. Most implantable biomedical devices have attributes of small size and high reliability, long retention rate, with very low power dissipation and field conformability. Clearly, most of the published works by researchers are using in analogue modulation and high carrier frequency, where the communication is still very short distance. So we consider in our work these points for introducing a new design for improved performance. Figure (1.17) shows the different biomedical devices applications and compares the power dissipation for each device with respect to data rate over communication range between telemetry device and reader over inductive passive coupling [67] [94] [158] and [164].

Figure (1.17) comparing the power dissipation for biomedical devices with respect to data rate

Finally, most of the acquisition data signals have been summarised, which can be observed or captured from the human body. Predominantly, this is generated by organs such as the heart under different conditions or is measured from the nervous system to communicate with the brain and perform the motion of the body's reaction with respect to the external world as shown in Figure (1.18). These are signals can be recorded monitored or captured from the human body. However, the new tele-medical health help care technology is able to access a web network that offers to the patient the facility for interface with hospital and their doctors remotely.

Figure (1.18) the acquisition and capture of signals from the body

#### 1.7 Motivation of Thesis

The main challenges in biomedical devices are strictly for a higher transfer rate, and transmitting over wireless communication. This mainly needs an efficient system to hand over the information with minimum error; enhanced encoding of information is the key factor to protect the original data especially with data acquisition returned from the human body, converted into digital information. Furthermore, the amount of health care data is increasing. It is called "BIOSTEC" which includes Bio-signals, Bio-medical devices, and Bio-health. Mostly the recent and previous reports and research in this area have studied the behaviour of diseases of the human body, such as epilepsy, brain, nervous system disorder; focusing on improving the prosthesis or treatment for it. This work tries to study and investigate the problem of low data rate over a given spectrum bandwidth. The challenge for design of a modulator is to transfer a high data rate from the implantable wireless device into a reader unit, over a digital channel at industrial scientific medical (ISM) frequency band. In addition, we need to work with new technologies to design an efficient and optimum system, to improve the low data rate for conventional biodevice systems.

#### **1.8** Thesis Organization

In this thesis we describe the current state of the research on a low power wireless telemetry system for medical applications. A study of existing biomedical device technologies and their key applications is presented. A brief assessment of future trends for wireless telemetry with a focus on emerging technologies with different digital modulation scheme techniques is given This thesis has been split into six chapters as:

#### • Chapter 1:

This chapter describes the general knowledge overview of the bio-telemetry and biomedical devices applied for medical applications. For example, implant telemetry, telemedicine, and healthcare, which describe the types of implantable sensors and acquisition signals data from the human body. Most of the researchers working in this area mention the behavioural diseases, specifically focusing on the transfer of data over wireless environment using inductive link

solutions. We summarise in detail the main design parameters for a wireless inductive coupling link for biodevices technology. In addition, these are demonstrated, described and concluded in figures, graphs and tables. Eventually, we try to clarify the applications of most biodevices working with wireless transfer data and the biomedical devices applications.

#### • Chapter 2:

This chapter focuses on analogue, digital wireless techniques for quadrature modulation, and coding the information signal. These are necessary as background for the digital modulator design in this thesis. We explore the basic principle of analogue and digital modulation categories, studying analysis mathematically and investigating different techniques. Methods which are commonly used for wireless applications may be suitable for biomedical implantable device purposes. The thesis also focuses on the appropriate modulation and demodulation techniques and the effect on power dissipation which includes the shared wireless received power with other parts in implant device, in a battery less system. Most of the common analogue and digital modulation schemes applied in biomedical devices, which are reported in many papers and journals, are reviewed, studied, and partially simulated. Summaries of the main modulation topologies appropriate for biomedical applications are the background of our work.

#### • Chapter 3:

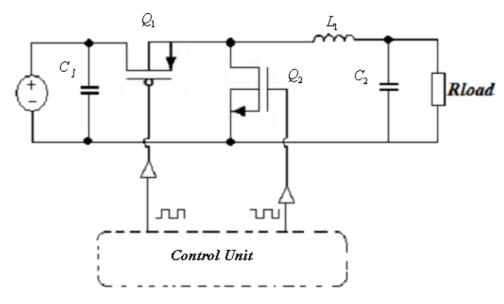

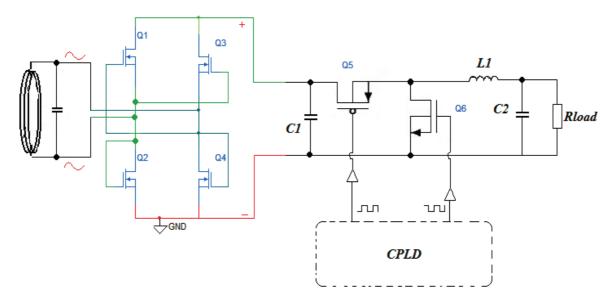

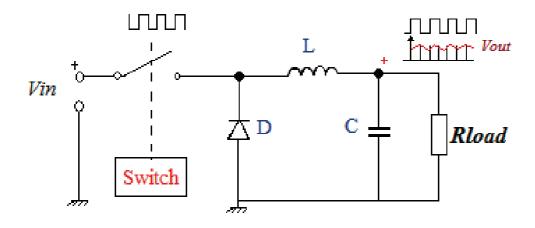

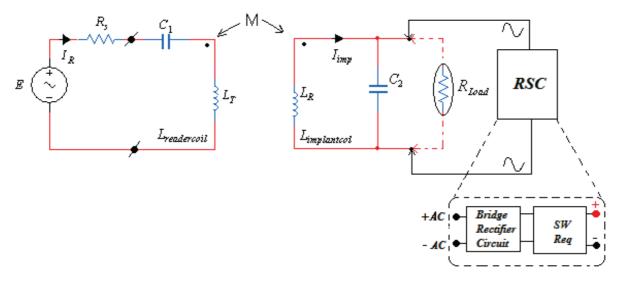

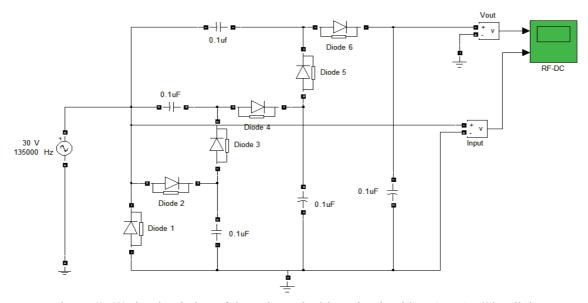

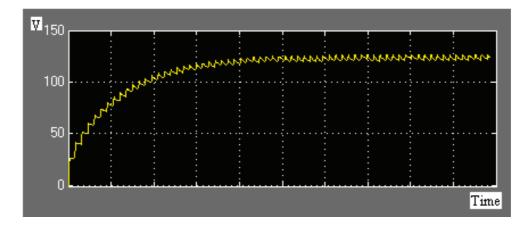

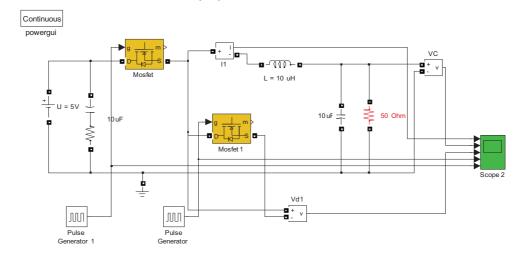

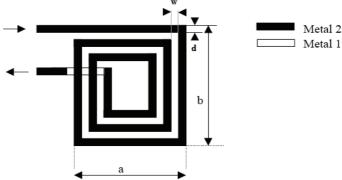

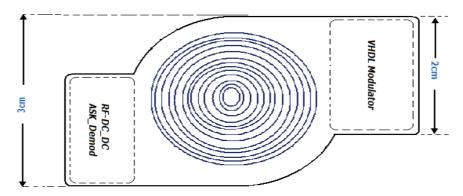

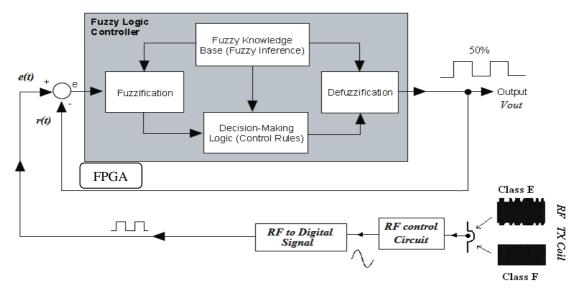

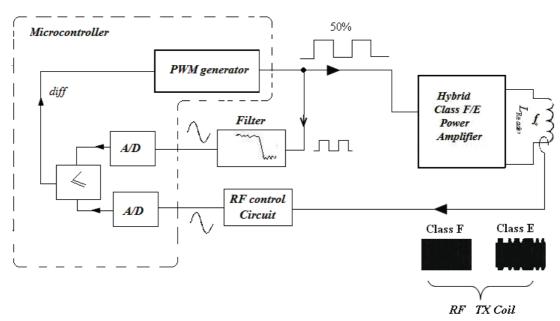

The third chapter presents the background of our work, the challenges, and tries to classify in four sections that can be specified as: first section: inductive coupling link. Obviously, this describes the background of the inductive coupling link and the principle of the magnetic coupling, covering the mathematical calculation for maximum transfer power, and optimum coupling coefficient between reader and implant, synthesis of power amplifier for transmission over the inductive link. The second part generally reviews the power amplifiers and emphasizes the power requirement to transfer the magnetic flux. That presents the new synthesized design for hybrid power amplifier transmitter link for class E and F power amplifiers. The third part covers the wireless power investigation to provide the essential DC voltage for implant devices inside the human body.

Finally, the last part demonstrates the wireless system that transmission of the high data rate over a wireless inductive coupling link.

#### • Chapter 4:

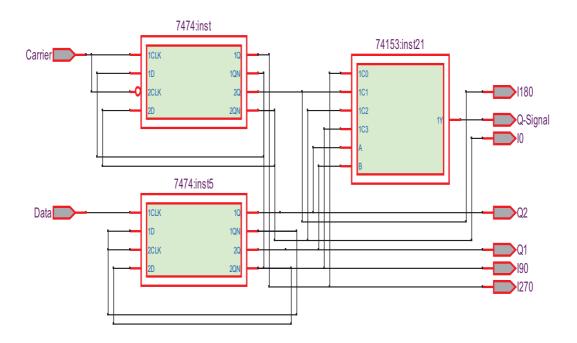

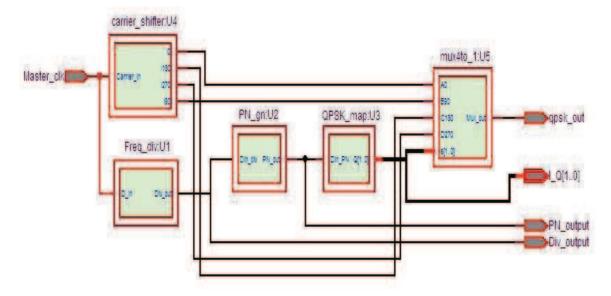

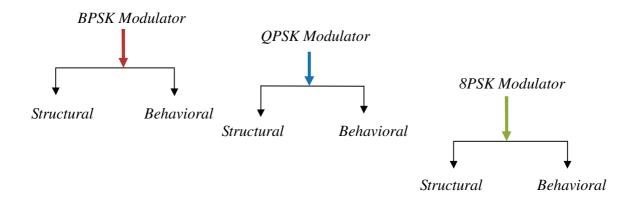

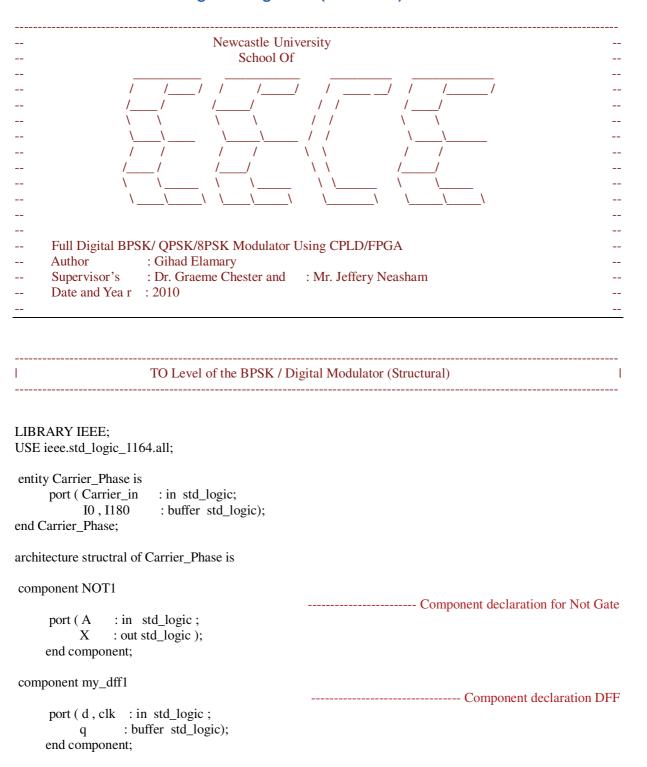

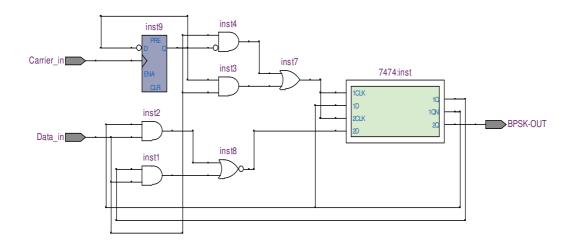

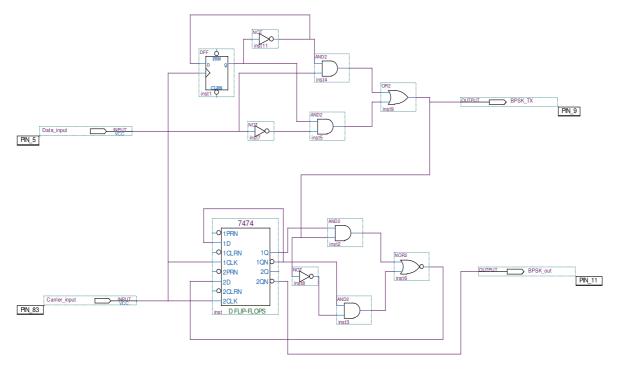

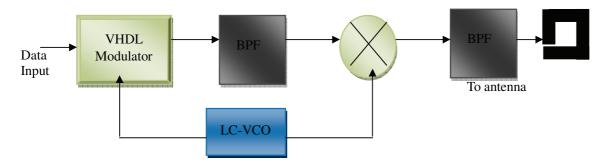

The fourth chapter demonstrates our new work approach, which describes the main work for the proposed modulator. The VHDL programming code is used to generate n-PSK digital signals. A new simple design for BPSK, QPSK and 8PSK modulators architecture modulators is applied for implantable telemetry applications. The modelled modulator has been designed and simulated and performance was evaluated by measurements. The design has low power consumption and size for biomedical applications. Furthermore, the advantages of this modulator are that it can be reconfigured and upgraded to enhance the data rate.

#### • Chapter 5:

The fifth chapter concludes the hardware work in the thesis describing the complete system design. Generally, the work was classified in two main parts: reader units and implant device. The evaluation lab measurements were performed for each part of project, concluding with the hardware and the measurement results discussion.

#### • Chapter 6:

The last chapter concludes and summarises the completed hardware work in this thesis: simulation, measurements and results discussion. A simulation-based comparison of several basic control algorithms has been carried out for controlling a different magnetic technique. This achieves good performance with auto-control and moderate complexity. Finally, the work described in this thesis can be improved and extended in many ways as mentioned in the suggestions for Future Work.

#### Publications

The following publications arising from this thesis work have resulted in posters and submitted publications.

#### A. Posters

- 1. Gihad Elamary, Graeme Chester, Jeff Neasham "**High Bandwidth Transcutaneous Wireless Telemetry**" The second event of the poster competition at North Umbria University (Supported by UK GRAND) UK on 03/05/2006.

- 2. Gihad Elamary, Graeme Chester, Jeff Neasham "Implantable telemetry devices" Newcastle University medical school poster competition on 05/05/2007

- 3. Gihad Elamary, Graeme Chester, Jeff Neasham"Implantable Electronics telemetry Devices" Graduate Poster Conferences Competition at Leeds University. (Supported by UK GRAND). 09/07/2007

#### **B.** Conference papers

- Gihad Elamary, Graeme Chester, Jeff Neasham "Experimental Digital BPSK Modulator Design with VHDL Code for Biodevices Applications". Porto-Portugal, 14/17. January. 2009. BIOSTEC Biodevices-2009. IEEE

- Gihad Elamary, Graeme Chester, Jeff Neasham "A Simple Digital VHDL QPSK Modulator Designed Using CPLD/FPGAs for Biomedical Devices Applications", London-UK 03/12/2009/ WCE 2009. ICEEE.

- 3. Gihad Elamary, Graeme Chester, Jeff Neasham "An Analysis of Wireless Inductive for Higher Data Rate Biomedical Telemetry Using a New VHDL n-PSK Modulator" 16th ICECS-2009-13th-16<sup>th</sup>/12/2009. IEEE

# Chapter

2

Literature Review for Analogue and Digital Modulations Applied in Biomedical Applications

## **Background and Literature Review**

### **Chapter II**

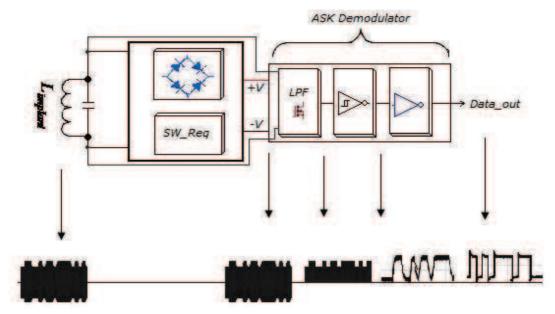

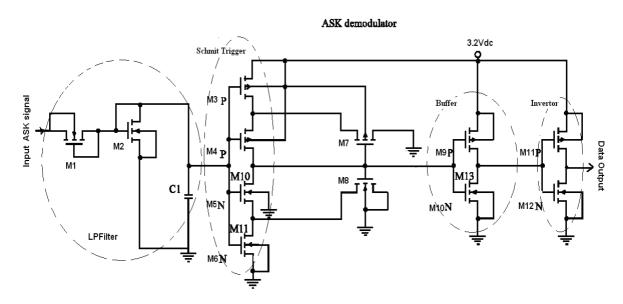

#### 2. Implantable Devices Modulation Schemes

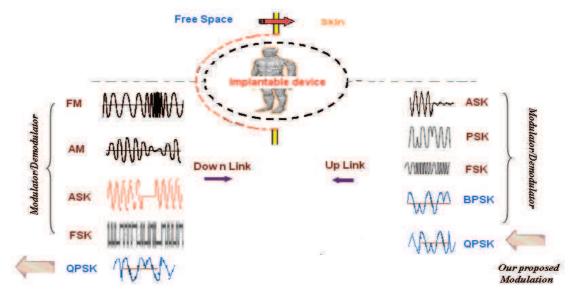

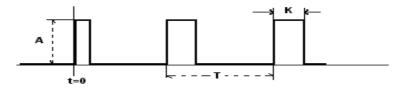

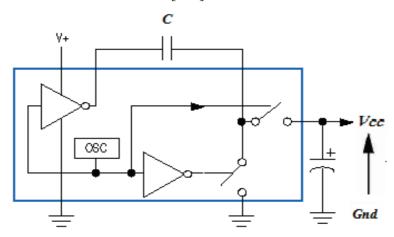

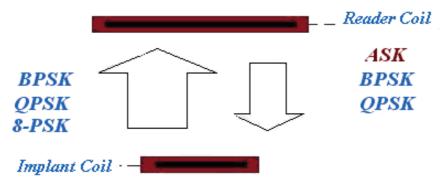

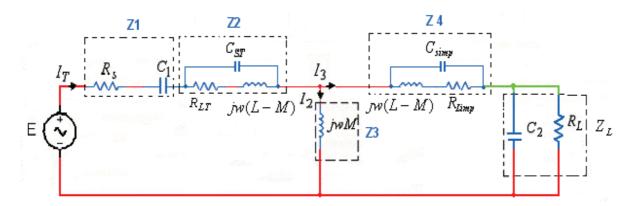

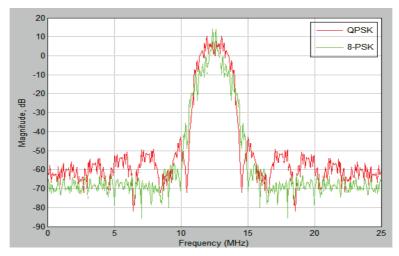

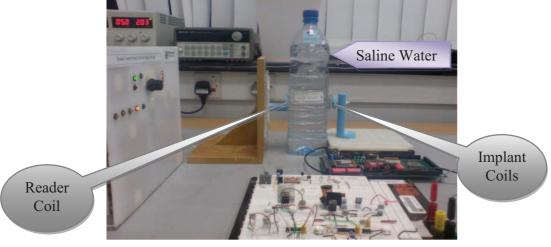

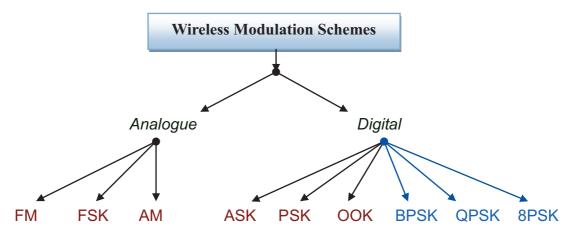

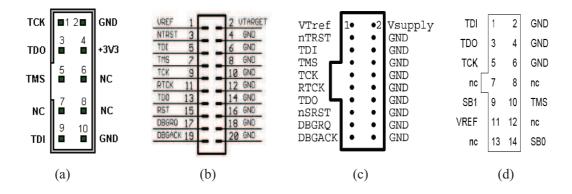

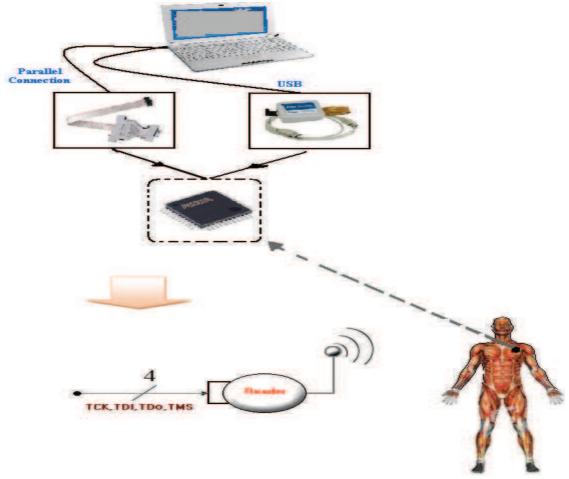

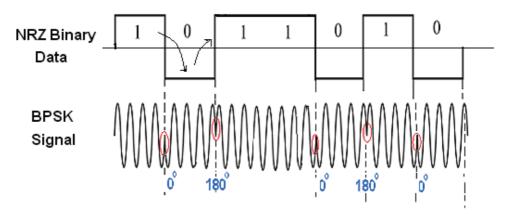

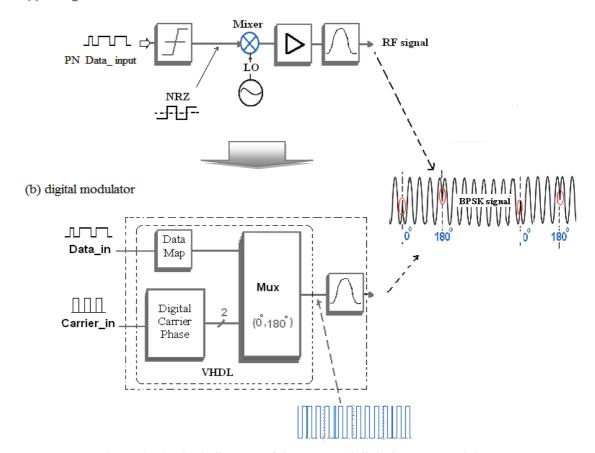

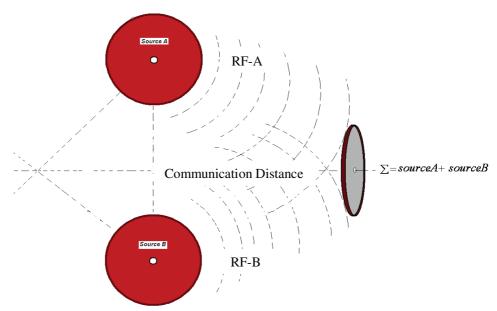

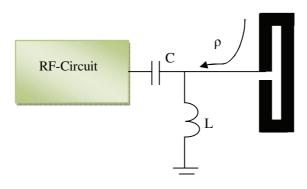

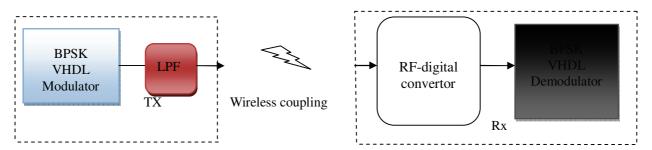

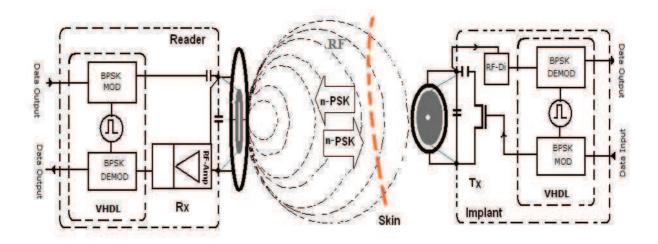

B a higher data rate and lower power consumption, augmented toward the wireless infrastructure environment. Principally, the gathered acquisition returned data from the body is defined as up-link, while the downlink provides the essential RF power signal and control information into the implant device. However, the modulator and demodulator are targeted for synthesis with low power consumption, and simplicity of circuits for implant devices [104] [136]. The magnetic field influence from a reader is modulated; subsequently a simple demodulator is use to detect the data at the implant part. The most common and simple modulator used is amplitude shift keying (ASK) [57] [65]. Typically, different RF schemes are applied for powering the implant downlink and back modulation from the body. Up-link techniques will be described in this chapter. In Figure (2.0), we demonstrate the most common analogue and digital modulation techniques applied for implantable communication that will be compared to our proposed VHDL-QPSK modulator design discussed in chapter four in detail.

Figure (2.0) Modulation techniques applied to most biomedical devices

#### 2.1 Analogue Modulation Background

#### 2.1.1 Introduction To Analogue Modulation

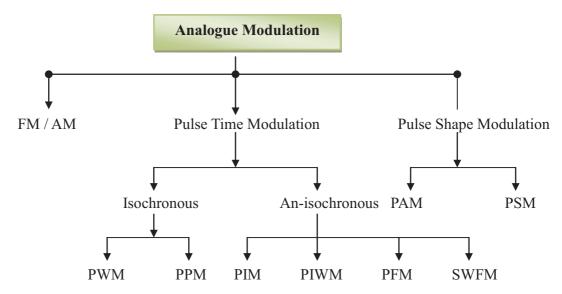

Analogue modulation schemes are generally limited in biomedical applications. There are few reported papers implementing the analogue modulation such as amplitude modulation (AM), frequency modulation (FM) and pulse width modulation [115], [125]. The analogue schemes can be classified into two categories; the pulse shape modulation (PSM) and the pulse time modulation (PTM). The classification hierarchy of the most common analogue modulation formats applied in telecommunication coding is described in Figure (2.1). One of the simplest applications of this format is pulse amplitude modulation (PAM), in this technique the amplitude of individual, regularly spaced pulses is varied in accordance with the amplitude of modulating signal. Such a format is inefficient with bandwidth, and does not deliver the signal to noise ratio (S/N). On other hand, the demodulation of PWM is complicated at implant device applications [137] [184]. Practically, the ASK modulation is more suitable than FM and AM at implant device [190], which uses a simple demodulator for reproducing the data. The second goal for designing the ASK demodulator is to reduce the effect on the implant device performance since it is sharing the same source as wireless power [136]. Obviously, the conventional analogue modulation is not appropriate for the most of biomedical devices as large circuits are needed and this causes high power dissipation, which is the main disadvantage of this scheme.

Figure (2.1) demonstration of the hierarchy of analogue modulations

#### 2.2 Background of Principle Digital Modulations

#### 2.2.1 Introduction to digital modulation

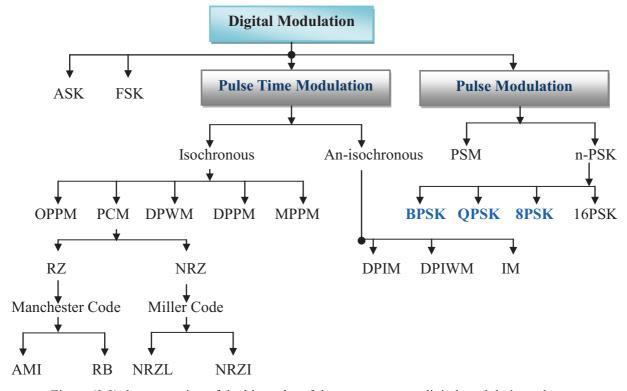

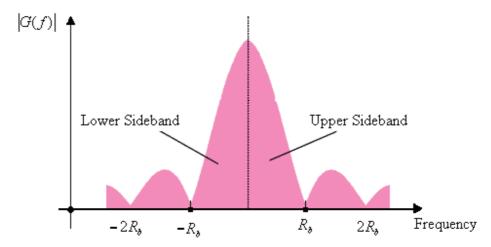

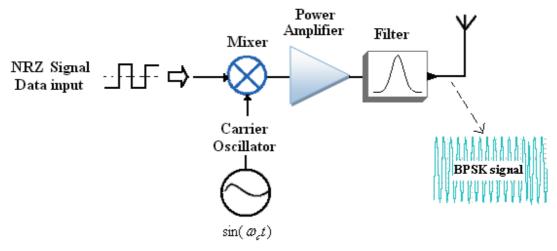

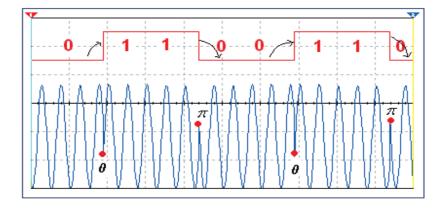

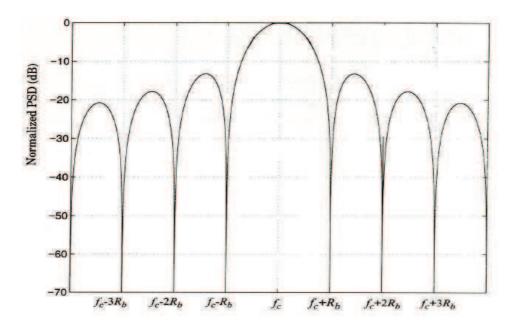

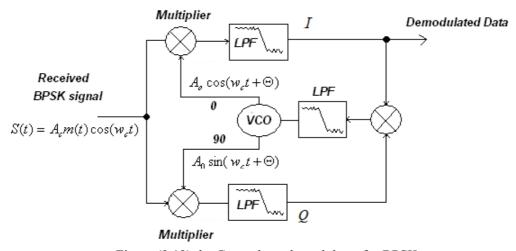

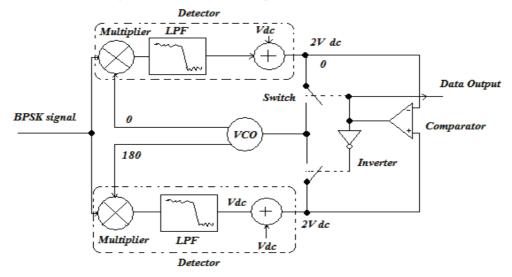

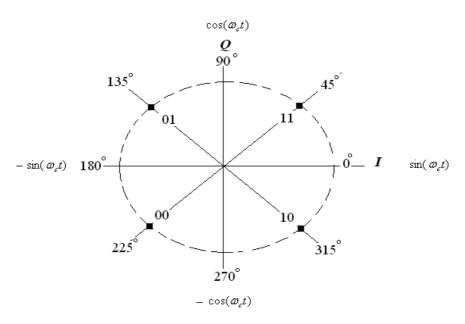

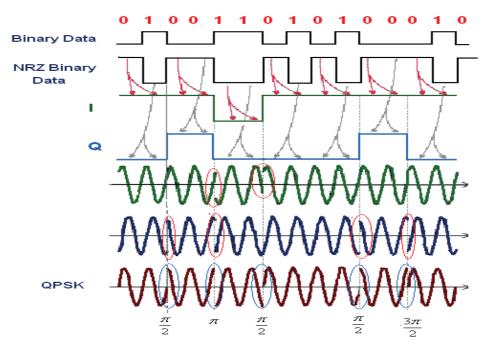

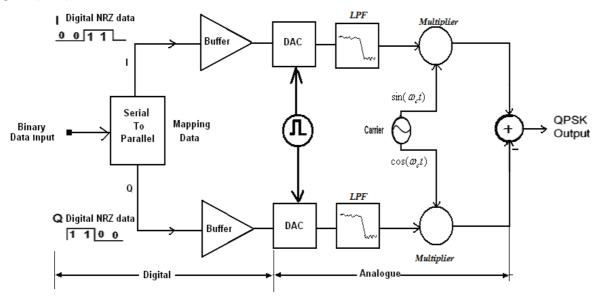

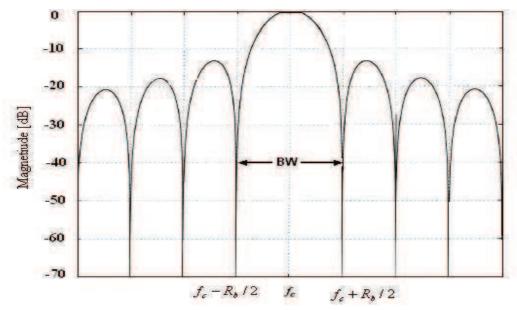

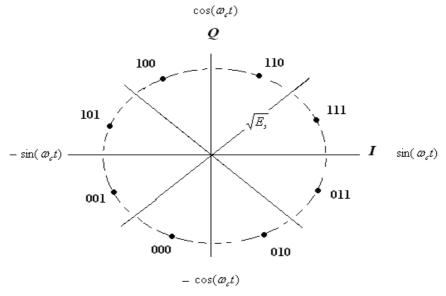

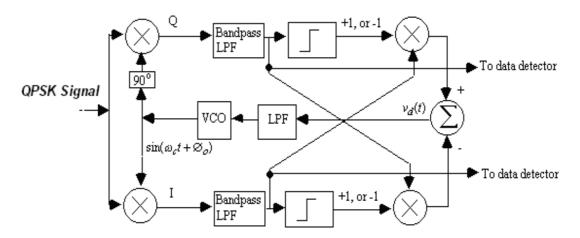

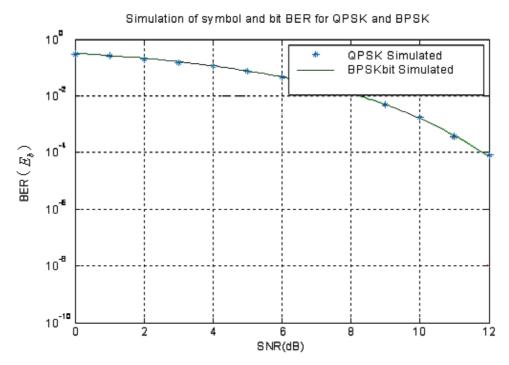

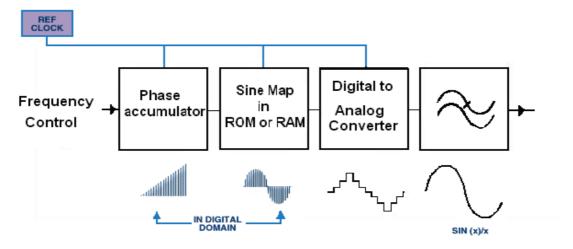

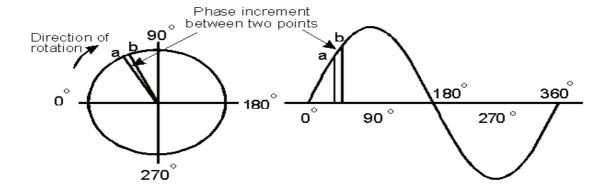

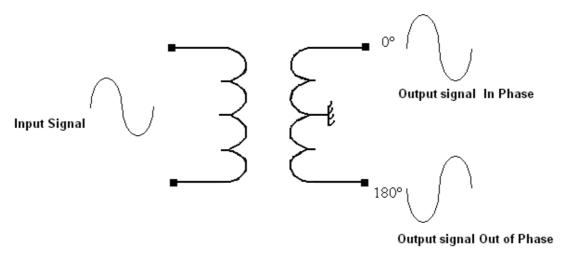

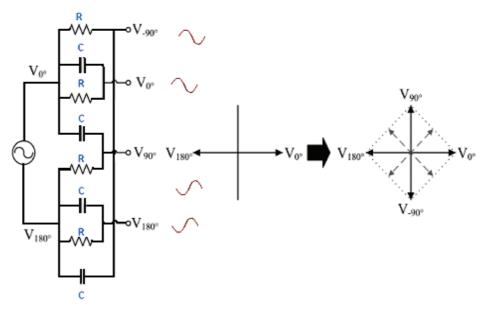

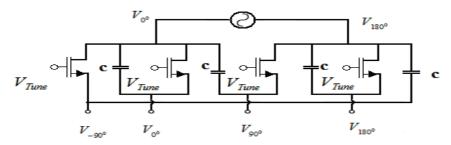

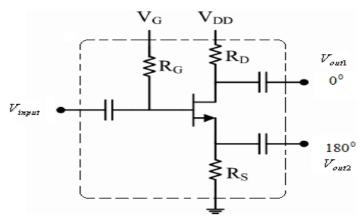

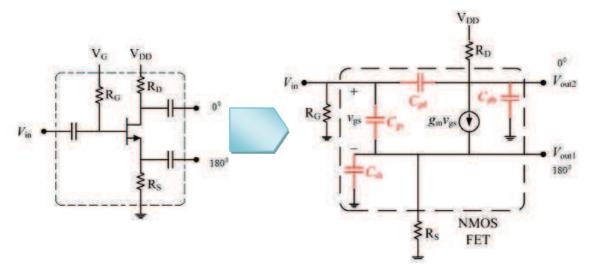

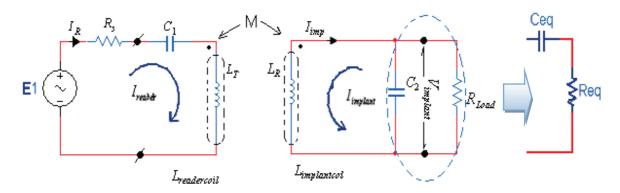

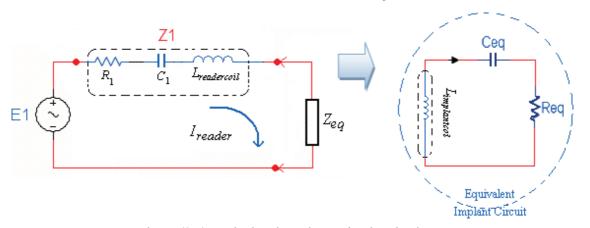

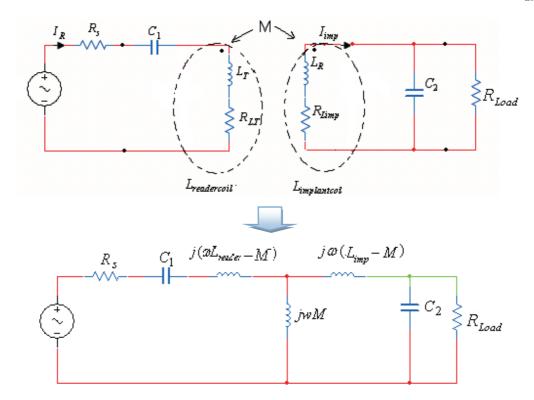

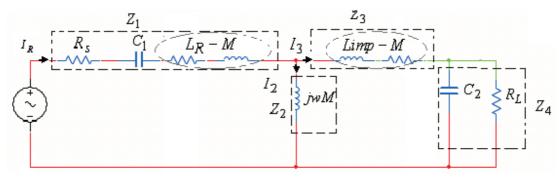

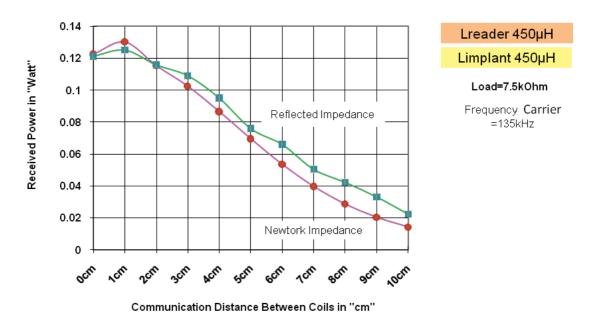

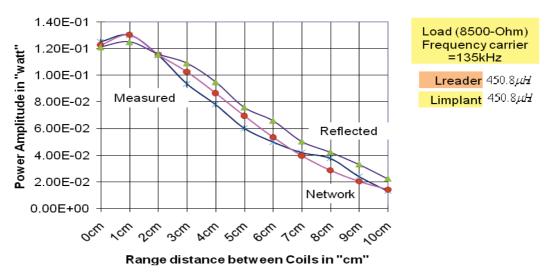

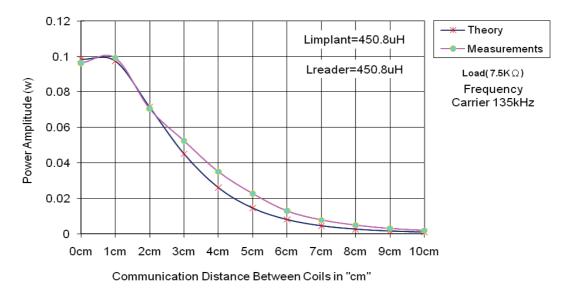

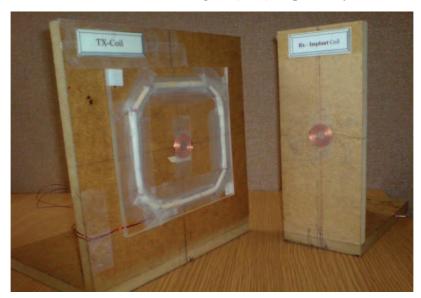

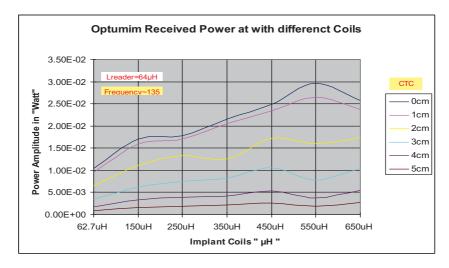

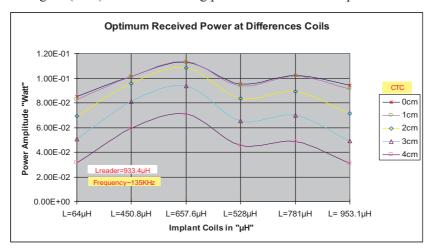

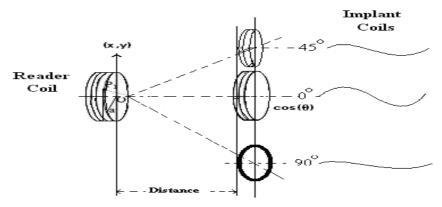

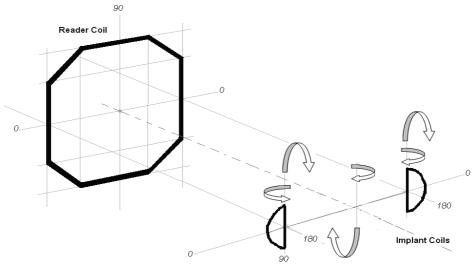

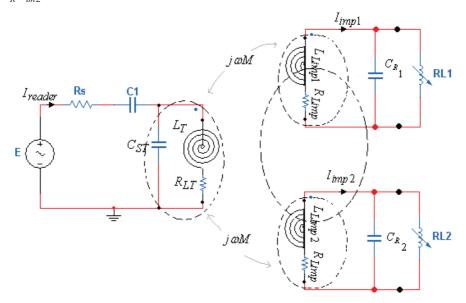

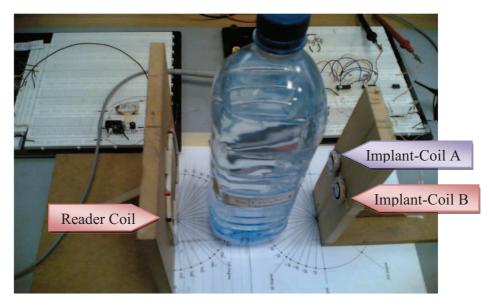

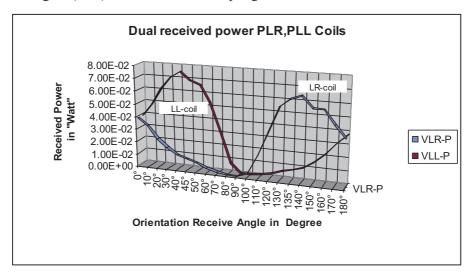

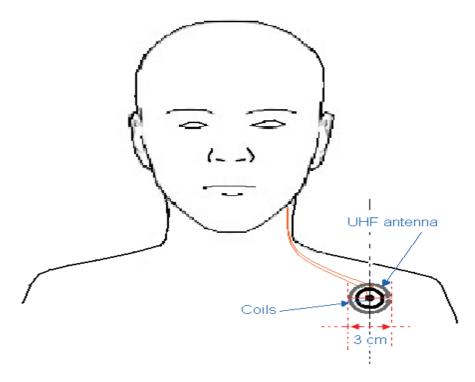

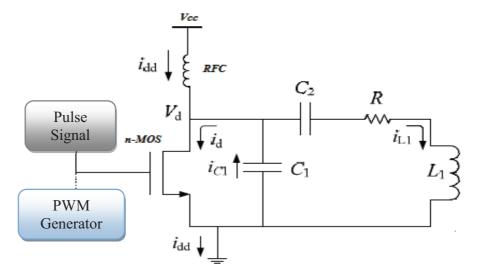

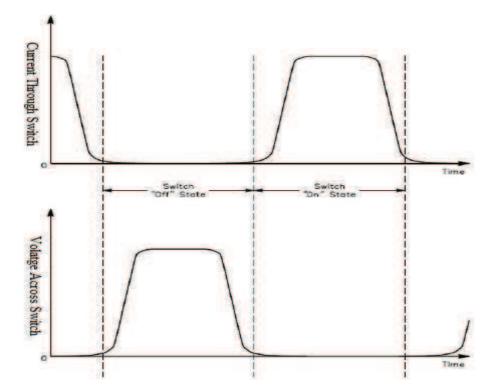

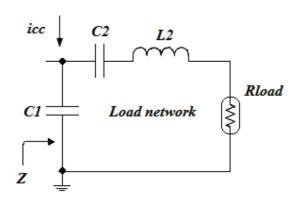

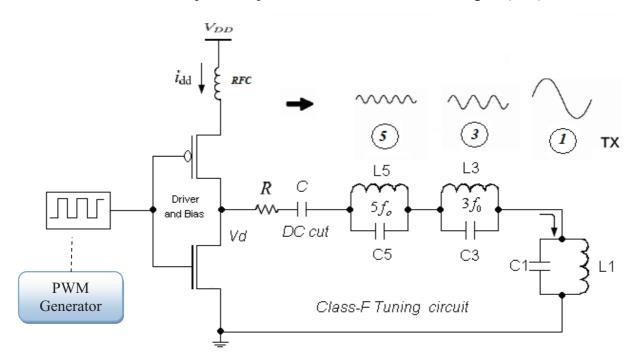

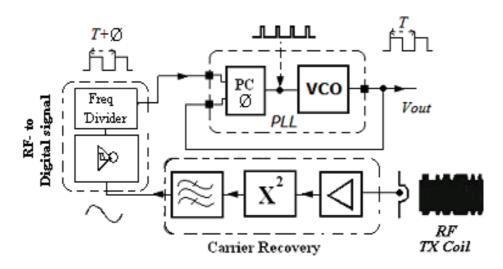

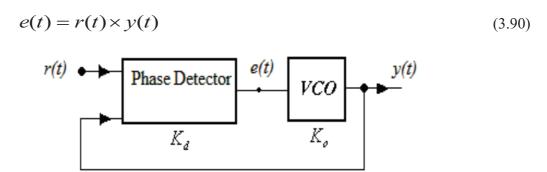

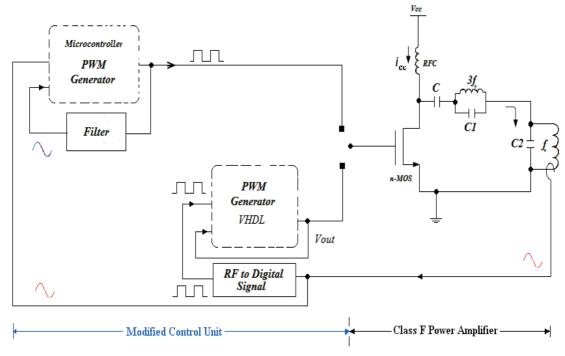

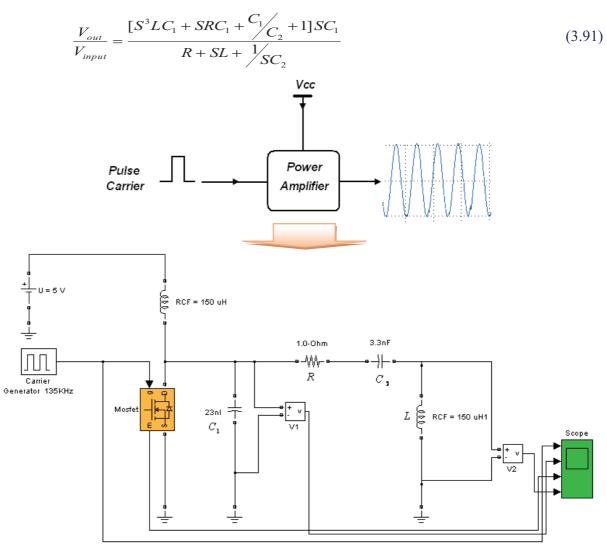

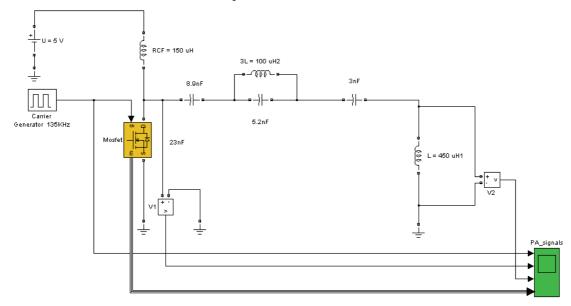

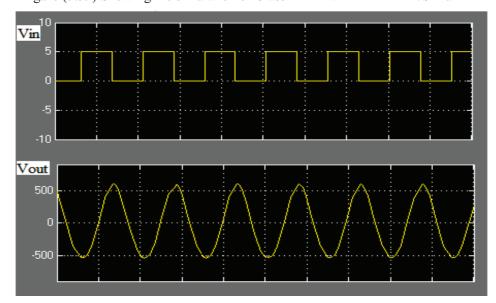

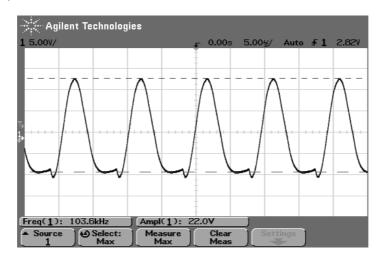

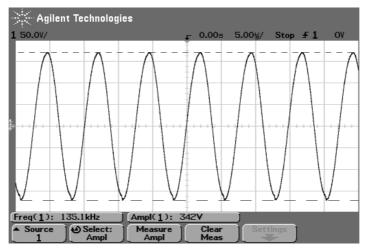

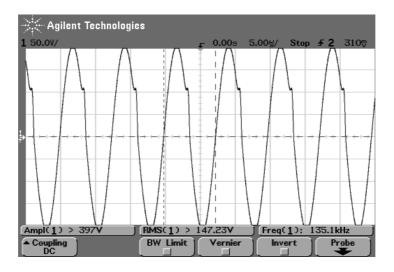

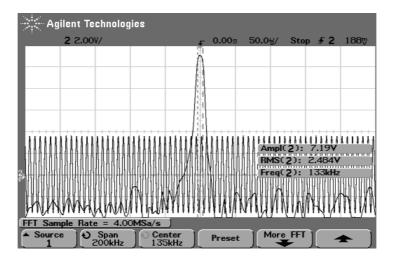

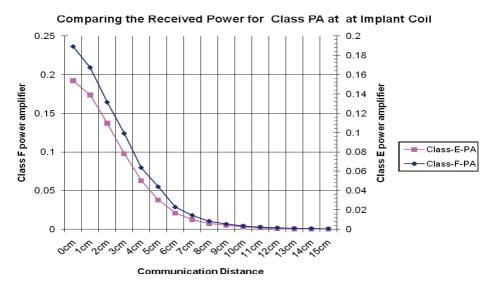

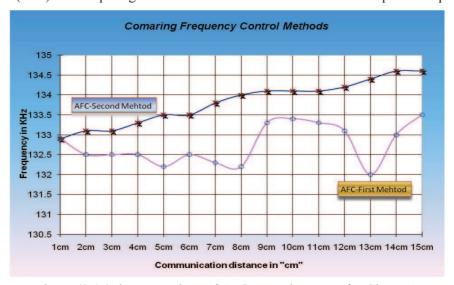

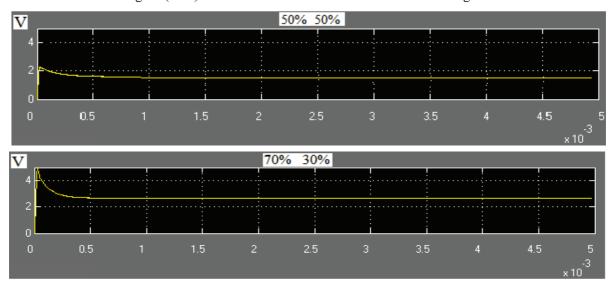

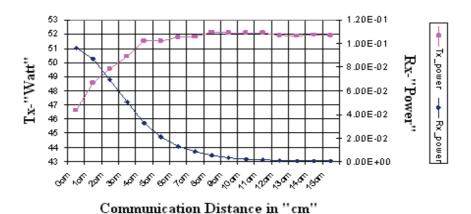

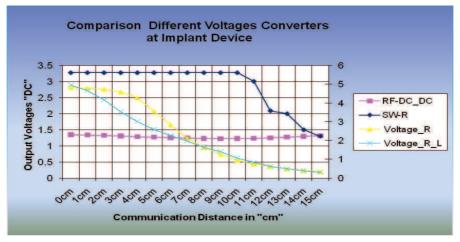

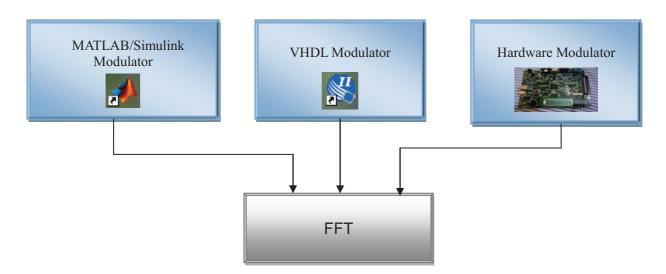

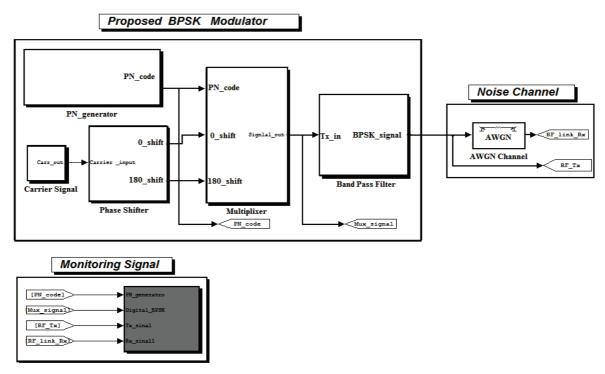

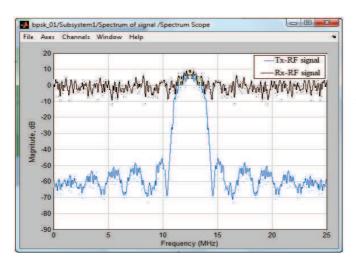

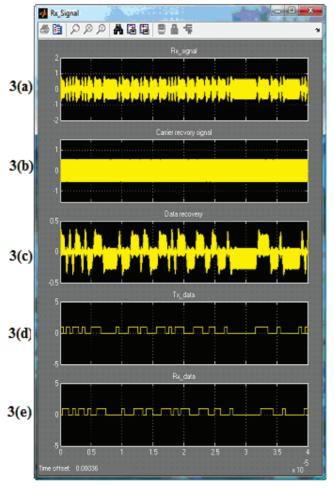

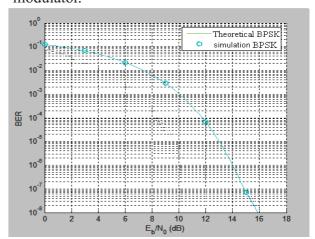

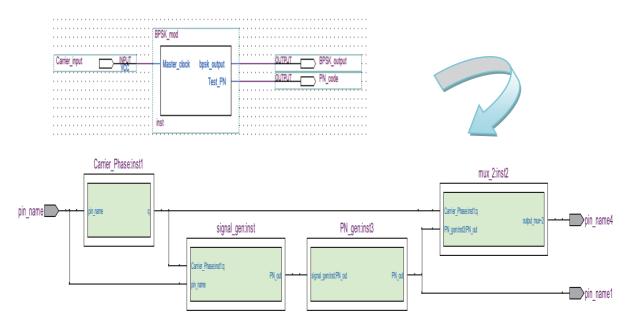

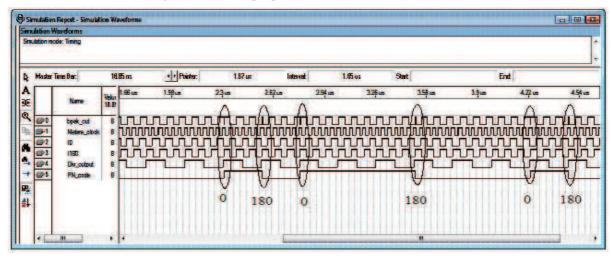

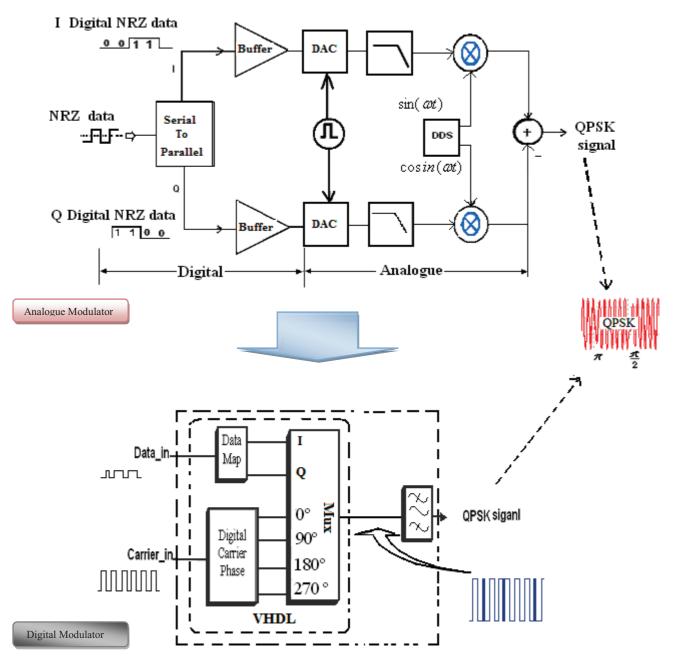

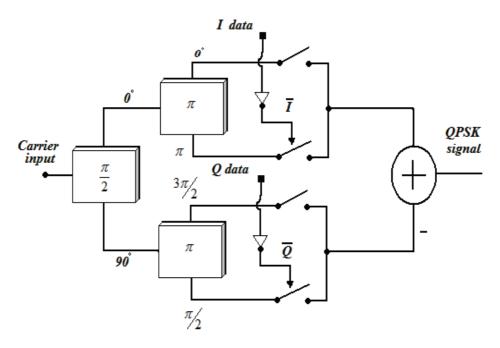

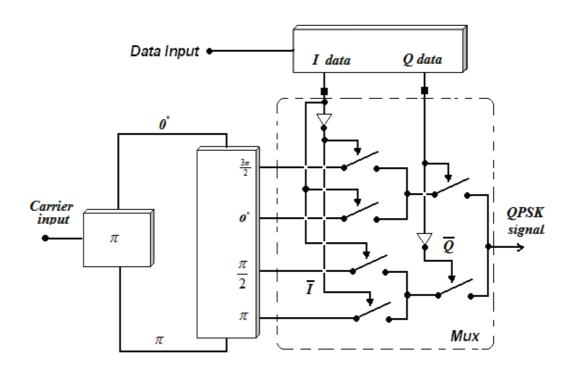

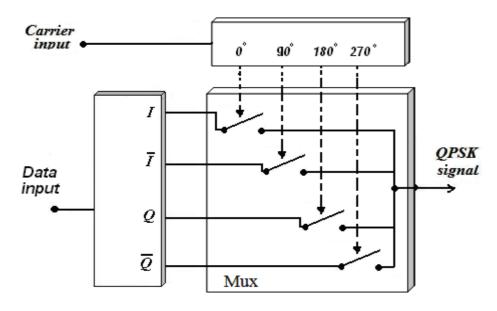

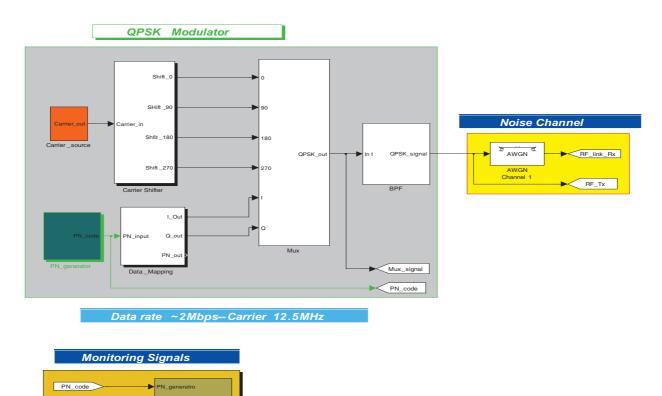

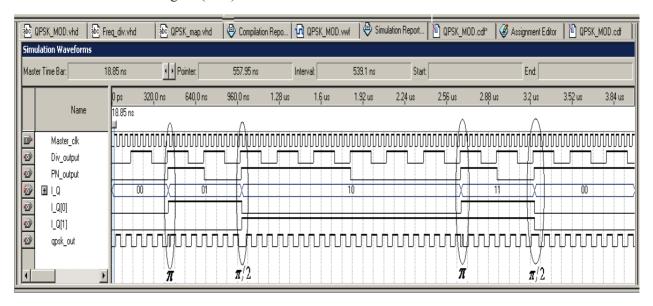

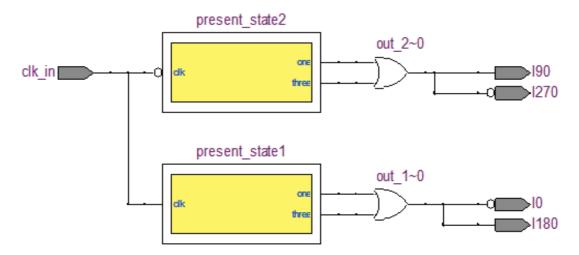

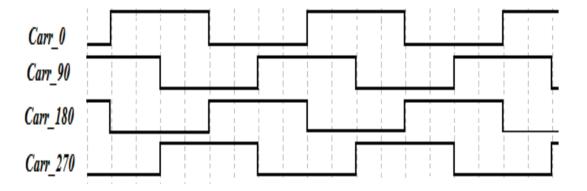

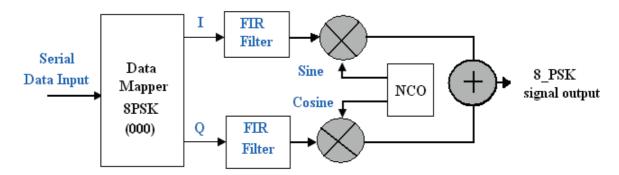

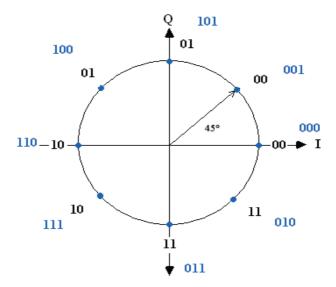

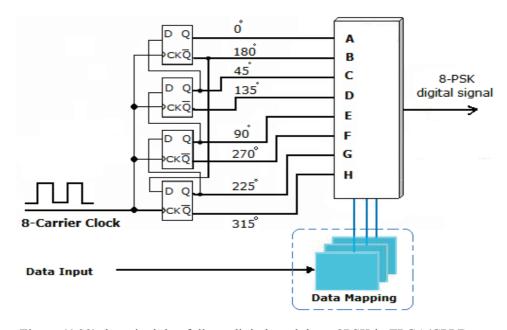

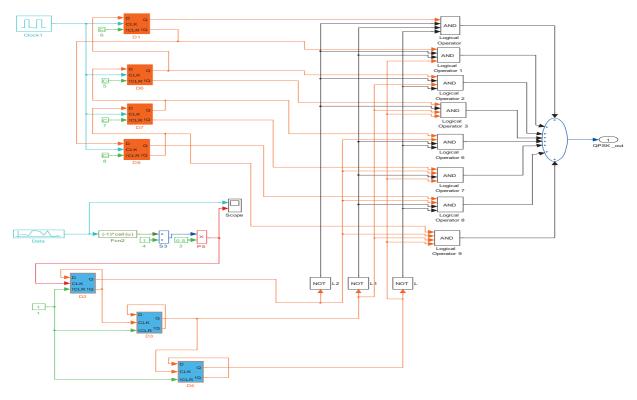

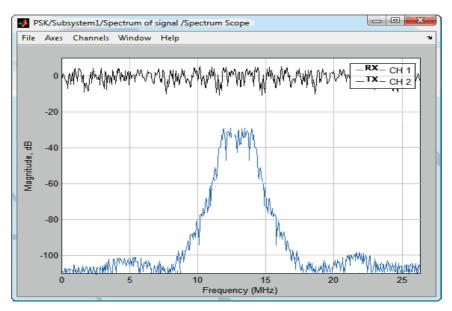

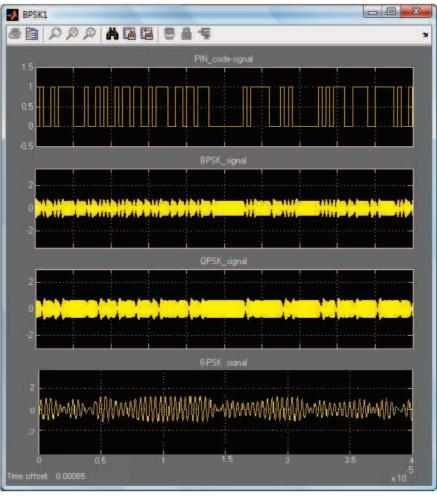

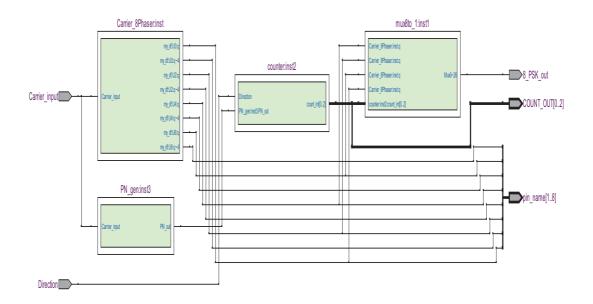

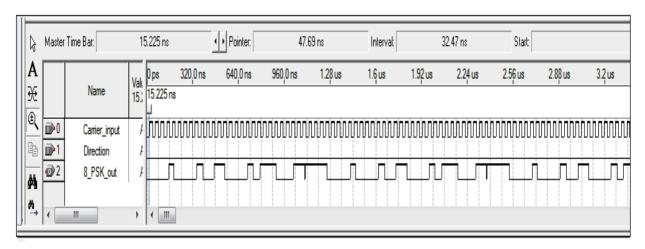

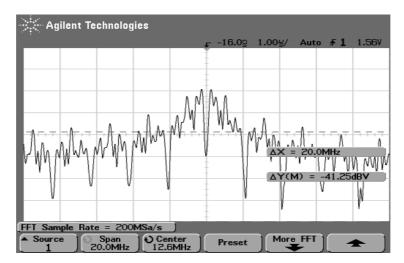

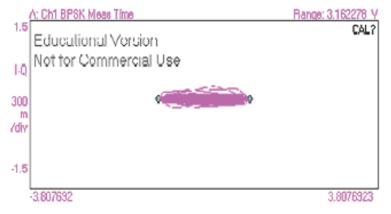

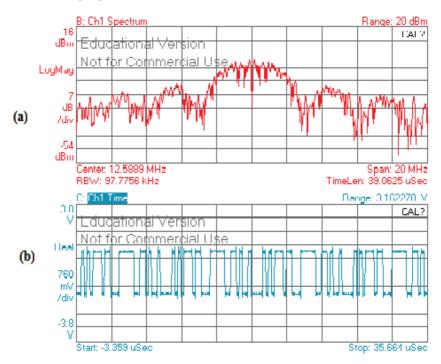

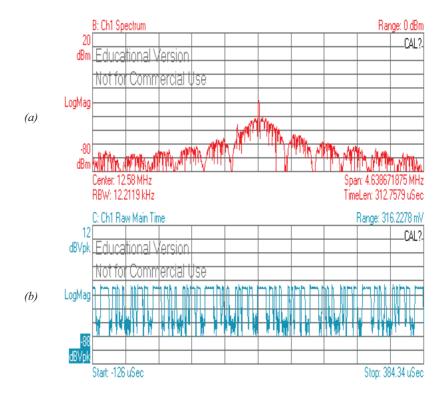

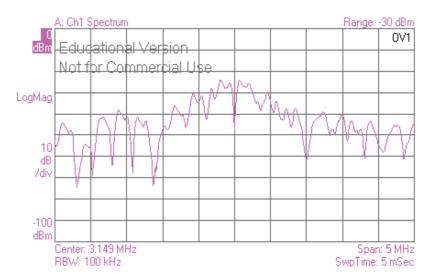

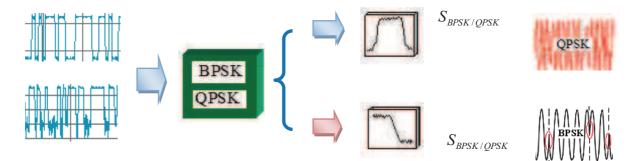

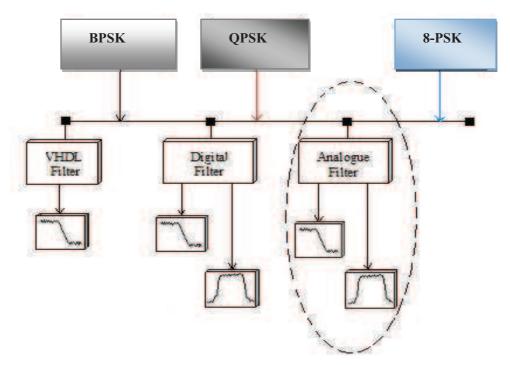

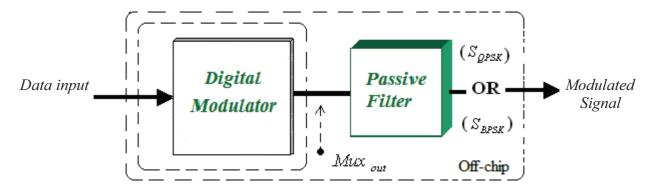

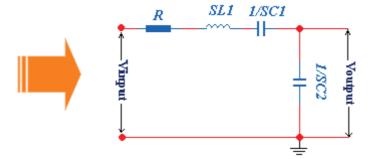

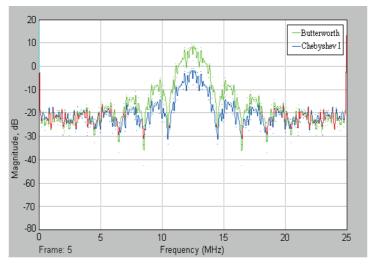

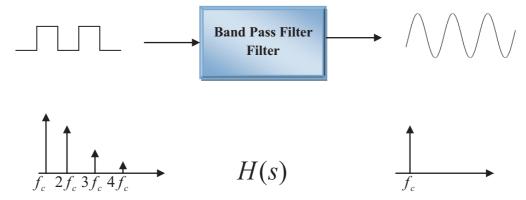

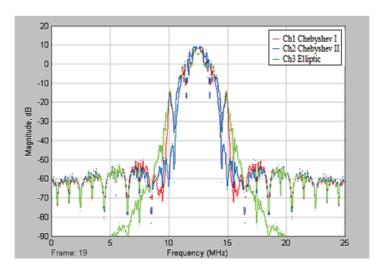

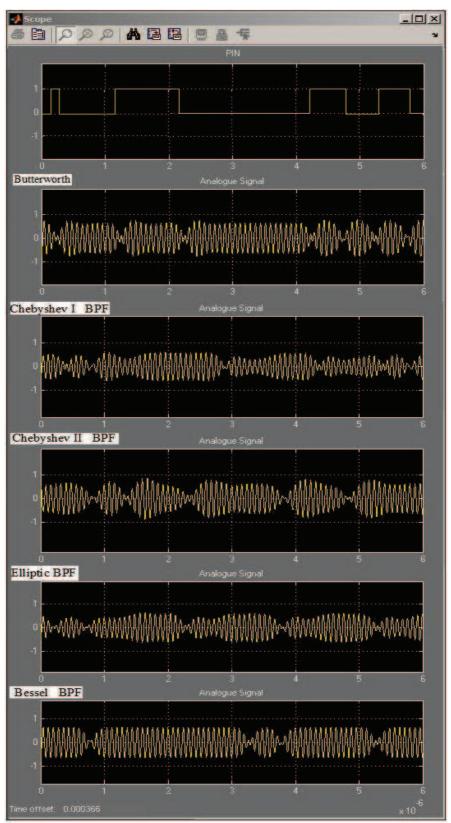

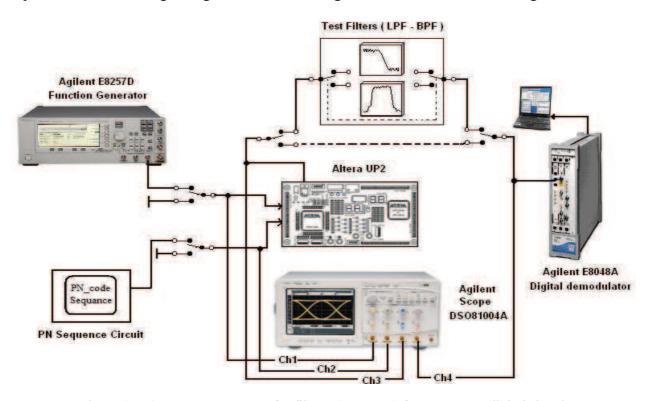

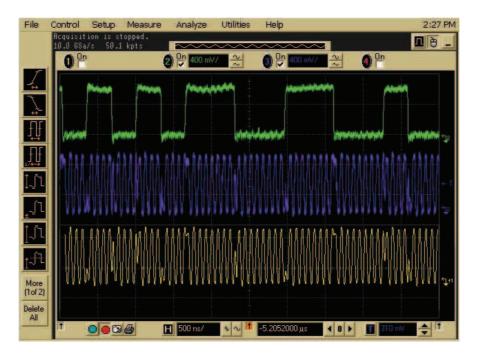

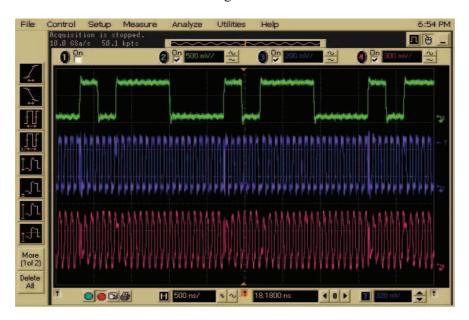

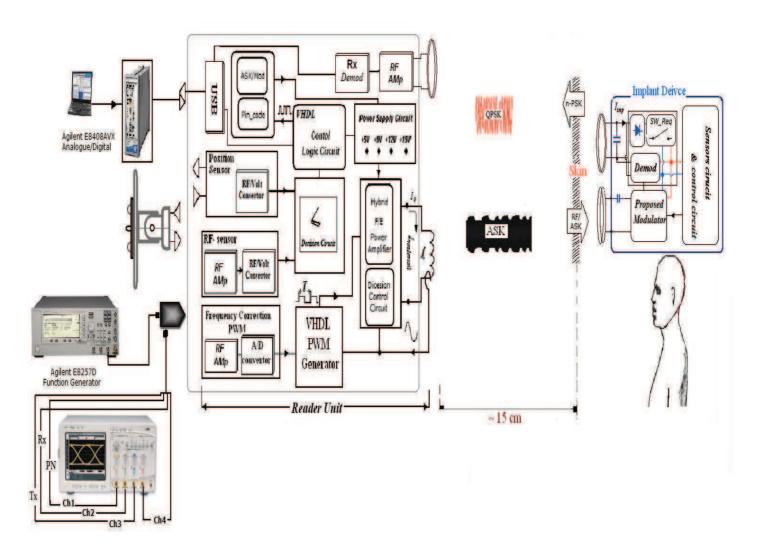

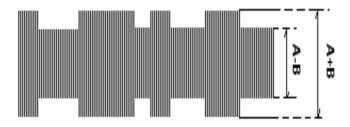

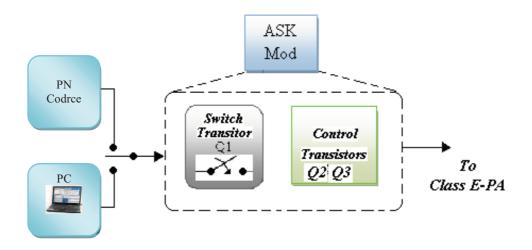

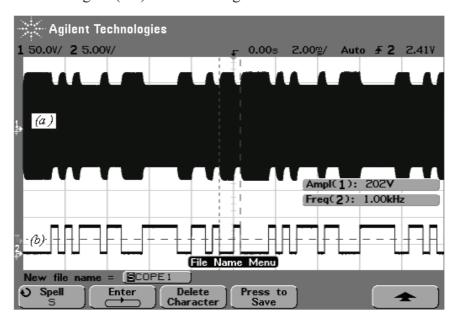

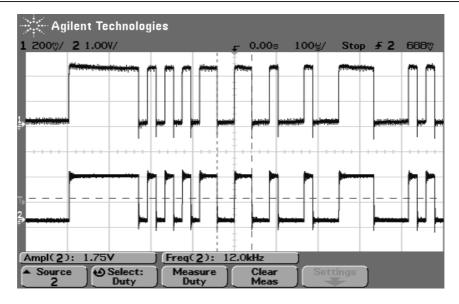

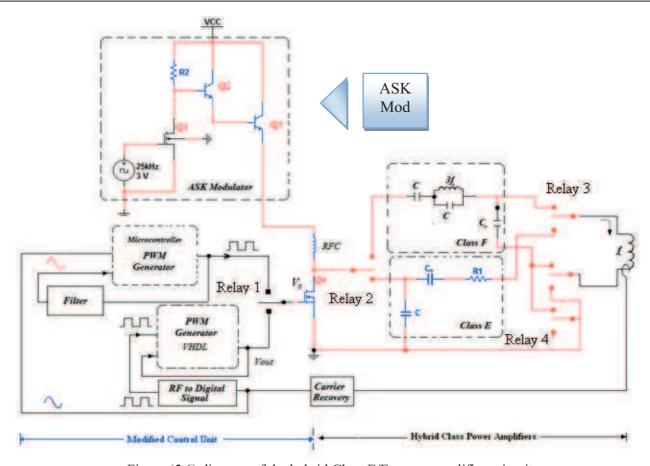

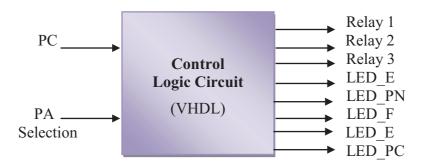

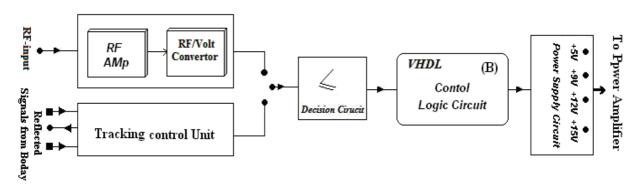

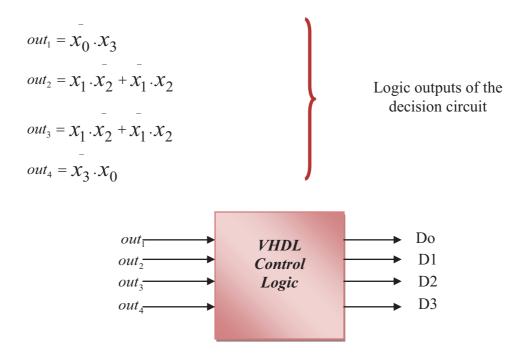

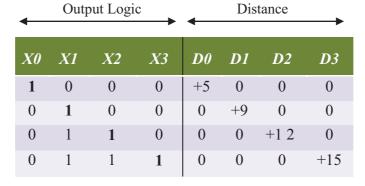

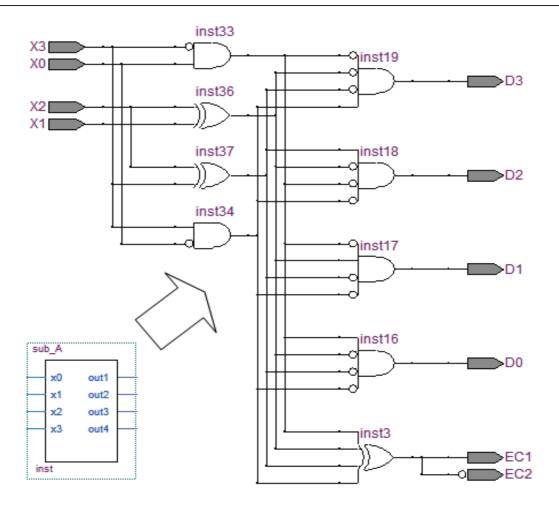

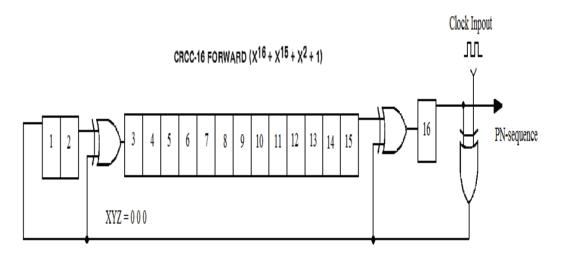

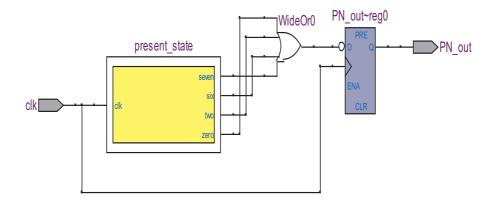

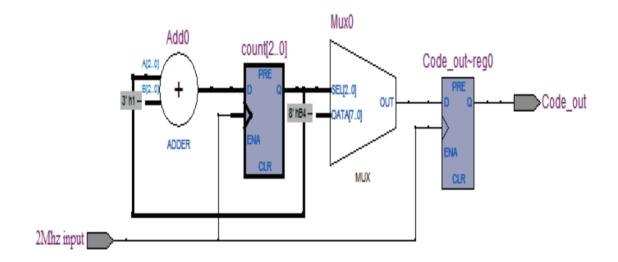

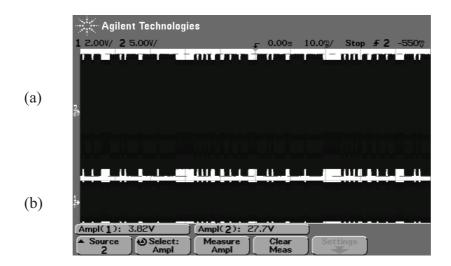

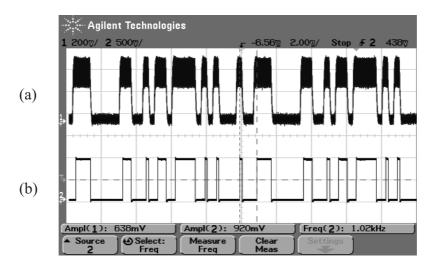

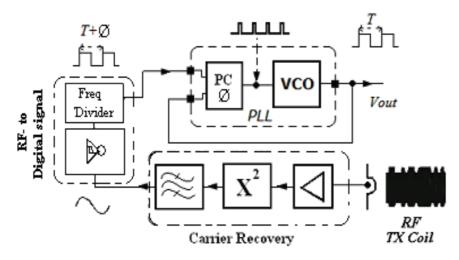

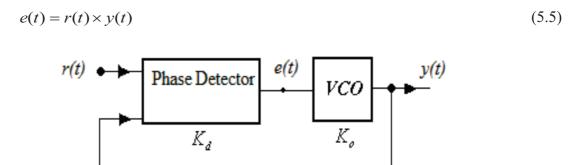

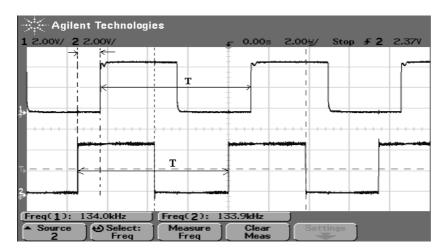

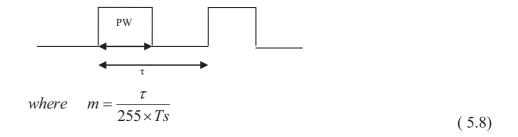

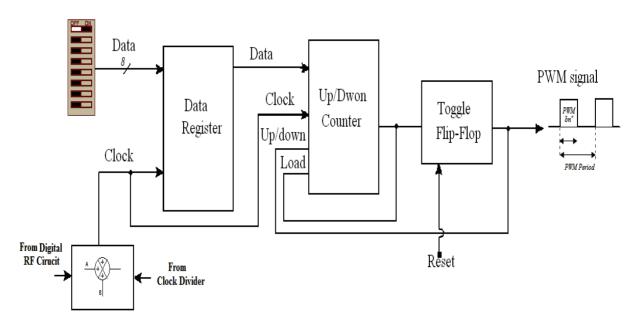

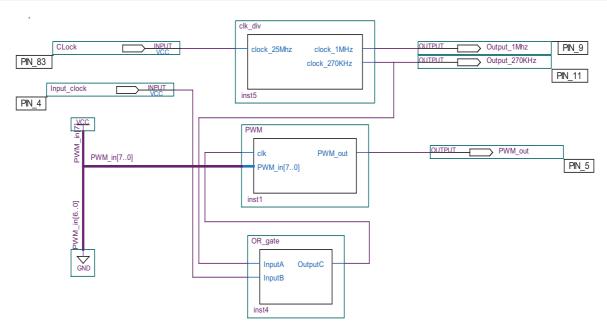

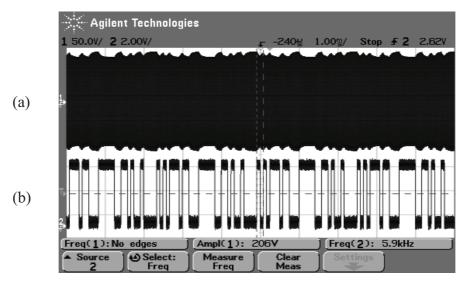

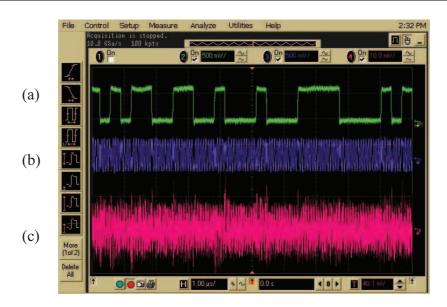

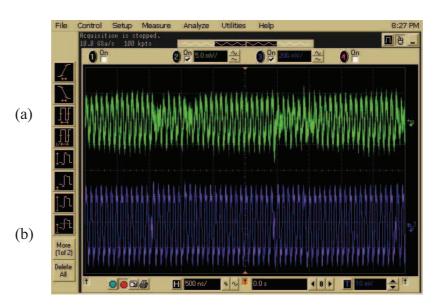

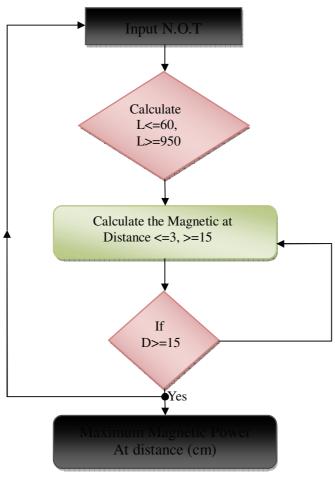

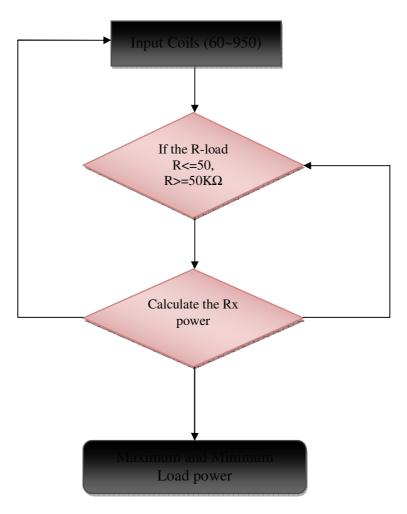

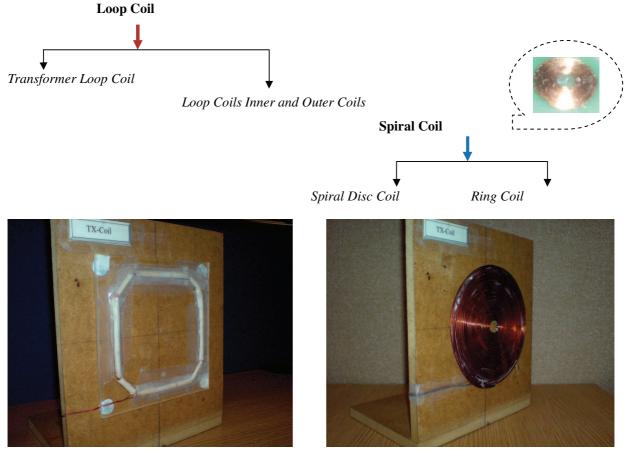

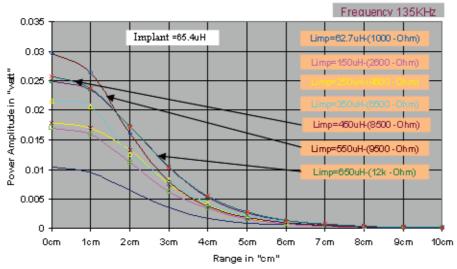

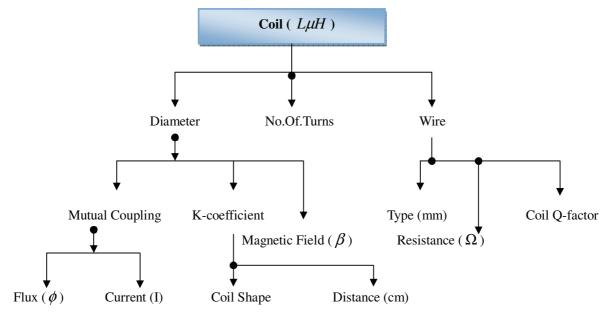

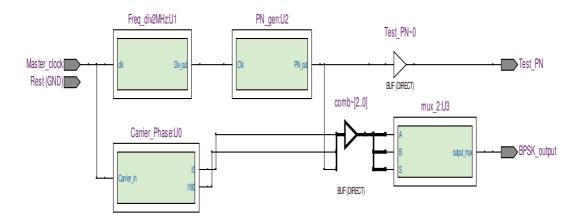

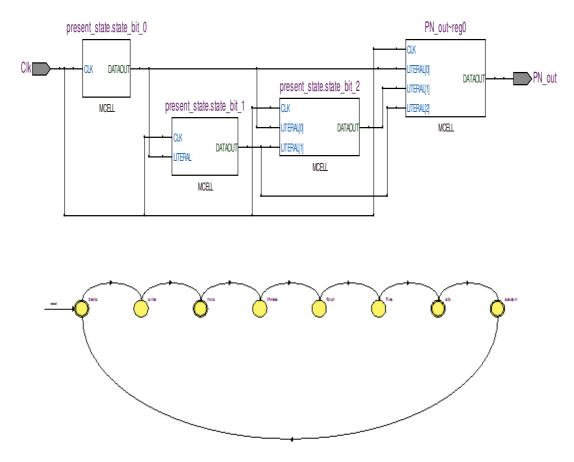

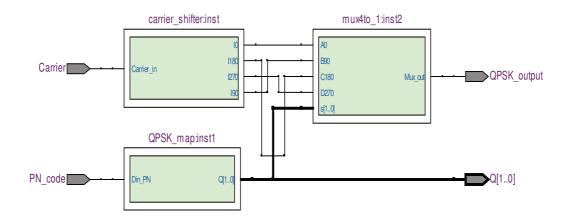

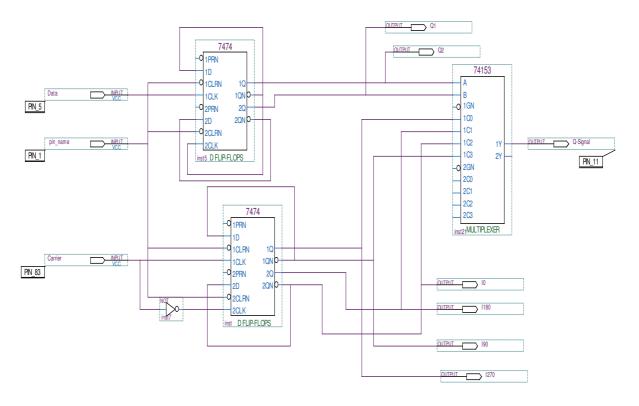

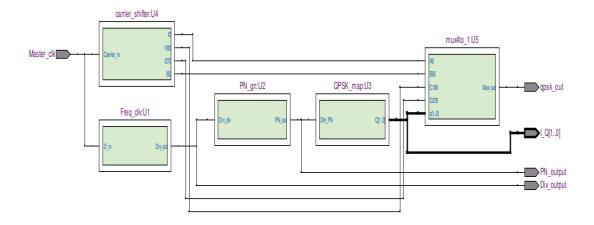

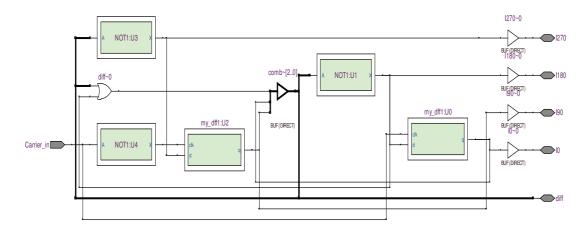

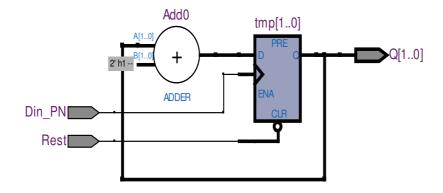

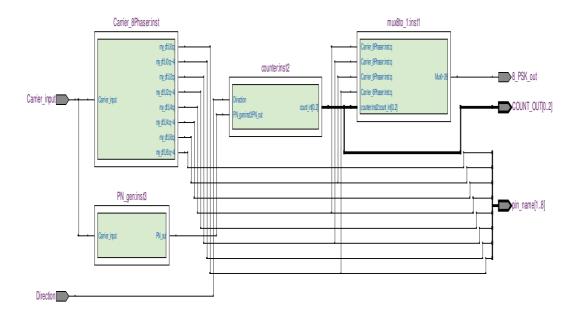

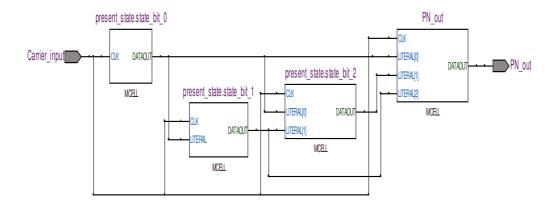

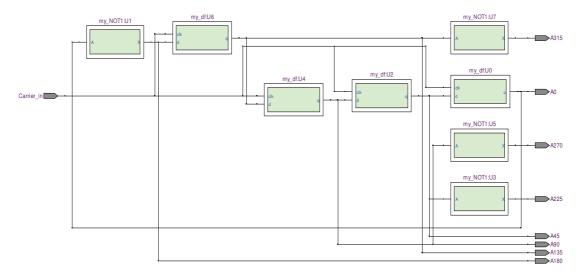

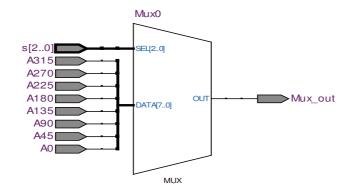

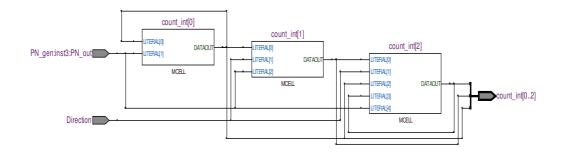

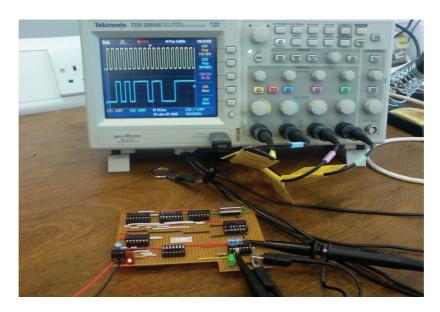

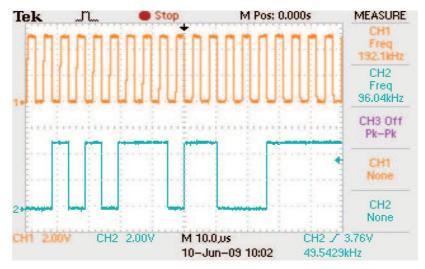

This section explains briefly the digital modulation techniques applied for biomedical devices. Generally, the transmissions of digital information are increasing at a rapid rate, which are used in several biomedical applications, to communicate between implant and reader. The most common modulation schemes are ASK, PSK, BPSK and QPSK employed in near field communication or satellite telemetry, RFID and commercial smart cards [1] [184]. Typically, there are other digital modulators, which not discussed in this thesis [9] [27] [216]. However, we describe in Figure (2.2) the classification hierarchy of the most common digital modulation formats [199], and investigate most of the common digital modulations, which are appropriate for medical application in this work. We are considering the simple implementation circuit, in reader unit or at implant devices, and these are analyzed and simulated where used to design a digital modulator that is suitable for medical purposes. However, in this thesis we choose pulse shape modulation techniques and selected the QPSK modulation as more appropriate to implement within digital hardware.