### A methodology for speeding up loop kernels by exploiting the software information and the memory architecture

KELEFOURAS, Vasileios <a href="http://orcid.org/0000-0001-9591-913X">http://orcid.org/0000-0001-9591-913X</a>, KRITIKAKOU, Angeliki and GOUTIS, Costas

Available from Sheffield Hallam University Research Archive (SHURA) at:

http://shura.shu.ac.uk/18360/

This document is the author deposited version. You are advised to consult the publisher's version if you wish to cite from it.

#### **Published version**

KELEFOURAS, Vasileios, KRITIKAKOU, Angeliki and GOUTIS, Costas (2015). A methodology for speeding up loop kernels by exploiting the software information and the memory architecture. Computer Languages Systems and Structures, 41, 21-41.

#### Copyright and re-use policy

See http://shura.shu.ac.uk/information.html

## A methodology for speeding up loop kernels by exploiting the software information and the memory architecture

Vasilios Kelefouras<sup>a</sup>, Angeliki Kritikakou<sup>b</sup>, Costas Goutis<sup>a</sup>

<sup>a</sup>Department of Electrical and Computer Engineering, University of Patras (kelefouras@ece.upatras.gr) Education and Research Department in Computer Science and Electrical Engineer

<sup>b</sup>Education and Research Department in Computer Science and Electrical Engineering, University of Rennes 1

#### Abstract

It is well-known that today's compilers and state of the art libraries have three major drawbacks. First, the compiler sub-problems are optimized separately; this is not efficient because the separate sub-problems optimization gives a different schedule for each sub-problem and these schedules cannot coexist as the refining of one, causes the degradation of another. Second, they take into account only part of the specific algorithms information. Third, they take into account only a few hardware architecture parameters. These approaches cannot give an optimumal solution.

In this paper, a new methodology/pre-compiler is introduced, which speeds up loop kernels, by overcoming the above problems. This methodology solves four of the major scheduling sub-problems, together as one problem and not separately; these are the sub-problems of finding the schedules with the minimum numbers of i) L1 data cache accesses, ii) L2 data cache accesses, iii) main memory data accesses, iv) addressing instructions. First, the exploration space (possible solutions) is found according to the algorithm's information, e.g. array subscripts. Then, the exploration space is decreased by orders of magnitude, by applying constraint propagation to the software and hardware parameters.

We take the C-code and the memory architecture parameters as input and we automatically produce a new faster C-code; this code cannot be obtained by applying the existing compiler transformations to the original code. The proposed methodology has been evaluated for five well-known algorithms in both general and embedded processors; it is compared with gcc and clang

Preprint submitted to Computer Languages, Systems and Structures January 30, 2015

compilers and also with iterative compilation.

*Keywords:* Data reuse, register allocation, optimization, memory hierarchy, loop tiling, data locality, Diophantine equations

#### 1. Introduction

Regarding data dominant applications (for example linear algebra, image, signal and video processing algorithms), the major performance critical parameters are i) the number of main memory accesses, ii) the number of L3/L2 cache accesses, iii) the number of L1 data cache accesses and iv) the number of executed instructions (we assume that the number of the algorithm instructions cannot be reduced and thus we reduce only the number of addressing instructions). The above compilation/scheduling sub-problems are interdependent and thus they cannot be optimized separately; actually, the refining of one sub-problem causes the degradation of another, e.g. a decrease of the number of L2 data cache accesses will consequently increase the number of L1 data cache accesses. Researchers try to solve this problem by using iterative compilation techniques.

Iterative compilation has five major drawbacks, i) there are memory efficient schedules which cannot be produced by applying the existing compiler transformations, ii) iterative compilation does not use all the existing transformations, including all the different transformation parameters, e.g. unroll factor values and tile sizes, because in this case compilation will last for years, iii) only one level of tiling is applied, which is not efficient, iv) register allocation is applied without taking into account the data reuse; this means that the arrays references are assigned into registers, without taking into account that some are accessed a lot and others do not, v) the data array layouts are not taken into account; we will show that when tiling to multidimensional arrays is applied, the data array layouts must change. These drawbacks are overcome by the proposed methodology.

The proposed methodology finds the exploration space (all possible solutions), neither by applying compiler transformations nor by utilizing the above sub-problems separately. Instead, the exploration space is produced by exploiting the algorithm's information; we create mathematical equations and inequalities, according to the array subscripts, the loops iterators and the loops bounds. These equations (subscript equations), give the data reuse and the production-consumption of the arrays; the memory access pattern of each array reference is given by its subscript equation. Given that the memory access pattern of each array is given by its subscript equation, we claim that all memory efficient solutions (exploration space) can be produced by processing these equations. The subscript equations are processed and a new iteration space is created. Each subscript equation gives either its iterators or even new iterators, to the new iteration space. Then, the exploration space is orders of magnitude decreased by applying constraint propagation to the software and hardware parameters. Regarding the hardware parameters, we produce register file and data cache inequalities, which contain all the (near)optimum tile sizes; these inequalities contain i) the tiles sizes in elements, ii) the shape of each array's tile. Furthermore, new data array layouts are generated, according to the data cache associativity. All the schedules with different tile sizes and data array layouts, than these the proposed methodology gives, are not considered, decreasing the exploration space.

The major contributions of this paper are: i) the optimization of the above subproblems as one problem and not separately for a wide range of algorithms and computer architectures, ii) the software information and several hardware parameters are fully exploited giving high execution speed solutions and a smaller search space, iii) the proposed methodology, due to the major contribution of number (ii) above, gives a smaller code size and a smaller compilation time, as it does not test a large number of alternative schedules, as the state of the art (SOA) libraries and iterative compilation do.

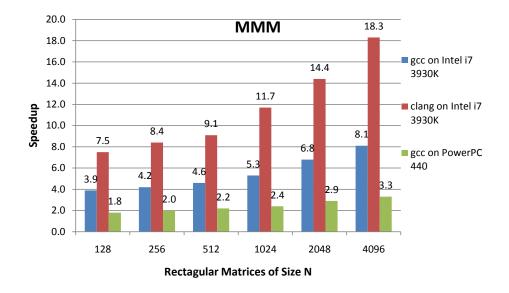

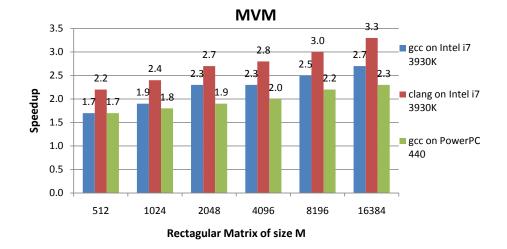

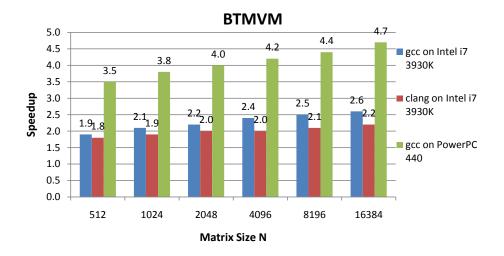

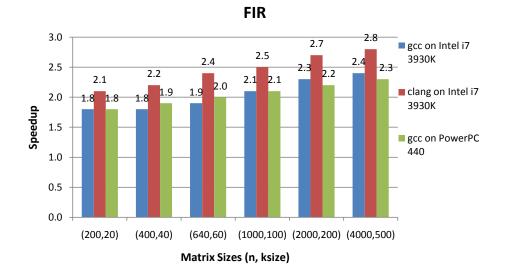

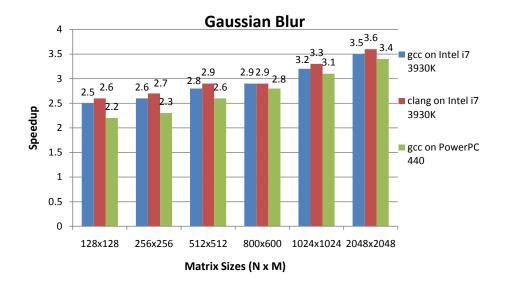

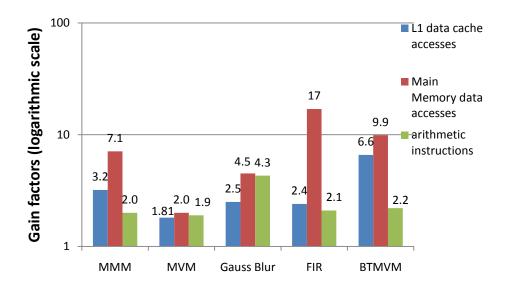

The experimental results are taken by using a general purpose processor, an embedded processor and Simplescalar simulator [1]. The proposed methodology is evaluated for five well-known data dominant algorithms over two different compilers (speedup from 1.8 up to 18.3) and iterative compilation technique (speedup up to 2.2).

The remainder of this paper is organized as follows. In Section 2, the related work is given. The proposed methodology is given in Section 3 while the experimental results are given in Section 4. Finally, Section 5 is dedicated to conclusions.

#### 2. Related Work

The independent optimization of the back end compiler phases (e.g. transformations, register allocation), leads to inefficient binary code due to the dependencies among them. These dependencies require that all phases should be optimized together as one problem and not separately. Toward this, much research has been done, either to simultaneously optimize only two phases, e.g. register allocation and instruction scheduling [2] [3] or to apply predictive heuristics [4] [5]. Nowadays compilers and related works, apply i) iterative compilation techniques [6] [7] [8] [9], ii) both iterative compilation and machine learning compilation techniques to restrict the configurations' search space and thus to decrease the compilation time [10] [11] [12] [13] [14] [15], iii) iterative optimizations or compiler transformations, by using the Polyhedral model [16] [17] [18] [19], iv) compiler transformations by using heuristics and empirical methods [20]. In iterative compilation, a large number of different versions of the program are generated-executed by applying many compiler transformations, at all different combinations. Iterative compilation requires extremely long compilation times to decrease the exploration space iterative compilation is applied with machine learning compilation techniques. The five major iterative compilation drawbacks are referred to the introduction. The proposed methodology achieves up to 2.1 times lower execution time and an orders of magnitude lower compilation time (Section 4).

The state of the art software libraries, such as ATLAS [21], GotoBLAS2 [22] Eigen [23], Intel\_MKL [24], PHiPAC [25], FFTW [26], OpenCV [27] and SPIRAL [28], manage to find a near-optimum binary code for a specific application by using a large exploration space (many different executables are tested and the fastest is picked). Although they achieve high speed, they are application specific and the final schedule is found mostly by using heuristics and empirical techniques. A comparison with the above libraries would be unfair because they use the SIMD (Single Instruction Multiple Data) vector instructions (they support load/store and arithmetical instructions with 128/256-bit data); however, our future work includes the support of SIMD instructions. In [29] [30] [31] [32], we have developed algorithm specific methodologies (we used the SIMD instructions), which produce lower execution time, lower compilation time and lower number of data accesses, than ATLAS [29] [30], FFTW [30] and OpenCV [32]. A comparison between the proposed methodology and [29] [30], is made in Section 4.

Furthermore, many sub-optimum methods exploiting the memory hierarchy have been analyzed in the past, such as [33] [34] [35] [36] [37] [38]. These works apply compiler transformations to the original code (this is not performance efficient). The cache performance optimizations and compiler techniques are presented in [39] and [40]. Finally, regarding data cache miss elimination methods, much research has been done in [41] [42] [43] [44] [45] [46] [47].

| <pre>for {</pre> | <pre>for.{S1;S2;}for.{S3;}S4;}</pre> |

|------------------|--------------------------------------|

|------------------|--------------------------------------|

Figure 1: Perfectly and imperfectly nested loops are shown at (a) and (b), respectively.

Regarding register allocation problem, many methodologies exist such as [48] [49] [50] [51] [52] [53] [54]. In [48] - [52], data reuse is not taken into account; this means that the array references are assigned into registers, without taking into account that some are accessed a lot and others do not. In [53] and [54], data reuse is taken into account either by greedily assigning the available registers to the data array references or by applying loop unroll transformation to expose reuse and opportunities for maximizing parallelism. In contrast to the proposed methodology, the [48] - [54] address the register allocation problem without taking into account the scheduling problem; instead of finding a good schedule that achieves data reuse and then apply register allocation, they just apply register allocation to the given schedule.

#### 3. Proposed Methodology

The proposed methodology takes C-code and the memory architecture parameters as input, and automatically produces a new faster C-code. The software information-characteristics, i.e. data reuse, production-consumption of intermediate results (when a datum is produced it is directly consumed, e.g. C[k] = C[k] + ...), data dependences, array subscript equations, existence of common array references, loop iterators, loop bounds, and the major memory architecture parameters, i.e. number of data cache memories, data cache sizes, data cache associativities, data cache line sizes, register file size, are fully exploited.

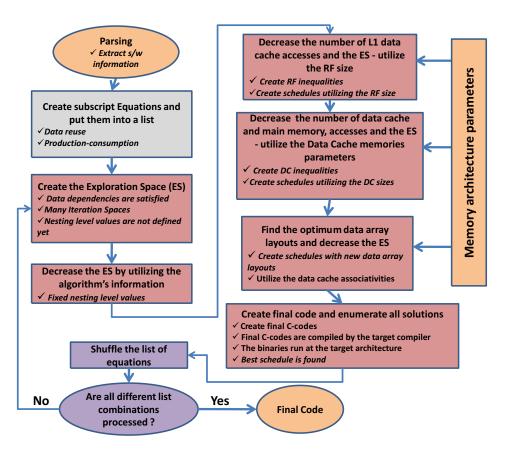

Figure 2: Flow graph of the proposed methodology.

The proposed methodology optimizes source code which contains loops (loop kernels); as it is well known, 90% of the execution time of a computer program is spent executing 10% of the code (also known as the 90/10 law) [55]. We take a loop kernel as input and we produce a new loop kernel which cannot be given by applying the existing transformations to the original code. The methodology optimizes both perfectly and imperfectly nested loops (Fig. 1), which i) no if-condition exists (if they do, current expression is skipped), ii) all the array subscripts are linear equations of the iterators (which in most cases do). Each loop kernel is optimized separately; each loop kernel may contain either perfectly or imperfectly nested loops (Fig. 1).

The proposed methodology is shown in Fig. 2. All the steps are automatic. Firstly, parsing is done; the loops, the loop bounds, the array references,

| for (i=0; i≤9; i++)    | $2^{i} + j = c_1, 0 \le c_1 \le 27$                         | (1) |

|------------------------|-------------------------------------------------------------|-----|

| for (j=0; j ≤9; j++)   | $i=c_{21}$ and $j=c_{22}$ , $0 \le c_{21}$ , $c_{22} \le 9$ | (2) |

| for (k=0; k ≤9; k++)   | $k=c_{3}, 0 \le c_{3} \le 9$                                | (3) |

| =A[2*i + j] + B[i][j]; | $2^{*}i + j - k = c_4$ , $-9 \le c_4 \le 27$                | (4) |

| =A[k];                 |                                                             |     |

Figure 3: The three first equations contain the separate data reuse of the three array references respectively, while the fourth equation contains the data reuse between the two different references of the array A.

the data dependences, the subscript equations etc, are identified. Then, one mathematical equation is created for each array's subscript and one for each two common array references (e.g. eq.(4) in Fig. 3, it is explained in Subsect. 3.3); each equation defines the memory access pattern of the specific array reference; data reuse is found by these equations. Given that the memory access pattern of each array is given by its subscript equation, we claim that all memory efficient solutions can be produced by processing these equations (Subsect.3.2). After all the equations have been created, all the equations are processed one by one, at all different combinations (Fig. 2), to examine all possible solutions (Subsect.3.2).

For each different combination (e.g. eq.(3), eq.(2), eq.(1) and eq.(4), in Fig. 3), all the equations are processed one by one, creating the new iteration space (Subsect. 3.4); the iteration space is defined by the iterators used and their nesting level values. Each equation inserts its iterators or even new iterators into the new iteration space; for an iteration space to be created all the equations must be fetched.

Afterwards, the exploration space is decreased by applying constraint propagation to the software and hardware parameters. Regarding the software parameters (Subsect.3.3), the exploration space is decreased by fixing the iterators nesting level values (all the schedules having different nesting level values than these the proposed methodology gives, are not considered, decreasing the exploration space). Regarding the hardware parameters, we apply loop tiling for each memory (including the register file) by producing register file and data cache inequalities (Subsect. 3.6 and Subsect. 3.7, respectively), which contain all the (near)-optimum tile sizes. Then, for each schedule has been produced so far, the (near)-optimum data array layouts are found (Subsect. 3.8); the proposed methodology selects both the schedules with the new and the default data array layouts, as by changing the layouts an additional cost is added which may degrade performance. All the schedules with different tile sizes and data array layouts than these the proposed methodology gives, are not considered, decreasing the exploration space. Finally, all these schedules are transformed into C-code, they are compiled by the target compiler and the output binaries are run to the target platform in order to find the one with the best performance (Subsect. 3.9).

The remainder of the proposed methodology has been divided into ten sub-sections. The first subsection contains the basic definitions and notations. The second presents a new loop transformation and the other seven ones explain in more detail the most complex steps of the proposed methodology (Fig 2). Finally the tenth subsection gives an example.

#### 3.1. Definitions and Notations

**Definition 1.** Equations which have more than one solutions for at least one constant value, are named type2 equations. All others, are named type1 equations, e.g. eq.(1) and eq.(4) in Fig. 3 are type2 equations, while eq.(2) and eq.(3) are type1 equations.

Arrays with type2 equations fetch their elements more than once, even if no other/extra iterator exists (the loop kernel contains only the type2 equation iterators), e.g. 2i + j = 7 holds for several iteration vectors (data reuse); on the other hand, if no extra iterator exists, arrays with type1 equations fetch their elements only once. However, both type1 and type2 arrays may fetch their elements more than once because of the existence of another loop iterator(s) above/between from/of theirs; for example, although eq.(3) in Fig. 3 is of type1, each element of A[k] is fetched 100 times because of the presence of i, j iterators.

To sum up, arrays with type2 equations achieve data reuse at all cases, while arrays with type1 equations achieve data reuse only at the case that extra iterators exist.

The arrays are classified into category-1 and category-2 arrays.

**Definition 2.** The arrays whose elements achieve data reuse are classified into category-1 arrays

**Definition 3.** The arrays whose elements do not achieve data reuse or data reuse cannot be exploited, are classified into category-2 arrays

**Definition 4.** The arrays whose subscript equations are of type1 and they contain all the loop kernel iterators (no extra iterator exists), are further classified into Category-2a arrays.

**Statement 1.** The Category-2a arrays fetch their elements just once (there is no data reuse).

**Proof 1.** The subscript equations of these arrays change their values in each iteration vector and thus a different element is fetched in each iteration.

**Definition 5.** The arrays whose subscript equations are not given by a compile time known expression (e.g. they depend on the input data), are further classified into Category-2b arrays.

**Statement 2.** Data reuse of Category-2b arrays cannot be exploited, as the arrays elements are not accessed according to a mathematical formula.

**Definition 6.** If all the iterators of an equation, exist in this equation only and not in another equation, then these iterators are named unique iterators, e.g. the i, j iterators of eq.(1) in Fig. 7 are unique, while the i, j iterators of eq.(1) in Fig. 3 are not.

#### 3.2. Proposed Loop Transformation

As it has been explained in the previous subsection, arrays with type2 equations fetch their elements more than once (data reuse), even if no extra iterator exists. For example, the iteration vectors (S = (i, j, k)) fetching A[4] of eq.(1) in Fig. 3, are more than one (data reuse), i.e. 2 \* i + j = 4 holds for S1 = (0, 4, X), S2 = (1, 2, X) and S3 = (2, 0, X), where X are all the valid k values. In this subsection, we propose a new loop transformation in order to exploit the data reuse of type2 equations. The new transformation treats the type2 equation as a Linear Diophantine Equation (LDE); the solution of an LDE is a mathematical expression which gives the exact iteration vectors that each array's element is fetched only once, e.g. if the proposed transformation is applied on 2 \* i + j = c1 of Fig. 3, each element of A[2 \* i + j] is accessed only once.

**Statement 3.** The proposed transformation is applied to type2 equations only and gives the minimum number of data accesses of the specific type2 array reference.

**Proof 2.** The minimum number of data accesses is achieved because each array's element is accessed only once.

The proposed transformation can be applied only if there are no loop carried data dependencies.

Let us give two examples, Fig. 4. The equation produced by the array subscript, gives all the information needed about the data reuse of array A. This equation is treated as a LDE here; its solution gives the i, j values that c is a constant value, e.g. c = 10 for all  $0 \le k \le 10$  values giving a j value within its bounds (source code 1 in Fig. 4). The solution of the Diophantine equation and the iterator bounds, give a new iteration space which all the array elements are fetched just once; i and j iterators are replaced by k and c iterators. To transform these equations into source code, a new iterator is added into the source code (c iterator) for all the array elements to be The added if-condition statements are necessary. accessed in order. In general, one if-condition statement is needed for each iterator, e.g. at source code 1, if-condition statements for both i and j iterators are needed; however, in most cases it is not necessary to add an if-condition statement for all the iterators because the Diophantine independent variable equals to the iterator, e.g. i=k in source code 1. Thus, the iterator bounds are preserved by the loop bounds and no if-condition statement is needed. The break statements have been inserted to decrease the number of idle iteration vectors.

If the proposed transformation is applied, the number of data accesses is minimized and the data cache lines utilization is increased since all the array's elements are fetched in order and thus from consecutive memory locations. However, the number of arithmetical instructions is increased (extra addressing and branch instructions). The schedule with the minimum number of data accesses does not always provide the best performance, since the number of extra instructions may degrade performance; the best performance depends on the target architecture. This is why type2 equations are treated both as LDE equations and not. The two codes in Fig. 4 are the schedules with the minimum number of data accesses.

#### 3.3. Create Equations

At this step, each array's subscript is transformed into a mathematical equation (Fig. 3).

**Statement 4.** Each subscript equation separately, gives the data reuse / production-consumption of the specific array.

| Source code 1:                                      | Source code 2:                                                                |

|-----------------------------------------------------|-------------------------------------------------------------------------------|

| for (i=0; i<=10; i++)                               | for (i=0;i<=10;i++)                                                           |

| for (j=0; j<=10; j++)                               | for (j=0;j<=10;j++)                                                           |

| A[2*i + j]=                                         | for (k=0;k<=12;k++)                                                           |

| ∽[2 · · · ]]−                                       | A[2*i + j + k + 3]=                                                           |

| Get subscript info:                                 | Get subscript info:                                                           |

| 2*i + i=c                                           | 2*i + j + k + 3=c                                                             |

| $(0 \le i, j \le 10 \text{ and } 0 \le c \le 30)$   | $(0 \le i, j \le 10 \text{ and } 0 \le k \le 12 \text{ and } 3 \le c \le 45)$ |

|                                                     | Solve Diophantine equation:                                                   |

| Solve Diophantine equation:                         | We set w=2i+j (1) and thus w+k=c-3 (2)                                        |

| i=k                                                 | (2) gives: w=k1 and k=c-3-k1                                                  |

| J=c-2k                                              | $(0 \le k1 \le 30 \text{ and } -12 \le k1 \le 42)$                            |

| $(0 \le k \le 10 \text{ and } 0 \le c - 2k \le 10)$ | (1) gives: i=k2 and j=w-2k2                                                   |

| $(0 \le k \le 10 \text{ and } -5 \le k \le 15)$     | $(0 \le k2 \le 10 \text{ and } -5 \le k2 \le 15)$                             |

| Thus, $0 \le k \le 10$                              | Final code 2:                                                                 |

|                                                     | for (c=3; c<=45; c++)                                                         |

| Final code 1:                                       | for (k1=0; k1<=30; k1++){                                                     |

| for (c=0; c<=30; c++)                               | for (k2=0; k2<=10; k2++){                                                     |

|                                                     | tempz = (c-3) - k1;                                                           |

| for (k=0; k<=10; k++){                              | if (tempz < 0) break;                                                         |

| temp = c - 2 * k;                                   | else if (tempz <= 12){                                                        |

| if (temp < 0) break;                                | tempy = k1 - 2 * k2;                                                          |

| else if (temp <= 10) {                              | if (tempy < 0) break;<br>else if (tempy <= 10) {                              |

| A[c]=                                               | A[c]=                                                                         |

| }}                                                  | }}}                                                                           |

Figure 4: Proposed transformation - scheduling with the minimum number of data accesses.

It is obvious that the memory access pattern of each array reference is given by its subscript equation.

**Statement 5.** The interaction of two or more equations gives i) the data reuse produced between the common array references (e.g. eq.(4) in Fig. 3) and ii) the interaction among the arrays data, i.e. by fetching one array's element, other array elements are consequently fetched.

Regarding (i), in the case that there are two array references of the same array, an additional equation is always created to give the iteration vectors that both references access identical elements, e.g in Fig. 3, A[2] is fetched by S1=(0,2,X) and S2=(1,0,X) according to eq.(1) and also A[2] is fetched by S3=(X,X,2) according to eq.(3), where X = [0,9]. Regarding (ii), it is obvious that by fetching one array's element, other array elements are consequently fetched, e.g. by fetching B(2,3) in Fig. 3, A(7) and A(0:9) are fetched because of the first and the second array reference respectively.

**Rule 1.** If there are two array references of the same array, an additional equation is created to describe the data reuse between these two references, e.g. eq.(4) in Fig. 3. These equations are further classified into type3 equations.

**Rule 2.** Regarding 2-d arrays, two equations are created and not one because the data array layout has not been found yet, e.g. if 9 \* i + j = c2 is taken instead of i = c21 and j = c22 for eq.(2) in Fig. 3, then row-wise layout is taken which may not be efficient.

The Type1, type2 and type3 equations, are treated differently (Subsections 3.3.1-3.3.3).

#### 3.3.1. Type1 equations

All type1 equations add their iterators into the new iteration space (their nesting level values are found next), e.g. eq.(2) of Fig. 3, gives either  $S_1 = (i, j)$  iteration space or  $S_2 = (j, i)$ .

#### 3.3.2. Type2 equations

Type2 equations are treated in two different ways, i.e. they are treated either as type1 equations or as Linear Diophantine Equations (LDE) (the transformation of Subsect. 3.2 is applied). In the second case, each element of the current equation array, is now accessed only once (optimum data reuse), e.g. if the proposed transformation is applied on 2 \* i + j = c1 of Fig. 3, each element of A[2\*i+j] is accessed only once. Type2 equations are treated in two different ways because the optimum data reuse of one array does not always provide the optimum data reuse or the best performance.

**Rule 3.** type1 equations give their iterators into iteration space, while type2 equations give either their iterators (they are treated as type1 equations) or new ones (the proposed transformation is applied, Statement 3), into iteration space.

#### 3.3.3. Type3 equations

Type3 equations contain the iteration vectors that both two array references fetch the identical elements (data reuse), e.g. A[2] is accessed by (0, 2, X) and (1, 1, X) because of the A[i + j] reference and by (X, X, 2) because of the A[k] reference in Fig.2. This kind of data reuse is fully exploited too, by treating the type3 equations as LDE. Let us give an example, Fig. 5. The equation giving the iteration vectors that both two references fetch the identical array elements, is i + j - k = c when c = 0. When c = 0 or k2 + tempy = tempz (final code 0 when c = 0 or final code 1, Fig. 5), only common elements are loaded. However, there are elements do not loaded in identical iteration vectors, i.e.  $c \neq 0$  in final code 0, and thus i + j - k = c.

**Rule 4.** type3 equations are treated as LDE equations only; the proposed transformation (Statement 3) is applied to type3 equations giving new iterators

#### 3.4. Find the exploration space

At this step the exploration space is found by processing all subscript equations. Firstly, the iteration space is created.

**Statement 6.** The iteration space is created by processing all subscript equations.

Given that the subscript equations give all the data access patterns and data reuse, we process all subscript equations to find all memory efficient solutions.

To create the iteration space, all equations are processed one by one according to the Rule 3 and Rule 4. The outermost iterators (smallest

| //Initial code     | Get subscript info                        | //final code                     |

|--------------------|-------------------------------------------|----------------------------------|

| for (i=0;i<=1;i++) | i + j = c1 (eq.1)                         | for (c=-2;c<=3;c++)              |

| for (j=0;j<=2;j++) | k = c2 (eq.2)                             | for (k1=0;k1<=3;k1++){           |

| 0 3 3 7            | i + j – k =c3 , <b>(eq.3)</b>             | for (k2=0;k2<=1;k2++){           |

| for (k=0;k<=2;k++) | c1=[0,3], c2=[0,2], c3=[-2, 3]            | tempz = -c + k1;                 |

| {                  | Solve the Diophantine equation            | on (eq.3): if (tempz > 2) break; |

| cnt2+=A[k];        | We set w=i+j (1) and thus w-k=c           | (2) else if (tempz >= 0){        |

| }                  | (2) gives: w=k1 and z=-c+k1               | tempy = k1 - k2;                 |

|                    | <b>k1=[0,3]</b> , since                   | if (tempy < 0) break;            |

|                    | (k1=[0,3] and k1=[-2,3])                  | else if (tempy <= 2) {           |

|                    | (1) gives: <b>i=k2</b> and <b>j=k1-k2</b> | cnt+=A[k2+tempy];                |

|                    | k2=[0,1], since                           | cnt2+=A[tempz];                  |

|                    | (k2=[0,1] and k2=[-2,3])                  | }}}                              |

Figure 5: Proposed transformation; the common elements of A[i+j] and A[k] are accessed just once.

nesting level values) of the new loop-kernel are these, whose equation has been processed first, e.g. if eq.(2) of Fig. 3 is processed first, the iteration space is either  $S_1 = (i, j)$  or  $S_2 = (j, i)$ . The iterators with the next larger nesting level values are these, whose equation has been processed second etc, e.g. if eq.(3) of Fig. 3 is processed after eq.(2), the iteration space is either  $S_1 = (i, j, k)$  or  $S_2 = (j, i, k)$ .

**Statement 7.** All the equations are processed (according to Rule 3 and Rule 4) one by one, by using all the different combinations, suffice the data dependences are preserved. We process all different combinations in order to examine all memory efficient solutions.

For a subscript equation, the sooner it is fetched, the better it is treated. This is because i) an array with small nesting level iterator values (its iterators are the upper ones) is fetched less times than one with large ones, e.g. in Fig. 6, 'A' array is fetched only once while 'B' is fetched  $N^2$  times; this is because compilers apply scalar replacement transformation (A(i, j)is replaced by a variable), and ii) for an equation whose iterators have not been assigned into iteration space, we can apply the proposed transformation (Statement 3), decreasing the number of the specific array's accesses.

Let us give an example, Fig. 3. The four equations of Fig. 3 give 7 different iteration spaces, i.e.  $S_1 = (i, j, k)$ ,  $S_2 = (j, i, k)$ ,  $S_3 = (c, p, k)$ ,  $S_4 = (k, c, p)$  (where c and p are the new iterators created, if the proposed transformation is applied to eq.(1)),  $S_5 = (k, i, j)$ ,  $S_6 = (k, j, i)$  and  $S_7 = (c, k1, k2)$  (where c, k1, k2 are the new iterators created, if the proposed transformation is applied to eq.(4)).

If there are N different equations, there are up to N! different equation combinations; in practice, the number of different combinations, is smaller than N! because i) identical schedules are produced and ii) data dependences may prohibit some combinations.

# **Statement 8.** The iteration space created according to statement 7, is further increased and it contains an enormous number of different schedules (exploration space)

This is because i) loop tiling can be applied for all memories (new iterators are inserted), ii) loop tiling can be applied for all different tile sizes and shapes, iii) the new iterators can take all the different nesting level values, iv) all the array references can be replaced by a different number of variables/registers, v) many different data array layouts can be used.

#### Statement 9. The exploration space is decreased by orders of magnitude

The exploration space is decreased by orders of magnitude because a) only the iteration spaces produced by Statement 7 are considered, b) all the schedules with different number of assigned variables/registers, tile sizes, nesting level values and data array layouts, than these the proposed methodology gives, are not considered.

#### 3.5. Decrease the exploration space by utilizing the algorithm's information

As it has been already mentioned in the previous subsection, by creating the exploration space according to Statement 7, the solutions achieve low data reuse are not examined, decreasing the exploration space; for example, for the Gaussian Blur algorithm, the iteration spaces which are tested and these which are excluded, are shown in Table 2 (Subsection 3.10).

However, the exploration space is decreased even more by utilizing the software characteristics; the nesting level values of the iterators created according to Statement 7, Rule 3 and Rule 4, become fixed (Rules 5, 6). All the schedules having different nesting level values than these the proposed methodology gives, are not considered, decreasing the exploration space even more (Rule 5 and Rule 6).

The exploration space is decreased according to the Rules 5, 6.

**Rule 5.** The unique iterators are not interchanged with iterators of another equation.

| Source code:                                                                                                                           | The equations are:                        | For equations'                | order                         |

|----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-------------------------------|-------------------------------|

| for (i=0; i <n; i++)<="" th=""><th>i=c<sub>11</sub> &amp; j=c<sub>12</sub> (1)</th><th>eq.1, eq.2, eq.3</th><th>3,</th></n;>           | i=c <sub>11</sub> & j=c <sub>12</sub> (1) | eq.1, eq.2, eq.3              | 3,                            |

| for (j=0; j <n; j++)<="" td=""><td>k=c<sub>21</sub> &amp; m=c<sub>22</sub> (2)</td><td></td><td></td></n;>                             | k=c <sub>21</sub> & m=c <sub>22</sub> (2) |                               |                               |

| for (k=0; k <n; k++)<="" td=""><td>j=c<sub>31</sub> &amp; m=c<sub>32</sub> (3)</td><td>eq. (1) gives:</td><td>eq. (3) gives:</td></n;> | j=c <sub>31</sub> & m=c <sub>32</sub> (3) | eq. (1) gives:                | eq. (3) gives:                |

|                                                                                                                                        |                                           | S <sub>1</sub> = (i, j, -, -) | S <sub>3</sub> = (i, j, k, m) |

| for (m=0; m <n; m++)<="" td=""><td></td><td></td><td>S<sub>4</sub> = (j, i, k, m)</td></n;>                                            |                                           |                               | S <sub>4</sub> = (j, i, k, m) |

| A[i][j] += B[k][m] + k * C[                                                                                                            | j][m];                                    | eq. (2) gives:                | S <sub>5</sub> = (i, j, m, k) |

|                                                                                                                                        |                                           | S <sub>2</sub> = (-, -, k, m) | S <sub>6</sub> = (j, i, m, k) |

Figure 6: An example, eq.(3) gives different iterators nesting levels.

In general, each array is accessed  $(q \times r)$  times, where q is the number of the iterations exist above its upper iterator and r is the number of the iterations exist between its upper and lower iterators. It can be easily be proved that if the unique iterators change their nesting level values without satisfying Rule 5, either the  $(q \times r)$  value increases or the iterators nesting level values are given by processing another equations' combination (it is not an issue here).

# **Rule 6.** The nesting level values of the unique iterators are defined according to the target compiler.

According to Rule 5, the unique iterators of an equation are not interchanged with iterators of another equation. Furthermore, in the case that they are interchanged with each other, the number of load/store and addressing instructions will remain constant; only the number of data cache misses changes. The number of cache misses changes because multi-dimensional arrays, access their elements from no consecutive main memory locations, e.g. if i and j iterators in Fig. 6 are interchanged, A is no further accessed row-wise but column-wise from main memory; however, the data array layout is found next. Apart from reducing the number of data cache misses, there is no use to interchange these iterators. Thus, only these nesting level values accessing the array row-wise are taken for now (C compiler stores the arrays row-wise in main memory), decreasing the number of the data cache misses, e.g. for A(i, j), the *i* iterator is defined as the outermost one.

#### 3.6. Decrease the number of L1 data cache accesses and the exploration space - utilizing the Register File (RF) size

At this step, the Register File (RF) size and the subscript equations are fully exploited, decreasing the number of L1 data cache accesses and the exploration space. For each iteration space has been created so far, loop tiling for the RF is applied. To utilize the RF size, RF inequalities are produced giving all the (near)-optimum tile sizes. These inequalities contain i) the number of the registers needed for each array reference and for scalar variables, ii) the shape of each array's tile.

The register file inequality is given by:

$$0.8 \times RFs \le L_{iter} + Var + ws + R_1 + R_2 + \dots + R_n \le 1.2 \times RFs$$

(1)

where RFs is the number of the available registers,  $L_{-iter}$  is the number of the different iterator references exist in the loop body, Var is the number of scalar variables, ws is the number of the working space registers, i.e. variables for intermediate results and  $R_i$  is the number of the variables/registers allocated for the i-th array.

$R_i$  is given by:  $R_i = it'_1 \times it'_2 \times \ldots \times it'_n$ , where the integer  $it'_i$  are the unroll factor values of the iterators exist in the array's subscript, e.g. for B(i, j) and C(i, i),  $R_B = i' \times j'$  (rectangular tile) and  $R_C = i'$  (diagonal line tile) respectively, where i' and j' are the unroll factors of i, j iterators.

**Rule 7.** Each subscript equation contributes to the creation of ineq.(1), i.e. equation i gives  $R_i$  and specifies its expression.

The iterators are tiled and the new tiled iterators are fully unrolled, according to the RF size, to exploit data reuse; in this way, the registers are reused as many times as the number of the available registers indicate (register utilization).

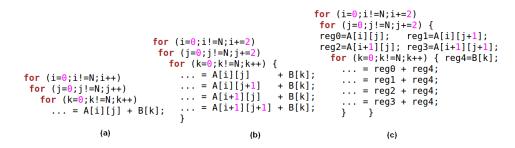

Let us give an example. In Fig. 7-a,  $R_A = i' \times j'$  and  $R_B = k'$  variables/registers are allocated for A and B arrays, respectively. If we choose a square tile for array A of size  $2 \times 2$ , i.e. 4 registers for A, and only 1 register for B, then the i, j iterators are tiled and the new tiled iterators are fully unrolled (Fig. 7-b). Then, by assigning the array references into registers, data reuse is achieved (Fig. 7-c). In Fig. 7-a, the (A,B) arrays are accessed  $(1, N^2)$  times while in Fig. 7-c  $(1, N^2/4)$  times, respectively.

**Rule 8.** For each iteration space has been created according to Statement 7, loop tiling for the RF is applied; this means that new iterators are created with loop bounds equal to the tile sizes; the new iterators are fully unrolled and all the array references are replaced by scalar variables according to the RF size and to the subscript equations, achieving data reuse.

Figure 7: An example, tiling for the RF is applied - we assign 4 registers for A (square tile of size  $2 \times 2$ ) and 1 for B.

The bound values of the register file inequality (eq.(1)) are not tight because the output code is C-code and during its compilation (translate the C-code into binary code), the compiler may not allocate the exact number of desirable addressing variables into registers. However, if assembly code would be produced instead of C-code, the register utilization would be the optimum.

The number of  $L_{iter}$  and ws registers is found after the allocation of the array elements into variables/registers, because they depend on the number of tiled iterators. The ws value depends on the target compiler and this is why it is found approximately; the bounds of the RF inequality are not tight for this reason too. The goal is to store all the inner loop reused array elements and scalar variables into registers minimizing the number of register spills.

**Statement 10.** All schedules satisfying ineq.(1), decrease the number of L1 data cache accesses.

**Proof 3.** The number of L1 data cache accesses is decreased for two reasons. First, loop tiling for the RF is applied. In general, by applying loop tiling for the RF, the number of L1 data cache accesses is decreased, as parts (tiles) of the arrays remain in the RF (data reuse) and therefore they are not fetched many times from L1. Second, loop tiling is applied according to the RF size and to the subscript equations (memory access patterns). The new iterators are fully unrolled and all the array references are replaced by scalar variables; each variable in the loop body corresponds to a register, minimizing the number of register spills. The larger the RF size, the larger the tiles used and the larger the data reuse being achieved. **Statement 11.** All schedules with different number of assigned variables/registers than these the proposed methodology gives, are not considered, decreasing the exploration space.

**Rule 9.** Each different set of  $it'_i$  values satisfying ineq.(1), gives a different schedule. All different  $it'_i$  values satisfying ineq.(1) are examined.

**Rule 10.** The  $R_i$  values of ineq.(1), are given by Rules 11-18.

**Rule 11.** The innermost iterator is never tiled because data reuse is decreased; if  $it_i$  is the innermost iterator, then  $it'_i = 1$ .

**Proof 4.** By tiling the innermost iterator, e.g. iterator k in Fig. 7, the array references-equations which contain it, will change their values in each iteration; this means that i) a different element is accessed in each k iteration and thus a huge number of different registers is needed for these arrays, ii) all these registers are not reused (a different element is accessed in each iteration). Thus, by tiling the innermost iterator, more registers are needed which do not achieve data reuse; this leads to low RF utilization.

**Rule 12.** The type1 array references which contain all the loop kernel iterators, do not achieve data reuse; thus only one register is needed for these arrays, i.e.  $R_i = 1$

**Proof 5.** The subscript equations of these arrays change their values in each iteration vector and thus a different element is fetched in each iteration.

**Rule 13.** If the proposed transformation (Statement 3) is applied to eq.(i), then only one register is needed for this array reference, i.e.  $R_i = 1$ .

**Proof 6.** In this case, the optimum data reuse for this array is achieved since each array's element is fetched just once (all array elements are fetched in-order); thus only one register is needed for this array, e.g. in Fig. 4, A[c] needs only one register.

**Rule 14.** If the proposed transformation (Statement 3) is applied to eq.(i), then the eq.(i) iterators are never tiled and thus  $it'_i = 1$ . Otherwise, the proposed transformation may be invalid.

| Source code (Matrix Matrix Multiplication):                                      | A potential output kernel is:                      |  |

|----------------------------------------------------------------------------------|----------------------------------------------------|--|

| for (i=0; i<60; i++)                                                             | //tiling for L1 data cache                         |  |

| for (j=0; j<60; j++)                                                             | for (ii=0; ii<60; ii+=10)                          |  |

| for (k=0; k<60; k++)                                                             | for (jj=0; jj<60; jj+=15)                          |  |

| C[i][j] += A[i][k] * B[k][j];                                                    | for (kk=0; kk<60; kk+=4)                           |  |

| ,                                                                                | //tiling for the RF                                |  |

| The equations are:                                                               | for (i=ii; i <ii+10; i+="2)&lt;/td"></ii+10;>      |  |

| i=c11 & j=c12 (1)                                                                | for (k=kk; k <kk+4; k+="4)" td="" {<=""></kk+4;>   |  |

| i=c21 & k=c22 (2)                                                                | regA1=A[i][k];                                     |  |

| k=c31 & j=c32 (3)                                                                | regA4=A[i][k+3];                                   |  |

| 1                                                                                | regA7=A[i+1][k+2];                                 |  |

| Suppose the equations' order (2), (3), (1),                                      | for (j=jj; j <jj+15; j++)="" td="" {<=""></jj+15;> |  |

| the iterator spaces are:                                                         | regC1=0; regC2=0; regB1=B[k][j]; regB2=B[k+1][j];  |  |

| S <sub>1</sub> =(i, k, j), S <sub>2</sub> =(k, i, j)                             | regB3=B[k+2][j];                                   |  |

|                                                                                  | regC1+=regA1 * regB1;                              |  |

| The RF inequalities for S <sub>1</sub> are:                                      | regC1+=regA2 * regB2;                              |  |

| Low $\leq 3 + 0 + 1 + i' + i'*k' + k' \leq Up$ , for i' $\neq 1$ and k' $\neq 1$ | regC1+=regA3 * regB3;                              |  |

| Low $\le 3 + 0 + 1 + 2 + i' \le Up$ , for k'=1                                   | regC1+=regA4 * regB4;                              |  |

| Low $\leq 3 + 0 + 1 + 2 + k' \leq Up$ , for i'=1                                 | regC2+=regA5 * regB1;                              |  |

|                                                                                  | regC2+=regA6 * regB2;                              |  |

| The L1 Data Cache inequality for S <sub>1</sub> is:                              | regC2+=regA7 * regB3;                              |  |

| Low' ≤ Tii*Tjj + Tii*Tkk + Tkk*Tjj ≤ Up'                                         | regC2+=regA8 * regB4;                              |  |

|                                                                                  | C[i][j]+=regC1; C[i+1][j]+=regC2; }}               |  |

Figure 8: An example, Matrix Matrix Multiplication (MMM) algorithm.

Let us give an example, Fig. 3. If the proposed transformation is applied to eq.(1), then the B array's iterators cannot be tiled and thus only one variable/register is needed for B array.

**Rule 15.** If there is a type1 array reference i) containing more than one iterators and one of them is the innermost one and ii) all ineq.(1) iterators which do not exist in this array reference have unroll factor values equal to 1, then only one register is needed for this array, i.e.  $R_i = 1$ . This gives more than one register file inequalities.

**Proof 7.** When Rule 15 holds, a different array's element is fetched in each iteration vector, as the subscript equation changes its value in each iteration. Thus, no data reuse is achieved and only one register is used. On the contrary, in the case that at least one iterator which do not exist in this array reference is tiled, common array references occur inside the loop body (e.g. regC1 is reused 3 times in Fig. 8); data reuse is achieved in this case and thus another RF inequality is created.

Let us give an example (Fig. 8). Suppose the  $S_1$  iteration space whose register file inequalities are shown in Fig. 8. The C array subscript contains *i* and *j* iterators. *j* iterator is the innermost one and thus  $i' \times 1$  registers are needed for this array; however, according to Rule 15, C array needs  $i' \times 1$  registers if  $k' \neq 1$  and 1 register otherwise (if k' = 1 then the C array fetches a different element in each iteration vector and thus only one register is needed). The array A needs  $i' \times k'$  registers while B array needs k' registers if  $i' \neq 1$  and 1 register otherwise. Note that if the i-loop is not tiled (i' = 0), the B and C array elements are not reused and there is 1 register for C and 1 register for B (Rule 15). The innermost iterator (j) is not tiled according to the Rule 11 (data reuse is decreased in this case).

**Rule 16.** We can decrease the number of  $it'_i$  values satisfying ineq.(1), by utilizing the L1 data cache line size. Regarding 1-d arrays, we can select the  $it'_i$  values to be either 1 or multiples of the L1 cache line size. Regarding multidimensional arrays, we can select the  $it'_i$  values which correspond to the x-axis, to be either 1 or multiples of the L1 cache line size. The arrays must be written into main memory aligned.

Moreover, there are cases that data reuse utilization is more complicated as common array elements may be accessed not in each iteration, but in each k iterations, where  $k \ge 1$ . This holds only for type2 equations (e.g. ai + bj + c) where k = b/a is an integer (data reuse is achieved in each k iterations). The proposed methodology exploits data reuse only when k = 1here (Rule 17) as for larger k values, the data reuse is low. For example, at Gaussian Blur algorithm (Subsection 3.10), each time the filter is shifted by one position to the right (mc iterator), 20 elements of in array are reused (reuse between consecutive iterations here, i.e. k = 1).

**Rule 17.** Arrays with type2 subscript equations which have equal coefficient absolute values (e.g. ai + bj + c, where  $a == \pm b$ ) fetch identical elements in consecutive iterations; data reuse is exploited by interchanging the registers values in each iteration. An extra RF inequality is produced for this case.

**Proof 8.** The above arrays access their elements in patterns. As the innermost iterator (let j) changes its value, the elements are accessed in a pattern, i.e. A[p], A[p+b],  $A[p+2 \times b]$  etc. When the outermost iterator changes its value, this pattern is repeated, shifted by one position to the right (A[p+b],  $A[p+2 \times b]$ ,  $A[p+2 \times b]$ ,  $A[p+3 \times b]$  etc), reusing its elements. This holds for equations with more than 2 iterators too.

|                       | L1                                 | L2                                 | Main Mem                           | Addr                               |

|-----------------------|------------------------------------|------------------------------------|------------------------------------|------------------------------------|

| Tiling for RF         | $\checkmark \checkmark \checkmark$ | $\checkmark$                       | $\checkmark$                       | $\checkmark \checkmark \checkmark$ |

| Tiling for RF, L1     | $\checkmark\checkmark$             | $\checkmark \checkmark \checkmark$ | $\checkmark\checkmark$             | $\checkmark\checkmark$             |

| Tiling for RF and L2  | $\checkmark\checkmark$             | $\checkmark$                       | $\checkmark \checkmark \checkmark$ | $\checkmark\checkmark$             |

| Tiling for RF, L1, L2 | $\checkmark\checkmark$             | $\checkmark\checkmark$             | $\checkmark \checkmark \checkmark$ | $\checkmark$                       |

Table 1: How tiling affects the number of memories accesses and addressing instructions; the more the ticks are, the less the number of accesses / addressing instructions, are.

To exploit data reuse of Rule 17, all the array's registers interchange their values in each iteration, e.g. in (Fig. 10 - a1.2), the (in0, in1, in2, in3, in4, in5) variables interchanging their values in each iteration.

**Rule 18.** Regarding very small arrays (e.g. filters in image processing algorithms), it is tested whether their iterators are fully unrolled or not (both solutions are taken).

To sum up, by applying loop tiling for the RF, as explained above, the numbers of i) load/store instructions (or equivalent the number of L1 data cache accesses) and ii) addressing instructions, are decreased. The number of addressing instructions is decreased for three reasons. Firstly, the array references are replaced by scalar variables and thus the address computations are simplified, e.g. A(i, j) is replaced by reg variable. Secondly, several common subscript expressions which occur by unrolling the loops are replaced by scalar variables, e.g. the array references array(i + j), array(i + j + 1), array(i + j + 2) and array(i + j + 3) are replaced by array(temp), array(temp+1), array(temp+2) and array(temp+3) respectively. Thirdly, loop unroll always decreases the number of addressing instructions.

3.7. Decrease the number of data cache and main memory accesses and the exploration space - utilizing the Data Cache memories parameters

The data cache memories sizes and the subscript equations are fully exploited, decreasing the number of data cache / main memory accesses and the exploration space. To utilize the data cache sizes, a data cache inequality for each data cache is produced, giving all the (near)-optimum tile sizes. Each inequality contains i) the tile size of each array and ii) the shape of each array tile.

The proposed methodology holds for each different cache hierarchy. The number of the levels of tiling for data cache is found by testing; for a 2 levels of data cache architecture, 1 level of tiling (either for L1 or L2 data cache), 2 levels of tiling and no tiling solutions, are applied to all the solutionsschedules that have been produced so far. The optimum number of levels of tiling cannot easily be found since the data locality advantage may be lost by the required insertion of extra load/store and addressing instructions, which degrade performance (Table 1). In table 1, we can see how tiling affects the number of data cache accesses and addressing instructions, e.g. if the performance critical parameter is the number of L1 data cache accesses or the number of addressing instructions, then tiling is not applied for data cache. The separate memories optimization gives a different schedule for each memory and these schedules cannot coexist, as by refining one, degrading another; thus, either a sub-optimum schedule for all the memories or a (near)optimum schedule only for one memory can be produced. However, if the goal is the minimum number of data accesses for a specific memory (let  $L_i$ ), loop tiling only for  $L_{i-1}$  is applied.

For the reminder of this paper, we refer to architectures having separate L1 data and instruction cache (vast majority of architectures). In this case, the program code always fits in L1 instruction cache since we optimize loop kernels only, whose code size is small; thus, upper level unified/shared caches, if exist, contain only data. On the other hand, if a unified L1 cache exists, memory management becomes very complicated.

Loop tiling is applied to category-1 and category-2a arrays only (Subsect. 3.1). The tiles of Category-1 arrays achieve data reuse and therefore they must definitely fit in data cache. Although category-2a tiles are not reused, they have to fit in data cache to avoid cache conflicts with the category-1 ones; in this way Category-1 tiles remain in data cache. Furthermore, Category-2b arrays cannot be partitioned into tiles as their elements are accessed in a 'random' way; this leads to a large number of data cache conflicts due to the cache modulo effect (especially for large arrays). To eliminate these conflicts, Rule 19 is introduced.

**Rule 19.** For all the Category-2b arrays, data cache size which equals to the size of one cache way is granted. In other words, an empty cache line is granted for each different modulo (with respect to the size of the cache) of these arrays memory addresses.

In this way the reused tiles remain in data cache.

**Rule 20.** For each register file inequality solution (schedule) produced so far, loop tiling is applied for all data cache memories and for all valid data cache tile sizes (ineq.(2)). All tile sizes do not satisfy ineq.(2), are not considered, decreasing the exploration space.

The data cache inequality is given by:

$$0.6 \times L_k \times \frac{(assoc - v)}{assoc} \le Tile_1 + \dots + Tile_n \le 1.1 \times L_k \times \frac{(assoc - v)}{assoc}$$

(2)

where  $L_k$  is the k-level data cache size, assoc is the data cache associativity (for an 8-way associative data cache, assoc = 8). v value is zero when no Category-2b array exist and one if at least one Category-2b array exists.  $Tile_i$  is the tile size of the ith array and  $Tile_i = T'_1 \times T'_2 \times T'_n \times ElementSize$ , where  $T'_i$  is the unroll factor of the *i* iterator and ElementSize is the size of each array's element in bytes ( $Tile_i$  refers only to Category-1 and Category-2a, array). The tiling inequality of Matrix-Matrix Multiplication algorithm is shown in Fig. 8, e.g.  $Tile_C = T_{ii} \times T_{jj}$  where  $T_{ii} = 10$  and  $T_{jj} = 15$ .

Regarding data cache tile sizes, they have to be multiples of the RF tiles sizes. Also, the tile sizes produced by L2 data cache, must be multiples of the tiles sizes produced by L1 data cache and RF (otherwise, a large number of addressing instructions is needed). Thus, the exploration space is further decreased.

The inequality bound values are not tight, i.e. 0.6 and 1.1, because smaller/larger tile sizes which divide exactly the array sizes, may achieve a lower number of addressing instructions (e.g. having an array of 2048 elements and only 800 fit in data cache, a tile size of 512 will achieve a lower number of addressing instructions than this of 800).

**Statement 12.** Each different set of  $T'_i$  values satisfying ineq.(2) gives a different schedule

**Statement 13.** All schedules satisfying ineq.(2) decrease the number of data cache / main memory accesses.

#### **Proof 9.** Likewise Statement 10.

Ineq.(2) gives a large number different tile sizes. However, the curve expressing the performance versus the tile sizes is smooth having a small number of change points. It is well known that such functions can be drastically speedup as it is not required to test all its points, i.e. tile sizes.

| <pre>//MVM kernel for (i=0; i! 100; i+=5) { reg1=0; reg2=0; reg3=0; reg4=0; reg5=0; for (j=0; j!=100; j++) {</pre>                                                                                                                                               | <pre>//write the new array, A'<br/>a=0;<br/>for (i=0; i! 100; i+=5)<br/>for (j=0; j!=100; j++) {<br/>A'[a]=A[i][j];<br/>a++;}</pre>                                                                                                                                                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>regB=X[j];<br/>reg1+=A[i][j] * regB;<br/>reg2+=A[i+1][j] * regB;<br/>reg3+=A[i+2][j] * regB;<br/>reg4+=A[i+3][j] * regB;<br/>reg5+=A[i+4][j] * regB;<br/>}<br/>Y[i] = reg1;<br/>Y[i+1]= reg2;<br/>Y[i+2]= reg3;<br/>Y[i+3]= reg4;<br/>Y[i+4]= reg5; }</pre> | <pre>//new MVM kernel<br/>a=-5;<br/>for (i=0; i! 100; i+=5) {<br/>reg1=0; reg2=0; reg3=0;<br/>reg4=0; reg5=0;<br/>for (j=0; j!=100; j++) {<br/>regB=X[j]; a+=5;<br/>reg1+=A[a] * regB;<br/>reg2+=A[a+1] * regB;<br/>reg3+=A[a+2] * regB;<br/>reg5+=A[a+4] * regB;<br/>}<br/>Y[i] = reg1; Y[i+1]= reg2;<br/>Y[i+2]= reg3; Y[i+3]= reg4;<br/>Y[i+4]= reg5; }</pre> |

Figure 9: Two potential output schedules for Matrix Vector Multiplication (MVM) algorithm. The code shown at the right is produced by changing the data array layout of that shown at the left.

**Statement 14.** The nesting level values of the new tiling iterators are found theoretically (no exploration is applied)

The nesting level values of the new (tiling) iterators are computed. For each different schedule produced by ineq.(2), The proposed methodology computes the total number of data accesses for all the different nesting level values and the best are selected.

The number of each array's accesses is found by:

$DataAccesses = n \times Tile\_size\_in\_elements \times Num\_of\_tiles$ , where n is the number of times each tile is fetched and equals to  $(q \times r)$ , where q is the number of iterations exist above the upper iterator of the array's equation and r is the number of iterations exist between the upper and the lower iterators of the array's equation.

It is important to say that tiling is applied for multiple index variable subscripts too (type2 equations), e.g. code shown in Fig. 4; the c iterator is tiled and all elements are fetched just once and in-order (consecutive memory locations). So far, compilers do not apply tiling in such cases.

#### 3.8. Find the optimum data array layouts and decrease the exploration space

At this step, the (near)-optimum data array layouts are found. In this way, the spatial data reuse is further utilized and the number of data cache misses is further decreased. For each schedule produced so far, the data array layouts change; both the schedules with the new data array layouts and not, are propagated to the next step. Both solutions are taken as by changing the data array layout the additional cost of re-writing the array to main memory may be high and the number of addressing instructions is increased. However, there are several cases that by changing the data array layout, the performance is increased, i.e. a) if the array whose layout is changed is reused several times, e.g. MMM, b) if the data array layout is precomputed, c) if the input data are produced by the current application at run time; in this case, the initialization and the change of the layout, are made together, decreasing the overhead.

By changing the data array layout, the tiles are written in consecutive main memory locations, i.e. just as they are fetched (tile-wise) according to the new schedule, to increase main memory page and data cache line utilization. In this way the number of the data cache misses is highly decreased. The multi-dimensional arrays are transformed into 1-d arrays having tile-wise data layout in main memory, e.g. Fig. 9. To change the data array layouts, the array subscripts are changed-simplified, i.e. for each array reference a new variable is replacing the previous subscript equation and extra addressing instructions are inserted; these addressing instructions increase/decrease the subscripts values.

**Rule 21.** If the number of the arrays is larger than the data cache associativity value, all the array tiles are stored into one array interleaved and tile-wise to eliminate the number of data cache misses due to the cache modulo effect. To do this, all the arrays are partitioned into identical number of tiles.

If the number of the arrays is larger than the data cache associativity value, the number of data cache misses is high even if the sum of the arrays size is smaller than the cache size. This is because at least one cache way contains more than one array's cache lines; this means that tiles do not remain in data cache as they conflict with each other due to the cache modulo effect. To overcome this problem, all array tiles are stored into one array interleaved and tile-wise (all tiles are written in consecutive main memory locations). In general, compilers and related works apply loop tiling without taking into account the data array layouts. In the case that the arrays are not written tile-wise in main memory, tiling cannot give a small number of data cache misses for multi-dimensional arrays because tiles are comprised by array sub-rows which are written in different main memory locations; this means that the sub-rows will conflict with each other and thus the tiles do not remain in data cache.

#### 3.9. Create final code and enumerate all solutions

At this step, all the solutions-schedules that have been produced so far, are transformed into C-code. These codes are compiled by the target architecture compiler and the binaries run to the target platform to find the fastest one. Each binary is run only once. Given the input size and the input data type (e.g. float, double), we do not use different input sets, as the proposed methodology optimizes applications which are not affected by the data values (see second paragraph of Section 3). It is important to say that if the input size or the input data type changes, the whole procedure is repeated, as the (near)-optimum schedule normally changes.

The number of the binaries tested depends on the application and on the hardware parameters; the number of binaries tested are from 1000 up to 100000 (the application execution time affects the compilation time). However, we can find a solution very close to the best very fast, by testing an orders of magnitude lower number of binaries. This is achieved by selecting only a few sets of different tile sizes for the data caches; performance is not highly affected by changing the data cache tile sizes, suffice they satisfy the proposed inequalities, i.e. tiles fit in the cache.

In the case that the schedule with the minimum number of data accesses for a specific memory is needed, the compilation time is very small as i) the procedure explained in Subsect. 3.7 is applied only for this memory (1 level of tiling) and ii) given that only the minimum number of data accesses is needed (the number of instructions is not taken into account here), it is possible to estimate their number, for each schedule, instead of running the schedules on the target platform.

#### 3.10. Motivation Example (Gaussian Blur)

Let us consider the C code shown in Fig. 11-(e) (Gaussian Blur) and an architecture of one level data cache. The equations produced are: (r =

| iteration spaces                                   |                                                        |  |

|----------------------------------------------------|--------------------------------------------------------|--|

| Different                                          | -                                                      |  |

| combinations                                       | Iteration spaces (common spaces occur)                 |  |

| eq.(4)-eq.(5)-eq.(6)                               | $S_1 = (r, c, mr, mc), S_2 = (c, r, mr, mc)$           |  |

| eq.(4)-eq.(6)-eq.(5)                               | $S_1, S_2, S_3 = (r, c, mc, mr), S_4 = (c, r, mc, mr)$ |  |

| eq.(5)-eq.(4)-eq.(6)                               | $S_5 = (r, mr, c, mc), S_6 = (r, mr, mc, c)$           |  |

|                                                    | $S_7 = (mr, r, c, mc), S_8 = (mr, r, mc, c)$           |  |

|                                                    | $S_9 = (c21, k1, c22, k2)$                             |  |

| eq.(5)-eq.(6)-eq.(4)                               | $S_5, S_6, S_7, S_8, S_9$                              |  |

| eq.(6)-eq.(4)-eq.(5)                               | $S_{10} = (mr, mc, r, c), S_{11} = (mr, mc, c, r)$     |  |

|                                                    | $S_{12} = (mc, mr, r, c), S_{13} = (mc, mr, c, r)$     |  |

| eq.(6)-eq.(5)-eq.(4)                               | $S_{10}, S_{11}, S_{12}, S_{13}$                       |  |

|                                                    |                                                        |  |

| Iteration spaces which are excluded                |                                                        |  |

| $P_1 = (r, mc, c, mr), P_2 = (r, mc, mr, c)$       |                                                        |  |

| $P_3 = (mc, r, c, mr), P_4 = (mc, r, mr, c)$       |                                                        |  |

| $P_5 = (c, mr, r, mc), P_6 = (c, mr, mc, r)$       |                                                        |  |

| $P_7 = (mr, c, r, mc), P_8 = (mr, c, mc, r)$       |                                                        |  |

| $P_{9} = (c, mc, r, mr), P_{10} = (c, mc, mr, r)$  |                                                        |  |

| $P_{11} = (mc, c, r, mr), P_{12} = (mc, c, mr, r)$ |                                                        |  |

| $P_{13} = (c22, k2, c21, k1)$                      |                                                        |  |

Table 2: Iteration spaces for the Gaussian Blur C-code.

c11, c = c12) (eq.(1)), (r + mr - 2 = c21, c + mc - 2 = c22) (eq.(2)), (mr = c31, mc = c32) (eq.(3)).

The proposed methodology processes the subscript equations one by one, for six different combinations, to create all the iteration spaces (Subsection 3.4 and Subsection 3.5). The iteration spaces created, are shown in Table 2  $(S_1 - S_{13})$ . Table 2 also shows the iteration spaces which are excluded  $(P_1 - P_{13})$ , decreasing the exploration space. The number of iteration spaces is further increased (Statement 8).

For each one of the  $S_1 - S_{13}$  iteration spaces, the register file size is utilized. Regarding  $S_1$ , four register file inequalities are produced. The first of the four is the following:

$0.8 \times RFs \le 3 + 2 + 2 + r' \times c' + 1 + mr' \le 1.2 \times RFs$ , if  $c \ne 1$  or  $r \ne 1$

A potential solution (r' = 2, c' = 2, mr' = 1) of the above RF inequality is shown at the left of Fig. 10.  $R_{in} = 1$  (only one register is used for this array) because of the Rule 15 and mc' = 1 because of the Rule 11. The first 3 values of the RF inequality correspond to the  $L_{iter}$ , Var and ws respectively (they are found after the register assignment);  $L_{iter} = 3$  because mr, mc and c iterators exist in the innermost loop, Var = 2 because addr1 and addr2 variables exist and ws = 2; the size of the ws depends on the target compiler and it is found approximately. The second inequality is given due to the Rule 15 and is the following:

$0.8 \times RFs \le 4 + 0 + 2 + 1 + 1 + 1 \le 1.2 \times RFs$ , if c = 1 and r = 1

$R_{mask} = 1$  because of the Rule 15.

Furthermore, if Rule 17 is applied the data reuse between different iterations (registers in0 - in5) is exploited too, giving the following inequality (a potential solution of this inequality is shown at the right of Fig. 10).

$0.8 \times RFs \leq 3 + 1 + 2 + r' \times c' + r' \times mr' \times c' + mr' \leq 1.2 \times RFs, \text{ if } c' \succ 1.2 \times RFs \text{ of } c' \geq 1.2 \times RFs$

The fourth inequality is produced if the *mask* array iterators are fully unrolled and all the array references are replaced by their constant values (Rule 18 - the *mask* array does not further exist). In this case the iteration space is reduced to  $S_1 = (r, c)$  and  $R_{out} = 1$ ,  $R_{in} = 1$ .

To sum up, all the different values satisfying the above inequalities are possible solutions. This is repeated for all the iteration spaces, i.e.  $S_1 - S_{13}$ .

All the schedules produced so far are further tiled according to the L1 data cache size, Subsect. 3.4 (solutions that utilize both the register file and the data cache and solution that utilize only the register file).

The L1 inequality is:

$0.6 \times L1 \le T_r \times T_c + (T_r + mr) \times (T_c + mc) + T_{mr} \times T_{mc} \le 1.1 \times L1$

All the tile sizes are multiples of the corresponding register file tile sizes. The nesting level values of the tiling iterators are computed as explained in Subsect.3.4.

Afterwards, all the schedules produced so far change their data array layouts (we examine the schedules with the new data array layouts and the schedules with the default data array layouts). Regarding Gaussian Blur, it is not performance efficient to change the data array layouts (for the vast majority of architectures). Finally, all the above schedules are compiled by the target compiler and they run at the target platform to find the fastest one.

```

A1.2)

A1.1)

for (row = 2; row < N-2; row++) {

for (row = 2; row < N-2; row+=2) {

for (col = 2; col < M-2; col+=6) {

for (col = 2; col < M-2; col+=2) {

out0=0;out1=0;out2=0;out3=0;out4=0;out5=0;

out0=0;out1=0;out2=0;out3=0;

for (mr=0; mr<5; mr++) {

for (mr=0; mr<5; mr++) {addr1=row+mr-2;</pre>

addr1=row+mr-2;

for (mc=0; mc<5; mc++) {

in0=in[addr1][col-2];

addr2=col+mc-2;

in1=in[addr1][col-1];

reg_mask=mask[mr][mc];

in2=in[addr1][col];

in3=in[addr1][col+1];

out0 += (in[addr1][addr2] * reg_mask) / 159;

in4=in[addr1][col+2];

out1 += (in[addr1][addr2+1] * reg_mask) / 159;

for (mc=0; mc<5; mc++) {

out2 += (in[addr1+1][addr2] * reg_mask) / 159;

reg_mask=mask[mr][mc];

out3 += (in[addr1+1][addr2+1] * reg_mask) / 159;

in5=in[addr1][col+3+mc];

}}

out0 += (in0 * reg_mask) / 159;

out[row][col]=out0;

out1 += (in1 * reg_mask) / 159;

out[row][col+1]=out1;

out2 += (in2 * reg_mask) / 159;

out[row+1][col]=out2;

out3 += (in3 * reg_mask) / 159;

out[row+1][col+1]=out3;

out4 += (in4 * reg_mask) / 159;

}}

out5 += (in5 * reg_mask) / 159;

in0=in1; in1=in2; in2=in3; in3=in4; in4=in5;

out[row][col]=out0;

out[row][col+1]=out1;

out[row][col+2]=out2;

out[row][col+3]=out3;

out[row][col+4]=out4;

out[row][col+5]=out5;

}

}

```

Figure 10: Two potential solutions of the example shown in Subsect. 3.10.