## A high-performance matrix-matrix multiplication methodology for CPU and GPU architectures

KELEFOURAS, Vasileios <http://orcid.org/0000-0001-9591-913X>, KRITIKAKOU, Angeliki, MPORAS, Iosif and VASILEIOS, Kolonias

Available from Sheffield Hallam University Research Archive (SHURA) at:

http://shura.shu.ac.uk/18333/

This document is the author deposited version. You are advised to consult the publisher's version if you wish to cite from it.

## **Published version**

KELEFOURAS, Vasileios, KRITIKAKOU, Angeliki, MPORAS, Iosif and VASILEIOS, Kolonias (2016). A high-performance matrix-matrix multiplication methodology for CPU and GPU architectures. Journal of Supercomputing, 72 (3), 804-844.

## Copyright and re-use policy

See http://shura.shu.ac.uk/information.html

## A high performance Matrix-Matrix Multiplication Methodology for CPU and GPU architectures

Vasilios Kelefouras, Angeliki Kritikakou, Iosif Mporas, Vasilios Kolonias

the date of receipt and acceptance should be inserted later

Abstract Current compilers cannot generate code that can compete with hand-tuned code in efficiency, even for a simple kernel like Matrix-Matrix Multiplication. A key step in program optimization is the estimation of optimal values for parameters such as tile sizes and number of levels of tiling. The scheduling parameter values selection is a very difficult and time-consuming task since parameter values depend on each other; this is why they are found by using searching methods and empirical techniques. To overcome this problem, the scheduling sub-problems must be optimized together, as one problem and not separately.

In this paper a Matrix-Matrix Multiplication methodology is presented where the optimum scheduling parameters are found by decreasing the search space theoretically while the major scheduling sub-problems are addressed together as one problem and not separately according to the hardware architecture parameters and input size; for different hardware architecture parameters and/or input sizes, a different implementation is produced. This is achieved by fully exploiting the software characteristics (e.g., data reuse) and hardware architecture parameters (e.g., data caches sizes and associativities), giving high quality solutions and a smaller search space. This methodology refers to a wide range of CPU and GPU architectures.

**Keywords** Matrix-Matrix Multiplication, Data reuse, optimization, SIMD, memory hierarchy, loop tiling

#### **1** Introduction

Matrix-Matrix Multiplication (MMM) is an important kernel in most varied domains and application areas. Its performance is of great practical importance and it highly depends on memory management; the most performance critical

Address(es) of author(s) should be given

sub-problems are these of finding the schedules with the minimum numbers of i) L1 data cache accesses, ii) L2 data cache accesses, iii) L3 data cache accesses, iv) main memory data accesses, v) addressing instructions. The above sub-problems depend on each other (e.g., a decrease on the number of L2 data cache accesses will consequently increase the number of L1 data cache accesses) and this is why they should be addresses together as one problem and not separately (in [1], a methodology for Matrix-Vector Multiplication is given).

Toward this, much research has been done, either to simultaneously optimize only two phases, e.g., register allocation and instruction scheduling (the problem is known to be NP-complete) [2] [3] or to apply predictive heuristics [4] [5]. Nowadays compilers and related works, apply either iterative compilation techniques [6] [7] [8] [9], or both iterative compilation and machine learning compilation techniques to restrict the configurations' search space [10] [11] [12] [13] [14] [15]. A predictive heuristic tries to determine a priori whether or not applying a particular optimization will be beneficial, while at iterative compilation, a large number of different versions of the program are generated-executed by applying transformations and the fastest version is selected; iterative compilation provides good results, but requires extremely long compilation times.

The state of the art (SOA) hand/self-tuning libraries for linear algebra, such as ATLAS [16], OpenBLAS [17], Eigen [18], Intel\_MKL [19], PHiPAC [20] and a few of the many noteworthy papers from the past such as [21] [22] [23] [24] for CPUs and [25] [26] for GPUs, do not give a theoretical solution; instead, they find the performance critical parameter values mostly by searching and by using heuristics and empirical techniques. The selection of the parameter values is a difficult and time consuming task for two reasons. First, many parameters have to be taken into account, such as the number of the levels of tiling, tile sizes, loop unroll depth, software pipelining strategies, register allocation, code generation, data reuse, loop transformations. Second, the optimum parameters for two slightly different architectures are different. Such a case is MMM algorithm, which is a major kernel in linear algebra and also the topic of this paper. In this paper the optimum scheduling parameters are found by decreasing the search space theoretically, for a wide range of CPU (including multi-cores) and GPU architectures.

A former MMM methodology for CPUs that support SIMD was introduced in [27]; the major contribution of [27] is that it addresses the major software and hardware parameters together, as one problem and not separately. This paper, extends [27] at four ways. First, the search space is decreased theoretically by applying static performance estimation. Second, this paper extends [27] to a wide range of computer architectures; this methodology has been extended to GPU architectures, to CPU architectures without SIMD unit and to CPU architectures different than those of the general purpose CPUs, e.g., microcontrollers, smaller processors with one level of data cache, processors with direct mapped data cache. Third, this methodology takes into account more hardware architecture parameters (the memories' latencies, the data cache line size, the number, the latencies and the type of the CPU function units, the number of the load/store units) and software characteristics (number of matrix operations, number of addressing instructions). Fourth, the proposed methodology, due to the major contribution of number three above gives a smaller search space, a smaller code size and a smaller compilation time, as it does not test a large number of alternative schedules.

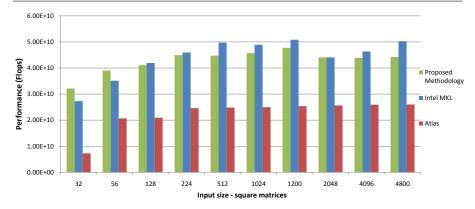

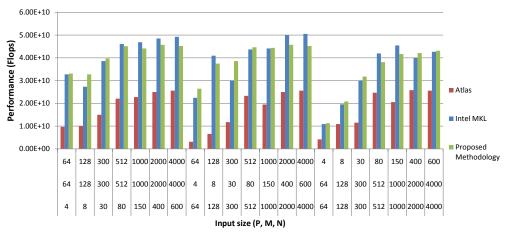

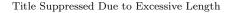

The proposed methodology is compared with the state of the art software libraries of ATLAS and Intel\_MKL. Although a performance comparison with Intel\_MKL is unfair, a detailed experimental analysis has been made as it is the fastest MMM library in the world for Intel general purpose processors. A performance comparison with Intel\_MKL is unfair for two reasons. First, Intel\_MKL developers have access to all the Intel processor architecture details which we do not, e.g., victim cache, hardware prefetchers; this is why Intel\_MKL library is the fastest library on Intel processors only. Second, Intel\_MKL loop kernels are written in assembly code while our method in C (assembly code is always more efficient); Intel developers write assembly code to deal with the low level transformations, e.g., register allocation, instruction selection and instruction scheduling. The proposed methodology lies at a higher level of abstraction and it is used to wide range of computer architectures. Implementing the proposed methodology in assembly code is beyond the scope of this paper and thus the low level transformations are applied by the target compiler (which is less efficient). The scope of this paper is not to provide the peak-performance MMM implementations, but to analytical give the architecture dependent high level transformation parameters (e.g., tile sizes) that achieve peak-performance. We strongly believe that if could modify the MKL library scheduling parameters according to the proposed methodology, an even higher performance would be achieved.

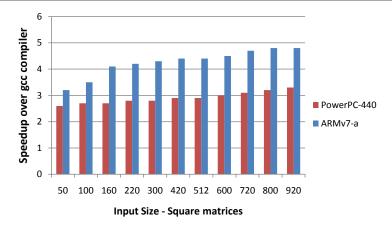

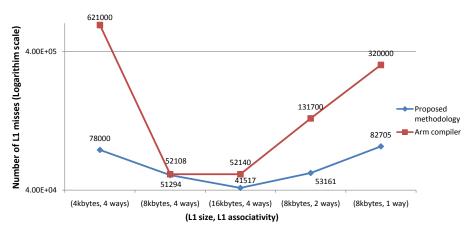

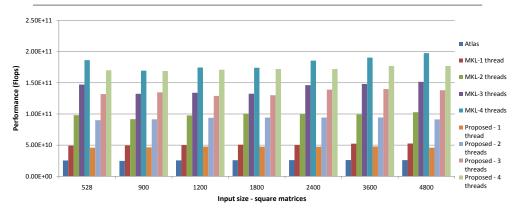

The proposed methodology is compared to the SOA libraries of ATLAS and Intel\_MKL for CPUs and cuBLAS for GPUs. The evaluation is done by using Intel Xeon CPU E3-1241 v3, Pentium Intel i7-2600K, Valgrind tool [28], ARMv7-a on GEM5 simulator, PowerPC-440 on Xilinx FPGA Virtex-5, Nvidia GeForce GTX-580, Gem5 [29] and SimpleScalar simulator [30].

The remainder of this paper is organized as follows. In Sect. 2, the related work is given. The proposed methodology is presented in Sect. 3. In Sect. 4, the experimental results are presented while Sect. 5 is dedicated to conclusions.

#### 2 Related Work

The problem of speeding up MMM is studied the last decates. A historical perspective is given in [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41]; these works present how hardware and software can work on scalable multi-processor systems for matrix algorithms.

ATLAS [16] [42] [43] [44] [45] is an implementation of a high performance software production/maintenance called Automated Empirical Optimization of Software (AEOS). In an AEOS enabled library, many different ways of performing a given kernel operation are supplied, and timers are used to empirically determine which implementation is best for a given architectural platform. ATLAS uses BLAS implementations. The BLAS (Basic Linear Algebra Subprograms) are routines that provide standard building blocks for performing basic vector and matrix operations. Intel Math Kernel Library (Intel MKL) [19] is a computing math library of highly optimized, extensively threaded routines for applications that require maximum performance. Intel\_MKL library has been written by Intel and this is why it performs the best for Intel processors only. MKL kernels have been written in assembly for maximum performance. During the installation of ATLAS and Intel\_MKL, on the one hand an extremely complex empirical tuning step is required, and on the other hand a large number of compiler options are used, both of which are not included in the scope of this paper. Although ATLAS is one of the SOA libraries for MMM algorithm, its techniques for supplying different implementations of kernel operations concerning memory management are empirical and hence it does not provide any methodology for it.

Regarding MMM implementations for one core, many related works exist such as [22,23,21,46–52]. In [22] BLIS is presented; BLIS is a framework for rapid instantiation of BLAS. In [23], BLIS extends the GotoBLAS approach to implement peak performance MMM implementations. In [21] a systematic analysis of the high-level issues affecting the design of high-performance matrix multiplication is given. Reference [24] gives a significant theoretical background on finding the optimum scheduling parameters, but it refers to specific CPUs architectures only. In [51], analytical models are presented for estimating the optimum tile size values assuming only fully associative caches, which in practice are very rare. The aforementioned works refer to specific CPU architectures only and find the scheduling parameters mostly by using empirical techniques.

Although loop-tiling is necessary to achieve high performance, the above works do not find the tile sizes and the number of levels of tiling, by taking into account the cache sizes, their associativities and the data arrays layouts, together as one problem; instead searching is applied. Let us give an example. According to ATLAS [16] (only cache size is taken into account), the size of three rectangular tiles (one for each matrix) must be smaller or equal to cache size; however, the elements of these tiles are not written in consecutive main memory locations and thus they do not use consecutive data cache locations; this means that having a set-associative cache, they cannot simultaneously fit in data cache due to the cache modulo effect. Moreover, even if the tiles elements are written in consecutive main memory locations (different data array layout), the three tiles cannot simultaneously fit in data cache if the cache is two-way associative or direct mapped. We will show that loop tiling is efficient only when cache size, cache associativity and data array layouts, are addressed together as one problem and not separately.

There are several works optimizing MMM for many cores [53-64]. The fastest implementations are given in [23] where MMM is parallelized on Intel Xeon Phi and on IBM Blue Gene/Q; an analysis is made on which loop is

going to be parallelized. The vast majority of previous works regarding multicore architectures, deal with cluster architectures; they partition the MMM problem into many distributed memory computers (distributed memory refers to a multiple-processor computer system in which each processor has its own private memory). SRUMMA [64] describes one of the best parallel algorithm which is suitable for clusters and scalable shared memory systems. Although SRUMMA minimizes the communication contention between CPUs, it does not optimize the MMM problem for one CPU (it runs the *cblas\_sgemm* AT-LAS optimized routine). Furthermore, about half of the above works, use the Strassen's algorithm [65] to partition the MMM problem into many multi-core processors; Strassen's algorithm minimizes the number of the multiplication instructions sacrificing the number of add instructions and data locality. The MMM code for one core, is either given by Cilk tool [66] or by cblas\_sgemm routine of ATLAS. At last, [67] and [68] show how shared caches can be utilized. All the above works, are empirical techniques and do not provide a theoretical model.

Regarding GPUs, several related works exist such as [25] [26] [69] [70] [71] [72] [73] [74] [75] [76]. Reference [26] show how to modify the MAGMA GEMM kernels in order to use more efficient the Fermi architecture. [69] presents a method for producing MMM kernels tuned only for a specific architecture, through a canonical process of heuristic autotuning, based on generation of multiple code variants and selecting the fastest ones through benchmarking. [71] provide implementations of Strassen's MMM algorithm as well as of Winograd's variant; they show that only for square matrices of very large sizes  $(16384 \times 16384)$  achieve 33% speedup over *cblas\_sgemm* (ATLAS routine for data of type float) and 21% over *cblas\_dgemm* (ATLAS routine for data of type double). [73] presents an in-depth study to reveal interesting trade-offs between shared memory and the hardware-managed L1 data caches for MMM. [74] investigates different performance techniques such as tiling, memory coalescing, prefetching, and loop unrolling, in trying to evaluate which method is the most efficient. [75] provides theoretical analysis why performance drawbacks appear for specific problem sizes when using cache memories. Finally, in [76], different data arrays layouts are evaluated, such Z-Morton and X-Morton. All the above works, are empirical techniques and do not give a methodology.

In contrast to the proposed methodology, the above works find tile sizes mostly by searching, since they do not exploit all the h/w and the s/w constraints. However, if these constraints are fully exploited, the optimum solution can be found by enumerating only a small number of solutions; in this paper, tile sizes are given by inequalities which contain the cache sizes and cache associativities.

#### 3 Proposed Methodology

In this paper a Matrix-Matrix Multiplication (MMM) methodology is presented where the sub-problems of finding the schedules with the minimum for (i=0; i<N; i++) for (j=0; j<M; j++) for (k=0; k<P; k++) C[i][j] += A[i][k] \* B[k][j];

Fig. 1 MMM unoptimized code

numbers of i) L1 data cache accesses, ii) L2 data cache accesses, iii) L3 data cache accesses, iv) main memory data accesses, v) addressing instructions, are addressed together as one problem and not separately. We find the scheduling parameters that achieve best performance by fully exploiting the software characteristics (production-consumption, data reuse and MMM parallelism) and the major hardware architecture parameters, i.e., the a) number of the cores, b) number of memories, c) size of each memory, d) number of registers, e) associativities of data cache memories, f) memories' latencies, e) SSE instruction latencies. For different hardware architecture parameters, different schedules for MMM are created.

It is well known that the search space, i.e., all different MMM implementations, is infinite and it cannot be searched. In this paper, we find the best schedules among these that exist in our search space. The search space being addressed consists of all the high level transformations that affect MMM performance including all different transformation orderings and all different transformation parameters (e.g., tile sizes); these are the number of levels of tiling, loop tiling for all the memories, register blocking, loop interchange, loop unroll, scalar replacement, data array layouts. The search space we use does not contain low level transformations, e.g., instruction scheduling to decrease the number of pipeline stalls (this is beyond the scope of this paper). Although, the low level transformations are not taken into account the search space being addressed is enormous and it is impractical to be searched, e.g., if the number of different tile sizes for each loop is 100, the number of all different schedules that apply loop tiling for L1 and L2 is  $(6! \times 100^6) = 7.2 \times 10^{14}$  (two levels of tiling add 6 new loops); if we consider that the compilation time of each schedule is 1 sec and given that  $1sec = 3.1 \times 10^{-8}$  years, the compilation time is very big; if we include all the above transformations, the number of the schedules becomes enormous. Given that the above transformations are strongly interdependent, the only way to decrease the search space is to be addressed together as one problem and not separately.

For the reminder of this paper, the three arrays names and sizes are that shown in Fig. 1, i.e.,  $C = C + A \times B$ , where C, A and B are of size  $N \times M$ ,  $N \times P$  and  $P \times M$ , respectively.

MMM performance depends on the time needed to the i) data to be loaded/stored (C, A and B arrays), ii) matrix operations to be executed, iii) addressing instructions to be executed (integer instructions only), iv) instructions to be loaded from instruction cache.

**Regarding (iv)**, the time needed for the instructions to be fetched from L1 instruction cache, is lower than the (i)-(iii) values above, since no instruction

cache conflicts occur; this is because the MMM code size is small and it always fits in L1 instruction cache. It is important to say that all the todays processors contain separate L1 data and instruction caches and thus we can assume that shared/unified L2/L3 caches, contain only data. Architectures with unified L1 caches are not discussed in this paper.

Eq. 1 and eq. 2 approximate the MMM execution time; eq. 1 holds for architectures that matrix operations and addressing operations are executed in parallel (we assume that the arrays are floating point numbers) and eq. 2 holds for architectures that do not (either no floating point Arithmetic Logic Unit (ALU) exists or the arrays are of type integer); in most architectures the load/store unit and the execution unit work in parallel.

$$T_{total} = max(T_{data}, T_{matrix-operations}, T_{addressing})$$

(1)

$$T_{total} = max(T_{data}, T_{matrix-operations} + T_{addressing})$$

(2)

Regarding the time needed to execute the matrix operations  $(T_{matrix-operations})$ , it is given by the following two equations, i.e., eq. 3 and eq. 4; eq. 3 is used in the case there is a separate multiplication unit working in parallel with the ALU and eq. 4 otherwise (the number of multiplications is larger than the number of additions).  $T_{matrix-operations}$  is a constant number.

$$T_{matrix-operations} = \frac{Mul_{lat} \times (N \times M \times P)}{Num_{Mult}}$$

(3)

$$T_{matrix-operations} = \frac{Mul_{lat} \times (N \times M \times P)}{Num_{Mult}} + \frac{Add_{lat} \times (N \times M \times (P-1))}{Num_{ALU}}$$

(4)

where  $Mul_{lat}$ ,  $Add_{lat}$ ,  $Num_{Mult}$  and  $Num_{ALU}$  are the latencies and the numbers of the multiplication and ALU units, respectively.

Regarding addressing instructions, the  $T_{addressing}$  value is not a constant number; it depends on the implementation/schedule. The number of addressing instructions is decreased when a) the number of the levels of tiling is decreased, b) the tile sizes are increased, c) more array references are assigned into available registers, d) loop unroll factor is increased.

**Regarding load/store instructions**,  $T_{data} \succ T_{matrix-operations}$  in most cases, i.e., if the data do not fit in L1 data cache. On the contrast to the  $T_{matrix-operations}$ ,  $T_{data}$  and  $T_{addressing}$  are not constant numbers; they depend on the schedule used. Also,  $T_{data}$  and  $T_{addressing}$  depend on each other; normally, by increasing  $T_{data}$  value,  $T_{addressing}$  is decreased and vice versa, while the number of the matrix operations remains constant.

To summarize, given that  $T_{matrix-operations}$  is a constant number and in most cases  $T_{matrix-operations} \prec T_{addressing}$  and  $T_{matrix-operations} \prec T_{data}$ , MMM performance can be increased only by minimizing both  $T_{data}$  and  $T_{addressing}$ values; given that  $T_{data}$  and  $T_{addressing}$  are interdependent, high performance is achieved, only for both low  $T_{data}$  and  $T_{addressing}$  values. This is because the separate optimization of the  $T_{data}$  and  $T_{addressing}$  values, gives different schedules which cannot coexist, as by refining one, degrading another.

$T_{data}$  value is found by decreasing the search space theoretically according to the memory hierarchy architecture parameters. For different cache hierarchy architecture, a different equation that estimates  $T_{data}$  value is created, e.g., for one level of data cache architecture  $T_{data}$  value is given by eq.7. These equations give theoretically the tile sizes that achieve a minimum  $T_{data}$  value.

As far the  $T_{addressing}$  value is concerned, it cannot be found theoretically. This is because the number of the addressing instructions highly depends on the target compiler and its optimizations, e.g., unroll factor values. Thus, we find all the schedules achieving a low  $T_{data}$  value and only these that achieve a low  $T_{addressing}$  value are selected; all the schedules achieving a low  $T_{data}$  value are converted into assembly code (by using the target compiler) and their number of addressing instructions is measured. Then, all schedules achieving both low  $T_{data}$  and  $T_{addressing}$  values are compiled and run to the target platform to find the fastest.

Instead of searching all different MMM schedules to find the best which is impractical because their number is enormous, only a small number is searched. The exploration space is decreased by orders of magnitude since we test only solutions that are close to the best; we test only these schedules achieving both low  $T_{data}$  and  $T_{addressing}$  values. In this way, the compilation time is drastically decreased.

A different schedule is emerged for different types of CPUs, CPU parameters and input size. The reminder of this paper presents all these schedules. The proposed methodology for CPUs with one core is given in subsection 3.1, while the proposed methodology for CPUs with more than one cores is given in subsection 3.2. The proposed methodology for GPU architectures is given in subsection 3.3.

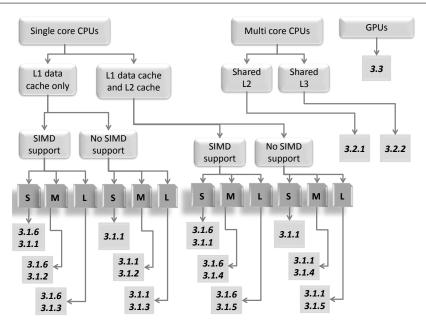

A different schedule is given according to the a) number and the type of the cores, b) number of cache memories, c) cache sizes, d) input sizes and e) whether an SIMD unit is supported or not (Fig. 2). In Fig. 2, 'S', 'M' and 'L' indicate small, medium and large input sizes, respectively. Also, the 3.1.1-3.1.6, 3.2.1, 3.2.2 and 3.3 values that are shown in Fig. 2 refer to the Subsect. 3.1.1 - Subsect. 3.1.6, Subsect.3.2.1, Subsect.3.2.2 and Subsect.3.3, respectively and they are given below.

#### 3.1 CPUs with one core

A different schedule is given according to the a) number of data cache memories, b) cache sizes, c) input sizes and d) whether an SIMD unit is supported or not (Fig. 2). The Subsect. 3.1.1 - Subsect. 3.1.6 which are shown in Fig. 2, are given below.

Fig. 2 All different MMM cases. The last nodes refer to the Subsections that provide the appropriate schedules. 'S', 'M' and 'L' indicate small, medium and large input sizes, respectively.

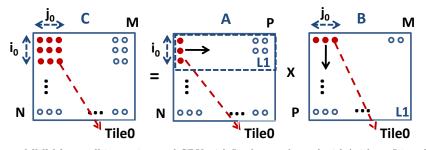

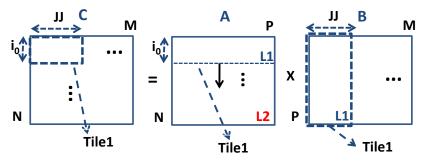

Fig. 3 MMM for small input sizes and CPU with L1 data cache and with/without L2 cache

# $3.1.1\ Small\ input\ sizes\ and\ CPU\ with\ L1\ data\ cache\ and\ with/without\ L2\ cache$

For small input sizes, i.e., if all the data of B, the data of  $2 \times i_0$  rows of A and the data of  $2 \times i_0$  rows of C fit in different ways of L1 data cache (ineq. 5), the scheduling given below is used (Fig. 3).

$$\frac{L1 \times (assoc - k1 - k2)}{assoc} \ge P \times M \times element\_size, \tag{5}$$

where  $k1 = \lceil \frac{2 \times i_0 \times P \times element\_size}{L1/assoc} \rceil \leq \frac{assoc}{4}, k2 = \lceil \frac{2 \times i_0 \times M \times element\_size}{L1/assoc} \rceil \leq \frac{assoc}{4}$ , L1 is the size of the L1 data cache memory in bytes,  $element\_size$  is the size of the arrays elements in bytes and assoc is the L1 associativity

$(assoc \neq 1)$ .  $P \times M$  is the size of the B array in elements. k1 is an integer and it gives the number of L1 data cache lines with identical L1 addresses used for  $2 \times i_0$  rows of A; k2 is an integer and it gives the number of L1 data cache lines with identical L1 addresses used for  $2 \times i_0$  rows of C; for the reminder of this paper we will more freely say that we use k1 cache ways for A, k2 ways for C and (assoc - k1 - k2) cache ways for B (in other words A, B and C are written in separate data cache ways). In the case that  $P \times M \gg 2 \times i_0 \times P + 2 \times i_0 \times M$ or in the case that a two-way set associative cache exists, 1 cache way is used for both A and C. In the case that assoc = 1, a slightly different schedule is given at the last paragraph of Subsect. 3.1.3.

The optimum production-consumption (when an intermediate result is produced it is directly consumed-used) of array C and the sub-optimum data reuse of array A have been selected by splitting the arrays into tiles according to the number of the registers, eq. 6 (Fig. 3). All different  $i_0, j_0$  combinations satisfying ineq. 6 give a feasible solution.

$$RF_{FP} \ge i_0 \times j_0 + i_0 + j_0$$

(6)

where  $RF_{FP}$  is the number of the available floating point registers. In the case that C,A and B contain integer numbers, ineq. 6 contains the addressing variables and the loop iterators.

We use  $i_0 \times j_0$  registers for C,  $i_0$  for A and  $j_0$  for B (Fig. 3). We assign registers across i, j iterators (Fig. 1) and not across k iterator because k is the innermost one (it is changes its value in each iteration and thus no data reuse is achieved).

The schedule is shown in Fig. 3. First, the first  $i_0$  elements of the first column of A are multiplied by the first  $j_0$  elements of the first row of B. Then, the first  $i_0$  elements of the second column of A are multiplied by the first  $j_0$  elements of the second row of B etc. This is repeated until the first  $i_0$  rows of A have been multiplied by the first  $j_0$  columns of B; then the same  $i_0$  rows of A as above, are multiplied by the next  $j_0$  columns of B etc.

Given that each row of A is multiplied by all columns of B, both A and B are reused M and N times, respectively; thus, they have to remain in L1 data cache. To do this, the cache lines of A and B must be written in L1 without conflict with each other and also with C.  $2 \times i_0$  rows of A and C have to fit in L1, the current processed  $i_0$  rows and the next ones, for two reasons. First, except from the first  $i_0$  rows of A and C, also the second  $i_0$  rows must be loaded in L1, without conflict with B. Second, when the third  $i_0$  rows of A are multiplied by B, the L1 cache lines containing the first  $i_0$  rows are replaced by the third  $i_0$  rows ones according to the LRU cache replacement policy, without conflict with the B ones. This is achieved by storing the rows of A, C and the columns of B in consecutive main memory locations and by using  $(k1 \times \frac{L1}{assoc})$  L1 memory size for A,  $(k2 \times \frac{L1}{assoc})$  for C and  $((assoc - k1 - k2) \times \frac{L1}{assoc})$  for B (ineq. 5). We can more freely say that this is equivalent to using k1 cache ways for A, k2 cache ways for C and (assoc - k1 - k2) cache ways for B. An empty cache line is always granted for each different modulo (with respect to

Table 1 Number of data accesses in memory hierarchy

|                              |                                                                       | ction 3.1.1 cas                                            | se                                                         |  |  |  |  |  |  |

|------------------------------|-----------------------------------------------------------------------|------------------------------------------------------------|------------------------------------------------------------|--|--|--|--|--|--|

|                              |                                                                       | neq.5 holds                                                |                                                            |  |  |  |  |  |  |

|                              |                                                                       | optimization                                               |                                                            |  |  |  |  |  |  |

|                              | С                                                                     | A                                                          | В                                                          |  |  |  |  |  |  |

| L1                           | $N \times M$                                                          | $N \times P \times M$                                      | $P \times M \times N$                                      |  |  |  |  |  |  |

| DDR                          | $N \times M$                                                          | $N \times P$                                               | $P \times M$                                               |  |  |  |  |  |  |

| Schedule in Subsection 3.1.1 |                                                                       |                                                            |                                                            |  |  |  |  |  |  |

|                              | С                                                                     | А                                                          | В                                                          |  |  |  |  |  |  |

| L1                           | $N \times M$                                                          | $\frac{N \times P \times M}{i_0}$                          | $\frac{P \times M \times N}{i_0}$                          |  |  |  |  |  |  |

| DDR                          | $N \times M$                                                          | $\frac{j_0}{N \times P}$                                   | $P \times M$                                               |  |  |  |  |  |  |

|                              | Subsection 3.1.2 case                                                 |                                                            |                                                            |  |  |  |  |  |  |

|                              | Ineq.6 holds                                                          |                                                            |                                                            |  |  |  |  |  |  |

|                              |                                                                       | optimization                                               |                                                            |  |  |  |  |  |  |

|                              | С                                                                     | A                                                          | В                                                          |  |  |  |  |  |  |

| L1                           | $N \times M$                                                          | $N \times P \times M$                                      | $P \times M \times N$                                      |  |  |  |  |  |  |

| DDR                          | $N \times M$                                                          | $N \times P$                                               | $P \times M \times N$                                      |  |  |  |  |  |  |

|                              |                                                                       | in Subsection 3                                            |                                                            |  |  |  |  |  |  |

|                              | С                                                                     | А                                                          | В                                                          |  |  |  |  |  |  |

| L1                           | $N \times M$                                                          | $\frac{N \times P \times M}{j_0}$                          | $\frac{P \times M \times N}{i_0}$                          |  |  |  |  |  |  |

| DDR                          | $N \times M$                                                          | $N \times P$                                               | $\frac{i_0}{P \times M \times N}$                          |  |  |  |  |  |  |

|                              | Subsec                                                                | ction 3.1.3 cas                                            | se                                                         |  |  |  |  |  |  |

|                              |                                                                       | 6 does not hold                                            |                                                            |  |  |  |  |  |  |

|                              |                                                                       | optimization                                               |                                                            |  |  |  |  |  |  |

|                              | С                                                                     | А                                                          | В                                                          |  |  |  |  |  |  |

| L1                           | $N \times M$                                                          | $N \times P \times M$                                      | $P \times M \times N$                                      |  |  |  |  |  |  |

| DDR                          | $N \times M$                                                          | $N \times P \times M$                                      | $P \times M \times N$                                      |  |  |  |  |  |  |

|                              | Schedule                                                              | in Subsection 3                                            |                                                            |  |  |  |  |  |  |

|                              | С                                                                     | A                                                          | В                                                          |  |  |  |  |  |  |

| L1                           | $\frac{N \times M \times P}{KK}$                                      | $\frac{N \times P \times M}{j_0}$                          | $\frac{P \times M \times N}{io}$                           |  |  |  |  |  |  |

| DDR                          | $\frac{N \times M \times P}{KK}$                                      | $N \times P$                                               | $\frac{i_0}{P \times M \times N}$                          |  |  |  |  |  |  |

|                              |                                                                       | ction 3.1.4 cas                                            | se 11                                                      |  |  |  |  |  |  |

|                              | Iı                                                                    | neq.7 holds                                                |                                                            |  |  |  |  |  |  |

|                              | No                                                                    | optimization                                               |                                                            |  |  |  |  |  |  |

|                              | С                                                                     | A                                                          | В                                                          |  |  |  |  |  |  |

| L1                           | $N \times M$                                                          | $N \times P \times M$                                      | $P \times M \times N$                                      |  |  |  |  |  |  |

| L2                           | $N \times M$                                                          | $N \times P$                                               | $P \times M \times N$                                      |  |  |  |  |  |  |

| DDR                          | $N \times M$                                                          | $N \times P$                                               | $P \times M$                                               |  |  |  |  |  |  |

|                              |                                                                       |                                                            |                                                            |  |  |  |  |  |  |

|                              |                                                                       | in Subsection 3                                            |                                                            |  |  |  |  |  |  |

|                              | С                                                                     | A<br>$N \times P \times M$                                 | В                                                          |  |  |  |  |  |  |

| L1                           | $N \times M$                                                          |                                                            | $\frac{P \times M \times N}{i_0}$                          |  |  |  |  |  |  |

| L2                           | $N \times M$                                                          | $\frac{J_0}{N \times P \times M}$                          | $P \times M$                                               |  |  |  |  |  |  |

| DDR                          | $N \times M$                                                          | $N \times P$                                               | $P \times M$                                               |  |  |  |  |  |  |

|                              |                                                                       |                                                            |                                                            |  |  |  |  |  |  |

|                              |                                                                       | ction 3.1.5 cas                                            | se                                                         |  |  |  |  |  |  |

|                              |                                                                       | 7 does not hold                                            |                                                            |  |  |  |  |  |  |

|                              |                                                                       | optimization                                               |                                                            |  |  |  |  |  |  |

|                              | С                                                                     | A                                                          | В                                                          |  |  |  |  |  |  |

| L1                           | $N \times M$                                                          | $N \times P \times M$                                      | $P \times M \times N$                                      |  |  |  |  |  |  |

| L2                           | $N \times M$                                                          | $N \times P \times M$                                      | $P \times M \times N$                                      |  |  |  |  |  |  |

| DDR                          | $N \times M$                                                          | $N \times P \times M$                                      | $P \times M \times N$                                      |  |  |  |  |  |  |

|                              |                                                                       |                                                            |                                                            |  |  |  |  |  |  |

|                              | Schedule in Subsection 3.1.5                                          |                                                            |                                                            |  |  |  |  |  |  |

| - T -                        | C<br><u><math>N \times M \times P</math></u>                          | A<br>$N \times P \times M$                                 | $B = P \times M \times N$                                  |  |  |  |  |  |  |

| L1                           | $\frac{\frac{N \times M \times I}{KK}}{\frac{N \times M \times P}{}}$ | $\frac{N \times I \times M}{j_0}$<br>$N \times P \times M$ | $\frac{I \times M \times N}{i_0}$<br>$P \times M \times N$ |  |  |  |  |  |  |

| L2                           | KK K                                                                  |                                                            |                                                            |  |  |  |  |  |  |

| DDR                          | $\frac{N \times M \times P}{KK}$                                      | $N \times P$                                               | $\frac{P \times M \times N}{II}$                           |  |  |  |  |  |  |

|                              |                                                                       |                                                            |                                                            |  |  |  |  |  |  |

|                              |                                                                       |                                                            |                                                            |  |  |  |  |  |  |

the size of the cache) of A, C and B memory addresses. It is important to say that if we use  $L1 \ge (P \times M + 2 \times i_0 \times P + 2 \times i_0 \times M) \times element\_size$  instead of ineq. 5, the number of L1 misses will be much larger because A, B and C cache lines would conflict with each other.

The time needed for the array elements to be loaded/stored, is approximated by eq. 7 and Table 1.

$$T_{data} = max(\frac{L1_{load\_lat} \times L1_{loads} + L1_{store\_lat} \times L1_{stores}}{L1_{ports}},$$

$$\frac{DDR_{load\_lat}}{line_{L1}} \times DDR_{loads} + DDR_{store\_lat} \times \frac{DDR_{stores} \times \lceil j_0 / line_{L1} \rceil}{j_0})$$

(7)

where  $L1_{load\_lat}$ ,  $DDR_{load\_lat}$ ,  $L1_{store\_lat}$ ,  $DDR_{store\_lat}$  are the L1 and DDR load and store latencies, respectively.  $L1_{loads}$ ,  $DDR_{loads}$ ,  $L1_{stores}$ ,  $DDR_{stores}$ , are the numbers of loads and stores occur for each memory and they are shown in Table 1.  $line_{L1}$  is the number of elements each L1 cache line contains and  $L1_{ports}$  is the number of L1 load/store ports. Without loss of generality, in eq. 7, we assume a memory architecture that only one L1 cache line is replaced at a time; if more than one cache lines are replaced in parallel, then eq. 7 is changed accordingly.

Regarding the number of DDR writes,  $\lceil j_0/line_{L1} \rceil$  L1 data cache lines are written to main memory for each  $j_0$  elements of C. For data cache architectures where reads and writes are executed in parallel, eq. 7 is changed accordingly.

From eq. 7 and Table 1, we can approximate the  $T_{data}$  value. Supposing that L1 and DDR load/store latencies are 1 and 50, respectively and also that  $L1_{ports} = 1$  and  $line_{L1} = 4$ , eq. 7 and Table 1 give

$$T_{data} = max(2 \times N \times M + \frac{N \times P \times M}{i_0} + \frac{P \times M \times N}{j_0},$$

$$\frac{50}{4} \times (N \times M + N \times P + P \times M) + 50 \times \frac{N \times M \times \lceil \frac{j_0}{4} \rceil}{j_0})$$

(8)

Regarding DDR access time, it is minimized when  $j_0$  is a multiple of cache line size, i.e., 4. Regarding L1 data cache access time, it is minimized when  $(\frac{1}{i_0} + \frac{1}{j_0})$  is minimized  $(i_0, j_0 \text{ are found according to ineq. 6 and <math>RF_{FP}$  is a power of 2). For  $RF_{FP} = 8$  or  $RF_{FP} = 16$ , the above equation is minimized when  $i_0 == j_0$ . Let us consider that there are 16 floating point registers. If  $i_0 == j_0$ , then  $i_0 = j_0 = 3$  and the number of L1 data cache accesses is  $N \times M + \frac{2NMP}{3}$ , while if  $i_0 = 1$  and  $j_0 = 14$ , the number of L1 data cache accesses is  $N \times M + \frac{15NMP}{14} > N \times M + \frac{2NMP}{3}$ . Also, if  $RF_{FP} = 8$ , then  $i_0 = j_0 = 2$  gives the minimum L1 data cache access time. However, in the case that  $RF_{FP} = 32$ , we cannot find a good  $i_0 = j_0$  solution, since several registers are wasted, i.e., if  $i_0 = j_0 = 4$  then 16, 4 and 4 registers are used for C, A and B, respectively, which means that only 24/32 registers are used; in this case, we do not fully utilize the RF size and thus a solution different than  $i_0 = j_0 = 5$ , then we need 35 register which are more than 32.

However, the best performance is not always achieved by minimizing  $T_{data}$  value; although  $i_0 == j_0$  case achieves a lower number of data accesses than  $j_0 \succ i_0$  case (for the most register file sizes), it achieves a larger number of

| for (i=0; i <n; i+="2)" th="" {<=""><th><b>for</b> (i=0; i<n; i++)="" th="" {<=""></n;></th></n;>             | <b>for</b> (i=0; i <n; i++)="" th="" {<=""></n;>                     |  |  |

|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--|--|

| for (j=0; j <m; j+="&lt;b">2) {</m;>                                                                          | for (j=0; j <m; j+="6)" td="" {<=""></m;>                            |  |  |

| <b>r1</b> =0; <b>r2</b> =0;r <b>3</b> =0; <b>r4</b> =0;                                                       | r1=0;r2=0;r3=0;r4=0;r5=0;r6=0;                                       |  |  |

| <b>for</b> (k=0; k <p; k++)="" td="" {<=""><td colspan="3">for (k=0; k<p; k++)="" td="" {<=""></p;></td></p;> | for (k=0; k <p; k++)="" td="" {<=""></p;>                            |  |  |

| <b>r5</b> =A[i][k]; <b>r6</b> =A[i+1][k];                                                                     | r7=A[i][k];                                                          |  |  |

| <b>r7</b> =B[k][j];                                                                                           | <b>r8</b> =B[k][j];                                                  |  |  |

| r1+=r5*r7;                                                                                                    | r1+=r7*r8;                                                           |  |  |

| r2+=r5*r8;                                                                                                    | <b>r8</b> =B[k][j+1];                                                |  |  |

| r3+=r6*r7;                                                                                                    | r2+=r7*r8;                                                           |  |  |

| r4+=r6*r8;                                                                                                    | <b>r8</b> =B[k][j+2];                                                |  |  |

| }                                                                                                             | r3+=r7*r8;                                                           |  |  |

| C[i][j]= <b>r1</b> ;                                                                                          | <b>r8</b> =B[k][j+3];                                                |  |  |

| C[i][j+1]= <b>r2</b> ;                                                                                        | r4+=r7*r8;                                                           |  |  |

| C[i+1][j]= <b>r3</b> ;                                                                                        | <b>r8</b> =B[k][j+4];                                                |  |  |

| C[i+1][j+1]= <b>r4</b> ;                                                                                      | r5+=r7*r8;                                                           |  |  |

| }}                                                                                                            | <b>r8</b> =B[k][j+5];                                                |  |  |

|                                                                                                               | r6+=r7*r8;                                                           |  |  |

|                                                                                                               | C[i][j]= <b>r1</b> ; C[i][j+1]= <b>r2</b> ; C[i][j+2]= <b>r3</b> ;   |  |  |

|                                                                                                               | C[i][j+3]= <b>r4</b> ; C[i][j+4]= <b>r5</b> ; C[i][j+5]= <b>r6</b> ; |  |  |

|                                                                                                               | }}                                                                   |  |  |

| (a)                                                                                                           | (b)                                                                  |  |  |

**Fig. 4** MMM optimized code for  $RF_{FP} = 8$ . In (a)  $i_0 = j_0 = 2$ , while in (b)  $i_0 = 1$  and  $j_0 = 6$ . (a) achieves a lower  $T_{data}$  value but (b) achieves a lower  $T_{addressing}$  value

addressing instructions; this is because in the first case, more array addresses per iteration, are computed (Fig. 4).

The above schedule achieves the minimum number of data accesses (for the most register file sizes). In this case, C array is loaded and stored once from L1 data cache, while A and B are loaded  $N/i_0$  and  $M/j_0$ , respectively (for square matrices,  $N^2$  stores and  $N^2 + N^3/i_0 + N^3/j_0$  loads occur). The row-column way of multiplying is the best. If we use another schedule, e.g., loop interchange transformation is applied and the iterators are k, i, j, instead of i, j, k and thus we use  $i_0 \times j_0$ ,  $i_0$  and  $j_0$  registers for A, C and B, respectively, then  $N^3/i_0$  stores and  $N^2 + N^3/i_0 + N^3/j_0$  loads occur, which are more than those in the previous case. A larger number of data accesses occurs because C is always accessed twice (C array is both loaded and stored); thus, it is more efficient to access C array once and A, B arrays more times, than the opposite.

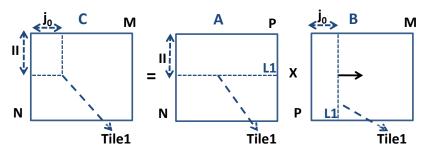

#### 3.1.2 Medium input sizes with L1 data cache only

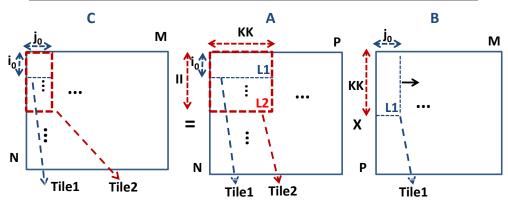

For medium input sizes where ineq. 9 holds, another schedule is used (Fig. 5). If all the data of a Tile1 of A and a Tile1 of B fit in separate ways of L1 cache (ineq. 9), the scheduling given below is used.

$$\frac{L1 \times (assoc - k)}{assoc} \ge II \times P \times element\_size \tag{9}$$

Fig. 5 MMM for medium input sizes and CPUs with L1 data cache only

where  $k = \lceil \frac{P \times j_0 \times element\_size}{L1/assoc} \rceil \leq \frac{assoc}{2}$ , L1 is the size of the L1 cache, assoc is the L1 associativity (assoc  $\neq 1$ ) and element\\_size is the size of the arrays elements in bytes.

k is an integer and it gives the number of L1 data cache lines with identical L1 addresses used for Tile1 of B; we use k cache ways for B and assoc - k cache ways for A (in other words A and B are written in separate data cache ways).

In order to the Tile1 tiles of A and B remain in L1 data cache, the cache lines of Tile1 of A must be written in L1 without conflict with the Tile1 of B ones. This is achieved by storing the Tile1 of A and the Tile1 of B in consecutive main memory locations and by using  $(k \times \frac{L1}{assoc})$  L1 memory size for B and  $((assoc - k) \times \frac{L1}{assoc})$  L1 memory size for A (ineq. 9). We can more freely say that this is equivalent to using k cache ways for B and (assoc - k)cache ways for A. An empty cache line is always granted for each different modulo (with respect to the size of the cache) of A and B memory addresses. We do not need any empty space for C because a) Tile1 of C size is much smaller than the other Tile1 tiles (normally,  $P \gg II \succ j_0$ ), b) each element of C is stored just once into memory (no data reuse) and c) C is stored into main memory infrequently; thus, the number of conflicts due to C can be neglected (victim cache if exists, eliminates the misses of C). However, if P is comparable to II, then an additional cache way must be used for C.

Ineq. 9 holds only when Tile1 of A and B are written in consecutive main memory locations. Given that the arrays are written row-wise in main memory, the elements of Tile1 of A are written in consecutive main memory locations, but the elements of Tile1 of B are not. Thus, the data layout of B is changed from row-wise to tile-wise, i.e., all elements are written in main memory just as they are fetched; first, the first  $j_0$  elements of the first row of B are written to main memory, then the first  $j_0$  elements of the second row of B etc.

It is important to say that if we use  $L1 \ge (II \times P + P \times j_0) \times element\_size$  instead of ineq. 9, the number of L1 misses will be much larger because A and B cache lines would conflict with each other.

The scheduling follows. First, the first  $i_0$  rows of A are multiplied by the first  $j_0$  columns of B exactly as in the previous subsection. Then the next  $i_0$  rows of A are multiplied by the same columns of B as above. This is repeated

Fig. 6 MMM for large input sizes and CPUs with L1 data cache only

until all the rows of Tile1 of A are multiplied by the first  $j_0$  columns of B. After the first Tile1 of A has been multiplied by the first Tile1 of B, the first Tile1 of A is multiplied by the second Tile1 of B etc. In this way, data reuse is achieved on both A and B arrays.

The time needed for the arrays elements to be loaded/stored, is approximated by eq. 7 and Table 1. Supposing that L1 and DDR load/store latencies are 1 and 50, respectively and also that  $L1_{ports} = 1$  and  $line_{L1} = 4$ , eq. 7 and Table 1 give

$$T_{data} = max(2 \times N \times M + \frac{N \times P \times M}{i_0} + \frac{P \times M \times N}{j_0},$$

$$\frac{50}{4} \times (N \times M + N \times P + \frac{P \times M \times N}{II}) + 50 \times \frac{N \times M \times \lceil \frac{j_0}{4} \rceil}{j_0}) \quad (10)$$

Regarding DDR access time, it is minimized when II is maximized and  $j_0$  is a multiple of cache line size, i.e., 4; also II is maximized when  $j_0 = 1$  (II and  $j_0$  are interdependent); there is a trade-off. Regarding L1 data cache access time, it is minimized when  $(\frac{1}{i_0} + \frac{1}{j_0})$  is minimized  $(i_0, j_0)$  are found according to ineq. 6).

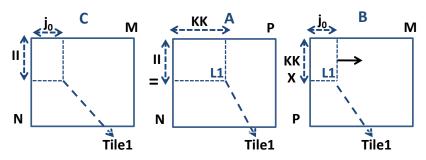

#### 3.1.3 Large input sizes and CPUs with L1 data cache only

For large input sizes, where ineq. 9 does not hold, the scheduling given below is used (Fig. 6).

In this case,  $i_0$  rows of A and  $j_0$  columns of B do not fit in L1; ineq. 9 cannot give  $j_0 > 1$  and  $i_0 > 1$ . Thus, P dimension is also tiled and Tile1 tiles become even smaller; Tile1 tiles contain  $i_0$  sub-rows of A and  $j_0$  sub-columns of B; the Tile1 tiles of A and B are of size  $II \times KK$  and  $KK \times j_0$ , respectively. KK is selected to be as large as possible since C array is both loaded and stored, KK times from main memory.

Now, instead of multiplying rows of A by columns of B, sub-rows of size KK are multiplied by sub-columns of B. The largest II integer value for KK = P/2 is selected that ineq. 11 holds. If ineq. 11, still cannot give an II value satisfying ineq. 6, KK = P/3 is selected etc.

$$\frac{L1 \times (assoc - k)}{assoc} \ge II \times KK \times element\_size$$

(11)

where  $k = \lceil \frac{j_0 \times KK \times element\_size}{L1/assoc} \rceil \leq \frac{assoc}{2}$ ,  $KK = \frac{P}{1}, \frac{P}{2}, ..., \frac{P}{n}$  and n is positive integer  $(n \ge 1)$ .

II sub-rows of A and  $j_0$  sub-columns of B of size KK, have to fit in separate ways of L1 data cache. It is important to say that ineq. 11 holds only when the tile elements of A and B are written in consecutive main memory locations; otherwise, the tile sub-rows/sub-columns will conflict with each other due to the cache modulo effect. As it was explained in the previous Subsection, we do not need any empty space for C. However, if the size of Tile1 of C is comparable to the others, then cache size which equals to one cache way must be granded for C.

Regarding the data layout of A, when P dimension is tiled, the data layout of A is changed from row-wise to tile-wise; A elements are written into memory just as they are fetched. If the data layout of A is not changed, ineq. 11 cannot give a minimum number of cache conflicts since the sub-rows of A will conflict with each other. The same holds for B. The data array layout of B is changed from row-wise to tile-wise.

The scheduling follows. The multiplication between two Tile1 tiles is exactly the same as in the previous case (Subsection 3.1.1). First, the first Tile1 of A is multiplied by all Tile1 tiles of the first Tile1 block row of B. Then, the second Tile1 of the first Tile1 block column of A is multiplied by all the Tile1 tiles of the first Tile1 block row of B. Then, the second Tile1 block column of A is multiplied by the second Tile1 block row of B etc.

The time needed for the array elements to be loaded/stored, is approximated by eq. 7 and Table 1. Supposing that L1 and DDR load/store latencies are 1 and 50, respectively and also that  $L1_{ports} = 1$  and  $line_{L1} = 4$ , eq. 7 and Table 1 give

$$T_{data} = max\left(\frac{2 \times N \times M \times P}{KK} + \frac{N \times P \times M}{i_0} + \frac{P \times M \times N}{j_0}\right),$$

$$\frac{50}{4} \times \left(\frac{N \times M \times P}{KK} + N \times P + \frac{P \times M \times N}{II}\right) + 50 \times \frac{\frac{N \times M \times P}{KK} \times \left\lceil \frac{j_0}{4} \right\rceil}{j_0}\right) (12)$$

Regarding DDR access time, it is minimized when KK and II are maximized and when  $j_0$  is a multiple of cache line size, i.e., 4.  $T_{data}$  highly depends on the KK and II values which are the largest possible according to the L1 data cache size.

In the case of direct mapped data cache, both A and B tiles compete with each other for the same L1 addresses. Given that both tiles cannot remain in L1 due to the cache modulo effect, we select Tile1 of A to be many times larger than Tile1 of B, i.e.,  $II \gg j_0$ . In this way, the main part of Tile1 of A remain in L1 and the number of L1 misses is kept low.

Fig. 7 MMM for medium input sizes and CPUs with L2 and L1 data cache

#### 3.1.4 Medium input sizes and CPUs with L2 and L1 data cache

If all the data of A and the Tile1 of B/C fit in separate ways of L2 cache (ineq. 13), the scheduling given below is used (Fig. 7).

$$\frac{L2 \times (assoc - 1)}{assoc} \ge N \times P \times element\_size$$

(13)

where L2 is the size of the L2 cache, *assoc* is the L2 associativity and *element\_size* is the size of the arrays elements in bytes (e.g., *element\_size* = 4 for floating point numbers).

Given that  $N \gg JJ$  for most cases, the size of A is much larger than the size of Tile1 of B and Tile1 of C, and thus  $((assoc - 1) \times \frac{L2}{assoc})$  and  $(\frac{L2}{assoc})$  L2 size is needed for A and B-C arrays, respectively.

Regarding L1 data cache,  $2 \times i_0$  rows of A and JJ columns of B have to fit in separate ways of L1 (ineq. 14).

$$\frac{L1 \times (assoc - k)}{assoc} \ge P \times JJ \times element\_size,$$

(14)

where  $k = \lceil \frac{2 \times i_0 \times P \times element\_size}{L1/assoc} \rceil \leq \frac{assoc}{2}$ , L1 is the size of the L1 data cache memory in bytes, *element\\_size* is the size of the arrays elements in bytes and *assoc* is the L1 associativity  $(assoc \neq 1)$ .

The scheduling follows. First, the first Tile1 of A is multiplied by the first Tile1 of B. The multiplication between two Tile1 tiles is the same as in Subsect. 3.1.1. Then, the second Tile1 of A is multiplied by the same Tile1 tiles of B as above etc. We select the whole A to fit in L2, since having a Tile1 of B in L1 data cache, its elements need to be multiplied by as many rows of A as possible before they are spilled to upper level memories.

The time needed for the array elements to be loaded/stored, is approximated by eq. 19 and Table 1.

$$T_{data} = max(\frac{L1_{load\_lat} \times L1_{loads} + L1_{store\_lat} \times L1_{stores}}{L1_{ports}}$$

Vasilios Kelefouras, Angeliki Kritikakou, Iosif Mporas, Vasilios Kolonias

$$\frac{L2_{load\_lat}}{line_{L1}} \times L2_{loads} + L2_{store\_lat} \times \frac{L2_{stores} \times \lceil j_0/line_{L1}\rceil}{j_0},$$

$$\frac{DDR_{load\_lat}}{line_{L2}} \times DDR_{loads} + DDR_{store\_lat} \times \frac{DDR_{stores} \times \lceil j_0/line_{L2}\rceil}{j_0})(15)$$

where  $L1_{load\_lat}$ ,  $L2_{load\_lat}$ ,  $DDR_{load\_lat}$ ,  $L1_{store\_lat}$ ,  $L2_{store\_lat}$ ,  $DDR_{store\_lat}$ are the L1,L2 and DDR load and store latencies, respectively.  $L1_{loads}$ ,  $L2_{loads}$ ,  $DDR_{loads}$ ,  $L1_{stores}$ ,  $L2_{stores}$ ,  $DDR_{stores}$ , are the numbers of loads and stores occur for each memory, according to Table 1.  $line_{L1}/line_{L2}$  are the numbers of elements each L1/L2 cache line contains and  $L1_{ports}$  is the number of L1 load/store ports. In eq. 7, we assume that only one L1/L2 cache line is replaced at the time; if more than one cache lines are replaced concurrently, e.g., two lines, then eq. 7 is changed accordingly.

Supposing that L1, L2 and DDR load/store latencies are 1, 4 and 50, respectively and also that  $L1_{ports} = 1$ ,  $line_{L1} = 4$ ,  $line_{L2} = 4$ , eq. 7 and Table 1 give

$$T_{data} = max(2 \times N \times M + \frac{N \times M \times P}{i_0} + \frac{N \times M \times P}{j_0},$$

$$N \times M + \frac{N \times M \times P}{JJ} + P \times M + 4 \times \frac{N \times M \times \lceil \frac{j_0}{4} \rceil}{j_0},$$

$$\frac{50}{4}(N \times M + N \times P + P \times M) + 50 \times \frac{N \times M \times \lceil \frac{j_0}{4} \rceil}{j_0})$$

(16)

Regarding DDR access time, it is minimized when  $j_0$  is a multiple of L2 cache line size, i.e., 4. Regarding L2 data cache access time, it is minimized when JJ is maximized and  $j_0$  is a multiple of L1 cache line size, i.e., 4. JJ is maximum according to the L1 data cache size. Regarding L1 data cache access time, it is minimized when  $(\frac{1}{i_0} + \frac{1}{j_0})$  is minimized.

#### 3.1.5 Large input sizes and CPUs with L2 and L1 data cache

For large input sizes, where ineq. 13 does not hold, the scheduling given below is used (Fig. 8).

In this case, ineq. 14 cannot give  $JJ \succ 1$  and  $i_0 \succ 1$ . Thus, P dimension is also tiled as in Subsect. 3.1.3 and Tile1 tiles become even smaller.

Thus, instead of multiplying rows of A by columns of B, sub-rows of size KK are multiplied by sub-columns of size KK. The Tile1 of A becomes of size  $i_0 \times KK$  and the Tile1 of B becomes of size  $KK \times j_0$ ; the largest  $j_0$  integer value for KK = P/2 is selected that ineq. 17 holds. If ineq. 17, still cannot give a  $j_0$  value satisfying ineq. 6, KK = P/3 is selected and etc.

$$\frac{L1 \times (assoc - k)}{assoc} \ge KK \times j_0 \times element\_size \tag{17}$$

where  $k = \lceil \frac{2 \times i_0 \times KK \times element\_size}{L1/assoc} \rceil \leq \frac{assoc}{2}$ ,  $KK = \frac{P}{1}, \frac{P}{2}, ..., \frac{P}{n}$  and n is positive integer  $(n \ge 1)$ .

Fig. 8 MMM for large input sizes and CPUs with L2 and L1 data cache

$2 \times i_0$  sub-rows of A and  $j_0$  sub-columns of B of size KK, have to fit in separate ways of L1 data cache. It is important to say that ineq. 17 holds only when the tiles of A and B are written in consecutive main memory locations (tile-wise); otherwise, the tiles sub-rows/sub-columns will conflict with each other due to the cache modulo effect.

To efficiently use the L2 cache, the array A is further partitioned into Tile2 tiles. A Tile2 tile of A (size of  $II \times KK$ ), a Tile1 tile of B (size of  $KK \times j_0$ ) and a Tile2 of C (size of  $II \times j_0$ ), have to fit in L2 cache (ineq. 18). Array A uses assoc - 1 L2 ways while B-C arrays use only one L2 way. This is because the sum of Tile2 of C and Tile1 of B, is of smaller size than one L2 way ( $II \gg j_0$ ); moreover, C and B tiles do not achieve data reuse in L2 and thus there is no need to remain in L2 (Tile1 of B is reused in L1 data cache not in L2).

$$\frac{L2 \times (assoc - 1)}{assoc} \ge II \times KK \times element\_size \tag{18}$$

The scheduling follows. First, the first Tile1 of the first Tile2 of A is multiplied by the first Tile1 of the first Tile1 block row of B. Then, the second Tile1 of the first Tile2 of A is multiplied by the same Tile1 of B as above etc. After the first Tile2 of A has been multiplied by the first Tile1 of B, it is multiplied by the remaining Tile1 tiles of the first Tile1 block row of B. Then, the second Tile2 of the first Tile2 block column of A is multiplied by the all Tile1 tiles of the first Tile1 block row of B etc. The procedure ends when all Tile2 block columns of A have been multiplied by all Tile1 block rows of B.

We select a big Tile2 of A to fit in L2, since a Tile1 of B which resides in L1 data cache, is multiplied by all rows of A; thus we multiply Tile1 of B with as many rows of A as possible before they are spilled to the upper level memory.

The time needed for the array elements to be loaded/stored, is approximated by eq. 19 and Table 1. Supposing that L1, L2 and DDR load/store latencies are 1, 4 and 50, respectively and also that  $L1_{ports} = 1$ ,  $line_{L1} = 4$ ,  $line_{L2} = 4$ , eq. 7 and Table 1 give

Fig. 9 MMM for CPUs with SIMD

$$T_{data} = max(\frac{2 \times N \times M}{KK} + \frac{N \times M \times P}{i_0} + \frac{N \times M \times P}{j_0},$$

$$\frac{N \times M \times P}{KK} + \frac{N \times M \times P}{j_0} + \frac{P \times M \times N}{II} + 4 \times \frac{\frac{N \times M \times P}{KK} \times \lceil \frac{j_0}{4} \rceil}{j_0},$$

$$\frac{50}{4}(\frac{N \times M \times P}{KK} + N \times P + \frac{N \times M \times P}{II}) + 50 \times \frac{\frac{N \times M \times P}{KK} \times \lceil \frac{j_0}{4} \rceil}{j_0}) \quad (19)$$

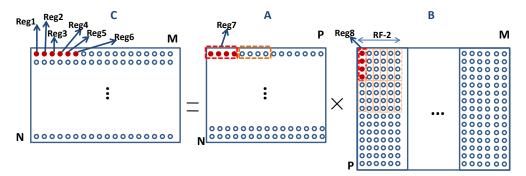

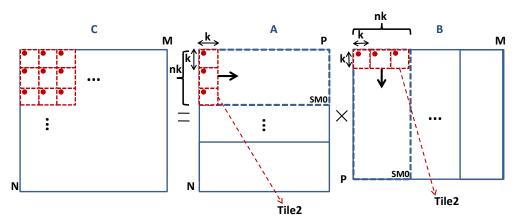

#### 3.1.6 CPUs with SIMD

In this case, a scheduling similar to that explained in Subsect. 3.1.1 is used. The optimum production-consumption (when an intermediate result is produced it is directly consumed-used) of array C and the sub-optimum data reuse of array A have been selected by splitting the arrays into tiles according to the number of XMM/YMM registers (eq. 20).

$$RF = p + 1 + 1$$

(20)

where RF is the number of the XMM/YMM registers and p is the number of the registers used for C array. Thus, we assign p registers for C and 1 register each for A and B.

Regarding  $T_{data}$  value, the best schedule here is similar to than given in Subsect. 3.1.1, i.e.,  $2 \times 2$ , 2 and 2 registers are used for C, A and B, when RF = 8 and  $3 \times 3$ , 3 and 3 registers are used for C, A and B, when RF = 16. However, the schedule according to ineq. 20 is faster on SIMD architectures since the lower number of addressing instructions has a larger effect on performance. As the *p* value increases, the number of SSE instructions decreases (it is explained below). We have evaluated both solutions in a large number of different architectures and the first (that of Fig. 9) is the fastest at all architectures.

The illustration example consists of the scenario that there are 8 XMM registers (XMM0:XMM7 of 16 bytes each) and the arrays contain floating point

20

data (4 byte elements). The first 4 elements of the first row of A (A(0, 0:3))and the first four elements of the first column of B (B(0:3,0)) are loaded from memory and they are assigned into XMM0 and XMM1 registers respectively (the elements of B have been written into main memory tile-wise, i.e., just as they are fetched). XMM0 is multiplied by XMM1 and the result is stored into XMM2 register (Fig. 4). Then, the next four elements of B (B(0:3,1)), are loaded into XMM1 register again; XMM0 is multiplied by XMM1 and the result is stored into XMM3 register (Fig. 9, Fig. 4). The XMM0 is multiplied by XMM1 for 6 times and the XMM2:XMM7 registers contain the multiplication intermediate results of the C array. Then, the next four elements of A (A(0, 4:7)) are loaded into XMM0 which is multiplied by XMM1 for 6 times, as above (Fig. 4); the intermediate results in XMM2:XMM7 registers, are always produced and consumed. When the 1st row of A has been multiplied by the first 6 columns of B, the four values of each one of XMM2:XMM7 registers are added and they are stored into main memory (C array), e.g., the sum of the four XMM2 values, is C(0, 0).

The above procedure continues until all the rows of A have been multiplied by all the columns of B. There are several ways to add the XMM2:XMM7 data; three of them are shown in Fig. 10, where 4 XMM registers are used to store the data of C, i.e., XMM1, XMM2, XMM3 and XMM4 (the SSE instructions' latencies are taken into account here). The first one (Fig. 10-a) sums the four 32-bit values of each XMM register and the results of the four registers are packed in one which is stored into memory (the four values are stored into memory using one SSE instruction). The second one, sums the four 32-bit values of each XMM register and then each 32-bit value is stored into memory separately (without packing). For most SIMD architectures, the second (Fig. 10-b) is faster than the first one, because the store and add operations can be executed in parallel (the first one has a larger critical path). The third one (Fig. 10-c), unpacks the 32-bit values of the four registers and packs them into new ones in order to add elements of different registers. For most SIMD architectures, the third is faster than the other two ones, because unpacking and shuffle operations usually have smaller latency and throughput values than slow hadd operations.

By using SSE instructions, eq.1 changes into eq. 21. KK is not shown in Fig. 9; KK is the tile size across dimension P and for large input sizes  $KK \prec P$  (Fig. 8). As the KK value decreases, the number of SSE instructions increases according to the following equation (code shown in Fig. 10 is executed more times).

$$T_{total} = max(T_{data}, T_{matrix-operations} + c \times \frac{N \times M \times \frac{P}{KK}}{p}, T_{addressing})$$

(21)

where c is the sum of the SSE instruction latencies shown in Fig. 10. Thus, as the p value increases, the number of SSE instructions decreases.

```

xmm7=_mm_hadd_ps(xmm1, xmm1);

xmm1=_mm_hadd_ps(xmm1, xmm1);

xmm7=_mm_hadd_ps(xmm7, xmm7);

_mm_store_ss((float *)C + address , xmm7);

xmm1= mm hadd ps(xmm1,

xmm1):

xmm2= mm hadd_ps(xmm2, xmm2);

xmm2= mm hadd ps(xmm2,

xmm2):

xmm7=_mm_hadd_ps(xmm2, xmm2);

xmm3=_mm_hadd_ps(xmm3, xmm3);

xmm7= mm hadd ps(xmm7, xmm7);

xmm3=_mm_hadd_ps(xmm3, xmm3);

mm store ss((float *)C + address + 1 , xmm7);

xmm4=_mm_hadd_ps(xmm4, xmm4);

xmm4=_mm_hadd_ps(xmm4, xmm4);

xmm7= mm hadd ps(xmm3, xmm3);

xmm7=_mm_hadd_ps(xmm7, xmm7);

xmm1=_mm_unpacklo_ps(xmm1,xmm2);

mm store ss((float *)C + address + 2 , xmm7);

xmm3=_mm_unpacklo_ps(xmm3,xmm4);

xmm3=_mm_unpackto_ps(xmm1, xmm3, _MM_SHUFFLE(3,2,3,2));

xmm8=_mm_shuffle_ps(xmm1, xmm3, _MM_SHUFFLE(3,2,3,2));

xmm7=_mm_hadd_ps(xmm4, xmm4);

xmm7=_mm_hadd_ps(xmm7, xmm7);

mm store ps((float *)C + address, xmm8);

mm store ss((float *)C + address + 3 , xmm7);

a)

b)

xmm9=_mm_unpacklo_ps(xmm1,xmm2);

xmm10= mm_unpacklo_ps(xmm3,xmm4);

xmm7=_mm_shuffle_ps(xmm9,xmm10,_MM_SHUFFLE(1,0,1,0));

xmm8=_mm_shuffle_ps(xmm9,xmm10,_MM_SHUFFLE(3,2,3,2));

xmm8=xmm7+xmm8:

xmm9=_mm_unpackhi_ps(xmm1,xmm2);

xmm10= mm unpackhi ps(xmm3,xmm4);

xmm7=_mm_shuffle_ps(xmm9,xmm10,_MM_SHUFFLE(1,0,1,0));

xmm10=_mm_shuffle_ps(xmm9,xmm10,_MM_SHUFFLE(3,2,3,2));

xmm10=xmm10+xmm7:

xmm8=xmm8+xmm10;

_mm_store_ps((float *)C + address, xmm8);

```

```

c)

```

Fig. 10 Three different ways for unpacking the multiplication results using SSE intrinsics; XMM1, XMM2, XMM3, XMM4 contain the C values. For most SIMD architectures, the three schedules are in increased performance order.

#### 3.2 Multi-core CPUs

To run MMM effectively in many cores, the MMM problem is partitioned into smaller sub-problems and each sub-problem corresponds to a thread; each thread runs in one core only. Each thread must contain at least p1 instructions, where p1 is found experimentally and differs from one CPU to another. Otherwise, the cores will remain several CPU cycles idle since the threads initialization and synchronization time is made comparable to the threads execution time; this leads to low performance. Furthermore, in order to achieve high performance, the number of the threads must be higher than p2, where p2 is found experimentally. The impact of p1 and p2 on performance is comparable to the memory management problem.

Regarding small input sizes, a large speedup cannot be achieved. This is because either a low p1 and/or a low p2 value is selected. In this case it is preferable to run MMM in fewer number of cores in order to increase p1 and/or p2.

The MMM execution time on a quad core CPU is approximated by eq. 22 and eq. 23.

22

23

Fig. 11 The proposed methodology for 4 cores having a shared L2 cache.

$$T_{total} = max(T_{total-core1}, T_{total-core2}, T_{total-core3}, T_{total-core4})$$

(22)

$$T_{total-corei} = \sum_{j=1}^{Num-of-Threads} T_{total-threadj}$$

(23)

where i = [1, 4] and  $T_{total-threadj}$  is the  $T_{total}$  value given in Subsect. 3.1.

Most multi core processors, typically contain 2 or 3 levels of cache, i.e., a) separate L1 data and instruction caches and a shared L2 cache, b) separate L1 data and instruction caches, separate unified L2 caches and a shared L3 cache. The proposed methodology for shared L2 and shared L3, is given in Subsect. 3.2.1 and Subsect. 3.2.2, respectively.

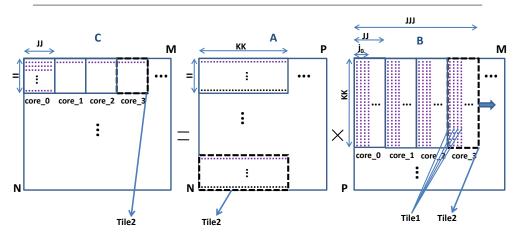

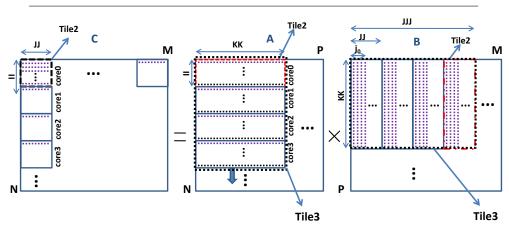

#### 3.2.1 CPUs with shared L2

To utilize L2 shared cache, we partition the three arrays into Tile2 tiles (Fig. 11). The Tile2 tiles of A, B and C, are of size  $II \times KK$ ,  $KK \times JJ$  and  $II \times JJ$ , respectively. Each multiplication between two Tile2 tiles creates a different thread. For small and medium input sizes, we always select KK = P (Fig. 11). Each multiplication between two Tile2 tiles is made as in Subsect. 3.1.5. Having q number of cores, each Tile2 of A is multiplied by q consecutive Tile2 tiles of B in parallel, each one at a different core (Fig. 11); thus, JJJ ( $JJJ = q \times JJ$ ) is evenly divisible by M.

One Tile2 of A and at least q Tile1 of B have to fit in L2 shared cache. The Tile2 of A is always fetched to all the cores. Also, q Tile1 tiles of different Tile2 tiles of B are loaded, which have no consecutive elements between themselves. The goal is these q Tile1 tiles of B and the next four ones, do not conflict with the Tile2 of A and do not conflict with each other. In general, an L2 cache

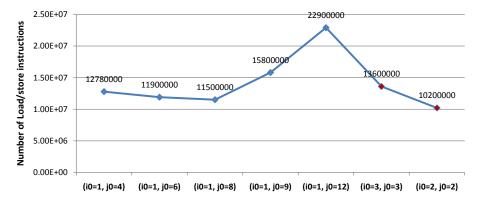

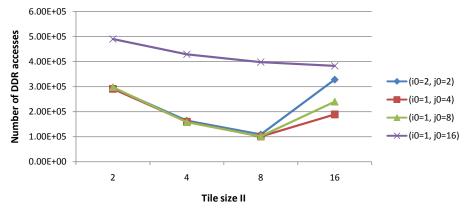

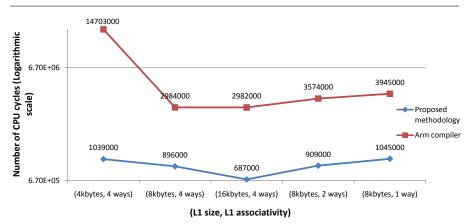

with  $assoc \ge q+1$  is needed here. Cache size equal to  $((assoc-q) \times \frac{L2}{assoc})$  and  $(q \times \frac{L2}{assoc})$  is needed for A (array A is written into main memory tile-wise) and B-C, respectively (ineq. 24). We select a big Tile2 of A to fit in L2 since having one Tile1 of B in each one of the q L1 data caches, their elements need to be multiplied by as many rows of A as possible before they are spilled to L2; Tile2 of A is reused  $M/j_0$  times. L2 cache size that equals to q L2 ways is used for the Tile1 tiles of B and C, since their size is small and their elements are not reused (Tile1 of B is reused in L1 data cache not in L2).