# Developing and Evaluating clOpenCL Applications for Heterogeneous Clusters

Tiago Filipe Rodrigues Ribeiro

Relatório Final do Trabalho de Projecto apresentado à

Escola Superior de Tecnologia e de Gestão

Instituto Politécnico de Bragança

para obtenção do grau de Mestre em Sistemas de Informação

# Developing and Evaluating clOpenCL Applications for Heterogeneous Clusters

Tiago Filipe Rodrigues Ribeiro

Relatório Final do Trabalho de Projecto apresentado à

Escola Superior de Tecnologia e de Gestão

Instituto Politécnico de Bragança

para obtenção do grau de Mestre em Sistemas de Informação

Orientador:

Prof. Dr. José Rufino

"Este Trabalho de Projecto não inclui as críticas e sugestões feitas pelo Júri."

Novembro 2012

Acknowledgements

I am grateful to Professor José Rufino, my supervisor, for all the support, dedication,

patience and aid during this project. Without his critical spirit and constant motivation

this project would not have been possible.

To my mother and father, who throughout my academic career and especially at this late

stage, remained always supporters and motivators, for me to successfully overcome all the

barriers. Mum, I know that, with all our strength we will overcome it all.

A reminder of my grandfather, who unfortunately, cannot witness my academic success,

but in all my heart I know he is very pleased with me.

To my remaining family I appreciate the interest and support shown.

A special thanks to my cousins Ricardo and Tiago for their friendship, help, support and

motivation, through difficult and needed times.

To my colleague Mário, who provided a great work environment and stayed with me all

the scholarship period. To my other friends for their goodwill and friendship that always

presented me with.

I also thank the Polytechnic Institute of Bragança for the conditions provided for carrying

out this project.

To all my thanks.

We did it...

V

# Abstract

In the last few years, the computing systems processing capabilities have increased significantly, changing from single-core to multi-core and even many-core systems. Accompanying this evolution, local networks have also become faster, with multi-gigabit technologies like Infiniband, Myrinet and 10G Ethernet. Parallel/distributed programming tools and standards, like POSIX Threads, OpenMP and MPI, have helped to explore these technologies and have been frequently combined, giving rise to Hybrid Programming Models.

Recently, co-processors like GPUs and FPGAs, started to be used as accelerators, requiring specialized frameworks (like CUDA for NVIDIA GPUs). Presented with so much heterogeneity, the industry formulated the OpenCL specification, as a standard to explore heterogeneous systems. However, in the context of cluster computing, one problem surfaces: OpenCL only enables a developer to use the devices that are present in the local machine. With many processor devices scattered across cluster nodes (CPUs, GPUs and other co-processors), it then became important to enable software developers to take full advantage of the full cluster device set.

This dissertation demonstrates and evaluates an OpenCL extension, named clOpenCL, which supports the simple deployment and efficient running of OpenCL-based parallel applications that may span several cluster nodes, thus expanding the original single-node OpenCL model. The main contributions are that clOpenCL i) offers a transparent approach to the porting of traditional OpenCL applications to cluster environments and ii) provides significant performance increases over classical (non-)hybrid parallel approaches.

**Keywords:** Hybrid Programming, Heterogeneous Computing, High-Performance Computing, MPI, OpenCL, clOpenCL.

## Resumo

Nos últimos anos , a capacidade de processamento dos sistemas de computação aumentou significativamente, passando de CPUs com um núcleo para CPUs multi-núcleo. Acompanhando esta evolução, as redes locais também se tornaram mais rápidas, com tecnologias *multi-gigabit* como a *Infiniband*, *Myrinet* e *10G Ethernet*. Ferramentas e *standards* paralelos/distribuídos, como *POSIX Threads*, OpenMP e MPI, ajudaram a explorar esses sistemas, e têm sido frequentemente combinados dando origem a Modelos de Programação Híbrida.

Mais recentemente, co-processadores como GPUs e FPGAs, começaram a ser utilizados como aceleradores, exigindo frameworks especializadas (como o CUDA para GPUs NVIDIA). Deparada com tanta heterogeneidade, a indústria formulou a especificação OpenCL, como sendo um standard para exploração de sistemas heterogéneos. No entanto, no contexto da computação em cluster, um problema surge: o OpenCL só permite ao desenvolvedor utilizar dispositivos presentes na máquina local. Com tantos dispositivos de processamento espalhados pelos nós de um cluster (CPUs, GPUs e outros co-processadores), tornou-se assim importante habilitar os desenvolvedores de software, a tirarem o máximo proveito do conjunto total de dispositivos do cluster.

Esta dissertação demonstra e avalia uma extensão OpenCL, chamada clOpenCL, que suporta a implementação simples e execução eficiente de aplicações paralelas baseadas em OpenCL que podem estender-se por vários nós do *cluster*, expandindo assim o modelo original de um único nó do OpenCL. As principais contribuições referem-se a que o clOpenCL i) oferece uma abordagem transparente à portabilidade de aplicações OpenCL tradicionais para ambientes cluster e ii) proporciona aumentos significativos de desempenho sobre abordagens paralelas clássicas (não-)híbridas.

Palavras-chave: Programação Híbrida, Computação Heterogénea, Computação de Alto Desempenho, MPI, OpenCL, clOpenCL.

# Contents

| $\mathbf{A}$ | ckno  | wledge           | ments                                          | V   |

|--------------|-------|------------------|------------------------------------------------|-----|

| $\mathbf{A}$ | bstra | act              |                                                | vii |

| $\mathbf{R}$ | esum  | 10               |                                                | ix  |

| Li           | st of | Acron            | ayms                                           | xix |

| 1            | Intr  | oducti           | on                                             | 1   |

|              | 1.1   | Conte            | xt                                             | 2   |

|              | 1.2   | Objec            | tives & Contributions                          | 3   |

|              | 1.3   | Disser           | tation Structure                               | 4   |

| 2            | Con   | $\mathbf{cepts}$ | and Technologies                               | 5   |

|              | 2.1   | Paralle          | el Computing Fundamental Concepts              | 5   |

|              |       | 2.1.1            | Sequential Execution versus Parallel Execution | 5   |

|              |       | 2.1.2            | Scalability and Acceleration                   | 7   |

|              |       | 2.1.3            | Amdahl's Law and Gustafson's Law               | 8   |

| 2.2 | Parall | el Computing Platforms                                           | 10 |

|-----|--------|------------------------------------------------------------------|----|

|     | 2.2.1  | SMP, Multi-Core and Many-Core Systems                            | 10 |

|     | 2.2.2  | Clusters                                                         | 12 |

|     | 2.2.3  | Grids/Clouds                                                     | 13 |

|     | 2.2.4  | Heterogeneous Systems                                            | 13 |

| 2.3 | Parall | el Programming Models and Frameworks                             | 15 |

|     | 2.3.1  | Shared Memory and Threads                                        | 15 |

|     | 2.3.2  | Message Passing                                                  | 16 |

|     | 2.3.3  | Heterogeneous Systems                                            | 19 |

|     | 2.3.4  | Hybrid Models                                                    | 25 |

| 2.4 | Cluste | er OpenCL                                                        | 26 |

|     | 2.4.1  | General Architecture                                             | 26 |

|     | 2.4.2  | Operation Model                                                  | 27 |

|     | 2.4.3  | Using clOpenCL                                                   | 28 |

|     | 2.4.4  | Distributed OpenCL                                               | 29 |

| 2.5 | Case S | Study: Matrix Product                                            | 29 |

| 2.6 | Exper  | imental Testbed                                                  | 30 |

|     | 2.6.1  | Computational Systems                                            | 31 |

|     | 2.6.2  | $Network(s) \qquad \dots \qquad \dots \qquad \dots \qquad \dots$ | 32 |

|     | 2.6.3  | Exploitation System                                              | 33 |

|     |        |                                                                  |    |

**35**

3 Preliminary Experiments

|   | 3.1 | General Experimental Conditions | 35 |

|---|-----|---------------------------------|----|

|   | 3.2 | Sequential Naive Approach       | 36 |

|   | 3.3 | BLAS Approaches                 | 37 |

|   | 3.4 | ATLAS BLAS                      | 39 |

|   | 3.5 | ACML BLAS                       | 40 |

|   | 3.6 | GSL BLAS                        | 41 |

|   | 3.7 | Matlab                          | 42 |

|   | 3.8 | Preliminary Results Analysis    | 46 |

|   |     |                                 |    |

| 4 | Par | dlel Approaches                 | 49 |

|   | 4.1 | Parallelization Strategy        | 49 |

|   | 4.2 | MPI-Only                        | 51 |

|   |     | 4.2.1 Test Deployment           | 56 |

|   |     | 4.2.2 Memory Issues             | 56 |

|   |     | 4.2.3 Using MMAP                | 57 |

|   |     | 4.2.4 Evaluation Results        | 59 |

|   | 4.3 | MPI-with-OpenCL                 | 59 |

|   |     | 4.3.1 Test Deployment           | 64 |

|   |     | 4.3.2 Memory Issues             | 64 |

|   |     | 4.3.3 Evaluation Results        | 64 |

|   | 4.4 | clOpenCL                        | 68 |

|   |     | 4.4.1 Test Deployment           | 72 |

|              |       | 4.4.2 No Memory Issues          | 72 |  |  |  |

|--------------|-------|---------------------------------|----|--|--|--|

|              |       | 4.4.3 Evaluation Results        | 72 |  |  |  |

|              | 4.5   | Results Discussion              | 74 |  |  |  |

| 5            | Con   | aclusions                       | 77 |  |  |  |

|              | 5.1   | Future Work                     | 78 |  |  |  |

| ${f Bi}$     | bliog | graphy                          | 79 |  |  |  |

| A            | Sou   | rce Code                        | 87 |  |  |  |

|              | A.1   | Preliminary Experiments         | 87 |  |  |  |

|              | A.2   | Parallel Approaches             | 87 |  |  |  |

| В            | Оре   | enCL Details                    |    |  |  |  |

|              | B.1   | OpenCL Terminology              | 89 |  |  |  |

|              |       | B.1.1 OpenCL Standard           | 91 |  |  |  |

|              |       | B.1.2 OpenCL Specification      | 91 |  |  |  |

|              |       | B.1.3 Framework                 | 96 |  |  |  |

|              | B.2   | OpenCL API Supported Data Types | 96 |  |  |  |

| $\mathbf{C}$ | Scie  | entific Contributions           | 99 |  |  |  |

|              | C.1   | Published Paper                 | 99 |  |  |  |

# List of Tables

| 3.1 | Sequential Naive Approach Execution Time (seconds)    | 37 |

|-----|-------------------------------------------------------|----|

| 3.2 | ATLAS BLAS Execution Time (seconds)                   | 40 |

| 3.3 | ACML BLAS Evaluation Execution Time (seconds)         | 41 |

| 3.4 | GSL BLAS Evaluation Execution Time (seconds)          | 42 |

| 3.5 | Matlab Matrix Product Results (seconds)               | 44 |

| 4.1 | Number of $C$ sub-matrices                            | 51 |

| 4.2 | Memory Consumption for $n=24K$ and $slice=2K$ (Gb)    | 57 |

| 4.3 | MPI-Only Evaluation Results                           | 59 |

| 4.4 | MPI-with-OpenCL Evaluation Results – naive kernel     | 66 |

| 4.5 | MPI-with-OpenCL Evaluation Results – optimized kernel | 68 |

| 4.6 | clOpenCL Evaluation Results – naive kernel            | 73 |

| 4.7 | clOpenCL Evaluation Results – optimized kernel        | 74 |

| R 1 | Built in Scalar Data Types                            | 07 |

# List of Figures

| 2.1  | Representation of the sequential execution model                                 | 6  |

|------|----------------------------------------------------------------------------------|----|

| 2.2  | Representation of the parallel execution model                                   | 6  |

| 2.3  | Optimal Scalability (linear), limited by Amdahl's Law [Bri12]                    | 7  |

| 2.4  | Speedup according to Amdahl's Law, for different values of $P$ and $N$ [Bar11a]. | Ĝ  |

| 2.5  | SMP system representation                                                        | 10 |

| 2.6  | Multi-core System representation                                                 | 11 |

| 2.7  | A Cluster system representation                                                  | 12 |

| 2.8  | A simplified view of the Message Passing Model                                   | 17 |

| 2.9  | CUDA architecture                                                                | 20 |

| 2.10 | clOpenCL (a) operation model, (b) host application layers                        | 27 |

| 2.11 | Matrix multiplication representation                                             | 30 |

| 2.12 | Cluster network(s) configuration                                                 | 32 |

| 3.1  | Example of a matrix transposition                                                | 36 |

| 3.2  | Matlab evaluation results graphic                                                | 44 |

| 3.3  | Speedups for all combinations                                                    | 45 |

| 3.4  | Preliminary tests results comparison                                             | 46 |

| 4.1 | Sliced matrix product representation                               | 50 |

|-----|--------------------------------------------------------------------|----|

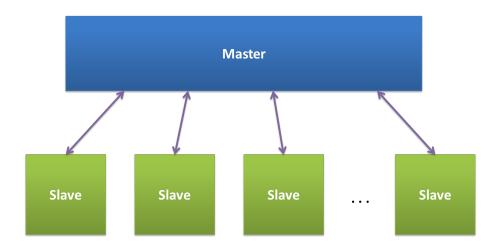

| 4.2 | Master – Slave Architecture                                        | 51 |

| 4.3 | A specific sliced matrix product                                   | 52 |

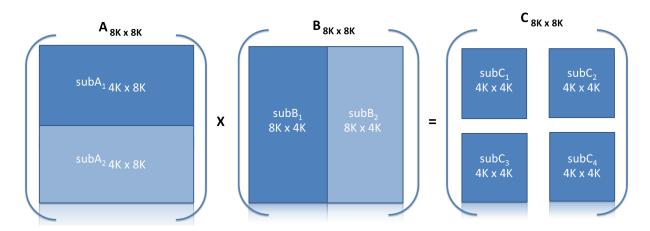

| 4.4 | Master-Slave Architecture of the MPI-with-OpenCL approach          | 60 |

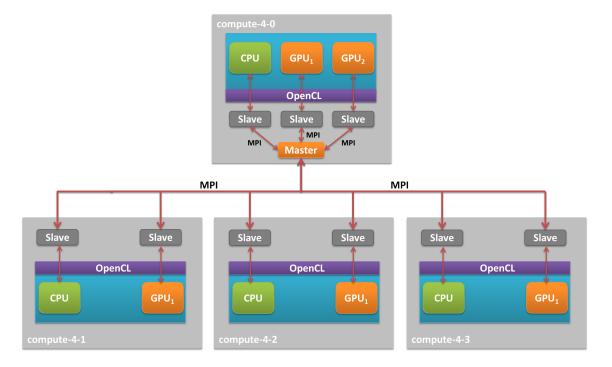

| 4.5 | A deployment of the clOpenCL Architecture                          | 69 |

| 4.6 | Host application execution method                                  | 70 |

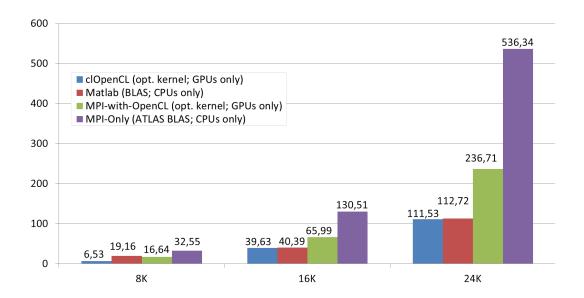

| 4.7 | Parallel Matrix Product – best execution times (s)                 | 75 |

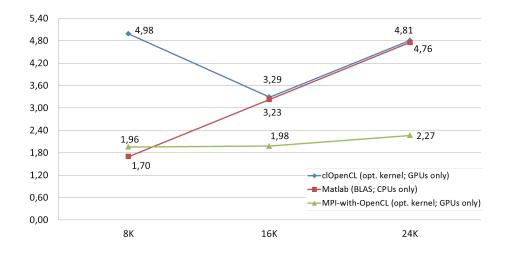

| 4.8 | Parallel Matrix Product – speedups relative to MPI-Only            | 75 |

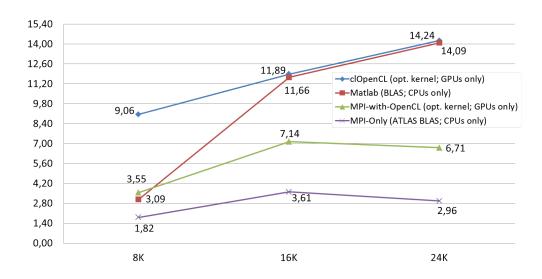

| 4.9 | Speedups relative to the ATLAS implementation                      | 76 |

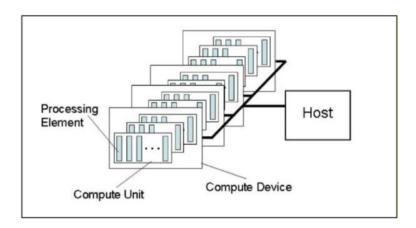

| B.1 | OpenCL platform                                                    | 92 |

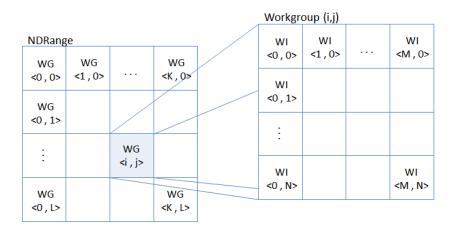

| B.2 | Representation of the NDRange where Work-items (WI) are grouped in |    |

|     | Work-groups (WG)                                                   | 94 |

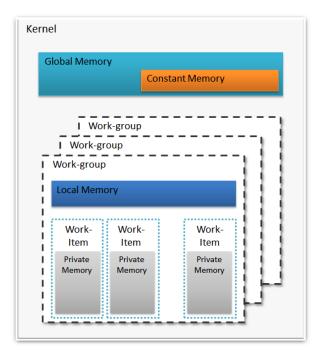

| В.3 | Memory Model representation                                        | 95 |

# List of Acronyms

AMD Advanced Micro Devices

**API** Application Programming Interfaces

APP Accelerated Parallel Processing

APU Accelerated Processing Unit

ASIC Application-Specific Integrated Circuit

ATLAS Automatically Tuned Linear Algebra Software

**BLAS** Basic Linear Algebra Subprograms

**BSD** Berkeley sockets

CU Compute Unit

C99 C Programming Language Standard

**CPU** Central Processing Unit

CUDA Compute Unified Device Architecture

**DSP** Digital Signal Processor

FPGA Field-Programmable Gate Array

**GPP** General Purpose Processors

**GPU** Graphics Processing Unit

GPGPU General-Purpose Graphics Processing Units

GVirtuS Generic Virtualization Service

**HPC** High-Performance Computing

IO Input Output

**ISA** Instruction Set Architecture

**ISO** International Organization for Standardization

**JIT** Just-In-Time

MPI Message Passing Interface

**OS** Operative System

OpenCL Open Computing Language

OpenMP Open Multi-Processing

**PE** Processing Element

**PVM** Parallel Virtual Machine

RAM Random Access Memory

**SDK** Software Development Kit

${f SMP}$  Symetric MultiProcessing

SIMD Single Instruction, Multiple Data

**SPMD** Single Program, Multiple Data

SSH Secure-Shell

VCL Virtual OpenCL

# Chapter 1

## Introduction

In the recent years, the computing systems processing capabilities have increased significantly, changing from one core CPUs to multi-core and many-core ones. Accompanying this evolution, local networks have also become faster, using Myrinet, Infiniband and 10G-Ethernet technologies. Parallel/distributed programming tools and standards, like MPI (Message Passing Interface) and OpenMP, have helped to explore these technologies and have been frequently combined, giving rise to Hybrid Programming Models. All of these contributed to the growing importance of Parallel Computing in the modern computing landscape.

In this context, clusters are still the main approach to Parallel Computing, they are being used to solve problems that need large computational power and/or storage capacity, and for such problems, clusters have the right features: large storage capacity, using resources available throughout its nodes; increased parallel processing capabilities, using the distributed CPUs. However, to solve increasingly demanding computational problems, an improve in performance is needed. For CPUs, higher clock speeds are no longer the only answer and, in their small package, one way to increase performance is by adding multiple cores. Because of this, devices like GPUs, with dozens/hundreads of cores have become programmable parallel processors, evolving from fixed function rendering devices

[Gro11], and are being coupled with traditional CPUs, creating heterogeneous systems.

Presented with so much heterogeneity, the process of developing software for such a wide array of architectures poses a number of challenges to the programming community [GHK<sup>+</sup>11], because programming approaches for multi-core CPUs and GPUs are very different. Thus, new standards where introduced to help for this kind of programming, like the OpenCL and CUDA standards. However, in cluster computing, one problem surfaces: these standards only enable a developer to use the devices that are present in the local machine.

Once recent clusters included highly parallel CPUs, GPUs and other types of coprocessors, it became important to enable software developers to take full advantage of these heterogeneous processing devices present across all nodes. In recent years different projects started to address this problem, taking CUDA or OpenCL as a starting point and creating extensions of these specifications.

This dissertation introduces and demonstrates an OpenCL extension, named clOpenCL, which supports the simple deployment and efficient running of OpenCL-based parallel applications that may span several cluster nodes, expanding the original single-node OpenCL model [ARPS12].

#### 1.1 Context

This work was conducted as part of a scholarship during the PERFORM (*Portability and Performance in Heterogeneous Parallel Systems*) research project (ref. PTD-C/EIA/100035/2008). The project was funded by the ERDF - European Regional Development Fund through the COMPETE Programme (operational programme for competitiveness) and by National Funds through the FCT (Portuguese Foundation for Science and Technology) within project FCOMP-01-0124-FEDER-010067.

In the context of the PERFORM project, an extension of the OpenCL standard (section 2.3.3) has been developed. This extension, called clOpenCL (more on section 2.4), is a library and a set of utilities and support services, which sustains an OpenCL execution environment extended to a cluster. clOpenCL allows OpenCL applications to benefit from operating in a cluster, in a quickly and almost transparent way.

## 1.2 Objectives & Contributions

The main objective of this dissertation was to assess the merits of the current clOpenCL implementation, regarding to its compatibility with the original OpenCL standard, its ease of use by programmers and its stability and operational performance. In this context, the starting point of this work was the familiarization with the OpenCL programming model. Later, clOpenCL was used as the execution platform of an OpenCL application in the area of Numerical Methods – a Matrix Multiplication application. This application was considered to be sufficiently representative of a typical OpenCL usage scenario and allowed to exploit the unprecedented potentialities introduced by clOpenCL. To complement the clOpenCL evaluation, other parallel variants were developed, in order to be used as comparison baselines (MPI-Only and MPI-with-OpenCL approaches).

The objectives initially set for this dissertation were achieved. Thus, its main contributions are: i) the offer of a transparent approach to the porting of traditional OpenCL applications to cluster environments and ii) the ability to provide significant performance increases over classical (non-)hybrid parallel approaches. These contributions were validated by a paper submitted and accepted in an international conference: "clOpenCL – Supporting Distributed Heterogeneous Computing in HPC Clusters" [ARPS12], see Appendix C.1.

### 1.3 Dissertation Structure

The remaining of this dissertation is organized as follows:

- Chapter 2 describes the main concepts related to the development of the current work and introduces the reader to the main frameworks used for the applications development, as well as the parallel test environment used.

- Chapter 3 describes preliminary tests and evaluations of the matrix multiplication algorithm, using well known sequential approaches and libraries.

- Chapter 4 describes in detail the important aspects about the implemented parallel approaches, the issues encountered during their development and the evaluation results. A discussion is also provided on the results obtained.

- Chapter 5 (last chapter) summarizes the main contributions of the work, and presents some ideas for future work.

The dissertation also includes the appendices: Appendix A, Appendix B and Appendix C, containing the references to the complete implemented code of the developed applications, complementary content and the scientific contributions.

# Chapter 2

# Concepts and Technologies

In this chapter, the developed work is contextualized, through an assessment of approaches and technologies related to the dissertation main themes. The core study of the dissertation is also introduced, as well as the experimental platform used.

## 2.1 Parallel Computing Fundamental Concepts

Parallel Computing is considered the pinnacle of modern computing. This form of computing has been used to attack complex problems in various areas of the Fundamental Sciences (Physics, Biotechnology, Genetics, Chemistry, Geology, Mechanics, Mathematics, etc.), Engineering (e.g., calculation and modelling of structures), and even more recently, Economy and Finance (stock market, datamining, etc.). For example, more accurate simulations, or simulations of larger problems, need large computational power and/or storage capacity, thus being typical targets for the use of Parallel Computing.

## 2.1.1 Sequential Execution versus Parallel Execution

Traditionally, most of the software has been developed on the assumption that it will be executed sequentially, i.e., on a single computer and requiring only a single processor. In

this perspective, the problem to be solved is subdivided into a series of instructions that are executed one after the other so, at a given time, only one instruction of the program is running. Figure 2.1 illustrates this (simplified) description of the Sequential Computing.

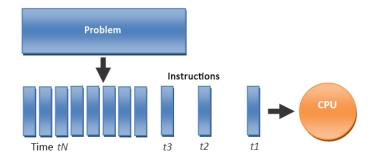

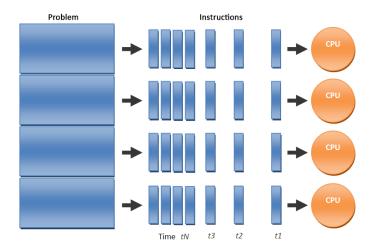

Figure 2.1: Representation of the sequential execution model.

In contrast, Parallel Computing includes the simultaneous use of multiple processors to solve, computationally, a particular problem, usually with the aim of accelerating its resolution. In this case, the problem addressed will be divided into sub-problems with a minimum possible of interdependencies, so that it can be resolved simultaneously, within specific tasks. Thus, the software must be parallelized, i.e. designed and developed, from the start, in order to be executed in parallel, by multiple processors. This vision is represented in Figure 2.2.

Figure 2.2: Representation of the parallel execution model.

#### 2.1.2 Scalability and Acceleration

A very important concept in parallel computing is Scalability. Scalability refers to the ability a parallel system has to support a proportional increase (i.e., linear) of performance (or, equivalently, an inversely proportional decrease in execution time) with the addition of more processors.

Ideally, the acceleration (also known as speedup) allowed by the parallelization of an application should be linear, i.e., the increase in the number of processors that perform the application, from N to N+1, should imply a reduction in execution time from  $T_N = T_1/N$  to  $T_{N+1} = T_1/(N+1)$ , where  $T_1$  is the sequential time (time with only one processor). In this context, the optimum speedup with N processors, is given by:

$$S_N = \frac{T_1}{T_N}$$

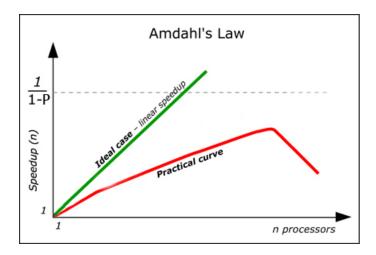

Therefore, in an ideal situation  $S_N = N$ , since  $T_N = T_1/N$ . However, very few parallel algorithms achieve this optimum acceleration. Most of these algorithms have a quasi-linear acceleration, for reduced numbers of processors, which stabilizes and tends to decline even with a large number of processors [Lab11a]. Figure 2.3 illustrates this case.

Figure 2.3: Optimal Scalability (linear), limited by Amdahl's Law [Bri12].

There are, however, some factors that can contribute to a good scalability, among which: i) the type of hardware used (particularly with regard to the bandwidth availability between the memory and the CPU, and of the local network); ii) the base algorithm and specific characteristics of the parallel application; iii) parallelization strategy and quality/expertise of the programmer.

#### 2.1.3 Amdahl's Law and Gustafson's Law

The potential acceleration of an algorithm in a parallel computing platform is given by Amdahl's Law, formulated in 1960 by the computers architect Gene Amdahl. This law states that in any program there are typically one or more portions inherently not parallelizable, which will limit the ability to accelerate the implementation of the program through parallelization. In this context, if P is the fraction of the program that is parallelizable, the speedup with N processors becomes:

$$S_N = \frac{1}{(1-P) + P/N}$$

Again, if the entire program is parallelizable (ideal situation, with P = 1.0), then  $S_N = N$ . On the other hand, if N is too big,  $S_N$  tends to 1/(1-P); this value represents an effective limit to the maximum acceleration achievable, demonstrating that it is useless to indefinitely add more and more units of parallel execution in an attempt to improve performance (this idea is conveyed by the dashed line in Figure 2.3).

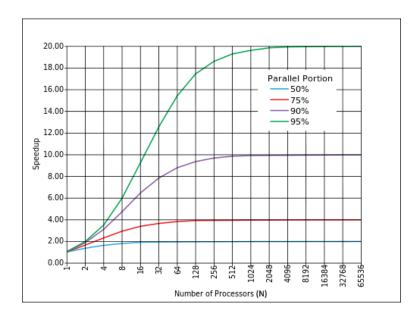

Figure 2.4 shows the speedup value according to Amdahl's Law, for different values of P and N. The theoretical limitation imposed to the speedup by the Amdahl's Law becomes clear. For instance, if the parallel portion of the program corresponds to 90% of runtime, it is not possible to obtain more than an acceleration of 10x against the purely sequential version, regardless of adding more than 512 processors.

Figure 2.4: Speedup according to Amdahl's Law, for different values of P and N [Bar11a].

Another important law in parallel computing is Gustafson's law, which is closely related to Amdahl's law. This law can be formulated as follows:

$$S(P) = P - \alpha(P - 1),$$

where P is the number of processors, S is the acceleration and  $\alpha$  the non-parallelizable part of the problem.

In a simplistic way, Gustafson's law states that problems with a large, repetitive data set can be efficiently parallelized. Thus, this law contradicts (to some extent) and complements Amdahl's Law, which describes the existence of a speedup limit that the parallelization can offer. The Amdahl's law also does not consider the variation in the availability of computing power as the number of systems increases. Therefore, the Gustafson's law proposes that programmers define the size of the problems in order to use the equipment available to solve these problems in a practical and fixed time. Thus, if a faster hardware is available, larger problems can be solved in the same amount of time.

Amdahl's law assumes a fixed size problem, implying that the sequential portion of the program does not change with the increase of the number of processors, and the parallel portion is evenly distributed over P processors. The impact of Gustafson's law, allowed problems to be reworked, so that the solution for large problems were possible, in the same amount of time [Sul12].

## 2.2 Parallel Computing Platforms

Parallel Applications may target a wide range of platforms. In this section we provide a brief description of the main parallel computing platforms used nowadays.

#### 2.2.1 SMP, Multi-Core and Many-Core Systems

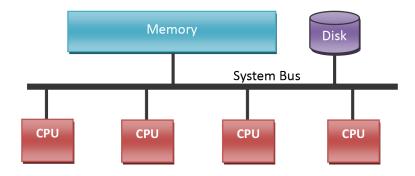

A computer system that uses symmetric multiprocessing is called SMP (Symetric Multiprocessor). This type of systems involve computational hardware that accommodates two or more identical processors connected to a single shared memory, and controlled by a single instance of an OS (Operating System) – see Figure 2.5.

Figure 2.5: SMP system representation.

SMP systems allow any processor to work on any task, no matter the location in memory of this task, provided that each task in the system is not running on two or more processors simultaneously. With the correct support provided by the OS, SMP systems can easily move tasks between processors in order to balance the load efficiently. However, one of the obstacles in the scalability of such type of systems is the bandwidth restrain and power consumption of the connections between the various processors, memory and disk. Another obstacle is that the maximum number of usable processors is relatively small (typically 32) [Wik12h].

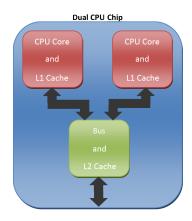

Nowadays, SMP systems evolved to **Multi-core Systems**. In this type of systems, multiple processor cores are integrated in a single chip (see Figure 2.6), instead of a single core per chip.

Figure 2.6: Multi-core System representation.

The Multi-core Systems were motivated by the high energy consumption (and consequent heat dissipation) of SMP systems, resulting from the strategy of increasing progressively the core frequencies. Introducing this type of systems has brought advantages, since the proximity of the processor cores lead to more economical manufacture: i) less raw material required; ii) sharing some components between multiple cores (e.g., L2/L3 caches), higher performance of the whole; iii) increased number of cores for the same physical area; iv) shorter paths of electrical signals.

The term Multi-core is related to **Many-core**. Many-core and Massively Multi-core are terms used to describe multi-core architectures with an especially high number of cores, in the order of the tens or hundreds, while Multi-core often refers only for dual-, triple-, quad- or octo-core units. Many-core is closely related to the GPUs architecture, for

example, which is being deployed in a broad spectrum of applications including Clusters, Clouds and Grids, in order to increase performance through parallelism.

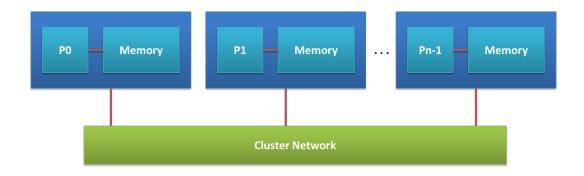

#### 2.2.2 Clusters

Clusters are another type of systems used in parallel computing. A cluster is a group of loosely coupled computers that work together, so that, in some aspects, it may be considered as a single computer. Clusters are composed by multiple individual machines connected by a network – see Figure 2.7. These individual machines, or compute nodes, are typically *SMP* or *Multi-core Systems*. While the machines in the cluster do not have to be homogeneous, load balancing is more difficult if they are not. As for the network, which links the cluster nodes, it may use widespread technologies (Ethernet) or very high-bandwidth proprietary technologies (Myrinet/Infiniband).

Figure 2.7: A Cluster system representation.

The most common type of cluster is the Beowulf cluster, which is implemented on multiple common commercial computers, connected by a local TCP/IP Ethernet network. A cluster with Multi-core Systems was the parallel computing platform used for the development of this project – see section 2.6.

### 2.2.3 Grids/Clouds

If a set of clusters is connected via the Internet, another parallel system arises, called Grid. Such systems are commonly used for computing as a service, for resolution of highly parallel problems, being the most distributed parallel computing form. Each cluster has its own independent management and specific hardware. What distinguishes grid computing from conventional high performance computing systems such as cluster computing is that grids tend to be more loosely coupled, heterogeneous, and geographically dispersed. Although a single grid can be dedicated to a particular application, commonly a grid is used for a variety of purposes. For certain applications, "distributed" or "grid" computing, can be seen as a special type of parallel computing that relies on complete computers (with onboard CPUs, storage, power supplies, network interfaces, etc.) connected to a network (private, public or the Internet) by a conventional network interface, such as Ethernet. This is in contrast to the traditional notion of a supercomputer, which has many processors connected by a local high-speed computer bus.

Related to Grid computing is the concept of Cloud Computing. However it is not a completely new concept, since it is also closely related to cluster computing and distributed systems in general. The concept of Cloud computing resides in the fact that the same Grid architecture is delivered on demand to external customers over the Internet for standard or high demanding tasks, while Grid computing is normally set to solve high demanding problems. These concepts are what distinguish these two models. Usually the Cloud service is delivered and driven by big enterprises, since they have the resources to create large-scale systems containing hundreds of thousands of computers, providing continuous support and on demand service [Mye12, FZRL08].

## 2.2.4 Heterogeneous Systems

The world is heterogeneous in nature. The diversity given by this provides richness and detail, providing also, at the same time, complexity and interaction where different entities

are optimized specifically for certain tasks and environments [GHK<sup>+</sup>11]. This happens in our world but, in computing, heterogeneous electronic systems also add richness, because they allow a programmer to choose the best architecture to execute the task at hand or to choose the best task that makes an optimal usage of a particular architecture. These two ways of approaching an heterogeneous environment, allow to be aware of the flexibility of an heterogeneous system when used to solve computational problems that involve a variety of different tasks. Thus, recently the computer design community, driven by the high performance computing (HPC) community, started to experiment with building heterogeneous systems, which combine a number of different classes of architectures.

To sum up, in general, heterogeneous computing consists on using processors with different instruction set architectures (ISAs), to solve computational problems in order to achieve high performance or to solve the problem quicker, by using a variety of different types of computational units, namely: general purpose processors (GPPs) (i.e. a CPU), special purpose processors (i.e. digital signal processor (DSP) [Wik12d] or a graphics processing unit (GPU)), a co-processor, or a custom acceleration logic (application-specific integrated circuit (ASIC) or field-programmable gate array (FPGA)) [Wik12e, Wik12f]. Heterogeneous computing can thus be considered a way of breaking the high performance computing barrier imposed by the limitations of Moore's Law [Sha06].

In the past years, parallel computing devices have been increasing in number and in processing capabilities. From the computational units mentioned above, newer to the computing scene are the GPUs, which are providing unprecedented levels of processing capabilities at low cost. The demand for real-time three-dimensional graphics rendering (a highly data-parallel problem) increased and, because of this, GPUs have evolved as rapidly as very powerful, full programmable and capable of supporting task and data parallelism. Now the combination of CPUs and GPUs is usual, creating a new generation of heterogeneous computing platforms. In these platforms, compute- and data-intensive portions of an application can be offloaded to the GPU, providing significant performance gains, while the host CPU executes other, less intensive tasks.

## 2.3 Parallel Programming Models and Frameworks

Parallel Applications may be developed using various programming models, including: Shared Memory, Threads, Message Passing and Hybrid. These models exist as an abstraction above the hardware and memory architecture. Although not apparent, the models mentioned are **not** specific to one type of machine or memory architectures. In fact, any of these models can be implemented (theoretically) on any hardware [Bar11a].

The next sections provide a brief description of these models and some related frameworks and implementations, with a main focus on those used to support this dissertation.

#### 2.3.1 Shared Memory and Threads

Shared memory refers to an extra large block of RAM that is attached to some address spaces, which can be accessed by several different CPUs in a multiple-processor computer system. In a shared memory system, all processors share a single view of data and the communication between processors can be as fast as memory accesses to a same location. As a result, all of these processes share the same memory segment and have access to it [Tec12]. This is great when the system has only a few processors that take advantage of the quick communication but, as more processors are added to a bus, the chances that there will be conflicts over access to the bus increase dramatically [Pac11]. This will likely cause the CPUs to cache memory, resulting in some complications [Wik12g]:

- CPU-to-memory connection becomes a bottleneck. Shared memory computers cannot scale very well. Most of them have ten or fewer processors.

- Cache coherence, whenever one cache is updated with information that may be used by other processors, the change needs to be reflected to the other processors, otherwise the different processors will be working with incoherent data. Such coherence protocols can, when they work well, provide extremely high-performance

access to shared information between multiple processors. On the other hand they can sometimes become overloaded and become a bottleneck to performance.

In shared memory multiprocessor architectures, such as those mentioned on the previous section, threads can be used to implement parallelism. Technically, a thread is defined as an independent stream of instructions that can be scheduled to run as such by the operating system.

#### **POSIX Threads**

Historically, hardware vendors have implemented their own proprietary versions of threads. These implementations differed substantially from each other making it difficult for programmers to develop portable threaded applications. In order to take full advantage of the capabilities provided by threads, a standardized programming interface was required. For UNIX systems, this interface has been specified by the IEEE POSIX 1003.1c standard. Implementations adhering to this standard are referred to as POSIX threads, or Pthreads.

Pthreads are defined as a set of C language programming types and procedure calls, implemented with a pthread.h header/include file and a thread library – though this library may be part of another library, such as libc, in some implementations [Bar12]. There are around one hundred Pthreads procedures, all prefixed "pthread." and they can be categorized into four groups: thread management (creating, joining threads, etc.), mutexes, condition variables, and synchronization between threads using read/write locks and barriers.

#### 2.3.2 Message Passing

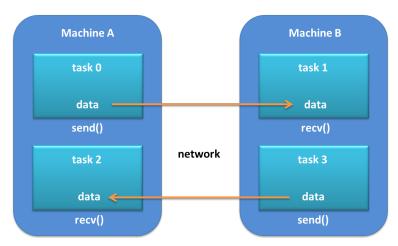

The Message Passing model uses messages exchanges between processors that have their own memory, in order to share data or synchronization state. Communicating processors can co-exist on the same computer system, using the busses and local memories for communication, or may be located on different systems, in this case interconnected via a data network, which can use common technologies (e.g., Ethernet) or very high speed ones (e.g., Myrinet, Infiniband, 10G Ethernet, etc.).

From the programming perspective, Message Passing models implementations typically include a library of subroutines that are embedded in the source code. The programmer is responsible for choosing and designing the whole parallelization strategy, including tasks synchronization. The programmer should also decide on how communication takes place: for example, if the most appropriate communication primitives are synchronous or asynchronous, what kinds of guarantees (delivery ones, sorting ones, etc.) are offered in message exchanges, etc..

Sets of tasks that use local memory during computation fit into this model; these tasks may exchange data through various communication patterns, which require cooperative complementary operations in the process involved (e.g., a send operation must have a corresponding receive operation). In Figure 2.8 it is possible to view a simplified representation of this model.

Figure 2.8: A simplified view of the Message Passing Model.

Examples of the Message Passing model are: PVM (Parallel Virtual Machine) [Lab11b], MPI (Message Passing Interface [For94], used on this project – see next – and MPL (Message Passing Library) [IBM].

#### MPI

In the 80s, there was a wide variety of Message Passing libraries but, these implementations differed substantially from each other, making it difficult for developers to create portable applications. Then, in 1992, the MPI Forum was formed, aiming to establish a standard interface for Message Passing implementations. Thus, in 1994, and subsequently in 1996, two Message Passing Interface<sup>1</sup> specifications were published.

Currently, MPI is the standard used by the industry, having replaced, virtually, all other Message Passing standards. Some of the main reasons for choosing MPI as a model for developing parallel programs are, among others [Bar11b]:

- **Standardization**: as mentioned previously, the MPI specification is the only one that can be considered a standard, and it is supported by virtually all platforms and computer architectures;

- **Portability**: there is no need to modify the code (or the changes will be minimal) when it is needed to transfer an MPI application to a different platform, provided this last one supports an implementation following the MPI standard;

- Functionality: over 115 routines are defined in MPI, covering a wide range of aspects;

- Safety: reliable communication interface, freeing the programmer from concerns about miscommunication;

- Availability: there are several MPI implementations, many open-source; the most used ones are OpenMPI [Tea11] and MPICH-2 [GLA+09], available for both Unix/Linux and Windows.

<sup>&</sup>lt;sup>1</sup> Part 1 and Part1 2 of MPI can be found at http://www.mcs.anl.gov/research/projects/mpi/.

#### MPICH2

The MPI implementation used in this project was MPICH-2, one of the most popular implementations in the industry. This is a high performance and widely portable implementation. It provides a MPI implementation that effectively supports different computation and communication platforms, including clusters: i) desktop systems; ii) shared memory systems; iii) multi-core architectures, high-speed networks (10G Ethernet, InfiniBand, Myrinet, Quadrics) and proprietary computing systems (Blue Gene, Cray, etc). MPICH-2 enables cutting-edge research in MPI, through a scalable modular framework that allows the use of other derived implementations [MPI11].

Choosing which MPI implementation to use may depend on how it behaves in executing a specific application. That is, it may be necessary to perform a benchmark on the program using different implementations, and using one or other depending on those benchmark results. In our case, the choice fell on MPICH-2, instead of OpenMPI. Due to memory limitations, OpenMPI is not suitable for large-scale problems [Sta11, fACR11], such as those used in this project. A slight increase in performance and less benchmarks variance were also observed with MPICH2, when compared to OpenMPI in our cluster.

## 2.3.3 Heterogeneous Systems

In this section we present the main models and frameworks currently used to exploit heterogeneous systems. Novel frameworks that extend those models to parallel/distributed execution environments are also present, with the exception of the clOpenCL framework, whose validation was one of the main purposes of this work, and thus is presented in a section of its own – see section 2.4.

#### **CUDA**

CUDA (Compute Unified Device Architecture) is a proprietary parallel computing platform and programming model developed by Nvidia [Nvi12] for graphics processing. CUDA enables software developers to have access to Nvidia graphics processing units (GPUs) to perform general purpose computing, using variants of standard programming languages: "C, C++ and Fortran" (standard languages with Nvidia extensions and certain restrictions). Moreover, CUDA gives developers access to the virtual instruction set and memory of the parallel computational elements, and requires developers to configure access of global memory, cache, and the amount of available threads. The developers will also be responsible for scaling the activities between the GPU and CPU [Wik12c].

Nvidia also provides what they call the "CUDA Toolkit", which gives a comprehensive development environment for C and C++ developers, including a compiler, math libraries and tools, for debugging and optimizing one's applications. CUDA also supports wrappers<sup>2</sup> for languages, like Python, Perl, Fortran, Java, Ruby, Haskell, Matlab, and so on, being these third-party ones.

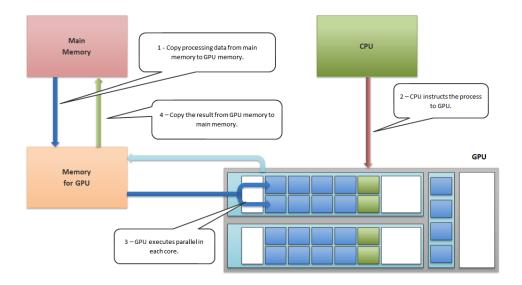

Figure 2.9 explains the CUDA processing flow, which demonstrates how CUDA enables the interaction with the GPU and global memory and the parallel throughput architecture of an enabled CUDA GPU.

Figure 2.9: CUDA architecture.

<sup>&</sup>lt;sup>2</sup> Wrapper libraries (or library wrappers) consist of a thin layer of code which translates a library's existing interface into a compatible interface.

Currently CUDA architecture shares the "market" with two competitors, namely: Khronos Group OpenCL [Gro12c] and Microsoft DirectCompute [Mic12]. But, unlike OpenCL, CUDA enabled GPUs are only available from Nvidia.

#### OpenCL

OpenCL is a parallel programming standard/framework for writing programs that execute across heterogeneous platforms (see section 2.2.4) and it was developed specifically to ease the programming burden when writing applications for this kind of platforms [GHK<sup>+</sup>11]. These platforms include CPUs, GPUs, Cell Broadband Engines [Wik12b], FPGAs (Field-Programmable Gate Arrays), DSPs (Digital Signal Processors), and other processor devices. The diversity in architectures allows the designer to provide optimized solutions for many kinds of problems. If a solution is designed within the OpenCL specification, it can scale with the growth and breadth of available architectures.

OpenCL is an open standard maintained by the non-profit technology consortium Khronos Group [Gro12b]. It has been adopted by Intel, AMD, Nvidia, and ARM Holdings. Each OpenCL implementation (i.e. an OpenCL library from AMD, Nvidia, etc.) defines platforms which enable the host system to interact with OpenCL-enabled devices. There are, presently, three major implementations of the OpenCL specification, being these the following: i) AMD APP SDK (for CPUs and AMD GPUs), ii) Nvidia's implementation (for NVIDIA GPUs only) and iii) Intel OpenCL SDK (for CPUs only).

This framework enables a language based on C99 standard [Wik12a] (with some limitations and additions) for writing kernels (programs that are to be executed on the device side, syntactically similar to a standard C function – see Appendix B.1). However, it ommits the use of function pointers, recursion, bit fields, variable-length arrays, and standard C99 header files. On the other hand, the language is extended to ease the use of parallelism with vector types and operations, synchronization and functions to work with work-items/groups. Memory region qualifiers were added (\_\_global, \_\_local,

\_\_constant, \_\_private (refer to Appendix B.1.2) and also many built-in functions, along with changes to the supported data types, which received the prefix "cl\_" (see Table B.1 in Appendix B.2).

OpenCL also provides APIs that are used to define and control the platforms, and enables parallel computing using task-based and data-based parallelism. With OpenCL, developers can give any application access to the GPU for non-graphical computing, extending this way, the power of the graphics processing unit beyond graphics.

When comparing CUDA and OpenCL one should stress the fact that CUDA supports Homogeneous Computing, while OpenCL targets, by design, Heterogeneous Computing. The later is the main reason for choosing OpenCL for this project, despite the maturity of CUDA: while CUDA only targets Nvidia GPUs (homogeneous approach), OpenCL targets any processor device that supports input and output (heterogeneous approach). This way, with OpenCL, it is possible to have multiple CPUs and GPUs, from different manufacturers and models, working together to increase performance.

Despite being a great step towards heterogeneous computing, the original OpenCL specification is unable to meet the needs of HPC applications for clusters and other distributed environments. This is due to the fact that OpenCL applications can only utilize the local devices present on a single machine. Therefore, in the OpenCL model, an application can only run in a single node and the number of OpenCL devices available to an application may be rather limited. All of this applies also to CUDA.

Thus, new or modified models are needed for OpenCL applications to be able to use several cluster nodes. To address this issue, several projects were initiated, and there are now several approaches available. In the next section a brief description of some of those approaches is provided (excluding the clOpenCL approach, presented in section 2.4).

#### MOSIX VCL

The Virtual OpenCL (VCL) cluster platform [BS11] can transparently run unmodified OpenCL applications in many devices (including GPU and APU devices) in a cluster, as if all the devices are located in the hosting node. It can create the abstraction of a global OpenCL platform combining all compute devices present in a cluster. VCL benefits OpenCL applications that can use many devices concurrently; it's users can start parallel applications on an hosting node, then VCL will manage and transparently run kernels of the application on different nodes.

The VCL cluster platform consists of three components: the *VCL library*, which is a cluster implementation of the OpenCL standard; the *broker*, which performs clusterwide allocation of resources; and a *back-end* daemon, which runs kernels on behalf of host applications. Therefore, the VCL structure is flexible enough, allowing the incorporation of many algorithms, such as *network optimizations*, *load-balancing* and *dynamic configurations* [BS11]. Note, however, that only VCL binaries are distributed.

#### Hybrid OpenCL

The Hybrid OpenCL [AONM11] project enables the utilization of OpenCL devices over the network. This platform consists of two elements: a runtime system that provides the abstraction of different OpenCL implementations and, a bridge program that connects multiple runtime systems over the network. The runtime system of the Hybrid OpenCL is divided in two parts: i) the host part, and ii) the remote part. The runtime systems of the remote part can be different. Also, the operating environment of the runtime systems of the remote part can be different from the host part.

This system was developed for a particular device independent OpenCL implementation, thus making it difficult to exploit high performance GPUs, for example. Also, although focusing on simplicity, some performance related issues still need to be tackled.

#### **GVirtuS**

The GVirtus (Generic Virtualization Service) [GML+11] is a framework for implementation of split-driver based abstraction components and the virtualization of hardware devices. GVirtuS fills the gap between in-house hosted computing clusters, equipped with custom devices, and pay-for-use high performance virtual clusters deployed via public or private computing clouds. It allows an instanced virtual machine to access CUDA powered GPGPUs in a transparent way, with an overhead slightly greater than a real machine/GPGPU setup. GVirtuS is hypervisor independent, and although it currently virtualizes nVIDIA CUDA based GPUs, it is not limited to a specific brand technology [fHPSC12]. The framework currently has full threadsafe support to CUDA drivers, CUDA runtime and OpenCL. Also, it partially supports OpenGL integration. GVirtuS approach is composed in two parts: GVirtuS Frontend, a dynamic loadable library with the same application binary interface that runs on the guest user space; GVirtuS Backend, a server application running on the host user space and performing concurrent requests [MCG+11].

#### rCUDA

rCUDA [DPnS<sup>+</sup>10] enables applications to concurrently use CUDA-compatible GPUs installed in remote computers as if they were local devices. To enable a remote GPU-based acceleration, rCUDA creates virtual CUDA-compatible devices on those machines without a local GPU. These virtual devices represent physical GPUs located in a remote host offering GPGPU services. As a result, all of the nodes are able to concurrently access the whole set of CUDA accelerators installed in the cluster.

This framework follows a client-server model where the client uses a wrapper library and a GPU network service listens for TCP requests. On the down side, the framework is limited in the number of compute devices that CUDA can handle (NVIDIA devices only).

### 2.3.4 Hybrid Models

Usually, the exploitation of heterogeneous systems is associated with hybrid models, although these models have been used, until recently, mainly in homogeneous systems. A hybrid model is a combination of several parallel programming models in the same program. They may be mixed in the same source; and they may be combinations of components or routines, each being in a single parallel programming model.

The most familiar hybrid model is the junction of MPI with OpenMP<sup>3</sup> [Gro12a], where OpenMP parallelization takes place at each node and MPI parallelization between nodes. Depending on the kind of communication and computation, these models can be used, generally, in two ways. In the first one, communication and computation do not overlap: MPI is called only outside of parallel regions and by the master thread; also, MPI is called by several threads. In the second one, communication and computation do overlap (while some of the threads communicate, the rest are executing an application): MPI is called only by the master thread; communication is carried out by several threads; each thread handles its own communication demands [vA08].

The hybrid approach is difficult: developers always want to use the best tools for each part of their program, and that sometimes means building their applications from pieces in different languages. However, this model usually translates in performance benefits, due to better computation/communication ratios.

In the work presented on this dissertation two different hybrid models were used: a hybrid model using i) MPI to manage a distributed set of worker processes, and ii) OpenCL to exploit computation on local worker-specific devices; another hybrid model (clOpenCL) based on i) a distributed set of OpenCL device-proxies (daemons), POSIX Threads to interact with a cluster-aware OpenCL routine, and iii) Open-MX for communications. The clOpenCL model is thoroughly explained in section 2.4.

$<sup>^3</sup>$  An API that can be used for multithreaded shared memory parallelization that enables parallelization of one part of the program at a time.

# 2.4 Cluster OpenCL

Frameworks like VCL, Hybrid OpenCL, GVirtuS and rCUDA, previously presented in section 2.3.3, try to cope with the limitations of specifications originally tailored to self-contained systems, by providing the necessary support for their instantiation in distributed environments, like clusters, grids and even clouds.

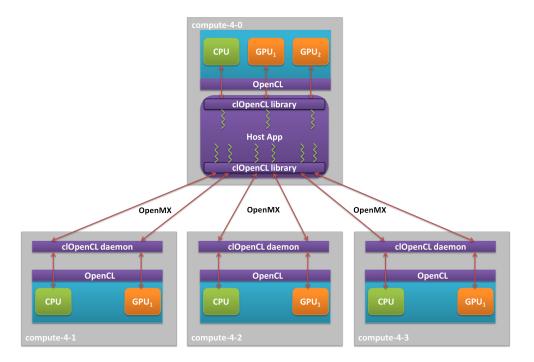

Making possible the running of unmodified OpenCL applications in a transparent way, on devices scattered in a cluster environment, was the main motivation of a novel framework, named clOpenCL (cluster OpenCL). clOpenCL was developed (as part of a R&D project to which this dissertation is related) using an hybrid programming model that mixes POSIX Threads, OpenCL and a low-level/high performance message passing library (Open-MX<sup>4</sup>) [Gog11].

#### 2.4.1 General Architecture

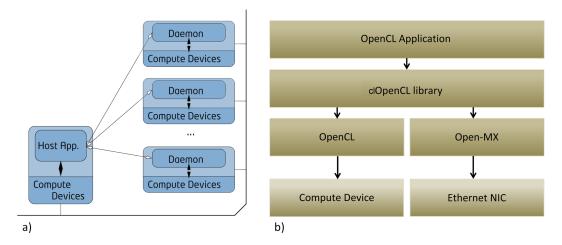

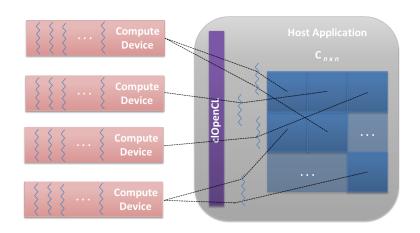

clOpenCL comprises a wrapper library and a set of daemons. Every call from an application to an OpenCL primitive is intercepted by the wrapper library, which redirects its execution to a specific daemon at a cluster node or to the local OpenCL runtime. clOpenCL daemons are simple OpenCL programs that listen and handle remote calls and interact with local devices. The host component of a typical clOpenCL application will be multi-threaded (POSIX Threads)<sup>5</sup>. It will start in a particular cluster node and will create OpenCL contexts, command queues, buffers, programs and kernels across all cluster nodes [ARPS12].

Figure 2.10.a) shows the clOpenCL operation model, where a single OpenCL host application component interacts with multiple compute devices, whether local or remote. Figure 2.10.b) represents the different software and hardware layers that support the host

<sup>&</sup>lt;sup>4</sup> An open-source message passing stack over generic Ethernet which provides low-level communication mechanisms at user-level space and allows to achieve low latency communication and low CPU overhead.

<sup>&</sup>lt;sup>5</sup> This is mainly for performance reasons, since there is no fundamental limitation for not using the process model on top of the clOpenCL library.

application component.

Figure 2.10: clOpenCL (a) operation model, (b) host application layers.

### 2.4.2 Operation Model

When the host program starts, the clOpenCL wrapper library, wich also wraps the main function, locates all active clOpenCL daemons by interacting with the Open-MX mapper service (this service creates a distributed directory, where each process, with an opened Open-MX end-point, is registered).

In a traditional OpenCL application, the programmer has to manipulate only the objects returned from the OpenCL API, namely: platforms and device identifiers, contexts, command queues, buffers, images, programs, kernels, events and samplers. These objects are actually pointers to complex OpenCL data structures, having their internal constitution not accessible to the programmer. In a distributed/parallel environment, where OpenCL primitives are executed in multiple daemons, those pointers cannot be used only to identify objects, because each daemon has its own address space. Therefore, for each object created by OpenCL, the wrapper library returns a "fake pointer" used as a global identifier, and stores the real pointer alongside with the corresponding daemon location.

Each time the wrapper library redirects an OpenCL primitive, its parameters are

packed into an Open-MX frame and sent to the remote daemon that will execute the primitive. Every parameters that reference OpenCL objects are previously mapped into their real pointers and the daemon is determined accordingly. The wrapper library and daemons do not maintain any information about calls to OpenCL primitives, i.e., they are stateless. Any data or state needed for subsequent primitive calls are maintained by the OpenCL runtime at each cluster node. Therefore, it is not necessary to manage complex data structures related to the OpenCL operation and state [ARPS12].

Typically, an OpenCL application starts with a discovery phase with the purpose of finding platforms and their respective devices locally (*i.e.*, available at the node where the application is hosted). In clOpenCL this discovery phase will return a set of all platforms and devices available (both *local* and *remote*) in the cluster nodes where the clOpenCL service (daemon) is running. In more detail, clOpenCL first returns all local platforms, if any (once it is not mandatory that any OpenCL platforms be locally available); afterwards it returns the remote platforms, node by node.

A problem with clOpenCL was to know to which cluster node a certain platform belongs. Thus, the OpenCL primitive clGetPlatformInfo was extended with a special attribute named CL\_PLATFORM\_HOSTNAME. Having the possibility of choosing specific cluster nodes where to run OpenCL kernels may be useful, e.g., for load balancing purposes.

## 2.4.3 Using clOpenCL

Porting OpenCL programs to clOpenCL, only requires linking to the OpenCL and clOpenCL libraries. This is accomplished by taking advantage of the GCC directives, -Xlinker --wrap, for function wrapping during link-time. Currently, clOpenCL does not support mapping buffer and image objects. However, as its current state, the clOpenCL platform is enough to the purpose of testing its general concept, including running basic OpenCL applications [ARPS12], like a kernel for matrix multiplication.

## 2.4.4 Distributed OpenCL

dOpenCL (distributed OpenCL) [KSG12] is a recent framework, developed at the same time as clOpenCL, with whom has resemblances: it supports transparent multi-node-multi-accelerator OpenCL applications and combines a wrapper client library with remote services. However, dOpenCL is oriented to general distributed environments, uses a TCP/UDP based communication framework, and devices may not be concurrently shared. In turn, clOpenCL targets HPC clusters, uses Open-MX to maximize the utilization of commodity Gigabit Ethernet links, and devices are fully shareable. Both approaches work on top of any OpenCL platform and so are able to exploit many device types.

## 2.5 Case Study: Matrix Product

To test, evaluate and demonstrate the usability of a new parallel programming framework, it is essential to choose appropriate case studies. In this work, clOpenCL was evaluated using a reference HPC "benchmark" algorithm: the Matrix Product algorithm.

Although simple, this "embarrassingly parallel" algorithm is sufficient to test the scalability and correctness of the current clOpenCL implementation. Choosing this algorithm also allows for the quick development of alternate implementations (both serial and parallel) to be used for control (correctness verification) and performance comparison purposes. Note, however, that the aim is not an HPC-class performance of the clOpenCL version but, as already stated, to assess its correctness and scalability.

#### Matrix Product Basic Concepts

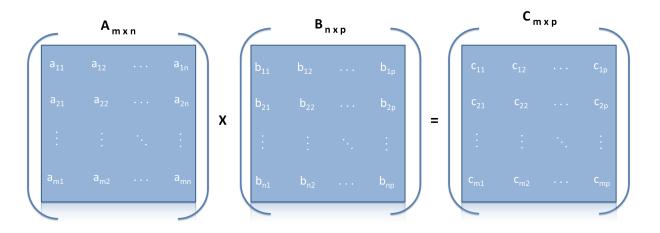

This section, quickly describes the concept of the matrix product in formal terms. The product of a matrix A of order  $m \times n$  (m rows and n columns) by a matrix B of order

<sup>&</sup>lt;sup>6</sup> The program that has virtually no communications between the system's parallel activities, is called embarrassingly parallel.

$n \times p$  (n rows and p columns), is a matrix C of order  $m \times p$  (m rows and p columns) – see Figure 2.11. An element in C, on the i-th row and j-th column, is obtained by the dot product of the entire i-th row of A by the entire j-th column of B (this is why if A has n columns, B must have n rows). For example, if vector i is a row of A that contains [a11, a12, ..., a1n], and vector j is a column of B that contains [b11, b12, ..., b1p], their dot product can be computed as follows: i.j = a11b11 + a12b12 + ... + a1nb1p.

Figure 2.11: Matrix multiplication representation.

If A and B are square matrices of order  $4 \times 4$ , the full matrix multiplication will require 16 products, i.e., each of the four rows of A must be multiplied by each of the four columns of B. If A and B are not square matrices, the product requires vectors of equal length, so the rows of the first matrix must have the same size as the columns of the second.

## 2.6 Experimental Testbed

To test, evaluate and demonstrate the usability of a developed parallel application, there is always a need for a parallel computing platform where these activities can be performed. The testbed platform used in this work was a small scale commodity cluster, operated

by the Informatics Laboratory of ESTIG/IPB. The Cluster concept, as a parallel execution platform, was already discussed at section 2.2. Therefore, in this section, only the particular aspects that characterize the used cluster will be described.

#### 2.6.1 Computational Systems

The cluster includes the following computational systems:

- a frontend (beta), with an Intel Core 2 Duo E6400 2.13GHz CPU and 4Gb of RAM;

- several subsets of compute nodes, defined taking into account their physical location, their hardware features and their degree of availability (continuous/intermittent):

- datacenter subset, with 4 computing nodes, each one with an Intel Core 2 Quad Q9650 3GHz CPU, 8Gb of RAM and two Ethernet 1Gbps NICs (on-board Intel 82566DM-2 and a PCI64 SysKonnect SK-9871); plus, the nodes are fitted with NVIDIA GTX 460 GPUs (1Gb of GDDR5 RAM): 1 node (compute-4-0) with 2 GPUs and the 3 remaining nodes (compute-4-1 to compute-4-3) with 1 GPU each; this subset is continuously available for work execution;

- labinf subset, with 8 computing nodes (compute-4-4 to compute-4-11), each

one with an Intel Core 2 Quad Q9400 2.6GHz CPU and 8Gb of RAM; this

subset is only available to work outside lessons hours;

- esa subset, with 3 computing nodes (esa-16-0 to esa-16-2), located at the ESA/IPB Informatics Resource Center, each one with an AMD Opteron 6128 Magny-Cours 2.0GHz "Octo-Core" CPU, and 16Gb of RAM; this subset is continuously available for work execution.

For this work only the nodes of the *datacenter* subset were used, taking advantage of all of the processing devices available there: 4 CPUs (16 cores in total) and 5 GPUs.

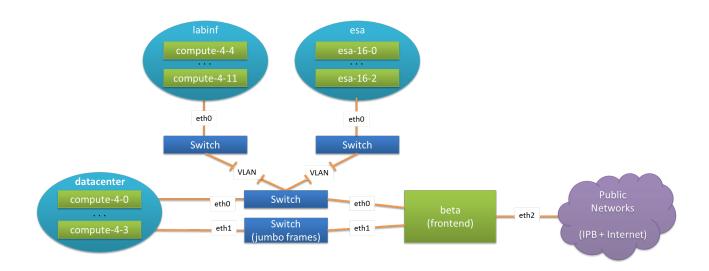

### 2.6.2 Network(s)

The frontend and the compute nodes are interconnected in a main private network  $(eth\theta)$ , based on 1Gbps Ethernet; however, for logistical reasons, only the datacenter node subset is directly connected to the same switch on which the frontend also connects; the remaining subsets, external to the datacenter, bind to this switch through a succession of switches properly configured to support a specific cluster VLAN. A secondary private network (eth1) also exists, connecting the datacenter node subset with the frontend; the 1Gbps Ethernet switch used for this purpose is configured with jumbo frames (mtu 9000); this secondary network is used as a "poor-man's", high speed network, once the cluster currently lacks Myrinet or Infiniband. This configuration is illustrated in Figure 2.12.

Figure 2.12: Cluster network(s) configuration.

It should be noted that the dispersion of the different node subsets, separated by multiple switches, is not advisable to perform work that use simultaneously different sets and have high communication needs. However that was not the case of this work, since only the *datacentre* node subset was used.

### 2.6.3 Exploitation System

All cluster systems run Linux Rocks [Gro12d] (version 5.4.3), a specific distribution for cluster environments, developed as part of a project that began in 2000. The ROCKS distribution is built upon the CentOS distribution, a community version of Red Hat Enterprise Server (RHEL), which is a commercial distribution. The choice of CentOS allows a solid and stable foundation, binary compatible with RHEL, which is a reference for the business market. The ROCKS distribution adds to CentOS a number of facilities: support to bulk (re)installation (automatic, over the network, via PXE) of compute nodes [Sac09]; a Ganglia system for node monitoring [Pro12b]; the SGE (Sun Grid Engine) system [Sun12] for queue management of deferred execution of work; the Condor system for the automatic load balancing of nodes through processes migration [Pro12a]; various MPI platforms (such as OpenMP and MPICH2), etc.

On ROCKS, the *frontend* node hosts all cluster user accounts and, in general, all the necessary software; these accounts are shared over the network via NFS, to the compute nodes; this sharing extends to a folder /share/apps, with applications installed on the *frontend* and accessible to all nodes; the nodes have a local partition (/state/partition1) immune to possible reinstallation, thus adequate to store, in a lasting way, large amounts of data.

OpenCL and Open-MX support software was also installed on the *frontend* and the *datacenter* node subset. The specific OpenCL platform and GPU driver versions used were AMD SDK 2.6 with driver 11.12, and CUDA 4.1.28 with driver 285.05.33. Open-MX 1.5.2 was used with the SysKonnect NICs (that provide better performance than the on-board Intel NICs), the ones used to build the secondary private network (*eth1*).

# Chapter 3

# **Preliminary Experiments**

As mentioned previously (see section 2.5), the Matrix Product algorithm was chosen to be the case study of this dissertation. Thus, in order to have an idea of the magnitude of the performance gains eventually achieved by the parallel approaches that would need to be developed (at least a clOpenCL based approach), a preliminary assessment was made of readily available and well-known sequential and parallel approaches, including naive approaches, approaches based on public domain linear algebra libraries and also commercial reference approaches.

# 3.1 General Experimental Conditions

All the experimental studies (including those of Chapter 4) were narrowed to square matrices of order  $n \in \{8K, 16K, 24K\}$ , filled with single-precision elements (4 byte floats). These 3 different orders were chosen to support a minimal scalability study. This configuration resulted into matrices of size no less than 256 Mbytes, 1 Gbyte and 2.25 Gbytes, respectively. As there are 3 matrices involved (the operands A and B, and the result matrix C = AB) the minimum theoretically RAM occupancy is 768 Mbytes, 3 Gbytes and 6.75 Gbytes, respectively.

For all experiments of this chapter, the complete matrices A and B were used to yield the complete matrix C, i.e., the whole A matrix was multiplied by the whole B matrix through a single execution of the matrix product function used. Furthermore, all experiments were performed in the cluster node compute-4-0, using a single core, except for Matlab. The compiler optimization levels used in each case are specifically stated. All execution times presented are averages of at least 3 runs.

## 3.2 Sequential Naive Approach

The first evaluated approach follows a naive sequential algorithm that served as a starting point to the development of the remaining variants.

Under this algorithm, the matrices A, B and C are first allocated (using the order n sizes previously mentioned); and initialized with float values. Then, matrix B is transposed into  $B^T$  (see Figure 3.1 for an example); this is done to accelerate the product of A rows by B columns (since arrays are stored in row-major order in programs developed in C language, the transposition of matrix B will make the dot product of A rows by B columns much more cache-friendly, by minimizing cache-misses). Finally, matrices A and  $B^T$  are multiplied.

$$\begin{bmatrix}

1 & 2 & 8 \\

3 & 4 & 3 \\

5 & 6 & 1

\end{bmatrix} =

\begin{bmatrix}

1 & 3 & 5 \\

2 & 4 & 6 \\

8 & 3 & 1

\end{bmatrix}$$

Figure 3.1: Example of a matrix transposition.

Code Excerpt 3.1 shows the implementation and invocation of the naive multiplication function (the full algorithm implementation code is in Appendix A.1).

```

#define SIZE 24576 //16384//8192

1

3

void mulMatrix(float *a, float *b, float *c)

// assumes "b" has been transposed

4

5

int i, j, k, cc;

6

float v;

int numCells;

8

9

10

numCells = SIZE*SIZE;

cc=0;

11

for(i=0; i<numCells; i+=SIZE){</pre>

12

for(j=0; j<numCells; j+=SIZE){</pre>

13

v = 0.0;

14

for(k=0; k<SIZE; k++)</pre>

15

v += a[i+k] * b[j+k];

16

c[cc] = v;

17

18

cc++;

}

19

20

^{21}

int main()

22

23

{

24

mulMatrix(a, bTrans, c);

25

26

//...

27

}

```

Code Excerpt 3.1: Sequential Naive Approach Matrix Product.

Table 3.1 presents the evaluation results, with GCC optimization level "O3".

Table 3.1: Sequential Naive Approach Execution Time (seconds).

| Order $n$ (SIZE) | 8 <i>K</i> | 16K      | 24K       |  |

|------------------|------------|----------|-----------|--|

| Execution Time   | 610,50s    | 4901,19s | 16569,40s |  |

# 3.3 BLAS Approaches

BLAS (Basic Linear Algebra Subprograms) [For12] are routines that provide standard building blocks for performing basic vector and matrix operations. The Level 1 BLAS perform scalar, vector and vector-vector operations; the Level 2 BLAS perform matrix-vector operations; the Level 3 BLAS perform matrix-matrix operations. Because BLAS routines are efficient, portable, and widely available, they are commonly used in the development of high quality linear algebra software.

The Level 3 BLAS provides the following function for the multiplication of two matrices (single-precision): sgemm(TransA, TransB, M, N, K, ALPHA, A, LDA, B, LDB, BETA, C, LDC). The function sgemm (Single Precision General Matrix Multiply) is not limited to perform a single product between two matrices, since the input parameters aren't only the matrices A, B and C. Instead, this routine calculates  $C = \alpha AB + \beta C$ , where  $\alpha$  and  $\beta$  are scalar coefficients. Thus, to perform the simple product C = AB, it is enough to have  $\alpha = 1.0$  and  $\beta = 0.0$ . The sgemm function has also the option of using the transposed forms of A, B, or both. The function full list of parameters and their meaning follows:

- TransA: specifies whether to transpose matrix A.

- TransB: specifies whether to transpose matrix B.

- M: number of rows in matrices A and C.

- N: number of columns in matrices B and C.

- K: number of columns in matrix A; number of rows in matrix B.

- ALPHA: scaling factor for the product of matrices A and B.

- A: matrix A.

- LDA: the size of the first dimention of matrix A; if passing a matrix A[m][n], the value should be m.

- B: matrix B.

- LDB: the size of the first dimention of matrix B; if passing a matrix B[m][n], the value should be m.

- BETA: scaling factor for matrix C.

- C: matrix C.

- LDC: the size of the first dimention of matrix C; if passing a matrix C[m][n], the value should be m.

3.4. ATLAS BLAS

All the non-naive approaches evaluated in the next sections (including Matlab) are based on Level 3 BLAS implementations. When using the **sgemm** function, special care must be taken to know which order (row/column major) is assumed by the implementation (the original specification is Fortran-oriented and so the original order is column-major).

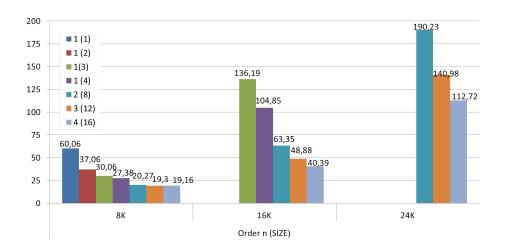

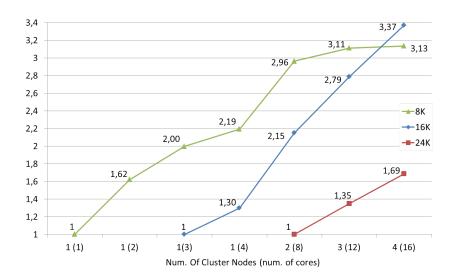

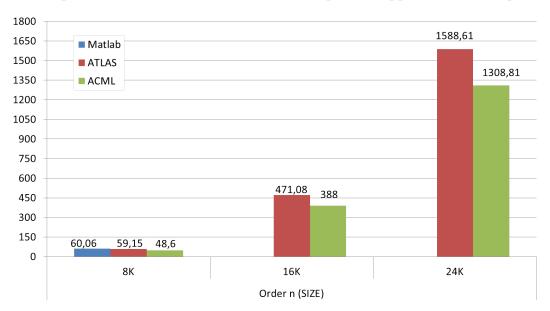

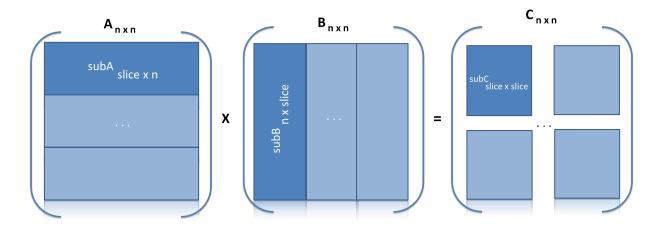

## 3.4 ATLAS BLAS

The Automatically Tuned Linear Algebra Software (ATLAS) [Sou12] provides a highly optimized implementation of the BLAS interface, heavily used in high-performance computing, and with C and Fortran77 interfaces. It is characterized for having an optimization approach called Automated Empirical Optimization of Software (AEOS), which is able to produce code specifically tuned for the target execution system. In our case, the ATLAS version used was optimized for the datacenter node subset CPUs (Core 2 Quad Q9650).