# Formal Design and Verification of Digital PID Gain Scheduling Controllers

A Model Checking Approach

## Pablo Armando Ordóñez Aguileta

Department of Engineering University of Sheffield

This dissertation is submitted for the degree of Doctor of Philosophy

February 2018

I would like to dedicate this thesis to my loving parents Pedro and Socorro.  $\ldots$

## Declaration

I hereby declare that except where specific reference is made to the work of others, the contents of this dissertation are original and have not been submitted in whole or in part for consideration for any other degree or qualification in this, or any other university. This dissertation, entitled "Formal Design and Verification of Digital PID Gain Scheduling Controllers", is my own work and contains nothing which is the outcome of work done in collaboration with others, except as specified in the text and Acknowledgements.

Pablo Armando Ordóñez Aguileta February 2018

### Acknowledgements

My sincerest gratitude to my adviser, Tony Dodd, I could not have done any of this without his support and encouragement throughout this long journey. His continuous guidance, advice, and perspective made this possible even when I thought it was not. I will be forever in debt with you Tony.

I would like to thank Andy Mills and Jun Liu for continuously providing feedback, perspective, and more importantly, support during the development of this thesis. You have been wonderful mentors and both of you played a fundamental role for the development of this work.

I am truly honoured to had been part of the ACSE UTC group during my doctoral studies. Not only did I have colleagues but I made friends, a wonderful group of people willing to help or discuss ideas, especially if that meant a quick visit to The Red Deer. Special thanks to Andrew, Masz, Chris, Romain, Kacper, Ibrahim, and Dan. That being said, thanks to The Red Deer for always being open when I needed it.

To all my wonderful friends in this side of the world, thank you for being my family away from home: Ariel, Debbie, AndyLú, Toño, Alepa, Mario, Jesús Alejandro, Yessi, Maza, Robbie, Matamoros, Jaimito, Yess, Aldo, Harry, Oli, Jeff, Liliana, Celeste, Jorgito, Anna-Lena, Samantha, Matei, Larín, and Antito. To Raquelín for helping me dance my problems away at the very end of this journey. To Lucy Kemp for being so supportive during the homestretch. To Matou for helping me so much when I needed it the most. A Karlira por quererme cuando menos lo esperaba.

And last but not least, I would like to thank my family. They have always supported me in whatever new challenge I took. To my dad and mom for everything. To my brother Pedrito for always being there for me. To my uncle Pablo and my aunt Sonia, for being my parents all over again. To my cousins Sonia, Made, and Pabloco, because you are basically my siblings. My parents always thought that education and knowledge could open any door, this is a testament to that idea.

### Abstract

The verification process of embedded systems is fundamental for their correct development. Embedded control is a popular choice among the engineering community, making the relationship between control systems and computer science very close. Gain scheduling is a typical approach for safety-critical systems (e.g. jet-engines). It is preferred due to a known route to certification. Nonetheless, stability and performance are hard to prove analytically. Consequently, safety and airworthiness are achieved by extensive testing, and therefore a new way for verification is desirable.

Model checking, an exhaustive verification technique, is a part of formal methods. Model checking can aid in detecting ambiguities and collisions in requirements, increasing and improving testing coverage and error-detection rate. However, there are still limitations and challenges to model checking. The *state-space explosion* problem limits its use to realistic dynamic control systems: Computational memory runs out or available data types are not appropriate for modelling.

This thesis addresses the formal design and verification of discrete PID gain-scheduled control systems. By the means of a novel abstraction methodology the control problem is resolved in a model checking environment; formally tuning the controller whilst systematically constructing a control schedule. The work in this overcomes typical constraints imposed by model checking. In this manner, the gain-scheduled controller can be efficiently generated and the resulting schedule is *correct-by-construction* with respect to high level performance requirements. This novel methodology incorporates computer science and control systems tools, proposing an *a priori* verification approach in contrast to current *a posteriori* testing activities. By combining computer science and control engineering, the gap between formal methods and control systems is reduced.

The next step in this line of research is to analyse the scalability of the approach using more realistic models and design cases; in this manner the *state-space explosion* problem can be addressed with a divide and conquer approach. Also, a trade-off analysis between benefits and the required effort learning the new approach in a real development cycle must be conducted to assess feasibility and capabilities of the approach.

## **Table of contents**

| Li                   | List of figures xv List of tables xxiii |          |                                                 |    |

|----------------------|-----------------------------------------|----------|-------------------------------------------------|----|

| Li                   |                                         |          |                                                 |    |

| Symbols and Acronyms |                                         |          | v                                               |    |

| 1                    | Intr                                    | oductio  | n                                               | 1  |

|                      | 1.1                                     | Motiva   | ation                                           | 1  |

|                      |                                         | 1.1.1    | System Verification                             | 1  |

|                      |                                         | 1.1.2    | Trends in Aerospace Systems                     | 2  |

|                      |                                         | 1.1.3    | Avionics Certification                          | 4  |

|                      |                                         | 1.1.4    | Safety-Critical Software Development Life Cycle | 5  |

|                      |                                         | 1.1.5    | Commercial Jet-Engine Control                   | 7  |

|                      |                                         | 1.1.6    | Formal Methods and Model Checking               | 0  |

|                      |                                         | 1.1.7    | Challenges for a Formal Development Approach    | 1  |

|                      | 1.2                                     | Aims a   | and Objectives                                  | 2  |

|                      | 1.3                                     | Contri   | butions                                         | 3  |

|                      | 1.4                                     | Thesis   | Overview                                        | 5  |

| 2                    | Lite                                    | rature ] | Review and Technical Background 1               | 7  |

|                      | 2.1                                     | Overv    | iew                                             | 7  |

|                      | 2.2                                     | Literat  | ure Review                                      | 8  |

|                      |                                         | 2.2.1    | Verification & Validation                       | 8  |

|                      |                                         | 2.2.2    | Controller Synthesis and Properties Generation  | 9  |

|                      |                                         | 2.2.3    | Challenges and Approaches                       | 21 |

|                      |                                         | 2.2.4    | Remarks                                         | 4  |

|                      | 2.3                                     | Techni   | cal Background                                  | 6  |

|                      |                                         | 2.3.1    | Dynamic Control Systems                         | 6  |

|                      |                                         | 2.3.2    | Formal Methods and Model Checking               | 9  |

|   |      | 2.3.3    | Model Checking and Hybrid Systems                               |  |  |  |

|---|------|----------|-----------------------------------------------------------------|--|--|--|

|   |      | 2.3.4    | Timed-Automata and Computation Tree Logic                       |  |  |  |

|   | 2.4  | Final I  | Remarks                                                         |  |  |  |

| 3 | Dyn  | amic Sy  | ystem Abstraction Methodology 37                                |  |  |  |

|   | 3.1  | Overv    | iew                                                             |  |  |  |

|   | 3.2  | Discre   | te-time SISO LTI Models                                         |  |  |  |

|   | 3.3  | Fixed    | Point Representation Using Integer Data                         |  |  |  |

|   |      | 3.3.1    | Data Types for Data Representation                              |  |  |  |

|   |      | 3.3.2    | Fixed Point Data Size Considerations                            |  |  |  |

|   |      | 3.3.3    | Fixed Point Arithmetic Using Integer Data                       |  |  |  |

|   |      | 3.3.4    | Ad Hoc Data Type                                                |  |  |  |

|   | 3.4  | Model    | ling Error Compensation                                         |  |  |  |

|   |      | 3.4.1    | Parametric Compensation - $\varepsilon_1$ Error                 |  |  |  |

|   |      | 3.4.2    | Fixed Point Representation Compensation - $\varepsilon_2$ Error |  |  |  |

|   |      | 3.4.3    | Scaling Compensation - $\varepsilon_3$ Error                    |  |  |  |

|   |      | 3.4.4    | Global Error                                                    |  |  |  |

|   | 3.5  | Safety   | Guarantees                                                      |  |  |  |

|   |      | 3.5.1    | Over and Under Approximation                                    |  |  |  |

|   |      | 3.5.2    | Abstraction Generation                                          |  |  |  |

|   | 3.6  | Final I  | Remarks and Discussion                                          |  |  |  |

| 4 | Con  | trol Pe  | formance Requirements Formal Verification 63                    |  |  |  |

|   | 4.1  | Overview |                                                                 |  |  |  |

|   | 4.2  | High I   | Level Requirements                                              |  |  |  |

|   | 4.3  | Desig    | n for Verifiability                                             |  |  |  |

|   |      | 4.3.1    | Automata Design                                                 |  |  |  |

|   |      | 4.3.2    | UPPAAL Automata                                                 |  |  |  |

|   | 4.4  | Requi    | rements Formulation for Verification                            |  |  |  |

|   | 4.5  | Case S   | Study: Thrust Control Verification                              |  |  |  |

|   |      | 4.5.1    | Verification Problem Formulation                                |  |  |  |

|   |      | 4.5.2    | System Abstraction                                              |  |  |  |

|   |      | 4.5.3    | Verification Results                                            |  |  |  |

|   |      | 4.5.4    | Discussion                                                      |  |  |  |

| 5 | Digi | tal PID  | Controller Formal Design 93                                     |  |  |  |

|   | 5.1  | Overv    | iew                                                             |  |  |  |

|    | 5.2    | Proble  | m Formulation                                   | 94  |

|----|--------|---------|-------------------------------------------------|-----|

|    |        | 5.2.1   | Discrete PID Controller                         | 94  |

|    |        | 5.2.2   | Controller Tuning: A Model Checking Formulation | 97  |

|    | 5.3    | Contro  | oller Synthesis Methodology                     | 100 |

|    |        | 5.3.1   | Timed-Automata Update                           | 101 |

|    |        | 5.3.2   | Requirements Formulation for Design             | 104 |

|    |        | 5.3.3   | Controller Tuning Algorithm                     | 105 |

|    | 5.4    | Case S  | Study: Thrust Control Design                    | 106 |

|    |        | 5.4.1   | Requirements and Initial Conditions             | 107 |

|    |        | 5.4.2   | Results and Discussion                          | 108 |

| 6  | Digi   | tal PID | Gain Scheduling Control Formal Design           | 115 |

|    | 6.1    | Overv   | iew                                             | 115 |

|    | 6.2    | Proble  | m Formulation                                   | 116 |

|    |        | 6.2.1   | Gain Scheduled PI Control                       | 116 |

|    |        | 6.2.2   | Schedule Design: A Model Checking Formulation   | 118 |

|    | 6.3    | Sched   | ule Synthesis Methodology                       | 119 |

|    |        | 6.3.1   | Timed-Automata Update                           | 119 |

|    |        | 6.3.2   | Requirements Formulation for Design             | 123 |

|    |        | 6.3.3   | Schedule Design Algorithm                       | 124 |

|    | 6.4    | Case S  | Study: Thrust Control Schedule Design           | 125 |

|    |        | 6.4.1   | Problem Formulation and Requirements            | 127 |

|    |        | 6.4.2   | Results and Discussion                          | 131 |

| 7  | Con    | clusion | s and Future Work                               | 145 |

|    | 7.1    | Conclu  | usions                                          | 145 |

|    | 7.2    | Future  | e Work                                          | 147 |

| Re | eferen | ces     |                                                 | 151 |

# List of figures

| 1.1 | Block diagram representation of an Electronic Engine Control (EEC) unit                    |    |

|-----|--------------------------------------------------------------------------------------------|----|

|     | and the functional features it contains as software                                        | 4  |

| 1.2 | V-Shaped software development cycle. Popular within the aerospace industry                 |    |

|     | for software development. This process makes clear emphasis on testing ac-                 |    |

|     | tivities throughout the whole cycle, which are fundamental when developing                 |    |

|     | safety-critical software.                                                                  | 5  |

| 1.3 | System verification: a posteriori approach. The verification takes place in                |    |

|     | the product or a prototype of the product. The construction of the prototype               |    |

|     | or product is performed before the verification activities takes place. If bugs            |    |

|     | are found another iteration of the design and verification process is necessary.           | 7  |

| 1.4 | Model checking verification approach: verification is performed in an $a$                  |    |

|     | priori manner. The verification is performed in a model of the system under                |    |

|     | analysis before generating the product or a prototype                                      | 8  |

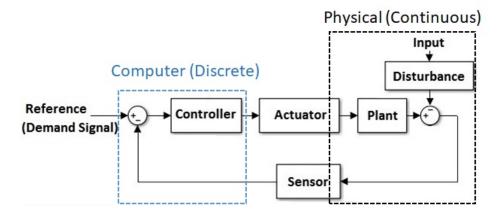

| 2.1 | Generic dynamic hybrid control system. A physical system regulated by a                    |    |

|     | computer-based controller.                                                                 | 27 |

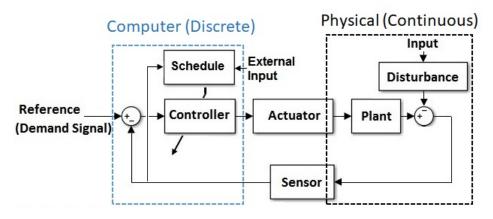

| 2.2 | Generic gain scheduled dynamic hybrid control system. A physical system                    |    |

|     | regulated by a computer based controller. The controller gains are con-                    |    |

|     | figurable while in operation depending on external factors and operating                   |    |

|     | points                                                                                     | 28 |

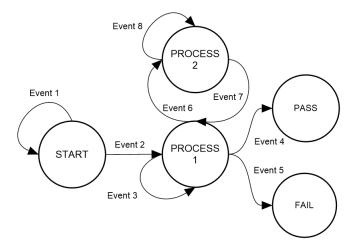

| 2.3 | Generic transition system consisting of five nodes and eight edges. Every                  |    |

|     | node represents a state of the system and the edges represent how actions                  |    |

|     | make the system move between states                                                        | 30 |

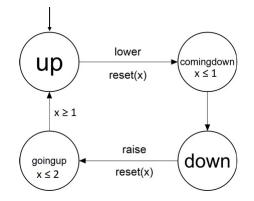

| 2.4 | Timed-Automaton example of a gate that open and closes on request. The                     |    |

|     | timing requirements regarding the opening and closing actions are modelled                 |    |

| _   | using the clock <i>x</i>                                                                   | 32 |

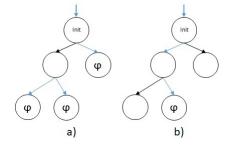

| 2.5 | Graphic representation of <i>state formulae</i> in combination with <i>path formulae</i> . |    |

|     | a) $\forall \varphi$ case and b) $\exists \varphi$ case                                    | 34 |

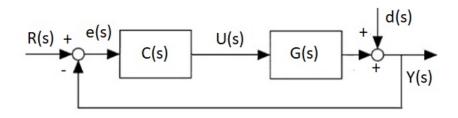

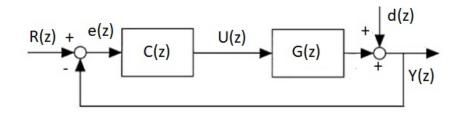

| 3.1 | Generic continuous time closed loop control system.                                 | 45 |

|-----|-------------------------------------------------------------------------------------|----|

| 3.2 | Generic discrete time closed loop control system.                                   | 47 |

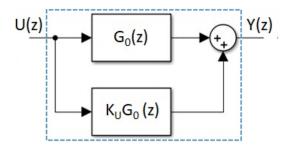

| 3.3 | Open loop representation of the plant model with gain error compensation            | 47 |

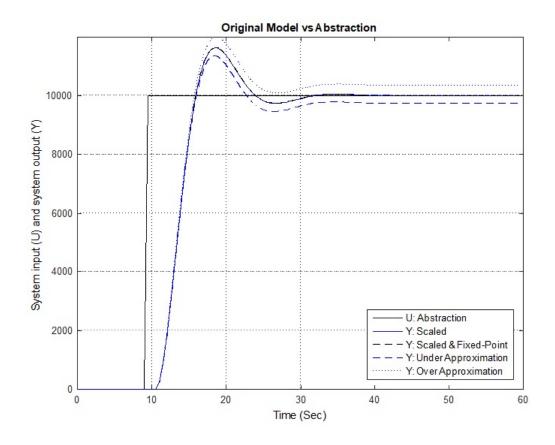

| 3.4 | Discrete-time system and discrete-time system abstraction response to a             |    |

|     | step input comparison. $K_U = 0.001$ . $K_S = 10,000$ . $K_S$ is used to scale the  |    |

|     | original system and original with fixed-point system responses (this is done        |    |

|     | for comparison purposes). The original input is a unit step, it is omitted in       |    |

|     | the comparison for scaling reasons.                                                 | 59 |

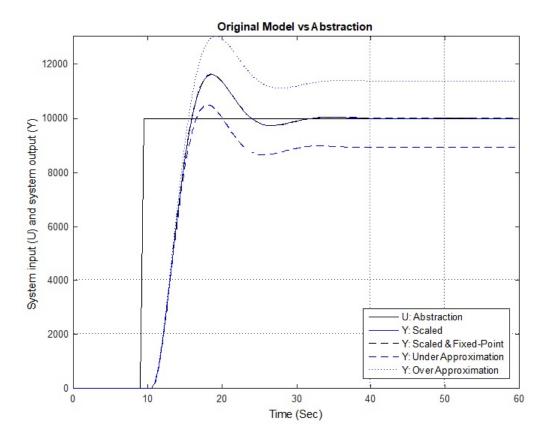

| 3.5 | Discrete-time system and discrete-time system abstraction response to a step        |    |

|     | input comparison. $K_U = 0.005$                                                     | 60 |

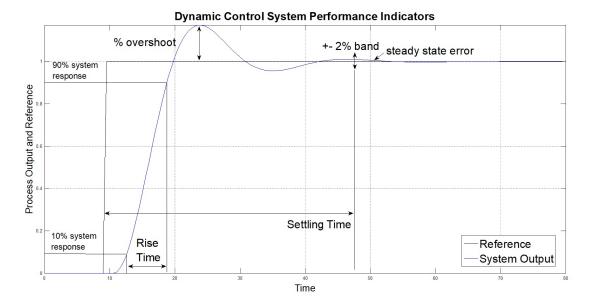

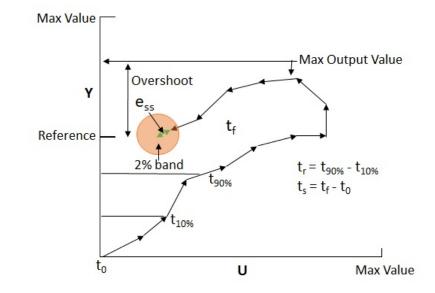

| 4.1 | Dynamic control system closed loop performance indicators: settling time,           |    |

|     | maximum overshoot, rise time, and steady state error.                               | 66 |

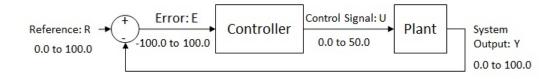

| 4.2 | Example of a simplified feedback control system consisting of a plant and a         |    |

|     | controller. The figure shows the most relevant control loop related variables       |    |

|     | and their respective operating ranges.                                              | 67 |

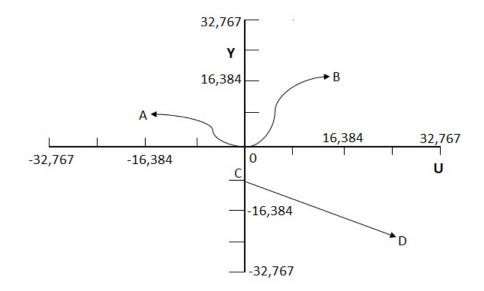

| 4.3 | Operating search space for an input $(U)$ - output $(Y)$ relationship using integer |    |

|     | data only. Input and output range: -32,767 - 32,767. The control problem            |    |

|     | becomes a path search in $(U, Y)$ coordinates - e.g. going from the origin to       |    |

|     | point A or point B, moving from point C to point D                                  | 68 |

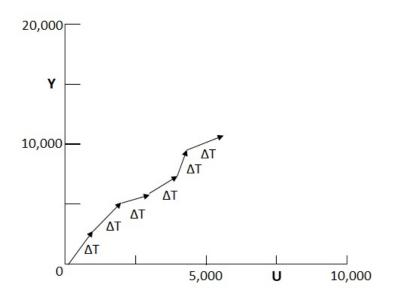

| 4.4 | Operating search space for an input $(U)$ - output $(Y)$ relationship using integer |    |

|     | data only. Input range: 0-10,000. Output range: 0-20,000. Every arrow               |    |

|     | represents a $\Delta T$ amount of time elapsed. The reference tracking control      |    |

|     | problem involves moving the output $Y$ from an initial point towards a final        |    |

|     | region by the means of changing the input U. Every $\Delta T$ both U and Y are      |    |

|     | updated using their respective dynamics.                                            | 69 |

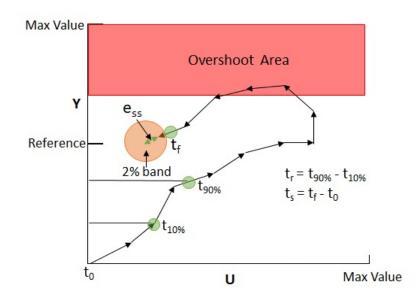

| 4.5 | Operating space for input signal $U$ and output signal $Y$ showing the control      |    |

|     | system performance indicators of interest. The reference tracking control           |    |

|     | problem becomes one of analysing the trajectory from the origin point to            |    |

|     | the reference point. The performance indicators become way-points in the            |    |

|     | trajectory                                                                          | 70 |

| 4.6 | Reference tracking control problem for input signal $U$ and output signal $Y$       |    |

|     | with performance requirements as way-points in the trajectory                       | 71 |

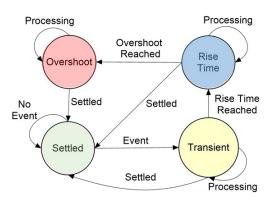

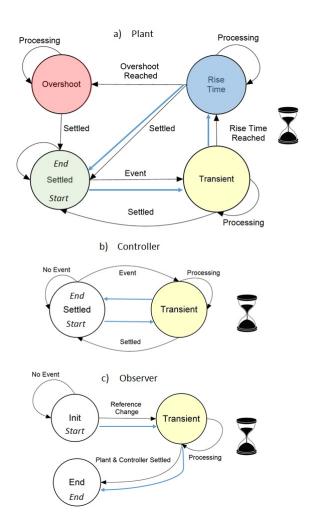

| 4.7 | Plant automaton. This automaton generates the output signal $Y$ using a             |    |

|     | discrete SISO LTI model and monitors its behaviour to determine transitions         |    |

|     | between states. The high level performance requirements are processed in            |    |

|     | this automaton under its different states.                                          | 73 |

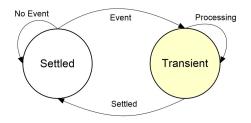

| 4.8   | Controller automaton. This automata generates the control signal <i>U</i> using a discrete SISO LTI model and monitors its behaviour to determine transitions between states. The controller automaton has less states than the <i>Plant</i> |    |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|       | automaton because in this problem formulation the control signal is not                                                                                                                                                                      |    |

|       | under analysis, it is simple required for it to be generated.                                                                                                                                                                                | 73 |

| 4.9   | Observer automaton. Automaton in charge of controlling the data flow                                                                                                                                                                         | 10 |

|       | between the controller and the plant. This automaton monitors the control                                                                                                                                                                    |    |

|       | signal $U$ and output process signal $Y$ to determine transitions between states.                                                                                                                                                            | 74 |

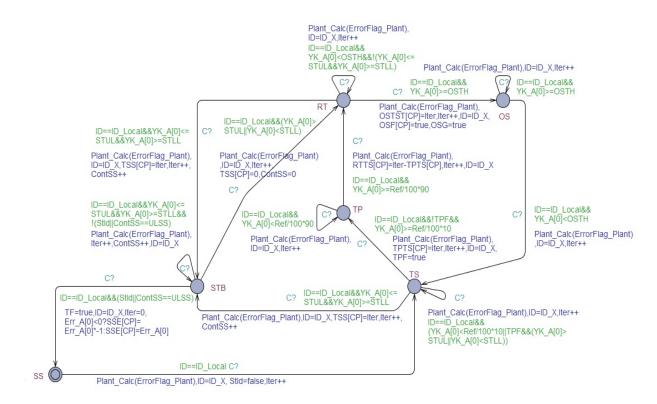

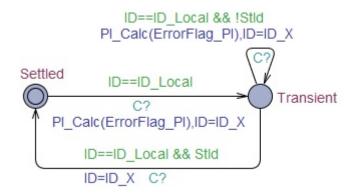

| 4.10  | UPPAAL implementation of the plant automaton. This automaton generates                                                                                                                                                                       |    |

|       | the output signal Y and monitors its behaviour to determine transitions                                                                                                                                                                      |    |

|       | between states.                                                                                                                                                                                                                              | 77 |

| 4.11  | UPPAAL implementation of the controller automaton. This automata gener-                                                                                                                                                                      |    |

|       | ates the control signal $U$ and monitors its behaviour to determine transitions                                                                                                                                                              |    |

|       | between states.                                                                                                                                                                                                                              | 78 |

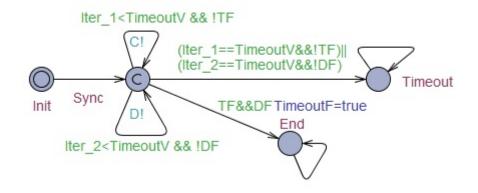

| 4.12  | UPPAAL implementation of the observer automaton. Automaton in charge of                                                                                                                                                                      |    |

|       | controlling the data flow between the controller and the plant. This automata                                                                                                                                                                |    |

|       | monitors the control signal U, output process signal Y, and the elapsed                                                                                                                                                                      |    |

|       | time to determine transitions between states. It coordinates the execution                                                                                                                                                                   |    |

|       | between plants and controllers using communication channels <i>C</i> and <i>D</i> . One                                                                                                                                                      |    |

|       | channel is used for the over approximation and the other one for the under                                                                                                                                                                   |    |

|       | approximation.                                                                                                                                                                                                                               | 79 |

| 4.13  | Proposed automata: a) Plant automaton. b) Controller automaton. c) Ob-                                                                                                                                                                       |    |

|       | server automaton. Performance requirements verification portrayed as a                                                                                                                                                                       |    |

|       | reachability problem: can the states labelled as <i>End</i> be reached starting at                                                                                                                                                           |    |

|       | the states labelled as <i>Start</i> visiting the states which follow the blue arrows                                                                                                                                                         |    |

|       | trajectories in a finite amount of time?                                                                                                                                                                                                     | 81 |

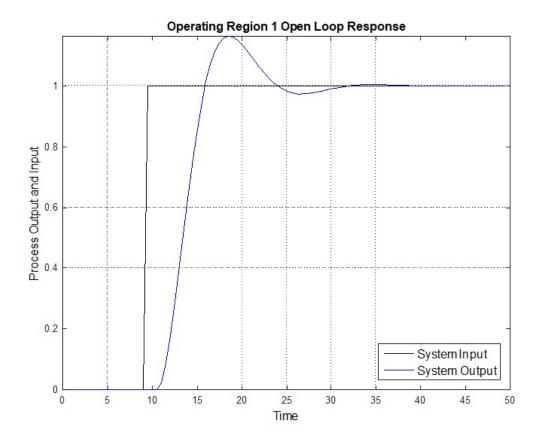

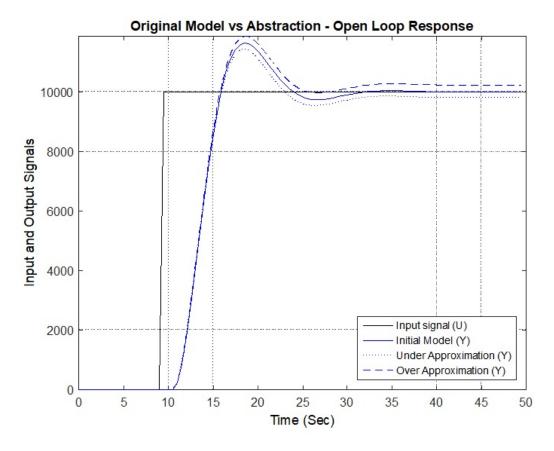

| 4 14  | Open loop response for the linear system part of the thrust control problem.                                                                                                                                                                 | 01 |

| 1.1 1 | The model corresponds to one of the operating regions in the thrust control                                                                                                                                                                  |    |

|       | problem.                                                                                                                                                                                                                                     | 84 |

| 1 15  | Open loop response comparison for the system abstraction and the initial                                                                                                                                                                     | 04 |

| т.15  | model for operating region 1 in the thrust control problem from Figure 4.14.                                                                                                                                                                 |    |

|       | The initial response is scaled up for comparison purposes (using $K_S = 10,000$ ).                                                                                                                                                           | 86 |

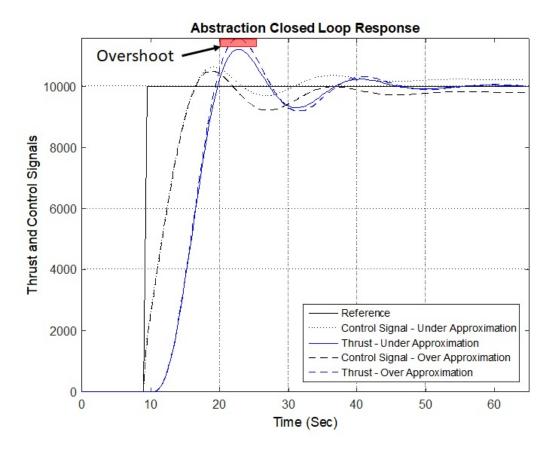

| 116   |                                                                                                                                                                                                                                              | 00 |

| 4.10  | Closed loop response of the system abstraction. Both over and under approx-                                                                                                                                                                  |    |

|       | imation responses are plotted. Highlighted in red is the area where the over                                                                                                                                                                 | 00 |

|       | approximation fails to meet the overshoot requirement                                                                                                                                                                                        | 89 |

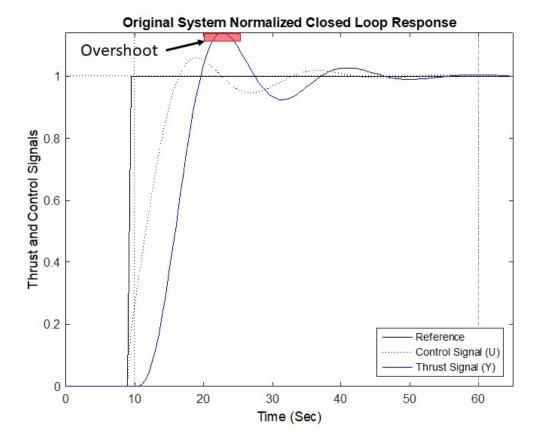

|      | Closed loop response of the original system. Highlighted in red is the area where the system fails to meet the overshoot requirement                                                                                                                                                                                                  | 90  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

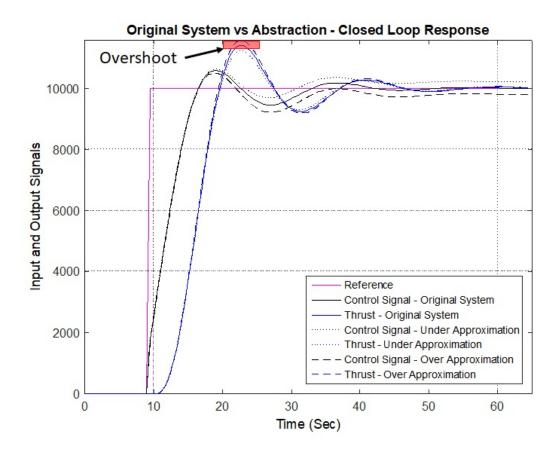

| 4.10 | Highlighted in red is the area where the over approximation and the original                                                                                                                                                                                                                                                          |     |

|      | system fail to meet the overshoot requirement. The original system response                                                                                                                                                                                                                                                           |     |

|      | is scaled for comparison purposes (using $K_S = 10,000$ )                                                                                                                                                                                                                                                                             | 91  |

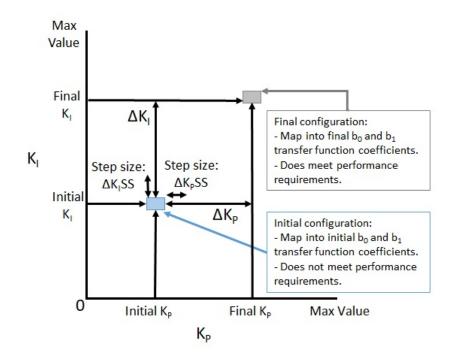

| 5.1  | Operating space for PI controller gains $K_P$ and $K_I$ . To tune the controller gains requires finding a different combination of gains which drive the system's dynamics into a trajectory that meets requirements. Starting from an initial set of gains a search is performed to find a possible solution to the control problem. | 98  |

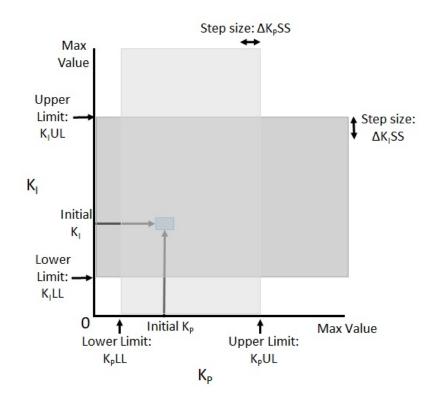

| 5.2  | control problem                                                                                                                                                                                                                                                                                                                       | 90  |

|      | for each gain is limited to a certain area with upper and lower boundaries. The available combination of controller gains are comprised in the intersection of the two areas. The model checker uses this bounded area as the search space                                                                                            |     |

|      | to find a controller gains combination that drives the system into meeting                                                                                                                                                                                                                                                            |     |

|      | requirements.                                                                                                                                                                                                                                                                                                                         | 99  |

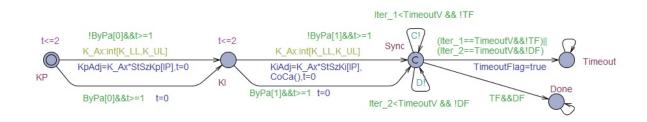

| 5.3  | Updated Observer automaton. Automaton in charge of the tuning procedure                                                                                                                                                                                                                                                               |     |

|      | of the controller gains and controlling the data flow between the controller                                                                                                                                                                                                                                                          |     |

|      | and the plant. This automaton monitors the control signal $U$ and output                                                                                                                                                                                                                                                              | 100 |

| 5.4  | process signal <i>Y</i> to determine transitions between states                                                                                                                                                                                                                                                                       | 102 |

| 5.4  | controlling the data flow between the controller and the plant. The controller                                                                                                                                                                                                                                                        |     |

|      | tuning process has been incorporated. Gains $K_P$ and $K_I$ are modified in order                                                                                                                                                                                                                                                     |     |

|      | to find a suitable combination which drives the process to meet requirements.                                                                                                                                                                                                                                                         |     |

|      | This automaton monitors the control signal $U$ , output process signal $Y$ , and                                                                                                                                                                                                                                                      |     |

|      | the elapsed time to determine transitions between states. It coordinates the                                                                                                                                                                                                                                                          |     |

|      | execution between plants and controllers using communication channels C                                                                                                                                                                                                                                                               |     |

|      | and <i>D</i> . One channel is used for the over approximation and the other one for                                                                                                                                                                                                                                                   |     |

| ~ ~  | the under approximation.                                                                                                                                                                                                                                                                                                              | 104 |

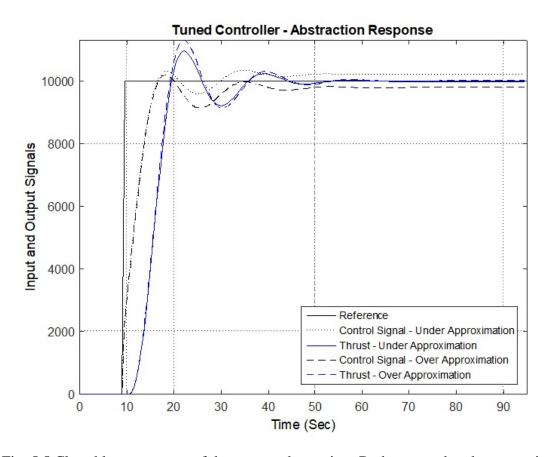

| 5.5  | Closed loop response of the system abstraction. Both over and under approx-                                                                                                                                                                                                                                                           | 100 |

| 5.6  | imation meet all the requirements                                                                                                                                                                                                                                                                                                     | 109 |

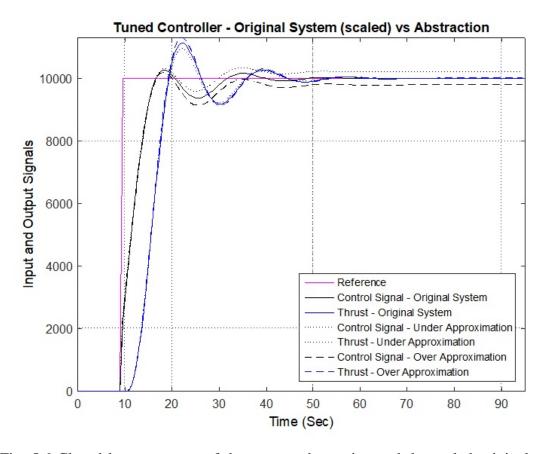

| 5.0  | Both the abstraction (over and under approximations) and the original system                                                                                                                                                                                                                                                          |     |

|      | meet the requirements as determined by the model checker. The original                                                                                                                                                                                                                                                                |     |

|      | system response is scaled for comparison purposes (using $K_S = 10,000$ )                                                                                                                                                                                                                                                             | 110 |

|      |                                                                                                                                                                                                                                                                                                                                       |     |

5.7

6.1

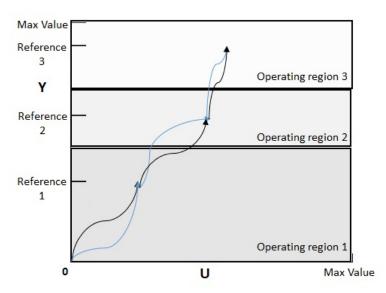

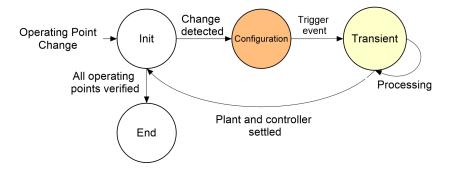

6.2

6.3

6.4

6.5

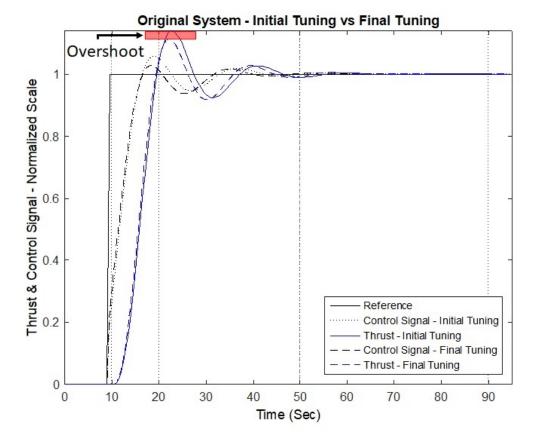

| Closed loop response for the original system using the initial PI controller            |     |

|-----------------------------------------------------------------------------------------|-----|

| gains and the final controller gains. Highlighted in red is the overshoot area          |     |

| where the initial controller tuning fails to meet the requirements                      | 111 |

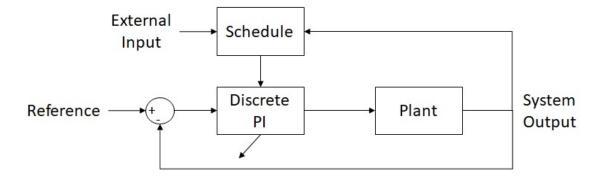

|                                                                                         |     |

| Gain scheduled control scheme. The controller has a proportional+integral               |     |

| (PI) structure (Equation 5.4). The schedule is driven by a combination of               |     |

| external inputs and the controlled variable                                             | 117 |

| Gain scheduled control problem portrayed as a <i>reachability</i> problem. Three        |     |

| different operating regions are presented. Each region has a different dynamic          |     |

| behaviour. Trajectories between reference points are given by the amount                |     |

| of possible schedule entries. In this case and for this example purpose only            |     |

| 2 possible trajectories are shown. The number of schedule entries will be               |     |

| generated as required.                                                                  | 118 |

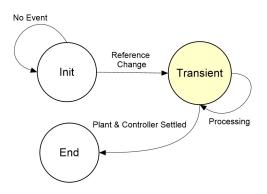

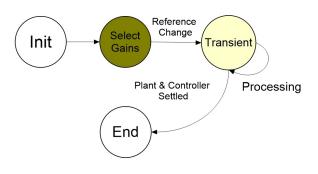

| Updated <i>Observer</i> automaton. Automaton in charge of controlling the data          |     |

| flow between the controller and the plant. This automaton keeps track of the            |     |

| changes in reference and operating regions and commands both the plant                  |     |

| and controller automata to change their respective dynamics if required.                |     |

| This automata monitors the control signal $U$ and output process signal $Y$ to          |     |

| determine transitions between states                                                    | 120 |

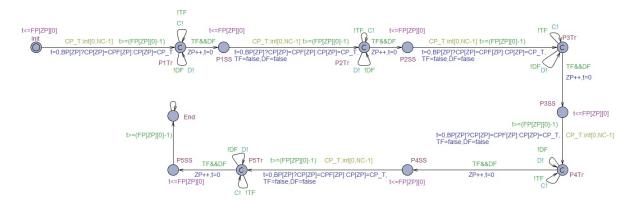

| UPPAAL implementation of the observer automaton. Automaton in charge                    | 120 |

| of controlling the data flow between the controller and the plant. The process-         |     |

| ing of different operating regions, their respective dynamics, and different            |     |

|                                                                                         |     |

| controller tunings has been incorporated. Every time a change in the op-                |     |

| erating point is detected the controller tuning can be non-deterministically            |     |

| selected. This automaton monitors the control signal $U$ , and output process           |     |

| signal $Y$ to determine transitions between states. It coordinates the execution        |     |

| between plants and controllers using communication channels <i>C</i> and <i>D</i> . One |     |

| channel is used for the over approximation and the other one for the under              |     |

| approximation. This particular automaton processes 5 different operating                |     |

| points                                                                                  | 122 |

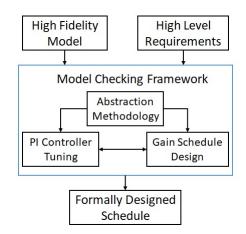

| Gain schedule formal design methodology. High fidelity model and high                   |     |

| level requirements are taken into the model checking framework. The model               |     |

| checking framework is composed of the abstraction methodology which                     |     |

| enables the formal PI controller tuning and the gain schedule design. Both              |     |

the controller tuning and the gain schedule design automata are used in

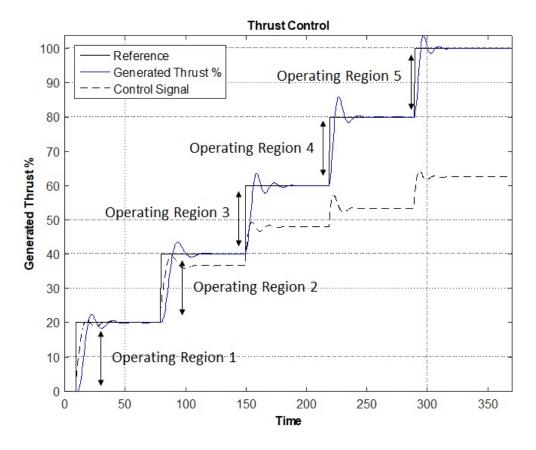

| 6.6  | Jet-engine thrust control. This is a possible behaviour of the control system      |

|------|------------------------------------------------------------------------------------|

|      | consisting of five operating regions. Each operating region has a particular       |

|      | dynamic. In this scenario the same controller tuning is used for all the           |

|      | operating regions                                                                  |

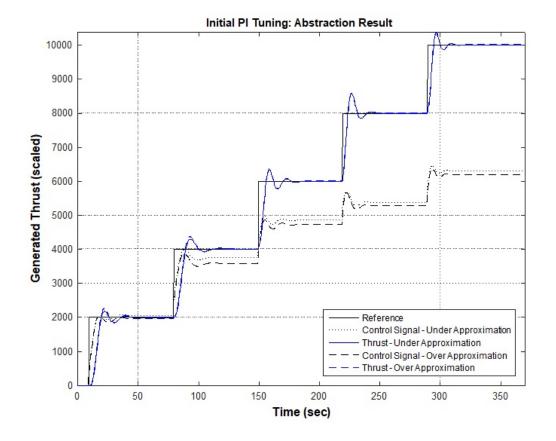

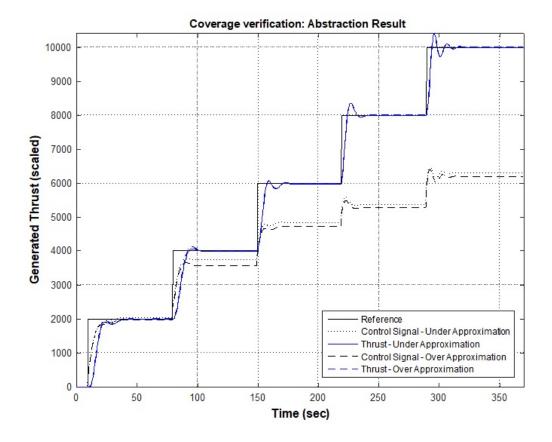

| 6.7  | Closed loop control system behaviour for the abstraction. Only one control         |

|      | tuning is available and used for the five operating regions. The performance       |

|      | indicators are listed in Table 6.4. The graph shows both the over and under        |

|      | approximations with their respective control signals                               |

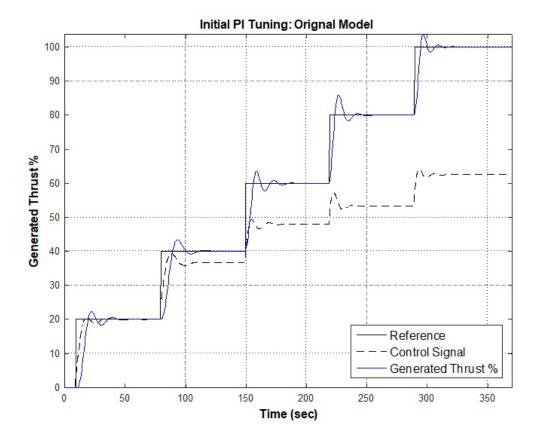

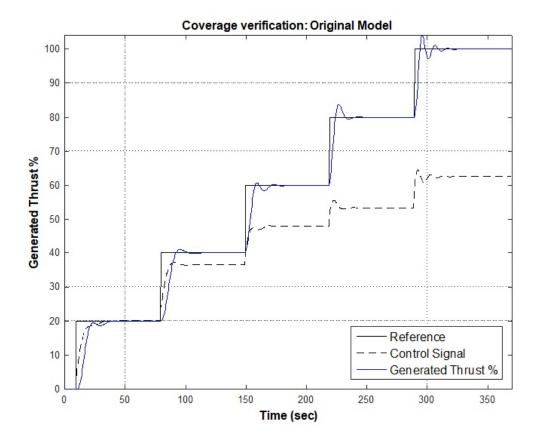

| 6.8  | Closed loop control system behaviour for the original system. Similar to           |

|      | Figure 6.7 only one control tuning is available and used for the five operating    |

|      | regions. The performance indicators are listed in Table 6.4. The graph shows       |

|      | generated thrust % and the control signal                                          |

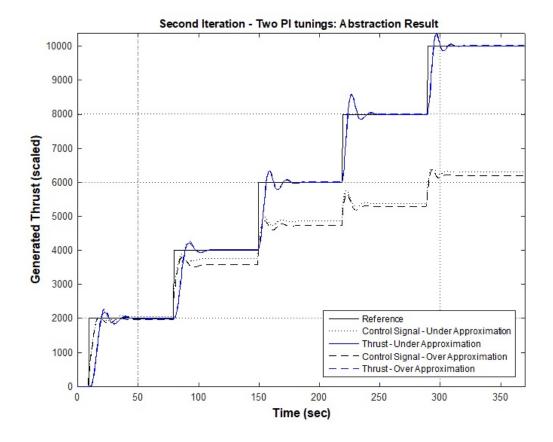

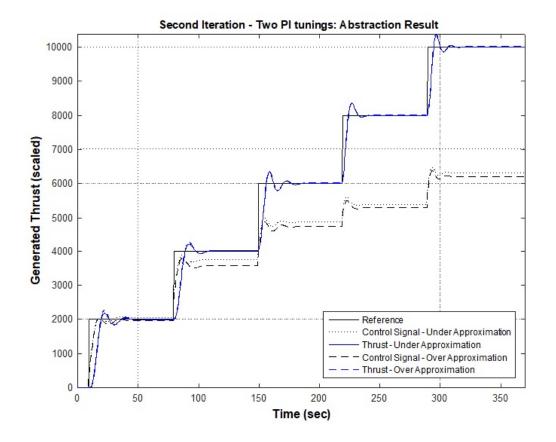

| 6.9  | Closed loop control system behaviour for the abstraction. Two control              |

|      | tunings are available. Tuning 1 is used for regions 1, 3, 4, and 5. Tuning 2 is    |

|      | used for region 2. The performance indicators are listed in Table 6.6. The         |

|      | graph shows both the over and under approximations with their respective           |

|      | control signals                                                                    |

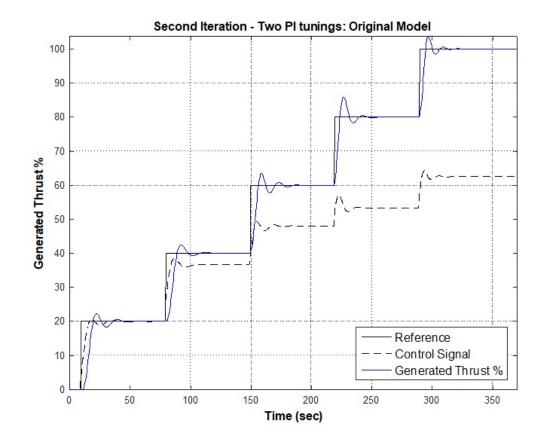

| 6.10 | Closed loop control system behaviour for the original system. Similar to           |

|      | Figure 6.9 two control tunings are available. Tuning 1 is used for regions 1,      |

|      | 3, 4, and 5. Tuning 2 is used for region 2. The performance indicators are         |

|      | listed in Table 6.6. The graph shows generated thrust % and the control signal.137 |

| 6.11 | Closed loop control system behaviour for the abstraction. Final schedule:          |

|      | Three control tunings are available. Tuning 1 is used for regions 1, 3, 4,         |

|      | and 5. Tuning 2 is used for region 2. Tuning 3 is used for region 4. The           |

|      | performance indicators are listed in Table 6.8. The graph shows both the           |

|      | over and under approximations with their respective control signals 139            |

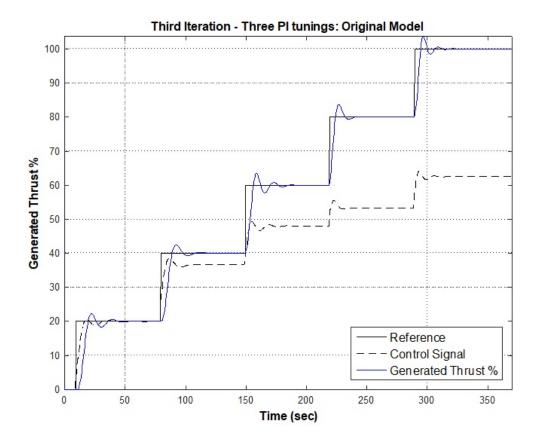

| 6.12 | Closed loop control system behaviour for the original system. Final schedule:      |

|      | similar to Figure 6.11 three control tunings are available. Tuning 1 is used       |

|      | for regions 1, 3, 4, and 5. Tuning 2 is used for region 2. Tuning 3 is used        |

|      | for region 4. The performance indicators are listed in Table 6.8. The graph        |

|      | shows generated thrust % and the control signal                                    |

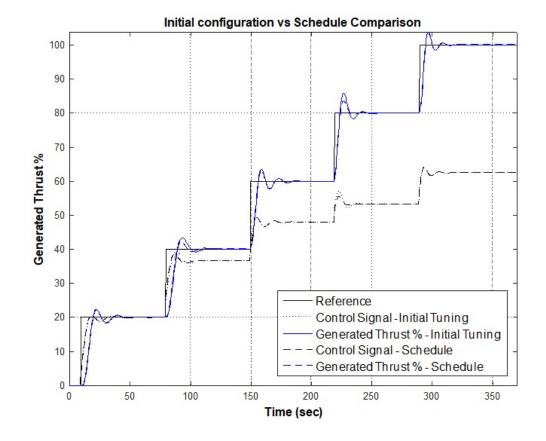

| 6.13 | Initial controller tuning versus final schedule. Final schedule: three control   |     |

|------|----------------------------------------------------------------------------------|-----|

|      | tunings are available. Tuning 1 is used for regions 1, 3, 4, and 5. Tuning 2 is  |     |

|      | used for region 2. Tuning 3 is used for region 4. The performance indicators     |     |

|      | for the final schedule are listed in Table 6.8. The performance indicators for   |     |

|      | the initial configuration are listed in Table 6.4. The graph shows generated     |     |

|      | thrust % and the control signal                                                  | 141 |

| 6.14 | Closed loop control system behaviour for the abstraction. <i>Counter-example</i> |     |

|      | trace tunings were used in this case: Tuning 3 for regions 1, 2, 3, and 4.       |     |

|      | Tuning 2 for region 5. The performance indicators are listed in Table 6.9. The   |     |

|      | graph shows both the over and under approximations with their respective         |     |

|      | control signals.                                                                 | 143 |

| 6.15 | Closed loop control system behaviour for the abstraction. <i>Counter-example</i> |     |

|      | trace tunings were used in this case: Tuning 3 for regions 1, 2, 3, and 4.       |     |

|      | Tuning 2 for region 5. The performance indicators are listed in Table 6.9.       |     |

|      | The graph shows generated thrust % and the control signal                        | 144 |

# List of tables

| 3.1 | Integer data type ranges.                                                             | 40  |

|-----|---------------------------------------------------------------------------------------|-----|

| 3.2 | Possible fixed point representations with 16-bit integer data type                    | 40  |

| 3.3 | Size considerations for data operations - binary case                                 | 41  |

| 3.4 | Fixed point representation - binary case                                              | 42  |

| 3.5 | A / B = C: Largest possible result - binary case                                      | 42  |

| 3.6 | Data size requirements                                                                | 43  |

| 3.7 | Ad hoc data type for abstraction                                                      | 44  |

| 3.8 | Possible compensation operations considering the aforementioned sources               |     |

|     | of error                                                                              | 52  |

| 3.9 | Mapping between original floating-point values and fixed-point integer rep-           |     |

|     | resentation.                                                                          | 57  |

| 4.1 | UPPAAL queries which can generate either a <i>witness</i> or a <i>counter example</i> |     |

| 7.1 |                                                                                       | 80  |

| 4.2 | Requirements verification results for the system abstraction.                         | 88  |

| 4.3 | Requirements verification results for the original system.                            | 90  |

| 1.5 | Requirements vermeation results for the original system.                              | 70  |

| 5.1 | Controller gains operating space configurations and verification results. The         |     |

|     | initial values for every iteration are $K_P = 0.1392$ and $K_I = 0.1496$              | 108 |

| 5.2 | Initial and final gain values for the PI controller                                   | 108 |

| 5.3 | Requirements design and verification results for the system abstraction               | 109 |

| 5.4 | Requirements comparison between initial and final controller tunings                  | 111 |

| 6.1 | Open loop continuous SISO LTI models for operating regions in the thrust              |     |

| 0.1 | control problem.                                                                      | 128 |

| 6.2 | Open loop discrete SISO LTI models for operating regions in the thrust                | 120 |

| 0.2 | control problem. Column 2 uses floating-point representation and column 3             |     |

|     | the selected fixed-point representation.                                              | 130 |

|     | the selected fixed-point representation                                               | 150 |

| 6.3 | System abstraction: integer-only discrete SISO LTI models for operating        |     |

|-----|--------------------------------------------------------------------------------|-----|

|     | regions in the thrust control problem. Two models are generated per region:    |     |

|     | under approximation and over approximation.                                    | 130 |

| 6.4 | Performance indicators for the system abstraction and the original model       |     |

|     | using the initial tuning only. The requirements that failed are highlighted in |     |

|     | bold                                                                           | 132 |

| 6.5 | Performance indicators for the system abstraction and the original model for   |     |

|     | operating region 2 using the set of gains obtained with Algorithm 4            | 133 |

| 6.6 | Performance indicators for the system abstraction and the original model after |     |

|     | 1 iteration. Two controller tunings are available for use. The requirements    |     |

|     | that failed are highlighted in bold                                            | 135 |

| 6.7 | Performance indicators for the system abstraction and the original model for   |     |

|     | operating region 4 using the set of gains obtained with Algorithm 4            | 135 |

| 6.8 | Performance indicators for the system abstraction and the original model after |     |

|     | 2 iterations: Final control schedule. Three controller tunings are available   |     |

|     | for use                                                                        | 138 |

| 6.9 | Performance indicators for the system abstraction and the original model       |     |

|     | performing the coverage verification. All three controller tunings from        |     |

|     | the final schedule are available for use. The requirements that failed are     |     |

|     | highlighted in bold                                                            | 142 |

|     |                                                                                |     |

# **Symbols and Acronyms**

### Symbols

| $b_0$            | Discrete PID coefficient zero                       |

|------------------|-----------------------------------------------------|

| $b_1$            | Discrete PID coefficient one                        |

| K <sub>D</sub>   | Controller Derivative gain                          |

| K <sub>I</sub>   | Controller Integral gain                            |

| K <sub>P</sub>   | Controller Proportional gain                        |

| Т                | System sampling period                              |

| δ                | Gain delta                                          |

| $\Delta_{K_I}$   | Controller integral gain total delta change         |

| $\Delta_{K_I}SS$ | Controller integral gain delta change step size     |

| $\Delta_{K_P}$   | Controller proportional gain total delta change     |

| $\Delta_{K_P}SS$ | Controller proportional gain delta change step size |

| ε                | Error                                               |

| E(z)             | Discrete-time System Error                          |

| F                | Fractional Digit                                    |

| Ι                | Integral Digit                                      |

| Kab              | Coefficients Scaling Gain                           |

| K                | System gain                                         |

| $K_S$          | Input-Output Scaling Gain                                           |

|----------------|---------------------------------------------------------------------|

| $K_U$          | Parametric Compensation Error Gain                                  |

| $\omega_n$     | System natural frequency                                            |

| А              | Path quantifier - For all computation paths                         |

| Е              | Path quantifier - For some computation paths                        |

| <>             | Eventually temporal operator                                        |

| []             | Globally temporal operator                                          |

| φ              | State formula - Logical expression that can be evaluated in a state |

| $\mathbb{R}$   | Real Numbers                                                        |

| R(z)           | Discrete-time System Reference                                      |

| $e_{ss}$       | Steady State Error                                                  |

| θ              | System transport delay                                              |

| $t_r$          | Rise Time                                                           |

| $t_s$          | Settling Time                                                       |

| OS             | UPPAAL query language Maximum Overshoot indicator                   |

| RT             | UPPAAL query language Rise Time indicator                           |

| SSE            | UPPAAL query language Steady State Error indicator                  |

| ST             | UPPAAL query language Settling Time indicator                       |

| U(z)           | Discrete-time System Input                                          |

| Y(z)           | Discrete-time System Output                                         |

| $\mathbb{Z}^+$ | Positive Numbers                                                    |

| ζ              | System damping ratio                                                |

## Acronyms

ARX Auto-Regressive with Exogenous Input

- CTL Computational Tree Logic

- CTS Continuous Time Systems

- DCS Distributed Control System

- DES Discrete Event Systems

- DO-178C Software Considerations in Airborne Systems and Equipment Certification

- DO-333 Formal Methods Supplement to DO-178C and DO-278A

- DPM Dynamic Power Management

- EASA European Aviation Safety Agency

- EEC Electronic Engine Control

- FAA Federal Aviation Administration

- FAR Federal Aviation Regulations

- FBW Fly By Wire

- FSM Finite State Machines

- LTI Linear Time Invariant

- LTL Linear Temporal Logic

- LT Linear Time

- MCDC Modified Condition Decision Coverage

- MEA More Electric Aircraft

- MEE More Electric Engine

- MOC Model of Computation

- NASA National Aeronautics and Space Administration

- ODE Ordinary Differential Equation

- PBW Power By Wire

- PID Proportional Integral Derivative

| PI | Proportional Integral |

|----|-----------------------|

- POA Power Optimized Aircraft

- PRISM Probabilistic Model Checker

- RSM Runway Safety Monitor

- SAT Propositional Satisfiability Problem

- SCADE Safety-Critical Application Development Environment

- SDV Simulink Design Verifier

- SISO Single Input Single Output

- SS Sequential Systems

- TIMES Totally Integrated More Electric Systems

- TS Transition Systems

- UPPAAL-Cora UPPAAL for Cost Optimal Reachability Analysis

- UPPAAL-TiGa UPPAAL for TImed GAmes based controller synthesis

- UPPAAL Uppsala and Aalborg Universities Real-Time systems model checker

- V&V Verification and Validation

#### xxviii

## Chapter 1

## Introduction

## 1.1 Motivation

Cyber-physical systems comprise a wide range of computer-based systems which require the integration of various technologies such as computers, control, and communications in order to achieve stability, performance, reliability, efficiency and robustness when dealing with physical systems [133]. Nowadays and thanks to advances in computer science and technology, it is extremely common to use computer-based systems on a day to day basis [7, 86]. From mobile phones to power grids, they are part of our civilization. The development of the hardware and software that makes this possible is a major engineering activity in many sectors. Along with the development of such systems the concept of system verification emerges: to ensure the correctness of the system against requirements. When the system does not entirely meet requirements the damages could be minor (e.g. a smart-phone reset) or catastrophic (e.g. the loss of human lives).

### 1.1.1 System Verification

A system failure can be very costly and even if no human lives are lost, the consequences of a software or hardware error could have severe repercussions. Intel lost millions of dollars because of the Pentium processor error [7, 130]; in 1996 the Ariane-5 rocket crashed a few seconds after launch [45, 96]; the Mars Pathfinder rover suddenly stopped working [82]; and patients died of an overdose of radiation using the Therac machine [99]. All these failures happened because of a bug in the system and the consequences were monetary, loss of credibility and the loss of human lives. Over the years the case for better verification procedures has been made and even if current practices have improved compared to when all those errors occurred, every now and then we are reminded of the gaps we need to fill.

In computer science, the related activities to software testing are referred to as *Verification and Validation* (V&V). These activities are a cornerstone for software development and are a huge component of any software development life-cycle [113]. They are different activities and address two different aspects of product development [21]:

- *Verification*: Are we building the product right? The product meets requirements doing what it is supposed to do in the way it is supposed to do it. The product is bug-free.

- *Validation*: Are we building the right product? The product does what it is supposed to do, it fulfils high level functional requirements.

The V&V activities use different approaches, tools, and procedures. The more complex the project or product, the need for novel and better tools arises. Over the years the software development community has come up with new standards, tools, procedures, and practices in order to provide higher quality products and avoid fatal failures. The type of product under development drives the V&V efforts and the amount of time spent in these activities. For safety-critical applications, such as control systems in automotive or aerospace industries, not being too careful is not an option and the software should be stressed as much as possible to prove its correctness and safety. Besides being able to detect the errors of the design, it is desirable to detect such errors as early as possible during the development process. Detecting an error in a higher layer of the design process can increase the cost of fixing it several orders of magnitude compared to the lowest development stages.

For many years now dynamic control systems are implemented using embedded control. The control algorithm is thus implemented on a computer-based system in a software manner. This change in paradigm meant versatility because modifying a controller meant simply a software change. More advanced control algorithms became available and new control theory was born [86]. Software engineering and control systems engineering are a fundamental component in cyber-physical systems. The control community should care about the software community because it relies strongly on it, and the software community should care about the control community for the same reason. Even if most of the time these two fields of engineering are considered independently, in practice they are one discipline and this fact should be made clear to both software and control engineers, especially in safety-critical control applications.

### 1.1.2 Trends in Aerospace Systems

The trend pattern for the aerospace industry is one of growth. The Federal Aviation Administration (FAA) has predicted that within the next 2 decades air traffic will increase by 150% to 250% compared to the beginning of this decade [62]. The long-term vision for future aircraft is one of a more electric machine. Companies and organizations are currently developing technology to bring the concepts of More Electric Aircraft (MEA) [136] and More Electric Engine (MEE) [73, 116] to a reality. Projects like Totally Integrated More Electric Systems (TIMES) and Power Optimized Aircraft (POA) [52] are part of this effort [39, 118].

Power-By-Wire (PBW) [79, 90] technology will then become crucial. PBW means that the power to move an actuator comes from electric sources. Having electric-powered actuators will increase the complexity of current electric systems; if it is considered that in the future the main propulsive power for aircraft will come from electric sources, complexity increases even more. To integrate different electric technologies for long term operation presents new unseen challenges in several engineering and design aspects. This change in paradigm is partly enabled by current computational power in embedded applications for the aerospace industry, and to address these new challenges embedded systems will play a key role to provide solutions for control, health, and communications.

Computer-based control was a big leap in aviation and for decades centralized embedded control has been used to address control challenges. The inclusion of the computer as a control device made software a very important component for aviation. As technology progressed computational power increased, allowing to enhance the on-board software and a number of additional functionalities became standard, providing not only control but also health management and safety features. In a modern aircraft jet-engine the control architecture is centralized, and by including more features on the same computer software has become more complex. There exists a dependency relationship among the various features of the software.

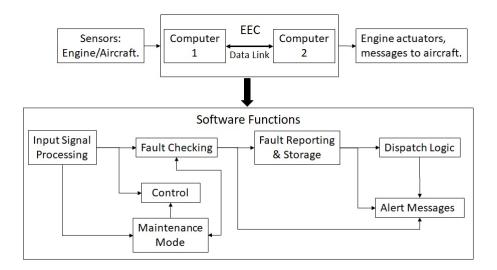

Figure 1.1 shows a generic block diagram representation of a centralized jet engine Electronic Engine Control (EEC) unit and typical functional features that are implemented in the form of software [38]. The system contains 2 computers for redundancy and safety purposes. Both computers run the same software while sharing information via a data link. The software components become strongly connected with a dependency relationship. Therefore the development of aviation control software has become more complex over the years: adding or removing features generates development and certification efforts for the sake of safety. As a result, time is invested and a higher cost in development has to be paid. The next step in control system architectures is one towards Distributed Control System (DCS) [10]: control and health management functions are executed on different computers; instrumentation wired to communication buses and local control processes supervised by a top level controller [116]. A more modular approach with local control loops would help to reduce complexity in development and accelerate certification processes

Fig. 1.1 Block diagram representation of an Electronic Engine Control (EEC) unit and the functional features it contains as software.

[62]. Nonetheless the DCS architecture is still under development with many open problems to solve. By partitioning functionalities the individual development effort may be reduced but the integration of all the features over a distributed architecture will require effort that is still unknown. Whether a distributed architecture becomes the standard practice or the centralized one remains the standard, software will become more complex in order to address the new challenges to come: more electric systems, more efficient systems, enhanced health management, more advanced control, etc.

### **1.1.3** Avionics Certification

For commercial aviation, the Federal Aviation Authority (FAA) and European Aviation Safety Agency (EASA) are the two major bodies in charge of aircraft certification [43]. Regulations to be fulfilled by a jet engine manufacturer can be found in Federal Aviation Regulations (FAR) parts 25 and 33 [50]. Part 25 is related to "Transport Category Airplanes" and Part 33 to "Aircraft Engines". All the certification activities for commercial airborne systems exist for safety reasons: they ensure that the right thing is being built in the right way, contemplating every aspect and detail of the aircraft.

Modern aviation systems use Fly By Wire (FBW) technology, evolving towards PBW technology. This means that control algorithms are and will be implemented in the form of software. It does not matter by which technique or method the controller has been developed; it will be implemented on an embedded computer system. Since the integration of computer systems into the aviation industry and as part of the certification process, software has to

be verified and validated versus requirements. DO-178C [51] is the standard created by regulation authorities to regulate and assess the safety of airborne software. This document does not specify how to make the software but rather describes what is to be expected of the software and the evidence to be provided for compliance. Standards like DO-178C identify a level of criticality of the related software according to its functionality by estimating the amount of damage that a malfunction in the software could generate. For the aviation industry the criticality levels go from A to F, level A being the most critical. Level A software malfunctions are classified as *catastrophic*, there exists a potential aircraft crash with potential human lives lost. A computer-based controller such as the EEC for a jet-engine is thus considered a safety-critical system.

#### **1.1.4** Safety-Critical Software Development Life Cycle

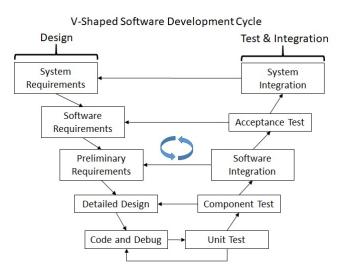

It is especially for safety reasons that certification standards like DO-178C exist, and qualifying software for certification efforts is extremely critical and burdensome. In order to accomplish this, software development processes and practices have been established to facilitate and aid in the software development life cycle. Software development cycles were born in computer science and depending on the type of software under development one is chosen over another. For aviation systems, perhaps the most popular is the *V-Shaped* development cycle [113].

Fig. 1.2 V-Shaped software development cycle. Popular within the aerospace industry for software development. This process makes clear emphasis on testing activities throughout the whole cycle, which are fundamental when developing safety-critical software.

Figure 1.2 shows a block diagram description of the process. It is a popular choice because it is easy to follow and there are clear deliverables in each phase [113]. This model makes clear emphasis on the testing phase of the software. For safety-critical systems, verification and validation activities strongly rely on testing and a good amount of effort is spent on this activity: unit testing, integration testing, and acceptance testing [113]. Currently, 1 defect per 1000 lines of code is an accepted measure for today's software [7]. Considering Boeing's 787 avionics system, it is estimated to contain around 6 million of lines of code and therefore that would mean 6000 defects. In software development, testing all possible scenarios becomes harder when the software itself grows in size. Exhaustive testing practices like Modified Condition Decision Coverage (MCDC) are not sufficient to detect all defects. It is estimated that current testing activities amount to approximately 30% to 50% of the total cost of a software project [7].

We cannot forget that in the end there is an engineer coding the software, as Leveson and Turned have pointed out: *"it is still a common belief that any good engineer can build software, regardless of whether he or she is trained in state-of-the-art software-engineering procedures"* [99]. The most frequent reason for software crashes are due to programming bugs while doing the implementation of an abstract design [26, 139]. The more complex and large a design is, the more the chances for error. If the tasks can be separated in a more modular architecture with defined objectives for each task, the implementation and validation of the design can be benefited. It is therefore desirable to find a new approach to verification and validation which relies not only on testing activities.

Formal methods provide the means to analyse cyber-physical systems with a mathematical rigour. A report by NASA and FAA concluded that formal methods should become a standard part of engineering [7]. Within formal methods there is model checking, an exhaustive verification technique. Given a formal description of the system (a model) and a formal description of a property (a requirement for the system), model checking can verify if such property is fulfilled by the system. Model checking brings formality to both requirements and modelling, which is in turn useful when dealing with high level requirements expressed in natural languages for a complex system.

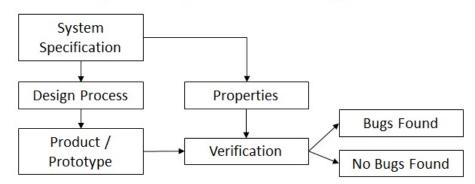

The usual verification process for a system versus requirements is an *a posteriori* one. A prototype of the product, or the product itself, is developed and the verification is performed using that prototype or product. Both the design and verification processes are driven by the system specifications but no formal approach is taken when bringing those specifications into low level requirements for the implementation or testing processes. Figure 1.3 shows a block diagram description of the process [7]. This is what most software development life-cycles

tend to follow: the verification is done in the actual product while it is under development. This falls well within the V-Shaped development cycle testing activities from Figure 1.2.

A posteriori system verification approach

Fig. 1.3 System verification: *a posteriori* approach. The verification takes place in the product or a prototype of the product. The construction of the prototype or product is performed before the verification activities takes place. If bugs are found another iteration of the design and verification process is necessary.

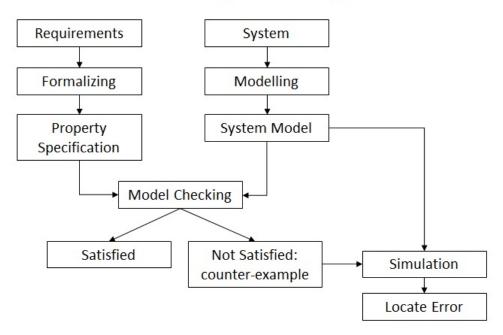

In contrast model checking provides an alternative to verification that relies on a model of the system and a formal description of its requirements (properties). Figure 1.4 shows the model checking approach to verification. The model checking verification approach works over a model of the system, not the product itself (e.g. the final code in the software). The verification is performed in an *a priori* manner: errors, inconsistencies, and bugs can be detected before the product development process takes place. This is an important change in paradigm when it comes to development and verification. To fully exploit these benefits a greater effort in modelling has to be performed, so there is a trade-off when choosing which verification approach to take. However, the exhaustive verification capabilities and the formality of the model checking approach are appealing features for safety critical systems such as jet-engine control software.

### **1.1.5** Commercial Jet-Engine Control

A jet-engine is one of the most complex pieces of machinery ever created. No engine is the same and performance varies from engine to engine and on the same engine over time [78]. The engine components degrade at different rates and after an overhaul or repair performance is also affected. This presents a challenge for the control system because it should be able to cope with both slow degradations in performance and rapid changes due to overhaul [78].

#### Model checking verification approach

Fig. 1.4 Model checking verification approach: verification is performed in an *a priori* manner. The verification is performed in a model of the system under analysis before generating the product or a prototype.

In its early days, jet-engine control consisted mainly in regulating fuel flow into the combustor, controlling the air-fuel mix. Over the years new control inputs have been progressively added to the control scheme. Actuators such as guide vanes, variable exhaust nozzles, variable compressor stators, and variable bleed valves, among others, have been added to the jet-engine in order to obtain more thrust, better efficiency, and reduce weight [166]. This in turn created the necessity for a change in the control scheme, giving birth to more advanced algorithms.

A modern engine control system is in charge not only of control activities. As shown in Figure 1.1, there are many other functions running in the control computer (e.g. EEC). The three main functions are [38]:

- Communication with the aircraft to receive control commands and report status.

- Running the control algorithm to meet engine performance.

- Health management for diagnostics, prognostics, and control.

Advances in computer power allowed the possibility to add health management functions. Because most of the health monitoring functions are related to control actuators, health management is tightly related to the control system itself [78]. Fault detection, isolation, and accommodation plays a fundamental role in engine control and performance [78, 166]. Jet-engine control must be fault tolerant and highly reliable for safety reasons, which means redundancy in both hardware and software components of the control system.