# University of New Mexico UNM Digital Repository

**Electrical and Computer Engineering ETDs**

**Engineering ETDs**

2-8-2011

# FUNDAMENTAL ISSUE IN SPACE ELECTRONICS RELIABILITY: NEGATIVE BIAS TEMPERATURE INSTABILITY

Jesse Mee

Follow this and additional works at: https://digitalrepository.unm.edu/ece etds

## Recommended Citation

Mee, Jesse. "FUNDAMENTAL ISSUE IN SPACE ELECTRONICS RELIABILITY: NEGATIVE BIAS TEMPERATURE INSTABILITY." (2011). https://digitalrepository.unm.edu/ece\_etds/175

This Thesis is brought to you for free and open access by the Engineering ETDs at UNM Digital Repository. It has been accepted for inclusion in Electrical and Computer Engineering ETDs by an authorized administrator of UNM Digital Repository. For more information, please contact disc@unm.edu.

| I I M                                                                              |                          |

|------------------------------------------------------------------------------------|--------------------------|

| Jesse K. Mee Candidate                                                             |                          |

| Electrical Engineering  Department                                                 | _                        |

| This thesis is approved, and it is acceptable in quality and form for publication: |                          |

| Approved by the Thesis Committee:                                                  |                          |

|                                                                                    | Luke Lester, Chairperson |

|                                                                                    | Olga Lavrova             |

|                                                                                    | Roderick Devine          |

|                                                                                    |                          |

|                                                                                    |                          |

|                                                                                    |                          |

|                                                                                    |                          |

|                                                                                    |                          |

|                                                                                    |                          |

|                                                                                    |                          |

|                                                                                    |                          |

|                                                                                    |                          |

# FUNDAMENTAL ISSUES IN SPACE ELECTRONICS RELIABILITY: NEGATIVE BIAS TEMPERATURE INSTABILITY

$\mathbf{BY}$

#### JESSE K. MEE

# **BACHELOR'S OF SCIENCE**

### **THESIS**

Submitted in Partial Fulfillment of the Requirements for the Degree of

**Master of Science**

**Electrical Engineering**

The University of New Mexico Albuquerque, New Mexico

December, 2010

© 2010, Jesse K. Mee

# **DEDICATION**

I dedicate this work to my wife Hannah, my son Trevor, and my daughter Lillian. My academic achievements would be meaningless without the love and support of my family.

# **ACKNOWLEDGEMENT**

I would first and foremost like to acknowledge to the extraordinary effort of Dr. Rod Devine for his assistance with experimental development, and conceptual understanding. None of this work would have been possible without his guidance. I would like to give a special thanks to Dr. Len Trombetta, Dr. Robert Kaplar, Dr. Harry Hjalmarson, and Dr. P. Goukar for their support of this research. I would like to thank Mr. Marc Owens for giving me the facility and the resources to perform this research. I would like to thank my friends and family for their love and support. I would finally like to thank my thesis committee members; Dr. Luke Lester, Dr. Rod Devine, and Dr. Olga Lavrova.

This work has been partially supported by the Air Force Research Laboratory, Kirtland AFB under contract # FA9453-06-C-0367.

# FUNDAMENTAL ISSUES IN SPACE ELECTRONICS RELIABILITY: NEGATIVE BIAS TEMPERATURE INSTABILITY

$\mathbf{BY}$

#### **JESSE K. MEE**

# **BACHELOR'S OF SCIENCE**

# **ABSTRACT OF THESIS**

Submitted in Partial Fulfillment of the Requirements for the Degree of

Master's of Science Electrical Engineering

The University of New Mexico Albuquerque, New Mexico

December, 2010

# FUNDAMENTAL ISSUES IN SPACE ELECTRONICS RELIABILITY: NEGATIVE BIAS TEMPERATURE INSTABILITY

<u>by</u>

#### Jesse K. Mee

B.S., Electrical Engineering, University of New Mexico, 2009 M.S., Electrical Engineering, University of New Mexico, 2010

# **ABSTRACT**

Negative Bias Temperature Instability (NBTI) in silicon based metal-oxide-semiconductor-field-effect-transistors (MOSFETs) has been recognized as a critical reliability issue for advanced space qualified electronics. The phenomenon manifests itself as a modification of threshold voltage (V<sub>th</sub>) resulting in degraded signal timing paths, and ultimately circuit failure. Despite the obvious importance of the issue, a standard measurement protocol has yet to be determined. This is a consequence of a large amount of complexity introduced by the strong dependencies of NBTI on temperature, electric field, frequency, duty cycle, and gate dielectric composition. Indeed, researchers are nowhere near a dependable circuit reliability lifetime predictor formula that would be accurate among a wide variety of technology specifications.

We have improved upon the traditional measurement techniques which suffered from an underestimation of the magnitude of  $V_{th}$  shifts because they failed to account for trapped charge relaxation. Specifically, we have developed a means for measuring the

maximum effect of NBTI by virtue of a method that can continuously monitor the  $V_{th}(t)$  without having to remove the stressing voltage. The interpretation methodology for this technique is explained in detail and the relevant approximations are justified. Using this method, we have examined the time and magnitude dependencies of change in  $V_{th}$  as a function of time ( $\Delta V_{th}(t)$ ) on temperature, vertical electric field, inversion channel carrier density, and source-drain voltage ( $V_{ds}$ ).

In the work presented here, we have evidenced temperature and vertical electric field dependent  $V_{th}$  shifts in  $SiO_2$  and HfSiON devices. Furthermore, we have collected substantial evidence that the traditional  $\Delta V_{th} = At^{\alpha}$  analysis fails to explain the experimental data in the early time domain. Finally, we have discovered that  $\Delta V_{th}(t)$  on p-channel field effect transistors with HfSiON gate dielectrics is dependent upon the magnitude of  $V_{ds}$  during the stressing cycle. To our knowledge this is not anticipated by any prior modeling attempts. We justify the exclusion of short channel effects as a possibility, leading us to conclude that positive charge in the dielectric stack is laterally mobile and subsequently transported out of the dielectric in the presence of the lateral electric field induced by  $V_{ds}$ .

# **TABLE OF CONTENTS**

| Ι  | DEDICATION                                        | iv  |

|----|---------------------------------------------------|-----|

| A  | ACKNOWLEDGEMENT                                   | v   |

| A  | ABSTRACT                                          | vii |

| Γ  | TABLE OF CONTENTS                                 | ix  |

| Т  | TABLE OF CONTENTS                                 | ix  |

| I  | LIST OF FIGURES                                   | xi  |

| I  | LIST OF TABLES                                    | xii |

| 1. | Chapter 1 – Introduction                          | 1   |

|    | 1.1 Background                                    | 1   |

|    | 1.2 Experimental Objective                        | 6   |

|    | REFERENCES FOR CHAPTER 1                          | 7   |

| 2. | Chapter 2 – Negative Bias Temperature Instability | 8   |

|    | 2.1 Reliability Issues for Space Electronics      | 8   |

|    | i. Radiation effects                              |     |

|    | ii. Hot Carrier Injection                         | 9   |

|    | iii. Negative Bias Temperature Instability        | 10  |

|    | 2.2 Physical Mechanism behind NBTI                | 10  |

|    | i. The Reaction Diffusion Model                   | 11  |

|    | ii. Two Stage Model                               | 13  |

|    | iii. Dynamic Stress Model                         |     |

|    | REFERENCES FOR CHAPTER 2                          | 17  |

| 3. | Chapter 3 – Experimental Methodology              | 19  |

|    | 3.1 Measurement Equipment                         | 20  |

|    | 3.2 Device Fabrication                            | 21  |

|    | 3.3 Measurement Methods                           | 24  |

|    | REFERENCES FOR CHAPTER 3                          | 28  |

| 4. | Cha | apter 4 – Experimental Results                         | 29 |

|----|-----|--------------------------------------------------------|----|

|    | 4.1 | Data Analysis Methodology                              | 29 |

|    | 4.2 | Full Curve Fit Vs Single Point Approximation           | 34 |

|    | 4.3 | The Start-stop Method Vs The Continuous Method         | 38 |

|    | 4.4 | Temperature Dependence                                 | 41 |

|    | 4.5 | Dependence on the Vertical and Lateral Electric Fields | 44 |

|    | 4.6 | Linear Region Vs Saturation Region Stress Conditions   | 49 |

|    | REF | FERENCES FOR CHAPTER 4                                 | 56 |

|    |     |                                                        |    |

| 5. | Cha | apter 5 – Discussion                                   | 58 |

|    | 5.2 | Positive Charge Trapping Kinetics                      | 58 |

|    | 5.2 | Lateral Charge Transport Theory                        | 62 |

|    | REF | FERENCES FOR CHAPTER 5                                 | 70 |

|    |     |                                                        |    |

| 6. | Cha | apter 6 – Conclusion                                   | 72 |

# **LIST OF FIGURES**

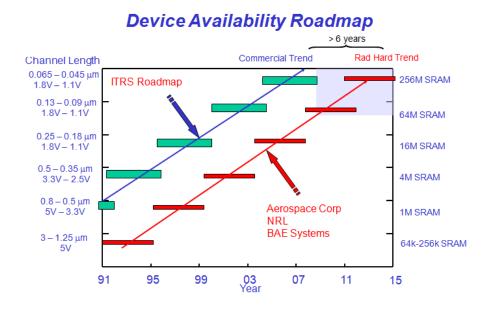

| Figure 1-1 Device Availability Roadmap for Space Electronics                                       | . 1 |

|----------------------------------------------------------------------------------------------------|-----|

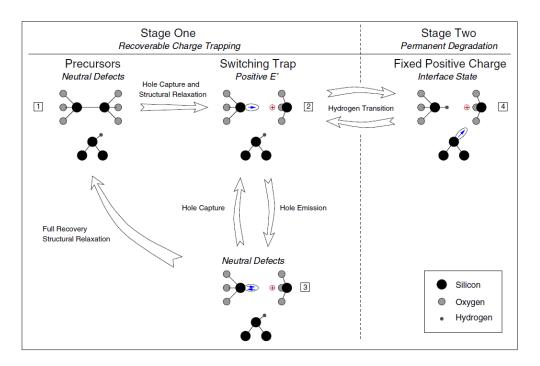

| Figure 2-1) Two stage model for NBTI.                                                              | 14  |

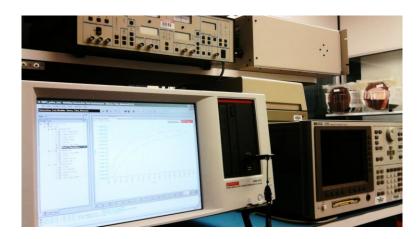

| Figure 3-1) Keithley 4200 SCS measurement system and the HP 4156 Analyzer                          | 20  |

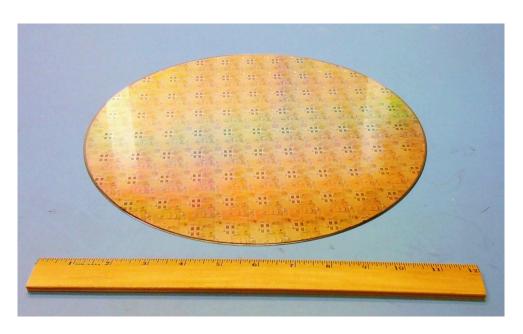

| Figure 3-2) 300mm Wafer from Texas Instruments.                                                    | 21  |

| Figure 3-3) Microscospic view of probe contacts on a 300mm wafer                                   | 23  |

| Figure 4-1) Square Root of I <sub>ds</sub> as a function of V <sub>gs</sub> .                      | 30  |

| Figure 4-2) $V_{th}(t)$ extracted from the start-stop method using two techniques                  | 36  |

| Figure 4-3) a) ΔV <sub>th</sub> (t) from Continuous Stress and Start-Stop Methods                  | 39  |

| Figure 4-4) Temp dependence of V <sub>th</sub> shifts resulting from NBTI                          | 42  |

| Figure 4-5) Activation energey reduced from plot of $ln(A_0e^{-E_A/kT})$ vs $1/T$                  | 43  |

| Figure 4-7) Field dependence of V <sub>th</sub> shifts on HfSiON devices                           | 45  |

| Figure 4-8) Ratio of changing I <sub>ds</sub> to the initial I <sub>ds</sub> °                     | 47  |

| Figure 4-9) V <sub>th</sub> Shifts on HfSiON devices as a function of time and V <sub>ds</sub>     | 50  |

| Figure 4-10) Ratio of $\Delta V_{th}(t, V_{ds})/\Delta V_{th}(t, V_{ds}=-0.1V)$ in HfSiON          | 51  |

| Figure 4-11) $\Delta I_{ds}(t)/I_{ds}^{o}$ and $V_{th}$ from MIT SOI SiO <sub>2</sub> techology    | 53  |

| Figure 4-12) $\Delta I_{ds}(t)/I_{ds}^{o}$ and $V_{th}$ from IBM 130nm SiO <sub>2</sub> technology | 55  |

| Figure 5-1) Charging/relaxing of charge traps in 130nm SiO <sub>2</sub>                            | 59  |

| Figure 5-2) $\Delta V_{th}(t)$ of devices stressed in linear and saturation modes of operation     | 61  |

| Figure 5-3) k*d(V <sub>th</sub> )/dt as a function of time                                         | 65  |

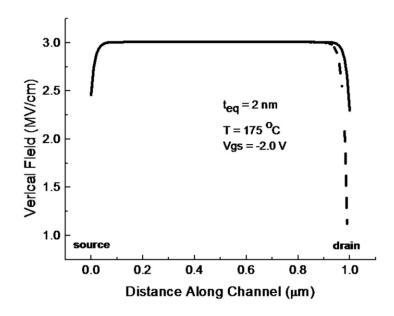

| Figure 5-4) Vertical electric field a function of distance along the channel                       | 66  |

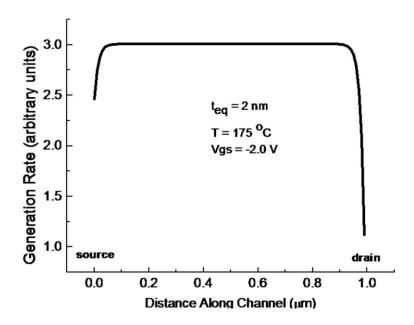

| Figure 5-5) Generation of charge as a function of distance along channel                           | 68  |

# **LIST OF TABLES**

| Table 4-1) $\alpha$ values deduced from approimate and exact determination of $V_{th}$ | 37 |

|----------------------------------------------------------------------------------------|----|

| Table 4-2) A and $\alpha$ fitting parameters from field dependece experiment           | 48 |

# 1. Chapter 1 – Introduction

#### 1.1 Background

It is well known that silicon based technology for radiation hardened space electronics is several technology generations behind its commercial counterparts; this is illustrated in FIG 1-1. So while presently hardened devices in the 90 – 65 nm node are in the research and development phase, commercial industry is addressing the developmental issues relating to 22 nm devices. A positive consequence of this delay is that the reliability lifetime, a current problem in the commercial industry, has not yet impacted the world of space based electronics.

Figure 1-1 Device Availability Roadmap comparing the radiation hard trend to the commercial trend

As silicon based technology evolves, increased device performance is being achieved by both scaling of transistor feature sizes and also by the introduction of new materials

whose influence on device reliability may be relatively unknown. In the former case the scaling of gate oxide thicknesses below 2nm without the corresponding reduction in supply voltage resulted in increased oxide electric fields and enhanced leakage currents. Compounded with the rapid increase in new materials and inherent risk of reliability loss, scaling results in increased power dissipation resulting from the density of active devices in a given chip area. Power dissipation is well known [1] to result in increased operational temperatures leading to more rapid deviation of device characteristics (threshold voltage shift, carrier mobility,...) and interconnect failure due to mechanisms such as electromigration. In the case of temperature enhanced device characteristic variation, one of the prime mechanisms in metal-oxide-semiconductor field effect transistor (MOSFET) p-channel devices is the *negative bias temperature instability (NBTI)*. Various authors have suggested that this degradation mechanism may be dominant in advanced, stronglysub-micronic technology. In addition, an equivalent effect in n-channel MOSFET devices has been observed and termed positive bias temperature instability (PBTI) which results from elevated temperature and positive bias with respect to substrate. It has been repeatedly shown, however, that characteristic shifts due to PBTI are significantly less than the shifts observed in NBTI. As a result, it is widely accepted that the underlying physical mechanism behind the phenomenon of NBTI results in the generation and trapping of positive charge. The origin of this positive charge remains in question and has captured the interest of researchers all over the world.

From perspective of circuit lifetime, PBTI and NBTI result in asymmetric degradation of the n-channel and p-channel MOSFETs since in magnitude NBTI>PBTI so to speak. The asymmetry induced generates timing issues that can ultimately lead to

logic upsets. This is evident by analysis of the full square law model for source drain current in a MOSFET [2],

$$I_{ds} = (W/L) \mu_{eff} C_{ox} \left[ \left\{ V_{gs} - (V_{th}^{0} + \Delta V_{th}) \right\} V_{ds} - 1/2 V_{ds}^{2} \right]$$

(1-1)

where W is the channel width, L the channel length and  $C_{ox}$  the gate dielectric stack capacitance.  $\mu_{eff}$  is the effective mobility of the inversion channel carriers (holes or electrons). In the p-channel devices, positive charge is trapped somewhere in the gate dielectric effectively making the threshold voltage ( $V_{th}$ ) more negative. From Eq. 1-1, an increase in  $\left| (V_{th} + \Delta V_{th}) \right|$  will result in a decrease in  $I_{ds}$  for a given  $V_{gs}$ . Coupled with the fact that the delay time for signal arrival in a CMOS circuit is inversely proportional to the source-drain current ( $I_{ds}$ ) of the transistor, the effect of NBTI will be to increase the delay time. As for the n-channel devices, the  $V_{th}$  remains essentially constant and thus an increased spread in signal arrival times is created. This degradation of the timing paths can potentially lead to logic upsets and ultimately circuit failure.

In the light of the previous discussion one might have expected that evidence of a reliability lifetime issue due to such mechanisms as NBTI in advanced CMOS technology would have already had a significant negative impact on the commercial industry. However, it has not and the explanation for this revolves around two characteristics of the commercial industry. The first is that commercial products are increasingly replaced after a few years of use (i.e. before wear-out) and thus strict lifetime requirements such as the old 24/7 for 10 years are not necessary. Secondly, the worst case, continuous operation scenario is seldom observed in modern electronics and one must consider, for example,

the duty cycle which can dramatically reduce the device "on time". Given that the characteristics of observed trapped charge relaxation phenomena occurring in NBTI [3], one can conclude that nature fortuitously works in reducing the overall magnitude of degradation. As an example, tests on 65 nm technology produced by one of the world's premier manufacturers of microelectronics (TSMC) resulted in a DC lifetime of 0.2 years and an AC lifetime of 10 years [4]! However, the reliability of advanced CMOS technology is a major cause for concern in the space industry where certain satellite applications require operational lifetimes ~ 10 - 15 years. Among the various mechanisms contributing to reliability loss in satellite electronics, such as electronic reliability (NBTI and PBTI), and the effects of irradiation via total ionizing dose and/or single event upset, NBTI is the least understood and continues to generate the most concern. It is crucial that a deeper understanding of the origin and nature of NBTI be achieved. The space industry will clearly evolve to more advanced technologies and device reliability will become the primary factor limiting the lifetime of a satellite.

Although the origin of NBTI is not understood, it appears clear that it is intimately related to the physics of the gate insulator/semiconductor interface and certainly, increasingly, to the nature of the complex oxide used as the gate insulator. In more advanced fabrication processes higher dielectric constant ( $\kappa$ ) gate insulators are being introduced in order to enable thicker dielectric films to be employed. Note that to first order the leakage current varies inverse exponentially with the dielectric thickness ( $t_{ox}$ ) [5] and that the gate capacitance  $C \propto \kappa/t_{ox}$ . Consequently, the same gate capacitance can be achieved using higher  $\kappa$  films which are thicker. However, it has been observed experimentally the use of high- $\kappa$  films enhanced NBTI and consequently

degraded lifetime reliability results. In the simplest case, this is believed to be the result from increased charge trap density in complex oxides. However, the real picture becomes much more complicated when we consider the process steps involved in the creation of the gate stack. First one starts with a thin ( $\sim 1$  nm) SiO<sub>2</sub> layer on the Si substrate, this is followed by an alternative dielectric such as HfSiO which may be then nitrided to form HfSiON. This process will not result in a simple HfSiON/Si gate stack but more likely at the very least HfSiON/SiON/Si having a minimum of two relevant mismatch interfaces (HfSiON/SiON and SiON/Si) and two "bulk" dielectrics, HfSiON and SiON, with their own charge trapping defect sites. The resulting complexity of the gate stack presently prevents identification of the exact nature and location of the traps and/or their spatial distribution. On the other hand, comparing the charging and relaxation kinetics of a device with a simple SiO<sub>2</sub> gate dielectric to a device with a "high  $\kappa$ " gate dielectric can offer valuable insight into the physical mechanism of NBTI.

Perhaps one of the most challenging aspects in the study of NBTI is the fact that measurement techniques vary considerably from one research group to another making cross referencing of research results very difficult. Though it appears unlikely at the present time, ultimately a generic protocol for the measurement of stress induced threshold voltage degradation needs to be established. As we will discuss in detail, in our own approach we target the reduction of error resulting from trapped charge relaxation by sustaining the stress throughout the experiment. This is achieved by measuring the change in source-drain current with time  $I_{ds}(t)$  while maintaining a stressing voltage on the gate and drain contacts. The device threshold voltage shift  $\Delta V_{th}$  can then be extracted from the fractional current change  $I_{ds}/I_{ds}{}^{o}$ . Bearing in mind certain approximations which

we will validate in a later chapter, the result of this continuous stress measurement will be shown to be a good representation of the full effect of trapped charge on the threshold voltage **in the DC stress mode**. This proves to be a crucial piece of information when trying to develop a better understanding of the physics, but may not be the best method on which to base a reliability lifetime predictor model. Building a reliable lifetime predictor formula will require careful examination of the circuit operation conditions as well as technology specifications.

#### 1.2 Experimental Objective

On the basis of the above discussion we developed a set of objectives for this thesis. Initially we will familiarize our self with optimized measurement techniques and data interpretation methodology for NBTI lifetime assessment. Upon development of optimized experimental procedures, we will study NBTI in advanced high-κ dielectrics. In particular, we will develop the hypothesis that in advanced dielectric gate stacks, NBTI is composed of a "dynamic" part related to spatially and energetically close defects which can trap charge and release it spontaneously, and a "static part" at the interface or in the dielectric which cannot release charge once trapped. For this reason, the outcome of the experiments on the high-κ devices will be compared to the results of equivalent experiments on devices with "basic" SiO<sub>2</sub> gate dielectrics where the relative content of dynamic terms may be less significant. Finally, potential explanations for our observed effects will be discussed, and the consequences of the phenomenon will be evaluated.

# **REFERENCES FOR CHAPTER 1**

- [1] International Technology Roadmap for Semiconductor, Executive Summery, pp.51 (2009)

- [2] S.M. Sze, *The Physics of Semiconductor Devices*, NY: Wiley, Chapter 8, 1981

- [3] R. A. B. Devine, J. K. Mee, H. P. Hjalmarson M. A. Quevedo-Lopez and H. N. Alshareef, "A simplified approach to estimating the total trap charge contributions in negative bias temperature instability," J. Appl Phys. 106, 024508 (2009)

- [4] Silicon Blue, "65LP Process Qualification Summary," pp. 6 (2009)

- [5] P. E. Nicollian, M. Rodder, D. T. Grider, P. Chen, R. M. Wallace, S. V. Hattangady, "Low Voltage Stress-Induced-Leakage-Current in Ultrathin Gate Oxides." Proc. 37<sup>th</sup> IEEE/IRPS (1999)

# 2. Chapter 2 – Negative Bias Temperature Instability

### 1.1 Issues for Space Electronics

Modification of semiconductor device characteristics resulting in reduction of circuit performance presents a major reliability concern for the production of space qualified electronics [1]. Degradation of circuit lifetime is a consequence of a variety of phenomena that contribute to reliability loss in space electronics. Among these phenomena are the effects of irradiation, hot carrier injection (HCI), and negative bias temperature instability (NBTI) [2, 3, 4]. A considerable amount of research has gone into the understanding and prevention of these issues and while all have progressed, some remain much more critical than others. For completeness, we will briefly describe the state of each issue.

## i. Radiation effects

Radiation effects manifest themselves in several different ways. Perhaps the most critical is cumulative long term ionizing damage due to energetic protons and electrons also know as total ionizing dose (TID) [2]. TID results in  $V_{th}$  shifts, timing skews, and leakage current. Fortunately, TID is proportional to  $l^2$  where l is the gate oxide thickness; therefore in heavily sub-micronic devices l is so small that TID becomes less relevant. Additionally, there are a series of radiation phenomena called single-event effects (SEE) [2] that are often less destructive than TID but can still be detrimental to a mission if not properly addressed. SEEs are caused by energetic particles passing through the active area of a circuit creating electron-hole pairs. This

can lead to single-event upsets such as bit-flips in a register, or single-event latchup which results in increased operating current. As space qualified technology has evolved, the issue of reliability loss due to radiation effects such as TID, and SEEs has been largely circumvented due to a global effort to build radiation hardened circuits. This effort has resulted in many "harden by process" technologies such as buried guard rings [5], and silicon on insulator (SOI) MOSFETs, as well as many "logical hardening" techniques such as the use of redundant elements, and error detection and correction (EDAC) memories [6]. In addition, given that the dose of radiation a satellite will expect to receive is completely dependent on the satellites operational orbit, a simple way to mitigate the effects of radiation is to select a low radiation orbit. However, in a lot of cases the developers do not have flexibility with regard to the operational orbit.

## ii. Hot Carrier Injection

The phenomenon of HCI arises primarily when device channel lengths are scaled below 1µm without the corresponding reduction in supply voltage. The resulting increase in vertical and lateral electric field near the MOSFET drain contact can supply enough kinetic energy to the carriers in the inversion channel to overcome the potential barrier at the semiconductor/insulator interface and depassivate Si-H bonds. The issue of HCI was reduced by the introduction of lightly-doped drains (LDD) which reduced the space charge region near the drain-end of the channel thereby reducing the electric field [2]. At the same time, the evolution to lower gate voltages reduced the effects of HCI by similarly lowering the drain field.

# iii. Negative Bias Temperature Instability

The physical mechanisms related to the phenomena described above are well understood and consequently the more critical issue moving forward is the more puzzling one. NBTI is a key reliability issue for advanced p-channel MOSFET technology [1,7]. As described in chapter 1, NBTI results in an increase in device threshold voltage and a consequent decrease in source-drain current and transconductance. This poses a major concern for the reliability of space qualified electronics as it can modify timing paths and increase the probability of circuit failure. At the present time, nobody truly understands the physical origin of NBTI, although some would claim they do. In the next section we will discuss a couple of the previous attempts to model the phenomenon.

#### 2.2 Physical Mechanism behind NBTI

Efforts to explain the origin of NBTI have evolved over time from the most basic scenarios in which the phenomenon was attributed to a single mechanism, to complicated multi-mechanism processes involving diffusion of protons or molecular hydrogen, and the capture/release of holes. This progression has been complicated by challenges surrounding the appropriate way to make stress time measurements, be it continuous stress with periodic on-the-fly sampling, or stress/measure/stress techniques. In consequence, research groups have published a variety of experimental results based on completely different measurement techniques and data analysis methodologies. Comparing results from one research group to the next is difficult and often the outcomes are contradictory.

More recently it has become widely acknowledged that multiple mechanisms are responsible for the threshold voltage degradation observed in NBTI. Specifically, experimental data supports both a rapid charge trapping mechanism that can be easily recovered, and a slower but possibly permanent mechanism which is prominent in the long time domain. The origin of these mechanisms has yet to be determined; however, several research groups have put forth models to explain the phenomenon. None of the following models can accurately predict the behavior we have observed in our experiments; nevertheless, examination of the previous modeling attempts and in particular, understanding where they have failed, builds valuable knowledge and is essential for the completeness of this study.

# i. The Reaction Diffusion Model

The original Reaction Diffusion (RD) [4] model for NBTI was undoubtedly the simplest case scenario. It involved only a single mechanism which resulted in the creation of an interface state, similar to those created in hot carrier injection. In this model a hole from the inversion channel, in the presence of a vertical electric field induced by the surface potential, is attracted to the semiconductor/insulator interface where it interacts with Si-H bonds created during passivation of the dangling Si bonds at the interface. This interaction was believed to weaken the Si-H bond to the point that it would break. At elevated temperature the Si-H bonds dissociate and subsequently the neutral atomic hydrogen captures a hole and becomes positively charged. The end result of this reaction,

$$Si_3 \equiv SiH + h^+ \rightarrow Si_3 \equiv Si^{\bullet} + H^+$$

is a silicon dangling bond which we call an interface state, and a positively charged hydrogen also called a proton. With the assistance of the vertical field, the proton would drift deeper into the oxide and become trapped. The RD model predicted magnitude dependence on temperature and  $t^{\alpha}$  time dependence over all time domains.

As curiosity surrounding NBTI grew, extensive experimental results began to reveal shortcomings in RD theory. Although the model could explain the degradation of threshold voltage under constant bias stressing, it failed to address the recovery dynamics. Furthermore, the ability of a hole from the inversion layer to depassivate the Si-H bond had come into question [8]. As a result, various extensions of RD theory tried to address these issues but with minimal success. In our own experiments we have found additional evidence that RD theory is not physical. This involved showing that the time dependence of the effect does not follow the  $t^{\alpha}$  behavior as predicted. We will discuss these results in detail in chapter 4.

Ultimately, it became clear that a single mechanism model based on the generation of interface states could not explain the time dependence or the recovery dynamics associated with NBTI. Consequently, the idea of a two component model was accepted to be more physical. The creation of interface states as described by RD theory is still believed to be one of the contributing mechanisms; however, the means by which the interface states are created remains in question. As for the second mechanism, we envision the rapid charging of defects in the oxide from holes in the inversion layer. The question remains as to how the holes overcome the potential barrier at the interface;

nevertheless, these trapped charges can apparently be rapidly filled and discharged, accounting for the recovery aspect of NBTI.

# ii. Two Stage Model

A more elaborated multi-mechanism explanation is the two stage model proposed by T. Grasser, et al [9]. In this theory the precursor for the phenomenon is a neutral interfacial oxygen vacancy, which upon the capture a hole, creates a positive defect called an  $E'_{\gamma}$  center. Next, the emission of a hole (electron capture) neutralizes the defect at which point the structure can either relax back to the original oxygen vacancy precursor, or re-capture a hole and return to the  $E'_{\gamma}$  state. This is the mechanism believed to account for the rapid charging and recovery dynamics observed in NBTI. As for the second mechanism, the  $E'_{\gamma}$  center can interact with the hydrogen passivating a neighboring silicon dangling bond at the interface. Simple thermodynamic arguments [10] show that it is energetically favorable for the hydrogen to migrate to the  $E'_{\gamma}$  center leaving behind an interface state whose charge will depend on the position of the Fermi-level. An illustration of this mechanism is shown in FIG 2-1.

Figure 2-1) Two stage model proposed by T. Grasser et al. Stage one is based on the HDL model for switching traps. Stage two illustrates a hydrogen transitions which results in the creation of an interface state.

This model resolves issues not addressed in the previous RD model such as variable time dependence and depassivation energies of hydrogen; however, the theory is not without question. In particular, some potential concerns arise when assuming all the mechanisms associated with NBTI happen at the interface and not in the bulk of the dielectric. This concept is contradictory to experimental results showing modification of degradation characteristics dependent of the density of defects in the "bulk" of the gate dielectric [11]. Additionally, the recoverable charging mechanism in this theory is based on a mechanism proposed by the Harry-Diamond-Laboratories (HDL); however, it has been shown [8] that resultant potential barriers in that mechanism are not deep enough to sustain the positive charge and consequently the system immediately relaxes to its initial oxygen vacancy precursor state. Nevertheless, its inclusion of multiple processes is

certainly more physical than previous single process explanations, thus we believe it is a step in the right direction.

# iii. Dynamic Stress Model

Some groups have elected to concentrate on the dynamic operation characteristic of CMOS circuits. A group from ASU [12] integrated dynamic voltage scaling and sleep mode into their circuit aging prediction model. Ultimately, they combined the RD theory [4] with a trapping/detrapping model [13] then developed an interface to introduce a variety of active and sleep periods. Their model attempted to predict threshold voltage degradation resulting from a combination of charging and relaxation times. They went on to examine the behavior of NBTI under a variety of different supply voltages (Vdd) arriving at the expected conclusion of increased V<sub>th</sub> degradation with increased Vdd.

This model addressed some key aspects involved with development of a reliability lifetime predictor formula for realistic circuit operation. However, it is based on the physical mechanisms as predicted by the RD model in combination with a hole trapping/relaxing process in the bulk of the dielectric which is not understood. As a result, there is still an enormous amount of improvement to be made.

Examination of these models has offered some valuable insight into the possible contributing mechanisms of NBTI. Although none of them can fully explain the results we will discuss in Chapter 4, each of them conveys important concepts to consider when developing our own explanation of the phenomenon. It is important to note, however, that deciding between theoretical models is not a primary objective for this thesis. Rather, the intention of this thesis is to advance our understanding of physical mechanisms relative to

NBTI in advanced dielectrics and to unveil to relevant variables and their associated dependencies on time and gate dielectric field magnitude.

## **REFERENCES FOR CHAPTER 2**

- [1] D. K. Schroder, J. A. Babcock, "Negative bias temperature instability: Road to cross in deep submicron silicon semiconductor manufacturing," J. Appl. Phys. **94**, 1 (2003)

- [2] D. Alexander, "Design Issues for Radiation Tolerant Microcircuits for Space,"

Proc IEEE/NESREC (1996)

- [3] M. Koyanagi, T. Huang, A, Lewis, and J. Y. Chen, "Hot Carrier Reliability in Submicron pMOSFETs" Proc. IEEE/ISCS (1989)

- [4] M. A. Alam, S. Mahapatra, "A comprehensive model for PMOS NBTI degradation," Microelectron. Reliab. 45, 71 (2004)

- [5] W. H. Morris, "Buried Guard Ring and Radiation Hardened Isolation Structures and Fabrication Methods" Silicon Space Technology Corporation, Pub. No. WO/2005/079400 (2005)

- [6] F. P. Miller, A. F. Vandome, J. McBrewster, "Error Detection and Correction,"

- [7] C. E. Blat, E. H. Nicollian, and E. H. Poindexter, "Mechanism of negative-bias-temperature instability," J. Appl. Phys. 69, 1712 (1991).

- [8] A. H. Edwards, "Interaction with silicon dangling orbital at the <111> Si/SiO<sub>2</sub> interface," Phys. Rev. B 44, 1832 (1991)

- [9] T. Grasser, B. Kaczer, W. Goes, Th. Aichinger, Ph. Hehenberger, and M. Nelhiebel, "A Two-Stage Model for Negative Bias Temperature Instability," Proc. 47<sup>th</sup> Annual IEEE/IRPS pp. 33-44 (2009)

- [10] P. M. Lenahan, "Atomic Scale Defects Involved in MOS Reliability Problems,"Microelectron. Eng. 69, 173 (2003)

- [11] J. K. Mee, R. A. B. Devine, and L. Trombetta, "Competing Charge Relaxation Mechanisms in HfSiON Insulator Field Effect Transistors," Proc. 218<sup>th</sup> Elect.

Chem. Soc. Conf. (2010)

- [12] R. Zheng, J. Velamala, V. Reddy, V. Balakrishnan, E. Mintarno, S. Mitra, S. Krishnan, Y. Cao, "Circuit Aging Prediction for Low-Power Operation," Proc. IEEE/CICC (2009)

- [13] S. Bhardwaj, W. Wang, R. Vattikonda, Y. Cao, S. Vrudhula, "Predictive modeling of the NBTI effect for reliable design," Proc. IEEE/CICC (2006)

# 3. Chapter 3 – Experimental Methodology

When considering the effects of time dependent trap charging as one does in NBTI measurements, there are a wide variety of experimental procedures for performing stress time measurements. From the classical start-stop methods to more modern on-the-fly techniques, it is important not only to be able to capture the **charging** mechanics, but also the charge relaxation phenomena as well. Our second experimental objective was, study NBTI in advanced high-κ dielectrics. Accordingly, we have performed a series of experiments on HfSiON technology to examine different features of the NBTI for the purpose of gaining a better understanding of the physical origin behind the phenomenon. This involved studying the time and magnitude dependence of threshold voltage shift on ambient temperature, the relative dependence on vertical electric field in the gate oxide (perpendicular to the inversion channel), the dependence on the electric field in the lateral sense (source-drain), and the dependence on charge density in the inversion channel. To address our third objective, compare to the results of HfSiON experiments to equivalent experiments on devices with "basic" SiO<sub>2</sub> gate dielectrics, we persisted to explore these effects on devices with SiO<sub>2</sub> gate dielectric stacks as well. One of the more challenging aspects of this study was acquiring samples that would be comparable. Though we never achieved this to the extent we would have preferred, we were able to acquire state-of-theart HfSiON, and SiO<sub>2</sub> samples; details of their fabrication will be discussed below. In addition to experiments concerning our understanding of the physical mechanisms in NBTI, we performed other experiments that explored traditional stress/measure/stress methods primarily for the purpose of comparison to our continuous stress data. This allowed us to extract information about the potential underestimation of device reliability

lifetime depending on the chosen measurement protocol; an important piece to the puzzle for developing a reliable predictor formula. Finally, we performed rapid data acquisition measurements in a continuous mode to increase our resolution in the sub 1 second time regime. This was very important for the support of a multi-mechanism NBTI process [1] and opposed the single mechanism [2] process that was initially proposed.

#### 3.1 Measurement Equipment

The majority of these experiments were performed at the Air Force Research Laboratories for the Space Electronics Branch. The samples under test were mounted on a temperature controlled vacuum chuck. Standard electrical MOSFET characteristics were measured using either the HP 4156 analyzer or the Keithley 4200 SCS measurement system. For our experiments, both of these systems provided a great deal of functionality with regards to manipulation of the voltages, and measurement intervals. The data acquisition time limitations of the HP meant that it was advantageous to use the Keithley when performing measurements that required high resolution in the short time. Nevertheless, the HP was more than adequate for executing the longer life tests.

Figure 3-1) Keithley 4200 SCS measurement system and the HP 4156 semiconductor parameter analyzer

Another advantage of the Keithley was the interactive test environment (ITE) software shown open in the active window in FIG 3-1. This ITE provided a user friendly way to set up continuous stress experiments, and stress/measure/stress experiments, as well as provided a path to arrange synchronized, rapid, execution of multiple tests back to back. The most valuable feature of the Keithley 4200 system is its potential to execute a complete  $I_{ds}(V_{gs})$  sweep in ~100ns! Assuming an appropriate level of accuracy is achieved during the acquisition of the curve, this method will ultimately allow for reduced approximation in determination of the full effect on threshold voltage as a result charge trapped in the gate oxide.

# 3.2 <u>Device Fabrication</u>

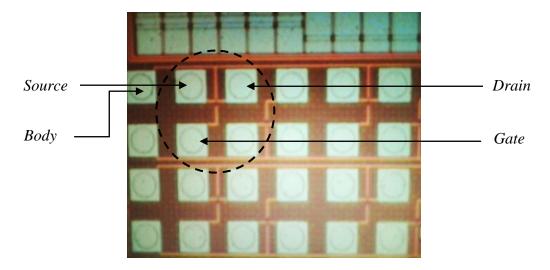

Figure 3-2) 300mm Wafer from Texas Instruments. Variety of technologies including 32nm pMOS & nMOS

Most of the experiments in this study were performed on a set of twenty-five 300mm test wafers from Texas Instruments; FIG 3-2. The entirety of the lot was built using a high-k HfSiON gate dielectric stack optimized for 32 nm technology. However, each pair of wafers in the lot was manufactured using a slightly different processing step (for example, different LDD implant). For the purpose of obtaining comparable results then, all of our measurements were performed on a single wafer. Because the original purpose of the lot was to evaluate gate stack performance and reliability for a variety of technology nodes, there was a wide range of device channel lengths available ranging from 10µm to 32nm. The devices used in the experiments reported here were primarily pchannel MOSFETs with 1 µm channel lengths. This length minimized the potential for short channel effects. Additionally, some devices with 10, 0.7, or 0.3 µm channel lengths were also used. The gate dielectric stacks were formed [3] of chemically oxidized Si (approximately 1 nm of SiO<sub>2</sub>) upon which HfSiO was deposited using the technique of atomic layer deposition (ALD). The hafnium and silicon precursors in the ALD process were Hf[N(CH<sub>3</sub>)C<sub>2</sub>H<sub>5</sub>]<sub>4</sub> and Si[N(CH<sub>3</sub>)C<sub>2</sub>H<sub>5</sub>]<sub>4</sub> respectively. The stack was then nitrided using the process of post deposition annealing in NH<sub>3</sub>. The metal electrodes were formed of physical vapor deposited (PVD) TaN. A conventional CMOS flow completed the fabrications process. FIG 3-3 is a magnification of the CMOS array showing the contact pads and, because there is only one metal layer, the physical features of the individual transistors.

$Figure \ 3-3)\ Probe\ contacts\ for\ CMOS\ array\ on\ 300mm\ TI\ wafer.\ Specifically\ labeling\ the\ contacts\ of\ a\ 45nm\ p-channel\ MOSFET$

Given that NBTI is strongly dependent on the physical properties of the gate oxide, we performed additional experiments on two sets of devices with the "classical" SiO<sub>2</sub> insulator. These dielectrics were much less complex than those of the high-κ devices simplifying the possible physical explanations, thus providing a great "baseline" for our physical interpretation of the data. The first set of devices were fully depleted, silicon-on-insulator (SOI) p-channel MOSFETs from Lincoln Labs at MIT. They contained a 2.6nm SiO<sub>2</sub> gate oxide and their channel lengths ranged from 130nm to 8μm. The second set was from IBM's 130nm process. Details of their manufacture are available at ibm.com under IBM's industry standard 130nm CMOS technology family. The relevant parameters in this context are the thickness and composition of the gate oxide which for these devices was 3.3nm and SiO<sub>2</sub> respectively.

#### 3.3 Measurement Methods

NBTI has been recognized as a reliability issue since the mid-1960's [4]. The first NBTI experiments were performed using a stress/measure/stress technique which we call a "start-stop" measurement. Devices under test would first be heated to between 100 °C and 200 °C and an initial I<sub>ds</sub>(V<sub>gs</sub>) sweep would be performed. After a finite amount of time in which a stressing voltage was applied to the gate electrode, the stress would be temporarily removed and another I<sub>ds</sub>(V<sub>gs</sub>) curve would be acquired. Immediately following the acquisition of the data, the stressing voltage would be re-applied to the gate and the process would repeat. This method suffers from the fact that during the time it takes to stop the bias stress and perform the  $I_{ds}(V_{gs})$  sweep (a few seconds), information is lost due to the relaxation of trapped charge in the oxide [5], particularly at the Si-SiON/HfSiON interfaces. Taking this data to be exact would result in both incorrect physical models, and inaccurate lifetime reliability predictor formulas. For the purpose of completeness we have used the start-stop method and subsequently compared the results to the more modern measurement methods. The details of these measurements vary between experiments and will be discussed below.

Researchers realized that until there is a way to acquire an IV curve in times less than the shortest relaxation time of trapped charge, we cannot get an accurate representation of the full magnitude of NBTI from traditional start-stop measurements. New, but approximate, methods for extracting a device's threshold voltage without having to interrupt the device's stressing conditions have been developed; typically they are referred to as "on-the-fly" measurements. For example, continuously measuring the frequency degradation of a ring oscillator and assuming that it is proportional to change

in threshold voltage is an on-the-fly method used to measure the reliability of a device under realistic circuit operation [6]. In our experiments we are more interested in the physics of the phenomenon so we have adopted a continuous stress implementation that allows us to see the maximum effect of NBTI on a single p-channel MOSFET. The details of this method will be discussed below. Using this continuous technique the assumption is made that any traps charged through application of the stress will remain charged throughout the entire  $I_{ds}(t)$  measurement and this will then reflect the full magnitude of the total charged trapped during the stressing period.

For the temperature dependence experiment we employed two measurement techniques. Using the start-stop technique,  $I_{ds}$  measurements were made as a function of the applied gate-source potential  $V_{gs}$  swept from 0V to -1.5V with the source-drain potential maintained at -0.9V. Source and substrate were grounded. In between  $I_{ds}(V_{gs})$  acquisitions, the gate and drain electrodes were subjected to a bias stress of  $V_{gs}$  = -1.5V and  $V_{ds}$  = -0.9V respectively. Bias stress time intervals varied from 10 s to 300 s and accumulated to 3600 s. At each time point, the total time required to remove the gate voltage and perform the  $I_{ds}(V_{gs})$  sweep was measured to be between 3.5 and 5 s. Alternatively, in a continuous technique, the source-drain current was probed every 5 seconds without the requirement to turn off the bias. This data was accumulated at three temperatures; 95 °C, 125 °C and 155 °C.

In the next set of experiments we explored the time and magnitude dependence of NBTI on both vertical and lateral electric fields. As in the previous case, we used two measurement techniques for each set of data. To specifically analyze the vertical electric field dependence with a start-stop technique,  $I_{ds}(V_{gs})$  measurements were made with  $V_{gs}$

swept from 0V to -2.0V, while  $V_{ds}$  was maintained at -2.0V. In between data acquisitions, the devices were subjected to a bias stress at one of four gate voltages; -2.0V, -1.7V, -1.5V and -1.3V. Since this placed the devices in the inversion mode, the approximate potentials across the dielectric stack were -1.1,-0.8,-0.7 and -0.5 V in the region of the source contact. The uniformity of the vertical field along the channel will be discussed later. Furthermore, in the simplest approximation of a two layer SiON(1 nm)/HfSiON (2 nm) structure, the potential would be non-uniformly divided resulting in a significant field in the SiON layer and a much smaller field in the high-k HfSiON part [5]. In these experiments, the bias time intervals varied from 10s to 120s and were accumulated to 2290 s total.  $V_{ds}$  was maintained at -2.0V during the bias stressing intervals and in all cases a constant temperature was maintained at 175C. For the second approach, the devices were biased in the saturation regime at each of the four gate voltages described above. As mentioned previously the transition from  $\Delta I_{ds}(t)$  to  $\Delta V_{th}(t)$  is approximate but justified.

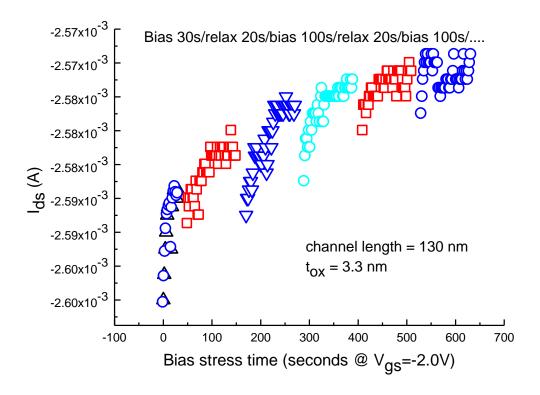

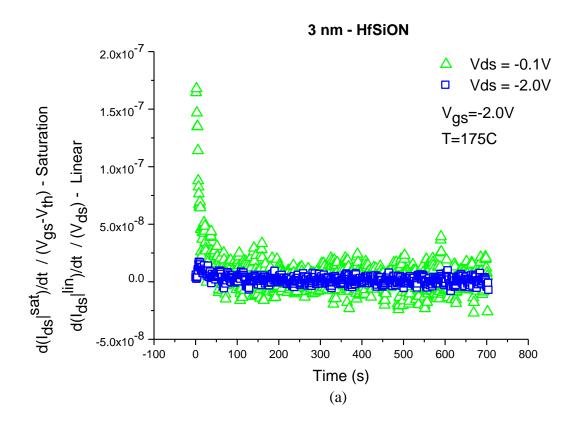

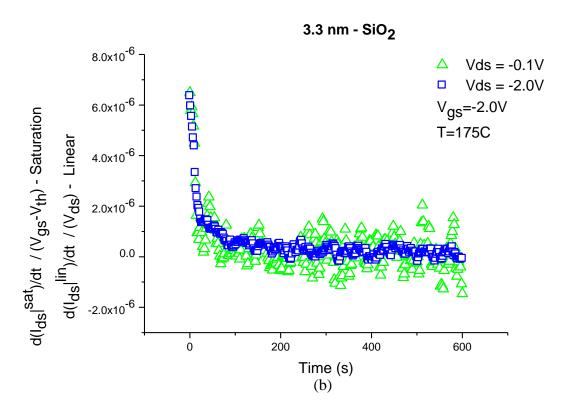

We developed two unique methods for examining the current density and lateral electric field dependence. In both methods we employed the continuous measurement technique. In the first approach, we increased the device channel length by an order of magnitude while maintaining the same channel width, oxide thickness, and stressing voltages. The effect of this was to decrease the source-drain current by an order of magnitude and proportionally decrease the magnitude of the electric field in the lateral direction. In a second approach, we were particularly interested in the fast trap charging effect as the devices made the transition from saturation to linear regime. This transition was achieved by reducing the source-drain voltage. To adequately capture this data it was

necessary to increase the resolution in the early time. As a result, these measurements were performed using the Keithley 4200 SCS system in a continuous mode wherein  $I_{ds}$  was probed approximately every 0.75 seconds without the interrupting the stress. The devices were all stressed at a temperature of 175C,  $V_{gs}$  = -2.0V, and  $V_{ds}$  took the values - 2.0V, -1.7, -1.5V, -1.25V, -1.0V, -0.75V, -0.5V, -0.25V, and -0.1V. We used 9 different source-drain voltages to give us more resolution as the device operation varied from the saturation region into the linear regime [7]. The results of these tests were without a doubt the most surprising/intriguing of the entire study and will be discussed in detail in Chapters 4 & 5.

### **REFERENCES FOR CHAPTER 3**

- [1] T. Grasser, B. Kaczer, W. Goes, Th. Aichinger, Ph. Hehenberger, and M. Nelhiebel, "A Two-Stage Model for Negative Bias Temperature Instability," Proc. 47<sup>th</sup> Annual IEEE/IRPS pp. 33-44 (2009)

- [2] M. A. Alam, S. Mahapatra, "A comprehensive model for PMOS NBTI degradation," Microelectron. Reliab. 45, 71 (2004)

- [3] M. A. Quevedo-Lopez, P. D. Kirsch, S. Krishnan, H. N. Alshareef, J. Barnett, H. R. Harris, A. Neugroschel, F. S. Aguirre-Tostado, B. E. Gnade, M. J. Kirm, R. M. Wallace, and B. H. Lee, "Systematic Gate Stack Optimization to Maximize Mobility with HfSiON EOT Scaling," Proc. 36<sup>th</sup> European Solid-State Device research Conference pp. 18-22, (2006)

- [4] B. Deal, M. Sklar, A. Grove, E, Snow, "Characteristics of the surface-state charge (Qss) of thermally oxidized silicon," J. Electrochem. Soc. 114, 266 (1967)

- [5] J. K. Mee, and R. A. B Devine, "Bias stress voltage dependence for fast and slow traps resulting in negative bias temperature instability," J. Appl Phys. 107, 024511 (2010)

- [6] R. Zheng, J. Velamala, V. Reddy, V. Balakrishnan, E. Mintarno, S. Mitra, S. Krishnan, Y. Cao, "Circuit Aging Prediction for Low-Power Operation," Proc. IEEE/CICC (2009)

- [7] D. A Neaman, Semiconductor Physics and Devices, NY: McGraw Hill, Chapter 11, 1981

# 4. Chapter 4 – Experimental Results

We performed a variety of experiments on p-channel MOSFETs with HfSiON gate dielectric, and compared the results to those on SiO<sub>2</sub> devices. These experiments were developed to test time and magnitude dependencies of threshold voltage shifts under an assortment of different stressing conditions. The goal was to decouple the electric field, temperature, and charge density components that are responsible for NBTI in order to improve our understanding of the physical mechanisms involved. Before we present the experimental results, it is necessary to describe our methodology for translating continuous current measurements into threshold voltage shifts. In the subsequent section we will justify our data interpretation methods, and discuss the approximations involved.

## 4.1 Data Analysis Methodology

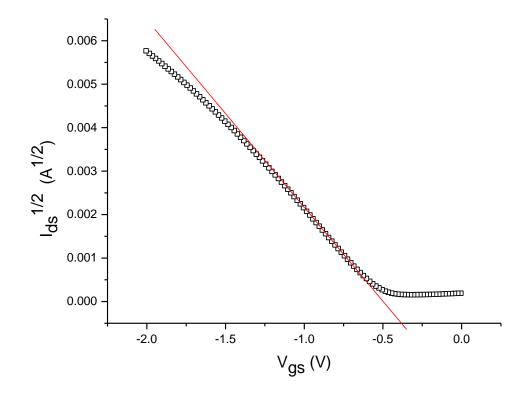

In order to appropriately analyze the data we must first translate change in sourcedrain current with time  $\Delta I_{ds}(t)$  to change in threshold voltage with time  $\Delta V_{th}(t)$ . This is simple for the case of the discrete stop-start method because we have a complete  $I_{ds}(V_{gs})$ data set. By plotting the square root of the  $I_{ds}$  in the saturation regime [1],

$$I_{ds}^{1/2} = [(W/2L) C_{ox} \mu]^{1/2} [V_{gs} - V_{th}^{o}], \qquad (4-1)$$

as a function of  $V_{gs}$  then taking the derivative, we obtain the slope of the "post threshold" region. Using slope intercept formula we can calculate  $V_{gs}$  for  $I_{ds} = 0$  which, from EQ 4-1, is equal to the threshold voltage.

Figure 4-1) Square Root of  $I_{\text{ds}}$  as a function of  $V_{\text{gs}}\text{-}$  The straight line is a guide to the eye

Translation of  $\Delta I_{ds}(t)$  into  $\Delta V_{th}(t)$  for the continuous method, where a single unique point on the  $I_{ds}(V_{gs})$  curve is captured at equal points in time, is considerably more complex than the equivalent analysis on the start-stop data set since it involves approximations. EQ 4-1 contains two parameters which can vary due to charge trapping/interface state generation, inversion channel carrier mobility  $\mu$ , and  $V_{th}$ . In order to eliminate one of these variables we examine first the situation for  $\mu$ . There are at least two reasons why the carrier mobility can change. First we consider the effect of vertical field resulting from  $V_{gs}$  [2]. Electric field dependent mobility is evidenced by FIG 4-1 where we have plotted  $(I_{ds})^{1/2}$  as a function of  $V_{gs}$ . From EQ 4-1, a plot of  $(I_{ds})^{1/2}$  versus

$V_{gs}$  should be a straight line of slope  $[(W/2L)\ C_{ox}\ \mu]^{1/2}$  and should intercept the  $V_{gs}$  axis at  $V_{th}$ . Disregarding the sub threshold behavior, the curvature at large  $V_{gs}$  is a result of electric field dependent mobility and can be expressed as [2]:

$$\mu = \mu_0 / (1 + \varphi \left[ V_{gs} - V_{th}^{\ o} - \Delta V_{th} \right])$$

(4-2)

where  $\phi$  is a constant and  $V_{th}^{\circ}$  is the threshold voltage at t=0 before the device has been subject to stressing. From EQ 4-2 it is clear that assuming the carrier mobility to be a constant in the data interpretation methodology has the potential to introduce an error depending on the magnitude of the change in  $V_{th}$  and the value of  $\phi$ . In the case of our continuous measurements, we maintain a unique set of  $V_{gs}$  and  $V_{ds}$  values, and variations in  $V_{th}$  are small with respect to  $V_{th}^{\circ}$ . As for the constant  $\phi$ , this can be deduced by fitting  $I_{ds}^{1/2}(V_{gs})$  with the full formula in EQ 4-1, including the modification of mobility term in EQ 4-2. In doing this, we determined  $\phi$  to be on the order of  $10^{-1}$ . As a result, to a first approximation it is reasonable to conclude that we can neglect electric field dependent mobility as expressed in EQ 4-2. The next step is to determine how trapped charge can modify the carrier mobility. We assume that trapped charge in the oxide, regardless of position (close to the Si/SiO<sub>2</sub> interface or in the bulk of the dielectric), can be represented by the quantity  $\Delta N_t$ . The resulting threshold voltage shift from the trapped charge can then be expressed as [3]:

$$\Delta V_{th} = -\Delta N_t \, q/C_{ox} \tag{4-3}$$

where q is the elemental charge. Given that this term modifies the threshold voltage, it changes the electric field in the vertical direction as well. The change in electron mobility as a result of trapped charge can be written as [4]:

$$\mu = \mu_0 / (1 + \alpha' \Delta N_t) \tag{4-4}$$

where  $\alpha'$  is a constant. Rearranging EQ 4-3 and substituting into EQ 4-4 yields:

$$\mu = \mu_0/(1 - \alpha' \Delta V_{th} C_{ox}/q)$$

(4–5)

Substituting EQ 4-5 into the general square law formula expressed in EQ 1-1 we arrive at the expression:

$$I_{ds} = [W/2L] \ C_{ox} \left[ \mu_o / (1 - \alpha' \ \Delta V_{th} \ C_{ox} \ / \ q \ ) \right] \left[ \{ V_{gs} - (V_{th}^{\ o} + \Delta V_{th}) \} V_{ds} - 1/2 {V_{ds}}^2 \right] \eqno(4-6)$$

This expression now contains a parameter that accounts for the modification of mobility as a result of trapped charge, and a parameter that influences the device threshold voltage. EQ 4-6 can be further simplified by removing the dependency of  $\Delta V_{th}$  from the denominator. Starting with EQ 4-5 in the form:  $\mu/\mu_0 = (1 - \Delta \mu/\mu_0) = (1 + \alpha' \Delta N_t)^{-1}$ . We can assume  $\alpha' \Delta N_t < 1$ , then by taking the series expansion we can approximate  $\Delta \mu/\mu_0$  by:

$$\Delta \mu/\mu_o \sim \alpha' \Delta N_t$$

(4-7a)

by rearranging EQs 4-3 and 4-7a we arrive at an expression whereby the parameter  $\alpha'$  can be determined from the slope of a  $\Delta V_{th}$  versus  $\Delta \mu/\mu_o$  plot:

$$\Delta V_{th} = -(q/\alpha' C_{ox}) \Delta \mu/\mu_o \tag{4-7b}$$

It has been experimentally shown that  $\alpha'$  is on the order of  $10^{\text{-}13}$  over a wide range of temperatures [5]; additionally, threshold voltage shifts relative to NBTI are typically in the range of 10's of mV. As a result, to a first approximation we can say that  $\alpha' \Delta V_{th} \, C_{ox} / q << 1$  thus we can neglect charge induced mobility in EQ 4-6. The inclusion of this approximation yields:

$$I_{ds} = [W/2L] C_{ox} \mu_o [\{V_{gs} - (V_{th}^{o} + \Delta V_{th})\} V_{ds} - 1/2 V_{ds}^{2}]$$

(4-8)

This simplified equation can be used to calculate the source-drain current after a threshold voltage shift. In addition, we know that the initial source-drain current ( $I_{ds}^{\,\,o}$ ), before accounting for any changes in characteristics, can be expressed by EQ 1-1. It is then trivial to show that by taking the ratio  $I_{ds}(t)/I_{ds}^{\,\,\,o}$ , we can obtain the expression:

$$I_{ds}/I_{ds}^{o} = (V_{gs} - V_{th}^{o} - \Delta V_{th} - 1/2V_{ds}) / (V_{gs} - V_{th}^{o} - 1/2V_{ds})$$

(4-9)

re-arranging:

$$\Delta V_{th} = [V_{gs} - V_{th}^{o} - 1/2V_{ds}](1 - I_{ds}/I_{ds}^{o})$$

(4-10)

This expression holds for the case that  $|V_{ds}| < |V_{gs} - V_{th}|$  corresponding the linear region of transistor operation [6]. For the case of the saturation regime ( $|V_{ds}| \ge |V_{gs} - V_{th}|$ ), we simply replace  $V_{ds}$  with  $(V_{gs} - V_{th})$  [6]. Note that this could also be accomplished by starting from the saturation current law, normalizing, and then solving the quadratic which yields:

$$\Delta V_{th} = -\left(V_{gs} - V_{th}^{o}\right) \ \pm \ \left[2(V_{gs} - V_{th}^{o})^{2} - 4(V_{gs} - V_{th}^{o})^{2} \left(1 - I_{ds}/I_{ds}^{o}\right)\right]^{1/2} / 2 \ (4-11)$$

Both equations, 4-10 and 4-11, are equivalent as they relate to the analysis of a device that has been stressed in the saturation regime; however, EQ 4-11 is not valid for the linear region.

The final obstacle to overcome with this interpretation methodology was acquiring an accurate value for  $I_{ds}{}^{o}$ . This challenge was a result of the characterization equipment whereby the stressing voltage was applied to the gate for 1-2 seconds before we recorded our first data point. Because this method uses a normalization technique, it hinges on an accurate initial value. To accomplish this we extrapolate the initial linear part of the  $I_{ds}(t)$  back to the origin and take that value to be  $I_{ds}{}^{o}$ .

#### 4.2 Full Curve Fit Vs Single Point Approximation

In the previous section we examined/justified the approximations required to translate  $\Delta I_{ds}(t)$  in to  $\Delta V_{th}(t)$  from the single point continuous stress method. We now take a look at experimental data from the HfSiON technology to gain a feeling for the amount of

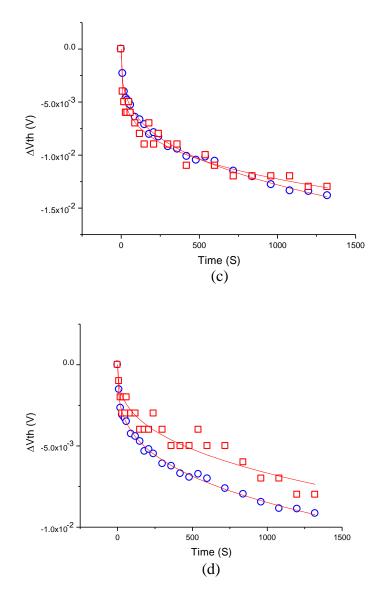

error induced by these approximations. The approach for this experiment was to extract a threshold voltage shift from a complete start-stop data set with two techniques: 1) using the complete  $I_{ds}(V_{gs})$  characteristic curve and extracting the threshold voltage using standard methods discussed above. 2) Using a unique  $I_{ds}$  value obtained from a complete  $I_{ds}(V_{gs})$  plot at the point  $V_{gs} = V_{bias}$ ,  $V_{ds} = -2V$ , then applying EQ 4-10. The result of this is  $\Delta V_{th}(t)$  plots from the same data set; the first case being the most accurate. FIG 4-2 shows the result of this analysis at 4 different gate voltages and a temperature of 175C.

Figure 4-2) Example of  $V_{th}(t)$  extracted from the start-stop method using two techniques; taking one unique point on the curve,  $I_{ds}(V_{bias})$ , then applying EQ 4-10 (O), using the complete characteristic curve then applying standard methods ( $\square$ ). Results are shown for  $V_{bis}$  of a)-2.0V, b) -1.7V, c) V-1.5V, and d)-1.3V . T=175C in all cases. Solid lines represent non-linear curve fit using  $\Delta V_{th} = At^{\alpha}$ .

Most importantly, this experiment confirmed that our approximations from EQ 4-10 are reasonably accurate within experimental error over a wide range of gate voltages. This was determined by fitting the data to a simple  $At^{\alpha}$  power law then comparing the fit parameters A and  $\alpha$ . The solid lines in FIG 4-2 are the result of the power law fit.

Clearly, the quality of this fit is affected by the value of  $V_{gs}$  and in general this analysis technique is very approximate. In the subsequent section we will show that assuming  $\Delta V_{th} = At^{\alpha}$  is not accurate for all time domain. In TABLE 4-1 we summarize the A and  $\alpha$  fit parameters for the approximate and exact determination of  $V_{th}$ . We conclude that our margin of error is < 5% for the stressing conditions of interest. Further analysis of FIG 4-2 raises some interesting questions; in particular, it is not yet clear whether the observed systematic variation between the two methods is a result of the approximations, or a consequence of the physical mechanisms involved. It is clear that our approximation results in a slight underestimation of the threshold voltage shift at large values of  $V_{gs}$  and a slight overestimation of the effect at small values  $V_{gs}$ . Consequently, even in the case of our continuous method, which was intended to capture the maximum effect, we still would underestimate the device reliability lifetime. It is because of this that the demand for rapid data acquisition systems has arisen. With these systems we could potentially eliminate approximations involved in our data interpretation methodology.

| $V_{gs}\left( V ight)$ | A <sub>start-stop</sub> APPROX | <b>α</b> <sub>start-stop</sub> APPROX | $A_{\it start-stop}$ FIT | <b>α</b> <sub>start-stop</sub> FIT |

|------------------------|--------------------------------|---------------------------------------|--------------------------|------------------------------------|

| -2.0                   | -0.0071                        | .21                                   | -0.0088                  | .20                                |

| -1.7                   | -0.0038                        | .23                                   | -0.0036                  | .24                                |

| -1.5                   | -0.0026                        | .24                                   | -0.0034                  | .24                                |

| -1.3                   | -0.0010                        | .31                                   | -0.0006                  | .36                                |

Table 4-1)  $\alpha$  values deduced from  $\Delta V_{th} = At^{\alpha}$  fits. Two methods were invoked; the start-stop method with translation into  $V_{th}$  minding approximations using EQ 4-10, and the start-stop method with exact determination of  $V_{th}$  from the full  $I_{ds}(V_{gs})$  curve.

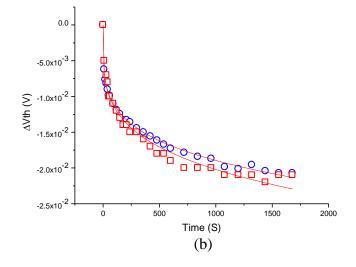

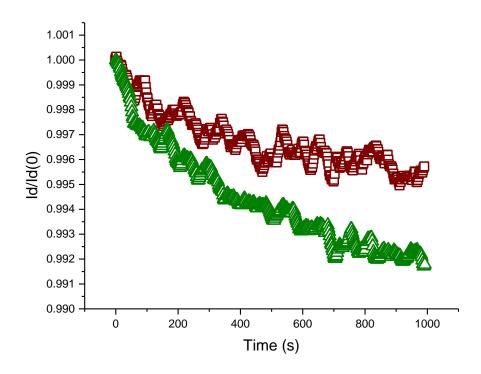

### 4.3 The Start-stop Method Vs The Continuous Method

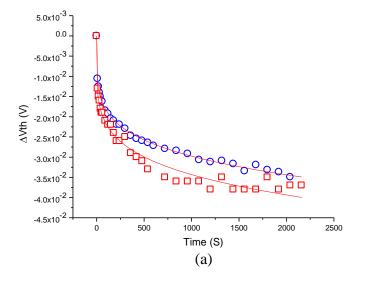

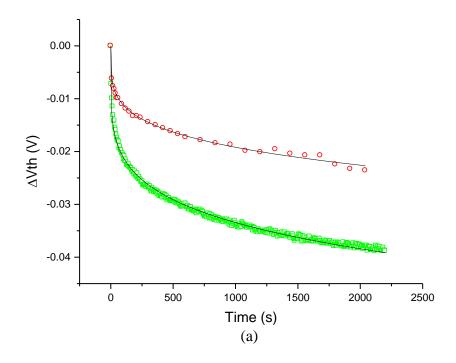

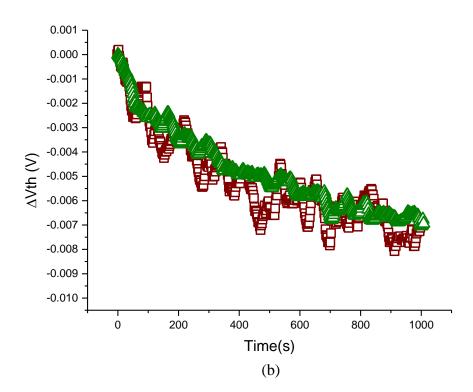

The traditional measurement techniques did not take into account parametric changes that are more rapid than we can measure. In our experiments, we invoked both start-stop, and continuous measurement methods to better visualize the shortcomings of the traditional techniques. In FIG 4-3 we show a typical result of these experiments. In this particular case, two HfSiON 1 µm p-channel MOSFETs were subjected to the following stress conditions: V<sub>gs</sub>=-2.0V, V<sub>ds</sub>=-1.7V, and T=175C. Here the start-stop curve (red circles), and continuous stress curve (green squares), are represented on a plot of threshold voltage change as a function of time ( $\Delta V_{th}(t)$ ). As expected, analysis of the  $\Delta V_{th}(t)$  curves reveals a dramatic difference in the magnitude of the measured effect dependent upon the measurement method. This is a consequence of charge relaxation during the 3-5 seconds it takes to acquire the  $I_{ds}(V_{gs})$  characteristics in the start-stop experiment. The continuous technique avoids this issue by virtue of the continuous stressing voltage on the gate. In both cases, the data appears to be well fit by a simple power law which was a typical means for interpreting these NBTI degradation curves [7]. The solid black lines in FIG 4-3 are the  $At^{\alpha}$  fits to the data.

Figure 4-3) a) Comparison of  $\Delta V_{th}(t)$  for the Continuous Stress Method ( $\Box$ ) and the Start-Stop Method (O). These measurements were performed on devices stressed at -1.7V on the gate and at a Temperature of 175C. b) At $^{\alpha}$  fit to continuous ( $\Box$ ) and start-stop (O),  $\Delta V_{th}(t)$  measurements extrapolated out to  $\Delta V_{th}/V_{th}{}^{o}$  = 0.1 (dotted line)

Most of the early modeling attempts, primarily the Reaction Diffusion Model [8], predicted that NBTI induced threshold voltage shifts follow an  $At^{\alpha}$  time dependence. This aspect of RD theory continues to be widely accepted among the NBTI community because it explains most "traditional" stress/measure/stress data. However, the results of our continuous stress measurements have made it clear that  $At^{\alpha}$  fails to explain the behavior in the early time domain. FIG 4-3b reveals that sub 100s, the continuous curve (green squares) exhibits a clear deviation from the power law. Note that this is accentuated in a log plot but could easily be overlooked on a linear plot. In summary, while a simple power law fit is useful for comparing the behavior of devices at long times, it does not accurately represent the true physical mechanisms involved, certainly at short time. As a result, we have begun to explore the possibility of an initial 'fast' mechanism that is overtaken by a slower mechanism at long times. This effect was not previously observed because it was masked by the inadequacies of typical  $\Delta V_{th}(t)$  measurements. In Chapter 5 we will discuss this theory in more detail.

FIG 4-3b is of particular interest in relation to building a reliable lifetime predictor formula because it reveals the importance of choosing an accurate data interpretation/collection methodology. The dotted line in this figure is at  $|\Delta V_{th}/V_{th}{}^{o}| = 0.1$  corresponding lifetime definition of 10% variation in threshold voltage. Extrapolation of the power law fits out to  $|\Delta V_{th}/V_{th}{}^{o}| = 0.1$  exposes the magnitude of error that can be achieved as a result of the measurement technique adopted. In this particular example, the continuous curve reaches 10% loss in  $V_{th}$  at ~7500s. Conversely, it takes the start-stop curve ~58500s to reach the same level! This corresponds to 2 and 16 hours respectively or a factor of 8 difference between the two methods. The mean time to failure in these

experiments may sound surprising at first but it is important to remember that we have accelerated the physical mechanisms by application of a large vertical field and high operation temperature. There is however, no reason to believe that these results would not scale to realistic operating conditions thus it is imperative to understand the characteristics of the measurements before making any predictions about the lifetime of a circuit.

## **4.4** Temperature Dependence

Understanding the time and magnitude dependence of  $\Delta V_{th}$  on temperature is critical when developing a model of the physical mechanisms in NBTI. Over the course of this study, we performed a large number of temperature dependence experiments on a variety of different technologies. As expected, the magnitude of threshold voltage degradation in the HfSiON technologies was significantly greater than that of the simple  $SiO_2$  devices. This is generally accepted to be the result of a higher defect density in the high-  $\kappa$  dielectric. An additional observation is the fact that each technology we tested had its own unique time dependence on temperature. It is clearly evident that the mechanisms involved in NBTI are strongly dependent on the gate dielectric processing steps making a generic reliability lifetime formula very complicated.

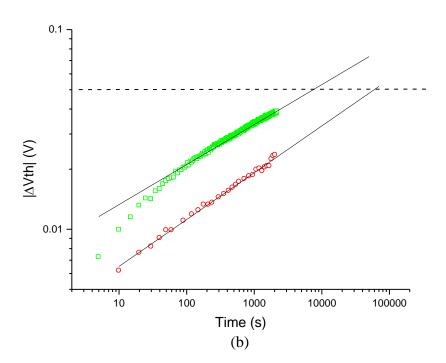

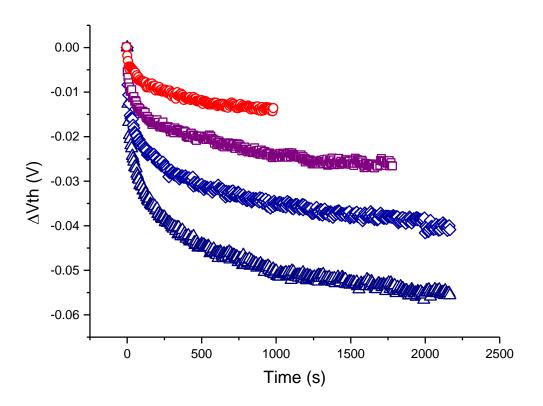

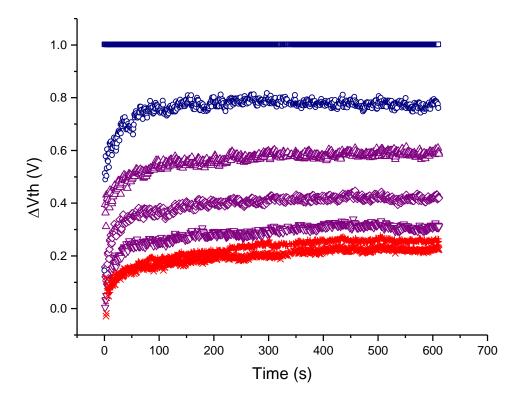

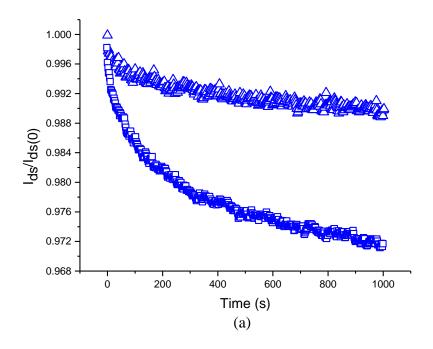

In FIG 4-4 we show the results from one of our first temperature dependence experiments. In this experiment we performed on-the-fly (OTF) continuous stress measurements at three temperatures; 95C, 125C, and 155C, while maintaining  $V_{gs}$  and  $V_{ds}$  at -1.5V and -0.9V respectively. Bearing in mind the limitations discussed previously, we subsequently fitted the data to the simple  $\Delta V_{th}$ =At $^{\alpha}$  power law from which we were

able to deduce  $\alpha(95C)=0.182$ ,  $\alpha(125C)=0.189$ , and  $\alpha(155C)=0.187$ . Clearly we observed magnitude dependence in the direction of increasing degradation with increasing temperature. However, there did not appear to be a time dependence on temperature associated with this effect.

Figure 4-4) Threshold voltage shifts resulting from NBTI as determined from continuous bias method for T=95C ( $\Delta$ ), T=125C ( $\Box$ ), T=155C (O). Gate dielectric stack was high- $\kappa$  HfSiON

The curves represented in Fig 4-4 have been fitted to an  $At^{\alpha}$  power law. Above we deduced the  $\alpha$  fitting parameter at each stressing condition which revealed no time dependence on temperature in the HfSiON samples. Secondly, we examined the prefactor

A. This prefactor contains a temperature activated term which is assumed by the RD model to be [8]:

$$\Delta V_{th} = A_0 e^{-E_A/kT} t^{\alpha} \tag{4-12}$$

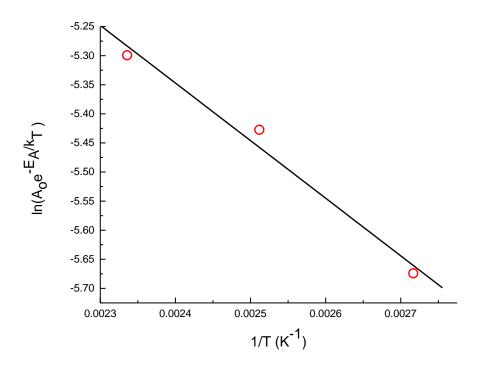

thus A  $\propto A_0 e^{-E_A/kT}$ . Consequently, a plot of the natural logarithm of the experimentally determined prefactor as a function of 1/T will yield the activation energy of the mechanism. In FIG 4-5 we show  $\ln(A_0 e^{-E_A/kT})$  vs 1/T. Linear fitting yields  $E_A$ =0.085±0.012 eV.

Figure 4-5)  $\ln(A_0 e^{-E_A/kT})$  vs 1/T plotted using the prefactor fitting parameter from the data shown in FIG 4-4

Given that we have deduced the activation energy of the mechanism as well as the time dependence, it is now possible to determine the "real" lifetimes at normal operation

Extrapolating the power law fits to the data at 155C out to  $|\Delta V_{th}/V_{th}| \sim 0.1$ , we conclude that the device  $V_{th}$  will vary by 10% in 3.43 days **under accelerated conditions**. Because we have determined the activation energy, we can take the ratio of the exponentials in EQ 4-12 and deduce a multiplying factor for the reliability lifetime at normal operating temperatures. Accordingly, we determined at 80 C, normal operation temperature, the HfSiON devices  $V_{th}$  will shift by 10% in 68.6 days. Note that this is the life time under normal operation temperatures; however, it is still accelerated by the magnitude of the gate voltage and the fact that we maintain the stress continuously throughout the experiment. Under normal circuit operation, one would expect a finite amount of "down time" in which the trapped charge would relax thus lengthening the lifetime. Taking into account factors such as this, make the development of a generic lifetime predictor formula very complex.

#### 4.5 Dependence on the Vertical and Lateral Electric Fields

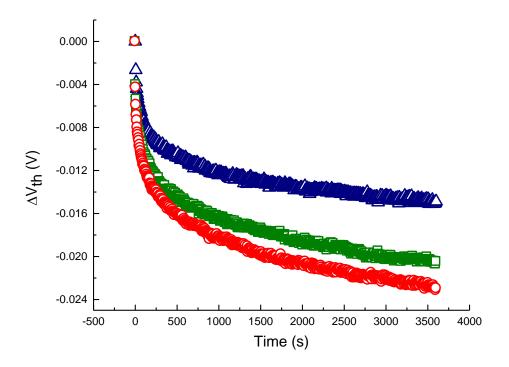

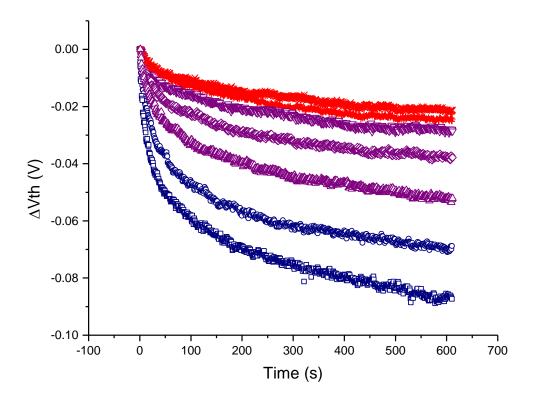

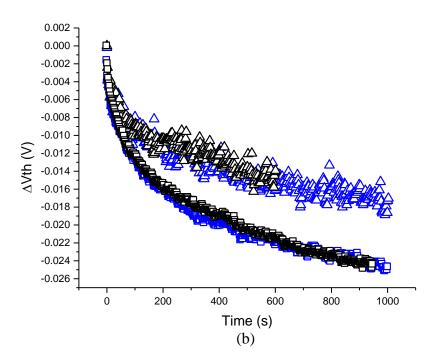

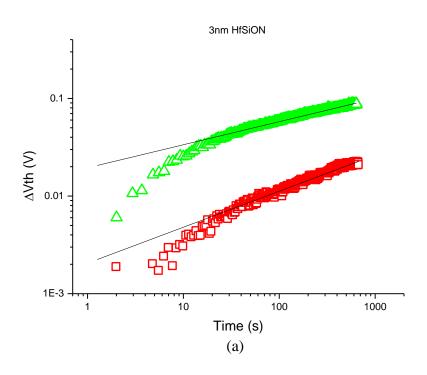

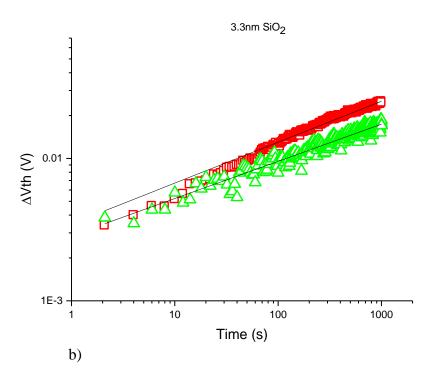

It is well know that the vertical electric field is responsible for triggering the degradation mechanisms involved in NBTI. In our experiments we explored the time and magnitude dependencies on the vertical electric field across the oxide, and lateral electric field across the carrier channel. In the first instance we examined the effect of vertical field on our HfSiON samples. In these experiments devices were stressed at one of the following unique gate voltages; -2.0V, -1.7V, -1.5V and -1.3V. The temperature was maintained at 175C and  $V_{ds}$ =-2.0V. As in the previous experiments, continuous current measurements were performed using the technique described in Chapter 3, then

subsequently translated into threshold voltage shifts via EQ 4-11. The  $\Delta V_{th}(t)$  curves in FIG 4-6 were measured on 1µm channel devices. We observed threshold voltage shifts of the order of 10mV at 1000s for devices stressed with -1.3V on the gate (circles). Comparatively, devices stressed with -2.0V on the gate (triangles) exhibited threshold voltage shifts of the order of 50mV at 1000s. We believe the resulting 5x increase in device degradation from -1.3V to -2.0V is a consequence of the stronger vertical electric field accelerating the charge creation/trapping mechanisms associated with NBTI. In chapter 5 we will discuss trap charging kinetics.

Figure 4-6) HfSiON threshold voltage shifts with time at T=175C and  $V_{gs}=$  -2.0V ( $\Delta$ ),  $V_{gs}=$  -1.7V ( $\Diamond$ ),  $V_{gs}=$  -1.5V ( $\Box$ ), and  $V_{gs}=$  -1.3V ( $\bigcirc$ ). The curves can be fitted to the formula  $\Delta V_{th}=At^{\alpha}$ . The fitted parameters A and  $\alpha$  are shown in TABLE 4-2.

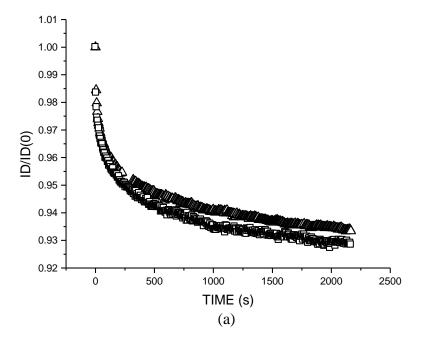

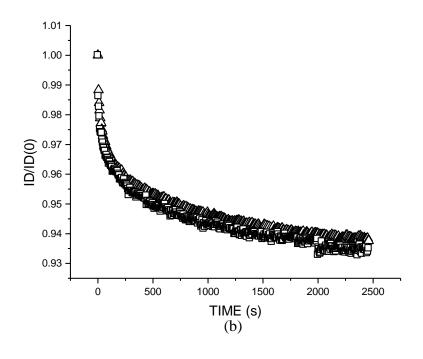

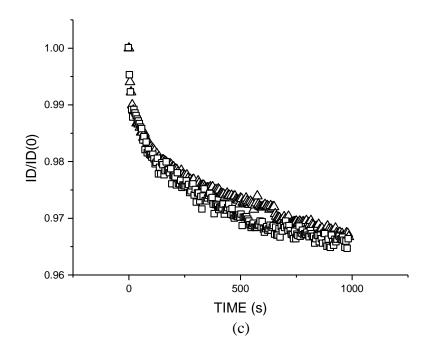

The next challenge was to examine the behavior under different electric fields in the lateral sense. Fortunately we had the luxury of many different technology nodes on our HfSiON wafers. This enabled our first experiment which was to increase the device channel length from 1µm to 10µm without increasing the drain voltage. Consequently, the lateral electric field across the inversion channel, and the source-drain current were reduced by an order of magnitude. There was no correlation to a change in threshold voltage as seen in FIG 4-7 evidencing the fact that the physical mechanisms responsible for NBTI are unaffected by the magnitude of the source-drain current, length of the channel, or the lateral electric field. In hindsight, this result was not as surprising as initially thought, given that the effect is believed to be a result of the creation of interface states compounded with a faster hole trapping mechanism; neither of which should be constrained by the density of charge in the inversion channel or the electric field in the lateral sense.

Figure 4-7) Ratio of the source-drain current to the initial source-drain current at t=0 for  $10\mu m~(\triangle)$  and  $1\mu m~(\Box)$  technology nodes at bias voltage of a) -2.0V, b) -1.7V, and c) -1.3V