# University of New Mexico UNM Digital Repository

**Electrical and Computer Engineering ETDs**

**Engineering ETDs**

9-12-2014

# Within-Die Delay Variation Measurement And Analysis For Emerging Technologies Using An Embedded Test Structure

fareena saqib

Follow this and additional works at: https://digitalrepository.unm.edu/ece etds

#### Recommended Citation

saqib, fareena. "Within-Die Delay Variation Measurement And Analysis For Emerging Technologies Using An Embedded Test Structure." (2014). https://digitalrepository.unm.edu/ece\_etds/225

This Dissertation is brought to you for free and open access by the Engineering ETDs at UNM Digital Repository. It has been accepted for inclusion in Electrical and Computer Engineering ETDs by an authorized administrator of UNM Digital Repository. For more information, please contact disc@unm.edu.

| Fareena Saqib Candidate                                                                  |

|------------------------------------------------------------------------------------------|

| Electrical & Computer Engineering  Department                                            |

| This dissertation is approved, and it is acceptable in quality and form for publication: |

| Approved by the Dissertation Committee:                                                  |

| Dr. James F. Plusquellic, Chairperson                                                    |

| Dr. Nasir Ghani                                                                          |

| Dr. Payman Zarkesh-Ha                                                                    |

| Dr. Charles Lamech                                                                       |

## Within-Die Delay Variation Measurement And Analysis For Emerging Technologies Using An Embedded Test Structure

by

#### Fareena Saqib

B.I.T., National University of Sciences and Technology (NUST), 2006 M.S., Electrical and Computer Engineering, University of New Mexico (UNM), 2010

#### **DISSERTATION**

Submitted in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy Engineering

The University of New Mexico

Albuquerque, New Mexico

July, 2014

©2014, Fareena Saqib

## Dedication

This dissertation is dedicated to my family, for all the love, support, and the many sacrifices made.

## Acknowledgments

First of all I wish to offer my gratitude to Almighty God for the Blessings bestowed upon me.

I would like to express my sincerest gratitude and indebtedness to my advisor and supervisor Dr. Jim Plusquellic for his untiring assistance, timely guidance, encouragement and creativity at every stage of this study. Working with him has been a true privilege, and I have benefited tremendously from his knowledge of science and engineering, both in depth and broadness, and his enthusiasm in supporting me to carry out and complete the research work. He is a role model that I can always look up to.

My deepest appreciation and thanks are extended to Dr. Nasir Ghani, Dr. Charles Lamech, and Dr. Payman Zarkesh-Ha for their continuous support, encouragement and valuable suggestions. I am also grateful to all the group members in the Electrical and Computer Engineering Department at the University of New Mexico for their assistance, motivation and valuable comments to improve the dissertation. I am especially grateful to Jim Aarestad for his dedicated assistance, guidance and professional contributions.

## Within-Die Delay Variation Measurement And Analysis For Emerging Technologies Using An Embedded Test Structure

by

#### Fareena Saqib

B.I.T., National University of Sciences and Technology (NUST), 2006 M.S., Electrical and Computer Engineering, University of New Mexico (UNM), 2010

Ph.D., Engineering, University of New Mexico (UNM), 2014

#### **ABSTRACT**

Both random and systematic within-die process variations (PV) are growing more severe with shrinking geometries and increasing die size. Escalation in the variations in delay and power with reductions in feature size places higher demands on the accuracy of variation models. Their availability can be used to improve yield, and the corresponding profitability and product quality of the fabricated integrated circuits (ICs). Sources of within-die variations include optical source limitations, and layout-based systematic effects (pitch, line-width variability, and microscopic etch loading). Unfortunately, accurate models of within-die PVs are becoming more difficult to derive because of their increasingly sensitivity to design-context. Embedded test structures (ETS) continue to

play an important role in the development of models of PVs and as a mechanism to improve correlations between hardware and models. Variations in path delays are increasing with scaling, and are increasingly affected by "neighborhood" interactions. In order to fully characterize within-die variations, delays must be measured in the context of actual core-logic macros. Doing so requires the use of an embedded test structure, as opposed to traditional scribe line test structures such as ring oscillators (RO). Accurate measurements of within-die variations can be used, e.g., to better tune models to actual hardware (model-to-hardware correlations).

In this research project, I propose an embedded test structure called REBEL (Regional dELay BEhavior) that is designed to measure path delays in a minimally invasive fashion; and its architecture measures the path delays more accurately. Design for manufacture-ability (DFM) analysis is done on the on 90 nm ASIC chips and 28nm Zynq 7000 series FPGA boards. I present ASIC results on within-die path delay variations in a floating-point unit (FPU) fabricated in IBM's 90 nm technology, with 5 pipeline stages, used as a test vehicle in chip experiments carried out at nine different temperature/voltage (TV) corners. Also experimental data has been analyzed for path delay variations in short vs long paths. FPGA results on within-die variation and die-todie variations on Advanced Encryption System (AES) using single pipelined stage are also presented. Other analysis that have been performed on the calibrated path delays are Flip Flop propagation delays for both rising and falling edge (tpHL and tpLH), uncertainty analysis, path distribution analysis, short versus long path variations and midlength path within-die variation. I also analyze the impact on delay when the chips are subjected to industrial-level temperature and voltage variations. From the experimental

results, it has been established that the proposed REBEL provides capabilities similar to an off-chip logic analyzer, i.e., it is able to capture the temporal behavior of the signal over time, including any static and dynamic hazards that may occur on the tested path. The ASIC results further show that path delays are correlated to the launch-capture (LC) interval used to time them. Therefore, calibration as proposed in this work must be carried out in order to obtain an accurate analysis of within-die variations. Results on ASIC chips show that short paths can vary up to 35% on average, while long paths vary up to 20% at nominal temperature and voltage. A similar trend occurs for within-die variations of mid-length paths where magnitudes reduced to 20% and 5%, respectively. The magnitude of delay variations in both these analyses increase as temperature and voltage are changed to increase performance. The high level of within-die delay variations are undesirable from a design perspective, but they represent a rich source of entropy for applications that make use of "secrets" such as authentication, hardware metering and encryption. Physical unclonable functions (PUFs) are a class of primitives that leverage within-die-variations as a means of generating random bit strings for these types of applications, including hardware security and trust.

Zynq FPGAs Die-to-Die and within-die variation study shows that on average there is 5% of within-Die variation and the range of die-to-Die variation can go upto 3ns. The die-to-Die variations can be explored in much further detail to study the variations spatial dependance.

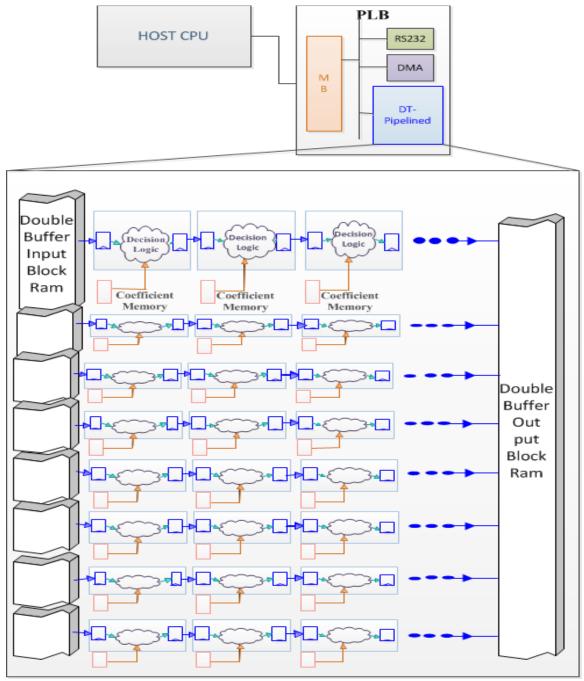

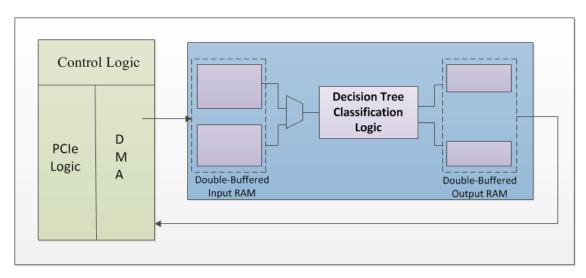

Additionally, I also carried out research in the area data mining to cater for big data by focusing the work on decision tree classification (DTC) to speed-up the classification step in hardware implementation. For this purpose, I devised a pipelined

architecture for the implementation of axis parallel binary decision tree classification for meeting up with the requirements of execution time and minimal resource usage in terms of area. The motivation for this work is that analyzing larger data-sets have created abundant opportunities for algorithmic and architectural developments, and data-mining innovations, thus creating a great demand for faster execution of these algorithms, leading towards improving execution time and resource utilization. Decision trees (DT) have since been implemented in software programs. Though, the software implementation of DTC is highly accurate, the execution times and the resource utilization still require improvement to meet the computational demands in the ever growing industry. On the other hand, hardware implementation of DT has not been thoroughly investigated or reported in detail. Therefore, I propose a hardware acceleration of pipelined architecture that incorporates the parallel approach in acquiring the data by having parallel engines working on different partitions of data independently. Also, each engine is processing the data in a pipelined fashion to utilize the resources more efficiently and reduce the time for processing all the data records/tuples. Experimental results show that our proposed hardware acceleration of classification algorithms has increased throughput, by reducing the number of clock cycles required to process the data and generate the results, and it requires minimal resources hence it is area efficient. This architecture also enables algorithms to scale with increasingly large and complex data sets. We developed the DTC algorithm in detail and explored techniques for adapting it to a hardware implementation successfully. This system is 3.5 times faster than the existing hardware implementation of classification.

## **Table of Contents**

| LIST OF FIGURES                                             | XIV   |

|-------------------------------------------------------------|-------|

| LIST OF TABLES                                              | XVIII |

| 1 INTRODUCTION                                              | 1     |

| 1.1 Sources of Within-Die Variations                        | 2     |

| 1.2 Proposed Embedded Test Structure (ETS)                  | 2     |

| 1.3 Decision Tree Classification (DTC)                      | 3     |

| 1.4 Organization                                            | 4     |

| 2 BACKGROUND                                                | 5     |

| 2.1 Test Structures for Within-Die Delay Measurement        | 5     |

| 2.1.1 Delay Measurements of Individual Gates                | 8     |

| 2.2 Design and Environment Effects on Within-Die Variations | 9     |

| 2.3 Within-Die Variations in FPGAs Reconfigurable Logic     | 10    |

| 2.4 Impact of Within-Die Spatial Process Variations         | 11    |

| 2.4.1 Clock Frequency                                       | 11    |

| 2.5 Static Timing Analysis                                  | 12    |

| 2.6 Design for Manufacturing and Yield                      | 12    |

| 2.7 Applications of Die-to-Die and Within-Die Variations    | 14    |

| 2.7.1 PUF Hardware Security                                 | 14    |

| 2.8 Summary                                              | 20  |

|----------------------------------------------------------|-----|

| 3 REBEL:EMBEDDED TEST STRUCTURE AND MACROS-UNDER-TEST    | .22 |

| 3.1 REBEL-Regional Delay Behavior                        | .22 |

| 3.2 Floating Point Unit (FPU Macro)                      | 28  |

| 3.3 Advance Encryption Standard (AES)                    | .31 |

| 3.3.1 Step1: Sub-Bytes                                   | 33  |

| 3.3.2 Step2: Shift Rows                                  | .33 |

| 3.3.3 Step 3:Mixed Columns                               | 34  |

| 3.3.4 Step 4: Add Round Key                              | .34 |

| 3.4 Chip Layout, with REBEL, AES and FPU Placement       | .35 |

| 3.4.1 ASIC Layout with REBEL and FPU                     | 35  |

| 3.4.2 FPGA Layout with REBEL and AES Round               | .37 |

| 4 EXPERIMENTAL SETUP                                     | .38 |

| 4.1 Experimental Setup for IC 90nm Chips                 | 38  |

| 4.2 Launch-Capture Clocking Sequence and Clock Strobing  | 39  |

| 4.2.1 Launch-Capture Clocking Sequence                   | 39  |

| 4.2.2 Clock Strobing                                     | 39  |

| 4.3 Delay Measurement Process                            | .40 |

| 4.4 Digital Snapshots and FF Delays                      | .43 |

| 4.5 Calibration and Power Rail Voltage Transient Effects | .44 |

| 4.6 Measuring and Calibrating Path Delays                | .48 |

| 4.7 Experimental Setup for FPGA Boards                   | 52  |

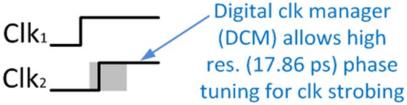

| 4.8 Launch-Capture Clocking Sequence and Clock Strobing  | 53  |

| 4.8.1 Launch-capture Clocking Sequence                               | 53 |

|----------------------------------------------------------------------|----|

| 4.8.2 Clock Strobing                                                 | 54 |

| 4.9 Delay Measurement Process                                        | 54 |

| 4.10 Measuring and Calibrating Path Delays                           | 56 |

| 5 ASIC EXPERIMENTAL RESULTS AND ANALYSIS                             | 58 |

| 5.1 Flip-flops Analysis                                              | 58 |

| 5.2 Uncertainty Analysis                                             | 62 |

| 5.3 Error in Estimating Path Delays                                  | 64 |

| 5.4 Path Distribution Analysis                                       | 67 |

| 5.5 Short vs. Long Path Variation                                    | 69 |

| 5.6 Within-Die Delay Variation Analysis                              | 71 |

| 6 FPGA EXPERIMENTAL RESULTS AND ANALYSIS                             | 75 |

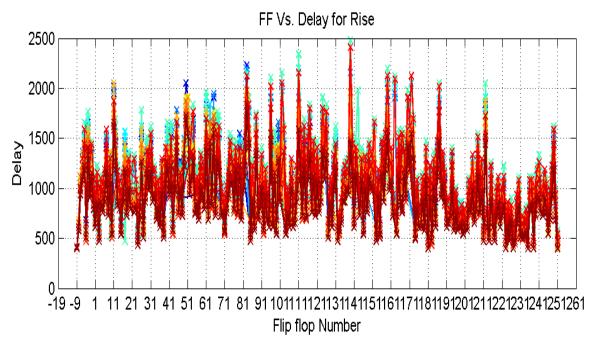

| 6.1 Flip Flop Analysis                                               | 75 |

| 6.1.1 Propagational delay tpHL and tpLH Analysis                     | 75 |

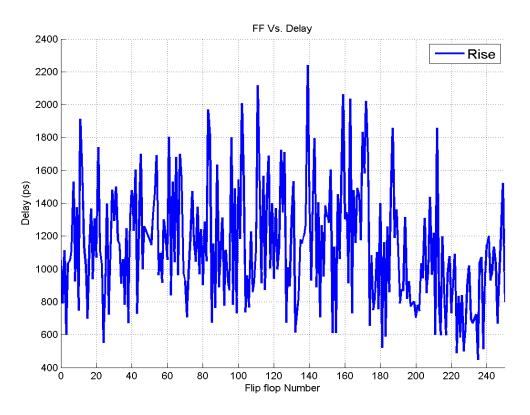

| 6.1.1.1 Rising Edge Propagation Delay (tpLH):                        | 76 |

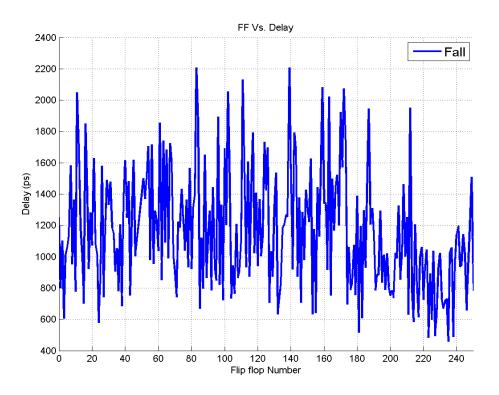

| 6.1.1.2 Falling Edge Propagation Delay (tpHL):                       | 77 |

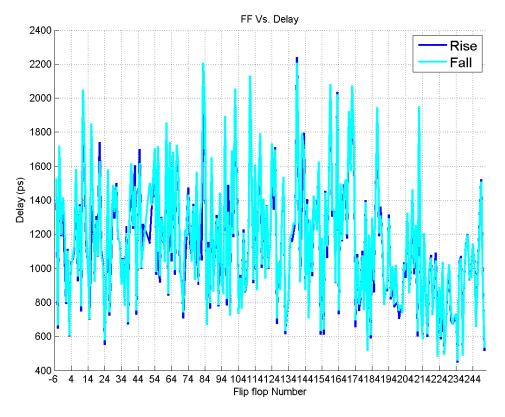

| 6.1.1.3 Comparative Analysis:                                        | 78 |

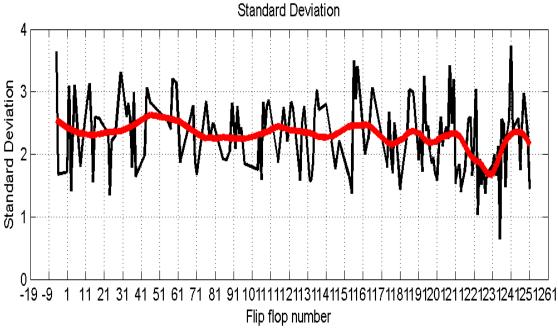

| 6.1.2 Average Rising Edge Flip-flops Delays                          | 79 |

| 6.1.3 Average Falling Edge Flip-flops Delays                         | 80 |

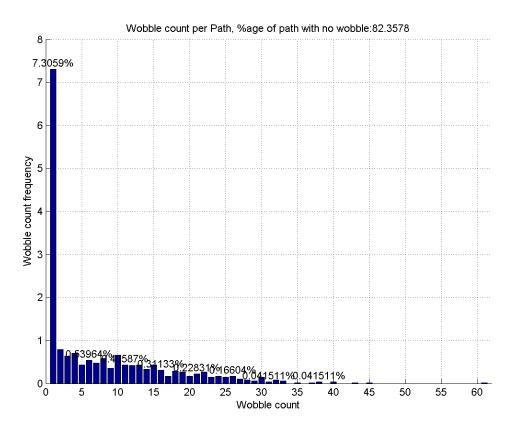

| 6.2 Sample analysis                                                  | 80 |

| 6.3 Uncertainty Analysis                                             | 85 |

| 6.4 Die-to-Die Variation in Flip-flops for Rising Edge in All Chips  | 86 |

| 6.5 Die-to-Die Variation in Flip-flops for Falling Edge in All Chips | 89 |

| 6.6 Path Distribution Analysis                                        | .91 |

|-----------------------------------------------------------------------|-----|

| 6.7 Die-to-Die Delay Variation Analysis                               | .94 |

| 6.8 Within-Die Delay Variation Analysis                               | .96 |

| 7 PIPELINED DECISION TREE IMPLEMENTATION                              | 00  |

| 7.1 Introduction1                                                     | 01  |

| 7.2 Background1                                                       | 04  |

| 7.3 Decision Tree Classification Architecture                         | 06  |

| 7.4 Experimental Results                                              | 115 |

| 7.4.1 Accuracy Of The Model                                           | 115 |

| 7.4.2 Comparison with Software Implementations                        | 16  |

| 7.4.3 Comparison with Previous Hardware Implementation                | 18  |

| 7.5 Resource Utilization                                              | 19  |

| 7.6 Data Streaming with High Performance Communication Link1          | 20  |

| 8 CONCLUSION                                                          | 23  |

| 9 FUTURE WORK                                                         | 27  |

| 9.1 Path Delay Measurement using TDCs1                                | 27  |

| 9.2 Path Delay Measurement as an Entropy Source for PUF Primitive1    | 29  |

| 9.3 Defect Analysis1                                                  | 31  |

| 9.4 Model to Hardware Correlation1                                    | 31  |

| 9.5 On-chip Clock using DLLs or PLLs and Bypass Capacitance on I/OPac | ds  |

| 13                                                                    | 32  |

| REFERENCES                                                            | 33  |

# **List of Figures**

| Fig. 3.1: REBEL Integration Strategy                                                 | 24   |

|--------------------------------------------------------------------------------------|------|

| Fig. 3.2: REBEL Row Control Logic                                                    | 25   |

| Fig. 3.3(a): Modified Clocked-LSSD Scan FF                                           | 27   |

| Fig. 3.3(b): Additional 'Front-End' Logic                                            | 27   |

| Fig. 3.4: Floating Point Unit Block Diagram                                          | 28   |

| Fig. 3.5: AES Engine.                                                                | 31   |

| Fig. 3.6: Mux-D Flip Flop.                                                           | 32   |

| Fig. 3.7: AES Round.                                                                 | 33   |

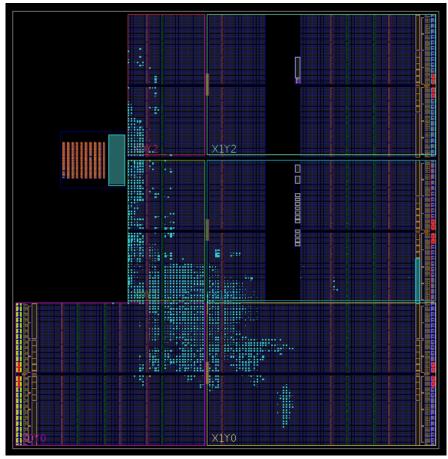

| Fig. 3.8: ASIC Layout                                                                | 35   |

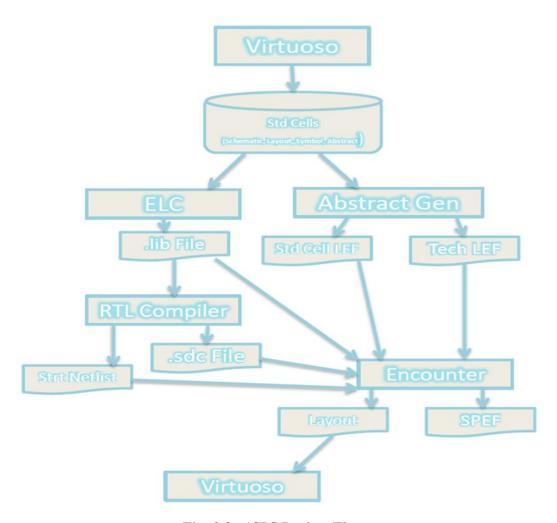

| Fig. 3.9: ASIC Design Flow.                                                          | 36   |

| Fig. 3.10: FPGA Layout                                                               | 37   |

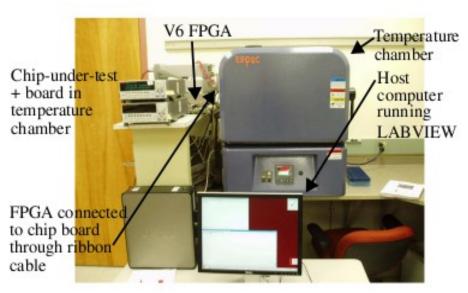

| Fig. 4.1: Experimental Setup                                                         | 39   |

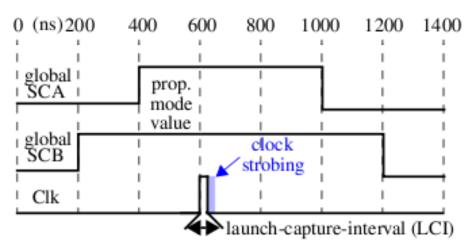

| Fig. 4.2: REBEL Launch-Capture (LC) Test Sequence. Clock strobing applies a          |      |

| sequence of LCIs of different widths                                                 | 40   |

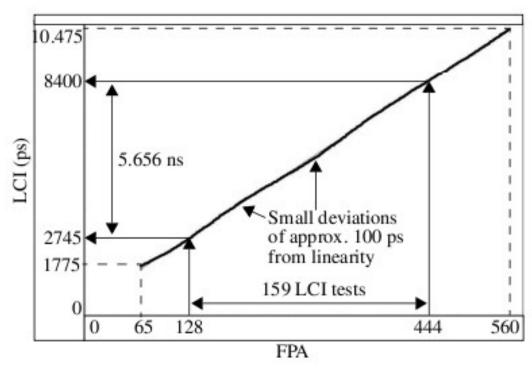

| Fig. 4.3: Oscilloscope measured launch-capture intervals (LCIs) for each of the F    | Fine |

| Phase Adjust (FPA) values on the FPGA. Row Header delay of 300 ps i                  | İS   |

| included                                                                             | 42   |

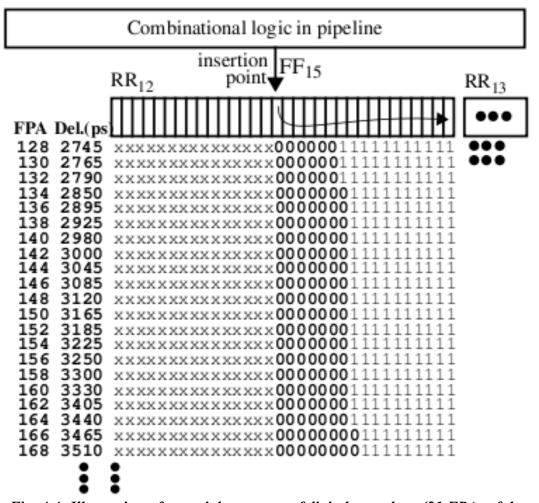

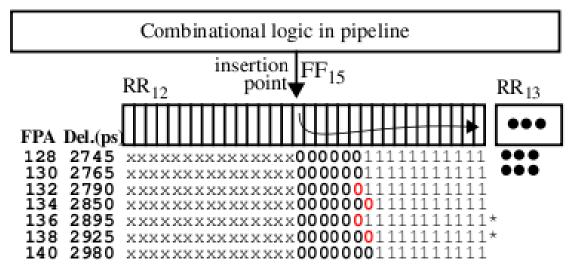

| Fig. 4.4: Illustration of a partial sequence of digital snapshots (21 FPAs of the 15 | 9)   |

| produced from a path delay test44                                                                          |

|------------------------------------------------------------------------------------------------------------|

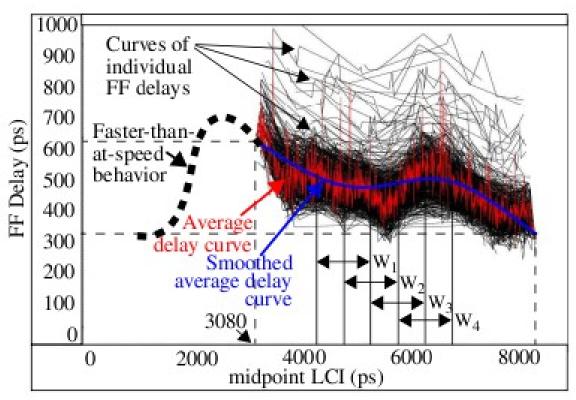

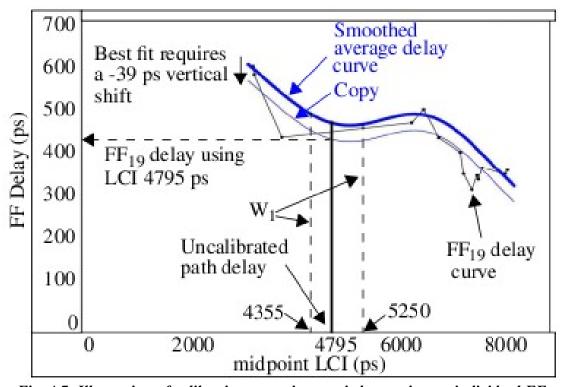

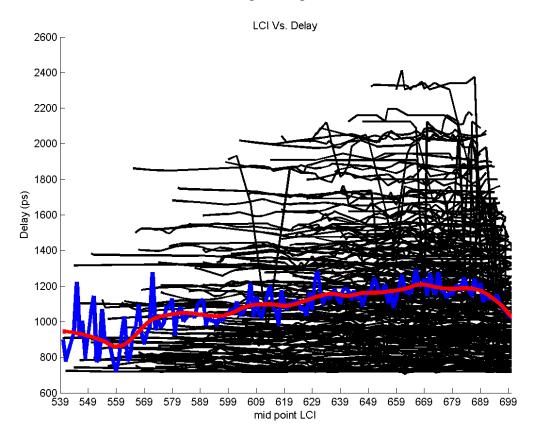

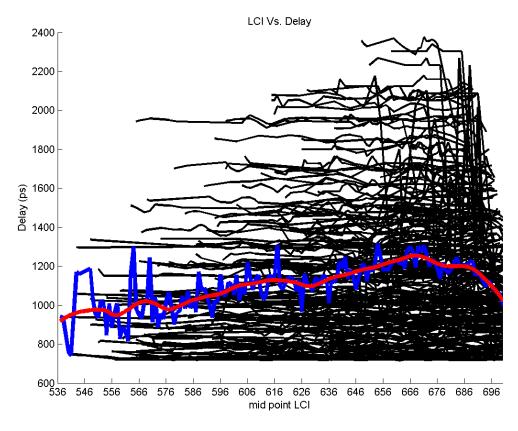

| Fig. 4.5: Curves of individual FF delays measured at different midpoint delays. Ar                         |

| average of all individual curves is superimposed, as well as a curve with only                             |

| the low frequency components of the 'Average delay curve'48                                                |

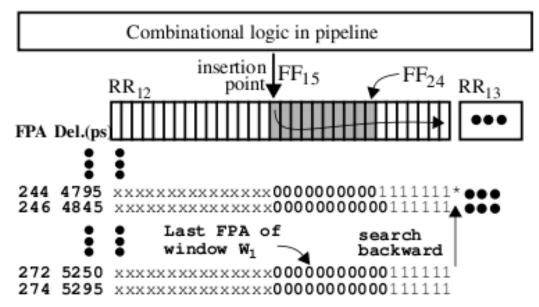

| Fig. 4.6: Calculating path delay using digital snapshots.                                                  |

| Fig. 4.7: Illustration of calibration operation carried out using an individual FF delay                   |

| curve and 'smoothed' average delay curve50                                                                 |

| Fig. 4.8: Delay calibration applied to example path from Fig. 4.6 using window1 (W <sub>1</sub> ) .5       |

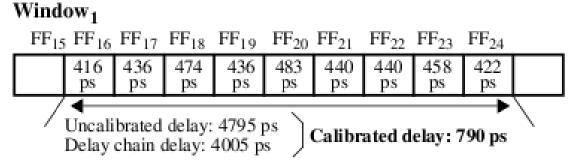

| Fig. 4.9: Zed Board with Zynq FPGA                                                                         |

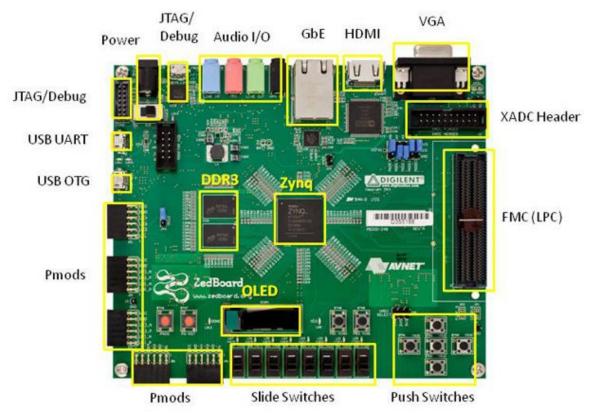

| Fig 4.10: Clock Strobing in FPGAImplementation54                                                           |

| Fig 4.11: Digital Snapshot from a path delay test                                                          |

| Fig 4.12: REBEL Integration with AES Engine                                                                |

| Fig 4.13: Block level Diagram of AES with REBEL Integration                                                |

| Fig. 5.1: Flip-Flop Delays for Falling and Rising Transitions                                              |

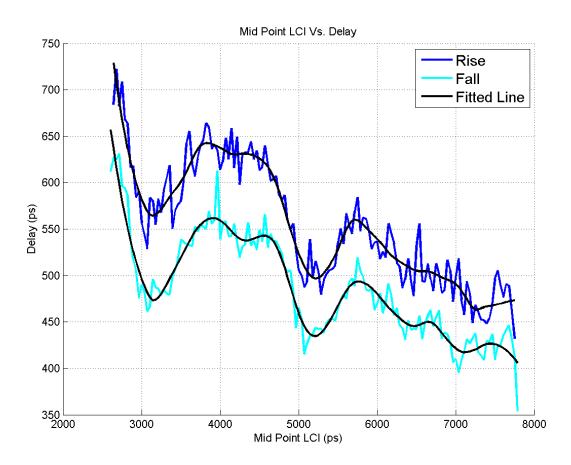

| Fig. 5.2: Mid-point LCI Average Delays for Rising and Falling Transitions                                  |

| Fig.5.3: Propagational Delay of Rising Edge.                                                               |

| Fig.5.4: Propagational Delay of Falling Edge                                                               |

| Fig. 5.5: Digital snapshots illustrating uncertainty using data given earlier in Fig. 4.462                |

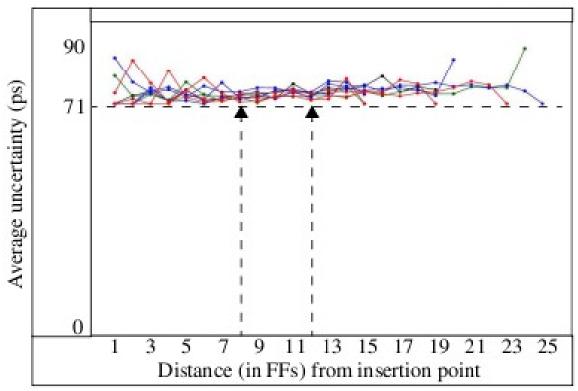

| Fig. 5.6: Average Uncertainty as a function of distance (in FFs) from the insertion point                  |

| for 4 chips at all TV corners                                                                              |

| Fig. 5.7: Calibration process applied to the 2nd of two consecutive windows illustrating                   |

| error in the estimation of path delay64                                                                    |

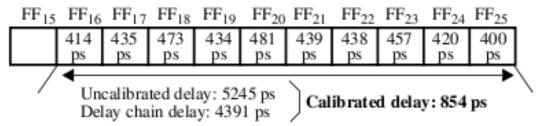

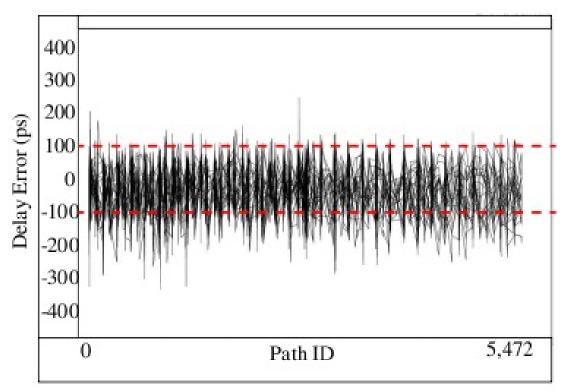

| Fig. 5.8: Delay errors computed using W <sub>1</sub> and W <sub>2</sub> of the proposed calibration method |

|            | for all paths and chips at 25°C, 1.2V                                                | 65  |

|------------|--------------------------------------------------------------------------------------|-----|

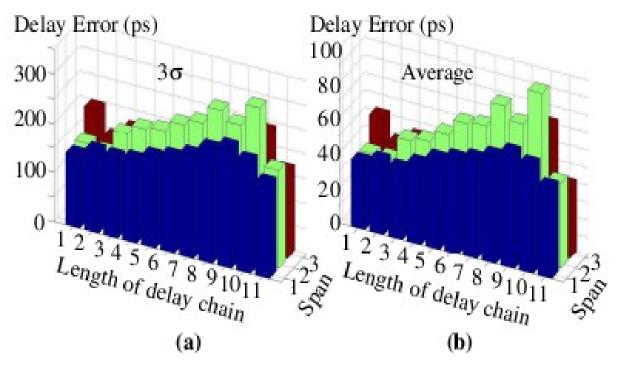

| Fig. 5.9:  | $3\sigma$ (a) and average (b) delay errors for all paths and chips at 25°C, 1.20V as | a   |

|            | function of 'length of the delay chain' (x-axis) and span (y-axis)                   | 66  |

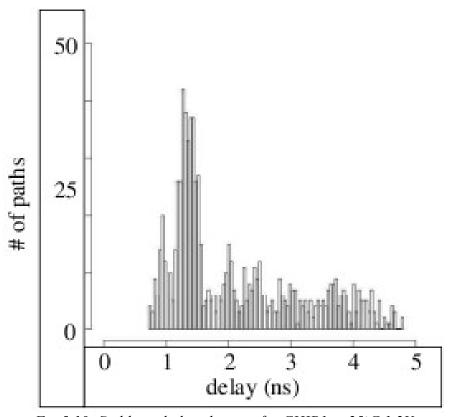

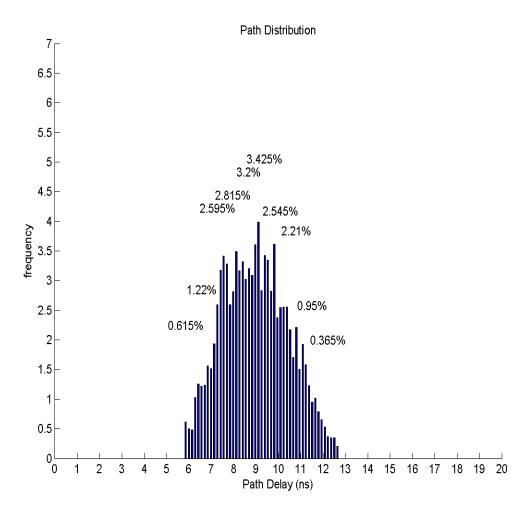

| Fig. 5.10: | Stable path distributions for CHIP1 at 25 °C, 1.20V                                  | 68  |

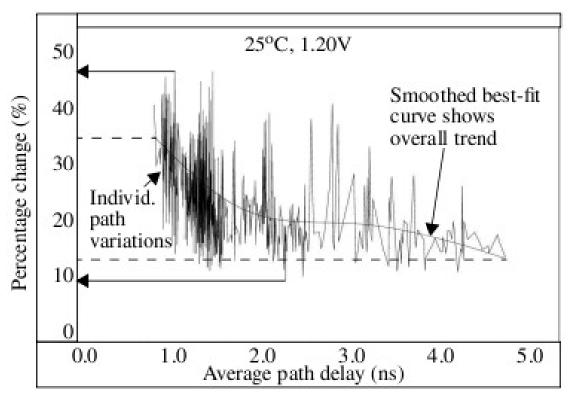

| Fig. 5.11: | Short vs. long path delay variation analysis at 25°C, 1.20V                          | 70  |

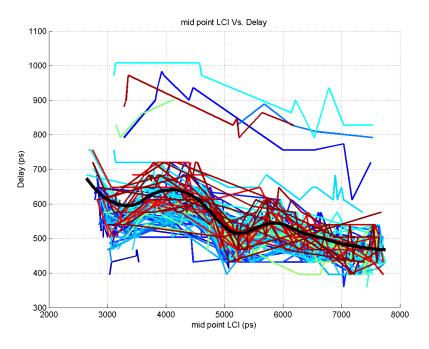

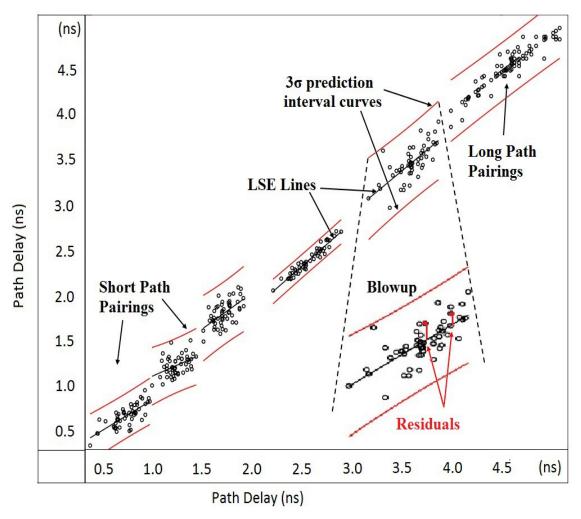

| Fig. 5.12: | Within-die delay variation analysis using regression: example scatter plots          |     |

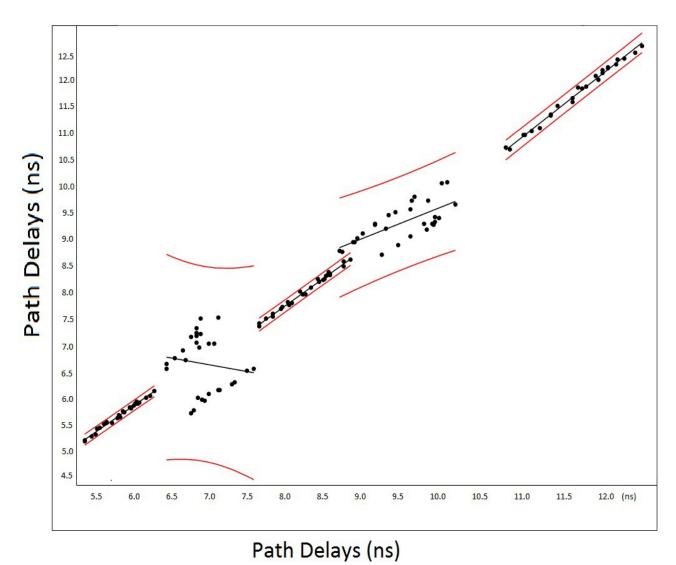

|            | from distribution of common to all chips                                             | 71  |

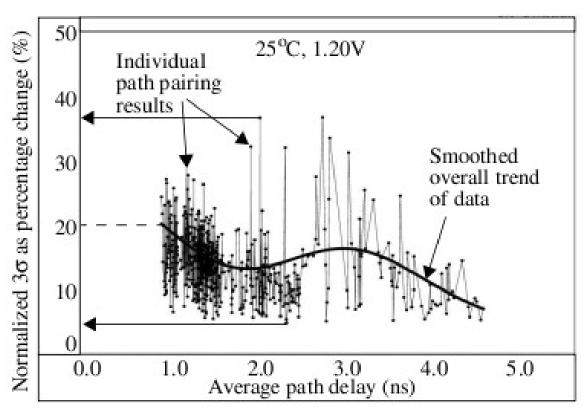

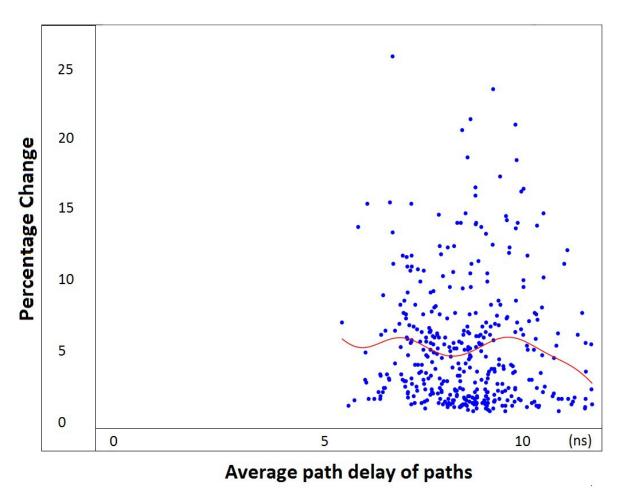

| Fig. 5.13: | Within-die variation analysis using regression. Average path delay vs.               |     |

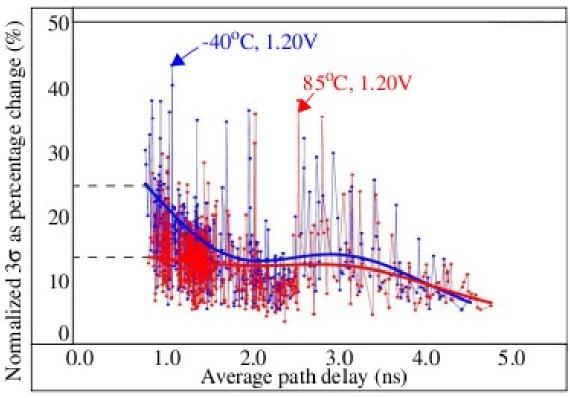

|            | normalized $3\sigma$ of residuals expressed as percentage change                     | 73  |

| Fig. 5.14: | Within-die variation analysis using regression using data from two addition          | al  |

|            | TV corners                                                                           | 74  |

| Fig. 6.1:  | Rising Edge Propagational Delay                                                      | .76 |

| Fig. 6.2:  | Falling Edge Propagational Delay                                                     | 77  |

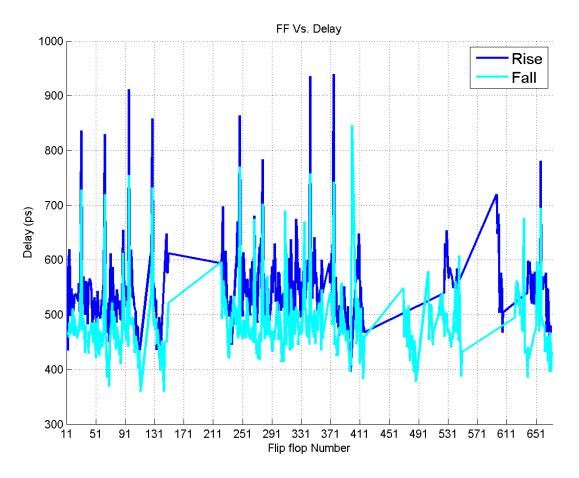

| Fig. 6.3:  | Rise versus Fall delay of Flip-Flops.                                                | 78  |

| Fig. 6.4:  | Average Rising delays of FFs for Chip1                                               | 79  |

| Fig. 6.5:  | Average Falling delays of FFs for Chip1                                              | 80  |

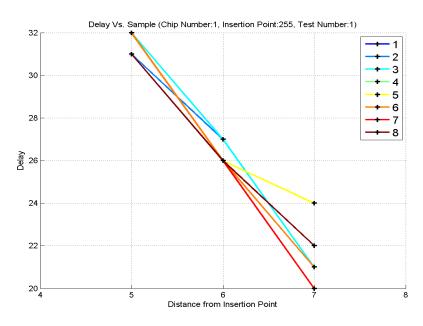

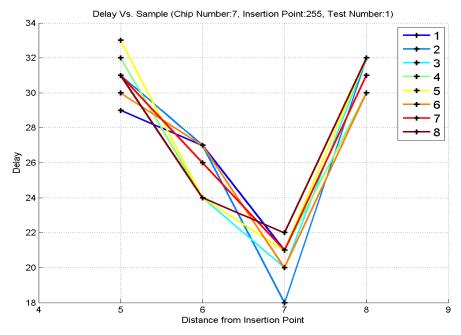

| Fig. 6.6:  | Delay versus Sample Analysis for Chip 1                                              | 81  |

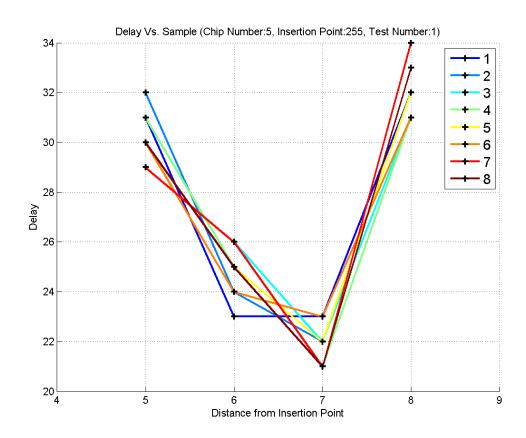

| Fig. 6.7:  | Delay versus Sample Analysis for Chip 5                                              | 82  |

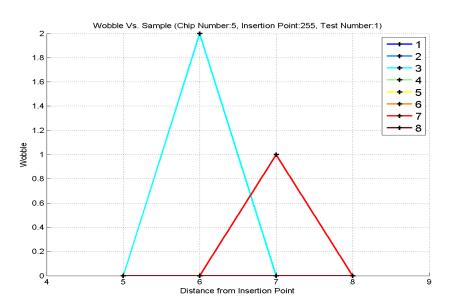

| Fig. 6.8:  | Uncertainty Analysis for Chip 5                                                      | 83  |

| Fig. 6.9:  | Delay Versus Sample Analysis for Chip 7.                                             | 83  |

| Fig. 6.10: | Uncertainty Analysis for Chip 7                                                      | 84  |

| Fig. 6.11: | Overall Uncertainty in path delays                                                   | 85  |

| Fig 6 12.  | Standard Deviation in Rising Edge for All Chips                                      | 87  |

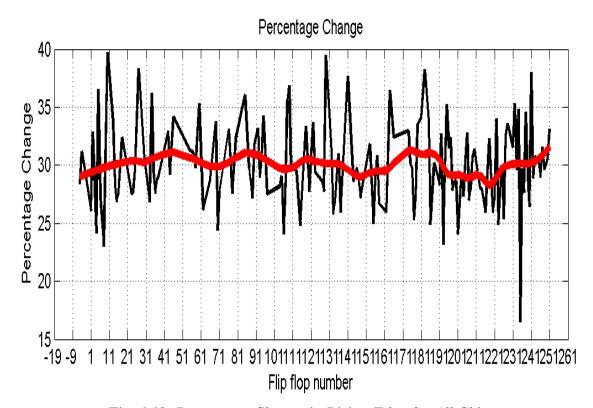

| Fig. 6.13: | Percentage Change in Rising Edge for All Chips                               | .88  |

|------------|------------------------------------------------------------------------------|------|

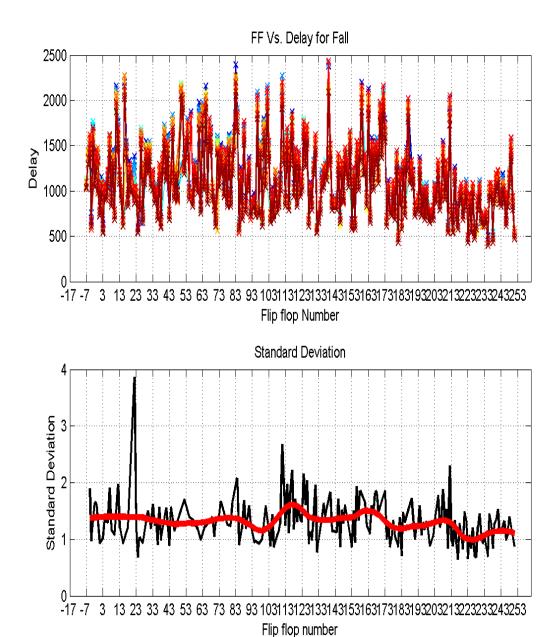

| Fig. 6.14: | Die-to-die Variation in Falling Edge in All Chips                            | 89   |

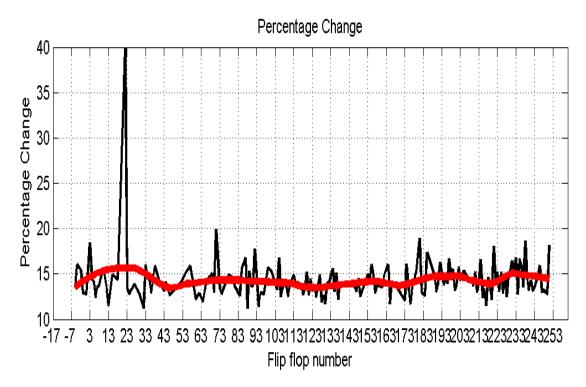

| Fig. 6.15: | Percentage Change in Falling Edge for All Chips                              | 90   |

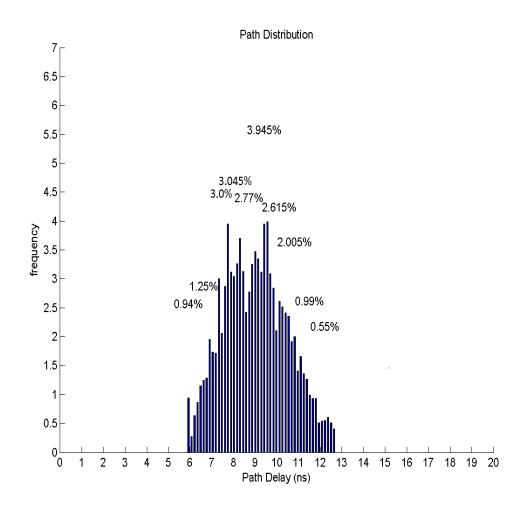

| Fig. 6.16: | Path Distribution for Chip 1                                                 | 91   |

| Fig. 6.17: | Stable Path Distribution for Chip 2                                          | 92   |

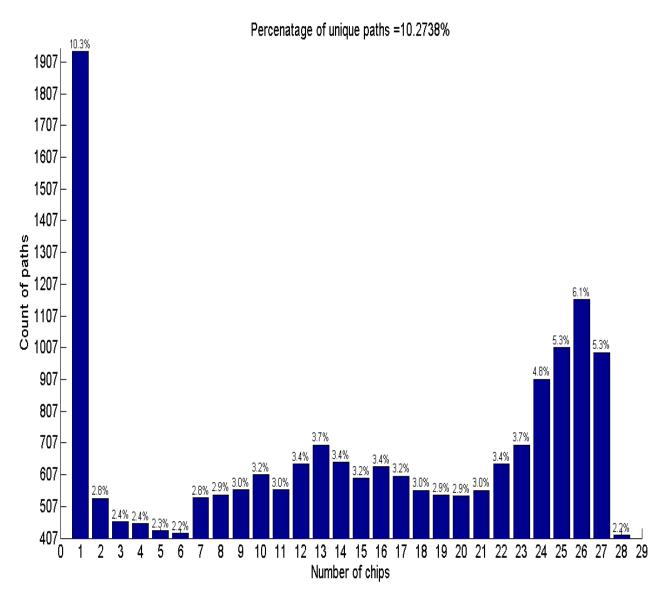

| Fig. 6.18: | Unique and Common Path ID Counter.                                           | 93   |

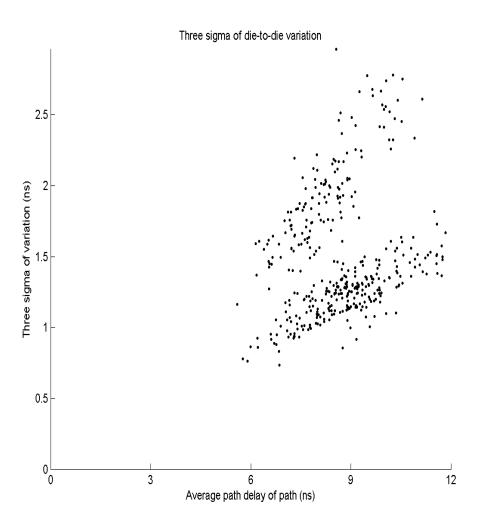

| Fig. 6.19: | Die-to-die Variation Analysis using Regression. Average path delay versus    |      |

|            | normalized $3\sigma$ of residuals.                                           | 94   |

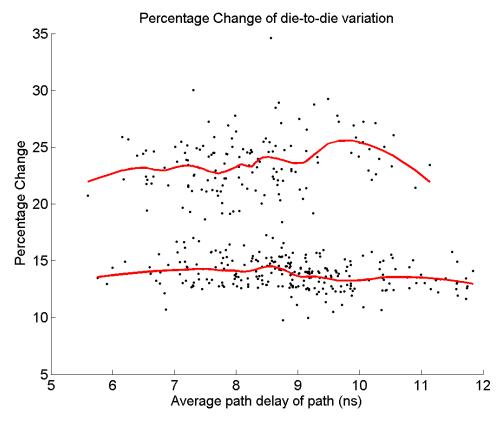

| Fig. 6.20: | Overall percentage change of die-to-die variation in path delay              | 96   |

| Fig. 6.21: | Within-die variation for short and long path pairings                        | 97   |

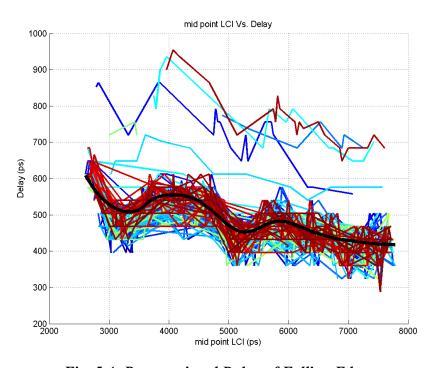

| Fig. 6.22: | Within-die delay variation analysis using regression: Example scatter plot f | orm  |

|            | distributions of common to all chips                                         | 98   |

| Fig. 6.23: | Overall percentage change of path delays variation.                          | 99   |

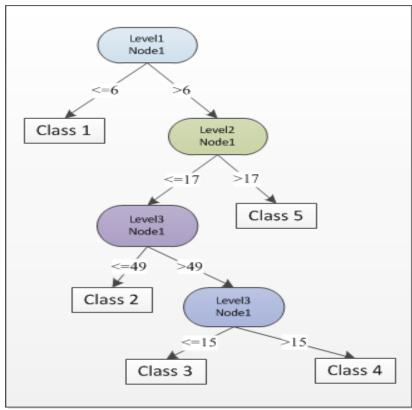

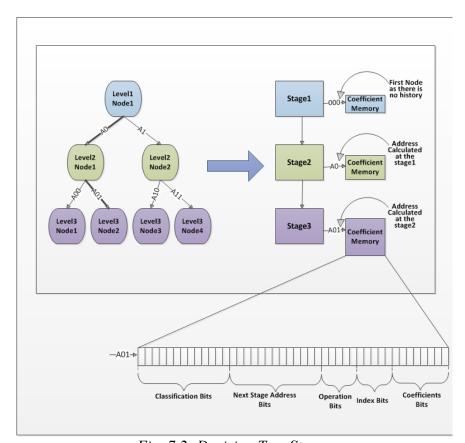

| Fig. 7.1:  | Decision rules in form of decision trees                                     | .106 |

| Fig. 7.2:  | Decision tree stages                                                         | .107 |

| Fig. 7.3:  | Decision tree classification system.                                         | .109 |

| Fig. 7.4:  | RTL level block diagram of hardware module                                   | .110 |

| Fig. 7.5:  | Parallel and pipelined decision tree Engine.                                 | .112 |

| Fig. 7.6:  | Streaming architecture                                                       | .121 |

| Fig. 0.1.  | Time to Digital Conversion (TDC)                                             | 128  |

# **List of Tables**

| Table 3.1: Configuration States for Row Control Logic          | 26  |

|----------------------------------------------------------------|-----|

| Table 7.1: Accurcy of decision tree model                      | 116 |

| Table 7.2: Comparison with software implementation             | 117 |

| Table 7.3: Comparison with Hardware implementations            | 119 |

| Table 7.4: The resource utilization of the decision tree model | 120 |

# CHAPTER 1 Introduction

Both random and systematic within-die process variations (PV) are growing more severe with shrinking geometries and increasing die size [1] [2] [3]. Embedded test structures (ETS) continue to play an important role in the development of models of PVs and as a mechanism to improve correlations between hardware and models. Variations in delay and power continue to increase with reductions in feature size, which places higher demands on the accuracy of variation models. Their availability can be used to improve yield, and the corresponding profitability and product quality of the fabricated ICs [4].

Decision tree classification (DTC) is a widely used technique in data mining algorithms known for its high accuracy in forecasting. As technology has progressed, and available storage capacity in modern computers increased, the amount of data available to be processed has also increased substantially, resulting in much slower induction and classification times. Many parallel implementations of decision tree classifications algorithms have addressed the issues of reliability and accuracy in the induction process. In the classification process, larger amounts of data require proportionately more execution time, thus hindering the performance of legacy systems. Hence, to cater for big data for data mining, further work on decision tree classification (DTC) to speed-up the

classification step in hardware implementation cannot be overemphasized.

#### 1.1 Sources of Within-Die Variations

Sources of within-die variations include optical source limitations, and layout-based systematic effects (pitch, line-width variability, and microscopic etch loading [5] [6] [7]. Unfortunately, accurate models of within-die PVs are becoming more difficult to derive because of their increasingly sensitivity to design-context. Stand-alone embedded test structures such as ring-oscillators (ROs) are becoming less effective for characterizing delay variations in actual product macros because they are typically placed around the layout region of the macro as opposed to being integrated into it. In such circumstances, ring oscillators (ROs) are not exposed to, e.g., the same types of distortions which are introduced by photo-lithography interference patterns [8]. Some of the proposed ETS, such as those that measure delay characteristics of the macro itself [9] [10], offer the best solution, but are difficult to integrate without having an adverse impact on area overhead, yield loss, performance, I/O interface, test cost, etc. of the product design.

### 1.2 Proposed Embedded Test Structure (ETS)

For accurate measurement of within-die variations, we propose and investigate an embedded test structure (ETS), called REBEL (Regional dELay BEhavior), which is designed to measure path delays in macros while minimizing the adverse effects on area overhead, yield loss, performance, etc. The proposed ETS is designed to serve applications such as model-to-hardware correlation [11], detection of hardware Trojans [12], design debug processes, detection of small delay defects [13], and physical unclonable functions [14]. Each of these areas requires accurate measurements of path

delays and/or the ability to differentiate at high resolutions between delays of neighboring paths. The REBEL ETS leverages the scan chain architecture to measure delay variations. In particular, it uses a special configuration of flush delay mode that is available in level sensitive scan design (LSSD) style scan chains. In previous work [15], the promise of capturing regional delay variations using a special launch-capture timing sequence applied while in flush delay mode has been demonstrated. We extended this technique here by allowing output signals from a design macro to be inserted into the flush delay chain for path delay measurements.

A key feature of our work is the evaluation of REBEL in multiple copies of a custom designed test chip fabricated in IBM's 90nm technology. The macro in which REBEL is integrated is an IEEE-754 compliant floating point unit (FPU), with 5 pipeline stages. Random test patterns are applied to the combinational logic within each of the pipeline stages and the measured delays are analyzed, with emphasis on evaluating the magnitude of within-die variations as a function of path length. A second important component of our experiments is the evaluation of delay variations while the chips are subjected to industrial-level temperature and voltage (TV) variations.

#### 1.3 Decision Tree Classification (DTC)

The process of converting unidentified or unprocessed data into actionable information that is important and valuable to the user is known as data mining [16]. Recent advances in technology and ever increasing demands for analyzing larger datasets have created abundant opportunities for algorithmic and architectural development and innovations. Hence data mining algorithms have become increasingly significant and complex. Similarly there is a great demand for faster execution of these algorithms,

leading to efforts to improve execution time and resource utilization.

Decision Tree Classification (DTC) is a widely used technique in data mining algorithms known for its high accuracy in forecasting. As technology has progressed and available storage capacity in modern computers increased, the amount of data available to be processed has also increased substantially, resulting in much slower induction and classification times. Many parallel implementations of decision tree classification algorithms have addressed the issues of reliability and accuracy in the induction process. In the classification process, larger amounts of data require proportionately more execution time, thus hindering the performance of legacy systems. We have devised a pipelined architecture for the implementation of axis parallel binary decision tree classification that dramatically improves the execution time of the algorithm while consuming minimal resources in terms of area.

### 1.4 Organization

The balance of this dissertation is organized as follows: chapter 2 discusses related work and background on process variation. chapter 3 describes the details of the REBEL ETS while chapter 4 describes the integration of REBEL into the FPU and AES (Experimental setup). In chapter 5, I present the results of hardware experiments, chapter 6 presents the results of experiments on FPGAs, Chapter 7 discusses the implementation of proposed architecture of parallel implementation of pipelined decision tree classification engine. Chapter 8 summarizes the work and contains conclusion. Chapter 9 encompasses suggestions for the future work.

# CHAPTER 2 Background

Process variation (PV) is a challenge of Integrated circuit design in the newer technologies with the shrinking node sizes. Variation can be defined in terms of die-to-die and within-die variation, where die-to-die variations can be due to change in temperature or processing conditions. These changes can be captured using scribe line test structures or small amount of embedded test structures are sufficient for die-to-die variations coverage.

Within-die variations on the other hand are caused by across-field effects [17] in compassing the layout design techniques, optical aberration and other random effects such as dopant fluctuations. Within-die characterization requires more density of test structures to capture the variations in all regions.

#### 2.1 Test Structures for Within-Die Delay Measurement

Monitoring die-to-die and within-die requires distributing embedded test structures across and within chips in order to capture the overall wafer-to-wafer and within chip systematic variations with spatial correlations. Within-die and die-to-die delay analysis of delay variations continues to be an active research area. Ring oscillators

(RO) based test structures have been successfully used to characterize within-die delay variations in ASICs and FPGAs [9] [10] [17] [18] [19] [20] [21].

The simplicity of the RO design makes it an attractive modality as an ETS. Tuan et al. [17] proposed a scheme of creating an RO from the path-under-test to measure the critical path delays. Das et al. [18] constructed a digitally re-configurable RO structure for measuring the gate-level delays and reported measurement accuracy of 1 ps and up to 26% within-die delay variation in 65nm technology.

Bhushan et al. [19] presented an RO-based variability measurement scheme and illustrated the experimental results from a 90nm technology node. RO based designs are also used to measure within-die variability in 90nm and 65nm FPGAs [17] [20] [21]. Several on-chip analog measurement systems are proposed by Kinniment et al. [22] to accurately measure the on-chip path timing differences with a resolution of 10ps. They explain the time measurement techniques utilizing parallel mutex with a tapped delay line, successive approximation method and amplification of small time differences to a measurable size in different proposed time measurement approaches. A measurement system is proposed to characterize individual gate delays using an on-chip sampling oscilloscope. Also a within-die variation characterization system is proposed by Zhang et al. which also uses an on-chip sampling oscilloscope [23]. Stand-alone RO-based delay measurements lack the ability to account for "circuit context". Macro embedded RO schemes, such as Path RO [10], can only be applied to hazard free and robust paths. These kinds of embedded test structures, where a set of ring oscillators is distributed cross the layout, are capable of capturing within-die variations, but are becoming increasingly less accurate as predictors of delay variations in actual product macros.

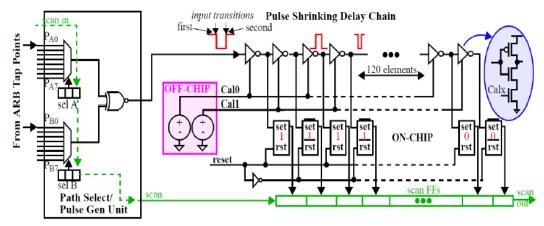

Various Time-to-Digital converters (TDCs) have been proposed for on-chip delay measurements with resolution as high as 5 ps and with low thermal sensitivity [11] [24] [25] [26]. Tapped delay lines are used by Dudek et al. [24] TDC using a technique vernier delay line with the a read-out circuitry, and achieved a 30 ps resolution with 128 delay stages and showed up to 5 ps is reachable using this methodology. Similarly, Datta et al. measured path delay by Modified Vernier Delay Line (MVDL), which digitizes the path delay forming MVDL and improves the resolution of delays [27]. However, to achieve the high accuracy measurement is sensitive to the symmetric routing in branches of MVDL, which will constrain the place and route tool [28]. Another TDC is proposed and designed with a resolution of 10ps [11], it measures the delay difference between two path signals out of several paths which are fanned out to the TDC from the macro-undertest. The delay between the two transitions produces a negative-going pulse with a width proportional to that difference of the transition timing of the glitch free paths. The TDC scheme, just like RO restricts their coverage because of condition of having glitch free paths. Also analog measurement systems and TDCs have large area overheads.

Truly embedded test structures, such as those that measure delay [9] [10] [15], and power [29] characteristics of the macro itself, offer the best solution. Path-RO creates an oscillator from the given path to measure the delay on chip, capturing the process variations [10] but this solution is difficult to integrate without having an adverse impact on area overhead, and test cost, etc. of the product design. Whereas another novel technique proposed by Acharyya et al. [29] that leverages the existing power control circuitry, added to reduce the power consumption, and measures the leakage current variation of these modules and this variation thus reflects the current variation across the

chip. The use of multiple power supply port measurement technique is incorporated to measure the within-die leakage current.

A LSSD-style scan-chain-based embedded test structure is proposed by Lamech et al. [11] and Aarestad et al. [15], utilizing the inherent flush delay mode for obtaining single-shot measurements of path delays in product macros induced by the history effect. This test structure leverages the existing scan structure and can be used to characterize the within-die delay variations by measuring the path delays of the macros. The embedded test scheme is called REBEL, a detailed description and analysis is performed in chapter 3. This proposed structure uses at-speed clock to measure the path delays for both short and long paths. The advantage of using the at-speed clock over the faster-than-at-speed clock is that the delays are more realistic and the supply voltage transience does not deteriorate the measured delay values and the path delay measurements are closer to the actual delays. I have used this technique for the experiments performed to examine the within-die variation of the 90nm test chips.

#### 2.1.1. Delay Measurements of Individual Gates

Authors [18] proposed a modified re-configurable ring oscillator to measure individual gate delay. The delay was averaged for the falling and the rising transition and showed up-to 26% within-die variation among the identical inverters which were placed close by on the chip. Symmetric multiplexers of large size having balanced delay and a set of inverters were used in the gate delay measurement cell, where cell was replicated in five stages for the delay measurement mechanism. A Pico-second Imaging Circuit Analysis was used to digitize the delay by counting the infra-red photons captured from the chip. The gate delay measurement of individual standard cells helped in

characterizing the stress, neighboring effect and other effects more efficiently.

Furthermore, in another measurement system for characterizing an on-chip within-die delay variations of standard cells, for both falling and rising edges, was proposed by Zhang et al. using sampling oscilloscope with a pico-second resolution [23] [30]. It displayed a strong correlation between the on-chip measurements and Monte-Carlo simulation. The experimental results confirmed that the delay variations of the on-chip are smaller for the gates with the bigger active area, and the NMOS has bigger variation than the PMOS.

#### 2.2 Design and Environment Effects on Within-Die Variations

The environmental factors can affect the behavior of a semiconductor circuit, like the temperature or supply voltage for a given process. Also the device parameters, for example the length of transistor, oxide thickness may vary caused by the non-uniformity in the manufacturing process.

There are many sources which can affect the fabrication process and to create an adequate model for characterizing delay variation it is important to identify these parameters. The impact of different layout topologies on variation is presented by Pang et al. [31], the authors measured the variability of various test structures and analyzed the effects of systematic and random components of within-die variations. Lithographic simulation capability in the routing engine can improve the product yield [8] by identifying and modifying the patterns in the layout to avoid lithography hot spots. Reticle Enhancement technology is discussed by Grobman et al. [32] and usage of other optimized techniques to achieve planarity in manufacturing process for the subwavelength technologies for better circuit timings.

Analysis of temperature dependence has been performed on the sub-threshold circuit 40nm chip [33]. The device under test had a 16x16 array with each unit having 8 ring oscillators, where they are placed in different supply voltage regions and later the outputs are level shifted to the nominal voltage. The variation was measured as deviation of delay/mean and showed that the variation was 1.4 times more when the temperature was dropped from 25°C to -40°C [33]. This variation was inversely proportional to the temperature, that is, the with-die delay variations were larger when the temperature was lowered.

#### 2.3 Within-Die Variations in FPGAs Reconfigurable Logic

In the domain of FPGAs re-configurable logic, techniques for the measurement of within-die variation is discussed by Sedcole et al. [21] in 90nm FPGAs and by Tuan et al. [17] in 65nm FPGAs. The effect of both random and systematic process variation on 18 Altera Cyclone II devices with 5 stage and 7 stage ROs was measured by Wang et al. [34].

For 90nm, the measure of process variation in 10 FPGA's using 135 stage ring oscillators is performed also the within-die delay variation characterization is performed with a small number of oscillator stages and shows that the mean random variation is ± 3.54% and systematic variation can vary the delay up to 3.66% additionally [21]. Whereas, for 65nm FPGA family a detailed analysis of the within-die variations is performed with the test structures implemented on the re-configurable logic, each created with four configurable logic blocks [17]. Using a large number of ring-oscillators, the analysis is performed on rising and falling edges independently and the data is processed to distinguish between the random and systematic variations. The results showed that the

random variation followed Gaussian distribution whereas the systematic variation was further modeled in the software timing models to evaluate the optimization of performance using a variation aware timing model, by calculating the maximum frequency for each design.

#### 2.4 Impact of Within-Die Spatial Process Variations

#### 2.4.1 Clock Frequency

A design with low overhead for calibration of maximum frequency has been proposed by Paul et al. [9]; where at the given voltage sensitivity, small set of paths is configured into a ring oscillator and the maximum frequency of a given chip is dynamically computed. Hence, the need of delay testing at operating voltages with all frequencies is eliminated through binning each chip into categories of different voltages and frequencies.

The product level variations for single and multi-core processors were simulated for maximum clock frequency and optimized throughput for 22nm technology [35]. They statistically measured the impact of parameter variations and compared the performance of multi-core processors with the single core processors and showed that multi-core processors were more variation tolerant because of the greater impact of memory latency and bandwidth on throughput.

Similarly possibilities of mitigating the performance loss was investigated by Palframan et al. [36], by introducing redundancy along the processor datapath in the form of one or more extra bit slices, leaving the dummy slices in the datapath unused to avoid excessively slow critical paths created by delay variation, which showed the reduction of delay penalty by 10% or more caused by the variation.

#### 2.5 Static Timing Analysis

The design environments utilize the static timing analysis for the delay variations in the paths through the chip, by considering the worst case delay by assuming all the segment delays to be maximum or minimum, which are not realistic [8]. Each element of the path has associated delay and models should be incorporated for process variations to do the statistical static timing analysis, to be able to get better model-to-hardware correlations.

A technique for computing the delay distribution task as a function of technology parameter of a circuit was presented by Mehr et al. [37]. They calculated the mean value of delay using normal distribution approximation of normalized delay and skewness of the delay distribution from Gaussian distribution; and compared the results with those of Monte-Carlo simulations. Channel length variation was engrossed which impacted the threshold voltage and load capacitance; and thus affected the gate delay. The study incorporated the impact of transistor stacking on the delay, by using Taylor Series. Also, it combined the load capacitance parameter to get more accurate delays [37].

### 2.6 Design for Manufacturing and Yield

The design for manufacturing (DFM), and design for yield [4] classifies the systematic and statistical variations, caused by the physical defects in the structure of transistors which can be catastrophic, or electrical variations in the composition of transistors, wires or vias, causing parametric defect which allows the chip to function in a specified range with varied power leakage [8]. Catastrophic defects fails the chips, whereas, the chips with parametric defects can function but they do not meet the design requirements, for example they do not function on the specified range or there is more

power leakage than specified.

A need of a DFM aware design tool is vital for the newer technologies where the feature sizes are shrinking. A broad range of work is ongoing to develop mechanisms for characterizing more accurately the within-die and die-to- die process variations (PV). The development of area-efficient structures and methods for validating variation models for the newer technologies is of greater importance, where the feature sizes are getting smaller than the wavelength of the light used to create them [8]. The physical variations also contributes more variation on the scaling devices, as a larger impact is produced on a smaller device size and causes a huge variation as compared to the larger devices.

The physical device parameters determine the behavior of the device and predicts the performance changes with the environmental factors, by the variability in the fabrication process. These variations are captured with the conventional test structures, but the process variations are getting more sensitive to the design context, which the traditional test structures residing on a different region then the actual macro cannot truly capture.

The die-to-die level variations can be captured with the limited number of test structures for testing and measurement. The test structures currently being used include, scribe-line structures, or a fewer number of ring oscillators embedded test structure to capture the variations. This methodology is not effective for characterizing the within-die and context-sensitive variations. Process Variations are more challenging to measure and model in within-die context, which includes the across field effects. The main sources of these are due to optical source limitations, and layout-based systematic effects [17]. Also pitch, line-width variability, and microscopic etch loading are the sources of variations

from the manufacturing process [5] [6] [7].

#### 2.7 Applications of Die-to-Die and Within-Die Variations

The process variations in the devices can be used for the identification [34] [35] [36] [37], authentication [38] [39] and generating unique keys for encryption, benefiting the nature of variations being random. The concept of using the manufacturing process variations as identifiers for integrated circuits is recent and is being used in physical unclonable functions (PUF). Where each device has its individual characteristics and it is impossible to have an exact duplicate, even if the same manufacturing process was used in the production. There are a large number of PUFs, which can be classified in many categories, e.g., Memory based, Delay based, and power grid PUFs which uses the process variation to produce unique identification mechanisms.

#### 2.7.1. Hardware Security

Computing platforms are being increasingly deployed in many critical infrastructures such as smart grid, financial systems, sensitive governmental organizations *etc.*, where consequences of a successful security attack could be potentially serious. Thus, these applications of computing platforms in high-risk areas motivate the need to build platforms with enhanced security.

The computing platforms are multifaceted and generally comprise of architectures, operating systems and routine libraries. For normal operation, they require interaction between numerous hardware components such as processor, chipset, memory and peripherals. In order to maintain security of these computing platforms it is essentially required to ensure that there are no known security deeds present in the run-

time interaction between these hardware units exploitable by attackers. However, validating complete security of the computing platforms may be difficult and inflexible because of the fact that there are a large number of elements in the hardware units and their mutual interaction is influenced by many control signals [40]. Tempering, duplicating and theft of service have become a grave concern for hardware vendors as it may have adverse effects on their income and reputation. For providing protection against this menace, hardware security built on cryptographic primitives using keys can be used. These keys are usually stored somewhere in the hardware. Therefore, the strength of the security depends mainly on the effort required by attackers to compromise them. The attackers have developed very advanced tools for attacking hardware. This has reduced and minimized the protection provided by storing a key in memory.

Physically Unclonable Functions (PUFs) can also be used to protect devices against attacks on their keys. PUFs are primitives that extract secrets from physical characteristics of integrated circuits (ICs) and can be used, *inter alia*, for protected key storage [41]. A PUF is a function that is embodied in a physical structure that consists of many random uncontrollable components. These primitives are produced during manufacturing mainly because of process variations. Due to this random structure a physical inducement or challenge generates unpredictable responses. Because of their physical properties PUFs are nonreplicable and very promising primitives for the purpose of authentication and storage of cryptographic keys [42].

Random variations in physical properties of chips are used by PUFs to differentiate one chip from another, and are impossible to duplicate even by the

manufacturer. Although process variations are effectively impossible to control or eliminate, but they can be measured. The specific varying properties exploited by the PUF can differ from one PUF design to another. However, common sources of parametric variation include propagation delay, metal resistance, transistor drive strength, and mismatches between complementary transistors [14].

PUFs are used in a number of security applications like authentication, identification, and secure key generation. PUF implementations are evaluated on their security characteristics (i) uniqueness, (ii) randomness, and (iii) reliability as well as conventional VLSI design metrics including area, power, and performance [43]. PUFs can take many forms among which some of the common ones are optical PUFs, paper PUFs, coating PUFs and silicon PUFs. In order to identify silicon devices, further variants include PUFs based on delays in a silicon circuitry such as arbiter PUFs and ring-oscillator PUFs, and PUFs based on the start-up behavior of memory cells such as SRAM PUFs, butterfly PUFs and flip-flop PUFs [44].

Potlapally [40] presented an overview of methods adopted to cater for intricacy of validating security of hardware in an industrial setting, and highlighted opportunities for the security research community pertaining to hardware security validation; while Handschuh [44] provided an overview of the state of the art in research on memory PUFs specifically on SPRAM PUFs and presented results from industrialization of such PUFs. Kursawe et al. [42] introduced a reconfigurable optical PUF, based on phase change memory, with a mechanism to convert it into a new unpredictable and uncontrollable challenge-response behavior. The description of their scheme however omitted possible optimizations. Quality factors of ring oscillator (RO) based PUF are negatively affected

by environmental noise and systematic variations in the die. To address this problem, Maiti and Schaumont [45] proposed two methods to achieve a higher reliability in an RO-based PUF, and attempted to verify their results using a small sample size of only five FPGAs.

The reliability of PUFs implemented in CMOS circuits is normally affected by environmental conditions such as voltage and temperature. Kumar et al. [46] investigated two methods for improving the reliability of delay based PUFs, by reducing temperature sensitivity. The first method focused on improving the gate overdrive by operating the PUF at an optimized supply voltage. The second method explored the negative temperature coefficient property of source feedback resistors. They reported 16% improvement in reliability for both these methods. Subsequently, Kumar et al. [47] proposed a temperature-invariant ring oscillator PUF architecture based on serial-input serial-output (SISO) topology interpreting the relative phase difference between two ring oscillators to a digital response bit. They reported that this phase difference based response generation was superior to frequency based response generation in terms of area and power.

Hori et al. [48] developed a physical unclonable function (PUF) with a hardware architecture structure as a large combinational logic. In this research work, the long feedback signal extracted the device variation. Accordingly, the output IDs generated in the different devices became different from each other. The authors have not yet evaluated the indemnity against the existing attacks such as model-building attacks.

Schrijen and Leest [49] investigated the reliability and uniqueness of static random access memories (SRAMs) ranging from 180nm to 65nm in different technology nodes

when used as PUF. The authors presented quantitative results but did not give any technology or architecture analysis as they did not have access to SRAM architectures of all of the tested memories.

For integration of PUFs into low-power and security applications, Lin et al. [50] studied the effects of process technology and supply voltage scaling on arbiter-based PUF circuit design. Using Monte Carlo-based statistical analysis, they demonstrated that advanced technologies and reduced supply voltage could improve the PUF uniqueness due to increased delay sensitivity.

Simon et al. [41] evaluated and compared reliability and uniqueness of Buskeeper PUF developed by them with those of D Flip-Flop (DFF) PUFs. The quality of bit strings generated by PUFs based on resistance variations, in the power grid metal wires and transistor on-resistance in 90 nm chip as well as in the power grid metal wires of 5 65 nm chip, was analyzed by Ju et al. [51]. The authors also investigated a voltage threshold technique to eliminate unstable bits. They reported that the PUF primitives generated cryptographic quality bit strings of length up to 1.6M bits. Bhargava et al. [43] compared bi-stable based PUFs (SRAM and sense amplifiers) and delay based PUFs (arbiter and ring oscillator) using measurements from a test-chip in 65nm bulk CMOS. Their reliability measurements were based on multiple evaluations of PUF circuits across operating voltage ranging from 1.0V to 1.4V and temperature ranging from -20°C to 85°C. They reported that bi-stable PUFs were more area-efficient than the delay-based PUFs.

Kumar and Burleson [52] presented a password based hardware authentication using PUF, called (PHAP), which was able to distinguish between a trusted party

and an adversary based on a simple user password during authentication. They showed that the time difference between real time execution of the system by a trusted party and simulation time by an adversary can be very large. Their simulation results showed that the probability of an adversary successfully attacking the system was very low.

The silicon physical unclonable functions (PUF) utilize the uncontrollable variations during integrated circuit (IC) fabrication process to facilitate security related applications such as IC authentication. Yin et al. [53] described a framework to generate secure PUF secret from ring oscillator (RO) PUF. Their work is based on group-based RO PUF, utilizing the concepts including (i) an entropy distiller to filter the systematic variation, (ii) a simplified grouping algorithm to partition the ROs into groups, (iii) a syndrome coding scheme to facilitate error correction, and (iv) an entropy packing method to enhance coding efficiency and security. They demonstrated that these concepts can create PUF secret that can pass the NIST randomness and stability tests.

A hardware-embedded delay PUF was designed by Aarestad et al. [54] to leverage path delay variations that occur in the core logic macros of a chip to create random bit strings. The bit strings produced by a set of 30 FPGA boards were evaluated for uniqueness, randomness, and stability. They also proposed an error avoidance scheme which provided significant improvement against bit-flip errors in the bit strings. Recently, Aarestad et al. [14] presented a PUF, called HELP, based upon path-delay variations. The HELP is capable of (i) comparing paths of widely differing lengths, (ii) reducing the area cost and providing a relatively small amount of entropy, (iii) minimizing invasive design with low area and performance impact, and 4)

providing a hardware-embedded PUF engine requiring no external testing resources. Further, HELP possesses a large number of paths typically found in logic macros such as the advanced encryption standard (AES). This large source of entropy enable HELP to generate large bitstrings, for achieving bit stability and avoiding errors. To prove this PUF concept, and to demonstrate its effectiveness, the authors designed a complete, functional FPGA-based implementation of this PUF and validated it on FPGA boards. Their results of hammering distance and NIST statistical test analysis established that the bitstrings, being of high quality, are unique and random, and hence appropriate for cryptographic applications.

In their review on some applications of memristor, Mokhtar and Abdullah [55] described that LTspice memristor model is used to simulate memristor behavior and applied to the basic delay element circuit. It controls the current flowing to the parasitic capacitor, thus controlling the delay. As process variations become more prevalent due to technology scaling into the nanometer regime, nano-electronic technologies such as memristors become viable options for improved security in emerging integrated circuits. Rose et al. [56] provided an overview of memristor-based PUF structures and circuits that illustrate the potential for nano-electronic hardware security solutions.

#### 2.8 Summary

In my research, I present REBEL (regional delay behavior) as an embedded test structure (ETS), for path delay measurement that can be utilized for measuring within-die variation, and in several other applications, for example, Trojan detection, delay defects detection, and Physical Unclonable Functions. I describe the detailed architecture of REBEL and demonstrate its effectiveness for measuring delays and capturing the within-

die variations caused by the environmental and physical process variations. I have integrated REBEL with a functional macro on the 90nm chips as well as on the 28nm Zynq FPGA to illustrate the effectiveness and efficacy of REBEL in measurement of within-die variations. REBEL is implemented on FPU (Floating Point Unit) in 90nm process technology and on AES (Advanced Encryption Standard) on 28nm FPGA boards; I have gathered and analyzed data from 52 copies of 90nm chips and 11 copies of FPGA boards. The results are elaborated in chapter 5 and chapter 6. Subsequently, in Chapter 7 I discuss the implementation of parallel hardware accelerator on pipelined decision tree classification engine, Chapter 8 concludes with the benefits of REBEL for various applications and summary of the work. Chapter 9 suggests the future work.

# CHAPTER 3 REBEL: Embedded Test Structure and Macros-Under-Test

Within-die variations are caused by a cross-field effects [17] in compassing the layout design techniques, optical aberration and other random effects such as dopant fluctuations. Within-die characterization requires more density of test structures to capture the variations in all regions.

#### 3.1 REBEL- Regional Delay Behavior

The embedded test structure called REBEL (Regional dELay BEhavior) is designed to measure path delays in a minimally invasive fashion; and its architecture measures the path delays more accurately. REBEL can be integrated with the traditional scan design which is used in the design for testability, to improve the observability and control-ability of the sequential design. There are many variants of scan cells, mux-D scan, LSSD scan and clocked LSSD scan are most widely used. In this chapter I discuss in detail the modifications needed to integrate REBEL into a clocked-LSSD-style scan architecture.

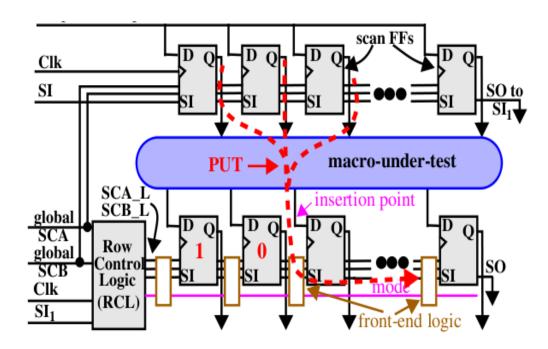

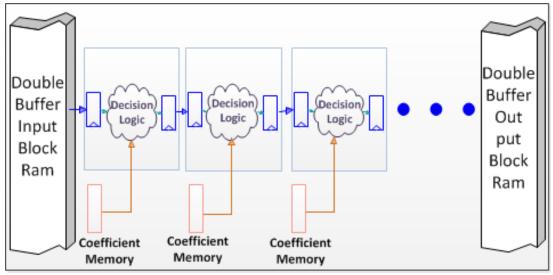

A REBEL ETS components consist of a set of scan-chains, row control logic header (RCL) and front-end logic for each scan cell to work in different operational modes. A row of scan flip-flops (FFs) is shown in Fig. 3.1 along the top which serves to launch transitions into the MUT. The bottom row is used to capture transitions that propagate through the MUT. REBEL ETS components are integrated into this row and are labeled "row control logic" and "front-end-logic" in the figure. Where the macrounder-test (MUT) is the combinational logic from a core logic macro.

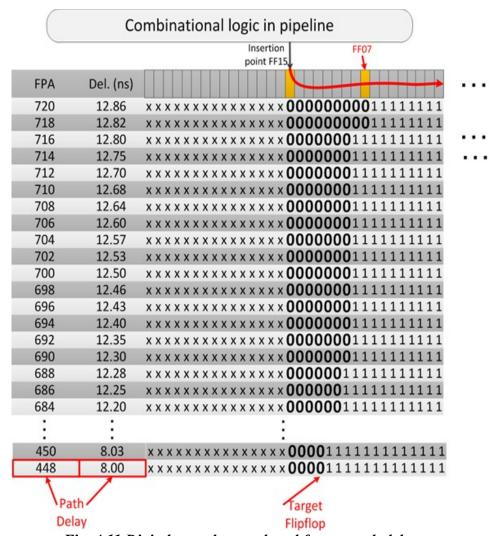

Transitions can be launched into the MUT using standard manufacturing delay test strategies such as launch-off-capture and launch-off-shift [28]. In either of these two scenarios, the scan chain is loaded with the initial pattern of the 2-pattern test and the system clk (Clk) is asserted to generate transitions in the MUT by capturing the output of a previous block or by doing a 1-bit shift of the scan chain, resp. The transitions that propagate through the MUT emerge on some of its outputs. REBEL allows only one of these transitions to be measured at a time in a specific region of the MUT, as indicated by the label PUT for path-under-test in the figure. The PUT's transition normally drives only the D input on the capture FF. However, the REBEL component labeled "front-end" logic allows this transition to be diverted to the scan input (SI) on the FF. This special logic also converts all scan FFs to the right of this insertion point FF into a delay chain. A digital snapshot of the signal as it propagates along the delay chain can be obtained by de-asserting Clk. The digital snapshot can be used to determine the timing of the PUT, and because it captures the temporal behavior of the PUT, it can also be used to determine if any glitching occurred. This is a unique and powerful feature of REBEL that is fully exploited in this work.

A special mode called flush-delay (FD) can be used to implement the delay chain in LSSD-based scan architectures. FD mode is enabled by asserting both the scan A and B

clock signals simultaneously. These signals are labeled "global SCA" and "global SCB" in Fig. 3.1. With both signals asserted, both the master and slave of a scan FF are transparent, allowing any transitions on SI to propagate through both latches after a  $\Delta t$  that represents the delay.

Fig 3.1: REBEL Integration Strategy

REBEL is required to implement two additional modes in the capture scan FFs shown along the bottom of Fig. 3.1 (in addition to the usual functional and scan modes). In particular, the scan FFs to the left of the insertion point need to preserve their contents during the Clk launch-capture (LC) event, while the FFs to the right of the insertion point need to implement the delay chain.

These two modes are realized using the RCL block, a special scan chain encoding and the front-end logic shown in Fig. 3.1. The mode is controlled by configuring two FFs in the RCL block while the scan chain encoding serves to specify the insertion point of the PUT.

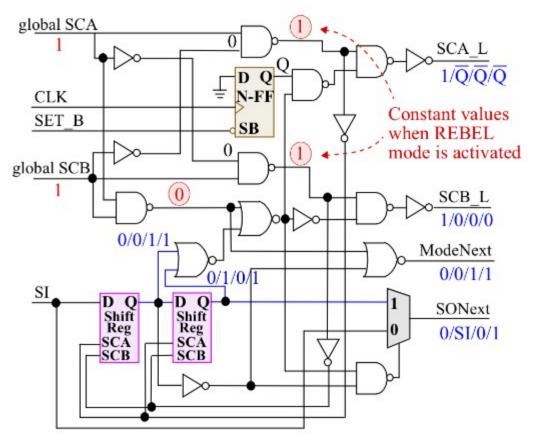

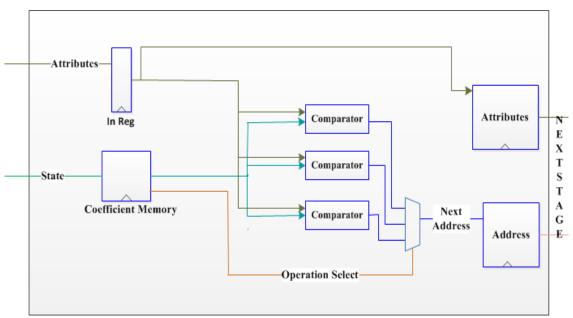

Fig 3.2: REBEL Row Control Logic

Fig. 3.2 shows a schematic diagram of the RCL. The top portion of the diagram controls local (row-specifichiefenercon) scan clock signals, labeled SCA\_L and SCB\_L (L for local) while the bottom portion contains two shift registers (Shift Reg) and mode select logic. A large portion of the RCL logic is dedicated to allow the scan FFs in the capture row, hereafter referred to as row-FFs, to operate in functional or scan modes. The chip-wide scan signals labeled 'global SCA' and 'global SCB' are used to specify one of the three possible operational states for the chip. When both are low, functional mode is in effect. Scan mode is implemented when these signals are asserted in a non-overlapping fashion. The timing mode used by REBEL is in effect when both of these signals are asserted, as illustrated by the annotations in Fig. 3.2.

| Shift Register | Mode of Operation             | Functionality                                                                                 |

|----------------|-------------------------------|-----------------------------------------------------------------------------------------------|

| 00             | functional mode               | All Scan FFs in row are in functional mode                                                    |

| 01             | Flush Delay Continuation mode | All Scan FFs in row are in Flush Delay Continuation mode                                      |

| 11/10          | Mixed mode                    | Left scan FFs in preserve-contents mode, right scan FFs in FD mode, referred to as mixed mode |

Table 3.1: Configuration modes for REBEL rows

When REBEL mode is in effect, the specific mode of operation of the associated row-FFs is determined by the two shift registers. Table 3.1 identifies the modes for each of the four configurations. The bit configuration "01" (FD continuation mode) is required only in cases where there are multiple regions in the MUT. Bit configurations "10" and "11" specify the mixed mode described above, where FFs to the left of the insertion point are in preserve-content mode while those to the right are in FD mode. The outputs from the RCL block shown in Fig. 3.2 are annotated to show the values under each of these four bit configurations. Further operational details of the RCL block can be found in [11].

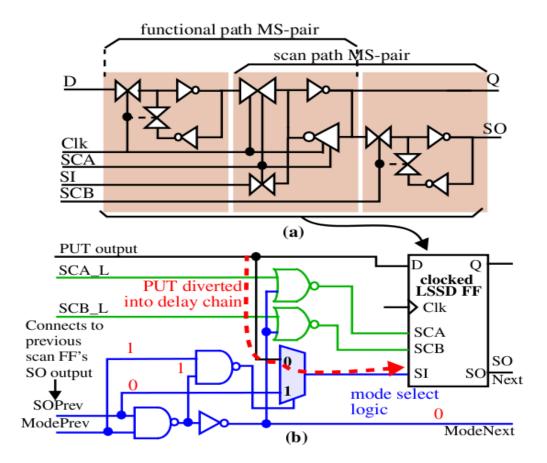

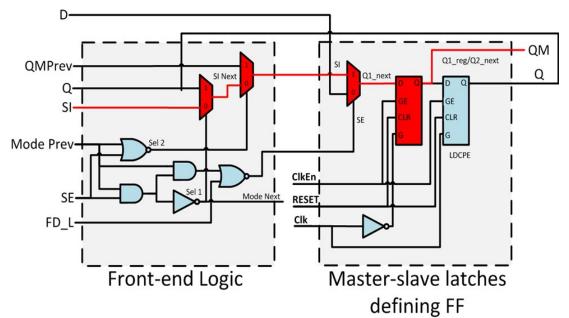

Fig. 3.3(a) shows a clocked LSSD FF (CLSSD) used in the FPU macro. It consists of three latches. The functional path master-slave (MS) pair shown on the left is driven by Clk. The slave latch is dual ported and also serves as the master in the scan path MS pair on the right. Fig. 3.3(b) shows the additional 'front-end' logic for REBEL. The functional path's D-input is fanned out to a 2-to-1 MUX, which allows for the insertion of a macro's PUT into the delay chain during the REBEL test.

Fig 3.3 (a) Modified clocked-LSSD scan FF and b) Additional front-end logic

This is accomplished with the mode select logic shown along the bottom of the figure. A specific insertion point is selected by pre-loading the row-FFs with a pattern of all '1's followed by a '0' from left to right along the row-FFs (see Fig. 3.1). Reference [11] provides specific operational details. Note that the front-end logic adds only a small capacitive load to the functional path and therefore the impact on performance is very small.

#### 3.2 Floating Point Unit (FPU) Macro

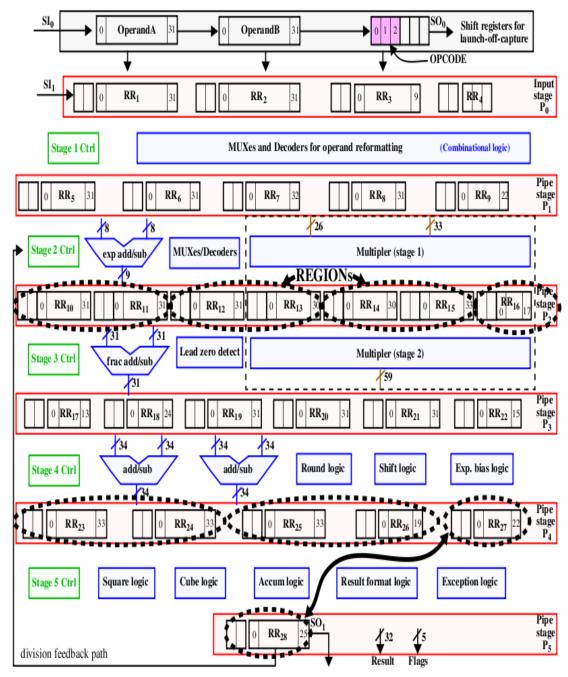

Fig 3.4: Floating Point Unit Block Diagram

Fig. 3.4 shows a block level diagram of a floating point unit (FPU) incorporated on the chips, as well as the inserted REBEL rows, labeled RRx from 1 to 28. All of the 817 FFs (56 row header FFs + 761 functional unit FFs) are wired together into a single scan

chain with input SI1 shown in the upper left and output SO1 shown along the bottom of the figure. A separate set of 70 shift registers are inserted on the inputs (top-most row in figure) which serves to enable a launch-off-capture testing strategy [28]. Here, the Input Stage P0 is loaded with the 1st pattern while the shift registers are loaded with the 2nd pattern.

The FPU is designed as a 5-stage pipeline, labeled P1 through P5, with MUXes, decoders, adder/subtractors, a multiplier, etc. inserted between the pipeline registers. The FPU is capable of carrying out 8 different operations, including add, subtract, float-tointeger, integer-to-float, negation, absolute value, multiplication and division. The 3-bit OPCODE shown along the top right in the figure determines the function. All operations except division can be carried out with a throughput of one operation/clk cycle. Division requires 5 clock cycles to complete with data fed back from the output of pipeline stage 5 to pipeline stage 2 through the 'division feedback path'. Given this pipeline structure and the constraints described above regarding REBEL, it is possible to carry out REBEL testing using 4 basic configurations. In the first two configuration, Cfg1 and Cfg2, the REBEL rows in pipeline stages P0, P1 and P3 are configured in functional mode while those in P2, P4 and P5 are configured in REBEL mode. In configurations Cfg3 and Cfg4, the rows in P0, P2 and P4 are configured in functional mode while those in P1, P3 and P5 are configured in REBEL mode. These 4 configurations collectively allow paths in all of the logic blocks to be tested using the REBEL ETS.

We create 2 configurations, Cfg1 and Cfg2, to handle a limitation that is illustrated in Fig. 3.1. In particular, the delay chain for insertion points on the right side of the MUT is very short and, in fact is non-existent for the right-most insertion point. The FD

continuation mode described in reference to Table 3.1 allows REBEL rows to serve as extensions of the delay chain. The dotted circles over row pairings RR 10-RR11, RR12-RR13, etc. (labeled REGIONs) in Fig. 3.4 illustrate how continuation rows are paired with mixed-mode rows. For example, RR10 of the RR10-RR11 pairing is configured in mixed mode which allows delays on each of the PUT outputs in this region to be measured, one at a time, while RR11 is used to extend the delay chain so that all insertion points can be timed along a non-zero length delay chain, particularly those on the right side of RR10. The circles illustrate the organization of mixed-mode (left) and continuation rows (right) for Cfg11.

A complementary pattern is used for Cfg 2 so that PUT outputs in, e.g., R11 can also be timed with R12 serving as its continuation row. Although only one path in each row can be tested at a time, up to 8 paths can be timed simultaneously across the various regions. Given these 4 configurations, there are a total of 684 Ffs that can serve as insertion points. This number excludes the 56 row header FFs and the 77 FFs in pipeline stage P1 (these FFs are always configured in functional mode).

We apply a random testing strategy to the FPU where the values placed in the functional rows are generated by an pseudo-random number generator. In order to allow specific functional units to be the target of our testing, we specify the OPCODE bits in the functional rows instead of inserting random values as we do for the remaining FFs of these rows. The top shift register row identifies the 3 OPCODE bits, which also exist in each of the pipeline stages (not shown). For each random pattern, a sequence of REBEL tests are applied which configure the position of the insertion point incrementally from left-to-right across each of the REBEL mixed-mode rows. Therefore, the same random

pattern is applied multiple times as a means of testing all path outputs. The insertion point in each RRx mixed-mode row is incremented until the right-most FF becomes the insertion point. The number of LC tests per test pattern is determined by the longest rows in each configuration, which are given as 34, 34, 33 and 32 for Cfg 1 through Cfg4, resp.

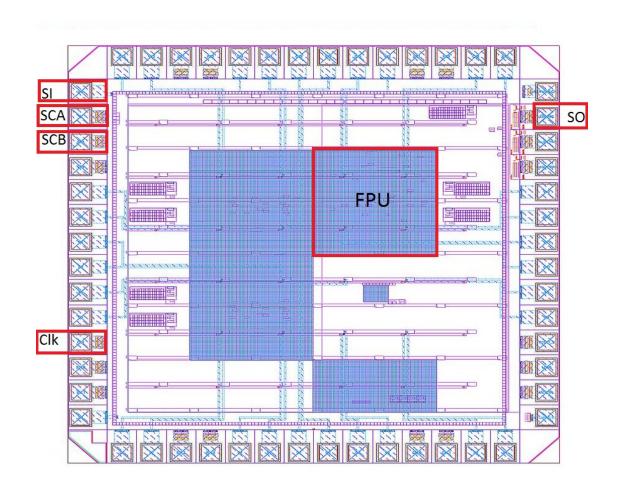

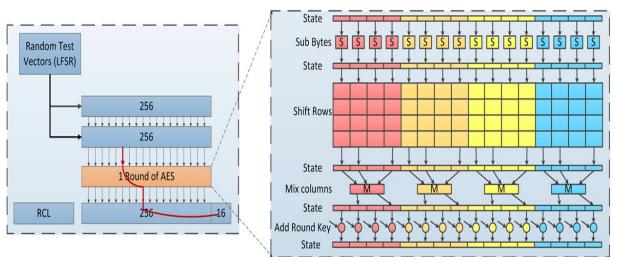

## 3.3 Advanced Encryption Standard (AES) Macro

Fig. 3.5: AES Engine

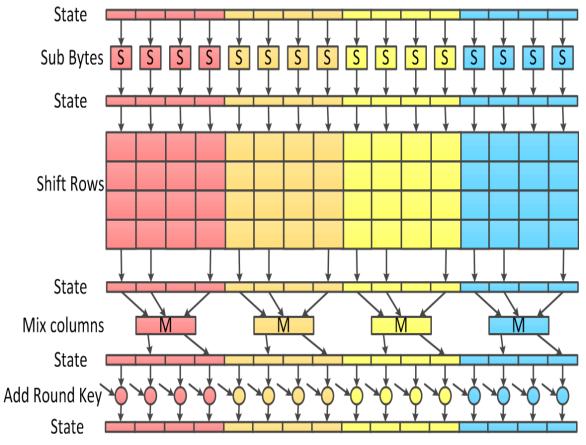

In the FPGA implementation of REBEL, the macro under test is a round of AES encryption. The combinational logic, shown in Fig 3.5, has an input of 256 and the output is also 256 bits. We utilize the input flip flops of the existing logic as launch row and use the output row as the capture row. The scan chain is implemented using Mux-D flip flops, which require only the system clock as compared to C-LSSD clock. The schematic diagram of Mux-D flip flop is shown in Fig. 3.6.

Fig. 3.6: Mux-D Flip Flop

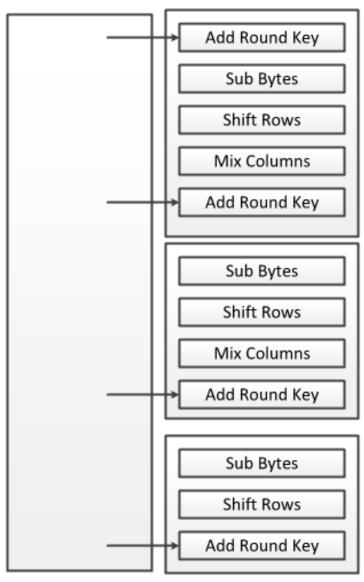

AES engine is a block cipher type of encryption with a block length of 128 bits. AES has different versions which allows for three different key lengths generation, that is, 128, 192, or 256 bits. The encryption rounds vary with the desired key size, for 128-bit key the processing includes 10 rounds, for 192 bit keys, 12 rounds and for 256 bits the number of rounds is 14. Each round of processing includes one single byte based substitution step using a non-linear substitution table (s-box), a row-wise permutation step, a column-wise mixing step, and the addition of the round key[57]. Figure (3.7) shows the different steps that are carried out in each round.

Fig. 3.7: AES Round

#### **3.3.1 STEP 1, SUB BYTES:**

This step performs a byte-by-byte substitution during the forward process of encryption. It consists of using a  $16 \times 16$  lookup table (s-box) to find a replacement byte for a given byte in the input state array. This substitution operates on each of the State bytes independently and the entries in the lookup table are created by using the notions of multiplicative inverses and bit scrambling to destroy the bit-level correlations inside each byte. The corresponding substitution step called InvSubBytes is used during decryption

#### 3.3.2 STEP 2, SHIFT ROWS:

Shifting the rows of the state array during the forward process. This step of

transformation hides the byte order inside each 128-bit or 256-bit block. The corresponding transformation during decryption is denoted InvShiftRows for Inverse Shift-Row Transformation.

#### 3.3.3 STEP 3, MIX COLUMNS:

This step of mixing up of the bytes in each column separately during the forward process further shuffles up the 128-bit input block. The shift-rows step along with the mix-column step causes each bit of the cipher text to depend on every bit of the plaintext after 10-14 rounds of processing. This way each bit of the plaintext affects every bit of the ciphertext in a block. The corresponding transformation during decryption is denoted InvMixColumns and stands for inverse mix column transformation.

#### 3.3.4 STEP 4, ADD ROUND KEY:

Adds the round key to the state of the previous step during the forward process by a simple bitwise XOR operation, that is each column of the state is XORed with a word from the key schedule. The corresponding step during decryption is denoted InvAddRound-Key for inverse add round key transformation.