# University of New Mexico UNM Digital Repository

Electrical and Computer Engineering ETDs

**Engineering ETDs**

2-8-2011

# Agile Testing Methods for IC Radios

Luis Martinez

Follow this and additional works at: https://digitalrepository.unm.edu/ece\_etds

**Recommended** Citation

Martinez, Luis. "Agile Testing Methods for IC Radios." (2011). https://digitalrepository.unm.edu/ece\_etds/173

This Thesis is brought to you for free and open access by the Engineering ETDs at UNM Digital Repository. It has been accepted for inclusion in Electrical and Computer Engineering ETDs by an authorized administrator of UNM Digital Repository. For more information, please contact disc@unm.edu.

| Luis Martinez                                                                         |               |

|---------------------------------------------------------------------------------------|---------------|

| Electrical and Computer Engineering                                                   |               |

|                                                                                       |               |

| This thesis is approved, and it is acceptable in quality<br>and form for publication: |               |

| Approved by the Thesis Committee:                                                     | , Chairperson |

| Bra-litto                                                                             |               |

| M. TImi F                                                                             |               |

| Magior Maraya                                                                         |               |

|                                                                                       |               |

|                                                                                       |               |

|                                                                                       |               |

|                                                                                       |               |

|                                                                                       |               |

|                                                                                       |               |

|                                                                                       |               |

|                                                                                       |               |

#### AGILE TESTING METHODS FOR IC RADIOS

BY

#### LUIS MARTINEZ

### BACHELORS OF SCIENCE IN COMPUTER ENGINEERING, UNIVERSITY OF NEW MEXICO, 2006

#### THESIS

Submitted in Partial Fulfillment of the Requirements for the Degree of

#### Master of Science in Computer Engineering

The University of New Mexico Albuquerque, New Mexico

December 2010

© 2010, Luis Martinez

#### **ACKNOWLEDGEMENTS**:

I herby acknowledge the great support and help of Dr. Jacob Rael of Broadcom Corp for his guidance, support, and instruction regarding IC radio design and testing. Through the long process of this project he showed great patience and provided valuable insight and ideas. I would also like to thank Guillermo Loyola or Broadcom Corp for his contributions to the JTAG portion of this thesis and his excellent instruction on interfacing RF chips and control machines. Finally, I would like to thank my advisor Dr. Ramiro Jordan for his patience and guidance throughout my graduate education and his help organizing and formatting this thesis.

### AGILE TESTING METHODS FOR IC RADIOS

BY

#### LUIS MARTINEZ

#### ABSTRACT OF THESIS

Submitted in Partial Fulfillment of the Requirements for the Degree of

### Master of Science in Computer Engineering

The University of New Mexico Albuquerque, New Mexico

December 2010

#### AGILE TESTING METHODS FOR IC RADIOS

BY

#### LUIS MARTINEZ

B.S., Computer Engineering, University of New Mexico, 2006

M.S., Computer Engineering, University of New Mexico, 2010

#### ABSTRACT

This thesis concentrates on the development of a new testing procedure for the radio used in Broadcom's WLAN and cellular chips. Verification and hardware testing for the radio is completed at the end of the development cycle by the fabrication of test chips which contain only radio specific hardware. Utilizing test chips allow for component specific design verification, performance analysis and debugging of the Integrated Circuit (IC) radio before large scale production. In this thesis we present a new testing method that is intended to improve the development time, lower costs, and provide more agility within the IC radio testing process. This thesis takes an in depth look at the development and deployment of these new testing methods. It provides an examination of the hardware requirements for testing IC radios and the software developed to automate test development and control testing procedures. The main components developed for this project are the Chip Communications and Control Module and the Phase-Locked Loop controller. Respectively, these components were designed to control the operation of a test chip and configure the mechanism that locks the chip's RF signal to a desired frequency. Previous testing methods include the use of Automated Testing Equipment (ATE) and small scale test platforms built around LabVIEW. These testing methods can be costly, impractical, require longer development cycles, and are not contusive to agile methodologies. The new procedures attempt to provide a better test platform for WLAN radios by addressing these issues and matching or exceeding the requirements of the previous test platforms.

# TABLE OF CONTENTS

| LIST OF FIGURES ix          |

|-----------------------------|

| LIST OF TABLES              |

| Chapter 1 1                 |

| Introduction:               |

| Background:                 |

| Current Techniques:         |

| Evolving Methodology:       |

| Summary:                    |

| Chapter 2                   |

| Introduction:               |

| JTAG Interface:             |

| JTAG Circuit Design:        |

| Handling Read/Write:        |

| Testing the JTAG:           |

| Summary:                    |

| Chapter 3                   |

| Introduction:               |

| Applying Baseband Settings: |

| Excel File Description:     |

| Python Automation:          |

| Decoding the Excel File:    |

| Calculating the Register Values:            |    |

|---------------------------------------------|----|

| Auto Generation TCL Procedures:             |    |

| Summary:                                    |    |

| Chapter 4                                   |    |

| Introduction:                               |    |

| The Chip Control and Communications Module: |    |

| Manipulating Register Data in TCL:          |    |

| Summary:                                    |    |

| Chapter 5                                   |    |

| Introduction:                               |    |

| The PLL in Depth:                           |    |

| The PLL Controller:                         |    |

| Summary:                                    | 50 |

| Chapter 5                                   | 52 |

| Introduction:                               | 52 |

| The Bring-Up Process:                       | 52 |

| Locking the PLL:                            | 55 |

| Unexpected Problems:                        | 56 |

| Summary:                                    | 59 |

| Chapter 6                                   | 60 |

| Introduction:                               | 60 |

| Additional Test Procedures:                 | 60 |

| Working in Parallel:                        | 60 |

| Python Automation for Large Procedures:         |

|-------------------------------------------------|

| Summary:                                        |

| Chapter 7                                       |

| Introduction:                                   |

| Compiling EpiDiag for Windows:                  |

| Using EpiDiag with Windows:                     |

| Summary:                                        |

| Chapter 8                                       |

| Introduction:                                   |

| The Performance of the Test Platform:           |

| Comparison to Pervious Platforms:               |

| Future Work:                                    |

| Conclusion: 69                                  |

| References:                                     |

| Appendix A: tc_reg_gen.py72                     |

| Appendix B: CCCM Initialization and Utilities76 |

| Appendix C: CCCM Format Register Function 80    |

| Appendix D: CCCM RF_PLL Function                |

# LIST OF FIGURES

| Figure 1 10  |

|--------------|

| Figure 2 11  |

| Figure 3 15  |

| Figure 4     |

| Figure 5 19  |

| Figure 6     |

| Figure 7     |

| Figure 8     |

| Figure 9     |

| Figure 10    |

| Figure 11 54 |

| Figure 12 55 |

| Figure 13 57 |

| Figure 14    |

| Figure 15    |

# LIST OF TABLES

| Table 1 | <br> |

|---------|------|

| Table 2 | <br> |

| Table 3 | <br> |

# **Chapter 1**

#### Introduction:

A common trait among test engineers is an insatiable obsession with control. Verification of test results requires patience, awareness and a strict regimen. Every variable must be accounted for and every scenario must be attended to. These goals, however, are in direct conflict with other extremely important aspects a test engineer must consider; speed and efficiency. In the design and application of integrated circuits (ICs), testing is oftentimes a bottleneck in the cycle of development. Although the ability to have governance of each and every variable in a controlled test environment is desirable, the practicality of doing so becomes increasingly difficult as the scale of an IC project grows. Ideally, testing will be fast, efficient, robust and cost effective.

Testing semiconductor circuits takes place in all stages of development. Before fabrication, circuit design is completed through simulation. During fabrication, parametric probe testing is used to check circuit continuity and interconnectivity issues during fabrication. Post fabrication, multiprobe testing is applied to a processed silicon wafer before the chips are cast into individual die. Multiprobe tests provide a variety of functional testing and are designed to quickly identify problems that may arise during fabrication. Final testing occurs as chips are separated from the wafer and packaged as individual units. In this stage, chips are run as they would be used in real world situations and to find issues that may have escaped previous testing.

For final testing, an IC may have many thousand individual programmable signals, each with a significant role to play in the function of the circuit. Because of the complexity involved in testing packaged ICs and a general lack of programming knowledge, there are many tools that offer a layer of abstraction. Tools such as LabVIEW and ChipScope are used for this exact purpose and they have made significant improvements in IC design and testing. Other innovations such as Automated Testing Environments (ATE) allow large scale testing of integrated circuits with little to no human involvement whatsoever. But what happens when testing? What happens when situations arise that are not helped, but hindered by the layer of abstraction which is intended to help the testing process? How do you bring costs down during final testing, and still provide adequate testing tools? This thesis will discuss the design and implementation of a text based testing method that is specifically applied to radio ICs. This test design provides a layer of abstraction, while offering other benefits such as better scalability, ease of development and version control. Completing the tasks require the utilization of many engineering disciplines. This includes software programming, IC design, IC testing, circuit design, and system integration. Much attention is given to the capabilities and resources of the Linux operating system and the examination of commercial and public software. The methods designed for this project were architected and implemented specifically for Radio test chips. This method was developed in conjunction with Broadcom Corporation for the Radio group in Broadcom's wireless LAN division and provides many industry implications.

#### Background:

In digital communications, a Radio refers to a device that can transmit or receive signals through modulation of electromagnetic waves with frequencies below that of visible light [9]. A radio will tune to a specified frequency and either broadcast or receive signals at that frequency. Radio ICs are integral components to a large array of wireless technologies. Wi-Fi, Wireless LAN and Bluetooth are just three examples of technologies that use radio frequency as a means of communication. Testing radio ICs proves to be an interesting challenge because of the scale of the device. Simulation and virtual testing is an important aspect of IC design, but it does not address real world situations that often arise during manufacture. As described in the article Virtual Tests Comes of Age, "while test simulation software is expected to reduce test time, it will not eliminate the need for real test" [10]. Their designs are not large enough to necessitate the use of Automated Testing Equipment (ATE), but large enough to require a sophisticated testing environment. Radios are developed as a System on Chip (SoC), which is to say it will be part of a chip that performs a number of different functions. After a radio is designed and simulated, it is fabricated into a test chip. A radio test chip is an intermediary implementation that is fabricated with the intention of verifying a design and testing for bugs on a platform that is completely isolated from a larger implementation, such as a WLAN chip. Obviously, the intention behind the fabrication of a test chip is to verify the radio's functionality before it is integrated into a larger design.

ATE greatly increases the ability to quickly and accurately test printed circuit boards (PCBs), ICs, and a number of related electronic components. In electronics ATE is

especially useful for large scale functional testing [7]. This technique involves applying a set of inputs to a device, then comparing the reported outputs to a set of expected outputs. Functional testing is ideal for production chips because it allows a test engineer to quickly test a high volume of units, commonly referred to as Units Under Test (UUT), to quickly identify and sort problematic units. The goal in testing a production chip with ATE is simply to determine where on the chip a defect, if any, is present. Once this is determined, the chip is sent back to a group of specialists in the area. Therefore, if ATE discovered a problem with the radio, it would be reported back to the radio group. For test chips, however, ATE is impractical and expensive.

Cost and scalability are the largest drawbacks for using ATE to test radio ICs. In an article for the EE times, Steve Carlson states, "the cost of testing complex system-on-chip designs will soon surpass the cost of manufacturing them [8]." One reason for this is scalability. In the same article, Carlson describes some of the costs, "for complex, high-speed SoC devices, testers cost between \$2,000 and \$9,000 per pin [8]." This is a common problem in IC design as it is often necessary to add new pins as design improvements and specification continually changes. Using the cost per pin described in Steve Carlson's article, if just ten chips are produced with fifty pins per chip the cost of ATE equipment would run between one million and four million dollars. This is before factoring the costs of setup, calibration and maintenance for the ATE equipment. For large companies like Broadcom it is not uncommon to design and fabricate eight to twelve test chips per year. Although it is always desirable to automate as much of any procedure as possible, it is just too expensive to continually develop thorough ATE for a

test chip. Also, at this stage in testing ICs it is extremely beneficial to have more interaction with the UUT than is commonly practiced using ATE. In order to save costs and allow for a more hands on interaction with the chip, a small scale test platform is needed.

#### **Current Techniques:**

Testing a radio requires the cooperation of a large group of people and often a diverse range of expertise. This group must decide on a test platform that ideally is easy to use, scalable, supports parallel development, and is highly customizable. The two major components for designing a design platform for a test chip are the physical interface and a software controller. The PCB board, which from this point on will be referred to as a test-board, is designed to allow interaction with the test chip. Most times, reading and writing to the chip is facilitated by a Joint Test Action Group (JTAG) interface. This interface will be expanded upon in the next Chapter. Software, such as National Instrument's LabVIEW or Agilent's Vee, is then used to create modules that will facilitate reading and writing to the chip and the programming of the chip's registers. Broadcom employs the use of LabVIEW for testing IC Radios. LabVIEW Modules are used for a variety of tasks, but the two most important are setting the radio's registers and controlling the Phase-Locked Loop (PLL). Setting the radio registers allows the test engineer to control the functional state of the radio. Specific configurations of the registers can determine if the radio is transmitting or receiving a signal, what frequency the radio is dialed to, and many other functions of the radio. The PLL will be covered in depth in Chapter 4. It is a device that is used by the radio in order to generate a stable frequency in which the radio 'locks' to and subsequently transmits or receives signals at.

The LabVIEW module for the PLL controller is the most complex and most important software module for testing IC radios. If the PLL controller does not work properly there is an extremely limited amount of testing that can be applied to the radio.

Although they can be very useful, there are many drawbacks to using commercial software like LabVIEW. Because LabVIEW is proprietary software, it costs money for each machine it is installed on. Also, because it is proprietary, there are no third party standards committees that manage LabVIEW such as there are using common programming languages [11]. Support for non Windows platforms is poor [11]. This means that although compatible with Linux and Apple LabVIEW is mostly used as a Windows application. LabVIEW ties the creation of user interfaces into a development cycle. It uses a graphical interface that allows non-programmers to build programs by dragging and dropping virtual representations of common electronic equipment and protocols. Hence, it can be inferred that a non-programmer can develop object oriented LabVIEW code, also known as G-code. Furthermore, it is fairly easy for a test engineer with little to no exposure to LabVIEW to create very simple LabVIEW modules. For complex models and large-scale projects, however, it becomes more important that a LabVIEW programmer posses an extensive knowledge of special LabVIEW syntax and tools. This requirement is one of the reasons that LabVIEW is not the optimal option for radio test chips.

Developing an interface for a radio test chip is a larger scale project and requires extensive knowledge of LabVIEW syntax. This requires some level of expertise and with so many people using their expertise in other areas it becomes increasingly difficult for a large group of people to develop effective LabVIEW modules. As such, the responsibility of developing LabVIEW code is given to very few individuals. Instead of having a test procedure that would allow many individuals to utilize their expertise to develop procedures for the interaction software, there is deficit of available resources. Also, LabVIEW on a Windows operating system is somewhat more difficult when using repository systems. Without the use of a repository, there is no simple way to ensure that a LabVIEW module is up to date or that the same version of a module is being used by a large group of people.

Perhaps the largest drawback for using LabVIEW in the test platform of IC radios is the apparent difficulty to quickly modify or expand a LabVIEW module. As the speed of the development cycle continues to increase, so does the benefit for agile testing methods. Requirements for testing applications can change very quickly and, therefore, modifications and expansions to the test platform must also be completed quickly. Too often, when using LabVIEW, a module must be fully recreated due to a minor design change. For example, a recent update of a Broadcom radio included an increase in register width from eight to nine bits. This seemingly simple change required the entire test platform to be rewritten to accommodate the extra bit. Finally, because LabVIEW is a graphical based programming language, it is difficult to automate the creation of LabVIEW code. This is especially prevalent for simple yet tedious tasks, such as correctly programming a large number of registers to a predetermined value.

At Broadcom, there are alternative tools that can be utilized to test production chips. Dr. Guillermo Loyola of Broadcom Corporation wrote an in house built test suite, EpiDiag. It allows for interface with chips through both JTAG and PCI interfaces. EpiDiag is used with the Linux operating system and has many of the characteristics that would benefit the current test chip procedures. It is compatible with CVS and highly customizable. An individual can modify his EpiDiag workspace by writing some simple procedures using the TCL language. EpiDiag is often used to test production chips and other ICs that do not require extensive register level programming. To this point, it had never been applied to test chips, which were largely tested using LabVIEW platforms.

#### Evolving Methodology:

IC design is a constantly evolving discipline, and testing should be a part of that evolution, not a relic that hinders progress. For this reason, it was paramount that a new testing procedure be developed to address the issues of the previous test platform. The new testing procedure should be scalable, allow for more automation, allow easy use with a centralized repository system, be highly customizable, allow for parallel development, and allow for more versatility in testing. Dr. Jacob Rael of Broadcom Corporation proposed using TCL procedures similar to what would be found in the EpiDiag test tool, while using Python to automate some of the more repetitive tasks. The test platform would be ideal for the Linux environment Broadcom employs for IC design and simulation and be more compatible with the current CVS repository. A Linux based test platform would also be compatible with EpiDiag, and thus include an existing JTAG controller and TCL interpreter. The desire to incorporate these features into the IC radio test platform, as well as mounting frustration using LabVIEW based methods, was the motivation for this project.

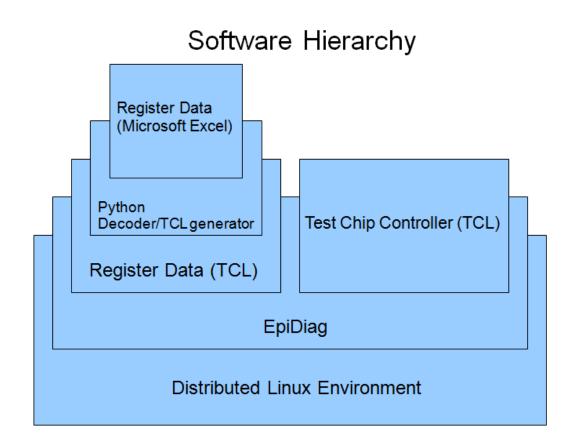

The first requirement to consider for the new test platform was the software. The software had to be able to perform all tasks completed using LabVIEW. The minimum requirements were to facilitate data I/O, interface with the radio test chip, and control the radio's PLL. In order to improve the test platform, the software was also required to be more agile in development, easier to manipulate, allow for more automation and be more contusive to parallel development. Linux was used as the primary operating system for the test system, which will be referred to as simply the Linux test environment. Using Linux, many of the necessary tools are already in place. Also, the distributed nature of the file system is beneficial to agile code development. Using tools already incorporated in Broadcom's distributed Linux OS, we could write Python code to encode/decode register data from the radio design into the testing environment, use TCL to develop a facilitator for the data flow, and use EpiDiag to interface the PC hardware and the chip. The software hierarchy is shown in Figure 1.

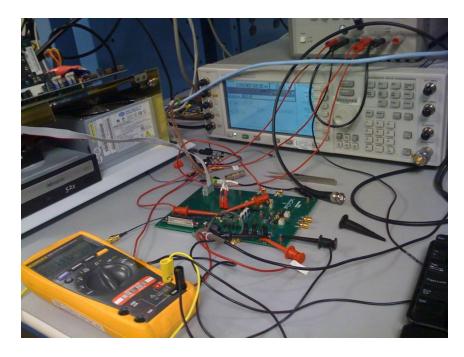

#### Figure 1 - A visual representation of the software hierarchy of the test platform

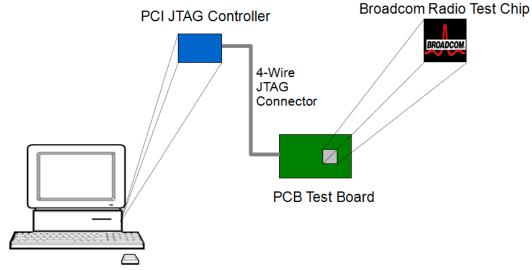

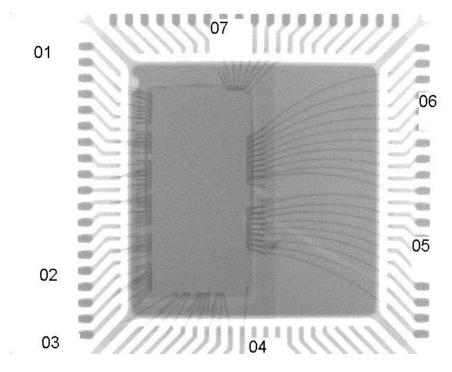

The second important aspect to consider was the hardware requirements. For this project, it was necessary to interface the chip with the controlling software. The standard procedure is to connect the control PC to a test-board that houses the chip via JTAG. This method was not altered, however certain changes for the JTAG circuit needed to be applied. This is discussed further in Chapter 2. The hardware connectivity is demonstrated in Figure 2.

# **Hardware Configuration**

Linux PC connected to Distributed Linux Environment

#### **Figure 2** – An illustration demonstrating the hardware configuration

This thesis will discuss all aspects of this new testing method. Chapter 2 will focus on the development of a JTAG interface that can be easily transferred from one test chip to another. Chapter 3 will focus on the application of the register data to the test chip. Chapter 4 will discuss a PLL and give an overview of the PLL controller that is written in the TCL language. Chapter 5 will discuss the "bring-up" process-which is the moment these tools are applied for the first time to a new test chip, in order to lock a PLL to a specific frequency. Chapter 6 will discuss the development of new test procedures and parallel development. Chapter 7 will discuss the application of this test suite to the Microsoft Windows operating system, and finally, Chapter 8 will discuss future work and conclusions.

#### Summary:

This Chapter is used as an introduction to IC radio testing and some of the problems encountered in current testing methods. In the introduction some of the basic concepts of IC testing are discussed such as when testing takes place in the development cycle and why it is such an important issue in IC design. There is also a brief introduction to ATE and LabVIEW and how they fit in the testing at Broadcom Corp. Near the end of the introduction there is a small discussion of the issues in IC radio testing using current techniques and an introduction to the testing methods presented in this thesis.

The next section of Chapter 1 discusses some of the background of IC radio testing at Broadcom. ATE testing, while very beneficial for large scale production chips, is much too expensive for test chips and small scale testing. Small scale testing involves the use of proprietary software such as LabVIEW, which comes with its own drawbacks such as development time, parallel development, modifications, expandability automation. The final section gives a brief overview of the Linux Test platform which was developed in an effort to remedy some of the shortcomings of LabVIEW based test platforms. The software and hardware hierarchies are introduced as well as the basic requirements of the test platform. Finally, the last section describes some of the benefits of the new test platform when compared to ATE and LabVIEW based test platforms. These include agility, modifiability, expandability, easier automation, and cost.

### **Chapter 2**

#### Introduction:

In order to properly test a chip a physical interface is required. There are a variety of physical interfaces that are capable of relaying control signals to and from a chip yet all serve the similar functions of applying power to the chip and providing a data I/O between the chip and a control system. This Chapter will focus on the JTAG interface, which is the transport control mechanism that facilitates the interaction between the chip and the control system for this project. JTAG is the common name for the IEEE 1149.1 standard for test access points as a method to test populated circuit boards and evolved into a commonly used method to debug integrated circuits [1]. In this Chapter there will be a brief introduction to the JTAG interface followed by descriptions of the JTAG circuit used for the project's test-board, how the JTAG controls are handled in software, and the verification of JTAG functionality for the project.

#### JTAG Interface:

As previously discussed, ATE is a powerful tool that greatly improves testing large quantities of chips; however it is nearly impossible to write ATE software that can anticipate each and every problem that may occur. Many Functional tests are done in the lab under the strict observation of a test engineer. Each chip has a test-board that allows direct interface with each input and output pin. While some chips use PCI or PCIe interfaces, the vast majority of all test boards are controlled using a JTAG interface. PCI and PCIe test boards do not utilize a JTAG sockets or JTAG busses, but still employ JTAG signals. The radio test chips that were used for this project were designed to use a

JTAG socket and bus. The JTAG interface is a special four or five-wire pin interface that is added to a chip. The connector pins are [1]:

- Test Data In (TDI)

- Test Data Out (TDO)

- Test Clock (TCK)

- Test Mode Select (TMS)

- Test Reset (TRST)

JTAG is a serial interface meaning there is only one data line available for input or output. The operating frequency of TCK is typically between 10-100MHz. Depending on if it is a read operation or write operation, one bit of data is transferred per clock cycle on the TDI or TDO wire.

JTAG support is available in EpiDiag and the tool can be used as a JTAG wrapper. A JTAG card is used to control JTAG signal flow and connects to a PC via a PCI slot. At Broadcom, JTAG cards utilize a 20MHz crystal oscillator. The PCI JTAG card has a five-wire JTAG pin interface and can facilitate the JTAG clock. This card is referred to as the JTAG master. EpiDiag's role is primarily to facilitate the clock of the PCI JTAG card and to encode/decode the JTAG signals. Until this point, EpiDiag had never been tested as being capable of interfacing a JTAG card with a test chip.

#### JTAG Circuit Design:

The JTAG circuit that was utilized on the test-board was designed to be simple and reliable. It was based on a circuit previously used for Broadcom test boards. Because EpiDiag had never been used to interface with a test chip, it was desireable to create a

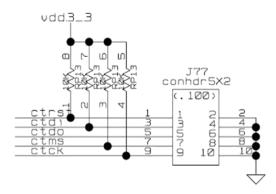

JTAG circuit with as little latency as possible. Figure 3 displays a JTAG pin socket with each wire connected to a 10k pull-up resistor. The JTAG interface between the test board and the JTAG signals at the pin socket operate at 3.3V.

**Figure 3 – The JTAG socket**

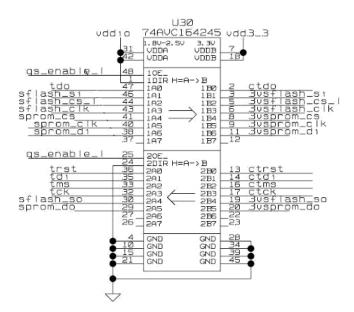

Figure 4 displays a bus buffer, which converts the 3.3V input signal to 1.2V. This is the operating voltage at the chip level. The signals for TCK, TDI, TMS, and TRST are input signals and are down-converted. The TDO signal is up-converted through the buffer from 1.2V to 3.3V. The buffer for this circuit is the, the Texas Instruments Quadruple Bus Buffer Gate [11]. This buffer was chosen due to its low latency for voltage conversion.

**Figure 4 – The JTAG signal mapping**

#### Handling Read/Write:

Reading and writing to a test-board is a large task due to the large number of registers that require setting for the radio test chip. Although most of this process is automated, there are procedures contained in EpiDiag that allow more direct control of the JTAG read and write functions. Unfortunately, this functionality had never been applied to test chips. Before this test method could be implemented, it was necessary to verify the ability to directly read and write to a JTAG register on the test chip using EpiDiag.

In order to read and write to a JTAG register, the JTAG master must first be configured to operate with the test chip's JTAG interface. This can be done using the TCL language and be incorporated into the overall test procedure. A test chip generally has registers with addresses between eight and ten bits in length, which eight bit data payloads. There is a special radio ID register that identifies the radio ID and version number. This register has a data payload of thirty-two bits. The 'jtag config' command is a special EpiDiag syntax that is used to adjust properties of the JTAG interface. The following code shows this initial setup of the address, the data registers and the clock divider on the JTAG to its highest possible value. Increasing the value of the clock divider will slow the frequency of the JTAG signals.

set addr\_len 10

set data\_len 8

set id\_len 32

jtag config clkd 30

jtag config ir \$addr\_len

jtag config dr \$id len

Writing to the radio is a straightforward process. The command for writing in EpiDiag is 'jtag writereg' and you need only to supply the destination address and the value to be stored at that address. The address must be in hexadecimal format, but the value can be hexadecimal or binary. Reading from the JTAG however, is somewhat tricky. Similar to the write command, the command to read from a register is 'jtag readreg', however the address for the readback path is offset. The offset itself is of varying magnitude. The general idea is that the offset is related to the total number of JTAG registers. If there are between 0x0 and 0x99 registers, the offset would to be 0x100 in hexadecimal. For example, if the offset is 0x100 and a value is written to address 0x4 then to read that value stored in at address 0x04, would read back from register 0x104. Similarly, if there are between 0x100 and 0x199 registers the offset is 0x200. An address stored in register 0x4 would be read back from register 0x204. For this project, the offset is 0x200. The code to readback from a register is shown below. The special case in the 'if' condition

refers to the radio ID register. When this is detected, the data length of the read register must be placed at thirty-two bits.

```

if {$addr != 0x01} {

set addr [expr $addr + 0x200]

set readval [jtag readreg $addr]

return $readval

}

```

#### Testing the JTAG:

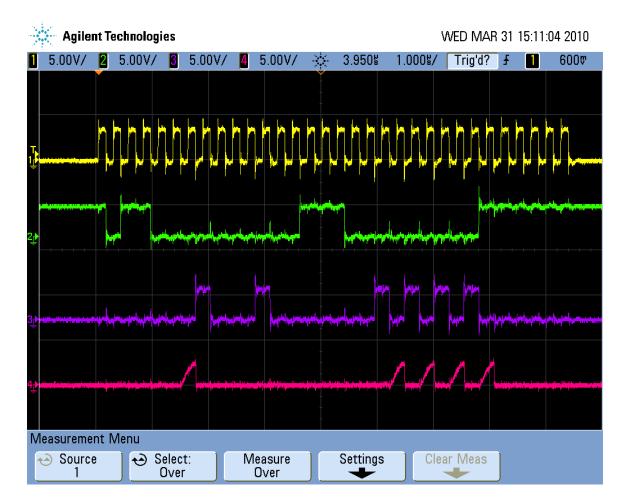

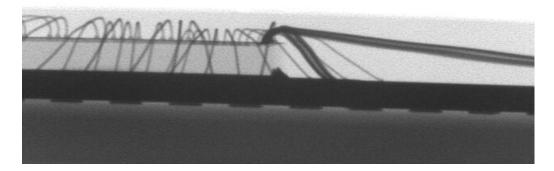

Testing of the JTAG consisted simply of reading and writing to a specific register using a distinct value such as 0x5a. The initial results were inconsistent, as some registers would read back the incorrect values while others appeared to be fully functional. This process was recreated in LabVIEW in an attempt to recreate the readback issue, however the LabVIEW test was able to prove the JTAG interface for the test chip and test-board was functioning properly. The next step was to trace the voltages of the signals from the board to the chip using a multi-meter to confirm the proper voltages from the JTAG socket to the chip. To enable measurements, the JTAG signals were set to continuously transmit on a loop. Using this technique, the proper voltages for each signal were traced before and after the buffer. The next test was to inspect the waveform of each signal with an oscilloscope, the results of which can be seen in Figure 5 along with a description of the signals.

Figure 5 – Oscilloscope probe displaying the JTAG signals

- Channel 1/Yellow- TCLK

- Channel 2/Green TMS

- Channel 3/Purple TDI

- Channel 4/Pink- TDO

When measured at the JTAG socket, it is clear the TDO signal is weaker than the others as there is some signal loss apparent on the TDO wire. The solution to this problem was to slow down the clock of the JTAG master enough to handle the relatively weak signal, the crystal of the JTAG master was swapped from 20 MHz to 12 MHz, and the clock

divider of the JTAG master was set to its highest possible value. This resulted in a significantly slower JTAG. The signals ran at roughly 4 MHz as opposed to the usual 20 MHz. By slowing the JTAG signals, the readback function was now able to work reliably. Although the read/write for the JTAG is much slower than it would be using LabVIEW, for testing the radio the difference in speed is negligible.

#### Summary:

This Chapter focused on the development of the JTAG interface of the test platform and discussed the problems encountered and how they were resolved. Next, a brief overview of the JTAG interface was given as well as a description of the TMS, TDI, TDO and TCLK signals. A description of the physical components of the JTAG interface was given. This portion described how the JTAG signals are relayed from a lab computer running on Linux, to a PCI JTAG card, to a PCB test board and finally to the test chip itself. The physical JTAG circuit that was designed for this project was then illustrated. At this point there was a description of the buffer that was used to up and down convert the JTAG signals from 3.3V to 1.2V and vice-versa.

The second half of this Chapter dealt with configuring and utilizing EpiDiag, a proprietary Broadcom utility, to control the JTAG interface. There were also code examples that displayed how EpiDiag could be configured to work with a wide variety of JTAG interfaces and how to read and write to registers. Special attention was given to the differences in read and write addressing when using JTAG. Finally, there was a description of how the JTAG circuit was tested and debugged as well as a description of the challenges in this process.

# Chapter 3

#### Introduction:

A radio functions as a state machine. By design, there are many programmable registers that can be set with binary strings. Changing the values of the programmable registers will alter the function of the radio. A major challenge in testing IC radios is correctly setting the programmable registers to achieve the desired radio state. Such is the topic of this Chapter. The first section describes the need for simulating the baseband settings for a test chip. The second section gives a description of the Microsoft Excel file that contains the state information of the radio. The next two sections how the Python programming language is used to parse the Excel file. The penultimate section of Chapter 3 describes how correct hexadecimal values are calculated for each register for a given radio state. The final section describes how TCL code that will be used to set a register state is auto generated in Python.

#### Applying Baseband Settings:

The baseband of a signal describes a range of frequencies from zero to the highest possible frequency for that signal. Technologies that transmit information using a baseband carrier include Ethernet and Composite Video. Wireless transmission at low frequencies will incur a lot of distortion and cannot be transmitted at the baseband frequency. In wireless communications, the baseband is modulated to a much higher frequency in order to allow for transmission at a higher radio frequency [12]. A consequence of the shifting is that the RF bandwidth of a signal is usually twice that of its

baseband bandwidth [12]. When a radio frequency is received by an antenna, it will be demodulated back to the baseband, thus the baseband in RF communications can be considered as the range of frequencies for a signal before and after frequency modulation.

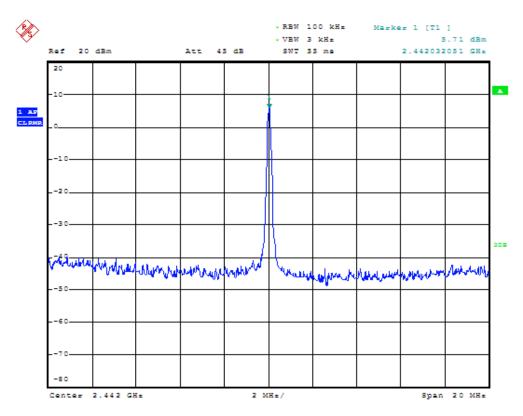

A major difference between a production WLAN chip and a radio test chip is that there is no baseband signal configuration present on a radio test chip. The presence of a baseband signal configuration allows a production chip to function in a specific radio mode. When a radio mode is selected, the programmable registers on the chip are loaded with specific register values that configure the chip to operate in the selected mode. For example, the chip may be configured to transmit at 2.442GHz. For test chips, the baseband configuration must be applied to programmable registers on the chip manually. This configuration is developed during the design of the chip and includes the same values that will be loaded onto production chips. For instance, the radio that was tested has a set of existing settings for transmission in G band (frequency range of 2.4GHz to 2.5GHz), receiving in G band, transmission in a band (frequency range of 4.7GHz to 6GHz), receiving in a band, and many other modes of operation. The documentation for the baseband signals is stored in Microsoft Excel files. With the LabVIEW model, the baseband signals would be manually added to new LabVIEW module for each test chip. This practice was tedious and left room for errors. This Chapter will discuss methods to generate TCL procedures using Python, translate Microsoft Excel Data into TCL code, and how to format register data using TCL.

#### Excel File Description:

During the design and simulation of a radio, Microsoft Excel becomes a powerful tool. It allows a design team to organize data in a very readable and useful manner. When designing a radio, the design team creates a JTAG register map that maps each JTAG register to a specific address. The JTAG register map also lists which fields or ports are present in each register. The term 'port' is simply a reference to a connection pin from the register on the chip to an external I/O signal. A port can refer to a 1 bit wire or multibit bus. In the JTAG register map, the port for each register is assigned a starting bit, stopping bit, reset value, preferred value and a brief description.

Microsoft Excel is also used to store and organize radio configuration data. A radio configuration file is simply a mapping of the JTAG ports of a radio to specific hexadecimal values. When these bits are instantiated on the radio, the radio will be configured to a specific state. Common states for the radio include transmit, receive and configuration. In order to centralize the data for this project, a single file was created that was called the JTAG Master. The JTAG Master is an Excel file organized by worksheet. The first Excel worksheet was reserved for the JTAG register map, while each subsequent worksheet was devoted to configuration data for a specific radio state. Organizing this data into a single file has the benefits of having a single point of reference for register information and allowing version control using a repository such as CVS.

The first portion of this document to be discussed in detail is the register map or JTAG register description. The register map is simply a document that provides a detailed description for each programmable register used by the radio. Registers are organized by address and, with the exception of the radio ID register, most have a data payload of eight bits. A subset of the register data is the field name for each signal. The field name is an English abstraction that is used to describe a digital signal in the radio. A field name has a corresponding start bit, end bit and reset value. Table 1 gives a brief description of the important categories in the JTAG description.

| Element       | Description                                                                                                                      |

|---------------|----------------------------------------------------------------------------------------------------------------------------------|

| register_name | A name or placeholder for each register. If none is given the default is REG[address]                                            |

| Address       | The hexadecimal address for each register                                                                                        |

| field_name    | A description of bits associated with specific digital signals on the chip.<br>Will also provide a width in big-endian notation. |

| start_bit     | The least significant bit for a corresponding field_name and register                                                            |

| end_bit       | The most significant bit for a corresponding field_name and register                                                             |

| reset_value   | The default value for a field_name if none is given in the baseband description.                                                 |

| Documentation | A small description of the field_name, including any special notes for programming.                                              |

| RTL_Name      | The RTL name for a field_name used in simulation. Is equivalent to field_name.                                                   |

| Table 1 – Example | of the register | r information | from the | Register <b>N</b> | <b>Jap Excel File</b> |

|-------------------|-----------------|---------------|----------|-------------------|-----------------------|

|                   |                 |               |          |                   | r                     |

The radio state is a mapping between the field names for each programmable register in the radio and their corresponding binary and hexadecimal values. Each radio state has unique set of values that are programmed to the chip. The radio states for transmit and receive in 'G' band, for example, have vastly different register values. There is a one to one mapping between a field name and a given value. This value is represented in both hexadecimal and binary format. Table 2 gives an example for a field name, the corresponding hexadecimal value, and corresponding binary value for a register that is configured to transmit in 'G' band.

| Transmit in 'G' band      |           |           |  |

|---------------------------|-----------|-----------|--|

| field_name                | Hex Value | Bin Value |  |

| i_wrf_jtag_bandgap_B<3:0> | 0x6       | 0110      |  |

Table 2 – Table displaying an entry in the Radio State Excel file

It is important to differentiate between the different radio states and to assign the correct binary value to the correct field name in the correct register. This process is outlined in the next section.

# **Python Automation:**

The Python programming language is an extremely versatile scripting language that can be used for an impressive array of tasks. Python can be used for simple calculations and scripting or for massive object-oriented programs. For this project, Python was an invaluable tool used for a variety of tasks, but the single most important was the translation of the JTAG registers from the Excel file into a TCL procedure. With the previous test platform, a test engineer would develop a LabVIEW module for each register state. For each LabVIEW module he would manually configure each register setting to match the data given in the Excel file. This is a long and tedious process and prone to mistakes. With the Linux test platform, a Python script was developed to automate this process. The script could be used to parse the Excel file, decode the register value, and store the value in a data structure that maps it to the correct hexadecimal register data to its register address. Automating this process using Python scripting saves large amounts of time and greatly reduces errors.

Once again, the purpose of the Python code is to parse the Excel file, decode the data and then auto-generate a TCL script that will have procedures that can be sourced to the test chip. There are unique tools and challenges for each portion, which are outlined below.

- A special tool is needed to parse a Microsoft Excel file using Python (this is not completely true as it is possible to create custom code to do just that, but that would be a thesis in itself). This is made possible with the use of a Python module named XLRD [3]. XLRD makes it possible for Python to decode data Microsoft Excel documents. Using XLRD, each cell of an Excel document can be saved into a Python data structure.

- Python does not natively support binary values. Character strings can be used to represent a binary value, but these are not mutable objects. There are tools

26

available that can treat a binary string as a mutable object. To do so, the MyHDL module is imported into the Python script. The MyHDL module is used to enable functions commonly associated with hardware description languages including classes for signal generation and simulation [2]. The intbv class allows binary strings to be interpreted as integers, which are mutable objects.

# Decoding the Excel File:

In order to create a baseband we must first decode and store all relevant information from the JTAG description of the Excel file. For this we need to import a Python module called xlrd, which will interface Python with Microsoft Excel and make it possible to read from an Excel document. Using commands from xlrd, we are able to open an Excel document with the following commands:

```

wb = open_workbook(register_settings_xls)

wb.sheet_names()

sh_final = wb.sheet_by_name(u'JTAG_final')

```

Using the preceding code, it is possible to open an excel document, and then load all data from the Excel workbook titled 'JTAG\_final' into a Python object called sh\_final. This object is similar to a two-dimensional array, and is indexed by row and column. Accessing the object sh\_final.cell\_value(0,0) will return the value placed into cell (0,A) from the Excel file. The Excel values are placed into Python data structures called dictionaries and lists [5]. A Python list is similar to an array or queue. It is an iterable object that has elements indexed by position. Unlike C or C++ arrays, Python lists are not typed, and may contain integers, strings, floats and any other Python object in a single list. A Python dictionary is a hashable object that is indexed by an immutable object (integers, floating point values, strings, etc.) called a key. Each key in a dictionary is unique and mapped to an associative 'definition', which can be any type of Python object such as integers, strings, lists, or even other dictionaries.

The JTAG register data is placed into a Python dictionary called, registers. This dictionary is indexed by the addresses of the JTAG registers. The definition for each address key is separate dictionary that is indexed by elements of the register, listed in column 1 of Table1. In this dictionary, the keys have, as their definitions, a list of the values for each element at that address. The data structure is illustrated in Table 2.

| Key: address | Definition: Dictionary with corresponding keys and addresses |                                                   |                              |

|--------------|--------------------------------------------------------------|---------------------------------------------------|------------------------------|

|              | Key: field name parameter                                    | Definition: List of field names in register       |                              |

|              | field_name                                                   |                                                   |                              |

|              |                                                              | Index                                             | Element                      |

|              |                                                              | 0                                                 | NOOP<2:0>                    |

|              |                                                              | 1                                                 | wrf_i_jtag_bb_AACI_TRIM<3:0> |

|              |                                                              | 2                                                 | wrf_i_jtag_bb_AACI_OFF       |

| 0x06         | Key: start bit parameter                                     | Definition: List of start bits for field names in |                              |

|              |                                                              | register                                          |                              |

|              | start_bit                                                    |                                                   |                              |

|              |                                                              | Index                                             | Element                      |

|              |                                                              | 0                                                 | 7                            |

|              |                                                              | 1                                                 | 4                            |

|              |                                                              | 2                                                 | 0                            |

|              | Key: end bit parameter                                       | Definition: List of end bits for field names in   |                              |

|              |                                                              | register                                          |                              |

|              | end_bit                                                      |                                                   |                              |

|              |                                                              | Index                                             | Element                      |

|              |                                                              | 0                                                 | 5                            |

|              |                                                              | 1                                                 | 1                            |

|              |                                                              | 2                                                 | 0                            |

|              | Key: reset parameter                                         | Definition: list of reset values for field names  |                              |

|              |                                                              | in register.                                      |                              |

|              | reset_value                                                  |                                                   |                              |

|              |                                                              | Index                                             | Element                      |

|              |                                                              | 0                                                 | 0                            |

|              |                                                              | 1                                                 | 0                            |

|              |                                                              | 2                                                 | 1                            |

Table 3 – A table displaying the distribution of bits in a register

The code below demonstrates how to decode the Excel object and organize the data into

Python data structures.

```

jtag reg keys = sh final.row values(0)[2:]

for rownum in range(1, sh final.nrows):

if sh final.cell value(rownum, 0)

or sh final.cell value(rownum,0) == 0:

addr name = hex2int(sh final.row values(rownum)[0])

key vals = sh final.row values(rownum)[2:]

tmp = key vals #create list equal to tmp

for x in range(len(jtag reg keys)):

tmp[x] = []

registers[addr name] = dict(zip(jtag reg keys, tmp))

addresses[addr name] = dict(zip(jtag reg keys, tmp))

else:

if sh final.cell value(rownum, 2)[0:6] != 'idcode':

key vals = sh final.row values(rownum)

key vals = key vals [2:]

mytmp = dict(zip(jtag reg keys, key vals))

for cell in mytmp.keys():

registers[addr name][cell].append(mytmp[cell])

```

A similar but much simpler method is used to load each radio state into a Python dictionary. The radio state is a simple one to one mapping between a field name and a binary value. Accordingly, only a single Python dictionary is needed utilizing a registers' field name as the dictionary key and the corresponding binary value as the dictionary definition. The code below demonstrates this process.

```

sh_radio_state = wb.sheet_by_name(xls)

for rownum in range(sh_radio_state.nrows):

radio_state_keys.append(sh_radio_state.cell_value(rownum, 0))

radio_state_bvals.append(sh_radio_state.cell_value(rownum, 2))

bitvals = dict(zip(radio_state_keys, radio_state_bvals))

```

### Calculating the Register Values:

Now that the register map and state values have been loaded into Python, the proper register values must be calculated for each radio state. The writing to a JTAG register via the EpiDiag tool requires the register value to be in hexadecimal format. Calculating this value is not as simple as to add up the value for each field name in a register. This is because a field name is assigned by position in the register. Therefore, if there were eight fields in a register of alternating value between 0 and 1, the register values in binary would be 01010101, which translate to 0x55 in hexadecimal format.

The register values are calculated by determining the binary value for each field name in the register map Excel file. This is accomplished by assigning the binary value of the field name from the radio state Excel file. The field name will match a similar field name found in the register map Excel file. This is simple to do in Python by using the 'has\_key()' method to quickly search for the existence of a key in a dictionary. The following code demonstrates this comparison by parsing each field name in the Python dictionary *addresses*, which is the dictionary containing the register map information. A second Python dictionary called *bitvals* is derived from the radio state Excel file. It contains the mapping of the field names to their binary values. It is here the has\_key() method is used.

```

for x in addresses[addr]['field_name']:

if bitvals.has key(x):

```

If there is a field name in the register map that is not represented in the radio state, that field is given its reset value. If the field name is represented in the *bitvals* dictionary, then the binary value taken from the *bitvals* dictionary is stored in the field. After the binary

values for each fieldname in a register are concatenated, it can be converted into the hexadecimal representation. To do this, the binary string is first converted to an intbv() object. The intbv() method allows the representation of a binary string as an integer value. Because the registers are represented with 8-bit values the intbv() object may repesent any value between 0 and 255. Because this object is interpreted as an integer, it is then converted to hexadecimal format and the register value is completed. The intbv object and final hex value are demonstrated below.

hexbv = hex(intbv(bv,0,256))

hexbv = hexbv.strip('L')

# Auto Generation TCL Procedures:

Writing test procedures in any language is a tedious process. For integrated circuits, this is especially true because most test procedures involve correctly setting a massive amount of registers. Writing long repetitive code by hand takes large amounts of time and is prone to mistakes. Automating these types of tasks saves time, mistakes and most importantly, boredom. After the success of automating code for the baseband registers it was only natural that similar processes would be implemented for other long testing procedures. The test procedures to control the integrated digital to analog converter (IDAC) and the FM tuning registers are especially long. Luckily, the data to control the IDAC and tuning registers is stored in Excel files similar to those that housed the baseband data. Auto-generating the TCL procedures to control the IDAC and the FM Tuning registers was simply a matter of modifying the procedure used to generate the baseband register procedure. Please refer to Appendix C and Appendix D for the code used to generate the IDAC and FM registers respectively.

#### Summary:

Chapter 3 focused on how the baseband register data is decoded from Microsoft Excel data into TCL procedures and how Python can be used to automate the process. Applying the baseband register data will configure the radio for a variety of operational states including those intended for transmission, reception, and calibration. The Excel data is categorized in two parts, the JTAG register map and the Radio Configuration Data. The register map and contains a full description of all programmable registers available in the radio including the address of the register, the ports within the register, and the size and position of each port. The radio configuration data assigns the ports of the radio to hexadecimal values. When the ports of the radio are assigned to these values, the radio is programmed to function in a given state. For example, the TxG state has ports that will enable the radio to transmit data in G band. The second half of the Chapter describes a Python utility named tc\_reg\_gen.py. This utility was written to complete three specific tasks:

- 1. Assigning the value of each port described in the radio configuration file to the correct register position in the register map.

- 2. Calculating an 8-bit hexadecimal value for each register based on the values read from the configuration file.

3. Creating TCL procedures that could transfer the register data to ports on the chip. Auto generation of large blocks of code helps to save time, resources, and reduces bugs or other mistakes that commonly occur when writing large portions of code.

32

# **Chapter 4**

#### Introduction:

In Chapter 2 it was shown that it is possible to read and write to a radio register via JTAG interface and using EpiDiag as a controller, so long as EpiDiag is configured correctly. Chapter 3 demonstrated a method to convert existing register data from a Microsoft Excel file into a TCL procedure. By loading the TCL procedure into EpiDiag, the register data could be written to the radio registers on the chip. The focus of Chapter 4 is the consolidation of these two concepts and various other additional utilities into a single piece of software. The purpose of the software is to provide a means of facilitating all communication and control of the chip. This Chapter will describe the function of the Chip Control and Communication Module (CCCM) while placing special emphasis on some of the more important procedures in the module.

### The Chip Control and Communications Module:

The main objective of the CCCM is to provide a toolbox in which all facets of control and communication with the chip can be called, accessed, and modified. The CCCM is designed as a living code that is constantly evolving and changing. Portions of code can be added by anybody for any specific reason. This is important to the concept of agility in testing. The code is stored in a CVS repository and stable versions are periodically checked in. Anybody with access to the CVS server can import a local copy of the CCCM then edit, customize, or add procedures that suit their specific needs. If a portion of code is useful and can be used by many people, it can be added to the repository version of the code. The CCCM is easily modified and very mutable, but that is not to imply it did not require a comprehensive framework and a complete set of built in utilities. The core functionality of the CCCM is to facilitate data I/O to the chip and the core procedures of the CCCM are encapsulated from the more specialized procedures on the chip. This aids the agility in coding the CCCM as specialized procedures exist independently and do not disrupt the core functionality of the module.

### Manipulating Register Data in TCL:

A large concern for this project was how to manipulate register data using the TCL language. Reading and writing to a register using TCL is extremely easy, however altering specific bits within a register presents a certain set of challenges. Specifically, we needed to answer the following questions:

- 1. How do we convert the integer or hexadecimal data that is read back from a register into a binary representation?

- 2. How do we ensure the size of the binary string remains consistent?

- 3. How do we change a specific bit or range of bits within our binary string without affecting the other bits in the string?

- 4. What is the best way to convert the newly formed binary string back into a hexadecimal representation so it can be written back to a register?

Although Broadcom did have a TCL method to address these issues, they were designed specifically for other applications and were not easily integrated into this test environment. For this reason, the TCL function *format\_register* was created for use with this project. The following is a brief description of how format\_register is used and some

of the more important portions of code that is used in the function. The complete format\_register code can be found in Appendix B.

When the function is called we pass in the initial register data in hex, the starting bit that will be altered, the ending bit that will be altered, and finally the value that will be inserted. The return value is an 8-bit hexadecimal number that can be written back to the register. An example of how to use the function is as follows.

set foo [format reg \$init \$insert 3 1]

In the preceding example if init was set to be 0xff and insert was set to 0x0, then the value returned and set to foo would be 0xf1.

Using TCL to convert the value read back from a register into a binary string is, in theory, extremely simple. TCL has a built in function *binary\_scan* that can be used to return a binary string from a given input value, but there is a heavy reliance on proper formatting of both the input value and return string. The single largest hurdle in using this function is correctly formatting all data. The read function will return data that is stored at a specific address and is interpreted in TCL as a hexadecimal string as opposed to a hexadecimal value [5]. This simply means if we set a variable in TCL it will be interpreted as a string until the variable is parsed using another TCL function. For most built in TCL functions this is not an issue, however, *binary scan* will return a 'type' error when it is passed the hex string read from a register. This can be addressed by simply formatting the hex string as an integer and then reformatting as a hex string. This effective, yet far from elegant fix is shown below:

35

#set variable to register value

set init\_val [read\_radio 0x3]

set init\_val [expr int(\$init\_hex\_str)]

#convert back to hex

set init\_hex\_val [format %x \$init\_val]

Once the input data is properly formatted, we can use the *binary scan* function to convert the reformatted hex string into a binary string. Concurrently, we can control the length of the binary string because the *binary scan* function utilizes many string formatting techniques, including denoting the length of a string. For this project, the registers are always 8-bits wide; hence the binary string is also set to be 8 characters wide. Controlling the width of the binary string is an important task because it helps to control data integrity. The code below demonstrates the use of *binary scan*.

if { \$init\_val > 15 } {

# puts "initial hex val \$init\_hex\_val"

#convert to binary number

binary scan [binary format H2 \$init\_hex\_val] B8 init\_bin\_val

} else {

set init\_msb 0000

binary scan [binary format H2 \$init\_hex\_val] B8 init\_bin\_val

set init\_bin\_val [concat \$init\_msb\$init\_bin\_val]

}

At this point the register data has been properly formatted as a binary string. Similarly, we convert the insertion value using the exact same method. With both the register data and the insertion data now represented as binary strings, we can use the start bit and the end bit to properly slice register's binary string. In TCL, the binary string is indexed as an array starting at 0 from the first character in the string. By contrast the register's byte order is reversed and first character of the binary string would correspond to bit 7 of the register. Because we know the register size, we can retrieve the correct bit from the TCL

array by subtracting both the start and the stop bit from the width of the resister. The most significant bits of the initial binary string are retrieved by slicing from the beginning string to the register width subtracted by the start bit, while the least significant bits are taken by slicing from the register width subtracted by the end bit to the end of the binary string. Concatenating the MSBs with the insertion string with the LSBs creates the new binary string.

Before the new value can be written back into the register, it must be converted back into a hexadecimal value. Formatting strings using functions from the standard TCL library proved to be difficult to implement and test. In order to save time and speed up the coding process the string is again broken into 4 bit segments and mapped directly to corresponding hex values. Finally, the register data is at its final state, and can be written back to the register.

#### Summary:

This Chapter is used as an introduction the CCCM or the Chip Control and Communication Module. The CCCM is the primary facilitator of data in the Linux test environment. The first section of this Chapter is an introduction to the CCCM and an overview of the benefits of having agile code for a project of this nature. The second portion of this Chapter is an overview of some of the challenges involved in controlling I/O data and properly formatting the binary code for the registers on the chip. Some of the more difficult challenges involved altering specific binary values in a register without altering the surrounding values. For this, the format\_register function was developed with

37

the specific requirement of manipulating binary data for a register, while keeping data integrity. The rest of the Chapter concerns how this was accomplished in detail.

# **Chapter 5**

## Introduction:

Phase-locked loops (PLL) are primarily used in communication systems for a variety of applications, such as recovering the clock from digital data signals, performing frequency and phase modulation and demodulation, and to synthesize exact frequencies for receiver tuning. In wireless communications, a PLL is implemented as a digital logic device and incorporated into a microchip. The PLL functions as an oscillator whose frequency is locked onto some frequency component of an input signal [6]. In other words, if a PLL is given a reference frequency of 2.4GHz, the PLL will increase or decrease its own output frequency until it too is 2.4GHz. A PLL performs a similar function to the phase of an input frequency and will also match the phase of a controlled oscillator to the phase of the input signal.

A simpler explanation of PLL is to view it as an example of a negative feedback system [6]. A PLL will compare the frequencies of two signals using a phase detector (PD). The first signal is called a reference frequency and is derived from a very stable source, often a crystal oscillator. The second input is given by feedback from the output of a controlled oscillator. If the signal frequencies do not match each other, an error signal is produced. This error signal is proportional to the difference between the two frequencies. The error signal is then passed through a low-pass filter (LPF). The filtered signal is used to drive a voltage-controlled oscillator (VCO), which creates the output frequency. The output frequency is passed through a frequency divider and then back to one of the inputs of the phase detector. This produces a negative feedback loop. If the output frequency diverges

39

away from the input signal, the error signal will increase. This will eventually drive the output frequency in the opposite direction, in order to reduce the error; therefore it is easy to illustrate how the output is "locked" to the reference frequency.

Most electronic systems provide reference frequencies that operate at tens to hundreds of Megahertz. For this project, the reference frequency is a crystal oscillator (XTAL) that has a frequency of 20MHz. The details regarding this will be discussed in the next Chapter. Because the reference frequency for most PLLs are in the tens to hundreds of Megahertz, and the operating frequency of the PLL is in the Gigahertz range, the frequency from the XTAL is divided to a desirable input range before it is applied as the reference frequency. This is best illustrated by modern processors, which operate with clocks from the high hundreds of Megahertz to a few Gigahertz, yet have relatively low speeds for reference crystals. These clocks are provided using clock generating Palls. This process is known as clock generation. In WLAN chips, the primary goal of the PLL design is clock generation.

## The PLL in Depth:

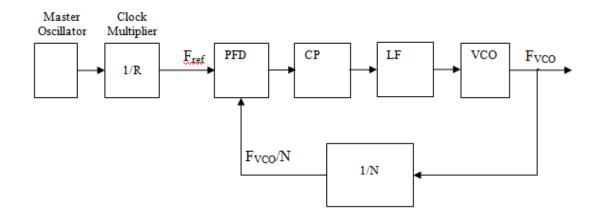

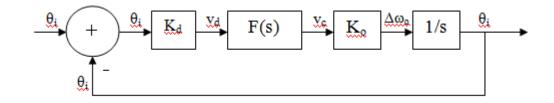

Figure 6, shown below, is a visual representation of the PLL.

Figure 6 – A visual diagram of the PLL

The crystal oscillator generates a clock that acts as a reference clock for the PLL, which goes to the phase frequency detector (PFD); which also has an input from the VCO. Depending upon the output of the PFD, the charge pump (CP) induces a current into the loop filter that is designed to work at a specific bandwidth. The basic function is that of a current to voltage converter that works in a specific bandwidth. The VCO is the main block of the PLL. The VCO takes the input from LPF, and depending upon the type of VCO, generates a clock that is feedback through though a divider circuit. This divides the  $F_{vco}$  by the user-defined value, which in turn is a second input of the PFD.

**Crystal Oscillator** – The purpose of the crystal oscillator is to generate a reference frequency. For this project, we used a 20MHz crystal. Accordingly, the initial reference frequency is also 20MHz.

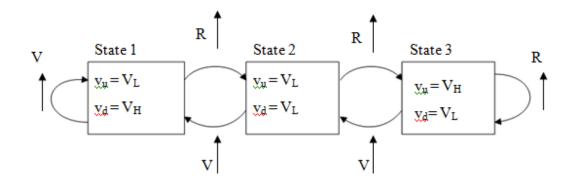

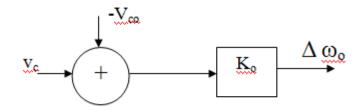

**PFD** – A Phase Frequency Detector takes two signals as inputs. The crystal oscillator provides the reference frequency,  $F_{ref}$ . The VCO frequency ( $F_{vco}$ ) is provided as feedback through the Voltage Controlled Oscillator. The PFD output is used to control the VCO in such a way that the phase difference between the two inputs is held constant [6]. For this reason, the PLL is referred to as a negative feedback system. An *n*-state PFD may be extended to as many states desired, but a three state PFD is the most widely used because it is simple and can act as both a phase and frequency detector. [Insert reference] A state diagram for the circuit is shown in Figure 7.

Figure 7 - The PLL state diagram

To expand upon the state diagram, we have our VCO frequency (V) and our reference frequency (R) these are digital frequencies represented by square wave clock cycles. The up arrow denotes a clock event. When R is triggered, we move to a higher State, while V moves toward a lower State. Suppose we are initially in State 1, if there is a clock events toggle for the reference frequency, we will move to State 2. If the VCO output triggers the next clock event we move back to State 1. As long as the VCO and reference frequencies toggle between each other, we will alternate between States 1 and 2. If the VCO is consistently falling behind the reference in phase, eventually there will be two reference events before a single VCO event and we will be in State 3.

The PFD output is denoted by  $v_u$  and  $v_d$ , which are translated as 'up' and 'down' respectively.  $V_H$  and  $V_L$  correspond to logical voltage high and logical voltage low and act as a switch for signals, which are then passed to the charge pump. From the state diagram we can infer in State 1 our reference frequency is running slower than our VCO frequency and must be decreased. Similarly, we can clearly see that both signals are in phase in State 2. The charge pump uses these values in the order they arrive.

**Charge Pump** – The charge pump has input dependant on the PFD. It will receive the up or down signal, which will control switches to steer current in or out of a capacitor. The purpose is to cause charge or discharge the capacitor. The time the switch is turned on is directly proportional to the phase difference of the VCO and reference signals. The voltage from the capacitor will be passed through a low pass filter and ultimately tune the VCO. The current value is increased when the 'up' signal is received by the charge pump, similarly, when the 'down' signal is received the current value is subtracted. A pseudo implementation of the charge pump is as follows

If up>down then:

Icp = x (where x is the current induced from the current sources in the charge pump) Else if down<up:

Icp = -x

Else:

Icp = 0 (where the output of the charge pump is drained to ground)

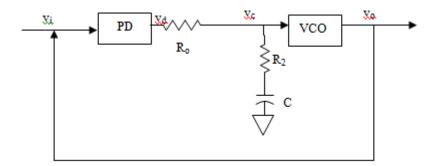

**Loop Filter** – A loop filter is used in order to attenuate the PFD signal at high frequencies, while still allowing for dc unity gain. If an attenuator is used instead of a loop filter it is possible to effectively reduce the ac gain, K. The drawback to this method is a reduction in DC gain, and therefore the dc voltage  $V_{co}$  the PFD can provide to the VCO is now limited. This greatly reduces the frequency range of the PLL and therefore, using a loop filter is the preferred method [6]. Adding a capacitor to an attenuator forms a simple loop filter. This is represented in Figure 8.With a large capacitor, the DC path to ground is blocked and the dc component is not attenuated [6].

**Figure 8** – The loop filter

Equation 5.1 represents the transfer function for the loop filter.