# University of New Mexico UNM Digital Repository

**Electrical and Computer Engineering ETDs**

**Engineering ETDs**

7-5-2012

# Dynamically reconfigurable management of energy, performance, and accuracy applied to digital signal, image, and video Processing Applications

Daniel Rolando Llamocca Obregon

Follow this and additional works at: https://digitalrepository.unm.edu/ece etds

#### Recommended Citation

Llamocca Obregon, Daniel Rolando. "Dynamically reconfigurable management of energy, performance, and accuracy applied to digital signal, image, and video Processing Applications." (2012). https://digitalrepository.unm.edu/ece\_etds/162

This Dissertation is brought to you for free and open access by the Engineering ETDs at UNM Digital Repository. It has been accepted for inclusion in Electrical and Computer Engineering ETDs by an authorized administrator of UNM Digital Repository. For more information, please contact disc@unm.edu.

| Daniel Rolando Llamocca Obregon                                                        |

|----------------------------------------------------------------------------------------|

| Candidate                                                                              |

|                                                                                        |

| Electrical and Computer Engineering                                                    |

| Department                                                                             |

|                                                                                        |

| This dissertation is approved, and it is acceptable in quality and form for publicatio |

| This dissertation is approved, and it is deceptable in quarty and form for publication |

| Approved by the Dissertation Committee:                                                |

|                                                                                        |

| MARIOS PATTICHIS . Chairperson                                                         |

| MARIOS PATTICHIS , Chairperson                                                         |

|                                                                                        |

| CHRISTOS CHRISTODOULOU                                                                 |

|                                                                                        |

| IAMES C. I VVE                                                                         |

| JAMES C. LYKE                                                                          |

|                                                                                        |

| RON LUMIA                                                                              |

## Dynamically Reconfigurable Management of Energy, Performance, and Accuracy applied to Digital Signal, Image, and Video Processing Applications

by

#### **DANIEL LLAMOCCA**

B.Sc., Electrical Engineering, Pontificia Universidad Católica del Perú, 2002

M.Sc., Computer Engineering, University of New Mexico, 2008 PhD., Computer Engineering, University of New Mexico, 2012

#### **DISSERTATION**

Submitted in Partial Fulfillment of the Requirements for the Degree of

#### Doctor of Philosophy Engineering

The University of New Mexico Albuquerque, New Mexico

May, 2012

@2012, Daniel Llamocca

### DEDI CATION

This dissertation is dedicated to my parents, Daniel and Arcelia. Besides their guidance and affection, they provided me with all the tools and opportunities that made from me who I am ...

#### Acknowledgments

I would like to express my deepest and sincerest gratitude to my advisor, Dr. Marios Pattichis, for introducing me to the fascinating world of research and for his stimulating and invaluable help during all these years. I am deeply grateful for his patience, encouragement, invaluable advice, and countless hours of work.

Special thanks to all of my friends and ECE, whose friendship and support made the days of work more bearable.

# Dynamically Reconfigurable Management of Energy, Performance, and Accuracy applied to Digital Signal, Image, and Video Processing Applications

by

#### **Daniel Llamocca**

B.Sc., Electrical Engineering, Pontificia Universidad Católica del Perú, 2002

M.Sc., Computer Engineering, University of New Mexico, 2008

PhD., Engineering, University of New Mexico, 2012

#### **Abstract**

There is strong interest in the development of dynamically reconfigurable systems that can meet real-time constraints in energy/power-performance-accuracy (EPA/PPA). In this dissertation, I introduce a framework for implementing dynamically reconfigurable digital signal, image, and video processing systems.

The basic idea is to first generate a collection of Pareto-optimal realizations in the EPA/PPA space. Dynamic EPA/PPA management is then achieved by selecting the

Pareto-optimal implementations that can meet the real-time constraints. The systems are then demonstrated using Dynamic Partial Reconfiguration (DPR) and dynamic frequency control on FPGAs.

The framework is demonstrated on: i) a dynamic pixel processor, i) a dynamically reconfigurable 1-D digital filtering architecture, and iii) a dynamically reconfigurable 2-D separable digital filtering system.

Efficient implementations of the pixel processor are based on the use of look-up tables and local-multiplexes to minimize FPGA resources. For the pixel-processor, different realizations are generated based on the number of input bits, the number of cores, the number of output bits, and the frequency of operation. For each parameters combination, there is a different pixel-processor realization. Pareto-optimal realizations are selected based on measurements of energy per frame, PSNR accuracy, and performance in terms of frames per second. Dynamic EPA/PPA management is demonstrated for a sequential list of real-time constraints by selecting optimal realizations and implementing using DPR and dynamic frequency control.

Efficient FPGA implementations for the 1-D and 2-D FIR filters are based on the use a distributed arithmetic technique. Different realizations are generated by varying the number of coefficients, coefficient bitwidth, and output bitwidth. Pareto-optimal realizations are selected in the EPA space. Dynamic EPA management is demonstrated on the application of real-time EPA constraints on a digital video.

The results suggest that the general framework can be applied to a variety of digital signal, image, and video processing systems. It is based on the use of offline-processing that is used to determine the Pareto-optimal realizations. Real-time constraints are met by

selecting Pareto-optimal realizations pre-loaded in memory that are then implemented efficiently using DPR and/or dynamic frequency control.

### **Table of Contents**

| List of Figures                                                            |    |

|----------------------------------------------------------------------------|----|

| List of Tables                                                             | XV |

| 1 Introduction                                                             | 1  |

| 1.1 Motivation                                                             | 1  |

| 1.2 Thesis Statement                                                       | 3  |

| 1.3 Innovations and Contributions                                          | 4  |

| 1.4 Organization                                                           | 4  |

| 2 A Dynamically Reconfigurable Pixel Processor System based on             |    |

| Power/Energy-Performance-Accuracy Optimization                             | 7  |

| 2.1 Introduction                                                           | 7  |

| 2.2 Background and Related Work                                            | 11 |

| 2.3 Pixel Processor architecture                                           | 14 |

| 2.4 Dynamic Frequency Control and Reconfiguration of the Pixel Processor   | 15 |

| 2.5 Optimization Framework for the Pixel Processor                         | 18 |

| 2.6 Experimental Setup                                                     | 25 |

| 2.7 Results and Analysis                                                   | 29 |

| 2.8 Conclusions                                                            | 39 |

| 3 Partial Reconfigurable FIR Filtering system using Distributed Arithmetic | 41 |

| 3.1 Introduction                                                           | 41 |

| 3.2 Background and related work                                            | 43 |

| 3.3 Stand-alone FIR Filter core implementation                             | 47 |

| 3.4 Dynamically Reconfigurable FIR filtering system                        | 53 |

|   | 3.5 Results.                                                                                                                                                                                                                                                                       | 59                                                       |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

|   | 3.6 Conclusions                                                                                                                                                                                                                                                                    | 70                                                       |

| 4 | Separable FIR Filtering in FPGA and GPU Implementations: Energy,                                                                                                                                                                                                                   |                                                          |

|   | Performance, and Accuracy Considerations                                                                                                                                                                                                                                           | 72                                                       |

|   | 4.1 Introduction                                                                                                                                                                                                                                                                   | 73                                                       |

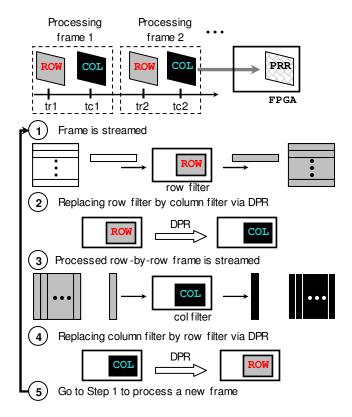

|   | 4.2 2D FIR Filter system on the FPGA                                                                                                                                                                                                                                               | 74                                                       |

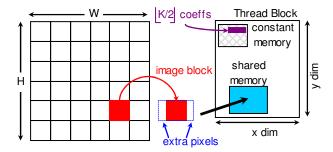

|   | 4.3 Filter implementation on the GPU                                                                                                                                                                                                                                               | 76                                                       |

|   | 4.4 Experimental Setup                                                                                                                                                                                                                                                             | 79                                                       |

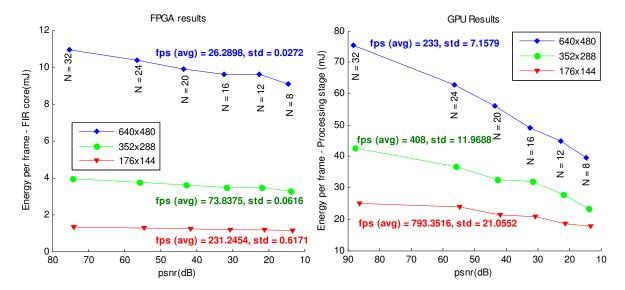

|   | 4.5 Results                                                                                                                                                                                                                                                                        | 82                                                       |

|   | 4.6 Conclusions                                                                                                                                                                                                                                                                    | 87                                                       |

| 5 | Dynamic Energy, Performance, and Accuracy Optimization and                                                                                                                                                                                                                         |                                                          |

|   |                                                                                                                                                                                                                                                                                    |                                                          |

|   | Management for Separable 2-D FIR Filtering for Digital Video                                                                                                                                                                                                                       | 88                                                       |

|   | Management for Separable 2-D FIR Filtering for Digital Video  5.1 Introduction                                                                                                                                                                                                     | <b>88</b><br>88                                          |

|   | •                                                                                                                                                                                                                                                                                  |                                                          |

|   | 5.1 Introduction                                                                                                                                                                                                                                                                   | 88                                                       |

|   | 5.1 Introduction                                                                                                                                                                                                                                                                   | 88<br>92                                                 |

|   | 5.1 Introduction                                                                                                                                                                                                                                                                   | 88<br>92<br>95                                           |

|   | 5.1 Introduction                                                                                                                                                                                                                                                                   | 88<br>92<br>95<br>101                                    |

|   | 5.1 Introduction                                                                                                                                                                                                                                                                   | 88<br>92<br>95<br>101<br>108                             |

| 6 | 5.1 Introduction                                                                                                                                                                                                                                                                   | 88<br>92<br>95<br>101<br>108<br>110                      |

| 6 | 5.1 Introduction  5.2 Background and related work  5.3 Video filtering using Dynamic Partial Reconfiguration  5.4 Optimization framework for video filters  5.5 Experimental Setup  5.6 Results and Analysis  5.7 Conclusions                                                      | 88<br>92<br>95<br>101<br>108<br>110<br>119               |

| 6 | 5.1 Introduction  5.2 Background and related work  5.3 Video filtering using Dynamic Partial Reconfiguration  5.4 Optimization framework for video filters  5.5 Experimental Setup  5.6 Results and Analysis  5.7 Conclusions  Concluding Remarks, future work and recommendations | 88<br>92<br>95<br>101<br>108<br>110<br>119<br><b>121</b> |

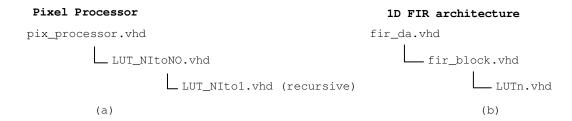

| A.1 Pixel processor and 1D FIR filter architectures                 | 126 |

|---------------------------------------------------------------------|-----|

| A.2 Dynamic Frequency Control core                                  | 127 |

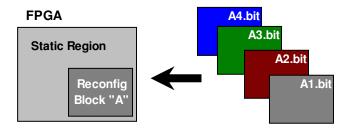

| B Reconfigurability on FPGAs                                        | 128 |

| B.1 Dynamic Partial Reconfiguration                                 | 128 |

| B.2 Technology that enables reconfiguration (full/partial) of FPGAs | 129 |

| C Related publications                                              |     |

| References                                                          |     |

# **List of Figures**

| 2.1 Pixel processor architecture                                           | 14 |

|----------------------------------------------------------------------------|----|

| 2.2 Embedded system over which we can perform DPPA management              | 16 |

| 2.3 Frequency control via the DCR Bus interface                            | 18 |

| 2.4 Multi-objective optimization of the PPA space                          | 23 |

| 2.5 Pixel Processor Slave PLB interface                                    | 26 |

| 2.6 Output 'oilp' image results for various input/output cases             | 29 |

| 2.7 Histograms for both 8-bit 'lena' and 12-bit 'oilp' images              | 30 |

| 2.8 Pixel Processor IP resource (slices) utilization as NI, NO, NC vary    | 32 |

| 2.9 32-bit I/O constrained implementations for 12-bit images               | 33 |

| 2.10 8-bit input constrained implementations                               | 34 |

| 2.11 Fixed-frequency (100 MHz) constrained implementations                 | 35 |

| 2.12 Fixed-frequency (100 MHz) constrained implementations (12-bit image)  | 37 |

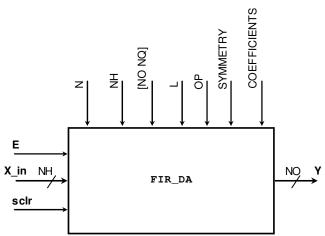

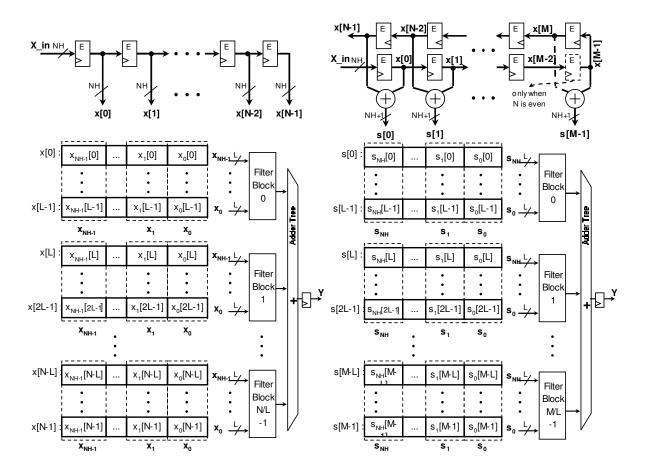

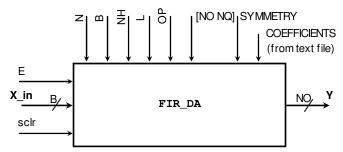

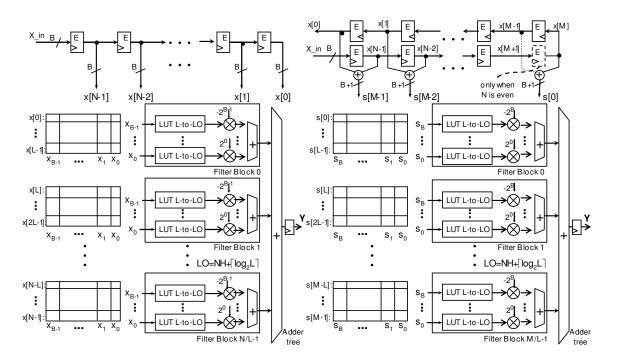

| 3.1 Generalized FIR DA Module                                              | 47 |

| 3.2 High-performance DA implementation based on the underlying LUT input   |    |

| size (L)                                                                   | 49 |

| 3.3 Filter Block architecture. SYMMETRY = YES                              | 50 |

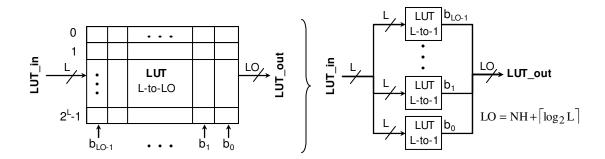

| 3.4 Realization of an L-to-LO LUT using LO L-to-1 LUTs                     | 51 |

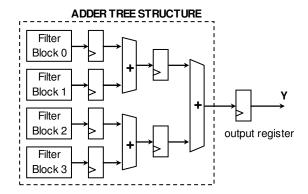

| 3.5 Adder tree structure for Filter blocks' outputs. M/L = 4               | 52 |

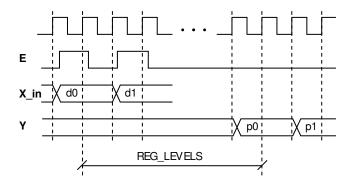

| 3.6 Latency measured from the moment 'd0' is input until its correspondent |    |

| output 'p0' is available                                                   | 52 |

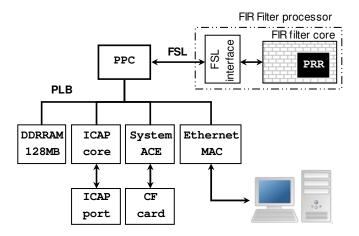

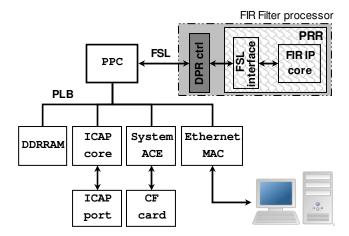

| 3.7 System Block Diagram                                                   | 52 |

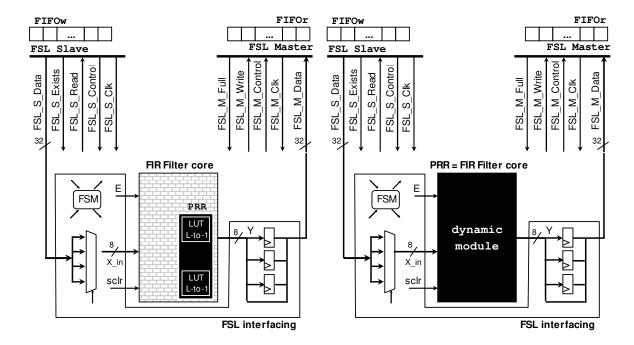

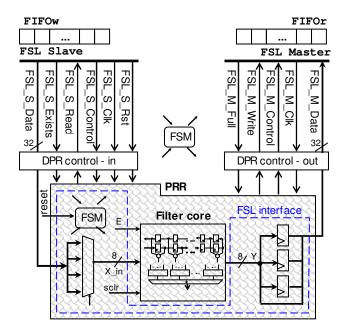

| 3.8 Dynamic FIR Filter processor interfacing with FSL.                     | 55 |

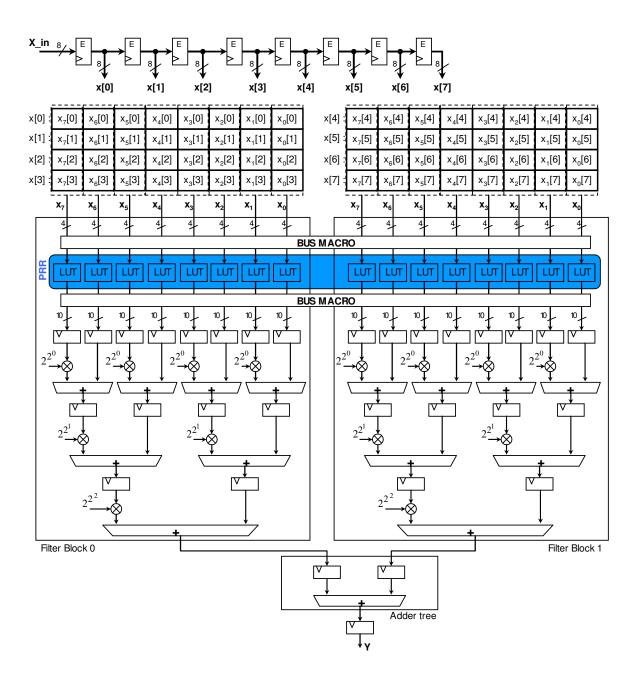

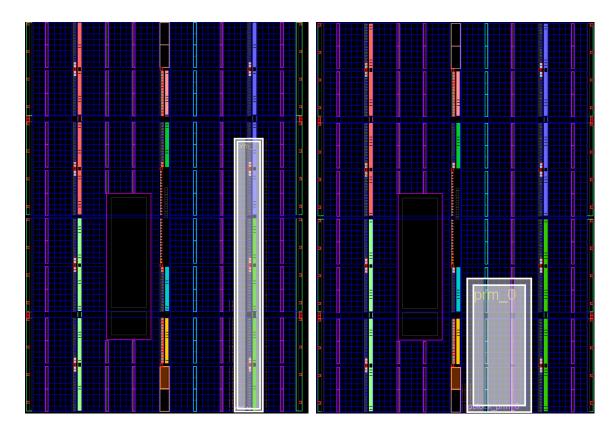

| 3.9 FIR filter core where the PRR and Bus Macros can be appreciated               | 57 |

|-----------------------------------------------------------------------------------|----|

| 3.10 FIR filter processor where the PRR is the FIR Filter core                    | 58 |

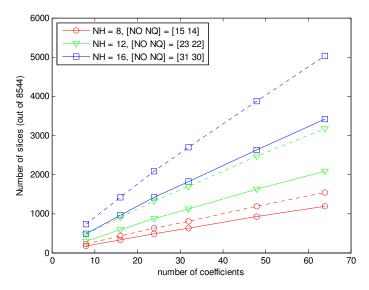

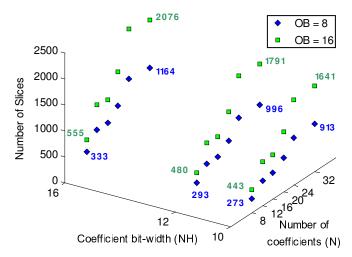

| 3.11 Resources vs. number of coefficients and input bitwidth                      | 60 |

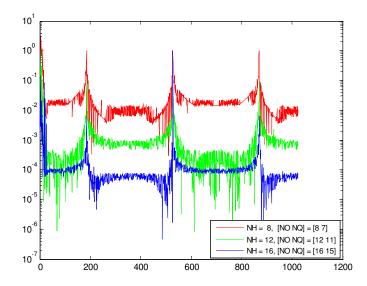

| 3.12 Relative error, N = 32. Three bitwidth cases                                 | 60 |

| 3.13 Dynamic reconfiguration region for (i) coefficient-only reconfiguration      |    |

| system, and (ii) full filter reconfiguration system                               | 62 |

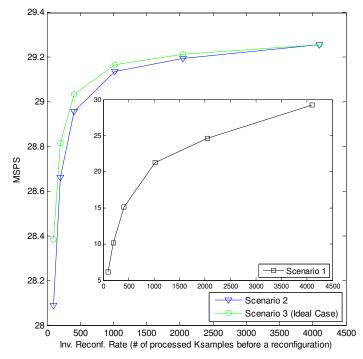

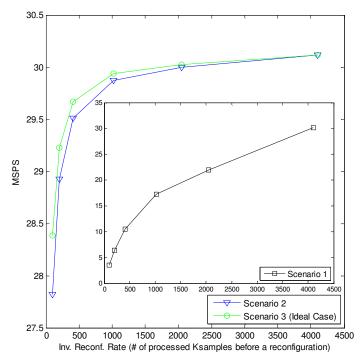

| 3.14 DPR system performance for coefficient -only reconfiguration                 | 66 |

| 3.15 DPR system performance for full filter reconfiguration                       | 66 |

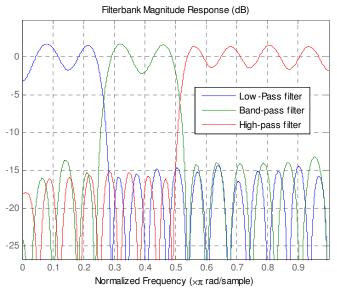

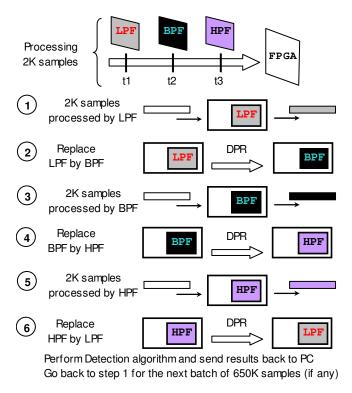

| 3.16 Filterbank used for R-wave detection                                         | 67 |

| 3.17 Filterbank data processing                                                   | 68 |

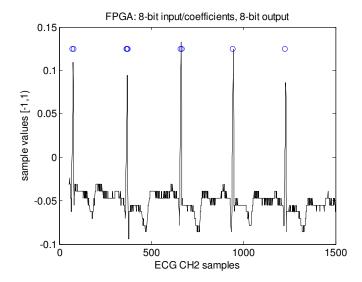

| 3.18 Perfect detection of R-waves for the first 5 ECG cycles                      | 69 |

| 4.1 System Block Diagram                                                          | 74 |

| 4.2 2D separable FIR filter implementation                                        | 75 |

| 4.3 Thread block configuration for row filtering                                  | 78 |

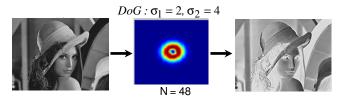

| 4.4 Frequency response – ideal filter with N = 48                                 | 79 |

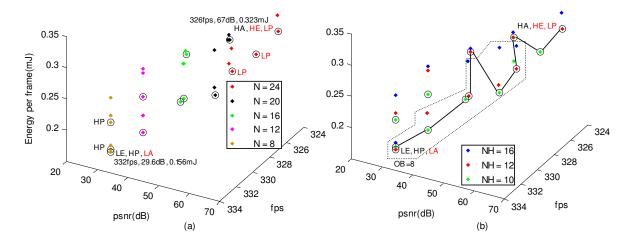

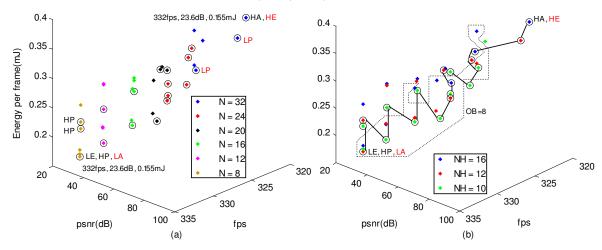

| 4.5 Performance, energy, and accuracy results for both FPGA and GPU. N:           |    |

| number of coefficients                                                            | 86 |

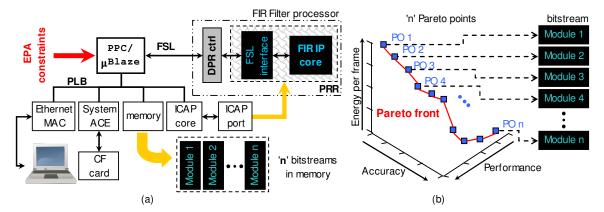

| 5.1 Multi-objective optimization of the EPA space                                 | 90 |

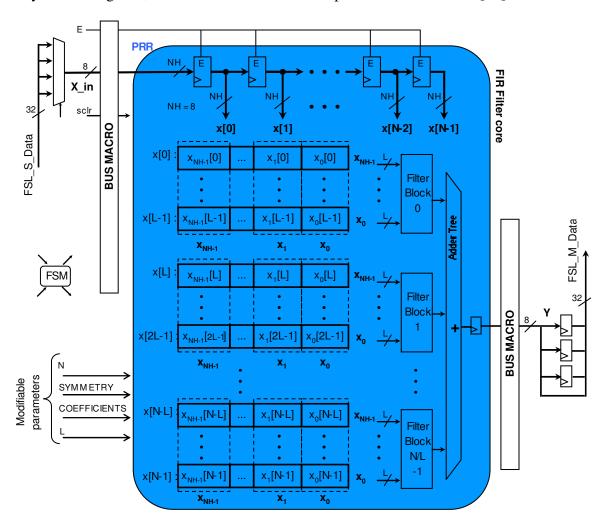

| 5.2 FIR Filter Intellectual Property (IP) core                                    | 95 |

| 5.3 High Performance FIR filter implementation                                    | 96 |

| 5.4 Embedded system over which we can apply Dynamic EPA management                | 97 |

| 5.5 PRR that includes the filter core for full-filter reconfiguration and the FSL |    |

| interface, needed for image filtering. B = 8                                      | 99 |

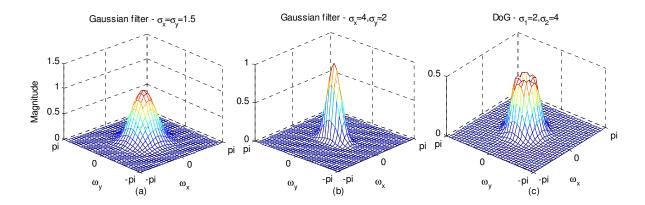

| 5.6 Frequency-magnitude responses for the three Gaussian filters                                 | 108 |

|--------------------------------------------------------------------------------------------------|-----|

| 5.7 Hardware resource utilization for the column filters                                         | 110 |

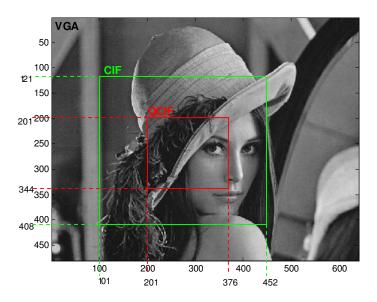

| 5.8 Cropped regions for the 'lena' image                                                         | 113 |

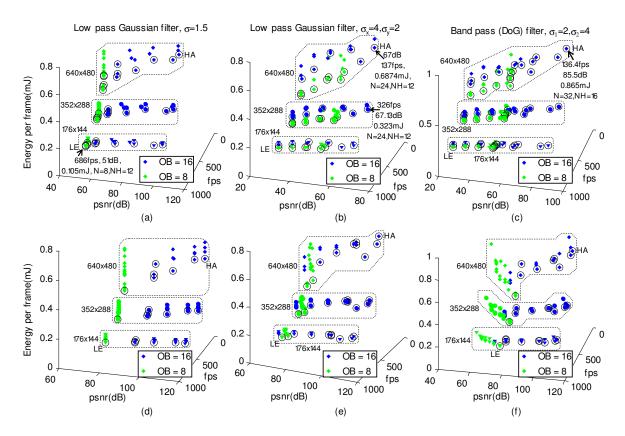

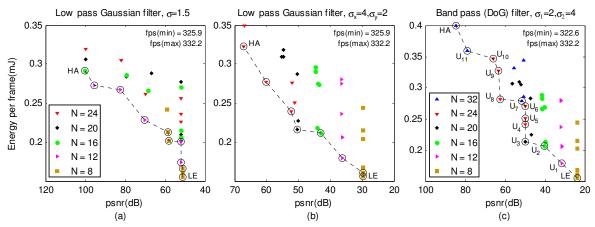

| 5.9 Pareto optimal realizations for the three filters and different image sizes                  | 114 |

| 5.10 Pareto-optimal realizations for the isotropic low pass Gaussian filter                      |     |

| (σ=1.5) for CIF resolution                                                                       | 115 |

| 5.11 Pareto-optimal realizations for anisotropic low-pass Gaussian filter ( $\sigma x$ =4,       |     |

| σy=2) for CIF resolution                                                                         | 116 |

| 5.12 Pareto-optimal realizations for DoG filter ( $\sigma$ 1=2, $\sigma$ 2=4) for CIF resolution | 116 |

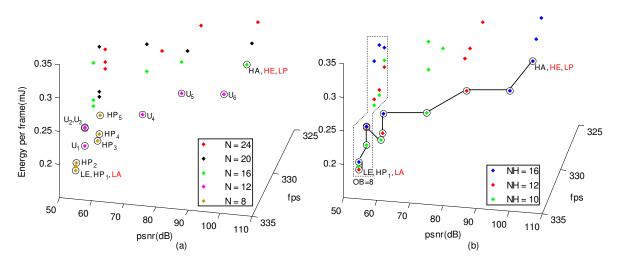

| 5.13 2D Pareto-optimal realizations for Energy-Accuracy space for all filter                     |     |

| types at CIF resolution                                                                          | 118 |

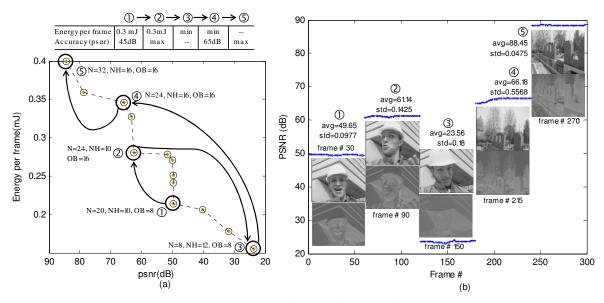

| 5.14 Dynamic EPA management example for DoG filtering of the foreman                             |     |

| video sequence (CIF resolution)                                                                  | 118 |

| A.1 VHDL code for Pixel Processor and 1D FIR filter                                              | 123 |

| A.2 VHDL code ('entity' declaration) for the Pixel Processor architecture                        | 123 |

| B.1 Basic premise of Partial Reconfiguration                                                     | 126 |

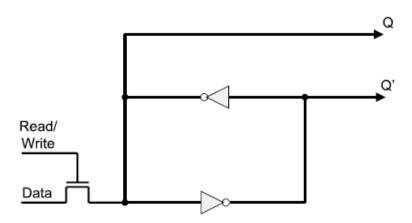

| B.2 Basic Xilinx SRAM cell                                                                       | 126 |

## **List of Tables**

| 2.1 Different types of power consumed at each rail for an FPGA                  | 20 |

|---------------------------------------------------------------------------------|----|

| 2.2 32-bit I/O pixel processor constrained implementations                      | 28 |

| 2.3 Pixel Processor Implementations for 8/12 bit input images unrestricted by   |    |

| I/O bitwidth                                                                    | 28 |

| 2.4 Pixel Processor implementations restricted at 100 MHz with unrestricted     |    |

| I/O bitwidths                                                                   | 28 |

| 2.5 Embedded Pixel Processor. Resource utilization (XCV4FX60)                   | 31 |

| 2.6 Fixed-frequency (100 MHz) constrained implementations                       | 36 |

| 2.7 Comparison against other single-pixel architectures (1 core)                | 39 |

| 3.1 FIR Filter implementation savings due to the use of filter blocks           | 49 |

| 3.2 Hardware Utilization on Virtex-4 XC4VFX20-11FF672 for coefficient-only      |    |

| reconfiguration                                                                 | 61 |

| 3.3 Hardware Utilization on Virtex-4 XC4VFX20-11FF672 for full filter           |    |

| reconfiguration                                                                 | 61 |

| 3.4 PRR measures for both dynamic partial reconfiguration system realizations . | 62 |

| 3.5 Reconfiguration time for both DPR system Realizations                       | 63 |

| 3.6 DPR system throughput (MSPS) as function of delay between                   |    |

| reconfigurations for 1-D FIR filtering with Full filter reconfiguration         | 65 |

| 4.1 Embedded FIR Filtering system resource utilization (Virtex-4 XCVFX20-       |    |

| 11FF672)                                                                        | 83 |

| 4.2 GPU running times (ms)                                                      | 84 |

| 4.3 Embedded system Power consumption (Watts) on the XCVFX20-11FF672            |    |

#### Chapter 1

#### Introduction

#### 1.1 Motivation

There is a strong interest in developing effective methods that can provide hardware systems that respond to run-time constraints on energy/power, performance, and accuracy. For example, it is interesting to consider scalable solutions that can deliver different performances based on energy constraints. Here, a low-energy solution will be needed when there is a requirement for long-time operation. On the other hand, a high-performance solution is often considered when there are no power (or energy) constraints.

Effective run-time management of hardware resources can be effectively handled through the use of Dynamic Partial Reconfiguration (DPR). DPR technology, currently available on Field Programmable Gate Arrays (FPGAs), enables the run-time allocation and de-allocation of hardware resources by modifying or switching off portions of the FPGA while the rest remains intact, continuing its operation. In addition to modifying resources, FPGAs with Digital Clock Managers (DCMs) also allow for real time modification of the operating frequency. These two technologies enable the development of dynamically reconfigurable systems that can meet constraints in power/energy, performance, and accuracy.

We consider digital Signal, Image, and Video Processing systems that are characterized in terms of their requirements on energy/power, performance, and precision. The goal of the dynamically reconfigurable system is to select an optimal

architecture that satisfies time-varying energy/power, performance, and accuracy (EPA/PPA) constraints. Thus, the process of determining an optimal solution is defined in terms of multi-objective optimization, with the goal of reducing energy/power consumption, while maximizing performance and accuracy, subject to time-varying EPA/PPA constraints.

The process of controlling Energy/Power, Performance, and Accuracy at run-time is referred as Dynamic Energy/Power-Performance-Accuracy (DEPA/DPPA) management. As an example of DPPA management, consider a simple example. Suppose that a video processing system is assigned the task of delivering performance at 30 frames per second (fps) on limited battery life that will also need to operate for at least 10 hours. If we can meet the performance and power requirements, we can then select the system realization with the highest accuracy. Then, after one hour, suppose that a fast moving target is observed. This will likely change the requirements to an increased frame rate. Now, suppose that we are asked to deliver performance at 100 fps at some minimum level of accuracy. This will certainly increase the minimum power requirements. In this case, we will select the hardware realization that has the lowest power requirements while meeting the performance (≥100 fps) and accuracy constraints. Thus, we see that DPPA management is especially important for video systems for which PPA requirements can vary over time.

Dynamic EPA/PPA management is more effective when applied to hardware architectures that are efficient in terms of resource consumption. We demonstrate dynamic EPA/PPA management on two resource-effective architectures associated with real-time video processing (that demands significant processing requirements).

The first application is the development of the *dynamic pixel processor*. Single-pixel operations include the implementation of functions that perform gamma correction, contrast enhancement, histogram equalization, histogram shaping, thresholding, Huffman table encoding, and quantization. Here, after computing an appropriate function, each output pixel only depends on the corresponding input pixel.

The second application is the development of the dynamic 2-D FIR filtering system. Here, the focus on 2-D FIR filtering comes from the large number of possible applications. The list of applications includes image and video denoising, linear image and video enhancement, image restoration, edge detection, face recognition, etc.

#### 1.2 Thesis statement

The main objective of this PhD dissertation is the development of a dynamic energy/power-performance-accuracy management approach for digital signal, image, and video processing architectures. This is possible by the use of Dynamic Partial Reconfiguration (DPR) and Dynamic Frequency Control on FPGAs. The dynamically reconfigurable architectures are evaluated in terms of energy/power-performance-accuracy trade-offs. In addition, the architectures presented in this work use techniques that minimize the amount of computational resources and make intensive use of DPR.

In particular, the research is focused on the development of a dynamic pixel processor, and a dynamic 2-D FIR filtering system. The energy/power-performance-accuracy (EPA/PPA) spaces for both the pixel processor and the 2-D FIR filter are explored. Moreover, the optimal realizations (in the multi-objective sense) are extracted from the

EPA/PPA space. The optimal realizations are then used in a dynamic management system to meet real-time varying constraints in the EPA/PPA spaces.

#### 1.3 Innovations and Contributions

A list of the primary innovations and contributions includes:

- Development of fully-parameterized hardware cores for signal, image, and video processing applications. The architectures are implemented with techniques that minimize the amount of computing resources and take advantage of Dynamic Partial Reconfiguration.

- Characterization of the optimal (in the multi-objective sense) hardware realizations

from the EPA/PPA space for the architectures presented.

- A new framework for dynamic energy/power, performance, and accuracy (EPA/PPA) management based on a multi-objective optimization approach that guarantees low energy, high accuracy, and high performance. The framework is applicable to a wide array of signal, image, and video processing architectures.

- Development of hardware systems that support dynamic energy/power, performance, and accuracy management that meet real-time EPA/PPA constraints. On hardware, dynamic EPA/PPA management is based on the run-time control of hardware resources and frequency of operation.

#### 1.4 Organization

This dissertation is organized into six chapters. In what follows, a summary of each chapter is provided.

Chapter 2 presents the dynamic pixel processor architecture and its corresponding dynamic energy/power-performance-accuracy management. The material presented in this chapter has been submitted for publication:

D. Llamocca and Marios Pattichis, "A dynamically Reconfigurable Pixel Processor system based on Power/Energy-Performance-Accuracy Optimization", in review, *IEEE Transactions on Circuits and Systems for Video Technology*.

The next two chapters deal with the details of the hardware implementation of a 2D FIR separable filtering system, with the ultimate goal of presenting the dynamic EPA/PPA management of the system in chapter 5.

In Chapter 3, a detailed description of a 1D FIR filter architecture is presented along with an efficient approach for dynamically modifying the filter parameters. The material presented in this chapter has been published in:

D. Llamocca, M. Pattichis, and G. Alonzo Vera, "Partial Reconfigurable FIR Filtering system using Distributed Arithmetic", *International Journal of Reconfigurable Computing*, vol. 2010, Article ID 357978, 14 pages, 2010.

Chapter 4 presents the 2D separable FIR filter implementation based on dynamic partial reconfiguration. By varying the number of coefficients and frame size, a limited version of the energy-accuracy space for 2D filter realizations is shown, and a comparison of the embedded system results with a GPU implementation is provided. The material presented in this chapter has been published in:

D. Llamocca, C. Carranza, and Marios Pattichis, "Separable FIR filtering in FPGA and GPU implementations: energy, performance, and accuracy considerations", in

Proceedings of the IEEE International Conference on Field Programmable Logic and Applications FPL'2011, Chania, Greece, Sept. 2011.

Chapter 5 develops the dynamic energy-performance-accuracy management for the 2D separable FIR filter. The material presented in this chapter is to be submitted to:

D. Llamocca and Marios Pattichis, "Dynamic Energy, Performance, and Accuracy Optimization and Management for Separable 2-D FIR Filtering for Digital Video" to be submitted to *IEEE Transactions on Image Processing*.

Chapter 6 presents conclusions, future work, and scope of the dissertation. Additionally the document has three appendices that include: i) a brief description of the VHDL code, ii) a discussion of the reliability of reconfiguring (whether fully or partial) the FPGA, and iii) a list of publications related with this dissertation.

#### Chapter 2

# A Dynamically Reconfigurable Pixel Processor System based on Power/Energy-Performance-Accuracy Optimization

#### **Abstract**

We introduce a dynamically reconfiguration framework for implementing single-pixel operations. The system relies on a multi-objective optimization scheme that generates Pareto-optimal implementations in the Power/Energy-Performance-Accuracy (PPA/EPA) spaces. The Pareto-optimal implementations and their PPA/EPA values are stored in DDR-SDRAM and can be chosen dynamically to meet time-varying constraints.

Results are shown in terms of power, accuracy (PSNR) of the resulting image, and performance in frames per second (fps). Dynamic PPA/EPA management is implemented using Dynamic Partial Reconfiguration (DPR) and dynamic frequency control.

Index Terms—Dynamic Partial Reconfiguration, Field-programmable gate-array (FPGA), LUT-based architectures.

#### 2.1 Introduction

There is a strong interest in developing effective methods that can provide hardware systems that respond to run-time constraints on power and performance. For example, it is interesting to consider scalable solutions that can deliver different performances based on energy constraints. Here, a low-energy solution will be needed when there is a

requirement for long-time operation. On the other hand, a high-performance solution is often considered when there are no power (or energy) constraints.

Effective run-time management of hardware resources can be effectively handled through the use of Dynamic Partial Reconfiguration (DPR). DPR technology, currently available on FPGAs, enables the run-time allocation and de-allocation of hardware resources without requiring system restart. In addition to modifying resources, FPGAs with Digital Clock Managers (DCMs) also allow for real time modification of the operating frequency.

Given the significant processing requirements associated with real-time video processing, it is interesting to consider applications associated with digital video. Here, we are primarily concerned with common single-pixel operations [1]. Single-pixel operations include the implementation of functions that perform gamma correction, contrast enhancement, histogram equalization, histogram shaping, thresholding, Huffman table encoding, and quantization. Here, after computing an appropriate function, each output pixel only depends on the corresponding input pixel. For example, in gamma correction, the output pixels are given by  $O = \alpha \times I^{\gamma}$ , where I denotes the image intensity of the input pixel for suitable values of  $\alpha$ , and  $\gamma$ . Similarly, in histogram equalization, a mapping is first computed between the input and output pixel.  $I\_eq = HistEq(\cdot)$ . Here,  $HistEq(\cdot)$  is a single-pixel operation.

To compare among different single-pixel realizations, we consider power requirements, performance in terms of frame rates, and accuracy (PPA). Then, the goal of the dynamically reconfigurable pixel processor is to select an optimal architecture that satisfies time-varying PPA constraints. Thus, the process of determining an optimal

solution is defined in terms of multi-objective optimization, with the goal of reducing power consumption, while maximizing performance and accuracy, subject to time-varying PPA constraints.

We refer to the process of controlling Power, Performance and Accuracy at run-time as Dynamic Power-Performance-Accuracy (DPPA) management. As an example of DPPA management, we consider a simple example. Suppose that a video processing system is assigned the task of delivering performance at 30 frames per second (fps) on limited battery life that will also need to operate for at least 100 hours. If we can meet the performance and energy requirements, we can then select the system realization with the highest accuracy. Then, after one hour, suppose that a fast moving target is observed. This will likely change the requirements to an increased frame rate. Now, suppose that we are asked to deliver performance at 100 fps at some minimum level of accuracy. This will certainly increase the minimum power requirements. In this case, we will select the hardware realization that has the lowest power requirements while meeting the performance (≥100 fps) and accuracy constraints. Thus, we see that DPPA management is especially important for video systems for which PPA requirements can vary over time (also see motivation in [2]).

DPPA management for audio and video processing had been suggested in earlier works (e.g. [3], [4]). In [3], [4], the authors suggested that DPR could be used for management of power and accuracy. More recently, we have the implementation of DPPA management using DPR in networking [5], dynamic arithmetic [6], DCT implementation [7]. In these papers, DPR was used to trade-off between power and

performance requirements. In [6], the authors considered trade-offs between power, performance, and precision.

To achieve DPPA management, a space of different realizations is generated. We use the term PPA space for the different realizations that we can generate. Then, we determine optimal realizations in the multi-objective sense. In other words, we determine the Pareto optimal front of all realizations [8]. To generate the PPA space, we produce a parameterized architecture based on the input bit-width, output bit-width, the number of cores, and the frequency of operation. An early version of a single-pixel architecture that allowed switching between function was presented in [9].

In terms of application, we are primarily interested in cases where the dynamic reconfiguration rate is relatively low. We do not expect run-time constraints to change faster than once a second. In this case, the DPR overhead is not significant. On the other hand, we note that the reduction of DPR overhead is an area of active research (e.g. [10], [11], [7], [12]).

The proposed DPPA management system is based on a bottom-up approach. First, we develop an efficient architecture for implementing single-pixel operations. Then, we parameterize the hardware description and vary the parameters to generate the PPA space. Third, we use multi-objective optimization to determine the Pareto-optimal realizations. The Pareto-optimal realizations are then stored in memory. DPPA management selects among Pareto-optimal realizations to meet time-varying constraints.

The main contributions of this work include: i) an optimization framework for dynamic PPA management of the pixel processor, ii) the development of a fullycustomizable intellectual property (IP) core in VHDL, and iii) a method to dynamically reconfigure via DPR and run-time reconfiguration of the operating frequency.

The rest of the work is organized as follows. Section 2.2 presents background and related work. Section 2.3 details the internal architecture and parameterization of the pixel processor. Section 2.4 explains how the pixel processor can switch among single-pixel realizations, and modify its frequency of operations at run-time. Section 2.5 details the multi-objective optimization framework. Section 2.6 presents the experimental setup. Then, the results are presented in Section 2.7. Finally, Section 2.8 lists the conclusions.

#### 2.2 Background and Related work

We begin with a summary of related work on the implementation of image processing systems based on Dynamic Partial Reconfiguration (DPR). In [7], the authors presented a design that dynamically reconfigures among Discrete Cosine Transform (DCT) modules of different sizes. The different DCT configurations were studied in terms of power, throughput, and (standard) image quality metrics. A dynamic systolic array accelerator for Kalman and Wavelet filters was presented in [13]. In [14], the authors presented a fingerprint image processing hardware whose stages (segmentation, normalization, smoothing, etc) are multiplexed in time via DPR. The 3D Haar Wavelet Transform (HWT) was implemented by dynamically reconfiguring a 1D HWT core thrice in [15]. A JPEG2000 decoder where the blocks are dynamically swapped is shown in [16]. In [17], an efficient 1D FIR Filtering system that combined the Distributed Arithmetic (DA) technique with DPR was presented.

There has also been some related work on the implementation of single-pixel processing functions, which usually entails two methods: LUT-based and custom hardware. In earlier work [9], we presented a basic architecture for single-pixel functions (8-bit input, 8-bit output) that stores the output pixel values in look-up tables (LUTs). The system could be dynamically reconfigured to perform arbitrary single-pixel functions. In [18], the authors presented custom architectures for 3 single-pixel functions (8-bit input, 8-bit output). A Xilinx® core for implementing gamma correction is described in [19]. In this implementation, the architecture is based on BlockRAMs whose contents can be modified on-demand. An ALTERA® LUT-based core allows for the run-time modification of LUT contents via a special interface [20]. These approaches do not address issues associated with run-time modifications of the input/output bit-widths or the frequency of operation.

A custom architecture for precise gamma correction is presented in [21]. In [22], the authors presented a contrast enhancement hardware that self-adjusts based on the histogram of the current frame. [23] presents a histogram equalization architecture. [24] performs image enhancement using a Successive Mean Quantization Transform. These architectures lack the versatility of the LUT-based approaches, but they can require far fewer resources for large input pixel bit-widths.

The trade-offs between power, performance, and accuracy for different architectures have also been investigated in the literature. Early work dealt with one or two of these properties at a time. In [25], the authors analyzed the precision requirements of a subset of recursive algorithms. In [3], the authors proposed the use of reconfiguration based on perceptual limits and the non-uniformity of video content in order to dynamically manage

power consumption, over which accuracy and performance depend on. Another example of power and precision trade-off is in [4], where the impact of numerical precision on power consumption is studied for audio processing applications. In [6], an application in dynamic arithmetic is presented where arithmetic cores are measured in terms of their power, performance, and precision requirements. Here, the use of DPR was shown to provide a low-energy example where the use of dynamic dual-fixed arithmetic cores was shown to perform as well as double floating point in an example from Linear Algebra. In [7], the authors presented a configuration manager that can dynamically adapt DCTs of different sizes based on PPA considerations.

To the best of our knowledge, no previous work has explored the Power-Performance-Accuracy space using a multi-objective optimization approach as proposed here. As it will be demonstrated by example, this approach offers some unique advantages, in that it allows for both joint and separable optimization based on a range of criteria and constraints.

This work seeks to extend prior research in the area of single-pixel operations for image enhancement by utilizing the LUT-based hardware presented in [9] and developing a fully-parameterized architecture that make use of DPR and dynamic frequency control to control the PPA space. In addition, we propose a multi-objective optimization framework to derive a set of optimal pixel processor realizations over which we can dynamically reconfigure to meet PPA constraints.

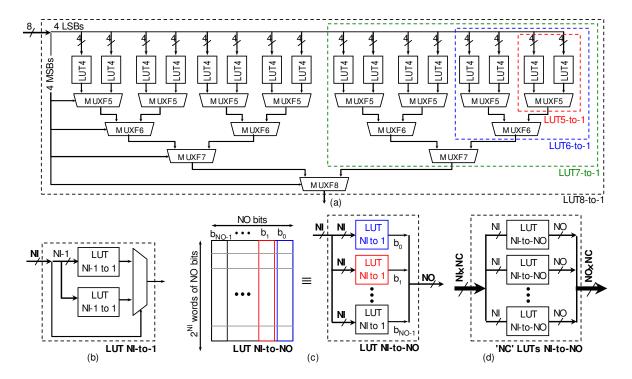

Figure 2.1. Pixel processor architecture. (a) Virtex-4 LUT8-to-1 implementation. Note the recursive implementation with specific CLB primitives (LUT4., MUXF5/6/7/8), LUT4 ≡ LUT4-to-1. (b) Recursive implementation of a NI-to-1 LUT. (c) Implementation of a NI-to-NO LUT. (d) Pixel processor core.

#### 2.3 Pixel Processor Architecture

The pixel processor architecture is detailed here. An earlier version of this architecture appears in [9]. Here, a fully-parameterized hardware architecture based on efficient mapping of LUTs is presented.

#### 2.3.1 Implementation of an NI-to-NO Look-Up Table (LUT)

1) LUT NI-to-1: This module uses NI input bits and one output bit. Xilinx® FPGAs contain hardwired L-to-1 LUT primitives with L = 4 (Virtex-II Pro, Virtex-4), and L = 6 (Virtex-5, Virtex-6). LUTs with higher number of input bits are built by combining the basic LUT primitives with multiplexers. Xilinx® devices let us instantiate primitives of optimized NI-to-1 LUTs for NI up to 8 [9]. Figure 2.1(a) shows the implementation of a LUT8-to-1. LUTs with NI > 8 are implemented by recursively combining two 'NI-1-to-

- 1' LUTs with a multiplexer, as in Fig. 1(b). The hardware complexity grows exponentially as NI increases, and thus there is a point at which a NI-to-1 LUT becomes unfeasible.

- 2) LUT NI-to-NO: Figure 2.1(c) depicts how a LUT NI-to-NO is built based on 'NO' LUTs NI-to-1. Each LUT NI-to-1 implements a column of the LUT NI-to-NO.

#### 2.3.2 Pixel Processor Architecture

The pixel processor architecture core is depicted in Fig. 2.1(d). It consists of a collection of 'NC' NI-to-NO LUTs. It provides the following parameters:

- NC: Number of single-pixel processor cores.

- NI: Number of input bits of each single-pixel processor (or the number of bits of the input pixel).

- NO: Number of output bits of each single-pixel processor (or the number of bits of the output pixel).

- LUT contents: provided in a text file. These values specify a unique single-pixel function (e.g. gamma correction, contrast stretching, etc).

Depending on the application, the LUT contents of each core can be identical or different. In addition, there might be applications in which NI and NO need to be different for each single-pixel processor core. However, for the vast majority of applications, NI and NO remain constant for all the cores.

# 2.4 Dynamic Frequency Control and Reconfiguration of the Pixel Processor

The pixel processor core parameters can be modified at run-time via Dynamic Partial Reconfiguration (DPR). This technology allows us to dynamically allocate resources as needed by particular applications. For the pixel processor, DPR allows the modification of the single-pixel function by re-using the same resources. To reduce resources, DPR allows us to reduce the number of input and/or output bits at the expense of degraded accuracy. To increase performance, we can use DPR to increase the number of cores. In addition, the frequency of operation can be dynamically modified by controlling the Digital Clock Manager (DCM). The DCM feature provides us with the ability to directly control power and performance. The combination of DPR and dynamic frequency control allows us to switch between different realizations.

#### 2.4.1 Dynamic Reconfiguration of the Pixel Processor:

DPR allows us to control NC (number of cores), NI (number of input bits), NO (number of output bits), and the LUT contents. A design where only the LUT contents can be dynamically altered was presented in [9]. Fig. 2.2(a) depicts the block diagram of an embedded system that allows for DPR.

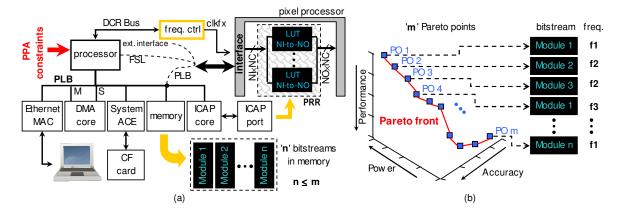

Figure 2.2. Embedded system over which we can perform DPPA management. (a) Embedded system that supports DPR and frequency control. The memory holds 'n' unique bitstreams that are needed for the Pareto front. The pixel processor can be connected to any interface (b) An example of a Pareto front with 'm' Pareto points (note that  $m \le n$ ). A Pareto point is a unique combination of a bitstream and frequency.

The processor can be hard-core (PowerPC) or soft-core (e.g., MicroBlaze, ARM). A Compact Flash (CF) stores partial bitstreams and input frames. The memory stores data needed at run-time (e.g. input video frames, processed video frames, and partial bitstreams). For fast data processing, a Direct Memory Access (DMA) controller can be used. The Ethernet core lets us get new partial bitstreams or video frames from a PC and to send processed video frames to the PC. It is also an interface for throughput measurements and system status. The Ethernet connection lets us perform DPR from the PC (and possibly a remote location).

To perform DPR, the Partial Reconfiguration Region (PRR) must be defined. In this case, the PRR is composed of 'NC' NI-to-NO LUTs and it is dynamically reconfigured via the internal configuration access port (ICAP), which is driven by the ICAP controller. The pixel processor I/O interface depends on the application (e.g., PLB interface, FSL interface as in [9], external, etc). The frequency control core, connected to the processor via the Device Control Register (DCR) bus, provides a clock to the pixel processor.

#### 2.4.2 Dynamic Reconfiguration of Frequency:

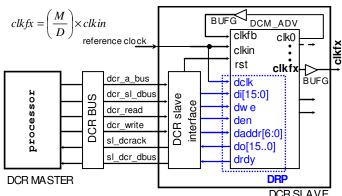

Digital Clock Managers (DCMs) inside FPGAs provide a wide range of clock management features [26]. Virtex-4 and Virtex-5 FPGAs use DCM, whereas Virtex-6 devices use a Mixed-Mode Clock Manager (MMCM).

The Dynamic Reconfiguration Port (DRP) of the DCM is used to dynamically adjust the frequency without reloading a new bitstream to the FPGA. The DRP uses register based control of the DCM frequency and phase.

Fig. 2.3 depicts the architecture for dynamic frequency control. The Xilinx® DCM primitive is named 'DCM\_ADV' (MMCM\_ADV for Virtex-6 FPGAs). We connect the

DCM to the Device Control Register (DCR) bus by means of a DCR Slave interface. The processor becomes the DCR Master. The specific architecture of the DCR Slave interface varies as different FPGA families provide a slightly different approach to load the M and D values. The frequency is dynamically controlled by modifying the ratio of M to D (see in Fig. 2.3).

Figure 2.3. Frequency control via the DCR Bus interface. The Dynamic Reconfiguration Port of the DCM is shown in blue.

#### 2.5 Optimization Framework for the Pixel Processor

The goal is to create a system that can select optimal realizations based on PPA constraints. The optimization is carried out for a specific single-pixel function. In this section, we detail: i) how a complete set of pixel processors is generated; ii) the manner in which Power, Performance, and Accuracy are measured; iii) how the optimal pixel processors are generated from the complete set; and iv) how we adjust pixel processor parameters and/or frequency based on PPA constraints.

#### 2.5.1 Generation of the set of single-pixel processors

The space of pixel processor realizations is generated by modifying the pixel processor parameters (NI, NO, and NC), and the frequency of operation. The LUT contents depend on NI and NO. The selection of the parameters and/or frequency combinations depends on the application.

The Power-Performance-Accuracy (PPA) space consists of the measurements for every single pixel processor realization. The generation of the PPA space is a lengthy process, and it is done offline.

#### 2.5.2 Performance measurements

Performance can be measured as the number of pixels (or bytes) processed per second, or by frames per second. The bytes per second processed is determined by the pixel size. Input pixels are usually 8-bit wide.

We are interested in measuring the performance of the IP shown in Fig. 2.2. The aim is to provide results from the IP angle, i.e. assuming that at every clock cycle NI×NC bits can be processed and NO×NC bits can be released. The performance of the entire embedded system depends on many factors (cache size, processor instruction execution, bus type and usage, etc.) that are subject to change. Here, the embedded system is just a generic test-bed.

The IP can process NI×NC bits and output NO×NC bits per clock cycle. Then, the number of bits it can process per unit of time is given by:

$$Performance (Mbps) = NI \times NC \times f(MHz)$$

(2.1)

For digital video processing, performance is measured in terms of frames per second (fps) given by:

$$fps = \frac{10^6}{Tframe(us)}, \quad Tframe(us) = \frac{1}{f(MHz)} \times \frac{frame\ size}{NC}$$

(2.2)

Note that 'fps' does not take into account the number of bits of the input pixels (NI)

#### 2.5.3 Power measurements

In this subsection, we detail the IP power consumption measurement. The IP (shown in Fig. 2.1) is the sole component included in the Partial Reconfiguration Region (PRR).

Table 2.1 provides a concise description of different power types that need to be considered. The device static power depends on the environment, the size of the device, and the device family. For all practical purposes, it is assumed to be constant. Since it does not depend on the IP implementation, we report it separately in Table 2.1 for the XC4VFX60 device.

Table 2.1: Different types of power consumed at each rail for an FPGA. For the XC4VFX60 Virtex-4, the device static power is 0.44W (at 25°C).

|         | Drawn by the device when it is powered up, configured with user logic, and there is no switching activity. |                                         |  |  |  |  |  |

|---------|------------------------------------------------------------------------------------------------------------|-----------------------------------------|--|--|--|--|--|

|         | Device                                                                                                     |                                         |  |  |  |  |  |

| Static  | static                                                                                                     | and without programming the user logic. |  |  |  |  |  |

|         | Design Consumed by the user logic when the device i                                                        |                                         |  |  |  |  |  |

|         | static programmed and without any switching activi                                                         |                                         |  |  |  |  |  |

| Dynamic | It is the fluctuating power as the design runs; it is generated by                                         |                                         |  |  |  |  |  |

| Dynamic | the switching user logic and routing.                                                                      |                                         |  |  |  |  |  |

In terms of comparing among different cases, we will only consider the sum of the dynamic and design static power (see Table 2.1). In order to estimate this power consumption, we use the FPGA power supply rails: (i) internal supply rail voltage *VCCINT* with current *ICCINT*, and (ii) auxiliary supply rail voltage *VCCAUX* with current *ICCAUX*. Here, we will not consider the output supply power since it is only associated with the power consumed by the external pins. Thus, the IP power is given by:

Power

$$IP = VCCINT \times ICCINTp + VCCAUX \times ICCAUXp$$

(2.3)

where the currents are given by:

$$ICCINTp = ICCINT - ICCINTQ$$

$ICCAUXp = ICCAUX - ICCAUXQ$  (2.4)

and *ICCINTQ*, *ICCAUXQ* are defined as the device static supply currents (of their respective voltage rails).

Measuring power directly (e.g. [6]) requires custom-built boards that provide access to the voltage rails themselves. Instead, we can accurately estimate power consumption using software tools that would be widely applicable to all devices. For the purposes of this work, the Xilinx Power Analyzer (XPA) is employed for these measurements (at 25°C). XPA provides an accurate estimate based on simulated switching activity of the place-and-routed circuit and exact utilization statistics. [27].

We also consider power consumption during dynamic partial reconfiguration. Unfortunately, there is no software tool available that can provide an estimate of this power consumption. In [6], through hardware measurements, it was determined that during DPR, the only supply current that increases is *ICCAUX* (Virtex-II Pro and Virtex-4). Thus, the DPR power can be estimated using:

$$Rec. Power = VCCAUX \times ICCAUX (increase)$$

(2.5)

From [6], we have that *ICCAUX* increases by 170 mA and 25 mA for the Virtex-II Pro (XC2VP30) and Virtex-4 (XC4VFX12) respectively. Assuming that these dynamic current measurements remain the same within the same device family, we can use these values in (2.5) and (2.6).

Furthermore, for our application in digital image and video, we will report energy consumption in terms of energy spent for processing a single frame:

Energy per

$$frame(uJ) = Power \times T frame(us)$$

(2.6)

For completeness, the frame size will also be reported along with the energy spent per frame (see (2.2)).

#### 2.5.4 Accuracy measurements

The accuracy is measured using the peak signal-to-noise ratio (PSNR). This is given by:

$$PSNR(dB) = 10 \times log_{10} \left( \frac{MAXValue^2}{MSE} \right)$$

(2.7)

where the MSE is the mean squared error between the pixel processor output and the result using double floating-point arithmetic.

#### 2.5.5 Generation of optimal Pixel Processor realizations

Based on the power, performance, and accuracy (PPA) measurements, we can select optimal pixel processor realizations. Here, we define a pixel processor realization to be optimal in the Pareto (multi-objective) sense [8]. A pixel realization is considered to be Pareto optimal if we cannot improve on its Power-Performance-Accuracy measurements without decreasing on at least one of them. We will next provide an example.

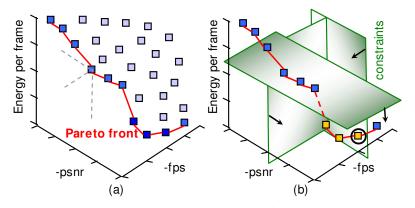

The goal is to minimize power, maximize performance, and maximize accuracy. For a given set of pixel processors, we want to find a subset of realizations whose results cannot be improved by any other realization for all three (PPA). The collection of all Pareto-optimal points forms a Pareto front (see Fig. 2.4). In Fig. 2.4, we are plotting realizations as points against power, and the negatives of performance and accuracy. Thus, optimal realizations appear lower-left in 2-D (see Fig. 2.4(a)). The idea is then extended to 3-D in Fig. 2.4(b).

We can also extend the example for satisfying multi-objective constraints. The idea is demonstrated in Fig. 2.4(c) and 2.4(d). Independent constraints appear as lines in 2-D and

planes in 3-D. Optimal realizations are then selected among the Pareto-optimal points that also satisfy the constraints. Dynamic constraint satisfaction only requires that we select Pareto optimal points when the constraints change. In the next section, we provide more details on the hardware implementation of this idea.

Figure 2.4. Multi-objective optimization of the PPA space. (a) 2-D Pareto Front. (b) 3-D Pareto Front. (c) Two constraints applied to the 2-D Pareto front. (d) Two constraints applied to the 3-D Pareto front. The circled point is the realization with the min. power consumption.

#### 2.5.6 Dynamic PPA Management based on DPR and dynamic frequency control

In hardware, Pareto-optimal realizations are represented by their associated partial bitstreams, frequency of operation, and PPA measurements. The realizations and associated parameters are stored in memory. We demonstrate the basic DPPA management framework in Fig. 2.2.

Dynamic PPA management is based on selecting a single realization that satisfies the dynamic constraints. An example of a single set of constraints is shown in Fig. 2.4(c) for two constraints (PA). Here, the Pareto-optimal points are plotted in yellow. Note that we

are interested in coming up with a single realization. When only PPA constraints are given, we can have more than one solution. Thus, it makes sense to consider the case where we are minimizing one objective while imposing constraints on the other two. We next consider an example to demonstrate the idea.

Without loss of generality, suppose that we want the minimum power realization (Ri) subject to minimum accuracy and performance requirements. In this case, we want to solve:

min Power(Ri),

Ri

Subject to:

$$Accuracy(Ri) \ge 50dB$$

$$Performance(Ri) \ge 30 fps$$

(2.8)

In this case, the Pareto-optimal points that satisfy the constraints are shown in yellow in Fig. 2.4(d). The realization that also minimizes power is circled. This is the optimal realization that is selected for DPR and/or dynamic frequency control. Note that if we also want the optimal solution to satisfy a power constraint, we can simply check whether the minimum power solution meets this constraint.

The implementation of *Ri* comes with specific values for the pixel processor parameters and frequency of operation.

Fig. 2.2(a) shows an embedded system that can modify the pixel processor parameters and the frequency of operation. Thus, each realization is represented in terms of its unique combination of partial bitstream and frequency of operation. Also, the Pareto-optimal front can contain bitstreams that are associated with more than one frequency. Fig. 2.2(b) illustrates how the user moves dynamically along the Pareto front via DPR and/or dynamic frequency control of the DCM.

#### 2.6 Experimental Setup

In this section, we provide specific details of the platform and the scenarios under which we test the pixel processor. We also provide details on the PLB interface and frequency control in Section 2.6.2.

#### 2.6.1 Platform testing scheme

Fig. 2.2(a) showed a generic embedded system. Here, the pixel processor system was implemented on the ML410 Xilinx® Development Board that houses a XC4VFX60-11FF1152 Virtex-4 FPGA. The PowerPC processor is selected and it is clocked at 300 MHz, with peripherals running at 100 MHz. Here, we note that the PowerPC has internal data and instruction caches that are used for data and instruction fetches from memory (64 MB DDR-SDRAM). The pixel processor IP is connected to the PLB Bus. The ICAP core used is provided by Xilinx®. The embedded system serves as a validating platform from which we extract the processed images.

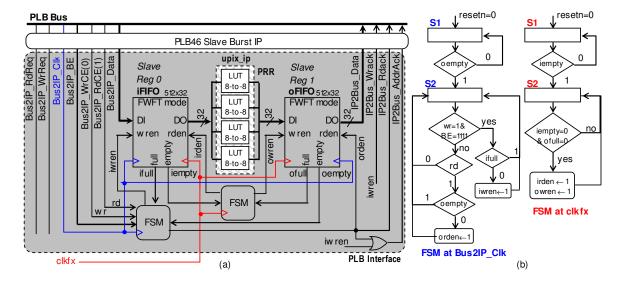

#### 2.6.2 PLB Interface and frequency control

The pixel processor is connected to the PLB bus (32-bit PLB Slave Burst interface). For the DMA core, we are using the Xilinx® Central Direct Memory Access (DMA) core with a PLB interface that supports burst transfers. The 32-bit PLB transaction requires  $NI\times NC \le 32$  and  $NO\times NC \le 32$  for optimal bus usage.

The frequency control core is shown in Fig. 2.3. The core acts as a slave to the DCR bus. The reference clock 'clkin' is the PLB clock (100 MHz). Thus,  $clkfx = (M/D) \times 100MHz$ .

Special care must be taken when varying 'clkfx'. For Virtex-4 devices, 'clkfx' is limited to 32-210 MHz in the 'low frequency mode', and to 210-350 MHz in the 'high

frequency mode' [28]. Switching frequency modes requires a sequence of reads/writes on the DCM dynamic reconfiguration port (DRP). To minimize overhead required for implementing clock speeds above 'PLB\_clock', we have constrained 'clkfx' to be lower or equal than 'PLB\_clock'. Thus, any M/D combination has to yield a 'clkfx' in the range of 32-100 MHz.

In Fig. 2.5, we show the Pixel processor implemented as a peripheral to the PLB. We handle the difference between the PLB and the Pixel Processor clocks by using input and output FIFOs and separate clock regions ('PLB\_clock' and 'clkfx'). FSMs are used to control the signals for each clock region. We clock the pixel processor coress (the PRR) at 'clkfx', while the rest is clocked at 'PLB\_clk'. Modifying the 'PLB\_clk' directly (i.e. 'PLB\_clk = clkfx') is undesirable since other peripherals (e.g. SystemACE, Ethernet core) use the 'PLB\_clk' value as a parameter, requiring the dynamic reconfiguration of these IPs each time we modify 'clkfx'.

Figure 2.5. (a) Pixel Processor Slave PLB interface. In the figure, NI=NO=8, NC=4. The PRR can change as long as NI×NC  $\leq$  32 and NO×NC  $\leq$  32. (b) State Machines for each clock region

# 2.6.3 Selection of pixel processor parameters and frequency of operation for the generation of the set of pixel processors

Typical image and video formats are limited to a maximum of 12 bits per sample (for each color channel). Thus, we work with 12-bit and 8-bit images. For reducing the input bitwidth, we simply select the most significant bits. To maintain high accuracy in the results, we require the number of outputs bits to be equal or above the number of input bits (NO $\geq$ NI). For the adjustable frequency of operation 'clkfx', we select five different frequencies (MHz): 100.00 (M=2,D=2), 66.66 (M=2,D=3), 50.00 (M=2,D=4), 40.00 (M=2,D=5), and 33.33 (M=2,D=6).

Three different testing scenarios are considered for the Pixel Processor: (i) 32-bit I/O constrained implementations, (ii) 8/12 input constrained implementations, and (iii) fixed-frequency constrained implementations. The parameters for each scenario are summarized in Tables 2.2, 2.3, and 2.4.

- 1) 32-bit I/O constrained implementations: Here, the pixel processor is implemented in the 32-bit embedded system of Subsection 2.6.1. The selection of the parameters NI, NO, NC (number of cores) depends upon the resource availability and the constraints NI×NC≤32 and NO×NC≤32. Table 2.2 shows the combination of parameters chosen for both 12-bit (NI: 12→5) and 8-bit images (NI: 8→5). In this case, we consider the power and resource measurements for implementing both the LUT-cores and the PLB interface.

- 2) 8/12 bit input constrained implementations: In this case, NI is either 8 or 12. We do not restrict NO and NC (except for NO≥NI). NC can be as high as the FPGA device can allow. Table 2.3 lists the parameters and frequency combinations. Power and resources measurements only consider the implementation of the LUT cores (NC NI-to-NO LUTs).

3) Fixed-frequency constrained implementations: This case is similar to the previous (8/12 bit input) case. However, the frequency is fixed and we allow the input bitwidth (NI) to vary. Table 2.4 lists the possible combinations. Power and resources measurements only consider the implementation of the LUT cores (NC NI-to-NO LUTs).

Table 2.2: 32-bit I/O pixel processor constrained implementations. 8-bit images: upper side of table. 12-bit images: entire table. Each case is tested for 5 different frequencies: 100, 66.66, 50, 40, and 33.33 MHz

| NI | NO (NC) |       |       |       |       |       |       |       |  |

|----|---------|-------|-------|-------|-------|-------|-------|-------|--|

| 5  | 5(4)    | 6 4)  | 7(4)  | 8(4)  | 9(2)  | 10(2) | 11(2) | 12(2) |  |

| 6  |         | 6(4)  | 7(4)  | 8(4)  | 9(2)  | 10(2) | 11(2) | 12(2) |  |

| 7  |         |       | 7(4)  | 8(4)  | 9(2)  | 10(2) | 11(2) | 12(2) |  |

| 8  |         | •     |       | 8(4)  | 9(2)  | 10(2) | 11(2) | 12(2) |  |

| 9  | 9(2)    | 10(2) | 11(2) | 12(2) | 13(2) | 14(2) | 15(2) | 16(2) |  |

| 10 |         | 10(2) | 11(2) | 12(2) | 13(2) | 14(2) | 15(2) | 16(2) |  |

| 11 |         |       | 11(2) | 12(2) | 13(2) | 14(2) | 15(2) | 16(2) |  |

| 12 |         | •     |       | 12(2) | 13(2) | 14(2) | 15(2) | 16(2) |  |

Table 2.3: Pixel Processor Implementations for 8/12 bit input images unrestricted by I/O bitwidth. Each implementation is tested for 5 different frequencies: 100.00, 66.66, 50.00, 40.00, and 33.33 MHz.

| Image  | NI | NC                     |    |    | NO |    |    |

|--------|----|------------------------|----|----|----|----|----|

| 8-bit  | 8  | 2<br>4<br>6<br>8<br>10 | 8  | 9  | 10 | 11 | 12 |

| 12-bit | 12 | 2<br>4<br>6<br>8       | 12 | 13 | 14 | 15 | 16 |

Table 2.4: Pixel Processor implementations restricted at 100 MHz with unrestricted I/O bitwidths.

| Image  | N<br>I |   | NO       |    |    |    |    |    |    | NC |

|--------|--------|---|----------|----|----|----|----|----|----|----|

|        | 5      | 5 | 6        | 7  | 8  | 9  | 10 | 11 | 12 | 2  |

|        | 6      |   | 6        | 7  | 8  | 9  | 10 | 11 | 12 | 4  |

| 8-bit  | 7      |   |          | 7  | 8  | 9  | 10 | 11 | 12 | 6  |

|        | 8      |   |          |    | 8  | 9  | 10 | 11 | 12 | 8  |

|        |        |   |          |    |    |    |    |    |    | 10 |

|        | 9      | 9 | 10       | 11 | 12 | 13 | 14 | 15 | 16 | 2  |

| 12-bit | 10     |   | 10       | 11 | 12 | 13 | 14 | 15 | 16 | 4  |

| 12-011 | 11     |   | <u> </u> | 11 | 12 | 13 | 14 | 15 | 16 | 6  |

|        | 12     |   |          |    | 12 | 13 | 14 | 15 | 16 | 8  |

## 2.7 Results and Analysis

This section details hardware resource utilization, optimization of the PPA space for the 3 scenarios of Section 2.6.3, and a discussion of the results. For demonstrating the results for 8-bit images, we use the 'lena' image of size 640x480. For 12-bit images, we use the 'oilp' image of size 512x512. Here, we note that the problem of assessing the accuracy of the results is closely related to the problem of video quality assessment [1]. In the proposed setup, we expect the users to dynamically adjust the accuracy constraints to meet their expectations. An example is provided in Section 2.7.4.

Fig. 2.6 shows some output results for image 'oilp', shown along with the selected I/O bit-widths and their accuracy. Note that the result images for NI=8,12 are nearly identical to those of the double floating point case. For NI=5, there are some clear artifacts in the lower right portion of the image; they appear for PSNR levels around 50dB.

Figure 2.6. Output 'oilp' image results for various input/output cases. Accuracy results are shown as well (simulated gamma correction for  $\gamma$ =0.5)

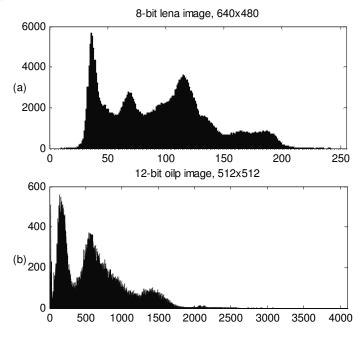

While the accuracy values do depend on specific images, we did not see the Pareto front to vary significantly from image to image. Clearly, the PSNR accuracy of the single pixel functions depends on the histogram of the image (see histograms for 'lena' and 'oilp' in Fig. 2.7).

Figure 2.7. Histograms for both 8-bit 'lena' and 12-bit 'oilp' images

#### 2.7.1 Embedded System results for 32-bit I/O constrained implementations

In this case, we report on the pixel processor implementations described in Table 2.2. In terms of the embedded system implementation, we consider the 8-bit and 12-bit systems separately. In each case, we define the PRR region to be sufficiently large for implementing the largest possible realization. Note that this constraint does not imply that the power consumption will be the same for all 8-bit or 12-bit implementations. Here, note that power consumption is a function of the utilized resources (not allocated resources).

For the 8-bit system, the PRR occupies a tightly packed area of 16×22=352 Slices with

a bitstream size of 47194 bytes. In the case of the 12-bit system, the PRR occupies  $36 \times 128 = 4608$  Slices with a bitstream size of 449015 bytes.

A summary of resource utilization results are given in Table 2.5. Note that the largest pixel processor in the 8-bit case (4 LUT8tot8) occupies 320 Slices (91% of the allocated space for the PRR), and in the 12-bit case (2 LUT12to16) it occupies 4318 Slices (93% of the allocated PRR Slices).

Table 2.5: Embedded Pixel Processor. Resource utilization (XCV4FX60). Case I: 8-bit inputs: NI=NO=8, NC=4. Case II: 12-bitinputs: NI=12,NO=16,NC=2

| Module            | Slice | (%) | FF   | (%) | LUT   | %   |

|-------------------|-------|-----|------|-----|-------|-----|

| Static Region     | 5308  | 21% | 5519 | 11% | 6517  | 13% |

| PRR (Case I)      | 320   | 1%  | 0    | 0%  | 576   | 1%  |

| PRR (Case II)     | 4318  | 17% | 0    | 0%  | 8576  | 17% |

| Overall (Case I)  | 5628  | 22% | 5519 | 11% | 7093  | 14% |

| Overall (Case II) | 9626  | 38% | 5519 | 11% | 15093 | 30% |

The average processing speed resulted in 352.85 Mbps, i.e. a video of size 640x480 can be processed at 143 fps.

Recall that in our applications, we expect that the dynamic reconfiguration rate will be small (in the order of seconds). A reconfiguration speed of 16.28 MB/s is obtained by using the Xilinx® ICAP core, resulting in 2.89 ms and 27.58 ms of reconfiguration time for the 8-bit and 12-bit cases respectively. On the other hand, a dynamic rate of 295.4 MB/s reported in [10] has been achieved using a custom-built DPR controller. However, note that additional hardware overhead is required for achieving faster rates. During reconfiguration, power increase was estimated to be 62.5 mW [6].

#### 2.7.2 Pixel Processor IP resource utilization

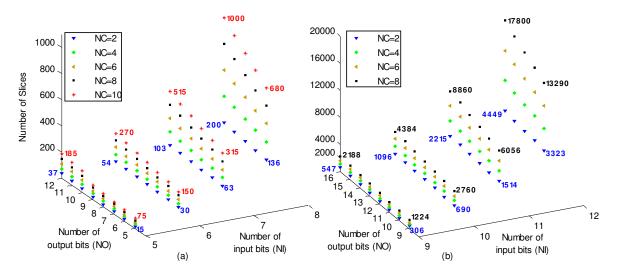

We demonstrate the resource scalability of the approach in Fig. 2.8. Here, the results are independent of the clock frequency. Instead, the resource consumption is a function of

NI, NO, and NC. The hardware resource utilization, based on the number of NI-to-NO LUT cores (NC) is shown in Fig. 2.8 for the cases listed in Table 2.4.

Resource requirements (slices) are clearly clustered for each NI and they grow exponentially as NI increases (e.g. 15,30,63,136 for NI=NO=5,6,7,8 in Fig. 2.8(a)). The amount of resources increases linearly with the number of cores (NC). When we increase the number of output bits (NO), the amount of resources also increases linearly with a less steep slope (e.g. 306 to 547 for NO=9 to 16, NI=9, in Fig. 2.8(b)). The case with NI=12, NO=16, NC=8 requires the largest amount of resources that we have tested in the XC4VFX60 FPGA. Furthermore, for the given device, based on the diversity of the testing, it did not make sense to consider cases for NI>12.

It is also worth noting that resource consumption does not vary significantly with the optimized architecture shown in Fig. 2.1. Thus, we have directed the Xilinx® ISE synthesizer to implement the LUTs without optimizing for the LUT contents, allowing us to effectively swap functions as needed.

Figure 2.8. Pixel Processor IP resource (slices) utilization as NI, NO, NC vary. Device: XC4VFX60 (25280 Slices). Note the exponential resource growth as NI increases. (a) 8-bit system. (b) 12-bit system

#### 2.7.3 Multi-objective Optimization of the PPA space

We present the results from multi-objective (PPA) optimization of the pixel processor for the 3 scenarios of Section 2.6.3. For comparison, we use gamma correction ( $\gamma$ =0.5) which represents a non-linear function that is used for image and video display (see example in Fig. 2.6).

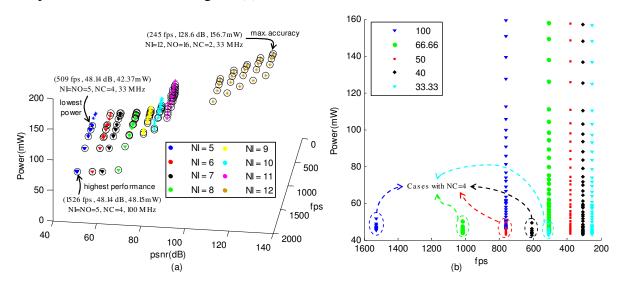

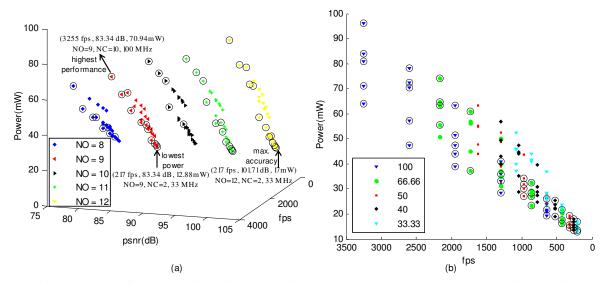

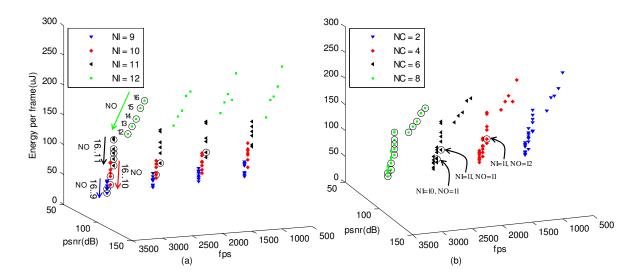

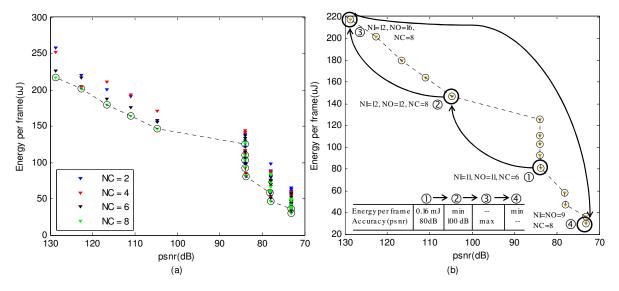

In Fig. 2.9(a), we show the PPA space and the Pareto front for the 32-bit I/O constrained implementations (12-bit image, NI: 12→5). The Pareto front appears to lie on a piecewise planar surface that includes 43% of all possible realizations. They also cover a wide range of the PPA space, suggesting that the approach is effective in generating a wide range of options. Maximum accuracy of 128.6 dB is achieved at 245 fps and power of 156.7 mW. Maximum performance is achieved at 1526 fps with an accuracy of 48.14 dB and power of 48.15 mW. As shown in Fig. 2.9(b), performance increases with frequency and the number of cores. In addition, it is important to note that the accuracy depends on NI and NO in Fig. 2.9(a).