# University of New Mexico UNM Digital Repository

**Electrical and Computer Engineering ETDs**

**Engineering ETDs**

2-13-2014

## A Physical Unclonable Function Based on Inter-Metal Layer Resistance Variations and an Evaluation of its Temperature and Voltage Stability

Jing Ju

Follow this and additional works at: https://digitalrepository.unm.edu/ece etds

#### Recommended Citation

Ju, Jing. "A Physical Unclonable Function Based on Inter-Metal Layer Resistance Variations and an Evaluation of its Temperature and Voltage Stability." (2014). https://digitalrepository.unm.edu/ece\_etds/128

This Dissertation is brought to you for free and open access by the Engineering ETDs at UNM Digital Repository. It has been accepted for inclusion in Electrical and Computer Engineering ETDs by an authorized administrator of UNM Digital Repository. For more information, please contact disc@unm.edu.

| Jing Ju                                                                                 |

|-----------------------------------------------------------------------------------------|

| Candidate                                                                               |

| Electrical & Computer Engineering  Department                                           |

| This dissertation is approved, and it is acceptable in quality and form for publication |

| Approved by the Dissertation Committee:                                                 |

| Dr. James F. Plusquellic , Chairperson                                                  |

| Dr. Payman Zarkesh-Ha                                                                   |

| Dr. Ryan Helinski                                                                       |

| Dr. Fernando Perez-Gonzalez                                                             |

|                                                                                         |

|                                                                                         |

|                                                                                         |

|                                                                                         |

|                                                                                         |

|                                                                                         |

|                                                                                         |

## A Physical Unclonable Function Based on Inter-Metal Layer Resistance Variations and an Evaluation of its Temperature and Voltage Stability

#### BY

### Jing Ju

B.E., Communication Engineering, Hunan University, 2006 M.E., Information & Communication Engineering, Hunan University, 2009

#### DISSERTATION

Submitted in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

Engineering

The University of New Mexico Albuquerque, New Mexico

December, 2013

©2013, Jing Ju

## **Dedication**

This work is dedicated to my parents and husband who have made this possible through their love and support.

## **Acknowledgments**

I would like to thank all who helped me directly or indirectly in making this work possible. First of all, I thank my husband Huiwen Xu who encourage me to pursue my Phd degree in the United States. I owe gratitude to all my family members for their support and encouragement, without which I would't have been able to come this far.

I heartily acknowledge Dr. Jim Plusquellic, my advisor and dissertation chair for his guidance, support, and contributions throughout this work. He is the main source of inspiration for me throughout this research work. I am so grateful for all the opportunities that he offered me. I also thank my committee members, Dr. Payman Zarkesh-Ha, Dr. Ryan Helinski and Dr. Fernando Perez-Gonzalez, for their valuable advice to this research work.

I also thank my colleague Charles Lamech, Jim Aarestad and Fareena Saqib, for all their help and support through the daily discussion.

To everyone at the Electrical & Computer Engineering Department at the University of New Mexico who made this possible, thank you.

## A Physical Unclonable Function Based on Inter-Metal Layer Resistance Variations and an Evaluation of its Temperature and Voltage Stability

by

#### Jing Ju

B.E., Communication Engineering, Hunan University, 2006

M.E., Information & Communication Engineering, Hunan University, 2009

Ph.D., Engineering, University of New Mexico, 2013

#### **ABSTRACT**

Keying material for encryption is stored as digital bistrings in non-volatile memory (NVM) on FPGAs and ASICs in current technologies. However, secrets stored this way are not secure against a determined adversary, who can use probing attacks to steal the secret. Physical Unclonable functions (PUFs) have emerged as an alternative. PUFs leverage random manufacturing variations as the source of entropy for generating random bitstrings, and incorporate an on-chip infrastructure for measuring and digitizing the corresponding variations in key electrical parameters, such as delay or voltage. PUFs are

designed to reproduce a bitstring on demand and therefore eliminate the need for on-chip storage.

In this dissertation, I propose a kind of PUF that measures resistance variations in inter-metal layers that define the power grid of the chip and evaluate its temperature and voltage stability. First, I introduce two implementations of a power grid-based PUF (PG-PUF). Then, I analyze the quality of bit strings generated without considering environmental variations from the PG-PUFs that leverage resistance variations in: 1) the power grid metal wires in 60 copies of a 90 nm chip and 2) in the power grid metal wires of 58 copies of a 65 nm chip. Next, I carry out a series of experiments in a set of 63 chips in IBM's 90 nm technology at 9 TV corners, i.e., over all combination of 3 temperatures: -40°C, 25°C and 85°C and 3 voltages: nominal and +/-10% of the nominal supply voltage. The randomness, uniqueness and stability characteristics of bitstrings generated from PG-PUFs are evaluated. The stability of the PG-PUF and an on-chip voltage-to-digital (VDC) are also evaluated at 9 temperature-voltage corners.

I introduce several techniques that have not been previously described, including a mechanism to eliminate voltage trends or 'bias' in the power grid voltage measurements, as well as a voltage threshold, Triple-Module-Redundancy (TMR) and majority voting scheme to identify and exclude unstable bits.

## **Table of Contents**

| L | ist of Figures                       | xii |

|---|--------------------------------------|-----|

| L | ist of Tables                        | XV  |

| 1 | Introduction                         | . 1 |

|   | 1.1 Motivation                       | 1   |

|   | 1.2 Introduction to PUFs             | . 2 |

|   | 1.3 Contributions                    | 6   |

|   | 1.4 Organization of the Dissertation | 9   |

| 2 | Background                           | 11  |

|   | 2.1 Definition of PUFs               | 11  |

|   | 2.2 PUF Extensions                   | 12  |

|   | 2.2.1 Controlled PUFs                | 13  |

|   | 2.2.2 Reconfigurable PUFs            | 14  |

|   | 2.3 PUF Implementations              | 15  |

|   | 2.3.1 Non-Electronic PUFs.           | 15  |

|   | 2.3.2 Delay-Based PUFs               | 16  |

|   | 2.3.3 Memory-Based PUFs.             | 21  |

|   | 2.3.4 Power Grid-Based PUFs          | 24  |

| 2.3.5           | Misc Category                                             | . 24 |

|-----------------|-----------------------------------------------------------|------|

| 2.4 App         | lications of PUF                                          | . 26 |

| 2.5 Perf        | Formance Metrics of PUFs                                  | 27   |

| 2.5.1           | Uniqueness                                                | . 28 |

| 2.5.2           | Stability (Reproducibility)                               | 29   |

| 2.5.3           | Randomness                                                | 30   |

| <b>2.6 Eval</b> | luation Methods of PUFs                                   | 30   |

| 2.6.1           | Hamming Distance                                          | . 30 |

| 2.6.2           | NIST SUITE                                                | .31  |

| 2.7 Tech        | nniques of Improving the Stability of PUFs                | 32   |

| 2.7.1           | Threshold Mechanism.                                      | . 32 |

| 2.7.2           | Majority Voting and TMR                                   | . 33 |

| 3 Two Pri       | mitives of a PUF Based on Resistance Variations in Metals | .35  |

| 3.1 Exp         | erimental Setup                                           | 35   |

| 3.1.1           | Test Chip Architecture: 90 nm chips                       | . 35 |

| 3.1.2           | Test Chip Architecture: 65 nm chips                       | . 38 |

| 3.1.3           | Challenge Scenarios                                       | . 39 |

| 3.2 Exp         | eriment Techniques                                        | . 40 |

| 3.2.1           | Bias Issues                                               | . 40 |

| 3.2.2           | Dealing with Bias                                         | . 43 |

| 3.2.3           | Bit Stability                                             | 45   |

| 3.2.4           | Statistical Characterization of the Bit Strings           | 46   |

| 3.3 Experimental Results                                               | 47 |

|------------------------------------------------------------------------|----|

| 3.3.1 PG90 Experiments                                                 | 47 |

| 3.3.2 PG65 Experiments                                                 | 53 |

| 3.3.3 Modulus Technique for Bias in PG65 Experiments                   | 57 |

| 3.4 Conclusion                                                         | 59 |

| 4 Stability Analysis of PG-PUFs with Environmental Variations          | 60 |

| 4.1 PGV Experiments and Challenge Scenarios                            | 61 |

| 4.2 Overhead                                                           | 62 |

| 4.3 Experimental Results                                               | 63 |

| 4.3.1 Bit Stability                                                    | 63 |

| 4.3.2 Statistical Characterization of the Bitstrings                   | 67 |

| 4.3.3 Bit-Flip Probability Analysis and Triple-Module-Redundancy (TMR) | 70 |

| 4.4 VDC experiments                                                    | 72 |

| 4.5 Temperature-Voltage Stability Analysis                             | 77 |

| 4.6 Conclusion                                                         | 80 |

| 5 Future Work                                                          | 81 |

| 5.1 Differential-Power-Analysis Resistant VDC                          | 82 |

| 5.2 An Improved Version of PG-PUF                                      | 84 |

| 6 Conclusion                                                           | 87 |

# **List of Figures**

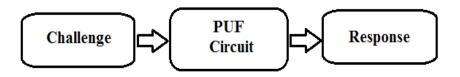

| Fig. 1.1: CRP Protocol                                                             | 3        |

|------------------------------------------------------------------------------------|----------|

| Fig. 1.2: The fingerprint of devices                                               | 4        |

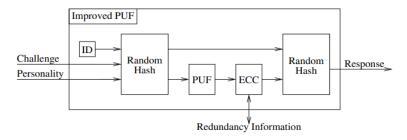

| Fig. 2.1: Using controls to improve a PUF[7]                                       | 13       |

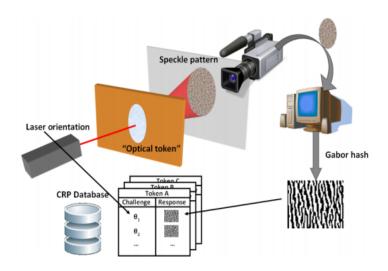

| Fig. 2.2: Basic operation of an optical PUF [12]                                   | 16       |

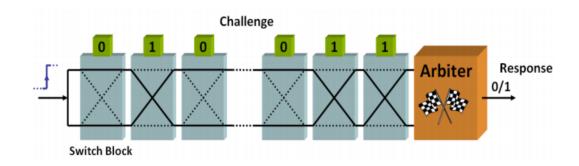

| Fig. 2.3: Basic operation of an arbiter PUF proposed by Gassened et al. [12]       | 17       |

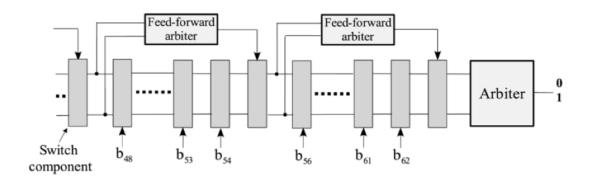

| Fig.2.4: Feed-forward arbiter scheme for improved security [19]                    | 18       |

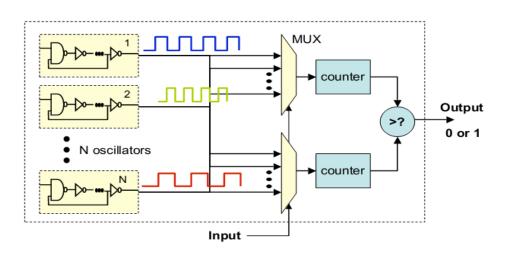

| Fig.2.5: Basic Ring-Oscillator PUF circuit proposes in [7]                         | 19       |

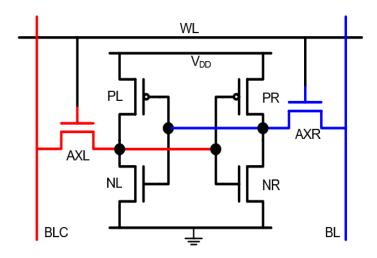

| Fig.2.6: Six transistor SRAM cell [29]                                             | 22       |

| Fig.2.7: Butterfly PUF: cross-coupled latches[32]                                  | 23       |

| Fig. 3.1: Block diagram of 90 nm chips, with voltage sense pins along top and tw   | o arrays |

| of SMCs, a 7x7 outer array and a 6x6 inner array                                   | 36       |

| Fig. 3.2: SMC schematic in 90 nm chips                                             | 37       |

| Fig. 3.3: a) Block diagram of 65 nm chip and (b) details of the SMC                | 39       |

| Fig. 3.4: V <sub>DD</sub> profile using SMCs of a 90 nm chip                       | 41       |

| Fig. 3.5: Voltage drops from 4,000 SMCs on a PG65 chip                             | 42       |

| Fig. 3.6: Average voltage drops across 80 rows of PG65                             | 43       |

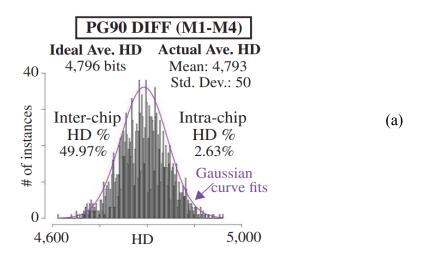

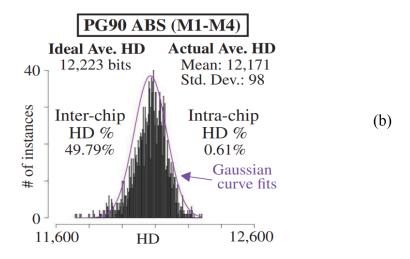

| Fig. 3.7: Distribution of HDs using (a) stable DIFF (M1-M4) (b) stable ABS (M1-M4) | -M4) bit |

| strings from PG90 exps.                                                            | 49       |

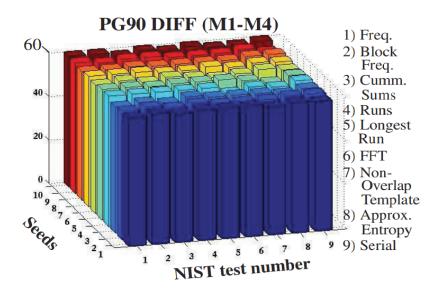

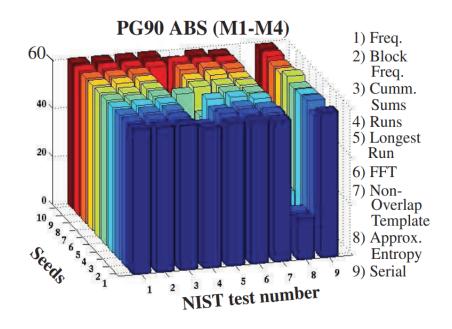

| Fig. 3.8: NIST test suite statistics using DIFF (M1- M4) stable bit strings in PG90 exps. |

|-------------------------------------------------------------------------------------------|

|                                                                                           |

| Fig. 3.9: NIST test suite statistics using ABS (M1-M4) stable bit strings in PG90 exps.   |

| 52                                                                                        |

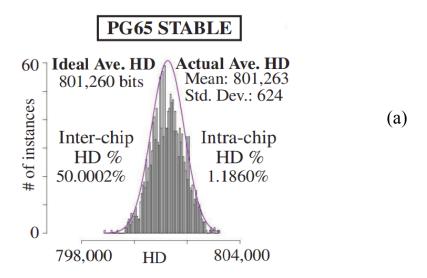

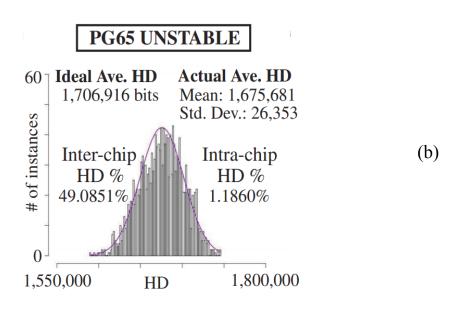

| Fig. 3.10: Distribution of HDs using (a) stable ABS (b) unstable ABS bit strings from     |

| PG65 exps54                                                                               |

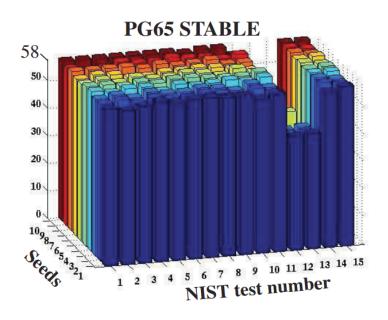

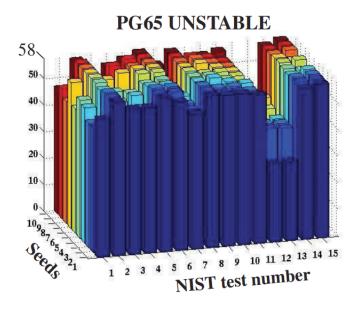

| Fig. 3.11: NIST test suite statistics using stable bit strings for PG65 exps              |

| Fig. 3.12: NIST test suite statistics using unstable bit strings for PG65 exps            |

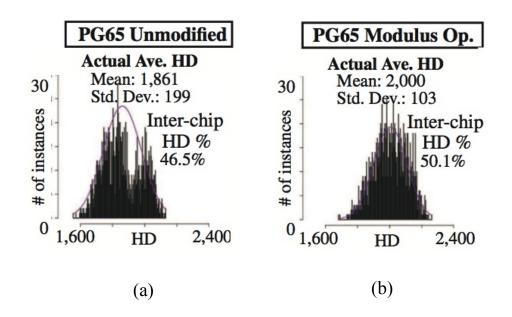

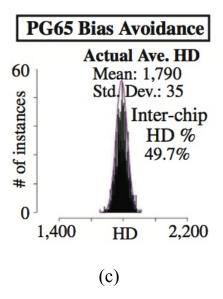

| Fig. 3.13: HD analysis of bit strings using unmodified voltages (a) with modulus op. (b)  |

| and using bias avoidance (c) for PG65 exps                                                |

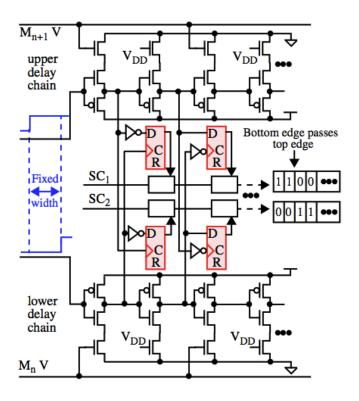

| Fig. 4.1: SMC schematic in 90 nm chips                                                    |

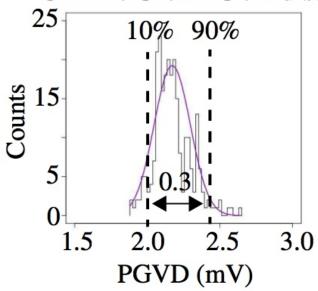

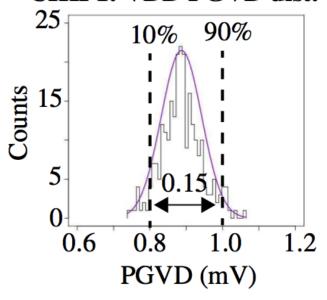

| Fig. 4.2: CHIP1 GND and VDD PGVD distribution with Gaussian curve fits and 10%            |

| and 90% thresholds.                                                                       |

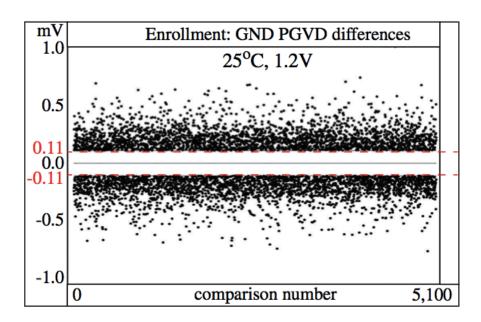

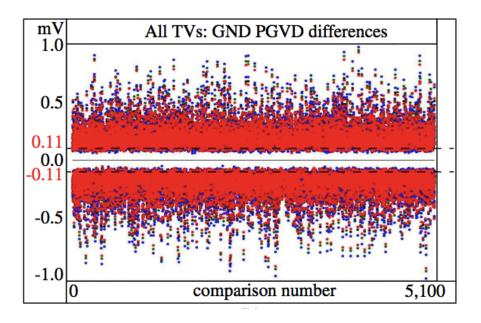

| Fig. 4.3: CHIP1 GND PGVD differences computed for bit generation during enrollment        |

| (a) and regeneration (b) at 9 TVs. Points in upper portion of plots generate '1's,        |

| points in lower portion generate '0's                                                     |

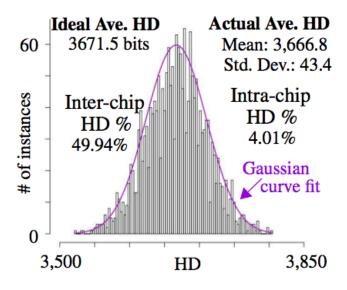

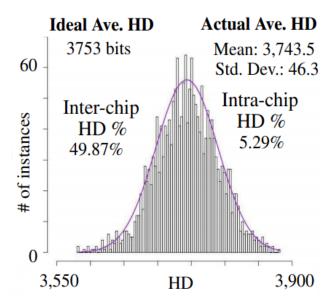

| Fig. 4.4: Distribution of HDs using stable bitstrings from 63 chips. Number of HD is      |

| 1,953 using bitstrings of length 7,343 bits                                               |

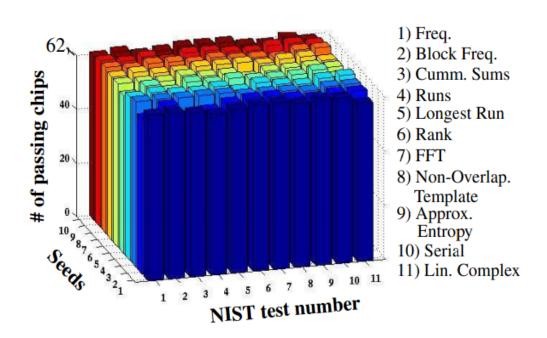

| Fig. 4.5: Number of passing chips from NIST tests using 11 of the 15 applicable tests 69  |

| Fig. 4.6: TMR process for bitstring regeneration.                                         |

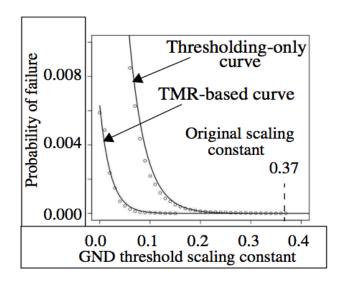

| Fig. 4.7: GND threshold scaling constant vs. probability of failure (y-axis)              |

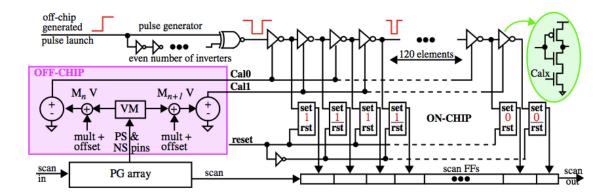

| Fig. 4.8: Voltage-to-Digital Converter (VDC). On the left side is off-chip | instrumentation    |

|----------------------------------------------------------------------------|--------------------|

| that measures two voltages from the PG array, adds and offset ar           | nd programs the    |

| Cal0/Cal1 inputs of the VDC on the right.                                  | 74                 |

| Fig. 4.9: Distribution of HDs using stable bitstrings from 63 chips. Nu    | umber of HDs is    |

| 1,953 using bitstrings of length 7,506 bits.                               | 75                 |

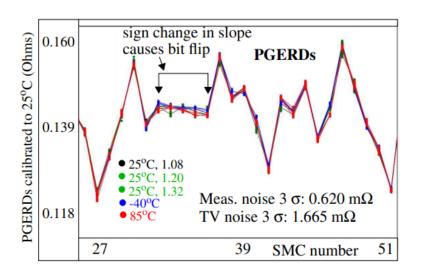

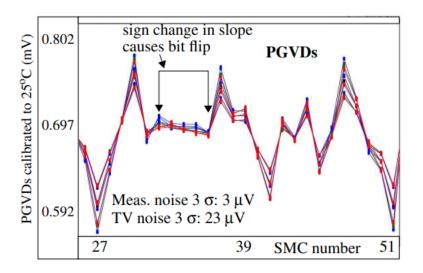

| Fig. 4.10: Subset of PGERD (top) and PGVDs (bottom) from M2-M3 me          | etal layer pairing |

| for GND grid. Data from 9 TV corners is calibrated to 25C                  | OC, 1.2V. All 11   |

| samples from 9 TV corners are also shown for each SMC                      | 79                 |

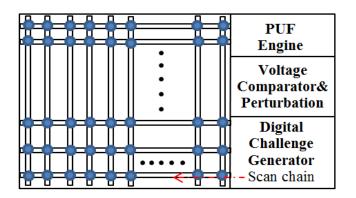

| Fig. 5.1: Proposed differential-Power-Analysis (DPA) resistance VDC        | 84                 |

| Fig. 5.2: PUF IP-block (blue circles represent SMC arrays)                 | 86                 |

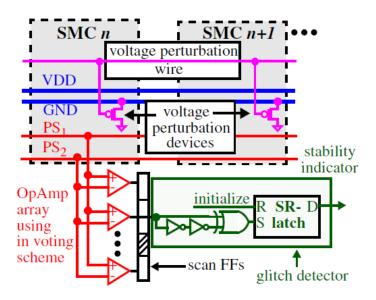

| Fig. 5.3: Voltage Comparator and Perturbation circuit                      | 87                 |

## **List of Tables**

| Table 3.1: Results for DIFF and ABS analyses with the thresholding scheme for PG90 |

|------------------------------------------------------------------------------------|

| exps50                                                                             |

| Table 3.2: Improvement of inter-chip HDs for DIFF and ABS analyses with the        |

| thresholding scheme for PG90 exps                                                  |

| Table 3.3: Results with the thresholding scheme for PG65 exps                      |

| Table 4.1: Results with the thresholding scheme for both PGV and VDC experiments   |

| across 9 TV corners for PG90 exps                                                  |

### Chapter 1

### Introduction

#### 1.1 Motivation

As electronic devices are becoming ubiquitous and interconnected around people's daily life, security, trustworthy computing, and privacy protection have emerged over the past decades as hardware design objectives of great significance. For many emerging applications that need exceptional security in identifying and authenticating users, such as intellectual property (IP) protection, system security is traditionally based on the protection of secret keys. Conventionally, these secret keys are based on battery-backed RAM or NVM such as ROMs, fuses, or flash/EEPROM. These secret keys need to be well managed and stored to avoid releasing information to attackers. Over the past several years, many kinds of attacks for exacting, estimating, or cloning secret keys that are stored digitally in NVM have been successfully developed and reported. When the adversaries have the full and direct access to ICs, the situation is getting especially problematic and worse. Also, integrating a NVM for an IC incurs additional costs and fabrication overhead.

The described problem has become more intense recently, and this motivated the

idea of using inherent random manufacturing variations to serve as identifiers for ICs. It provides a promising alternative which can address the present challenges of traditional security that were described earlier. This idea is not new and a kind of circuits called Physical Unclonable Functions, which store secret keys in silicon circuits by exploiting uncontrollable randomness due to manufacturing process variations, have been proposed and successfully implemented to overcome some of the problems faced by traditional techniques. PUFs are easy to build and can be implemented without any additional manufacturing steps since they are based on the existing resources of physical variations of the IC. Due to the inherent properties and advantages of PUFs, the research of them has becoming more and more attractive in recent years.

#### 1.2 Introduction to PUFs

When ICs are manufactured, there will be inevitable inherent process difference even these ICs are fabricated from the same lot or wafer. Precise control over the fabrication of IC components is becoming more difficult in advanced technology generations, resulting in a wide range of electrical variations among and within the replicated copies of the chip. Due to the existing manufacturing process variations, it is difficult or impossible to create two exact ICs. A PUF is such an embedded structure that are designed to be sensitive to variations in the printed and implanted features of wires and transistors on the IC. Signal variations that occur within the IC are the source of entropy for the PUF.

Usually, the physical variations of manufacturing process manifest as analog variations in the chips' parametric properties, such as wire delay, threshold voltage.

Therefore, a PUF is designed to measure and 'digitize' these analog electrical variations. When characterizing the PUF in a more understandable way, it can be considered as a function that maps challenges to responses. The basic operation is shown in Fig. 1.1: when a **Challenge** (C) is applied to the PUF, it reacts with a **Response** (R). And the Challenge together with its associated response is known as Challenge-Response Pair (CRP).

Fig. 1.1: CRP Protocol.

By applying a set of 'challenges' to the PUF, it can produce a large, ideally exponential, set of unique bitstring, which can be considered as the fingerprint or DNA of a chip. Since the challenges are typically 'digital' and therefore they can be generated on-chip from a pseudo-random number generator such as a linear feedback shift register (LFSR).

Nothing in manufacturing process of a chip is exact, and therefore, all fabricated physical components, e.g., wires and transistors, on the chip vary from their nominal characteristics. Although it is possible to measure these physical variations directly, it is extremely difficult or impossible to do so without sophisticated process and equipment. The analog electrical and parametric variations that result, on the other hand, can be measured and processed more easily, and in many cases, this can be done using on-chip

instrumentation. Many proposed PUF-based systems are defined in this manner, and differentiated by the type of electrical and/or parametric variations they leverage. The magnitude and stability of variations in, e.g., transient current delay, leakage, resistance, capacitance, etc. are dependent on the technology and environment, and therefore, some PUF systems can better meet the important criteria described above than others.

Fig. 1.2: The fingerprint of devices.

Due to the inherent and particular characteristics, PUFs are promising components in the next generation of IC security and the bitstring generated from PUFs can be used in security applications such as encryption, authentication, feature activation, metering, etc. Since the bitstrings are generated on-the-fly using dedicated hardware primitives and processing engines, and thereby avoid the need for storage in on-chip NVMs. This feature not only improves their resilience to invasive attacks designed to steal the secret key material, but it also reduces the cost of manufacturing the IC. The latter is true because, in many cases, PUFs are designed using components that can be fabricated using standard

complementary metal-oxide-semiconductor (CMOS) processing steps, and therefore, the cost of integrating non-standard components, such as NVM, is eliminated. Another important characteristic of the PUF as a next generation security mechanism is its potential for generating large numbers of repeatable random bits. This feature offers new opportunities for software processes to strengthen security mechanisms, for example, by allowing frequent rekeying in encrypted communication channels and by allowing a large, changing set of shared keys to be utilized among multiple communicating entities.

From the above description of PUFs, we know PUFs can provide security advantages over traditional key generation mechanisms because they are volatile and very difficult to clone. Unfortunately, the analog nature of the underlying random variable make the PUF sensitive to environmental variations such as temperature and power supply noise. For some important applications such as keys for encryption, they require that the PUF must produce the same bit string for a fixed challenge under varying environment. Therefore, in order to effectively move from theoretical exercises to commercial products, the 'quality' of the bitstring produced can be measured against many statistical metrics, but needs to meet three important criteria: 1) the bit string is unique for each chip, and thereby able to distinguish each chip in the population, 2) the bit string is random for each chip, and therefore is difficult or impossible to model and predict by an adversary, and 3) the bit string is stable, i.e., it remains constant for a given chip over time, and under varying environmental conditions. A PUF that is able to meet these requirements can be used in applications related to security including system identification, key generation for encryption, authentication via CRPs, IP protection,

remote service etc.

In this dissertation, Inter-chip hamming distance (HD) is used to determine the uniqueness of the bitstrings among the population of chips. Similarly, the National Institute of Standards and Technology (NIST) statistical test suite is used to evaluate the randomness of the bitstrings produced by each chip. And intra-chip HD can be used to evaluate stability of the bitstrings, i.e., the ability of each chip to reproduce the same bitstring time-after-time, under varying temperature and voltage conditions.

#### 1.3 Contributions

In this dissertation, I investigate two implementations of a PUF that measures resistance variations in metal wires that define the power grid of the chip, and we call it PG-PUF. There are several benefits of the PG-PUF. First, resistance of metal wires varies linearly with temperature and can easily be designed to be resistant to aging effects such as electromigration. Second, resistance can be measured using a simple direct current (DC) process, which can improve signal-to-noise significantly over PUFs that leverage alternating current (AC) characteristics, such s delay. Third, metal components are ubiquitous on a chip, with the power grid consuming a large fraction of the metal resources, e.g., 15-25% is typical in most commercial power grid designs. Fourth, the power grid is a stacked structure, offering a 3<sup>rd</sup> dimension in which to leverage entropy. Last, the interconnected structure of the wires in the power grid complicates the interaction among variations in resistance that occur, thereby increasing the complexity of model building attacks.

In order to fully leverage metal resistance variations, I design a PUF that can measure them in each of the metal layers of the power grid. In order to reduce bias issues and correlations that exist in the  $V_{DD}$  and GND grids, inter-metal layer voltage drops/rises, which are computed by subtracting the voltages measured from consecutive metal layers, are introduced. By this method, the independent resistance variations that occur in each of the metal layers of the power grid can be leveraged.

First, the experiments are carried out on a set of chips fabricated in IBM's 90nm, 9 metal layer bulk silicon process, and on a set of 65 nm chips fabricated in IBM's silicon-on-insulator (SOI) process at room temperature. The quality of the bit strings are evaluated using inter-chip and intra-chip HD, as well as a suite of statistical tests available from NIST [1].

Then, I focus on determining the temperature and voltage (TV) stability of the PG-PUF. A significant benefit of using metal structure is that "noise-related" variations, such as those introduced by TV variations, result in linear changes to the measured voltages. This linear scaling characteristic allows the relative magnitude of two voltages to remain consistent across changes in temperature and voltage, which, in turn, improves the stability of the PUF to bit-flips, when compared for example to PUFs which leverage transistor-based variations. In the experiments, I evaluate the PG-PUF at 9 TV corners, i. e., over all combinations of 3 temperatures; -40°C, 25°C, 85°C, and 3 voltages; nominal and +/-10% of nominal. The evaluation is carried out on a set of chips fabricated in IBM's 90 nm, 9 metal layer bulk silicon bulk silicon process. The stability of the bitstring is measured using intra-chip HD and 'probability of failure' techniques. Randomness and

uniqueness are also evaluated using NIST test suite and inter-chip HD methods.

I also investigate an on-chip voltage-to-digital converter (VDC) for measuring voltage variations (which reflect resistance variations in the metal wires) and its stability across the 9 TV corners. The VDC is used to digitize the voltage drops produced from each metal layer of the power grid.

Besides, I introduce several noise resilient bit-flip avoidance schemes, which are used to reduce the probability of a failure to reproduce the bitstring to less than 1E-9 under varying environmental variations. One technique is called thresholding mechanism, which derives a voltage threshold from a chip's voltage drop distribution profile that is used to decide whether a given voltage comparison generate a strong bit or a weak bit. The second scheme is a bitstring replication method that mimics a popular scheme used in fault tolerance called Triple-Module-Redundancy (TMR). TMR is proposed for fixedlength bitstrings that can further improve the stability of the bitstrings. Although these techniques discard a large fraction of bits, they provide several advantages and can be used as an alternative to error correction and Helper Data schemes [2][3]. The helper data (public data) associated with these methods reveals nothing about the secret bitstring since every bit is independent from others. Also, the helper data is simple data for both of these techniques and its size can be easily reduced by using a certain compression technique. What's more, these methods increase the difficulty of model-building since bitstrings are constructed using only a subset of the possible voltage pairings. However, for error correction scheme, the complex algorithm implementation will require significant resources and overhead. And also the error correction scheme will release

some secret information. Therefore, both the thresholding and TMR are easier and cheaper to implement on chip when compared with the error correction schemes. That's the main reason we avoid using the error correction scheme to fix unstable bits issues for PUFs. In this dissertation, both techniques are demonstrated to provide a significant improvement to inter-chip HD and the results obtained from NIST statistical tests.

### 1.4 Organization of the Dissertation

This dissertation is organized as follows:

In Chapter 1, the motivation of using PUFs for security applications is briefly described. Then the basic idea of PUFs and their advantages over conventional methods are given. Finally, the requirements for PUFs in order to be used for practical security applications and some methods of evaluating the quality of them are discussed.

In Chapter 2, the development of definition for PUFs are described. Then the previous work about PUFs and classification of the popular PUFs are covered. Also, the applications of PUFs are discussed. Besides, several statistical methods for evaluating the quality of bitstrings generated from PG-PUFs are briefly described. Finally, some techniques used to improve the stability of PUFs are given.

In Chapter 3, two implementations of PG-PUFs for both IBM 90 nm and 60 nm technologies are introduced and experiments are carried out without considering environmental variations. The output bitstrings are analyzed and evaluated by using interchip HD, intra-chip HD and NIST tests suite.

In Chapter 4, experiments are carried out across different temperatures and voltages in order to evaluate the stability of PG-PUFs against environmental variations. Several methods of improving the stability of PG-PUFs are demonstrated. The quality of bitstrings are also evaluated using statistical tests.

In Chapter 5, some future work is proposed.

Finally, the findings and contributions of this dissertation are concluded.

## Chapter 2

## **Background**

Study on manufacturing process variations and PUFs has been gaining increasing interest and attention since the concept of PUFs was firstly introduced in [4]. Over the past couple of years, the attention on PUFs has risen substantially, making them a hot topic in the field of hardware security and leading to an expansion of published results. This chapter will provide an overview of PUFs. The basic definition will be given in Section 2.1, different types of PUFs will be classified in Section 2.3, many important applications will be discussed in Section 2.4. At the end of this chapter, several methods used for evaluating the quality of PUFs will be listed. And many techniques used to improve the stability of PUFs are also discussed.

#### 2.1 Definition of PUFs

It is widely accepted that the significance and complexity of process variations is increasing as technologies are aggressively scaled [5][6]. The idea of using these manufacturing process variations as identifiers for ICs has showed up for a long time. However, the concept of PUFs didn't appear until recent years. There have already been several proposals for the definition of required PUF properties. Firstly, they were called

Physical One-Way Function [4], and later renamed to Physical Random Functions [7], but eventually resolved to Physical Unclonable Functions (PUFs). The exact definition for this kind of circuits is still under discussion. The most popular definition of PUFs is described in [8] by Gassend et al.:

"A physical Random Function (PUF) is a function that maps challenges to responses that is embodied by a physical device, and that verifies the following properties:

- Easy to evaluate: The physical device is easily capable of evaluating the function in a short amount of time.

- Hard to predict: From a polynomial number of plausible physical measurements, an attacker who no longer has the device, and who can only use a polynomial amount of resources can only extract a negligible amount of information about the responses to a random chosen challenge."

There are also other descriptions of PUFs, e.g., in [9], the authors described that "Physical Unclonable Functions consist of inherently unclonable physical systems. They inherit their unclonability from the fact that they consist of many random components that are present in the manufacturing process and cannot be controlled. When a stimulus is applied to the system, it reacts with a response".

#### 2.2 PUF Extensions

From the description in section 1.2, we know that PUF is a function that can map challenges to responses. Therefore, according to how many CRPs different PUFs can

generate with the same hardware resources, there are two different situations: strong PUFs and weak PUFs. Usually, Strong PUFs can produce an exponential number of CRPs which are more difficult for attackers to model and learn, while weak PUFs only have a linear number of them. Besides trying to generate as many CRPs as possible, people have also developed some other methods to increase the security of PUFs. Some people use pre-processing or post-processing schemes to obtain more robust bitstrings. Some people combine PUFs with a particular algorithm which can make model-building attacks more difficult. In the following part, I will discuss more details on how to obtain these improvements.

#### 2.2.1 Controlled PUFs

The concept of Controlled PUFs or (CPUFs) was introduced by Gassend et al. in [2], which combine a PUF with other primitives. The CPUFs can only be accessed via an algorithm that is physically bound to the PUF in an inseparable way, and any attempt to break the link between the PUF and the algorithm will definitely lead to the destruction of the PUF. Therefore, by using controls to the PUFs, it is possible to make a PUF more robust and reliable. In [7], the authors summarized several controls that can be placed around the PUF to improve its function. Fig. 2.1 shows the full details of these controls.

Fig. 2.1: Using controls to improve a PUF[7].

#### 2.2.2 Reconfigurable PUFs

In 2009, the authors in [10] defined a new primitive, called reconfigurable PUF (rPUF). The rPUF is a PUF with a mechanism, which can transform the original PUF into a new PUF with a new unpredictable and uncontrollable challenge-response behavior. Meanwhile, the rPUF can still preserve all the security properties of the original PUF. In this literature, two practical instantiations of rPUFs were presented. One is based on the optical PUF. When the structure of the optical PUF is irradiated with a laser beam outside the normal operating conditions, the structure will change its internal configuration. This change will cause a rearrangement of the optical scatters, which will lead to a completely new random CRP behavior. Another is based on phase change memory. By rewriting the memory cells, a new random CRPs can also be generated.

Later in 2011, more novel structures of the reconfigurable PUFs were discussed in [11]. The first method is adding reconfigurable elements before the challenges applied to the PUF, while the original properties and performance of the PUF will still be preserved; another idea is to add extra reconfigurable components to process the output before using it as an authentication key. The authors in the literature also stated that instead of only making CPRs reconfigurable by processing the challenge and responses directly, they can also alter the main PUF circuit to update the challenge-response behavior.

### 2.3 PUF Implementations

Since the introduction of concept of PUFs, many studies on PUFs have been reported.

There have been a large variety of PUF implementations, and the list still keeps getting larger. In this section, I will mainly discuss the following several types of PUFs: 1) Non-electronic PUF. (2) Delay-based PUF. (3) Memory-based PUF. (4) Power-grid PUF. 5) Misc Category.

#### 2.3.1 Non-Electronic PUFs

An earlier non-electronic PUF is a so-called optical PUF [4], which use microscopic refractive glass spheres in a small transparent epoxy plate. It is stimulated using a heliumneon laser and the speckle pattern represents the response. The basic implementation and operation of an optical PUF is shown in Fig. 2.2 [12]. It is obvious that the optical PUF has a really complex structure and therefore cannot be used for large scale production.

Fig. 2.2: Basic operation of an optical PUF [12].

In [13], the authors introduced a technique which can make use of the reflection of a focused laser beam by the irregular fiber structure of a paper document. The particular

pattern of the reflection can be used as fingerprint of that paper and therefore can be used as anti-counterfeiting strategy for currency notes. In [14], the authors proposed a new technique for exacting unique fingerprints from identical CDs. It was observed that the manufacturing variations of the lengths of lands and pits on a regular CD are large enough to be measured from the electrical signal of the photodetector in a regular CD player. In [15], a kind of PUFs called magnetic PUFs were introduced, which use the inherent uniqueness of the particular patterns in magnetic media, e.g., for credit cards. Other non-electronic PUFs including RF-DNA [16] and acoustical PUFs [17] were also proposed.

## 2.3.2 Delay-Based PUFs

Delay-based PUFs utilize the variations in propagation delay of identical circuits to derive a secret response. There are mainly two popular types of delay-based PUFs: arbiter PUFs and ring oscillator (RO) PUFs.

The basic idea of the arbiter PUF was proposed in [18][19], which exploits the statistical delay variations of wires and transistors across ICs to introduce a digital race condition on two paths on a chip and to be implemented with an arbiter to decide which path won the race. The basic structure of the arbiter PUFs is shown in Fig. 2.3. In this structure, a sequence of switches is connected in series and each of them is controlled by one bit of the challenge. At the end, an arbiter decides which path is faster and assigns a digital '1' or '0' accordingly. In real world, the two delay paths are 'lay-out' in an identical fashion. However, due to the uncontrollable manufacturing processing variations, the

delays of these two delay paths vary randomly across different chips, which can allow the generation of unique responses for every IC.

Fig. 2.3: Basic operation of an arbiter PUF [12]

From the structure of the arbiter PUF, it is known that the total delay of the chain should be the sum of the delay of the separate blocks. Therefore, the arbiter PUF is susceptible to model-building attacks. By observing a number of CPRs, the attackers can build a mathematical model of the PUF that predicts the response to an unseen challenge. In order to make the model-building attacks to the arbiter PUF more difficult, in [19], a feed-forward arbiter PUF was depicted as shown in Fig. 2.4. In this structure, multiple challenge bits are determined by the racing result in intermediate stages instead of being provided by a user as that for the basic arbiter PUFs [8][18]. Since the internal feed-forward bits are hidden to an adversary, it is difficult to build a precise model of a feed-forward arbiter PUF.

Fig. 2.4: Feed-forward arbiter scheme for improved security [19].

However, experimental results from literatures [20] show that with more advanced modeling techniques it is still possible to build an accurate model for the feed-forward arbiter PUF. More advanced architectures were proposed in [11][21]. In [21], the authors developed a new set of techniques for FPGA-based PUF design and implementation, which use reconfigurable structure to eliminate some of the classical arbiter-based PUF limitations and make them more resistant to modeling.

Also, note that arbiters in practice are implemented by D flip-flops. When the absolute delay difference of the arriving signals is smaller than its setup and hold time, which results in metastability and high sensitivity to environmental variations. In order to solve these problems, Devadas et al. in [22] introduced a new arbiter-based PUF structure that exploits programmable delay lines (PDL) to tune and cancel out the delay skews caused by asymmetries in routing on FPGAs. The authors in this literature also stated that there is still other direction of improving the security of arbiter-based PUFs, which is by reducing noise probability in PUF responses. Further, a PDL-based symmetric switch

structure was also introduced to resolve the routing issues.

Another type of delay-based PUFs is called Ring-Oscillator PUF (RO-PUF). The basic structure of a RO-PUF is proposed in [7] as shown in Fig. 2.5. An AND gate in the loop allows to enable/disable the oscillation. As introduced in [7], the RO-PUF uses a different approach towards measuring small random delay deviations caused by manufacturing variability. The source of this randomness is again the uncontrollable effect of process variations on the delay of digital components. The basic idea of RO-PUF is to connect the output of the delay chain (that for the Arbiter PUFs) to the input and measure the frequency (instead of delay).

Fig. 2.5: Basic Ring-Oscillator PUF circuit proposes in [7].

However, the RO-PUF suffers from the systematic or correlated process variation and the environmental noise caused by the voltage and temperature variations, which degrade the uniqueness and the stability of PUF responses [12]. There have been many effective solutions trying to improve the performance of RO-PUFs [23][24][25]. In [23],

the authors presented a temperature-ware cooperative RO-PUF implementation to reduce the hardware cost. In [24], Maiti et al. proposed a compensation method to mitigate the negative influence of systematic process variations. The method is as follows: firstly place the group of ring oscillators as close as possible to each other, and secondly pick the physically adjacent pair of ROs while evaluating a responses bit. Also, they introduced a novel configurable ring oscillator technique, which can drastically reduce the effect of noise on PUF responses. In [26], Mansouri et al. introduced a new type of RO-PUF. In this structure, the inverters composing the ring oscillators can be supplied by independent voltages. The authors stated that this basic concept can be used to design temperature-aware RO-PUFs, whose output bits do not depend on the operating temperature. Therefore, the reliability of the PUF is improved to temperature variations.

Also, an improved RO-PUF called reconfigurable PUF with a mechanism to update its challenge-Response pairs was proposed in [10]. This PUF preserves the properties of original PUF but has unpredictably different challenge-Response behaviors after every reconfiguration.

For all the delay-based PUFs, they are based on the delay variations and propagation time comparison or rings oscillator frequency comparisons. There exist contest that these delays or frequencies are too similar to decide the response. Based on this contest, the Grenoble INP team in [27] developed a PUF based on asynchronous communication in order to generate violation depending of flip-flop set-up time. When a synchronous design does not respect the setup time, this can induce metastability in the circuit (a "quasi-stable" state which will be resolved either by '0' state or by '1' state in

an undefined time).

Besides these two popular types of delay-based PUFs, in [28], a new delay-based PUF architecture called glitch PUF was proposed, which exploits glitches that behave non-linearly from delay variation between gates and the characteristic of pulse propagation of each gate. The authors presented a method to accurately acquire the waveforms and to convert them into response bits and also evaluate the characteristics of glitch PUF. This structure is expected to solve the current problem of delay-based PUF that it is easy to predict the relation between delay information and generated information.

### 2.3.3 Memory-Based PUFs

In this section, another popular type of PUFs that leverage the bi-stability characteristics of memory primitives will be listed. It is implemented by putting a memory cell into an metastable state and then releasing it. In most cases, digital memory cells heavily prefer one of the two stable states. However, in some cases, meta-stability results, which results in oscillations between stable states and non-deterministic settling times. There have shown several kinds of memory-based PUFs such as Static Random-Access Memory (SRAM) PUFs [29][30][31], Butterfly PUFs [32], Flip-flop PUFs [33], Latch PUFs [34].

In [29], the authors provided the first construction of an intrinsic PUF based on SRAM memory randomness. The typical SRAM PUF is implemented with six transistors (MOSFETs) as shown in Fig. 2.6, and formed of two cross-coupled inverters and two access transistors connecting to the data bit-lines based on the word-line signal. In the

same year, a very similar concept was also presented in [30].

Fig. 2.6: Six transistor SRAM cell [29].

Later in the year of 2008, the authors of [32] proposed a new PUF structure called Butterfly PUF that can be used on all types of FPGAs. The structure of the butterfly PUF is as shown in Fig.2.7, constructed as symmetrically as possible by manual routing of the signal wires. It consists of two latches, each with a preset signal and a clear signal. The data signal is transferred to the output when the CLK is high. The stable state of the butterfly PUF depends on the slight differences in the delays of the connecting wires which are designed using symmetrical paths on the FPGA matrix.

The authors in [35] introduced an SRAM PUF which they implemented on a microcontroller using the internal SRAM block. In [33], the authors proposed a so-called flip-flops PUF, which is based on the power-up behavior of regular flip-flops. The experimental results in this literature show that this flip-flop PUFs is equivalent to the previous proposed SRAM PUFs. The authors stated that the flip-flops PUFs have some

advantages with regard to the use in reconfigurable devices.

Fig. 2.7: Butterfly PUF: cross-coupled latches [32].

In [36], the authors presented detailed evaluations of 90 nm 6T-SRAM as PUF for secure key generation in wireless sensor nodes. In order to put SRAM PUF in low-power security applications, a design for using a 65 nm 10T sub-threshold SRAM as a PUF was proposed in [37]. In this design, significant improvements are achieved in power consumption and security over existing designs. Experimental results show that this design is suitable for ultra-low power security applications since it have more than 50% of uniqueness and near 100% reliability with a 60% of power saving.

These memory-based PUFs are reasonably resistant to model-attacks compared to the delay-Based PUFs as their responses are based on independent random elements. But the memory-based PUFs grow with overheads (size) exponentially related to the length of their challenges.

#### 2.3.4 Power Grid-Based PUFs

The power grid-based PUF (PG-PUF) was firstly proposed in [38], which is based on the resistance variations in the power grid of a chip. There are two strategies for the PG-PUFs in this paper: one is based on voltage drops, and another is based on equivalent resistance. Voltage drops and equivalent resistances in the power distribution system are measured using external instruments and it is again observed that these electrical parameters are affected by random manufacturing variability.

The authors in [38] also stated that there are many advantages using process variations of power grid as PUFs. Firstly, the PG-PUFs is based on the variations in only passively components of the IC, specifically the power grid, and is therefore less susceptible to environmental variations. Secondly, because the power grid is an existing distributed resource in every design, the overhead of the PG-PUFs is lower than other kind of PUFs.

# 2.3.5 Misc Category

In the year of 2011, many novel PUFs showed up [39][40][41][42][43]. In [39], the authors presented PUF circuits designed to exploit inherent fluctuations in physical layout, called litho-PUFs. Variations arising from proximity effects, density effects, etch effects, and non-rectangularity of transistors are leveraged to implement lithography-based PUFs. And the authors showed that the uniqueness level of these PUFs are adjustable and are typically much higher than traditional ring-oscillator or tri-state buffer

based approaches. In [40], the authors proposed a PUF called PE-PUF. This PUF takes into account process variations, temperature, power supply noise and crosstalk, which are major sources of variations and noise in ICs. In [41], the authors introduced a new class of dynamic PUF (DPUF) that employs dynamic system alteration with respect to individual gate speeds, enabling each user to create his own PUF as needed. The authors stated that this DPUF has very high unpredictability and can easily be stabilized. The authors in [42] presented a PUF called Bi-stable Ring PUF. The basic idea of it is based on the fact that an inverter ring consisting of an even number of inverters has two possible stable states. The PUF proposed in [43] is built using leakage sensors with each measuring the leakage current of a transistor. When compared with a popular ring oscillator PUF architecture of the same entropy, the authors stated that this proposed PUF consumes about 80% less power, occupies about 85% less area, and has a high level of stability across a wide range of temperature. Very recently, the authors in [44] used the Buskeeper as a PUF, and gave experimental results showing that the Buskeeper PUF can be considered as a good alternative to D flip-flop PUFs since the Buskeeper PUF are much more efficient than D flip-flops in regard to the amount of hardware resources required while they can maintain the performance as well as the already and generally accepted ones. In [45], J. Aarestad et al. introduced a new PUF called the Hardware-Embedded Delay PUF, or HELP, which leverages the natural variations that occur in the path delays of a core micro on a chip to create an unique, stable, and random bistring of virtually any length.

# 2.4 Applications of PUF

PUFs have shown great promise in many security applications such as IC identification [7][46][47][48], generating unique keys for encryption [49][50], authentication [8][47] [51][52], IP protection on FPGAs [32], RFID for anti-counterfeiting [53].

The unclonability property makes PUFs attractive for supporting anticounterfeiting technologies, in the biometric sense. Therefore, PUFs can be used to

identify and authenticate a chip. The process works by the following steps: at time '0'

(after manufacturing), a trusted entity applies a process called enrollment phase. In this

phase, a subset of challenges are applied from the much larger number of available

challenges and the challenge-Response pairs (CPRs) are stored in a secure database. This

database need to be securely managed by the trusted party, only who has knowledge of

which challenges are applied; later in the field, during the authentication process, the

trusted party apply a challenge and then check whether the response is close enough to

that in the database. After the use of the CPRs, it needs to be removed from the database

in order to avoid information release to attackers.

Secret keys are essential and important to many security applications such as IP protection and software licensing as well as conventional ID cards and smart cards. The response bitstrings of PUFs are proposed to integrate secret keys for the use in cryptography. When compared to the conventional methods of storing secret keys in NVM, PUFs have some additional security against probing and side-channel attacks: 1) PUFs do not require a key-programming step, as is true of conventional methods; 2) the

secret key is not generated and stored in volatile memory until it's needed. Usually, the response bitstrings of PUFs cannot be directly used as secret key due to the environmental noise such as temperature and supply voltage. Therefore, an intermediate processing step is required to extract a crypto key from the responses of PUFs. I will describe several of the popular methods used to decrease or remove the noise in the output bitstrings of PUFs in Section 2.7.

In recent years, Intellectual Property (IP) protection of FPGA hardware designs has gaining more attention and becoming a requirement for many IP vendors. In [54], the authors explained why PUFs can be a very valuable technology to protect a company's IP and present several cryptographic algorithms and protocols to use them in IP protection applications. In [29][49], new protocols are introduced for the IP protection problem on FPGAs based on public-key cryptography. In [32], the authors introduced the Butterfly PUF and stated that it promises to be a significantly secure way to protect IP with no additional costs in manufacturing.

In [55][53], the authors stated that in order to make Radio Frequency Identification (RFID) tags resistant against many attacks, they can be linked to PUFs inseparably. The authors demonstrated that PUFs can securely authenticate an RFID with minimal overheads. The authors also stated the PUF-based unclonable RFIDs can be used in anti-counterfeiting and security applications.

#### 2.5 Performance Metrics of PUFs

In order to apply PUFs in security applications such as encryption key storage, unique

device identifiers, they should possess several properties that determine the quality of bitstrings generated by these PUFs. Mainly, there are three characteristics to evaluate their performance. They are uniqueness, stability and randomness.

#### 2.5.1 Uniqueness

This characteristic is used to evaluate how much one chip is different from one another. It is the basis for PUFs to serve as identifiers. The inter-chip HD will be applied to evaluate the uniqueness and decide how many PUF output bits are different from other PUFs. The histogram of the inter-chip HD can be characterized as a Gaussian distribution and summarized using an average value of  $\mu_{inter}$ . The ideal inter-chip HD is 50%. Usually, the evaluation results of proposed PUFs cannot achieve the ideal uniqueness. Some publications have been focused on how to improve the uniqueness, e.g. in [56], the authors proposed a novel arbitration scheme called Response Generation according to Delay Time Measurement (RG-DTM), which divide the delay-time differences at regular interval and decide the response by the time domains of the interleaved response 0 and 1. In [57], the authors proposed an arbiter-based PUF circuit built on current starved inverters, whose drain currents are set by local current mirrors. This circuit amplifies process variations that result in great uniqueness when compared against a simple inverter chain. The experimental results in this literature show superior performance in uniqueness and reliability.

# 2.5.2 Stability (Reproducibility)

When repeatedly applying the same challenge to a PUF, ideally, the responses should

keep the same. Also, when PUFs are used in practical implementations they can be subjected to all kinds of environmental variations such as temperature, varying supply voltages and different voltage ramp-up curves. To my knowledge, there is no PUF that can avoid the 'bit flip' problem, and it must be dealt with before PUFs can be used for encryption applications. The intra-chip HD will be used to evaluate the stability of output bitstrings generated from PUFs.

In most literatures, the authors applied error correction or helper data schemes to gain good reliability [2][3]. However, the overhead associated with these blocks increase very quickly with increasing error correction capability and can become prohibitively large for many applications. Also, these schemes require additional helper or syndrome bits to be publicly stored, which may leak information. Recently, several new reliability improvement methods have been presented. In [58], the authors proposed an effective method of regenerating a finite and exact sequence of bits, which exposes response patterns and keeps secret the particular challenge that generate response patters. The experimental results show that this method can efficiently and reliably generate bitstrings under extreme environmental variations.

Later in 2012, Bhargava et al. demonstrated 3 reliability enhancing techniques for bi-stable PUF designs: directed accelerated aging (DAA), multiple evaluations (MA) and activation control (AC) [59]. From the measured results in this literature, these three techniques are able to reduce the percentage of unreliable bits by up to 40%, 83%, and 71% respectively.

#### 2.5.3 Randomness

Besides uniqueness and stability described above, it is also important to analyze the randomness of output bitstrings generated from PUFs. Here, the NIST tests suite are applied to test the randomness of them. In [60], the authors used the NIST tests suite to evaluate the randomness of output strings for PUFs, resulting in excellent raw material for key generation and for authentication. In [61], the authors stated that the amount of randomness in the PUF output could be a significant limitation. They introduced a method of passing the PUF response to a shift-register, and discover that the randomness of the PUF output could be greatly increased while maintaining reliability. Also, the authors showed experimental results that authentication with the shifted response data is superior to that with non-shifted data.

### 2.6 Evaluation Methods of PUFs

## 2.6.1 Hamming Distance

In order to evaluate the uniqueness and stability for a PUF implementation, HD has been introduced to measure these metrics. The test analyzes the relationship between CRPs' HD for each PUF. The inter-chip HD and intra-chip HD are introduced to evaluate these two metrics of PUF realizations. In order to study the statistical behavior of PUFs, all inter-chip and intra-chip HD measurements are often combined and summarized as histograms. In many cases, the HD histograms can be characterized as a Gaussian distribution and summarized using a  $\mu_{inter}$  and  $\mu_{intra}$  and a  $\sigma_{inter}$  and  $\sigma_{intra}$ .

For a particular challenge, the inter-chip HD between two different PUF instantiations is the distance between the two responses, resulting from applying this challenge simultaneously to both different PUFs. The inter-chip HD, when expressed as a fraction, the ideal value is 50%, i.e., half of the bits are different on average.

For a particular challenge, the intra-chip HD between two measurements on the same PUF instantiation is the distance between the two responses, resulting from applying this challenge twice to the same PUF. Intra-chip HD is strongly tied to random noise and systematic environment variations, such as those introduced by temperature and supply voltage. The intra-chip HD expresses the average noise in the response, and reflects reproducibility. When expressed as a fraction, the ideal value is 0%, i.e., the bit string can be reliably regenerated across different environmental conditions.

#### 2.6.2 NIST SUITE

The National Institution of Standards and Technology (NIST) test suite is regarded as an industrial standard to test cryptographic random number generator (RNGs) and recently has been widely used to evaluate the randomness of bitstrings generated by PUFs [62] [63]. The NIST Test Suite has totally 15 tests [1], including Frequency Test, Frequency Test within a Block, Runs Test, Longest Run of ones in a Block, Binary Matrix Rank Test, Discrete Fourier Transform Test, Non-overlapping Template Matching Test, Overlapping Template Matching Test, Maurer's "Universal Statistical" Test, Linear Complexity Test, Serial Test, Approximate Entropy Test, Cumulative Sums Test, Random Excursions Test. For many of them, it is assumed the bit sequence is large, on order of

10<sup>3</sup> to 10<sup>7</sup>. Therefore, parameters are chosen according to NIST recommendations, e.g., the length of bit sequence n>100 for Frequency Test, n>38,912 for Binary Matrix Rank Test, block length M=32 for Block Frequency Test, block length m=2 for approximate Entropy test and block length m=5 for Serial Test.

# 2.7 Techniques of Improving the Stability of PUFs

## 2.7.1 Threshold Mechanism

For some PUFs, the response bit is generated by comparing two analog values such as delay and voltage. When the compared two values are very similar, there exists the possibility that they maybe cause bit flipping due to the environmental variations. For example, in the first measurement, value1>value2; however, due to the small difference of these two compared values and the environmental variations, in the second measurement, it is possible that value1<value2. In this case, the bit generated by the PUFs is considered as an unstable bit. The bistrings produced from PUFs can not be used in the application of encryption if they contains unstable bits. As we know, people usually use the error correction and Helper Data to deal with the bit-flipping problems of PUFs. However, due to the additional overhead and possibility of leaking information of these schemes, a 'threshold' mechanism can be setup and used as an alternative to deal with the 'bit-flips' to improve the stability of output bitstrings. According to the idea of the 'threshold' mechanism, when applying each challenge to PUFs and comparing two analog values, the bits generated by those that are less than the threshold values will be discarded.

Therefore, the threshold mechanism should serve several primary goals: 1) it needs to avoid bit-flipping under different environmental noise; 2) it also needs to preserve as many strong bits as possible for each chip; 3) it should make the number of strong bits consistent across chip.

# 2.7.2 Majority Voting and TMR

Majority voting is a mechanism that the final result is decided according to the majority, that is, more than half the votes. For our PUF experiments, majority voting is the process of collecting multiple measurements through repeatedly sampling, and determining one output bit based on the individual value of the single measurement.

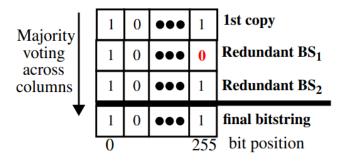

I also use a technique called Triple Modular Redundancy (TMR) [64] to improve the stability of the output bitstrings. The basic principle of the TMR is fault-tolerant form of N-modular redundancy, in which three system perform process and that result is processed by a majority voting system to produce a single output. If any one of the three systems fails, the other two systems can correct and mask the fault. In this dissertation, I will apply the basic idea of TMR into the stability improvement of PG-PUFs. The process is as follows: I investigate this technique by using fixed-length bitstrings, e.g., 256 bits. A TMR-based bitstring is created during enrollment by copying the first 256 strong bits into the first copy of the fixed-length bitstring. The second two copies are created by parsing the remaining strong bits and searching for matches to the first copy. The positions of the matching bits are indicated by writing a '1' in the public storage bitstring, while the positions of the skipped bits are indicated by writing a '0'. Later during regeneration, the

public storage bitstring is consulted to determine which challenges are to be used to reconstruct the 3 copies of the bitstring. Once created, the final bitstring is obtained by majority voting on each bit.

# Chapter 3

# Two Primitives of a PUF Based on Resistance Variations in Metals

This chapter will follow the structure of our paper [65], and mainly focus on the following several aspects. Firstly, two implementations of PUFs for both 65 nm and 90 nm technologies are described in Section 3.1. Secondly, the experimental techniques and procedure are given in Section 3.2. Finally, the experimental results are analyzed by statistical tests in Section 3.3.

# 3.1 Experimental Setup

## 3.1.1 Test Chip Architecture: 90 nm chips

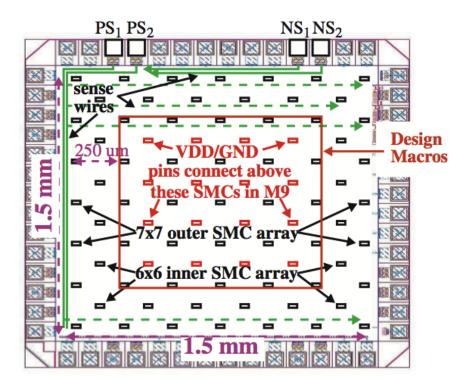

Fig. 3.1 gives a block diagram of the 90 nm test chip architecture. The chip padframe consists of 56 I/Os, and surrounds a chip area of approx. 1.5 mm x 1.5 mm. Four PADs labeled  $PS_1$ ,  $PS_2$ ,  $PS_2$ ,  $PS_3$ ,  $PS_4$ ,  $PS_5$  along the top of the figure refer to voltage sense connections, the 'P' version for sensing voltages near  $V_{DD}$  and the 'N' version for voltages near GND.

These four terminals wire onto the chip and connect to 85 copies of a Stimulus/Measure circuit (SMC). The SMCs are distributed across the entire chip (see small rectangles) as two arrays, a 7x7 outer array and a 6x6 inner array. Although not shown, a scan chain connects serially to each of the SMCs to allow each of them to be controlled.

Fig. 3.1: Block diagram of 90 nm chips, with voltage sense pins along top and two arrays of SMCs, a 7x7 outer array and a 6x6 inner array.

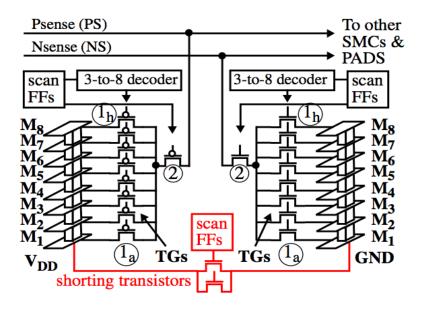

The schematic diagram of the SMC is shown in Fig. 3.2. A pair of large 'shorting transistor', capable of sinking approx. 10 mA of current through the power grid when enabled, are shown along the bottom of the figure. A set of 16 'pseudo' pass gates (hereafter referred to as transmissions gates or TGs) serve as voltage sense devices. Eight

of the TGs connect to 8 (of the 9) metal layers that define the  $V_{DD}$  stack-up of the power grid, as shown on the left side of Fig. 3.2, while the other 8 connect to the GND stack-up. Scan FFs and 3-to-8 decoders allow exactly one of the pass gates to be enabled in each of the stack-ups.

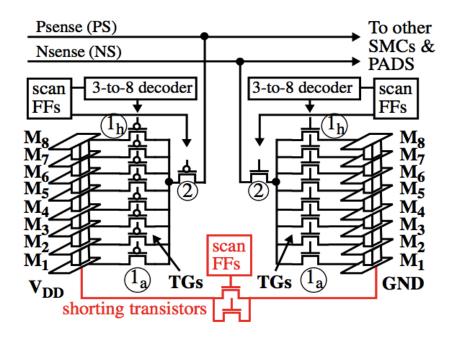

Fig. 3.2: SMC schematic in 90 nm chips.

An additional TG connects to the drains of the 8 stack-up TGs, labeled as '2' in Fig. 3.2, one for  $V_{DD}$  and one for GND. Separate scan FFs control the connection to the chipwide wires that route to the  $P/NS_X$  pins of Fig. 3.1. The configuration and control mechanism allows any  $V_{DD}$  and GND voltages to be measured using off-chip voltmeters. We refer to these experiments using PG90, for power grid 90 nm chips.

A 'challenge' in our experiments is applied by configuring the scan chain to 1) enable the shorting transistors within an SMC, and 2) enable two TGs in the same SMC,

in particular, the TG labeled 2 in Fig. 3.2 and one from the group 1<sub>a</sub> through 1<sub>h</sub>. Once enabled, the voltage drop/rise is measured on the NS and PS pads using voltmeters.

Although the details of the power grid are not shown, approx. 20% of the routing resources are used to define it, as would be typical of a high-performance commercial power grid. Moreover, the metal wires defining the power grid are at least 3 times wider than the minimum width, and via arrays (as supposed to single via) are used to connect one metal layer to the next. The low resistance associated with these wires and via arrays produces voltage drops in some experiments of 500  $\mu$ V or less. Although our off-chip instrumentation can measure voltage drops at high resolution (approx. 5  $\mu$ V), these levels will challenge the capabilities of on-chip 'instruments'. We discuss solutions to these issues and others as lessons learned in the following sections.

# 3.1.2 Test Chip Architecture: 65 nm chips

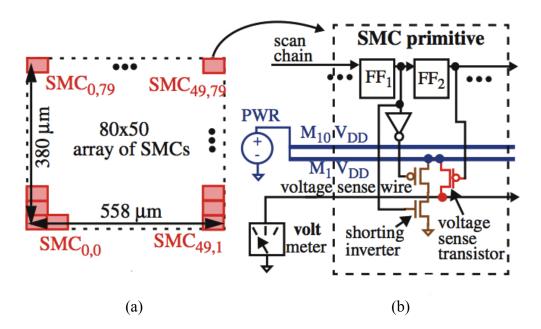

The 65 nm test chip architecture is shown as a block diagram in Fig. 3.3(a). A 50x80 array of SMCs are distributed, in close proximity, over a region that spans 560 m by 380 m. The power grid is wired in a mesh configuration over 10 metal layers using wide metal wires and via arrays. The details of the SMC are shown in Fig. 3.3(b). Each consists of a shorting inverter, a sense transistor and two scan FFs. The shorting inverter draws approx. 1 mA and introduces a 5-10 mV drop on the V<sub>DD</sub> grid. The single sense transistor allows only M1 voltages to be sensed. We refer to these experiments as PG65.

Fig. 3.3: a) Block diagram of 65 nm chip and (b) details of the SMC.

## 3.1.3 Challenge Scenarios

There are several 'challenge' scenarios possible in the PG90 and PG65 experiments. The basic approach we take in our experiments is to enable the shorting devices within each SMC, as well as the corresponding pass gates, one at a time, and then measure the voltage drop/rise produced at each location. A bit in the digital response of our PG-PUF is obtained by comparing two voltages obtained from a pairing of SMCs on a single bit.

In order to increase the size of the bitstring generated from the PG-PUFs, each of these voltages can be compared with other voltages in various combination to produce a bit string. We focus our analysis on bit string generated by using each voltage in (n-1) comparisons, where n is the total number of voltages measured from one chip. Bit strings

constructed in this manner are referred to as all combinations or AC.

As is customary, we randomize the order in which the comparisons are made. On chip, this can be accomplished using an LFSR and a seed. The process is modeled in our experiments using the functions srand (seed) and rand () from the C programming library. In order to show that the characteristics of the bit strings are insensitive to the value of the seed, we report statistical results using 10 different seeds.

In addition to randomizing the order of the pairings, we found that periodically inverting the comparison order within pairings produced better results. In particular, inverting every group of three comparisons worked well for both the PG90 and PG65 experiments. For example, for a randomized set of pairing numbered 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, etc., pairings numbered 3, 4, 5, 9, 10, 11, etc. are inverted. Note that the inversion operation occurs after the randomization, which makes this process trivial to implement on chip.

# 3.2 Experiment Techniques

#### 3.2.1 Bias Issues

The voltage measured from the chips in our experiments consists of three basic components: bias, regional variation and noise component. From the PUF perspective, only the regional variation component is important, and the other two components actually work to reduce randomness and stability, resp. Bias is a systematic voltage trend that is introduced by, e.g., a non-uniform distribution of power port connections to the power grid (the case for the PG90 chips) or non-uniform power grid mesh (the case for

the PG65 chips). Any type of systematic voltage trend will produce bits that are biased to 0 or 1 across chips, and needs to be reduced or eliminated in practice. We first discuss the biases that exist on our data sets and then methods of dealing with them.

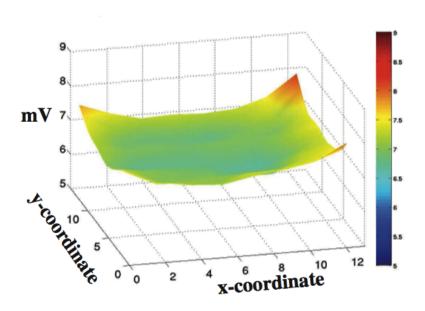

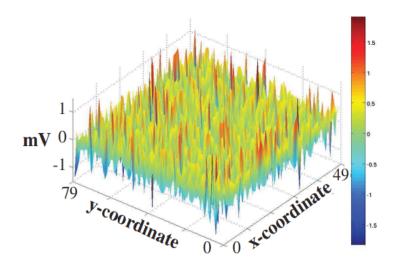

Fig. 3.4:  $V_{DD}$  profile using SMCs of a 90 nm chip.

Fig.3.4 show the voltage drop profile obtained from PG experiments on one of the 90 nm chips as each SMC is enabled. The voltage drop profile is derived from the M1 sense transistors on the  $V_{DD}$  grid. The (x,y)-plane in the figure represents the position in the array of the SMC in the 2-D array. From the bowl-like surface, it is clear that the voltage drops are larger along the edges of the power grid than in the center. This systematic voltage trend is caused by the non-uniform distribution of the power port connections, which from Fig. 3.1 are located over the 'Design Macros' in the center region of the chip, i.e., there are no power ports along the edges.

Fig. 3.5: Voltage drops from 4,000 SMCs on a PG65 chip.

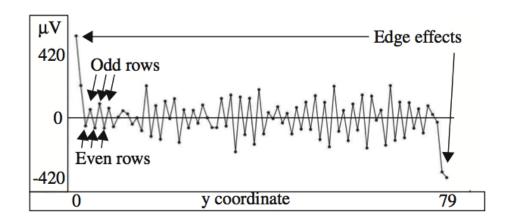

Although much less apparent, a small bias also exists in the voltage drop profile shown in Fig. 3.5, which is derived from one of the 65 nm chips. Here, the voltage differences computed for the SMCs are plotted for each of the 4,000 elements of the array shown in Fig. 3.3. The majority of the voltage variations (approx. +/- 1 mV from Fig. 3.5) is introduced by regional resistance variations in the metal defining the power grid. However, a small 'saw-tooth-shaped' bias exists between adjacent rows of approx. 200  $\mu$ V, which is introduced by a pattern in power grid metal mesh that is different for the even and odd rows of the array. This subtle pattern is revealed by computing an average voltage using the voltages measured across each row, for each of the 80 rows in the array. Averaging reduces the random variations allowing the bias effect to be more easily observed.

Fig. 3.6 plots the average values on the y-axis for each row identified along the x-axis. It is clear that the average voltages are smaller for even-numbered rows, than for odd-numbered rows. Moreover, the points labeled 'edge effects' reveal a second source of bias that is introduced by the power grid architecture. In this case, the increase in the voltage drops/rises is caused by the close proximity of these SMCs to the edge of the power grid.

Fig. 3.6: Average voltage drops across 80 rows of PG65.

# 3.2.2 Dealing with Bias

There are several ways of eliminating the bias from the voltage measurements in these chips. The multi-layered architecture of the SMCs used in the PG90 chips allow voltage drops/rises to be computed across each of the metal layers. In order to reduce bias effects and correlations that exist in the  $V_{DD}$  and GND stack-ups, we compute inter-layer voltage drops/rises, which can be computed by subtracting pair-wise, the voltages measured from the consecutive metal layers, i.e.,  $V_{M1}$ - $V_{M2}$ ,  $V_{M2}$ - $V_{M3}$ , etc. These Voltage differences, called power grid voltage difference (PGVD), also allow the PUF to leverage the

independent resistance variations that occur in each of the metal layers of the power grid, and given their differential nature, significantly reduces bias effects such as those discussed in reference to Fig. 3.4. The bit string is then produced by comparing these voltage differences, e.g., if  $V_{M1}$ - $V_{M2}$  in the  $V_{DD}$  stack-up at SMC<sub>1</sub> is greater than the voltage  $V_{M1}$ - $V_{M2}$  in the  $V_{DD}$  stack up at SMC<sub>2</sub>, then a '1' is generated, otherwise a '0'.

In the PG65 chips, each SMC has only one 'voltage sense' transistor connected to the  $V_{DD}$  grid, and therefore, computing inter-layer voltage drops is not possible. In this case, we avoid the bias by restricting voltage comparisons between SMCs positioned on every other row ( to deal with the "saw-tooth" effect) and eliminate those positioned along the edges of the array (to deal with "edge effects"). In particular, we eliminate the SMCs along the left and right columns, the bottom row and the top two row. This reduces the size of the array to 77x48, and restricts comparisons between SMCs on the remaining 39 odd numbered rows and the 38 even numbered rows. We refer to this scheme as bias avoidance.

We also propose a more general technique to eliminate bias which is applicable to any type of PUF measurement, including, for example, RO frequencies and delays. For PUFs based on voltage measurements, the method first divides the voltage drops by a value that upper bounds the noise level. The general idea here is to eliminate the smaller noise variations, effectively reducing the range of values observed in a set of repeated samples for a given challenge to 1 or 2 distinct values. Once the voltage drops are redigitized, the remainder from applying a modulus is used in the comparison operation to produce the bit. The modulus is chosen to preserve the regional (high frequency)

variation while simultaneously 'trimming off' the bias effects present in the high order bits. This approach is also applicable for PUFs that compare digital values, e.g., counter values in RO-based PUFs. In this case, the modulus operation eliminate systematic, across chip shift in frequency.

# 3.2.3 Bit Stability

In our experiments, we found that unstable bits, defined as bits that are susceptible to 'flipping' because their voltages are very similar, actually reduce several quality metrics associated with the overall bit string, including inter-chip HD and NIST statistical test results. Moreover, including unstable in the bit string requires the inclusion of error correction and Helper data schemes, that weaken security and increase overhead.