# University of New Mexico UNM Digital Repository

**Electrical and Computer Engineering ETDs**

**Engineering ETDs**

9-5-2013

## A Dynamically Reconfigurable Parallel Processing Framework with Application to High-Performance Video Processing

John Hoffman

Follow this and additional works at: https://digitalrepository.unm.edu/ece etds

#### Recommended Citation

$Hoffman, John. "A \ Dynamically \ Reconfigurable \ Parallel \ Processing \ Framework \ with \ Application \ to \ High-Performance \ Video \ Processing." \ (2013). \ https://digitalrepository.unm.edu/ece_etds/119$

This Dissertation is brought to you for free and open access by the Engineering ETDs at UNM Digital Repository. It has been accepted for inclusion in Electrical and Computer Engineering ETDs by an authorized administrator of UNM Digital Repository. For more information, please contact disc@unm.edu.

| John Colby Hoffman                                                                    |       |

|---------------------------------------------------------------------------------------|-------|

| Candidate                                                                             |       |

|                                                                                       |       |

| Electrical and Computer Engineering                                                   |       |

| Department                                                                            |       |

|                                                                                       |       |

| This dissertation is approved, and is acceptable in quality and form for publication: |       |

| Approved by the Dissertation Committee:                                               |       |

| MARIOS PATTICHIS ,Chairpe                                                             | erson |

|                                                                                       |       |

| CHRISTOS CHRISTODOULOU                                                                |       |

|                                                                                       |       |

| PAYMAN ZARKESH-HA                                                                     |       |

|                                                                                       |       |

| CARLOS LOPEZLEIVA                                                                     |       |

### A Dynamically Reconfigurable Parallel Processing Framework with Application to High-Performance Video Processing

by

### **John Colby Hoffman**

Electrical Engineering, Texas Tech University USA, 1998

M.Sc., Computer Engineering, University of New Mexico, USA, 2009

#### **DISSERTATION**

Submitted in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy Engineering

The University of New Mexico Albuquerque, New Mexico

July, 2013

©2013, Hoffman C. John

### **Dedication**

I dedicate this dissertation to my family, especially...

My brilliant and outrageously loving and supportive wife, Corrina; our energetic, inquisitive, and one of the joys of my life boy, Nathaniel; our exuberant, sweet, and the other joy of my life girl, Breeanna; to the guy who has always been there for me my brother, Chad; to Dad and Mom for instilling the importance of hard work and higher education; to my grandfather, late grandmother, for summers of joy while I grew up on the farm; to my wife's entire wonderful and supportive family.

### Acknowledgements

I heartily acknowledge Dr. Marios Pattichis, my advisor and dissertation chair, for continuing to encourage me through the years of classroom teachings and the long number of months writing and rewriting these chapters. His guidance and professional style will remain with me as I continue my career.

I also thank my committee members for their valuable recommendations pertaining to this study and assistance in my professional development. Gratitude is extended to my friends at Raytheon Company, Xilinx, inc. and Altera, inc. for pushing me to finish this research.

### A Dynamically Reconfigurable Parallel Processing Framework with Application to High-Performance Video Processing

by

### **John Colby Hoffman**

Electrical Engineering, Texas Tech University USA, 1998

M.Sc., Computer Engineering, University of New Mexico, USA, 2009

Ph.D., Engineering, University of New Mexico, USA, 2013

#### **Abstract**

Digital video processing demands have and will continue to grow at unprecedented rates. Growth comes from ever increasing volume of data, demand for higher resolution, higher frame rates, and the need for high capacity communications. Moreover, economic realities force continued reductions in size, weight and power requirements. The ever-changing needs and complexities associated with effective video processing systems leads to the consideration of dynamically reconfigurable systems.

The goal of this dissertation research was to develop and demonstrate the viability of integrated parallel processing system that effectively and efficiently apply preoptimized hardware cores for processing video streamed data. Digital video is decomposed into packets which are then distributed over a group of parallel video processing cores. Real time processing requires an effective task scheduler that distributes video packets efficiently to any of the reconfigurable distributed processing nodes across the framework, with the nodes running on FPGA reconfigurable logic in an inherently "Virtual" mode.

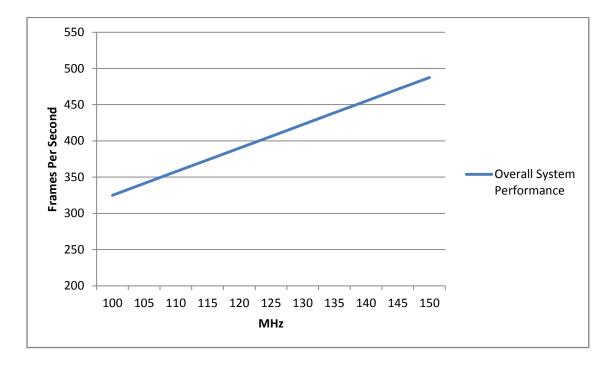

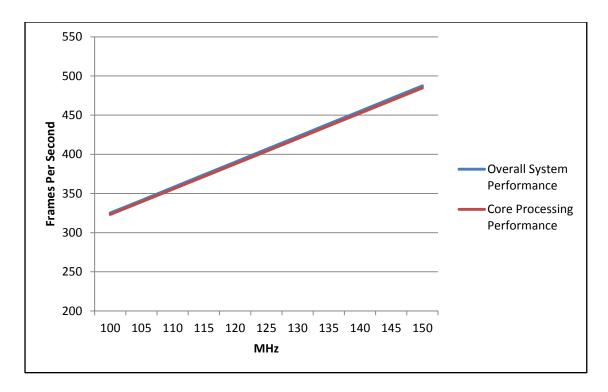

The developed framework, coupled with the use of hardware techniques for dynamic processing optimization achieves an optimal cost/power/performance realization for video processing applications. The system is evaluated by testing processor utilization relative to I/O bandwidth and algorithm latency using a separable 2-D FIR filtering system, and a dynamic pixel processor. For these applications, the system can achieve performance of hundreds of 640x480 video frames per second across an eight lane Gen I PCIe bus. Overall, optimal performance is achieved in the sense that video data is processed at the maximum possible rate that can be streamed through the processing cores. This performance, coupled with inherent ability to dynamically add new algorithms to the described dynamically reconfigurable distributed processing framework, creates new opportunities for realizable and economic hardware virtualization.

## **Table of Contents**

| Abstrac | t                                                        | vi  |

|---------|----------------------------------------------------------|-----|

| Chapter | 1                                                        | . 1 |

| 1.0     | Overview                                                 | 1   |

| 1.1.    | Motivation for Dissertation Research                     | 3   |

| 1.2.    | Related Research                                         | . 7 |

| 1.3.    | Thesis statement                                         | 12  |

| 1.4.    | Innovations and Contributions                            | 13  |

| 1.5.    | Organization                                             | 14  |

| Chapter | 2                                                        | 15  |

| 2.1.    | DPR Resource Interconnection                             | 17  |

| 2.2.    | Data Switching and Packet Routing                        | 26  |

| 2.3.    | Round Robin / Weighted Round Robin / Deficit Round Robin | 33  |

| 2.3.1.  | Queue Service Prioritization Policies                    | 34  |

| 2.4.    | State of the Art for Reconfigurable Computing            | 35  |

| 2.4.1.  | Embedded Reconfigurable Computing                        | 37  |

| 2.4.2.  | FPGA Reconfiguration Methodology                         | 39  |

| 2.4.3.  | Frameworks for FPGA Reconfigurable Computing             | 40  |

| 2.4.4.  | Multi-Soft-Core Reconfigurable Computing                 | 42  |

| 2.4.5.  | Video Processing and Reconfigurable Computing            | 43  |

| 2.4.6.  | Description of FPGA Cores                                | 45  |

| 2.4.6.  | 1. FIR Filter Core                                       | 46  |

| 2.4.6.  | 2. Pixel Processor Core                                  | 47  |

| Chapter | 3                                                        | 50  |

| 3.0     | Overview and Motivation                                  | 50  |

| 3.1.    | Hardware Architecture                                    | 51  |

| 3.2.    | Software Architecture                                    | 53  |

|   | 3.2.1. Linux Partial Reconfiguration Platform Driver | . 53 |

|---|------------------------------------------------------|------|

|   | 3.2.2. Video Packet Processing                       | . 55 |

|   | 3.3. FPGA Packet Processing Regions                  | . 56 |

|   | 3.3.1. Static Packet Processor Region                | . 57 |

|   | 3.3.1.1. BAR Address 1 – Packet Processors           | . 59 |

|   | 3.3.1.2. Reconfigurable Round-Robin-Controller       | . 59 |

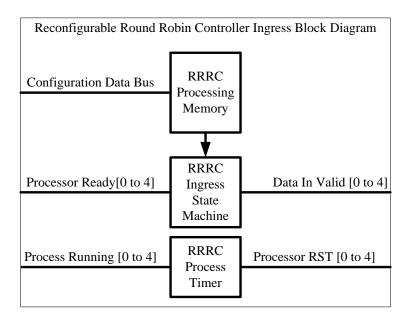

|   | 3.3.1.2.1. RRRC State Machines                       | . 61 |

|   | 3.3.1.2.2. Non Weighed Round Robin Mode              | . 61 |

|   | 3.3.1.2.3. Weighed Round Robin Mode                  | . 62 |

|   | 3.3.1.2.4. RRRC Process Timer                        | . 63 |

|   | 3.3.1.2.5. Framework Bus Timer                       | . 63 |

|   | 3.3.1.2.6. Moving Data To and From Cores             | . 64 |

|   | 3.3.1.3. BAR Address 2 – DPR                         | . 64 |

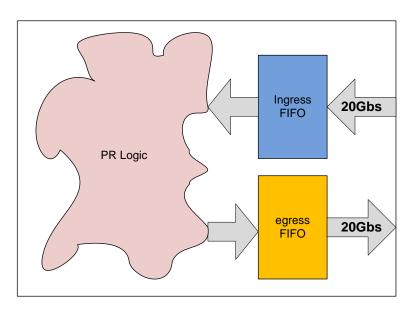

|   | 3.3.1.3.1. DPR Core PACKET FIFO                      | . 65 |

|   | 3.3.1.3.2. DPR Core CONFIG                           | . 66 |

|   | 3.3.1.3.3. DPR Core ICAP OUTPUTS                     | . 67 |

|   | 3.3.1.3.4. DPR Core RESET                            | . 67 |

|   | 3.3.1.3.5. DPR Core ERROR                            | . 68 |

|   | 3.3.1.3.6. DPR Core Procedure after Errors           | . 68 |

|   | 3.3.1.3.7. DPR Core Interface Signals                | . 69 |

|   | 3.4. DPR Regions                                     | . 70 |

|   | 3.5. Base System Test Application                    | . 73 |

|   | 3.5.1. Test Application                              | . 73 |

|   | 3.5.2. Test Procedure for PCIe Performance           | . 74 |

|   | 3.5.2.1. PCIe Performance                            | . 75 |

| C | Chapter 4                                            | . 77 |

|   | 4.0 RVPPF DPR Loopback                               | . 77 |

|   | 4.1.1. RVPPF DPR Loopback FPGA Core                  |      |

|   | 4.1.2. RVPPF Loopback Speed Calculations             |      |

|   | 4.1.3. RVPPF DPR Loopback Host Application           |      |

|   | 4.1.4. RVPPF DPR Loopback Implementation             |      |

|   |                                                      |      |

| 4.1.5.  | RVPPF DPR Loopback Results                            | 83  |

|---------|-------------------------------------------------------|-----|

| 4.2.    | RVPPF DPR Video 1-D and Separable 2-D FIR Filter      | 84  |

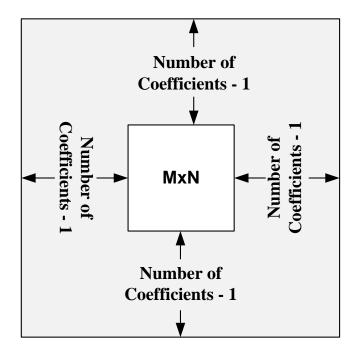

| 4.2.1.  | Removing Filter Edge Effects                          | 85  |

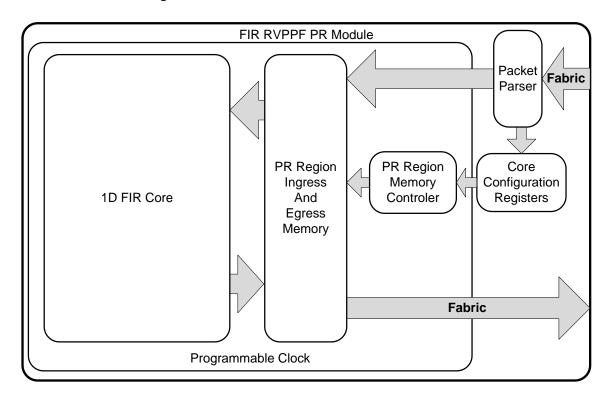

| 4.3.    | RVPPF DPR FIR Filter FPGA Core                        | 87  |

| 4.3.1.  | 1-D FIR Filter Mode                                   | 88  |

| 4.3.2.  | 2-D Separable FIR Filter Mode                         | 88  |

| 4.3.3.  | RVPPF DPR FIR Filter Processing Core                  | 89  |

| 4.3.3.  | 1. 1-D FIR Filter Speed Calculations                  | 90  |

| 4.3.3.  | 2. 2-D Separable FIR Speed Calculations               | 91  |

| 4.3.4.  | RVPPF DPR FIR Host Application                        | 93  |

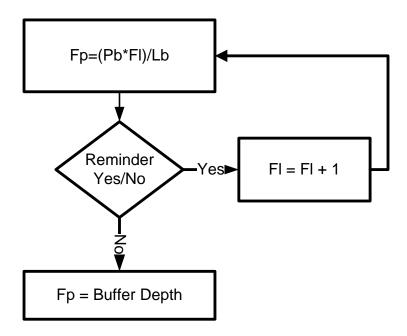

| 4.3.4.  | Host Video Buffer and RRRC Configuration              | 95  |

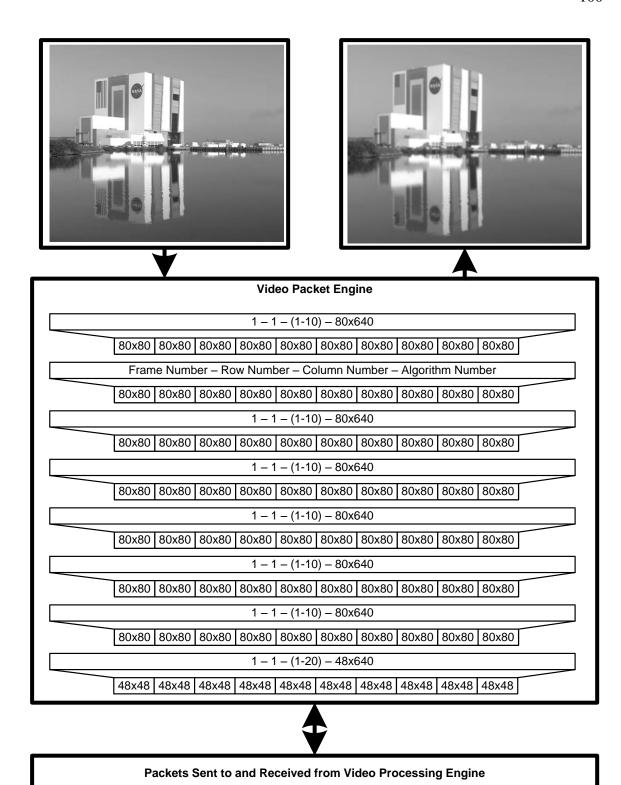

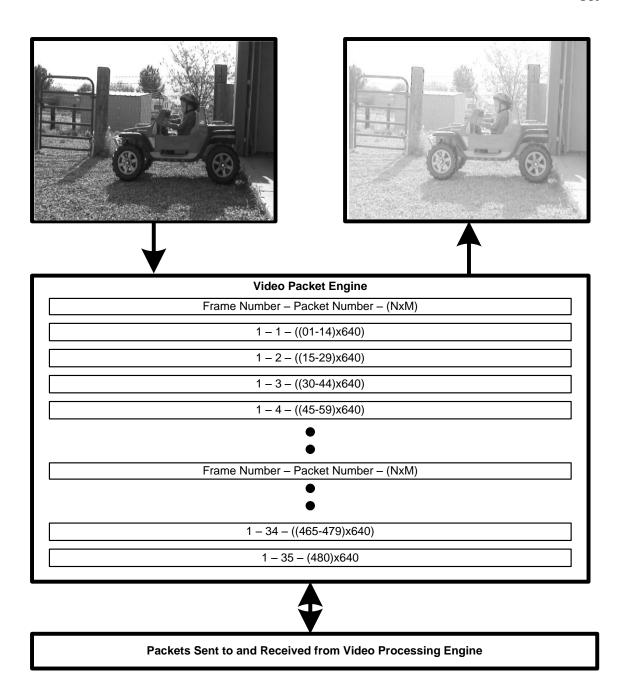

| 4.3.5.  | Construction of the Video Packets                     | 99  |

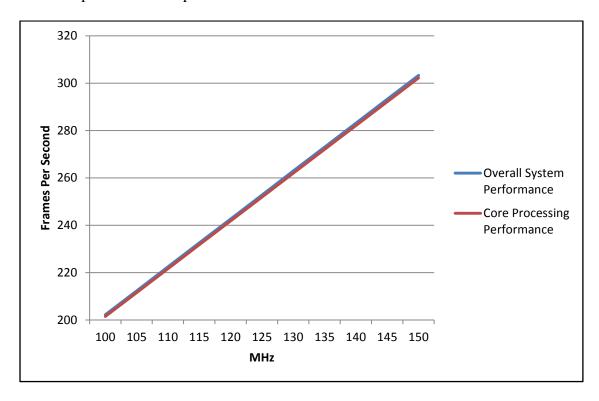

| 4.3.6.  | RVPPF 1-D DPR FIR Results                             | 102 |

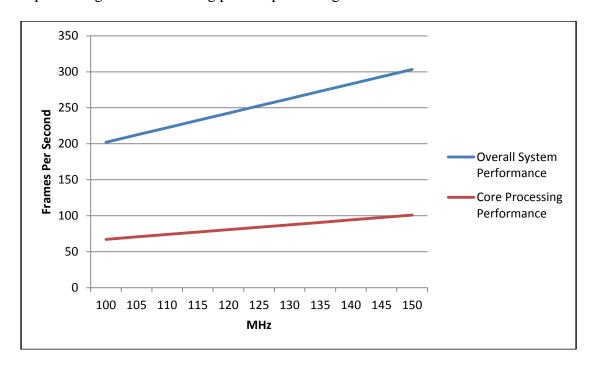

| 4.3.7.  | RVPPF 2-D Separable DPR FIR Results                   | 102 |

| 4.4.    | RVPPF Pixel Processor                                 | 103 |

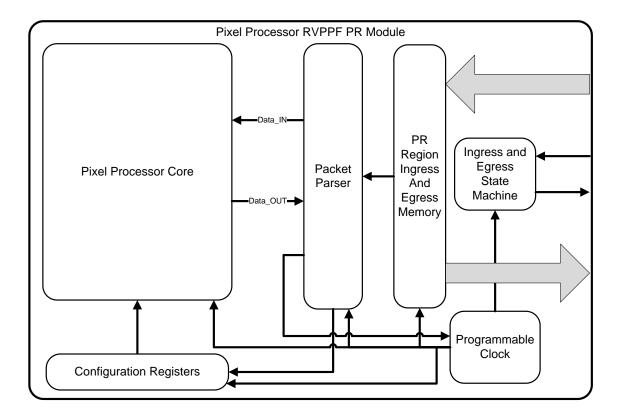

| 4.4.1.  | RVPPF Pixel Processor FPGA Core                       | 104 |

| 4.4.2.  | RVPPF Pixel Processor Host Application                | 106 |

| 4.4.3.  | RVPPF DPR FIR Filter Block RAM                        | 107 |

| 4.4.4.  | Construction of the Video Packets for Pixel Processor | 108 |

| 4.4.5.  | RVPPF Pixel Processor Results                         | 110 |

| 4.5.    | Summary                                               | 111 |

| Chapter | 5                                                     | 112 |

| 5.0     | Review of Motivations and Design                      | 113 |

| 5.1.    | Research Contributions                                | 115 |

| 5.2.    | Future Research Directions                            | 116 |

| Acronvi | ns and Abbreviations                                  | 117 |

# **List of Figures**

| Figure 1. Researched DPR Region Topologies A to C    | 21 |

|------------------------------------------------------|----|

| Figure 2. Splash 2 Interconnection Architecture      | 22 |

| Figure 3. Researched DPR Region Topologies D to F    | 24 |

| Figure 4. Switch Buffer Architectures [41]           | 28 |

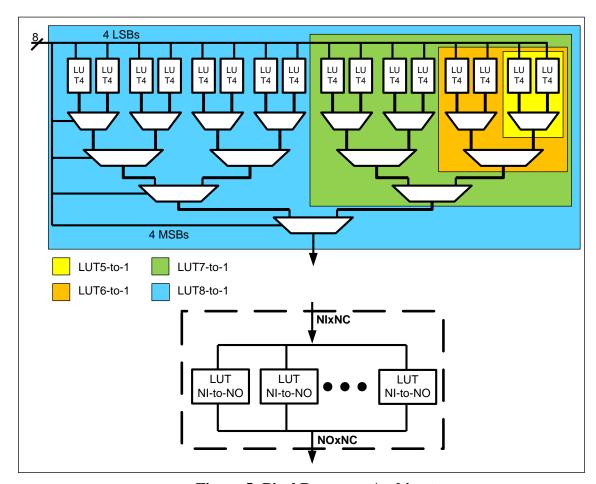

| Figure 5: Pixel Processor Architecture               | 48 |

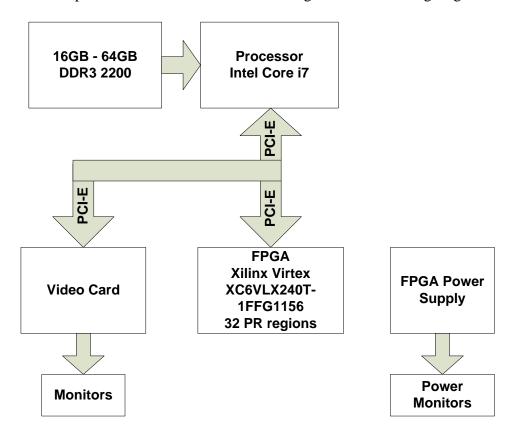

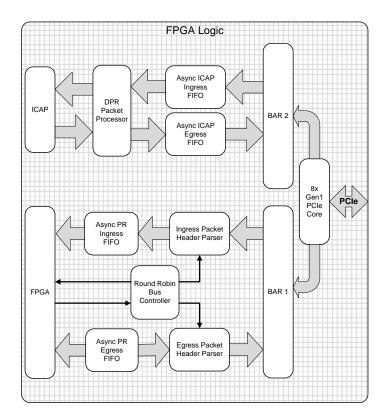

| Figure 6. DPR Video Packet Processing Architecture   | 51 |

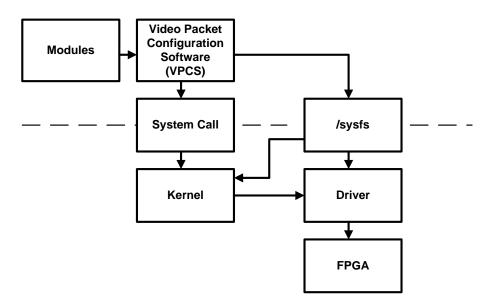

| Figure 7. DPR Service Composition                    | 54 |

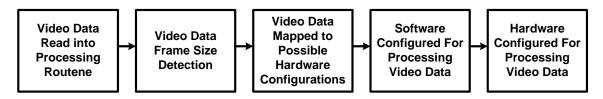

| Figure 8. Video Processing Chain                     | 55 |

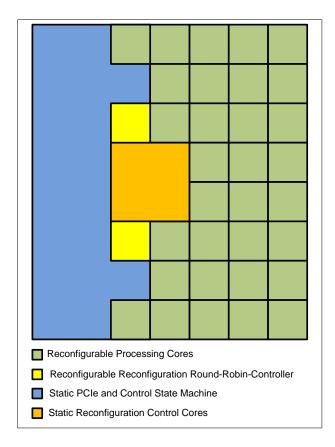

| Figure 9. FPGA Device Layout                         | 56 |

| Figure 10. Notional Static Framework                 | 57 |

| Figure 11. Static Core Logic                         | 58 |

| Figure 12. RRRC Ingress Block Diagram                | 60 |

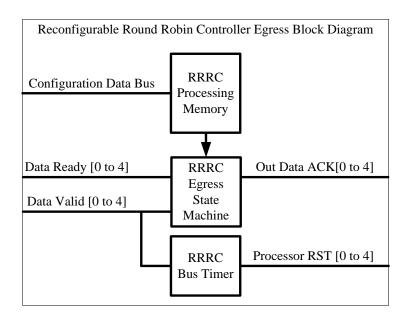

| Figure 13. RRRC Egress Block Diagram                 | 60 |

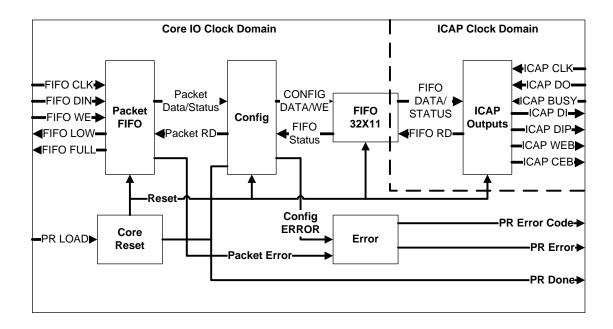

| Figure 14. DPR Packet FIFO                           | 65 |

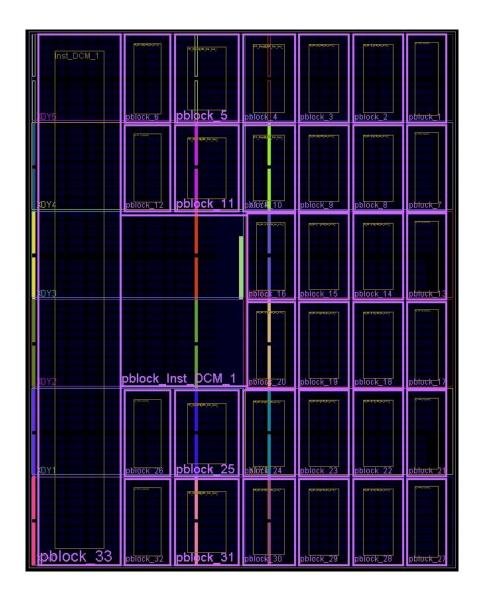

| Figure 15. Dynamic Partial Reconfiguration Regions   | 71 |

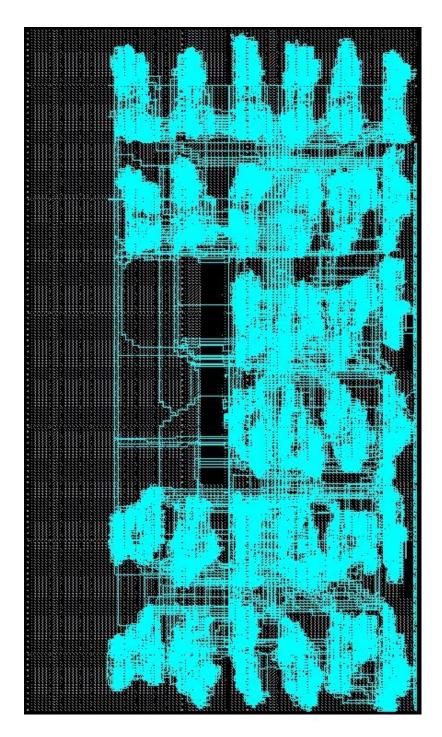

| Figure 16. Dynamic Partial Reconfiguration Placement | 72 |

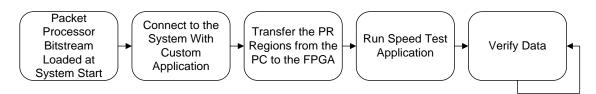

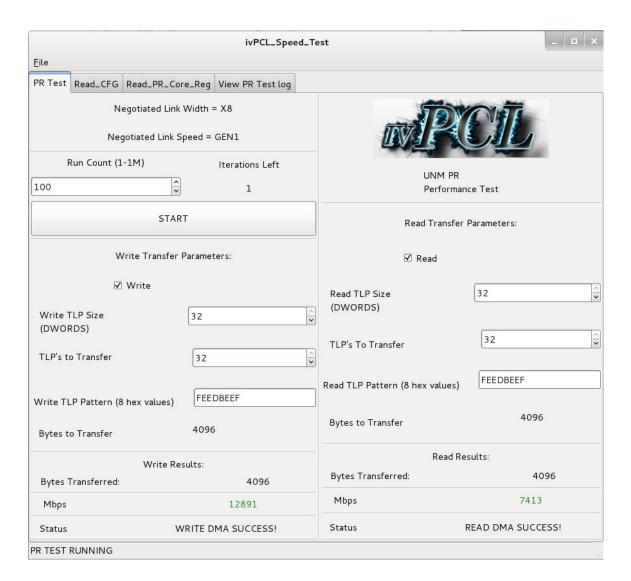

| Figure 17. Test Application Flow                     | 73 |

| Figure 18. Speed Test GUI                            | 74 |

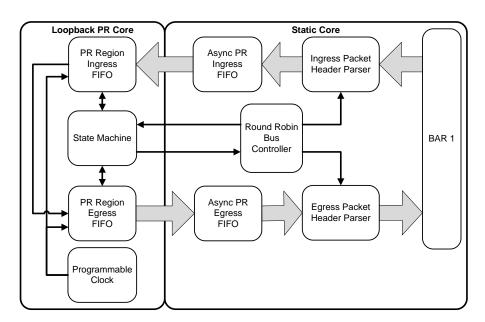

| Figure 19. L-DPR-STM Core Block Diagram              | 79 |

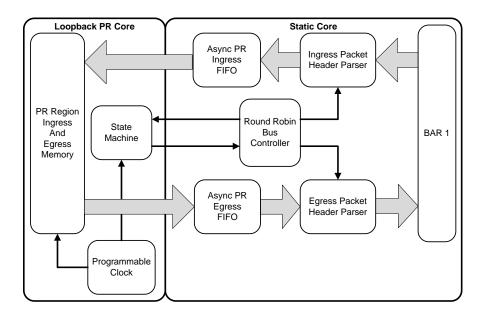

| Figure 20. L-DPR-CTM Core Block Diagram              | 80 |

| Figure 21. Frames per Second                         | 84 |

| Figure 22 Filter Memory Structure                    | 86 |

| Figure 23. FIR implementation for the RVPPF    |

|------------------------------------------------|

| Figure 24. Buffer Depth Process                |

| Figure 25. Packet Identification Process       |

| Figure 26. RVPPF 1-D DPR FIR Results           |

| Figure 27. RVPPF 2-D Separable DPR FIR Results |

| Figure 28. Pixel Processor PR Module           |

| Figure 29. Packet Identification Process       |

| Figure 30. RVPPF Pixel Processor Results       |

|                                                |

|                                                |

| List of Tables                                 |

| List of Tables  Table 1: FIR Filter I/Os       |

|                                                |

| Table 1: FIR Filter I/Os                       |

# Chapter 1 Introduction

This dissertation focuses on the application of dynamically reconfigurable hardware to develop effective and novel means to implement adaptable and high performance video processing methods with FPGA technology. The primary motivation for this research comes from the need for flexible, reprogrammable or reconfigurable solutions that can be deployed before design requirements have been finalized, and can then be adapted to changing requirements after deployment.

Prior research enabling exploitation of FPGA reconfiguration technology has begun to address some of the many complexities associated with the development of hardware and configurable hardware whose functionality can be changed during operation. The potential of self-adaptable hardware to enable revolutionary new applications has led to a large and growing body of work in reconfigurable computation. The recent explosive growth of video datasets motivates the exploration of how dynamically reconfigurable methods can be used for video processing. The use of dynamically reconfigurable methods for video processing has received very little attention. This dissertation research will build on recent ivPCL research by extending the dynamic pixel processor and dynamically reconfigurable FIR system in a high-performance video processing system.

### 1.0 Overview

Dynamic Partial Reconfiguration (DPR) of Field Programmable Gate Array (FPGA) devices represents a major disruptive technology that can be used to meet vital needs for increased system efficiency and resiliency. This value proposition can be

demonstrated for applications such as satellite-based image processing [1] [2]. For these systems, upgrades are typically quite complex, risky, and expensive. Furthermore, available resources are constrained by Size, Weight, and Power (SWAP) requirements. FPGA devices incorporated into these systems represent high-value, finitely-limited resources. Once deployed, the available FPGA logic is strictly finite.

Consequently, an ability to reconfigure the logic of such devices after deployment enables revision of the design logic, as necessary, to correct design deficiencies or to alter or enhance functionality. The logic of an FPGA device is specified (programmed) in the manner of uploading one or more files to the device that specifies the configuration of the device logic. These files are commonly referred to as *bitstream* files. When an electrically reprogrammable FPGA device is initially programmed following power-on or reset, a default bitstream is loaded to that device, often from an associated memory through the device programming [3].

It is obvious that, at a minimum, non-run-time reconfiguration enables corrections and upgrades. Beyond a specified reconfiguration, DPR can be used to correct, enhance, or replace firmware functional blocks in the FPGA reconfigurable logic while that device is operating in the system without disruption of other ongoing functions. Programming these devices with partial bitstreams can now be accomplished over high speed multigigabit per second Serializer/Deserializer (SerDes) interfaces and devices which will be configured and programmed specifically to support ongoing device level needs. This capability provides modification flexibility analogous to software while realizing functional density and performance efficiency of hardware. Cost-effective, easily-modified systems are essential to today's complex systems and development success,

which can be accomplished with this approach. However, achieving this outcome requires the right tools and correct techniques; but moreover it most requires a structured (well-posed) yet flexible architectural approach.

For this to be a reality will require the development of the appropriate techniques and necessary tools which leads to a packet based parallel processing framework for complex infrastructures such as an FPGA Application Store for FPGA Intellectual Property (IP) development and horizontal deployment.

This research builds off of recent work in the area of Dynamic Energy/Power-Performance-Accuracy (EPA/PPA) management which provided a management approach for digital signal, image, and video processing architectures. In this work EPA/PPA was demonstrated with the use of Dynamic Partial Reconfiguration (DPR) and Dynamic Frequency Control (DFC) on FPGAs [4] [5] [6] [7].

### 1.1. Motivation for Dissertation Research

The majority of FPGA hardware designs and implementations tend to be expensive, tedious, and static. The term static is used here to refer to the fact that the designs are completed according to pre-defined (fixed) requirements. Indeed, even if the initial architects use a well-structured architectural design, once detailed design, timing optimization, and final verification, there is considerable risk associated with asking a later design team to attempt modification. Thus, design modification rarely happens, especially for large and complex designs.

Yet device geometries continue to shrink because the density difference between FPGA technology and standard cell Application Specific Integrated Circuit (ASIC) technology is roughly an order of magnitude [8]. In part, this is due to the simple fact

that the logical design of FPGA technology is based on ASIC technology perhaps supplemented with more customized design of the embedded memory structures themselves. Inherently, the logic density of programmable logic will remain at least an order of magnitude lower than that achievable in customized directly instantiated logic.

The implication of this fact is that the achievable density of FPGA technology directly tracks that of the underlying ASIC technology and consequently continues to grow at that same rate. Emerging FPGA devices can achieve or perhaps exceed the capabilities achievable a decade ago in a dense standard cell technology and consequently remain complex to design. Moreover, physical constraints that limit the ability of a signal to propagate across a die become increasingly adverse at the individual logic cell level necessitating much more knowledge of physical placement of function than had been necessary in older FPGA technologies. The end result is that the difficulties in designing FPGAs are driving tool requirements to provide analogous physical optimization required for ASIC design. Yet the end result needs to be far cheaper and faster [9].

Fortunately, the underlying optimization technologies developed for ASIC design needed now to address the issues with FPGA design were available a decade ago and have matured since. Unfortunately widespread adaptation has not occurred due to the additional costs associated with the need for those same more sophisticated tool flows and inertial resistance to make significant investments and change without clear widespread adoption.

The engineering process for firmware can be accelerated with increased use of functional component reuse. Unfortunately, the present FPGA industry process does not

directly lead to reusable components for a number of reasons including design methodology. However, once it becomes inherently advantageous to create physically modular IP blocks for partially reconfigurable designs, reuse through standardization can become a natural and pervasive result. The combination of physical and logical standardization in turn can lead to the natural evolutionary result of macro-scale modular pre-tested/pre-validated components with specific physical layout within a standard, regular shaped region all built on established tools, technology, expertise and conformal with the considered base of products and related IP. Having accomplished that, it is apparent that even enormous applications reasonably decomposable into structured components of smaller, more manageable sizes are more easily created in a manner that converges to an acceptably sub-optimum solution much more effectively and quickly than with non-partitioned single monolithic applications. This divide-and-conquer method is the basis of modern systems engineering practice. This practice produces designs whose individual components and aggregated designs can be far more reasonably revised and refined than large non-structured monolithic implementations.

Furthermore, if those same applications were to be created conformal to a regularized macro-scale tiling with standardized electrical and messaging interconnections, then the FPGA fabrics provisioning of local and global routing resources can be partitioned to accommodate tile-to-tile and longer pass-through routing. Under a suitable framework for defining interconnection, tiling, and resource provisioning, the placement of individual functional tiles becomes a problem in tile assembly.

A primary consideration for the specification of this framework is one of tradeoffs between manageable complexity of individual tiles, nominal average tile utilizations, and total number of unique tiles. Tile size fidelity encapsulates a number of FPGA (Combinational Logic Blocks) CLBs, but partitions the CLB fabric with sufficient granularity to provide sufficient ability to accommodate the majority of smaller reuseable macro-functional elements.

However, the necessity to provide this same design paradigm for systemic creation of standardized physical and electrical macro elements that in turn systemically leads to the necessity to create interoperable and swappable components then directly enables the feasibility of near-real-time DPR device reconfiguration. Enabling rapid and dynamic firmware reconfiguration also suggests that defects can be more easily corrected after the product is fielded and consequently it becomes possible to put the product in the field to begin evaluation sooner. This means that other potentially major issues normally are only discovered by integration, in actual use, or when exposed to real-world circumstances can be discovered and corrected earlier and more effectively leading to cost reduction, faster deployment, and better results.

FPGA DPR firmware will provide immediate or real-time updates to fielded hardware. Rapid responses can be deployed horizontally in near-real time to networks of systems with these capabilities. It provides rapid responses and the capability for immediate solutions to be horizontally deployed across numerous systems and platforms.

Situation tailored capability becomes an important goal. System hardware capabilities can be modified at a given moment to adapt the current environment or

situation. Moreover, dynamic functional adaptations as well as application mobility across networked systems becomes a realizable possibility [10].

### 1.2. Related Research

There has been considerable research over the past decade on the subject of reconfigurable computation; however there remains substantial work to be accomplished to create technologies, techniques, and tools that enable exploitation of reconfigurable hardware. A survey of recently published literature testifies to the lack of sophisticated capabilities and tools to use DPR technology within a broad-based mainstream design methodology. Examples that clearly demonstrate limitations within the current art are discussed in following paragraphs and are related to results established during the course of this research.

SRAM-based FPGA technologies in particular have attracted substantial attention due to investments made by companies including Xilinx in reconfiguration technology. Reconfigurable technologies occupy the performance-density /cost space between ASIC and custom silicon and microprocessor-based software solutions and consequently have attracted considerable attention. While the ability to reprogram (reconfigure) SRAM-based FPGAs has existed since these products were first introduced, in practice, it happens very infrequently. With each generation, device complexities continue to grow and consequently the complexity of the potential reconfiguration trade spaces grow even faster. Compounding the issue, the latest generation devices now provide the ability to reprogram portions of a design while the device continues to operate.

Examination of the literature suggests that there are many open issues regarding how to efficiently and effectively use these capabilities. Recent research by Fons [11]

suggests that the existing run-time reconfigurable computing ecosystem is at a sufficient "level of maturity" for the "professional design and development of embedded electronic systems." However, at the same time he qualifies this remark noting that further advances are required, especially regarding automation tools. While the basic low-level technology capabilities exist, sophisticated capabilities to effectively and efficiently exploit hardware reconfiguration do not.

The author states that "when working with reconfigurable hardware technology the development effort required to get any application to produce even modest performance is high compared with a purely software implementation, and any seemingly small detail can easily result in a significant performance degradation [11]."

Fons discusses an open system architecture driven by a reconfiguration engine that in turn supplies inputs to a logic synthesis tool for creating applications on SRAM-based FPGAs. The described framework identifies and labels recognized computational tasks that otherwise would commonly be synthesized into static logic. The author investigates a number of specific application implementations while incorporating on-the-fly reconfiguration techniques into those designs. In one such example, implementation of a CORDIC function is examined. Trigonometric functions are synthesized and a microcontroller is used to reconfigure ran FPGA with the new function. When the associated application software code invokes the function, the associated function is loaded into the FPGA. FPGA execution is performed on demanded when the application invokes one of the supported functions. This then initiates an automated mechanism to affect data transfer with the FPGA as well as with the FPGA for partial reconfiguration download.

In contrast to the highly automated and highly interactive processing techniques investigated in the present research, Fons' approach focused on demand-driven function synthesis that then is used to reconfigure a device to meet a new need. Within this paradigm, reconfiguration performance is a function of the power of available FPGA design automation and synthesis tool performance. The author in fact notes that the time "required by the CAD tools to place and route a design into a physical device can be extremely long" and thus this approach would benefit from on-going work high-level language synthesis for greater abstraction and that "the complexity of embedded systems increases at a rate that is not met by the development of advanced CAD tools for managing such a large design space" and consequently "there exists risk that this progress remains only in research prototypes and some products."

Aggaarwal et al [12]proposed the System Coordination Framework (SCF). This work focuses on heterogeneous computation including FPGAs, CPUs, and other processing elements. Their research primarily addresses inter-processor task communications through message passing between different tools (and languages). This occurs while executing on multiple, different processing devices ranging from embedded to High-Performance Computing (HPC) systems.

Unlike their work addressing more distributed applications, the present research focuses on task coordination related to the direct control of information flows through a highly parallelized FPGA fabric, performing processing tasks on that hardware, and then scheduling and controlling the allocation, reconfiguration, and continual modification of the logic incorporated within that same FPGA hardware fabric. The very high speed and continual DPR techniques described herein show how individual DPR regions within an

array of such regions can be independently modified in an adaptive manner quickly and effectively.

The NSF Center for High-Performance Reconfigurable Computing also has done extensive research in the area of FPGA Design Frameworks for Dynamic Partial Reconfiguration [13] [14]. That research focused on the actual physical layout of FPGA devices and not the communication network fabric or the optimizations needed to achieve an efficient dynamic partial reconfiguration framework. These topics demand better solutions than are currently available and the current research directly addressed both.

Tan and DeMara [15] discuss why a sophisticated partial reconfiguration framework is essential to integrate and optimize existing FPGA technologies in order to exploit the potential of PR and DPR techniques. Towards this end, they suggest standardized APIs, abstracted data structures, and structured access to heterogeneous logic and communication resources. Important framework attributes were suggested to include (1) autonomous FPGA partial reconfiguration without manual intervention, (2) task-level granularity, (3) reconfiguration bitstreams generated at run-time as well as during design. This prior research work serves to reinforce motivations for the current dissertation.

Similarly, Marconi [16] recently investigated issues associated with PR hardware task scheduling and placement assuming pre-designed hardware tasks. Hardware tasks were defined by three parameters: area (width and height), reconfiguration time, and its execution time. This work explores aspects of area utilization, hardware allocation overhead, execution time, and resource scheduling. The author also discussed reconfiguration overhead due to aspects of existing configuration infrastructures. This

work was limited and expanded on in this dissertation with respect to resource scheduling of the data flow through the reconfigurable system before during and after the reconfiguration.

Other research directions related to better DPR methods and process flows include bitstream size compression algorithms [17]. Sudarsanam [18] proposed modification of a niche DPR technique for relocation of blocks tied to a specific family of devices, modifying an approach developed by Carver et al. [19] adding a decompression algorithm for obtaining the next word in the bitstream. One reported limitation of that approach is that current floor planning tools do not allow static routing in the partial regions. This limited their number of achievable partial regions. As will be seen in the results from this work, the approach we have taken towards DPR does not suffer from similar limitations. Indeed, the studied application involved thirty two processing cores that could be individually and dynamically programmed into the device and dynamically reconfigured.

Krill et al [20] proposed a DPR design flow and demonstrated implementation of an Intellectual Property (IP) core for Color Space Conversion (CSC) for image processing. They proposed a DPR environment which they used to generate a CSC IP core optimized in terms of the area/speed ratio, providing both static and multiple reconfigurable areas. One significant difference between the current work and previous published results concerns the number and complexity of DPR regions. This work describes a framework for developing place-able DPR pre-placed macros and assigning placement of those macros, and additionally defines DPR interconnection and a novel reconfiguration task scheduling mechanism. Unlike this work the scheduling mechanism does not address the

actual scheduling of the data being processed during or the changes to the flow of the data which are a result of the reconfiguration process.

In [21], Clemente et al. developed a reconfiguration scheduler for implementing task-graphs at run-time, steering execution in the reconfigurable resources while performing pre-fetch and replacement, avoiding most of the reconfiguration delays. In their proposed scheduling environment, task-graphs are analyzed at design-time to extract useful information. This information requires simple computations at run-time to obtain optimized schedules. The authors developed a hardware implementation of the optimization techniques. The authors discuss efficiency for their evaluated scheduling protocol which manages a specified task-graph for required performance under enforced constraints. They schedule run-time reconfigurations only including one reconfiguration circuit and where reconfiguration latencies are assumed significant. As previously mentioned, this work describes a novel mechanism that provides for adaptive scheduling of reconfiguration tasks.

Consequently, while there remains substantial work to be done in regards to development of a DPR ecosystem that includes sophisticated tools to support machine state based process optimization as well as visualization and understanding tools for future highly concurrent, dynamically changing processing systems. Results from this work can be leveraged to grow existing techniques and tools to begin to create needed solutions.

### 1.3. Thesis statement

The main objective of this Ph.D. dissertation is to develop an effective framework for dynamically reconfigurable parallel processing. The target application for this

research is a video processing system. The thesis of this research is that a highperformance video processing system can be developed for real-time video streaming applications.

The effectiveness of this system is demonstrated in the high-performance achieved for video processing applications. In summary, the system characteristics include:

- Linux based dynamically reconfigurable system (DRS) for packet-based video processing

- Vendor development flow coupled with a Matlab and Simulink environment which facilitates DPR video processing applications

- Demonstration of the architecture in parallel processing of digital video data streams across a single channel

For reproducibility of the results, the design was implemented on a standard Xilinx FPGA PCIe development card that is widely available. The actual system described within this dissertation utilized a Xilinx Virtex 6 based ML605 development board.

### 1.4. Innovations and Contributions

The primary contributions of the dissertation include:

- Partial Reconfiguration System for packet-based processing: This includes the

development and implementation of a Linux based Dynamically Reconfigurable

System (DRS) for packet-based video processing which facilitate DPR video

processing applications and test fixtures.

- Parallel processing of a digital video data stream across a channel passed into the FPGA fabric.

- A reconfigurable packet processing bus arbitration engine used for processing digital video data streams.

- 4. Reconfigurable multi-core processing system that can be adjusted to different video processing sizes (e.g., 64x64 and 32x32).

- 5. Development of a custom Linux driver for packet processing and dynamic partial reconfiguration.

- 6. Reconfigurable Packet Processor Round Robin Controller.

- 7. High-performance video processing system that is demonstrated using a dynamic pixel processor and dynamic, separable 2-D FIR implementation.

- 8. Overall, optimal performance is achieved in the sense that video data is processed at the maximum possible rate that can be streamed through the processing cores.

### 1.5. Organization

This dissertation is organized as follows:

- Chapter 2 presents basic background on FPGAs, Dynamic Partial Reconfiguration and Packet processing frameworks.

- Chapter 3 presents motivation for the proposed dissertation research.

- Chapter 4 explains the hardware and software architectures of the implemented

Dynamic Partial Reconfiguration systems.

- Chapter 5 presents the implementation results and discussion.

- Chapter 6 provides the conclusion for this dissertation and future work.

# **Chapter 2 Background**

This chapter provides topologic descriptions of the custom DPR scalable systems that were developed and subsequently applied at the University of New Mexico for the purpose of exploring DPR architectures and architectural trade-offs, and a review of the current state of the art DPR approaches in signal, image and video processing.

The specific DPR topology configurations that were evaluated are described. To accomplish that required the development of a DPR development, evaluation, and test environment. That environment is described including features, architecture, and furthermore an analysis of achievable output precision resulting due to limitations associated with various scalable architecture nuances.

The underlying physical structure of the FPGA logic fabric leads to a natural two dimensional tiling problem associated with the assignment of specific logic elements to the actual Combinational Logic Blocks (CLB) that are designated by the specified design to execute that logic function. Ultimately, all of the logic functions that are to be executed by the FPGA must be assigned to a specific CLB which itself would have specific physical coordinates associated with it. From a bitstream programming viewpoint, tile location represents a specific programming address in an address space. The purpose of the software tools that compile abstract hardware descriptive code (typically developed in VHDL or Verilog) is to translate the abstract code into technology specific primitive logic library elements and then to map that logic to specific locations within the CLB fabric of the FPGA device.

This physical mapping is constrained by local and physical routing (wire interconnect) resources as well as the physical loading and signal time delays resulting from the length and impedance of those interconnects. Consequently, the optimized placement of each of those instantiated logic elements results in multiple simultaneous NP-complete optimization problems [22]. As a result, placed designs are never optimum but instead are sub-optimum but optimal in the sense that a finite set of specific design constraints have been met [23].

Therefore the design of logic for FPGA devices involves the simultaneous requirement to create a logically correct design while also meeting all required physical and timing constraints for the assigned programmed logic. A key difference between FPGA logic design and Application Specific Integrated Circuit (ASIC) design is that ASIC designs result in silicon mask sets which produce transistor based logic directly fabricated in silicon. The logic in a FPGA device can be moved if the device is reprogrammed. This section addresses the structured methodology for moving or altering the placement of logic in an FPGA fabric during the normal run-time operation of that device.

To address the idea of redefining the logic of an FPGA device during operation, it is essential to first provide a structure for defining how, when, and where logic within the functioning device can be modified. Consequently, it is useful to organize physical structuring of the DPR problem organized into high level topological arrays of resources interconnected through specific architectural topologies.

The next section details the set of specific architectural topologies that were explored in the course of this research and details relevant attributes and features for each.

### 2.1. DPR Resource Interconnection

The FPGA CLBs consist of logic implemented by lookup tables (LUTs) and which are immersed in an associated interconnection fabric. The interconnection fabric itself contains both local as well as global routing resources (wire and driver logic).

Hur et al [24] explored trading hardwired interconnect performance with use of programmable resources. They evaluated performance against configuration costs for soft and hard crossbar interconnection and observed that for their application that the hardwired interconnection achieved significantly higher performance. Thus, it is clear that the reconfiguration overhead can be significant.

An LUT with its configuration storage is clearly larger than the logic it will be programmed to implement. Likewise, the interconnect fabric consists of more gates than would be necessary with a direct connection between logic elements [25].

When a PR region is reconfigured, any associated functional interconnections likewise must be reconfigured. Historically, PR methodology would have required bus macros which would be geographically spread out to provide connection resources available to accommodate multiple module interconnectivity. Lacking pre-optimized resource allocation, use of soft programmable resources for general interconnection is not efficient because resulting interconnection resources are distributed over a sub-optimum larger surface area and consequently consume even more resources.

Furthermore, with specific predetermined wire delays, timing of soft networks are highly unpredictable with wide variance prior to placement and routing. Subsequently, it may be difficult to guarantee or even meet design-time timing constraints due to this unpredictable net delay skew. In the case of PR circuits that are also adaptively changed, managing both the complexity of co-optimization of functional adaptation as well as interconnection synthesis is intractable without imposing structural constraint on allowable combinations.

To compose complex designs in either ASIC and FPGA technologies, it is common to use predesigned libraries, macro functions, or IP building blocks. As with other design paradigms it is common to develop building blocks for general use conformal to standards. Never-the-less compatibility remains a challenge. IP products address specific functional needs and corresponding interfaces are likewise functionally specific. As a result integration with other functions requires translational logic with alternative mappings for each required interface variant. It is for this and other reasons that standardized chip level interconnect strategies and associated IP have emerged to provide structured options.

One such chip level interconnection standard is the Advanced Microcontroller Bus Architecture (AMBA) from Arm [25] developed for ARM processors. ARM Holdings, PLC (UK) [26] licenses silicon IP for a wide range of custom ASICs and standard microcontroller and microprocessor products including some later generation FPGAs.

#### AMBA 4.0 defines five interfaces:

- Advanced eXtensible Interface (AXI)

- Advanced High-performance Bus (AHB)

- Advanced System Bus (ASB)

- Advanced Peripheral Bus (APB)

- Advanced Trace Bus (ATB)

The Advanced eXtensible Interface (AXI) specifically targets high speed designs.

AXI is a master/slave interface that is extensible using a switch or fabric. AXI provides separate address/control and data phases to support non-aligned byte-wide data transfers.

The bus standard accommodates multi-address burst transactions for efficient bus utilization. The bus specification is flexible providing multiple levels of performance and complexity allowing one or more bus masters.

AXI-Lite provides a lightweight version when full bus capability is not needed.

AXI Coherency Extensions (ACE) provides memory cache coherency support. AHB was introduced with AMBA-2 with AHB-Lite added in AMBA-3. AHB provides a single-edge clock protocol supporting multiple bus masters, split transactions, burst transfers, and single-cycle bus master handover. AHB is a non-tristate, pipelined architecture with bus widths up to 128 bits. AHB-Lite is a reduced subset for single master systems.

Finally, APB connects to AHB for low bandwidth and register interfaces for peripherals like serial ports. It is similar to AHB but is less complex; requiring fewer resources to implement.

The research associated with the current Ph.D. dissertation did not integrate a standardized interface such as AMBA, but given that the Xilinx Zync family incorporates two ARM processors, integration of this and/or another similar chip-level interconnection standard logically represents a next step in increasing the capability and flexibility of the design framework. The general approach taken to evaluating interconnection

architectures is described below. Bus or switch connected architectures are more suitable for adaptation to standards including AMBA but lattice structures are more suited to pipelined data flows architectures and structurally more closely resemble concurrent filter structures, the application subject of this research.

In addition to the physical and logical issues associated with interconnection, equally important is the physical arrangement and associations of DDPR regions.

Consider an FPGA design developed to support DPR where reconfiguration is performed on a by-physical-region basis. To accomplish this, the FPGA fabric is partitioned into a finite set of mutually exclusive physical regions which we generally refer herein to as DPR regions. An example of a regular partitioning of the fabric from the results can be seen in Figure 15 as well as in Figure 16 later on in this work.

A DPR design with multiple simultaneously running DPR regions can be split across a single FPGA fabric and/or across multiple FPGAs. The specific manner in which this would be accomplished would depend on system processing requirements constrained by the finite available interconnection resources between regions.

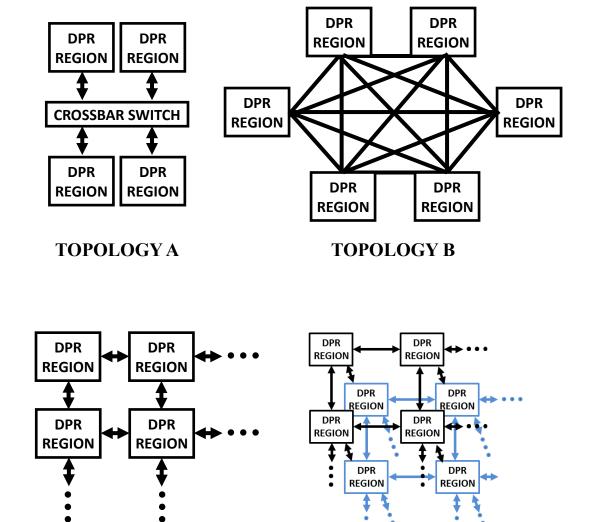

Interconnection resource allocation could either be optimally tuned for a specific application class, or alternately provisioned with sufficient resources to provide flexibility to accommodate a broader range of applications. Once utilizing DPR techniques, even interconnection resource provisioning can be reconfigured such that the system can be conditionally optimized for a particular class of processing techniques depending on its utilization environment. Figure 1 as follows depicts several common interconnection topology schemes that could be considered.

**TOPOLOGY C**

2-D Rectangular

Lattice

Figure 1. Researched DPR Region Topologies A to C

3D Rectangular Lattice

Topology *A* represents a crossbar style interconnection scheme. Each pair of DPR regions is connected through a central crossbar switch. This crossbar switch provides selectable direct interconnections and consequently allowing each individual DPR region to directly communicate with any other DPR region. The realization of this crossbar switch itself conceptually could be realized by a DPR region in a device. Alternatively a

specialized crossbar switching device or yet another FPGA device dedicated for routing could be used to create this connection capability.

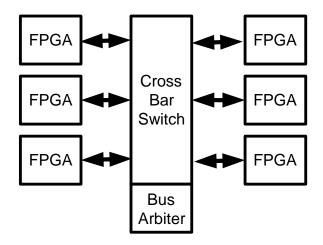

There are various well known forms and architectures of crossbar switches and the properties of those are very well established. Example crossbar realizations can be found in many development systems [26] [27] [28] [29] [30] [31] [32]. In Figure 2, we show an application of this topology that was studied within the Splash 2 [33] development system.

Figure 2. Splash 2 Interconnection Architecture

The Splash 2 architecture consists of sixteen (16) FPGAs individually connected to a common central crossbar. Switch connections between the DPRs are programmable and controlled by an additional seventeenth FPGA device. This architecture can be applied to DPR regions with either intra or external communication requirements. The advantage that DPR has in this type of architecture is the interconnect can remain static during multiple DPR configurations and by updating only the Bus Arbitration scheme to match the processing requirements the system can be optimized.

A fully connected interconnect topology can be seen in Topology B where all of the DPR regions connect to each other. This topology has the advantage of removing the crossbar latency from interconnections but the number of connections to each region grows as N! where N is the number of fully interconnected regions.

Both Topologies A and B have each FPGA connected to every other so they represent the most flexible topologies [34] [35] [36]. However, this flexibility comes at a cost. The ability to scale the number of region interconnections is nominally a linear function of the region boundary length, L. Hence the number of viable nodes N that can be interconnected in this manner is bound by a relationship of form  $O(N!) < \alpha \cdot f(L)$  where  $\alpha$  is some finite constant. Moreover, intra-region information flow and control complexity for each independent region would be anticipated to grow  $O(N!^2)$  whereas the region area would be anticipated to be  $o(L^2)$ . Thus this imposes an even more restrictive asymptotic bound of  $O(N!^2) < \beta \cdot f(L)^2$  for some finite constant  $\beta$ . Conversely, as the number of regions increases in a system, the number of possible connections required grows with O(N!). Since routing resources are finitely bound, the average number of available connections between any two regions consequently must be reduced.

The inability to scale combined with necessity to develop DPR macros that are themselves individually dependent on *N* and consequently topology dependent. This means that DPR region must be developed in a system-dependent manner. A fully interconnected topology increases system power and heat dissipation due to the total number of wire and drivers comprising the interconnection resources required as well as increasing interconnection control and flow logic.

2-D or 3-D mesh (or lattice) interconnection is represented by Topology *C*. The bottom of Figure 1 depicts rectangular 2-D or 3-D lattices. Interconnect routing for 2-D or 3-D lattices are either direct node to node interconnected or otherwise pass-through routed. These topologies allow a given DPR region to communicate directly with its neighbors. However, communication non-neighboring regions must be relayed through an intermediate region. Currently this type of topology is not realistic in DPR systems because of the large and complex nature of the communication requirements between nodes. However, with newer stacked die devices like the Virtex 7-2000T, which comprises of four of the largest FPGAs in the 7 Series devices on a Stacked Interposer, a hybrid of this type of interconnect, may be adapted in the near future. Examples of systems that use 2-D meshes are [37] [38] and systems that use a 3-D mesh are [39].

Figure 3. Researched DPR Region Topologies D to F

In systems where the algorithm is designed to be ran in a pipelined manner, for which a series of independent algorithms are applied, such as encryption and decryption of data. A linear interconnection scheme between DPR regions comprising of the stages, can efficiently implement pipelined applications. In this type of application data is sent into the system from one end of the chain for each DPR region to process in order. The result is then output from the last FPGA. One feature of this architecture, seen in

topology E, is (if designed to do so) for problems such as encryption/decryption, is that the data can be fed into the stages in one direction for encryption and in the reverse order for decryption.

A hybrid topology of the cross bar and pipeline architecture is the shared access memory topology. This topology allows the architecture to take advantage of a wide variety of algorithmic optimizations and still maintain the ability to share information between DPR regions. An adaptation to this topology can be seen in Topology *F* where the I/O Cross Bar can directly load the independent DPR regions and directly access the shared access memory through the memory cross bar. One of the primary concerns with this type of topology is both the I/O and memory cross bar must communicate with one another else data corruption can occur. For this architecture to be the most efficient, the bus between the memory cross bar should be scaled such that data through put is maintained. This type of architecture has been used in multi node single instruction multiple data applications. One example of this can be found in [40] the Texas Memory Systems S4 Vector Processing system.

The realized architecture can be best described as a layered hybrid interconnection architecture where the video data distribution and routing layer is represented by a crossbar connected network as discussed previously. The next section details the numerous possible complexities and tradeoffs that are associated with packet-switched architectures and additionally explains a novel approach to scheduling with specific details provided in Section 3.3.1.2.

However, it additionally should be understood that underlying that layer, at the DPR fabric layer, Filter Processing Cores can be viewed as a 2-D lattice network. This is described in 3.2.2 and depicted in Figure 15.

## 2.2. Data Switching and Packet Routing

Because this work focuses on packet-based processing and involves distributed queuing and routing of data packets, it is essential to understand the architecture in terms of its characteristics related to packet switch technologies and techniques. A significant result from this research was to propose and develop a novel approach to data queue allocation and scheduling using a novel Adaptive Weighted Round Robin (AWRR) scheduling protocol that is optimized for the adaptive video FPGA DPR application described by this work. The implementation of the AWRR protocol is detailed in Section 3.3.1.2.

There are many possible technologies, topologies and architectural approaches to provide data flow mechanisms in a system. When data flows require aggregation or deaggregation, those flow points become shared resources for data producers or consumers. Historically, the primary means for parallel accessibility to shared common resources involves either a common exchange media (such as a bus or other common, arbitrated media) or a switched network. Bus architectures for processing applications have largely dominated all but the very high-end applications for the last several decades.

System level performance is bounded by interconnectivity capabilities and capacities. However, there are increasingly challenging physical bounds on achievable speed and bandwidth of bussed technologies. Combined with the emergence of high-

speed serial interconnect technologies, this has resulted in increased emphasis on switching architectures.

A significant attribute and potential benefit of switch based architectures is the concentration of connection management complexity together into the control for that switch fabric. For a single, centralized switch, the majority of the complexity of system interconnection is concentrated in that switch. Consequently, viable solutions must be compact and efficient [41].

When considering the general topic of switch technologies, there are a few general categories that are widely discussed in the literature. These include:

- Cell Based Switching

- Packet Based Switching

- Time Division Multiplexing (TDM)

- Circuit Switching

- Connection/Connection-less Switching

- Dynamic path routing

- Memory-less Crossbar Switch

Especially when examining complex or distributed switching systems, often the system can be functionally decomposed into multiple layers of switching that are themselves constructed from one of the other categories of switches. Thus the higher level represents an abstraction of a service that is provided by the lower layer of the switch fabric. Consequently, to really understand switching technology, it is helpful to first understand the primitive constructs that are common to switch architectures.

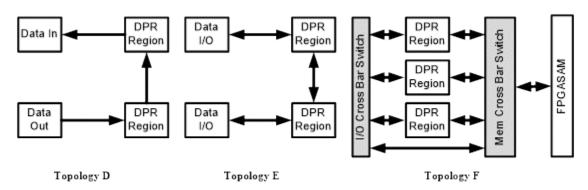

Data that flows through a system must be buffered at any point associated with delay. Delay occurs due to competition for use of a shared element or path through the switch. For a switched network, there are three general forms of buffering. Buffering can occur at the input to the switch, at the center of the switch, or the output of the switch. This concept is illustrated in Figure 4 below.

Figure 4. Switch Buffer Architectures [41]

For purpose of this work, we explain some of the primary considerations involved with architectural aspects of designing the queuing structures for packet switching and we will explain the corresponding considerations and issues that contribute to the architectural choices made during this work.

The problem of understanding switch data flow complexity can be discussed in terms of the allocation and use of the data buffering used to provide the queuing structures in the switch. Understanding switch behavior (capability, capacity, and limits) can be discussed in terms of the queuing mechanisms. Consequently, it is helpful to consider the types of queues that can be constructed. For instance, queues can be allocated with fixed memory resources or can draw their memory resources from a pool of memory buffers. This pool of buffers could either be made up of fixed-size blocks that can be linked and unlinked together to provide the memory for the queue, or a contiguous

block of memory could be allocated. Either case requires a mechanism to organize the pool, to allocate and de-allocate use of memory, and also to manage cleanup if irregular sized blocks of memory are permitted.

As discussed previously, queues can be associated with inbound traffic, outbound traffic, or centrally located and consequently associated with a combination of inbound or outbound traffic. Queues can be used for data collection from inbound traffic. They can be used to buffer data as a Transmission Queues for outbound traffic. Queues can be used to replicate traffic to provide multi-cast or broadcast service. They also can be used to organize, prioritize, sort, or reorder traffic.

Unless queues are assigned fixed memory resources, they must share them. Fixed assignment can mean permanent or hardwired allocation or it can simply mean statically fixed (meaning that resources can later be re-allocated). If resources are sharable and not statically allocated, then it is necessary to consider different protocols for queue provisioning. Allocation and management can occur on a per-path, per flow, or per traffic class/sub-class basis, or even user defined. Sharing can involve demand-driven, dynamic allocation, or statically-based allocation.

Shared resources consequently involve considerations including thresholds and limitations. When differentiation occurs, it can be on a per-path, flow, or class basis. Algorithms can be applied to shape the traffic flows, or applied to encourage resource utilization, such as the case with "greedy flow" algorithms.

Looking at an individual queue, a first consideration is when it is possible to simply put data into the queue. The queue is intended to be the place where data delay can be accommodated and consequently it is assumed that data cannot wait on queue

availability. However, data is not always available to place in a queue or else there would not be a rate matching or delay need to begin with. Queues are typically designed to underflow their input capacity, at least slightly. However, because the queue represents a finite memory resource, only a finite amount of data can exist in the queue at any moment. Hence, once the queue fills, data must either be overwritten or else input discarded. There are various protocols for queue admission management including [41]:

- Drop Tail

- Packets are dropped from end if queue fills

- Lost packets are an arbitrary result of resource over-allocation

- Random Early Discard (RED)

- Packets discarded when queue depth exceeds threshold

- Probability of drop increases as depth grows

- When queue fills acts like drop tail

- Weighted Random Early Discard (WRED)

- Drop probability is class dependent

- Drop Head

- Not frequently used

- Prioritizes new packets over old

- Class based versus flow based policies

Queues are "serviced" when data is read (removed) from the queue. For output buffered queues, switching control mechanisms must control physical path connectivity to the queue input port such that the port is guaranteed available whenever data arrives.

One physical mechanism often used to provide that guarantee is to use a multiport input

such that there is always and available port. For output buffered switches, output buffers are serviced by the corresponding data consumer per the rate and service mechanism for that specific consumer. In contrast, for input-buffered switches, the actual act of switching occurs through the process of selecting which source queue is to be serviced next. Commonly used queue servicing or scheduling mechanisms include:

- FIFO (First-In-First-Out) or FILO (First-In-Last-Out)

- Queue service is based on packet arrival time

- Periodic versus Aperiodic; Virtual Clock or Bounded Time

- Weighting selection prioritization based on queue depth (un-serviced content)

- Per packet

- Per word

- Flow / Class differentiation

- Prioritization

- Strict Prioritization

- Round Robin / Weighted Round Robin / Deficit Round Robin

- Hybridization

As will be seen in later sections, individual data flows incorporate FIFO queue structures. However, there are multiple service scheduling mechanisms that occur concurrently. At the highest level of task process coordination, this work describes an adaptive variation of a Weighted Round Robin (WRR) scheduler.

Of course there are many possible tradeoffs involved in selection of queue structures, queue use policies, and queue service policies [41]. The current application drove selection of a set of structures and techniques. As the DPR framework evolves, it

will prove necessary to provide a wider range of scheduling mechanisms in order to optimize resource use for other anticipated flow traffic and processing algorithm characteristics.

Commonly considered tradeoffs include:

- Algorithm Complexity. In this research, the desired types of processing were mostly known a priori.

- Memory cost, organization, and provisioning. In the Ph.D. dissertation,

performance is optimized to match fixed resources

- Fairness. Fairness is a concern when there a multiple flows with differing

priorities and variation in traffic statistics. Fairness allows all consumers some

amount of resource utilization. This is a more sophisticated need than required

for this Ph.D. dissertation.

- Flow isolation or protection. When processing multiple video flows, it may be

desirable to preclude variable processing in one flow to adversely impact the

ability of another to meet service guarantees.

#### • Efficiency:

- Temporary over-subscription. It is desirable in some cases to permit oversubscription of resources to occur, especially if back pressure or other means can be applied to provide overall elasticity

- Permanent over-subscription. This work is "virtually" permanently oversubscribed and adaptively adjusts resources to maximize the overall efficiency, fully using available resources

The design of a full featured framework for packet processing DPR is very analogous to design of a packet routing switch fabric. Indeed, the data distribution and routing of application data is a packet switching problem. Overlaid to that is the hardware virtualization of logic resources. These resources must be scheduled for FPGA reconfiguration at that time where they are needed for processing and then replaced with other functions. Thus the total footprint of available logic functions can greatly exceed the instantaneous logic actually present in the device at a given time.

One of the significant achievements of this work was achieving the DPR reconfiguration programming over a multi-lane high speed serial interface consequently leading to region reconfiguration turn-around times that are of an order similar to task processing times.

# 2.3. Round Robin / Weighted Round Robin / Deficit Round Robin

Because of the limitations of strict priority protocols an alternative approach commonly referred to as "Round Robin" scheduling is popular. In a simple round robin protocol, queues are organized in a linear ordered manner and each queue is serviced in order (if data available) until all have been serviced at which point the scheduling mechanism goes back to the first of the list [41]. Scheduling essentially begins examining the service request state of the first queue in the list. If service is requested, then a packet is removed from the queue, otherwise the queue pointer moves to the next in the list and the process repeats until all queues have been visited, in which case the pointer goes back to the start of the list. Each queue serviced has exactly one packet removed from the queue.

Simple Round Robin does not provide a capability to differentiate among queues with high traffic rates. Since each queue essentially gets equal treatment, then data arrivals in low data rate queues are more likely to be immediately serviced. Arrivals in relatively high data rate queues therefore experience congestion and backup with corresponding increase in average latency.

To overcome this limitation of Simple Round Robin, the idea of Weighted Round Robin is to apply a weighting factor to the selection process. The weight determines the average number of packets to service from each non-empty queue. Therefore, the number of packets to service would be the weight divided by an average packet size.

A limitation of Weighted Round Robin is that the algorithm is not well suited when there does not exist any a priori knowledge of packet sizes, packet sizes have widely varying sizes, ill-suited statistical characteristics, packet sizes are unpredictable, or change over time. Shreedhar and Varghese [42]originally proposed the idea of Deficit Round Robin (DRR) to overcome associated issues. In DRR, a threshold size is used to hold back first-in-line packets whose length exceeds this threshold. This threshold value is used as a deficit counter for the queue and is increased by a default deficit amount for the next schedule time. If the size still exceeds the current count (also referred to as the credit), the count is again increased and this continues until the packet is serviced. Whenever a packet is serviced from a DRR queue, its credit is decreased by the packet size.

#### 2.3.1. Queue Service Prioritization Policies

Among the most commonly used methods for queue selection for service are those policies that are priority-driven. A strict prioritization protocol assigns a linear priority

to each possible selection and whenever the highest priority queue demands service, it is serviced prior to any other queue [41]. If that queue is empty then the service goes to the next highest priority queue that requires service. Strict prioritization guarantees that the highest priority data is always serviced first. The shortcoming is that if the system flows and priorities are not carefully considered, it is possible that lower priority traffic can experience extensive delays, might be discarded, or may not be guaranteed to ever be serviced.

A strict priority protocol can be augmented with additional rules that either promote/demote data traffic priorities, or allow limited amounts of low priority data to be serviced. The later rule is commonly referred to as a leaky bucket protocol [41].

## 2.4. State of the Art for Reconfigurable Computing

In today's systems, reducing system size, weight, and power (SWaP) is critical for operational life and budgetary constraints. SWaP budgets are driven down to extend battery life, reduce form factor for better mobility and logistics, and expand the market. In platforms such as cell phones, SWaP constraints are different because there is a need to support fast embedded processors for the increasing image and video processing needs while still staying within the SWaP budget.

Reconfigurable Computing (RC) has been identified as the solution to provide substantial performance benefits while maintaining the tight SWaP budgets compared to traditional microprocessors or GPUs [43]. The Dynamic Instruction Set Computer (DISC), first proposed by Wirthlin and Hutchings [44] was one method introduce to address this issue by using a medium grain Configurable Logic ArraY (CLAY) device from National semiconductors. This computer had an instruction set made up of

independent hardware units configured into the device as needed. The architecture's performance was limited by the reconfiguration time overhead and the number and size of the processors was fixed.

Other research has been concerned with detection of bottle necks in RC. These include High-level synthesis tools increase FPGA productivity [45], Characterization and Optimization of Atomic Operations in GPUs [46] and Integrated Development Toolset and Implementation Methodology for Partially Reconfigurable System-on-Chips [47]. These systems have been primarily focused on RC development systems and not creating a low SWaP framework to apply general or specific algorithms.

For RC, one of the primary areas of interest is reducing the Data Movement this has been looked at in both the reconfiguration time, data dependency between tasks, inter-task communication as well as task resource utilization [48]. However, in addressing these scheduling issues, the authors did not consider dynamically reconfigurable systems.

A large amount of research has also been associated with the use of multiple chips, ranging from the use of processors, DSPs and/or FPGAs including Multi-Level Performance Prediction of Multi-FPGA Systems, Multilevel-PGAS Programming Model for Reconfigurable Supercomputing [49] and Bridging Parallel and Reconfigurable Computing with Multilevel PGAS and SHMEM [50] [51]. These approaches addressed issues associated with working with multiple devices and modeling the data flow through these parallel systems. However, these prior approaches fall short of looking at the issues of data movement and reconfiguration of multiple RC engines in a single heterogeneous low SWaP architecture, as done in this dissertation research.

## 2.4.1. Embedded Reconfigurable Computing

Dynamic Partial Reconfiguration (DPR) refers to an on-going process reconfiguring portions of an FPGA during run time while other portions remain active. Research continues towards developing more useful methodologies that can realize the potential utility of FPGA DPR [18]. The existing literature speaks to the considerable potential for fundamental change in flexibility, effectiveness and efficiency. Perhaps the most important advantage afforded by DPR is an ability to employ smaller or few FPGAs reducing cost, packaging, and power [15]. Capabilities for PR have existed for several years, yet the design methodologies, flows, and tool capabilities capable of effectively using PR remain limited. Existing methodologies for PR previously have been largely ad hoc, cumbersome, or poorly integrated into the regular design flow [18].

Fons [11] however, noted that the first commercial products/systems driven by PR technologies are beginning to enter the marketplace. In his dissertation, the author provides an introduction into the history of reconfigurable computational technologies. The author also provides an extensive and detailed explanation of the differing FPGA technologies. Most relevant to this work, the author discusses the different forms of PR technologies (including those from Xilinx.) The author discusses PR in terms of context planes for FPGA reconfiguration defined as planes of programmable resources. FPGAs are envisioned as reconfiguration capabilities multiplexed in a manner that only one of the configuration planes is active at a given time. Consequently, creating a multi-context FPGA requires multiple memory bits for each programming bit location. These memory bits would be used to define the multiple planes of configuration information. The model allows for background loading of one of the contexts while another is active and

executing. In this model, one configuration plane is active at a given time and the device switches among alternate context of already programmed configurations. The author provides extensive information on the body of work accomplished and his published work serves as a good reference to understand DPR technologies.

With dynamically and partially reconfigurable designs, it is necessary that the speed of the reconfiguration be accomplished in a time that is sufficiently small such that the operation of reconfiguration is not the limiting factor in the process. This was accomplished by designing and implementing a High Speed Dynamic Partial Reconfiguration Controller (HSDPRC) core that maximized the bandwidth of the ICAP. The work used on chip temperature and voltage active feedback for Dynamic Partial Reconfiguration. This approach created a DPR controller that is tightly coupled with the FPGA silicon and the system behavior than previous work had not accomplished [4].

There is strong interest in the development of dynamically reconfigurable systems that can meet real-time constraints in energy/power-performance-accuracy (EPA/PPA). Recently, in his Ph.D. dissertation research, Dr. Llamocca described a research framework for implementing dynamically reconfigurable digital signal, image, and video processing systems. However, the proposed architecture was not scalable since it did not use a video packet based approach for dealing with system scaling issues [52] [53] [54] [55]. Additionally, this research was built on an embedded processing system where a processor running in the fabric moved the data in and out of the processing cores.

The proposed dissertation architecture provides a scalable architecture for sustaining high-performance in multi-core, dynamically reconfigurable systems.

Moreover, the run-time adaptability of the scheduling protocol described here is uniquely targeted towards dynamically reconfigurable applications.

## 2.4.2. FPGA Reconfiguration Methodology

Programming the soft logic of an FPGA is significantly different than writing software for a processor. Low level design is typically accomplished in Register Transfer Level (RTL) Verilog or VHDL and is similar to ASIC design. The primary difference is that RTL for FPGA design includes additional limitations on language use to guide proper circuit inference within the logic synthesis tools. In addition to RTL design, there is dramatic increase in design complexity.