# University of New Mexico UNM Digital Repository

**Electrical and Computer Engineering ETDs**

**Engineering ETDs**

1-28-2015

# LARGE-AREA, WAFER-SCALE EPITAXIAL GROWTH OF GERMANIUM ON SILICON AND INTEGRATION OF HIGH-PERFORMANCE TRANSISTORS

Swapnadip Ghosh

Follow this and additional works at: https://digitalrepository.unm.edu/ece etds

#### Recommended Citation

Ghosh, Swapnadip. "LARGE-AREA, WAFER-SCALE EPITAXIAL GROWTH OF GERMANIUM ON SILICON AND INTEGRATION OF HIGH-PERFORMANCE TRANSISTORS." (2015). https://digitalrepository.unm.edu/ece\_etds/97

This Dissertation is brought to you for free and open access by the Engineering ETDs at UNM Digital Repository. It has been accepted for inclusion in Electrical and Computer Engineering ETDs by an authorized administrator of UNM Digital Repository. For more information, please contact disc@unm.edu.

| Swapnadip Ghosh Candidate                                                                |               |

|------------------------------------------------------------------------------------------|---------------|

| Canaidate                                                                                |               |

| Electrical and Computer Engineering                                                      |               |

| Department                                                                               |               |

|                                                                                          |               |

| This dissertation is approved, and it is acceptable in quality and form for publication: |               |

| Approved by the Dissertation Committee:                                                  |               |

| Sang M Han                                                                               | , Chairperson |

| Sanjay Krishna                                                                           |               |

| Ganesh Balakrishnan                                                                      |               |

|                                                                                          |               |

| Daniel Feezell                                                                           |               |

|                                                                                          |               |

|                                                                                          |               |

|                                                                                          |               |

|                                                                                          |               |

|                                                                                          |               |

|                                                                                          |               |

|                                                                                          |               |

# LARGE-AREA, WAFER-SCALE EPITAXIAL GROWTH OF GERMANIUM ON SILICON AND INTEGRATION OF HIGH-PERFORMANCE TRANSISTORS

#### $\mathbf{BY}$

#### **SWAPNADIP GHOSH**

B.Tech University of Kalyani, India

## **DISSERTATION**

Submitted in Partial Fulfillment of the Requirements for the Degree of

**Doctor of Philosophy Engineering**

The University of New Mexico Albuquerque, New Mexico **December, 2014**  © 2014, Swapnadip Ghosh

#### **DEDICATION**

I dedicate this work, first and foremost, to my beautiful wife, Sudakshina Das. Her support and understanding of all the late evenings and weekends spend studying and working in the lab has allowed me to fulfill my research goals for this work. Without the sacrifices she made in allowing me to pursue my dreams, none of this work would have been possible. She has been the best friend, supporter, and partner I could have asked for.

Second, this work is dedicated to my parents Parimal Ghosh, and Aruna Ghosh for their support and encouragement to fulfill my potential and pursue my dreams. I hope I have made them proud of my accomplishments and will continue to do so in my future endeavors.

Third, I also dedicate this work to my extended family and friends for their encouragement and understanding when I was often absent from family functions, both mentally and physically.

#### **ACKKNOWLEDGEMENTS**

I wholeheartedly acknowledge my research advisor, Sang Han, in the accomplishment of this work. He has been a dedicated teacher, mentor, and friend to me throughout graduate school, and I know he will continue to be so in the future. I also thank him for the long hours spent teaching me the art of technical writing.

I wish to thank my dissertation committee for taking the time to read my dissertation and provide me with feedback on my research. They are all excellent teachers and I have greatly enjoyed and benefited from attending their courses.

I thank our research group members both past and present for their assistance with my work. In particular, I thank Darin Leonhardt for teaching me about vacuum systems and equipment, and for mentoring me at the beginning of graduate school. I also thank Luis Tribby, Josephine Sheng, Mi Zhou, Jose Bonilla, and Sarun Atiganyanun for their help and feedback on my research, and for making the lab more fun and interesting.

I also acknowledge the entire CHTM staff for their help in keeping the lab safer and for keeping equipment running that was required to carry out my experiments. I also thank the CHTM staff for creating a festive atmosphere during all the holidays and for feeding me often at their delicious potlucks.

I also acknowledgethe support by, or in part by, the National Science Foundation (DMR-0907112).

## LARGE-AREA, WAFER-SCALE EPITAXIAL GROWTH OF GERMANIUM ON SILICON AND INTEGRATION OF HIGH-PERFORMANCE TRANSISTORS

#### BY

#### **SWAPNADIP GHOSH**

B.Tech University of Kalyani, India PhD, Engineering, University of New Mexico, 2014

#### **ABSTRACT**

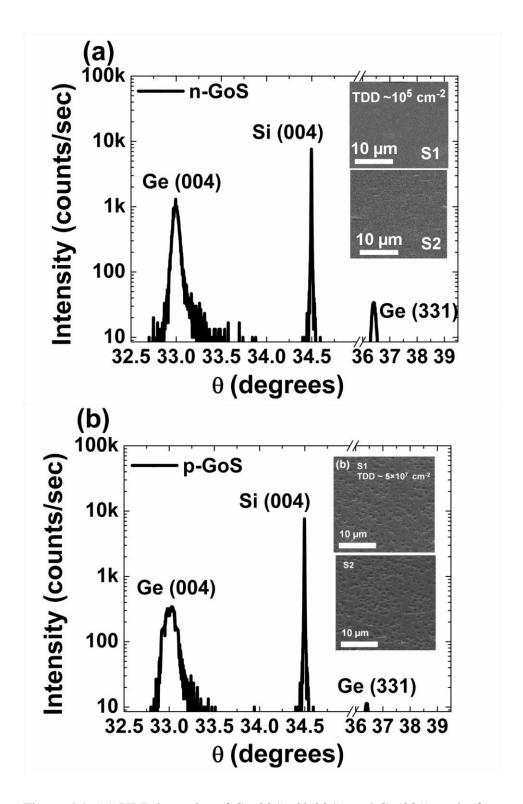

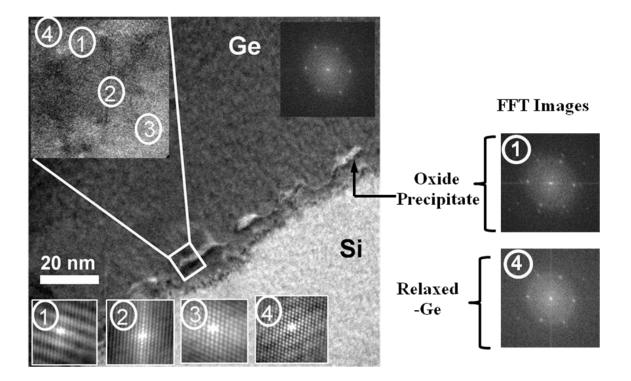

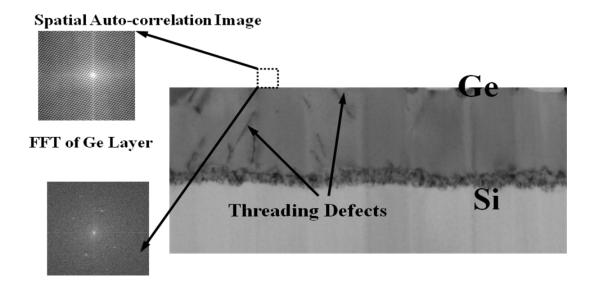

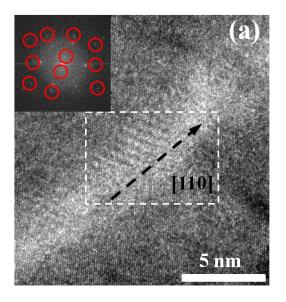

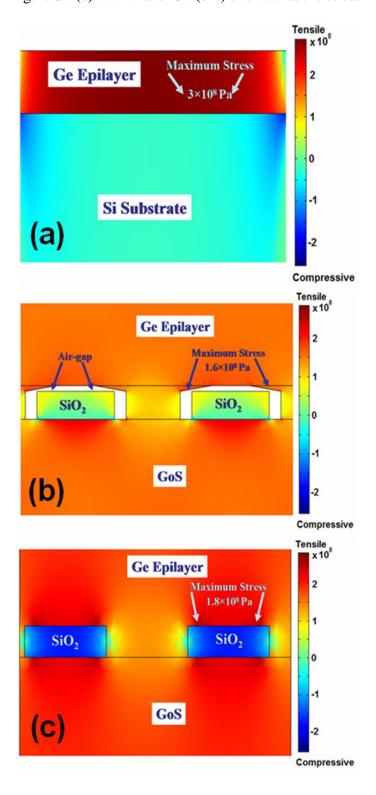

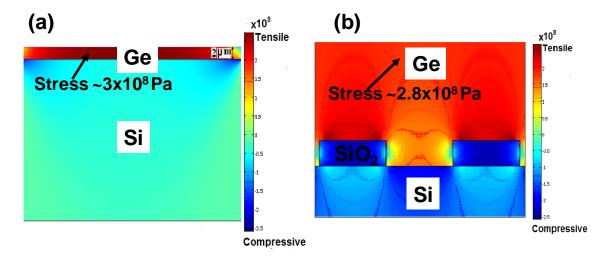

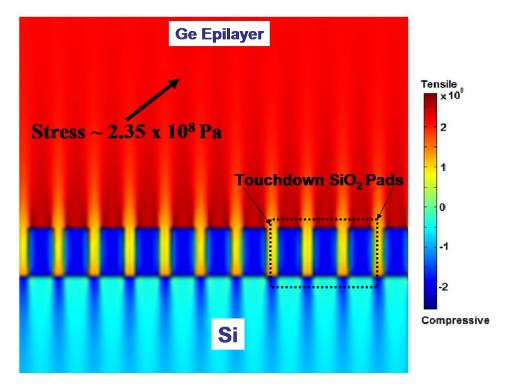

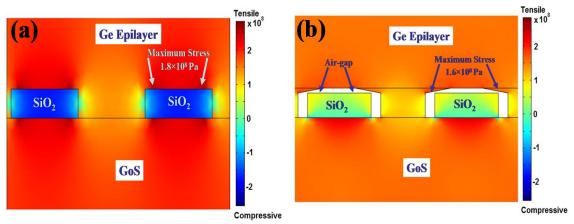

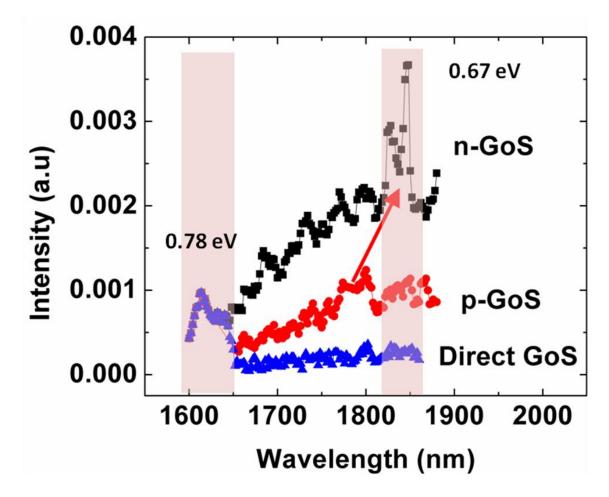

Building on a unique two-step, simple MBE growth technique, we have investigated possible dislocation locking mechanisms by dopant impurities, coupled with artificially introduced oxygen. In the case of n-type Ge grown on Si, our materials characterization indicates that the dislocation density (DD) can reach the  $\sim 10^5$  cm<sup>-2</sup> level. compared to p-type and undoped Ge on Si (GoS). We note that our Ge film covers the entire underlying Si substrate at the wafer scale without mesas or limited-area growth. In this presentation, we will focus on the use of n-type impurity (phosphorus) diffusing from the Si substrate and the introduction of O at the Ge-Si interface. The O is introduced by growing a thin chemical SiO<sub>2</sub> layer on top of the Si substrate before Ge epitaxy begins. Z-contrast cross-sectional TEM images suggest the presence of oxygen precipitates in ntype Ge, whereas these precipitates appear absent in p-type Ge. These oxygen precipitates are known to lock the dislocations. Supporting the argument of precipitate formation, the TEM shows fringes due to various phase boundaries that exist at the precipitate/Ge-crystal interface. We speculate that the formation of phosphorus (P) segregation resulting from slow diffusion of P through precipitates at the precipitate/Gecrystal interface facilitates dislocation locking. Impurity segregations in turn suppress O

concentration in n-type Ge indicating reduced magnitude of DD that appears on the top surface of n-Ge compared to p-Ge film. The O concentrations (10<sup>17</sup> to 10<sup>18</sup> cm<sup>-3</sup>) in the n- and p-type GoS films are measured using secondary ionization mass spectroscopy. We also demonstrate the technique to improve the Ge epitaxial quality by inserting airgapped, SiO<sub>2</sub>-based nanoscale templates within epitaxially grown Ge on Si. We have shown that the template simultaneously filters threading dislocations propagating from Ge-Si interface and relieves the film stress caused by the TEC mismatch. The finite element modeling stress simulation shows that the oval air gaps around the SiO<sub>2</sub> template can reduce the thermal stress by 50% and help reduce the DD. We have then compared the structural and electrical characteristics of n-type Ge films with its p-type counter parts. In n-type Ge, the DD decreases from ~10<sup>9</sup> cm<sup>-2</sup> near the Ge-Si interface to ~10<sup>5</sup> cm<sup>-2</sup> <sup>2</sup> at the film surface. In contrast, we observe  $5\times10^7$  cm<sup>-2</sup> TDD at the film surface in ptype Ge. The full width at half-maximum for our n-type Ge(004) XRD peak is ~70% narrower than that of p-type Ge. As a stringent test of the dislocation reduction, we have also fabricated and characterized high-carrier-mobility MOSFETs on GoS substrates. We also report p- and n-MOSFETs with  $\mu_{eff}$  of 401 and 940 cm<sup>2</sup>/V-s and a subthreshold slope of 100 and 200 mV/decade, respectively. These effective mobilities show an exceptional 82 and 30% improvement over that of conventional Si channel MOSFETs. We also investigate the optical quality of ultra-low DD GoS film by measuring photoluminescence (PL). The n-type Ge PL main peak shows pronounced tensile-strain  $(\times 0.8\%)$  than that of p-type which is an indicator of direct BG shrinking at the  $\Gamma$  bandedge. Going beyond epitaxial engineering and device fabrication, we have also recently demonstrated a scalable path to create a 2D array of Ge quantum dots (QDs) on responsive SiGe substrates based on elastic mechanical deformation and subsequent SiGe compositional redistribution, coupled with MBE growth. For large-scale manufacturing of single-electron transistors, we have also demonstrated that a spatially structured elastic compressive stress to the SiGe substrate with thermally annealing leads to a compositional redistribution of Si and Ge in the near-surface region of SiGe substrates, forming a 2D array of Ge-depleted nanoscale regions. Based on these latest findings, we have also begun to chart a future direction for my research group, where one can explore new advanced device architectures, such as Si-compatible, optically actuated, Gequantum dot-based field effect transistors.

# TABLE OF CONTENTS

| LIST  | OF FIGURES xiv                                                             |

|-------|----------------------------------------------------------------------------|

| LIST  | OF TABLESxxvii                                                             |

| Chapt | ter 1 Introduction                                                         |

| 1.1   | MOSFET Scaling Benefits                                                    |

| 1.2   | Beyond Scaling                                                             |

| 1.3   | Emerging CMOS Technology Roadmap5                                          |

| 1.4   | The Promise of Silicon Photonics9                                          |

| 1.5   | Why Germanium?                                                             |

| 1.6   | Importance of Heteroepitaxy of Ge-on-Si                                    |

| 1.7   | Barriers to High-Quality Epitaxial Ge-on-Si                                |

| 1.8   | Previously Reported Research of Ge-on-Si                                   |

| 1.8.1 | Growth of High Quality Relaxed Ge Layers Using Compositional Grading35     |

| 1.8.2 | Two Step CVD Growth With Low Temperature Buffer Layer                      |

| 1.8.3 | Multiple Hydrogen Annealing for Heteroepitaxy                              |

| 1.8.4 | Heteroepitaxy using Super Lattice Structures (SLS)                         |

| 1.8.5 | Heteroepitaxy using Aspect Ratio Trapping (ART) Method                     |

| 1.9   | Selective Growth using Nanoheteroepitaxy                                   |

| Chapt | ter 2 Growth of Ge-on-Si using Molecular Beam Epitaxy and Characterization |

| Techn | niques                                                                     |

| 2.1   | Theory of Crystal Growth                                                   |

| 2.2   | Form Islanding to Surface Roughness                                        |

| 2.2.1 | Three Growth Modes                                                         |

| 2.2.2 I  | sland Growth Mode or Volmer-Weber growth (VW) mode             | 50       |

|----------|----------------------------------------------------------------|----------|

| 2.2.3 I  | Layer Growth Mode or Frank Van der Merwe (FVM) Mode            | 52       |

| 2.2.4 \$ | Stranski-Krastanov (SK) Growth Mode                            | 52       |

| 2.3      | Molecular Beam Epitaxy.                                        | 54       |

| 2.4      | Selective Epitaxial Growth                                     | 59       |

| 2.5      | Heterogeneous Atomistic Nucleation Theory                      | 59       |

| 2.6      | Nucleation Density and of Energetics of Ge on SiO <sub>2</sub> | 65       |

| Chapt    | ter 3 Material and Device Characterization Techniques          | Material |

| Chara    | acterizations                                                  |          |

| 3.1      | X-ray Diffraction.                                             | 69       |

| 3.2      | X-ray Photoelectron Spectroscopy                               | 71       |

| 3.3      | Scanning Electron Microscopy                                   | 74       |

| 3.4      | Focused Ion Beam.                                              | 75       |

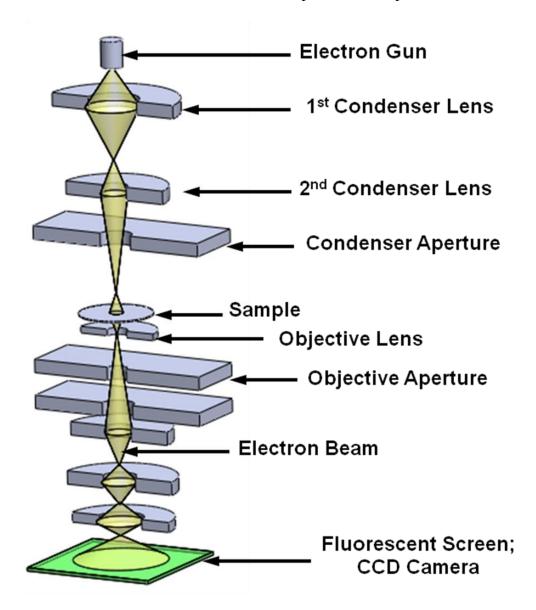

| 3.5      | Transmission Electron Microscopy                               | 77       |

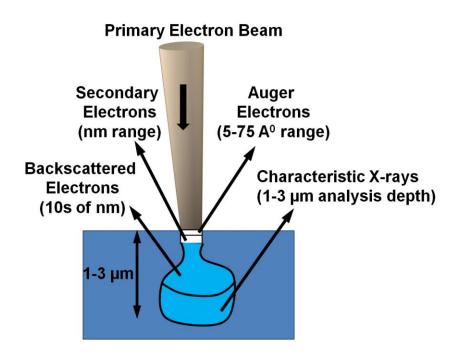

| 3.6      | Energy Dispersive Spectroscopy                                 | 79       |

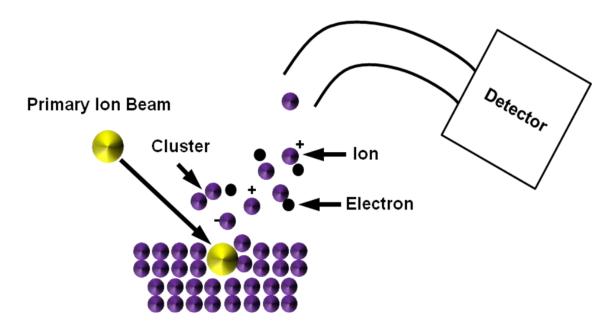

| 3.7      | Secondary Ion Mass Spectroscopy                                | 81       |

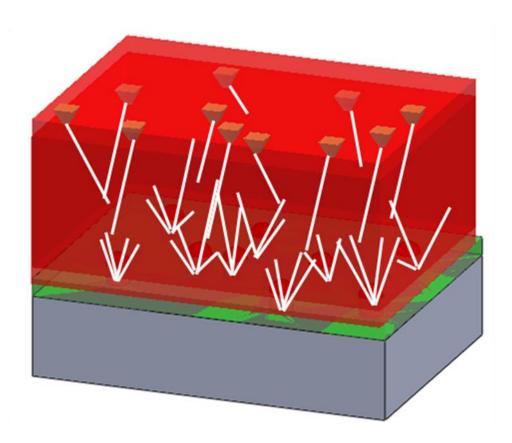

| 3.8      | Etch Pit Density.                                              | 82       |

| 3.9      | Photoluminescence                                              | 83       |

| 3.10     | Interferometric Lithography                                    | 84       |

| Carr     | ier Transport Characterizations                                |          |

| 3.11     | Hall Measurement.                                              | 86       |

| 3.12     | Capacitance-Voltage                                            | 87       |

| 3 13     | Current-Voltage                                                | 89       |

| Chap  | ter 4 Ultra-Low-Dislocation-Density, Wafer-Scale, Epitaxial Ge-on-S       | i          |

|-------|---------------------------------------------------------------------------|------------|

| 4.1   | Introduction and Background.                                              | 91         |

| 4.2   | Experimental Details.                                                     | 92         |

| 4.3   | Growth Results and Discussions                                            | 94         |

| 4.3.1 | Selective Growth of Ge in Nanoscale Openings in Chemical SiO <sub>2</sub> | 94         |

| 4.3.2 | Mechanism of Stacking Fault Removal by Annealing Ge Islands               | 102        |

| 4.3.3 | Mechanism of Dislocation Locking by Oxide Precipitates and Impuritie      | es107      |

| 4.4   | Plan-view Characterization of Ge Films.                                   | 121        |

| Chap  | ter 5 Investigation on Thermal Stress Stress Relief in Ge-on-Si           | using air- |

| gappe | ed SiO <sub>2</sub> nanotemplates                                         |            |

| 5.1   | Introduction and Background                                               | 124        |

| 5.2   | Experimental Details                                                      | 125        |

| 5.3   | Results and Discussions.                                                  | 127        |

| 5.4   | Mechanism of Thermal Stress Reduction using Air-gap                       | 128        |

| 5.5   | Finite Element Modeling of Air-gapped Templates                           | 129        |

| 5.6   | Conclusions.                                                              | 132        |

| Chap  | ter 6 High-Speed Transistors on Ge-on-Si Substrates                       |            |

| 6.1   | Introduction                                                              | 133        |

| 6.2   | Germanium Growth on Silicon.                                              | 135        |

| 6.3   | Materials Characterization.                                               | 138        |

| 6.4   | Metal-Semiconductor Field Effect Transistors Fabrication                  | 139        |

| 6.5   | Effect of Dislocations and Dielectric Layers on                           | Electrical |

| Chara | cteristics                                                                | 142        |

| 6.5.1 | Hole Mobility in Ge Epilayer                                                    |                             | 142      |

|-------|---------------------------------------------------------------------------------|-----------------------------|----------|

| 6.5.2 | Current-Voltage Characteristics of                                              | of Metal-Semiconductor      | Schottky |

| Conta | ct                                                                              |                             | 150      |

| 6.5.3 | C-V Characterization and Interface Trap I                                       | Densit                      | 154      |

| 6.5.4 | J-V Characteristics and                                                         | External Transconducta      | ince of  |

| MESI  | FETs                                                                            |                             | 161      |

| 6.6   | Conclusions                                                                     |                             | 168      |

| 6.7   | Metal-Oxide-Semiconductor Field Effect                                          | Transistors                 | 170      |

| 6.8   | Material Growth and Characterization                                            |                             | 170      |

| 6.9   | Device Fabrication                                                              |                             | 173      |

| 6.10  | Results and Discussion                                                          |                             | 174      |

| 6.11  | Effective Mobility of MOSFETs                                                   |                             | 177      |

| 6.12  | Conclusions                                                                     |                             | 178      |

| 2D Â  | ter 7 FUTURE DIRECTION: Creating rray of Ge Quantum Dots Using Stress tribution | -                           |          |

| 7.1   | Introduction                                                                    |                             | 180      |

| 7.2   | Proposed Mechanism of Fabricating Long                                          | g-Range, Periodic QDs of Ge | 180      |

| 7.3   | Experimental Details                                                            |                             | 183      |

| 7.4   | Analytical Contact Model                                                        |                             | 185      |

| 7.5   | Applied Compressive Stress vs. External                                         | Torque                      | 187      |

| 7.6   | Effect of Compressive Stress and Temper                                         | ratures in Indentation      | 188      |

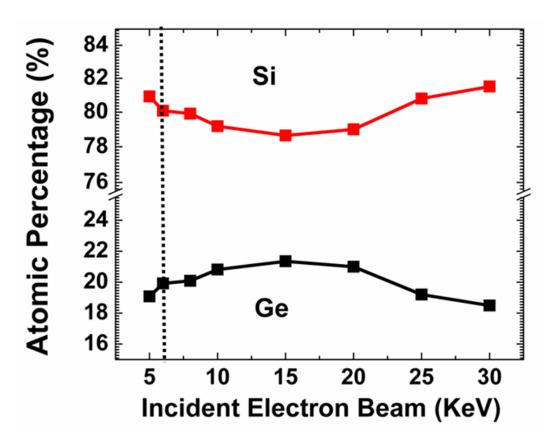

| 7.7   | EDX Calibration for Quantitative Compo                                          | ositional Analysis          | 190      |

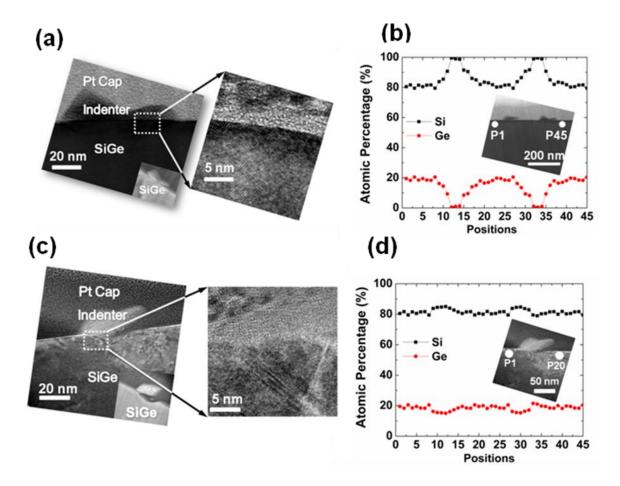

| 7.8   | Deformation and Characterizations                                               |                             | 192      |

| 7.9    | Conclusions                                                                 |

|--------|-----------------------------------------------------------------------------|

| Chapt  | ter 8 Conclusions                                                           |

|        | 8.1 Summary of Research and Future Work                                     |

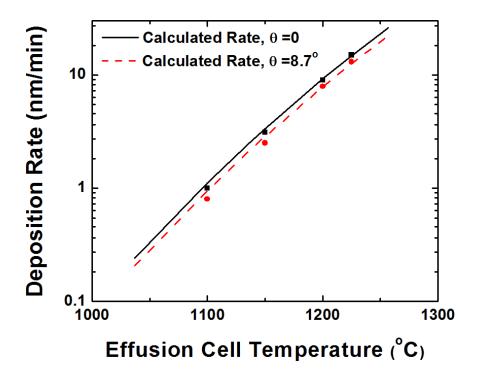

| APPE   | NDIX A MBE Calculated and Measured Deposition Rates                         |

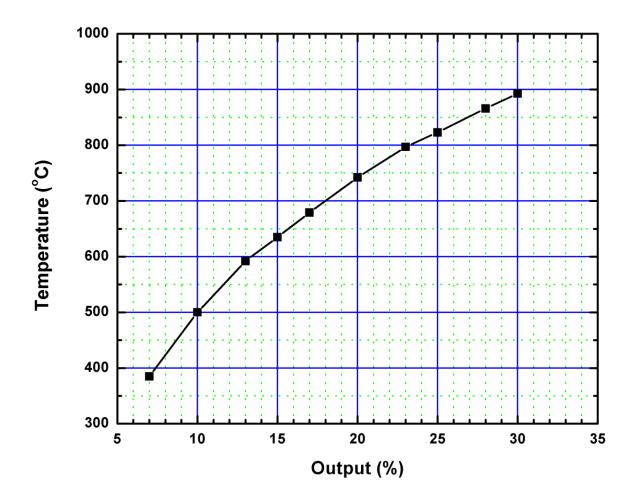

| APPE   | NDIX B MBE Substrate Heater Calibration                                     |

| APPE   | NDIX C Finite Element Modelling Using COMSOL Multiphysics201                |

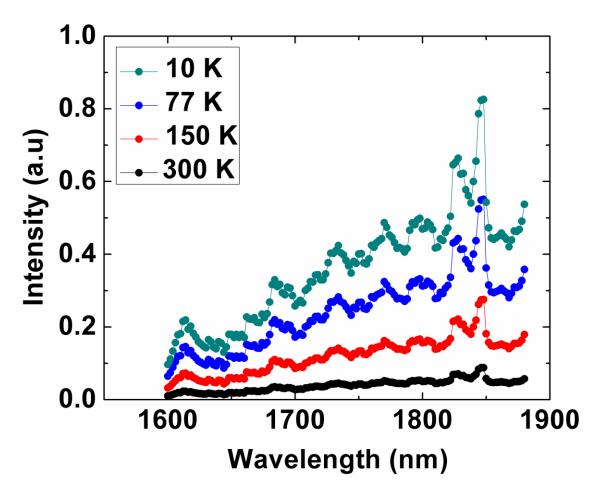

| APPE   | NDIX D Photoluminescnce Characterization of Ge-on-Si Films203               |

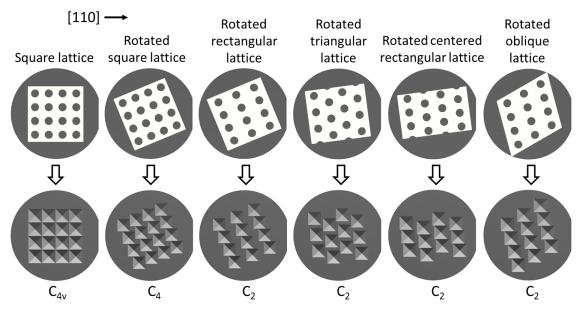

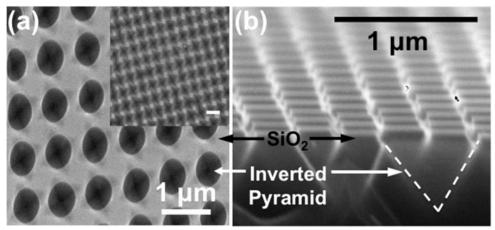

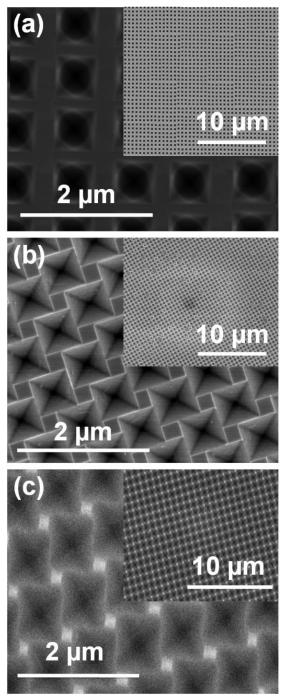

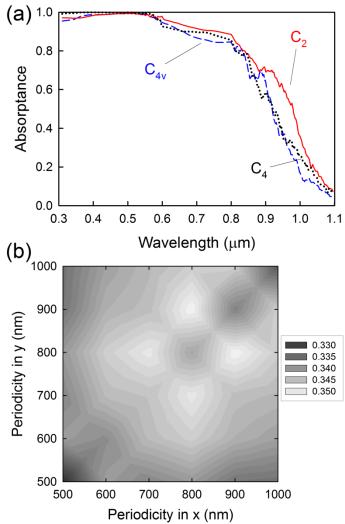

| APPE   | NDIX E Symmetry-Breaking Nanostructures on Crystalline Silicon for Enhanced |

| Light- | Trapping in Thin Film Solar Cells. 205                                      |

| Refere | ences                                                                       |

# LIST OF FIGURES

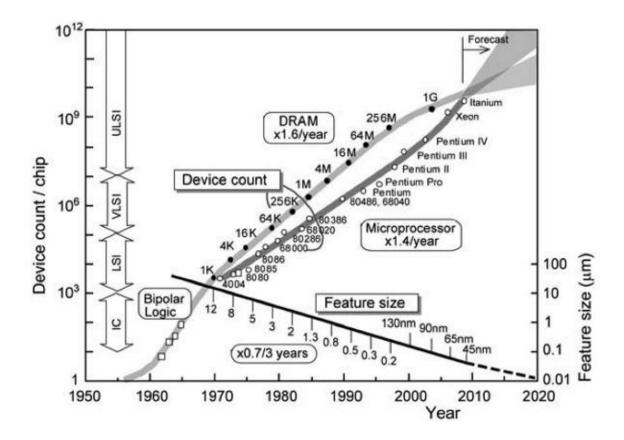

| Figure 1.1. Trends in device count/chip and feature size of MOS device, as a function of |

|------------------------------------------------------------------------------------------|

| the year of production2                                                                  |

| Figure 1.2: Schematic of n-MOSFET                                                        |

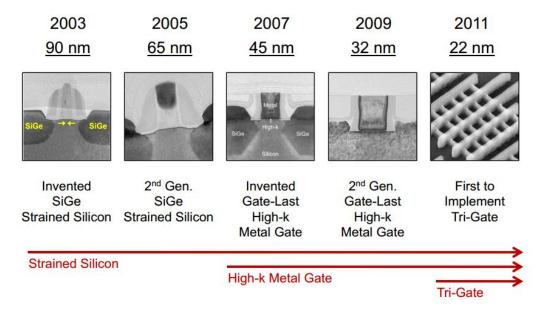

| Figure 1.3: Intel Si-Transistors Scaling and Roadmap until 2012                          |

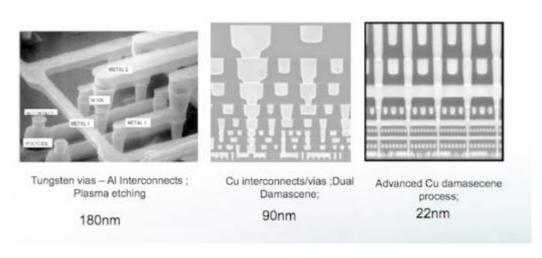

| Figure 1.4: Evolution of Metallization                                                   |

| Figure 1.5: MOSFET Transistor Scaling and Roadmap                                        |

| Figure 1.6: Components for Siliconization                                                |

| Figure 1.7: Carrier drift velocity (cm/s) as a function of electric field (V/cm)         |

| Figure 1.8: Band-diagram from source side to drain side under ballistic limit14          |

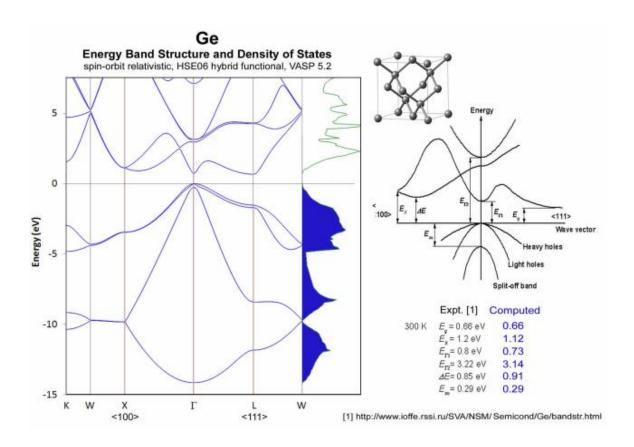

| Figure 1.9: Computed energy band structure and density of states at equilibrium of       |

| elemental Germanium                                                                      |

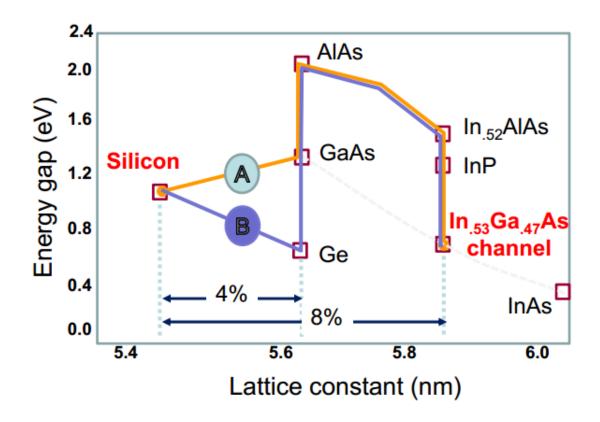

| Figure 1.10. Energy gap versus lattice constant for many important semiconductors.       |

| Especially important is the Ge-GaAs-AlAs system that is widely researched due to the     |

| similarity of the lattice constants of the materials                                     |

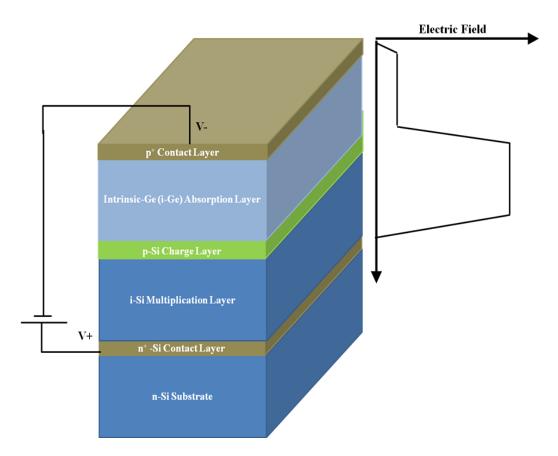

| Figure 1.11. Near-infrared avalanche photodetector fabricated from Germanium on Si       |

| substrate utilizing a Ge based absorption layer and a Si based carrier multiplication    |

| layer                                                                                    |

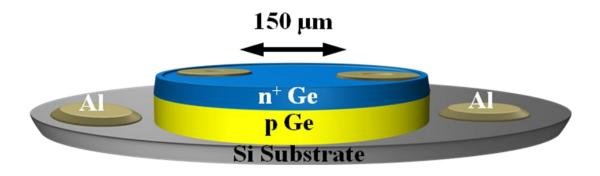

| Figure 1.12. Light emitting diode fabricated from Germanium on Si substrate utilizing a  |

| Ge based absorption layer and a Si based carrier multiplication layer. In this case Ge   |

| based devices can be used as a source.                                                   |

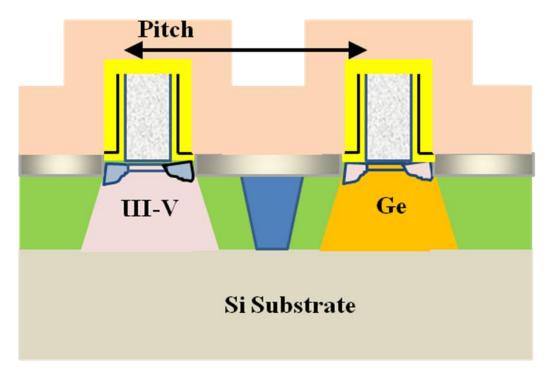

| Figure 1.13. High mobility complementary metal-oxide-semiconductor transistors            |

|-------------------------------------------------------------------------------------------|

| utilizing a Ge based p-metal oxide semiconductor and III-V n-metal oxide semiconductor    |

| structure on Si substrate                                                                 |

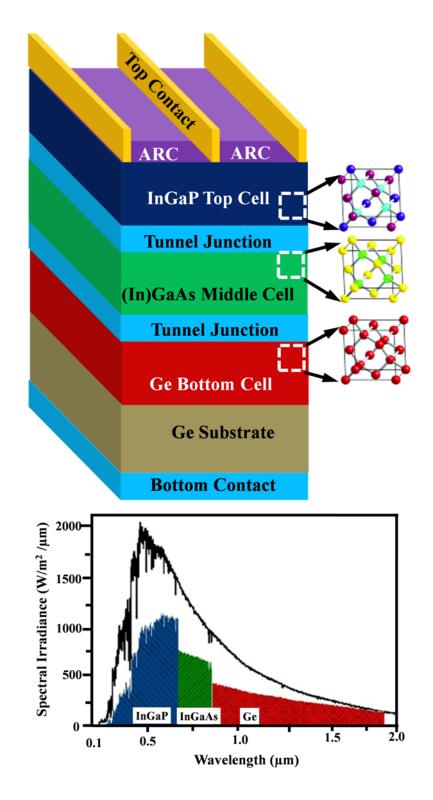

| Figure 1.14 Schematic of a triple junction solar cell. The cell consists of a series of   |

| layers in order of largest to smallest bandgap from top to bottom. Each layer collects a  |

| range of the solar spectrum shown in the inset at the lower right. The III-V layers are   |

| closely lattice matched to one another and to the Ge substrate                            |

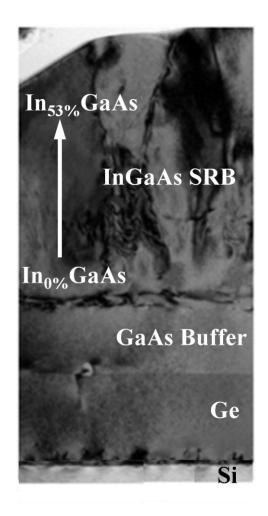

| Figure 1.15. Ternary III-V alloys integrated on GoS virtual substrate. The Ge is used as  |

| a buffer layer in between GaAs buffer and underlying Si substrate                         |

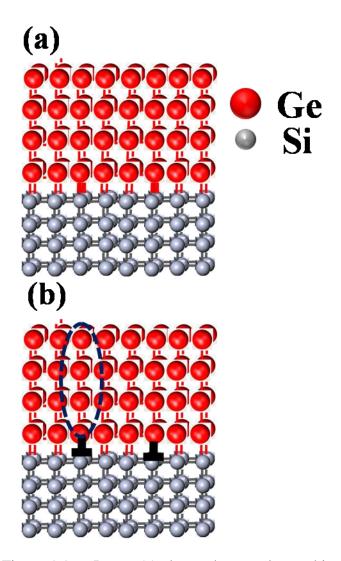

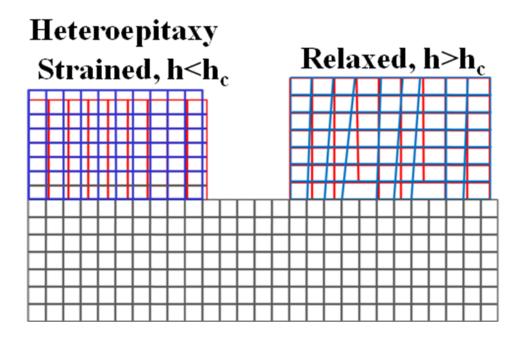

| Figure 1.16. Image (a) shows the pseudomorphic growth of Ge on Si. Image 1.16(b)          |

| shows the nucleation of a misfit dislocation to relieve the stress at larger Ge           |

| thickness                                                                                 |

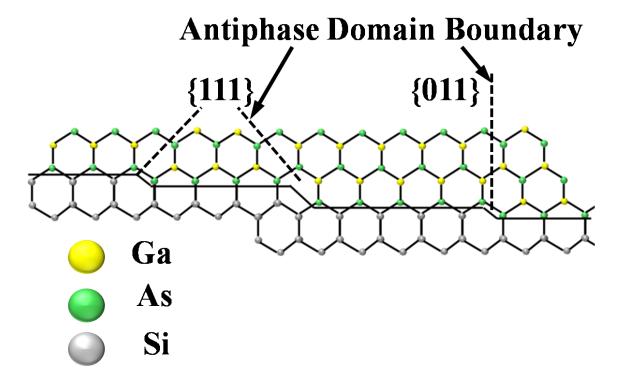

| Figure 1.17. Antiphase domain boundary that occurs from the epitaxial growth of a III-    |

| V semiconductor on group-IV materials such as Ge or Si in the presence of single height   |

| atomic steps                                                                              |

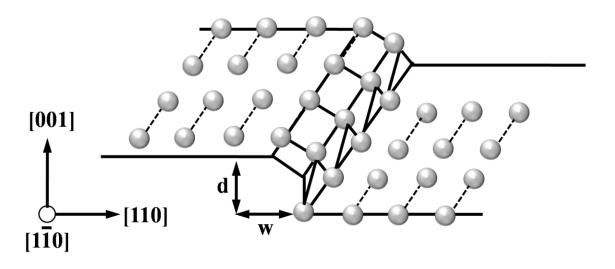

| Figure 1.18. Rendition of the double height step reconstruction that occurs on substrates |

| offcut by several degrees toward the [110] direction. The morphology suppresses the       |

| formation of anti-site defects occurring in zinc-blende epitaxy on diamond cubic          |

| materials                                                                                 |

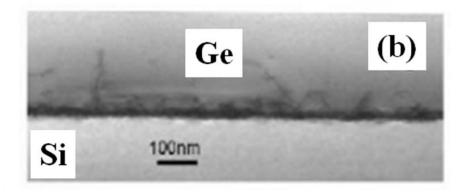

| Figure 1.19: (a) Cross-sectional TEM image of unannealed GoS layer. Misfit                |

| dislocations can b visible in the TEM image. (b) Cross-sectional TEM image of GoS         |

| layer grown using MHAH method. Dislocations are mostly confined at the Ge/Si              |

| interface 37                                                                              |

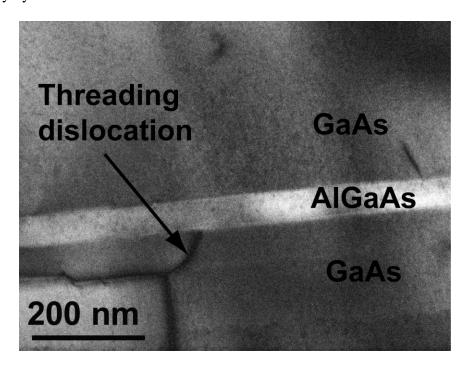

| Figure 1.20: The principal of strained layer defect filtering is illustrated in the                                                                                                                                                                                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| transmission electron microscope image of an $Al_{0.3}Ga_{0.7}As$ -GaAs structure. The stress                                                                                                                                                                                                                                           |

| field of the $Al_{0.3}Ga_{0.7}As$ layer repels the stress field associated with the threading                                                                                                                                                                                                                                           |

| dislocation and bends it into the (001) growth plane                                                                                                                                                                                                                                                                                    |

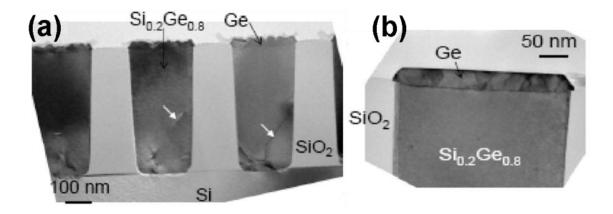

| Figure 1.21. Heteroepitaxial growth selectively takes place within the patterned trenches                                                                                                                                                                                                                                               |

| and traps threading dislocations between the SiO <sub>2</sub> walls leading to high-quality material                                                                                                                                                                                                                                    |

| near the tops of the trenches. Coalescence of adjacent trenches, however, can lead to the                                                                                                                                                                                                                                               |

| nucleation of additional defects. In addition, the mask material itself may induce defects                                                                                                                                                                                                                                              |

| as the epitaxial film grows laterally over the mask regions                                                                                                                                                                                                                                                                             |

| Figure 1.22. Finite element model showing the deformation of lattice planes occurring in                                                                                                                                                                                                                                                |

| the tensile strained heteroepitaxial island and within the compressively stained                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                         |

| substrate                                                                                                                                                                                                                                                                                                                               |

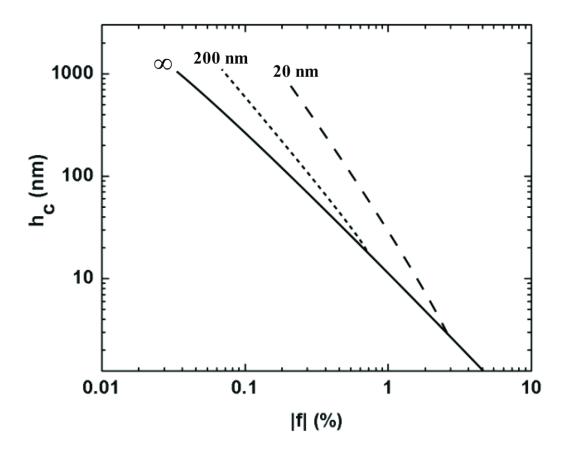

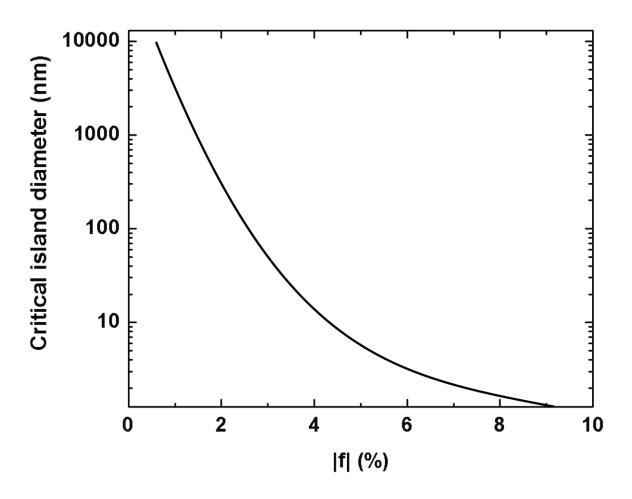

| Figure 1.23. Critical thickness versus lattice mismatch based on Matthew's total energy                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                         |

| Figure 1.23. Critical thickness versus lattice mismatch based on Matthew's total energy                                                                                                                                                                                                                                                 |

| Figure 1.23. Critical thickness versus lattice mismatch based on Matthew's total energy calculation. The solid line is Matthew's result for a planar film in contact with the                                                                                                                                                           |

| Figure 1.23. Critical thickness versus lattice mismatch based on Matthew's total energy calculation. The solid line is Matthew's result for a planar film in contact with the substrate. The dotted and dashed lines represent an island of 200 and 20 nm,                                                                              |

| Figure 1.23. Critical thickness versus lattice mismatch based on Matthew's total energy calculation. The solid line is Matthew's result for a planar film in contact with the substrate. The dotted and dashed lines represent an island of 200 and 20 nm, respectively, in contact with the substrate based on Luryi and Suhir's model |

| Figure 1.23. Critical thickness versus lattice mismatch based on Matthew's total energy calculation. The solid line is Matthew's result for a planar film in contact with the substrate. The dotted and dashed lines represent an island of 200 and 20 nm, respectively, in contact with the substrate based on Luryi and Suhir's model |

| Figure 1.23. Critical thickness versus lattice mismatch based on Matthew's total energy calculation. The solid line is Matthew's result for a planar film in contact with the substrate. The dotted and dashed lines represent an island of 200 and 20 nm, respectively, in contact with the substrate based on Luryi and Suhir's model |

| Figure 1.23. Critical thickness versus lattice mismatch based on Matthew's total energy calculation. The solid line is Matthew's result for a planar film in contact with the substrate. The dotted and dashed lines represent an island of 200 and 20 nm, respectively, in contact with the substrate based on Luryi and Suhir's model |

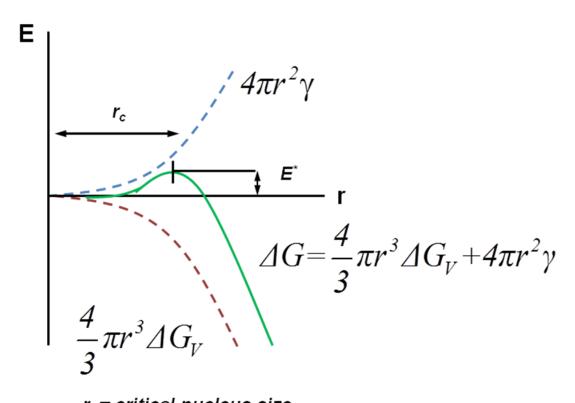

| Figure 2.3: A plot showing activation energy for nucleation ( <i>E</i> ) as a function of    |

|----------------------------------------------------------------------------------------------|

| nucleation size (r)                                                                          |

| Figure 2.4: The three modes of epitaxy, 4-2(a) Volmer-Weber growth , (b) Frank-van der       |

| Mere, (c) Stranski-Krastanov51                                                               |

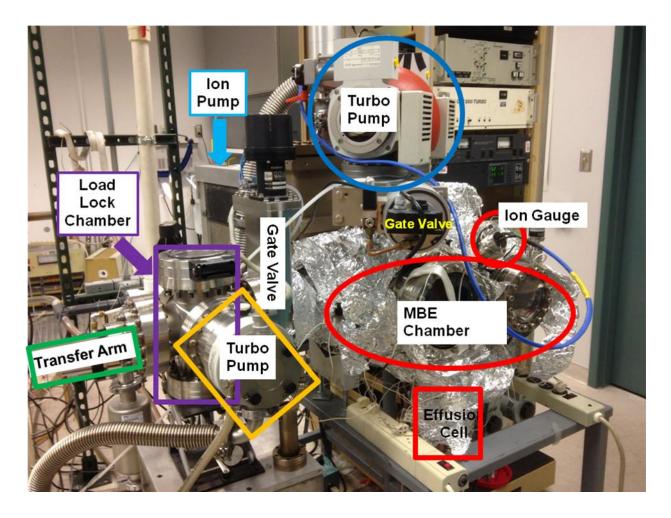

| Figure 2.5: The molecular beam epitaxy vacuum chamber system used in this work with          |

| major components labeled                                                                     |

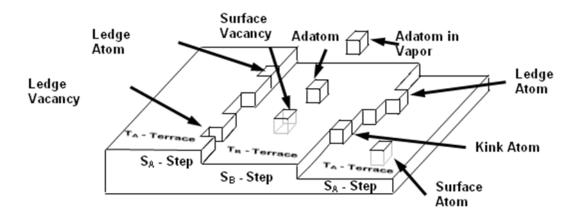

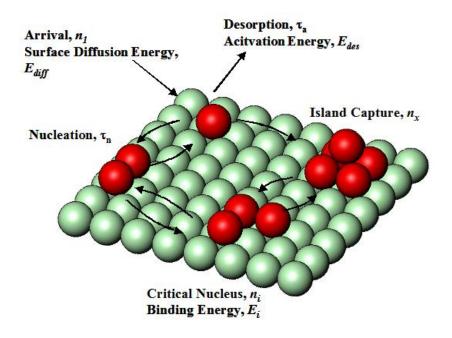

| Figure 2.6: Depiction of the atomic processes occurring on a surface due to impingement      |

| of atoms from an evaporation source. The notation used in developing atomistic               |

| nucleation theory is also shown for each process                                             |

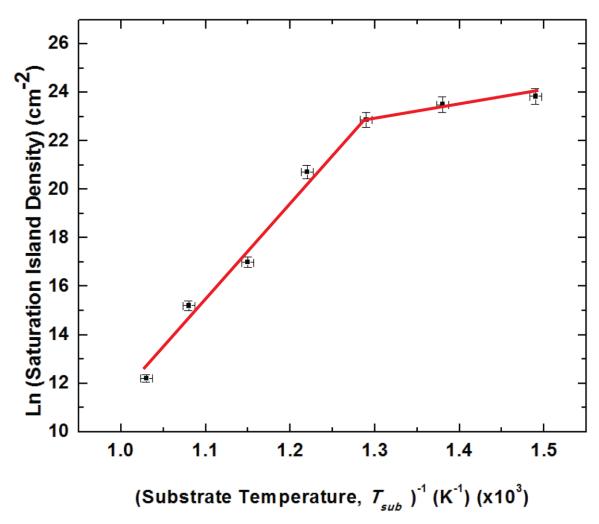

| Figure 2.7: Natural log of the saturation nucleation density versus reciprocal substrate     |

| temperature. This plot reveals two distinct slopes that occur over the temperature           |

| intervals of 673 to 773 K and 773 to 973 K, and this graph is used to extract the activation |

| energies involved in the nucleation process                                                  |

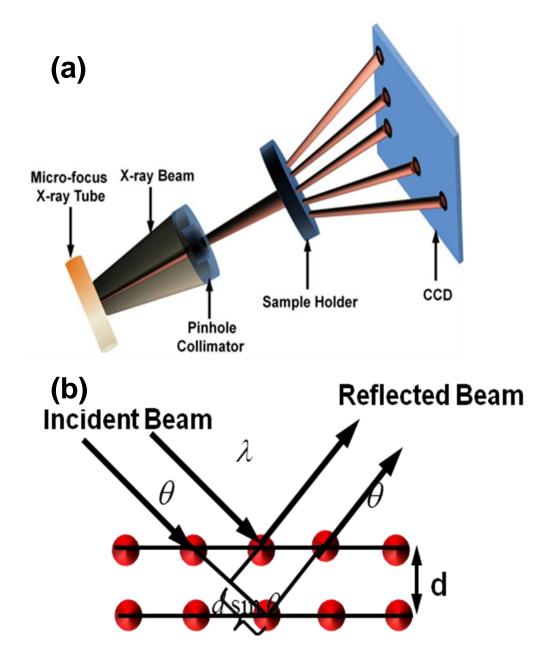

| Figure 3.1: (a) A 3D view of x-ray diffraction set-up. The x-ray is being generated from a   |

| x-ray tube, passing through pinhole collimator, and sample, and ultimately hitting the       |

| CCD screen. The diffraction spots are generated on the screen. (b) a schematic showing       |

| how x-ray interact with atoms in a crystal                                                   |

| Figure 3.2: A schematic illustrating a phenomenon called photoelectric effect, which is      |

| the key for x-ray photoelectron spectroscopy                                                 |

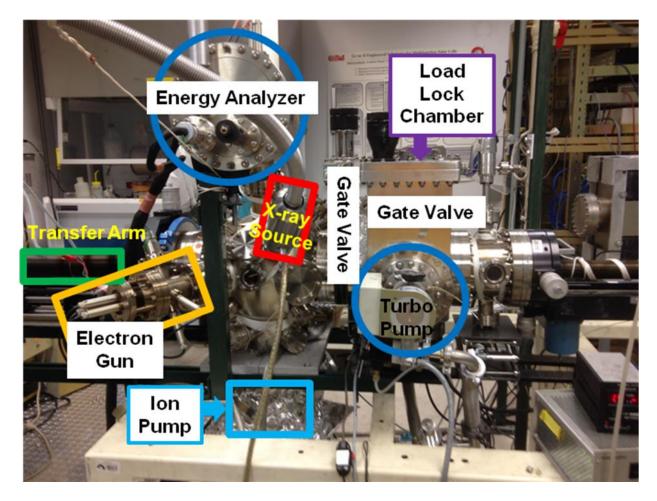

| Figure 3.3: An experimental set-up of x-ray photoelectron spectroscopy system73              |

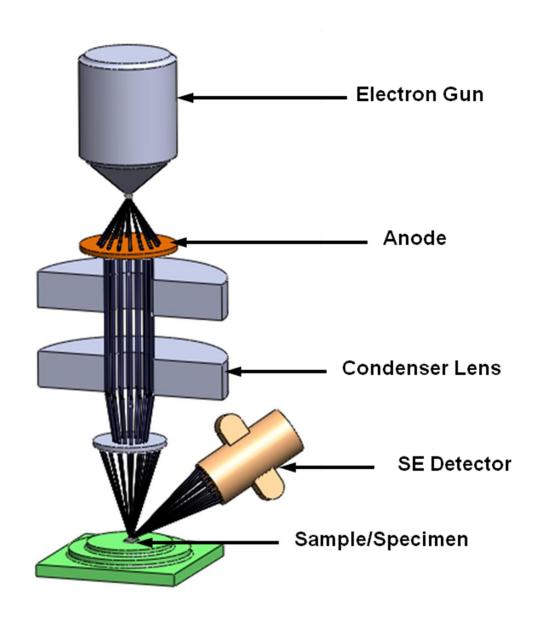

| Figure 3.4: A 3D cut-out view of scanning electron microscope                                |

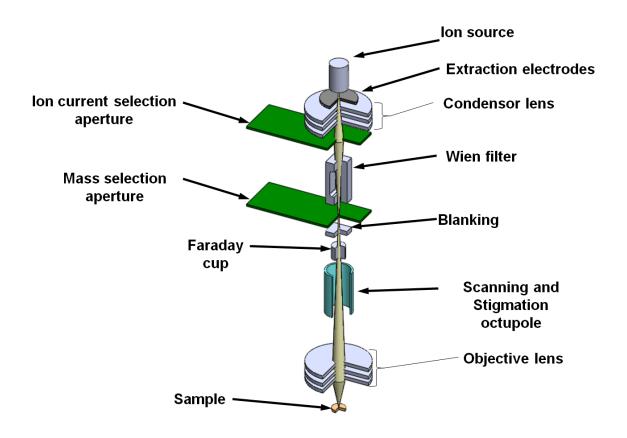

| Figure 3.5: A 3D cut-out view of focused ion beam instrument                                 |

| Figure 3.6: A 3D cut-out view of transmission electron microscope instrument78                                                                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.7: A schematic of energy dispersive microscopy technique80                                                                                                                         |

| Figure 3.7: A schematic diagram of secondary ion mass spectrometry method. The                                                                                                              |

| primary ion beam is shown in yellow, and secondary ions are shown in purple. Postive                                                                                                        |

| and negative ions and electrons are being produced during this process                                                                                                                      |

| Figure 3.8: A 3D view of heteroepitaxial layer involving etch pits. These pits correspond                                                                                                   |

| to threading defects or stressed region in the epitaxial layer. EPD allows us to count the                                                                                                  |

| density of threading dislocation in a large area                                                                                                                                            |

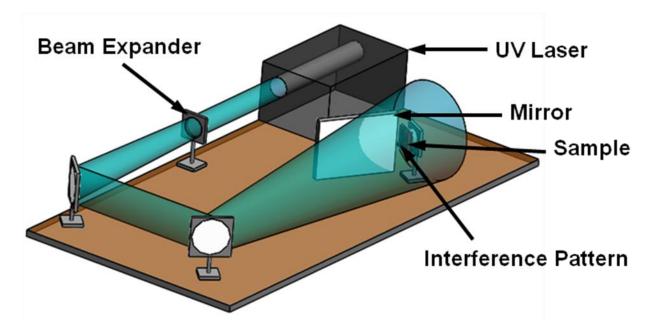

| Figure 3.9: A 3D view of the interferometric lithography experimental setup and                                                                                                             |

| operating principle85                                                                                                                                                                       |

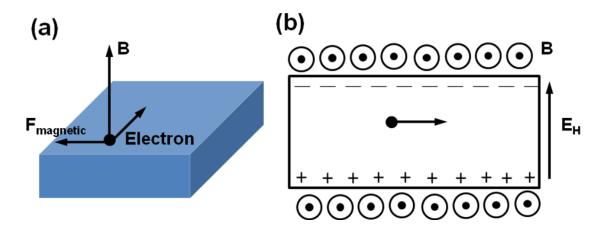

| Figure 3.10: (a) A moving electron on the conductor that experiences a magnetic field B.                                                                                                    |

| (b) A separation of charges occur because of the moving electrons under magnetic force.                                                                                                     |

| A Hall voltage is generated because of this effect                                                                                                                                          |

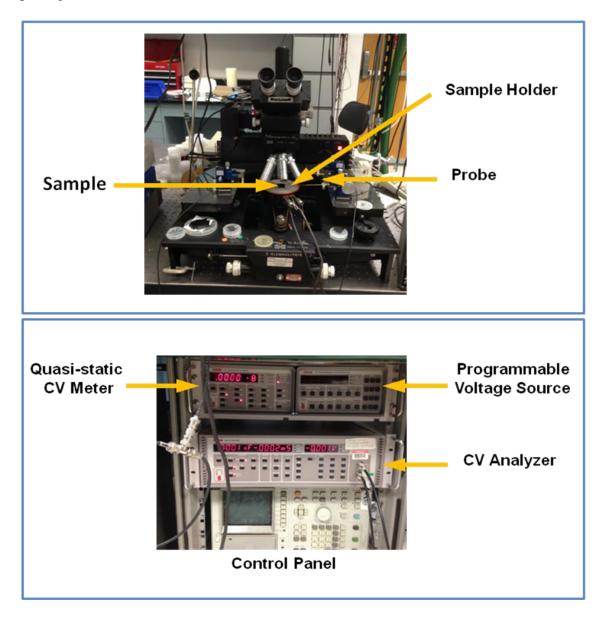

| Figure 3.11: An experimental set-up of capacitance-voltage measurement system88                                                                                                             |

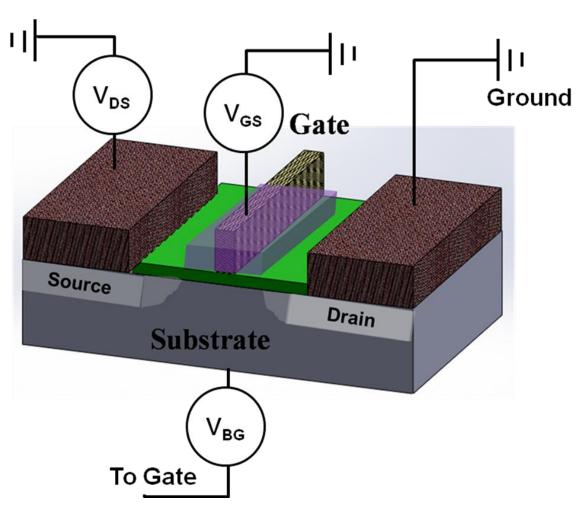

| Figure 3.12: Schematic of electrical characterization of a field effect transistor device.                                                                                                  |

| Four probes are used, one for back gate, one for top gate and other two for source and                                                                                                      |

| drain contacts90                                                                                                                                                                            |

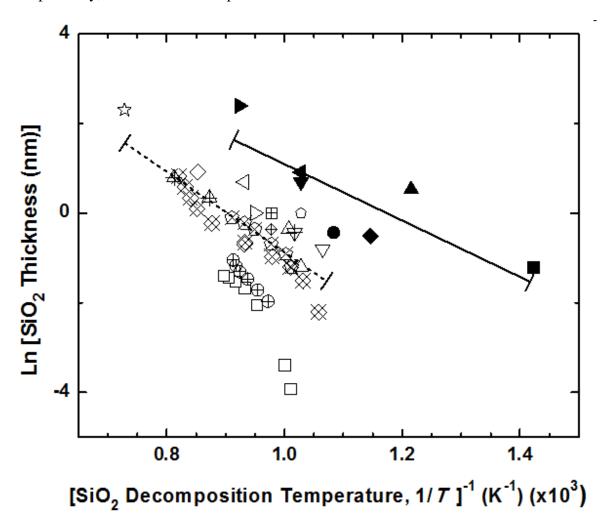

| Figure 4.1: Natural log of SiO <sub>2</sub> thickness versus inverse temperature of the SiO <sub>2</sub>                                                                                    |

| decomposition. The broken line is a linear fit to the data without a Ge vapor flux (open                                                                                                    |

| symbols). The solid line is a linear fit showing the same trend but shifted to lower                                                                                                        |

| temperatures in the presence of a vapor flux of Ge or Si atoms (closed symbols). Data                                                                                                       |

| points are referenced as follows: $(\blacksquare);^{124}(\bullet);^{133}(\blacktriangledown);^{135}(\blacktriangleleft);^{127}(\blacktriangleright);^{133}(\Lambda);^{126}(\forall);^{140}$ |

| $(8);^{129}(X);^{134}(M)^{127}\ (\Xi);^{139}\ (\chi);^{132}\ (\psi);^{132}(\Box);^{132}(\Xi);^{141}\ (/);^{130}(:);^{128}\ (E);^{125}(O);^{132}(\Box);^{139} and$ |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ( $\Pi$ ) <sup>131</sup> (taken from PhD thesis of Darin L <sup>95</sup> )                                                                                        |

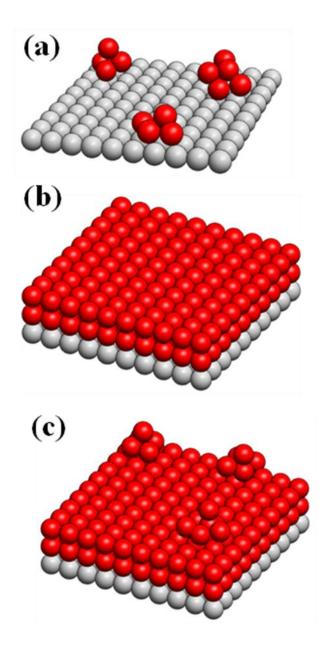

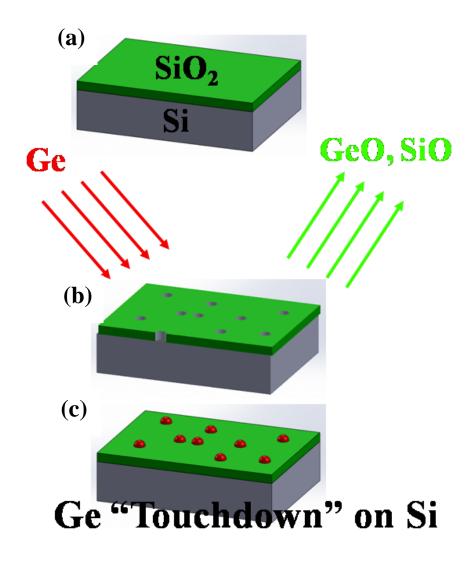

| Figure 4.2: A schematic illustrating the process from void nucleation and growth to Ge                                                                            |

| island formation. Shown in 4.2(a) is a surface of Si substrate with chemically grown                                                                              |

| oxide on it. Images in 4.2(b) show the process of void formation in the Si-SiO <sub>2</sub> interface                                                             |

| toward the SiO <sub>2</sub> surface. In 4.2(c), Ge selectively nucleates and grows on the newly                                                                   |

| exposed Si within the void openings                                                                                                                               |

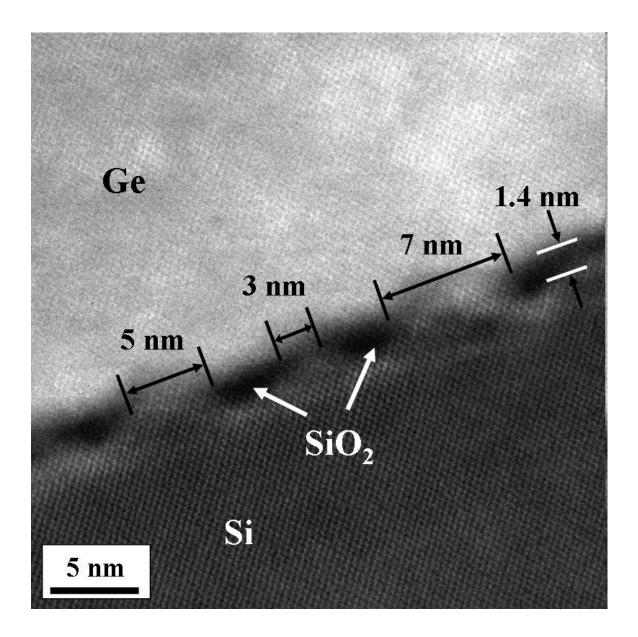

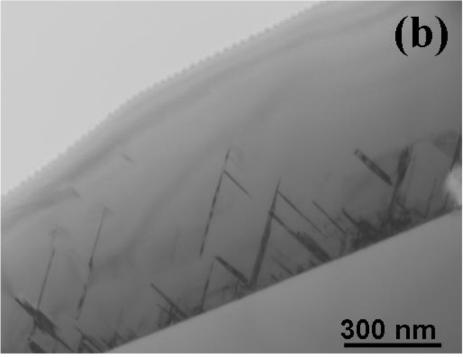

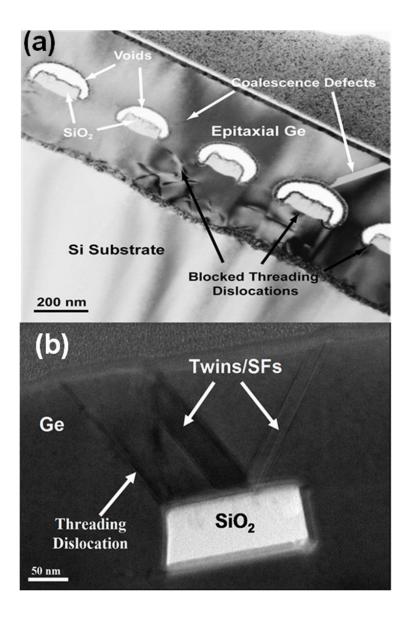

| Figure 4.3. High resolution cross-sectional transmission electron micrograph showing                                                                              |

| the Ge/SiO <sub>2</sub> /Si interface. Voids of 3 to 7 nm in diameter are created in the SiO <sub>2</sub> where                                                   |

| Ge subsequently nucleates and grows as islands                                                                                                                    |

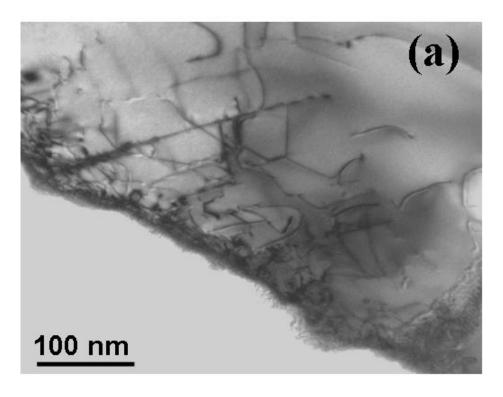

| Figure 4.4: Low-resolution transmission electron micrographs, 4.4(a) Ge grown directly                                                                            |

| on on Si substrate leading to a large density of threading dislocations, and 4.4(b) Ge                                                                            |

| grown on chemically oxidized Si substrate through touchdown method and having a large                                                                             |

| density of stacking faults, many of which terminate within 200 nm of the interface103                                                                             |

| Figure 4.5: (a) a high-resolution cross-sectional transmission electron microscope image                                                                          |

| of 12-nm of Ge deposited on Si substrate sample, where the Ge islands have just started                                                                           |

| to coalescence. A Ge island which is nucleated in a twin relationship to the underlying Si,                                                                       |

| shown in the right. This has led to a coherent twin boundary at the junction with the                                                                             |

| epitaxial Ge island on the left. The magnified filtered image of twin boundary is shown                                                                           |

| in the inset. The diffraction patterns of the islands and substrate are also included as                                                                          |

| insets. (b) a schematic illustrating a coherent and incoherent twin boundary106                                                                                   |

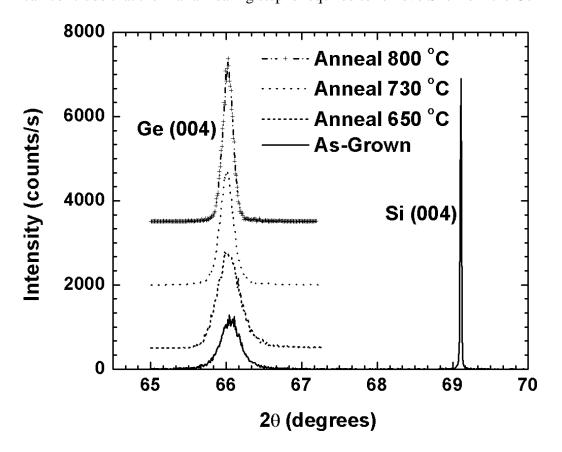

| Figure 4.6: The x-ray diffraction peaks of the (004) reflection of Ge films that are                          |

|---------------------------------------------------------------------------------------------------------------|

| (bottom to top) unannealed (solid line), annealed at 923 (dotted line), 1003 (dashed line),                   |

| and 1073 K (dot-dashedline)                                                                                   |

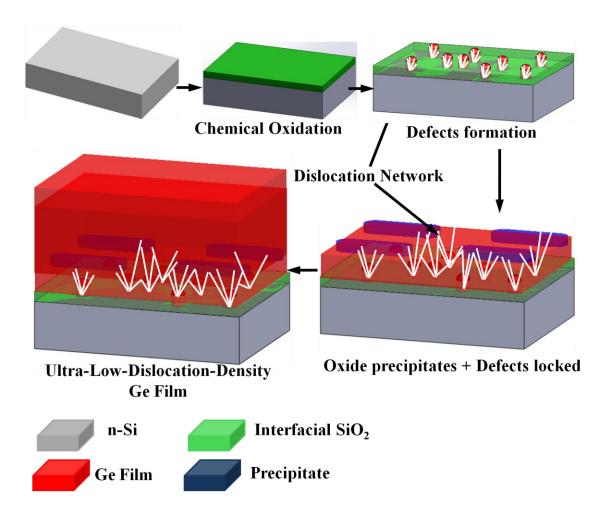

| <b>Figure 4.7:</b> Dislocation locking by oxide precipitates and phosphorus impurities in Ge                  |

| growth on n-type Si susbtarte. The precipitate blocks are shown by dark blue colors. The                      |

| final Ge film surface shows no defects                                                                        |

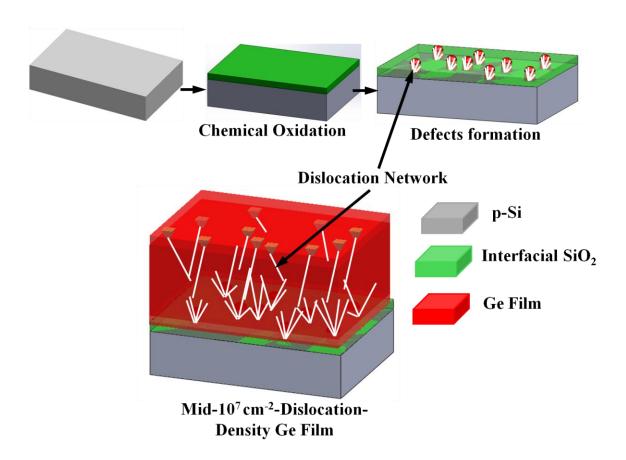

| Figure 4.8 No Dislocation locking by oxide precipitates and born impurities in Ge growth                      |

| on p-type Si substrate. The precipitates are missing in this growth process. The dark                         |

| cross mark on the schematic represents that this particular step is missing from the entire                   |

| growth process. The final Ge film surface show a significant density of threading                             |

| defects                                                                                                       |

| Figure 4.9: (a) XRD intensity of Ge(004), Si(004), and Ge(331) peaks for n-type GoS                           |

| substrate. (Inset) SEM images of etch pits on n-type surface. (b) XRD intensity of                            |

| Ge(004), Si(004), and Ge(331) peaks for p-type GoS substrate. (Inset) SEM images of                           |

| etch pits on p-type surface                                                                                   |

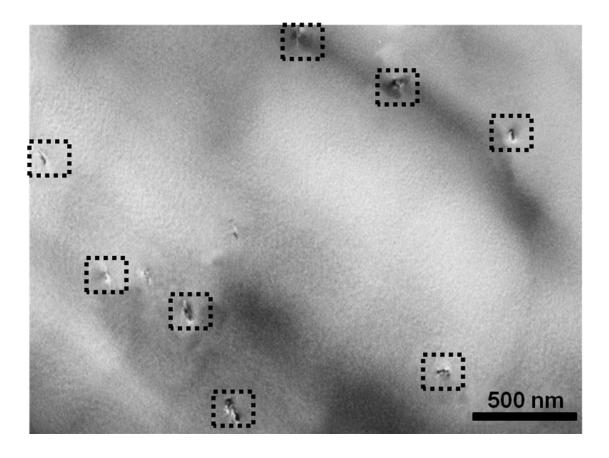

| Figure 4.10 : The TEM characterization show TDD on the order of $\sim 10^5$ cm <sup>-2</sup> . Oxide          |

| precipitates tend to lock dislocations                                                                        |

| Figure 4.11 : The TEM characterization show TDD on the order of $\sim 5 \times 10^7$ cm <sup>-2</sup> . Oxide |

| precipitates is absent in this p-type GoS, and no locking mechanism occurs in this type of                    |

| growth                                                                                                        |

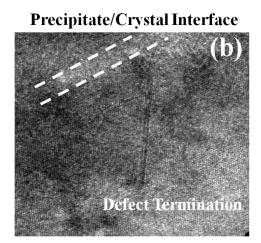

| Figure 4.12: (a) A magnified view of a oxide precipitate region in a n-type Ge epilayer.                      |

| Inset shows a FFT image of oxide precipitate. Extra set of weak diffraction spots are                         |

| observed, that arise from polycrytallinity of oxide precipitate. (b) A magnified view of           |

|----------------------------------------------------------------------------------------------------|

| oxide precipitate which is terminating a defect lines                                              |

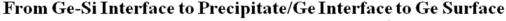

| Figure 4.13: A series of nano-probe EDX images, (a) right at Ge-Si interface, (b)at oxide          |

| precipitate-Ge-crytsal interface, and (c) at slightly above the oxide precipitate118               |

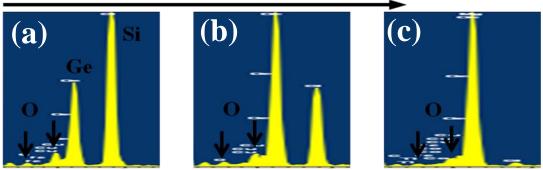

| Figure 4.14: SIMS spectrums of n-type and p-type GoS substrates. The blue line                     |

| represents concentration of Ge in GoS substrate, which is maximum. The O                           |

| concentration for p- and n-type GoS substrates are shown here. The O concentration in              |

| p-type is higher than that of in n-type, causing more defects in the p-type GoS                    |

| substrate                                                                                          |

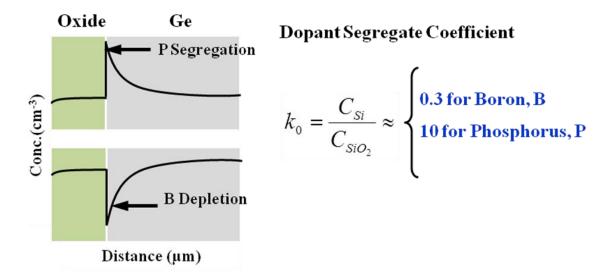

| Figure 4.15: Phosphorus atoms preferentially segregate at oxide-Ge interface. In contrst,          |

| B atoms don't segregate at the oxide-Ge inetrface. The phosphorus segregation results to           |

| dislocation locking at the Ge epilayer                                                             |

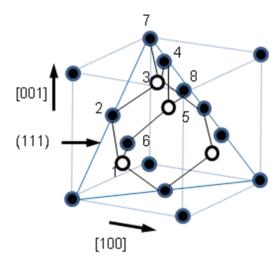

| Figure 4.16: a characteristic hexa-ring (six-atom ring) in the diamond lattice structure of        |

| Ge, represented by atom numbers 1, 2, 3, 4, 5, and 6.                                              |

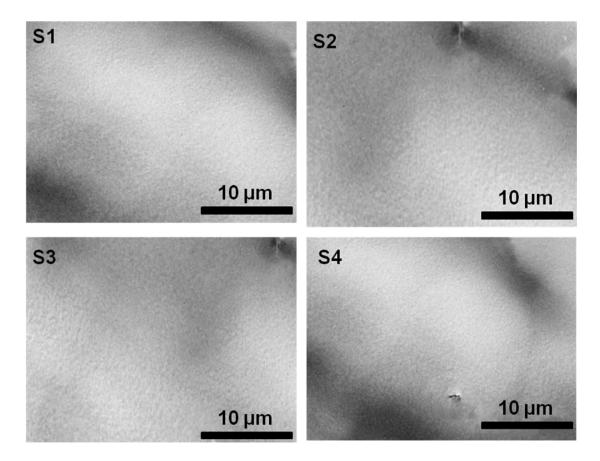

| Figure 4.17: Plan-view transmission electron micrograph images showing almost no                   |

| dislocations in a n-type GoS film. S1, S2, S3 and S4 show four different parts of the              |

| sample. This enables us to get a good statistical estimation about the total TDD124                |

| Figure 4.18: Plan-view transmission electron micrograph showing dislocations in a p-               |

| type GoS film                                                                                      |

| Figure 5.1: TEM images of (a) Ge forms a void over the SiO <sub>2</sub> template while epitaxially |

| grown on GoS. The template filters threading dislocations. (b) Ge grown in direct contact          |

| with the template over GoS                                                                         |

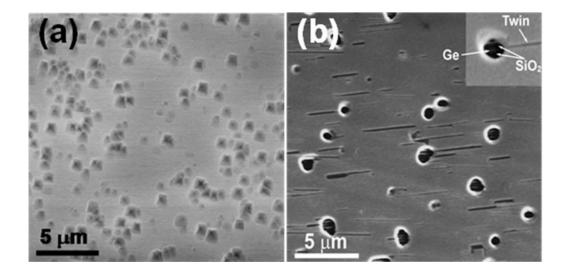

| Figure 5.2: (a) Scanning electron micrograph of annealed GoS film etched for 30 s                         |

|-----------------------------------------------------------------------------------------------------------|

| revealing square shaped etch pits. (b) Scanning electron micrograph of epitaxial Ge film                  |

| grown via SiO2 trenches on GoS film etched for 30 s revealing etch pits                                   |

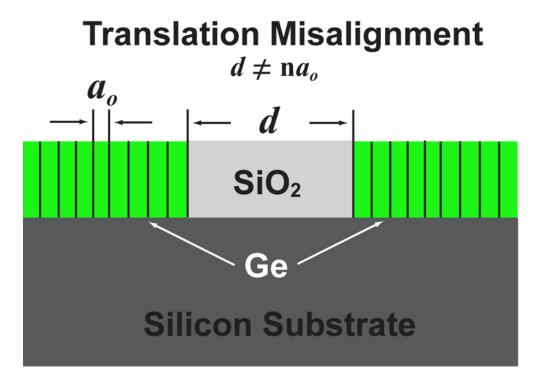

| Figure 5.3: Potential misalignment of Ge islands that leads to defect formation upon coalescence          |

| substarte (b) Ge forms a void over the $SiO_2$ template while epitaxially grown on $GoS$ (c)              |

| Ge grown laterally in contact with the SiO <sub>2</sub> template over GoS                                 |

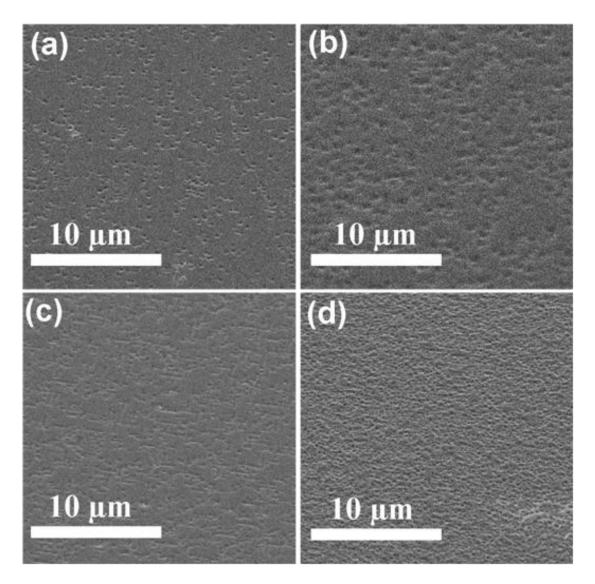

| Figure 6.1: Scanning electron micrograph images of etch pits formed in the Ge film                        |

| epitaxially grown on SI-Si film (a) with dislocation density of $2x10^7$ cm <sup>-2</sup> (Sample A) (b)  |

| with dislocation density of $5x10^7$ cm <sup>-2</sup> (Sample B) (c) with dislocation density of $7x10^7$ |

| cm <sup>-2</sup> 142                                                                                      |

| Figure 6.2: Scanning electron micrograph images of etch pits formed in the Ge film                        |

| epitaxially grown on SI-Si film (a) with dislocation density of $2x10^7 \text{ cm}^{-2}$ (Sample A) (b)   |

| with dislocation density of $5x10^7$ cm <sup>-2</sup> (Sample B) (c) with dislocation density of $7x10^7$ |

| cm <sup>-2</sup> 143                                                                                      |

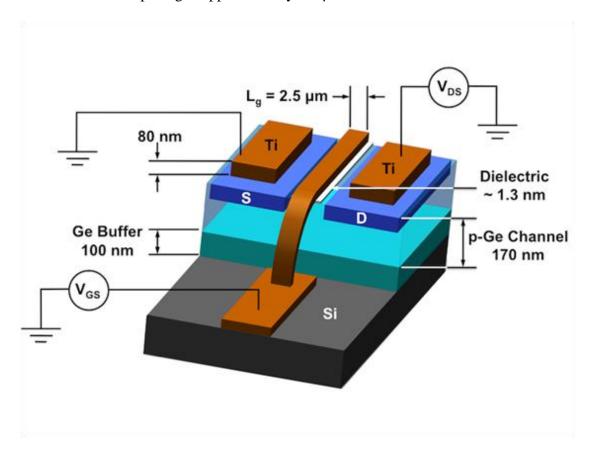

| Figure 6.3: Schematic diagram of p-channel MESFETs with 2.5-µm gate length                                |

| fabricated on epitaxially grown Ge on SI-Si substrates, using a 200 mm Si compatible                      |

| process flow                                                                                              |

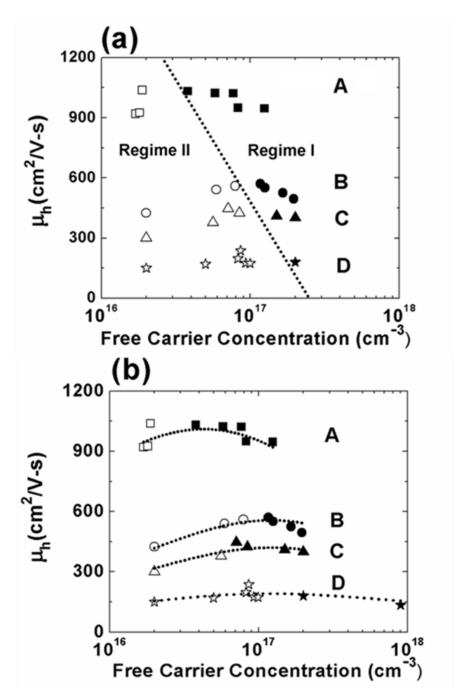

| Figure 6.4: (a) Hole mobility $(\mu_h)$ as a function of net free carrier concentration in p-GoS          |

| films. Two types of symbols are used to represent the specific transport characteristics of               |

| four different p-GoS samples. The open symbols are used to represent Regime II for                        |

| Samples A-D, where the mobility is largely determined by dislocation scattering. The                      |

| solid symbols are used to represent Regime I for Samples A-D, where the mobility is                       |

| largely determined by ionized impurity scattering. (b) shows the comparison between                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------|

| experimental data and analytical model for the mobility. The model tracks the                                                              |

| experimentally measured mobility (Regime I and II) very well for Sample A, but the                                                         |

| goodness of fit decreases with increasing TDD                                                                                              |

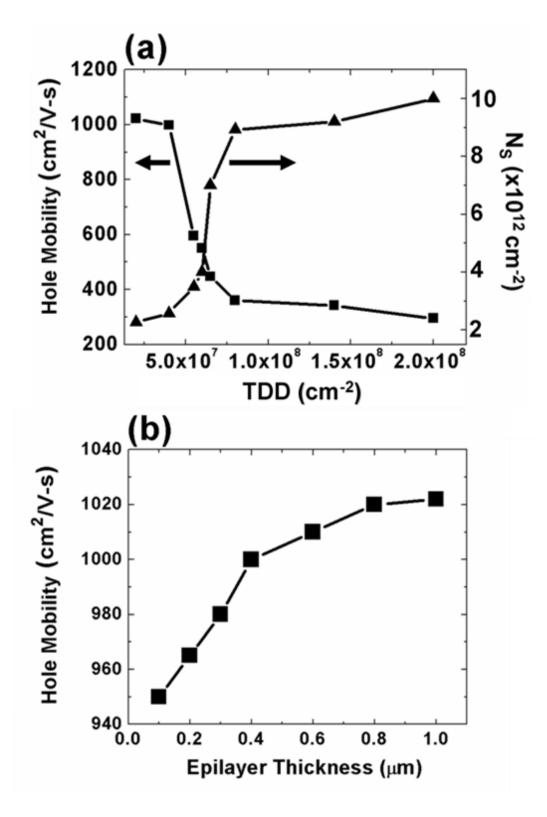

| Figure 6.5: (a) Hole mobility ( $\mu h$ ) and sheet-carrier density (NS) measured by Hall                                                  |

| measurement at room temperature as a function of dislocation density. (b) The hole                                                         |

| mobility (µh) measured as a function of the epilayer thickness                                                                             |

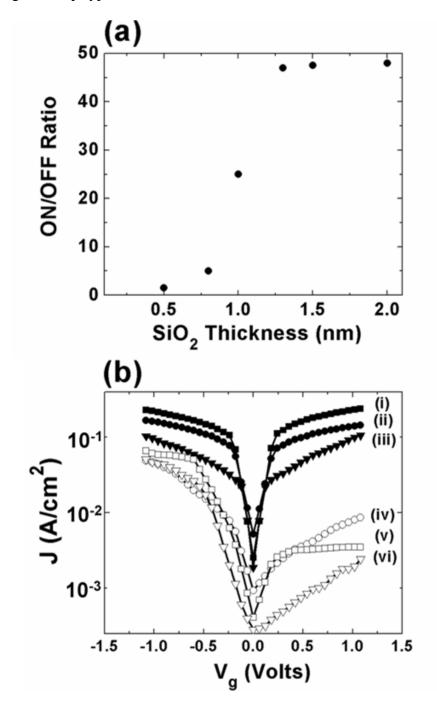

| Figure 6.6: (a) The room temperature ON/OFF ratio (forward to reverse current density                                                      |

| ratio) from Ti/SiO <sub>2</sub> /p-GoS Schottky diode stack on Sample A as a function of varying                                           |

| SiO <sub>2</sub> thickness. (b) Forward-bias and reverse-bias Schottky characteristics with three                                          |

| different dielectric layers (i.e., SiO <sub>2</sub> , Al <sub>2</sub> O <sub>3</sub> and HfO <sub>2</sub> ). (i)-(iii) represent Schottky  |

| characteristics from Sample D, and (iv)-(vi) represent Schottky characteristics from                                                       |

| Sample A                                                                                                                                   |

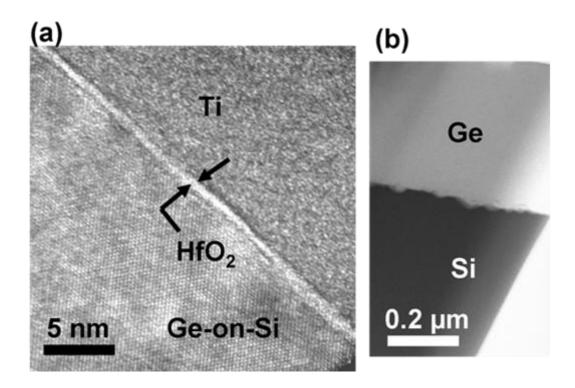

| Figure 6.7: (a) High-resolution, cross-sectional TEM image of Ti/1.3-nm HfO <sub>2</sub> /p-GoS                                            |

| stack and (b) corresponding STEM image                                                                                                     |

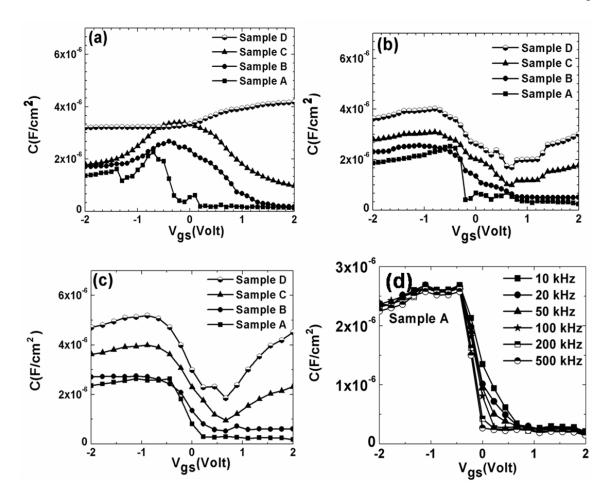

| Figure 6.8: C-V characteristics of Ti/1.3-nm dielectric/p-GoS Schottky contacts for                                                        |

| Samples A-D with three different dielectric layers: (a) SiO <sub>2</sub> , (b) Al <sub>2</sub> O <sub>3</sub> , and (c) HfO <sub>2</sub> . |

| The C-V characteristics are obtained using split C-V technique. The $C_{HF}$ is obtained at                                                |

| 100 kHz                                                                                                                                    |

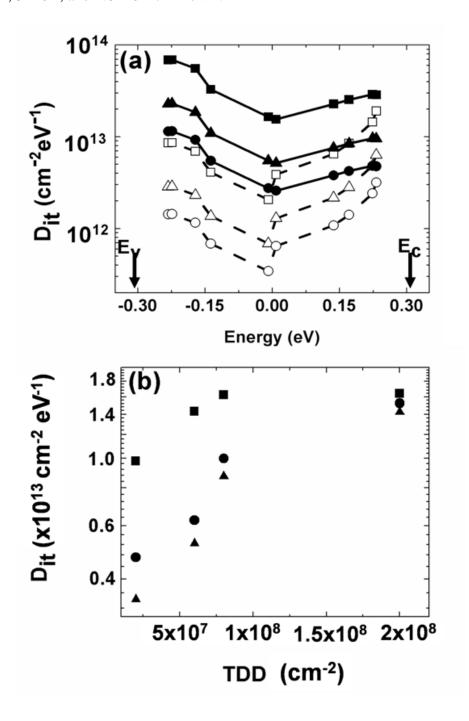

| Figure 6.9: (a) $D_{it}$ as a function of Ge energy surface potential before and after FGA at                                              |

| 350 °C for 15 min. The energy surface potential axis is labeled with the convention that                                                   |

| 0.0 V represents the mid-gap position (Ei), -0.33 V represents the VB edge and 0.33 V                                                      |

| represents the CB edge. Do levels for three different dielectric layers are shown in the                                                   |

| image. (b) Near-VB-edge $D_{it}$ as a function of defect density for SiO <sub>2</sub> , Al <sub>2</sub> O <sub>3</sub> and |

|----------------------------------------------------------------------------------------------------------------------------|

| HfO <sub>2</sub> 162                                                                                                       |

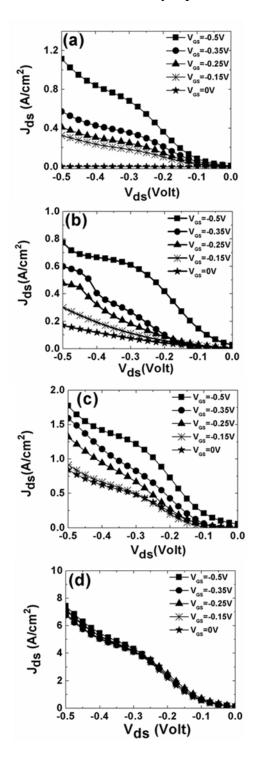

| Figure 6.10: Figures 6.10 (a-d) correspond to the $J_{ds}$ – $V_{ds}$ characteristics obtained from                        |

| four different TDD samples (Samples A-D). The gate bias is increased from 0 to -0.5 $\mathrm{V}$                           |

| at 0.1 V steps                                                                                                             |

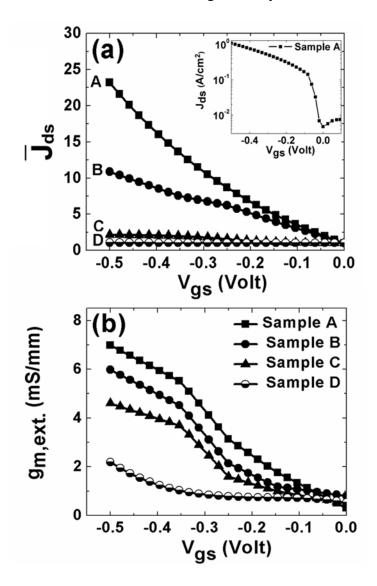

| Figure 6.11: (a) Normalized vs. $V_{gs}$ . Inset shows $J_{ds} - V_{gs}$ characteristics obtained from                     |

| Sample A with HfO <sub>2</sub> interfacial layer. (b) $g_{m,ext} vs. V_{gs}$ for Samples A-D. $V_{ds}$ is biased at        |

| -0.4 V to be in the saturation region. These measurements are performed at 300 K166                                        |

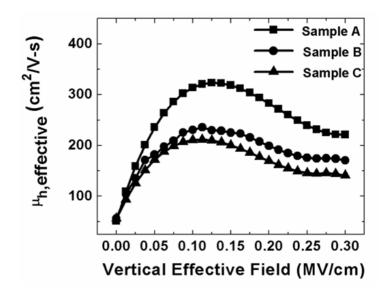

| Figure 6.12: Effective hole mobility as a function of vertical electric                                                    |

| field                                                                                                                      |

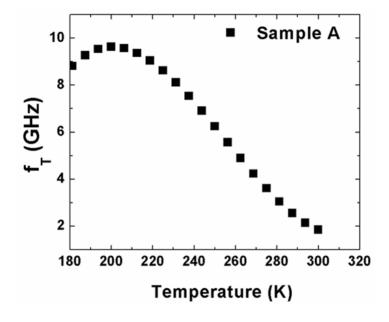

| Figure 6.13: Cut-off frequency as a function of operating temperature at $V_{ds} = -0.5 \text{ V}169$                      |

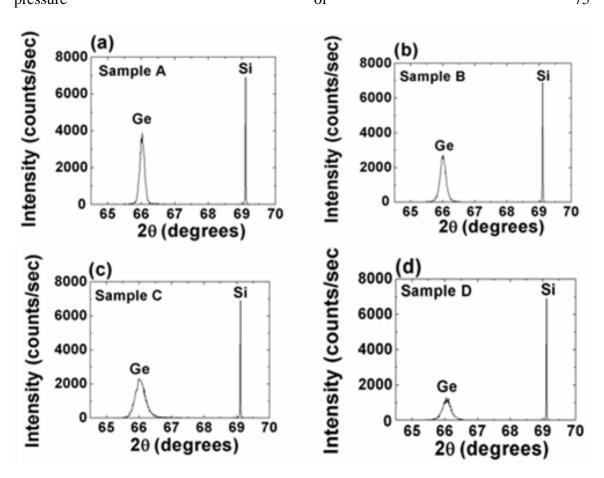

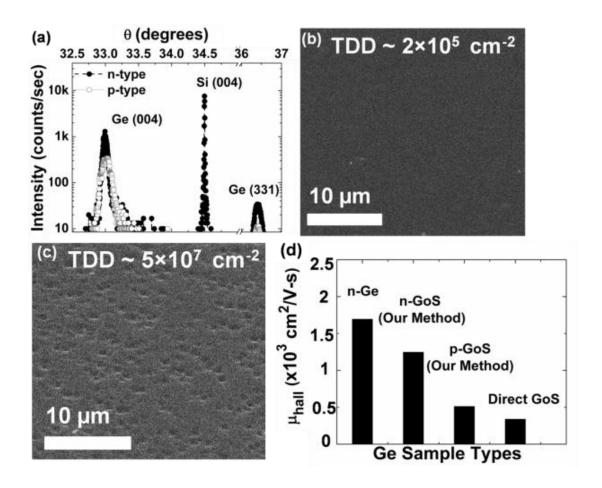

| Figure 6.14:(a) XRD intensity of Ge(004), Si(004), and Ge(331) peaks. (b) SEM images                                       |

| of etch pits on n-type surface. (c) SEM images of etch pits on p-type surface. (d) Majority                                |

| carrier mobility in Ge substrate and GoS substrates. n-Ge (100) wafer, purchased from                                      |

| MTI corporation, has a As doping level of $5\times10^{16}$ cm <sup>-3</sup>                                                |

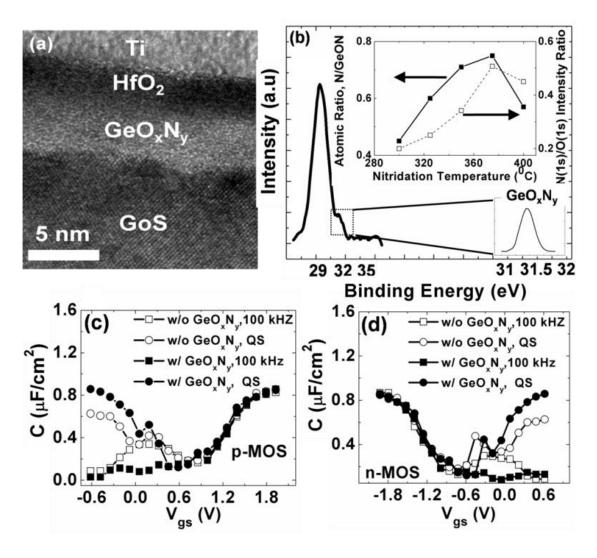

| Figure 6.15 :(a) High-resolution, cross-sectional TEM image of Ti/5-nm HfO <sub>2</sub> /8-nm                              |

| $\text{GeO}_x N_y / \text{GoS}$ stack. (b) XPS Ge3d peak with a shoulder corresponding to the oxidation                    |

| state of Ge in $\text{GeO}_xN_y$ . (Inset) N/Ge and N/O ratios are used to compare the N content in                        |

| the $\text{GeO}_x N_y$ layer formed at different nitridation temperatures. (c) and (d) C-V                                 |

| characteristics of p- and n-MOS with and without GeO <sub>x</sub> N <sub>y</sub>                                           |

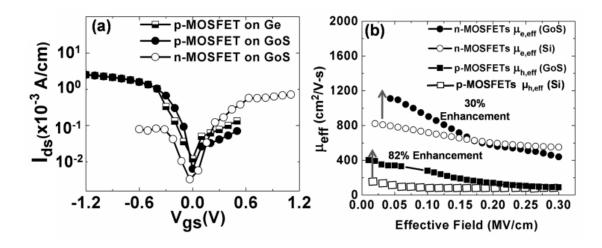

| Figure 2.16:(a) Subthreshold slope of p-MOSFETs fabricated on n-Ge and n-GoS, and n-                                       |

| MOSFETS fabricated on p-GoS: 80, 100, and 200 mV/decade. (b) $\mu_{h,eff}$ and $\mu_{e,eff}$ for p-                        |

| and n MOSEETs as a function of electric field                                                                              |

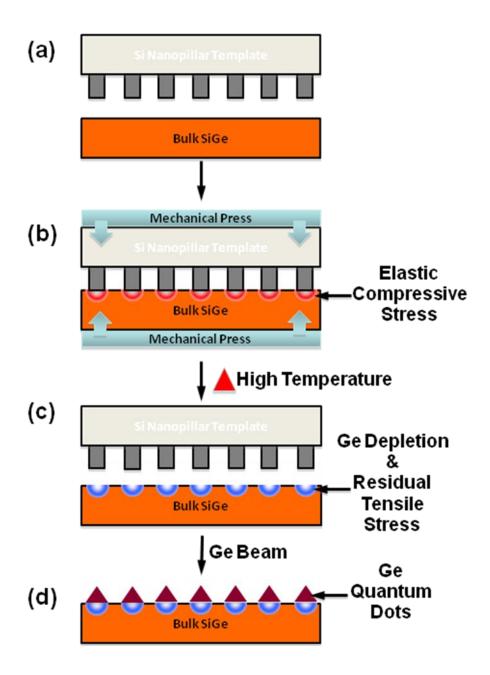

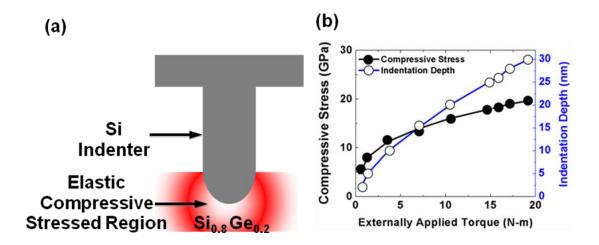

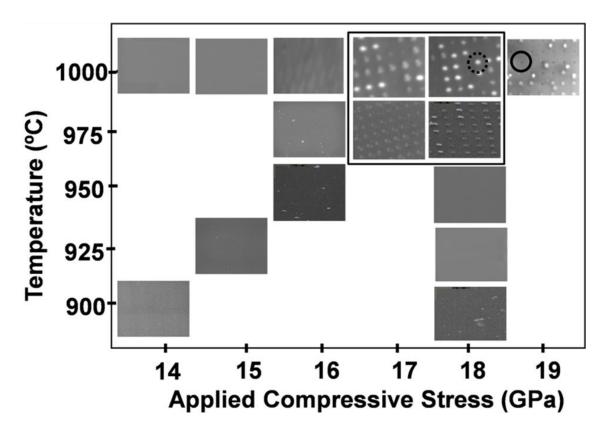

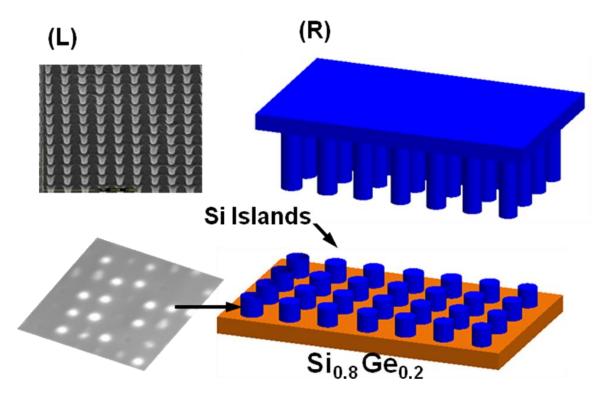

Figure 7.1:(a) A schematic of a 2D array of indentors and a bulk SiGe substrate before they are in contact with each other. (b) an assembly of the system including a mechaniucal press, a 2D array of indentors and a bulk SiGe substrate once they are in contact. The mechanical press exerts elastic compressive stress to near-surface of SiGe substrate through these indentors. (c) this system is now annealed at high temperature. Once the annealing is performed, the 2D array of indentors are withdrawn from the surface of SiGe substrate, leading to patterned residual tensile sress and Ge depletion in the near-surface of SiGe substrate. (d) once this stress-patterned is subjected to Ge beam in a MBE chamber, a 2D array of QDs of Ge start to form on the SiGe substrate......182 Figure 7.2:(a) A 2D view of the assembly consisting of a single indentor and a bulk SiGe substrate. The mechanical press exerts elastic compressive stress to the surface of SiGe substrate through indentors. (b) a plot of elastic compressive stress under each indentor as Figure 7.3: set of scanning electron microscopy (SEM) images of the surfaces of the Si<sub>0.8</sub>Ge<sub>0.2</sub> substrates as a function of externally torque and annealing temperature......189 Figure 7.4: (L) SEM images of a 2D array of Si indentors and a 2D array of Si leftovers on the surface of SiGe substrate. (b) 3D rendition of a 2D array of Si indentors, and Si Figure 7.5: the calibration parameters where atomic percentages of Si and Ge (in vertical axis) are plotted as a function of incident electron beam energy. The optimum atomic percentage ratio of 0.8:0.2 between Si and Ge is obtained with 6 KeV......191 Figure 7.6 (a) cross-sectionaal transmission electron microscope image of stack including a Si leftover and SiGe substrate. This case corresponds to elastic deformation where no

# LIST OF TABLES

| Table 1-1: Transistor parameters scaling based on constant-voltage scaling           | 3      |

|--------------------------------------------------------------------------------------|--------|

| Table 2-1. Expressions for the exponent $p$ and energy $E_n$ in Equation (2-19) that | depend |

| on the condensation regime and whether the islands are two or three-dimensional      | 9564   |

| Table 6-1: Dopant concentration based on sheet resistance                            | 174    |

#### **CHAPTER 1 INTRODUCTION**

#### 1.1 MOSFET Scaling Benefits

Compact integrated circuits (ICs) are the heart of present technology. Over last few decades, we have seen a phenomenal progress in terms of the integration of ICs. For instance, to realize denser ICs on a chip, our presnt technology offers ultra-low-scale-integration (ULSI) instead of very-large-scale-integration (VLSI). Over the past 50 years, Moore's law, first stated in 1965, has been considered to be sacrosanct for all VLSI people which simply described that the number of transistors on a chip to double about every two years <sup>1</sup>. This remarkable progress in integration has been realized by continual downscaling of the gate-length in metal-oxide-semiconductor field-effect transistors (MOSFETs). To abide by Moore's law, the physical dimensions of MOSFETs have been downscaled using constant field scaling approach where the MOSFETs not only become smaller over this years but they also become inexpensive, power efficient, become faster, and enable more logic functions per unit area of a die. The large density, by integrating more and more devices/chip allows technologist to offer superior performance from ICs at reduced cost per function as shown in Figure 1.1.

Figure 3.1. Trends in device count/chip and feature size of MOS device, as a function of the year of production <sup>2</sup>.

#### 1.2 Beyond Scaling

We mention in our previous section that the scalability is the main reason of the tremendous success in complmentary metal-oxide-semiconductor (CMOS) compatible Silicon (Si) based IC technologies. According to Moore's law, shrinkage in physical dimensions of transistors boost device performance. Based on constant-field scaling approach, upon the physical dimension of transistor by S (scaling factor), the depletion width has to be shrunk by S to ensure normal device performance. The doping density increases with reducing depletion width, and applied voltage at the transistor terminal reduces by factor S to maintain constant-field since

$depletion\ width \sim \sqrt{(doping\ density) \bullet (applied\ voltage)}$

As a result, the direct consequence of constant-field scaling is three-folds: first, increased component density by a factor of  $S^2$ ; second, increased speed of a transistor by a factor of  $S^2$  because of the reduced transit time of carriers in transistors and capacitance RC delay; third, power-density of the component remains constant.

However, constant-field scaling approach fails as physical dimensions of the transistors shrink further to 100 nms<sup>3</sup> because the applied voltage can not be scaled anymore by a factor of *S* with continuously shrinking dimensions because of constraint on the threshold bias to avoid increasing standby power during "off" state of transistors. Considering impossibility of continuously scaling applied voltage with shrinking dimensions, for the first time in 2005 <sup>4</sup>, a constant-voltage scaling approach was proposed to overcome this challenge. The following table 1-1 shows performance parameters of transistor based on constant-voltage scaling,

Table 1-1: Transistor parameters scaling based on constant-voltage scaling

| Regular Parameters  | Scaled Parameters   |

|---------------------|---------------------|

| $W, L, t_{OX}, X_j$ | Scaled by S         |

| $V_{dd}$ , $V_t$    | Do not scale        |

| $N_a$ , $N_d$       | $S^2N_a$ , $S^2N_d$ |

| $I_{d, \ sat}$      | $SI_{d,sat}$        |

| $P_{ds}$            | $SP_{ds}$           |

For simplicity, we consider an example of n-MOSFET, and corresponding schematic is shown in Fig. 1.2.

Figure 1.2: Schematic of n-MOSFET

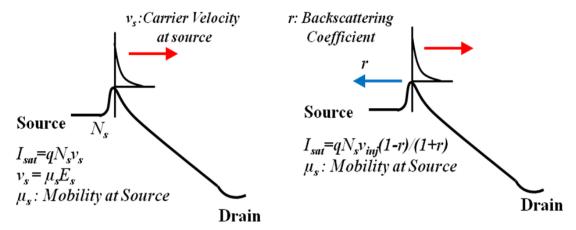

In case of n-MOSFETs, electrons are the major carriers in the inversion channel. Considering a channel length of L, and electron velocity of v, the transit time (t) for carriers from source to drain is  $t = \frac{L}{v}$ . The transit time for carriers is becoming smaller with shorter L, considering that v approaches to  $v_{sat}$  in small channel length transistor. Essentially this means that the transistors speed always increases with shrinking physical dimension of transistors. Besides benefiting speed, however, the saturation current density and power density go up with shorter channel length of transistors. The direct consequence of increasing power density is significant heat dissipation, prohibits further increase in the clock speed of transistors.

Researchers have realized that further increase in the clock speed can not be only improved through scaling, and time has arrived to reconsider a complete new device architecture or reexamine different material platform that can offer higher clock speed than that of Si. For instance, transistors built on SiGe substrate can offer an intrinsic speed of 500 GHz <sup>5</sup> compared to 100 GHz <sup>6</sup> on Si platform, and transistors fabricated on material such as InP can offer intrinsic speed of 1000 GHz <sup>7</sup>. The speed bottleneck is also depended on propagation delay through passive interconnects. Several ideas have been proposed to replace aluminum-based (electric conduction) and SiO<sub>2</sub> (electric insulation) interconnects by Cu-based and low-k dielectric materials (such as

doped SiO<sub>2</sub>). Another efficient approach to reduce propagation delay is to use optical interconnects instead of electric interconnects. In this retrospect, Si-based photonics allows designing of interconnects extremely efficient, and potentially a strong contender in next generation device architecture.

## 1.3 Emerging CMOS Technology Roadmap

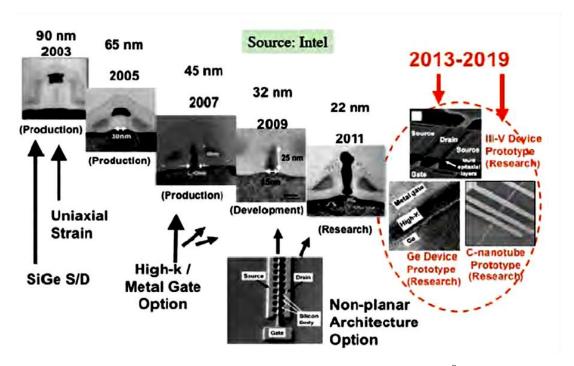

Figure 1.3: Intel Si-Transistors Scaling and Roadmap until 2012 8.

Over the past decade or so, various novel processes and design architectures are being introduced into fabrication of advanced Si-MOSFETs in order to maintain the historical 17% improvement per year. Figure 1.3 shows evaluation of advanced Si-based transistors roadmap proposed by Intel in 2012 <sup>8</sup>. As the physical dimension of gate-length starting to shrink such as 90 nm, 60 nm, Intel introduced strained-Si instead of bulk-Si substrate in their MOSFETs. Intel put too much effort in introducing strained-Si in this technology nodes because to get benefit from increasing carrier mobility (and thus improving ON current) by strain engineering. To achieve their

goal to produce strained-Si based transistors in a large-manufacturing scale <sup>9,10</sup>, Intel adopted uniaxial-strain induced process in their sub-100 nm logic-technology nodes. A major invention occurred in 2007 when Intel for the first time introduced High-k dielectric as gate oxide, and gate-last technique instead of conventional SiO<sub>2</sub>, and gate-first technique in their transistor fabrication processes. The main reason behind adopting high-k gate dielectric was to maintain oxide thickness at low gate leakage current. Later in 2011, Intel has revolutionized their design of transistors by putting tri-gate geometry in 22-nm-node transistors for the very first time. However, scaling beyond 22-nm or 10-nm-node would probably require a complete new device architecture or a new material platform altogether.

Figure 1.4: Evolution of Metallization <sup>8</sup>

As the speed of transistors becoming higher with shrinking transistors geometry, it is becoming incredibly important to maintain the speed through back-end metal lines that interconnect these transistors. Figure 1.4 shows an evaluation of back-end metallization schemes that have been taken place over these years with shrinking dimensions of transistors, such as 180 nm to 22 nm. Before 180 nm nodes,

mostly the metallization schemes used Al interconnects through SiO<sub>2</sub> vias. However, we notice Al interconnects through W vias were used at 180 nm nodes to minimized RC delay between transistors. This invention opened up a new path for metal interconnects, however faced tremendous mechanical stability. In comparison to 180 nm nodes, IBM revolutionized assembly of interconnects at 90 nm nodes by introducing Cu interconnects/vias thorugh dual damascence. This allowed IBM to demonstrate an assembly of interconnects upto 9 layers at 90 nm node technology. Since then, this Cu interconnects/vias have been matured to integrate in 22 nm node technology which allowed Intel to assembly more than 9 layers of interconnects. Hence, the 22 nm nodes with several layers of interconnects allowed chips to perform complex logic functions efficiently than before. However, beyond 22 nm or so on, the density of transistors and number of interconnects that are going to exist in a chip will be incredibly large. As a direct consequence of large number of interconnects, the time delay among transistors will be a critical issue. It is entirely possible that scaling beyond 22-nm or 10-nm-node would probably require a complete new interconnect platform. Presently, Intel and others are speculating to make use of optical interconnects instead of traditional electric interconnects. Si-based photonics can potentially provide a good platform for optical interconnects which can perform efficiently with smaller footprint of transistors.

Figure 1.5: MOSFET Transistor Scaling and Roadmap <sup>9</sup>

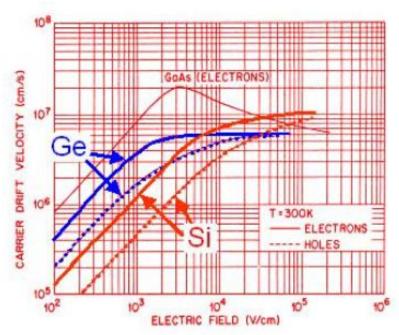

Scaling beyond 22 nm or smaller will probably require total structural changes in the transistors designing or probably require to use a higher carrier mobility materials such as Germanium or III-V semiconductors than that of Si. Figure 1.5 shows a roadmap predicted by ITRS on scaling of MOSFETs and its architectures. With smaller nodes, not only transistors start to use High-k dielectrics as a gate oxide also the architecture of transistors moved from planar to non-planar. For instance, ultra-thin body FETs or multi-gate FETs architectures are considered as potential replacement for bulk-MOSFETs because of their inherent superior electrostatic integrity <sup>10-12</sup>. Another promising alternative is to use higher-carrier mobility channel materials such as Ge which possess four and two times larger holes and electron mobility than that of Si counterpart <sup>13-16</sup>. The roadmap also predicts about three major materials platform that potentially can complement existing Si-based technology, are Ge, III-V semiconductors such as GaAs, InP, InAs etc <sup>17-19</sup>, and carbon-nanotubes <sup>20-21</sup>.

### **1.4** The Promise of Silicon Photonics

"As newer, faster microprocessors roll out, the copper connections that feed those processors within computers and servers will prove inadequate to handle the crushing tides of data." (*Paniccia & Koehl, 2006*).

Electronics is the technology of controlling the flow of electrons whereas photonics is the technology of controlling electrons whereas photonics is the technology of controlling the flow of photons. Electronics and photonics have been joined together in semiconductor optoelectronic devices where photons generate mobile electrons, and electrons generate and control the flow of photons generate and control the flow of photons. The compatibility of semiconductor optoelectronic devices and electronic devices has, in recent years, led to substantive advances in both technologies. Semiconductors are used as optical detectors, sources (LEDs and lasers), amplifiers, waveguides, modulators, sensors, and nonlinear optical To meet challenges in highdensity data communication systems, real-time sensing/detection, and high-speed control/actuation, it has become necessary to develop a new compactly integrated optolectronics platform that can potentially capable of handling large speed-bandwidth requirements. One of the most studied systems of optoelectronics is the Si photonics system. The Si-based photonics system studies the principles and technologies of merging electronics and photonics into the silicon platform. It is considered a more efficient and lower cost optical solution for high density data communications in optical fiber system and computer system. It is expected that a successful monolithic integration of silicon based nanophotonic devices and microelectronic devices will lead to a more

significant "micro optoelectronics revolution" than the well-known "microelectronics "revolution".

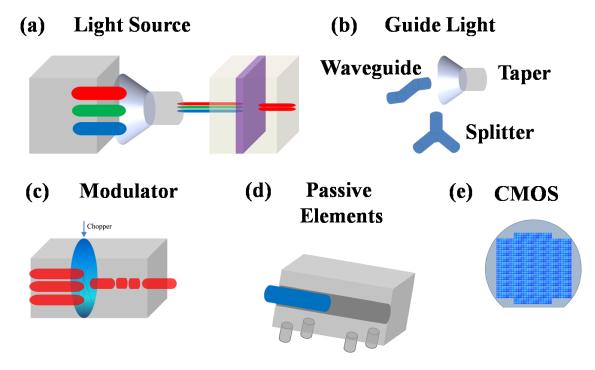

Figure 1.6: Components for Siliconization <sup>22</sup>

Si photonics offers a promising platform where optics and electronics can be integrated monolithically using conventional CMOS processing <sup>23</sup>. Figure 1.6 shows few examples of source, detector, modulator etc. that can built on Si photonics platform. There are some exclusive features that a Si platform can offer compared to it electronics counterpart.

First, photons will be transmitting information in a Si photonics platform. There are many benefits of optical communications: 1) high-speed or bandwidth can be achieved owing to short RC delay; as different wavelength photons don't interact with each other, so multiple wavelengths can co-exist in a communication channel resulting in large information carriage. This technique is called wavelength-

division-multiplexing (WDM). For instance, Luctera corporation demonstrated the capability of Si photonics device by showing performance from a four-channel WDM transceiver <sup>24</sup>; 2) optical fiber offers low-attenuation which can be used for long-distance communication; 3) optical fibers are low-cost transmission medium mostly based on silica and polymer materials which are inexpensive compared to traditional metal lines.

Second, optical interconnects among chip-to-chip or device-to-device can be totally deployed at different levels using Si photonics platform. The propagation delay between circuits or chips is mostly dominated by RC delay. Once the optical interconnects are deployed and activated, the RC delay issue no longer exists, and the speed will no longer be limited by scaling. For instance, the propagation delay of optical interconnects, which are not subjected to RC delay, is the gate delay, which decreases with physical dimension. Besides very short propagation delay, optical interconnects also provides large capacity/unit area by employing dense WDM technique, which succeeds in the optical fiber systems <sup>25</sup>.

Third, Si photonics is a perfect platform where electronic and photonic components can be integrated using hybrid integration scheme. The integration itself is a challenging task, and needs careful designing of each component, which is a subpart of this large Si photonics platform. The major components of this platform are optical devices (both active and passive) such as LASER, modulator, filters, waveguides, and electronic devices such as Si CMOS circuitry. For instance, Si is an ideal material for passive components in the optical interconnects, owing to its transparency in the wavelength range of 1.1  $\mu$ m to 7  $\mu$ m. The function of Si-based optical interconnects is not limited by the most useable near infrared (NIR) communication wavelength of 1.3 $\mu$ m

to 1.55 µm. Beside optical interconnects, owing to large refractive index difference between Si and SiO<sub>2</sub> as a core and cladding materials (Si~3.6 and SiO<sub>2</sub>~ 1.5), Si platform can be used to design a compact waveguide for propagating optical information between components. Although Si is a good choice for designing passive components, however, it is not an ideal choice for active application such as photodetection, generation, and electrooptic modulation. Intrinsic Si without further material engineering, lacks in electrooptic effect (Pockel effect) because of its centrosymmetric crystal structure <sup>26,27</sup>. Additionally, Si is not an efficient photodetector due to its transparency at NIR wavelengths. In comparison, SiG based devices can create electrooptic modulation, and photodetection more efficiently than Silicon. The band-gap (BG) of SiGe can be artificially engineered to produce optical modulation, which is which is based on Franz-Keldysh (FK) effect <sup>28</sup>. Also, tensile-strained engineering scheme can be used to capture photogenerated carriers more efficiently using SiGe based devices <sup>29,30</sup>.

## 1.5 Why Germanium?

Previous sections somehow capture the idea that there is a significant need for finding devices built from new materials, which potentially can perform faster than that of devices fabricated using existing Si CMOS technology. The major reason of finding new materials platform is two-fold: first, the devices would not be limited by scaling, and second, the new material would complement Silicon. Among many materials, Ge is one of such promising material that have shown enormous promise. Germanium possesses many advantages compared to its counterpart Silicon. The lattice electron and hole mobility ( $\mu_n$  and  $\mu_p$ ) are 3900 and 1900 cm<sup>2</sup>/V-s for Ge, compared to 1400 and 470 cm<sup>2</sup>/V-s for Si. In other words, the electron and hole bulk

mobility of Ge is 2.75 and 4 times than that of Si <sup>31</sup>. The direct consequence of high lattice mobility is large surface mobility that Ge provides. As a result, owing to large bulk and surface mobility, the transistors fabricated from Ge shows high speed. Besides outstanding mobility of Ge, the electron and hole mobility in Ge are more symmetric compared to Si. This leads to smaller footprint area in Ge-based pMOS in a CMOS inverter cell, compared to Si-based pMOS.

Figure 1.7: Carrier drift velocity (cm/s) as a function of electric field (V/cm) <sup>31</sup>