#### University of New Mexico UNM Digital Repository

Electrical and Computer Engineering ETDs

**Engineering ETDs**

6-9-2016

Fast and Scalable Architectures and Algorithms for the Computation of the Forward and Inverse Discrete Periodic Radon Transform with Applications to 2D Convolutions and Cross-Correlations

Cesar Carranza

Follow this and additional works at: https://digitalrepository.unm.edu/ece\_etds

#### **Recommended** Citation

Carranza, Cesar. "Fast and Scalable Architectures and Algorithms for the Computation of the Forward and Inverse Discrete Periodic Radon Transform with Applications to 2D Convolutions and Cross-Correlations." (2016). https://digitalrepository.unm.edu/ece\_etds/44

This Dissertation is brought to you for free and open access by the Engineering ETDs at UNM Digital Repository. It has been accepted for inclusion in Electrical and Computer Engineering ETDs by an authorized administrator of UNM Digital Repository. For more information, please contact disc@unm.edu.

Cesar Alberto Carranza De La Cruz

Candidate

Electrical and Computer Engineering

Department

This dissertation is approved, and it is acceptable in quality and form for publication: Approved by the Dissertation Committee:

MARIOS PATTICHIS

, Chairperson

RAMIRO JORDAN

VINCE CALHOUN

DANIEL LLAMOCCA

### Fast and Scalable Architectures and Algorithms for the Computation of the Forward and Inverse Discrete Periodic Radon Transform with Applications to 2D Convolutions and Cross-Correlations

by

#### Cesar Carranza

B.Sc., Electrical Engineering, Pontificia Universidad Católica del Perú, 1994

M.Sc., Computer Science, Centro de Investigación Científica y de Educación Superior de Ensenada, 2010

M.Sc., Computer Engineering, University of New Mexico, 2012

#### DISSERTATION

Submitted in Partial Fulfillment of the Requirements for the Degree of

### Doctor of Philosophy Engineering

The University of New Mexico

Albuquerque, New Mexico

May, 2016

# Dedication

To my family, for their support.

# Acknowledgments

I would like to thank my advisor, Professor Marios Pattichis, for his advice.

## Fast and Scalable Architectures and Algorithms for the Computation of the Forward and Inverse Discrete Periodic Radon Transform with Applications to 2D Convolutions and Cross-Correlations

by

#### Cesar Carranza

B.Sc., Electrical Engineering, Pontificia Universidad Católica del Perú, 1994

M.Sc., Computer Science, Centro de Investigación Científica y de Educación Superior de Ensenada, 2010

M.Sc., Computer Engineering, University of New Mexico, 2012 PhD., Engineering, University of New Mexico, 2016

#### Abstract

The Discrete Radon Transform (DRT) is an essential component of a wide range of applications in image processing, e.g. image denoising, image restoration, texture analysis, line detection, encryption, compressive sensing and reconstructing objects from projections in computed tomography and magnetic resonance imaging. A popular method to obtain the DRT, or its inverse, involves the use of the Fast Fourier Transform, with the inherent approximation/rounding errors and increased hardware complexity due the need for floating point arithmetic implementations. An alternative implementation of the DRT is through the use of the Discrete Periodic Radon Transform (DPRT). The DPRT also exhibits discrete properties of the continuousspace Radon Transform, including the Fourier Slice Theorem and the convolution property. Unfortunately, the use of the DPRT has been limited by the need to compute a large number of additions  $O(N^3)$  and the need for a large number of memory accesses.

This PhD dissertation introduces a fast and scalable approach for computing the forward and inverse DPRT that is based on the use of: (i) a parallel array of fixed-point adder trees, (ii) circular shift registers to remove the need for accessing external memory components when selecting the input data for the adder trees, and (iii) an image block-based approach to DPRT computation that can fit the proposed architecture to available resources, and As a result, for an  $N \times N$  image (N prime), the proposed approach can compute up to  $N^2$  additions per clock cycle. Compared to previous approaches, the scalable approach provides the fastest known implementations for different amounts of computational resources. For the fastest case, I introduce optimized architectures that can compute the DPRT and its inverse in just  $2N + \lceil \log_2 N \rceil + 1$  and  $2N + 3 \lceil \log_2 N \rceil + B + 2$  clock cycles respectively, where B is the number of bits used to represent each input pixel. In comparison, the prior state of the art method required  $N^2 + N + 1$  clock cycles for computing the forward DPRT. For systems with limited resources, the resource usage can be reduced to O(N) with a running time of  $\lceil N/2 \rceil (N+9) + N + 2$  for the forward DPRT and  $\lceil N/2 \rceil (N+2) + 3 \lceil \log_2 N \rceil + B + 4$  for the inverse.

The results also have important applications in the computation of fast convolutions and cross-correlations for large and non-separable kernels. For this purpose, I introduce fast algorithms and scalable architectures to compute 2-D Linear convolutions/cross-correlations using the convolution property of the DPRT and fixed point arithmetic to simplify the 2-D problem into a 1-D problem. Also an alternative system is proposed for non-separable kernels with low rank using the LU decomposition. As a result, for implementations with enough resources, for a an image and convolution kernel of size  $P \times P$ , linear convolutions/cross correlations can be computed in just  $6N + 4 \log_2 N + 17$  clock cycles for N = 2P - 1.

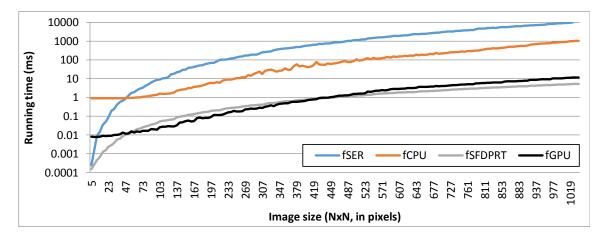

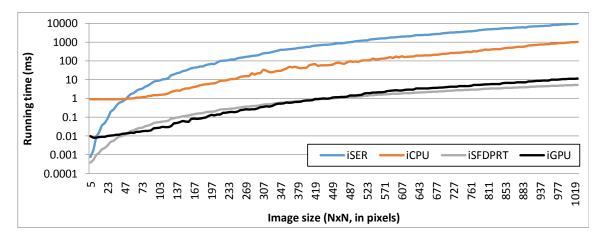

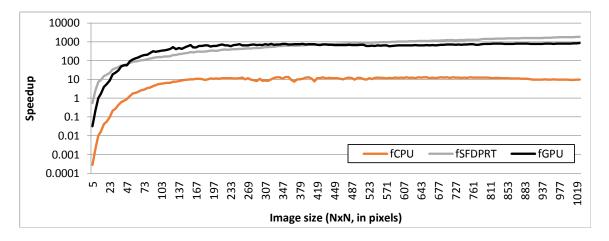

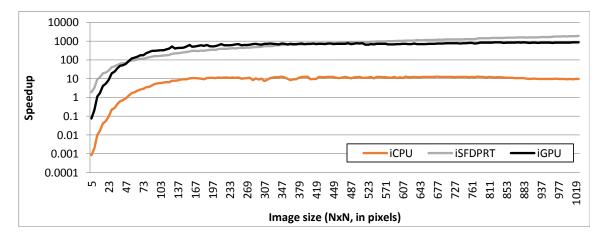

Finally, I also propose parallel algorithms to compute the forward and inverse DPRT using Graphic Processing Units (GPUs) and CPUs with multiple cores. The proposed algorithms are implemented in a GPU Nvidia Maxwell GM204 with 2048 cores@1367MHz, 348KB L1 cache (24KB per multiprocessor), 2048KB L2 cache (512KB per memory controller), 4GB device memory, and compared against a serial implementation on a CPU Intel Xeon E5-2630 with 8 physical cores (16 logical processors via hyper-threading)@3.2GHz, L1 cache 512K (32KB Instruction cache, 32KB data cache, per core), L2 cache 2MB (256KB per core), L3 cache 20MB (Shared among all cores), 32GB of system memory. For the CPU, there is a tenfold speedup using 16 logical cores versus a single-core serial implementation. For the GPU, there is a 715-fold speedup compared to the serial implementation. For real-time applications, for an 1021x1021 image, the forward DPRT takes 11.5ms and 11.4ms for the inverse.

# Contents

| $\mathbf{Li}$ | List of Figures x |         |                                                                 |     |

|---------------|-------------------|---------|-----------------------------------------------------------------|-----|

| $\mathbf{Li}$ | st of             | Table   | s x                                                             | xvi |

| 1             | Intr              | oducti  | ion                                                             | 1   |

|               | 1.1               | Thesis  | s Statement                                                     | 3   |

|               | 1.2               | Contra  | ibutions                                                        | 3   |

|               |                   | 1.2.1   | Specific contributions for the Scalable and Fast DPRT and its   |     |

|               |                   |         | inverse                                                         | 5   |

|               |                   | 1.2.2   | Specific contributions for the Fast 2-D Convolutions and Cross- |     |

|               |                   |         | Correlations Using Scalable Architectures                       | 7   |

|               |                   | 1.2.3   | Specific contributions for the computation of the DPRT and      |     |

|               |                   |         | its inverse on multi-core CPUs and GPUs                         | 9   |

|               | 1.3               | Overv   | iew of Dissertation                                             | 10  |

| <b>2</b>      | Scal              | lable F | Fast Discrete Periodic Radon Transform and its inverse          | 11  |

|               | 2.1               | Introd  | luction                                                         | 13  |

|               | 2.2               | Backg   | round                                                           | 18  |

|               |                   | 2.2.1   | Notation summary                                                | 18  |

|               |                   | 2.2.2   | Discrete Periodic Radon Transform and its Inverse               | 19  |

|               |                   | 2.2.3   | previous DPRT implementations                                   | 22  |

|               | 2.3               | Metho   | odology                                                         | 23  |

|   |                 | 2.3.1  | Partial DPRT                                                  | 23 |

|---|-----------------|--------|---------------------------------------------------------------|----|

|   |                 | 2.3.2  | Scalable Fast Discrete Periodic Radon Transform (SFDPRT) $.$  | 25 |

|   |                 | 2.3.3  | Inverse Scalable Fast Discrete Periodic Radon Transform (iSF- |    |

|   |                 |        | DPRT)                                                         | 29 |

|   |                 | 2.3.4  | Fast Discrete Periodic Radon Transform (FDPRT) and its        |    |

|   |                 |        | inverse (iFDPRT)                                              | 32 |

|   |                 | 2.3.5  | Pareto-optimal Realizations                                   | 41 |

|   | 2.4             | Impler | mentation Details                                             | 42 |

|   |                 | 2.4.1  | Scalable Fast Discrete Periodic Radon Transform               |    |

|   |                 |        | (SFDPRT)                                                      | 42 |

|   |                 | 2.4.2  | Inverse Scalable Fast Discrete Periodic Transform Implemen-   |    |

|   |                 |        | tations                                                       | 53 |

|   | 2.5             | FPGA   | Implementation                                                | 54 |

|   | 2.6             | Result | s and discussion                                              | 59 |

|   |                 | 2.6.1  | Results                                                       | 59 |

|   |                 | 2.6.2  | Discussion                                                    | 65 |

|   | 2.7             | Conclu | usions                                                        | 69 |

| 3 | Fast            | 2-D    | Convolutions and Cross-Correlations Using Scalable Ar-        |    |

|   | $\mathbf{chit}$ | ecture | s                                                             | 70 |

|   | 3.1             | Introd | uction                                                        | 71 |

|   | 3.2             | Backg  | round                                                         | 77 |

|   |                 | 3.2.1  | Basic notation                                                | 77 |

|   |                 | 3.2.2  | Separable decomposition for non-separable kernels             | 77 |

|   |                 | 3.2.3  | The discrete periodic radon transform (DPRT)                  | 79 |

|   |                 | 3.2.4  | Circular convolutions using the DPRT                          | 80 |

|   | 3.3             | Metho  | odology                                                       | 81 |

|   |                 | 3.3.1  | Computing 1-D circular convolutions using circular shifts     | 81 |

|   |                 | 3.3.2  | Fast 1-D circular convolution hardware implementation         | 82 |

|          |      | 3.3.3   | Fast and scalable 2-D linear convolutions and cross-correlations   | 84   |

|----------|------|---------|--------------------------------------------------------------------|------|

|          |      | 3.3.4   | Scalable 2-D Linear Convolution using LU decomposition (S2-        |      |

|          |      |         | DLCLU)                                                             | 87   |

|          |      | 3.3.5   | Overlap and Add for larger images                                  | 95   |

|          | 3.4  | Result  | ts                                                                 | 96   |

|          |      | 3.4.1   | Experimental setup                                                 | 96   |

|          |      | 3.4.2   | Running time                                                       | 97   |

|          |      | 3.4.3   | Pareto comparisons                                                 | 100  |

|          | 3.5  | Concl   | usions                                                             | 101  |

| 4        | Dis  | crete I | Periodic Radon Transform implementation on GPUs and                | l    |

|          | mul  | ti-core | e CPUs                                                             | 105  |

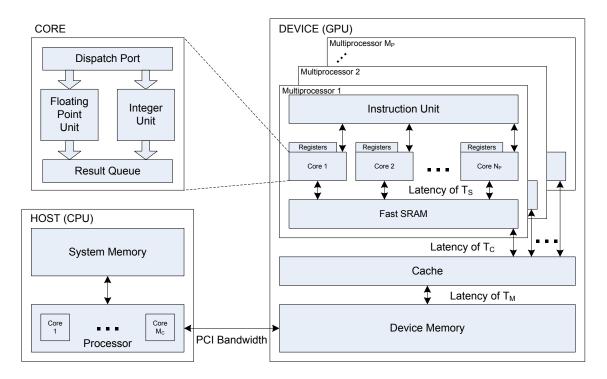

|          | 4.1  | Archit  | tecture overview for multi-core CPUs and GPUs                      | 106  |

|          | 4.2  | Parall  | el Algorithms for computing the forward and inverse DPRT $$ . $$ . | 108  |

|          |      | 4.2.1   | Analysis of the DPRT and iDPRT properties to parallelize the       |      |

|          |      |         | processing                                                         | 112  |

|          |      | 4.2.2   | Parallel DPRT and iDPRT on a multi-core CPU system                 | 113  |

|          |      | 4.2.3   | Parallel DPRT and iDPRT on a GPU                                   | 115  |

|          | 4.3  | Imple   | mentation of proposed algorithms on a CPU and GPU processors       | 3118 |

|          |      | 4.3.1   | Serial implementation of the DPRT and iDPRT on the HOST            | 123  |

|          |      | 4.3.2   | Parallel implementation of the DPRT and iDPRT on the HOST          | 123  |

|          |      | 4.3.3   | Parallel implementation of the DPRT and iDPRT on the DE-           |      |

|          |      |         | VICE                                                               | 124  |

|          | 4.4  | Result  | ts and Conclusions                                                 | 132  |

| <b>5</b> | Cor  | nclusio | ns and future work                                                 | 137  |

| Α        | List | ; of pu | blications                                                         | 141  |

| В        | Ado  | ler tre | es resource computation                                            | 144  |

| С            | Adder trees resource computation for Convolution                              | 146      |

|--------------|-------------------------------------------------------------------------------|----------|

| D            | Source code for the Serial DPRT and iDPRT on the HOST                         | 147      |

| $\mathbf{E}$ | Source code for the Parallel DPRT and iDPRT on the HOST                       | 152      |

| F            | Source code for the Parallel DPRT and iDPRT on the DEVIC (GPU GM204, Maxwell) | E<br>158 |

| Re           | eferences                                                                     | 166      |

# List of Figures

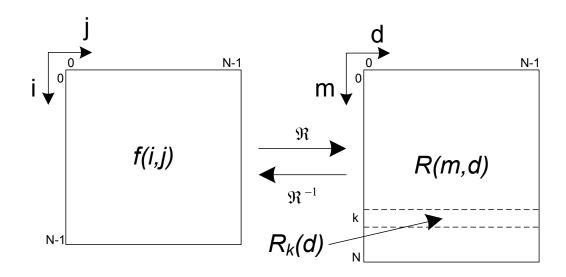

| 2.1 | Illustration of the DPRT and its iDPRT for a function $f$ of size                 |    |

|-----|-----------------------------------------------------------------------------------|----|

|     | $N \times N$ , where N is prime. Each row of $R(m, d)$ , denoted as a vector      |    |

|     | $R_k(d), k = 0, \ldots, N$ , represents a projection of $f(i, j)$                 | 20 |

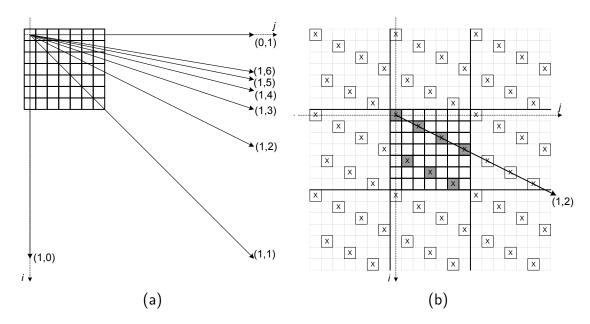

| 2.2 | DPRT Example for a $7 \times 7$ image. (a) Prime directions; (b) Main             |    |

|     | image (at center with bold boxes) and its periodic extensions. Pixels             |    |

|     | marked with $\times$ : samples along periodic line for prime direction $(1, 2)$ , |    |

|     | pixels marked with $\times$ in grey boxes are added to compute $R(2,0)$ .         | 21 |

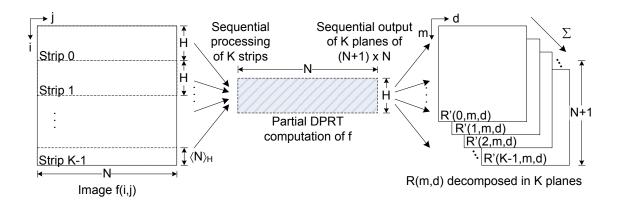

| 2.3 | Scalable DPRT concept. The input image is divided into $K$ strips.                |    |

|     | The DPRT is computed by accumulating the partial sums from each                   |    |

|     | strip                                                                             | 23 |

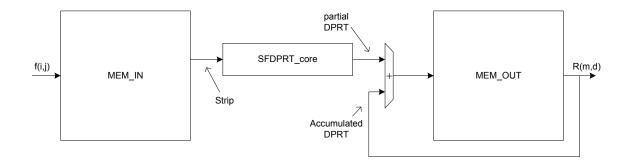

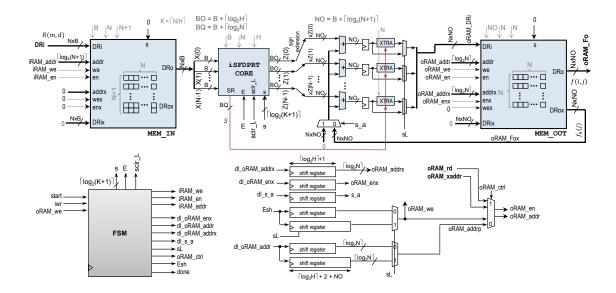

| 2.4 | Top level system for implementing the Scalable and Fast DPRT                      |    |

|     | (SFDPRT). The ${\tt SFDPRT\_core}$ computes the partial sums. ${\tt MEM\_IN}$     |    |

|     | and MEM_OUT are dual port input and output memories. A Finite                     |    |

|     | State Machine (FSM, not shown in the figure) is needed for control.               |    |

|     | See text in Sec. ?? for more details.                                             | 25 |

| 2.5 | Top level algorithm for computing the scalable and fast DPRT (SFD-                |    |

|     | PRT). Within each loop, all of the operations are pipelined. Then,                |    |

|     | each iteration takes a single cycle. For example, the Shift, pipelined            |    |

|     | Compute, and the Add operations of lines ??, ??, and ?? are always                |    |

|     | computed within a single clock cycle. Refer to section <b>??</b> for the          |    |

|     | notation.                                                                         | 27 |

|     |                                                                                   |    |

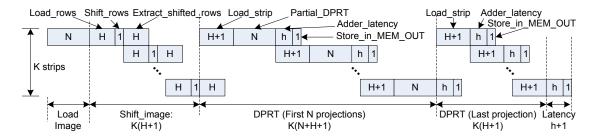

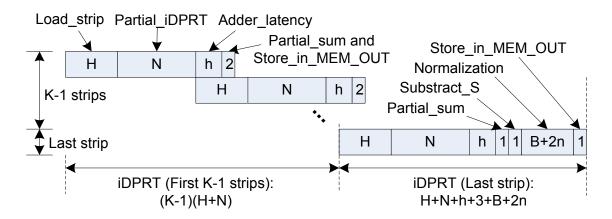

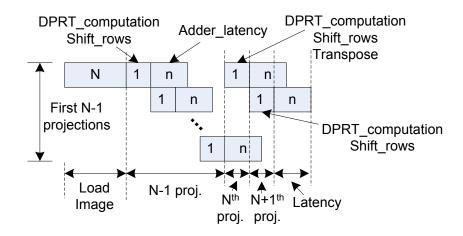

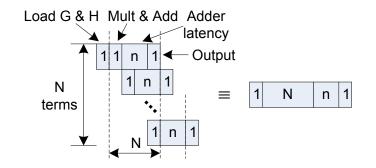

- 2.6 Running time for scalable and fast DPRT (SFDPRT). In this diagram, time increases to the right. The image is decomposed into K strips. Then, the first strip appears in the top row and the last strip appears in the last row of the diagram. Here, H denotes the maximum number of image rows in each strip,  $K = \lceil N/H \rceil$  is the number of strips, and  $h = \lceil \log_2 H \rceil$  represents the addition latency.

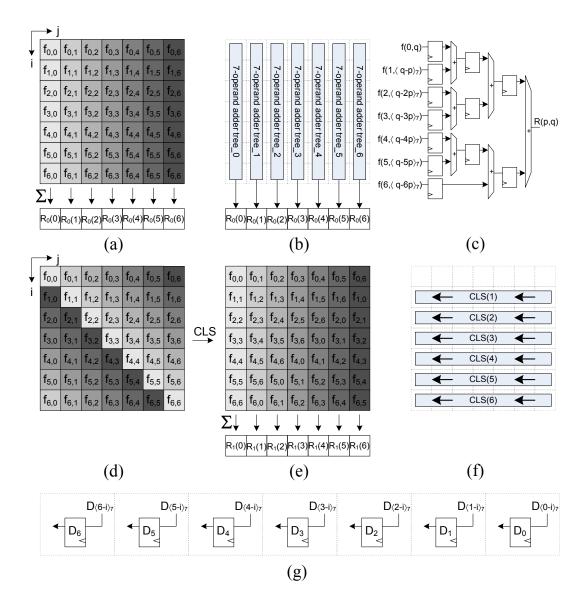

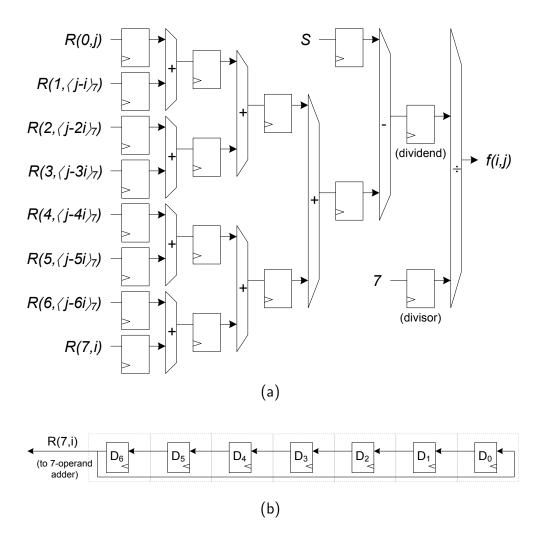

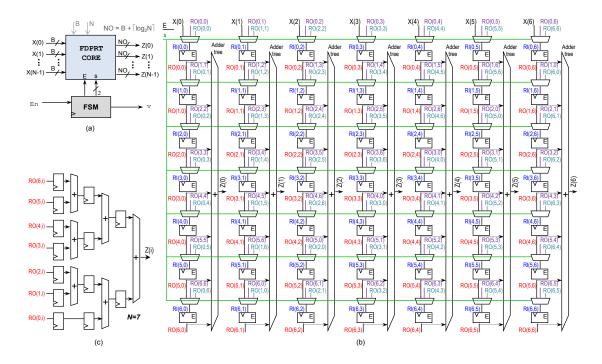

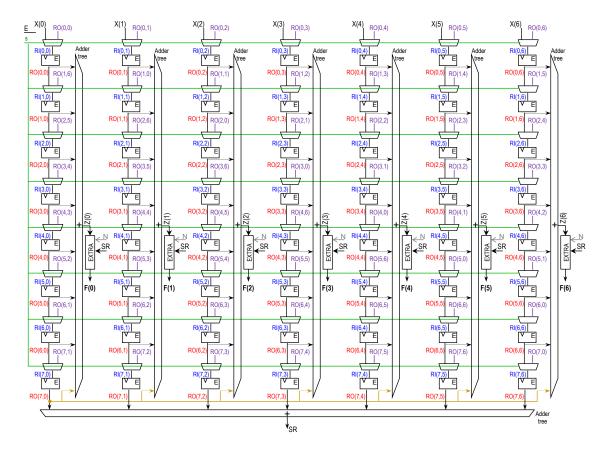

2.10 Projection computation example for the first two prime directions for a 7×7 image. (a) Pixels are added along each column using an adder tree for prime direction (1,0). (b) Array of 7-operand adder tree for performing the additions. (c) Detailed architecture of the 7-operand adder tree\_p (fully pipelined) to compute the projection p, element q. (d) For prime direction (1,1), pixels sharing the same gray-scale value need to be added but are not aligned along the columns. (e) Pixels are properly aligned along each column following the required number of circular, left, shifts. (f) Circular Left-Shift (CLS) structure for aligning image samples for prime direction of (1, 1), all shifts are performed in parallel in a single clock cycle.. (g) Detailed architecture for CLS(i).

2.12 Running time for fast DPRT (FDPRT). In this diagram, time increases to the right. The DPRT is computed in N + 1 steps (projections). Each projection takes 1 + h clock cycles. Here,  $n = \lceil \log_2 N \rceil$  represents the addition latency. Pipeline structure: Since fully pipelined adder trees are used, the computation of subsequent projections can be started after one clock of the previous projection. 37

- 2.13 (a) Adder architecture example for N = 7. The fully pipelined 7operand adder tree used for the FDPRT is now modified to compute the iFDPRT (*i* projection, element *j*): After the shift registers align the data, the adder tree receives all the terms to compute  $\sum_{m=0}^{6} R(m, \langle j - mi \rangle_7) + R(7, i)$ . Note that R(7, i) is an additional term for the 7-operand adder tree (provided by an additional CLS(1) holding  $R_N(d)$ ). After all the terms are added, *S* needs to be substracted and then divide the result by 7 to obtain f(i, j). In a full implementation, 7 of those adders  $(j = 0, \ldots, N - 1)$  are used to be able to compute in parallel one projection, to obtain one complete row of *f*. (b) Additional modified CLS(1) to hold  $R_N(d)$  and provide R(N, i) to all of the 7-operand adder trees on each projection *i*. . .

| The implementation of $Load\_shifted\_image(f)$ of Fig. ??. The                |    |

|--------------------------------------------------------------------------------|----|

| process shifts the input image during the loading process in order             |    |

| to avoid the transposition associated with the last projection. The            |    |

| shifting is performed using the circular left shift registers that are         |    |

| available in SFDPRT_core.                                                      | 45 |

| Process for implementing $Load\_strip(r, M)$ of Fig. ??                        | 45 |

| The implementation of $Add_partial_result$ of Fig. ??. The process             |    |

| is pipelined where all the steps are executed in a single clock cycle.         | 46 |

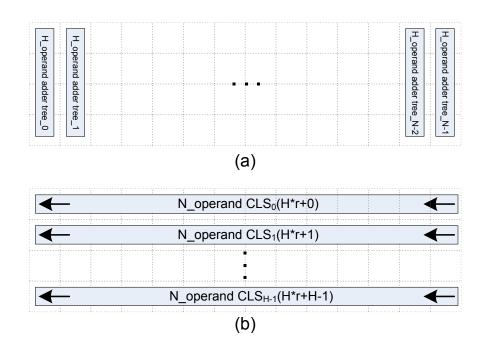

| SFDPRT_core architecture. (a) Array of H-operand adder tree for                |    |

| performing the $H \times N$ additions in parallel in one clock cycle. (b)      |    |

| Circular Left-Shift (CLS) structure for aligning image samples, all            |    |

| shifts are performed in parallel in a single clock cycle                       | 47 |

| $7 \times 7$ pattern example for storing $f$ in MEM_IN. (a) Original $f$ . (b) |    |

| Shifted $f$ . (c) Accessing column number 4 of $f$ , note that each value      |    |

| belongs to a different RAM, therefore all the values can be retrieved          |    |

performing the  $H \times N$  addition Circular Left-Shift (CLS) struct shifts are performed in parallel 2.20  $7 \times 7$  pattern example for stori Shifted f. (c) Accessing column belongs to a different RAM, the in one clock cycle. (d) Accessing row number 4 of f, observe that

2.16

2.17

2.18

2.19

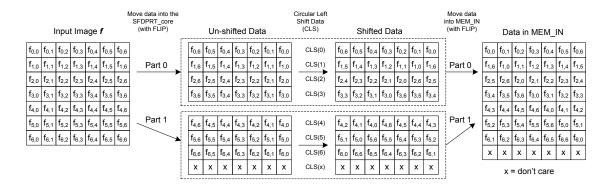

- the data is shifted and needs to be un-shifted before computing the 482.21 $7 \times 7$  example of Loading image f into MEM\_IN using the algorithm described in Fig. ?? with H = 4, N = 7. Then,  $K = \lceil N/H \rceil = 2$ , and the loading of f into MEM\_IN is divided in two parts. . . . . . 50

- 2.22 $7 \times 7$  example of Loading strips of f, into SFDPRT\_core using the algorithm described in Fig. ?? with H = 4, N = 7, row\_mode. Then,  $K = \lceil N/H \rceil = 2$ , and the loading of f into SFDPRT\_core is divided in two parts. 52

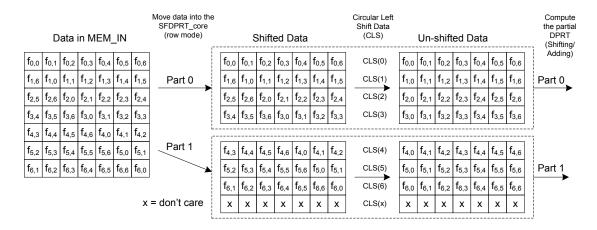

- $7 \times 7$  example of Loading strips of f, into SFDPRT\_core using the 2.23algorithm described in Fig. ?? with H = 4, N = 7, column\_mode and  $K = \lceil N/H \rceil = 2$ . Note that the loading of f into SFDPRT\_core is divided in two parts. 52

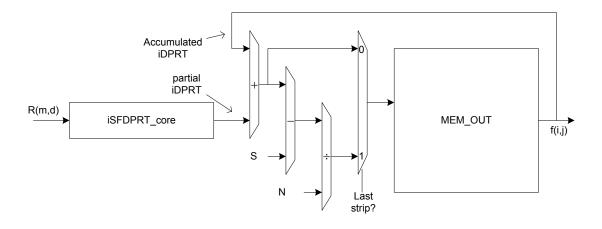

| 2.25 | System for implementing the inverse, scalable and fast DPRT (iSFD-               |

|------|----------------------------------------------------------------------------------|

|      | PRT). The system uses the $iSFDPRT\_core$ core for computing partial             |

|      | sums. The system uses dual port input and output memories, an                    |

|      | accumulator array and a Finite State Machine for control. See text               |

|      | in Sec. $??$ for more details. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $55$ |

- 2.26 Fast DPRT (FDPRT) hardware. (a) FDPRT core and finite state machine (FSM). (b) Structure of the FDPRT core including: pipelined adder trees, registers, multiplexers (for shifting and fast transposition) for N = 7. (c) Pipelined adder tree architecture for N = 7. 56

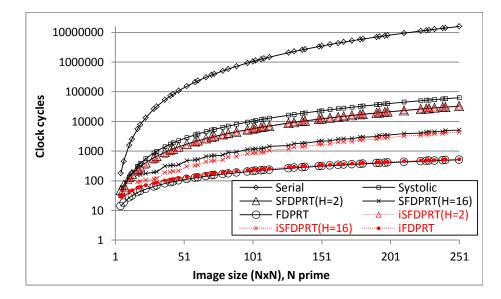

- 2.29 Comparative running times for the proposed approach versus competitive methods. Running times in clock cycles for: (i) the serial implementation of [1], (ii) the systolic [2], and (iii) the FPGA implementation of the SFDPRT for H = 2 and 16 are presented. The measured running times are in agreement with Tables ?? and ??. 61

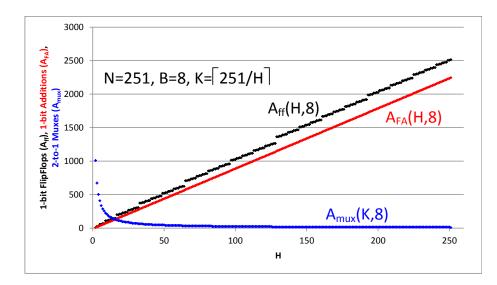

- 2.30 Resource functions: (i) number of adder tree flip-flops  $A_{ff}(.)$ , (ii) number of 1-bit additions  $A_{fa}(.)$ , and (iii) number 2-to-1 multiplexers  $A_{mux}(.)$  for N = 251, B=8. Refer to Table ?? for definitions. . . . . 63

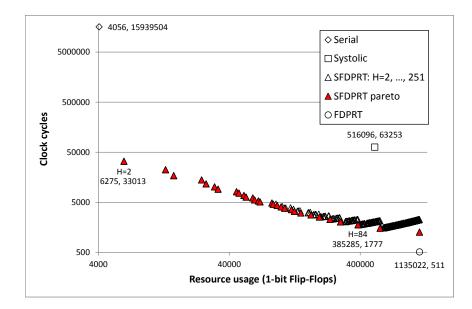

- 2.31 Comparative plot for the different implementations based on the number of cycles and the number of flip-flops only. Refer to Fig. ?? for a comparative plot for the different implementations based on the number of cycles and the number of 1-bit additions. Also, refer to Table ?? for a summary of RAM and multiplexer resources. The plot shows the Pareto front for the proposed SFDPRT for H = 2, ..., 251, for an image of size  $251 \times 251$ . The Pareto front is defined in terms of running time (in clock cycles) and the number of flip-flops used. For comparison, the serial implementation from [1], and the systolic implementation [2] is shown. .....

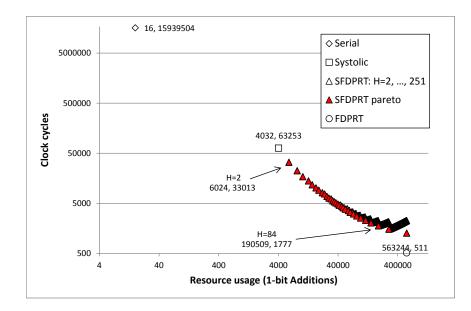

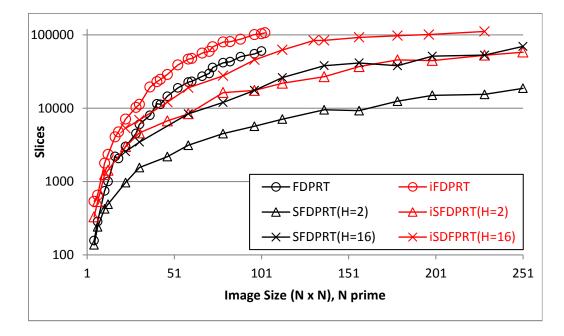

- 2.32Comparative plot for the different implementations based on the number of cycles and the number of one-bit additions only (or equivalent 1 bit full adders). Refer to Fig. ?? for a similar comparison based on the number of flip-flops. Pareto front for the proposed SFDPRT for H = 2, ..., 251, for an image of size  $251 \times 251$ . The Pareto front is defined in terms of running time (in clock cycles) and the number of 1-bit additions. For comparison, the serial implementation from |1|, and the systolic implementation |2| is shown. The fastest implementation is due to the FDPRT. 65. . . . . . . . . . . . 2.33FPGA slices for a Virtex-6 implementation for both the forward and inverse DPRTs for H = 2, 16, N prime and  $2 \le N \le 251$ . . . . . . 66

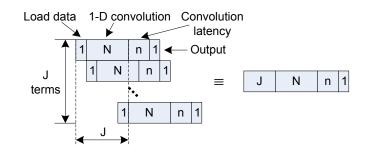

- 3.3 Running time for the implementation of the fast architecture for computing 1-D Circular convolutions. In this diagram, time increases to the right. The number of clock cycles for each term of  $F_m(d)$  is shown on each strip. The strip on the right represents the total running time.  $n = \lceil \log_2 N \rceil$  represents the addition latency. . . . . 84

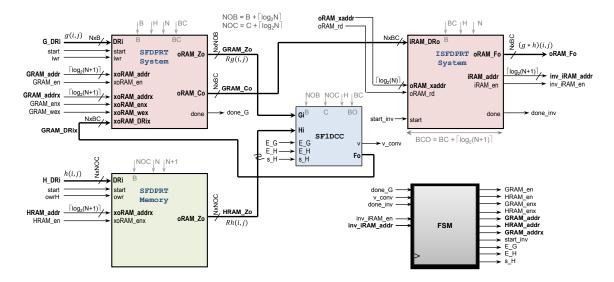

- 3.5 Fast and scalable architecture system for computing 2D convolutions. A modification is needed for computing fast cross-correlations (see below). Refer to Fig. ?? for the sequence of operations. The DPRT is computed by a fast and scalable block denoted by SFDPRT\_System. SFDPRT\_System computes the DPRT of the zero padded input image g. For regular convolution kernels, the DPRT of the zero-padded convolution kernel h can be pre-computed and stored in the SFDPRT Memory block as shown here. Alternatively, in adaptive filterbank applications, it can be introduced an extra SFDPRT\_System block for computing the DPRT in real time. Furthermore, for computing cross-correlations in real-time, a fast transposition is needed before applying the DPRT. It is computed J circular convolutions in parallel (row-wise) using the SF1DCC\_System block. Control is performed by a finite state machine (FSM block).

- 3.6 Running time for computing J circular convolutions in parallel using J fast convolution blocks (see basic block structure in Fig. ??). In this diagram, time increases to the right. Here, it takes one cycle to perform a parallel load for each block. Overall, it is required J+N+n+1 to compute everything, where  $n = \lceil \log_2 N \rceil$  represents the addition latency.

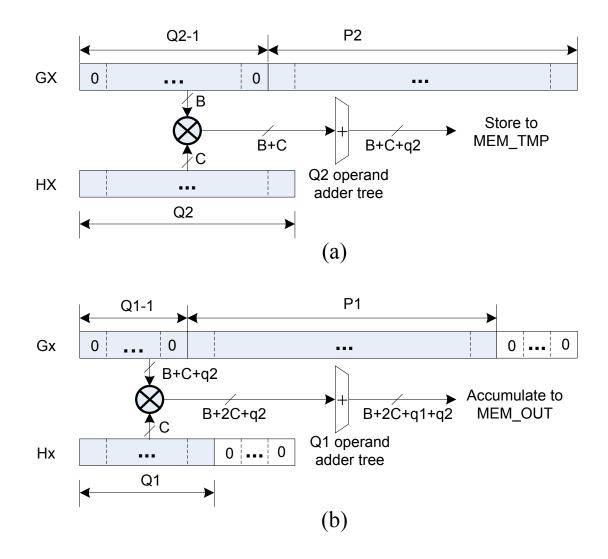

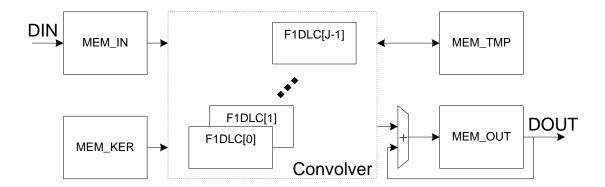

- 3.9 Fast 1-D linear convolver (F1DLC) block representation. Assume  $P_2 \ge P_1, Q_2 \ge Q_1$ . GX size is  $P_2 + Q_2 1$ , HX size is  $Q_2$ . Gray boxes denotes the usage of the F1DLC. Bit usage is for full accuracy. Recall, B is the number of bits for the input image, C for the kernel,  $q1 = \lceil \log_2 Q_1 \rceil$  and  $q2 = \lceil \log_2 Q_2 \rceil$ . The set of  $Q_2$  multipliers is represented by the  $\otimes$  symbol, the input and output bits for each one is indicated in the. All the multipliers are connected to a  $Q_2$ -operand adder tree. (a) Convolver processing rows. (b) Convolver processing columns.

| 3.10 | Algorithm for computing the 1-D linear convolution between the                                             |     |

|------|------------------------------------------------------------------------------------------------------------|-----|

|      | signal $GIN$ and the preloaded row or column kernel $HX$ . The output                                      |     |

|      | is stored in $\texttt{MEM}=\texttt{MEM\_TMP}$ for rows, or accumulated in $\texttt{MEM}=\texttt{MEM\_OUT}$ |     |

|      | for columns. $SG$ is the final size of the convolved signal, $SH$ is the                                   |     |

|      | size of the current kernel and $x = 0, \dots, SG - SH$ .                                                   | 94  |

| 3.11 | S2DLCLU System (top level diagram). Bus width is for maximum                                               |     |

|      | accuracy. DANIEL must provide the final version with more detail.                                          | 94  |

| 3.12 | Algorithm for computing the 2-D linear convolution between the                                             |     |

|      | image $g(i, j)$ and the non-separable kernel $h(i, j)$ decomposed into $r$                                 |     |

|      | separable kernels $h_R(i,j)$ for rows and $h_C(i,j)$ for columns. $g'(i,j)$                                |     |

|      | holds the results of the row-convolution in $\texttt{MEM\_TMP}.$ The output is                             |     |

|      | stored in MEM_OUT                                                                                          | 95  |

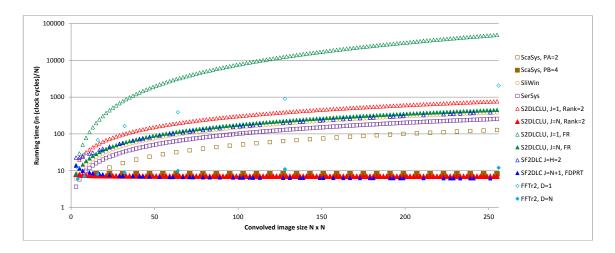

| 3.13 | Running time in clock cycles (normalized by image size $N$ ) versus                                        |     |

|      | convolved image size for all methods.                                                                      | 99  |

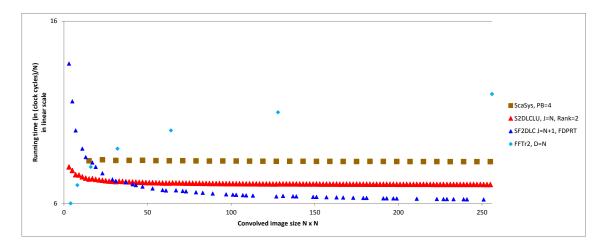

| 3.14 | Running time in clock cycles (normalized by image size $N$ ) versus                                        |     |

|      | convolved image size for the fastest methods.                                                              | 100 |

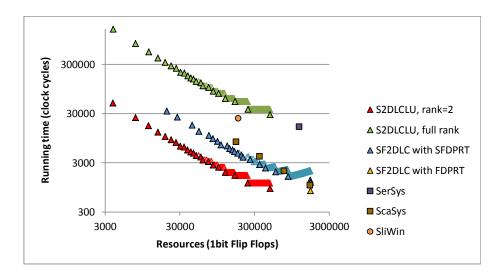

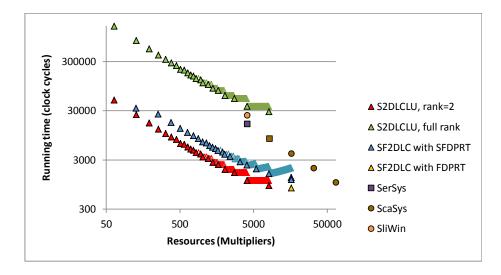

| 3.15 | Resources (1-bit FlipFlops) vs Running time.                                                               | 102 |

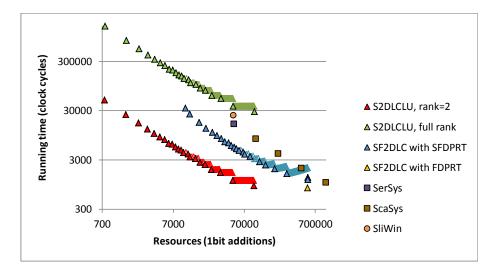

| 3.16 | Resources (1-bit Additions) vs Running time.                                                               | 103 |

| 3.17 | Resources (Multipliers) vs Running time                                                                    | 103 |

| 4.1  | Top level block diagram of the CPU and GPU architecture. The                                               |     |

|      | block on the lower-left represents the ${\bf HOST}$ system (the CPU).                                      |     |

|      | The block on the right represents the $\mathbf{DEVICE}$ where all the com-                                 |     |

|      | putations are performed (the GPU). Top-left shows the detail of one                                        |     |

|      | CORE                                                                                                       | 108 |

| 4.2  | Serial algorithm for computing the forward Discrete Periodic Radon                                         |     |

|      | Transform $R(m, d)$ of the image $f(i, j)$ of size $N \times N$                                            | 109 |

| 4.3  | Serial algorithm for computing the inverse Discrete Periodic Radon                                         |     |

|      | Transform $f(i, j)$ of the radon space $R(m, d)$ of size $(N + 1) \times N$ .                              | 110 |

| 4.4  | Main parallel algorithm for computing the forward Discrete Periodic                  |     |

|------|--------------------------------------------------------------------------------------|-----|

|      | Radon Transform $R(m,d)$ of the image $f(i,j)$ of size $N \times N$ on a             |     |

|      | CPU with $M_C$ cores                                                                 | 114 |

| 4.5  | Kernel algorithm for each core on the HOST to compute one set of                     |     |

|      | prime directions of the Discrete Periodic Radon Transform ${\cal R}(m,d)$            |     |

|      | of the image $f(i, j)$ of size $N \times N$ . Consecutive prime directions           |     |

|      | $dirIni$ through $dirEnd$ are computed. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 114 |

| 4.6  | Main parallel algorithm for computing the inverse Discrete Periodic                  |     |

|      | Radon Transform $f(i,j)$ of the radon space $R(m,d)$ of size $(N+1)\times N$         |     |

|      | on a CPU with $M_C$ cores                                                            | 115 |

| 4.7  | Kernel algorithm for each core on the HOST to compute one set of                     |     |

|      | prime directions of the inverse Discrete Periodic Radon Transform                    |     |

|      | $f(i,j)$ of the radon space $R(m,d)$ of size $(N+1) \times N$ . Consecutive          |     |

|      | prime directions $dirIni$ through $dirEnd$ are computed                              | 115 |

| 4.8  | Main parallel algorithm for computing the forward Discrete Periodic                  |     |

|      | Radon Transform $R(m,d)$ of the image $f(i,j)$ of size $N\times N$ on a              |     |

|      | GPU with $M_P \times N_P$ cores                                                      | 118 |

| 4.9  | Kernel algorithm for each core on the DEVICE to compute one ray of                   |     |

|      | the forward Discrete Periodic Radon Transform ${\cal R}(m,d)$ of the image           |     |

|      | $f(i,j)$ of size $N \times N$                                                        | 119 |

| 4.10 | Main parallel algorithm for computing the inverse Discrete Periodic                  |     |

|      | Radon Transform $f(i, j)$ of the radon space $R(m, d)$ of size $(N+1) \times N$      |     |

|      | on a GPU with $M_P \times N_P$ cores                                                 | 120 |

| 4.11 | Kernel algorithm for each core on the DEVICE to compute one ray                      |     |

|      | of the inverse Discrete Periodic Radon Transform $f(i, j)$ of the radon              |     |

|      | space $R(m,d)$ of size $(N+1) \times N$ .                                            | 120 |

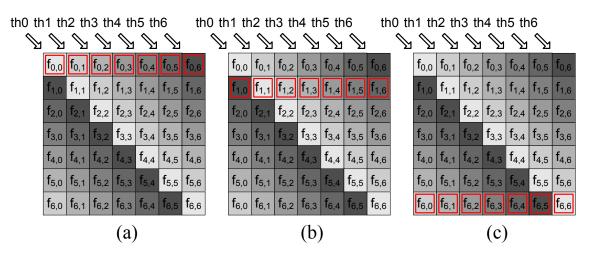

- 4.12 Input image of size N × N, N = 7. For the prime direction m = 0, pixels with the same grayscale level are added to compute one output pixel (radon space), i.e. 7 rays in parallel are computed. (a) 7 threads in parallel start computing 7 rays. Red boxes highlight the first pixel loaded for each thread. (b) Second set of pixels are highlighted.

(c) Last set of pixels are highlighted. Assuming the threads are syncronized, note that all threads read the same row of pixels. . . . 126

- 4.13 Input image of size N × N, N = 7. For the prime direction m = 1, pixels with the same grayscale level are added to compute one output pixel (radon space), i.e. 7 rays in parallel are computed. (a) 7 threads in parallel start computing 7 rays. Red boxes highlight the first pixel loaded for each thread. (b) Second set of pixels are highlighted.

(c) Last set of pixels are highlighted. Assuming the threads are synchronized, note that all threads read the same row of pixels. . . 126

- 4.14 Kernel algorithm for each core on the GPU to compute one ray of the forward Discrete Periodic Radon Transform R(m, d) of the image f(i, j) of size  $N \times N$ . R(m, d) is mapped to a vector radon[k] and f(i, j) is mapped to a vector img[k], both using row-major order. 127

- 4.15 Kernel algorithm for each core on the GPU to compute one ray of the inverse Discrete Periodic Radon Transform f(i, j) of the radon space R(m, d) of size  $(N + 1) \times N$ . R(m, d) is mapped to a vector radon[k]and f(i, j) is mapped to a vector img[k], both using row-major order. 128

- B.1 Required tree resources as a function of the number of strip rows or number of blocks (X), and the number of bits per pixel (B). Refer to Table ?? for definitions of  $A_{ff}, A_{FA}, A_{mux}$ . For  $A_{ff}$ , the resources do not include the input registers, but do include the output registers since they are implemented in SFDPRT\_core and iSFDPRT\_core. . . 145

- C.1 Required tree resources as a function of the zero padded image (N), and the number of bits per pixel (D). Refer to Table ?? for definitions of  $A_{ffb}, A_{FA}$ . Remove step ?? to compute  $A_{ff}$  (without input buffers) 146

## List of Tables

| 2.1 | Total number of clock cycles for computing the DPRT. In all cases,        |    |

|-----|---------------------------------------------------------------------------|----|

|     | the image is of size $N \times N$ , and $H = 2,, N$ is the scaling factor |    |

|     | for the SFDPRT                                                            | 60 |

- 2.3 Resource usage for different DPRT and inverse DPRT implementations. Here, consider an image size of  $N \times N$ , B bits per pixel,  $n = \lceil \log_2 N \rceil$ ,  $h = \lceil \log_2 H \rceil$ ,  $K = \lceil N/H \rceil$ , and H = 2, ..., N. For the adder trees, define  $A_{ff}$  to be number of required flip-flops, and  $A_{FA}$ to be the number of 1-bit additions. For the register array, define  $A_{mux}$ to be the number of 2-to-1 MUXes.  $A_{ff}$ ,  $A_{FA}$ , and  $A_{mux}$  grow linearly with respect to N and can be computed using the algorithm given in the appendix (Fig. ??). For the inverse DPRT, note that each divider is implemented using  $3(B + 2n)^2$  flip-flops,  $(B + 2n)^2$  1-bit additions, and  $(B + 2n)^2$  2-to-1 MUXes [3]. Here, the term "1-bit additions" refers to the number of equivalent 1-bit full adders. ...

| 2.4 | Total number of resources for RAM (in 1-bit cells) and MUXes (2- $$ |    |

|-----|---------------------------------------------------------------------|----|

|     | to-1 muxes). The resources are shown for $N = 251$ . Except for the |    |

|     | MUXes for the SFDPRT, the values refer to any $H$ . The number of   |    |

|     | MUXes for the SFDPRT refer to values of $H$ that lie on the Pareto  |    |

|     | $front^*$                                                           | 63 |

3.1 Resource usage for different 1-D Circular Convolutions implementations. Here, there are two zero padded images g and h of size  $N \times N$ , B and C bits per pixel respectively and  $n = \lceil \log_2 N \rceil$ . For the adder tree, it is defined  $A_{ffb}$  to be number of required flip-flops including input buffers, and  $A_{FA}$  to be the number of 1-bit additions.  $A_{ffb}$  and  $A_{FA}$  grow linearly with respect to N and can be computed using the algorithm given in the appendix (Fig. ??). For the multipliers, note that each one is implemented using two inputs of size B + n and C + n bits and an output of B + C + 2n bits. Here, the term "1-bit additions" refers to the number of equivalent 1-bit full adders. . . . . 89

- 3.3 Resource usage for different Linear Convolvers implementations. Here, all the quantities are given for maximum accuracy. For the adder tree, define  $A_{ffb}$  as the number of required flip-flops including input buffers, and  $A_{FA}$  to be the number of 1-bit additions.  $A_{ffb}$  and  $A_{FA}$  grow linearly with respect to Q2 and can be computed using the algorithm given in the appendix (Fig. ??). For the multipliers, note that each one is implemented using two inputs of size  $B + C + q^2$  and C bits and an output of  $B + 2C + q^2$  bits. Here, the term "1-bit additions" is used to refer to the number of equivalent 1-bit full adders. Recall  $N^2 = P^2 + Q^2 1$ .

- 3.4 Running time for a 2-D linear convolution between an image g(i, j)and a large non-separable kernel h(i, j) with rank r, both of size  $P \times P$ . The convolved result f(i, j) has a size of  $N \times N$ , where N = 2P - 1,  $n = \lceil \log_2 N \rceil$  and  $p = \lceil \log_2 P \rceil$ . For ScaSys P needs to be a composite number  $P = P_A \times P_B$ . For FFTr2, D = 1, ..., Nrepresents the number of 1-D FFT units running in parallel. . . . . 99

- 3.5 Resource usage for a 2-D linear convolution between an image g(i, j)and a large non-separable kernel h(i, j), both of size  $P \times P$ . The convolved result f(i, j) has a size of  $N \times N$ , where N = 2P - 1,  $n = \lceil \log_2 N \rceil$  and  $p = \lceil \log_2 P \rceil$ . For ScaSys P needs to be a composite number  $P = P_A \times P_B$ . Define  $A_{ffb}(a, b)$  to be number of required flip-flops inside the *a*-operand of *b* bits adder tree including input buffers,  $A_{ff}()$  without input buffers and  $A_{FA}()$  to be the number of 1-bit additions, all grow linearly with respect to N and can be computed using the algorithm given in the appendix (Fig. ??). . . . 102

- 3.6 Memory usage for a 2-D linear convolution between an image g(i, j)and a large non-separable kernel h(i, j) both of size  $64 \times 64$ . For ScaSys  $P_A = 2, 4, 8, 16. \ldots 104$

| 4.1 | Technical specifications for the GPU GM204, compute capability $5.2$ |     |

|-----|----------------------------------------------------------------------|-----|

|     | (Maxwell Architecture)                                               | 129 |

| 4.2 | Closest running time to 33.33ms for real time video applications of  |     |

|     | fSER, fCPU and fGPU $\hdots$                                         | 136 |

## Chapter 1

## Introduction

The Discrete Radon Transform (DRT) is an essential component of a wide range of applications in image processing [4, 5]. Applications of the DRT include the classic application of reconstructing objects from projections in computed tomography, radar imaging, and magnetic resonance imaging [4, 5]. Furthermore, the DRT has also been applied in image denoising [6], image restoration [7], texture analysis [8], line detection in images [9], and encryption [10]. More recently, the DRT has been applied in erasure coding in wireless communications [11], signal content delivery [12], and compressive sensing [13].

A popular method for computing the DRT involves the use of the Fast Fourier Transform (FFT). The basic approach is to sample the 2-D FFT along different radial lines through the origin and then use the 1-D inverse FFT along each line to estimate the DRT. This direct approach suffers from many artifacts that have been discussed in [6]. Assuming that the DRT is computed directly, Beylkin proposed an exact inversion algorithm in [14]. A significant improvement to this approach was proposed by Kelley and Madisetti by eliminating interpolation calculations [15].

The initial motivation of the current dissertation is to investigate the development of DPRT algorithms that are both fast and scalable. Here, I use the term *fast* to refer to the requirement that the computation will provide the result in the minimum number of cycles. Also, I use the term *scalable* to refer to the requirement that the approach will provide the fastest implementation based on the amounts of available resources. The dissertation also develops new, efficient, parallel algorithms for computing the DPRT and its inverse on GPUs and multi-core CPUs.

The scope of the dissertation was then expanded to cover convolution and crosscorrelation applications. The interest in convolution and cross-correlation is due to the fact that these operations are essential in a wide range of applications in the field of image and video processing. The performance of most image processing systems is directly affected by the speed at which we can perform 2-D convolutions. There is thus perennial interest in developing fast methods for computing 2-D convolutions. There is also renewed interest in developing fast convolution methods that can fit in new devices. The dissertation presents novel implementations of 2-D convolutions and cross-correlations that can be computed as fast as O(N) clock cycles provided that we have the available resources.

### 1.1 Thesis Statement

I believe that it is possible to develop fast and scalable architectures and algorithms for the computation of the Discrete Periodic Radon Transform (DPRT) and its inverse (iDPRT), that will enable the application of the DPRT in different areas where its use was limited due the lack of a fast implementation (e.g., in 2D convolutions and cross-correlations). Furthermore, I believe that it is possible to develop highly efficient, parallel DPRT and iDPRT algorithms on existing GPUs and multi-core CPUs.

### **1.2** Contributions

A list of the main contribution includes:

- A scalable and fast framework for computing the DPRT and its inverse. The dissertation develops a set of parallel algorithms and associated scalable architectures to compute the forward and inverse DPRT of an N × N image that allows effective implementations based on different constraints on running time and resources. In terms of resources and running time, the scalable framework provides optimal configurations in the multi-objective sense. In terms of performance, the fastest architecture computes the DPRT in linear time (with respect to N). This is the fastest implementation to date.

- A scalable and fast framework for computing convolutions and cross correlations for relatively large image sizes (of the order of the image size). Scalability

is based on the scalable DPRT framework, the scalable computation of 1D convolutions in the DPRT domain, LU decompositions, and the use of an overlap and add approach. Similar to the FFT, the DPRT can be used for computing linear convolutions using zero-padding. To compute 2-D linear convolutions between an image of size  $P_1 \times P_2$  and a relatively large (of the order of the image size) and non-separable kernel  $Q_1 \times Q_2$ , we can use DPRTs of size of  $N \times N$ where  $N = \text{NextPrime}(\text{max}(P_1+Q_1-1, P_2+Q_2-1))$ . In terms of resources and running time, each solution (by itself) is optimal in the multi-objective sense. When the rank of the non-separable kernel is low, the framework based on the LU decomposition becomes the optimal solution, and for high-rank kernels, the framework based on the DPRT is the optimal solution. In terms of performance, the fastest architecture based on the DPRT computes the 2-D linear convolution in linear time (with respect to N). And for low rank kernels, the fastest architecture based on the LU decomposition computes the 2-D linear convolution in linear time.

• A scalable and fast framework for computing the forward and inverse DPRT using GPUs and multi-coure CPUs. Scalability on the GPUs is a function of the number of multi-processors (MIMD) and their associated cores (SIMD). For the CPUs, scalability is a function of the number of cores (MIMD).

## 1.2.1 Specific contributions for the Scalable and Fast DPRT and its inverse

Specific contributions over the best previous algorithms, architectures and practical implementations of the DPRT are as follows:

- Fast and scalable architecture that can be adapted to available resources: The proposed approach is designed to be fast in the sense that column sums are computed on every clock cycle. In the fastest implementation, a prime direction of the FDPRT is computed on every clock cycle. More generally, the approach is scalable, allowing to handle larger images with limited computational resources.

- Pareto-optimal DPRT and iDPRT based on running time and resources: The proposed approach is shown to be Pareto-optimal in terms of the required cycles and required resources. Thus, as compared to previous approaches, the scalable approach provides the fastest known implementations for the given computational resources. As an example, in the fastest case, for an N×N image (N prime), the DPRT is computed in linear time (2N+[log<sub>2</sub>N]+1 clock cycles) requiring resources that grow quadratically (O(N<sup>2</sup>)). In the most limited resources case, the running time is quadratic ([N/2] (N + 9) + N + 2 clock cycles) requiring resources that grow linearly (O(N)). A Pareto-front of optimal solutions is given for resources that fall within these two extreme cases. All prior research in this area focused on the development of a single

architecture. Furthermore, when sharing comparable computational resources, the proposed approach is always better than previously published approaches. For example, in [2], the authors reported the fastest previous implementation that required  $N^2 + N + 1$  clock cycles requiring resources that grow quadratically with N. Similar results are obtained for the inverse DPRT, although results for this case were not previously reported.

- Fastest possible implementation of the FDPRT and iFDPRT: For the fastest case, it is shown that the scalable architecture can be further reduced to obtain the FDPRT and iFDPRT in  $2N + \lceil \log_2 N \rceil + 1$  and  $2N + 3 \lceil \log_2 N \rceil + B + 2$  cycles respectively (*B* is the number of bits used to represent each input pixel).

- Parallel and pipelined implementation: Parallel and pipelined implementations are proposed providing an improvement over the sequential algorithm proposed by [16] and used in [1],[2]. For H = 2,..., N, the scalable approach computes N × H additions in a single clock cycle. Furthermore, shift registers are used to make data available to the adders in every clock cycle. Then, additions and shifts are performed in parallel in the same clock cycle.

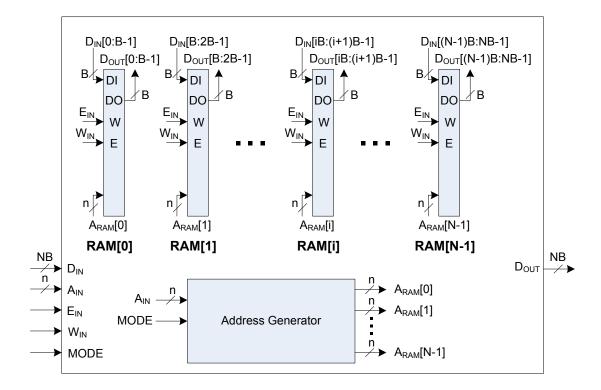

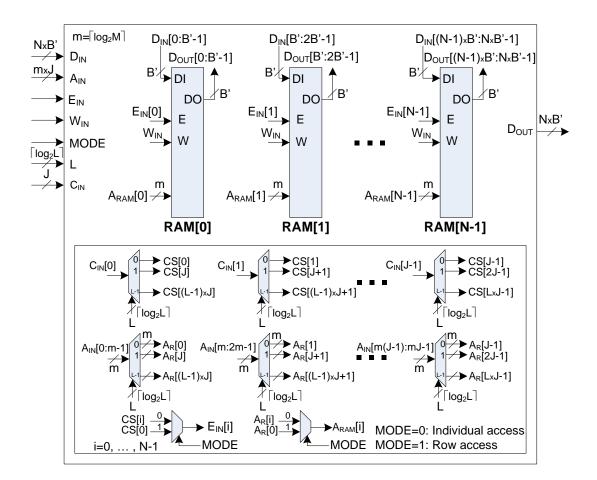

- Unique fast transposition method: A RAM-based architecture and associated algorithm that provides a complete row or column of the input image in one clock cycle. Using this parallel RAM access architecture, transposition is avoided since the image can be accessed by either rows or columns.

• Generic architectures: The proposed architectures are not tied to any particular hardware. They can be applied to any existing hardware (e.g., FPGA or VLSI).

# 1.2.2 Specific contributions for the Fast 2-D Convolutions and Cross-Correlations Using Scalable Architectures

The contributions are listed in terms of the DPRT and LU based methods. We begin with contributions for both the DPRT and LU frameworks and then present the specific contributions for each framework.

Specific contributions over the best previous 2-D convolution/cross-correlation systems for non-separable and relatively large kernels are as follows:

- Fast and scalable architectures that can be adapted to available resources for both frameworks: The proposed approaches are designed to be fast because of the mapping of 2-D convolutions into fast 1-D convolutions. For the DPRT framework, scalability comes from the control of the number of 1-D convolution kernels. For the LU framework, scalability comes from the separability of the kernels and its decomposition into low-rank 1D kernels. For the fastest implementations, a throughput of N convolved pixels per clock cycle is achieved.

- Pareto-optimal 2-D convolutions and cross-correlations based on running time and resources for both frameworks: The proposed ap-

proaches are shown to be Pareto-optimal in terms of the required cycles and required resources. Thus, as compared to previous approaches, the scalable approach provides the fastest known implementations for the given computational resources. For each framework, a Pareto-front of optimal solutions is given for resources that fall within the fastest and the slowest running time. The proposed approach is always better than previously published approaches for large and non-separable kernels.

- Generic architectures for both frameworks: The proposed architectures are not tied to any particular hardware. They can be implemented in an FPGA.

- Custom SRAM architectures to provide fast transposition and accumulation of the results for computing fast cross-correlations and the LU framework: The dissertation presents different RAM-based architectures and associated algorithms that allow access, storage or accumulation of the results from a row or column in a single clock cycle. Using the custom SRAM architectures, transposition is avoided since the partial results can be accessed by either rows or columns.

- Parallel and pipelined 1-D circular convolvers for the DPRT framework: The DPRT framework loads N pixels in a single clock cycle and computes one output pixel per clock cycle.

- Parallel and pipelined 1-D linear convolvers for LU framework: The LU framework loads a complete row of pixels in a single clock cycle and

computes one output pixel per clock cycle.

# 1.2.3 Specific contributions for the computation of the DP-RT and its inverse on multi-core CPUs and GPUs

The contributions are as follows:

- Parallel implementations of the DPRT and iDPRT on multi-core CPUs: The parallel implementations distribute processing of the prime directions among all the logical cores available. Compared to a serial (single-core) implementation, the proposed approach achieved a tenfold speedup with 16 logical cores (C and Pthreads implementation).

- New parallel and memory efficient DPRT and iDPRT implementations on GPUs: The proposed approach distributes the computation of the prime directions among the multiprocessors (MP). Within each MP, the rays associated with each prime direction are distributed among the cores. The proposed algorithms were coded in C/CUDA where: (i) parallel threads were synchronized to always read the same row of pixels at the same time, (ii) efficient memory access is achieved by enforcing row-major ordering for reads and writes, and (iii) further specific optimizations for the GPU Nvidia GeForce GTX980 were applied (pixel width, optimal concurrency of warps, fast address calculation and modulo operation masking). For 16 multi-process with 128 cores each, compared to a serial implementation, the speedup is of the order of 715 (max=853x for DPRT, max=873x for inverse DPRT).

### 1.3 Overview of Dissertation

This dissertation is organized into 5 chapters. The work described in each chapter is presented below.

Chapter 2 presents a new scalable approach to compute the DPRT and its inverse that balances the use hardware resources versus execution time.

Chapter 3 presents a fast and scalable framework for computing 2-D linear convolutions and cross-correlations for relatively large and non-separable kernels.

Chapter 4 presents new parallel algorithms for the computation of the forward and inverse DPRT on CPUs and GPUs. The proposed algorithms are implemented in currently available hardware.

Chapter 5 presents conclusions and future work.

Also, on the appendices I include a summary of my research (App. A), two algorithms for the computation of flip-flops, full adders and muxes in adder trees (App. B, C) and the source code for the CPU and GPU implementations of the DPRT and its inverse (App. D, E,F).

### Chapter 2

# Scalable Fast Discrete Periodic Radon Transform and its inverse

This chapter describes Fast and Scalable architectures and algorithms for computing the DPRT and its inverse (iFDPRT). The work presented here has been published in:

C. Carranza, D. Llamocca, and M. Pattichis, "Fast and scalable computation of the forward and inverse discrete periodic radon transform,", IEEE Transactions on Image Processing, vol. 25, no. 1, pp. 119-133, Jan 2016.

C. Carranza, D. Llamocca, and M. Pattichis, "A scalable architecture for implementing the fast discrete periodic radon transform for prime sized images," in 2014 IEEE International Conference on Image Processing (ICIP), Oct 2014, pp. 1208-1212.

C. Carranza, D. Llamocca, and M. Pattichis, "The fast discrete periodic radon

transform for prime sized images: Algorithm, architecture, and vlsi/fpga implementation," in 2014 IEEE Southwest Symposium on Image Analysis and Interpretation (SSIAI), April 2014, pp. 169-172.

In what follows, the content of the first journal have been merged with extracts of the other two in order to provide a better understanding to the reader.

The discrete periodic radon transform (DPRT) has been extensively used in applications that involve image reconstructions from projections. Beyond classic applications, the DPRT can also be used to compute fast convolutions that avoids the use of floating-point arithmetic associated with the use of the Fast Fourier Transform. Unfortunately, the use of the DPRT has been limited by the need to compute a large number of additions and the need for a large number of memory accesses.

This chapter introduces a fast and scalable approach for computing the forward and inverse DPRT that is based on the use of: (i) a parallel array of fixed-point adder trees, (ii) circular shift registers to remove the need for accessing external memory components when selecting the input data for the adder trees, (iii) an image block-based approach to DPRT computation that can fit the proposed architecture to available resources, and (iv) fast transpositions that are computed in one or a few clock cycles that do not depend on the size of the input image.

As a result, for an  $N \times N$  image (N prime), the proposed approach can compute up to  $N^2$  additions per clock cycle. Compared to previous approaches, the scalable approach provides the fastest known implementations for different amounts of computational resources. For example, for a 251 × 251 image, for approximately 25% fewer flip-flops than required for a systolic implementation, the scalable DPRT is computed 36 times faster. For the fastest case, optimized architectures are presented that can compute the DPRT and its inverse in just  $2N + \lceil \log_2 N \rceil + 1$  and  $2N + 3 \lceil \log_2 N \rceil + B + 2$  cycles respectively, where B is the number of bits used to represent each input pixel. On the other hand, the scalable DPRT approach requires more 1-bit additions than for the systolic implementation and provides a trade-off between speed and additional 1-bit additions.

### 2.1 Introduction

Fixed point implementations of the DRT can be based on the Discrete Periodic Radon Transform (DPRT). Grigoryan first introduced the forward DPRT algorithm for computing the 2-D Discrete Fourier Transform as discussed in [17]. In related work, Matus and Flusser presented a model for the DPRT and proposed a sequential algorithm for computing the DPRT and its inverse for prime sized images [16]. This research was extended by Hsung et al. for images of sizes that are powers of two [18].

Similar to the continuous-space Radon Transform, the DPRT satisfies discrete and periodic versions of the the Fourier slice theorem and the convolution property. Thus, the DPRT can lead to efficient, fixed-point arithmetic methods for computing circular and linear convolutions as discussed in [18]. The discrete version of the Fourier slice theorem provides a method for computing 2-D Discrete Fourier Transforms based on the DPRT and a minimal number of 1-D FFTs (e.g., [17, 19]).

A summary of DPRT architectures based on the algorithm described by [16] can

be found in [20]. In [16], the DPRT of an image of size  $N \times N$  (N prime) requires (N + 1)N(N - 1) additions. Based on the algorithm given in [16], a serial and power efficient architecture was proposed in [1]. In [1], the authors used an address generator to generate the pixels to add. The DPRT sums were computed using an accumulator adder that stores results from each projection using N shift registers. The serial architecture described in [1] required resources that grow linearly with the size of the image while requiring  $N(N^2 + 2N + 1)$  clock cycles to compute the full DPRT.

Also based on the algorithm given in [16], a systolic architecture implementation was proposed in [2]. The architecture used a systolic array of  $N(N+1)(\log_2 N)$  bits to store the addresses of the values to add. The pixels are added using using (N+1)loop adder blocks. The data I/O was handled by N + 1 dual-port RAMs. For this architecture, resource usage grows as  $O(N^2)$  at a reduced running time of  $N^2 + N + 1$ cycles for the full DPRT.

The motivation for the current chapter is to investigate the development of DPRT algorithms that are both fast and scalable. Recall that *fast* refers to the requirement that the computation will provide the result in the minimum number of cycles. On the other hand, *scalable* refers to the requirement that the approach will provide the fastest implementation based on the amounts of available resources.

This chapter is focused on the case that the image is of size  $N \times N$  and N is prime. For prime N, the DPRT provides the most efficient implementations by requiring the minimal number of N + 1 primal directions [21]. In contrast, there are 3N/2 primal

directions in the case that  $N = 2^p$  where p is a positive integer [22]. On the other hand, despite the additional directions, it is possible to compute the directional sums faster for  $N = 2^p$ , as discussed in [23, 24]. However, it is important to note that prime-numbered transforms have advantages in convolution applications. Here, just like for the Fast Fourier Transform (FFT), zero-padding can be used to extend the DPRT for computing convolutions in the transform domain. Unfortunately, when using the FFT with  $N = 2^p$ , zero-padding requires the use of FFTs with double the size of N. In this case, it is easy to see that the use of prime-numbered DPRTs is better since there are typically many prime numbers between  $2^p$  and  $2^{p+1}$ . For example, it can be shown that the *n*-th prime number is approximately  $n \log(n)$ which gives an approximate sequence of primes that are  $n \log(n), (n+1) \log(n+1)$ which is a lot more dense than what can be accomplished with powers of two  $2^n, 2^{n+1}$ [25]. As a numerical example, there are 168 primes that are less than 1000 as opposed to just 9 powers of 2. Thus, instead of doubling the size of the transform, It can be used a DPRT with only a slightly larger transform.

This chapter introduces a fast and scalable approach for computing the forward and inverse DPRT that is based on parallel shift and add operations. Preliminary results were presented in conference publications in [26, 27]. The conference paper implementations were focused on special cases of the full system discussed here, required an external system to add the partial sums, assumed pre-existing hardware for transpositions, and worked with image strip-sizes that were limited to powers of two. The current chapter includes: (i) a comprehensive presentation of the theory and algorithms, (ii) extensive validation that does not require external hardware for partial sums and transpositions, (iii) works with arbitrary image strip sizes, and also includes (iv) the inverse DPRT. In terms of the general theory presented in this chapter, the conference paper publications represented some special cases. The contributions of the current chapter over previously proposed approaches are summarized in the following paragraphs.

Overall, a fundamental contribution of the chapter is that it provides a fast and scalable architecture that can be adapted to available resources. The approach is designed to be fast in the sense that column sums are computed on every clock cycle. In the fastest implementation, a prime direction of the DPRT is computed on every clock cycle. More generally, the approach is scalable, allowing to handle larger images with limited computational resources.

Furthermore, this chapter provides a Pareto-optimal DPRT and inverse DPRT based on running time and resources measured in terms of one-bit additions (or 1-bit full-adders) and flip-flops. Thus, the proposed approach is shown to be Paretooptimal in terms of the required cycles and required resources. Here, Pareto-optimality refers to solutions that are optimal in a multi-objective sense (e.g., see [28]). Thus, in the current application, Pareto-optimality refers to the fact that the scalable approach provides the fastest known implementations for the given computational resources. As an example, in the fastest case, for an  $N \times N$  image (N prime), the DPRT is computed in linear time  $(2N + \lceil \log_2 N \rceil + 1 \text{ clock cycles})$  requiring resources that grow quadratically ( $O(N^2)$ ). In the most limited resources case, the running time is quadratic ( $\lceil N/2 \rceil (N + 9) + N + 2$  clock cycles) requiring resources that grow linearly (O(N)). A Pareto-front of optimal solutions is given for resources that fall within these two extreme cases. All prior research in this area focused on the development of a single architecture. Similar results are obtained for the inverse DPRT, although results for this case were not previously reported.

In terms of speed, this chapter describes the fastest possible implementation of the DPRT and inverse DPRT. For the fastest cases, assuming sufficient resources for implementation, the fast DPRT (FDPRT) and the fast inverse DPRT (iFDPRT) are introduced to compute the full transforms in  $2N + \lceil \log_2 N \rceil + 1$  and  $2N + 3 \lceil \log_2 N \rceil + B + 2$  cycles respectively (*B* is the number of bits used to represent each input pixel).

To achieve the performance claims, parallel and pipelined implementations are described providing an improvement over the sequential algorithm proposed by [16] and used in [1],[2]. To summarize the performance claims, let the  $N \times N$  input image be sub-divided into strips of H rows of pixels. Then, for H = 2, ..., (N - 1)/2, this scalable approach computes  $N \times H$  additions in a single clock cycle. Furthermore, shift registers are used to make data available to the adders in every clock cycle. Then, additions and shifts are performed in parallel in the same clock cycle.

In addition, the use of fast transpositions is presented. A unique transpositions method is proposed based on a RAM-based architecture and associated algorithm that provides a complete row or column of the input image in one clock cycle. Using this parallel RAM access architecture, transposition is avoided since the image can be accessed by either rows or columns.

Finally, a generic family of architectures is provided. Thus, the proposed archi-

tectures are not tied to any particular hardware. They can be applied to any existing hardware (e.g., FPGA or VLSI).

The rest of the chapter is organized as follows. The mathematical definitions for the DPRT and its inverse along with previous DPRT implementations are given in section 2.2. The proposed approach is given in section 2.3. Section 2.4 describes the architecture implementation details. Section 2.6 presents the results. Conclusions and future work are given in section 2.7.

### 2.2 Background

The purpose of this section is to introduce the basic definitions associated with the DPRT and provide a very brief summary of previous implementations. The notation is introduced in section 2.2.1. Then the definitions of the DPRT and its inverse are produced in section 2.2.2. A summary of previous implementations is given in section 2.2.3.

#### 2.2.1 Notation summary

Consider  $N \times N$  images where N is prime. Let  $Z_N$  denote the non-negative integers: {0,1,2,..., N-1}, and  $l^2(Z_N^2)$  be the set of square-summable functions over  $Z_N^2$ . Then, let  $f \in l^2(Z_N^2)$  be a 2-D discrete function that represents an  $N \times N$  image, where each pixel is a positive integer value represented with B bits. Also, subscripts are used to represent rows. For example,  $f_k(j)$  denotes the vector that consists of the elements of f where the value of k is fixed. Similarly, for R(r, m, d),  $R_{r,m}(d)$ denotes the vector that consists of the elements of R with fixed values for r, m. Here, note that all but the last index is fixed.  $\langle \alpha \rangle_{\beta}$  is used to denote the modulo function. In other words,  $\langle \alpha \rangle_{\beta}$  denotes the positive remainder when  $\alpha$  is divided by  $\beta$  where  $\alpha, \beta > 0$ .

To establish the notation, consider the following an example. For an  $251 \times 251$ 8-bit image, we have N = 251, B = 8, and f represents the image. Then,  $f_1(j)$ represents the row number one in the image. In 3-dimensions,  $R_{1,2}(d)$  denotes the elements R(r = 1, m = 2, d), where d id allowed to vary. For the modulo-notation,  $\langle 255 \rangle_{251} = 4$  represents the integral remainder when 255 is divided by N = 251. R(m, d) is used to denote the DPRT of f and R'(r, m, d) to index the r-th partial sum associated with R(m, d). Here, R' is used for explaining the computations associated with the scalable DPRT.

#### 2.2.2 Discrete Periodic Radon Transform and its Inverse

The definition of the DPRT and its inverse (iDPRT) based on [18] is given as follows. Let f be square-summable. The DPRT of f is also square summable and given by:

$$R(m,d) = \begin{cases} \sum_{i=0}^{N-1} f(i, \langle d+mi \rangle_N), & 0 \le m < N, \\ \\ \\ \sum_{j=0}^{N-1} f(d,j), & m = N, \end{cases}$$

(2.1)

where  $d \in Z_N$  and  $m \in Z_{N+1}$ . The row vector k of R(m, d) is denoted as  $R_k(d)$ which represents the k projection of f(i, j). Fig. 2.1 provides an illustration of the

Figure 2.1: Illustration of the DPRT and its iDPRT for a function f of size  $N \times N$ , where N is prime. Each row of R(m, d), denoted as a vector  $R_k(d)$ ,  $k = 0, \ldots, N$ , represents a projection of f(i, j).

DPRT applied to a discrete image f(i, j) of size  $N \times N$ , where N is prime; also the k projection of f(i, j),  $R_k(d)$ , is shown, k = 0, ..., N.

Observe that the summations in (2.1) are done over the discrete periodic line segment parameterized by  $(i, \langle d + mi \rangle_N)$  for the projections captured with  $0 \leq m < N$  and (d, j) for the projection captured with m = N. The projections are given along the directional vectors (1, m) for  $0 \leq m < N$  and (0, 1) for m = N which represent the prime directions. The prime directions of an  $7 \times 7$  image f(i, j) are shown in Fig. 2.2(a), and an example of one periodic line segment (defined by the prime direction (1,2)) used to compute R(2,0) is shown in Fig. 2.2(b).

The iDPRT recovers the input image as given by:

$$f(i,j) = \frac{1}{N} \left[ \sum_{m=0}^{N-1} R(m, \langle j - mi \rangle_N) - S + R(N,i) \right]$$

(2.2)

Figure 2.2: DPRT Example for a  $7 \times 7$  image. (a) Prime directions; (b) Main image (at center with bold boxes) and its periodic extensions. Pixels marked with  $\times$ : samples along periodic line for prime direction (1, 2), pixels marked with  $\times$  in grey boxes are added to compute R(2, 0)

where:

$$S = \sum_{j=0}^{N-1} \sum_{i=0}^{N-1} f(i,j).$$

(2.3)

From (2.3), it is clear that S represents the sum of all of the pixels. Since each projection computes the sums over a single direction, the results can be added from any one of these directions to compute S as given by:

$$S = \sum_{d=0}^{N-1} R(m, d).$$

(2.4)

Note that the DPRT as given by (2.1) requires the computation of N + 1 projections. All of these projections are used in the computation of iDPRT as given in (2.2). In (2.2), the last projection computes R(N, i) that is needed in the summation.

#### 2.2.3 previous DPRT implementations

DPRT implementations have focused on implementing the algorithm proposed in [16]. The basic algorithm is sequential that relies on computing the indices i, j to access f(i, j) that are needed for the additions in (2.1). For each prime direction, as shown in (2.1), the basic implementation requires  $N^2$  memory accesses and N(N-1)additions. For computing all of the prime directions  $(N + 1), (N + 1)N^2$  memory accesses and (N + 1)N(N - 1) additions are required.

Based on [16], hardware implementations have focused on computing memory indices, followed by the necessary additions [1], [2]. An advantage of the serial architecture given in [1] is that it requires hardware resources that grow linearly with N (for and  $N \times N$  image). Unfortunately, this serial architecture leads to slow computation since it computes the DPRT in a cubic number of cycles ( $N(N^2+2N+1)$ clock cycles). A much faster, systolic array implementation was presented in [2]. The systolic array implementation computes N indices and N additions per cycle. Overall, the systolic array implementation requires hardware resources that grow quadratically with N while requiring  $N^2 + N + 1$  clock cycles to compute the full DPRT.

The proposed architecture does not require memory indexing and computes the additions in parallel. Furthermore, the new architecture is scalable, and thus allows to consider a family of very efficient architectures that can also be implemented with limited resources.

Figure 2.3: Scalable DPRT concept. The input image is divided into K strips. The DPRT is computed by accumulating the partial sums from each strip.

### 2.3 Methodology

This section presents a new fast algorithm and associated scalable architecture that can be used to control the running time and hardware resources required for the computation of the DPRT. Additionally, the approach to the inverse DPRT (iDPRT) is extended. At the end of the section, an optimized architecture implementation that computes the DPRT and iDPRT in the least number of clock cycles is provided

#### 2.3.1 Partial DPRT

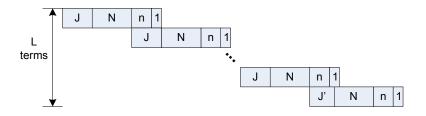

For the development of scalable architecture implementations, the concept of the partial DPRT is introduced. The basic concept is demonstrated in Fig. 2.3 and formally defined below.

The idea is to divide f into strips that contain H rows of pixels except for the last one that is composed of the remaining number of rows needed to cover all of the

N rows (see Fig. 2.3). Here, note that the height of the last strip will be  $\langle N \rangle_H \neq 0$ since N is prime. Now, let K be the number of strips, then  $K = \lceil N/H \rceil$ . In what follows, let r denote the r-th strip. the DPRT over each strip is computed using:

$$R(m,d) = \begin{cases} \sum_{r=0}^{K-1} \sum_{i=0}^{L(r)-1} f(i+rH, \langle d+m(i+rH) \rangle_N), \\ 0 \le m < N \\ \sum_{r=0}^{K-1} \sum_{j=0}^{L-1} f(d, j+rH), \\ \sum_{r=0}^{K-1} \sum_{j=0}^{L-1} f(d, j+rH), \\ m = N \end{cases}$$

(2.5)

where

$$L(r) = \begin{cases} H, & r < K - 1 \\ & & \\ \langle N \rangle_H & r = K - 1. \end{cases}$$

(2.6)

Let R'(r, m, d) denote the r-th partial DPRT defined by:

where, r = 0, ..., K - 1 is the strip number. Therefore, the DPRT can be computed as a summation of partial DPRTs using:

$$R(m,d) = \sum_{r=0}^{K-1} R'(r,m,d).$$

(2.8)

Similarly, the partial iDPRT of R(m, d) is defined using

$$f'(r, i, j) = \sum_{m=0}^{L(r)-1} R(m + rH, \langle j - i(m + rH) \rangle_N)$$

(2.9)

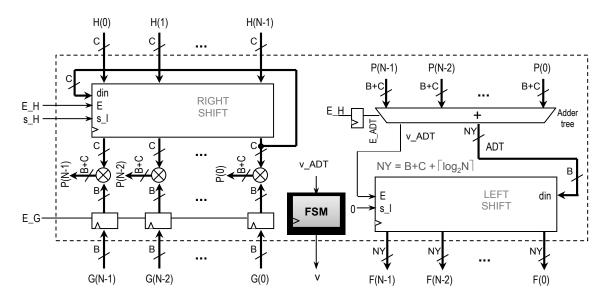

Figure 2.4: Top level system for implementing the Scalable and Fast DPRT (SFD-PRT). The SFDPRT\_core computes the partial sums. MEM\_IN and MEM\_OUT are dual port input and output memories. A Finite State Machine (FSM, not shown in the figure) is needed for control. See text in Sec. 2.3.2 for more details.

which allows to compute the iDPRT of R(m, d) using a summation of partial iDPRTs:

$$f(i,j) = \frac{1}{N} \left[ \sum_{r=0}^{K-1} f'(r,i,j) - S + R(N,i) \right].$$

(2.10)

In what follows, let  $n = \lceil \log_2 N \rceil$ ,  $h = \lceil \log_2 H \rceil$ , and  $R'_{r,m}(d)$  be an N-th dimensional vector representing the partial DPRT of strip r.

# 2.3.2 Scalable Fast Discrete Periodic Radon Transform (SF-DPRT)

In this section, the scalable DPRT hardware architecture is developed by implementing the partial DPRT concepts presented in Fig. 2.3. The top-level view of the hardware architecture for the scalable DPRT is presented in Fig. 2.4 and the associated algorithm in Fig. 2.5. Refer to Fig. 2.3 for the basic concepts. The basic idea is to achieve scalability by controlling the number of rows used in each rectangular strip. Thus, for the fastest performance, the largest pareto-optimal strip size that can be implemented using available hardware resources is chosen. The final result is computed by combining the DPRTs as given in (2.7).

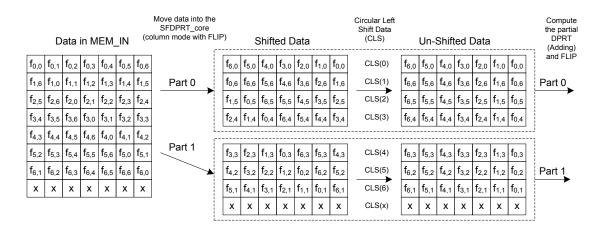

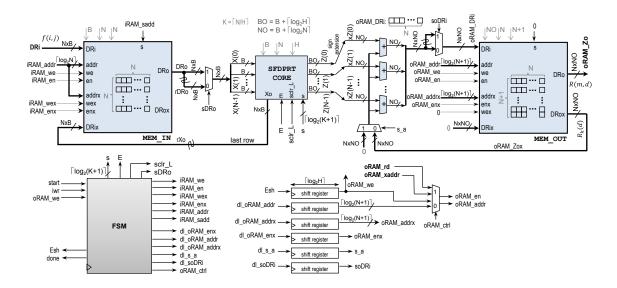

An overview of the architecture is presented in Fig. 2.4. Here, we have three basic hardware blocks: the input memory block (MEM\_IN), the partial DPRT computation block (SFDPRT\_core), and output/accumulator memory block (MEM\_OUT). The input image f is loaded into the input buffer MEM\_IN which can be implemented using a customized RAM that supports access to each image row or column in a single clock cycle. Partial DPRT computation is performed using the SFDPRT\_core. SFDPRT\_core is implemented using an  $H \times N$  register array with B bits depth so as to be able to store the contents of a single strip. Each row of the SFDPRT\_core register array is implemented using a Circular Left Shift (CLS) register that can be used to align the image samples along each column. Each column of this array has a *H*-operand fully pipelined adder tree capable to add the complete column in one clock cycle. The output of the adder trees provide the output of the SFDPRT\_core, which represents the partial DPRT of f. This combination of shift registers and adders allows the computation of  $H \times N$  additions per clock cycle with a latency of h. At the end, the outputs of the SFDPRT\_core are accumulated using MEM\_OUT. The required computational resources are summarized in section 2.6.

A fast algorithm for computing the DPRT is summarized in Fig. 2.5. Also a detailed timing diagram for each of the steps is presented in Fig. 2.6. For the timing diagram, note that time increases to the right. Along the columns, each step and the required number of cycles is labeled. Furthermore, computations that occur in parallel will appear along the same column. To understand the timing for each

```