# University of New Mexico UNM Digital Repository

Computer Science ETDs

**Engineering ETDs**

12-1-2009

# Using ant colony optimization for routing in microprocesors

Tamanna Arora

Follow this and additional works at: https://digitalrepository.unm.edu/cs\_etds

### Recommended Citation

Arora, Tamanna. "Using ant colony optimization for routing in microprocesors." (2009). https://digitalrepository.unm.edu/cs\_etds/ 72

This Thesis is brought to you for free and open access by the Engineering ETDs at UNM Digital Repository. It has been accepted for inclusion in Computer Science ETDs by an authorized administrator of UNM Digital Repository. For more information, please contact disc@unm.edu.

| Tamanna Arora                                                                   |                         |

|---------------------------------------------------------------------------------|-------------------------|

| Computer Science                                                                |                         |

| This thesis is approved, and form for publication <i>Approved by the Thesis</i> |                         |

| sst Prof Melanie Mos                                                            | es Autolia , Chairperso |

| rof. George F Luger                                                             | Searge L. Dry           |

| Prof. Payman Zarkesh-I                                                          | ta within Zahle         |

|                                                                                 |                         |

|                                                                                 |                         |

|                                                                                 |                         |

|                                                                                 |                         |

|                                                                                 |                         |

|                                                                                 |                         |

# USING ANT COLONY OPTIMIZATION FOR ROUTING IN MICROPROCESSORS

BY

TAMANNA ARORA

B.E, COMPUTER SCIENCE, INDRAPRASTHA UNIVERSITY, 2007

# **THESIS**

Submitted in Partial Fulfillment of the Requirement for the Degree of

**Master of Science Computer Science**

The University of New Mexico Albuquerque, New Mexico

December, 2009

# **ACKNOWLEDGMENTS**

"If I have seen further it is by standing on the shoulders of giants."

— Isaac Newton, Letter to Robert Hooke, February 5, 1675

First and foremost I offer my sincerest gratitude to, Dr. Melanie Moses, my advisor and committee chair for recognizing my commitment and honoring me with the research assistantship; for her guidance, support and patience, in mentoring me towards the completion of this research. I appreciate her organized approach of teaching the subject with practical relevance and the time she has dedicated to help me in understanding the fundamentals. I feel that one of the most important and sometimes difficult steps in learning how to conduct research is to decide how to formulate problems, work independently, and to set goals for oneself. She has constantly helped me with all these aspects. I owe her special thanks to help me write my papers and thesis and her invaluable suggestions that helped me clarify and better articulate my ideas. Your guidance will continue to encourage me in my future endeavors.

I would like to extend sincere thanks to Prof. Alan L. Davis and Mike A. Lodder for answering all my questions and doubts that I had, while I explored the topic in the thesis further. They also provided the data necessary for understanding the scope of the problem.

I also want to thank Prof. Payman Zarkesh for his constant support, for answering my numerous questions and all the help he has offered during the course of my thesis. He has always offered his expert comments from his experience in the field of VLSI. He has

also constantly helped me to make sure that my understanding of this VLSI problem and the solution is correct.

I am extremely grateful to Prof. George Luger who allowed me to simply come and talk to him about my research. I was glad to have talked to him about my ideas. It was during these discussions that I was able to think about the problem from various different perspectives. He provided his valuable guidance and feedback about my approach and insight into new possibilities. You have always been a source of moral support, encouragement and enlightenment.

I feel it necessary to mention also the friends who have been with me in the past few years. I am extremely thankful for all your support and encouragement that has pushed me to succeed.

Finally, I would like to thank my brother and my parents for their constant support over the years. The encouragement and love that they have selflessly and tirelessly invested in me is undoubtedly the greatest source of my ambition, inspiration, dedication and motivation. They have taught me far more than words can express.

# USING ANT COLONY OPTIMIZATION FOR ROUTING IN MICROPROCESSORS

$\mathbf{BY}$

# TAMANNA ARORA

# **ABSTRACT OF THESIS**

Submitted in Partial Fulfillment of the Requirements for the Degree of

**Master of Science Computer Science**

The University of New Mexico Albuquerque, New Mexico

December, 2009

# USING ANT COLONY OPTIMIZATION FOR ROUTING IN MICROPROCESSORS

by

#### Tamanna Arora

B.E., Computer Science, Indraprastha University, 2007M.S., Computer Science, University of New Mexico, 2009

#### **Abstract**

Power consumption is an important constraint on VLSI systems. With the advancement in technology, it is now possible to pack a large range of functionalities into VLSI devices. Hence it is important to find out ways to utilize these functionalities with optimized power consumption. This work focuses on curbing power consumption at the design stage. This work emphasizes minimizing active power consumption by minimizing the load capacitance of the chip. Capacitance of wires and vias can be minimized using Ant Colony Optimization (ACO) algorithms. ACO provides a multi agent framework for combinatorial optimization problems and hence is used to handle multiple constraints of minimizing wire-length and vias to achieve the goal of minimizing capacitance and hence power consumption. The ACO developed here is able to achieve an 8% reduction of wire-length and 7% reduction in vias thereby providing a 7% reduction in total capacitance, compared to other state of the art routers.

# **TABLE OF CONTENTS**

| LIST | r <b>of</b> 1 | FIGURESx                      |

|------|---------------|-------------------------------|

| LIST | r <b>OF</b> ' | ΓABLESxiii                    |

|      |               |                               |

| СНА  | PTE           | R 1 Introduction              |

|      | 1.1           | Technological Advances        |

|      | 1.2           | The Routing Problem.          |

|      | 1.3           | Problem Formulation           |

|      | 1.4           | Routing Benchmark and Format5 |

|      | 1.5           | Ant Colony Optimization       |

|      |               |                               |

| СНА  | PTE           | R 2 Previous Work             |

|      | 2.1           | Detailed Routing9             |

|      | 2.2           | Routing Models                |

|      | 2.3           | Routing Algorithms            |

|      |               | 2.3.1 Multi Layer Routing     |

|      |               | 2.3.2 Academic Routers        |

|      | 2.4           | Tradition Approaches          |

|      | 2.5           | ACO Metaheuristic             |

|      |               | 2.5.1 Problem Representation  |

|      |               | 2.5.2 Ants Approach           |

|      |               | 2.5.3 Ant Colony System       |

|     |     | 2.5.4   | Steiner Trees for VLSI Routing                      | 30 |

|-----|-----|---------|-----------------------------------------------------|----|

|     |     |         |                                                     |    |

| СНА | PTE | R 3 AN  | Γ Colony System for VLSI Routing                    | 32 |

|     | 3.1 | ISPD    | 98 Benchmark Suite                                  | 32 |

|     | 3.2 | ACO     | Algorithm for Manhattan Routing - Model Formulation | 34 |

|     | 3.3 | ACO     | Algorithm for Manhattan Routing (ACO-Route)         | 36 |

|     |     | 3.3.1   | Create Manhattan Grid                               | 36 |

|     |     | 3.3.2   | Sort Nets.                                          | 40 |

|     |     | 3.3.3   | Route Nets                                          | 41 |

|     |     | 3.3.4   | Ordering Problem                                    | 46 |

|     |     | 3.3.5   | Un-routable Nets                                    | 47 |

|     | 3.4 | ACO     | Algorithm for Non-Manhattan Routing                 | 51 |

|     |     | 3.4.1   | Grid Based Approach                                 | 52 |

|     |     | 3.4.2   | Sort Nets                                           | 54 |

|     |     |         |                                                     |    |

|     |     |         |                                                     |    |

| СНА | PTE | R 4 Res | ults and Discussions                                | 55 |

|     | 4.1 | ACO     | Parameter                                           | 55 |

|     |     | 4.1.1   | Search Parameters                                   | 55 |

|     |     | 4.1.2   | Number of Ants                                      | 58 |

|     | 4.2 | ACO     | Algorithm                                           | 60 |

|     |     | 4.2.1   | Results: ACO Route                                  | 60 |

|     |     | 4.2.2   | Results:ACO-NMRoute                                 | 69 |

|     | 4.3 | Verifi  | cation                                              | 72 |

|    | 4.4    | Discussion                      | 74 |

|----|--------|---------------------------------|----|

| СН | IAPTEI | R 5 Conclusion and Future Scope | 77 |

| AP | PENDI  | X                               | 82 |

| RF | FEREN  | JCFS                            | 91 |

# **List of Figures**

| 2.1 | (a) Symmetric Grid (b) Asymmetric Grid12                                             |

|-----|--------------------------------------------------------------------------------------|

| 2.2 | An example of cell, net and pins of cell                                             |

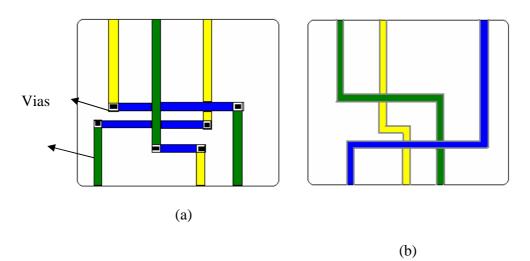

| 2.3 | Vertical and Horizontal Layers connected by vias                                     |

| 2.4 | (a) Grid Based (b) Gridless Model                                                    |

| 2.5 | (a) Layered Model (b) Unreserved Layer Model14                                       |

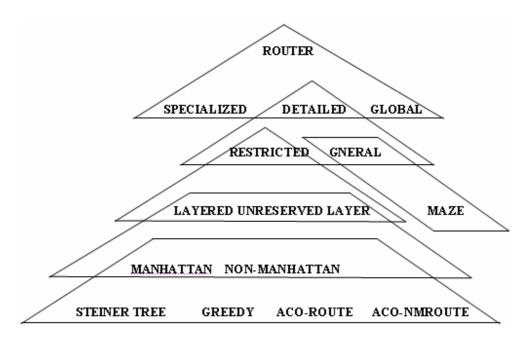

| 2.6 | Routing Hierarchy. 16                                                                |

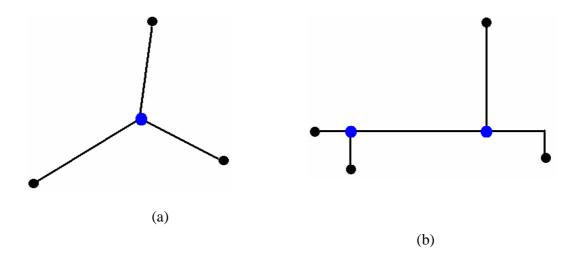

| 2.7 | (a) An example of Steiner tree where blue points represents Steiner points. (b) An   |

|     | example of rectilinear minimal Steiner tree                                          |

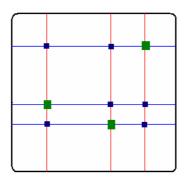

| 3.1 | A Hanan grid formed by three terminal nodes of a net (green nodes). Blue nodes       |

|     | are formed by the intersection of Hanan grid lines                                   |

| 3.2 | The figure shows the pin locations chosen on the grid. If more than one pin is       |

|     | used, the left and right grid locations are used. For every additional pin location; |

|     | first the upper left and right locations are used followed by lower left and right.  |

|     | 37                                                                                   |

| 3.3 | The graph shows the number of pins used by different components in benchmark         |

|     | chips                                                                                |

| 3.4 | (a) Shows three nodes to be routed to form a net. (b) Shows formation of a Hanan     |

|     | grid. (c) Shows the layered model of the Hanan grid with two horizontal (blue)       |

|     | and two vertical (red) layers                                                        |

| 3.5 | Perimeter of the given net is 2(A+B) where A and B is the manhattan distance         |

|     | between minimum and maximum x and y coordinates of components                        |

|     | respectively41                                                                       |

| 3.6  | (a), (b) and (c) shows a step by step procedure of routing using the                   |

|------|----------------------------------------------------------------------------------------|

|      | heuristic makes ants meet soon. A net consisting three nodes 1, 2 and 3 is shown.      |

|      | Ants start from these nodes and choose the next node using the                         |

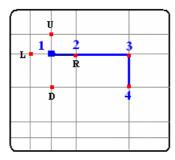

| 3.7  | At every step Manhattan architecture allows four possible directions in which an       |

|      | ant could move                                                                         |

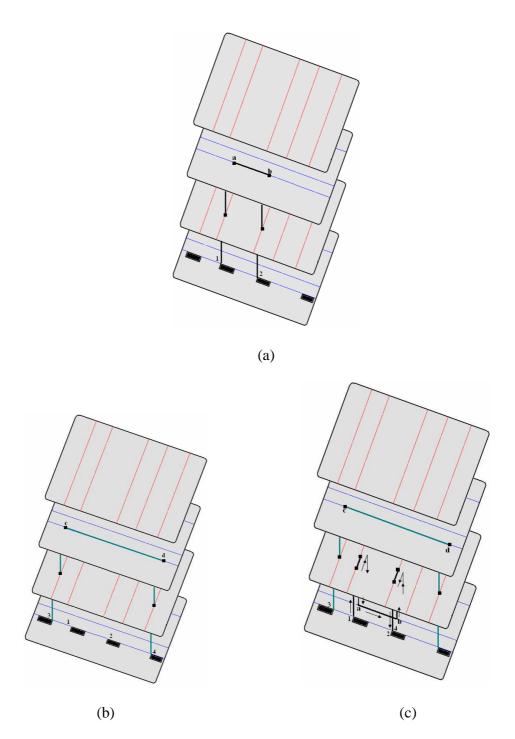

| 3.8  | A routed net connecting terminal 1 and 2. (b) Route found using ACO-Route to           |

|      | connect terminal 3 and 4. (c) As the two routes overlap the route connecting           |

|      | terminal 1 and 2 is shifted to another horizontal route on the first layer to make     |

|      | space for the route connecting terminal 3 and 4                                        |

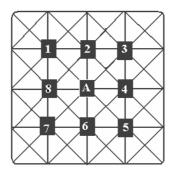

| 3.9  | Eight possible neighbors of node A51                                                   |

| 3.10 | Effect of diagonal routing on wire-length51                                            |

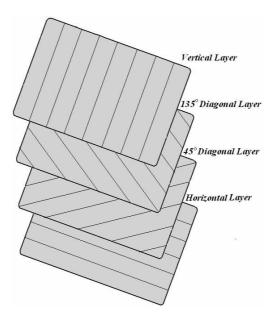

| 3.11 | An example of diagonal routing showing four layers: horizontal, vertical, $45^{\circ}$ |

|      | diagonal and 135° diagonal layer                                                       |

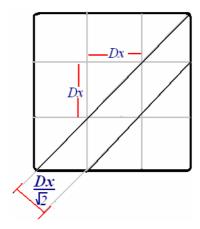

| 3.12 | The distance between two diagonals defines the pitch in the non-manhattan              |

|      | routing54                                                                              |

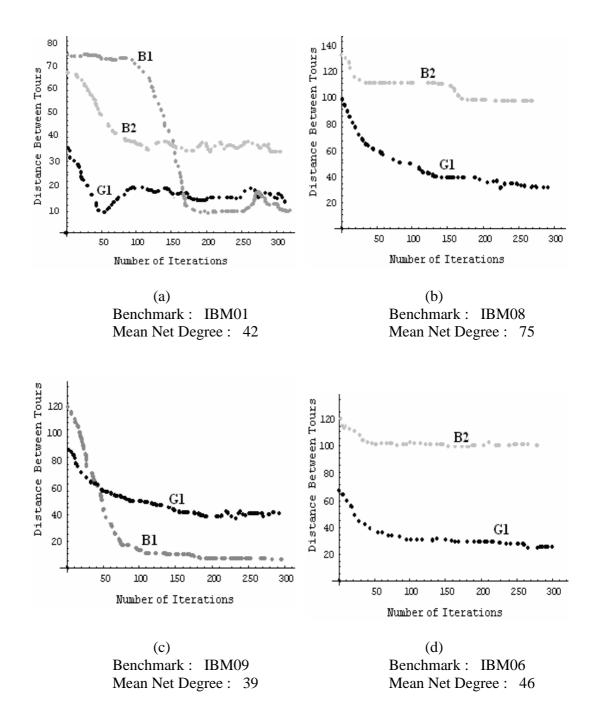

| 4.1  | Graphs showing change in distance between tours with the iterations of the             |

|      | algorithm with different sets of parameter values. (The distance between tours is      |

|      | measured as the number of arcs contained in one tour but not in another.)57            |

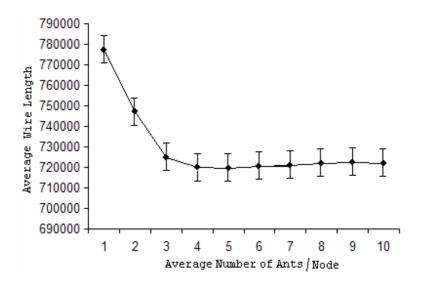

| 4.2  | Comparison of average Wire-Length Computed by algorithm with increase in               |

|      | average number of ants per node                                                        |

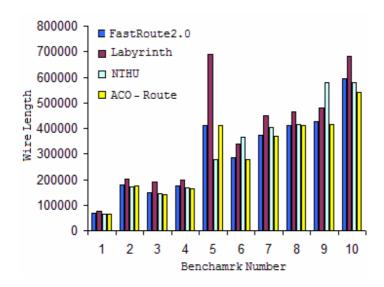

| 4.3  | Comparison of wire-length computed by Fast Route2.0, Labyrinth Router, NTHU            |

|      | and ACO-Route                                                                          |

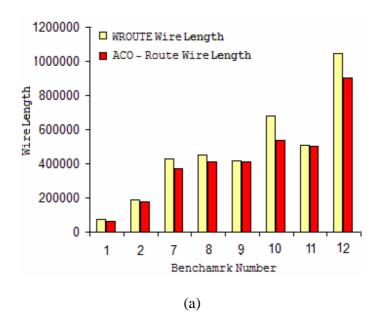

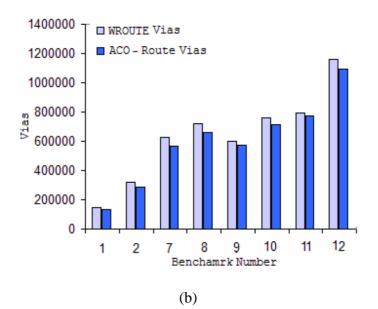

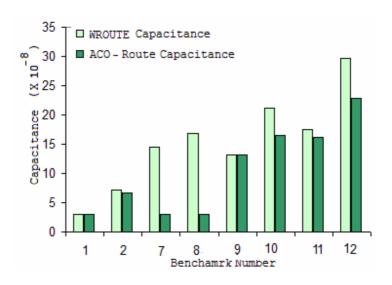

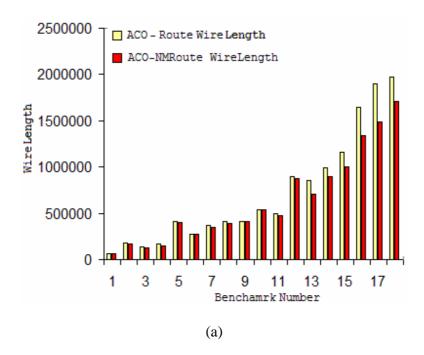

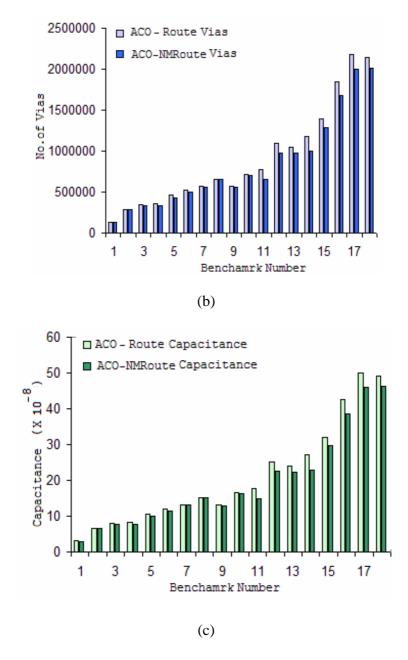

| 4.4 | Comparison of (a) wire-length (b) vias and (c) capacitance computed by ACO- |

|-----|-----------------------------------------------------------------------------|

|     | Route and WROUTE68                                                          |

| 4.5 | Comparison of (a) wire-length, (b) vias and (c) capacitance computed by ACO |

|     | Route and ACO-NMRoute71                                                     |

| A.1 | Representation of various possible orientations of a component on a chip87  |

# **List of Tables**

| 4.1  | Different Sets of Parameter Values used in graphs below                      |

|------|------------------------------------------------------------------------------|

| 4.2  | Value of ACO Parameters used in ACO Algorithm60                              |

| 4.3  | Number of Nets Routed using Alternate Strategy61                             |

| 4.4  | Wire -Length and Vias After All Nets Are Routed                              |

| 4.5  | Comparison of ACO-Route with Labyrinth and Fast Router63                     |

| 4.6  | Percentage improvement obtained by ACO-Route over Labyrinth Router, Fast     |

|      | Route 2.0 and NTHU Router                                                    |

| 4.7  | Comparison of Number of Vias, Wire-Length and Capacitance Computed By        |

|      | ACO-Route and WROUTE66                                                       |

| 4.8  | Percentage improvement obtained by ACO-Route over WROUTE68                   |

| 4.9  | Wire-Length and Vias Computed By ACO-NMRoute69                               |

| 4.10 | Comparison of ACO-Route Wire-Length with Half-Perimeter Wire-Length73        |

| 4.11 | Reduction in number of nets routed using alternate routing strategy when the |

|      | number of routing layers is increased from four to six74                     |

| 4.12 | Scaling Coefficients76                                                       |

| A.1  | IBM ISPD98 Benchmark Suite Details90                                         |

# CHAPTER 1

# Introduction

# 1.1 Technological Advances

Rapid advances in VLSI technology have increased the number of transistors that can be placed on a single chip to about two billion [1]. Such advances in technology simultaneously decrease chip cost [2, 3] and increase information processing power of chip. The processing power of the chip is the result of switching transistors i.e. the process of charging and discharging. Every time a transistor switches, power is consumed by the chip. With each process generation, the transistors have shrink in size and can be switched quickly. This increased switching capacity combined with an increase in number of transistors leads to increased power consumption by the chip [4]. Thus, power efficient designs are key goals in current VLSI design.

Power dissipation in a VLSI circuit consists of the two major components: static power and dynamic power [5]. Static power component is due to the leakage current drawn continuously from the power supply. A small amount of current leaks through the transistor even when it is switched off. This is known as leakage current. The major component of power is dynamic power. The dynamic power component is dependent on the supply voltage, the load capacitances and the frequency of the operation. One of the components of load capacitance is the wire capacitance. Wires are used to connect various components on a chip and hence define all the operations to be performed on the

chip. The large resistance of wires causes a voltage drop between the source and drain leading to sub threshold leakage which causes a power drain.

Moreover as device dimensions have scaled down, wires are spaced closer together which has increased wire capacitance relative to gate capacitance [6].

A study conducted at Berkley [7] shows that 60-70% of the total chip power is consumed by transistors and the remaining 30-40% power is dissipated in the form of heat and capacitance through wires and vias. As device dimensions scale down further, wires will be an increasingly important contributor to dynamic power.

Modern VLSI circuits route wires on multiple metal layers and vias provide an electrical connection between two adjacent routing layers. Thus in complex circuit design which contains about 2 million nets to be routed, wires and vias play a fundamental role. This necessitates the importance of minimizing the capacitance by minimizing the wirelength and vias used to route these nets.

The active power P consumed by a chip can be written [8] as:

$$P = a C V^2 f (1.1)$$

where a is the activity factor,

C denotes the total load capacitance,

V represent the voltage supplied and

f is the clock cycle.

Today, most of the VLSI design methodologies are based on library cell approach. The routing is used repetitively during placement phase to find the optimal placement for any cell. Most wire-routing problems are computationally hard [9]. Moreover, determining that whether an instance of a routing problem is solvable is NP-complete

[10], hence there is no deterministic algorithm to find the optimal routing in polynomial time.

# 1.2 The Routing Problem

The routing problem is defined as locating a set of paths to route wires that connect all the nets in the net-list. A net is a set of cells (also called terminal nodes) that need to be connected to each other in a predefined manner. The number of nets on a chip ranges from 50,000-3,000,000 [11]. And each one of these nets has large number of possible routes. This gives us an insight that routing problem is computationally very difficult (NP-complete) [9, 10].

The routing problem is one the most widely investigated problems in VLSI design automation, and there are various performance and design constraints associated with it. One of the important constraints that affect the efficiency and the usability of the chip is the power consumed by the chip. From Eq. 1.1 it follows that the power consumed by the chip is a function of capacitance induced. Moreover the two main capacitance inducing components on a chip are the routed wires and vias. This implies that minimizing the number of wires and vias could effectively reduce the power consumption of the chip.

However, there is a tradeoff between the number of vias and wire length used in routing. Vias help in reducing wire-lengths by allowing wires to route through shorter routes available in different routing layers. Thus minimizing vias could increase the total routed wire-length whereas minimizing wire-length could require more vias. Thus the goal of this thesis is to minimize the power consumption of the chip by finding routing solutions that minimize the total capacitance induced by the wires and vias together.

The routing of the large number of nets on a chip takes about 30% of total design time and 90% of chip area [12]. Traditionally, the routing problem is divided into two phases. The first phase is called as global routing, which generates an approximate routing for each net. It assigns a routing region for each net, without specifying actual geometric layout of wires. Detailed routing is the process of implementing the actual geometries of the interconnections among the pins specified by a net list. It completes the point to point wiring by specifying geometric information such as location and width of wires and their layer assignment.

# 1.3 Problem Formulation

The global routing problem is typically studied as a graph problem. The routing regions, their relationships and capacities are modeled as graphs. However, the design style and objective functions strongly affect which graph models are used, and as a result there are several graph models used by different routing algorithms. The order in which nets are routed is important. In a sequential approach nets are routed one at a time. The ordering problem is defined as finding a particular permutation of routing nets such that the nets that are routed later do not suffer from blockages or unavailability of routing paths.

This work considers the problem of routing multi terminal nets in a three dimensional routing geometry. Given a set of nets to be connected, the algorithm tries to find the routing that uses optimal length of wire-length and vias to route the nets. The algorithm casts the routing problem as a multi-objective graph problem and solves for wire-length and vias.

The routing of nets with more than two terminals can be formulated as a tree problem which can be stated as:

Given a set of nets in a netlist  $N=\{N1, N_2, N_3 ... N_n\}$  and the placement of various components  $P=\{P1, P_2, P_3 ......P_n\}$ , find a tree for each net  $N_i$ , which routes the net, such that the objective function is satisfied. The objective function is to:

- i) Minimize the total wire length used by all the nets together.

- ii) Minimize the number of vias used by the nets.

- iii) Minimize the capacitance introduced by the vias and wires.

# 1.4 Routing Benchmark and Format

There has been extensive research in the field of placement and routing algorithms for VLSI circuits. For example, there are several new academic placers and routers that use different approaches like simulated annealing [13], artificial intelligence [14] and neural networks[15]. These approaches are compared using publicly available standard circuit benchmarks and suites. The Design Automation (DA) community has heavily relied on these benchmark suites to compare and validate their algorithms. These benchmark suites are maintained by the Collaborative Benchmarking Laboratory [16]. Benchmarks are available for placement, routing and both placement and routing simultaneously. We use routing benchmarks from the ISPD benchmark suite [11].

Any complete EDA (Electronic Design Automation) system is a disparate set of heterogeneous tools stitched together [17]. During the design flow these different tools interact with each other using data-file generation and translation. These files are generated in a particular format by one tool and translated by another tool to its internal

data structure. Thus 'format' is defined as a file or set of files that contain data in a given syntax that is understood by different interacting tools [18]. One of the most recent and versatile format is the Bookshelf format. Bookshelf is an object oriented format that contains information in the form of library. Being object-oriented allows reuse of the same specifications for more complex circuits and across different platforms. This research uses IBM ISPD98 benchmarks in bookshelf format and is described below in detail.

# 1.5 Ant Colony Optimization

'Ant Colony Optimization' provides a multi-agent framework for combinatorial optimization problems. This nature inspired metaheuristic originates from the capability of ants to find shortest paths from their nest to food source. Natural ants achieve this goal through constant co-ordination and indirect communication using a chemical substance called pheromone [19].

This collective problem solving ability results from a reinforcement process in which ants deposit a pheromone trail as they return from food source to their nest [20]. Since ants following the shortest path can complete their trips in less time, they will make more trips between their nests and the food source, and deposit more pheromone on shorter paths compared to longer paths. The strength of pheromone on each path guides remaining ants to the food source [19].

ACO algorithms have been widely and successfully used in combinatorial optimization problem solving. Every ant in the ant colony practices an independent sequential decision process aimed at constructing a feasible solution for the optimization

problem at hand by using only information local to the current decision step. The outcomes of the search process are used to locate the most promising search areas, and the parameters used by the approach are updated to focus the search in the promising areas. Due to this independent decision making, this ACO algorithm is highly parallelizable. Ants use pheromone information to guide the search process and to transfer knowledge from an iteration of the optimization algorithm to the next. In ACO all decisions that lead an ant to a good solution are considered equally important and receive the same amount of pheromone. The collective behavior of ants independently searching for best solution results in the establishment of the shortest route.

There are many algorithms derived from ant colony metaheuristic which are used to formulate solutions for many different problems. Two of the main categories are static and dynamic combinatorial optimization problems. Static problems are those whose topology and parameters do not change while the problem is being solved. An example of static optimization problems is the Traveling Salesman problem (TSP). The TSP can be stated as: Given a number of cities and the cost of traveling from city to any other city, what is the least-cost round-trip route that visits each city exactly once and then returns to the starting city [21].

Dynamic optimization problems are those in which the topology and parameters change while the problem is being solved. An example of dynamic optimization problem is routing in communication networks. The traffic patterns and network parameters in communication networks change continuously with time. The ACO metaheuristic captures these differences and is general enough to comprise the ideas common to both application types.

The ACO algorithm differs from other heuristic approaches. The heuristic experience gained during the execution of an ACO algorithm (pheromone trails) is updated in real time. This allows the algorithm to perform a cumulative search over the whole search space. This thesis adapts an ACO based algorithm for static routing to find optimal routes for routing of components on VLSI chips. Optimal routes are defined for a group of components placed on a chip, while minimizing route length, number of vias, capacitance and time taken to calculate routes. Combining these constraints defines a set of objectives that can be utilized by these ants to find solution to the routing problem.

# **CHAPTER 2**

# **Previous Work**

# 2.1 Detailed Routing

In the two phase routing approach, a detailed routing phase follows a global routing phase. During the global routing phase, wire paths are constructed through a subset of routing regions, connecting the terminals of each net. The detailed router places the actual wire segments within the region indicated by the global router, thus completing the required connections between the terminals [22]. Global routing controls the success of detailed routing. In new designs the placement and routing occurs simultaneously and global routing is responsible for guiding placement engines and hence impacts lithography, chemical polishing and manufacturing of the chip. The detailed routing problem is usually solved incrementally, routing either a particular region or a particular net at a time.

Important nets could be routed first, depending on how importance is defined. Below are the definitions for various terms related to routing.

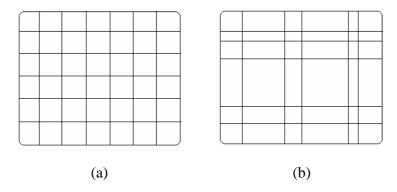

**Grid**: Manhattan geometry where only horizontal and vertical lines are allowed. The routing region if formed either of symmetrical or asymmetrical grid lines. Symmetric grid has equal distance between any two horizontal or vertical lines. Asymmetric grid does not have equidistant separation (Figure 2.1). Horizontal lines are called rows and vertical lines are called columns [14, 23].

**Routing Region**: The area between different cells on a chip, set aside for routing nets is called the routing region.

**Switchbox and Channel**: Channel and Switchbox are two routing methods in which the routing region is divided into rectangular blocks. The perimeters of these blocks contain pins which need to be connected. A rectangular block with terminals assigned to fixed positions on three or four sides is called a switchbox. If terminals are assigned to fixed positions only two opposite sides of a rectangular region is called a channel [24].

**Interconnect**: Interconnects (also called wires) are used to connect devices on a chip.

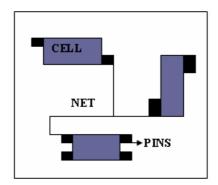

**Via**: Same net spanning different layers are connected using vias. Vias are represented as the intersection of two lines on two different metal layers.

**Cell**: The design of VLSI circuits involving many thousands of transistors becomes manageable when the system is partitioned into smaller logic blocks called cells [15]. A cell is a simple logic unit stored in cell library. A single cell contains about 100-1000 transistors.

**Terminal Nodes**: A cell has input/output pins to connect to other cells. The pins which a cell uses for input/output purpose are called terminal nodes.

Net: A net is a set of cells that need to be connected to each other in a predefined

manner (Figure 2.2).

Subnet: A simple connection between two points is called a subnet. Every net

consists of one or more subnets and each subnet consists of two terminals.

**Net list**: A set of all the nets to be routed on a single chip.

**Pitch**: The center to center distance between two interconnects.

Parasitic capacitance: Parasitic capacitance is the unavoidable and usually unwanted

capacitance that exists between the parts of metal interconnects or other parts of circuit

simply because of their proximity to each other.

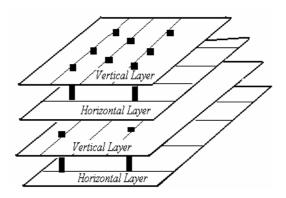

Layer: Modern VLSI circuits route wires on multiple metal layers. Multiple layers

provide tiers of horizontal and vertical routing area, stacked over each other and

connected by vias (Figure 2.3).

2.2 **Routing Models**

Characteristics of a routing problem largely depend on the topology of the routing

region and the constraints the problem takes into consideration. These characteristics also

define that how the problem would be approached or what algorithms or model would be

used to solve it. Various routing models are discussed below:

11

Figure 2.1: (a) Symmetric Grid (b) Asymmetric Grid

Figure 2.2: An example of cell, net and pins of cell.

Figure 2.3: Vertical and Horizontal Layers connected by vias.

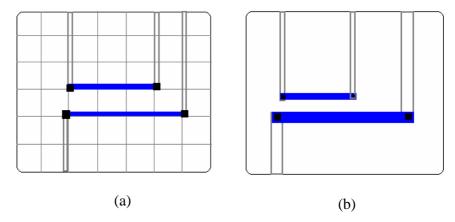

Grid and Gridless Models: The grid-based approach requires that the terminals, wires and vias should conform to a grid. The presence of grid makes computation easy, but it requires large amount of memory to maintain the grid, and the wire width is restricted. In the gridless approach an imaginary grid is constructed by extrapolation of placed components' coordinates. The gridless approach is considered more practical primarily because all the wires in a design do not have same widths (Figure 2.4). Gridless approaches allow arbitrary location of terminals, nets and vias and arbitrary wire width [22, 25, 26].

Figure 2.4: (a) Grid Based (b) Gridless Model

Layered Approach: Modern VLSI circuits route wires on multiple metal layers. Multiple layers provide tiers of horizontal and vertical routing area, stacked over each other and connected by vias. Wires on same layer cannot cross each other, unless they form a connection, whereas wires on different layers that cross each other do not connect unless an explicit connection through a via is established. Multiple layers allow a higher density of components, which shrinks the distances between cells, thus reducing wire-

lengths. Moreover, layered model utilizes wires with varying thickness in different metal layers. In order to minimize resistance, thick metal wires are used in upper metal layers and used to lay long routes between distant cells. Thus the layered approach provides an effective method to reduce wire resistance [27, 28]. However thick wires also increase the coupling capacitance of the wires[29].

If any net segment is allowed to be placed in any layer, it is called an unreserved layered model. When certain type of segments are restricted to particular layers, than it is a reserved layer model. Most of the routing algorithms use reserved layer models where horizontal assignments are reserved to one particular layer and vertical assignments in another layer. Such models can be easily extended from two layers to three layers (Figure 2.5). Modern design typically use six to eight routing layers.

Figure 2.5: (a) Layered Model (b) Unreserved Layer Model

# 2.3 Routing Algorithms

Routing is a complex task. Decomposition of routing problem makes the automatic routing of today's VLSI circuits possible. The following hierarchy [30] shows the decomposition of the routing problem. At the first level of hierarchy are the global, detailed, and specialized routers. The global router distributes the nets over the entire chip. Once the terminals of each channel are determined the detailed router will find the exact location of wire segments of each net. The specialized router is designed to solve a specific problem like routing of power wires, ground wires and wires that has some particular constraints. Power and ground wires require special attention for two reasons (1) they are usually routed in one layer in order to reduce the parasitic capacitance of contacts, and (2) they are usually wider than other wires ( signal and data) since they carry more current.

Detailed routers further divide into general purpose and restricted routers. The general purpose routers impose very few constraints on the routing problem and operate on single connection at a time. General purpose routers work on the entire design in a serial fashion, while restricted routers require some constraint on the routing problem, like limits on maximum routing area used, maximum delay that can be tolerated etc. Because of their limited scope they are able to perform better in terms of tackling any particular type of routing problem. Routers typically use a rectangular grid in which horizontal and vertical wires are placed in different layers, called Manhattan routing. Some routers use a rectangular grid that also allows diagonal connections known as

Figure 2.6: Routing Hierarchy [30]

Non-Manhattan routing. At the lowest level of hierarchy different techniques are presented, but in general these techniques can be grouped into 3 broad categories i.e. (1) algorithms (2) expert systems, and (3) neural networks. The routing algorithm developed in this thesis uses a layered approach in which different layers are assigned for different routing directions. Also the algorithm is used to route both manhattan and non-manhattan architectures. The Ant Colony algorithm based router uses a heuristic based approach to route the chip.

# 2.3.1 Multi Layer Routing

Multi-layer routing allows tiers of horizontal and vertical routing area, stacked over each other and connected by vias. Vias provide an electrical connection between any two points on different routing layers. Multiple layers allow a higher density of components, which shrinks the distances between cells, thus reducing wire-lengths [31]. One of the widely used routing method uses an alternate horizontal and vertical routing layer called as HV routing. This pattern can be repeated depending on the number of layers, e.g. if four routing layers are allowed we get an HVHV routing, and so on.

Some of the important routing algorithms are discussed below:

#### i) Maze Routers:

Maze Router is one of the earliest automatic routing algorithms. Maze routers are general-purpose routers which find the shortest rectilinear path between source point and destination point on a gridded model. In the first Maze router [32] Lee proposed an algorithm to find a short path between two points that crosses a minimum number of existing paths. It considers the routing surface as a rectangular array of cells. The algorithm starts by marking the source cells as visited. In successive steps, it visits all the unvisited neighbors of visited cells. This continues until the destination cell is visited. Due to the breadth-first nature of the search, maze router is guaranteed to find the shortest path between source and destination.

There are four phases in simple maze router (1) setup phase, (2) expansion phase, (3) backtrack phase and (4) cleanup phase [33]. The setup phase determines the two points to be connected as source and destination. In the expansion phase, all the unvisited neighbors are visited in a least cost fashion. The cost of visiting each neighbor is depicted as a numeral in the grid below. Once the destination point is reached the router heads for backtracking phase.

Some of the drawbacks of Lee's algorithm are that it routes one net at a time, so there is possibility of having some nets un-routed at the end of the routing process. Also, as it follows breadth first search, it requires a large amount of storage space and its performance degrades rapidly when the size of grid increases. The time and space complexity of Lee's algorithm is  $O(h \times w)$  for a grid of dimension  $h \times w$ . To improve the memory requirements and speed of basic maze router, different techniques have been proposed [34-38]. Due to its simplicity it can be used for both custom, semi-custom ICs as well as large PC boards. Most FPGAs use some variation of the maze router.

### ii) Greedy Router:

The greedy router routes the channel in a left-to-right, column-by-column manner, wiring each column completely before starting the next. Within each column the router tries to maximize the utility of the wiring, using simple, "greedy" heuristics. The router does not use horizontal and vertical constraints. All decisions are made locally at a column. Greedy router is always able to complete the routing. But this complete routing is at the expense of some additional columns added at the end of the channel [39]. It may place a net on more than one track for a few columns, and "collapse" the net to a single track later on [40]. To route any complete net-list greedy router requires three nonnegative integers: initial channel width, minimum jog-length, and steady-net constant. A jog is a vertical wire that brings a pin closer to another pin on the channel side. Thus minimum jog-length signifies a constraint that tells that a router can not use a jog shorter than length *j* the minimum jog-length. Generally *j* constraint exists and defined due to fixed channel width. A high value of *j* implies longer running straight wires and hence

reduces number of vias. Whereas a small value of j implies shorter wires which spans fewer tracks and thus reduces the number of routing tracks.

As it routes column by column, it allows horizontal wires to change tracks which leads to use of large number of vias. Moreover as it is based on a greedy approach, its searches often terminate at solutions having local optimums, thus giving sub-optimal solutions.

#### iii) Steiner Tree Based Algorithms

Global routing algorithms presented above were not suitable for global routing on multiterminal nets. The algorithms can only route two terminal nets. To route any multiterminal net, the net is first broken into multiple two terminal nets. The quality of routing in such approaches was highly dependent on how the multi-terminal nets are broken into two terminal nets. To achieve optimal results, the way of decomposing a net should be based upon how a router approaches the routing problem i.e. whether it routes on column basis or row basis or a combination of both.

One of the key methods for routing multi-terminal nets is the Steiner Tree approach. A Steiner tree is minimum weight tree connecting a designated set of vertices, called terminals, in an undirected graph or points in a space. The weight or cost of a Steiner tree is expressed as the sum of lengths of all the edges of the tree. The Steiner tree algorithm is used to solve various similar sub problems like in inverter tree and clock tree algorithms as well as in global and detailed routing. A rectilinear Steiner tree has only rectilinear edges. The problem of finding rectilinear Steiner tree of minimum cost is NP hard [41, 42]. In view of the NP hardness, several heuristic algorithms have been developed. Most of the heuristic algorithms depend on minimum cost spanning tree. A

minimum spanning tree is a spanning tree with minimum weight or cost. A spanning tree of a graph is a sub graph which is a tree and connects all the vertices together. A graph may have several minimum spanning trees. Hwang [43, 44] shows that the ratio of the cost of a minimum spanning tree to that of an optimal rectilinear Steiner tree is no greater than 3/2. This is due to the relationship between Steiner tree and minimum cost spanning tree - the Steiner trees are generated by first finding the minimum cost spanning tree.

The Steiner tree algorithm first define an underlying grid G(S) of S as the grid obtained by drawing horizontal and vertical lines through each point of S. The next step involves finding the minimum cost spanning tree of the graph. An approximation of optimal rectilinear Steiner tree can be obtained by rectilinearizing each edge of a minimum spanning tree [22]. The difference between the Steiner tree problem and the minimum spanning tree problem is that in the Steiner tree problem, extra intermediate vertices and edges may be added to the graph in order to reduce the length of the

Figure: 2.7: (a) An example of Steiner tree where blue points represents Steiner points.

(b) An example of rectilinear minimal Steiner tree.

spanning tree. These new vertices introduced to decrease the total length of connection are known as Steiner points or Steiner vertices. A Steiner point is a non-terminal vertex of degree three or four, while a corner point is a non-terminal vertex of degree two where the two edges meeting at a corner point are perpendicular. Non-terminal vertices of degree two with two collinear incident edges are removed by merging both edges. There are various different versions of Steiner trees algorithms. Accurate estimation of rectilinear Steiner minimal trees could be obtained using either optimal algorithms [45, 46] or near optimal heuristics [47, 48]. But these algorithms are computationally very expensive to use in practice [49]. Moreover the time complexity increases exponentially with increase in number of terminals of the net. Thus there are heuristic based Steiner tree algorithms that are suggested for VLSI routing [50-52]. Each different version uses a different heuristic to obtain a good estimation of optimal Steiner tree formed by VLSI nets. One of the algorithm cktsteiner [53] uses numerical model simulation to determine Steiner points. The algorithm models the routing grid as a circuit with grid nodes acting as output ports. The simulation helps to determine the voltage at various nodes which hence decides if a node could be a Steiner point or not. Some of the approaches use Ant Colony Optimization technique to solve Steiner tree problem in VLSI nets [54]. The Ant Colony Optimization technique is discussed below.

# 2.3.2 Academic Routers

Based on the approaches described above there are many academic routers that have been developed. Many of these routers are used as benchmarks for comparison by various other academic routers and have been stated as state-of-the-art academic routers [55-57]. Some of these academic routers are Labyrinth Router [58], FastRoute [59], FastRoute [60] and NTHU Router [61].

Labyrinth Router uses maze routing to provide accurate routing of all nets and wire length estimation, at the expense of longer running time. FastRoute uses a congestion driven Steiner tree construction to determine good Steiner nodes and Steiner tree topologies. For routing purposes the routing area is divided into rectangular regions called global bins. Each bin has a fixed routing capacity. Congestion occurs when the number of routing tracks routed through a particular bin exceeds its capacity. During placement of cells different placements are evaluated by approximating the route length. This is known as approximation. FastRoute is used to evaluate different cell placements to determine which placements result in minimum wire-length and congestion levels. FastRoute2.0 is an improvement in terms of congestion and wire-length compared to FastRoute, but it requires longer run time. The advantage of FastRoute2.0 is that it is fast enough to use for approximation and accurate enough to route most (but not all) nets. This makes the approximation much more useful because approximation is much more accurate if the same algorithm is used for approximation and actual routing.

These algorithms approach the Steiner tree problem by concentrating on one major objective: to minimize the total length of the tree. These algorithms do not take into account any other criterion that could affect the total power consumption of the chip which requires minimizing the total capacitance of the chip. Moreover Steiner tree algorithm has the planar property i.e. it could be embedded in a plane such that its edges intersect only at their end points. Due to this property a Steiner tree could be efficiently

implemented in a single layer. But for multi-layer routing the Steiner tree need to be extended over different layers. Because a single layer Steiner tree is not built with the constraint of vias, this extension over multiple layers is not efficient and leads to reduced reliability due to large number of vias.

The more recent NTHU Router [20] decomposes all multi-pin nets into a set of two pin nets and draws a congestion map, followed by adaptive maze routing, and it is very fast.

## 2.4 Traditional Approaches

Many important problems lie in the category of combinatorial optimization problems and are hard to solve. The notion of problem hardness is captured by the fact that the time needed to solve an instance in the worst case grows exponentially with instance size.

Often, approximate algorithms are the only feasible solution at low computational cost.

Most approximate algorithms are either construction algorithms or local search algorithms. Construction algorithms build solutions to a problem under consideration in an incremental way starting with an empty initial solution and iteratively adding opportunely defined solution components without backtracking until a complete solution is obtained. In the simplest case, solution components are added in random order. Often better results are obtained if a heuristic estimate of adding a solution component is taken into account. An example of such a heuristic is greedy heuristic. A disadvantage of a greedy heuristic is that only a very limited number of solutions can be generated. Also, greedy decisions in early stages of the construction process strongly constrain the

available possibilities at later stages leading to very poor moves in the final phase of solution construction.

Local Search algorithms start from a complete initial solution computed by one of the approximate methods and try to find a better solution in an appropriately defined neighborhood of the current solution. Moving from one solution to a neighbor solution requires defining a neighborhood relation on the search space. As an example, the neighborhood of routed path in a graph is another path differing by only one graph edge. Every candidate solution has more than one neighbor solution, the choice of which one to move to is taken using only information about the solutions in the neighborhood of current one, hence the name local search. The choice of an appropriate neighbor relation is crucial for the performance of local search algorithms. Local search algorithms are known as incomplete algorithms, because the search process may stop even if the best solution found is not optimal.

The routers described above fall into either of the categories of local search or constructional algorithm. For example, maze router is a local search algorithm which iteratively expands in its neighborhood until it reaches the destination point. On the other hand, greedy routers make a decision based on local information and move in the direction which looks most promising in the local scenario. A Steiner tree based algorithm is constructional algorithm as it uses the minimum spanning tree algorithm as its starting point and iteratively adds edges to the spanning tree to form a Steiner tree. Among the academic routers used above, most of them use variations of maze routing combined with constraint specification.

#### 2.5 ACO Metaheuristic

Ant Colony Optimization metaheuristic is a probabilistic technique of stochastic solution construction. A solution is built iteratively by adding solution components to partial solutions constructed by ants. The pheromone information is updated by the ants at run-time to reflect the information acquired during search. [20]. The stochastic component in ACO allows the ants to build a wide variety of different solutions and hence explore a much larger number of solutions than greedy heuristics. At the same time, the use of heuristic information, can guide the ants towards the most promising solutions. Moreover the ant's search experience implements a form of reinforcement learning that is used for solution construction in future iterations of the algorithm. Additionally, the use of a colony of ants can give the algorithm-increased robustness, and in many ACO applications the collective interaction of a population of agents is needed to efficiently solve a problem. The domain of application of ACO algorithms is vast. ACO algorithms are being extensively used for NP hard combinatorial problems. This includes both single objective and multi-objective problems like routing, data mining and voice recognition [62-64].

## 2.5.1 Problem Representation

According to Dorigo and Stutzle [20] a combinatorial optimization problem can be represented as  $(S, f, \Omega)$ , where S is the set of candidate solutions, f is the objective function which assigns an objective function (cost) value f(s, t) to each candidate solution  $s \in S$ , and  $\Omega(t)$  is a set of constraints. The parameter t indicates that the

objective function and the constraints can be time dependent. The goal is to find a globally optimal solution  $s_{opt}$  that is, a minimum cost solution that satisfies the constraints  $\Omega$ .

The problem representation of a combinatorial optimization problem  $(s, f, \Omega)$ , which is exploited by the ants, can be characterized with a finite set  $C = (c_1, c_2, \ldots, c_n)$  of given components, the states of the problem defined in terms of sequences  $x = (c_i, c_j, \ldots, c_n)$  over the elements of C, finite set of constraints  $\Omega$  that defines the set of feasible states, set  $S^*$  of feasible solutions such that  $S^* \subseteq S$  and a cost function f(s, t) associated to each candidate solution. Given this representation, artificial ants build solutions by moving on the construction graph Gc = (C, L), where the vertices are the components C and the set C fully connects the components. The graph C is called construction graph and C are called connections.

## 2.5.2 Ants' Approach

The solution construction is carried out by artificial ants by moving on the construction graph Gc. Ants do not move arbitrarily on G, but rather follow a construction policy, which is a function of the problem constraints  $\Omega$ . It exploits the graph Gc to search for feasible solutions s of minimum cost. It has a memory M that is used to store information about the path it followed. Memory is used by an ant for various different purposes: to build feasible solutions using the constraint  $\Omega$ , to evaluate the already found solutions, and to deposit pheromone on the path traversed. Pheromone trail encoding acts as ant memory and is updated regularly by the ants during the search process. Ants could be assigned a start state and a termination condition. The heuristic

value used by the ant represents a priori information about the problem instance. An ant selects the move by applying a probabilistic decision rule. Its probabilistic decision is a function of locally available pheromone trail and heuristic value, ant's memory storing its search history and the problem constraints. Once a complete solution is built the amount of pheromone on each connection in the solution is updated. The construction procedure of an ant stops when at least one of the termination conditions is satisfied.

It is an important characteristic of ACO, that ants move independently and each ant find its own solution to the problem under consideration. Good quality solutions emerge as the result of the collective interaction among the ants via indirect communication mediated by the information that ants read and write into the variables storing pheromone trails. Thus it is a distributed learning, in which individual ants do not adapt their behavior, but they modify the way the problem is represented and perceived by other ants.

## 2.5.3 Ant Colony System

There are various different versions of ant colony optimization algorithms used today, and most are advanced versions of a very simple ACO model called 'ant system'. Some of the advanced versions are rank-based ant systems, max-min ant system, elite ant system and ant colony system. ACO algorithms have been successfully implemented for solving Traveling Salesman Problem (TSP). This work employs 'Ant Colony System' for VLSI routing. Here we explain how ACS has been used to solve the TSP. In the next section we modify this algorithm for VLSI design.

To solve TSP, Ant colony system [20, 65, 66] is implemented as a colony of m ants which are initially placed on n cities either randomly or using some initialization scheme. This city is known as the start city of the ant and is stored in ants' memory M. An ant also maintains a list of visited cities to keep track of the cities it has already visited. The start city is added to the list of visited cities. An ant iteratively moves from one city to another. An ant k located at city i chooses to go to an unvisited city j with a probability given by:

$$p_{ij}^{k}(t) = \frac{\left[\boldsymbol{\tau}_{ij}(t)\right]^{\alpha} \cdot \left[\boldsymbol{\eta}_{ij}\right]^{\beta}}{\sum_{l \in N_{i}^{k}} \left[\boldsymbol{\tau}_{ij}(t)\right]^{\alpha} \cdot \left[\boldsymbol{\eta}_{ij}\right]^{\beta}} \quad if \quad j \in N_{i}^{k}$$

(2.1)

Where  $p_{i,j}$  = Probability that an ant at node i will move to node j.

$\tau_{i,j}$  = Amount of pheromone on path i, j.

$\eta_{i,j}$  = Desirability of any path i, j is a priori heuristic information. In the case of TSP,  $\eta_{i,j} = 1/d_{i,j}$  where d is the distance between two cities i and j.

$\alpha$  = Parameter to control the influence of  $\tau_{i,j}$ .

$\beta$  = Parameter to control the influence of  $\eta_{i,j}$

$N_i$  = is the feasible neighborhood of ant k that is, the set of cities which the ant has not yet visited.

When  $\alpha$  is set to 0, the selection probability is proportional to  $\eta_{i,j}$  and the closest cities are more likely to be selected. The algorithm acts like a greedy algorithm. When  $\beta$  is set to 0, only pheromone amplification is at work and hence no heuristic information is used. This leads to poor results due to occurrence of stagnation, i.e. as all ants follow the same path and construct the same tour, no new paths are explored and the algorithm terminates with a sub optimal solution. After an ant k travels from a city i to city j using the above

probability  $p_{i,j}^k$  the pheromone trail of the ant is updated. This is known as 'local pheromone trail update'.

The goal of local pheromone trail update is to make the path taken by ant k less desirable for the following ants and hence stimulate exploration of paths that have not been visited by ants. Thus to reduce the desirability of the path taken by an ant, the amount of pheromone on the path is reduced by a constant factor  $\xi$ .

$$\tau_{i,j} = (1 - \xi)\tau_{i,j} \tag{2.2}$$

After each ant has completed its tour, pheromone trails are updated. This is known as 'global pheromone trail update'. Global pheromone updation could either be applied to each ant of the colony or only to the best ant of the iteration. For TSP, the best ant is the one with minimum tour length in the current iteration.

Pheromone update is a two step procedure. First all the pheromone trails are lowered by a constant factor  $\rho$ . This is known as evaporation. Evaporation is necessary as it allows unlimited accumulation of pheromone trails and enables the algorithm to forget bad decisions taken during the previous iterations. The pheromone evaporation is represented by the following equation.

$$\boldsymbol{\tau}_{i,j} = (1 - \rho) \boldsymbol{\tau}_{i,j} \qquad \forall (i,j) \in L \tag{2.3}$$

After pheromone evaporation the second step is pheromone deposition. In Ant Colony System, only the best ant is allowed to add pheromone after each iteration. This is an important feature of Ant Colony System as it reduces the complexity of pheromone update from  $O(n^2)$  required in case when pheromone update is applied to each ant of the

colony to O(n) when update is applied only from the best ant. To make sure that the amount of pheromone deposited is an indication of the quality of the path, this amount is a function of the tour length traversed by the best ant. Thus the amount of pheromone deposited is given by:

$$\Delta \tau_{i,j}^{bs} = \frac{1}{C^{bs}} \tag{2.4}$$

Where  $\Delta \tau^{bs}{}_{i,j}$  is the amount of pheromone deposited on the path taken by the best ant of the iteration and  $C^{bs}$  is the tour length traversed by the best ant.. Therefore, the pheromone update could be represented as:

$$\tau_{i,j} = (1 - \rho)\tau_{i,j} + \rho \Delta \tau_{i,j}^{bs}, \quad \forall (i,j) \in T^{bs}$$

(2.5)

Thus we see that the ants are guided, in building their tours, by both heuristic information and pheromone information and an edge with a high amount of pheromone is a very desirable choice.

## 2.5.4 Steiner Trees for VLSI Routing

This section discusses the Steiner tree based techniques that are used to solve VLSI routing. As discussed earlier, due to high complexity of finding accurate Steiner trees, heuristic based algorithms are used to find estimates of optimal or near optimal Steiner trees. One such heuristic based algorithm suggested by Yu Hu [54] uses the ACO approach to construct rectilinear Steiner trees using the heuristic that requires ants to start at each cell to be connected and meet as quickly as possible. The algorithm uses an ACO

approach in which when an ant A meets another ant B, ant A dies and the visited list (list of nodes visited by ants) is merged to the visited list of ant B. A very similar approach is taken by Das [67], that instead of using the make ants meet soon heuristic, uses a bias value for the paths already taken. This bias value attracts the ant to the path already taken by another ant. To simplify the problem another algorithm suggested by Luyet [68] uses a distributed approach in Ant Colony Optimization to solve the Steiner tree problem. The method uses a preprocessing step that reduces the search space by identifying edges or non terminal vertices which do not belong to at least one minimal Steiner tree and edges or non terminal vertices which belong to all minimal Steiner trees. The probability of choosing an edge is a function of greedy force Gf(m) and trail intensity Tr(m) where m is a move based on these two parameters.

## Chapter 3

## Ant Colony Algorithm for VLSI Routing

This chapter discusses the Ant Colony Optimization algorithm for the NP-hard problem of routing VLSI chips. Placement of components on a chip can affect the routability, wire-length and timing constraints of routes laid at later stages. Thus to achieve a more optimized placement that has minimum congestion and route blockage, routing and placement are completed simultaneously, iterating between the two, instead of completing placement before considering routing. The information exchange between placers and routers occurs through a set of files. Different routers may require that this information be supplied in a particular format. Due to this reason there exist several different formats to specify the input information to the router (Appendix A gives a brief overview of some of these formats). This work uses ISPD98 benchmark suite in bookshelf format.

#### 3.1 ISPD98 Benchmarks Suite

ISPD (International Symposium on Physical Design) benchmarks are derived from IBM internal design format and include circuits comprising wide variety of library components like memory, logic, processor etc. Every circuit in this benchmark is a translation from VIM (Very-Large-Scale Integrated Model- IBM's internal data format) into net format, which is a simple hyper-graph representation originally proposed by Wei and Cheng [11, 69]. The ISPD benchmark includes 18 circuits named IBM01 to IBM 18 and each one having different complexity and size. The benchmarks exclude any

information related to functionality, timing and technology. The benchmark includes information related to cell placement, size and orientation, connectivity information and circuit row information in the bookshelf format. For each benchmark circuit this information is contained in a set of 6 files. The four important files used for routing are described below. (A detailed description of these files is available in Appendix A.)

- (i) IBMxx.aux: This file is known as Auxiliary File and has an extension .aux. The auxiliary files contain the set of input files and the placement method.

- (ii) IBMxx.nodes: This file is known as nodes file and contains information about specific objects. It specifies

- Total number of objects.

- Total number of terminal objects.

- For each object it specifies object name, width, height and whether it is a terminal or non-terminal object. To signify a non-terminal object the keyword 'terminal' is omitted.

- (iii) IBMxx.nets: A nets file specifies the set of nets. It includes

- Total number of nets

- Total number of pins

For each net it includes net-degree, pins forming the part of net and whether a particular pin is acting as an input or output in the net. An input is represented using 'I' and an output using 'O' in front of the component name.

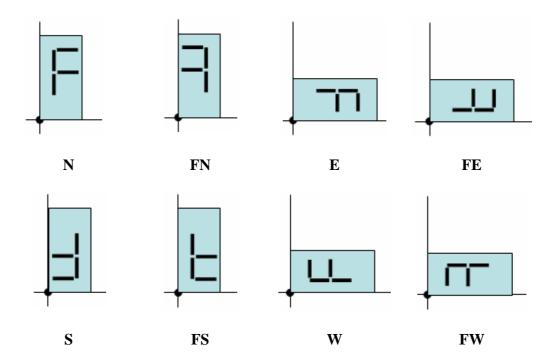

(iv) IBMxx.pl: A placement file specifies the location and orientation of objects. The orientation of a component could either be N, FN, E, FE, S, FS, W, and FW [70]. The default orientation is "vertically and face up" and is represented as N (North). Other orientations are obtained by flipping N, E, W and S orientations by right angle about X or Y axis and are represented as FN, FS, FW and FE.

## 3.2 ACO Algorithm for Manhattan Routing - Model Formulation

This section describes the assumptions and the approach taken to formulate a model in which an Ant Colony Optimization algorithm could be implemented to route VLSI chips in a power efficient manner.

The key assumption made for this model is that each cell component and wires are assumed to have zero width and height. As mentioned earlier, wide wires are used in upper metal layers and narrow wires in lower metal layers to minimize resistance and capacitance effects. However, in this model the layers are implemented in memory, and no parameters are used to depict upper and lower metal layers differently. The description of ACO algorithm in Chapter 2 specifies that the application of ACO to a combinatorial optimization problem requires that the problem must be represented as a construction graph Gc=(C, L) which could be exploited by ants and the nodes of the graph are characterized as a finite set of components C which are joined by the connections L. Thus to model the connections between different cells on a chip, these cells are assumed as mere points forming the nodes of a graph Gc.

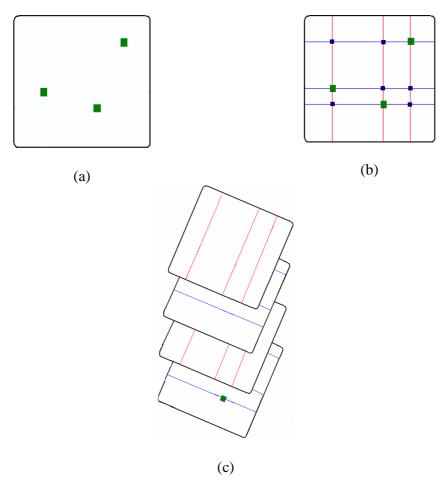

Manhattan architecture allows only horizontal and vertical routes. To represent such architecture, a grid-less approach is adopted for routing, i.e. the router does not depend on a grid to locate wires on a surface but instead it places wires in a space according to the placement of the components which are to be routed. Thus in a grid-less approach a Hanan grid is created from the coordinates of the cell location [54]. A Hanan grid is formed by the intersection of horizontal and vertical lines drawn at each node of the net (Figure 3.2). Hanan [71] showed that there is always a minimal rectilinear Steiner tree for the nodes of a net placed on the Hanan grid [72, 73]. Due to this reason a grid-less router guarantees a solution if one exists. Another advantage of grid-less router is that it allows variable wire and via widths and variable wire spacing which is required for complex circuit design [25, 26]. This Hanan grid is implemented as layered model with two horizontal and two vertical layers (four routing layers total).

The following steps provide an overview of the ACO approach to VLSI routing.

- 1. A Hanan grid is created from the component coordinates.

- 2. All possible pairs of x and y coordinates are stored in memory.

- 3. The nets from the net-list file are sorted according to their size.

- 4. The ACO algorithm routes one net at a time.

- 5. The route solution returned by ACO is fitted into the best possible route and layer.

Figure 3.1: A Hanan grid formed by three terminal nodes of a net (green nodes). Blue nodes are formed by the intersection of Hanan grid lines.

## 3.3 ACO Algorithm for Manhattan Routing (ACO-Route)

This section discusses each step of the algorithm in detail.

#### 3.3.1 Create Manhattan Grid

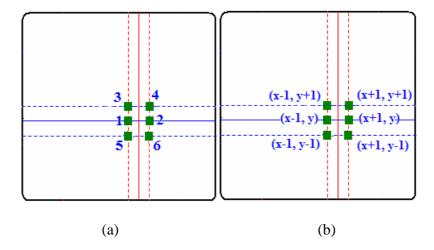

The first step for the routing procedure involves creating a Hanan grid from the coordinates of all the components placed on chip. The coordinates are read from the placement file and stored in memory. These components have multiple pins which act as an input or an output in a net. Each time a component is listed as an input or an output, one of its pin participates in the net. To accommodate multiple pins belonging to a single component, the grid coordinates around the component's location are used. The following methodology is used while choosing the coordinates of the pins.

- If a component is used in a net only once, the component coordinate location defines its position on the grid.

- 2. If a component is used twice, left and right coordinate locations are used.

3. If a component is used more than twice the upper left and right followed by lower left and right grid locations are used for every additional pin location.

Figure 3.2: The figure shows the pin locations chosen on the grid. If more than one pin is used, the left and right grid locations are used. For every additional pin location; first the upper left and right locations are used followed by lower left and right.

The locations are chosen in a manner such that they are symmetrical about the x and y axis. Moreover in the case of more than one pin, the actual component location is not used as a pin location. The actual component location is used as a center point to choose the offset for other pin locations. The alternate locations chosen as pin coordinates were also checked to make sure that they do not coincide with any other similarly chosen pin or component location. In real scenario the cell components placed on the chip has a particular length and width. The pins which form a part of a particular net lie on either of the grid points. The ACO model assumes these components as points (with 0 length and width). This allows ample space between two placed components for the pin locations chosen in the above manner.

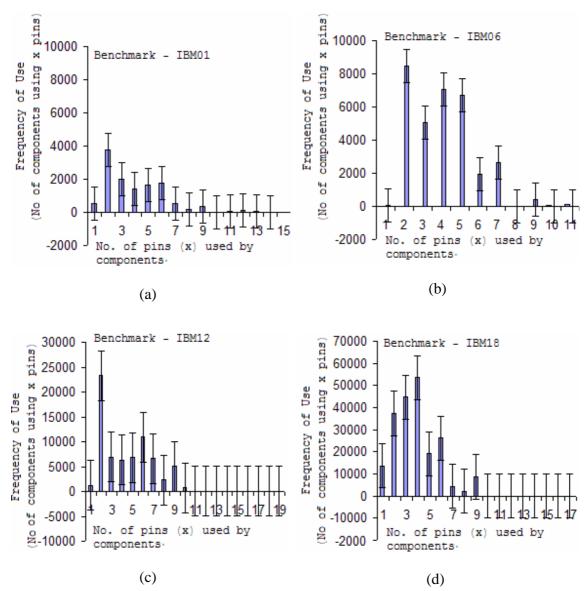

Figure 3.3: The graph shows the number of pins used by different components in benchmark chips.

Figure 3.3 shows the number of pins used per component on the x axis and the frequency of the use on the y axis. Each time a component is used in a net, a different component pin is used by the net. The error bars represent the standard deviation. The median for the number of pins over all the benchmarks is 22.5.

The coordinates of components are stored in memory. A Hanan grid is created by the intersection of horizontal and vertical lines passing through these coordinate locations. The coordinates of the nodes created by the intersection of Hanan grid lines are also calculated and stored in memory. A node belonging to a net must be distinguished from the nodes formed by the intersection of the Hanan grid lines while they are stored in memory.

Figure 3.4: (a) Shows three nodes to be routed to form a net. (b) Shows formation of a Hanan grid. (c) Shows the layered model of the Hanan grid with two horizontal (blue) and two vertical (red) layers.

To implement a layered model, every route on this grid is assigned a count equal to n where n is the number of horizontal or vertical layers allowed. Whenever a particular route on the grid is used, its count is reduced by one. The horizontal and vertical routes are identified by the coordinate positions of the route. Any route could be used for VLSI routing until its count drops to zero. Thus count helps to make sure that a routing should be performed efficiently by using all the available layers.

#### 3.3.2 Sort Nets

The nets from the net-list file are read and sorted according to their size, where the size of a net is a function of its degree, i.e. number of nodes in the net, and the perimeter it engulfs. The reason for sorting the nets before routing is because the algorithm ACO-Route routes one net at a time. If the nets are routed one at a time, it is crucial to decide which nets are routed first, as the nets which are routed later would be unable to use the routing space used by the already routed nets. Short nets are routed first. Short nets have less routing flexibility thus routing them first guarantees a higher routing completion rate. Moreover the capacitance is lower on upper layers and hence the smaller routes are routed in lower layers whereas upper layers are used for long routes. Moreover this minimizes the blockage that might be caused if long routes are routed first. The nets are arranged in an ascending order by size.

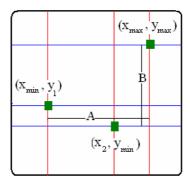

A net perimeter is calculated as the manhattan distance between the maximum and minimum x and y coordinates of a net's components (Figure 3.4). Nets are routed first by degree and then by net perimeter. It should be noted that, given z nets, there exists z!

ways to order the nets but there does not exist a polynomial time algorithm that could find which of these z! permutations could be the most feasible or efficient ordering to route the nets. Thus in spite of ordering the nets to route in a particular sequence, the algorithm later uses a *rip and reroute*.

Figure 3.5: Perimeter of the given net is 2(A+B) where A and B is the manhattan distance between minimum and maximum x and y coordinates of components respectively.

#### 3.3.3 Route Nets

Before routing the first net, the grid is initialized with small amount of pheromone on each of its paths. To route the nets, the first net from the ordered set of nets is picked and the ant colony algorithm is applied on this single net. The ants are randomly distributed on the nodes of the net. The number of ants and other ACO parameters like  $\alpha$  (pheromone parameter),  $\beta$  (desirability parameter), and  $\rho$  are varied to find the best fit as discussed in experiment and results section. The current node on which the ant is placed is marked as visited in the ant's memory. The movement of the ant from one node to another is controlled using the heuristic suggested by Yu-Hu [54] which requires the ant to meet another ant of the same net as quickly as possible. The capacitance of a wire is directly

proportional to its length and hence this heuristic makes the ant take the shortest possible path to meet another ant quickly, which reduces the wire-length used for routing.

The probability of choosing any of the nodes is a function of the desirability of the path connecting to the node and the amount of pheromone on that path (Section 2.4.5). Thus the *make ants meet soon* heuristic is used to calculate the desirability of the path. Following the heuristic, the desirability of an unvisited node j when the ant is located at node i, is defined as the node that minimizes the distance between the node j and all other ants belonging to the same net. Hence desirability  $(\eta)$  could be written as:

$$^{\alpha'}\eta_{i,dir} = \frac{1}{Min\left[^{\alpha'}D_{i,j},^{\alpha'}D_{i,k},^{\alpha'}D_{i,l},^{\alpha'}D_{i,m}\right]}$$

(3.1)

Where  $\alpha'$  is the terminal node from where the current ant started.

is the current node of the ant that started at  $\alpha$ '

dir is the next node decided by this function, which is not yet already visited.

is the total distance between ant's next node j and all other ants when the previous given node is i and can be defined as:

$${}^{\alpha'}D_{i,x} = \left[\sum_{a=1}^{n} M_{i,a} + M_{x,i}\right] For \, a \neq \alpha'$$

(3.2)

Where  $M_{i, a}$  is the Manhattan distance between point 'i' and 'a'.

a is the current position for other ants of the net.

Thus the probability of choosing an arc (i, j) could be defined as following:

$$P_{i,j} = \frac{(\tau_{i,j}^{\alpha})(\eta_{i,j}^{\beta})}{\sum (\tau_{i,j}^{\alpha})(\eta_{i,j}^{\beta})}$$

(3.3)

Where  $P_{i,j}$  = Probability that an ant at node i will move to node j.

$\tau_{i,j}$  = Amount of pheromone on path i, j.

$\eta_{i,j}$  = Desirability of any path i, j.

$\alpha$  = Parameter to control the influence of  $\tau_{i,j}$ .

$\beta$  = Parameter to control the influence of  $\eta_{i,j}$ .

Also when an ant A meets another ant B, all the intermediate points covered by ant A are added to the route list of ant B, and all the intermediate points covered by ant B are added to the route list of ant A. The path for ants A and B is marked as completed, which helps reduce the redundant steps taken by ant A to reach the starting point of ant B and vice versa. This is unlike the algorithm used in [54] where when two ants meet, one of the ants dies and the other ant is responsible for completing the search process.

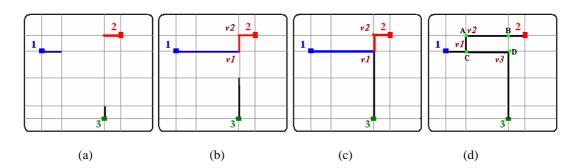

Figure 3.6: (a), (b) and (c) shows a step by step procedure of routing using the heuristic *makes ants meet soon*. A net consisting three nodes 1, 2 and 3 is shown. Ants start from these nodes and choose the next node using the heuristic. (d) Shows a routing while this heuristic is not used (where v1, v2 and v3 indicates vias).

Moreover this heuristic avoids taking inefficient redundant routes as shown in Figure 3.6 (d). The routes (A, B) and (C, D) is an example of inefficient routing that increases the wire-length and requires comparatively more vias.

Every ant keeps a continuous record of the following:

- a) Steps taken to complete the tour.

- b) Tour length, measured as Manhattan length of the route.