Michigan Technological University

Digital Commons @ Michigan Tech

Dissertations, Master's Theses and Master's Reports

2017

# MINIMUM TIME CONTROL OF PARALLELED BOOST CONVERTERS

Shishir Patel Michigan Technological University, sjpatel2@mtu.edu

Copyright 2017 Shishir Patel

### **Recommended Citation**

Patel, Shishir, "MINIMUM TIME CONTROL OF PARALLELED BOOST CONVERTERS", Open Access Master's Thesis, Michigan Technological University, 2017. https://digitalcommons.mtu.edu/etdr/530

Follow this and additional works at: https://digitalcommons.mtu.edu/etdr Part of the <u>Controls and Control Theory Commons</u>, <u>Electrical and Electronics Commons</u>, and the <u>Power and Energy Commons</u>

## MINIMUM TIME CONTROL OF PARALLELED BOOST CONVERTERS

By Shishir J. Patel

## A THESIS

Submitted in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

In Electrical Engineering

# MICHIGAN TECHNOLOGICAL UNIVERSITY

2017

@ 2017 Shishir J. Patel

This thesis has been approved in partial fulfillment of the requirements for the Degree of MASTER OF SCIENCE in Electrical Engineering.

Department of Electrical and Computer Engineering

Thesis Advisor : Dr. Wayne W. Weaver

Committee Member : Dr. Gordon G. Parker

Committee Member : Prof. John T. Lukowski

Department Chair : Dr. Daniel R. Fuhrmann

# Contents

| A        | Abstract xvi                                               |              |                                                                |    |  |

|----------|------------------------------------------------------------|--------------|----------------------------------------------------------------|----|--|

| 1        | Intr                                                       | Introduction |                                                                |    |  |

|          | 1.1                                                        | Thesis       | s objective                                                    | 1  |  |

|          | 1.2                                                        | Previo       | ous art                                                        | 2  |  |

|          | 1.3                                                        | Thesis       | s organization                                                 | 4  |  |

| <b>2</b> | Ove                                                        | erview       | of Boost converters in and as DC Microgrid                     | 6  |  |

|          | 2.1                                                        | Mathe        | ematical model of a Boost converter                            | 6  |  |

|          |                                                            | 2.1.1        | Discrete modeling of Boost converter in CCM                    | 8  |  |

|          |                                                            | 2.1.2        | Discrete modeling of Boost converter in DCM                    | 10 |  |

|          |                                                            | 2.1.3        | Simulation of Boost converter using discrete model             | 12 |  |

|          | 2.2                                                        | Mathe        | ematical model of multiple/paralleled Boost converters con-    |    |  |

|          |                                                            | nected       | l to a resistive load                                          | 14 |  |

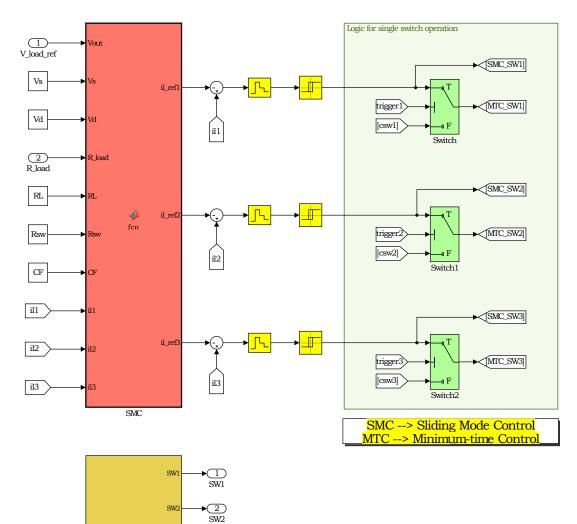

| 3        | Sliding Mode Control (SMC) and Minimum Time Control(MTC)   |              |                                                                | )  |  |

|          | of paralleled boost converters                             |              | 20                                                             |    |  |

|          | 3.1 Sliding Mode Control(SMC) of Multiple Boost Converters |              | 21                                                             |    |  |

|          |                                                            | 3.1.1        | Sliding Mode Controller design                                 | 21 |  |

|          |                                                            | 3.1.2        | Simulation of Multiple Boost Converters with SMC $\ . \ . \ .$ | 23 |  |

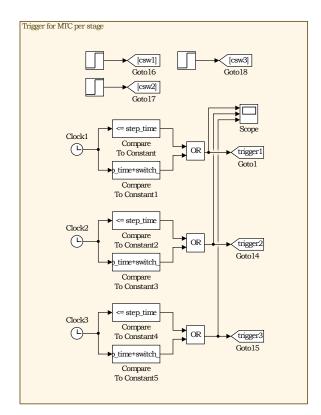

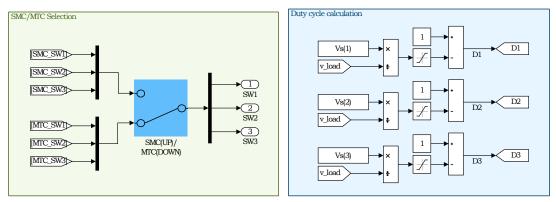

|          | 3.2                                                        | Minim        | num Time Control (MTC) of Paralleled Boost Converters          | 28 |  |

|          |                                                            | 3.2.1        | MTC concept and objectives                                     | 28 |  |

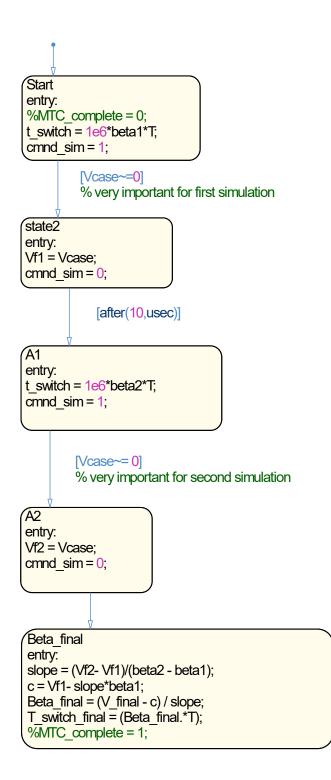

|          |                                                            | 3.2.2        | Minimum Time Control (MTC) algorithm                           | 33 |  |

| A  | App   | pendice | 2S                                                              | 91 |

|----|-------|---------|-----------------------------------------------------------------|----|

| Re | efere | nces    |                                                                 | 86 |

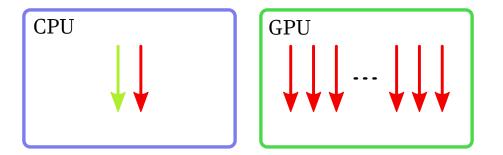

|    |       | 5.2.3   | GPU based implementation of MTC as an alternative               | 83 |

|    |       | 5.2.2   | Non-linear modeling of system parameters                        | 82 |

|    |       | 5.2.1   | Concurrent execution for Real time MTC                          | 81 |

|    | 5.2   | Future  | Work                                                            | 81 |

|    | 5.1   | Thesis  | summary                                                         | 80 |

| 5  | Con   | clusior | n and Future Work                                               | 80 |

|    | 4.4   | Param   | eter sensitivity analysis                                       | 78 |

|    |       | 4.3.2   | SMC vs MTC phase plane comparison                               | 75 |

|    |       | 4.3.1   | SMC vs MTC time domain comparison                               | 73 |

|    | 4.3   | Compa   | arison of performance between SMC and MTC $\ldots$ .            | 73 |

|    | 4.2   | HIL si  | mulation results and analysis                                   | 65 |

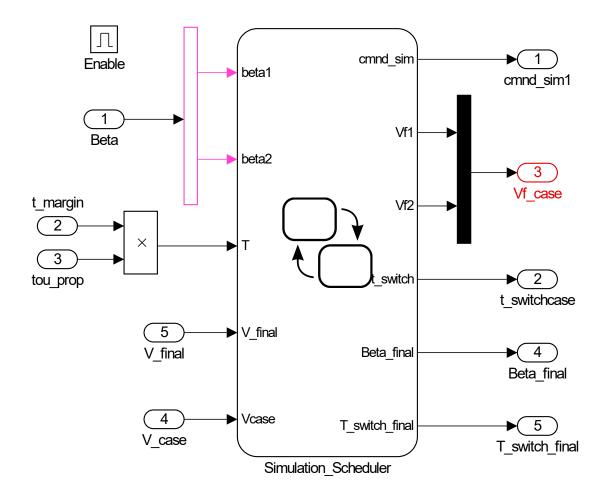

|    |       | 4.1.2   | Software implementation for real-time MTC                       | 62 |

|    |       | 4.1.1   | Hardware implementation for real time MTC                       | 60 |

|    | 4.1   | Minim   | um time control (MTC) system architecture for emulation .       | 59 |

| 4  | Rea   | l-time  | control system implementation and validation of MTC             | 59 |

|    |       | 3.2.6   | Simulation of paralleled boost converter with MTC $\ . \ . \ .$ | 45 |

|    |       |         | of MTC                                                          | 44 |

|    |       | 3.2.5   | Comparison between CCM and DCM based implementation             |    |

|    |       | 3.2.4   | CCM based iteration of paralleled boost converters for MTC      | 40 |

|    |       | 3.2.3   | DCM based iteration of paralleled boost converters for MTC      | 35 |

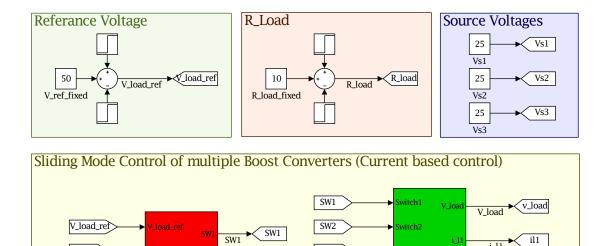

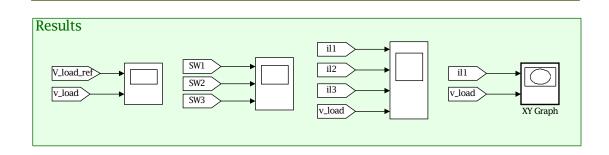

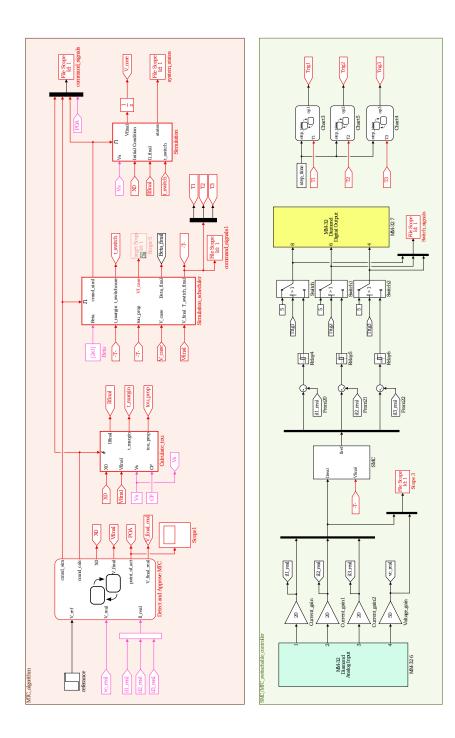

| A.1 | Simulink Model for SMC of Multiple boost converters           | 91  |

|-----|---------------------------------------------------------------|-----|

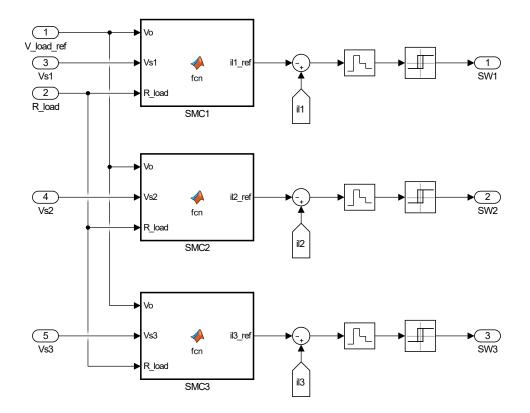

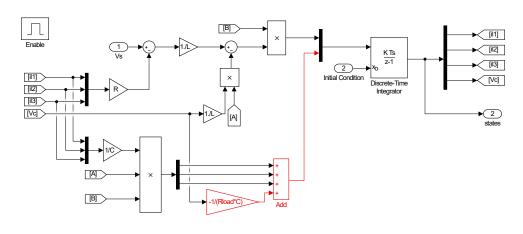

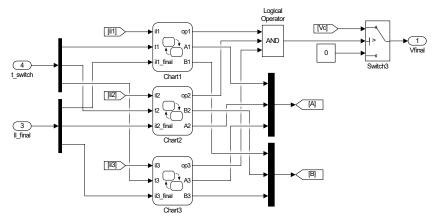

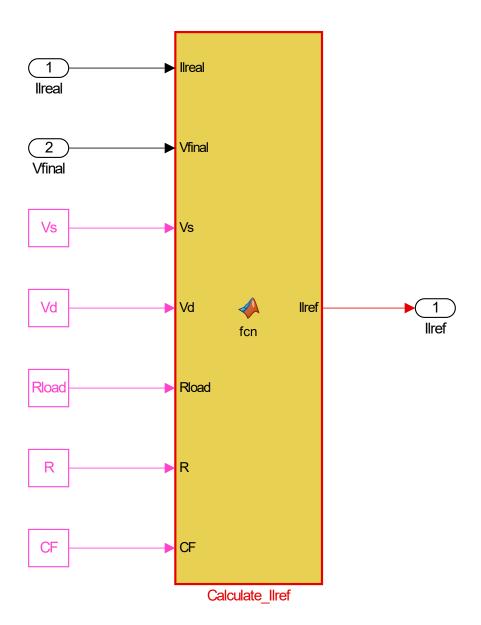

| A.2 | Simulink Model for MTC of Multiple boost converters           | 93  |

| A.3 | Simulink Real-time Model for MTC of Multiple Boost Converters | 97  |

| A.4 | HIL simulation results for experimental cases                 | 103 |

| A.5 | MATLAB code for implementation of SMC and MTC for paralleled  |     |

|     | Boost converters                                              | 126 |

| A.6 | GPU based implementation for MTC                              | 163 |

|     |                                                               |     |

# List of Figures

| 2.1 | Voltage source boost converter with constant resistance                                      | 6  |

|-----|----------------------------------------------------------------------------------------------|----|

| 2.2 | Boost converter when $A = 1, B = 1$                                                          | 8  |

| 2.3 | Boost converter when $A = 0, B = 1$                                                          | 8  |

| 2.4 | Boost converter during DCM when $A = 0, B = 0$                                               | 10 |

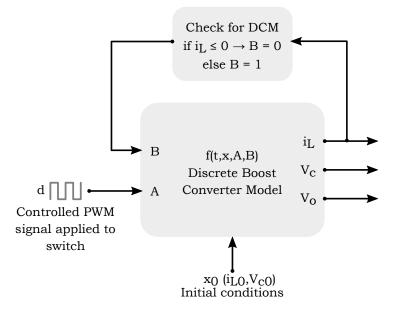

| 2.5 | Functional representation for simulation of discrete boost converter                         | 12 |

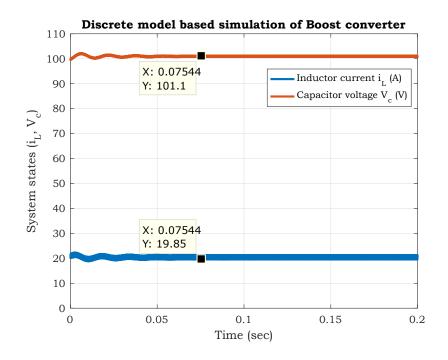

| 2.6 | Discrete model based simulation of boost converter                                           | 13 |

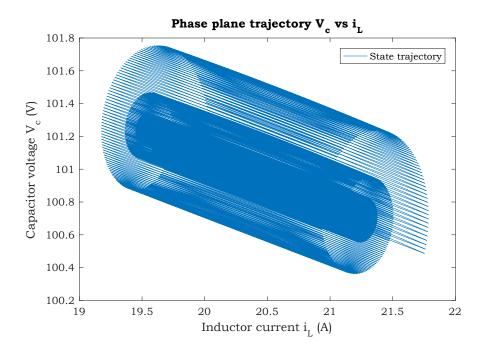

| 2.7 | Phase plane trajectory $V_C \rightarrow i_L$ from simulation shown in Figure 2.6             | 14 |

| 2.8 | n- paralleled boost converters connected to a non-variable resistive                         |    |

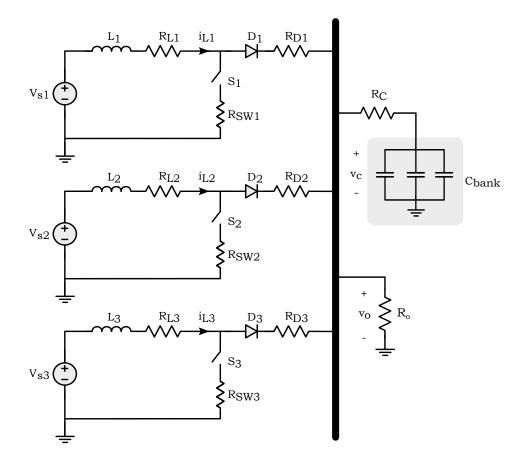

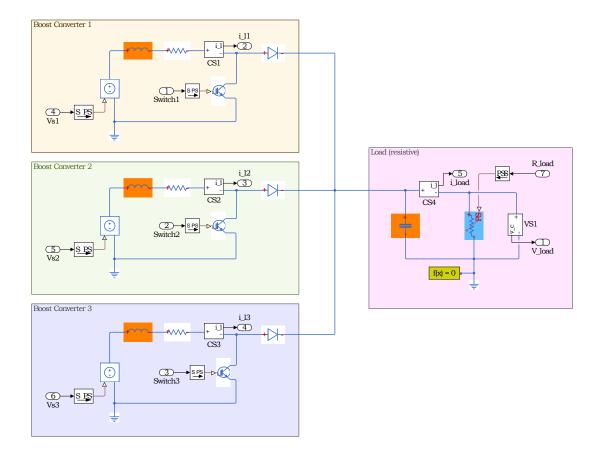

|     | load                                                                                         | 16 |

| 2.9 | 3- paralleled boost converters connected to a non-variable resistive                         |    |

|     | load                                                                                         | 18 |

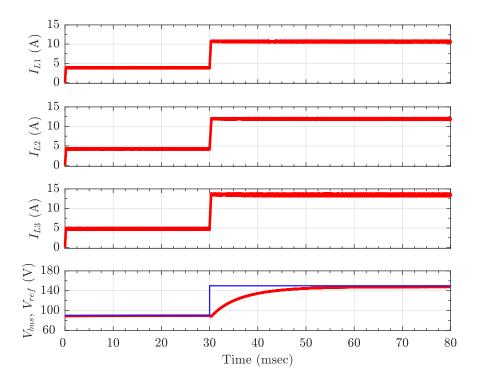

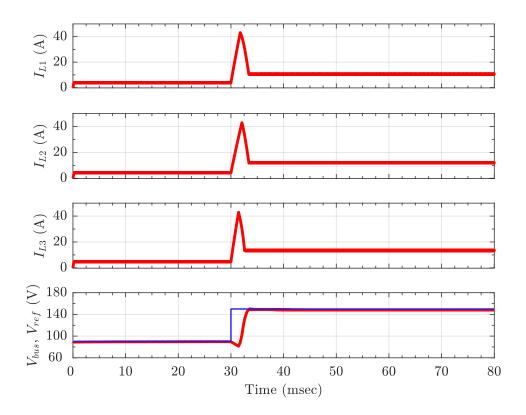

| 3.1 | System states under sliding mode control (SMC); step change in                               |    |

|     | $V_{ref}$ at $t = 30 ms$                                                                     | 25 |

| 3.2 | Instantaneous Energy (in Joules) stored in passive elements during                           |    |

|     | SMC; (a) $E_{L_1}$ , (b) $E_{L_2}$ , (c) $E_{L_3}$ , (d) $E_{C_{bank}}$                      | 26 |

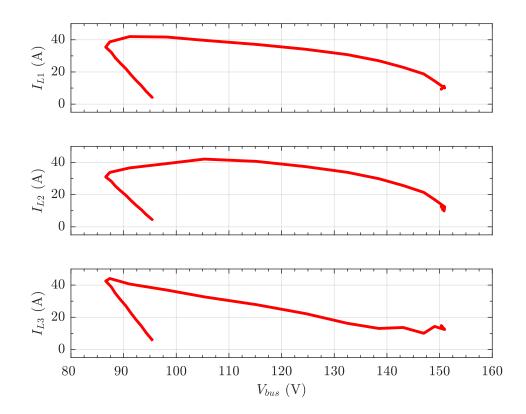

| 3.3 | Phase plane trajectories $I_{L_n} \to V_{bus}$ for all boost converter stages                |    |

|     | over time $t = [0, 80] ms \dots \dots$ | 27 |

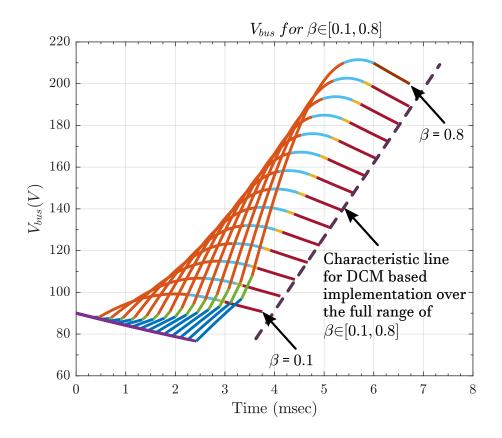

| 3.4 | $V_{bus}$ over $\beta \in [0.1, 0.8]$ for DCM based implementation of MTC                    | 38 |

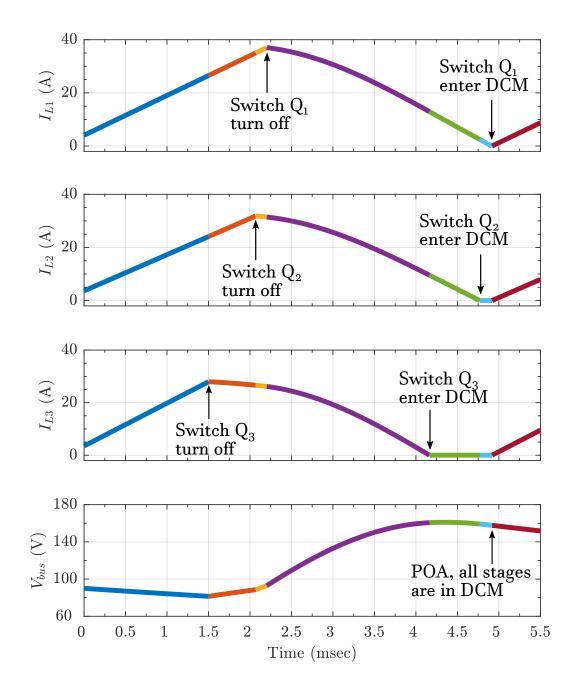

| 3.5 | System states during DCM based implementation of MTC $\ . \ . \ .$                           | 39 |

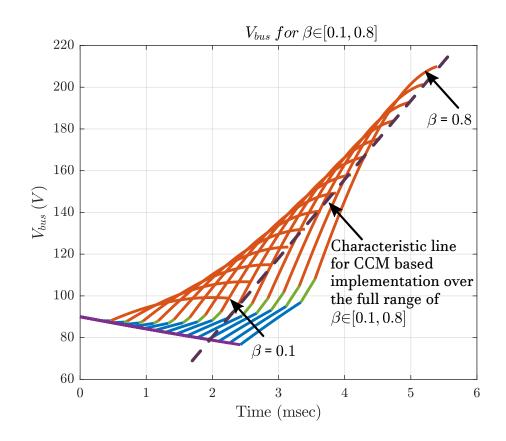

| 3.6 | $V_{bus}$ over $\beta \in [0.1, 0.8]$ for CCM based implementation of MTC                    | 41 |

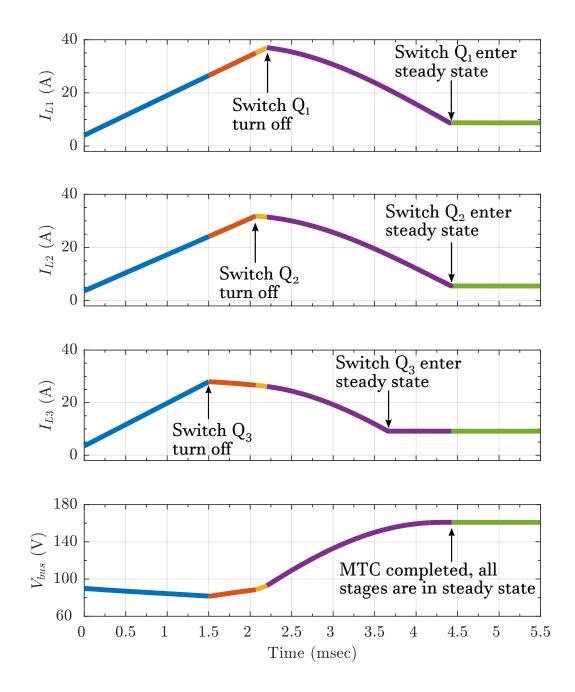

| 3.7 | System states during CCM based implementation of MTC $\ . \ . \ .$                           | 43 |

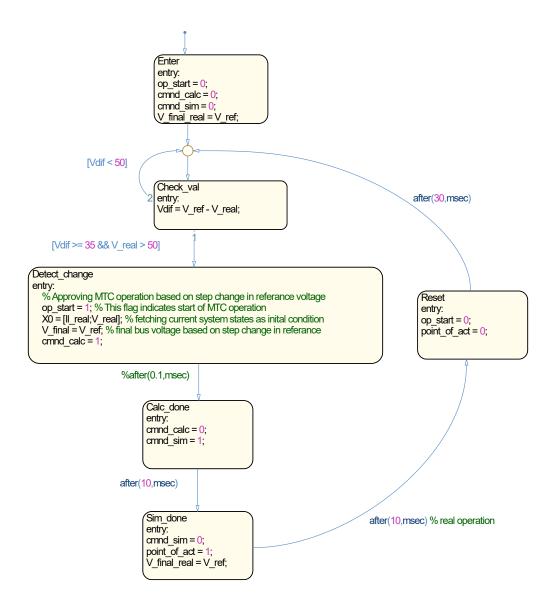

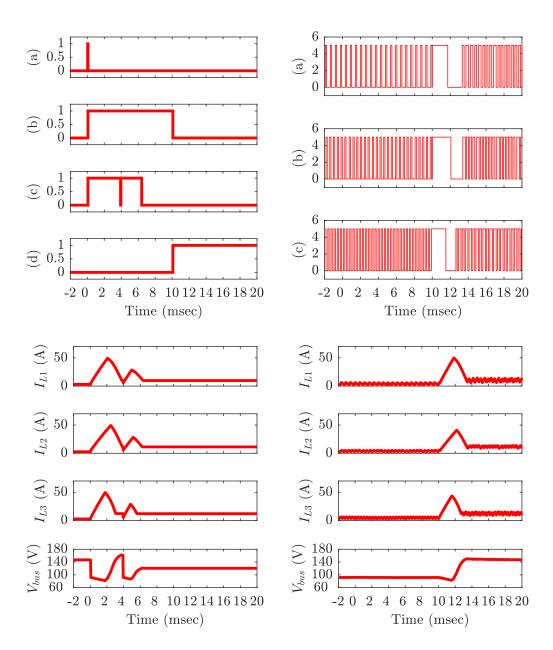

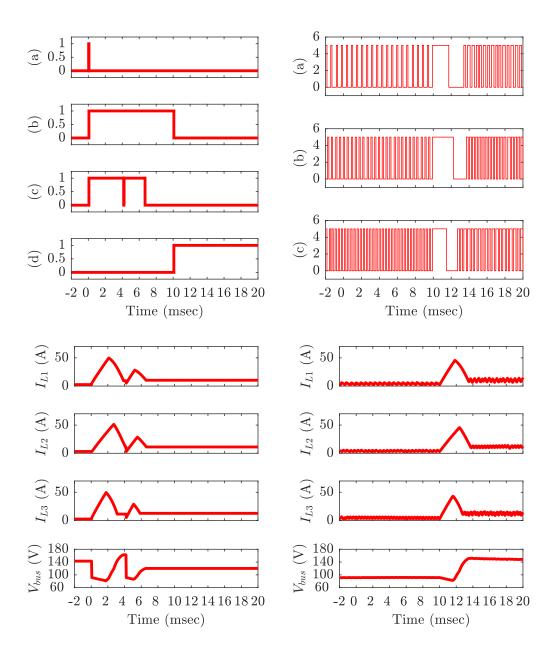

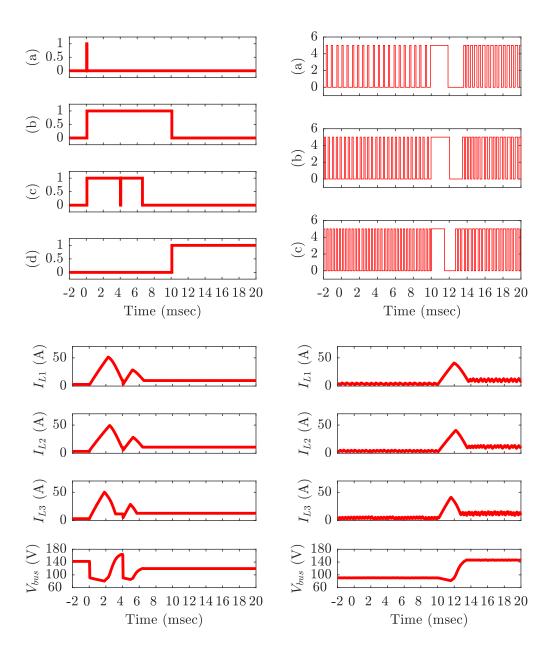

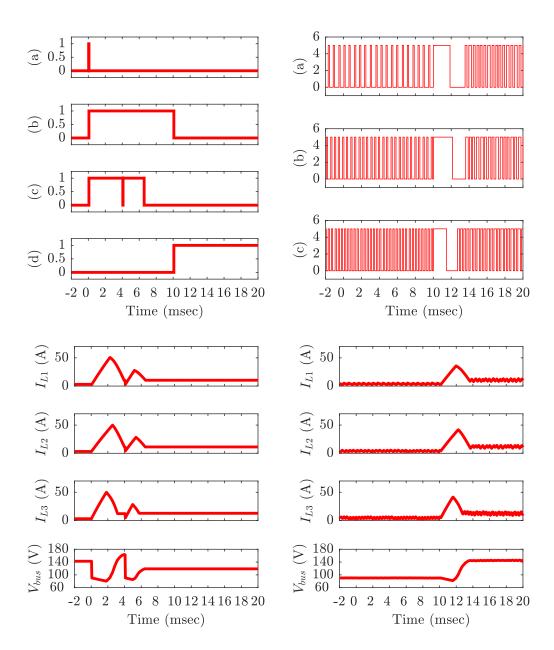

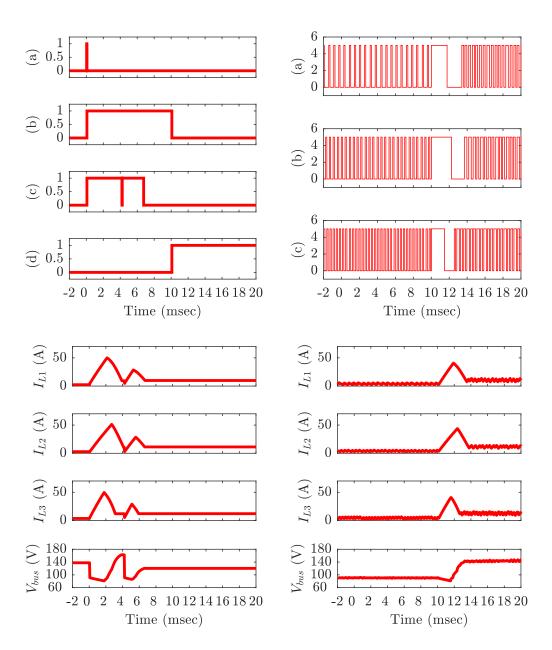

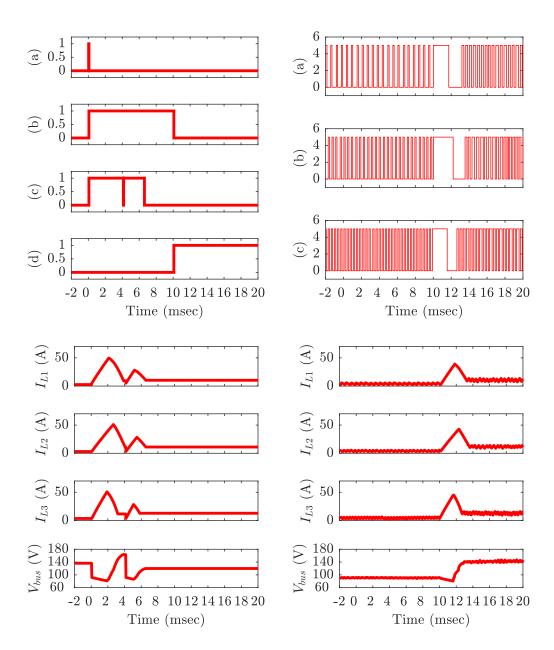

| 3.8 | System states operating under SMC+MTC operation during sim-                                  |    |

|     | ulation; MTC triggered at $t = 30 \text{ ms}$                                                | 53 |

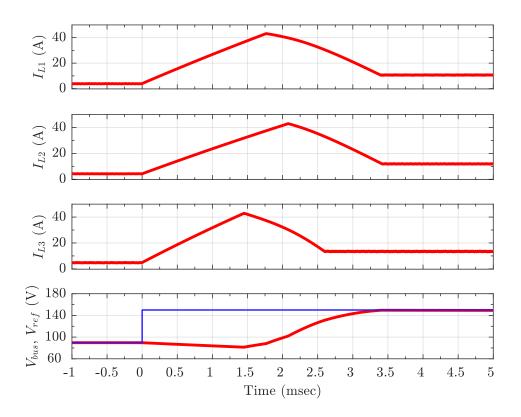

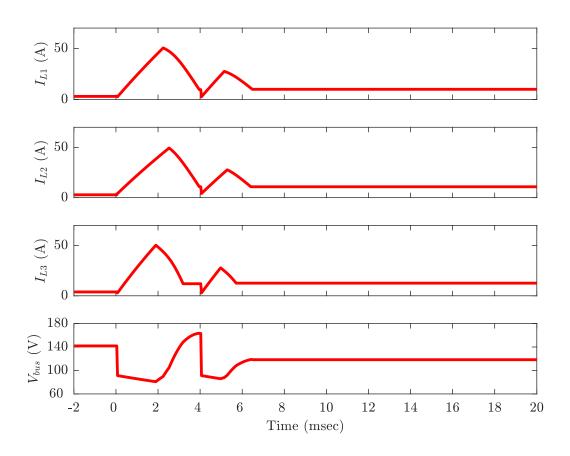

| 3.9  | System states during simulation of MTC with 3-boost converter                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | stages, plotted with trigger point at time $t = 0$ ms $\ldots \ldots \ldots$                                                                                              | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

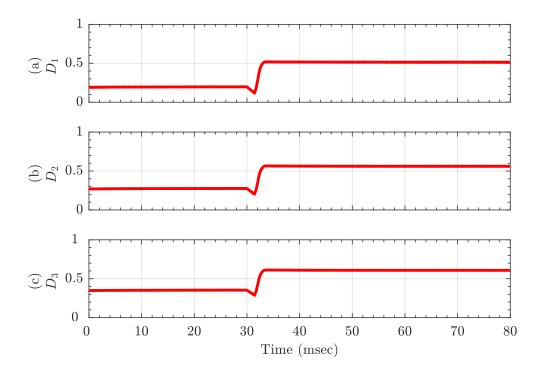

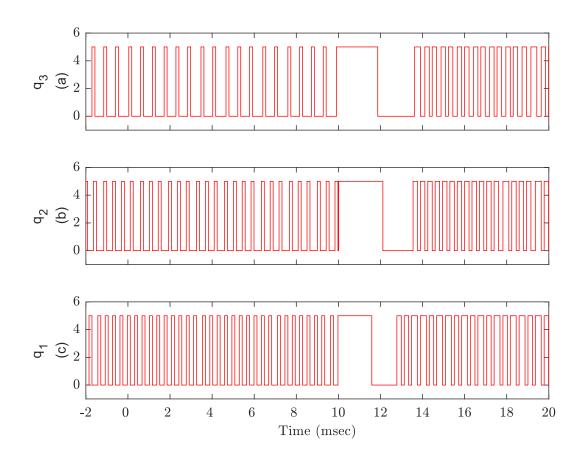

| 3.10 | Duty cycle $(D)$ for all boost converter stages during SMC and MTC                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | operation, (a) $D_1$ , (b) $D_2$ , (c) $D_3$                                                                                                                              | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

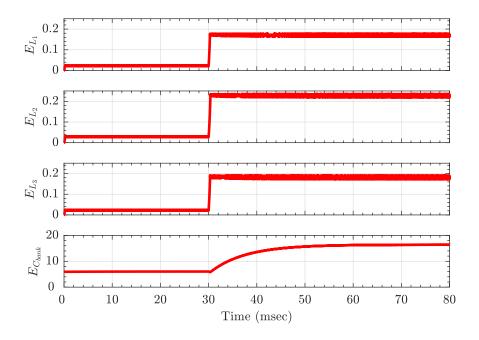

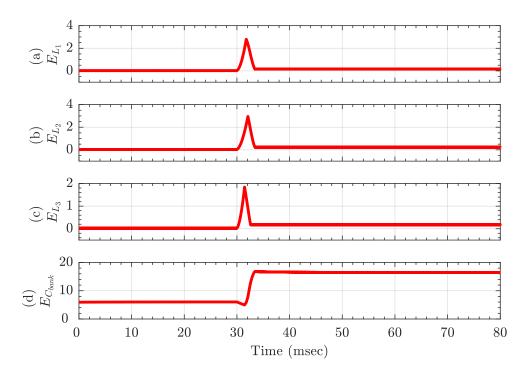

| 3.11 | Instantaneous Energy (in Joules) stored in passive elements during                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | SMC+MTC operation; (a) $E_{L_1}$ ,(b) $E_{L_2}$ , (c) $E_{L_3}$ , (d) $E_{C_{bank}}$                                                                                      | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

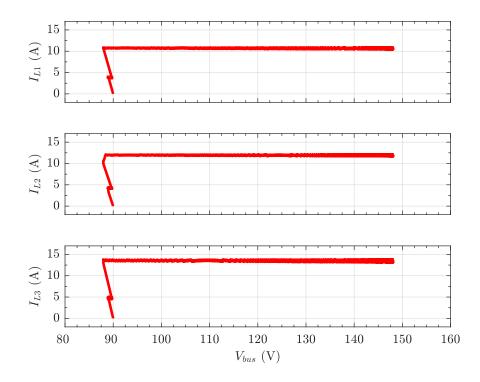

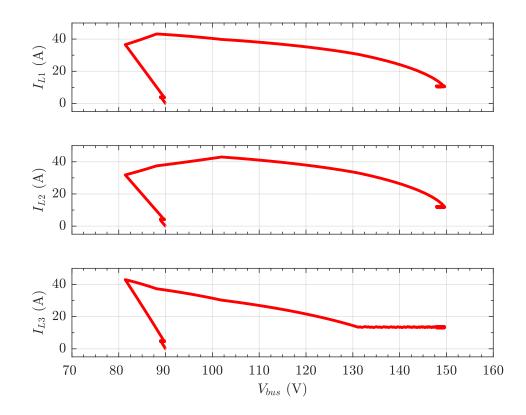

| 3.12 | Phase plane trajectories $I_{L_n} \to V_{bus}$ for all boost converter stages                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | over time $t = [0, 80]$ ms                                                                                                                                                | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

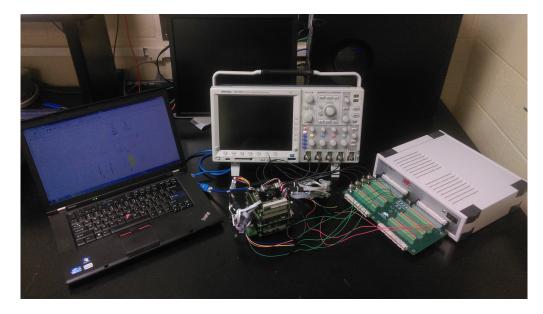

| 4.1  | Experimental setup for HIL Simulation                                                                                                                                     | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

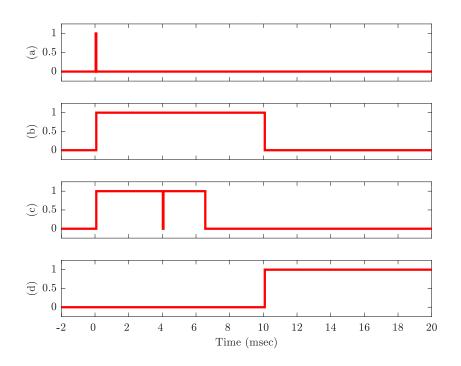

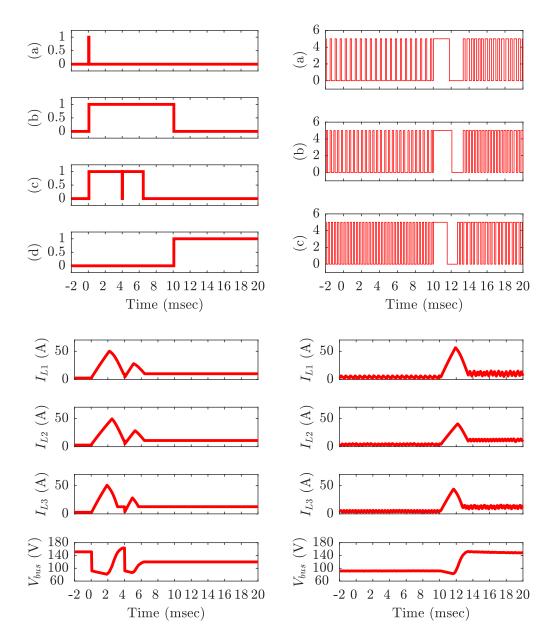

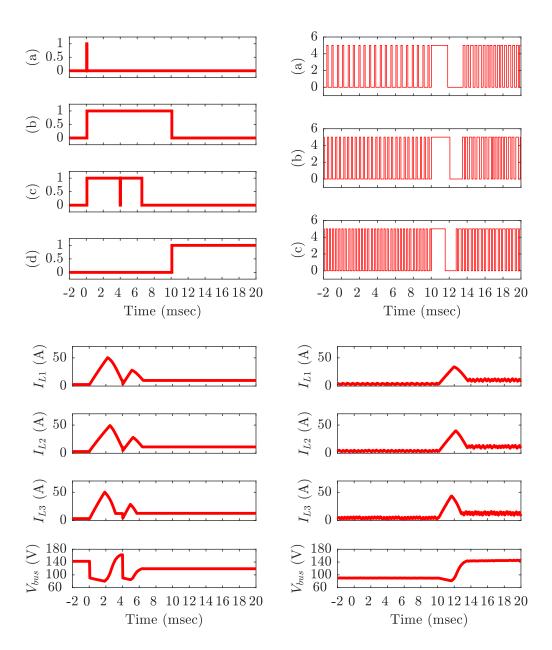

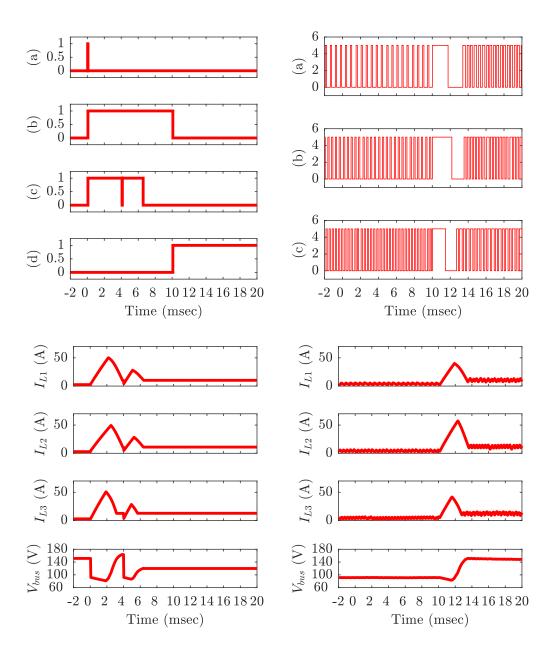

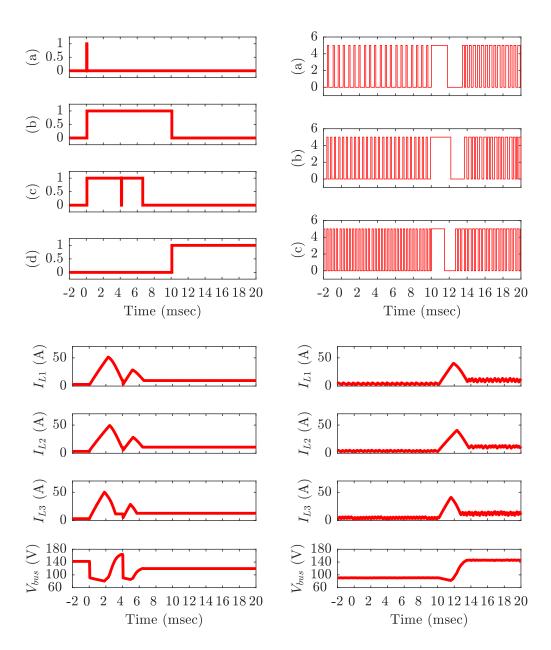

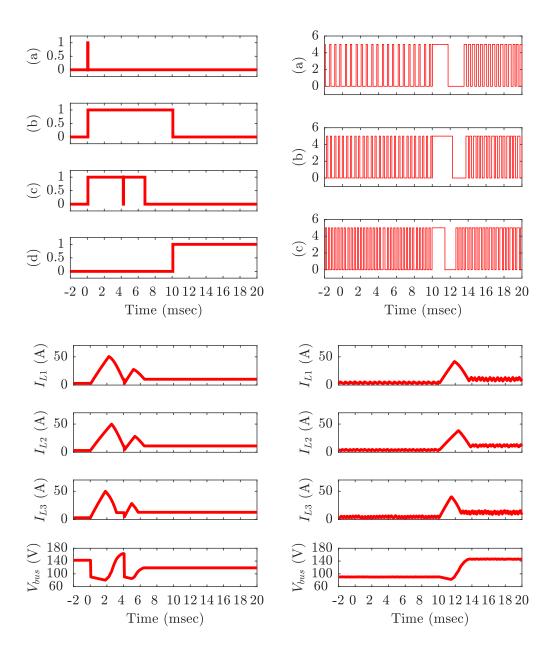

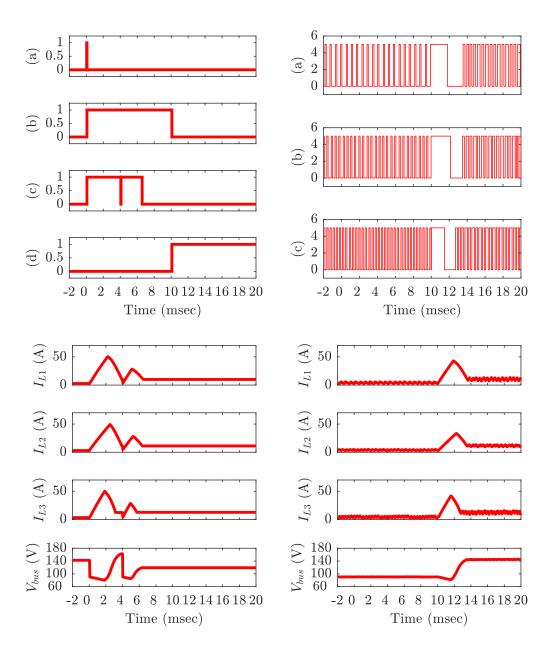

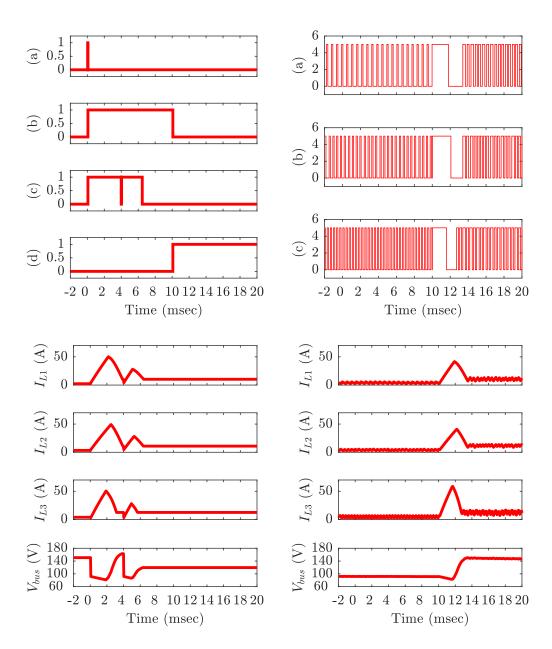

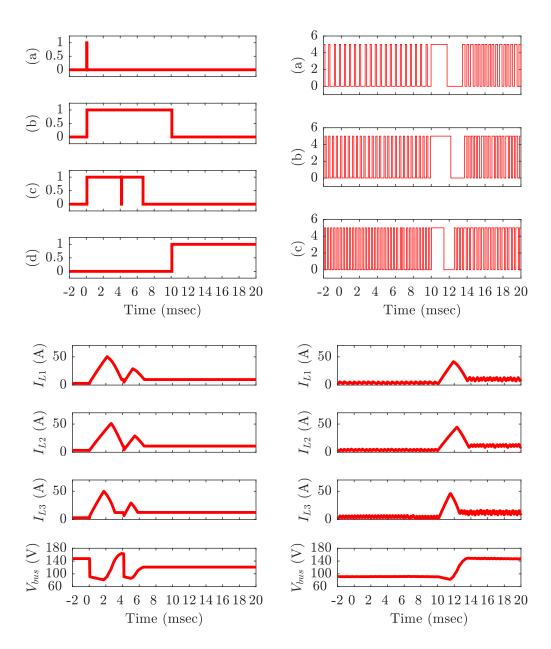

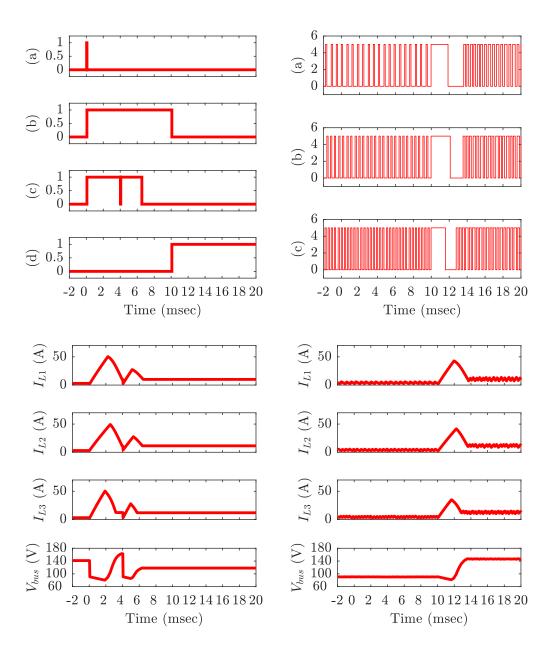

| 4.2  | Trigger signals during concurrent execution of MTC; (a) Simula-                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | tion for MTC algorithm triggered, (b) Simulation enable signal, (c)                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | sequential strobe signals indicating execution of MTC algorithm for                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | two $\beta$ values, (d) MTC trigger for Real-time execution $\ . \ . \ .$ .                                                                                               | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

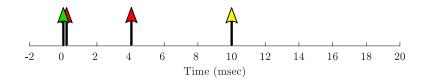

| 4.3  | Timeline of trigger signals for execution of MTC algorithm in real-                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | time                                                                                                                                                                      | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

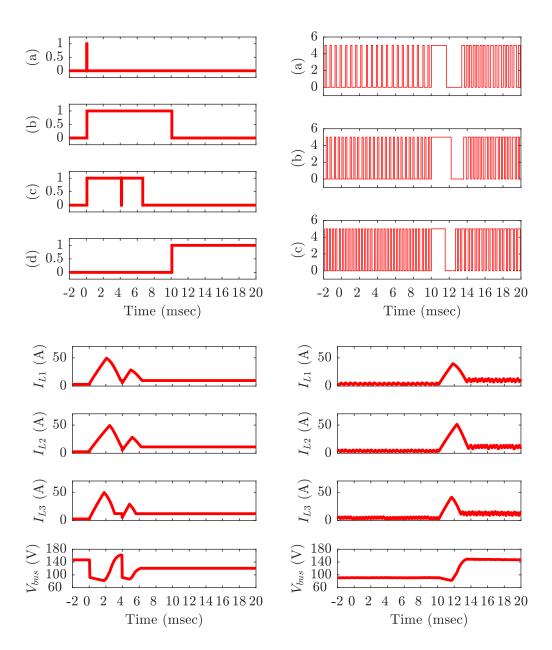

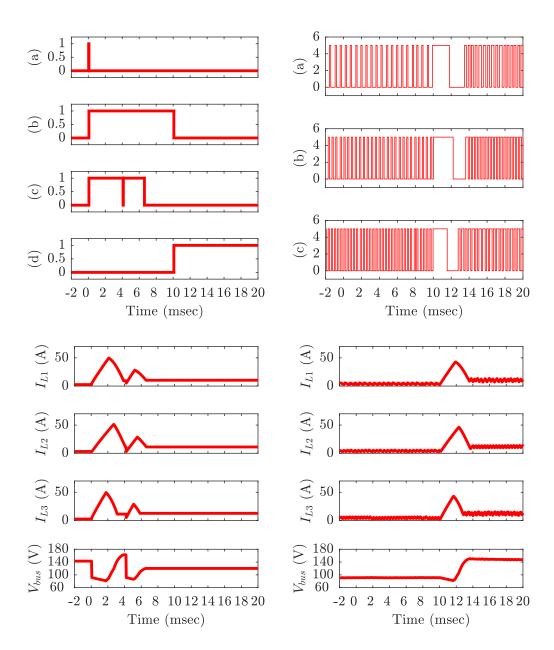

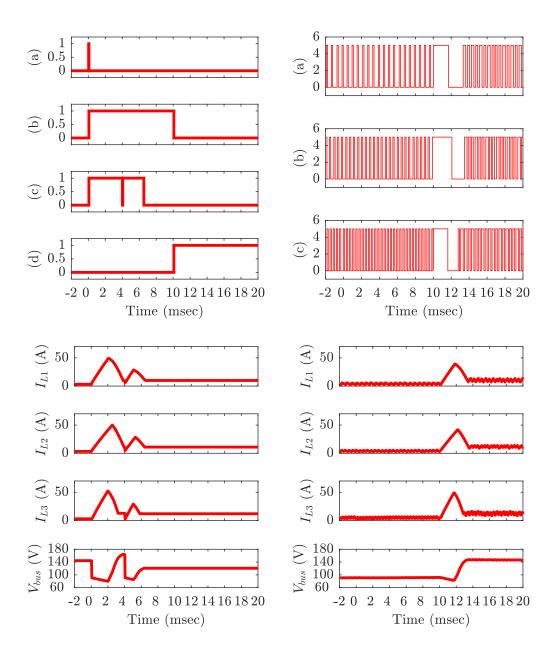

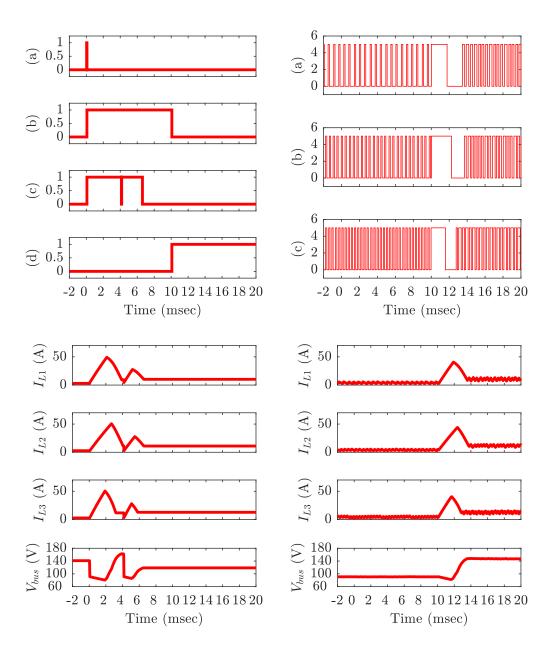

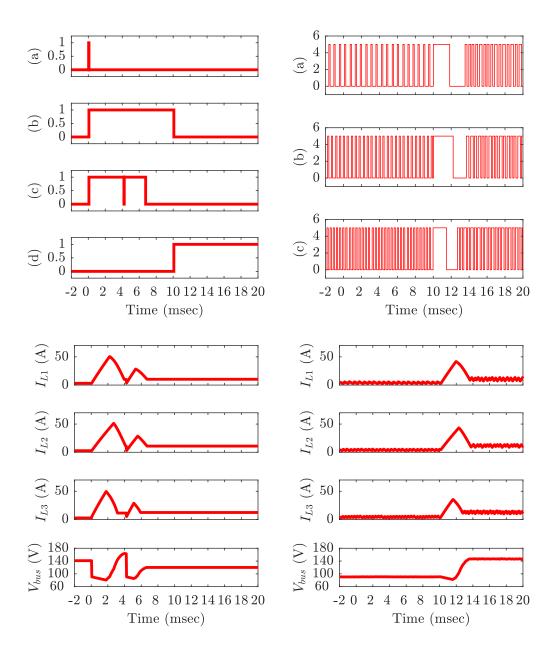

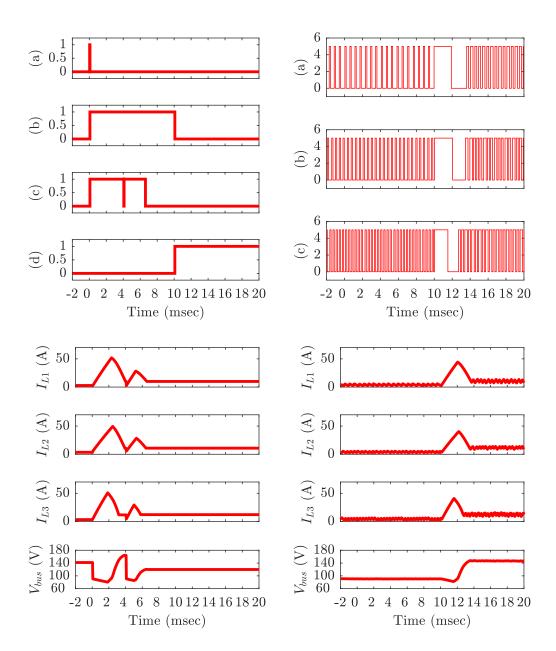

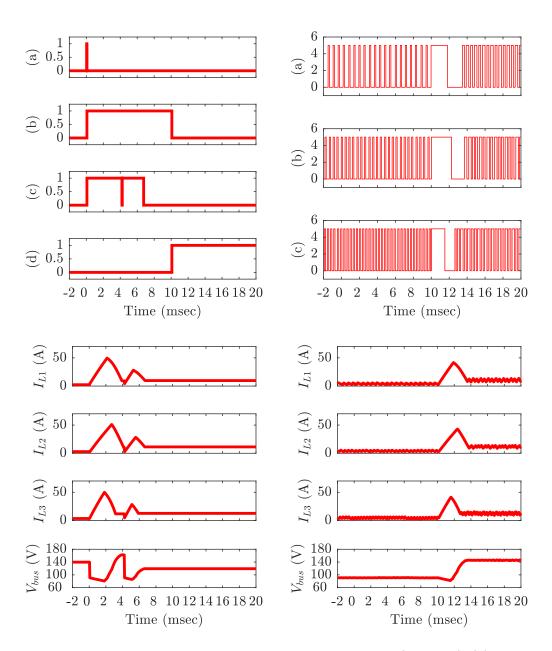

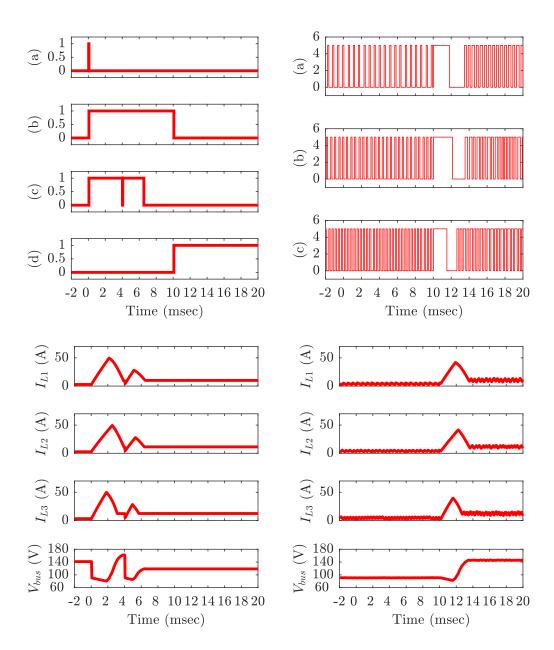

| 4.4  | System states during execution of MTC algorithm                                                                                                                           | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4.5  | Switching signals applied at gates of power switches                                                                                                                      | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

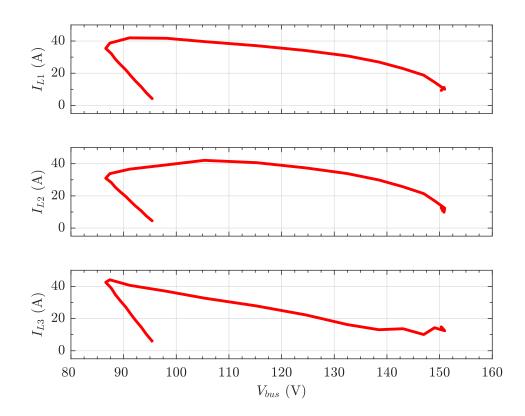

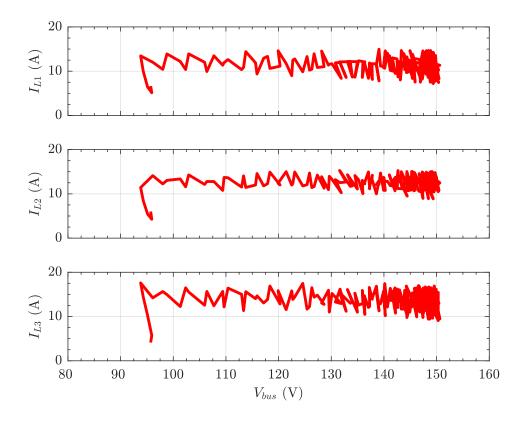

| 4.6  | System states during real-time execution of MTC projected as phase                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | plane trajectories                                                                                                                                                        | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

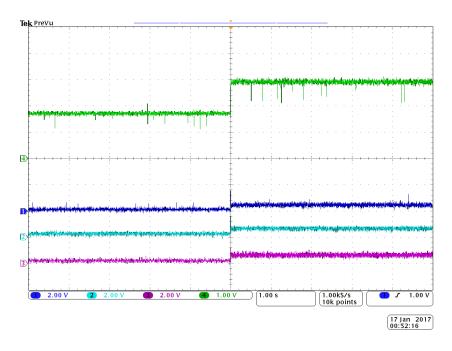

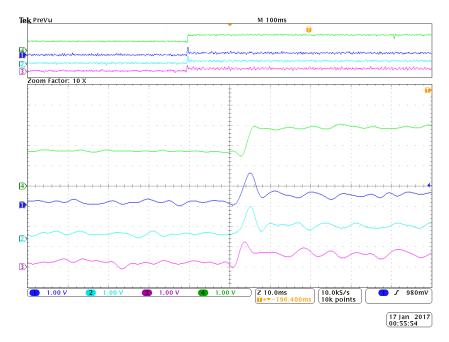

| 4.7  | Oscilloscope capture of MTC operation on time scale of $1s\ldots$                                                                                                         | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4.8  | Horizontally stretched oscilloscope capture of MTC operation on                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | time scale of $10 ms$                                                                                                                                                     | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

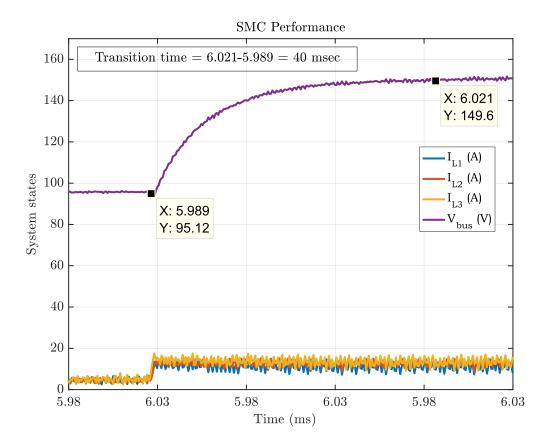

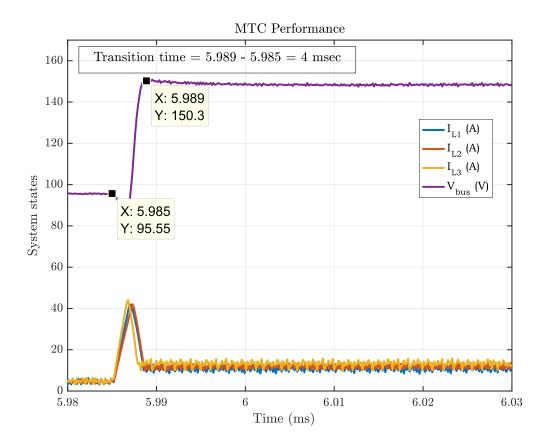

| 4.9  | System states during real time execution of SMC                                                                                                                           | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4.10 | System states during real time execution of SMC                                                                                                                           | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      | <ul> <li>3.10</li> <li>3.11</li> <li>3.12</li> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> <li>4.8</li> <li>4.9</li> </ul> | <ul> <li>stages, plotted with trigger point at time t = 0 ms</li> <li>3.10 Duty cycle (D) for all boost converter stages during SMC and MTC operation, (a) D<sub>1</sub>, (b) D<sub>2</sub>, (c) D<sub>3</sub></li> <li>3.11 Instantaneous Energy (in Joules) stored in passive elements during SMC+MTC operation; (a) E<sub>L1</sub>, (b) E<sub>L2</sub>, (c) E<sub>L3</sub>, (d) E<sub>Cbank</sub></li> <li>3.12 Phase plane trajectories I<sub>Ln</sub> → V<sub>bus</sub> for all boost converter stages over time t = [0, 80]ms</li> <li>4.1 Experimental setup for HIL Simulation</li> <li>4.2 Trigger signals during concurrent execution of MTC; (a) Simulation for MTC algorithm triggered, (b) Simulation enable signal, (c) sequential strobe signals indicating execution of MTC algorithm for two β values, (d) MTC trigger for Real-time execution</li> <li>4.3 Timeline of trigger signals for execution of MTC algorithm in real-time</li> <li>4.4 System states during real-time execution of MTC projected as phase plane trajectories</li> <li>4.6 System states during real-time execution of MTC projected as phase</li> <li>4.7 Oscilloscope capture of MTC operation on time scale of 1 s</li> <li>4.8 Horizontally stretched oscilloscope capture of MTC operation on time scale of 10 ms</li> </ul> |

| 4.11 | System states during real-time execution of SMC projected as phase            |     |

|------|-------------------------------------------------------------------------------|-----|

|      | plane trajectories                                                            | 76  |

| 4.12 | System states during real-time execution of MTC projected as phase            |     |

|      | plane trajectories                                                            | 77  |

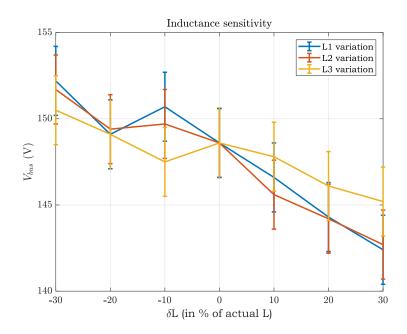

| 4.13 | Sensitivity of $V_{bus}$ with respect to inductance $L_i$ of individual boost |     |

|      | converter stage $\delta$                                                      | 79  |

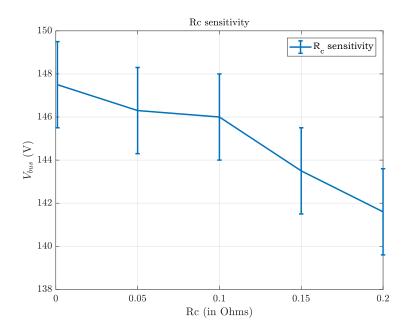

| 4.14 | Sensitivity of $V_{bus}$ with respect to ESR $R_c$ of the Capacitor bank      |     |

|      | $C_{bank}$                                                                    | 79  |

| 5.1  | Execution of tasks in CPU(few high-speed heterogeneous threads)               |     |

|      | vs GPU(large number of homogeneous threads at moderate speed)                 | 84  |

| A.1  | HIL emulation with $L_1 = 0.07L_1 (-30\% change) \dots \dots \dots$           | 103 |

| A.2  | HIL emulation with $L_1 = 0.08L_1 (-20\% change) \dots \dots \dots$           | 104 |

| A.3  | HIL emulation with $L_1 = 0.09L_1 (-10\% change) \dots \dots \dots$           | 105 |

| A.4  | HIL emulation with $L_1 = 1.1L_1 (+10\% change) \ldots \ldots \ldots$         | 106 |

| A.5  | HIL emulation with $L_1 = 1.2L_1 (+20\% change)$                              | 107 |

| A.6  | HIL emulation with $L_1 = 1.3L_1 (+30\% \ change)$                            | 108 |

| A.7  | HIL emulation with $L_2 = 0.07L_2 (-30\% change) \dots \dots \dots$           | 109 |

| A.8  | HIL emulation with $L_2 = 0.08L_2 (-20\% change) \dots \dots \dots$           | 110 |

| A.9  | HIL emulation with $L_2 = 0.09L_2 (-10\% change) \dots$                       | 111 |

| A.10 | HIL emulation with $L_2 = 1.1L_2 (+10\% change) \ldots \ldots$                | 112 |

| A.11 | HIL emulation with $L_2 = 1.2L_2 (+20\% change) \ldots \ldots \ldots$         | 113 |

| A.12 | HIL emulation with $L_2 = 1.3L_2 (+30\% \ change)$                            | 114 |

| A.13 | HIL emulation with $L_3 = 0.07L_3 (-30\% change) \dots \dots \dots$           | 115 |

| A.14 | HIL emulation with $L_3 = 0.08L_3 (-20\% change) \dots \dots$                 | 116 |

|      |                                                                               |     |

| A.15 HIL emulation with $L_3 = 0.09L_3 (-10\% change) \dots \dots \dots$   | 117 |

|----------------------------------------------------------------------------|-----|

| A.16 HIL emulation with $L_3 = 1.1L_3 (+10\% change) \ldots \ldots \ldots$ | 118 |

| A.17 HIL emulation with $L_3 = 1.2L_3 (+20\% change)$                      | 119 |

| A.18 HIL emulation with $L_3 = 1.3L_3 (+30\% change)$                      | 120 |

| A.19 HIL emulation with $R_C = 0.001\Omega$                                | 121 |

| A.20 HIL emulation with $R_C = 0.05\Omega$                                 | 122 |

| A.21 HIL emulation with $R_C = 0.1\Omega$                                  | 123 |

| A.22 HIL emulation with $R_C = 0.15\Omega$                                 | 124 |

| A.23 HIL emulation with $R_C = 0.20\Omega$                                 | 125 |

# List of Tables

| 1 | Paralleled Boost Converter system parameters                           | 23 |

|---|------------------------------------------------------------------------|----|

| 2 | Paralleled boost converter system parameters                           | 46 |

| 3 | Initial and final system states for 3-paralleled boost converters dur- |    |

|   | ing MTC                                                                | 47 |

| 4 | Maximum ON time for boost converter switches during MTC $$             | 47 |

| 5 | Equivalent contribution of each boost converter stage for MTC $$ .     | 48 |

| 6 | Absolute and relative contribution factor for each boost converter     |    |

|   | during MTC                                                             | 48 |

To my grandfather, Mohan Patel.

# Acknowledgments

Firstly, I would like to express my sincere gratitude to my advisor Dr. Wayne Weaver for the continuous support, for his immense patience, motivation, and knowledge. His guidance helped me in all the time of research and writing of this thesis. I could not have imagined having a better advisor and mentor for Masters study. It was truly a previledge for me to have an access to the laboratory and research facilities. It not only helped me to conduct the research but also provided an excellent opportunity to learn and experiment even beyond the scope of this thesis.

Besides my advisor, I would like to thank the rest of my thesis committee, Dr. Gordon Parker and Prof. John Lukowski for their insightful comments and encouragement.

Last but not the least, I would like to thank my family, especially my parents for encouragment and unconditional support that always inspired me pursue this path. I will alway be debtful for their sacrifices througut my life.

# Nomenclature

| MTC            | Minimum Time Control                        |

|----------------|---------------------------------------------|

| $\mathbf{SMC}$ | Sliding Mode Control                        |

| IGBT           | Insulated Gate Bipolar Transistor           |

| MOSFET         | Metal Oxide Surface Field Effect Transistor |

| MBC            | Multiple Boost Converter                    |

| VCS            | Voltage Controlled Source                   |

| CCS            | Current Controlled Sources                  |

| CCM            | Continuous Conduction Mode                  |

| DCM            | Discontinuous Conduction Mode               |

| SBC            | Single Board Computer                       |

| $\mathbf{ESR}$ | Equivalent Series Resistance                |

| PWM            | Pulse Width Modulation                      |

| CPU            | Central Processing Unit                     |

| GPU            | Graphical Processing Unit                   |

# Abstract

Demand for electrification is booming in both, traditional and upcoming generations of technological advancements. One of the constituent blocks of these electrified systems is Power conversion. Power conversion systems are often constructed by paralleling multiple power converter blocks for high performance and reliability of overall system. An advanced control technique is developed with an aim to optimize system states of heterogeneous power converters within minimum time while maintaining feasible stress level on individual power converter blocks. Practical implementation of real-time controller and performance improvement strategies are addressed. Experimental results validating high performance control scheme, and sensitivity analysis of system states as measure of system robustness are also presented.

# 1 Introduction

## 1.1 Thesis objective

Switching mode power supplies are a fundamental component of modern power system, providing most efficient and controllable energy conversion solution. Over many decades of improvements made this technology even superior for all range of power applications. Along with the advancements in computational resources and wide range of control system, power electronics converters have dominated almost every aspect of power systems whether it be a power supply for a lowpower microprocessor[1] or high-power wind-turbines[2][3] to electric vehicles[4][5]. Sophisticated control systems are replacing the role of conventional energy sources by incorporating electrical energy sources along with the power converters.

Significant interest in the range of medium to high power applications are, pulsed power systems where energy is supplied in form of pulses to the load, and quick response systems such as transient stabilization[3]. Often times, high power applications are implemented through combination of several medium power modules to share the overall load[6] [7]. Increasing interest in electrification of naval vessels, amphibious vehicles and motor vehicles demand high speed performance in their operations. A pulsed radar system that conventionally operates through high-frequency oscillators and resonators is also in need for more efficient and less bulky solution for low to mid range detection applications.

To implement above mentioned applications through power converters, a sophisticated control approach is needed. High power applications consist large number of medium power converters that share power load depending on their capabilities. It is also important to note that these modules may or may not be identical in nature. So, the control system should also consider non-symmetric nature of the system. What makes a pulsed power application most challenging is the power level and time duration of pulse. So, it makes overall system very vulnerable to withstand pulses of power that force system to operate at its extreme level. While pulse power applications take minimum time for state transitions, it is also important to facilitate that performance in least amount of time possible so that the overall speed of operation can be increased.

To fulfill the demands for high-power high-speed application, prime objective of this thesis is to develop a control method/architecture that can implement minimum time control for multiple paralleled boost converters in real-time.

## **1.2** Previous art

Numerous research endeavors have been made in providing a feasible solution for the minimum time control problem. Varying from low to high power applications, those solutions fit into a well defined criteria for which the control system/approach was designed. Some of those previous works are briefly discussed in this section.

One of the implementations [8] focusing on minimum time control of single stage boost converter is through finding a solution for a trajectory with boundary conditions and storing the calculated trajectory in a static memory. This kind of approach using pre-calculated trajectories take less time for computation while running the system but the limitation of the approach is that it can not be extended to n-number of parallel boost converter based system. As the number of stages grow, the complexity to find an analytical solution for an optimal control trajectory grows rapidly and hence it can not be a viable option for quick realtime transition. Another important factor to be considered for an off-line solution method is that the accuracy of real-time transition depend on the available memory storage. So, the available on-board memory becomes an important factor in hardware selection.

Another research [9][10][11] focused on multiple power converter stages provide minimum time control solution through mixed-signal compensatory design. One prominent advantage of this method is that the complete control system is implemented through hardware and does not require an on-line computational burden. The control method primarily designed for low-power applications does not consider non-homogeneity of the system. So, all of the power converter stages are assumed identical. Due to the homogeneity in system, a control can be designed merely by considering only one stage and expanding to whole system of n number of stages. It assumes equal sharing of current among the stages and hence makes it very simplified for low power applications. Although, this method provides least computationally expensive solution, it do not fit to most of practical power system application.

Other relevant works [12][13][14][15] that address the minimum time control or similar approach for a specific application and assumption. But most of the methods either consider a simplified topology or non real time solution. There are no solutions available for multiple converters/interleaved converters to have lightweight, scalable and real-time approach that consider non-ideal system parameters. Hence, it is prime focus of this thesis to develop a control method that address all of the short-comings of the methods discussed here.

### **1.3** Thesis organization

A detailed mathematical modeling of a boost converter is derived for different modes of operation, Continuous Conduction Mode (CCM) and Discontinuous Conduction Mode (DCM). The discrete modeling approach is extended for multiple/paralleled Boost converters interfaced to a resistive load. The mathematical implementation derived in the chapter 2 is used for iteration of paralleled boost converter in Minimum Time Control (MTC) operation.

Chapter 3 illustrates the implementation of Sliding Mode Control (SMC) as one of the robust control technique for paralleled boost converter. A concept of contribution and non-identical sharing of inductor currents is introduced as key aspect of MTC. The core content of the thesis, MTC algorithm, is elaborated in this chapter and the simulation results are also illustrated to compare the performance of MTC with SMC.

A real-time implementation of the control system is described in chapter 4. The architecture of the discrete control system for Hardware-in-loop (HIL) emulation of paralleled boost converters under MTC is described. Real-time experimental results for SMC and MTC are also juxtaposed for time domain and phase trajectory point of view. Sensitivity analysis and the experimental results are also demonstrated to highlight robustness of the MTC operation. Final chapter 5 summarize the reported work with conclusive remarks and focuses on several key aspects of the proposed method that can significantly improve the performance (speed of response) of the overall system.

# 2 Overview of Boost converters in and as DC Microgrid

## 2.1 Mathematical model of a Boost converter

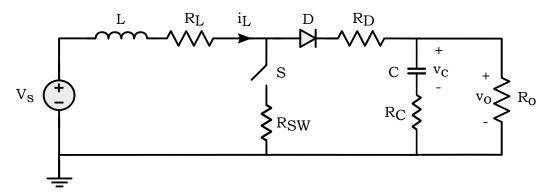

Boost converter/regulator is one of the constituent blocks of a DC microgrid that translate input voltage to a higher level output voltage [16]. The voltage source boost converter shown in Figure 2.1, has voltage source  $V_s$ , ideal controlled electronic switch (IGBT/MOSFET) S, and ideal diode D as an uncontrolled switch. Duty cycle(d) of the PWM signal applied at the gate terminal determine ON time dT, and OFF time (1 - d)T of the switch. Where, T represents the time period of applied PWM signal. Energy storing passive elements, inductance L and capacitance C, have their equivalent series resistances (ESR) represented as  $R_L$  and  $R_c$  respectively. Similarly, electronic switch and diode have their ON resistance modeled as  $R_{SW}$  and  $R_D$  accordingly.

Figure 2.1: Voltage source boost converter with constant resistance

Resistances of electronic devices depends on hardware specifications and include losses in the system model. However, one of the fundamental parameters attributed to electronic devices, cut-off voltage, is omitted from the model Boost converter. For high power applications the effect of any voltage drop of scale of several hundreds of millivolts tend to alter overall system performance at no significant level. One another reason, elaborated in detail in section (3.2.1), to eliminate the terms with non-significant impact on accuracy of system model is to reduce simulation time while running in real-time.

Assuming strictly non-linear and ideal switching of a transistor S and diode D, the boost converter circuit operates in a different manner according to the discrete state of the switch and diode. In general, boost converter has two modes of operations [17] [18], namely,

- 1. Continuous conduction mode (CCM)

- 2. Discontinuous conduction mode (DCM)

CCM is the mode of operation in which, inductor current  $i_L$  remains always nonzero and positive for any switch period; whereas, during DCM inductor  $i_L$  can reduce to zero during OFF period of switch. Depending upon switch state and inductor current there exist multiple combinations of the boost converter circuit. In order to simplify discrete modeling of the boost converter circuit, these combinations are lumped with the linear model of individual circuit combination through binary variables designated as A and B. Where,

$$A = \begin{cases} 1, & Switch \ S \ is \ ON \\ 0, & Switch \ S \ is \ OFF \end{cases}$$

(2.1)

$$B = \begin{cases} 1, & inductor \ current \ i_L \in (0, \infty) \\ 0, & inductor \ current \ i_L = 0 \end{cases}$$

(2.2)

## 2.1.1 Discrete modeling of Boost converter in CCM

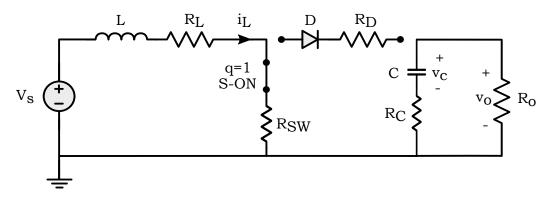

According to equations (2.1) and (2.2), binary variable B = 1 and A = 1/0 represents the state of switch S. Two different circuit typologies resulting from this combination are illustrated in Figure 2.2-2.3.

Figure 2.2: Boost converter when A = 1, B = 1

Figure 2.3: Boost converter when A = 0, B = 1

Using KVL and KCL for the circuit shown in Figure 2.2, differential equations of

system states, current through inductor  $i_L$  and voltage across capacitor  $v_C$ , and output voltage across load resistor  $v_O$  are:

$$\frac{di_L}{dt} = \frac{(R_L + R_{SW})}{L}i_L + 0v_C + \frac{1}{L}V_S$$

(2.3)

$$\frac{dv_C}{dt} = 0i_L - \frac{1}{(R_o + R_C)C}v_C + 0V_S$$

(2.4)

$$v_O = 0i_L + \frac{R_o}{R_o + R_C} v_C + 0V_S \tag{2.5}$$

Similarly, the differential system of equations for circuit shown in Figure 2.3 can be represented as:

$$\frac{di_L}{dt} = -\frac{R_o(R_L + R_D) + R_c(R_o + R_L + R_D)}{L(R_o + R_c)}i_L - \frac{R_o}{L(R_o + R_c)}v_C + \frac{1}{L}V_S \quad (2.6)$$

$$\frac{dv_C}{dt} = \frac{R_o}{(R_o + R_c)C} i_L - \frac{1}{(R_o + R_C)C} v_C + 0V_S$$

(2.7)

$$v_O = \frac{R_o R_c}{R_o + R_C} i_L + \frac{R_o}{R_o + R_C} v_C + 0V_S$$

(2.8)

Combining both aforementioned discrete systems, using Boolean arithmetic for variables A and B, yields into following set of equations:

$$\frac{di_L}{dt} = \frac{(R_L + R_{SW})}{L} i_L A - \frac{R_o(R_L + R_D) + R_c(R_o + R_L + R_D)}{L(R_o + R_c)} i_L \overline{A}$$

(2.9)

$$- \frac{R_o}{L(R_o + R_c)} v_C \overline{A} + \frac{1}{L} V_S$$

$$\frac{dv_C}{dt} = \frac{R_o}{(R_o + R_c)C} i_L \overline{A} - \frac{1}{(R_o + R_C)C} v_C + 0 V_S$$

(2.10)

$$v_o = \frac{R_o R_c}{R_o + R_C} i_L \overline{A} + \frac{R_o}{R_o + R_C} v_C + 0V_S \tag{2.11}$$

Since the boost converter is operating in CCM mode and hence B = 1, as per the Boolean redundancy law, none of the equations (2.9)-(2.11) contain Boolean variable B. These set of equations represents all combinations of system. There exist few ome states for CCM mode based on state of electronic switch.

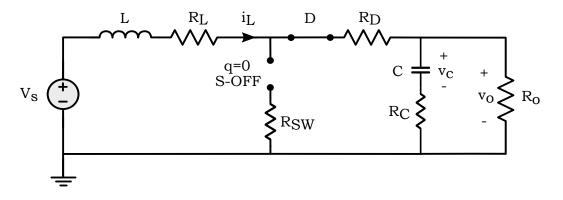

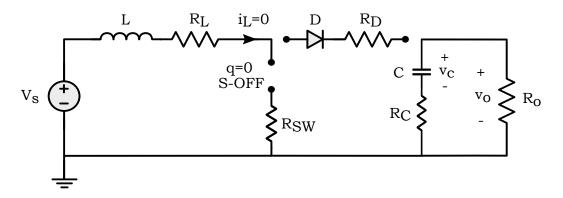

#### 2.1.2 Discrete modeling of Boost converter in DCM

Discontinuous mode of boost converter attributes to the zero inductor current  $i_L = 0$ . In contrast to CCM, where inductor current remains always non-zero due to closed electric path either through switch S or diode D; in DCM there exist an additional circuit configuration. When A = 0 and B = 0, electronic switch S and diode D remain in OFF mode, and, hence leave no electric path for inductor current  $i_L$  to flow. The circuit configuration of this mode is illustrated in Figure (2.4).

Figure 2.4: Boost converter during DCM when A = 0, B = 0

Differential system of equations for the circuit configuration (A = 0 and B = 0)

shown in Figure (2.4) is represented as:

$$\frac{di_L}{dt} = 0i_L + 0v_C + 0V_S \tag{2.12}$$

$$\frac{dv_C}{dt} = 0i_L - \frac{1}{(R_o + R_C)C}v_C + 0V_S$$

(2.13)

$$v_O = 0i_L + \frac{R_o}{R_o + R_C} v_C + 0V_S \tag{2.14}$$

Apart from this DCM specific circuit configuration, rest of the circuit combinations from CCM, Equations (2.9)-(2.11), remain unchanged for  $i_L > 0$ . Hence, complete discrete model with CCM and DCM modes can be represented in combined from as follows:

$$\frac{di_L}{dt} = \frac{(R_L + R_{SW})}{L} i_L AB - \frac{R_o(R_L + R_D) + R_c(R_o + R_L + R_D)}{L(R_o + R_c)} i_L \overline{A}B \quad (2.15)$$

$$- \frac{R_o}{L(R_o + R_c)} v_C \overline{A}B + \frac{1}{L} V_S B$$

$$\frac{dv_C}{dt} = \frac{R_o}{(R_o + R_c)C} i_L \overline{A}B - \frac{1}{(R_o + R_C)C} v_C + 0V_S$$

(2.16)

$$v_O = \frac{R_o R_c}{R_o + R_C} i_L \overline{A}B + \frac{R_o}{R_o + R_C} v_C + 0V_S$$

(2.17)

The aforementioned discrete model of boost converter will provide strong foundation in extension of single stage boost converter to multiple boost converter system with minimal changes. In addition, the extended multiple/paralleled boost converter model based on discrete modeling approach will be incorporated crucially in implementation of MTC algorithm elaborated in section (3.2).

#### 2.1.3 Simulation of Boost converter using discrete model

In general, average modeling of boost converter [19] is a very versatile method for simulation and implementation of controls. The average modeling approach emphasis on average of ON- and OFF- state of system and connects duty cycle d of PWM signal, applied at the gate of switch S, with the system states  $i_L$  and  $v_C$ . With identical system parameters, there is no functional difference in operation boost converter, but discrete modeling approach provides full access to system model at each switch transitions, from  $1(ON) \rightarrow 0(OFF)$  and  $0(OFF) \rightarrow 1(ON)$ , hence implementation of discrete controls becomes much easier. In order to exemplify how to simulate discrete model, a functional block diagram of simulation process is illustrated in Figure 2.5. It is important to note that the step-time (model update time) for simulation is significantly lower than time period of PWM signal.

Figure 2.5: Functional representation for simulation of discrete boost converter

Figure 2.6: Discrete model based simulation of boost converter

To validate system response with discrete model, a sample boost converter simulation starting from steady state and operating under duty cycle d based open-loop control is illustrated in Figure 2.6. Note that the system states  $i_L$  and  $V_C$  begins with initial conditions close to the steady state values. The deviations at the beginning, due to switching of system states, settle down very quickly and continue with steady state response. Besides from time based depiction of system states, phase-plane representation of system states provide more insight into the state transitions per switching event instead of time. This method of representing system states, phase plane trajectories, will be used extensively in later sections to evaluate and analyze performance of SMC (in (3.1)) and MTC (in (3.2)) based controls algorithms. A phase plane trajectory for a time-domain simulation result shown in Figure 2.6 is given in Figure 2.7.

**Figure 2.7:** Phase plane trajectory  $V_C \rightarrow i_L$  from simulation shown in Figure 2.6

From the phase trajectory, it is evident that the system states converge circularly to the steady state within finite time. Additionally, each switch transition provide more insight to variance and steady state error of the inductor current and capacitor voltage.

# 2.2 Mathematical model of multiple/paralleled Boost converters connected to a resistive load

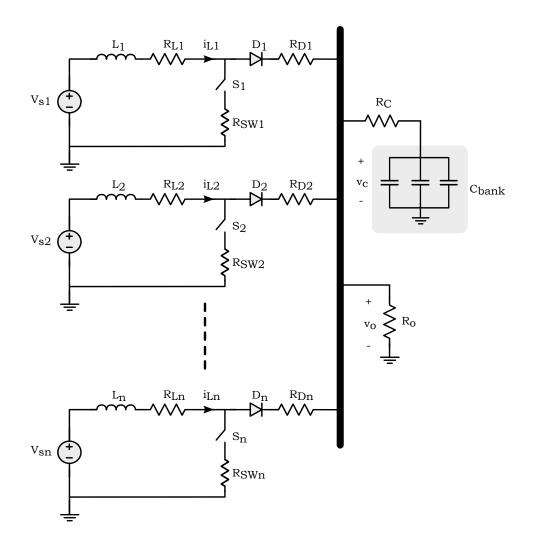

The discrete modeling approach developed in section (2.1.2) for a single boost converter can be easily extended for multiple boost converters connected to a load. A simplified electrical network of multiple boost converter is illustrated in Figure 2.8, where *n* number of boost converter low-side stages are connected a bus. All of the individual boost converters are assumed to be connected to an independent energy source and hence form a parallel network of boost converters. In the literature, similar typologies developed for low-power applications emphasis on identical system parameters, i.e.  $L_1 = L_2 = \ldots = L_n = L$ . The assumption of identical system parameters simplifies the control system architecture by a large extent and reduces the computational complexity for optimal control of system states. This is accomplished by reducing system complexity to one of the stages and then sharing/dividing control law among the stages equally.

While this approach of sharing system states, i.e inductor current  $i_L$ , among all stages simplifies the computational burden of optimization problem, but do not provide similar performance to the system that has heterogeneous system parameters. Practical systems, specifically for high-power applications, are not suitable to be considered as identical. Hence, the prime focus of this study is to include non-identical system parameters into the system modeling. An added advantage of this approach is that it covers the system with identical parameters as one of its subset cases.

By extending the approach of discrete modeling of a boost converter in CCM and DCM modes for multiple/paralleled boost converters network, each stage has has binary variable  $B_n = \{0, 1\}$  and  $A_n = \{0, 1\}$  to represents state of switch  $S_n$ . The combination resulting from these Boolean variables convert each converter stage into one of the configurations as illustrated in Figure 2.2,2.3 and 2.4. Irrespective of mode of operation (CCM/DCM) for an individual boost converter, the flow of energy (inductor current  $I_L$ ) remains unidirectional, from source  $V_{Sn}$  to load.

Figure 2.8: n- paralleled boost converters connected to a non-variable resistive load

Mathematical model of n-paralleled boost converters is :

$$\frac{di_{L1}}{dt} = \frac{(R_{L1} + R_{SW1})}{L_1} i_{L1} A_1 B_1 - \frac{R_o}{L_1 (R_o + R_c)} v_C \overline{A}_1 B_1 \qquad (2.18)$$

$$- \frac{R_o (R_{L1} + R_{D1}) + R_c (R_o + R_{L1} + R_{D1})}{L_1 (R_o + R_c)} i_{L1} \overline{A}_1 B_1 + \frac{1}{L_1} V_{S1} B_1$$

$$\frac{di_{L2}}{dt} = \frac{(R_{L2} + R_{SW2})}{L_2} i_{L2} A_2 B_2 - \frac{R_o}{L_2 (R_o + R_c)} v_C \overline{A}_2 B_2$$

$$-\frac{R_{o}(R_{L2}+R_{D2})+R_{c}(R_{o}+R_{L2}+R_{D2})}{L_{2}(R_{o}+R_{c})}i_{L2}\overline{A}_{2}B_{2}+\frac{1}{L_{2}}V_{S2}B_{2} \quad (2.19)$$

$$\vdots$$

$$\frac{di_{Ln}}{dt} = \frac{(R_{Ln}+R_{SWn})}{L_{n}}i_{Ln}A_{n}B_{n} - \frac{R_{o}}{L_{n}(R_{o}+R_{c})}v_{C}\overline{A}_{n}B_{n}$$

$$-\frac{R_{o}(R_{Ln}+R_{Dn})+R_{c}(R_{o}+R_{Ln}+R_{Dn})}{L_{n}(R_{o}+R_{c})}i_{Ln}\overline{A}_{n}B_{n}+\frac{1}{L_{n}}V_{Sn}B_{n} \quad (2.20)$$

$$\frac{dv_{C}}{dt} = \left\{\frac{R_{o}}{(R_{o}+R_{c})C}i_{L1}\overline{A}_{1}B_{1}+\frac{R_{o}}{(R_{o}+R_{c})C}i_{L2}\overline{A}_{2}B_{2}+\cdots\right.$$

$$+\frac{R_{o}}{(R_{o}+R_{c})C}i_{Ln}\overline{A}_{n}B_{n}\right\} - \frac{1}{(R_{o}+R_{C})C}v_{C} \quad (2.21)$$

$$v_{O} = \left\{\frac{R_{o}R_{c}}{R_{o}+R_{C}}i_{L1}\overline{A}_{1}B_{1}+\frac{R_{o}R_{c}}{R_{o}+R_{C}}i_{L2}\overline{A}_{2}B_{2}+\cdots\right.$$

$$+\frac{R_{o}R_{c}}{R_{o}+R_{C}}i_{Ln}\overline{A}_{n}B_{n}\right\} + \frac{R_{o}}{R_{o}+R_{C}}v_{C} \quad (2.22)$$

Hereafter, a simplified version of 3-paralled boost converters shown in Figure 2.9 will be used to design control methods for the multiple/paralleled boost converter network. The simplified network will also be considered as reference to demonstrate simulation and experimental results in following sections of this thesis. Reduced order mathematical model for the microgrid network shown in Figure 2.9 can be described by Equations (2.23)-(2.27). As noted earlier, parasitic components of inductor, capacitors and electronic switches are taken into account to replicate identical system behavior as much as feasible. Here, it is important to

note that all inductor currents  $i_{L1}$ ,  $i_{L2}$ ,  $i_{L3}$ , and capacitor voltage  $v_C$  are dependent states and linked together. However, inductor currents of individual stages are separate; indicates that there is no direct electrical connection between two boost converter stages and they transfer energy individually from sources to load.

Figure 2.9: 3- paralleled boost converters connected to a non-variable resistive load

$$\frac{di_{L1}}{dt} = \frac{(R_{L1} + R_{SW1})}{L_1} i_{L1} A_1 B_1 - \frac{R_o}{L_1 (R_o + R_c)} v_C \overline{A}_1 B_1

- \frac{R_o (R_{L1} + R_{D1}) + R_c (R_o + R_{L1} + R_{D1})}{L_1 (R_o + R_c)} i_{L1} \overline{A}_1 B_1 + \frac{1}{L_1} V_{S1} B_1 \quad (2.23)$$

$$\frac{di_{L2}}{dt} = \frac{(R_{L2} + R_{SW2})}{L_2} i_{L2} A_2 B_2 - \frac{R_o}{L_2(R_o + R_c)} v_C \overline{A}_2 B_2$$

$$- \frac{R_o(R_{L2} + R_{D2}) + R_c(R_o + R_{L2} + R_{D2})}{L_2(R_o + R_c)} i_{L2} \overline{A}_2 B_2 + \frac{1}{L_2} V_{S2} B_2 \qquad (2.24)$$

$$\frac{di_{L3}}{dt} = \frac{(R_{L3} + R_{SW3})}{L_n} i_{L3} A_3 B_3 - \frac{R_o}{L_3 (R_o + R_c)} v_C \overline{A}_3 B_3$$

$$- \frac{R_o (R_{L3} + R_{D3}) + R_c (R_o + R_{L3} + R_{D3})}{L_3 (R_o + R_c)} i_{L3} \overline{A}_3 B_3 + \frac{1}{L_3} V_{S3} B_3 \qquad (2.25)$$

$$\frac{dv_C}{dt} = \left\{ \frac{R_o}{(R_o + R_c)C} i_{L1}\overline{A}_1 B_1 + \frac{R_o}{(R_o + R_c)C} i_{L2}\overline{A}_2 B_2 + \frac{R_o}{(R_o + R_c)C} i_{L3}\overline{A}_3 B_3 \right\} - \frac{1}{(R_o + R_C)C} v_C$$

(2.26)

$$v_{O} = \left\{ \frac{R_{o}R_{c}}{R_{o} + R_{C}} i_{L1}\overline{A}_{1}B_{1} + \frac{R_{o}R_{c}}{R_{o} + R_{C}} i_{L2}\overline{A}_{2}B_{2} + \frac{R_{o}R_{c}}{R_{o} + R_{C}} i_{L3}\overline{A}_{3}B_{3} \right\} + \frac{R_{o}}{R_{o} + R_{C}} v_{C}$$

$$(2.27)$$

Equation (2.27) represents actual voltage across load  $R_o$  which is almost equivalent to bus/capacitor voltage  $v_C$ , given  $R_c \ll R_o$ .

# 3 Sliding Mode Control (SMC) and Minimum Time Control(MTC) of paralleled boost converters

Designing the control system for the DC-DC boost converter is a complex process due the non-linear characteristic of converter. The non-linearity of a boost or any other type of power converter is studied under specific category of systems, known as, Variable Structure System(VSS) [20]. The variable structure of system, here boost converter, attributes to the different system configuration due to condition of switches. Depending on the state of power electronic switch, an overall system will reduce to a subsystem and will have specific characteristic according to the mode of operation. Mathematical model and equivalent electrical circuit for a boost converter is elaborated in section (2.1) during possible switch configurations.