Dissertations, Master's Theses and Master's Reports - Open

Dissertations, Master's Theses and Master's Reports

2014

### MINING AND VERIFICATION OF TEMPORAL EVENTS WITH APPLICATIONS IN COMPUTER MICRO-ARCHITECTURE RESEARCH

Hui Meen Nyew Michigan Technological University

Follow this and additional works at: https://digitalcommons.mtu.edu/etds

Part of the Computer Sciences Commons

Copyright 2014 Hui Meen Nyew

#### **Recommended Citation**

Nyew, Hui Meen, "MINING AND VERIFICATION OF TEMPORAL EVENTS WITH APPLICATIONS IN COMPUTER MICRO-ARCHITECTURE RESEARCH", Dissertation, Michigan Technological University, 2014. https://digitalcommons.mtu.edu/etds/796

Follow this and additional works at: https://digitalcommons.mtu.edu/etds

Part of the Computer Sciences Commons

## MINING AND VERIFICATION OF TEMPORAL EVENTS WITH APPLICATIONS IN COMPUTER MICRO-ARCHITECTURE RESEARCH

By

Hui Meen Nyew

#### A DISSERTATION

Submitted in partial fulfillment of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

In Computer Science

MICHIGAN TECHNOLOGICAL UNIVERSITY

2014

© 2014 Hui Meen Nyew

| This dissertation has been approved in partion of DOCTOR OF PHILOSOPHY in Compu | al fulfillment of the requirements for the Degree ster Science. |

|---------------------------------------------------------------------------------|-----------------------------------------------------------------|

|                                                                                 | Department of Computer Science                                  |

|                                                                                 |                                                                 |

| Dissertation Co-Advisor:                                                        | Dr. Nilufer Onder                                               |

| Dissertation Co-Advisor:                                                        | Dr. Soner Onder                                                 |

| Committee Member:                                                               | Dr. Zhenlin Wang                                                |

Committee Member: Dr. Ossama Abdelkhalik

Department Chair: Dr. Charles Wallace

To my parents, my family, friends, and teachers.

### **Contents**

| Li | st of 1 | Figures  |             |          |                |        |          |     |    |          |    |     |     |     |  |  |  | <br>V    |

|----|---------|----------|-------------|----------|----------------|--------|----------|-----|----|----------|----|-----|-----|-----|--|--|--|----------|

| Li | st of ' | Tables   |             |          |                |        | • •      |     |    |          |    |     |     |     |  |  |  | <br>vii  |

| Pr | eface   |          |             |          |                |        | • •      |     |    |          |    |     |     |     |  |  |  | <br>ix   |

| Al | ostrac  | et       |             |          |                |        | • •      |     |    |          |    |     |     |     |  |  |  | <br>X    |

| 1  | Intr    | oductio  | n           |          |                |        | • • •    |     |    |          |    | •   |     |     |  |  |  | <br>. 1  |

| 2  | Bac     |          | d and Rel   |          |                |        |          |     |    |          |    |     |     |     |  |  |  |          |

|    | 2.1     | Verific  | ation and   | Validati | ion            |        |          |     |    |          |    |     |     |     |  |  |  | <br>. 5  |

|    | 2.2     | Simula   | ation Verif | ication  | and \          | Valid  | datio    | on  |    |          |    |     |     |     |  |  |  | <br>. 7  |

|    | 2.3     | Runtin   | ne Verifica | ation .  |                |        |          |     |    |          |    |     |     |     |  |  |  | <br>. 8  |

|    | 2.4     | Invaria  | ınt Extract | ion      |                |        |          |     |    |          |    |     |     |     |  |  |  | <br>. 10 |

|    | 2.5     | Rule I   | nduction.   |          |                |        |          |     |    |          |    |     |     |     |  |  |  | <br>. 10 |

|    |         | 2.5.1    | Associat    | ion Rul  | es .           |        |          |     |    |          |    |     |     |     |  |  |  | <br>. 11 |

|    |         | 2.5.2    | Decision    | Rules    |                |        |          |     |    |          |    |     |     |     |  |  |  | <br>. 11 |

|    |         | 2.5.3    | Associat    | ion Rul  | e Me           | etrics | S        |     |    |          |    |     |     |     |  |  |  | <br>. 12 |

|    |         | 2.5.4    | Decision    | Rule M   | <b>1</b> etrio | cs .   |          |     |    |          |    |     |     |     |  |  |  | <br>. 13 |

|    |         | 2.5.5    | Rule Min    | ning Al  | gorit          | hms    |          |     |    |          |    |     |     |     |  |  |  | <br>. 14 |

|    | 2.6     | Reason   | ning with   | Tempor   | al Da          | ata    | • •      |     |    |          |    |     |     |     |  |  |  | <br>. 15 |

| 3  | App     | lication | Domain      | and Fr   | ame            | wor    | <b>k</b> |     |    |          |    |     |     |     |  |  |  | <br>17   |

| 4  | Firs    | t Order  | Logic Co    | onstrair | nt Sp          | ecif   | icat     | ion | (F | <b>O</b> | LC | SL) | 1 2 | 2 . |  |  |  | <br>21   |

|    | 4.1     | Trace    | Files and I | Events   |                |        |          |     |    |          |    |     |     |     |  |  |  | <br>. 22 |

|    | 4.2     | Instrur  | nentation   |          |                |        |          |     |    |          |    |     |     |     |  |  |  | <br>. 22 |

|    | 4.3     |          | OLSCL G     |          |                |        |          |     |    |          |    |     |     |     |  |  |  |          |

<sup>&</sup>lt;sup>1</sup>©2013 AAAI. Portions reprinted with permission, from **Hui Meen Nyew**, Nilufer Onder, Soner Onder and Zhenlin Wang, "A First-Order Logic Based Framework for Verifying Simulations", in Proceedings of the Twenty-Seventh AAAI Conference on Artificial Intelligence (AAAI 2013), Pre-PhD student Abstracts.

<sup>&</sup>lt;sup>2</sup>©2014 ACM. Portions reprinted with permission, from **Hui Meen Nyew**, Nilufer Onder, Soner Onder, and Zhenlin Wang, "Verifying Micro-architecture Simulators using Event Traces," in Proceedings of the 2014 International Conference on Supercomputing (ICS'14).

|    | 4.4    | Stream  | n Processing and Sliding Windows                  | . 25         |

|----|--------|---------|---------------------------------------------------|--------------|

|    |        | 4.4.1   | Sliding Window                                    |              |

|    |        | 4.4.2   | Constraint Checker                                | . 27         |

|    | 4.5    | Constr  | raint Specifications                              |              |

| 5  | Stat   | e Flow  | Temporal Analysis Graph (SFTAG) <sup>3</sup>      | . 31         |

|    | 5.1    |         | G graph                                           |              |

|    | 5.2    |         | ruction of SFTAGs                                 |              |

|    | 5.3    |         | Studies                                           |              |

|    | 0.0    | 5.3.1   | Pipeline Temporal Information                     |              |

|    |        | 5.3.2   | DRAM                                              |              |

|    |        | 5.3.3   | Bus Arbiter                                       |              |

|    | 5.4    |         | mance                                             |              |

|    |        |         |                                                   |              |

| 6  |        | •       |                                                   |              |

|    | 6.1    |         | ring                                              |              |

|    | 6.2    |         | luster Distance Measurement                       |              |

|    | 6.3    |         | Distance Measurement                              |              |

|    |        | 6.3.1   | Euclidean Distance Metric                         |              |

|    |        | 6.3.2   | Least Squares Distance Metric                     |              |

|    |        | 6.3.3   | Least Least Square Distance Metric                |              |

|    | 6.4    |         | ation                                             |              |

|    |        | 6.4.1   | 186.CRAFTY Dendrogram                             |              |

|    |        | 6.4.2   | Floating Point Division Instruction In 256.BZIP2  |              |

|    |        | 6.4.3   | Reorder Buffer Full Ratio                         |              |

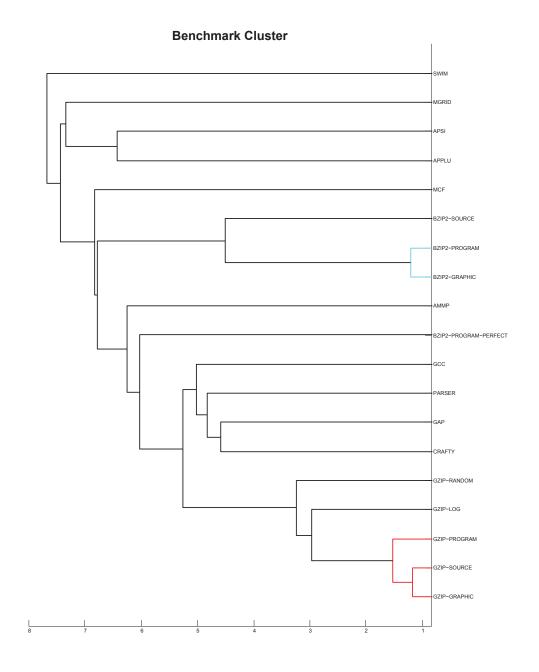

|    |        | 6.4.4   | Cluster of Clusters                               | . 62         |

| 7  | Con    | clusion |                                                   | . 69         |

|    | 7.1    | Contri  | butions                                           | . 70         |

|    | 7.2    | Future  | ework                                             | . 70         |

| Re | eferen | ices .  |                                                   | . <b>7</b> 1 |

| Aı | pend   | lix     |                                                   | . 79         |

| -1 |        |         | Copyright Permission from ACM for Chapter 4 and 5 |              |

|    |        |         | Copyright Permission from AAAI for Chapter 4      |              |

|    |        |         |                                                   |              |

<sup>&</sup>lt;sup>3</sup>©2014 ACM. Portions reprinted with permission, from **Hui Meen Nyew**, Nilufer Onder, Soner Onder, and Zhenlin Wang, "*Verifying Micro-architecture Simulators using Event Traces*," in Proceedings of the 2014 International Conference on Supercomputing (ICS'14).

# **List of Figures**

| 1.1  | Simulator verification using event traces                                                                                                                    | 3  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1  | Framework overview                                                                                                                                           | 20 |

| 4.1  | The FOLCSL grammar                                                                                                                                           | 25 |

| 4.2  | Sliding window                                                                                                                                               | 26 |

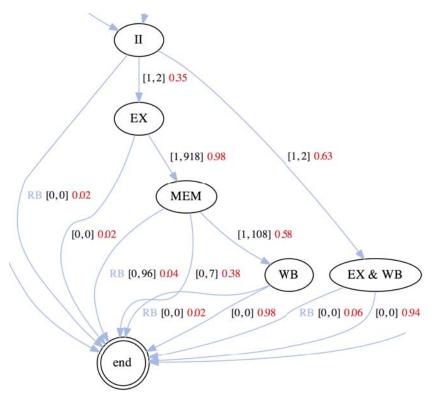

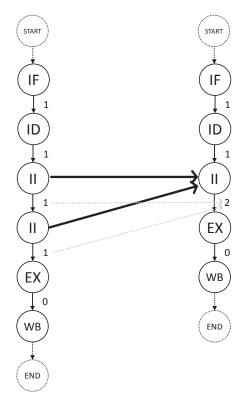

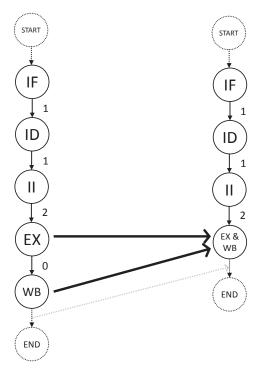

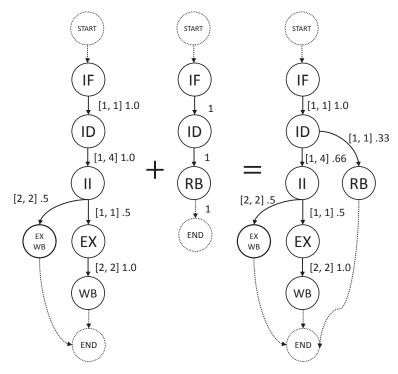

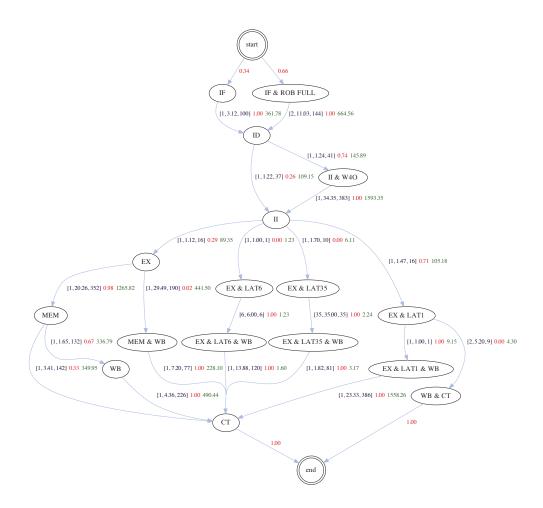

| 5.1  | Portion of FAST pipeline temporal representation. EX&WB has two outgoing edges ended at END. One edge is due to rollback and the other is normal termination | 32 |

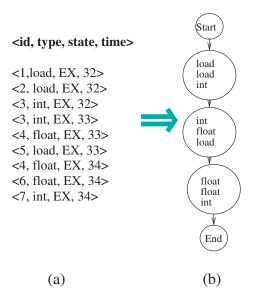

| 5.2  | Events emitted from the simulator are processed into windows                                                                                                 | 34 |

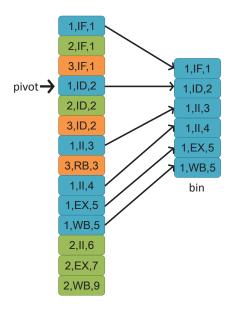

| 5.3  | Group events with specific sequence number into a bin                                                                                                        | 35 |

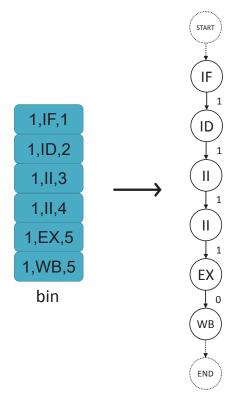

| 5.4  | Constructed bin represented as a graph                                                                                                                       | 36 |

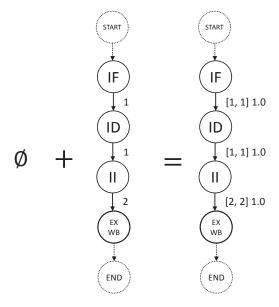

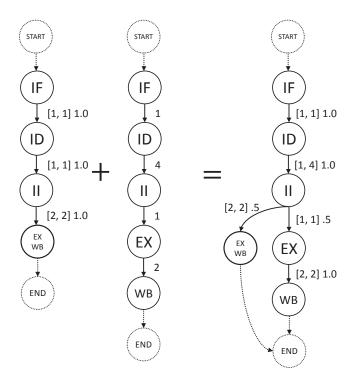

| 5.5  | Combining adjacent nodes with the same label                                                                                                                 | 37 |

| 5.6  | Combine parallel nodes                                                                                                                                       | 38 |

| 5.7  | Merge bin graph into the total graph $G$                                                                                                                     |    |

| 5.8  | Merge second bin graph into the current total graph $G$                                                                                                      | 4( |

| 5.9  | Merge third bin graph into the current total graph $G$                                                                                                       | 41 |

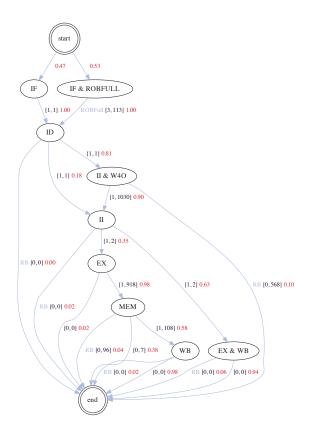

| 5.10 | FAST pipeline temporal representation                                                                                                                        | 42 |

| 5.11 |                                                                                                                                                              | 43 |

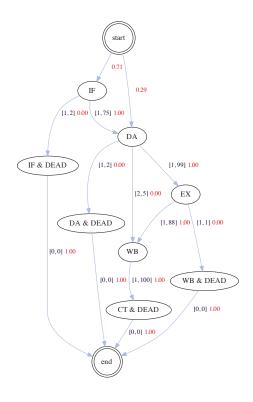

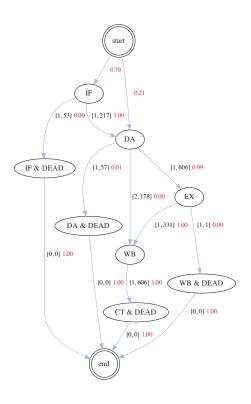

| 5.12 | SimpleScalar/Rambus pipeline temporal representation                                                                                                         | 44 |

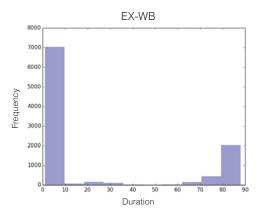

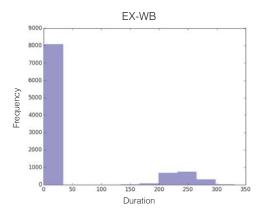

| 5.13 | SimpleScalar EX to WB distribution                                                                                                                           | 44 |

| 5.14 | SimpleScalar/Rambus EX to WB distribution                                                                                                                    | 45 |

| 5.15 | Finding the temporal information about the instructions leaving the EX stage.                                                                                | 45 |

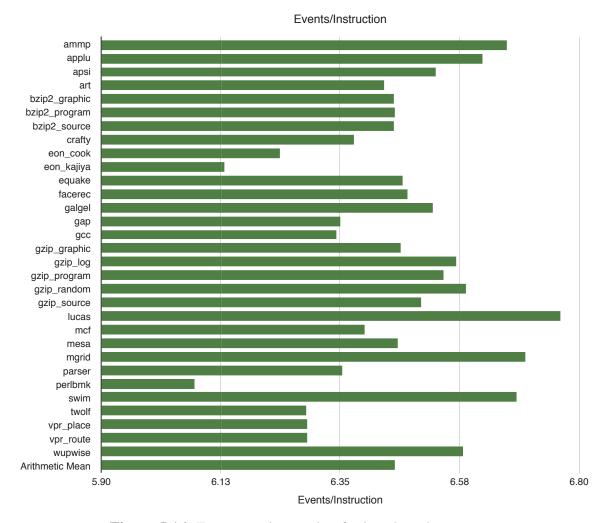

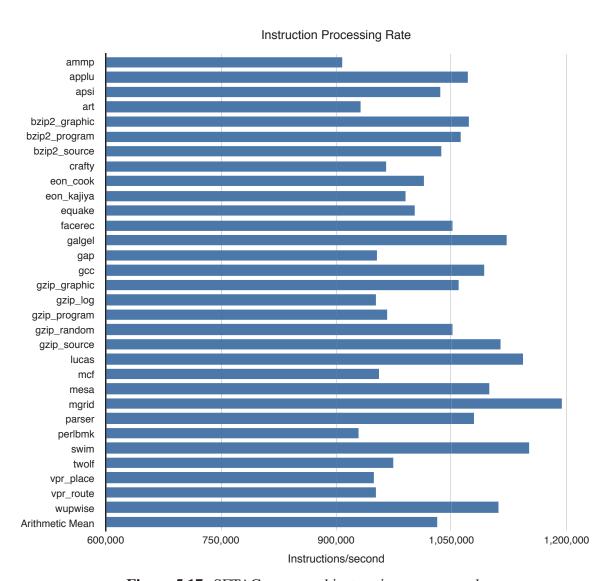

| 5.16 | Events per instruction for benchmark programs                                                                                                                | 48 |

| 5.17 | SFTAG processed instructions per second                                                                                                                      | 49 |

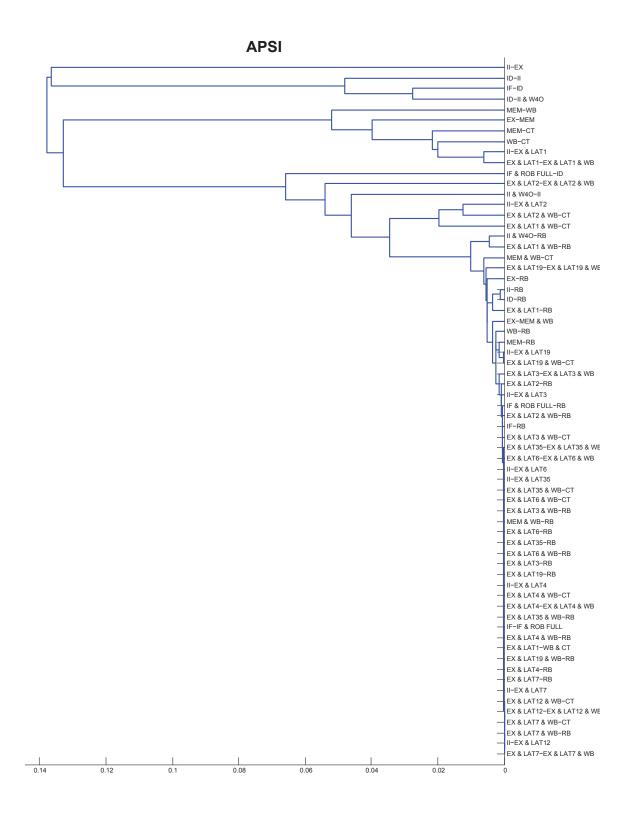

| 6.1  | APSI dendrogram computed using Euclidean distance                                                                                                            | 56 |

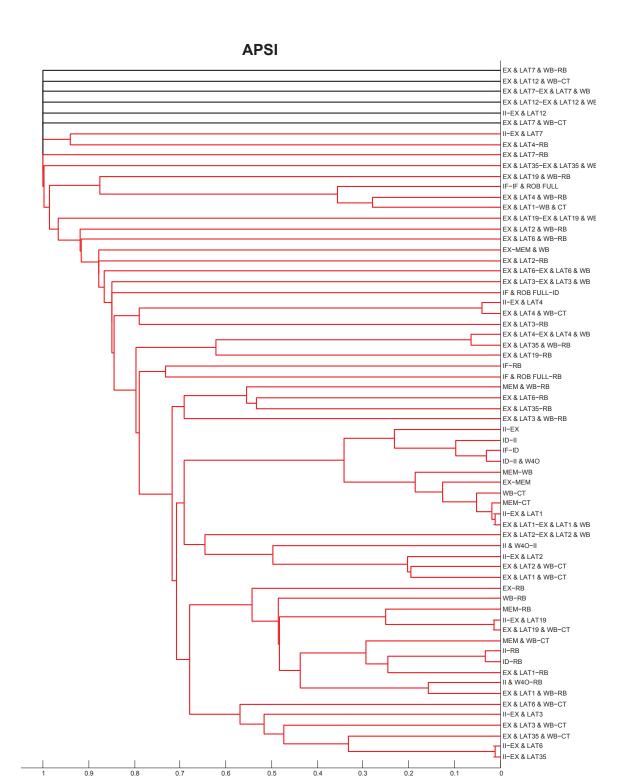

| 6.2  | APSI dendrogram computed using least squares distance                                                                                                        | 58 |

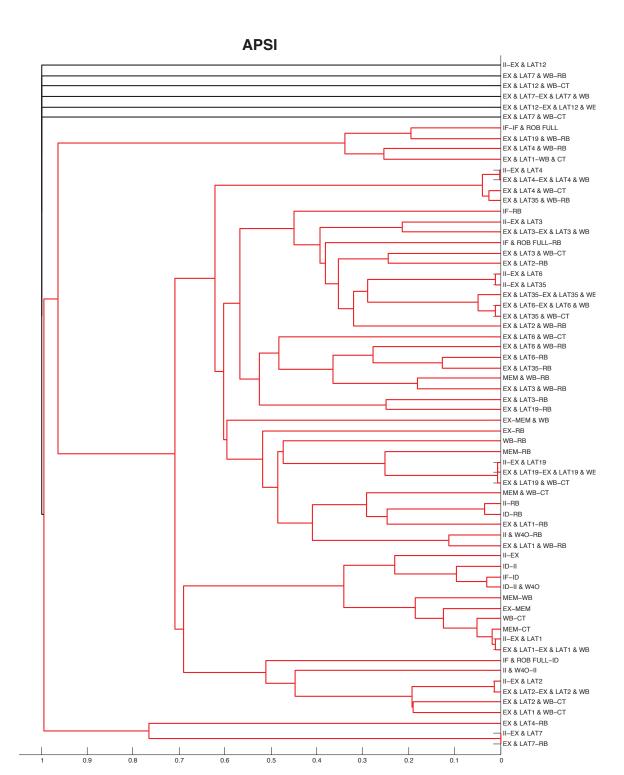

| 6.3  | APSI dendrogram computed using least least squares distance                                                                                                  |    |

| 6.4  | A Section of the 186.CRAFTY dendrogram                                                                                                                       | 6  |

| 6.5  | A section of the 186.CRAFTY SFTAG                                                                                                                            | 6  |

| 6.6  | Dendrogram of II-EX&LAT19                                                                                                                                    |    |

| 6.7  | Dendrogram of EX&LAT19&WB-CT                                                                                                                                 |    |

| 6.8  | Dendrogram of EX&LAT19&WB-RB                                                                                                                                 | 65 |

| 6.9  | SFTAG of 256.BZIP-PROGRAM executed with a perfect branch predictor. | 67 |

|------|---------------------------------------------------------------------|----|

| 6.10 | Benchmark cluster                                                   | 68 |

## **List of Tables**

| 5.1 | Type of instructions entering and leaving <i>EX</i> stage | 46 |

|-----|-----------------------------------------------------------|----|

| 6.1 | List of ratio values for START-IF&ROBFULL edges           | 66 |

### **Preface**

This dissertation contains my research work done during my PhD years at the Department of Computer Science at Michigan Technological University. The main contributions of this work are in twofold, namely, mining simulation data and verifying of simulation properties. Two previously published articles are included in Chapter 4 and Chapter 5.

Chapter 4 contains material previously published in AAAI conference in 2013. My contributions to this work were the design and implementation of the entire framework including the FOLSCL language, translator, sliding window algorithm, and event instrumentation. In addition, I designed and conducted the experiments. This work could not have been done without the help of my research committee members: Dr. Nilufer Onder (main advisor), Dr. Soner Onder (co-advisor), and Dr. Zhenlin Wang, who gave me continual guidance and help. They participated in the initial research idea, improved the language and its implementation, and pin-pointed the events needed for instrumentation. They gave me a clear idea about the experimental setup and participated fully in writing the article.

Chapter 5 contains portions of articles previously published in AAAI 2013 and ACM ICS 2014 conferences. My contributions to this work were to design and develop the verification framework and the SFTAG structure. In addition, I applied various data mining techniques to extract the properties of the simulation from the raw data stream and designed various distance measurements. I designed and conducted the experiments. The success of this work stems from the collaborative work of my research committee members Dr. Nilufer Onder, Dr. Soner Onder and Dr. Zhelin Wang, who provided enormous help. They brainstormed ideas, provided valuable insights in designing the SFTAG internal representation and the visualization. Furthermore, they suggested a lot interesting ideas such as clustering, measurement metrics, and a lot important simulation events for additional instrumentation. They spent a lot time writing and perfecting the article with me.

In both of the published articles, Dr. Nilufer Onder's expertise in artificial intelligence and suggestions to use temporal networks and reasoning has led to the development of SFTAG and the expansion of the initial work. Dr. Zhenlin Wang, a professor and researcher who is very knowledgeable in system area, helped me a lot in designing the FOLSCL language and implementing the translator. Dr. Wang's idea of using MinneSPEC instead of full inputs for the SPEC2000 benchmark led to significantly shorter experimental turnaround times. He also suggested various distance measurements which widened my knowledge in this area and led to the design of the "least least squares" distance metric and better clustering results. Dr. Soner Onder, an excellent and prominent researcher in computer architecture,

guided me in the instrumentation process. He spent a lot time helping me analyzing and understanding the data. He also kindly provided the computing resources (research cluster named *Istanbul*) needed for this work. The personal contributions described above are just some of the highlights. All of the work was done collectively and the contributions are gratefully acknowledged.

### **Abstract**

Computer simulation programs are essential tools for scientists and engineers to understand a particular system of interest. As expected, the complexity of the software increases with the depth of the model used. In addition to the exigent demands of software engineering, verification of simulation programs is especially challenging because the models represented are complex and ridden with unknowns that will be discovered by developers in an iterative process. To manage such complexity, advanced verification techniques for continually matching the intended model to the implemented model are necessary. Therefore, the main goal of this research work is to design a useful verification and validation framework that is able to identify model representation errors and is applicable to generic simulators.

The framework that was developed and implemented consists of two parts. The first part is First-Order Logic Constraint Specification Language (FOLCSL) that enables users to specify the invariants of a model under consideration. From the first-order logic specification, the FOLCSL translator automatically synthesizes a verification program that reads the event trace generated by a simulator and signals whether all invariants are respected. The second part consists of mining the temporal flow of events using a newly developed representation called State Flow Temporal Analysis Graph (SFTAG). While the first part seeks an assurance of implementation correctness by checking that the model invariants hold, the second part derives an extended model of the implementation and hence enables a deeper understanding of what was implemented. The main application studied in this work is the validation of the timing behavior of micro-architecture simulators. The study includes SFTAGs generated for a wide set of benchmark programs and their analysis using several artificial intelligence algorithms. This work improves the computer architecture research and verification processes as shown by the case studies and experiments that have been conducted.

## Chapter 1

### Introduction

"In this, the idea is that we interpret the input from our senses in terms of a model we make of the world. One can not ask whether the model represents reality, only whether it works. A model is a good model, if first, it interprets a wide range of observations in terms of a simple and elegant model. And second, if the model makes definite predictions that can be tested, and possibly falsified, by observation."

— Stephen Hawking, Origin of the Universe, Berkeley, March 13, 2007

Computer simulation programs are essential tools for scientists and engineers to understand a particular system of interest. As expected, the complexity of the software increases with the depth of the model used. In addition to the exigent demands of software engineering, verification of simulation programs is especially challenging because the models represented are complex and ridden with unknowns that will be discovered by developers in an iterative process. To manage such complexity, advanced verification techniques for continually matching the intended model to the implemented model are necessary. Therefore, the main goal of this research work is to design a useful verification and validation framework that is able to identify model representation errors and is applicable to generic simulators. To achieve this, we defined five pillars of our design philosophy.

- 1. *Formalism* The methodology is based on formal foundations.

- 2. *User friendliness* The verification system is easy to use. Simulation properties can be described in a clear and concise manner.

- 3. *Independence* The verification process is decoupled from the actual simulator. The modifications needed on existing simulators are minimal.

- 4. *Reuse value and flexibility* A property is defined once and used in subsequent verifications. Defined properties can easily be transferred to the variants of the model being studied.

- 5. *Scalability* It is possible to process very large amounts of data, and data streams with unknown length. The execution overhead of the verifier is minimal.

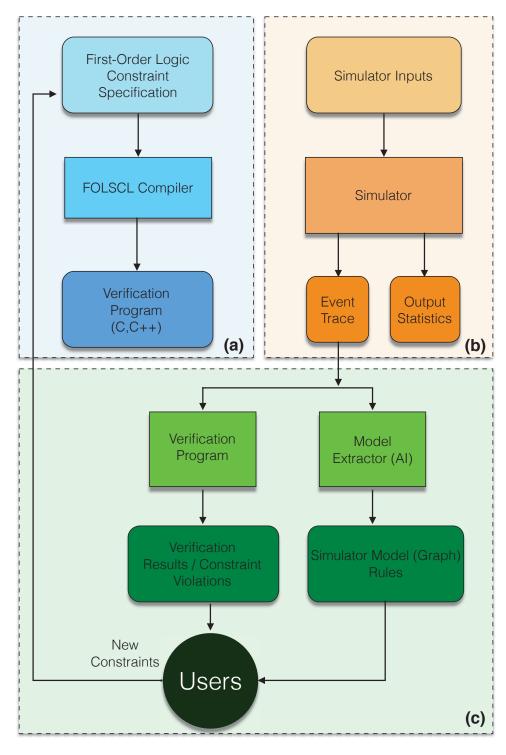

Our techniques rely on generating event traces from an execution of the target simulator and using the trace in two complementary processes. Figure 1.1 shows the general framework. For the first process, we developed a first-order logic based language, which we call, First-Order Logic Constraint Specification Language (FOLCSL). Using the language, invariants of the model under consideration are specified. Examples of such invariants in the computer architecture domain include, every fetched instruction must be decoded (instruction pipeline constraint), no more than two load instructions can simultaneously access the cache (resource constraint), and the execution step of an integer type instruction takes a single cycle (temporal constraint). From the first-order logic specification, we automatically synthesize a verification program as shown in Figure 1.1(a). This verification program reads the event trace generated by running the simulator using a particular input set as shown in Figures 1.1(b) and 1.1(c) and signals whether all invariants are respected. In this approach, if the constraint specification is complete and the verification program returns no errors, it can be stated that for the set of inputs tested, the simulator has faithfully followed the model. Unfortunately, the domain of invariants is large and even domain experts might omit necessary constraints to catch all the errors in the simulator. We therefore developed a second approach complementing the first.

In our second approach, we process the event trace using several artificial intelligence algorithms, and attempt to derive the simulated model from the event trace. To represent the simulated model we developed a representation, which we call *State Flow Temporal Analysis Graph (SFTAG)*. An SFTAG presents a temporal, probabilistic view of the states encountered during simulation. For example, in the computer micro-architecture domain, the first nodes of an SFTAG may specify that 47% of the instructions start at the "instruction fetch" stage, whereas 53% start at the "reorder buffer full" stage. Presenting the constraints in the form of temporal graphs enables the user to gain a deeper understanding of what the simulator actually implements. Using the derived model, further invariant constraints can be formulated and added to the initial set of constraints, in essence complementing the former process. These two processes are used iteratively with different inputs as shown in Figure 1.1, each time improving the set of constraints.

The strength of the outlined approach lies in its power to verify the implementation by both performing a check of the invariants and visually describing what the simulator implements. Furthermore, this is done in a very practical and general manner. Event traces can be easily

Figure 1.1: Simulator verification using event traces.

generated from any type of simulator by inserting output statements at specific points. Most existing simulators already provide mechanisms to generate an event trace. For example, SimpleScalar [1] and Gem5 [2] simulators used by computer architects produce event traces by simply setting an option. It also is easy to generate an event trace in automatically synthesized simulators such as FAST ADL [3] by augmenting appropriate points in the description.

Our experiments and case studies show that such traces contain sufficient information to verify that the simulator faithfully implements its execution model when these traces are processed with the appropriate algorithms. Although the data sets are very large and these algorithms have bad asymptotic complexity, by applying advanced filtering and windowing techniques, we are able to keep the running times within reasonable limits.

The main contributions of this research work are twofold. First, we designed a formal verification language and implemented the software that allows users to describe simulation properties and check the properties against the output events. Second, we developed and implemented an algorithm that is capable of processing large data sets and representing the temporal information in a graphical form that is amenable to both visual inspection and automatic analysis. Our framework improves the computer architecture research and verification processes as shown by the case studies and experiments we have conducted.

The organization of this dissertation is as follows. In Chapter 2, previous work related to this research is discussed. Techniques and algorithms that this research is built upon are reviewed in the same chapter. Chapter 3 gives an overview of the framework. The constraint language, First-Order Logic Constraint Specification Language (FOLCSL), is presented in Chapter 4. In Chapter 5 we describe State Flow Temporal Analysis Graphs (SFTAGs) and the algorithms to construct them. We illustrate the application of SFTAGs through case studies and experiments in Chapter 6. The summary of our research, conclusion and future work are given in Chapter 7.

## Chapter 2

## **Background and Related Work**

The main topics in this section include verification, validation, and rule induction. We provide a brief review of verification and validation in a general project management context, within software engineering, and in the context of simulation software. We present a summary of rule induction techniques along with metrics of rule quality.

### 2.1 Verification and Validation

Verification and validation are the foundations of software testing. Without referring to the exact definitions, some of us might think they mean the same thing. But they do not. The definition of these words depend on the context.

The Project Management Body of Knowledge (PMBOK) Guide [4] definitions cover a wide scope providing the following definitions:

*Verification* - The evaluation of whether or not a product, service, or system complies with a regulation, requirement, specification, or imposed condition. It is often an internal process.

*Validation* - The assurance that a product, service, or system meets the needs of the customer and other identified stakeholders. It often involves acceptance and suitability with external customers.

One of the earliest definitions of software verification and validation comes from Barry Boehm [5] who defined both terms as follows:

*Verification* - to establish the truth of the correspondence between a software product and its specification (derived from Latin word *veritas*).

*Validation* - to establish the fitness or worth of a software product for its operational mission (derived from Latin word *valere*).

In layman's terms, verification can be expressed as "Am I building the software right?" and validation can be expressed as "Am I building the right software?" [5]. The distinction between these two terms is important because it defines the focus, scope, and the life-cycle for each process.

On the other hand, Sargent's [6] definitions are more specific toward simulation software. His definitions are as follows:

*Model verification* - ensuring computer program of the computerized model and its implementation are correct.

*Model validation* - substantiation that a computerized model within its domain of applicability possesses a satisfactory range of accuracy consistent with the intended application of the model.

We adopt Sargent's definitions because of their specificality and relevance to our work.

Other closely related concepts are *model credibility* and *model accreditation* [6]. Model credibility is concerned with developing the users' confidence and trust they require in order to use a model and in the information derived from that model. Model accreditation determines if a model satisfies specified model accreditation criteria according to a

specified process. The definition of the term model accreditation also debatable. Balci [7] mentioned that the definition given by the Department of Defense differs from the ISO definition. By Department of defense standard, accreditation is the certification that a model or simulation is acceptable for a specific purpose. On the other hand, ISO defines accreditation as the formal recognition of a body or person that is competent to carry out specific tasks and certification as third party written assurance that a product, process or service conforms to specific characteristics. Balci used the ISO definitions because they are more widely used in engineering disciplines and educational sectors. According to the ISO standard, first party refers to the application sponsor, second party refers to the application developer and the third party is the independent certification agent.

In computer architecture research, the term *validation* is used in a manner that is close to Sargent's definition. To validate a model, the *accuracy* of the implemented model is compared with an actual implementation of a specific processor. For example, the SimpleScalar Sim-alpha implementation, which faithfully implements the specific structure of the Alpha 21264 processor, has been validated by comparing the estimated cycle counts produced by the simulator with the cycle counts obtained by running the same benchmark program on the physical machine [8, 9]. The results indicated that the simulated cycles are within 2% of the actual implementation [10].

#### 2.2 Simulation Verification and Validation

A specific category of verification is the verification of simulations. Recently, the accuracy of simulation models have attracted interest, especially in scientifically and politically sensitive areas such as global climate models [11, 12] and medical decision making [13]. Due to the large amount of simulation data that needs to be interpreted and verified by domain experts, a range of visualization techniques have been developed.

Chen et al. describe visualization as a search process where the users start with a set of data and visualization tools, and search for the best parameters and configurations to visualize the set of data [14]. Using the same concept of search, Ahrens et al. developed an iterative verification method that is used for comparing simulations that run different algorithms [15]. The method involves four steps, namely, identifying the features to compare, making an hypothesis about the identified feature, visualizing the identified features, and finally creating quantitative plots or charts that reveal the differences between the simulations. The process is repeated until the simulators used are verified. Han et al. developed a three step methodology visualizing the assembly line of modular buildings. In the first step, the proposed production line is developed using *Value Stream Mapping*. In the second step, the simulation of the proposed design is built for verification. Finally, 3D visualizations

are automatically developed for validation based on the outputs of lean production and simulation.

Sargent proposed another simulation verification and validation process where a simulation model is separated into a conceptual model and a computerized model [6]. The conceptual model is developed first and is followed by conceptual model validation. This process is repeated until the model is satisfactory. Next, the conceptual model is turned into a computerized model and is followed by computerized model verification. Similarly, the process is repeated until the model is satisfactory. This verification process was adopted by Huang et. al.'s agent based simulation where the conceptual model was evaluated by six domain experts and the computerized model verification was done by code walkthrough, trace analysis, input/output testing, and boundary testing [16].

Verification can also be done by analyzing the simulation output using statistical techniques (e.g., simulations in computational fluid dynamics [17], agent-based modeling [18]). Sanchez described the important issues that researchers should be aware of while analyzing simulation outputs [19]. One of the issues is the *initialization bias* which means that the outputs that include the warm-up period may cause the overestimation or underestimation of the steady state performance. The initialization bias is also one of the well researched problems in computer architecture domain. SimPoint [20] and SMARTS [21] reduce the initialization bias by warming up the simulator before collecting the simulation data.

Kleijnen discussed the suitability of specific statistical tests based on the availability of data [22, 23]. He identified three situations, (i) no real data is available, (ii) real data and simulated data are available but input data is not available, and (iii) both input and output data are available. For the first case he suggested using sensitivity analysis, for the second case, student *t*-test is appropriate, and regression test or bootstrapping can be applied for the last case.

### 2.3 Runtime Verification

Runtime verification is a process that verifies a program's dynamic execution behavior against formally specified behavioral properties [24] and has its roots in model checking [25]. Leucker and Schallhart define runtime verification as "the discipline of computer science that deals with the study, development, and application of those verification techniques that allow checking whether a run of a system under scrutiny satisfies or violates a given correctness property" [26].

Broadly speaking, runtime verification involves four major research areas [27]:

- 1. logics for monitoring

- 2. online checking algorithms

- 3. extraction of observations necessary for checking

- 4. reduction of checking overhead

The logics used for monitoring provide a means to specify the behavioral properties of a running program and are mainly based on linear temporal logic (LTL) [28]. LTL allows reasoning about states using four operators, namely, next (property holds in the next state), final (property will hold at a state in the future), global (property holds at every state on the path), until (property hold until finally another property holds), and release (a second property holds along the path up to and including the first state where the first property holds). Recently published LTLs include AspectJ, which provides a runtime verification framework for Java programs [29], and EAGLE, which provides support for recursive parameterized equations [24]. Comparison of LTLs with different levels of expressivity is provided by Bauer, Leucker and Schallhart [26, 30].

The monitoring algorithms for runtime verification are built on model checking algorithms, which are updated to work online and incrementally [27, 31]. Generation of traces, also commonly known as *instrumentation*, deals with the question "How are observations made and recorded?". Inefficient implementation of runtime verification can degrade a system's performance significantly. Major sources of overhead reside in observation extraction and checking algorithms. This issue falls into overhead management [27, 32, 33]. Last but not least, feedback and runtime enforcement addresses the question of what to do when a violation is discovered.

Recent work related to checking and monitoring is the Temporal Rover [34]. It uses temporal logic to describe assertions. The assertion statements are written as source code comments (C, C++, Verilog, VHDL) which are then embedded into the original source code via the provided parser. In the mechatronics field, runtime verification is utilized on a self-optimizing system. Zhao et al. [35] developed a service on top the real time operating system (RTOS) to dynamically monitor and check the consistency and safety of a system after performing component replacements. The authors first model the system using real-time UML state charts. Following this, a series of translations are applied to process the model into *Kripke* structure and *Büchi* automata which will be fetched during the verification process. Further applications of runtime verification are in multi-agent simulations of natural domains such as biological, cognitive and social domains. Bosse and

colleagues show that the widely used differential equations in multi-agent system modeling are inadequate [36]. They address it by designing logic based Temporal Trace Language (TTL) to check and analyze multi-agent systems dynamically. Runtime verification can also be used to ensure C memory safety. Rosu et al. proved that strong termination and strong memory safety are undecidable in general, but strong memory safety of strong terminating programs is decidable, thus it is runtime verifiable [37].

### 2.4 Invariant Extraction

Verification can also be done by observing a simulator's invariant properties such as every instruction must terminate at some point. If an observed invariant property doesn't make sense, it might indicate that the simulator has some flaws. For example, an invariant of a processor simulator stating that there exists an instruction that stays in the pipeline for a million cycles raises a red flag because it is unlikely to happen in a real implementation.

Some work related to this area has been published in recent years. One example is IODINE [38] that automatically extracts low-level dynamic invariants such as state machine protocols, request-acknowledge pairs, and mutual exclusion. Another example is GoldMine [39]. It performs static analysis on a register-transfer level (RTL) design and constructs a decision tree using a supervised learning algorithm on a simulation trace. The decision tree represents the assertions of the design. Another recent work by Mandouh and Wassal [40] utilizes frequent and sequential patterns mining and known templates to extract RTL design properties.

Extracting invariant properties can be done in variety of ways. Data mining techniques are very efficient for this purpose. For example GoldMine utilize decision tree algorithms and Mandouh and Wassal use frequent and sequential pattern mining algorithms to automatically generate hardware design properties. In the next section, we describe some data mining techniques we used in our work.

### 2.5 Rule Induction

Rule induction techniques are effective in extracting properties of a simulation that follows certain patterns. We used rule induction to extract bus arbiter properties which are best described in the form of *if* and *then* rules (Section 5.3.3). Two widely used rule formats are association rules and decision rules. We begin by describing the basic concepts and follow

by listing some of the mining algorithms.

#### 2.5.1 Association Rules

The concept of association rules is formally defined in Rakesh Agrawal et. al.'s 1993 paper [41] where they use it to study a large database of customer transactions in a supermarket environment. The following definition is based on Agrawal et al. Let  $\mathscr{I} = I_1, \dots, I_m$  be a set of binary attributes with size m, called *items*. Let T be a database of transactions. Each transaction  $t \in T$  is represented as a binary vector, with t[k] = 1 if t contains item  $I_k$  and t[k] = 0 otherwise. Let X be a subset of  $\mathscr{I}$ . A transaction t satisfies X if for all items  $I_k$  in X, t[k] = 1.

An association rule is an implication of the form  $X \Longrightarrow I_j$ , where  $X \neq \emptyset$ ,  $X \subset \mathcal{I}$ ,  $I_j \in \mathcal{I}$  and  $X \cap I_j = \emptyset$ . The rule  $X \Longrightarrow I_j$  is satisfied in T with the confidence factor c where  $0 \le c \le 1$  if and only if at least c% transactions in T that satisfy X also satisfy  $I_j$ . In some text [42] the  $I_j$  is replaced with a set Y, i.e.,  $X \Longrightarrow Y$ , where  $X \neq \emptyset$ ,  $Y \neq \emptyset$   $X, Y \subset \mathcal{I}$ , and  $X \cap Y = \emptyset$ .

#### 2.5.2 Decision Rules

Besides association rules, there is another class of rules called *decision rules*. If we regard a decision tree as graphical representation then its text equivalent representation is a set of decision rules. Decision rules are also known as classification rules [43]. A rule can be written in disjunctive form (Horn clause) or in implication form. In disjunctive form it follows Horn form which is a clause with at most one positive literal (unnegated literal).

Disjunction form:

$$\neg p \lor \neg q \lor \dots \lor \neg t \lor u \tag{2.1}$$

If a rule is in Horn form, it can easily be rearranged into an equivalent implication form.

$$p \wedge q \wedge \dots \wedge t \Longrightarrow u$$

(2.2)

Nevertheless, the implication form is more commonly used. Sometimes it is written in the

form of an if-then statement.

if

$$p$$

and  $q$  and  $\cdots$  and  $t$  then  $u$  (2.3)

The *if* part (left side) of a rule is known as the rule *antecedent* or *precondition*. The *then* part (right side) of a rule is known as the rule *consequent* and it contains a class prediction. If the condition in a rule antecedent holds true for a given tuple, we say that the rule *covers* the tuple.

Several rule metrics has been developed to measure the quality of the rules. These metrics are used in filtering, pruning and the measurement of confidence during or after the rule extraction process. In the next two sections, we describe some of the well known rule measurement metrics.

#### 2.5.3 Association Rule Metrics

The *support* of a rule  $X \Longrightarrow Y$  that holds in a set of transactions T is defined as:

$$supp(X \Longrightarrow Y) = P(X \cup Y) \tag{2.4}$$

The notation  $P(X \cup Y)$  indicates the probability that a transaction contains the union of sets A and B. This should not be confused with P(X or Y).

The *confidence* of a rule  $X \Longrightarrow Y$  that holds in a set of transactions T is defined as:

$$conf(X \Longrightarrow Y) = P(Y|X)$$

$$= \frac{supp(X \cup Y)}{supp(X)}$$

$$= \frac{freq(X \cup Y)}{freq(X)}$$

(2.5)

where freq(A) is number of transactions that contain the itemset A. A set of items is known as *itemset*.

*Lift* is a correlation measure of two itemsets. The lift between itemset *X* and itemset *Y* can be measured as follows:

$$lift(X,Y) = \frac{P(X \cup Y)}{P(X)P(Y)}$$

(2.6)

If the lift value less than 1, it means the occurrence of *X* is *negatively correlated* with the occurrence of *Y*. If the lift value is greater than 1, it means the occurrence of *X* is *positively correlated* with the occurrence of *Y*. If the lift value is zero, it means *X* and *Y* are independent and there is no correlation between them.

Support and confidence are usually used to measure rule interestingness. For example one might be interested on rules with 100% confidence. Lift, on the other hand, serves as an extra measurement metric, that is rule correlation measurement.

### 2.5.4 Decision Rule Metrics

The *coverage* of a rule is the ratio between the number of records covered by a rule and the number of records in a data set.

$$coverage(R) = \frac{n_{covers}}{|D|} \tag{2.7}$$

where *R* is a rule,  $n_{covers}$  is the number of records covered by *R* and |D| is number of records in *D*.

The accuracy of a rule is percentage of the rule can correctly classify, defined as:

$$accuracy(R) = \frac{n_{correct}}{n_{covers}} \tag{2.8}$$

where  $n_{correct}$  is number of records that are correctly classified by R.

### 2.5.5 Rule Mining Algorithms

Decision rules can be extracted by first constructing a decision tree using algorithms such as Quinlan's ID3 [44], ID3's successor [45], and CART by Breiman et al. [46]. Then, the paths from the root node to each leaf node in the tree are traced to form the rules. Alternatively, we can use sequential covering algorithms to learn the rules directly from a data set. Widely used sequential covering algorithms include AQ [47] and CN2 [48]. The general strategy is shown in algorithm 1:

#### Algorithm 1 Sequential Covering Algorithm

```

Input:

D data set.

C set of class values

V set of all attributes and their possible values

Output:

R set of rules

1: R \leftarrow \emptyset

2: for all c \in C do

repeat

3:

4:

r \leftarrow learn1Rule(D, V, c)

remove records covered by r from D

5:

R = R \cup r

6:

7:

until termination condition(s)

8: end for

9: return R

```

Algorithm 1 works by generating a rule that correctly classifies some instances in D that belong to a class c, removing the instances that are covered by the generated rule, and repeating the process for the remaining instances. The termination condition usually is "when all the instances in D that belong to class c are correctly classified."

The construction of rule r in algorithm 1 can be done in many different ways. One method is shown in algorithm 2. Since the consequent is fixed to a class c, only the antecedent needs to be constructed. The process starts with an empty antecedent and on each iteration it adds the most promising attribute-value pair (i.e.  $a^* = v^*$ ) to the rule's antecedent. The process repeats until the rule r correctly classifies all the class c instances in D.

#### Algorithm 2 learn1Rule

```

Input:

D data set

V set of all attributes and their possible values

c a class value

Output:

r a rule

1: \alpha \leftarrow \emptyset (antecedent)

2: repeat

for all attribute-value pair, (a = v) \in V do

3:

r' \leftarrow if \ \alpha \wedge (a = v) \ then \ c

4:

5:

computeAccuracy(r')

end for

6:

7:

let (a^* = v^*) be the attribute-value pair of the maximum accuracy over D

\alpha \leftarrow \alpha \land (a^* = v^*)

V = V - \{a^*\}

9:

r \leftarrow if \ \alpha \ then \ c

11: until r correctly classifies all c instances of D

12: return r

```

In the next section, we describe artificial intelligence techniques for representing, reasoning with, and mining temporal information.

### 2.6 Reasoning with Temporal Data

Temporal reasoning is an important field of artificial intelligence as evidenced by continual developments and growing number of applications [49]. Temporal reasoning operates on a formal representation of time and provides a means to reason about temporal aspects of knowledge [50, 51]. There are two main ways of representing temporal information. *Qualitative models* represent relations between events such as "A occurs during B" or "A is before B" [52, 53]. *Quantitative models* represent numeric information using points of time [54] or using intervals of time [55]. The reasoning problems solved using temporal representations can be broadly classified into three as follows:

1. *Consistency checking*: Finding whether a collection containing temporal data is free of contradictions.

- 2. Inference: Answering queries based on temporal data.

- 3. *Optimization*: Minimizing temporal networks or finding a minimal set of temporal constraints.

Simple temporal networks (STNs) introduced by Dechter, Meiri, and Pearl [55] are widely used as a representation of quantitative intervals. STNs have been extended in a range of directions, including disjunctive temporal networks [56, 57, 58], temporal networks with alternatives [59], preferences and uncertainty [60, 61, 62, 63], fuzzy preferences [64], and time dependent temporal constraints [65].

Temporal data mining is the application of artificial intelligence and statistical techniques to extract information from static or longitudinal temporal data [66]. Widely studied domains of temporal data mining include finding temporal association rules [67], discovery of frequent sequences [68, 69, 70], and describing and discovering common trends in time series [71, 72, 73, 74]. Examples of recent work in these areas are finding calendar-based [75] or relative [76] temporal association rules, finding frequent sequences in longitudinal electronic patient records [77] or spatiotemporal human activity data [78], and finding patterns of temporal variation in online media [79]. Higher order mining refers to mining results of temporal discovery for further discoveries such as finding trends or changes in association rules [80, 81].

In our work, we generate temporal flow information in the form of probabilistic state flow graphs called SFTAGs as explained in Chapter 5. We analyze SFTAGs by clustering with respect to edges and benchmark programs. We also process these graphs for higher order relationships by clustering the clusters as discussed in Chapter 6. In the next chapter, we present an overview of our framework's design and its application domain.

## Chapter 3

## **Application Domain and Framework**

"If it is not useful or necessary, free yourself from imagining that you need to make it. If it is useful and necessary, free yourself from imagining that you need to enhance it by adding what is not an integral part of its usefulness or necessity. And finally: If it is both useful and necessary and you can recognize and eliminate what is not essential, then go ahead and make it as beautifully as you can."

— Paul Rochleau & June Sprigg, Shaker Built: The Form and Function of Shaker Architecture

While the techniques developed in this dissertation can be applied to any simulator, the main emphasis of our work is the validation of the timing behavior of micro-architecture simulators. Like many other fields, state of the art computer architecture research inherently relies on software simulations to develop new ideas and to improve existing well-established designs. We can broadly classify these simulators into three main groups:

1. Functional Simulators: Functional simulators implement an interpreter for the simulated architecture's instruction set. No hardware details are modeled. By using a functional simulator, researchers can start developing the system software for a new architecture before the architecture is built, as the functional simulators enable simulated execution of the programs compiled for the new architecture. Since they do not model any of the specifics of the architecture, they are mainly used to develop and debug system software. They are also useful for collecting statistics such as the number and the type of instructions executed by a benchmark program, or generate instruction and data address traces which can be used to study the hit/miss behavior of caches and the memory subsystem.

2. Cycle-Accurate Simulators: Cycle-accurate simulators model a processor architecture in sufficient detail so that accurate information about how a given program would execute under a new design can be quantitatively estimated. The simulator typically simulates the behavior of individual hardware structures within a processor, such as registers, register files, pipeline stages, buffers, arbiters as well as the details of the datapath, including on-processor busses. While it is impossible to predict the attainable clock-speed for the processor (i.e., the cycle time), the number of cycles it would take to execute the given program is accurate and will match the actual processor when it is built, if the simulator has been correctly implemented.

Cycle-accurate simulators are rather complex pieces of software as their implementation typically takes tens of thousands of lines of high-level program code, such as C. Cycle-accurate simulators also serve a crucial role in actual processor development and their use is essential to finalize the micro-architecture design. Currently, hand-coded cycle-accurate simulators such as SimpleScalar [82, 1], RSIM [83], M5 [84], GEM5 [2] as well as those generated from domain-specific architecture description languages are used widely both by the industry and academia. Examples of architecture description languages include Mimola, nML, Lisa, Expression, ASIP Meister, TIE, Madl, ADL++, GNR, among others [85].

3. Full System Simulators: Typically, whether it is a functional or cycle accurate simulator, operating system calls are intercepted and executed on behalf of the simulated program. Components of a computer system other than the CPU, such as various I/O devices, are not modeled. Alternatively, the simulator may also implement the behavior of these components, allowing the simulation of a complete computer system. In such a case, it is possible to "boot" an operating system within the simulator framework. Such a framework then becomes usable for developing the device drivers and studying the behavior of the operating system as well. Such simulators are called *full-system simulators*. Due to significant processing overhead, the CPU is modeled only at the functional level and not at the cycle-accurate level. Since the boundary between functional and cycle-accurate simulation is not rigid, it is also possible to simulate certain components at the cycle-level and the rest in a functional manner.

Full-system simulators are also useful to create "boot and run" environment for machines that no longer exist, allowing us to preserve the history of computing.

This dissertation specifically targets cycle-accurate simulators. Having a formal verification framework is important in this context due to two reasons. First, while generation from an architecture description language can facilitate the application of formal validation techniques for cycle-accurate simulators, using an architecture description language in itself will not prevent model representation errors. Second, hand-coded simulators are still widely used as companies rely on their developed code base to improve

the future versions of existing processors. As a result, verification of cycle-accurate simulators is still a difficult task and remains an area dominated by ad-hoc techniques, except for simpler embedded processors where a formal specification language can be used to describe the architectural details.

In order to facilitate a better understanding the issue of timing and how our framework fits into the cycle-accurate simulation domain, we briefly review the general structure of cycle-accurate simulators. Mauer et al. [86] give a taxonomy of simulators and classify them into Integrated, Functional-First, Timing-Directed and Timing-First. In this work, we used ADL [3] generated simulators used in this study are all *integrated* simulators whereas SimpleScalar [1] simulators can be considered Functional-First. Irrespective of this classification, almost all cycle-accurate simulators embody a main loop of simulation such that each iteration of the loop corresponds to one clock cycle of the architecture. Within each iteration, procedures (or methods) which implement the functionality of individual hardware components are called. For example, a cycle-accurate simulator which implements a two pipeline stage micro-architecture of instruction fetch and execute will first calls the instruction fetch and then the execute procedures. Since the modeling is performed at a register level, (i.e., the changes in the values of processor registers are accurately reflected in the corresponding program variables) calling of the instruction fetch might result in loading the instruction word into the simulated instruction register. The execute procedure then can perform the desired operation, and the loop is iterated again. Typically, machine registers, buffers, etc. become variables in the simulator, including the memory which can be represented as an array.

It is important to observe that in this modeling approach, the simulator generates a series of *events* which result from the execution of procedures that model the behavior of various hardware components. While a functional-first simulator would act like a functional simulator in terms of actual interpretation of instructions, to qualify as a cycle-accurate simulator, it has to model and find the actual clock cycle a particular events happens, such as the execution or writing back the result of an instruction. Therefore, cycle-accurate simulators can easily be annotated to print out a trace file which contains the events that take place and the clock cycle at which each event happens. We explain the structure of the trace file in Section 4.1.

In addition to performing simulator verification, our framework can be used as a debugging tool while developing a simulator. We present our working framework through a use-case scenario example. Alma, a micro-architecture researcher developed a novel processor prototype in an existing simulator. She wants to make sure that the modified simulator does not break the unmodified portion of the simulator and the modified portion of the simulator correctly represents her conceptual model.

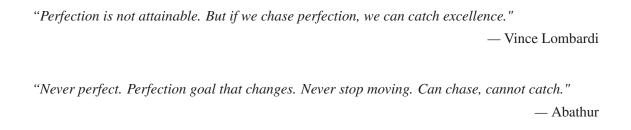

**Figure 3.1:** Framework overview.

Using our framework, all Alma needs is to instrument the events that she is interested in and write the constraint specifications in FOLCSL based on her conceptual model. The written set of constraint specifications are translated to C/C++ code via FOLCSL's translator and then compiled into an executable verifier. The right section of Figure 3.1 depicts the process. To check whether the simulator adheres to the constraint specifications, Alma runs the verifier in parallel with the simulator. The events output from the simulator are streamed into the verifier and the verifier checks the events against the constraint specifications. The verifier signals Alma if it finds any violations. In addition, Alma can utilize the output events from the simulator to generate SFTAG graphs. Instead of running the verifier, Alma runs the SFTAG processor which takes the events generated by the simulator and processes them into SFTAG graphs. The SFTAG graphs show the temporal relationship of the events. Furthermore, if Alma can produce the SFTAG graphs of the original simulator and compare them with the current graphs, she can learn the changes between the graphs and reason about the modifications she made. Alma can further study the SFTAG graphs as a whole using data mining techniques such as clustering to reveal difficult to see patterns. The left section of Figure 3.1 depicts this process.

In the next two chapters, we explain the components of our framework in detail. In Chapter 4, we present the structure of the trace files and events, the first-order logic constraint specification language (FOLCSL) we developed, and the verification algorithms that use FOLCSL constraints. In Chapter 5, we present the SFTAG structure, the algorithms to generate SFTAGs, and the case studies we conducted.

## Chapter 4

## First Order Logic Constraint Specification (FOLCSL) 1 2

First-order logic constraint specification language (FOLCSL) is designed to specify the invariants which must hold during the execution of the simulator. The language allows constraint specification using a subset of first-order logic. The constraints are specified by referencing a particular event and associating it with other events. Expressions refer to the names used in a given trace, therefore, we first formally describe the expected form of trace data and then follow with the instrumentation methods.

<sup>&</sup>lt;sup>1</sup>©2013 AAAI. Portions reprinted with permission, from **Hui Meen Nyew**, Nilufer Onder, Soner Onder and Zhenlin Wang, "A First-Order Logic Based Framework for Verifying Simulations", in Proceedings of the Twenty-Seventh AAAI Conference on Artificial Intelligence (AAAI 2013), Pre-PhD student Abstracts.

<sup>&</sup>lt;sup>2</sup>©2014 ACM. Portions reprinted with permission, from **Hui Meen Nyew**, Nilufer Onder, Soner Onder, and Zhenlin Wang, "Verifying Micro-architecture Simulators using Event Traces," in Proceedings of the 2014 International Conference on Supercomputing (ICS'14).

#### **4.1** Trace Files and Events

A trace T is a sequence of events  $T = \xi^1 \cdots \xi^l$ , represented as n-tuples:  $\xi^i = \langle e_1^i, \cdots, e_n^i \rangle$  where,  $e_j^i$  refers to the  $j^{th}$  attribute of the  $i^{th}$  event. Each  $e_j^i$  is an integer. For example,  $\xi^i = \langle a^i, s^i, t^i \rangle$  is an event generated by a processor simulator where  $a^i$  is the instruction sequence number,  $s^i$  is the pipeline stage or special events such as reorder buffer full, and  $t^i$  is the cycle time at which the  $i^{th}$  event has been observed. It can be read as follows: At time  $t^i$ , the  $a^i$ -th instruction is at state  $s^i$ . A sample trace generated by the simulator is:

- 1. 114, IF, 1008

- 2. 114, ROB Full, 1008

- 3. 109, EX, 1008

The first line of the trace states that instruction 114 is at instruction fetch stage (*IF*) and at machine cycle 1008. At the same time reorder buffer full (*ROB Full*) event occurs for the same instruction (second line of the trace). The last line of the trace indicates that instruction 109 is at execution stage (*EX*) at machine cycle 1008. FOLCSL does not require the declaration of text attributes such as *ID*, *ROB Full* or *EX* above. Text attributes have no domain specific meaning attached to them by the language and they are treated just like any other constant.

We consider every type of activity within the simulator to be an *event*, and broadly classify events into two main groups, namely, those events which affect a single object and those which globally affect all or a subset of objects. For example, in a superscalar processor simulator, an object is an instruction. Fetching, decoding, and executing an instruction are all considered to be events which affect a single instruction. In contrast, events such as the initiation of a *rollback* due to a branch misprediction is considered to be *global* as it affects every instruction in the processor.

### 4.2 Instrumentation

Trace data is generated by inserting instrumentation statements into the simulator. An instrumentation statement outputs an event in the format described in Section 4.1. In our early implementation, instrumentation statements were simple printf statements in C

language. The printf statement outputs an event in comma-separated values (CSV) format. Each field in the CVS line is an attribute of the event. For example:

```

printf("%lld, %d, %lld\n", sequence, state, cycles);

```

The above example outputs an event with 3 attributes. The advantage of using this approach is that CSV is a widely used format. CSV APIs are available for many different programming languages. Parsing CSV data is as simple as calling the appropriate function. Furthermore, user can add additional event attributes by just changing number of CSV fields when invoking the verifier or the SFTAG processor without altering their event reader. However, this flexibility comes with a cost. The printf statement is expensive and each will be executed billions of times while the simulator is running. This overhead increases the simulator running time by twofold or more. For instance, 173.applu benchmark using large MinneSPEC [87] as input running on an uninstrumented simulator takes about 3 minutes to complete, but the same benchmark using the same input running on an instrumented simulator takes more than 6 minutes to finish. Because of the incurred overhead, we decided to trade some flexibility for efficiency. To achieve this, instead of outputting the events in CSV text format, we output events in fixed size binary format. This way we free a lot of computational power in parsing CSV lines and converting text strings to binary values and vice versa.

All of our tested simulators are written in C/C++ language. Here we demonstrate how instrumentation for a simulator in C can be done. Simulators written in other language can adapt similar coding structures. First we declare a C structure as follows:

```

typedef struct {

signed long long cycle;

unsigned int instruction_seq;

int state_id;

} Event;

```

Then we assign the proper value to each structure member before outputting the structure in binary as shown in the code below.

Outputting the events in binary format dramatically reduces the incurred overhead. For example, the 173.applu benchmark using large MinneSPEC as input running on an unmodified simulator takes about 3 minutes to complete. Same benchmark with same inputs running on simulator that outputs binary events takes a little over 3 minutes.

Alternatively, if the simulator contains a built-in trace generator, one can avoid instrumentation by converting the original trace into proper format before feeding it into the verifier or the SFTAG processor. For example, the SimpleScalar simulator [82, 1] has a -ptrace option that outputs instruction events.

Although instrumentation is relatively straight-forward in this framework. Great care must be taken while placing the instrumentation statement in the simulator code. The rule of thumb is that every output event must correctly represent the instruction, the instruction location, and the time at which the instruction is at that state. Besides that, global events which affect a subset of instructions require attaching the event to all affected instructions individually. For example, *rollback* is a global event in a processor pipeline but it only affects a subset of instructions, namely, all uncommitted instructions that are still in the pipeline. In order to properly handle these types of events, we attach the rollback state to all uncommitted instructions when a rollback event occurs.

### 4.3 The FOLSCL Grammar

A *constraint C* is a quantified statement that includes arithmetic and Boolean expressions and contains domain facts specified by the user. For example, the following constraint 4.1 specifies that each instruction that goes through the instruction fetch (*IF*) stage should go through the instruction decode (*ID*) stage unless a rollback (*RB*) that flushes the pipeline occurs.

$$\forall z \in T \ \exists y \in T, \quad (s^z = IF) \ \Rightarrow \ (a^y = a^z) \land ((s^y = ID) \lor (s^y = RB))$$

(4.1)

Verbally, the above expression specifies that for every event z that has the state attribute s equal to instruction fetch (IF), the verifier needs to find another event y with the same sequence number such that the stage attribute s of event y is equal to instruction decode (ID), or it needs to find another matching event whose stage attribute s is rollback (RB).

```

constraint \rightarrow quantification, statement;

statement \rightarrow \neg statement

\rightarrow statement \land statement

\rightarrow statement \vee statement

\rightarrow statement \Leftrightarrow statement

\rightarrow statement \Rightarrow statement

\rightarrow expression relation expression

\rightarrow (statement)

\rightarrow identifier

expression \rightarrow expression + expression

\rightarrow expression - expression

\rightarrow expression * expression

\rightarrow expression / expression

\rightarrow (expression)

\rightarrow terminal

\rightarrow identifier

relation \rightarrow > | \ge | < | \le | = | \ne

quantification \rightarrow \forall \mid \exists

```

**Figure 4.1:** The FOLCSL grammar.

FOLCSL constraints consists of fully quantified variables, arithmetic expressions and Boolean expressions. The language has the simple grammar shown in Figure 4.1. Note that a terminal in the language is an integer or an event attribute and an identifier is a variable name or a function. In our current implementation, functions are restricted to built-in functions only and they are implicitly declared.

# 4.4 Stream Processing and Sliding Windows

FOLCSL and the associated trace description treat an instruction as an object which moves through different states at some time point. The language allows the user to command the full power of first-order logic in specifying the invariants which need to hold. A direct consequence of this flexibility is the enormous size of the trace data which needs to be processed. As an invariant can reference arbitrary events, it may be necessary to compare

all events to each other. Given that the number of dynamic instructions for a benchmark program are in the order of billions and each instruction will have multiple events, an uncompressed full trace of a single benchmark program takes many terabytes of storage space. Therefore, instead of storing the trace and processing it afterwards, we process the data as a stream. In our approach, whenever all the *required events* are available they are immediately processed and all the *expired events* are discarded. As a result, a minimal amount of data is kept in memory during the verification process and the number of event comparisons is minimized. To achieve this, we employ an algorithm based on *sliding windows* [68] while checking the events against the constraint specifications.

### 4.4.1 Sliding Window

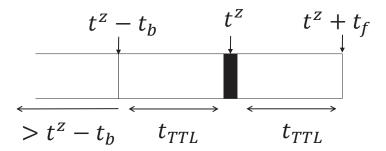

The sliding window approach views the trace as a chronologically ordered stream of events. Let  $\xi^z$  be our pivot event. We can buffer all events from time  $t^z - t_b$  to time  $t^z + t_f$  to form a sliding window that pivots at time  $t^i$ . If we assume that an instruction's maximum time to live (TTL) in the pipeline is  $t_{TTL}$ , then a given constraint can be verified by just checking events in the sliding window that pivots at time  $t^z$  with  $t_b = t_f = t_{TTL}$ . Note that, in the event of a context switch or a roll-back, the TTL values are reset, so the window is always bounded. The required events are all those events which reside in the sliding window and the expired events are all events such that their occurrence time is less than  $t^z - t_b$ . Figure 4.2 depicts the sliding window for constraint 4.1, where  $t^z$  is the pivot.

**Figure 4.2:** Sliding window.

The sliding window data structure provides three advantages. First, it requires minimal amount of memory space for data. Second, the verification process can begin before the full trace is generated, allowing traces with an unknown length to be processed, such as a data stream from a network. Finally, for each pivot event, only the events residing in the sliding window need to be considered instead of all the events in the full trace. This significantly speeds up the verification process and makes processing very large traces feasible.

### 4.4.2 Constraint Checker

Within a sliding window, all permutations of the events are verified against the constraints. A more efficient way would be to view the verification process as an assignment of values to event variables, similar to constraint satisfaction problems (CSP). Using that view, existing CSP algorithms can be used. Our main checker algorithm is a backtracking search algorithm which uses depth-first search by assigning values to each variable and backtracking when a given assertion fails. To further reduce processing time, we prune the search space by evaluating critical expressions of a constraint before all variables get assigned a value. In constraint 4.2 shown below, if the evaluation of expression  $s^z = IF$  is true and  $a^y = a^z$  is false, we know that the constraint is guaranteed to be false regardless of the value x. As a result, we can immediately backtrack and assign another value for y. Note that, instead of evaluating the expression  $a^y = a^z$ , one can evaluate the expression  $t^x > t^y$  first and if it evaluates to false we can still claim that the constraint is guaranteed to be false without knowing the result of expression  $a^y = a^z$ . But doing so will not eliminate any nodes from the search space because three of the variables z, y and x already had values assigned when the expression  $t^x > t^y$  was evaluated.

$$\forall z \in T \ \forall y \in T \ \exists x \in T, \ (s^z = IF) \ \Rightarrow \ (a^y = a^z) \ \land \ (t^x > t^y)$$

$$\tag{4.2}$$

More efficient CSP heuristics such as propagation, variable ordering and intelligent backtracking [88] can also be employed by the checker.

# 4.5 Constraint Specifications

While the domain of constraints is fairly large, several classes of constraints are particularly interesting to look at as they are necessary to catch some of the most common modeling errors. A common error in simulator development is the violation of resource constraints. For example, if an architecture provides only two memory ports, at no time we should have more than two memory operations performing an access. While such an error would immediately get caught in a real hardware implementation as the hardware would not run, a simulator may continue to execute and yield incorrect results. In this section, we give examples targeting several common modeling errors which occur while modeling the resources involved, the temporal behavior of instructions and modeling competing instructions such as arbitration. In order to easily specify such constraints, FOLCSL

includes several built-in functions that use sets to enforce resource based invariants. Two of these are the *set* function which collects events into a set, and the *car* function which computes the cardinality of a set. The following example specifies a constraint that indicates at most two instructions can simultaneously access the memory ports.

$$\forall q \in T, \ car(set(\forall z \in T, (s^z = MEMPORT) \land (t^z = t^q))) < 2$$

(4.3)

Similar to resource constraints, temporal constraints can be violated without a visible indication that such a violation has occurred. Temporal constraint violations include omission of a simulation step (i.e., a corresponding hardware stage), as well as cases such as the violation of the latency of a particular pipeline stage. Such violations are very difficult to catch using ad-hoc techniques, particularly when these violations occur only for a small subset of the executed instructions. The following example encodes the requirement that an instruction that leaves the instruction fetch stage (IF) must either enter the instruction decode (ID) stage or the rollback (RB) state and in doing so, it should take at least a cycle, but no more than K cycles, where K is a constant value that depends on the simulated model:

$$\forall z \in T \ \exists y \in T, \ (s^z = IF) \ \Rightarrow (a^y = a^z) \land$$

$$(t^y - t^z > 0) \land (t^y - t^z \le K) \land$$

$$((s^y = ID) \lor (s^y = RB))$$

$$(4.4)$$

When multiple instructions compete for a particular resource, a subset of those instructions might have higher priority over other instructions. This process, which is typically carried out by an arbiter at the hardware level, is particularly difficult to verify as the combination of the set of instructions must be taken into account while writing the FOLCSL statements. In the following example, we specify through constraint 4.5 that *LOAD* instructions are given priority to move from *EX* to *WB* stage.

$$\forall z \in T \ \forall y \in T, \ \exists x \in T \ \exists w \in T$$

$$(s^{z} = EX) \land (h^{z} = LOAD) \land (s^{y} = EX) \land (h^{y} \neq LOAD) \land (t^{y} = t^{z}) \Rightarrow$$

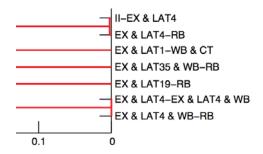

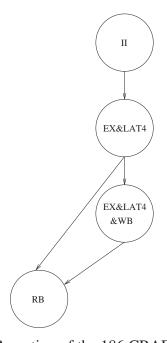

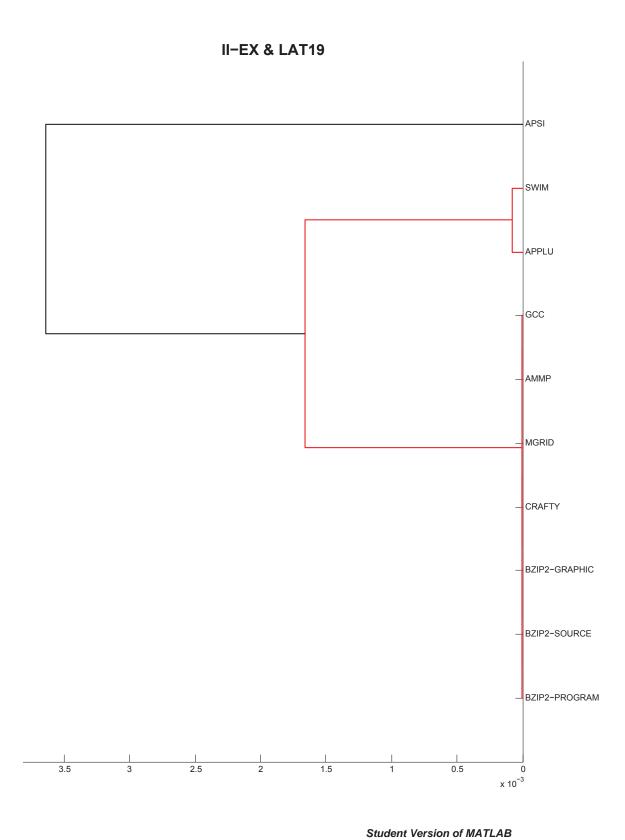

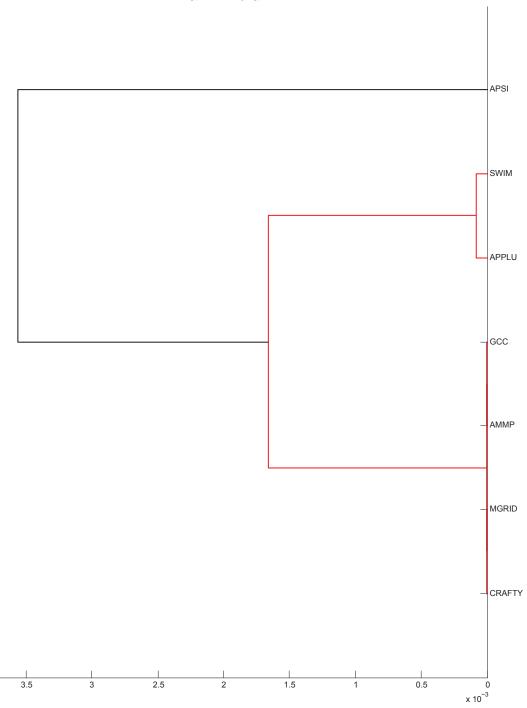

$$(a^{x} = a^{z}) \land (a^{w} = a^{y}) \land$$