Michigan Technological University

Create the Future Digital Commons @ Michigan Tech

Dissertations, Master's Theses and Master's Reports - Open

Dissertations, Master's Theses and Master's Reports

2013

# DESIGN AND IMPLEMENT DYNAMIC PROGRAMMING BASED DISCRETE POWER LEVEL SMART HOME SCHEDULING USING FPGA

Xin Yang michigan technological

Follow this and additional works at: https://digitalcommons.mtu.edu/etds

Part of the Electrical and Computer Engineering Commons Copyright 2013 Xin Yang

#### **Recommended Citation**

Yang, Xin, "DESIGN AND IMPLEMENT DYNAMIC PROGRAMMING BASED DISCRETE POWER LEVEL SMART HOME SCHEDULING USING FPGA", Master's report, Michigan Technological University, 2013. https://digitalcommons.mtu.edu/etds/601

Follow this and additional works at: https://digitalcommons.mtu.edu/etds Part of the <u>Electrical and Computer Engineering Commons</u>

# DESIGN AND IMPLEMENT DYNAMIC PROGRAMMING BASED DISCRETE POWER LEVEL SMART HOME SCHEDULING USING FPGA

Ву

Xin Yang

A REPORT

Submitted in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

In Electrical Engineering

MICHIGAN TECHNOLOGICAL UNIVERSITY

2013

© 2013 Xin Yang

This report has been approved in partial fulfillment of the requirements for the Degree of MASTER OF SCIENCE in Electrical Engineering

Department of Electrical and Computer Engineering

Report Advisor: Shiyan Hu

Committee Member: Sumit Paudyal

Committee Member: Chaoli Wang

Department Chair: Daniel R. Fuhrmann

# Contents

| Section I. Abs    | tract                        | 3  |

|-------------------|------------------------------|----|

| Section II. Intro | oduction                     | 4  |

| 1.                | History                      | 4  |

| 2.                | Today's power grid           | 4  |

| 3.                | Daily life power consumption | 4  |

| 4.                | Solutions                    | 5  |

| Section III. Algo | prithm                       | 8  |

| 1.                | Dynamic programming method   | 8  |

| 2.                | Proposed algorithm           | 8  |

| 3.                | Example                      | 13 |

| 4.                | Nash equilibrium             | 16 |

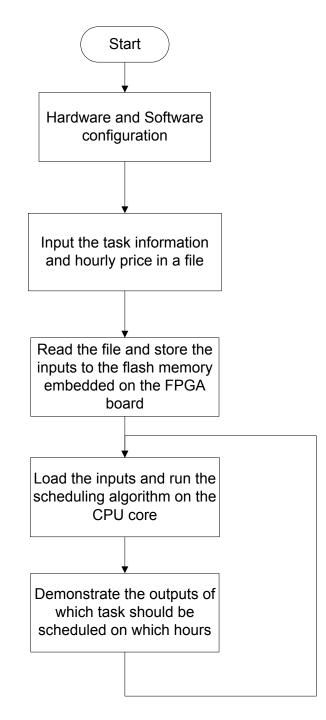

| Section IV. Flow  | v charts                     | 19 |

| 1.                | Procedure                    | 19 |

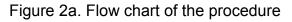

| 2.                | Individual user scheduling   | 20 |

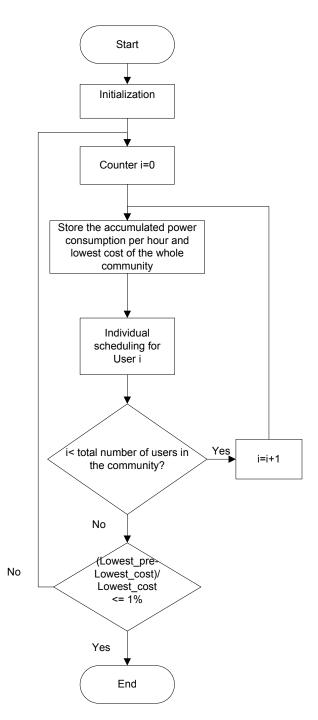

| 3.                | Multiple users scheduling    | 21 |

| Section V. FPG    | GA Structure                 | 22 |

| 1.                | Choosing FPGA board          | 22 |

| 2.                | NIOS II processor            | 23 |

| Section VI. Instruction of implementation in Quartus II | 25 |

|---------------------------------------------------------|----|

| 1. Schematic                                            | 25 |

| 2. SOPC builder                                         | 31 |

| 3. Clock source and Phase Lock Loop(PLL)                | 36 |

| Section VII. Hardware Testing                           | 37 |

| 1. Example 1                                            | 37 |

| 2. Example 2                                            | 38 |

| 3. Example 3                                            | 44 |

| Section VIII. Problems Solution                         | 54 |

| Section IX. Conclusion                                  | 56 |

| Section X. Code in NIOS II                              | 57 |

| Section XI. Appendix                                    | 65 |

| Section XII. References                                 | 80 |

# I. Abstract:

With the development and capabilities of the Smart Home system, people today are entering an era in which household appliances are no longer just controlled by people, but also operated by a Smart System. This results in a more efficient, convenient, comfortable, and environmentally friendly living environment. A critical part of the Smart Home system is Home Automation, which means that there is a Micro-Controller Unit (MCU) to control all the household appliances and schedule their operating times. This reduces electricity bills by shifting amounts of power consumption from the on-peak hour consumption to the offpeak hour consumption, in terms of different "hour price". In this paper, we propose an algorithm for scheduling multi-user power consumption and implement it on an FPGA board, using it as the MCU. This algorithm for discrete power level tasks scheduling is based on dynamic programming, which could find a scheduling solution close to the optimal one. We chose FPGA as our system's controller because FPGA has low complexity, parallel processing capability, a large amount of I/O interface for further development and is programmable on both software and hardware. In conclusion, it costs little time running on FPGA board and the solution obtained is good enough for the consumers.

# II. Introduction

### 1. History

Over a century ago, Nikola Tesla proposed the architecture of the power grid and people followed the design and developed it. During that time, electricity was a luxury resource that was used for lighting. Today, the power grid is used in almost all fields and people may not survive without it. Following the rapid technology development and no longer satisfying the present situation of the power grid, people are now concerned about issues such as greenness, efficiency, sustainability and reliability. The power grid could have the capability to become "smarter", a smarter grid [1] [2].

### 2. Today's power grid

There are many ways to make the power grid become smarter, such as improving the efficiency and reliability, developing environmentally friendly generators, managing the power consumption for consumers and so on so forth [3]. A basic and important part of the smart grid is the smart home. Specifically, if household tasks or daily power consumption could be arranged and scheduled, a more efficient system could be developed.

### 3. Daily life power consumption

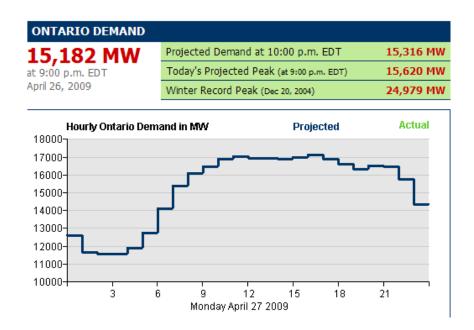

The following figure demonstrates the inefficiency power consumption that would occur during daily life. This is a plot of the power consumption for the province Ontario, Canada, on a normal weekday in April 27, 2009 [4].

Figure 1. Power consumption in Ontario on a normal day

We could easily find out that the peak power consumption occurred during the afternoon and low power consumption during the late night when most people were asleep [5]. The inefficiency occurs when the power companies must build the power plant which could support this high demand. These power plants with more capacity need more maintenance and repair cost. Hence, utility companies have to purchase power at higher rate. Furthermore, consumers typically purchase power with same price during different time periods. As the result, consumers would not consider adjusting their power consumption.

#### 4. Solutions

In order to improve this inefficient situation, utility companies would like to choose a "time of use" policy, which means that the power rate could be variable due to the total amount of power consumption. For example, higher power rate occurs during the afternoon and lower power rate occurs during the late night. Hence, for our individual consumers, we would like to have a smart system to help us schedule our household tasks in a reasonable way to reduce our electricity bill. The result could be that the controller for the system assists us to shift parts of

soft loads from the peak demand hours to the low demand hours. Soft loads are the loads can be scheduled, like washing clothes. During the day, the consumer may not need a precise washing time for clothes but ask for an end time to do this job. So, he/she can put the clothes there and let the smart washing machine decide when the clothes should be washed. These kinds of jobs are called soft loads, and hard loads are exactly the opposite. As previously stated, due to the smart scheduling, in terms of the individual the electricity bill is surely reduced when the hourly power rate offered by the utility company remains the same. These kinds of smart shifting behaviors can not only affect our electricity bill, but can also help the environment. For instance, in a typical week in October, one needs to do laundry. Thursday night during the high power demand hours, and Friday morning during the low power demand hours could be chosen as the time to start the laundry. The difference is, the power plants will need to add immediate and long-term generation capacity to support the electricity grid on Friday, which results in an increasing fuel levels in the plants by burning more coal for that kind of capacity buildup. Hence, due to the help of the smart scheduling, the emissions could be reduced [6].

However, if all the consumers in this community considered this reasonable scheduling by using the same smart system, they would all like to shift their loads from the peak demand hours to the low demand hours simultaneously. This would result in a bad situation that the original low demand hours become the high demand hours. Hence, if we need to solve this problem, communication with the other users is one of the prerequisites. Good news is that the smart system has a good capacity of communication. Thus, the controller could schedule the tasks based on the other's arrangement in an optimal way. This solution has two major advantages. On one hand, it has less complexity and results in a time saving strategy. On the other hand, it would allow the users to change the schedule optionally, since whenever the consumer inputs the newest schedule information to the controller in real time, the controller would immediately calculate the best scheduling option based on the other users' schedule.

- 6 -

This method is basically a dynamic programming strategy, which solves complex problems by dividing them into some simpler "sub-problems" and each time solves the sub-problem only once; the current solution depended on the previous computed optimal solution [7]. In this report, our proposed method is dynamic programming-based and focuses on the scheduling for the multi-user-community.

Since we need a Micro-Controller Unit (MCU) for the carrier of this proposed algorithm, FPGA is chosen due to its low complexity, convenient reprogrammability both on software and hardware and the technology trend. This is preliminary work for the controller of the Smart Home system, because in our work, the controller can only schedule the tasks but not perform other smart behaviors like real life wireless remote controls, controlling the power level of the household appliances based on the temperature and so on so forth. Fortunately, it is not hard to do further developments on the FPGA controller and that is exactly its critical advantage.

## III. Algorithm

#### 1. Dynamic programming method

Since our proposed algorithm is dynamic programming method based, I would like to introduce the dynamic programming strategy first. Dynamic programming is more like a divide and conquer algorithm, which divides the problems into pieces of sub-problems and then conquers them step by step. But, the difference is that these sub-problems are usually not mutually independent. If we solve this problem using the divide and conquer algorithm, some of the sub-problems may be calculated many times. Thus, if we could store the solutions of previous subproblems and use them to solve the next one, an abundance of repeated work would be avoided. For example, we could use a table to record all the solutions of the sub-problems we have already solved, no matter whether these subproblems would or would not be used for the future. This is the basic thinking of the dynamic programming algorithm. Keeping in mind, dynamic programming is not a typical algorithm that has a standard mathematical expression or clear structure. It is a way, a ladder, of solving the optimization problem. For different decision processes, there is different dynamic programming method-based algorithm [7].

#### 2. Proposed algorithm

Now, I would like to present our proposed algorithm in the following paragraph. First of all, individual scheduling is presented. Assume that there are *n* hours in the time period, and there are *m* tasks that need to be scheduled during the time period. In our case, each task has 5 factors, which are the start time *Task [i] [0]*, the end time *Task [i] [1]*, power level 1 *Task [i] [2]*, power level 2 *Task [i] [3]* and the total power consumption *Task [i] [4]*. For an easy simulation, we only divide time into hourly periods and only have two options of the power levels for each task. Furthermore, each task can only be operated continuously and can also change its power level during the operating time period. Hence, the total power consumption *Task [i] [4]* for one task would be,

$$Task [i][4] = \sum_{t=Task [i] [0]}^{Task [i] [1]} Energy_{task [i],t}$$

(1)

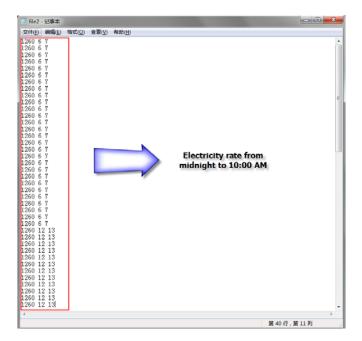

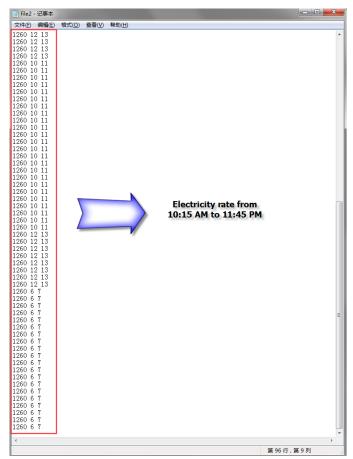

Since we are on the premise that the utility company is using the "time of use" strategy, different power consumption at different times has different power rates. These prices for the different hours are offered to the customers before the day starts and the prices would not change during that day. For example, Table 1, which is shown below, indicates the price related with certain hours in Ontario from May, 2012 to Apr, 2013. [8] In our case, we assume each hour has 3 factors, *hours [j] [0]*, *hours [j] [1]* and *hours [j] [2]*. *hours [j] [0]* represents the threshold value. If the total power consumption of the community in this hour is larger than the threshold value, the power rate would be *hours [j] [1]*. Otherwise, if the community total power consumption is less than the threshold value, the power rate would become *hours [j] [2]*. Then, we could start our scheduling algorithm in this condition for seeking the best or one of the best solutions to schedule all of the *n* tasks.

| From     | То       | Summer Rate<br>(May - Oct) | Winter Rate<br>(Nov - Apr) | Comparison of Time-of-Use Rates                                                               |  |  |

|----------|----------|----------------------------|----------------------------|-----------------------------------------------------------------------------------------------|--|--|

| 7:00 AM  | 8:00 AM  |                            |                            | 12                                                                                            |  |  |

| 8:00 AM  | 9:00 AM  | mid-peak rate              | on-peak rate               | 11 - 10 -                                                                                     |  |  |

| 9:00 AM  | 10:00 AM | 9.9 cents/kWh              | 11.8 cents/kWh             | 9                                                                                             |  |  |

| 10:00 AM | 11:00 AM |                            |                            | 48 -<br>47 -<br>5 -<br>5 -<br>5 -<br>5 -<br>5 -<br>5 -<br>5 -<br>5                            |  |  |

| 11:00 AM | 12:00 PM |                            |                            | ž 6 -                                                                                         |  |  |

| 12:00 PM | 1:00 PM  |                            |                            | \$ 5 -                                                                                        |  |  |

| 1:00 PM  | 2:00 PM  | on-peak rate               | mid-peak rate              | 3                                                                                             |  |  |

| 2:00 PM  | 3:00 PM  | 11.8 cents/kWh             | 9.9 cents/kWh              | 2 -                                                                                           |  |  |

| 3:00 PM  | 4:00 PM  |                            |                            |                                                                                               |  |  |

| 4:00 PM  | 5:00 PM  |                            |                            | Off Peak Mid Peak On Peak                                                                     |  |  |

| 5:00 PM  | 6:00 PM  | mid-peak rate              | on-peak rate               |                                                                                               |  |  |

| 6:00 PM  | 7:00 PM  | 9.9 cents/kWh              | 11.8 cents/kWh             | Note<br>Off peak rates are charged                                                            |  |  |

| 7:00 PM  | 8:00 PM  |                            |                            | on weekends and holidays.                                                                     |  |  |

| 8:00 PM  | 9:00 PM  |                            |                            | The rates shown to the left<br>apply Monday to Friday.                                        |  |  |

| 9:00 PM  | 10:00 PM |                            |                            |                                                                                               |  |  |

| 10:00 PM | 11:00 PM |                            |                            | Based on a small sample of 152 households,                                                    |  |  |

| 11:00 PM | Midnight |                            |                            | we calculate that, on average, time-of-use<br>consumption typically breaks down as follows:   |  |  |

| Midnight | 1:00 AM  | off-peak rate              | off-peak rate              | consumption typically breaks down as follows.                                                 |  |  |

| 1:00 AM  | 2:00 AM  | 6.3 cents/kWh              | 6.3 cents/kWh              | Off-peak: 63.4%                                                                               |  |  |

| 2:00 AM  | 3:00 AM  |                            |                            | Mid-peak: 16.0%<br>On-peak: 20.5%                                                             |  |  |

| 3:00 AM  | 4:00 AM  |                            |                            |                                                                                               |  |  |

| 4:00 AM  | 5:00 AM  |                            |                            | This results in a blended rate of<br>8.0 cents/kWh.                                           |  |  |

| 5:00 AM  | 6:00 AM  |                            |                            | ·                                                                                             |  |  |

| 6:00 AM  | 7:00 AM  |                            |                            | Help us improve our sample by participating<br>in our <u>Ontario Electricity Usage</u> study. |  |  |

First 600 Kilowatt Hours per month:7.4 cents/kWhAbove 600 kWh:8.7 cents/kWh

Table 1. 2012-2013 Ontario Time of Use Electricity Rates

The easiest way for scheduling these tasks that comes to mind would usually be the enumeration algorithm. However, since we have hundreds of tasks for multiusers and need to schedule them on at least 24 hours, the enumeration algorithm would cost a large amount of time to accomplish the job. This is due to the number of repeating sub problems that would grow exponentially while the size of the input is increasing. Fortunately, our proposed dynamic programming based algorithm is especially useful to deal with this kind of problems. Hence, it is very easy for us to abandon the way using the enumeration algorithm, even though using the enumeration algorithm can get the global optimal solution.

Back to the point, let **Sched (E, C)** be the main function of our scheduling. **E** denotes the current total energy consumption, while **C** denotes the current total cost. Thus, we obtained Table 2 for the optimization process for each task, assuming the start time is 12:00am.

| Hour | 12:00am | 1:00am      | 2:00am         | 3:00am |  |

|------|---------|-------------|----------------|--------|--|

| Ways |         |             |                |        |  |

| 1    | (0,C1)  | (0,C4)      | ► (0,C11)      |        |  |

| 2    | (E1,C2) | (E1,C5)     | (E1,C12)       |        |  |

| 3    | (E2,C3) | (E2,C6)     | (E2,C13)       |        |  |

| 4    |         | (E1+E1,C    | (E1+E1,C14)    |        |  |

| 5    |         | (E1+E2,C8)  | (E1+E2,C15)    |        |  |

| 6    |         | (E2+E1,C9)  | (E2+E1,C16)    |        |  |

| 7    |         | (E2+E2,C10) | (E2+E2,C17)    |        |  |

| 8    |         |             | (E1+E1+E1,C18) |        |  |

| 9    |         |             | (E1+E1+E2,C19) |        |  |

| 10   |         |             | (E1+E2+E1,C20) |        |  |

| 11   |         |             | (E1+E2+E2,C21) |        |  |

| 12   |         |             | (E2+E1+E1,C22) |        |  |

| 13   |         |             | (E2+E1+E2,C23) |        |  |

|      |         |             |                |        |  |

Table 2. Scheduling the tasks without pruning

**E1** and **E2** denote the power level choices of the task respectively. For the first hour, we could schedule the task in 3 ways: no schedule, schedule it in power level 1, or schedule it in power level 2. And each of these schedules would cause a cost named  $C_i$ . Since each schedule is based on the previous solution, we have a cost when this task does not schedule on this hour, or  $(0, C_x)$ . We could easily find out that the solution numbers for *j*th hour is  $3^{2*i}+1$ , and this number we obtained without simplification. With simplification, some of the solution could be abandoned due to its lower energy consumption and higher cost in the same row. For example, looking at the second row, at this hour, there are 2 outputs of cost for total power consumption **E1+E2**. So, if  $C_8$  is bigger than  $C_7$ , which means the

5<sup>th</sup> way costs more, compared to the 6<sup>th</sup> way, while consuming the same power at this time. Thus, the 5<sup>th</sup> way at 1:00am should be abandoned. For the result, the solution following this abandoned solution at the next hour should all be deleted, since for those child solutions, their parent solution is no longer an optimal one. Then, we do the same comparison for all the solutions in the same column mutually as long as no higher cost with lower energy consumption solutions remain. That is a huge simplification for this table, and the new one, as an example, is shown below in Table 3.

| Hour | 12:00am | 1:00am      | 2:00am         | 3:00am |  |

|------|---------|-------------|----------------|--------|--|

| Ways |         |             |                |        |  |

| 1    | (0,C1)  | →(0,C4)     | → (0,C11)      |        |  |

| 2    | (E1,C2) | ₩E1,C5      | (E1,C12)       |        |  |

| 3    | (E2,C3) | (E2,C6)     | (E2,C13)       |        |  |

| 4    |         | (E1+E1,C7)  | (E1+E1,C14)    |        |  |

| 5    |         | (E2+E1,C9)  | (E1+E2,C15)    |        |  |

| 6    |         | (E2+E2,C10) | (E2+E2,C17)    |        |  |

| 7    |         |             | (E1+E1+E1,C18) |        |  |

| 8    |         |             | (E1+E1+E2,C19) |        |  |

| 9    |         | J           | (E2+E1+E2,C20) |        |  |

| 10   |         |             | (E2+E2+E1,C21) |        |  |

| 11   |         |             |                |        |  |

|      |         |             |                |        |  |

Table 3. Scheduling the tasks with pruning

For *j*th hour,  $j \in [1,24]$ , the combination of energy is (*a*\*E1+*b*\*E2), and *a* <= *j*, *b*<= *j*. Hence, we could find out that the solution numbers for *j*th hour become no more than(j + 1)<sup>2</sup>. Assume that in the real life, the power level would usually be an integer number. Let C equals to the maximum value in the E set, then the solution number for **j**th hour becomes no more than C\*j.

After one task scheduling, the next task scheduling which is based on the previous one, would be easy and we would like to schedule it in the same way as the previous one was done. After finishing all the tasks for individual customers, we would like to re-schedule the tasks from the beginning for better scheduling. The advantage of doing so is that more precise optimization would occur. What we need to do is just removing one task from the scheduler, recalculating the total energy consuming for each of hours the task used to schedule on, and reschedule the tasks into the scheduler just like a new task based on the rest tasks. Multi-user tasks scheduling is almost the same as the individual user task scheduling. In multi-user tasks scheduler and repeat the work, which is shown through the example below.

#### 3. Example

Let us assume that we have 9 tasks, and each of them has 5 factors (start time=0, end time=6, power level 1=1, power level 2=2, total energy=4). The hourly price for all hours is \$1 if the total energy consumption for each hour is below or equal to 1 and the hourly price would be \$2 if the total energy consumption for each hour is above 1. Then, the scheduling for the first task is shown below.

| <i>j</i> th<br>hour<br>ways | 1 <sup>st</sup> (0) | 2 <sup>nd</sup> (1) | 3 <sup>rd</sup> (2) | 4 <sup>th</sup> (3) | 5 <sup>th</sup> (4) | 6 <sup>th</sup> (5) | 7 <sup>th</sup> (6) |

|-----------------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

| 1                           | (0,0)               | ▶(0,0) ▼            | (0,0)               | (0,0)               | →(0,0)              | →(0,0) 🦷            | (0,0)               |

| 2                           | (1,1)               | (1,1)               | (1,1)               | (1,1)               | (1,1)               | (1,1)               | (1,1)               |

| 3                           | (2,4)               | *(2,4)              | *(2,4)              | *(2,4)              | *(2,4)              | *(2,4)              | *(2,4)              |

| 4                           |                     | (2,2)               | (2,2)               | (2,2)               | (2,2)               | (2,2)               | (2,2)               |

| 5                           |                     | *(3,5)              | *(3,5)              | *(3,5)              | *(3,5)              | *(3,5)              | *(3,5)              |

| 6                           |                     | (3,5)               | (3,3)               | (3,3)               | (3,3)               | (3,3)               | (3,3)               |

| 7                           |                     | (4,8)               | *(4,6)              | *(4,6)              | *(4,6)              | *(4,6)              | *(4,6)              |

| 8                           |                     |                     | (4,6)               | (4,4)               | (4,4)               | (4,4)               | (4,4)               |

| 9                           |                     |                     |                     |                     |                     |                     |                     |

\* need to be pruned

Table 4. Example of pruning for task 1

The red ones are the final schedule for task 1 which is the optimum solution as there is no other task scheduled. Now, we need to schedule the next task depending on the task 1's scheduling.

| <i>j</i> th                                                | 1 <sup>st</sup> (0) | 2 <sup>nd</sup> (1) | 3 <sup>rd</sup> (2) | 4 <sup>th</sup> (3) | 5 <sup>th</sup> (4) | 6 <sup>th</sup> (5) | 7 <sup>th</sup> (6) |

|------------------------------------------------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

| hour<br>ways                                               | Prev 1              | Prev 1              | Prev 1              | Prev 1              | Prev 0              | Prev 0              | Prev 0              |

| 1                                                          | (0,1) 🤊             | (0,2)               | (0,3)               | •(0,4)              | (0,4)               | ₹0,4)               | ▶(0,4)              |

| 2                                                          | (1,4)               | (1,5)               | (1,6)               | (1,7)               | (1,5)               | (1,5)               | (1,5)               |

| 3                                                          | (2,6)               | (2,7)               | (2,8)               | (2,9)               | *(2,8)              | *(2,8)              | *(2,8)              |

| 4                                                          | //                  | *(2,8)              | *(2,9)              | *(2,10)             | (2,8)               | <b>(</b> 2,6)       | 2,6)                |

| 5                                                          |                     | *(3,10)             | *(3,11)             | *(3,12)             | <b>*(3,11)</b>      | *(3,9)              | *(3,9)              |

| 6                                                          |                     | (3,10)              | (3,11)              | (3,12)              | (3,10)              | (3,9)               | (3,9)               |

| 7                                                          |                     | (4,12)              | (4,13)              | (4,14)              | *(4,13)             | *(4,12)             | *(4,12)             |

| 8                                                          |                     |                     | *(4,14)             | *(4,15)             | (4,13)              | (4,11)              | (4,10)              |

| 9                                                          |                     |                     |                     |                     |                     |                     |                     |

| * need to be pruned Table 5. Example of pruning for task 2 |                     |                     |                     |                     |                     |                     |                     |

*Prev n* means in this hour period, *n* units' power has already been scheduled due to previous scheduling. After scheduling, we figure out that the total cost is lowest when we arranged the task 2 uniformly in power level 1 on the last four time periods. Repeat the scheduling using our proposed algorithm for the rest tasks. After one time full-tasks scheduling, we arrange all the tasks in the way shown in the following table.

| <i>j</i> th<br>hour<br>tasks | 1 <sup>st</sup> (0) | 2 <sup>nd</sup> (0) | 3 <sup>rd</sup> (2) | 4 <sup>th</sup> (3) | 5 <sup>th</sup> (4) | 6 <sup>th</sup> (5) | 7 <sup>th</sup> (6) |

|------------------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

| 1                            | 1                   | 1                   | 1                   | 1                   |                     |                     |                     |

| 2                            |                     |                     |                     | 1                   | 1                   | 1                   | 1                   |

| 3                            | 2                   | 2                   |                     |                     |                     |                     |                     |

| 4                            | 2                   | 2                   |                     |                     |                     |                     |                     |

| 5                            | 2                   | 2                   |                     |                     |                     |                     |                     |

| 6                            | 2                   | 2                   |                     |                     |                     |                     |                     |

| 7                            | 2                   | 2                   |                     |                     |                     |                     |                     |

| 8                            | 2                   | 2                   |                     |                     |                     |                     |                     |

| 9                            | 2                   | 2                   |                     |                     |                     |                     |                     |

Table 6. All tasks scheduling

In order to optimize the arrangement, we prefer to run it again. First, we should "delete" task 1 from the table. Then, depending on the existing arrangement, reschedule task 1 and reschedule the rest after it. Finally, we would obtain the following arrangement.

| <b>j</b> th<br>hour<br>tasks | 1 <sup>st</sup> (0) | 2 <sup>nd</sup> (0) | 3 <sup>rd</sup> (2) | 4 <sup>th</sup> (3) | 5 <sup>th</sup> (4) | 6 <sup>th</sup> (5) | 7 <sup>th</sup> (6) |

|------------------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

| 1                            | 2                   | 1                   | 1                   |                     |                     |                     |                     |

| 2                            |                     |                     |                     | 1                   | 1                   | 1                   | 1                   |

| 3                            | 2                   | 2                   |                     |                     |                     |                     |                     |

| 4                            | 2                   | 2                   |                     |                     |                     |                     |                     |

| 5                            | 2                   | 2                   |                     |                     |                     |                     |                     |

| 6                            | 2                   | 2                   |                     |                     |                     |                     |                     |

| 7                            | 2                   | 2                   |                     |                     |                     |                     |                     |

| 8                            | 2                   | 2                   |                     |                     |                     |                     |                     |

| 9                            | 2                   | 2                   |                     |                     |                     |                     |                     |

Table 7. All tasks rescheduling

Then, we met equilibrium, no matter how many further rescheduling we run. For this simple example, this arrangement is one of the optimum solutions. Most of the time, we may not obtain the optimum solution using this algorithm, but we could get a solution very close to the optimum one after rescheduling  $\lambda$  times. In order to determine this  $\lambda$ , we could compare the lowest cost in  $\lambda$ th time and in ( $\lambda$ -1)th time. If the difference is below a certain value, like 1%, which the consumers may accept, the controller shall stop rescheduling the tasks. Then we could do this progress for all the users in the community, just treating multi-users as multi-tasks. Finally, equilibrium would be met and all the users in the community would satisfy the result [9].

#### 4. Nash equilibrium

Our proposed algorithm is to find Nash equilibrium. "In game theory, the Nash equilibrium is a solution concept of a non-cooperative game involving two or more players, in which each player is assumed to know the equilibrium strategies of the other players, and no player has anything to gain by changing only his own strategy unilaterally" [10]. In the system, like our "smart community", where

multiple independent consumers are trying to optimize their own utility unilaterally, Pareto Optimality is very hard to achieve. Pareto optimality or Pareto efficiency means that in the system, "no one can be made better off without making at least one individual worse off [11]." Hence, Nash equilibrium is fair and reasonable among consumers since everyone in the system is choosing the individual optimal strategy depending on others' choices. Following is the normal math definition of Nash equilibrium. In a game set G={S1,...,Sn: u1,...un}, there is a Strategy Profile (s1\*,...,sn\*), where si\* $\in$ Si(Si is the strategy set of player i). If any si\* is the best strategy to the combination of others' strategies (s1\*,...,s\*i-1,s\*i+1,...,sn\*), or ui(s1\*,...,s\*i-1,s\*i,s\*i+1,...,sn\*) ≥ui((s1\*,...,s\*i-1,sij\*,s\*i+1,...,sn\*) where sij $\in$ Si, then the strategies(s1\*,...,sn\*) is a Nash equilibrium of the game set G [12].

Apparently, our algorithm keeps finding the Nash equilibrium until the improvement of the two scheduling solutions for the whole community is less than a certain value. For instance, our solution is implemented in a community with 100 customers. The controller would do the scheduling for the first customer, and repeat the procedure until the last one. The strategy for each scheduling depends on what we have scheduled for the previous ones. After one complete scheduling for these 100 customers, we could obtain a game set G1=  $\{S1_1, S2_1, ..., S100_1: c1_1, c2_1, ..., c100_1\}$ , where  $Si_1$  denotes the strategy of customer *i* and  $c_{j_1}$  denotes the cost of customer *j* using its strategy in the 1<sup>st</sup> scheduling. Then in the 2<sup>nd</sup> scheduling for the whole community, we would change everyone's scheduling strategy one by one, depending on the Strategy Profile of the whole community  $(S1_2, S2_2, ..., Si - 1_2, Si_1, Si + 1_1, ..., S100_1)$ , to obtain a new Strategy Profile  $\{S1_2, S2_2, ..., Si - 1_2 Si_2, Si + 1_1, ..., S100_1\}$ . After a Strategy Profile  $\{S1_2, S2_2, \dots, Si - 1_2 Si_2, Si + 1_2, \dots, S100_2\}$  is obtained, the controller shall start the 3<sup>rd</sup> scheduling for the community. Since each individual scheduling strategy is set depending on all the other strategies in the community, the controller must be able to find a game set  $G_k$ , in which any  $Si_k$  is the best strategy to the combination of others' strategies (s1,...si-1,si+1,...,sn).

- 18 -

Additionally, the best strategy means the strategy with the lowest cost. It is important to remember that finding the Nash equilibrium does not mean that we should find out Minimum(c1+c2+...+c100). However, this **k** value is hard to find since the tasks' number in a community may be very large. In fact, we only need to go through  $\lambda$  times, like mentioned in the earlier paragraph. After  $\lambda$  times scheduling, the difference of the total cost between two complete scheduling for the community is less than a very small value. Then, we would obtain a solution that is very close to the Nash equilibrium and the customers would be satisfied.

The algorithm part is completed and therefore I would like to present the hardware and software setup in the next sections. Due to the complexity of the algorithm, I decided to use the CPU core embedded on the FPGA board to do the calculation, or scheduling. The following are flow charts of the whole procedure of scheduling.

# IV. Flow Charts

#### 1. Procedure

### 2. Individual user scheduling

Figure 2b. Flow chart of the algorithm for individual user scheduling

3. Multiple users scheduling

# V. FPGA Structure

### 1. Choosing FPGA board

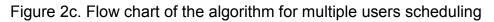

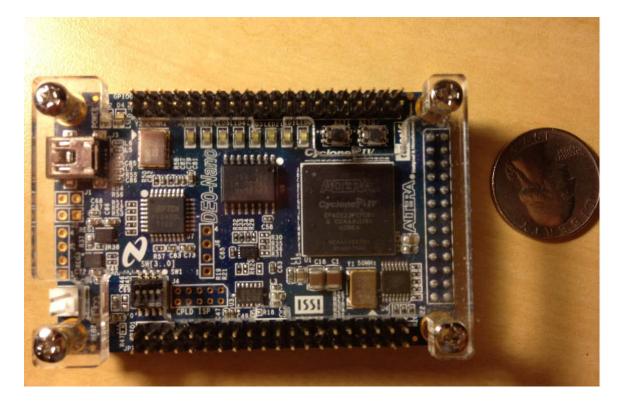

At the beginning of the project, I chose Altera's DE0 Nano board, which is shown below, as my controller due to its small size of body, good portability, and enough logic elements and comparatively large memory storage. Cyclone IV EP4C22 FPGA, which has 150,000 logic elements, is embedded in the DE0-Nano board. This FPGA education board also has 32MB SDRAM [13]. However, since it has no Flash Memory embedded on the board, it is kind of difficult to load the task information and hourly electricity price, which needs to be input by the operators from the keyboard or from a file. Hence, I finally abandoned this board and used Altera's DE2 board as the MCU. Even though this board is about 10 times larger than DE0-Nano board and only has Cyclone II FPGA core with 68,416 logic elements and 8MB SDRAM, it still fits this project [14].

Figure 3a. DE0-Nano board

A photograph of the DE2 board is shown below in Figure 3. It demonstrates the location of the key component. The components with a yellow square frame are used in our project.

Figure 3b.DE2 board

### 2. NIOS II processor

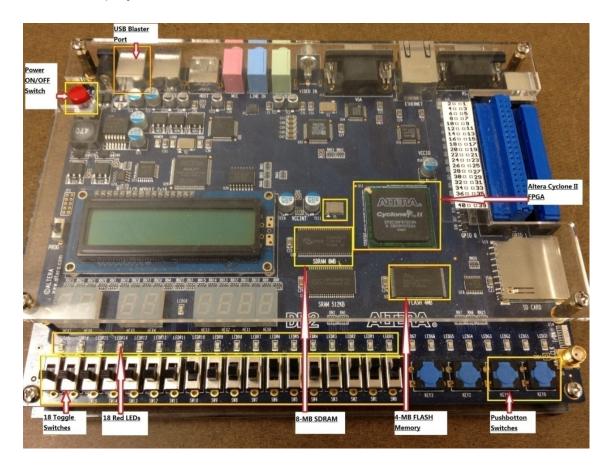

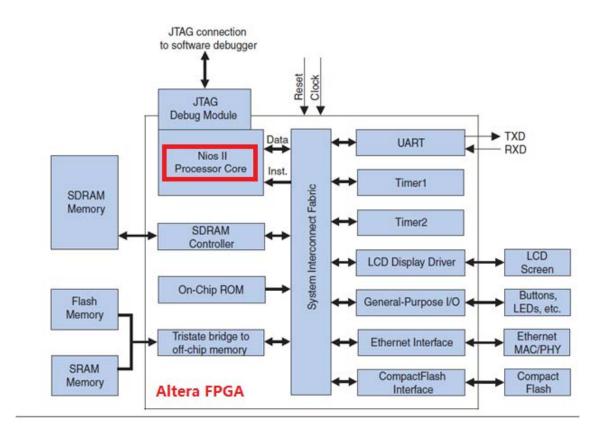

In order to implement the comparatively complex algorithm, the NIOS II Processor embedded in Cyclone II FPGA is used in this project. Figure 4, obtained from Altera, shows an example of the architecture of a NIOS II Processor System [15].

Figure 4.Example of a NIOS II Processor System

This architecture is very important for us to build a System on Programmable Chip (SOPC). I will review this figure later when I use the SOPC builder in Quatus II.

# **<u>VI.</u>** Instruction of Implementing in Quartus II

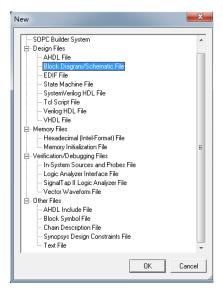

### 1. Schematic

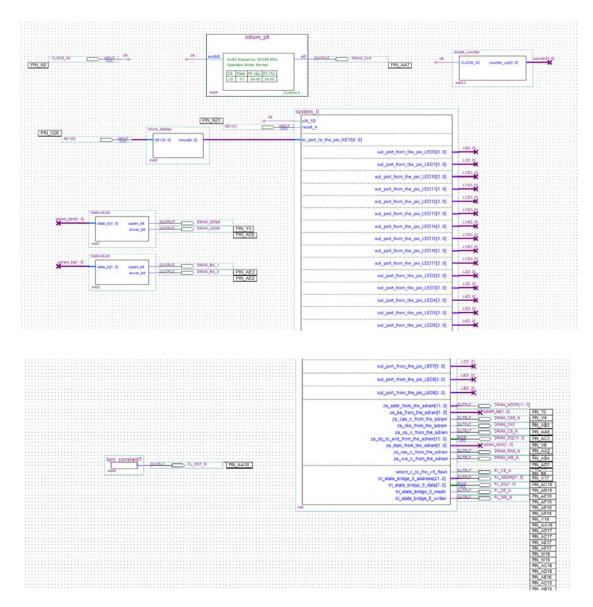

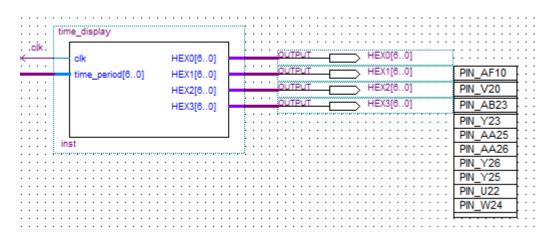

First of all, we need to create the hardware configuration in Quartus II. A new project should be built and after we will create a schematic file as our project's top entity. The overview of the hardware schematic is shown below as the Figure 5a and Figure 5b.

Figure 5. Overview of the schematic2

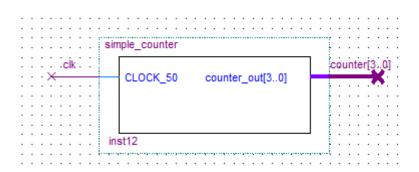

A system clock is needed, so we will create an input connecting to *CLOCK\_50*, which has 50Mhz power level, followed by the wire named clk. This wire could connect to any modules, which need clock sources.

|        | .cik     |  |

|--------|----------|--|

|        | CLOCK_50 |  |

| PIN_N2 |          |  |

Figure 6.System Clock Source

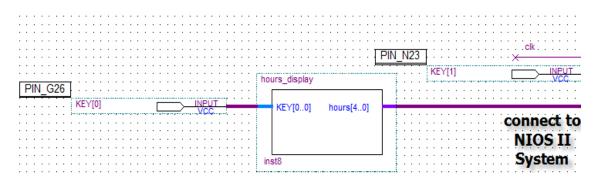

Use KEY[1] as the *reset* input and KEY[0] to choose the particular hours to demonstrate the tasks scheduled on them.

Figure 7.KEY modules

In this case, if KEY[0] is not pushed, the tasks scheduled on *hour[0]* would be displayed on the board by turning on the LEDs. If KEY[0] is pushed one time, the tasks scheduled on *hour[1]* would be displayed and so on so forth. In this simulation, I set the number of hours up to 24 and the output has 5 bits. The Verilog code of this KEY controlling module is shown below.

KEY,

hours

);

input [0:0]KEY;

output reg [4:0]hours;

always @(negedge KEY[0])

if (hours>5'd22) hours<=0;

else hours<=hours+1;</pre>

#### endmodule

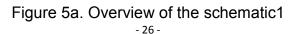

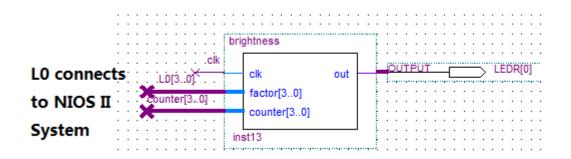

Following is the demonstrated used LEDs output module and its brightness control used counter module. Each LED represents a task. If the power level of the running task is high, the LED would become brighter, otherwise it would become fainter. In our project, I assume that the power level range of all the tasks is between 1 and 15. *Counter* is used to count the clock. Since it only has 4 bits, *counter* will keep increasing between 0 and 15 in 50 Mhz frequency as the same as the system clock. Hence, the brightness of the LED would be set proportionally depending on the power level of the corresponding task, since during each 16 units time period the LED would be turned on in *factor* number unit time period and be turned off in (16 - *factor*) number unit time period.

Figure 8.LEDs output module

Figure 9.Brightness control used counter module

The Verilog codes for these two module are shown below.

```

module simple_counter (

```

CLOCK\_50,

counter\_out

);

*input* CLOCK\_50;

output reg [3:0] counter\_out;

always @ (posedge CLOCK\_50)

begin

counter\_out <= #1 counter\_out + 1;</pre>

end

endmodule

module brightness (

# clk, factor,

counter,

out

);

input clk;

*input* [3:0]factor;

*input* [3:0]counter;

output reg out;

always @ (posedge clk)

if (factor==0) out<=0;</pre>

else if (counter<=factor) out <=1; else out <=0;</pre>

endmodule

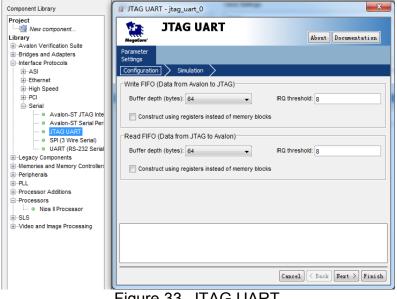

### 2. SOPC builder

The most important part is the CPU core of this system. We will use *SOPC builder* to create an on chip system, which is shown below.

| Devia    | e Family: Cyc                        | Name               | 8                                               |        |              | Sour       | ce   |         |

|----------|--------------------------------------|--------------------|-------------------------------------------------|--------|--------------|------------|------|---------|

| Devic    | cyc                                  | clk_5              |                                                 |        |              | Exter      |      |         |

|          |                                      |                    |                                                 |        |              |            |      |         |

| Jse      | Connecti                             | Module Name        | Description                                     | Clock  | Base         | End        | Tags | IRC     |

| V        |                                      | 😑 сри              | Nios II Processor                               |        |              |            |      |         |

|          |                                      | instruction_master | Avalon Memory Mapped Master                     | clk_50 |              |            |      |         |

|          |                                      | data_master        | Avalon Memory Mapped Master                     |        | IRQ          | 0 IRQ 31   | 1    | ←       |

|          | $ \downarrow \downarrow \rightarrow$ | jtag_debug_module  | Avalon Memory Mapped Slave                      |        | 0x01802800   | 0x01802fff |      |         |

| 1        |                                      | onchip_memory2     | On-Chip Memory (RAM or ROM)                     |        |              |            |      |         |

|          | $ \uparrow \rightarrow$              | s1                 | Avalon Memory Mapped Slave                      | clk_50 |              | 0x01801fff |      |         |

| <b>V</b> |                                      | ⊟ jtag_uart        | JTAG UART                                       |        |              |            |      |         |

|          | $   \rightarrow$                     | avalon_jtag_slave  | Avalon Memory Mapped Slave                      | clk_50 | 0x01803130   | 0x01803137 |      | $\succ$ |

| 1        |                                      | ⊟ sdram            | SDRAM Controller                                |        |              |            |      |         |

|          | $ \uparrow \rightarrow$              | s1                 | Avalon Memory Mapped Slave                      | clk_50 |              | 0x00ffffff |      |         |

| 1        |                                      | ☐ cfi_flash        | Flash Memory Interface (CFI)                    |        |              |            |      |         |

|          | $   \rightarrow$                     | • s1               | Avalon Memory Mapped Tristate Slave             | clk_50 |              | 0x017fffff |      |         |

| 1        |                                      | tri_state_bridge_0 | Avalon-MM Tristate Bridge                       |        |              |            |      |         |

|          | $  \rightarrow   \rightarrow$        | avalon_slave       | Avalon Memory Mapped Slave                      | clk_50 |              |            |      |         |

|          | $    \subseteq$                      | tristate_master    | Avalon Memory Mapped Tristate Master            |        |              |            |      |         |

| <b>V</b> |                                      | pio_LED0           | PIO (Parallel I/O)                              |        |              |            |      |         |

|          | $  \longrightarrow$                  | • s1               | Avalon Memory Mapped Slave                      | clk_50 | 0x01803000   | 0x0180300f |      |         |

| 1        |                                      | pio_LED1           | PIO (Parallel VO)                               |        |              |            |      |         |

|          | $  \rightarrow$                      | • s1               | Avalon Memory Mapped Slave                      | clk_50 |              | 0x0180301f |      |         |

| V        |                                      | pio_LED2           | PIO (Parallel I/O)                              |        |              |            |      |         |

|          | $  \rightarrow$                      | • s1               | Avalon Memory Mapped Slave                      | clk_50 |              | 0x0180302f |      |         |

| V        |                                      | pio_LED3           | PIO (Parallel VO)                               |        |              |            |      |         |

|          | $  \rightarrow$                      | • s1               | Avalon Memory Mapped Slave                      | clk_50 |              | 0x0180303f |      |         |

| V        |                                      | pio_LED4           | PIO (Parallel I/O)                              |        |              |            |      |         |

|          | $  \rightarrow$                      | • s1               | Avalon Memory Mapped Slave                      | clk_50 | © 0x01803040 | 0x0180304f |      |         |

| V        |                                      | pio_LED5           | PIO (Parallel I/O)                              |        |              |            |      |         |

|          | $  \rightarrow$                      | • s1               | Avalon Memory Mapped Slave                      | clk_50 |              | 0x0180305f |      |         |

| <b>V</b> |                                      | pio_LED6           | PIO (Parallel I/O)                              |        |              |            |      |         |

|          | $  \rightarrow$                      | • s1               | Avalon Memory Mapped Slave                      | clk_50 | 0x01803060   | 0x0180306f |      |         |

| 1        |                                      | pio_LED7           | PIO (Parallel VO)                               |        |              |            |      |         |

|          | $  \longrightarrow$                  | • s1               | Avalon Memory Mapped Slave                      | clk_50 |              | 0x0180307f |      |         |

| V        |                                      | ☐ pio_LED8         | PIO (Parallel I/O)                              |        |              |            |      |         |

|          | $  \longrightarrow$                  | s1                 | Avalon Memory Mapped Slave                      | clk_50 |              | 0x0180308f |      |         |

| 1        |                                      | □ pio_LED9         | PIO (Parallel VO)                               |        |              |            |      |         |

| _        | $  \rightarrow$                      | s1                 | Avalon Memory Mapped Slave                      | clk_50 |              | 0x0180309f |      |         |

| V        |                                      | □ pio_LED10        | PIO (Parallel I/O)                              |        |              |            |      |         |

| _        | $  \longrightarrow$                  | • s1               | Avalon Memory Mapped Slave                      | clk_50 | 0x018030a0   | 0x018030af |      |         |

| 1        |                                      | ☐ pio_LED11        | PIO (Parallel VO)                               |        |              |            |      |         |

|          | $  \rightarrow$                      | • s1               | Avalon Memory Mapped Slave                      | clk_50 | 🖹 0x018030b0 | 0x018030bf |      |         |

| V        |                                      | □ pio_LED12        | PIO (Parallel I/O)                              |        |              |            |      |         |

| _        | $  \longrightarrow$                  | • s1               | Avalon Memory Mapped Slave                      | clk_50 | 0x018030c0   | 0x018030cf |      |         |

| V        |                                      | ☐ pio_LED13        | PIO (Parallel VO)                               |        |              |            |      |         |

| _        | $  \longrightarrow$                  | s1                 | Avalon Memory Mapped Slave                      | clk_50 |              | 0x018030df |      |         |

| V        |                                      | □ pio_LED14        | PIO (Parallel I/O)                              |        |              |            |      |         |

|          | $\rightarrow$                        | s1                 | Avalon Memory Mapped Slave                      | clk_50 | 0x018030e0   | 0x018030ef |      |         |

| 1        |                                      | □ pio_LED15        | PIO (Parallel I/O)                              |        | 1.           |            |      |         |

| _        | $  \longrightarrow$                  | s1                 | Avalon Memory Mapped Slave                      | clk_50 |              | 0x018030ff |      |         |

| 1        |                                      | □ pio_LED16        | PIO (Parallel I/O)                              |        |              |            |      |         |

|          | $ \longrightarrow $                  | s1                 | Avalon Memory Mapped Slave                      | clk_50 | 0x01803100   | 0x0180310f |      |         |

| 1        |                                      | □ pio_LED17        | PIO (Parallel I/O)                              |        |              |            |      |         |

| _        | $  \rightarrow$                      | s1                 | Avalon Memory Mapped Slave                      | clk_50 | ■ 0x01803110 | 0x0180311f |      |         |

| <b>V</b> |                                      | pio_KEY            | PIO (Parallel VO)<br>Avalon Memory Mapped Slave | clk 50 | ■ 0x01803120 |            |      |         |

Figure 10.SOPC builder setup

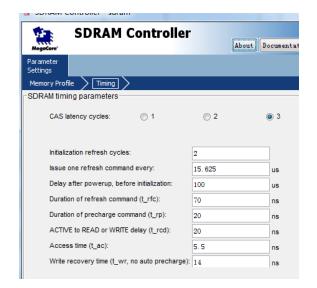

CPU is the core and it connects to all of the other parts of system. Jtag uart is used for the FPGA board to communicate with the PC. For example, through the jtag\_uart interface, the input file could be stored from the PC to the Flash Memory embedded on the FPGA board. Then, we created several I/O interfaces like *pio\_key* and *pio\_ledx* to connect the CPU core to the I/O pins on the FPGA board. It's painless to quickly add a System ID component, named sysid, to keep track of whether the BSP driver package currently used is still compatible with the hardware we are trying to run it on. It is also painless to add an Onchip memory. Actually we don't need to use it since I decided to store all the instructions, library, etc. in the SDRAM. Why I would like to use SDRAM as my CPU memory is that the memory space in onchip memory is too small to support the full c library. I could only use the full c library to use file operation in NIOS II. In Figure 4, it shows that we need an *SDRAM* controller to connect the real SDRAM memory and to control its behavior. For each particular FPGA chip, we should consider the configuration of the SDRAM controller. Datasheet of the target board is needed here.

| SDRAM Controller          |

|---------------------------|

| Parameter<br>Settings     |

| Memory Profile > Timing > |

| Presets: Custom           |

| Data width                |

| Bits: 16 💌                |

| _ Architecture            |

| Chip select: 1            |

| Address widths            |

| Row: 12 Column: 8         |

Figure 11.SDRAM Controller Memory Profile configuration

Figure 12.SDRAM Controller Timing Configuration

Flash Memory Interface, named cfi\_flash, is also added in the SOPC. In order to correctly use Flash Memory, indicating in Figure 4, tri\_state\_bridge is also required, and the slave side should connect to the CPU and the master side should connect to the Flash Memory. Flash Memory Interface's setup is shown below.

|                       | MegaCore                                      | Flash Memor                                     | y Ir        |

|-----------------------|-----------------------------------------------|-------------------------------------------------|-------------|

|                       | Parameter<br>Settings                         | Traing                                          |             |

|                       | Attributes Presets: Cust                      | Timing X                                        |             |

|                       | Size                                          |                                                 |             |

|                       | Address Wi                                    | idth (bits): 22                                 |             |

| MegaCore'             |                                               |                                                 | About       |

| Parameter<br>Settings |                                               |                                                 |             |

| Attributes            | Timing                                        |                                                 |             |

| Setup: 40             | Wait: 1                                       | 60 Hold: 40                                     | Units: ns 👻 |

|                       | eriod is 20.0 ns.<br>rity is in units of Ava  | alon clock period.                              |             |

|                       |                                               | te transfers: 40.0 ns                           |             |

|                       | ate time for read and<br>e for read and write | I write transfers: 160 ns<br>transfers: 40.0 ns |             |

|                       |                                               |                                                 |             |

Figure 13.Flash Memory Interface Configuration

The NIOS II CPU core is setup as shown below, notice that SDRAM is chosen.

| Select a Nios II core:                                                                       |                  |                                                                                                  |                                                                                                                                                               |

|----------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                              | ○Nios II/e       | ○Nios II/s                                                                                       | ●Nios II/f                                                                                                                                                    |

| Nios II<br>Selector Guide<br>Family: Cyclone II<br>f <sub>system:</sub> 50.0 MHz<br>cpuid: 0 | RISC<br>32-bit   | RISC<br>32-bit<br>Instruction Cache<br>Branch Prediction<br>Hardware Multiply<br>Hardware Divide | RISC<br>32-bit<br>Instruction Cache<br>Branch Prediction<br>Hardware Multiply<br>Hardware Divide<br>Barrel Shifter<br>Data Cache<br>Dynamic Branch Prediction |

| Performance at 50.0 MHz                                                                      | Up to 5 DMIPS    | Up to 25 DMIPS                                                                                   | Up to 51 DMIPS                                                                                                                                                |

| Logic Usage                                                                                  | 600-700 LEs      | 1200-1400 LEs                                                                                    | 1400-1800 LEs                                                                                                                                                 |

| Hardware Multiply: Embe                                                                      | dded Multipliers | <ul> <li>Hardware Divide</li> </ul>                                                              |                                                                                                                                                               |

| Reset Vector: Mem                                                                            | ory: sdram       | ▼ Offset: 0x0                                                                                    | 0×00800                                                                                                                                                       |

| Exception Vector: Memo                                                                       | ry: sdram        | ↓ Offset: 0x20                                                                                   | 0x008000                                                                                                                                                      |

Figure 14.NIOS II core overview

After we created all of the components of the system and added a system 50Mhz clock, we need to refresh the system and Auto-Assign Base Addresses for all of the components and then generate it.

| -11. 50                          |                           |              |

|----------------------------------|---------------------------|--------------|

| clk_50                           |                           |              |

| reset_n                          |                           |              |

|                                  |                           |              |

| in_port_to_the_pio_KEY[40]       |                           |              |

|                                  | Lo[3.]o]                  | • • •        |

| out_port_from_the_pio_LED0[30]   | <b>—</b> X                |              |

|                                  | L1[3.0]                   |              |

| out_port_from_the_pio_LED1[30]   | <b>—</b> X                |              |

|                                  | .L10[30]                  |              |

| out_port_from_the_pio_LED10[30]  |                           | . : :        |

|                                  | .L11[30]                  | . : :        |

| out_port_from_the_pio_LED11[30]  |                           | . : :        |

|                                  | L12[30]                   | . : :        |

| out_port_from_the_pio_LED12[30]  |                           | . : :        |

|                                  | L13[30]                   | . : :        |

| out_port_from_the_pio_LED13[30]  | X                         | . : :        |

|                                  | L14[3.0]                  | . : :        |

| out_port_from_the_pio_LED14[30]  |                           | . : :        |

|                                  | L16(30)                   | . : :        |

| out_port_from_the_pio_LED15[30]  |                           | . : :        |

|                                  | L16[30]                   | . : :        |

| out_port_from_the_pio_LED16[30]  |                           | . : :        |

|                                  | 14779 01                  | . : :        |

| out_port_from_the_pio_LED17[30]  | L17[30]                   | . : :        |

|                                  | L2[3.0]                   |              |

| out_port_from_the_pio_LED2[30]   |                           |              |

|                                  | L3[3.0]                   | . : :        |

| out_port_from_the_pio_LED3[30]   |                           | . : :        |

|                                  | .L4[30]                   | . : :        |

| out_port_from_the_pio_LED4[30]   |                           | . : :        |

|                                  | L5[3.0]                   | . : :        |

| out_port_from_the_pio_LED5[30]   |                           | . : :        |

|                                  | L6[3.0]                   | . : :        |

| out_port_from_the_pio_LED6[30]   | <b>— X</b>                |              |

|                                  | .L7[30]                   |              |

| out_port_from_the_pio_LED7[30]   | <b>—</b> X                |              |

|                                  | L8[3.0]                   |              |

| out_port_from_the_pio_LED8[30]   | <b>— — ×</b>              |              |

|                                  | L9[3.0]                   |              |

| out_port_from_the_pio_LED9[30]   | <b>— X</b>                |              |

|                                  |                           |              |

| zs_addr_from_the_sdram[110]      | DRAM_ADDR[110]            |              |

| zs_ba_from_the_sdram[10]         |                           | PIN_         |

| zs_cas_n_from_the_sdram -        |                           | PIN_         |

| zs_cke_from_the_sdram -          |                           | PIN_         |

| zs_cs_n_from_the_sdram -         |                           | PIN_         |

| zs_dq_to_and_from_the_sdram[150] |                           | PIN_         |

| zs_dqm_from_the_sdram[10]        | sdram_dpm[10]             | PIN_         |

| zs_ras_n_from_the_sdram -        |                           | PIN_         |

| zs_we_n_from_the_sdram -         |                           | PIN_         |

|                                  |                           | PIN_         |

| select_n_to_the_cfi_flash -      | PUTPUT FL_CE_N            | PIN          |

| tri_state_bridge_0_address[210]  | PUTPUT FL_ADDR[210]       | PIN_         |

| tri_state_bridge_0_data[70]      | = <u>RVIB</u> FL_DQ[70] [ | PIN_         |

| tri_state_bridge_0_readn -       |                           | PIN_         |

| tri_state_bridge_0_writen        |                           | PIN_<br>PIN_ |

Figure 15.SOPC module

The figure above is the quick look of the SOPC module. Since we only create a SDRAM controller in the SOPC, we have to connect the controller pins to the

input pins of the SDRAM embedded on the FPGA board. Followed by the controller pins of *SDRAM* is the flash controller pins. Just a reminder, the Flash Memory reset pin must connect to the reset pin or simply a constant 0.

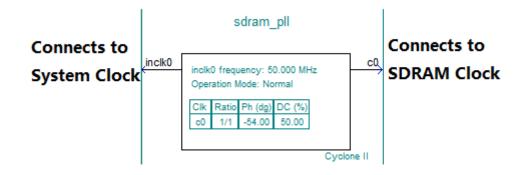

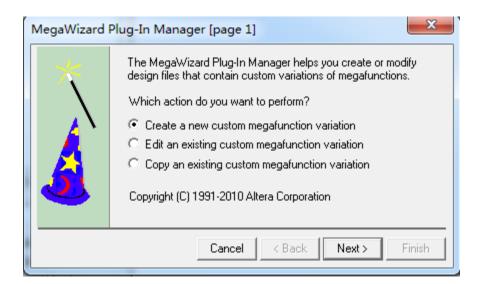

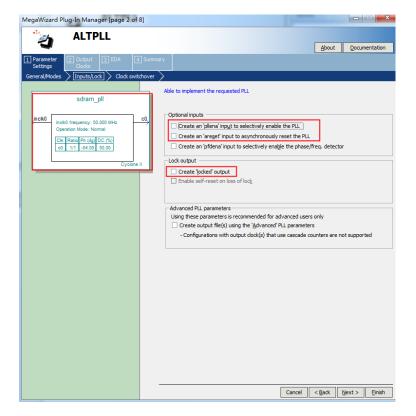

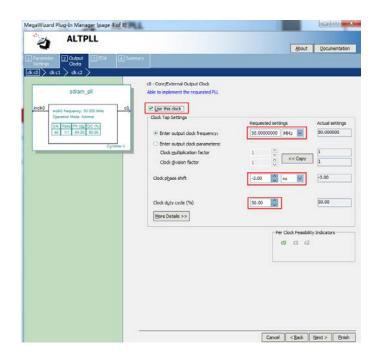

## 3. Clock source and Phase Lock Loop(PLL)

In order to make sure all the signals are stable on the clock edge, a Phase Lock Loop (PLL) module is needed to create a second clock signal into SDRAM. We should also consider the setup of the PLL module, since that may cause an error when building the project if some values are incorrect for each particular FPGA board. The setup for DE2 board, or Cyclone II EP2C35F672C6 FPGA chip, is shown below.

Figure 16.PLL module

# VII. Hardware Testing

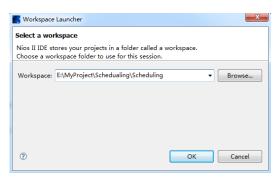

## 1. Example 1

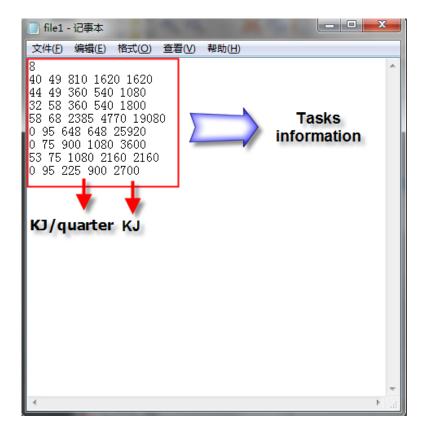

I would like to have two tests to demonstrate my work. First one is the example I analyzed in the part **Algorithm.** Assume there are 10 tasks and we are supposed to assign them in 7 hours. First, since we need to input our information into the FPGA board using txt format file, a Zip file named files.zip should be created under scheduling\_0\_syslib folder, including 2 txt format files named file1.txt and file2.txt storing the tasks information and hourly price information respectively. Due to the software work, the names of these files cannot be modified and the txt files cannot be compressed. See the following figure.

| file1.txt - 记事本     ロ     区       文件(F) 编辑(E) 编载(G) 查看(V) | ☐ file2.txt - 记事本     □     □     ☑       文件① 编辑(E) 裕式(Q) 查看(V) 帮助(H) |                | ng 🕨 scheduling_0_syslib 🕨              |                             | cheduling_0_syslib | <u>م</u> |

|-----------------------------------------------------------|-----------------------------------------------------------------------|----------------|-----------------------------------------|-----------------------------|--------------------|----------|

| 帮助(H)<br>10 个                                             | 1 1 2<br>1 1 2                                                        | 组织 ▼ □ 打开 計    | 打印 刻录 新建文件夹                             |                             | ≡ -                |          |

| 0 6 1 2 4<br>0 6 1 2 4                                    | 1 1 2<br>1 1 2                                                        | ★ 收藏夹          | 名称                                      | 修改日期                        | 类型                 | 大小       |

| 06124<br>06124                                            | 1 1 2 1 1 2                                                           | 🚺 下载           | 퉬 .settings                             | 2012/10/14 18:54            | 文件夹                |          |

| 0 6 1 2 4                                                 | 1 1 2                                                                 | 📃 桌面           | 퉬 Debug                                 | 2012/10/20 16:08            | 文件夹                |          |

| 0 6 1 2 4                                                 | 1 1 2<br>1 1 2                                                        | 📃 最近访问的位置      | 퉬 task_samples                          | 2012/10/17 23:17            | 文件夹                |          |

| 0 6 1 2 4<br>0 6 1 2 4                                    | 1 1 2                                                                 |                | cdtbuild                                | 2012/10/14 18:54            | CDTBUILD 文件        | 2 KB     |

| 0 6 1 2 4                                                 | 1 1 2                                                                 | 篇 库            | .cdtproject                             | 2012/10/20 16:17            | CDTPROJECT 文件      | 3 KB     |

| 0 6 1 2 4                                                 | 1 1 2<br>1 1 2                                                        |                | .project                                | 2012/10/14 18:54            | PROJECT 文件         | 3 KB     |

|                                                           | 1 1 2                                                                 |                | ile1.txt                                | 2012/10/22 16:27            | 文本文档               | 1 KB     |

|                                                           | 1 1 2                                                                 |                | file2.txt                               | 2012/10/22 16:27            | 文本文档               | 1 KB     |

|                                                           | 1 1 2<br>1 1 2                                                        | _              | 💞 files.zip                             | 2012/10/22 16:28            | 快压 ZIP 压缩文件        | 1 KB     |

|                                                           | 1 1 2                                                                 | 迅雷下载           | readme.txt                              | 2012/10/14 18:54            | 文本文档               | 2 KB     |

|                                                           | 1 1 2                                                                 |                | system.stf                              | 2012/10/14 19:05            | STF 文件             | 2 KB     |

|                                                           | 1 1 2<br>1 1 2<br>1 1 2<br>1 1 2<br>1 1 2<br>1 1 2                    | 🜏 家庭組          |                                         |                             |                    |          |

|                                                           | 112                                                                   | 🖳 计算机          |                                         |                             |                    |          |

|                                                           |                                                                       | 🚨 BOOTCAMP (C: |                                         |                             |                    |          |

|                                                           |                                                                       | 💿 DVD RW 驱动器   |                                         |                             |                    |          |

|                                                           |                                                                       | 🕞 学习工作 (E:)    |                                         |                             |                    |          |

|                                                           |                                                                       | Macintosh HD ( |                                         |                             |                    |          |

|                                                           |                                                                       | 游戏娱乐 (G:)      |                                         |                             |                    |          |

|                                                           |                                                                       | Apple iPhone   |                                         |                             |                    |          |

|                                                           |                                                                       |                |                                         |                             |                    |          |

|                                                           |                                                                       |                |                                         | ""<br>書日期: 2012/10/16 21:19 |                    | ,        |

|                                                           |                                                                       |                | 修成日期: 2012/10/22 16:27 回致<br>大小: 284 字节 | ≟口刑: 2012/10/16 21:19       |                    |          |

Figure 17.Input information of Example 1

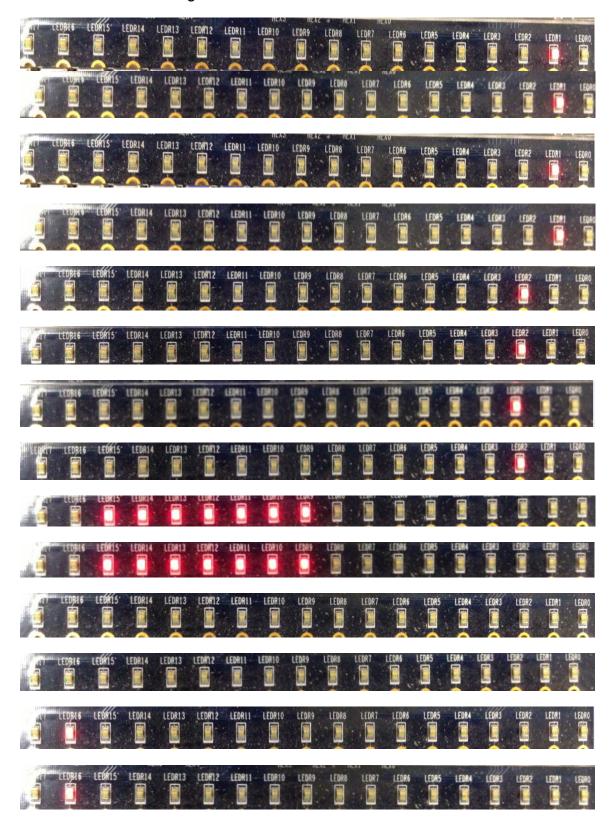

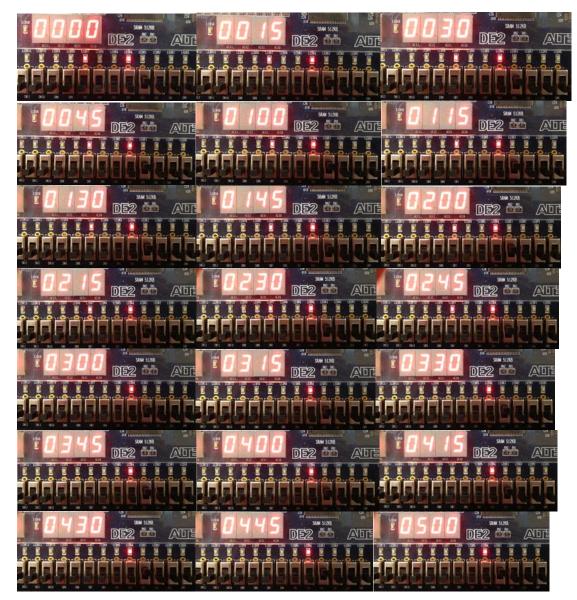

Then the result run in FPGA shows below from hour 0 to hour 6. We could see that the tasks with higher power level would be brighter.

Figure 18. Hourly power consumed of Example 1

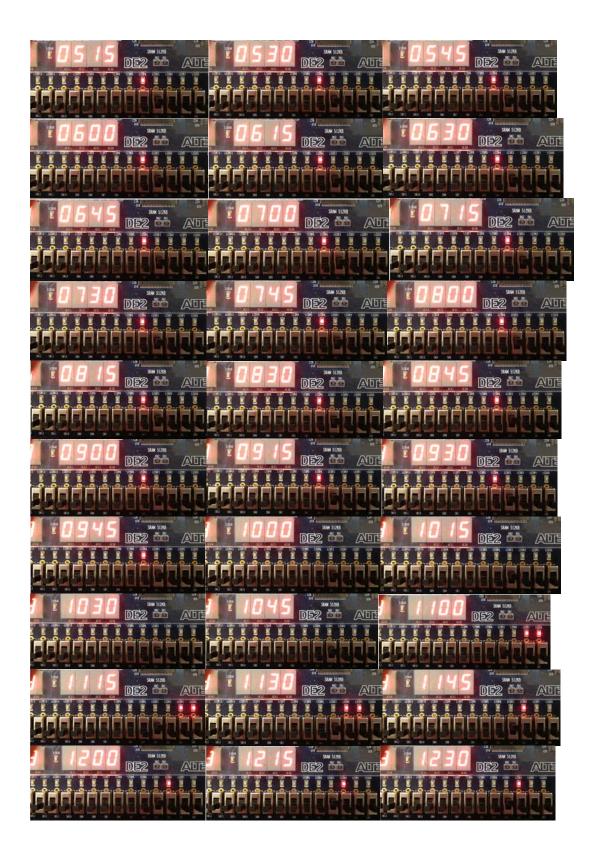

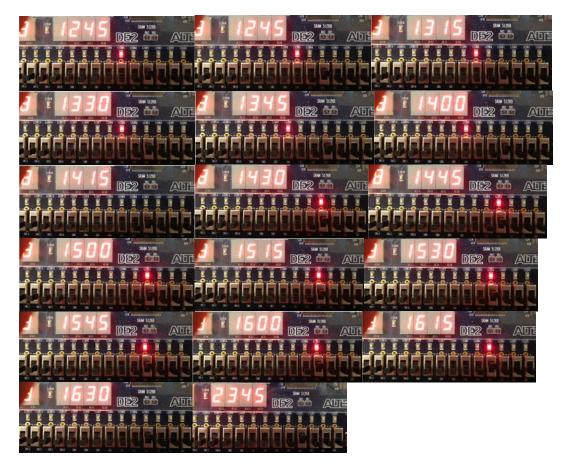

## 2. Example 2

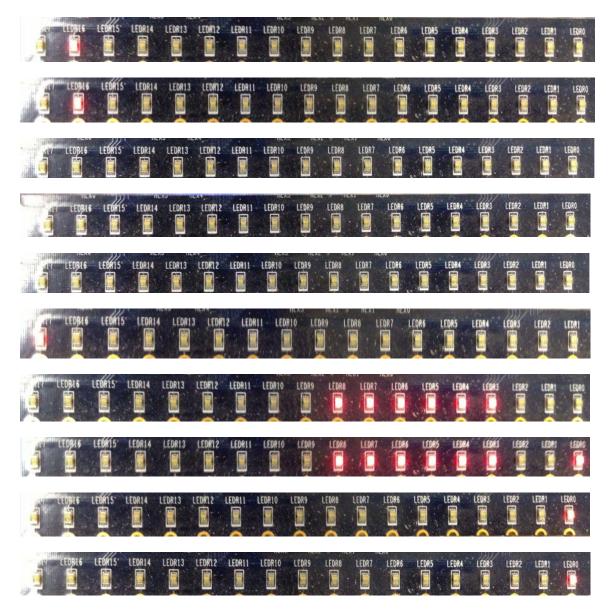

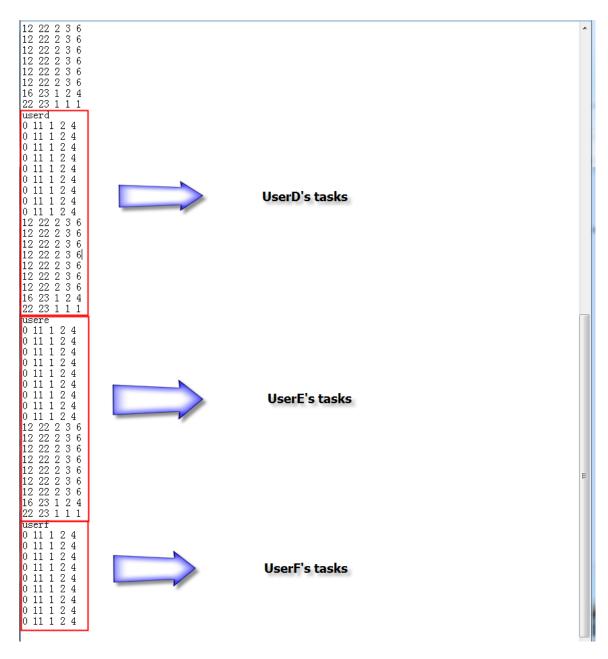

Another example is shown below

| □ file1.txt - 记事本 □ □                                       |                                                    |                    |

|-------------------------------------------------------------|----------------------------------------------------|--------------------|

| 文件(F) 编辑(E) 格式(O) 查看(V) 帮助(H) 文件(F) 编辑(E) 格式(O) 查看(V) 帮助(H) | C→ C→ C Schedualing → Scheduling → scheduling_0_sy | /slib ► 🔻 🍫 👔      |

| 18<br>0 11 1 2 4<br>1 1 2                                   |                                                    |                    |

| 0 11 1 2 4                                                  | 组织 ▼ 創打开 ▼ 打印 刻录 新建文件夹                             |                    |

| 0 11 1 2 4<br>0 11 1 2 4<br>1 1 2                           | 📕 🍌 下载 🔹 🔺 名称                                      | 修改日期 👂             |

|                                                             | 💻 桌面                                               | 2012/10/14 18:54 5 |

| 0 11 1 2 4 1 1 2                                            | 💹 最近访问的位置                                          | 2012/10/22 16:33 3 |

| 0 11 1 2 4<br>0 11 1 2 4<br>1 1 2                           | task samples                                       | 2012/10/22 16:46 3 |

| 0 11 1 2 4 1 1 2                                            | 篇cdtbuild                                          | 2012/10/14 18:54 C |

| 12 22 2 3 6 1 1 2                                           | N版 .cdtproject                                     | 2012/10/22 16:34 C |

| 12 22 2 3 6<br>12 22 2 3 6<br>1 1 2                         | ■ 图片                                               | 2012/10/14 18:54 P |

| 12 22 2 3 6 1 1 2                                           | 🖹 文档 📄 file1.txt                                   | 2012/10/17 22:55 3 |

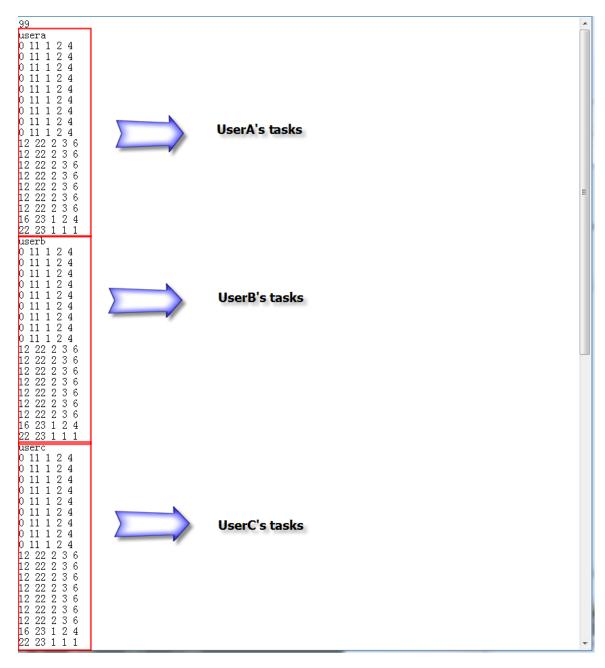

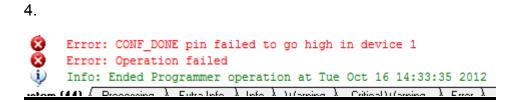

| 12 22 2 3 6<br>12 22 2 3 6<br>1 1 2                         | □ 迅雷下载                                             | 2012/10/16 22:47 🕇 |