Michigan Technological University

Create the Future Digital Commons @ Michigan Tech

Dissertations, Master's Theses and Master's Reports - Open

Dissertations, Master's Theses and Master's Reports

2009

# Development of room temperature operating single electron transistor using FIB etching and deposition technology

Manoranjan Acharya Michigan Technological University

Follow this and additional works at: https://digitalcommons.mtu.edu/etds

Part of the Electrical and Computer Engineering Commons Copyright 2009 Manoranjan Acharya

#### **Recommended Citation**

Acharya, Manoranjan, "Development of room temperature operating single electron transistor using FIB etching and deposition technology", Dissertation, Michigan Technological University, 2009. https://digitalcommons.mtu.edu/etds/69

Follow this and additional works at: https://digitalcommons.mtu.edu/etds Part of the <u>Electrical and Computer Engineering Commons</u>

### Development of Room Temperature Operating Single Electron Transistor Using FIB Etching and Deposition Technology

By

### MANORANJAN ACHARYA

#### A DISSERTATION

Submitted in partial fulfillment of the requirements

for the degree of

### DOCTOR OF PHILOSOPHY

(Electrical Engineering)

MICHIGAN TECHNOLOGICAL UNIVERSITY 2009

© 2009 Manoranjan Acharya

This dissertation, "Development of Room Temperature Operating Single Electron Transistor Using FIB Etching and Deposition Technology", is hereby approved in partial fulfillment of the requirements for the degree of DOCTOR OF PHILOSOPHY in the field of Electrical Engineering.

DEPARTMENT: Electrical and Computer Engineering

Signatures: Dissertation Advisor

Dr. Paul L. Bergstrom

Department Chair\_\_\_\_\_

Dr. Daniel R. Fuhrmann

Date

### Dedicated to

My grandmother Nishamani

### Acknowledgement

There are many supporting hands behind this work, without which, this work could not have been completed. I would like to express my deepest gratitude to all of them. My sincere thanks to my advisor, Dr. Paul L. Bergstrom, for his guidance and advice throughout this project and my study at Michigan Technological University (MTU). I am thankful to my committee members, Drs. Warren Perger, Yoke Khin Yap, and John A. Jaszczak, for sharing their technical insights and shaping my dissertation. Thanks to Mr. Owen Mills and the entire ACMAL team at MTU for their help in teaching and using FIB and FESEM systems. I thank to the staff in the ECE department, Mr. Michael Chase, Mr. John Miller, and Mr. Mark Kilpela, for their assistance in equipment setup. Special thanks to the director Microfabrication facility at MTU, Mr. William Knudsen, for his continuous support in experimental design, laboratory setup, and sample preparation.

I would also like to appreciate the help from the fellow graduate students and postdocs in Dr. Bergstrom's research group for their valuable inputs in preparing this document. Special thanks to Dr. Santosh Karre and Mr. Dawdon Cheam for their help and discussion during the experimental work. Thanks to Mr. Douglas Banyai for his help in Matlab coding and device modeling.

Manoranjan Acharya

Date

### ABSTRACT

The single-electron transistor (SET) is one of the best candidates for future nano electronic circuits because of its ultralow power consumption, small size and unique functionality. SET devices operate on the principle of Coulomb blockade, which is more prominent at dimensions of a few nano meters. Typically, the SET device consists of two capacitively coupled ultra small tunnel junctions with a nano island between them. In order to observe the Coulomb blockade effects in a SET device the charging energy of the device has to be greater that the thermal energy. This condition limits the operation of most of the existing SET devices to cryogenic temperatures. Room temperature operation of SET devices requires sub-10nm nano-islands due to the inverse dependence of charging energy on the radius of the conducting nano-island. Fabrication of sub-10nm structures using lithography processes is still a technological challenge. In the present investigation, Focused Ion Beam based etch and deposition technology is used to fabricate single electron transistors devices operating at room temperature. The SET device incorporates an array of tungsten nano-islands with an average diameter of 8nm. The fabricated devices are characterized at room temperature and clear Coulomb blockade and Coulomb oscillations are observed. An improvement in the resolution limitation of the FIB etching process is demonstrated by optimizing the thickness of the active layer. SET devices with structural and topological variation are developed to explore their impact on the behavior of the device. The threshold voltage of the device was minimized to  $\sim$ 500mV by minimizing the source-drain gap of the device to 17nm. Vertical source and drain terminals are fabricated to realize single-dot based SET device. A unique process flow is developed to fabricate Si dot based SET devices for better gate controllability in the device characteristic. The device

parameters of the fabricated devices are extracted by using a conductance model. Finally, characteristic of these devices are validated with the simulated data from theoretical modeling.

# **Table of Contents**

| Acknowledgement                                                                | iv  |

|--------------------------------------------------------------------------------|-----|

| ABSTRACT                                                                       | v   |

| List of Figures                                                                | ix  |

| List of Tables                                                                 | xiv |

| Chapter 1: Introduction                                                        | 1   |

| 1.1. Background                                                                | 1   |

| 1.2. CMOS Scaling: Issues and Probable Solutions                               | 3   |

| 1.3. Single Electron Devices: A Successor of CMOS                              | 7   |

| 1.4. Research Objectives                                                       |     |

| 1.5. Dissertation Outline                                                      |     |

| Chapter 2: Theory of Single Electron Transistors and Device Design             |     |

| 2.1. Theory of Operation                                                       |     |

| 2.2. Single Dot and Multi Dot SETs                                             |     |

| 2.3 Evolution in Technologies for SETs                                         |     |

| 2.4. Modeling the V-I current characteristic of a Single Electron Transistor   | 30  |

| 2.5. Design of Single Electron Transistor Device                               |     |

| Chapter 3: Fabrication of Single Electron Transistor                           | 46  |

| 3.1. Focused Ion Beam Technology                                               |     |

| 3.2. Material Deposition and Fabrication of Nano-islands by FIB                | 64  |

| 3.3. Fabrication of Tunnel Junction for RT-SET                                 | 72  |

| 3.4. Process Integration                                                       | 74  |

| Chapter 4: Device Characterization                                             | 109 |

| 4.1. Experimental Set-Up for Device Characterization                           | 109 |

| 4.2. Room Temperature Characterization of the FIB Etch Deposition based SET: . | 114 |

| 4.3. Characterization of Vertical SET devices:                                 | 122 |

| 4.4. SET with Silicon Quantum Dots:                                            | 125 |

| Chapter 5: Analysis and Discussion                                             | 130 |

| 5.1. Extraction of Device Parameters                                           | 130 |

| 5.2. Impact of Structural Variation on the Device Behavior                     | 133 |

| 5.3 Impact of Topological Variation on the Device Behavior                     | 141 |

| 5.4: Impact of additional Non-participating dots                               | 149 |

| 5.5: Impact of Material Properties:                                            | 155 |

|                                                                                |     |

| 5.6. Multiple Peaks and Non-periodicity in the Coulomb Oscillation: | 159 |

|---------------------------------------------------------------------|-----|

| 5.7. Model Verification                                             | 161 |

| Chapter 6: Conclusion                                               | 170 |

| Chapter 7: Future Work                                              | 173 |

| Chapter 8: Appendix                                                 | 175 |

| 8.1. Fabrication Process Parameters                                 | 175 |

| 8.2 Code for Simulation                                             | 177 |

| References                                                          | 188 |

# **List of Figures**

| Fig. 1: The increasing rate of the transistors per chip [Source: www.intel.com]                               |

|---------------------------------------------------------------------------------------------------------------|

| Fig. 2.1: Charging of a metallic sphere with no-charge and charged state15                                    |

| Fig. 2.3: V-I characteristic of a SET device. Where C1, C2, and R1, R2 represents the junction                |

| capacitances and resistances respectively for the two junctions in the SET respectively. $Q_0$                |

| represents the gate voltage induced charge.[Reprinted with permission from K.K. Likharev,                     |

| Proceedings of the IEEE, Vol 87 (4), 1999]                                                                    |

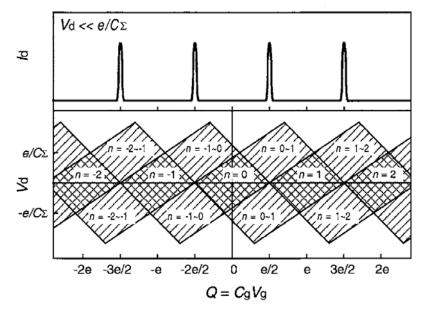

| Fig. 2.4: Coulomb Oscillation and stability diagram of a SET. $V_{\rm d}$ represents the source-drain voltage |

| and $C_{\Sigma}$ is the effective capacitance of the device. [Reprinted with permission from the publisher    |

| of Ref-41]                                                                                                    |

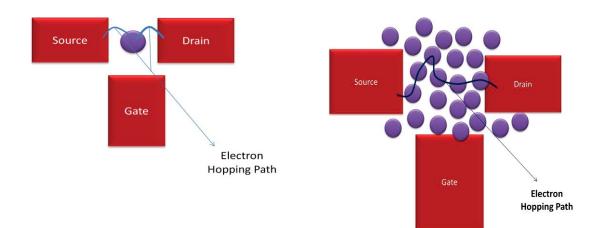

| Fig.2. 5: A pictorial view of (Left) Single dot based and (Right) Multi-Dot Based SET devices with            |

| possible path of electron transport22                                                                         |

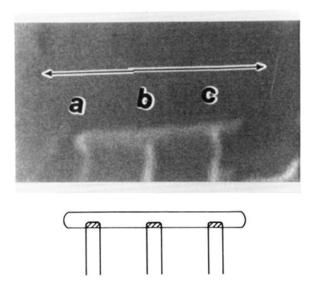

| Fig. 2.6: SEM image of the first fabricated SET by Fulton and Dolan. The junctions labeled as a, b            |

| and c are formed where the vertical electrodes overlap the contact, the longer horizontal central             |

| electrode. [Reprinted with permission from T. Fulton and G. Dolan, Phy. Rev. Lett, Vol. 59,                   |

| p109 (1987)]23                                                                                                |

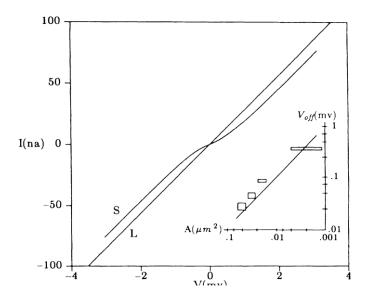

| Fig 2.7: The V-I characteristic of the SET device fabricated by Fulton and Dalon. [Reprinted with             |

| permission from T. Fulton and G. Dolan, Phy. Rev. Lett, Vol. 59, p109 (1987)]24                               |

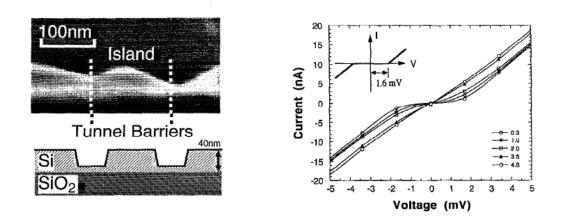

| Fig 2.8: SEM image of a 100nm diameter island on a SOI wire as fabricated by Ali et al. and (Right)           |

| the V-I characteristic of the device fabricated using this island. [Reprinted with permission from            |

| D.Ali and H. Ahmed, Appl. Phys. Lett, Vol.64, p2119, (1994)]25                                                |

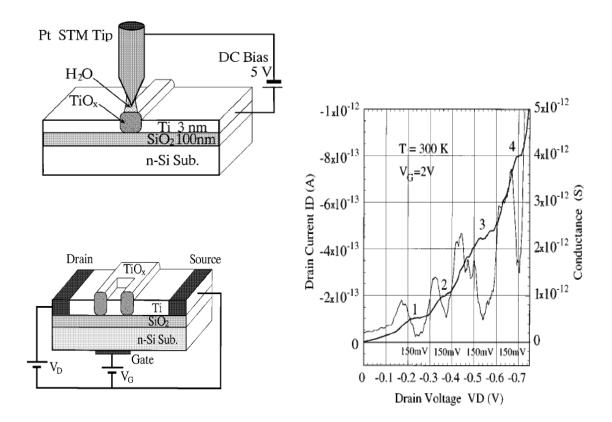

| Fig 2.9: The room temperature SET fabricated by STM tip by Matsumoto et al. (left top) Principle of           |

| STM nano-oxidation process using STM tip as cathode.(left bottom) Cross-sectional view of                     |

| single electron transistor fabricated by STM nano-oxidation process.(right) Drain current-                    |

| voltage characteristics ~thick line and conductance (fine line) of SET at room temperature.                   |

| Gate bias is set to 2 V. [Reprinted with permission from K. Matsumoto, M. Ishii, K. Segawa, Y.                |

| Oka, B. J. Vartanian and J. S. Harris, Appl. Phys. Lett, Vol. 68, p1,(1996)]27                                |

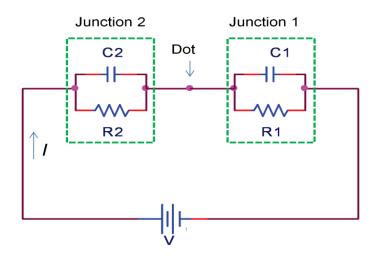

| Fig. 2.10: Two junction representation of a single dot SET system. The gate terminal is not shown. 32         |

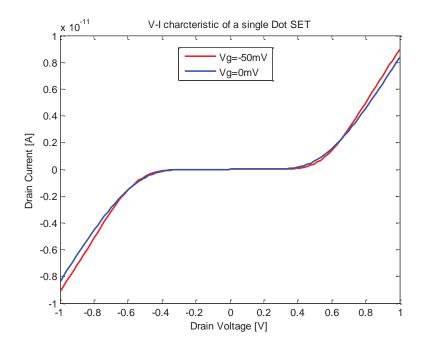

| Fig. 2.11: Simulated V-I characteristic for a double junction SET device using master equation model.         |

| The parameters for the simulation is input from Table2.1                                                      |

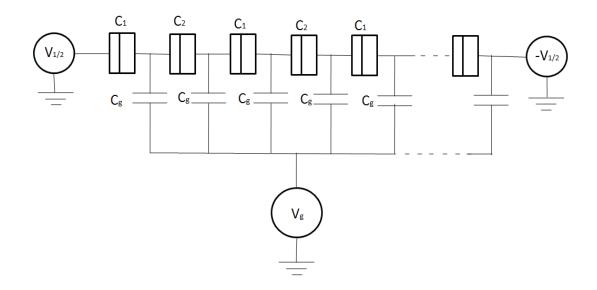

| Fig. 2.12: Modeling the multi dot SET with an array of tunnel junctions of capacitance C1 and C2 $$    |

|--------------------------------------------------------------------------------------------------------|

| biased by a voltage V. The gate coupling can be represented by the gate voltage Vg and gate            |

| capacitances Cg for each dot                                                                           |

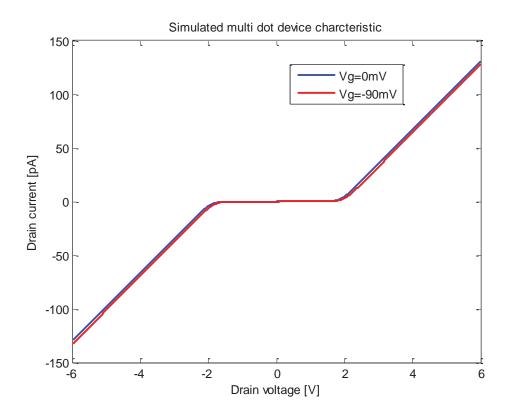

| Fig. 2.13: Simulated V-I characteristic of a multi dot SET device with 10 junctions in the dominant    |

| conducting path (DCP)                                                                                  |

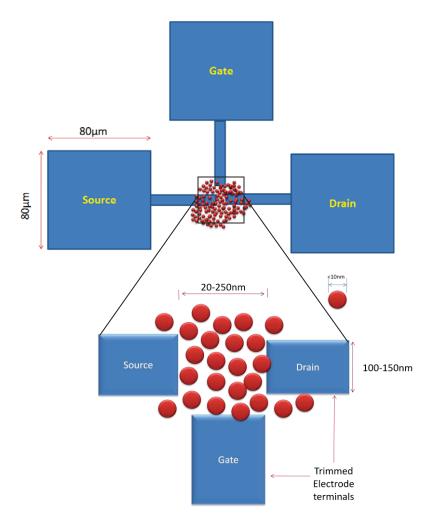

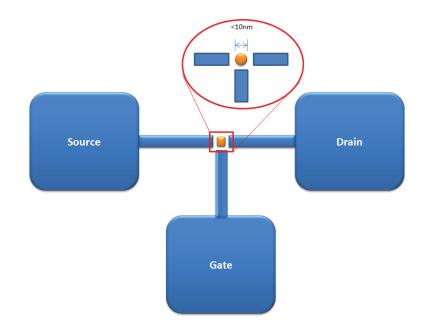

| Fig. 2.14: Design of the investigated SET device                                                       |

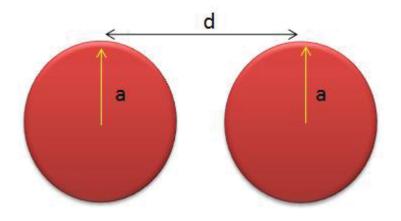

| Fig.2.15: Schematic for computation of the capacitance between two neighboring islands in the active   |

| area of the SET device                                                                                 |

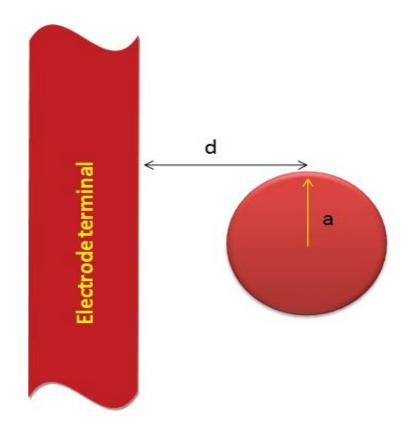

| Fig. 2.16: Schematic for computation of the capacitance between island and the electrode terminals 44  |

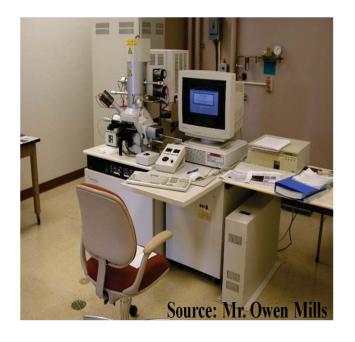

| Fig. 3.1: (Left) Hitachi FB-200A FIB system.(Right) The Schematic diagram of FIB Column[ The           |

| right image is reprinted with permission from S. Reyntjens and R. Puers, J. Micromech.                 |

| Microeng Vol. 11 p287 (2001)]                                                                          |

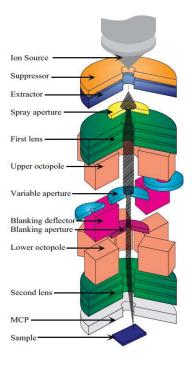

| Fig. 3.2: The basic principle of FIB operation (a) Imaging (b) Etching (c) Deposition                  |

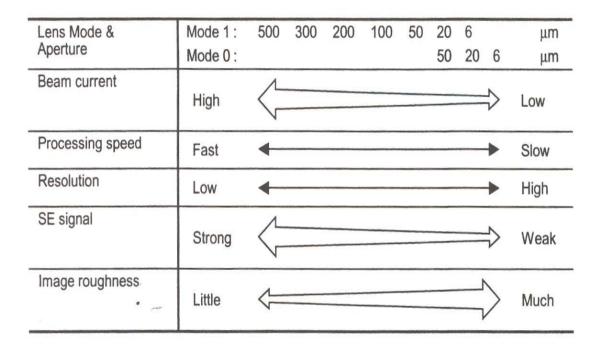

| Fig. 3.3: The variation in the beam parameters and capabilities for different beams in the Hitachi FB- |

| 2000A FIB System                                                                                       |

| Fig. 3.4: Schematic diagram of the proposed Single dot based SET by FIB direct writing technique 56    |

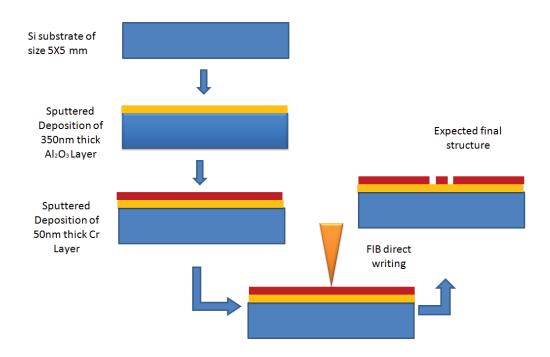

| Fig. 3.5: Process Flow for fabricating the nano structure for a single dot based SET by FIB direct     |

| writing technique                                                                                      |

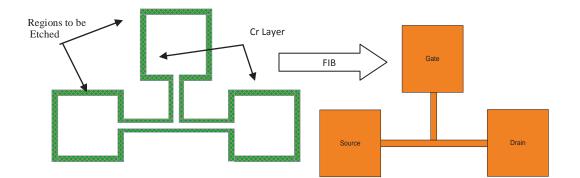

| Fig. 3.6: Pictorial view of (Left) generated pattern for Pads and Electrodes fabrication. (Right)      |

| Expected Pads and electrodes before the gap formation                                                  |

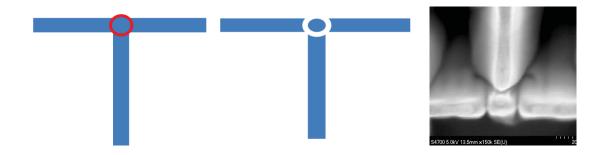

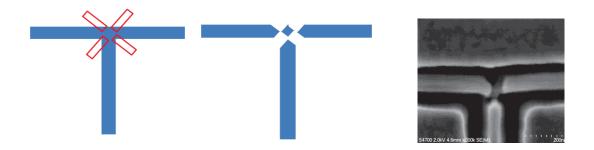

| Fig. 3.7(a): Old layout (developed by Karre et al [69]) with the SEM image of the minimum structure    |

| possible                                                                                               |

| Fig. 3.7(b): New layout with the SEM image of the obtained nano structure                              |

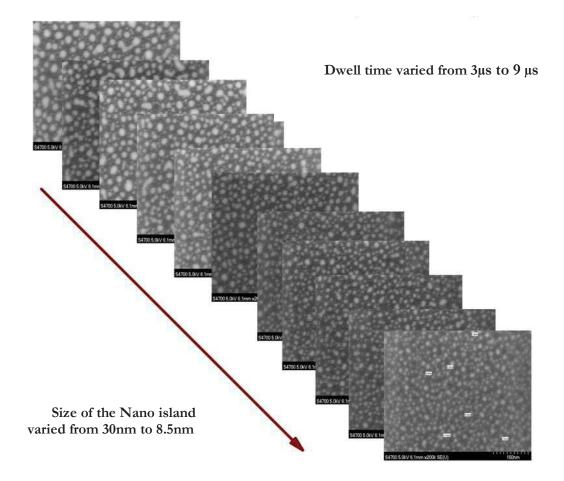

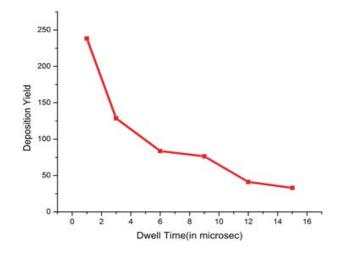

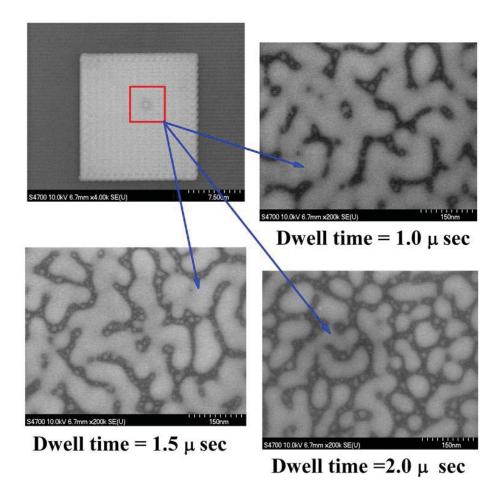

| Fig. 3.8: Variation of deposited nano-island size with increase in dwell time of MI200 beam            |

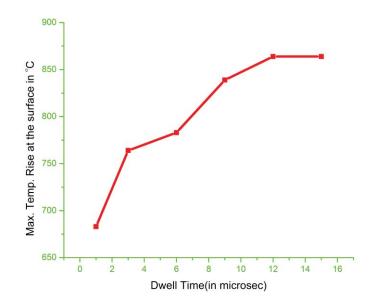

| [Reprinted with permission from P. S. Karre, PhD Dissertation, MTU, 2008]67                            |

| Fig. 3.9: Increase in surface temperature with respect to the dwell time during FIB deposition process |

|                                                                                                        |

| Fig. 3.10: Variation of deposition yield with respect to dwell time as obtained from the FEA based     |

| calculation71                                                                                          |

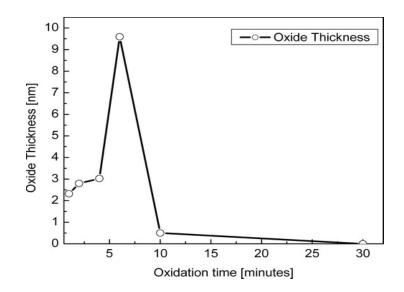

| Fig. 3.11: Thickness of the tungsten oxide with respect to the oxidation time [Reprinted with          |

| permission from P. S. Karre, PhD Dissertation, MTU, 2008]74                                            |

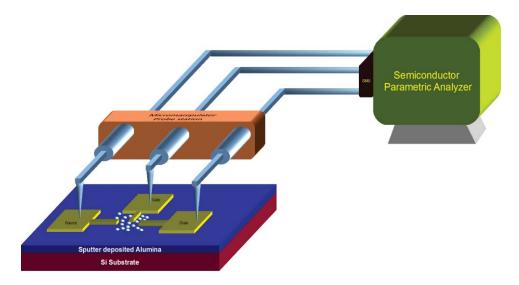

| Fig. 3.12: Process flow for FIB etch deposition based RT-SET fabricationError! Bookmark not            |

| defined.                                                                                               |

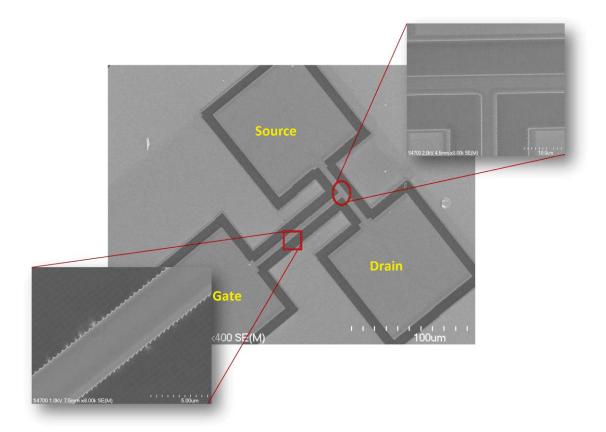

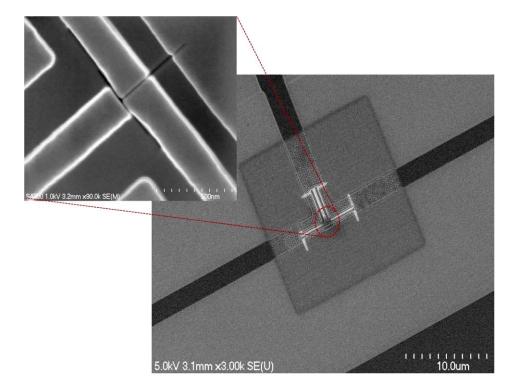

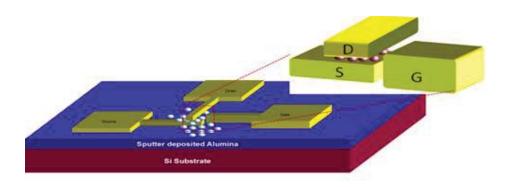

| Fig. 3.13: Scanning electron micrograph of the micro-pads and electrodes. The top inset shows the    |

|------------------------------------------------------------------------------------------------------|

| magnified view of the active area before electrode trimming. The bottom inset shows the              |

| magnified view of an electrode78                                                                     |

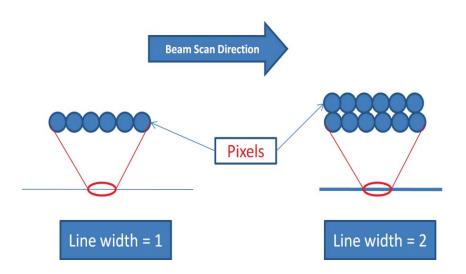

| Fig. 3.14: Illustration of pattern line width and the pixel arrangement                              |

| Fig. 3.15: Scanning Electron Microscope image of the inter electrode nano gap for the targeted RT-   |

| SET (Before The process optimization)82                                                              |

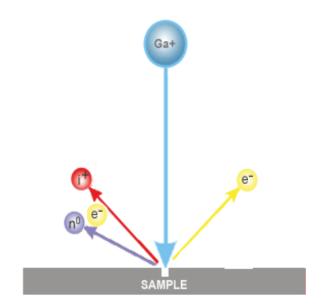

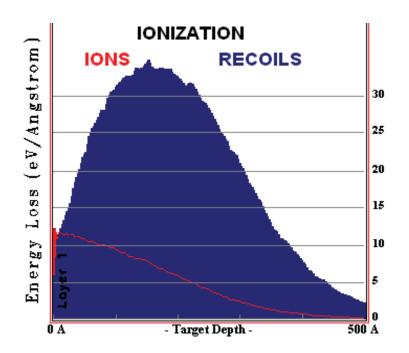

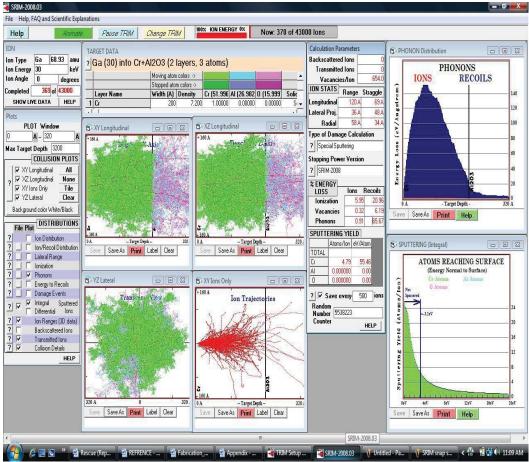

| Fig. 3.16: Pictorial view of ion-solid interaction                                                   |

| Fig. 3.17: Dissipation of ion energy for different events in sample surface                          |

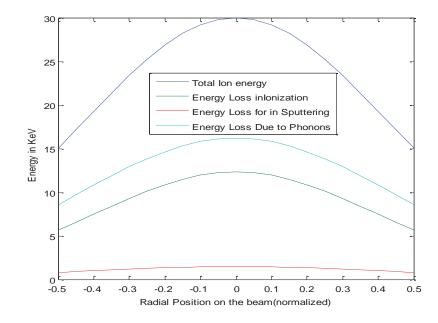

| Fig. 3.18: Trajectories of the displaced atoms (Left) and the incident ions (Right)                  |

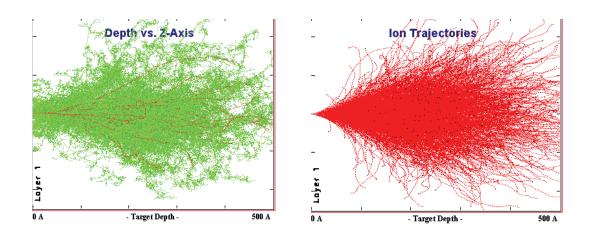

| Fig. 3.19: Distribution of the phonon energy beneath the sample surface                              |

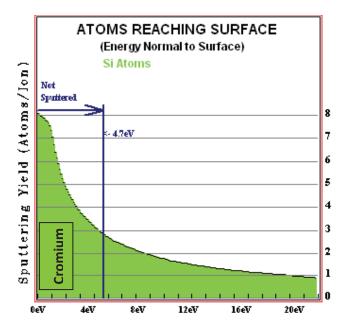

| Fig. 3.20: Distribution of moving atoms reaching at the surface. The atoms having energy more than   |

| the surface binding energy will be sputtered out                                                     |

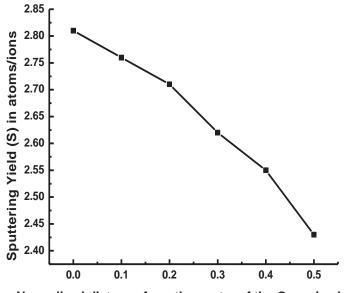

| Fig. 3.21: Variation of the sputtering yield with respect to the position in beam profile            |

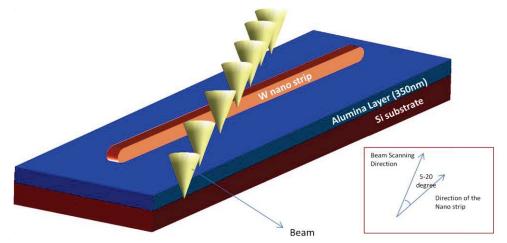

| Fig. 3.22: Pictorial view of the experimental set-up to study the beam profile dependency in the FIB |

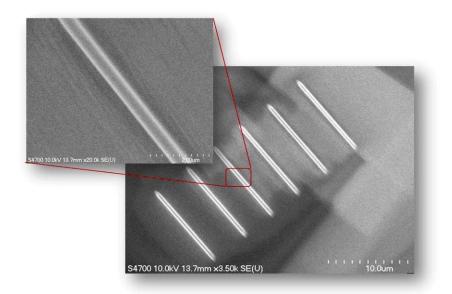

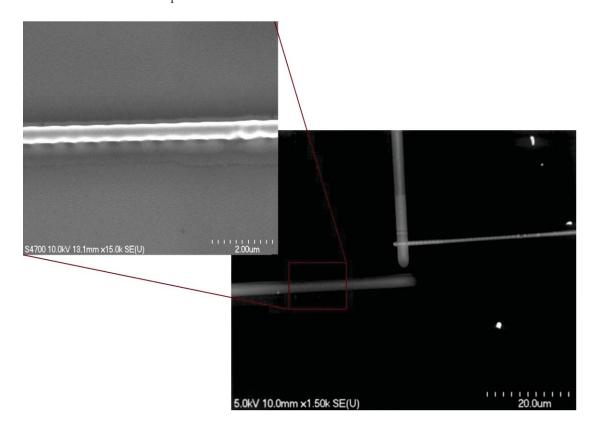

| etching process                                                                                      |

| Fig. 3.23: SEM image of the Tungsten Nano strip deposited by FIB deposition process (at different    |

| magnification)                                                                                       |

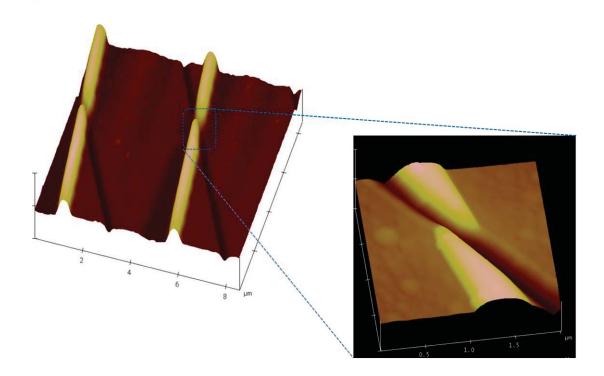

| Fig.3.24: AFM image of W nano strips at different magnification, after being etched by FIB in an     |

| oblique direction                                                                                    |

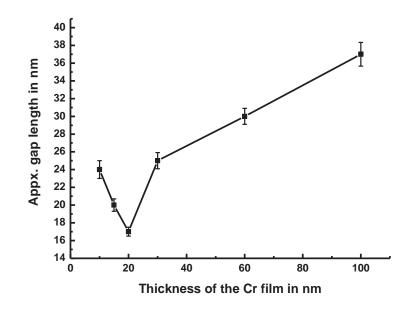

| Fig. 3.25: SEM images (the s are not in the same scale) of the inter electrode gaps fabricated in Cr |

| films of different thickness (a)100nm,(b)50nm,(c)20nm,(d)15nm95                                      |

| Fig. 3.26: Experimental inter-electrode gap length                                                   |

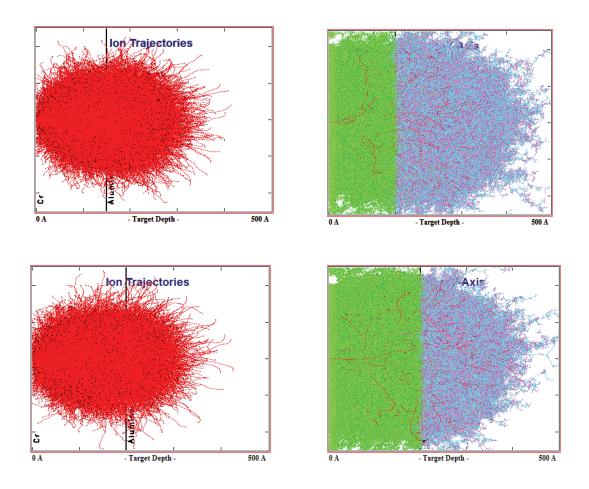

| Fig. 3.27: Ion and displaced atom trajectories and collision cascades for Cr film of (top) 15nm and  |

| (bottom) 20nm over 350nm thick Alumina film as obtained from the TRIM model                          |

| Fig. 3.28: The SEM micrograph of a Sub-20nm source-drain gap based SET. The inset shows the          |

| electrode terminals and the nano gap before the dot deposition                                       |

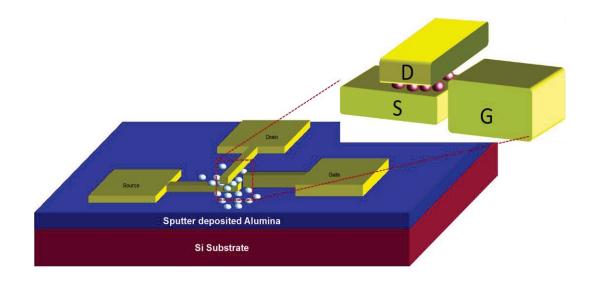

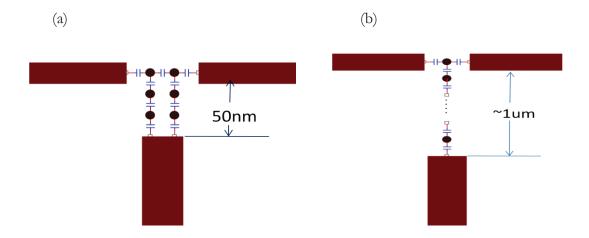

| Fig. 3.29: Pictorial view of the device configuration for a vertical SET                             |

| Fig. 3.30: SEM image of a vertical device. The extended figure shows the magnified view of an FIB    |

| deposited electrode102                                                                               |

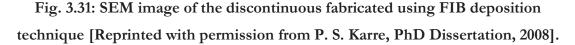

| Fig. 3.31: SEM image of the discontinuous fabricated using FIB deposition technique [Reprinted       |

| with permission from P. S. Karre, PhD Dissertation, 2008]106                                         |

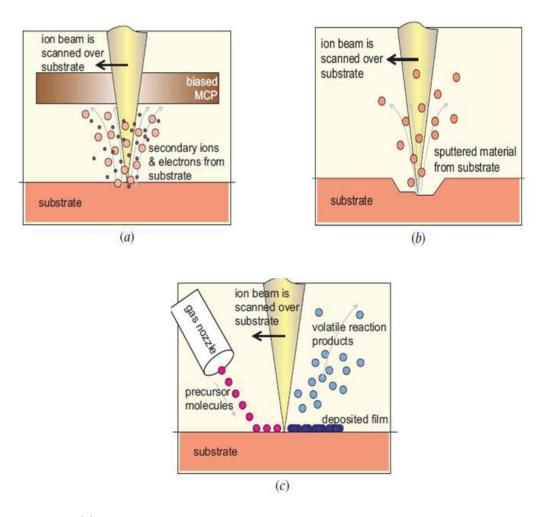

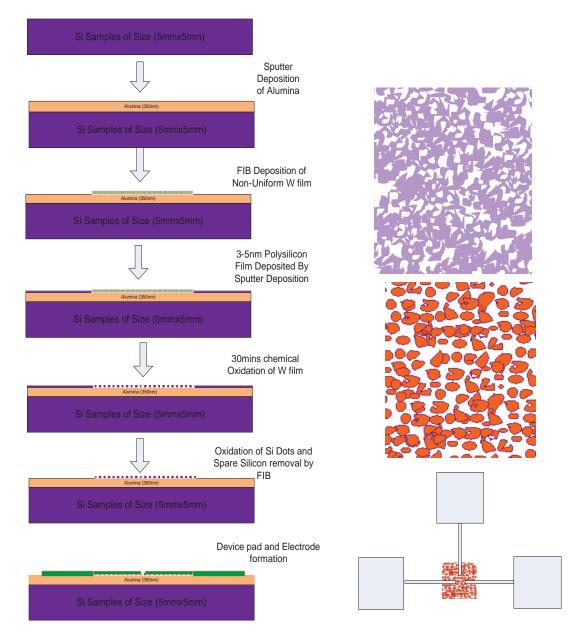

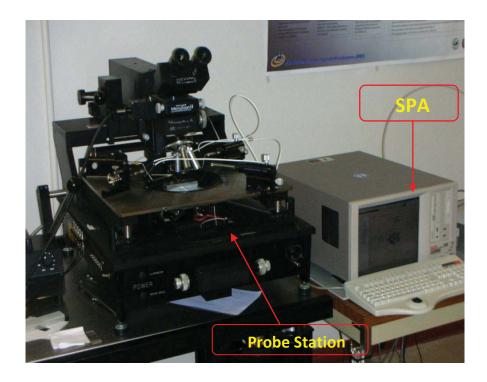

| Fig. 4.1: A pictorial view of the measurement set-up for characterizing the SET devices              |

| Fig. 4.2: Digital picture of the measurement set-up used for characterizing the SET devices          |

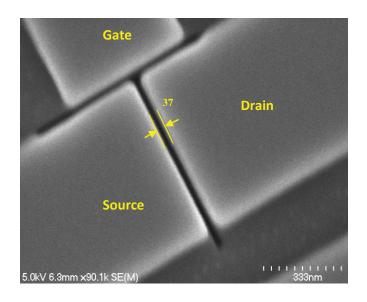

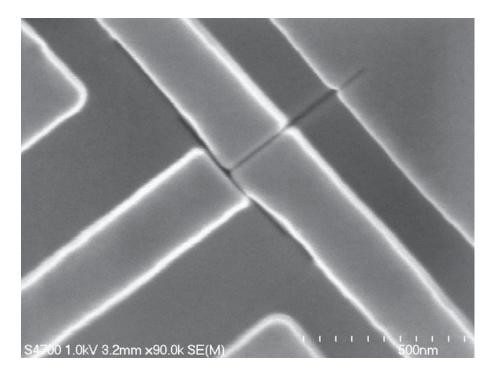

| Fig. 4.3 SEM image of the nano structure for the SET with 17nm Source-drain gap116                     |

|--------------------------------------------------------------------------------------------------------|

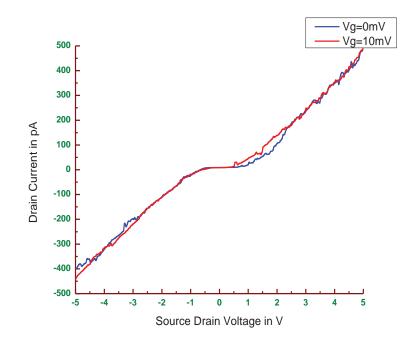

| Fig. 4.4: Coulomb blockade characteristic of a 17nm source-drain gap based SET device                  |

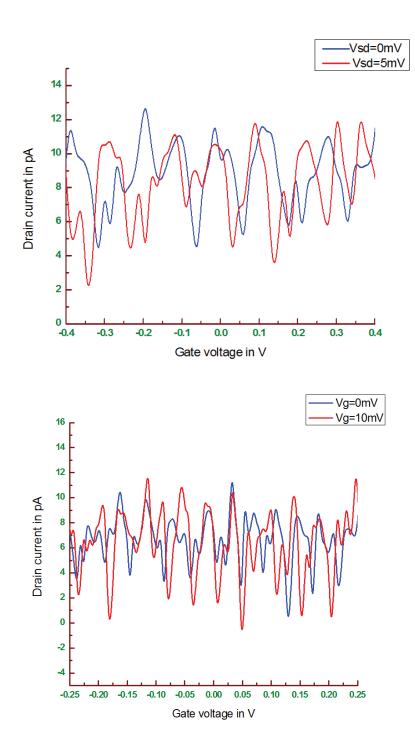

| Fig. 4.5: Coulomb oscillation for a device with 17nm source-drain gap                                  |

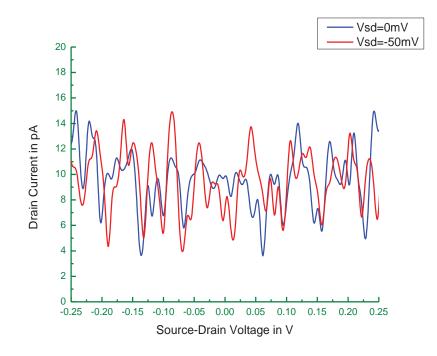

| Fig. 4.6: Coulomb blockade characteristic of SET devices with different source to drain gap (a) S-D    |

| gap=35nm (b) S-D gap=150nm                                                                             |

| Fig. 4.7: Coulomb oscillation characteristic of FIB etch deposition based SET device with (a) 35nm     |

| source-drain gap and (b) 150nm source-drain gap121                                                     |

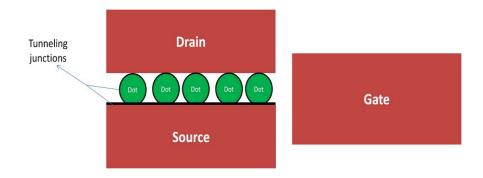

| Fig. 4.8: Configuration of a Vertical SET device                                                       |

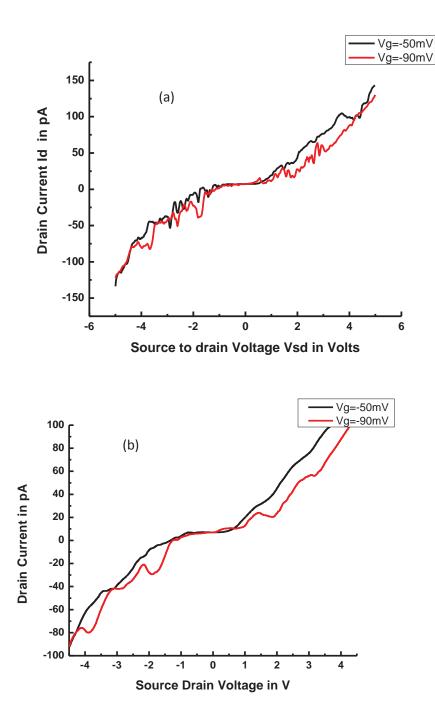

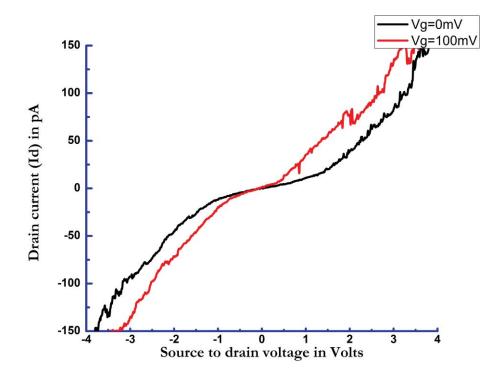

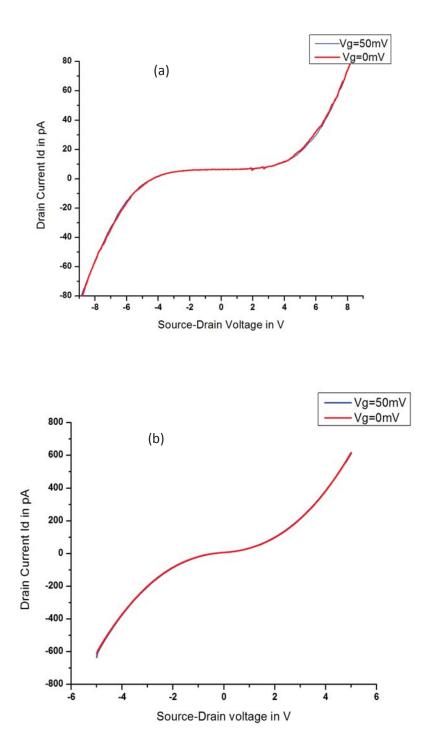

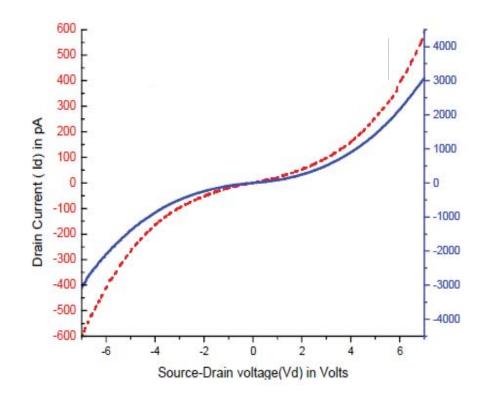

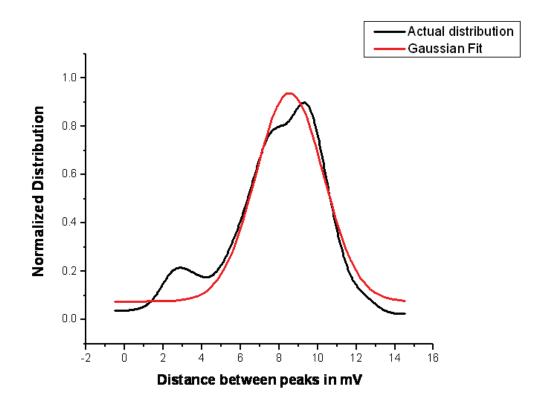

| Fig. 4.9: Source-drain V-I characteristic of a Vertical SET device for two different gate voltages (a) |

| Original Data (b) Smoothen by averaging 30adjacent points                                              |

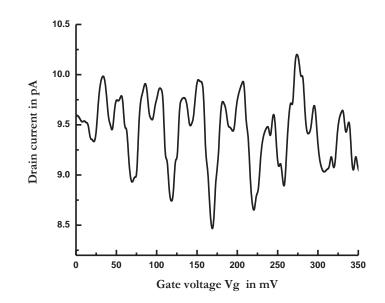

| Fig. 4.10: Coulomb oscillation for a vertical SET device                                               |

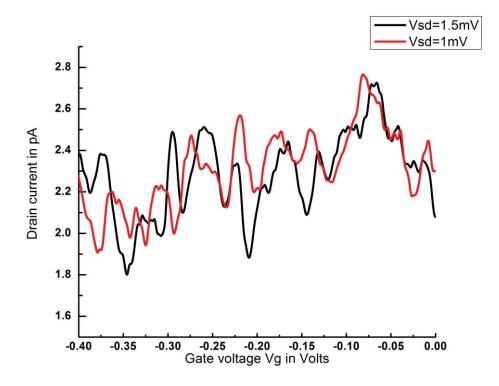

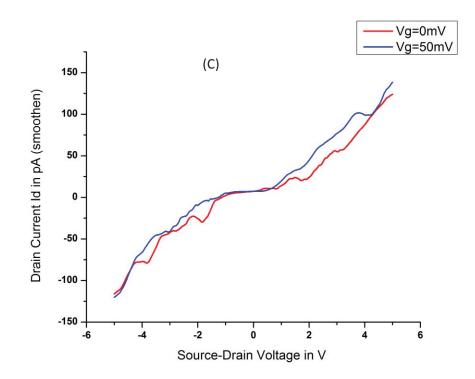

| Fig. 4.11: V-I characteristic of a Si quantum dot based SET device at room temperature                 |

| Fig. 4.12: Coulomb oscillation for a Si dot based SET                                                  |

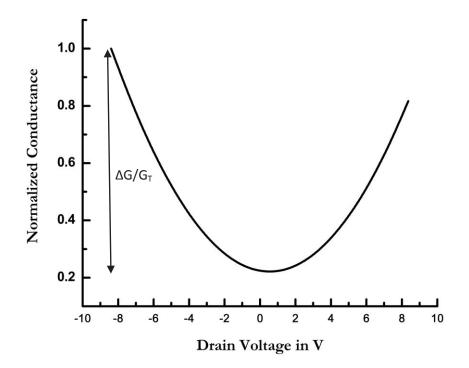

| Fig. 5.1: Normalized conductance with respect to drain voltage                                         |

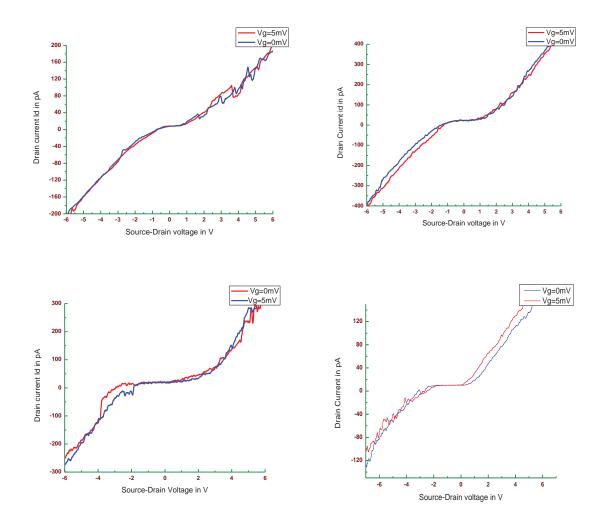

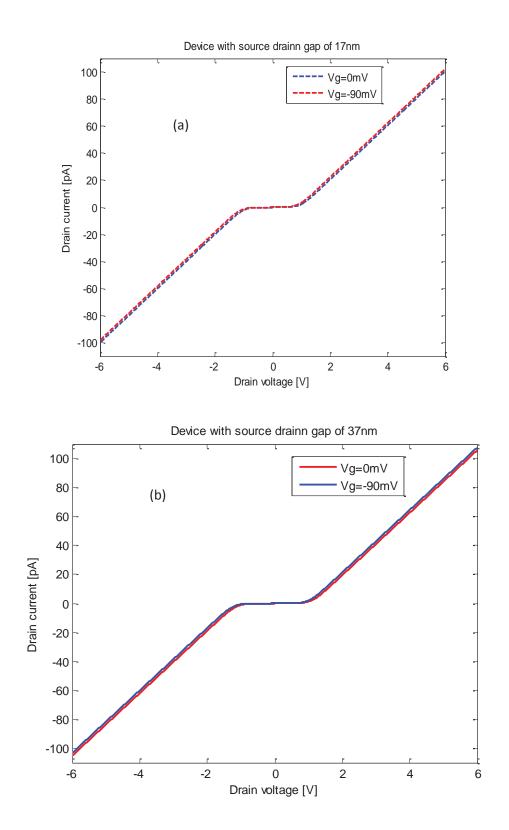

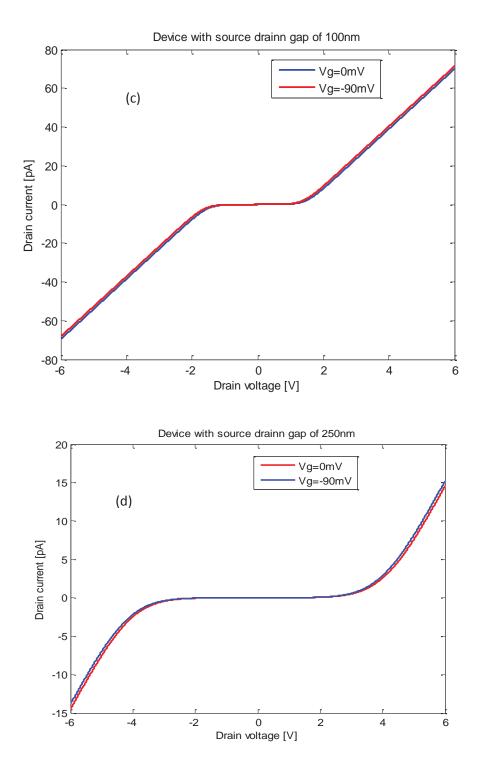

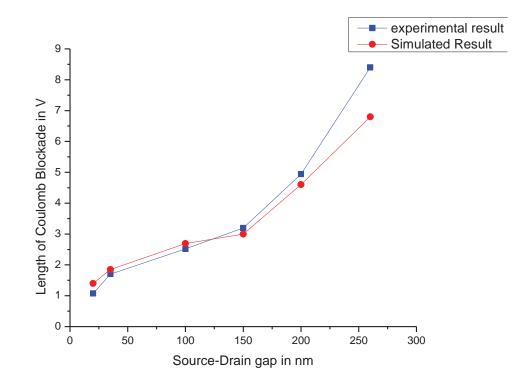

| Fig. 5.2: Room temperature V-I characteristic of the SET devices with different source drain gaps      |

| (top left) ~20nm (top right) ~37nm (bottom left) ~50nm (bottom right) 150nm. The electrode             |

| width and the gate gap for all the devices are kept constant as 100nm and 50nm respectively.135        |

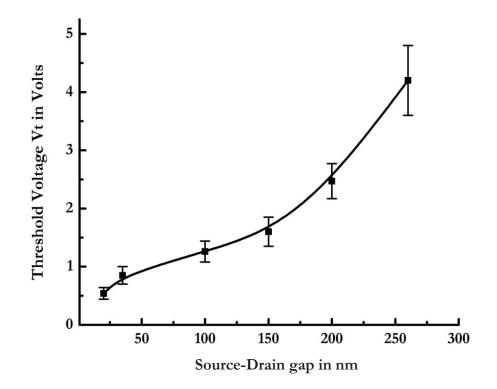

| Fig. 5.3: Variation of the Threshold voltage with respect to the Source-Drain gaps                     |

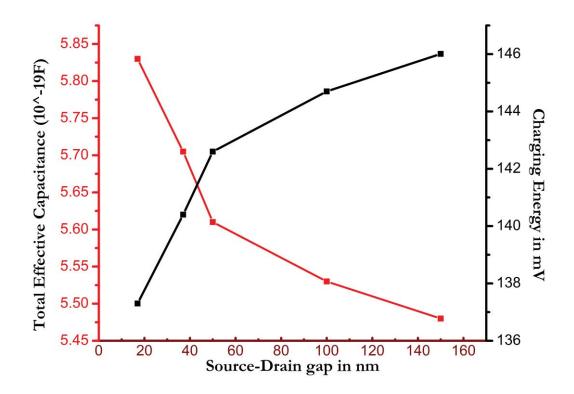

| Fig. 5.4: The variation of charging energy and total effective capacitance with respect to the source  |

| drain gap138                                                                                           |

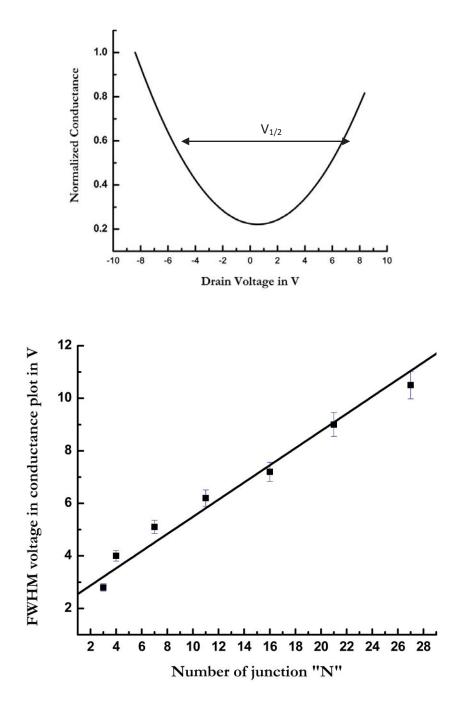

| Fig. 5.5 The dependency of FWHM voltage $V_{1/2}$ in the conductance plot with respect to the number   |

| junction in the DCP (source-drain gap) for room temperature operating SET Device140                    |

| Fig. 5.6: Pictorial view of SET devices with different topology (top) Vertical Source and drain,       |

| (middle) Bottom Gate device (Bottom) Top gate device                                                   |

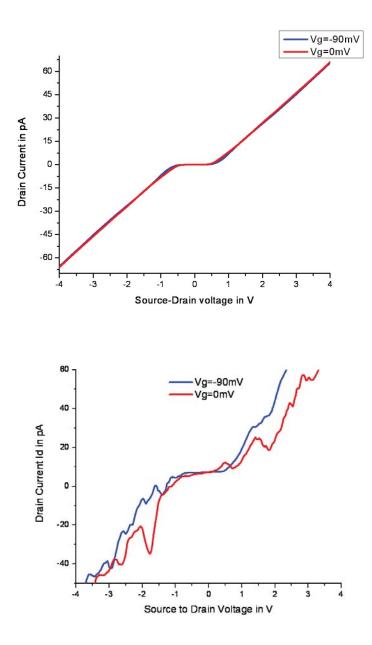

| Fig. 5.7: Coulomb blockade characteristic of the SET devices of different topology (Top left)          |

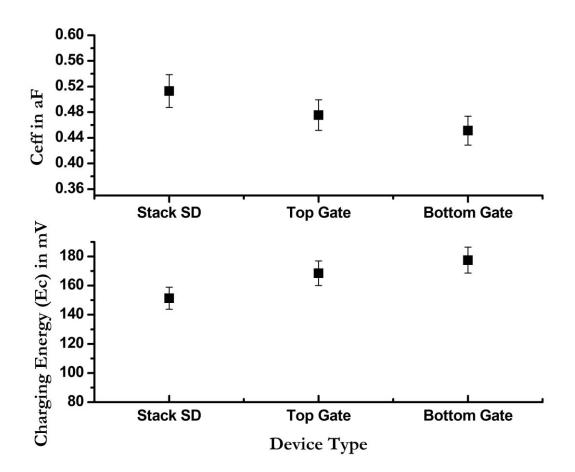

| Bottom gate (Top right) Top gate (Bottom) Vertical Source and Drain144                                 |

| Fig. 5.8: Plots showing the charging energy and the effective capacitance for SET with different       |

| topology as extracted from the experimental V-I characteristic                                         |

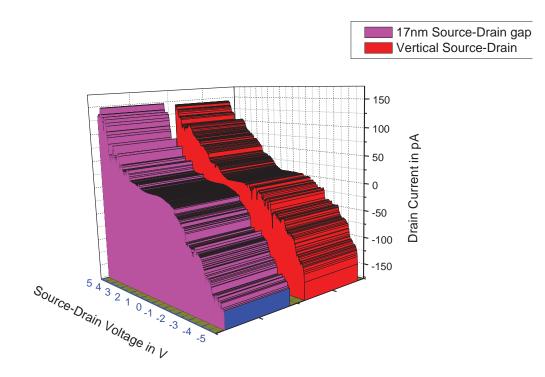

| Fig. 5.9: Comparison of the Coulomb blockade characteristic of a 17nm source drain device and a        |

| vertical source-drain device                                                                           |

| Fig. 5.10: Capacitive model of the SET devices (a) Device with 17nm S-D gap (b) Device with            |

| vertical S-D terminals                                                                                 |

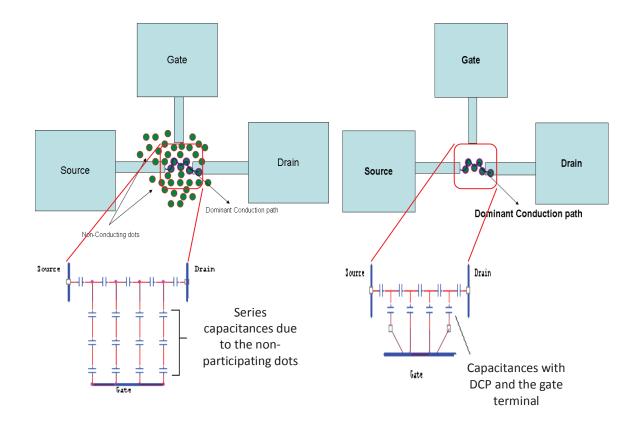

| Fig. 5.11: Room temperature V-I characteristics of the SET devices with (blue line) and without (red    |

|---------------------------------------------------------------------------------------------------------|

| dash) the non-participating dots151                                                                     |

| Fig. 5.12: Pictorial view of a SET device (left) with and (right) without additional non-participating  |

| dots. The inset represents an approximated capacitance model of such device152                          |

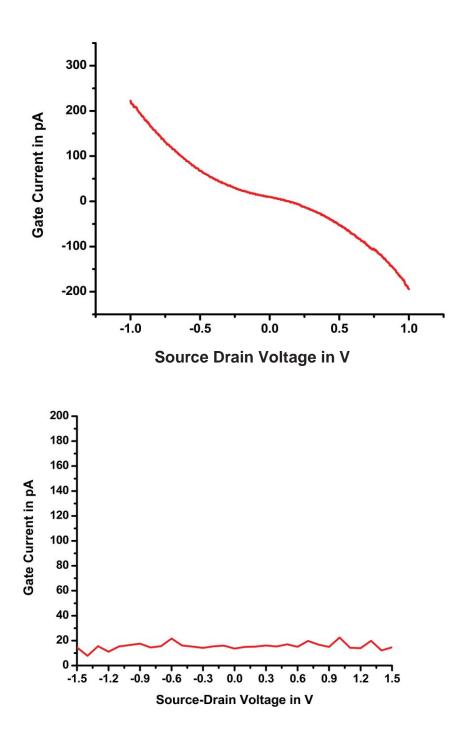

| Fig. 5.13: Plot showing the gate current with respect to the source-drain voltage in a multi dot RT-    |

| SET (left) with and (right) without non-participating additional dots154                                |

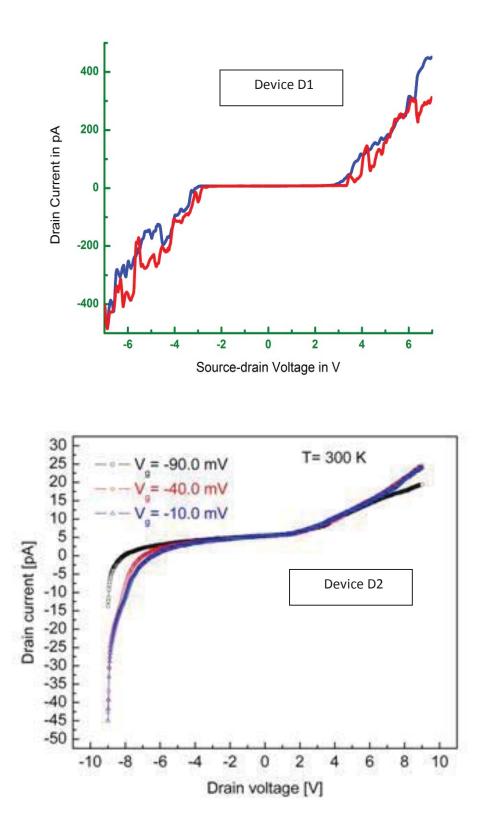

| Fig. 5.14: The V-I characteristic of the devices with different material setups [Top left-D1,Top right- |

| D2 Bottom D3] showing the Coulomb blockade for different gate voltages156                               |

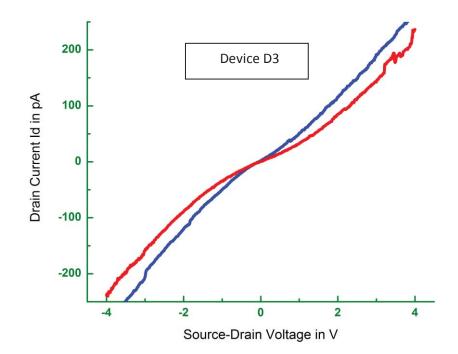

| Fig. 5.15: The distribution of the spacing between the multiple peaks in the Coulomb oscillation of a   |

| 17nm based SETdevice161                                                                                 |

| Fig. 5.16: Theoretical (Left) and experimental non-linear characteristic of a SET device with vertical  |

| source and drain terminal164                                                                            |

| Fig. 5.17: Simulated V-I characteristic of planar devices fabricated by FIB etch and deposition         |

| process with different source and drain gaps (a)17nm, (b) 37nm, (c) 100nm166                            |

| Fig. 5.18: Coulomb blockade length with respect to source-drain gap. Comparison between                 |

| simulated results with the experimental data168                                                         |

# **List of Tables**

| Table 1.1: A comparison study of the next generation emerging devices                   | 10  |

|-----------------------------------------------------------------------------------------|-----|

| Table 2.1: Parameters used for simulation of a single dot SET device                    | 34  |

| Table 2.2: Parameters used for simulation of multi-dot SET device                       | 39  |

| Table 3.1: Hitachi FB-2000A FIB System Beam details                                     | 52  |

| Table 3.2: Parameters for the deposition process of Al2O3 and Cr layer                  | 58  |

| Table 3.3: FIB process parameters for fabrication of micro/nano structures for the SE   | Т   |

| device                                                                                  | 61  |

| Table 3.4: Fabrication parameters for 17nm source drain gap formation                   | 81  |

| Table 5.1 Dimensional parameters of SET with different topology                         | 143 |

| Table 5.2: Device parameters for vertical device and 17nm S-D gap based device          | 149 |

| Table 5.3: Description of the SET devices with different material set-ups               | 155 |

| Table 5.4: Device parameters for simulating the V-I characteristic of a vertical device | 163 |

### **Chapter 1: Introduction**

### 1.1. Background

The new trends in lifestyle in the ubiquitous society, which could be called a "Hi-Tech Style" are widely spreading these days. Progress in ultrafast communication systems, is virtually shrinking the globe every day. Miniaturization in the storage technologies has given the privilege to have terabytes of data, in a wallet, thanks to the progress in microelectronics.

The genesis of micro electronics can be traced back to the demonstration of the bipolar junction transistor (BJT) in 1947 [1]. This Nobel Prize winning invention eliminated the requirements of massive vacuum tubes with hundreds of terminal voltages even for minimal functionalities. The transistor operation was possible by power consumption in order of milli watts rather than a few hundred watts as for equivalent vacuum tube circuits. The BJT devices became the elemental block for any electronic circuits with various functionalities. However, the real capability of the BJT devices was fully exploited only when many of them can be integrated in a single chip, demonstrated in the invention of the integrated circuit in 1958 [2]. These two discoveries opened the path for high functionality based electronic technology. However, for complex application the power dissipation in the high density BJT based circuits became a major issue. Efforts to resolve the power dissipation issue gave birth to the third breakthrough, the invention of Complementary Metal-Oxide Semiconductor or CMOS. CMOS based integrated circuits were announced in 1963 [3]. Collectively these three inventions demonstrated the conceptual basis for the modern low power micro-electronics.

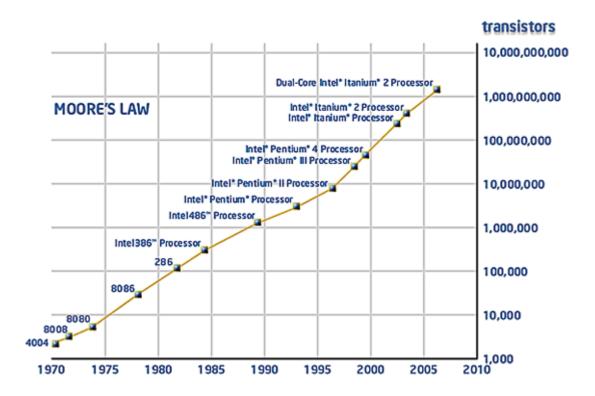

Since its birth in 1960s, the tremendous growth in the micro-electronics industry in the last four decades is driven by the need to have portable devices having the capability of better computing coupled with large data storage and ultra low power consumption [1]. These requirements have increased the momentum of research and development efforts in semiconductor industry resulting in better performance and higher component packing density [4]. The development in micro-electronics, such as increased speed, increased complexity in functionalities, and the reduction in power dissipation etc. are made possible by continuously scaling the CMOS device, which is the fundamental block for any electronic circuit [5]. Scaling down the device size increases the number of devices per unit area, thus increasing the number of operations per second. This helps in multiplying the functionalities [6]. The last four decades have evidenced the trend in increasing the number of transistor per chip as per the famous Moore's Law [7]. As shown in Fig. 1.1, the number of transistors per chip doubled in almost every 24 months, doubling the speed and functionalities of operation. Remarkably, the industry has kept pace with this exponential growth for that last four decades. However, the issue with this growth is that when the exponential growth in the device density rapidly approaches infinity, the physical systems generally cannot run to infinity [8]. Even Moore himself pointed out in 2003 that "No exponential change of a physical quantity can, however, continue forever" [9]. This could very well mean reaching a dead end with existing CMOS scaling. This predicted dead end is based on definitive physical laws which need to be understood.

Fig. 1: The increasing rate of the transistors per chip [Source: www.intel.com]

#### **1.2. CMOS Scaling: Issues and Probable Solutions**

The basic idea of scaling is to reduce the dimensions of the CMOS transistors and the wires connecting them in integrated circuits [6]. Scaling of CMOS was first proposed by Dennard et. al. [10] to secure the switching characteristic by suppressing the short channel effect. It was recognized that by reducing the dimensional parameters like the gate length  $(L_g)$  and gate width  $(W_g)$  by a factor K, a decrease in the propagation delay, the drain current, and threshold voltage would result by the same factor (1/K) [11]. This is the basis for CMOS scaling demonstrated by Moore's law over the last four decades [12].

The scaling can be done in two different ways 1. Constant Field Scaling and 2. Constant Voltage Scaling. A CMOS device works by modifying the electric field just beneath the surface

of the silicon layer in the gate area to control the flow of current between sources and drain. Constant field scaling achieves the same electric field profile in the smaller transistor by reducing the applied voltage along with all the key dimensions, including the gate oxide thickness  $(t_{\alpha})$ [6]. The constant field scaling can lead to increased number of circuits in a given chip area with no increase in the total power dissipation [13]. During the 1980s the constant field scaling was replaced by constant voltage scaling in order to maintain a constant voltage throughout different generations of chips. The constant field scaling was reinvented [14]. One of the most important reasons is its positive impact on the power density.

Following constant field scaling, the device size decreased to 0.25 micron without any major issue. But when the device size reached 90nm with 50-60nm gate length, leakage current in the sub-threshold region became an issue [15]. Hence, leakage power became significant to limit the scaling. With further reduction in device size, the scaling is confronted with some fundamental limitations along with limitations based on other factors like process, materials and system. According to Meindl, et al. [15,16] the theoretical and practical limitations in device scaling can be codified into 5 different categories 1. Fundamentals, 2. Materials, 3. Device, 4. Circuits and 5. Systems. The fundamental limits can be derived from the physical principles such as quantum mechanics, thermodynamics and electromagnetism. The material limits are determined by the carrier mobility, carrier saturation velocity, break down field strength, and thermal conductivity. The impact of these parameters on device performance is of great concern when the device size goes below 100nm. [16, 17]. Taking an example, at the 65nm technology node, the thickness of the gate oxide is 1.2nm, which is a

few monolayers of Si-O bonds [18]. Hence further reduction in the gate oxide is almost impossible due to the high tunneling current. It is likely that tunneling currents arising from silicon dioxide (SiO<sub>2</sub>) thinner than 0.8 nm cannot be tolerated, even for high-performance systems [12]. Apart from the above material limitations, process related limitations to fabricate a device of channel length below 60nm is always a challenge. With scaling, as the functionalities per chip multiplies, it multiplies the number of devices and hence the total leakage current. This requires efficient and fast dissipation of heat generated by the leakage current, which is still a technological limit at the system level.

These limitations raise the question regarding the existence of CMOS technology in the future. This also drives tremendous effort in research to make the CMOS technology survive for the longest period possible. As discussed above, one of the biggest impediments to the CMOS scaling is the leakage current both from the sub threshold leakage and the gatedielectric leakage. The effort to overcome these issues can be categorized in two different ways; new materials and new device setups. Gate dielectric leakage current is basically caused by the hot carrier effect and electron tunneling through the gate dielectric. To reduce these currents, high-K based gate dielectrics can be introduced to have a higher physical thickness with same electric field magnitude. However, the benefits of just replacing the SiO<sub>2</sub> with a high-K material for the same electrical field are limited by the presence of two-dimensional electric fringing fields from the drain through the physically thicker gate dielectric [19, 20]. The use of higher-K materials must therefore be combined with a concurrent reduction of the electrical thickness. In addition, other factors like thermal stability, the impact of surface states etc. have to be considered for using high-K materials. Replacement of poly-Si gate electrodes by a metallic gate is another technique to improve the device scaling below the 50nm regime. Its advantages to counteract the gate capacitance degradation and carrier mobility degradation have made it an unique technique for today's sub-50nm CMOS technology. Combination of these two material set-ups can be used for future high performance low power circuits to push the device size even further.

Other than the different material set-ups, new device set-up has been developed to improve the functionality favoring the device scaling. Double/multi-gate MOSFETs [21] or FinFET [22] in which a second gate is added opposite to the traditional gate, have been recognized for their potential to better control the short-channel effects. It is also shown that a Double Gate –FET (DG-FET) can be scaled to a very short channel length (25 to 30 nm) while achieving the expected performance derived from scaling [23]. However, issues in setting up multiple threshold voltage in the same chip along with the fabrication challenges limit its future for future ultra-low power ULSI circuits. Strained Si based devices is also been of great interest for their potential to increase the carrier mobility. In particular combination of strained Si technique with SOI based devices has proven immense potential in the scalability of the devices [24]. Vertical MOSFET configuration provides other new device options for higher levels of functional integration [25].

Advanced techniques in material and device set-ups along with development in the process technology will improve the device performance and will continue the CMOS scaling in the near future till the gate length in a transistor reaches 10nm limit. However, no possible solution is still known to advance the scaling below the 10nm limit. In the sub-10nm regime the materials will lose their bulk properties and the performance of the devices will be dominated by the quantum effects.

Nano-scale devices, which utilize the quantum effects for its operation, are a possible solution for the devices of the next generation. Some of the potential candidates are the, 1D structures (Carbon nanotubes and nano wires), spintronic devices, resonant tunneling devices, single electronics, molecular electronic devices, ferro magnetic logic devices, and devices based on quantum cellular automata [4]. Carbon nanotube based FETs are already demonstrated as a potential device for future logic circuits [26]. However, the difficulties in understanding the detailed physics and the fabrication issue limit their development for future ULSI circuits. Dominance of the Schottky tunneling barrier between the source/drain and the channel, over the carrier transport is another issue that needs to be overcome in these devices [27,28].

#### **1.3. Single Electron Devices: A Successor of CMOS**

When the CMOS reaches the ultimate limits of scaling of below 10nm, single electron effects limit the normal transistor action at the smallest length scales and hence some perceive the Single Electron Devices to be a natural successor to the CMOS devices. Single Electron Devices operate on the simple principle of Coulomb blockade, and can manipulate electrons at the level of elementary charge, hence their operation is guaranteed even if the size of the device is reduced to the molecular level. Single Electron Devices not only function as simple switching device but also show immense potential for large scale integration. Single Electron Transistors (SETs) are the most fundamental three terminal single electron devices. Single Electron Transistors are quantum devices in which, instead of working with currents and voltage levels, which are defined by millions of electrons as in today's CMOS technology, one can realize the limit of performing logic operations with single or small number of electrons [29]. Hence, these devices can work with extremely low power dissipation. The low power consumption and sensitivity to high charge of the SETs makes a potential candidate for sensing and ULSI based applications [30, 31].

The field of single electron devices is developed by several Nobel prizes and Nobel prize winning discoveries and insights. One can argue that the origin of SET devices started in the early 20th century when Robert Milkman showed by his oil drop experiment that charge is discrete and single valued. He achieved localization of a single electron in an oil drop and found out how to measure its elementary charges. For his breakthrough discovery he received the Nobel Prize in 1923. To replicate the same phenomenon in solid state it took several decades. It was in late 1980s when the first manipulation of single electrons realized what is known as single electronics today. But before that could happen, quantum mechanical modeling, explaining the quantum mechanical tunneling of electrons had to be developed. The Coulomb blockade effect, which is the basic working principle for the single electronic devices, was first explained by C. Gorter [32]. In 1951, he explained correctly the current suppression in low bias voltage as the cause of Coulomb repulsion. After ten years the same current suppression effect at low bias was again observed by C. Neugebauer and M. Webb during their study of current conduction in granular films [33]. It took another two decades until 1985 when D. Averin and K. Likharev [34] formulated the popular orthodox theory to explain the single electron tunneling phenomena. This theory quantitatively describes the single electron charging effects such as Coulomb blockade and Coulomb oscillations. The experimental realization of Single Electronic devices started after the invention of the Scanning Tunneling Microscope (STM). The STM was used in several variations to build the single electron devices in nano-scale and opens the possibilities of manufacturing room temperature operating single electron transistors. However, STM is not the first method of fabricating Single Electron Transistors. Dolan and Fulton [35] used a double shadow evaporation method and fabricated the first Single Electron Transistor showing single electron charging effects. Since then tremendous development has occurred in the field of single electron transistors. The evolution in the design and process technology in the SET devices is detailed in the following chapter.

The most important reason for the increasing interests for Single Electronic Transistor Devices is due to its ultra low power consumption and small size. Table 1 shows the ITRS-2007 report for the comparison in the parameters of different research devices. As it can be observed, the comparative data in Table 1.1 shows that the SET device beat peer devices due to its low power consumption and high device density capability. The only issue retarding the progress of SET devices as for future ULSI systems is its lower fan-out [35]. However, this could be solved by innovative circuit design such as the binary decision diagram [36].

| Device<br>Typical example devices |              | ł       | _                                                                                           | ل<br>الأ                                                         |                                                         | •                                                          | $\square$                               |                                                                  |

|-----------------------------------|--------------|---------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------|---------------------------------------------------------|------------------------------------------------------------|-----------------------------------------|------------------------------------------------------------------|

|                                   |              |         | FETE                                                                                        | xtension                                                         |                                                         |                                                            |                                         |                                                                  |

|                                   |              | FET [A] | 1D structures                                                                               | Channel<br>replacement                                           | SET                                                     | Molecular                                                  | Ferromagnetic<br>logic                  | Spin transistor                                                  |

|                                   |              | Si CMOS | CNT FET<br>NW FET<br>NW hetero-<br>structures<br>Nanoribbon<br>transistors with<br>graphene | III-V compound<br>semiconductor and<br>Ge channel<br>replacement | SET                                                     | Crossbar latch<br>Molecular<br>transistor<br>Molecular QCA | Moving domain<br>wall<br><u>M</u> : QCA | Spin Gain<br>transistor<br>Spin FET<br>Spin Torque<br>Transistor |

| Cell Size                         | Projected    | 100 nm  | 100 nm [D]                                                                                  | 300 nm [I]                                                       | 40 nm [O]                                               | 10 nm [U]                                                  | 140 nm [Y]                              | 100 nm [C]                                                       |

| (spatial<br>pitch) [B]            | Demonstrated | 590 nm  | ~1.5 µm[E]                                                                                  | 1700 nm [J]                                                      | ~200 nm [K, L]                                          | ~2 µm [V]                                                  | 250 nm [Z, AA]                          | 100 µm [AB]                                                      |

| Density                           | Projected    | 1E10    | 4.5E9                                                                                       | 6.1E9                                                            | 6E10                                                    | 1E12                                                       | 5E9                                     | 4.5E9                                                            |

| (device/cm2)                      | Demonstrated | 2.8E8   | 4E7                                                                                         | 3.5E7                                                            | ~2E9                                                    | 2E7                                                        | 1.6E9                                   | 1E4                                                              |

| Switch Speed                      | Projected    | 12 THz  | 6.3 THz [F]                                                                                 | >1 THz                                                           | 10 THz [Q]                                              | 1 THz [W]                                                  | 1 GHz [Y]                               | 40 GHz [AC]                                                      |

| Switch Speed                      | Demonstrated | 1.5 THz | 200 MHz [G]                                                                                 | >300 GHz                                                         | 2 THz [R]                                               | 100 Hz [V]                                                 | 30 Hz [Z, AA]                           | Not known                                                        |

| Circuit Speed                     | Projected    | 61 GHz  | 61 GHz [C]                                                                                  | 61 GHz [C]                                                       | 1 GHz [0]                                               | 1 GHz [U]                                                  | 10 MHz [Y]                              | Not known                                                        |

| Carcun speed                      | Demonstrated | 5.6 GHz | 220 Hz [H]                                                                                  | Data not available                                               | 1 MHz [P]                                               | 100 Hz [V]                                                 | 30 Hz [Z]                               | Not known                                                        |

| Switching                         | Projected    | 3E-18   | 3E-18                                                                                       | 3.00E-18                                                         | 1×10 <sup>-14</sup> [O]<br>[>1.5×10 <sup>-17</sup> ][S] | 5E-17 [X]                                                  | ~1E-17[Z]                               | 3E-18                                                            |

| Energy, J                         | Demonstrated | 1E-16   | 1E-11 [H]                                                                                   | 1Е-16 [Л]                                                        | 8×10 <sup>-17</sup> [T]<br>[>1.3×10 <sup>-14</sup> ][S] | 3E-7 [V]                                                   | 6E-18 [AA]                              | Not known                                                        |

| Binary<br>Throughput,             | Projected    | 238     | 238                                                                                         | 61                                                               | 10                                                      | 1000                                                       | 5E-2                                    | Not known                                                        |

| GBit/ns/cm <sup>2</sup>           | Demonstrated | 1.6     | IE-8                                                                                        | Data not available                                               | 2E-4                                                    | 2E-9                                                       | 5E-8                                    | Not known                                                        |

|                                   |              | RT      | RT                                                                                          | RT                                                               | RT [M, N]                                               | RT                                                         | RT                                      | RT                                                               |

|                                   |              | Si      | CNT,<br>Si, Ge, III-V,<br>In <sub>2</sub> O <sub>2</sub> , ZnO, TiO <sub>2</sub> ,<br>SiC,  | InGaAs, InAs,<br>InSb                                            | III-V, Si, Ge,                                          | Organic<br>molecules                                       | Ferromagnetic<br>alloys                 | Si, III-V,<br>complex metals<br>oxides                           |

| lesearch Activit                  | (AD)         |         | 379                                                                                         | 62                                                               | 91                                                      | 244                                                        | 32                                      | 122                                                              |

Table 1.1: A comparison study of the next generation emerging devices

#### [Source:ITRS2007]

### **1.4. Research Objectives**

Development of the FIB etch-deposition based SETs and optimization of its fabrication process is the core of the present work. Additional objectives such as characterization of the multi tunnel junction (MTJ) based devices and the impact of design parameters on the device behavior are also set to support the study. In specific the objectives include:

- $\checkmark$  Exploring the fabrication of single dot based RT-SET using FIB.

- ✓ Characterizing the FIB etch and deposition process and studying the factors limiting resolution in the nano regime. Studying the impact of beam profile during FIB etching.

- $\checkmark$  Optimizing the FIB etching process to maximize the resolution.

- ✓ Development of fabrication process for RT-SETs using FIB etch and deposition technology.

- ✓ Improvement in the performance of the RT-SETs through design.

- ✓ Studying the impact of structural and topological variation in the performance of a RT-SET device.

- ✓ Exploring the realization of semiconductor quantum dot based RT-SETs.

- ✓ Device characterization and demonstration of Coulomb blockade effect and Coulomb oscillation at room temperature.

- ✓ Device modeling and comparison of modeling and experimental results.

### **1.5. Dissertation Outline**

This dissertation details the research carried out for developing Single Electron Transistors operating at room temperature using Focused Ion Beam etch and deposition technology. Chapter 2 describes the theory of SETs, the evolution of technology for fabricating the SET devices and the design of room temperature operating SET devices.

Chapter 3 details the fabrication of the SET devices using FIB etch and deposition processes. The issues in FIB etching process in nano-scale regime and their possible solution is also detailed in this chapter. The characterization process along with the device current voltage characteristic of the fabricated SET devices are discussed in Chapter 4 and analyzed in Chapter 5. Finally, the conclusion of the work is described in Chapter 6 and the future recommendations are summarized in Chapter 7.

# Chapter 2: Theory of Single Electron Transistors and Device Design

The increase in the demand of complex functionalities and unmatched computational ability in present electronic circuits requires higher device density and efficient design. Although new and reliable design technique like DFM (design for manufacturability) and multi-layer routing can enhance the device density by some factor [37], ultimately device size is the key parameter to increase the device density in the demanding ULSI circuits. The reduction of the device dimensions of the CMOS devices by continuous scaling has placed the devices in the length scales of sub 50nm. However, as discussed in the Chapter 1, the device scaling is difficult when the gate length reaches below 30nm. At sub 30nm length scale, the Coulomb blockade and single electron charging effects become dominant, thus impacting the characteristics of the CMOS transistors, in a detrimental way. These effects can be utilized as the basic principles to realize functional devices, which have potential to be used as nano electronic devices. The Single Electron Transistor (SET) is one of such device which has great potential to work in conjunction with CMOS devices for future high speed ULSI circuits.

The SET device works in the principle of Coulomb blockade, which is prominent when the device dimension is scaled down to a few nano-meters [38]. In SET devices, a free electron can be confined in a nano-meter sized island and can tunnel to/from the electrode terminal by quantum mechanical tunneling. The islands can be made up of any metal or semiconductor material.

### **2.1. Theory of Operation**

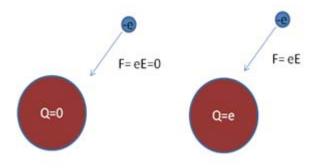

The operation of a Single Electron Transistor device can be derived from the charge quantization principle. The charge in any small isolated electron puddle is quantized: it contains only an integer number of electrons. Also this charge can only change in multiples of a single electron [39]. The operation principle of a SET can be explained from this charge quantization effect with a simple example of charging a conducting sphere (representing an island) [40]. Consider a small sphere which is electrically conductive and initially electro neutral. At this point the net charge on the island is zero as the number of protons is equal to number of electrons inside it. Thus the electric field outside the island is zero. Now to charge this island by supplying some electrons to it, the electrons have to expend some energy. For the first electron, a weak external force can do the job as there is no repulsive force from the sphere. Once the sphere is charged by one electron the net charge Q on the sphere is now -e. Hence, as shown in Fig 2.1, to move the second electron in to the sphere, a force F = e E is the required overcome the repulsion due to the additional electric field E by the existing electron in the sphere. This phenomena repeats every time one additional electron is added to the island. The generated electric field depends on the size of the island, the number of additional electrons in it and the material properties of the island. Though the fundamental charge  $e = 1.6 \times 10^{-19}$  Coulomb is very small on the human scale of things, the field is inversely proportional to the square of the island size and may become rather strong for nano scaled structures [40]. The energy required to overcome this field is called

the charging energy and for each electron it can be defined as  $E_c = \frac{e^2}{2C_{eff}}$ , where  $C_{eff}$  is the effective capacitance of the island. The effective capacitance,  $C_{eff}$ , is determined by

the size of the island and the electrostatics of the ambient.

Fig. 2.1: Charging of a metallic sphere with no-charge and charged state

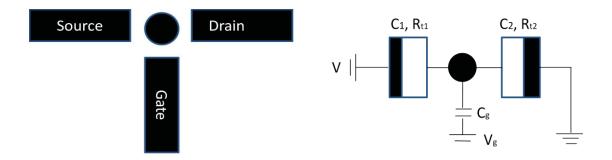

The SET device works in the principle described above where the electron transport to/from the dot takes place by tunneling from the electrode terminals through the tunnel junction. The basic structure of a typical SET device consists of a central island capacitively coupled to the source and drain electrode terminals by two small tunnel junctions. A third gate electrode can be resistively or capacitively coupled to the central island. Electrons can tunnel from the source to the drain electrode through the island. The electron tunneling from the electrodes to/from the nano-island occurs only when the energy supplied by the voltage source is large enough to overcome the charging energy of the system. Hence, in a drain current characteristic of the SET's, the current is suppressed for the lower bias region. This represents the confinement of a single electron, which is only possible when the energy supplied by the voltage is less than the charging energy of the device. The suppression of the current due to this single electron confinement is called Coulomb blockade effect. The charging energy of the device depends on the effective capacitance of the island with respect to the ambient surrounding and the charge on it. The charge on the island can be controlled by varying voltage on the gate electrodes [39,40,41,42]. Hence, the flow of electron current from the source to drain electrode can be modulated by the voltage in the gate electrode. Figure 2.2 shows the schematic of a SET device along with its electrostatic model.

Fig. 2.2: (Left) Basic structure of a SET device. (Right) The electrostatic model of the device.

Throughout the history of the single electronics, a generalized theory has been used to explain the characteristic of the SET devices. This simple and effective theory called the as "orthodox theory" was first developed by Kulik, et al [43]. This theory is based on the following assumptions:

- 1. The electron energy quantization inside the conductors is ignored, i.e., the electron energy spectrum is treated as continuous;

- The time for electron tunneling through the barrier is assumed to be negligibly small in comparison with other time scales (including the interval between successive tunneling events);

Coherent quantum processes consisting of several simultaneous tunneling events ("co-tunneling") are ignored.

Despite the above assumptions, orthodox theory has very good quantitative agreement with the experimental data [40, 41]. From the outcomes of this theory it is observed that at least two conditions have to be satisfied to make SET devices operable: 1. The charging energy has to be greater than the thermal energy and 2. Tunnel resistance of the junctions has to be greater than the quantum resistance. The first condition has to be satisfied in order to distinguish the Coulomb blockade effect from the thermal agitation of the electrons. At the same time the resistance of the tunnel junction has to be large enough to avoid the band broadening effect which eventually may destroy the electron confinement in the islands [44]. These conditions are quantitatively represented in Eq. 2.1 and 2.2.

$$E_c \left(=e^2/2C_{eff}\right) > k_B T \tag{2.1}$$

$$R_t \gg R_Q \tag{2.2}$$

Where,  $E_c = Charging \, Energy \left( = \frac{e^2}{2C_{eff}} \right)$ ;

$T = Temperature, \quad k_B = Boltzmann Constant;$  $R_t = Tunneling resistance of the tunnel junctions;$  $R_Q = Quantum Resistance = \frac{h}{e^2} (= 25.6k\Omega);$

From Eq. 2.1 it can be observed that the effective capacitance,  $C_{eff}$ , is the parameter which determines the critical temperature at which the device can operate. From a simple calculation it can be obtained that the effective capacitance,  $C_{eff}$ , of the island has to

be in order of  $10^{-18}$ F or lower to make a SET device operable at room temperature (T=300K). The effective capacitance consists of the self capacitance of the quantum dot and its capacitance with respect to the source, drain and gate electrodes. Considering the island to be spherical in shape, it can be calculated that for an effective capacitance to be in order of aF the diameter of the island has to be 10nm or less. This is one of the challenges for progress in the fabrication of the SET operating at room temperature.

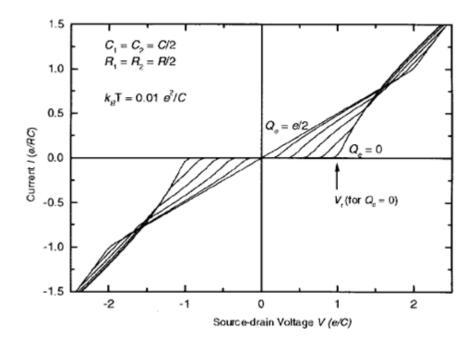

Figure 2.3 shows the V-I characteristic of a SET device with different gate voltage  $V_g$ . This non linear I-V characteristic of the device shows that for voltages less than e/C the dc current is suppressed due to Coulomb blockade effect. After a threshold voltage  $V_i$  the Coulomb blockade is overcome and the current approaches one of its linear asymptotes. For a SET device it can be observed that, the threshold voltage, as well as the source drain current in its vicinity, are a periodic function of the gate voltage.

Fig. 2.3: V-I characteristic of a SET device. Where C<sub>1</sub>, C<sub>2</sub>, and R<sub>1</sub>, R<sub>2</sub> represents the junction capacitances and resistances respectively for the two junctions in the SET respectively. Q<sub>0</sub> represents the gate voltage induced charge.[Reprinted with permission from K.K. Likharev, Proceedings of the IEEE, Vol 87 (4), 1999,© 1999 IEEE]

The presence of this oscillation in the drain current with respect to the gate voltage can be explained by the stability diagram as shown in Fig. 2.4 [38]. In the stability diagram the x-axis represents the gate voltage and the y-axis represents the source-drain voltage. The double-hatched rhombic-shaped regions, which are called Coulomb diamonds, are the stable region. Outside the Coulomb diamonds, the number of electrons in the island fluctuates between certain numbers. However inside the Coulomb diamond region, the fluctuation is minimum, i.e., the electron number changes only between two adjacent integers. In the unstable region, the degree of the fluctuation is related to how far the voltage conditions are apart from the Coulomb diamonds. In the stable (Coulomb diamonds) regions, when there is a finite voltage between the source and drain, electrons are transferred one by one between the two electrodes. And this can be represented as a periodic oscillation in the drain current (or Conductance) with respect to the gate voltage. This is called the Coulomb oscillation and is shown in Fig. 2.4.

Fig. 2.4: Coulomb Oscillation and stability diagram of a SET.  $V_d$ represents the source-drain voltage and  $C_{\Sigma}$  is the effective capacitance of the device. [Reprinted with permission from Y. Takahashi, Y. Ono, A. Fujiwara and H. Inokawa "Silicon single-electron devices" J. Phys. Condens. Matter Vol. 14, R995, 2002,© 2002 Institute of Physics]

#### **2.2. Single Dot and Multi Dot SETs**

The current conduction in a SET device takes place by tunneling of electrons from the source to the drain electrode through the quantum dot. Depending on the number of quantum dots taking part in this conduction process, the SET devices can be divided in two categories: 1.Single Dot based SET where only one dot takes part in the electron transport process; and 2. Multi-Dot based SET, where more than one dot can take part in the electron

transport process. In a single dot based device the electron tunneling occurs only through two tunnel junctions. In the other hand, for a multi dot based device an electron traverses an array of tunnel junctions for its tunneling from the source to the drain electrode. Hence, the multi-dot based SET devices are also called as Multi Tunnel Junction (MTJ) based SETs. Depending on the orientation of the dots, the MTJ devices can also be two dimensional (2D) or one dimensional (1D) devices. In a 1D MTJ base SET, there is just one path for the electron. The electron from the source terminal hops from one dot to another to reach the drain terminal. However, in 2D MTJ based devices, there is more than one parallel path. Theoretical work [45, 46] in 2D MTJ based SET devices shows that the electron will follow a dominant conducting path (DCP) to tunnel from the source to drain electrodes. However, the characteristics of the device can depend on the capacitance presence due to the addition dots other than the DCP. A pictorial view of the electron transport path in a single and 2D multi dot based SET device is shown in Fig. 2.5. For a same size of dots the critical temperature for a MTJ based device is higher than that for a single dot based device. This is because of the reduction in the effective capacitance in the case of MTJ device due to series capacitance by the additional dots. However, this reduction in effective capacitance can lead to a higher threshold voltage, which is undesirable. In this work, MTJ based devices are studied and the impact of this additional capacitance is also investigated.

Fig.2. 5: A pictorial view of (Left) Single dot based and (Right) Multi-Dot Based SET devices with possible path of electron transport.

Both the single dot and multi dot based SET requires sub-10nm sized quantum dots to operate at room temperature. Fabrication techniques enabling sub-10 nm feature sizes are indispensable for fabricating SET devices, operable at room temperature. Various structures for SETs have experimentally fabricated. Most of them are developed for low temperature application. From the initial studies on Single Electron systems, mainly metals and III-V compound semiconductors have been used to investigate the basic physics of the transport and to explore possible applications, because of the ease of confinement of electrons possible in the two dimensional electron gas (2DEG) in III-V compounds. The material requirements for the SET are that, the central island can be made of semiconducting material or a metal. Both metallic and semiconducting central islands are studied in the present work.

#### 2.3 Evolution in Technologies for SETs

The first experimental demonstration of the SET devices based on a metallic island was done by Fulton and Dolan in 1987 [35]. The charging effect and Coulomb blockade behavior was observed experimentally by employing the configuration shown in Fig. 2.6 in which three Al-Al junctions with small area and overlap capacitance are formed on a small common electrode. The device is fabricated using e-beam lithography and multiple angle deposition-oxidation-deposition cycle [47]. As the size of the central island is much larger than 10nm, the device could only work in 1.1-4.2K temperature. The V-I characteristic of the device is shown in Fig. 2.7.

Fig. 2.6: SEM image of the first fabricated SET by Fulton and Dolan. The junctions labeled as a, b and c are formed where the vertical electrodes overlap the contact, the longer horizontal central electrode. [Reprinted with permission from T. Fulton and G. Dolan, Phy. Rev. Lett, Vol. 59, p109 (1987), © 1987 American Physical Society]

Fig 2.7: The V-I characteristic of the SET device fabricated by Fulton and Dalon. [Reprinted with permission from T. Fulton and G. Dolan, Phy. Rev. Lett, Vol. 59, p109 (1987), © 1987American Physical Society].

In a further investigation, Coulomb oscillations were also observed in a device with a narrow GaAs channel interrupted by two potential barriers. However these devices were only good for low temperature applications [below 4.2K] as the observed effective capacitance is much higher than the critical value of that for room temperature application [48]. A further increase in the charging energy is achieved by using silicon on insulator (SOI) layer of separation by implanted oxygen (SIMOX) process. The first SOI wafer used in SET fabrication was reported by Ali and Ahmed [49] as shown in Fig. 2.8. The  $E_c$  reported by this method was 1.6 meV. The island size was still limited by lithography, and the Coulomb blockade (CB) effects observed at few Kelvin temperatures. The operating temperature has

been increased by decreasing the size of the nano-island with the advances in the fabrication technology. In 1996 Nakamura and Chen, et al. [50] reported an aluminum island based SET that can operate at 100K temperature. These devices function and exibit the Coulomb blockade effect with an artificially fabricated 20-nm island electrode by utilizing standard e-beam lithography and three-angle evaporation process. A charging energy of ~12meV and an overall capacitance of ~15aF are reported in these devices. These resultant parameters are also far from the required charging energy for the room temperature operation of the device.

Fig 2.8: SEM image of a 100nm diameter island on a SOI wire as fabricated by Ali et al. and (Right) the V-I characteristic of the device fabricated using this island.

[Reprinted with permission from D.Ali and H. Ahmed, Appl. Phys. Lett, Vol.64, p2119, (1994), © 1994 American Institute of Physics]

The first room temperature operating Coulomb oscillation was reported by Matsumoto et al. using scanning tunneling microscopy (STM) as a fabrication process [51]. Using the STM tip as a cathode, the surface of the titanium metal has been oxidized, and a few tens of nanometer wide oxidized titanium line was made to realize the Coulomb blockade effect in a Ti/TiOx system. The principle of this nano oxidation process for Ti/TiOx system on  $SiO_2$  is shown in Fig. 2.9. The Coulomb staircase of 150 mV period is observed in the current–voltage characteristics of this SET system at room temperature. The oxidation process for forming the tunnel junction is further used in a different way to fabricate silicon based SETs operating at room temperature.

Fig 2.9: The room temperature SET fabricated by STM tip by Matsumoto et al. (left top) Principle of STM nano-oxidation process using STM tip as cathode.(left bottom) Cross-sectional view of single electron transistor fabricated by STM nano-oxidation process.(right) Drain current–voltage characteristics ~thick line and conductance (fine line) of SET at room temperature. Gate bias is set to 2 V.

[Reprinted with permission from K. Matsumoto, M. Ishii, K. Segawa, Y. Oka, B. J. Vartanian and J. S. Harris, Appl. Phys. Lett, Vol. 68, p1,(1996), © 1996American Institute of Physics]

Takahashi et al. reported the first room temperature operating Si single electron transistor using pattern dependant oxidation (PADOX) method [52]. In this process, a onedimensional Si wire was converted into a Si island with tunneling barriers at each end by means of pattern dependent oxidation of a very thin Si layer on SO<sub>2</sub>. Using this technique the total capacitance of the device can be reduced to  $\sim$ 2aF which enable conductance oscillation at room temperature.

An improved version of PADOX is called vertical-PADOX which uses vertical thermal oxidation of a long silicon wire with a thickness modulation resulting in higher charging energy. The fabricated SETs by both PADOX and V-PADOX are recognized to show Coulomb oscillation at room temperature. However, repeatability in the fabrication of the tunnel barrier is the biggest issue in these processes [53, 54]. This issue was further addressed by a controlled formation of the tunnel barrier. Thermal oxidation is used in metal system to improve the device parameters and operating temperature by decreasing the island size. Shirakasi et al. [55] reported a Nb/Nb oxide based SET device fabricated by thermal oxidation and scanning probe microscopy (SPM) based anodization technique. These devices showed extremely high charging energy and are operable at room temperature.

Apart from the conventional technique, in which the fabrication of the nano islands solely rely on the resolution limits of the lithography process, non-conventional bottom-up techniques can be used to fabricate the SET which are more likely to operate at room temperature. Non-lithographical techniques, based on nucleation of silicon are used to produce Si nano crystals which can be used as the quantum islands for a multi dot based SET device. Dutta et al. [56, 57] reported SETs with silicon nano crystals, where the charging energies were in the range of few tens of meV. The nano crystals of size ~8nm were deposited using VHF-plasma CVD technique, on a SOI substrate. The source and drain electrodes were formed with an inter-electrode gap of 30nm. SETs with a charging energy of a few meV were observed. In a similar investigation for metallic system, clear Coulomb blockade effects have been observed in lateral metal nanostructures with gold nano crystals fabricated by combined electron beam lithography and ionized beam deposition. An overall capacitance of 0.2aF and a charging energy of 0.4eV were observed [58]. Although, the nano crystal based SET showed substantial increase in the charging energy, lack of repeatability in the fabrication of the tunnel junctions and the nano islands is one of the biggest issue in them. In some further efforts one dimensional nano island array based SET were fabricated with improved controllability in the tunnel junction fabrication [59]. However, the obtained charging energies were only good for low temperature operation.

The non-conventional one dimensional nano structure like carbon nano-tubes (CNT) can also be used to realize the SET devices. J. Kong et al. in 2000 reported a SET device operating at 160K temperature, using potassium doped semiconducting single walled CNT as the island [60]. In the very next year W. Henk et. al. reported a room temperature operating SET device showing the charging energy Ec of 120meV. The devices feature a short (down to ~20 nanometers) nanotube section that is created by inducing local barriers into the tube with an atomic force microscope. In a similar work room temperature operation of the SET device is achieved by controllably grown carbon nano tubes by using the patterned chemical catalyst based thermal CVD process[61]. Introduction of the SET devices. However, such approaches have limited ability to reproducibly achieve the positional and dimensional accuracy for the required nano structure to realize the operation of the SET devices. Integration of the SET devices with the conventional CMOS circuits,

which is the prime motivation for researching this device, requires precise positioning of the associate nano structure, which is still a technology challenge with the above mentioned process.

From the above discussion it can be inferred that although different technologies have been explored to fabricate the SET devices, even with elevated operating temperature, repeatability and the compatibility with CMOS technology still needs to be improved. The present work looks at the potential technologies for realizing room temperature operating SET devices which can be fabricated more reliably and much faster than some existing technologies and compatible with the CMOS processing.

## **2.4. Modeling the V-I current characteristic of a Single Electron Transistor**

In a single dot SET device, the current conduction takes place by tunneling of electrons through two capacitive junctions. The non-linear current voltage characteristic of such a device can be explained using orthodox theory [62]. A master equation based model using the orthodox theory can be used to predict the behavior of the device for different device parameters [63]. However, this model cannot predict the characteristic of a device having more than one dot. The device characteristics of a multi-dot SET system can be explained using the charge soliton analysis [64] in which the multi-dot SET system can be analyzed as a linear array of tunnel junctions. In the present work SET devices with different structural and topological configuration have been investigated with the possibility of having both multi dot and single dot behavior in different devices. Hence, both master equation and

a soliton based modeling approaches are made to predict the behavior of different sets of devices.

#### 2.4.1. Master Equation Approach for Modeling a Single Dot SET

A master equation based model as previously studied by Amman et. al.[63] has been developed to predict the behavior of the SET device. A single dot based SET device can be modeled as two capacitive junctions driven by an ideal voltage source across them. The state of these two junctions can be modeled semi classically and characterized by the voltage across the junction. Figure 2.10 shows a representation of a single dot based SET device by a two junction system. If  $V_1$  and  $V_2$  are the voltage drops across the two junctions and N is the extra electron as supplied by the external circuit, the state of the system can be represented by Eq. 2.3.

$$V_1 = \frac{C_2}{C_1 + C_2} V - \frac{Ne}{C_1 + C_2} - V_p$$

(2.3a)

$$V_2 = \frac{C_1}{C_1 + C_2} V + \frac{Ne}{C_1 + C_2} + V_p$$

(2.3b)

Fig. 2.10: Two junction representation of a single dot SET system. The gate terminal is not shown.

Where  $C_1$  and  $C_2$  are the capacitances of the two junctions respectively and  $V_p$  is the additional voltage which represents the misalignment of the Fermi levels in the two consecutive junctions when N and V are zero [65]. The probability  $\rho(V, N, t)$ , that N electrons are in the middle dot at time t and applied voltage V can be expressed using the master equation as shown in Eq. 2.4 [66,67].