Create the Future Digital Commons @ Michigan Technological University

Dissertations, Master's Theses and Master's Reports - Open

Dissertations, Master's Theses and Master's Reports

2011

## Memory resource balancing for virtualized computing

Weiming Zhao Michigan Technological University

Follow this and additional works at: https://digitalcommons.mtu.edu/etds Copyright 2011 Weiming Zhao

#### **Recommended Citation**

Zhao, Weiming, "Memory resource balancing for virtualized computing", Dissertation, Michigan Technological University, 2011. https://digitalcommons.mtu.edu/etds/183

Follow this and additional works at: https://digitalcommons.mtu.edu/etds

#### MEMORY RESOURCE BALANCING FOR VIRTUALIZED COMPUTING

By

WEIMING ZHAO

#### A DISSERTATION

Submitted in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

(Computer Science)

#### MICHIGAN TECHNOLOGICAL UNIVERSITY

2011

© 2011 Weiming Zhao

This dissertation, "Memory Resource Balancing for Virtualized Computing," is hereby approved in partial fulfillment of the requirements for the degree of DOCTOR OF PHILOS-OPHY IN COMPUTER SCIENCE.

Department of Computer Science

Signatures:

| Dissertation Advisor |                   |

|----------------------|-------------------|

|                      | Dr. Zhenlin Wang  |

| Committee Member     |                   |

|                      | Dr. Steven Carr   |

| Committee Member     |                   |

|                      | Dr. Steven Seidel |

| Committee Member     |                   |

|                      | Dr. Jindong Tan   |

| Department Chair     |                   |

|                      | Dr. Steven Carr   |

| Date                 |                   |

To my parents and my wife

# Contents

| Li | st of l | Figures                                       |

|----|---------|-----------------------------------------------|

| Li | st of [ | Fables                                        |

| Ac | know    | vledgments                                    |

| Ał | ostrac  | et                                            |

| 1  | Intr    | oduction                                      |

|    | 1.1     | Our Low Cost Working Set Size Tracking Method |

|    | 1.2     | Local Memory Resource Balancing               |

|    | 1.3     | Global Memory Resource Balancing              |

|    |         | 1.3.1 Live Migration Based Global Balancing 5 |

|    |         | 1.3.2 Remote Cache Based Global Balancing 5   |

|    | 1.4     | Dissertation Organization                     |

|    | 1.5     | Summary of Contributions                      |

| 2  | Bacl    | kground And Related Work 9                    |

|    | 2.1     | Memory Management                             |

|    |         | 2.1.1 Memory Management In A Native OS        |

|   |     | 2.1.2                          | Memory Management With Virtualization                        | 10 |

|---|-----|--------------------------------|--------------------------------------------------------------|----|

|   |     |                                | 2.1.2.1 Software-Based Techniques                            | 11 |

|   |     |                                | 2.1.2.2 Hardware-Based Technique                             | 13 |

|   |     | 2.1.3                          | Dynamic VM Memory Allocation Resizing                        | 13 |

|   | 2.2 | Worki                          | ng Set Size Estimation                                       | 14 |

|   |     | 2.2.1                          | Working Set                                                  | 14 |

|   |     | 2.2.2                          | Miss Ratio Curve Based Working Set Size Estimation           | 15 |

|   |     |                                | 2.2.2.1 MRC Tracking                                         | 16 |

|   |     | 2.2.3                          | Other Techniques For Working Set Size Estimation             | 18 |

|   | 2.3 | Virtual                        | I Machine Migration                                          | 19 |

|   | 2.4 | Remot                          | e Memory                                                     | 20 |

|   | 2.5 | Other'                         | Techniques Of Memory Resource Balancing For Virtual Machines | 22 |

|   | 2.6 | Progra                         | m Phases                                                     | 22 |

|   |     | 2.6.1                          | Online Phase Detection                                       | 24 |

| 2 | Ŧ   |                                |                                                              | 25 |

| 3 | Low | Cost Working Set Size Tracking |                                                              |    |

|   | 3.1 | LRU-F                          | Based Working Set Size Estimation                            | 25 |

|   |     | 3.1.1                          | Basic Design of LRU List                                     | 27 |

|   |     | 3.1.2                          | Overhead Analysis                                            | 28 |

|   | 3.2 | AVL-7                          | Tree Based LRU Design                                        | 29 |

|   | 3.3 | Dynan                          | nic Hot Set Sizing                                           | 30 |

|   | 3.4 | Interm                         | ittent Memory Tracking                                       | 31 |

|   |     | 3.4.1                          | Selection of Events                                          | 33 |

|   |     | 3.4.2                          | Phase Detection                                              | 33 |

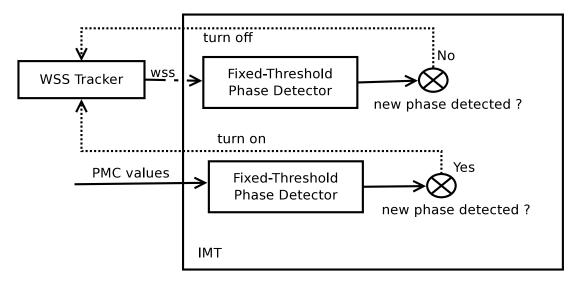

|   |                    |                             | 3.4.2.1 Fixed-Threshold Phase Detection                                | 35                                                  |

|---|--------------------|-----------------------------|------------------------------------------------------------------------|-----------------------------------------------------|

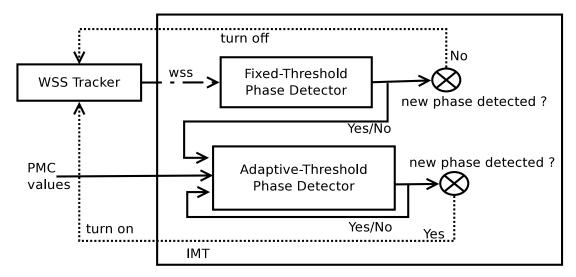

|   |                    |                             | 3.4.2.2 Adaptive-Threshold Phase Detection                             | 36                                                  |

|   | 3.5                | Experi                      | mental Evaluation                                                      | 36                                                  |

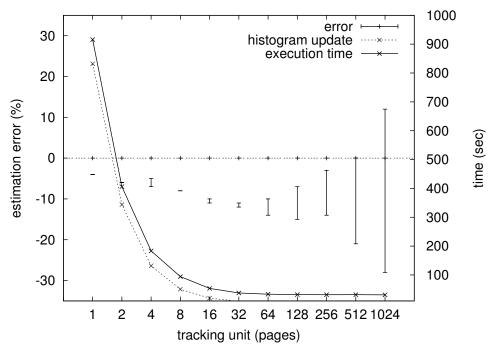

|   |                    | 3.5.1                       | Tracking Granularity                                                   | 37                                                  |

|   |                    | 3.5.2                       | OS-based Vs. LRU-based Memory Growth Estimation                        | 40                                                  |

|   |                    | 3.5.3                       | Working Set Size Estimation                                            | 40                                                  |

|   |                    | 3.5.4                       | Effectiveness of Dynamic Hot Set Sizing and AVL-Tree Based LRU<br>List | 40                                                  |

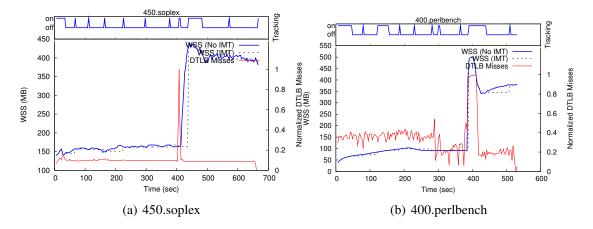

|   |                    | 3.5.5                       | Evaluation of Intermittent Memory Tracking                             | 44                                                  |

|   |                    |                             | 3.5.5.1 Fixed-Threshold Vs. Adaptive-Threshold                         | 44                                                  |

|   |                    |                             | 3.5.5.2 Selection of Hardware Performance Events                       | 46                                                  |

|   |                    | 3.5.6                       | Overhead Revisited                                                     | 47                                                  |

|   |                    |                             |                                                                        |                                                     |

|   | 3.6                | Chapte                      | er Summary                                                             | 49                                                  |

| 4 |                    | -                           | ory Resource Balancing                                                 |                                                     |

| 4 |                    | al Mem                      |                                                                        | 51                                                  |

| 4 | Loca               | al Mem<br>Local I           | ory Resource Balancing                                                 | <b>51</b><br>51                                     |

| 4 | <b>Loca</b><br>4.1 | al Mem<br>Local I<br>Impler | ory Resource Balancing                                                 | <b>51</b><br>51<br>52                               |

| 4 | <b>Loca</b><br>4.1 | al Mem<br>Local I<br>Impler | ory Resource Balancing                                                 | <b>51</b><br>51<br>52<br>53                         |

| 4 | <b>Loca</b><br>4.1 | al Mem<br>Local I<br>Impler | ory Resource Balancing                                                 | <b>51</b><br>51<br>52<br>53<br>53                   |

| 4 | <b>Loca</b><br>4.1 | al Mem<br>Local I<br>Impler | ory Resource Balancing                                                 | <b>51</b><br>51<br>52<br>53<br>53<br>54             |

| 4 | <b>Loca</b><br>4.1 | al Mem<br>Local I<br>Impler | ory Resource Balancing                                                 | <b>51</b><br>51<br>52<br>53<br>53<br>54<br>54       |

| 4 | <b>Loca</b><br>4.1 | al Mem<br>Local I<br>Impler | ory Resource Balancing                                                 | <b>51</b><br>51<br>52<br>53<br>53<br>54<br>54<br>55 |

| 5                                         | Gloł | bal Mer | nory Reso       | ource Bal  | ancing                                                      | 1 |

|-------------------------------------------|------|---------|-----------------|------------|-------------------------------------------------------------|---|

| 5.1 Live Migration Based Global Balancing |      |         | bal Balancing 6 | 1          |                                                             |   |

|                                           |      | 5.1.1   | Informat        | ion Policy | y                                                           | 2 |

|                                           |      |         | 5.1.1.1         | Online N   | Memory Demand Prediction 63                                 | 3 |

|                                           |      |         | 5.1.1.2         | Live Mi    | gration Time Estimation 63                                  | 3 |

|                                           |      | 5.1.2   | Transfer        | Policy .   |                                                             | 4 |

|                                           |      | 5.1.3   | Placeme         | nt Policy  |                                                             | 4 |

|                                           | 5.2  | Remot   | e Caching       | 5          |                                                             | 5 |

|                                           |      | 5.2.1   | Overview        | W          |                                                             | 5 |

|                                           |      | 5.2.2   | Cache C         | lient Desi | gn                                                          | 5 |

|                                           |      | 5.2.3   | Remote          | Cache De   | sign                                                        | 7 |

|                                           |      | 5.2.4   | Manage          | Cache Siz  | ze                                                          | 7 |

|                                           | 5.3  | Experi  | mental Re       | esults     |                                                             | 3 |

|                                           |      | 5.3.1   | Evaluatio       | on of Mig  | ration Based Global Balancing 68                            | 8 |

|                                           |      |         | 5.3.1.1         | Accurac    | y of Migration Time Estimation 68                           | 3 |

|                                           |      |         | 5.3.1.2         | Using M    | Iigration For Global Memory Balancing       69              | 9 |

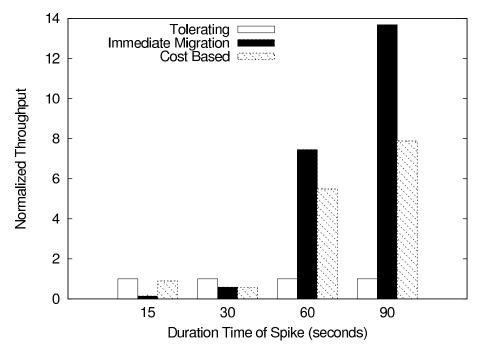

|                                           |      |         | 5               | .3.1.2.1   | Scenario 1: Short Burst of Memory Demand 69                 | 9 |

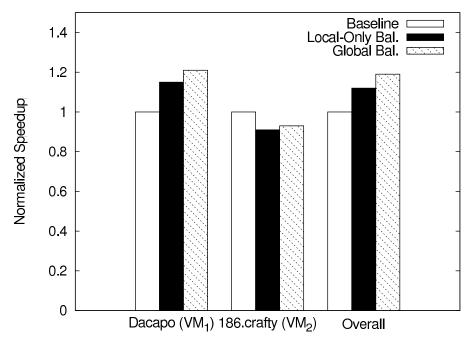

|                                           |      |         | 5               | .3.1.2.2   | Scenario 2: Balancing Two VMs                               | 0 |

|                                           |      |         | 5               | .3.1.2.3   | Scenario 3: Balancing Two VMs with Long Mi-<br>gration Time | 1 |

|                                           |      |         | 5               | .3.1.2.4   | Scenario 4: Balancing Six VMs / Two Hosts 72                | 2 |

|                                           |      |         | 5               | .3.1.2.5   | Scenario 5: Balancing Six VMs / Three Hosts . 72            | 2 |

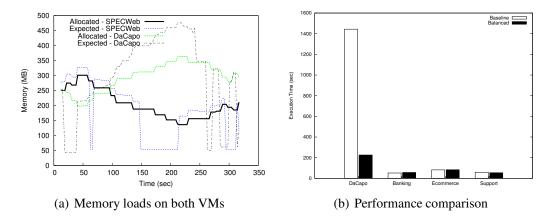

|                                           |      | 5.3.2   | Evaluatio       | on of Rem  | note Cache Based Global Memory Balancing 74                 | 4 |

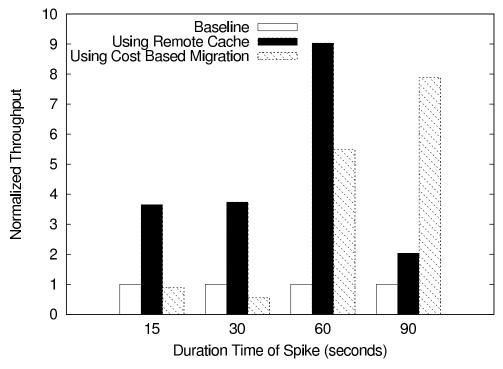

|                                           |      |         | 5.3.2.1         | Penalty    | Alleviation For Memory Spikes                               | 4 |

|   |                   |                  | 5.3.2.2           | Symmetrical Remote Caching            | 75       |

|---|-------------------|------------------|-------------------|---------------------------------------|----------|

|   |                   |                  | 5.3.2.3           | Multiple Cache Clients                | 75       |

|   |                   | 5.3.3            | Putting A         | All Together                          | 76       |

|   | 5.4               | Chapte           | er Summa          | ry                                    | 76       |

|   |                   |                  |                   |                                       |          |

|   |                   |                  |                   |                                       |          |

| 6 | Con               | clusion          |                   |                                       | 79       |

| 6 | <b>Con</b><br>6.1 |                  |                   | · · · · · · · · · · · · · · · · · · · |          |

| 6 |                   | Contri           | butions .         |                                       | 79       |

| Ū | 6.1<br>6.2        | Contri<br>Future | butions .<br>Work |                                       | 79<br>80 |

# **List of Figures**

| 1.1 | Organization of virtualization                                                                                                                                                                                                                                                                                                                                                                                                         | 2  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Solution overview                                                                                                                                                                                                                                                                                                                                                                                                                      | 3  |

| 2.1 | Address spaces in a native OS and a virtualized OS                                                                                                                                                                                                                                                                                                                                                                                     | 11 |

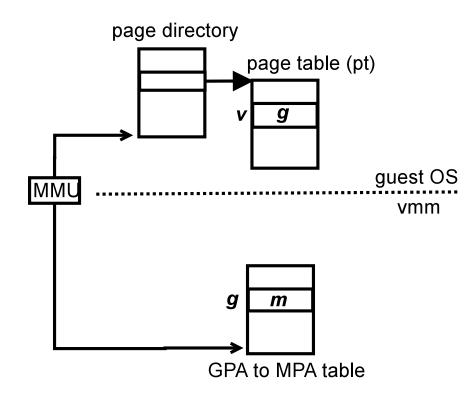

| 2.2 | Examples of address translation                                                                                                                                                                                                                                                                                                                                                                                                        | 12 |

| 2.3 | Address mapping with MMU virtualization                                                                                                                                                                                                                                                                                                                                                                                                | 13 |

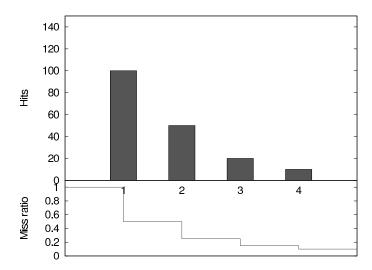

| 2.4 | LRU histogram example                                                                                                                                                                                                                                                                                                                                                                                                                  | 16 |

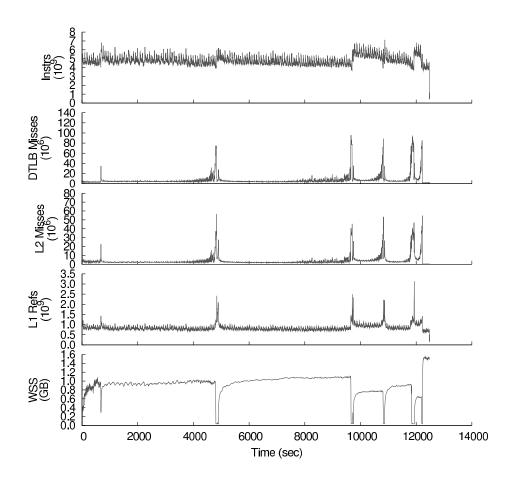

| 2.5 | Phases of 429.mcf                                                                                                                                                                                                                                                                                                                                                                                                                      | 23 |

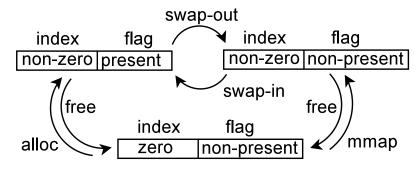

| 3.1 | Transitions of PTE states                                                                                                                                                                                                                                                                                                                                                                                                              | 27 |

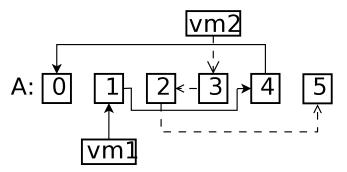

| 3.2 | An example of LRU lists                                                                                                                                                                                                                                                                                                                                                                                                                | 28 |

| 3.3 | An example of AVL-based LRU list                                                                                                                                                                                                                                                                                                                                                                                                       | 29 |

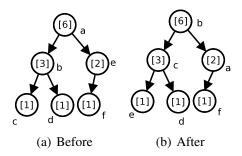

| 3.4 | Hot set management. Suppose an access to physical page $p_a$ is trapped.<br>Then the permission in the corresponding PTE in page table $PT_1$ is restored<br>and the address of the PTE is added to the PTE table. Next, $p_a$ is enqueued<br>and $p_b$ is dequeued. Use $p_b$ to index the PTE table and locate the PTE of<br>page $p_b$ . The permission in the PTE of page $p_b$ is revoked and page $p_b$<br>becomes <i>cold</i> . | 30 |

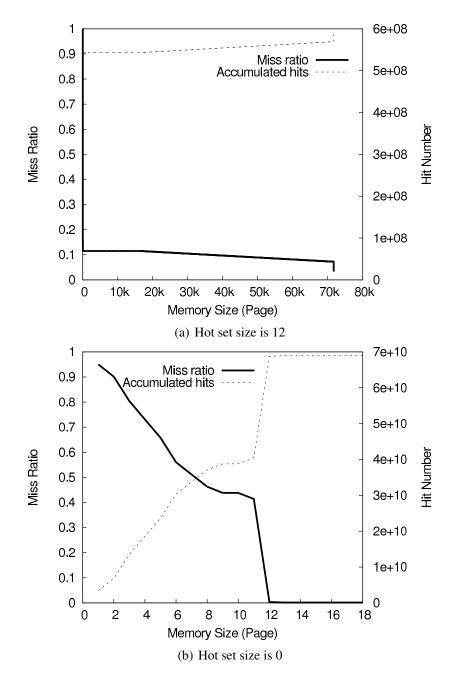

| 3.5 | Miss ratio curve of 171.swim                                                                                                                                                                                                                                                                                                                                                                                                           | 32 |

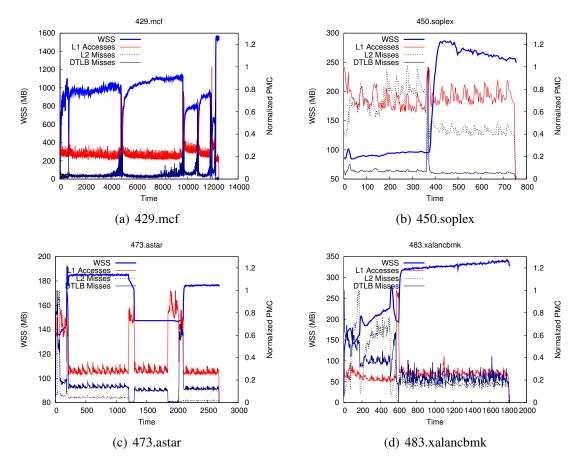

| 3.6 | Examples of WSS and performance events                                                                                                                                                                                                                                                                                                                                                                                                 | 34 |

| 3.7 | Fixed-threshold IMT                                                                                                                                                                                                                                                                                                                                                                                                                    | 35 |

| 3.8  | Adaptive-threshold IMT                                                                                                                                                                                                              | 37 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

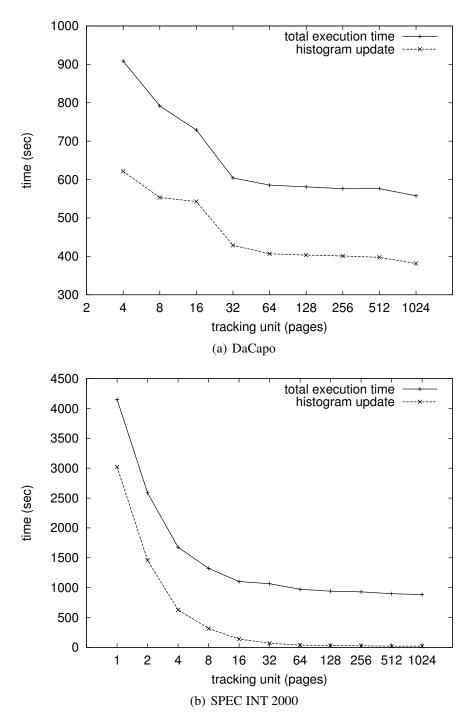

| 3.9  | Relationship between tracking unit, accuracy and overhead                                                                                                                                                                           | 38 |

| 3.10 | Relationship between tracking unit and performance                                                                                                                                                                                  | 39 |

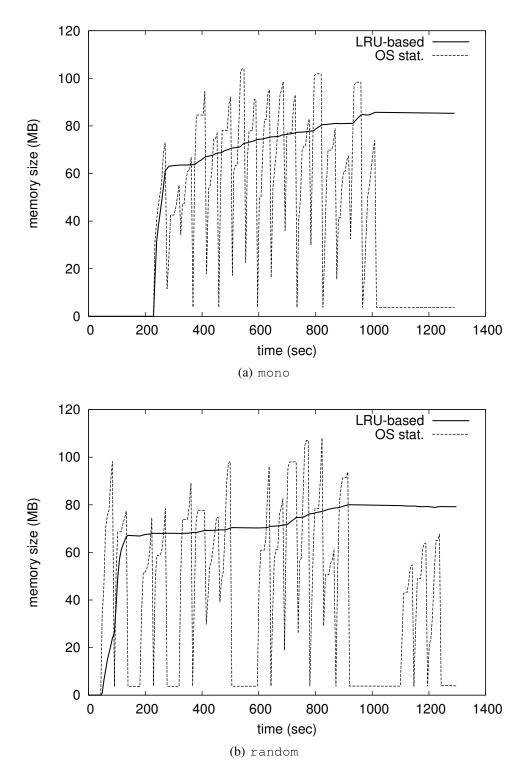

| 3.11 | Swap LRU vs. swap usage                                                                                                                                                                                                             | 41 |

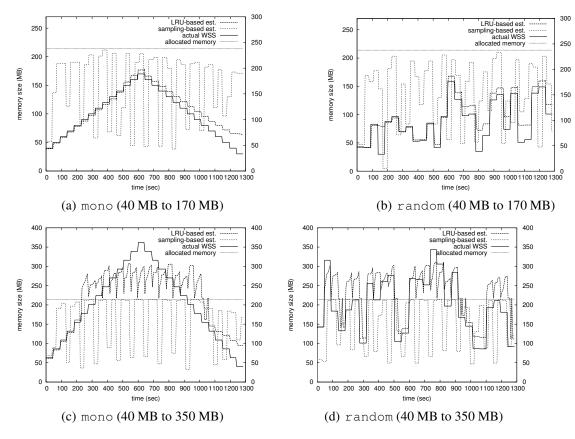

| 3.12 | WSS estimation                                                                                                                                                                                                                      | 42 |

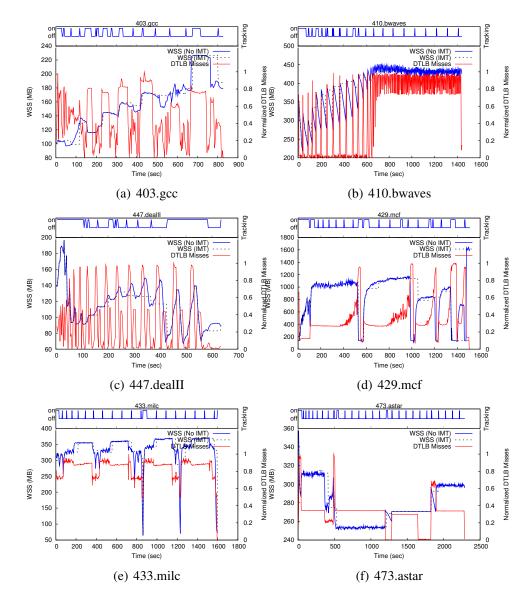

| 3.13 | Examples of using adaptive-thresholds IMT (simple cases)                                                                                                                                                                            | 46 |

| 3.14 | Examples of using adaptive-thresholds IMT (common cases)                                                                                                                                                                            | 47 |

| 3.15 | Examples of using adaptive-thresholds IMT (special cases)                                                                                                                                                                           | 48 |

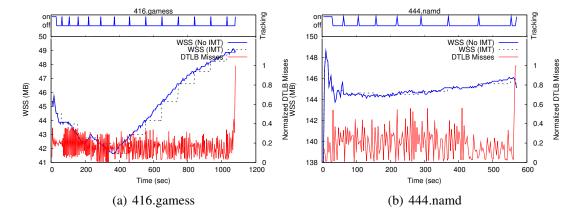

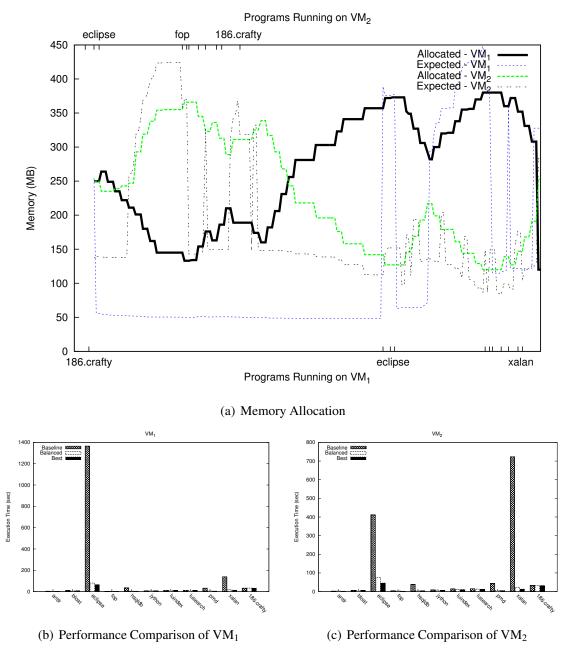

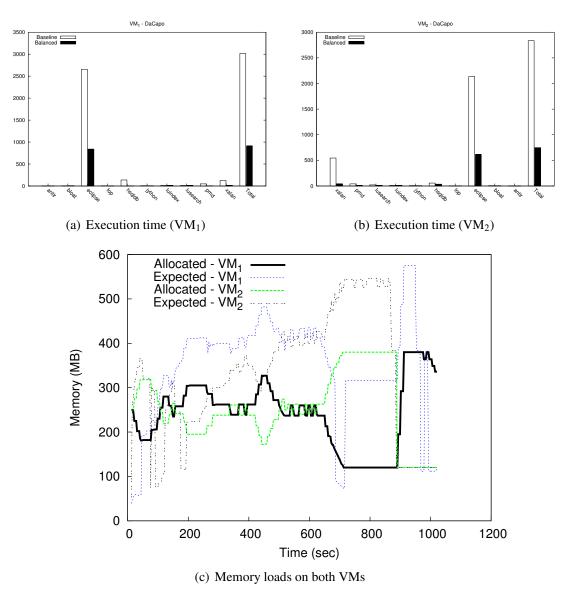

| 4.1  | Local memory resource balancing: DaCapo + 186.crafty. For read-<br>ability, in Fig. 4.1(a), only a few program names of DaCapo are labeled.<br>Fig. 4.1(b) and 4.1(c) show the complete program names in the order of<br>execution. | 55 |

| 4.2  | DaCapo + SPEC Web                                                                                                                                                                                                                   | 56 |

| 4.3  | DaCapo + DaCapo'                                                                                                                                                                                                                    | 57 |

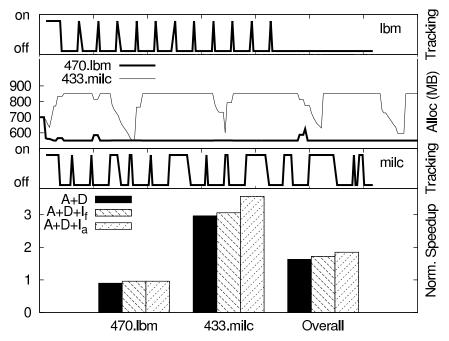

| 4.4  | Memory balancing of 470.1bm and 433.milc                                                                                                                                                                                            | 58 |

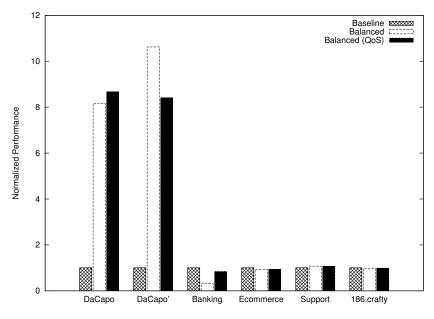

| 4.5  | Performance comparison: DaCapo + DaCaPo' + 186.crafty + SPEC Web                                                                                                                                                                    | 58 |

| 5.1  | Overview of remote caching                                                                                                                                                                                                          | 66 |

| 5.2  | Performance of SPEC JBB with 12 warehouses using migration                                                                                                                                                                          | 70 |

| 5.3  | Performance comparison: DaCapo and 186.crafty                                                                                                                                                                                       | 71 |

| 5.4  | Throughputs comparison of SPEC JBB with 12 warehouses                                                                                                                                                                               | 74 |

# **List of Tables**

| 3.1 | Overhead reduction with DHS and ABL                                   | 43 |

|-----|-----------------------------------------------------------------------|----|

| 3.2 | Up ratios and MREs of various fixed-thresholds and adaptive-threshold | 45 |

| 3.3 | Effects of different hardware performance events and policies         | 48 |

| 3.4 | Overhead reduction and up ratios of IMT                               | 50 |

| 4.1 | Major page faults and execution time                                  | 54 |

| 5.1 | Migration time estimation                                             | 68 |

| 5.2 | Speedups of SPEC JBB                                                  | 72 |

| 5.3 | Speedups of using migration for 6 VMs on 2 hosts                      | 73 |

| 5.4 | Speedups of using migration for 6 VMs on 3 hosts                      | 73 |

| 5.5 | DaCapo + DaCapo': performance of using remote cache                   | 75 |

| 5.6 | Performance of using shared cache server and dedicated cache server   | 76 |

| 5.7 | Speedups of global balancing for 6 VMs on 2 hosts                     | 77 |

## Acknowledgments

Foremost, I owe my deepest gratitude to my advisor, Dr. Zhenlin Wang for the continuous research guidance, for his patience, motivation, enthusiasm, immense knowledge in my Ph.D. study and research. His guidance helped me in all the time of research and writing of this dissertation. I appreciate all his contributions of time, ideas and funding to make my Ph.D. experience productive and stimulating. I could not have imaged having a better advisor and mentor for my Ph.D. study.

My sincere thanks also go to Dr. David Poplawski, for his invaluable guidance and encouragement on my two-year's teaching experience. Before I came to Michigan Tech, I had no idea at all about how to lecture a course. I still remember how nervous I was when I first stood at the classroom. But in the next year, I built the confidence and even started to enjoy the lecturing, which would not happen without Dr. Poplawski's support and mentoring.

I also would like to thank the rest of my thesis committee: Dr. Steven Carr, Dr. Steven Seidel and Dr. Jingdong Tan, for their kind help and valuable comments on this work.

Last but not the least, I would like to thank my parents for giving birth to me at the first place and supporting me spiritually throughout my life.

xviii

## Abstract

Virtualization has become a common abstraction layer in modern data centers. By multiplexing hardware resources into multiple virtual machines (VMs) and thus enabling several operating systems to run on the same physical platform simultaneously, it can effectively reduce power consumption and building size or improve security by isolating VMs.

In a virtualized system, memory resource management plays a critical role in achieving high resource utilization and performance. Insufficient memory allocation to a VM will degrade its performance dramatically. On the contrary, over-allocation causes waste of memory resources. Meanwhile, a VM's memory demand may vary significantly. As a result, effective memory resource management calls for a dynamic memory balancer, which, ideally, can adjust memory allocation in a timely manner for each VM based on their current memory demand and thus achieve the best memory utilization and the optimal overall performance.

In order to estimate the memory demand of each VM and to arbitrate possible memory resource contention, a widely proposed approach is to construct an LRU-based miss ratio curve (MRC), which provides not only the current working set size (WSS) but also the correlation between performance and the target memory allocation size. Unfortunately, the cost of constructing an MRC is nontrivial. In this dissertation, we first present a low overhead LRU-based memory demand tracking scheme, which includes three orthogonal optimizations: AVL-based LRU organization, dynamic hot set sizing and intermittent memory tracking. Our evaluation results show that, for the whole SPEC CPU 2006 benchmark suite, after applying the three optimizing techniques, the mean overhead of MRC construction is lowered from 173% to only 2%.

Based on current WSS, we then predict its trend in the near future and take different strategies for different prediction results. When there is a sufficient amount of physical memory on the host, it locally balances its memory resource for the VMs. Once the local memory resource is insufficient and the memory pressure is predicted to sustain for a sufficiently long time, a relatively expensive solution, VM live migration, is used to move one or more VMs from the hot host to other host(s). Finally, for transient memory pressure, a remote cache is used to alleviate the temporary performance penalty. Our experimental results show that this design achieves 49% center-wide speedup.

## Chapter 1

## Introduction

Virtualization is becoming pervasive in massive data centers, cloud computing, and enterprise infrastructure, driven by a number of important benefits, such as dramatic cost reduction, increased application availability and more efficient IT administration. According to Gartner (16), today, 25% of installed server workloads are virtualized. IDC even forecasts that, by 2014, more than 70% of applications on newly shipped servers will run in virtual machines (29). However, in a virtualized environment, efficient and effective memory resource management is still a challenging problem. In this dissertation we propose a memory resource balancing scheme to improve performance and memory resource utilization for center-wide virtualized computing. We demonstrate that our solution can accurately monitor memory demand of each virtual machine with very low overhead and can effectively improve overall system performance.

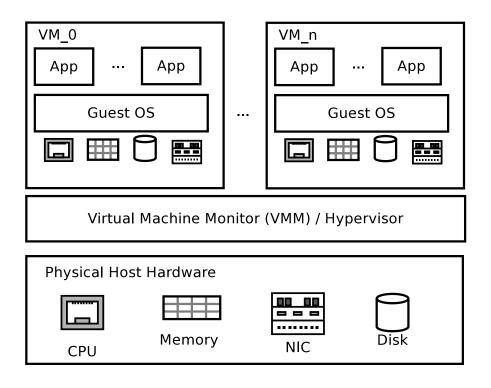

Virtualization technologies like Xen(9), VMware(54), and Denali(56) have become a common abstraction layer in modern data centers. They enable multiple operating systems to run on their own virtual machines independently. Figure 1.1 shows an example, where the hypervisor multiplexes the hardware of a single physical machine with several virtual machines and a guest OS runs inside each virtual machine independently. One of the main advantages of using virtualization is server consolidation. It is not uncommon to achieve a 15-to-1 or even higher *consolidation ratio* (11), which is the ratio of virtual to physical machine without disruptive performance impact. For a data center that hosts a large number of servers, this can effectively save power consumption, floor space occupancy and air conditioning costs. Besides, virtualization can improve availability by live migration (15). When one physical server fails or needs maintenance, the virtual machines it hosts can be transparently migrated to another physical machine with negligible application downtime.

The core of virtualization is the *virtual machine monitor* (VMM), which is also called *hypervisor*. VMM is responsible for creating and managing multiple instances of virtual hardware platforms. A lot of physical resources like CPUs or network interface cards can

Figure 1.1: Organization of virtualization

be multiplexed in a time-sharing manner, which is similar to how multiple processes of a native OS would share them. However, the memory system is shared through address space partitioning. That is, each virtual machine is allocated with a fixed amount of address space of physical memory. However, differing from how a native OS manages virtual memory and physical memory for its processes, for the purpose of fidelity, the VMM is not actively involved in memory management of each VM. More specifically, when created, each VM is allocated with a fixed amount of physical memory. Then, it is the guest OS's responsibility to manage that amount of physical memory without the involvement of the hypervisor. As a result, the hypervisor is unaware of memory demand of VMs and thus unable to dynamically balance memory resources.

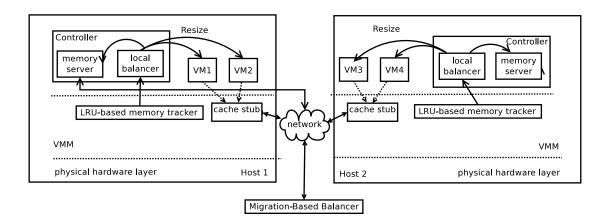

In our solution, we first design a low cost but accurate LRU-based working set size tracking scheme as the foundation of memory resource balancing. The LRU-based working set size model correlates memory allocation size and performance impact. Based on the model, we design a local memory balancing scheme, which dynamically adjusts memory allocation amount via ballooning (54, 9) on a single physical machine. Then it is extended to a global environment, where the physical memory of all interconnected machines is balanced via live migration and remote caching. To the best of our knowledge, our work uniquely coordinates the global memory balancing techniques with a local balancing scheme. Without effective local memory balancing, the effectiveness of global memory balancing will be significantly weakened. Figure 1.2 shows the overview of our solution.

Figure 1.2: Solution overview

## 1.1 Our Low Cost Working Set Size Tracking Method

A widely proposed method to guide memory resource allocation is the LRU-based miss ratio curve (MRC) (38, 12, 67, 60, 30, 51) that plots memory access miss ratios versus various physical memory amount. When the memory resources of a system are well balanced, the number of its page fault occurrences is minimal and thus it achieves optimal performance. Unfortunately, the cost of maintaining an MRC is nontrivial. For example, our experiments show that, a straightforward implementation of the MRC brings a mean overhead of 173% for SPEC CPU 2006 benchmark suite.

To minimize the overhead, we introduce three optimizations (65, 66):

- 1. An AVL-tree-based implementation of LRU list, denoted as *ABL*. Typically, an LRU list is implemented by a linked list. However, it requires a linear search to find a node's *LRU distance*, which is the distance of the node from the head of the list to its current position. In our implementation, nodes are organized into an AVL-tree in such a way that a pre-order traversal of the tree gives the same sequence as given by traversing the linked list. With the help of an auxiliary field in each node, we can find a node's LRU distance by traversing from the current node to the root of the tree, which takes  $O(\log N)$  time instead of the O(N) time of using linked list, where N is the memory allocation size of the monitored VM.

- 2. Dynamic hot set sizing, denoted as *DHS*. *Hot set* is the set of pages that are most recently accessed and intercepted. In order to construct the MRC, a sufficient number of memory accesses need to be intercepted to acquire the addresses of their access targets. To avoid excessive interceptions that may cause significant overhead, after each interception, the accessed page is put into the hot set. Subsequent accesses to the pages in the hot set will not be intercepted until they are evicted from the hot

set. When a hot set is full, the oldest page is evicted. Hence, the larger the size of a hot set, the less the memory accesses are intercepted and vice versa. However, increasing the hot set also lowers the accuracy of the MRC. Our design is able to dynamically adjust hot set size to balance between overhead and accuracy. In some cases, if the hot set size exceeds the working set size, it substantially overestimates the memory demand. Our design can also detect such pathological cases and then adjust the estimation result.

3. Intermittent memory tracking, denoted as *IMT*. Most programs exhibit phasing behaviors in terms of IPC, branch prediction miss rates, and memory demand, etc. That is, the metrics are stable within a period while there exist disruptive transitions between the periods. Exploiting this attribute, we design an intermittent tracking scheme, which is able to turn off memory tracking when the monitored VM enters a stable phase and re-enable it when a new phase is encountered. Experimental results show that, by using this intermittent tracking design, memory tracking can be turned off for 82% of the execution time while accuracy loss is no more than 4%.

The three optimization techniques are orthogonal to each other. When combined together, the mean overhead is lowered to only 2%.

### **1.2 Local Memory Resource Balancing**

Based on the working set size tracking scheme, we design a local memory resource balancer, which dynamically adjusts physical memory allocation of all VMs of a single physical machine to improve overall performance (64). By analyzing a VM's miss ratio curve, its performance impact with respect to various memory allocation sizes can be estimated. This provides the necessary information for arbitration when multiple VMs compete for memory resources. Though there exists an allocation plan that brings the best overall performance, finding an optimal solution requires brute force searching of nearly  $O(M^V)$  time, where M is the total allocable memory size and V is the number of VMs to be balanced. We propose a quick heuristic based algorithm, which can find the near optimal solution in O(M) time.

Experimental results demonstrate that, on a host with 2 VMs, when both VMs run a CPU intensive workload and a memory intensive workload in an interleaved way, our local memory balancer reduces the total number of page faults by a factor of 25. As a result, the performance of the memory intensive workload is boosted by 11 and 8 times, respectively, while the execution time of CPU intensive workload is nearly unaffected. Even in a complicated case, in which 4 VMs with mixed workloads compete for memory during the execution, it still achieves an overall speedup of 1.72.

### **1.3 Global Memory Resource Balancing**

Although local memory balancing improves memory utilization of a single host, from the perspective of the whole data center, memory resource imbalance may still exist. It is quite often that some hosts suffer from memory overloading while others have idle memory, which calls for a global memory balancer. On the other hand, local memory balancing reclaims free memory, which is the base of global memory balancing.

We propose two mechanisms to balance center-wide global memory resources: live migration based balancing and remote cache based balancing, which is close to the idea of Williams *et al.* (57). A major distinction between them is whether free memory is dynamically reclaimed or not. In the work of Williams *et al.*, the memory used for global balancing is statically reserved, while in our work, the local memory balancer dynamically reclaims idle memory and utilizes them for global balancing. As a result, our scheme can achieve higher memory resource utilization. In addition, the decision making algorithm of migration is different too. More details will be discussed in Section 2.5.

#### **1.3.1** Live Migration Based Global Balancing

Using live virtual machine migration (15), VMs can be moved from one host to other hosts with negligible service downtime, given that all VMs share network storage systems, which is commonly seen in a data center. This allows us to move VMs from the memory overloaded host to others with sufficient free memory and thus improve global memory utilization. Unfortunately, migration is an expensive operation. Thus, we design a heuristic based algorithm which initiates migration only if the memory pressure is predicted to sustain for enough long time.

#### **1.3.2 Remote Cache Based Global Balancing**

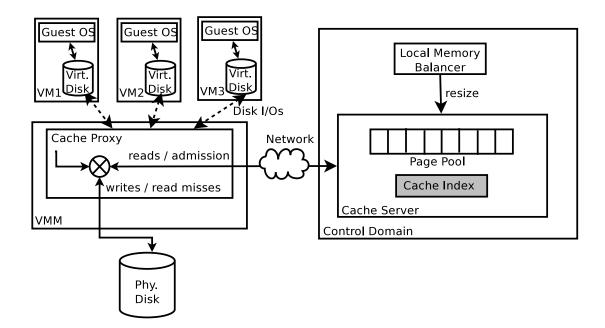

At the other end of the spectrum is burst memory pressure. Even if a host has enough free memory, the local balancer may not response so quicly to completely eliminate page swapping. Based on the fact that for page level data transferring, the latency of a 1 Gbps Ethernet is about 1 to 2 orders of magnitude lower than disk I/O (14), we design a remote cache to convert relatively slow disk I/Os to faster network transfer. As shown in Figure 1.2, disk I/Os are intercepted by VMM and then the requests are sent to a remote host. The remote host runs a sizable memory server, which works as a disk cache. The local memory balancer on the remote host manages the capacity of its cache to ensure that only free memory will be used to serve other hosts.

## **1.4 Dissertation Organization**

The rest of this dissertation is organized as follows. In Chapter 2, we briefly cover relevant background knowledge and discuss related work.

In Chapter 3, our low cost LRU-based working set size tracking scheme is presented. We then describe our implementation and experimental results.

In Chapter 4, we describe how we use the tracked working set size information to balance memory resources for all VMs on a single host. We show that our local balancing can significantly boost overall performance.

In Chapter 5, we first design a migration based global balancing mechanism to solve long term memory imbalance. We then present a remote cache based global balancing scheme to mitigate the performance penalty when spikes of memory demand occur or when migration is impossible.

We conclude this dissertation in Chapter 6 by discussing the limitations and possible future work.

## **1.5 Summary of Contributions**

We make the following contributions in this dissertation:

- 1. A novel low cost LRU-based WSS estimation scheme which employs a more efficient data structure and exploits hardware performance counters to construct LRU-based miss ratio curve and accurately estimate the current WSS of a VM.

- 2. A memory balancing mechanism to dynamically adjust the amount of each VM's memory allocation to improve performance.

- 3. An algorithm to predict memory trend and decide when to apply VM migration to improve global memory resource utilization.

- 4. A design of remote cache that uses free memory of a remote host to alleviate the impacts of a burst of memory requirement.

We implement all the design on an open source hypervisor and demonstrate that our WSS estimator can effectively and efficiently track working set size. And the local balancer is able to boost performance. Even when there exists significant memory contention, the

overall performance can be improved. And the experimental results also reveal that our global memory balancer can further improve system performance.

## Chapter 2

## **Background And Related Work**

This chapter discusses background materials and related work. It first describes the most pertinent background knowledge about how memory is managed under virtualization and discusses various approaches to estimate memory demand. It then discusses virtual machine migration and existing studies about remote memory, the two schemes that can be applied to global memory balancing, followed by extensive research on memory balancing for virtual machines. Finally, the background and related work about program phases are discussed.

### 2.1 Memory Management

In this section, we first briefly introduce how memory is managed in a native operating system. Then we describe how memory management is adapted for virtualization and the challenges that virtualization brings.

#### 2.1.1 Memory Management In A Native OS

Virtual memory was first described in 1960s (21) and it has become a standard feature of modern general-purpose operating systems. It gives each process an illusion that it is running on a standalone and contiguous memory address space, called *virtual address space*. The size of a virtual address space can be larger than the amount of available real, physical memory. Typically, memory is allocated and reclaimed at a fixed granularity, called *page*, whose size is determined by processor architecture. Both virtual address space and physical address space are measured at the unit of page size. Inside the operating system, it maintains a translation table for each process, named *page table*, which maps a

virtual page number to a physical page frame number. Inside a processor, there is a *memory management unit* (MMU) that dynamically translates virtual addresses that an application references to the corresponding physical addresses by looking up the current page table.

When a system runs out of physical memory, and if some process requests for a free page, the OS selects some physical frame, saves its contents on a secondary storage (called *swapping-out* or *paging-out*) and allocates the page to the process. Later on, if the previously paged out data is needed, it is loaded into a free physical memory frame, which is called *paging-in* or *swapping-in*. This page swapping scheme is called *demand-paging*. The strategy that determines which pages are swapped out is called *page replacement policy*.

Since the latency of disk accesses is usually thousands of times longer than that of memory accesses, frequent page swapping will significantly damage the performance. A theoretically optimal page replacement policy should select a page whose next use will be the farthest in the future (2). However, in a general purpose OS, it is impossible to precisely predict the future memory access behaviors. In real world, a commonly used algorithm is the *least recently used (LRU)* replacement policy or its approximation. It works based on the property of program locality. That is, the pages that have been heavily and recently used are also most likely to be heavily used in near future. For an OS that uses demand-paging and the LRU page replacement policy, a process that heavily uses a set of pages will automatically secure those pages in physical memory.

#### 2.1.2 Memory Management With Virtualization

To create a virtualized environment, the hypervisor runs at the most privileged level that a native OS runs at. For CPUs without virtualization support, guest OSes and its processes run at the non-privileged level. Those privileged operations in the guest OS, such as page table setup, I/O instructions and etc. are either statically replaced with calls to the hypervisor or dynamically trapped and emulated via binary rewriting by the hypervisor. With hardware virtualization support, an unmodified guest OS runs on the CPU directly without intervention by the VMM until it tries to execute a restricted instruction. At this point, the hypervisor takes the control to emulate the instruction.

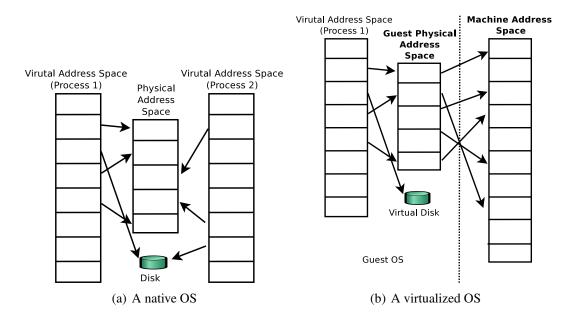

When an operating system runs on the top of hypervisor, another level of memory address space, *guest physical address (GPA)* space, is introduced. To avoid confusion, in virtualization, the real physical address is specifically referred as *machine physical address (MPA)*. GPA is used by guest OSes in their physical address space. The purpose of using GPA is to provide the guest OS the impression that it is running on a real machine with certain amount of contiguous physical memory starting from address 0 because there is no guarantee that every guest OS will be allocated with contiguous machine memory and most OSes

Figure 2.1: Address spaces in a native OS and a virtualized OS

do not support fragmented physical address space. The size of the GPA space of an OS is the same as the amount of machine memory that the hypervisor statically allocates to the guest OS when it is created. Meanwhile, the hypervisor maintains a mapping table to map the contiguous GPA space to the possibly scattered MPA space. Figure 2.1 contrasts the address spaces between a native OS and a virtualized OS.

To support the translation from GPA to MPA, currently there are two kinds of approaches based on whether the processor supports MMU virtualization or not (1, 53, 39): two software-based techniques and a hardware-based approach.

#### 2.1.2.1 Software-Based Techniques

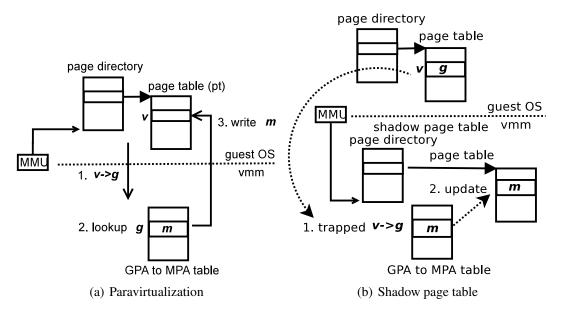

Without hardware assistance to automatically translate GPA to MPA, two software-based approaches, *paravirtualization* and *shadow page table* are used. Since the processor only supports VA to MPA translation, the hypervisor has to translate GPA to MPA and setup the page tables.

Using paravirtualization, the guest OS is modified to make explicit requests to its hypervisor for page table updating. For example, when the guest OS attempts to map a virtual address v to its guest physical address g, instead of directly updating its page table, it delegates the operation to its hypervisor. When the hypervisor receives the request, it first finds the corresponding machine address m for g by looking up its GPA-to-MPA table, and then it fills up page table entry of v with m. As a result, when the guest OS accesses v, the

Figure 2.2: Examples of address translation

The two figures show the operations when the guest OS attempts map a virtual address v to a guest physical address p that corresponds to a machine address m, using paravirtualization and shadow page table, respectively

MMU will map it to m. Figure 2.2(a) illustrates the operations. This approach is adopted by Xen (9). It is highly efficient but requires some modifications to the guest OS kernel.

An alternative technique is the shadow page table, which is adopted by VMware ESX(54). In this scheme, there exist two sets of page tables, one is used by the guest OS for VA to GPA mapping, and the other one is maintained by hypervisor and used by MMU, named shadow page tables, that maps VA to MPA directly. The shadow page tables are invisible to guest OSes while the page tables used by guest OSes are not used by the processor. With hardware assistance or binary code rewriting, all page table creations or updates from guest OSes will be trapped by the hypervisor and it will then update its shadow page tables accordingly. For instance, as Figure 2.2(b) shows, when a guest OS maps a virtual address v to a guest physical address g by updating its page table, this operation is intercepted by the hypervisor. The hypervisor then finds the machine address m for g by looking up its GPA-to-MPA table and sets up a mapping of v to m in the corresponding shadow page table. Since only the shadow page table is exposed to the MMU, an access to v will be mapped to the machine address m. On x86/x86-64 platform, both the first generation virtualization technologies from Intel and AMD, named VT-x(53) and AMD-V(6), respectively, support the interception of page table updating but are lack of hardware assisted MMU virtualization.

Figure 2.3: Address mapping with MMU virtualization

#### 2.1.2.2 Hardware-Based Technique

In the second generation virtualization technology, Intel and AMD introduce *Extended Page Table* and *Rapid Virtualization Indexing*, respectively. Both of them support MMU virtualization, with which, both the page tables in the guest OS and the GPA-to-MPA mapping table are exposed to MMU, as illustrated by Figure 2.3. Given a VA, the hardware will first index the page tables used by the guest OS to get the GPA, and then index the set of page tables provided by the hypervisor to map the GPA to MPA.

Note that, no matter which technique is used, the hypervisor is only responsible for assisting the mapping from GPA to MPA. It does not involve in memory management, such as page allocation, reclaiming or swapping. Therefore, the hypervisor has little knowledge about its VMs' memory utilization.

#### 2.1.3 Dynamic VM Memory Allocation Resizing

The memory allocation size of a VM is determined when it is created. Resizing physical memory allocation of a guest OS in runtime is similar to changing physical memory

amount to a native OS without rebooting, which is nontrivial and not well supported by most OSes. Though memory hot plugging, a mechanism that allows plugging/unplugging DIMMs physically, has been proposed (24, 42), it is not widely adopted by most OSes. Even it is supported by some OSes, it is not suitable for VM memory resizing because of its high cost and coarse granularity. To perform a DIMM unplugging, the OS has to migrate pages to gather those scattered free pages into a contiguous, DIMM-aligned address space, which is an expensive operation. Besides, hot plugging/unplugging usually works on a large granularity.

Waldspurger proposes the *ballooning* (54) mechanism, which has been widely adopted for VM memory resizing. The "balloon" is installed into the guest OS as a kernel space driver. To decrease an OS's memory allocation by n pages, the hypervisor instructs the balloon to "inflate" by n pages. The driver then applies for n pages from the guest OS. From the guest OS's perspective, those pages are owned by the driver. But actually, those pages are reclaimed by the hypervisor and can be allocated to other VMs. Similarly, releasing memory from the ballooning driver restores the memory allocation for a VM. As the balloon is completed deflated, the allocation amount of the guest OS is just the same as it sees during the boot time, which is the upper bound of its resizing range. And the lower bound of the resizing range is determined by how many pages the balloon driver can apply for. Theoretically, all user-owned pages can be reclaimed by swapping them out but it may result in system unstability.

One advantage of the ballooning mechanism is that it takes advantage of a guest OS's knowledge about which pages are the most suitable for reclaiming.

### 2.2 Working Set Size Estimation

In this section, we first introduce the concept of working set. We then discuss various techniques to estimate the size of a working set.

#### 2.2.1 Working Set

Denning (17) first defined the working set as the set of memory pages referenced by a process during a time interval. The size of the working set (WSS) is the amount of memory that a process needs without paging. Even if the process has very large memory footprint, those pages not in its working set can be reclaimed without performance penalty. The same idea can be extended to VMs. Assuming a guest OSes can well utilize their allocated physical memory, and if the memory allocation amount of each VM is exactly its WSS, then the physical memory allocation on the host is optimal. Therefore, working set size estimation provides a necessary metric that ensures the system to reach the maximum performance as expected.

#### 2.2.2 Miss Ratio Curve Based Working Set Size Estimation

The miss ratio curved (MRC) based WSS estimation is a widely proposed technique (38, 13, 67, 60, 30, 51). A page miss ratio curve plots the page miss ratios against various amount of memory allocation. When the allocation size is no less than a system's WSS, the miss ratio is 0, which means all accesses will hit in main memory. When the allocation size is less than its WSS, the MRC tells the ratio of many accesses that will cause page swapping. With an MRC, we can redefine WSS as the size of memory that results in less than a predefined tolerable page miss rate. Since an MRC models the performance and memory allocation size, it is especially suitable for memory resource arbitration. For example, when two applications compete for memory resources, in order to achieve optimal overall performance, the arbitration scheme needs to evaluate how the performance would be impacted by varying their allocation sizes

A commonly used method to calculate MRC is Mattson's stack algorithm (38). It was initially proposed to reduce the time of trace-driven cache simulation. The algorithm uses an LRU stack to store the page numbers of accessed page frames. For each entry of the LRU stack, its distance to the top of the stack is called *stack distance* or *LRU distance*. Each stack entry *i* is associated with a counter, denoted as Hist(i). When a page is referenced, the algorithm first searches the page number in the stack and computes it stack distance, *dist*. It then increments the hit counter Hist(dist) by one. Finally, it updates the stack by moving the page number to the top of the stack. One can plot an *LRU histogram* by relating each counter value to its corresponding LRU distance.

If there is a stack with depth D and we reduce it to depth d, then the expected miss ratio can be calculated as follows:

$$Miss\_ratio(d) = \frac{\sum_{i>d}^{D} Hist(i)}{\sum_{i=0}^{D} Hist(i)}$$

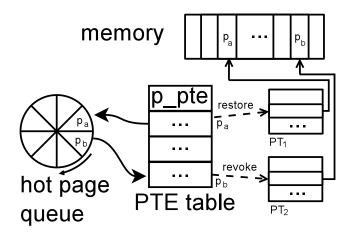

For example, given a system with only four pages of physical memory, the top half of Figure 2.4 shows the hit counts for some application that makes a total of 200 memory accesses. The histogram indicates that 100 accesses hit the most recently used (MRU) page, 50 accesses hit the second MRU slot, and so on. Apparently the page hit rate is (100 + 50 + 20 + 10)/200 = 90%. We can tell that if we reduce the system memory size

Figure 2.4: LRU histogram example

by a half, the hits to the first two MRU slots are still there while the hits to the next two MRU slots now become misses. The hit rate becomes (100+50)/200 = 75%. The LRU histogram thus can accurately predict miss rate with respect to the LRU list size. The bottom part of Figure 2.4 is the miss ratio curve corresponding to the histogram on the top.

#### 2.2.2.1 MRC Tracking

Since the Matterson's algorithm was originally used for off-line analysis, to track the MRC at runtime, it needs to collect sufficient amount of memory access addresses.

Zhou et al. (67) propose two approaches to capture memory accesses and construct page MRC for an application. The first is a hardware approach, where an MRC monitor is connected to the memory bus to track all memory accesses. For efficiency, pages are grouped into multiple page groups and pages in the same group are assumed to have the same stack distance. Thus, MRC is constructed at the granularity of page group. The MRC monitor consists of three array-like components: an array that servers as the LRU stack where each entry is doubly linked, a hit counter array, and a group header array that keeps the heads of page groups. Since the MRC monitor snoops physical memory accesses without capturing context switching, it tracks the MRC of the entire system. Though this approach has little runtime overhead, it is unavailable on current commodity processors. The second approach is called OS approach, which is implemented in an OS and requires no extra hardware support. Though the components of the MRC monitor can be easily implemented in software, it is challenging to acquire enough memory accesses. To solve this problem, it partitions the physical pages into two groups: frequently accessed pages and infrequently accessed pages. For the first group, it scans the "accessed" bit of page tables. For the second group, it uses page protection techniques to detect references to those pages. That is, the OS revokes access permission for them. As a result, an access to such a page will be trapped as a protection fault. One difference between the OS approach and the hardware approach is that, in the former one, it constructs MRC based on virtual page numbers, while in the later one, MRC is constructed based on physical page numbers.

Based on the OS approach of Zhou et al., Yang et al. present an MRC based virtual memory manager that tracks WSS of a garbage-collected application and computes the appropriate heap size to improve the application's performance(60, 59). In their work, the MRC implementation is improved by attaching an AVL tree to the page list to accelerate LRU distance computing. Specifically, each leaf node of the tree points to up to k consecutive pages of the linked list of size N and each non-leaf node of the tree records the total number of pages of its subtree. Therefore, there are  $\lceil \frac{N}{k} \rceil$  number of leaf nodes. To find a page's LRU distance, it first searches linearly to find the page's position within the group, which takes O(k) time. It then walks up the AVL tree and counts the number of pages that are positioned before the accessed page, which takes  $O(\log \lfloor \frac{N}{k} \rfloor)$  time. When a page of LRU distance *i* is accessed, it needs to be moved to the head of the linked list. However, if the leaf nodes that correspond to the first i-1 pages of the linked list are already full, after the moving, those leaf nodes need to be updated to guarantee that each of them points to no more than k pages. Otherwise, the leaf node that points to the first page group will contain k+1 pages. The number of leaf nodes to be updated is  $O(\lceil \frac{N}{k} \rceil)$ . As a result, the total time of each MRC update is  $(O(k) + O(\log \lfloor \frac{N}{k} \rfloor) + O(\lfloor \frac{N}{k} \rfloor))$ . Therefore, given a small k, the total time cost for MRC updating is bounded by  $O(\lceil \frac{N}{k} \rceil)$ , though when locality is good the overhead is close to  $O(\log N)$ . In this dissertation, we further improve the LRU list by completely replacing the linked list with AVL tree and achieves an  $O(\log N)$  time complexity.

Instead of using the page protection based technique to intercept memory accesses, the hypervisor exclusive cache (34) intercepts memory accesses from a VM by capturing its disk I/Os. It is designed as a memory balancing mechanism for virtual machines. In this scheme, each VM gets a small amount of machine memory, called *direct memory*, and the rest of the memory is managed by the hypervisor in the form of exclusive cache. Because of the small amount of memory allocation, the guest OS will use page swapping heavily. Those disk I/Os are intercepted by the hypervisor and if they hit the exclusive cache, they are actually redirected to native memory operations in the form of cache admissions or cache hits. With the information of disk I/O requests, it can infer the memory accesses, construct an MRC for each VM and use it to estimate WSS for each VM. By adjusting the cache size of a VM, it achieves the effect of physical memory balancing. However, this design introduces an additional layer of memory management. Moreover, since the cache is exclusive, a VM's memory states spread across its direct memory and the hypervisor, which breaks the semantics of a hypervisor and complicates VM migration. In addition, it requires modification to the guest OS to notify the hypervisor of page release.

Besides the memory access interception techniques, another approach to monitor page accesses is by periodically checking if a page is accessed or not. On most processors, when a page is accessed, the hardware will automatically set the "access bit" in the corresponding page table entry (28). By periodically checking and scanning the access bit of a process's page table, the access frequency of each page of the process can be estimated and used to construct MRC. However, sequentially scanning the whole page table is expensive. To accelerate this process, Zhang *et al.* (63) present a "locality jumping" scheme that utilizes the spatial locality of a program to skip checking many non-accessed pages. This scheme is proposed for an OS to improve its cache utilization through tracking the MRC of each process and applying page coloring. However, in a virtualized environment, setting and clearing the access bit in hypervisor may disturb a guest OS's memory management because its page replacement policy usually relies on the access bits to infer page usage.

RapidMRC (52) collects memory accesses by using the sampling functions available in the performance monitoring units (PMU) of PowerPC processor and builds an MRC for an L2 data cache. The PMU can be configured to record the address of a memory access that matches predefined criterion (e.g. L2 cache miss) into a *sampled data address register*. By periodically sampling the register, it can collect enough information of memory accesses to build an MRC. However, on x86/x86-64 platform, not all processors support recording the addresses of memory accesses. For example, the PMUs on processors prior to the latest Nehalem microarchitecture only record the architectural states of the processor (i.e. state of the general purpose registers, the flag register and the instruction pointer register). Only on Nehalem microarchitecture, the PMU is enhanced with load latency information that contains the memory address for delayed load operations that are randomly selected by hardware (28).

### 2.2.3 Other Techniques For Working Set Size Estimation

In addition to the MRC-based WSS estimation techniques, many other approaches have been proposed.

VMware ESX server adopts a sampling strategy (54). During a sampling interval, accesses to a set of random pages are monitored. By the end of sampling period, the page utilization of the set is used as an approximation of global memory utilization. The merit of this technique is the very low cost. However, it lacks the model between allocation size and performance impact.

Magenheimer (36) uses an operating system's own performance statistics to guide memory resource management. However, the memory usage reported by most modern operating systems is larger than its working set size because it includes the infrequently used areas that can be reclaimed without a notable performance penalty.

Geiger (30), proposed by Jones et al., infers information about page admissions or evictions

of a guest OS's buffer cache by observing page faults and intercepting disk I/Os. For each intercepted disk I/O, Geiger tracks the disk location and the associated memory page and infers if a page is newly allocated or evicted from the buffer. For example, when a page is read from disk, if the memory page is associated with a different disk location, then the previous content of page is assumed to be evicted. It uses this information to simulate an exclusive cache and to construct an MRC, which is similar to Lu *et al.*'s exclusive cache (34) except that it does not actually provide caching. When a guest OS's memory is overloaded, the MRC tells how much extra memory is needed. However, it is unable to detect over-allocated memory because, in this case, there is no page eviction.

## 2.3 Virtual Machine Migration

In virtualization, transferring a VM from its current host to another is called *VM migration*. When the source and target hosts have different available memory resources, VM migration can be used for memory load balancing though it is a relatively heavyweight solution.

Typically, migration requires both the source and destination hosts reside in the same network and share centralized storage (like NAS or SAN), thus only memory states need to be synchronized. Two metrics are commonly used to evaluate the time cost of migration: *downtime* and *total migration time*. The former one is the period during which the VM is frozen and its services are temporarily unavailable in order to complete state transfer. The latter one is the period from the initiation to the completion of the whole migration process, during which performance degradation may occur due to state synchronization. If the downtime is sufficiently low (e.g. lower than the timeout thresholds of network protocols), it can be classified as *live migration*. That is, from user's perspective, service unavailability is unnoticeable during the migration.

A straightforward *stop-and-copy* (44) migration scheme, which first halts the source VM, then copies all pages to the destination host and finally resumes service on the new VM, has the minimum total migration time, but its downtime is equal to its total migration time, which is usually unacceptable for live services. At the other end of the spectrum is the demand-driven *copy-on-reference* migration scheme(61). It first uses a very short *stop-and-copy* phase to send essential data, then the new VM is started. The rest of the pages are transferred when they are first used. Though it has very short downtime, its total migration time is very long.

Clark *et al.* propose a balanced approach (15) for live migration, called *pre-copy migration*, which copies memory pages in multiple rounds from the source host to the destination host. When migration starts, it iteratively copies the pages that are dirtied during the previous iteration. Meanwhile, the VM is still running on the source host. During the migration, all pages that have been copied are write-protected by setting the corresponding page table

field, thus any polluted pages will be logged by the hypervisor. Eventually, after certain rounds of copying, if the number of all dirty pages is small enough or the number of precopying iterations reaches a preset threshold, a stop-and-copy phase finishes the migration. It has low downtime and its total migration time depends on the page dirty rate of the guest OS. For example, in our evaluation, for a VM with 1200 MB memory, when it runs 186.crafty, a program with low memory activity, the migration time is only 13 seconds. However, for the same VM, when it runs SPEC JBB, a program with much more memory writes, the migration time is 64 seconds.

## 2.4 Remote Memory

Due to the mechanic nature of hard disk drives (hdd), the performance of hdd is mainly limited by the seek time and rotational delay, which are both on the order of milliseconds. For example, for a high-end 15000 rpm HP SAS Enterprise drive, the average latency is 2.58 ms (27). Compared with disk I/Os, the high speed networking has much lower latency. For example, Chen *et al.* demonstrate that, when continuously requesting a 4KB data block, the latency of a Gigabit Ethernet is about 100 microseconds, which is more than 100 times longer than that of native memory copying but it is still 2 orders of magnitude lower than the 10,000-microsecond latency of a disk (14). The gap between native memory copying and network transferring is even smaller with faster networking technologies such as InfiniBand, Myrinet and Quadrics that provides up to 10 Gbps throughput.

As motivated by the outstanding performance of networking against hard drives, much research proposes to utilize remote memory to improve performance for a cluster environment.

Markatos *et al.* implement a *reliable remote memory pager* (37) that uses remote main memory for paging. In this design, the client forwards the paging requests to a remote server over Ethernet network. Servers are user level programs that listen to a socket and accept connections. Clients are implemented as a block device that redirects swapping operations to the servers. A client can distribute its swap space allocation requests to multiple servers. Meanwhile, a machine that acts as memory server can service multiple clients by instantiating a separate server instance for each client. In order to prevent data loss due to server crash, it introduces two RAID-like schemes: mirroring and parity-based redundancy. Using mirroring, the client sends a write request to two different servers. With parity-based scheme, pages to be swapped out are XORed and the parities are also transferred to servers.

Flouris *et al.* design the *Network RamDisk* (20), which is similar to the remote memory pager. It improves the performance of parity checking by using a parity cache. The experimental results show that the Network Ramdisk brings a four to eight fold speedup against the hard drive.

Newhall *et al.* design the *Nswap* (41), which supports limited dynamic growing and shrinking of the remote memory pool. The shrinking is performed by migrating some pages from the current memory server to other servers. Therefore, the total cache size in the whole network is unchanged.

Liang *et al.* present a *high performance network block device* (HPBD) (33), which runs over InfiniBand networking and utilizes its Remote Direct Memory Access (RDMA) operations for one sided communication. Its server design is a simple memory pool, without extra reliability policies. The evaluation results show that, the latency of transferring 4KB data is only a few microseconds, which is at the same magnitude as native memory transferring. As a result, HPBD is only 1.45 times slower than local memory operations, but is up to 21 times faster than the local disk.

To improve the communication efficiency, Werstein *et al.* propose a kernel-to-kernel network memory for page swapping (55). It uses a lightweight UDP-like communication channel over Ethernet and works within the kernel space.

In a virtualized environment, block devices like disks are virtualized to guest OSes. A special driver domain then redirects the disk I/Os from guest OSes to physical devices. Hence, there are two places for the client module. One is within the guest OS and acts as a kernel block device driver, the same way as the client module in a native OS. The other way is to postpone the redirection to the driver domain, just before it is actually sent to the physical disks. Hines *et al.* compare the two options in their MemX (26), a remote memory implementation for Xen virtual machines. It shows that the former option incurs slightly more overhead because the network traffic needs to traverse the extra virtual network of the guest OS.

Instead of using remote memory to replace a whole disk device, another approach is to use it as a cache between memory and disk. An important advantage of cache design is that it supports variable size. If the remote machine has less idle memory, it can shrink the capacity of its memory server. Using a write through cache design, it can simply discard some pages. For caches with write back policy, if the disks are network shared, the server can write the dirty pages back to the disk before discarding them. One example is REMOCA (14) that uses remote memory as an exclusive cache above disks for Xen virtual machines. For read requests, the client will look up its directory to check the availability of the pages. If the requested page is not in remote memory, it will read from local disk. For write requests, it adopts write through policy for better reliability. In order to achieve better cache utilization, it employs exclusive cache design. That is, after the client retrieves a page from the cache, the requested page is evicted by the cache. In order to cache a clean page evicted by the guest OS, it modifies the guest OS kernel to explicitly notify the eviction.

## 2.5 Other Techniques Of Memory Resource Balancing For Virtual Machines

Two migration-based VM load balancing schemes, Black-box and Gray-box strategies (58) are proposed by Wood *et al.*. Both of the strategies migrate hot-spot VMs to other hosts with enough resources, but differ in the way of collecting VM load information. The black-box approach is fully OS-agnostic, which inherits Geiger's disk I/O monitoring scheme to infer memory load and hence inherits its drawbacks too. The gray-box approach queries the performance statistics provided by each guest OS to estimate memory load, which is insufficient to support memory load balancing on a single host.

Williams et al. present overdriver(57), a mechanism that employs VM migration and network memory to balance memory resources for a data center. When a VM's memory overload is predicted to sustain for sufficiently long time, a migration-based solution will be used to alleviate memory pressure on that host. Otherwise, it will use physical memory on a remote host to mitigate the penalty of page swapping. In order to decide if the duration of memory overload is transient or not, it first constructs a workload profile for the VM that records the ratio of occurrences for each duration length of overloading. When memory overloading is detected, it uses the profile to get the ratio of overload of its current duration and compare the ratio against a threshold to decide if an overloading is transient or not. However, without local memory tracking and balancing, it is unable to effectively reclaim sufficient free memory to allow for migration, nor can it decide the appropriate size of the remote cache at runtime. Thus, waste of memory resources may still occur. Besides, its workload profile is only meaningful for a fixed memory allocation, which makes this scheme unsuitable for VMs with dynamically changed memory allocation. And in order to construct the profile, it needs to collect enough historic overloading events, which lowers its effectiveness during that time window.

## 2.6 Program Phases