Knowledge Commons, http://knowledgecommons.lakeheadu.ca

**Electronic Theses and Dissertations**

Electronic Theses and Dissertations from 2009

2017

# Mitigating the impact of decompression latency in L1 compressed data caches via prefetching

Rea, Sean

https://knowledgecommons.lakeheadu.ca/handle/2453/4134 Downloaded from Lakehead University, KnowledgeCommons

# Mitigating the Impact of Decompression Latency in L1 Compressed Data Caches via Prefetching

by

Sean Rea

A thesis

presented to Lakehead University

in partial fulfillment of the requirement for the degree of

Master of Science

In

Electrical and Computer Engineering

Thunder Bay, Ontario, Canada

September 1, 2017

Copyright 2017 Sean Rea

#### Abstract

Expanding cache size is a common approach for reducing cache miss rates and increasing performance in processors. This approach, however, comes at a cost of increased static and dynamic power consumption by the cache. Static power scales with the number of transistors in the design, while dynamic power increases with the number of transistors being switched and the effective operating frequency of the cache.

Cache compression is a technique that can increase the effective capacity of cache memory without experiencing the same gains in static and dynamic power consumption. Alternatively, this technique can reduce the physical size and therefore the static and dynamic energy usage of the cache while maintaining reasonable effective cache capacity. A drawback of compression is that a delay, or decompression latency, is experienced when accessing the compressed data, which affects the critical execution path of the processor. This latency can have a noticeable impact on processor performance, especially when implemented in first level caches.

Cache prefetching techniques have been used to hide the latency of lower level memory accesses. This work aims to investigate the combination of current prefetching techniques and cache compression techniques to reduce the effect of decompression latency and therefore improve the feasibility of power reduction via compression in high level caches.

We propose an architecture that combines L1 data cache compression with table-based prefetching to predict which cache lines will require decompression. The architecture then performs decompression in parallel, moving the delay due to decompression off the critical path of the processor. The architecture is verified using 90nm CMOS technology simulations in a new branch of SimpleScalar, using Wattch as a baseline, and cache model inputs from CACTI. Compression and decompression hardware are synthesized using the 90nm Cadence GPDK and verified at the register-transfer level.

The results of our verifications demonstrate that using Base-Delta-Immediate (B $\Delta$ I) compression, in combination with Last Outcome (LO), Stride (S), and Two-Level (2L) prefetch methods, or hybrid combinations of these methods (S/LO or 2L/S), provides performance improvement over Base-Delta-Immediate (B $\Delta$ I) compression alone in L1 data cache. On average, across the SPEC CPU 2000 benchmarks tested, Base-Delta-Immediate (B $\Delta$ I) compression results in a slowdown of 3.6%. Implementing a 1K-Set Last Outcome prefetch mechanism improves slowdown to 2.1% and reduces the energy consumption of the L1 Data Cache by 21% versus a baseline scheme with no compression.

## Acknowledgements

For introducing me to computer architecture and providing me with an engaging topic to study while at Lakehead, thank you Dr. Atoofian. I have learned a lot under your supervision.

Thank you to Dr. Mansour and Dr. Tayebi for endorsing my application for part-time studies back in 2012 and to Dr. Natarajan for keeping an eye on me for the first few years. Thank you Dr. Christoffersen for your active role in enabling students at Lakehead to have access to Cadence tools.

Thank you to all my family who have given their support and made every accommodation possible for me to pursue this degree. Most importantly, thank you Marcelle and Adam for supporting my decision to continue with my studies.

Sean Rea rea@ieee.org

# Contents

| List of Figuresv                                 |

|--------------------------------------------------|

| List of Tables                                   |

| List of Symbolsix                                |

| List of Abbreviations                            |

| Chapter 1 Introduction                           |

| Chapter 2 Background and Related Work            |

| 2.1 Memory Hierarchy                             |

| 2.2 Cache Compression                            |

| 2.2.1 Related Work in Cache Compression          |

| 2.2.2 Base-Delta                                 |

| 2.2.3 Base-Delta-Immediate                       |

| 2.3 Data Prefetching and Data Value Prediction10 |

| 2.3.1 Related Work in Prefetching                |

| 2.3.2 Last Outcome                               |

| 2.3.3 Stride and Hybrid Stride / Last Outcome    |

| 2.3.4 Two-Level and Hybrid Two-Level / Stride    |

| 2.4 Thesis Motivation15                          |

| Chapter 3 Cache Compression and Prefetching16    |

| 3.1 Compression Architecture                     |

| 3.1.1 Power Considerations                       |

| 3.2 Prefetching Architecture                     |

| 3.2.1 FETCH                                      |

| 3.2.2 MEM                                        |

| 3.3 Hardware Design                              |

| 3.3.1 Hierarchical Carry-Lookahead Adder         |

| 3.3.2           | 26 Implementation in Verilog        |  |

|-----------------|-------------------------------------|--|

| Chapter 4       | Simulation Methodology              |  |

| 4.1             | Methodology                         |  |

| 4.1.1           | Simpoint                            |  |

| 4.1.2           | 2 CACTI                             |  |

| 4.1.3           | SimpleScalar                        |  |

| 4.1.4           | Environment                         |  |

| 4.2             | Synthesis and Static Power Analysis |  |

| 4.3             | Dynamic Power Analysis              |  |

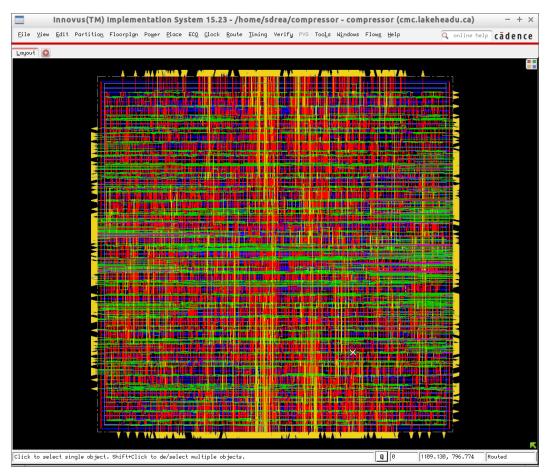

| 4.4             | Place and Route in Cadence Innovus  |  |

| Chapter 5       | Results                             |  |

| 5.1 Compression |                                     |  |

| 5.2             | Prefetching                         |  |

| 5.3             | Compression and Prefetching73       |  |

| Chapter 6       | Summary and Future Work77           |  |

| 6.1             | Contributions77                     |  |

| 6.2             | Future Work                         |  |

| Bibliogra       | phy                                 |  |

| Appendix        | A Verilog Source                    |  |

# List of Figures

| Figure 2.1 – Memory Hierarchy                                            | 4  |

|--------------------------------------------------------------------------|----|

| Figure 2.2 – 32-Byte Cache Line Compressed with Base-Delta               | 8  |

| Figure 2.3 – 32-Byte Cache Line Compressed with Base-Delta (2 Bases)     | 8  |

| Figure 2.4 – Changes to Tag and Data Architecture for B∆I Compression    | 9  |

| Figure 2.5 – Last Outcome Prefetching                                    | 12 |

| Figure 2.6 – Stride Prefetching                                          | 13 |

| Figure 2.7 – Stride State Machine                                        | 14 |

| Figure 2.8 – Two-Level Prefetch Table and Pattern History Table          | 15 |

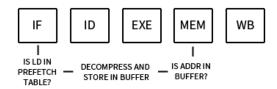

| Figure 3.1 – Prefetching Applied to Classic RISC Architecture            |    |

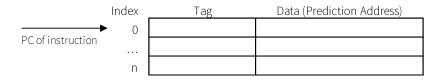

| Figure 3.2 – Prefetch Table Structure                                    | 19 |

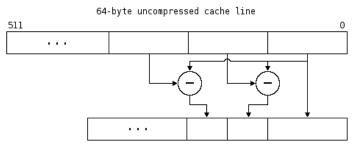

| Figure 3.3 – Compressor Design                                           | 22 |

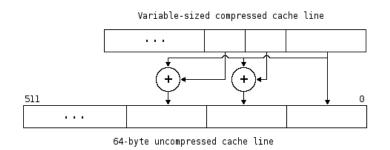

| Figure 3.4 – Decompressor Design                                         | 22 |

| Figure 3.5 – Truth Table for Full Adder                                  | 24 |

| Figure 3.6 – Karnaugh Map for Full Adder                                 | 24 |

| Figure 3.7 – Adder Design                                                | 26 |

| Figure 3.8 – HDL Structure of Compressor                                 |    |

| Figure 3.9 – Testbench Waveforms for Compressor in Xilinx ISE            |    |

| Figure 3.10 – HDL Structure of Decompressor                              | 29 |

| Figure 4.1 – Simulation Flow Diagram                                     |    |

| Figure 4.2 – CACTI Output                                                |    |

| Figure 4.3 – Compression Model Verification Results                      | 43 |

| Figure 4.4 – Compressor VCD Header                                       | 45 |

| Figure 4.5 – Compressor VCD ASCII Value                                  |    |

| Figure 4.6 – Decompressor VCD Header Variables                           |    |

| Figure 4.7 – Decompressor VCD ASCII Value                                |    |

| Figure 4.8 – Genus Gates Report for Compressor (Condensed)               | 49 |

| Figure 4.9 – Compressor Routing in Innovus                               |    |

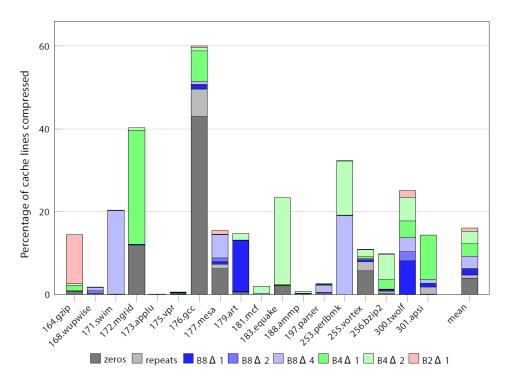

| Figure 5.1 – Percentage of L1 Data Cache Lines Compressed by Each Scheme | 57 |

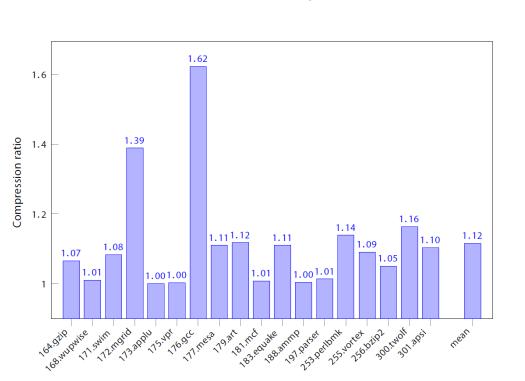

| Figure 5.2 – Compression Ratio of L1 Data Cache                          | 58 |

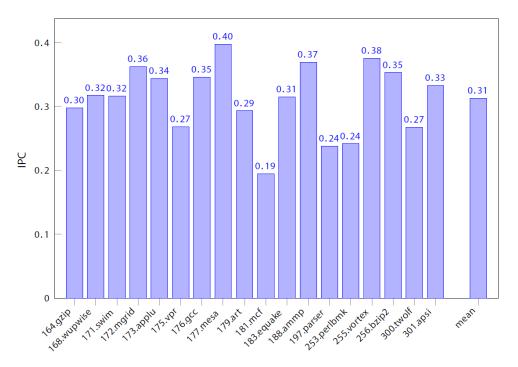

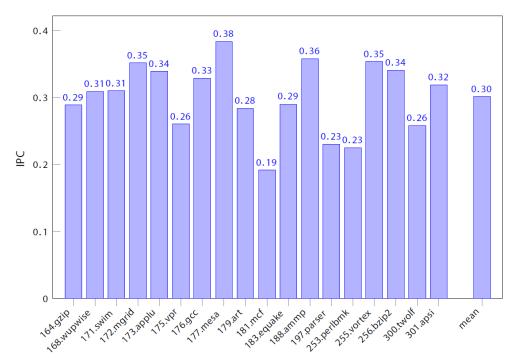

| Figure 5.3 – IPC of Baseline Scheme                                      | 60 |

| Figure 5.4 – IPC of Compressed Scheme                                    | 60 |

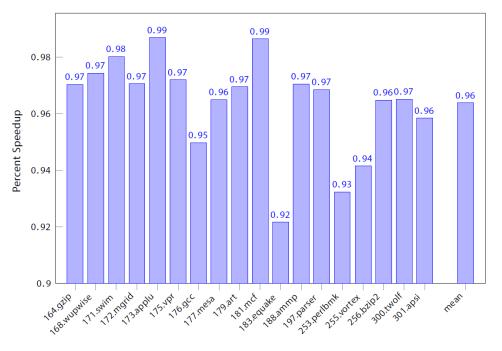

| Figure 5.5 – Speedup of Compressed Scheme vs Baseline                    | 61 |

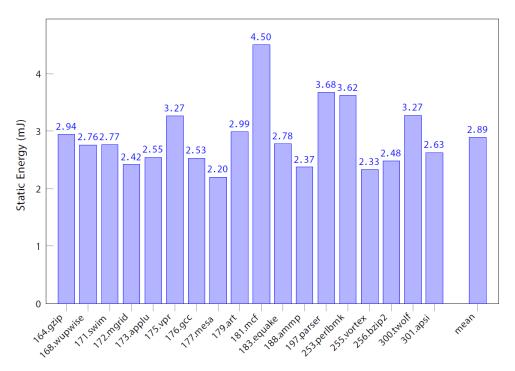

| Figure 5.6 – L1 Data Cache Static Energy (Baseline Scheme)                    |

|-------------------------------------------------------------------------------|

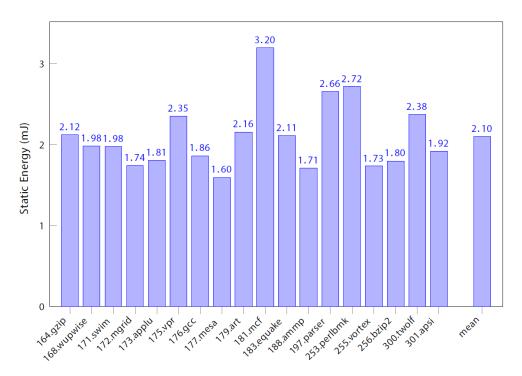

| Figure 5.7 – L1 Data Cache Static Energy (Compressed Scheme)                  |

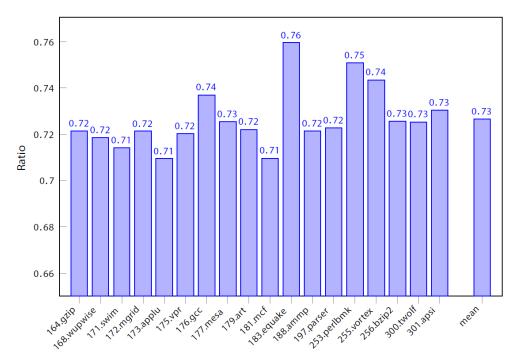

| Figure 5.8 - L1 Data Cache Static Energy Ratio - Compressed vs Baseline       |

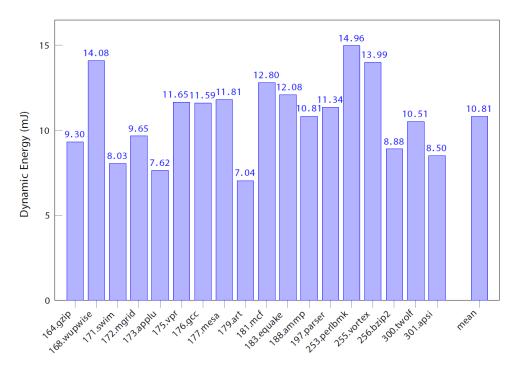

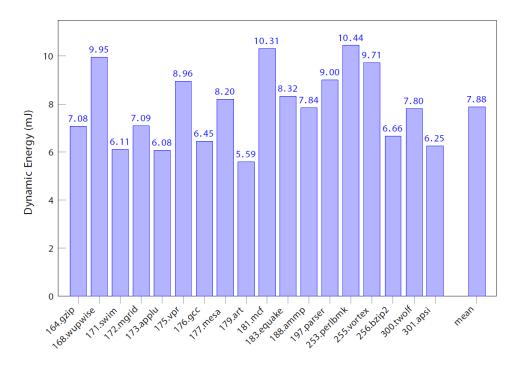

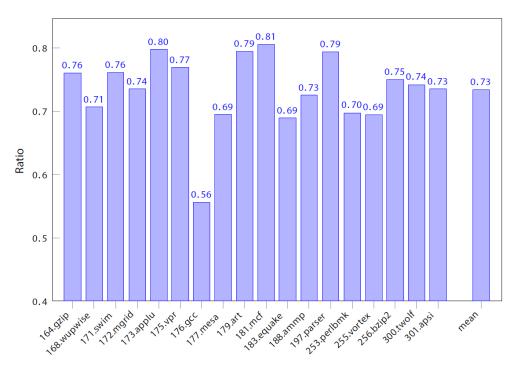

| Figure 5.9 – L1 Data Cache Dynamic Energy (Baseline Scheme)                   |

| Figure 5.10 – L1 Data Cache Dynamic Energy (Compressed Scheme)                |

| Figure 5.11 – L1 Data Cache Dynamic Energy Ratio – Compressed vs Baseline     |

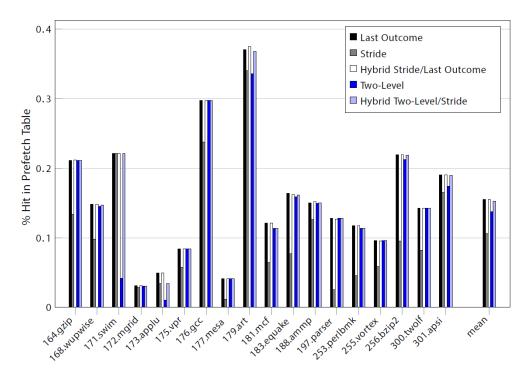

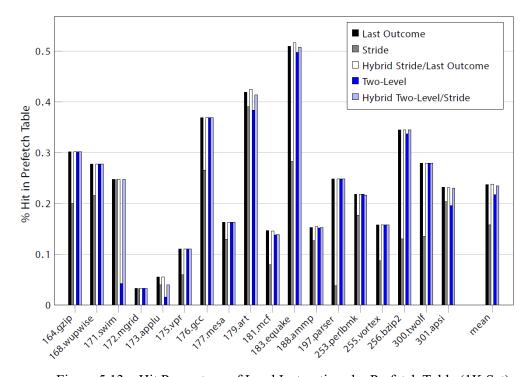

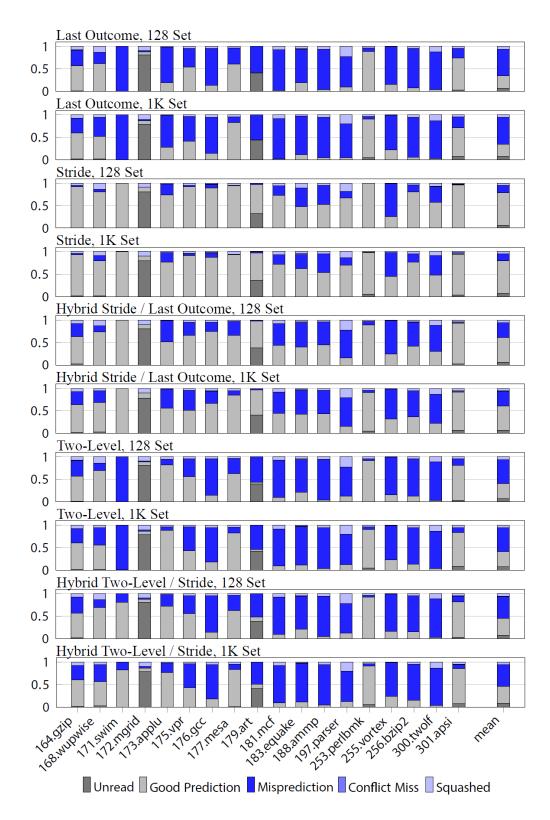

| Figure 5.12 – Hit Percentage of Load Instructions by Prefetch Table (128 Set) |

| Figure 5.13 – Hit Percentage of Load Instructions by Prefetch Table (1K Set)  |

| Figure 5.14 – Prediction Accuracy of 10 Prefetch Table Configurations         |

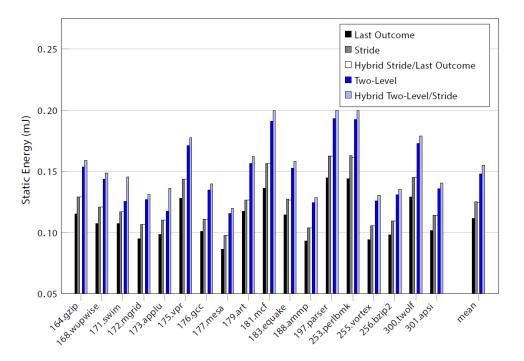

| Figure 5.15 – Static Energy by Prefetch Table (128 Set)                       |

| Figure 5.16 – Static Energy by Prefetch Table (1K Set)71                      |

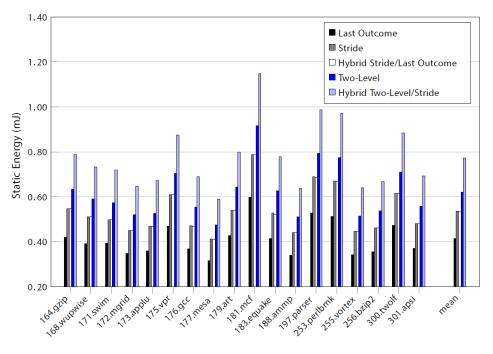

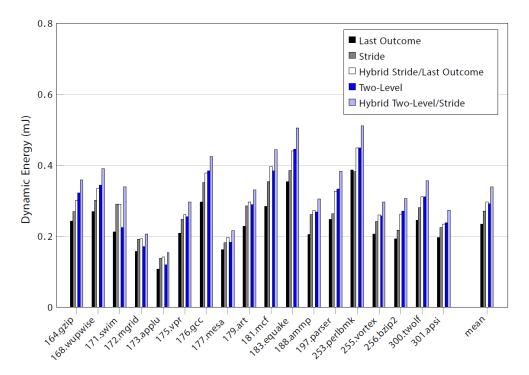

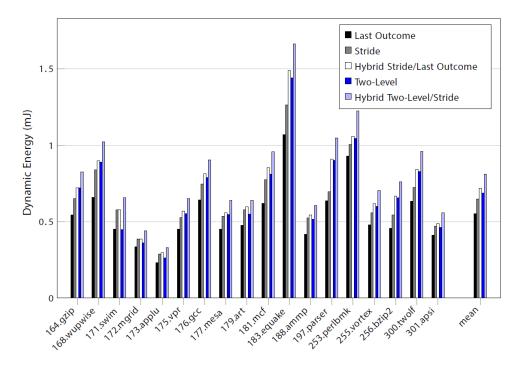

| Figure 5.17 – Dynamic Energy by Prefetch Table (128 Set)                      |

| Figure 5.18 – Dynamic Energy by Prefetch Table (1K Set)                       |

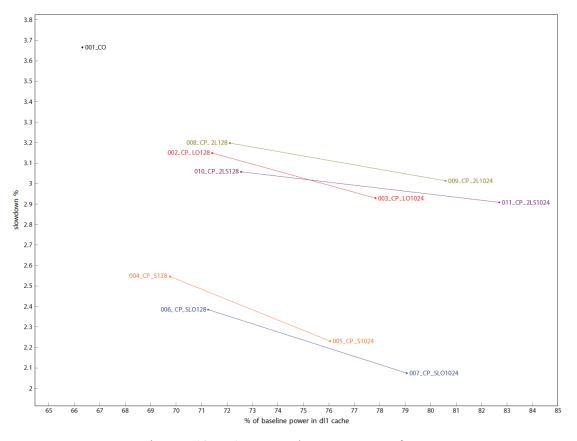

| Figure 5.19 – L1 Data Cache Energy vs Performance                             |

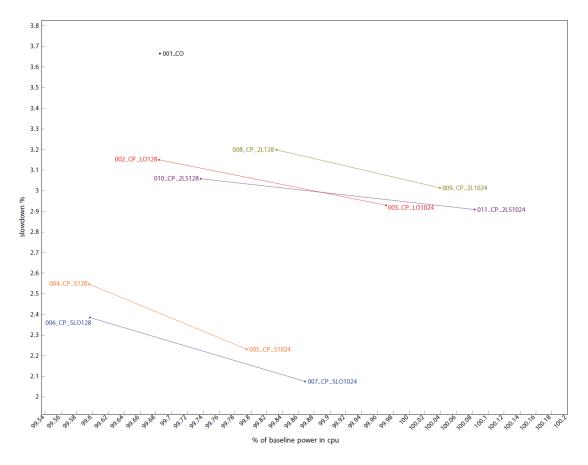

| Figure 5.20 – CPU Energy vs. Performance                                      |

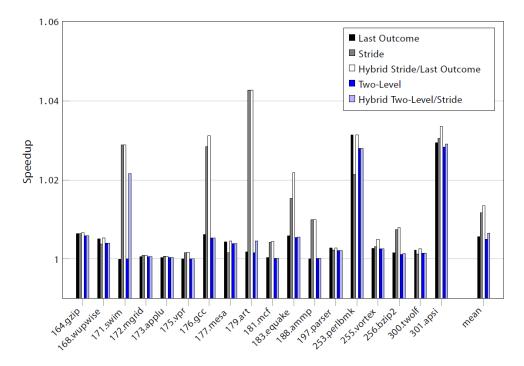

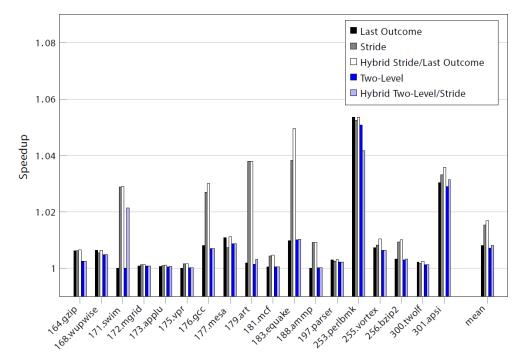

| Figure 5.21 – Speedup Due to Prefetching (128 Set, vs. Compressed Only)75     |

| Figure 5.22 – Speedup Due to Prefetching (1K Set, vs. Compressed Only)        |

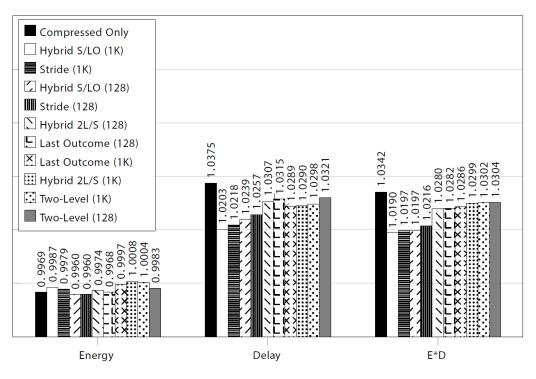

| Figure 5.23 – Energy-Delay Product (CPU)                                      |

# List of Tables

| Table 3.1 – Compression Events                                            | 16 |

|---------------------------------------------------------------------------|----|

| Table 3.2 – Power Events                                                  | 18 |

| Table 3.3 – Prefetch Table Power Events                                   | 19 |

| Table 3.4 – Two-Level Table Power Events                                  | 20 |

| Table 3.5 – Decompression Buffer Power Events                             | 20 |

| Table 3.6 – Compressor Test Cases                                         |    |

| Table 4.1 – 164.gzip CPI Values by Simulation Point                       |    |

| Table 4.2 – Simpoint Error by Maximum Number of Clusters                  |    |

| Table 4.3 – SimPoint Error                                                |    |

| Table 4.4 – 100M SimPoint Results                                         |    |

| Table 4.5 – CACTI L1 Cache Configurations and Power Results               |    |

| Table 4.6 – CACTI L2 Cache Timing                                         |    |

| Table 4.7 – CACTI Prefetch Table Configurations and Power Results         |    |

| Table 4.8 – CACTI Pattern History Table Power Results                     | 40 |

| Table 4.9 – CACTI Decompression Buffer Power Results                      | 40 |

| Table 4.10 – Delta Datatype and Overflow Information                      |    |

| Table 4.11 – Boundary Conditions for Compression                          | 43 |

| Table 4.12 – Initial Static Power Analysis of Decompressor by PDK         | 49 |

| Table 4.13 – Compressor Static Power Determination                        |    |

| Table 4.14 – Decompressor Static Power Determination                      | 51 |

| Table 4.15 – 164.gzip Compressor Static Power Values by Simulation Point  |    |

| Table 4.16 – Static Power for Compressor and Decompressor                 |    |

| Table 4.17 – 164.gzip Compressor Dynamic Power Values by Simulation Point | 53 |

| Table 4.18 – Compressor Dynamic Power Results from Cadence Genus          | 54 |

| Table 4.19 – 164.gzip Decompressor Power Values by Simulation Point       | 54 |

| Table 4.20 – Decompressor Power Results from Cadence Genus                | 55 |

# List of Symbols

| ci                 | carry-in                                     |

|--------------------|----------------------------------------------|

| $c_{i\!+\!1}$      | carryout                                     |

| Е                  | energy                                       |

| $g_i$              | generate function                            |

| $G_i$              | block generate function                      |

| М                  | maximum number of SimPoint clusters          |

| $p_i$              | propagate function                           |

| $\mathbf{P}_{i}$   | block propagate function                     |

| t                  | time                                         |

| $t_{\rm VCD,  ps}$ | value change dump timestamp (in picoseconds) |

# List of Abbreviations

| 2L       | two-level prefetcher                        |

|----------|---------------------------------------------|

| BΔI      | base-delta-immediate compression            |

| BBV      | basic block vector                          |

| CMC      | Canadian Microelectronics Corporation       |

| CMOS     | complementary metal-oxide-semiconductor     |

| CPI      | cycles per instruction                      |

| CPU      | central processing unit                     |

| EDP      | energy-delay product                        |

| FIFO     | first-in, first-out                         |

| FLAC     | free lossless audio codec file format       |

| FPC      | frequent pattern compression                |

| GHB      | global history buffer                       |

| GPDK     | generic process design kit                  |

| IPC      | instructions per cycle                      |

| L1       | level-1 cache                               |

| L2       | level-2 cache                               |

| L3       | level-3 cache                               |

| LO       | last outcome prefetcher                     |

| LRU      | least recently used                         |

| PC       | program counter                             |

| PDK      | process design kit                          |

| PNG      | portable network graphics file format       |

| RISC     | reduced instruction set computer            |

| simpoint | simulation point                            |

| S        | stride prefetcher                           |

| S/LO     | hybrid stride/last outcome prefetcher       |

| SPEC     | Standard Performance Evaluation Corporation |

| VCD      | value change dump                           |

| ZCA      | zero-content augmented cache                |

| ZIP      | ZIP file format                             |

### Chapter 1

### Introduction

In 2016, it has been estimated that the world creates 2.5 quintillion bytes of data per day [1]. At the time, that estimate suggested that 90% of the world's data had been created in the previous two years alone. In as early as 2013, it was approximated that Information and Communication Technologies were consuming nearly 10% of the world's electricity generation [2]. With this rate of data growth, and the current impact computing has on the world's energy consumption, there is a need to investigate ways to improve the way we store and process data.

Linked with the growth of our data generation is the emergence of a rapidly growing mobile device market. This market relies heavily on low power, battery supplied devices. Unavoidably, the best way to provide a longer battery life for these devices is for the devices themselves to consume less power. While improvements can be made to the devices themselves (e.g. supply voltage and device size), in many applications, the best way to reduce power is to find efficiencies at the architectural level [3]. Redefining the architecture can result in orders of magnitude in reduction of power depending on the specific application.

When we look at the data we are creating, it is clear that patterns exist that create inefficiencies in the way it is stored and processed [4]. Data patterns may consist of values that are repeated over-and-over again, values that are very close to each other, and even large sets of null data. Some of the greatest sources of data in the world today are the cameras on our mobile devices. Images are a great example of data that consists of patterns. Pixel data contains sequences of values, which can be identical or very close in magnitude (when looking at color value, brightness, etc.). Programs that manipulate this image data generally handle large data arrays. These arrays are frequently initialized to some repeated value, often zero. And frequently enough, the developers of those programs may over-provision data types to hold that data such that most of it goes unused (narrow data). These inefficiencies in our data contribute to unnecessary storage and processing.

In computing architecture, we utilize a memory hierarchy to ensure that the data we use most frequently is closest to the CPU and therefore accessible as fast as possible. The closest memory spaces, L1 and L2 cache, take up large areas on-chip and consume large amounts of power. Depending on the architecture, cache memory in a processor can account for upwards of 40% of the total power budget [5]. Because the cache must handle our data, which is full of inefficiencies, a significant portion of this energy consumption could be avoided via compression.

Compression is possible by replacing the most inefficient patterns with a set of smaller representations, known as encoding. Encoding can be done with a fixed dictionary or a compression scheme can dynamically and iteratively assign code words to patterns. Most of our data is compressible to some extent, whether it is text, image, or audio data. This is why, in main memory, it is common to store and transfer large files in a compressed format (e.g. ZIP, PNG, FLAC).

Cache-level compression in a processor is a technique that can increase the effective capacity of the cache, and therefore improve performance of the processor, by compressing cache lines before they are stored in the cache. Alternatively, this same method can be used to reduce the physical size of the cache and therefore reduce the power consumption.

Typically, cache lines consist of several bytes of data. In set-associative caches, multiple lines, or ways, may be stored at a given cache index. Each of these ways store a complete uncompressed cache line. If we can compress the size of these cache lines, we can store more data in each set. Alternatively, we could reduce the physical size of the cache and store the same, or similar, amounts of data.

The power of a cache depends on its size and the frequency of accesses. By reducing the total size of the cache, we can significantly reduce the power consumption. In addition, the size of the data lines we read from the cache are potentially reduced in size as well. Therefore, we can model the savings in dynamic power consumption in the cache by considering the size ratio of compressed data vs an uncompressed cache line.

In the past, researchers have avoided implementing compression in high-level caches such as L1 data cache because of the impact decompression latency has on the overall performance of the processor [4, 6, 7]. Access times at this level are in the order of a few clock cycles. To add even a few clock cycles to this access time will cause significant performance delays and defeat the intent of the high-level cache.

However, it is possible to implement additional techniques, such as prefetching, to remove the some of the burden of decompression from the processor's critical path. If this approach is successful, it could lead to improving the feasibility of implementing compression in high-level caches (specifically L1 data cache).

Our work focusses on the combination of data cache compression and table-based prefetching to explore the feasibility of implementing compression in L1 data cache. We evaluate this new architecture by examining what impact it has on the performance and power consumption of a CPU during the execution of standard benchmarks. Specially, this work makes three key contributions:

(1) An architecture is proposed that combines compression, specifically Base-Delta-Immediate compression, in L1 data cache with table-based prefetching methods, such as Last Outcome, Stride, and Two-Level, to predict which cache lines will require decompression. The architecture then performs decompression in parallel, therefore moving the delay due to decompression off the critical path of the processor.

(2) Modifications are made to Wattch [5], a branch of SimpleScalar [8] that is an open-source processor modelling tool for analyzing and optimizing power consumption at the architectural level. This tool is extended to model Base-Delta-Immediate compression in combination with table-based prefetching to show the benefit of performing decompression as a parallel activity to execution and increase the feasibility of implementing compression in L1 caches.

(3) 64-byte compressor and decompressor hardware is designed in 90nm CMOS and tested for implementation with Base-Delta compression. Static and dynamic power analysis is performed on the new hardware, reinforcing its suitability for use in a power-reducing compressed cache scheme.

The remainder of this thesis is organized into five chapters. Chapter 2 provides an overview of cache compression and prefetching and recent research that has been done in these areas. In Chapter 3, we define the proposed compression and prefetching architecture, discuss what changes are necessary to accommodate the new architecture in a conventional superscalar processor, and provide the details of the hardware design for the compressor and decompressor units. Chapter 4 discusses the tools used and modified to model the compression and prefetching architecture. In Chapter 5, the results of simulation are provided and discussed. Finally, Chapter 6 provides a summary of the work done, the significance of the results, and future work that could be done to advance this research.

### Chapter 2

### **Background and Related Work**

In this chapter, we review the concepts of memory hierarchy, compression, data value prediction, and prefetching. We review existing work in the areas of cache compression, data value prediction, and prefetching and go into detail of the operation of one compression scheme, Base-Delta-Immediate, three prediction schemes: Last Outcome, Stride, and Two-Level as well as hybrid combinations of these schemes. Finally, the motivation behind this work is presented.

#### 2.1 Memory Hierarchy

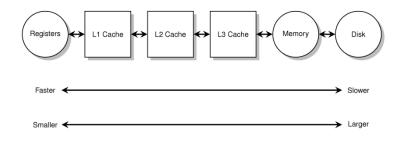

The speed in which a processor can read information from memory has a great impact on the performance of that processor. Fast memory, however, is expensive. For this reason, memory is organized into levels that exploit small amounts of fast memory close to the processor, and larger, slower levels of memory farther away. This organization is referred to as the Memory Hierarchy. In this hierarchy, between the central processing unit (CPU) and "main memory" are various levels of cache memory.

Figure 2.1 – Memory Hierarchy

When the data for a given address is stored in the high-level cache (i.e. L1 cache), then the processor has fast access to this information. If the data is not there, the processor must retrieve it from lower levels. This is referred to as a cache miss. Cache misses are classified by three types: compulsory misses, capacity misses, and conflict misses [9]. Compulsory misses occur during start-up, when no information exists in

the cache. Capacity misses occur if the cache is not large enough for all the blocks required during the execution of a program and blocks are discarded. If these discarded blocks must be read again, they must be fetched from lower levels. Conflict misses occur if the cache is not fully associative. In this case, blocks may be discarded even before the cache is full.

Increasing the capacity of the cache can reduce the number of capacity and conflict misses and therefore increase performance. This, however, comes at a cost of increased power consumption.

#### 2.2 Cache Compression

Similar to data files in main memory, the data within cache memory consists of patterns that can be exploited by compression techniques to save space. Cache compression is a method that can be used to increase the capacity of the cache without experiencing the same increase in power consumption.

Because the intent of cache memory is to provide low latency access to data, compression and decompression must be performed at the hardware level in the processor rather than at the software level, as is commonly performed on files in main memory. This same requirement for low latency cache access is why most of the previous work done on the topic of cache compression focusses on low-level cache (i.e. L2 cache and L3 cache). Because L1 caches typically have access latencies in the order of a few clock cycles, adding a decompression latency on top of that can degrade performance beyond acceptable levels.

The ideal compression scheme for implementation in L1 cache is one that is, of course, fast, but is also capable of encoding the most common patterns that exist within data stored in memory. These most common patterns can be grouped into four main categories: zeros, repeated values, narrow values, and other patterns [4].

#### Zeros

Zero values are widely used throughout programs, primarily in variable initializations, null pointers, false boolean values, and sparse matrices [4].

#### **Repeated Values**

Similar to zero values, repeated values may appear in the form of variable initializations. Another cause for repeated values is image data. Adjacent pixels tend to contain similar information such as colour data [4].

#### **Narrow Values**

It is common for developers to over-allocate space to variables to protect from overflow during execution of a program. In some cases, these variables never come close to their maximum values. A small value stored as a large data type is considered a narrow value [4].

#### **Other Patterns**

This group is not meant to include all other patterns, but rather patterns that specifically have low dynamic range. For example, an array of pointers that all point to the same region of memory [4].

#### 2.2.1 Related Work in Cache Compression

Research has been done to evaluate hardware-based data compression in CPU caches [4, 6, 7, 10, 11, 12] as well as in GPGPU [13]. The following papers have explored which methods exploit the most opportunities in data patterns and at which levels in cache they are most beneficial. A common understanding among this work is that decompression latency is a problem when implementing in fast caches and is cited as the reason for avoiding L1 compression in some works [4, 6, 7].

In [7], the authors present Frequent Pattern Compression (FPC), which compresses data that fits into one of seven patterns. Each 32-bit word is evaluated separately so data is not compressed spanning multiple words. The scheme is evaluated in L2 cache with L1 cache being left uncompressed. The design is evaluated against the Wisconsin Commercial Workload Suite and six benchmarks from the SPEC CPU 2000 suite. The scheme provides compression ratios ranging from 1.0 to 2.4 over all their benchmarks. This scheme captures the main three groups of patterns that exist in data. However, this scheme does not address the behaviour of low dynamic range that data exhibits.

In [11], the authors exploit the common scenario of storing null data in caches by augmenting the uncompressed cache with an additional cache that is only required to store the addresses of zero-content cache lines. The authors evaluate this zero-content augmented (ZCA) cache in every combination of cache level from L1 to L3. They found that implementing ZCA in L3 alone was sufficient to experience most of the benefit and found up to a 22% speedup when run against SPEC CPU 2000 benchmarks. Because this scheme only looks at zeros, decompression latency is not an issue, and the authors are able to explore this technique in all levels of cache without affecting the read latency. This scheme, however, does not address most of the patterns that exist within cache data.

In [12], the authors compress the cache line by encoding 32-bit words that appear in a predefined list of "frequent values." The scheme requires that a cache line be compressible to 50% in size or less or it is not compressed at all. Encoding bits are required for each word in the cache line. The authors determine that their scheme can improve the miss rate for six integer benchmarks from SPEC CPU 95 as much as 36.4%. Due to the table-lookup nature of the scheme, it cannot capture all repeating values efficiently. As well, it misses the important narrow values that occur within the data.

In [4], the authors present a new compression scheme that this work builds upon, called Base-Delta-Immediate. In addition to null data and repeating values, this work exploits two trends in data called narrow values and low dynamic range. The scheme compresses cache lines that can be represented as a single base and an array of small deltas. The authors evaluated their scheme against the SPEC CPU 2006 benchmark suite, among other benchmarks. The authors achieve an average compression ratio of 1.53 across all benchmarks when compressing L2 cache. Due to the impact decompression latency would have on L1 cache, the authors focus on L2. Because this scheme addresses all the patterns discussed in the other works, and more, it is the compression scheme we use. We will address the issue of implementing this scheme in L1 cache by combining common prefetching techniques to mask the effect of the decompression latency.

#### 2.2.2 Base-Delta

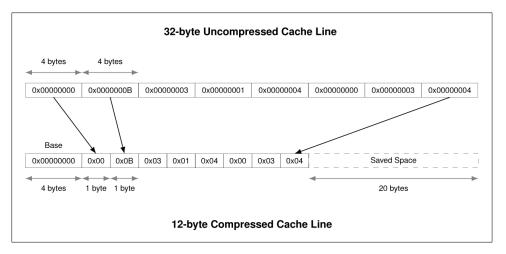

Back to [4], the authors first describe the foundation of their scheme, called Base-Delta. Base-Delta is a cache compression scheme that stores a cache line as one large base value along with an array of smaller deltas. The concept behind the scheme is that, for many cache lines, the data values have a low dynamic range (the difference between values is small). For example, Figure 2.2 shows an example of how a 32-byte cache line may be compressed using a **Base 4 Delta 1** compression scheme.

Figure 2.2 – 32-Byte Cache Line Compressed with Base-Delta

From the figure, you can see how this cache line benefits from low dynamic range. In this example, the **Base 4 Delta 1** scheme is used. This means the chosen size of the base is 4 bytes, and the size of the deltas is 1 byte.

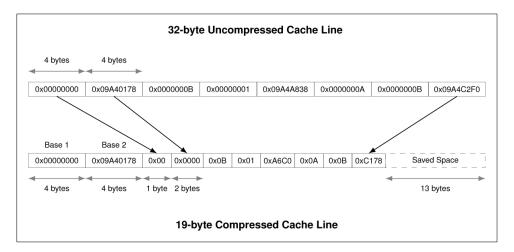

In some cases, compression may benefit from having multiple bases. For example, the cache line in Figure 2.3 clearly shows patterns with low dynamic range around two bases.

Figure 2.3 – 32-Byte Cache Line Compressed with Base-Delta (2 Bases)

Determining two optimized bases is a high latency task that is not feasible during execution. The authors resolve this issue by implementing the **immediate** portion of their compression making Base-Delta-Immediate [4].

#### 2.2.3 Base-Delta-Immediate

Base-Delta-Immediate ( $B\Delta I$ ) compression implements a 2-base Base-Delta scheme where one base is always zero. This method sees much of the benefit of a 2-base system, without adding the need to store a second base. To implement this immediate base, an array of flag bits called the **immediate mask** is included in the tag to identify which deltas refer to the base and which refer to zero.

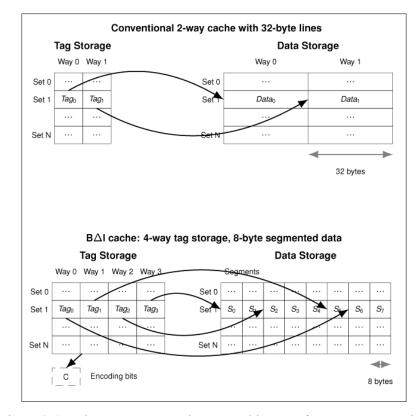

To change a conventional cache into a Base-Delta-Immediate cache, we double the number of tags. This allows us to utilize the vacant space in the cache created during compression. Next, we modify how the tags point to the data stored in the cache. The data array is divided into 8-byte segments rather than 64-byte blocks. Rather than pointing to a constant 64-byte block, the tag now points to a variable-size compressed block. The location of the compressed block at a given cache index is determined by summing the size of cache blocks stored in front of it. Lastly, we add the encoding bits (and immediate mask, as mentioned above) to the tag. This allows us to define the type of compression applied to the data for a given way. These changes to the architecture are shown in Figure 2.4.

Figure 2.4 – Changes to Tag and Data Architecture for B∆I Compression

These changes are implemented functionally in SimpleScalar and have their power and access time impact modeled using CACTI (see Chapter 4, Simulation Methodology). The additional hardware required for compressing and decompressing the  $B\Delta I$  cache lines is discussed separately in Chapter 3.

#### 2.3 Data Prefetching and Data Value Prediction

Prefetching is a method that can be used to reduce the miss rate of all three types of cache misses. Data can be prefetched (read in parallel to execution, before it is requested), either directly into the next-levelup cache or into a custom buffer that can be accessed faster than main memory [9]. While successful prefetches can reduce memory latency and improve overall processor performance, unused prefetches will have a negative impact on power consumption while having no positive impact on performance.

Data value prediction is similar to prefetching such that it employs a table-based predictor to improve performance of the processor. Unlike prefetching, data value predictor tables do not store the address in memory where the data exists. Rather, it stores the data itself – specifically the result of single-register producing instructions. The processor then continues execution using this predicted result. If an incorrect prediction is made, the processor pipeline must be flushed of any instructions that depend on this data.

The approach we take concerning prefetching is neither a direct application of prefetching nor of data value prediction. Rather, our prefetcher predicts which address in the L1 data cache will be accessed based on the program counter of each load instruction. Then, in parallel, the processor decompresses this data in the cache, if it is compressed, and inserts it into an external buffer.

The key similarities between prefetching and data value prediction are the prediction table methods used. These methods have been explored extensively for both applications. We look at this past research to determine which tables are best suited for our application.

Reviewing the prediction schemes presented in literature, five types stand out as candidates for this work, as discussed in [14]. The simplest, Last Outcome, is evaluated first to determine how quickly we can recover the cost of decompression with the lowest possible complexity. Next, Stride and the hybrid Stride/Last Outcome predictors are used and evaluated. Lastly, the Two-Level and hybrid Two-Level/Stride predictors are looked at to capture more complex patterns. Global History Buffer is discussed as a potential extension by evaluating the benefit of predictor tables with a depth greater than one.

#### 2.3.1 Related Work in Prefetching

In [14], data value predictors are discussed using Last Outcome, Stride, 2-Level Pattern History methods, and two hybrids of these methods. Data Value Prediction uses prediction tables in the same way as prefetching. Data Value Predictors predict the data value rather than the address of the data in memory. Accuracy is critical for Data Value Predictors because if an incorrect prediction is made, any progressed instructions dependant on this value much be flushed out of the pipeline. The authors found that the Last Outcome scheme was correct 28-62% of the time and incorrect up to 72% of the time. Stride was correct 35-77% and 3-6% incorrect. Two-Level makes minor improvements in prediction accuracy over Last Outcome (1-3%). However, the two-level table scheme greatly improves the misprediction rate to 1-13%. The first hybrid scheme implements Last Outcome when Stride is not in steady state. This results in a correct predictions rate of 49-80% and incorrect predictions 20-51%. The second hybrid predictor combines the 2-Level scheme with Stride. This scheme made correct predictions 50-82% of the time and mispredictions only 5-18% of the time. This scheme is, however, the most complex to implement.

An important takeaway from this research are the incorrect prediction rates. In the Data Value Predictor method, if we make an incorrect prediction, we must flush the processor of any instructions that depend on the incorrect value. In our compression-prefetching method, we do not have to purge any information. However, incorrect predictions will cause unnecessary cache accesses which will increase power and may evict useful data from the decompression buffer (depending on the depth of the buffer).

In [6], the authors present a two-table prefetching scheme called Global History Buffer (GHB). GHB itself, as with the above research on Data Value Predictors, explores multiple prediction schemes: Address Correlation, Distance Correlation and Constant Stride. The key benefit of GHB is the two independently sized tables. The first is the Index Table which only stores the tag and a pointer to the head of a list stored in the GHB Table. The GHB acts as a circular buffer, keeping only the latest information. The authors investigate different table configurations with a degree of four (values prefetched each access). They found that GHB Distance prefetching resulted in a 20% speedup over conventional table Distance prefetching when indexed by the miss address and 6% when indexed by the program counter (PC).

The key enabler of the Global History Buffer is to minimize space and hold the latest information about cache misses. The same technique can be applied to our prediction table. However, this approach will only be useful if tables with a depth greater than 1 prove to be valuable. The Global History Buffer approach

will not be explored directly in this work, but this work can easily be extended to explore this possibility in a later study.

#### 2.3.2 Last Outcome

For this thesis, prefetching techniques are used to predict which cache lines may require decompression from L1 data cache before the instruction is decoded using the PC of the instruction. The intent is to load the data from a compressed cache, decompress it, and make it available to the CPU in parallel with other stages to remove the bottleneck that is decompression latency.

The simplest scheme that will be implemented is Last Outcome. Figure 2.5 shows the traditional implementation of this scheme.

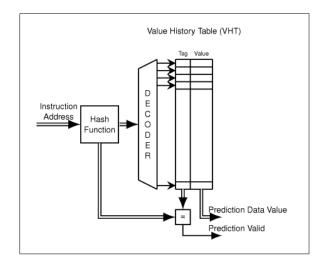

Figure 2.5 – Last Outcome Prefetching

In the figure, you see that a table exists to store two values for each entry: tag and value. **Tag** identifies the load instruction address and **Value** identifies the memory address loaded by that instruction. The configuration of the table can be varied similar to that of cache memory: associativity, depth (multiple values per tag), etc. Unlike the traditional architecture, in this work it is not necessary to verify if the prediction is correct in order to validate instructions with dependencies. If it is incorrect, the processor will merely suffer the full latency of decompression.

#### 2.3.3 Stride and Hybrid Stride / Last Outcome

As mentioned earlier, the authors in [14] propose a hybrid prediction table that implements a Constant Stride prefetcher, and uses the Last Outcome result when the stride prefetcher is not in a steady state. We have already reviewed the behaviour of the Last Outcome table. So, let us review the functionality of a stride prefetcher.

#### **Stride Prefetching**

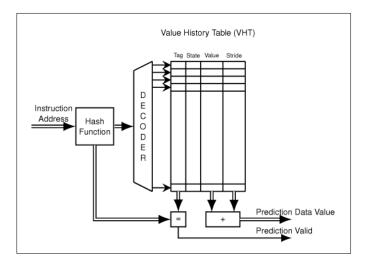

Similar to Last Outcome, we will be indexing the Stride table by Program Counter (PC) of each load instruction. When an entry is updated in the table, the value of the stride is calculated as the difference between the current and last memory addresses that are loaded. The state of the prefetcher can be Init, Transient, or Steady. Therefore, as shown in Figure 2.6, the table requires four columns: Tag, State, Value, and Stride.

Figure 2.6 – Stride Prefetching

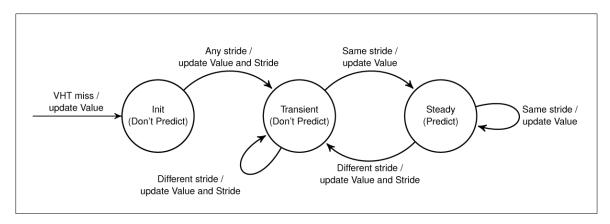

When a line in the table is first entered, there is no previous data from which to calculate the stride. The entry is in an initialized state. After this line is updated at least once, a stride can be calculated and the entry is in the transient state. The line will remain in this transient state until an update occurs that produces the same stride value as is currently stored in the table. When this occurs, the table is updated to steady state and this value for the stride is used. Figure 2.7 shows an overview of the state machine for this prefetcher.

Figure 2.7 – Stride State Machine

#### 2.3.4 Two-Level and Hybrid Two-Level / Stride

In addition to a hybrid S/LO prefetch table, the authors in [14] propose a hybrid prediction table that implements a Two-Level prefetcher, and uses the Stride result when the Two-Level prefetcher does not make a prediction. We have already reviewed the behaviour of the Stride table. So, let us review the functionality of a two-level prefetcher.

#### **Two-Level Prefetching**

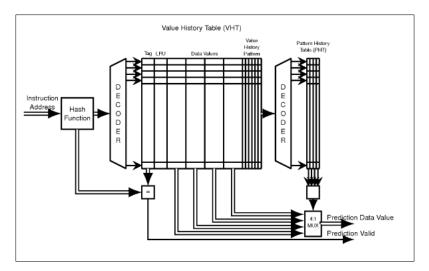

Similar to the previous methods, we index the two-level table by Program Counter (PC) of each load instruction. When an entry is updated in the table, the LRU and pattern information are updated. If the address does not already exist in the table at this location, then the least-recently-used address is replaced. As shown in Figure 2.8, the table requires four columns: Tag, LRU, Value History Pattern, and Data Values. The data values in our case are load addresses.

A second table exists called the Pattern History Table. This table is indexed by the value history pattern and ranks the addresses stored as values in the value history table. During the FETCH stage, if we hit the prefetch table for a given load instruction PC, we index the PHT at the resultant pattern. If there exists a rank greater than a pre-set threshold, then we predict that value from the prefetch table. During the MEM stage, if a value in the table is the target of a load instruction, the rank is increased. The other values in the table are decreased such that there is a net zero ranking.

As with the other tables, we are not concerned if a misprediction is made as the result will simply be a full decompression latency seen by the MEM stage and an unused value eventually being evicted from the decompression buffer.

Figure 2.8 - Two-Level Prefetch Table and Pattern History Table

#### 2.4 Thesis Motivation

Among all the works mentioned so far relating to cache compression, there exists two common gaps in the research. First, due to the impact of the decompression latency, apart from ZCA compression in [11], previous work has not used compression in L1 cache. We hope to address this issue by introducing prefetching of the decompressed information to side step this decompression latency in our architecture.

Second, all the works on compression that were mentioned above have focussed on using their compression schemes to improve performance of the cache. This work intends on reviewing the benefit of reducing the size of the cache to save power, and implementing prefetching as a means of maintaining performance.

### Chapter 3

### **Cache Compression and Prefetching**

In this chapter, we present a new architecture that combines cache compression with a prefetching mechanism to predict which memory addresses might require decompression based on the program counter of the instruction. The design of the compressor and decompressor hardware are discussed including the selection of the hierarchical carry-lookahead adder and the theory behind it.

#### 3.1 Compression Architecture

The compression architecture discussed in this work is a detailed implementation of the high-level design presented by the authors in [4]. To implement this architecture for L1 data cache, we must consider when data would be compressed and when it would be decompressed in a superscalar processor. In this architecture, data compression takes place when data is written into the cache. That is, on any write operation or a read miss. Decompression takes place on a read hit. These events are summarized in Table 3.1 and represent the major insertion points for this new architecture in a superscalar processor.

| L1 Data Cache Event | Action     |

|---------------------|------------|

| Read Hit            | Decompress |

| Read Miss           | Compress   |

| Write Hit           | Compress   |

| Write Miss          | Compress   |

Table 3.1 – Compression Events

#### Decompression

On a **Read Hit**, we check the encoding bits for the hit cache line. If the line is encoded as compressed, we put this cache line to the decompression hardware. After a number of cycles equal to the decompression latency, the uncompressed result is available at the output of the decompressor hardware. If the line is not

compressed, the line is read as usual from the cache and is available in a number of cycles equivalent to the access time of the L1 data cache.

The additional logic required to check the encoding bits to determine if the line is compressed or not is included in the design of the decompressor. The CPU can read the result from the output of the decompressor regardless of compression. If the data is uncompressed, the result will available significantly faster as it is merely passing the input data through a single multiplexer.

#### Compression

On a **Read Miss** or **Write Miss**, we check the compressibility of the data to be written into the cache line. Based on the best possible compression scheme that this data fits into, the size of the cache line is determined. Then, we check the size of the cache set at the miss address. If there is room for the new cache line, compressible or not, then it is written to the cache. If there is not enough room, we evict data in the cache at that index in an LRU fashion until there is enough room.

On a **Write Hit**, we treat compressibility in the same manner as any miss with one minor change. When determining the space remaining in the set at the write address, we do not consider the space currently occupied by the hit address. This space will be overwritten by the new write data. This is critical as the new data may consume more space and may not even be compressible. If this is the case, we can expect one or more segments to be thrown from the cache to accommodate the new data.

Because updating the cache, and therefore compression, occurs off the critical execution path, this is not a time-critical task. Therefore, each instance of writing data to the cache goes through the compressor hardware. The compressor hardware itself, as you will see later in this chapter, checks the 64-byte data for compressibility, selects the optimum compression scheme (or no compression scheme), and outputs the encoding bits and data to be written (compressed or not). This means that no additional logic is required to be added to the CPU to accommodate compression.

#### 3.1.1 **Power Considerations**

When modelling the power consumption for this compression architecture, we can take into consideration that fact that we are reading and writing smaller sets of data from and to the cache. Static power and tag dynamic power remain the same. However, we can represent the data array dynamic energy calculation as:

$$E_{dynamic, compressed} = \frac{size \ of \ compressed \ cache \ line}{size \ of \ uncompressed \ cache \ line} \times E_{dynamic, per \ access}$$

(3.1)

Relating to the cache events mentioned previously in Table 3.1, we can model power with respect to these events as well. The power impact is shown in Table 3.2.

| L1 Data Cache Event | Power Impact                    |

|---------------------|---------------------------------|

| Read Hit            | Tag Read, Data Read             |

| Read Miss           | Tag Read, Tag Write, Data Write |

| Write Hit           | Tag Read, Tag Write, Data Write |

| Write Miss          | Tag Read, Tag Write, Data Write |

Table 3.2 – Power Events

#### 3.2 Prefetching Architecture

From the compression architecture described earlier, you can see that we add decompression clock cycles for a read hit if the data is compressed in the cache. These additional cycles are necessary to allow the decompression hardware enough time to decompress the line. The purpose of the prefetching architecture is to avoid having this decompression of L1 data cache lines on the critical path of the processor. To accomplish this, we look for a way to perform decompression in parallel to other stages in the CPU. Consider the classic RISC architecture shown in Figure 3.1 [9].

Figure 3.1 – Prefetching Applied to Classic RISC Architecture

In the Instruction Fetch (IF) stage, the program counter (PC) is used to access the next instruction from memory. At this point, it is important to know if the next instruction is a load instruction, if the data to be loaded is currently compressed in L1 data cache, and most importantly, what is the address of this data in memory. If we have this information, we can then read the compressed data from L1 data cache and decompress it in parallel with the Instruction Decode (ID) and Execution (EXE) stages.

In the Memory Access (MEM) stage, data is read from memory at the address determined during the ID and EXE stages. If we have a buffer containing cache lines that have been decompressed already, we will read from here rather than from the cache.

We actually do not need to know much about the instruction to accomplish this. Similar to [14] and [15], we index our prefetch table using only the PC of the instruction. We do not populate the table every time we generate a single register result, as done in [14], nor do we populate the table on a cache miss. Rather, in our architecture we add entries to our prefetch table each time we suffer the full decompression latency on a compressed cache hit. This means that each entry represents a load instruction. At a minimum, we store the address of the compressed cache line in the cache. Depending on the prefetch table scheme, we store other information to aid in making a correct prediction of the next compressed address that is read by this load instruction.

Figure 3.2 – Prefetch Table Structure

This architecture requires updating the behavior of the CPU in two key areas: FETCH stage and MEM stage.

#### 3.2.1 **FETCH**

After we fetch an instruction, we want to know if we should begin reading from the L1 data cache. We check our prefetch table for an entry at the index of our program counter. If we return an address prediction from the table, then we populate another table called the decompression buffer. The power considerations for this table are shown in Table 3.3.

| Prefetch Table Event | Power Impact                                               |

|----------------------|------------------------------------------------------------|

| Read Hit             | Tag Read, Data Read, Decompression Buffer Tag / Data Write |

| Read Miss            | Tag Read                                                   |

Table 3.3 – Prefetch Table Power Events

If we are using one of the Two-Level prefetching schemes, we will require a second table access. This table is referred to as the Pattern History Table (PHT). In this case, if the request hits the prefetch table, a pattern is returned. We then read the PHT at the pattern index, and return a reference to a value that is stored in the prefetch table. This value is the prediction address. The power considerations for the prefetch table change as well, as we only read the table data if the PHT hits over the threshold.

| Two-Level Table Event | Power Impact                                                       |

|-----------------------|--------------------------------------------------------------------|

| Prefetch Read Hit     | Prefetch Tag Read                                                  |

| Prefetch Read Miss    | Prefetch Tag Read                                                  |

| PHT Read Hit          | PHT Read, Prefetch Data Read Decompression Buffer Tag / Data Write |

| PHT Read Miss         | PHT Read                                                           |

Table 3.4 – Two-Level Table Power Events

The decompression buffer contains the complete decompressed 64-byte cache lines. It is implemented as a FIFO cache. This buffer should be large enough that data is not being evicted before it is required in the MEM stage. However, as the table gets larger, the power consumption and access time rise. Therefore, we need to determine the best value for this table experimentally.

#### 3.2.2 **MEM**

In the MEM stage, for a load instruction, we will now know the actual address of the data to be read from the cache. At this point in the new architecture, we read the decompression buffer to see if our data exists there, decompressed. We will use the data if the PC and address of data in the buffer match the instruction that is now in the MEM stage. If the data is there, we can read it as fast as the access time for the table. The access time and power of the table depend on the size of the table.

Table 3.5 – Decompression Buffer Power Events

| Decompression Buffer Event | Power Impact                      |

|----------------------------|-----------------------------------|

| Read Hit                   | Buffer Tag Read, Buffer Data Read |

| Read Miss                  | Buffer Tag Read                   |

If we are using a stride or two-level prefetcher, we use this opportunity to update the stride and stride state or the pattern history of the entry in the prefetch table. If we must access the cache directly in the MEM stage, this is where we add entries into our prefetch table. However, we only do this if we are on the critical path. For example, we do not update our prefetch table if we are decompressing into the decompression buffer.

#### 3.3 Hardware Design

Because read latency is such an important aspect of cache memory, especially in L1 cache, this compression scheme must be implemented at the architectural level (rather than at the software / compiler level). Therefore, it requires additional hardware to implement compression / decompression. In [4], the authors provide a high-level concept of the compression and decompression schemes. However, no design is presented or evaluated. It is important to verify that the new hardware required for this proposed architecture does not have power requirements that exceed the benefit of the architecture itself. Furthermore, it is important to define the delay requirements for decompression, as this has a direct impact on the performance of the CPU in the proposed architecture. For these reasons, we designed 64-byte compressor and decompressor units in Verilog to confirm the power consumption penalty as well as the hardware delay.

#### Compressor

The compressor unit contains separate hardware to evaluate the cache line for each type of compression scheme in parallel. This method prioritizes speed over resource usage. Because much of the hardware required to evaluate the different compression schemes is the same (largely based on adders / subtractors), a more resource-optimized approach would be to evaluate each method serially using the same hardware. In the future, it would be interesting to evaluate this approach for compression, as this task does not fall on the critical execution path. In the current design, we evaluate each compression scheme in parallel with the design shown in Figure 3.3.

To perform compression, the 64-byte cache line is divided into 2, 4, or 8-byte segments. The first segment is chosen as the **base**. Then, this base is subtracted from each of the remaining segments. The result of this subtraction is the array of **deltas**. A delta is stored as either a 1, 2, or 4-byte value, depending on the compression scheme being used. If all deltas can be stored without overflow, then the compression is valid.

Variable-sized compressed cache line

Figure 3.3 – Compressor Design

#### Decompressor

The decompressor unit follows the same design, except the subtraction operation is replaced by simple addition. Unlike the compressor, it is important that we prioritize speed over resource usage in the decompressor because our intent is to minimize the decompression latency. Figure 3.4 shows the design.

To perform decompression, the compressed cache line is divided into segments depending on the encoding of the data. The first 2, 4, or 8 bytes is the base. The base is carried to the decompressed line as-is. The remaining bytes are divided into 1, 2, or 4-byte deltas. These deltas are added to the base to create the decompressed segment. As a redundancy, the first delta is always zero (representing the delta of the first segment which is the base).

Figure 3.4 – Decompressor Design

The basis of the compressor and decompressor designs used for this project are 64-bit, 32-bit, and 16-bit adders. Compression requires a subtraction operation between 8, 4, and 2-byte blocks within a single cache line depending on the compression scheme. Decompression works in the opposite manner. Addition of 8, 4, and 2-byte "bases" with 1, 2, and 4-byte "deltas" restores the data to an uncompressed state. Large adders are discussed in depth in [16] and, as with the overall design approach, provide the opportunity to prioritize

speed over resource allocation. Ultimately, we selected the hierarchical carry-lookahead adder as the basis of the design due to its balance between speed and resource usage.

#### 3.3.1 Hierarchical Carry-Lookahead Adder

The primary goal of this work is to avoid the latency of decompression on the critical execution path by using prefetching to perform decompression in parallel. However, when prefetching fails (i.e. compulsory misses during start-up, or when the predicted load address is incorrect), the processor will see the full penalty of decompression. Therefore, it is important to minimize this delay as much as possible. The delay of the decompressor depends on the design of the adders used in the new hardware.

Simple adders implement a "full adder" block for each bit and propagate carry bits serially through the circuit. While these circuits use a small number of gates, and therefore consume less power, they are very slow. Each bit requires the previous bits to be evaluated first causing many gate delays.

Alternatively, we can consider a full 64-bit carry lookahead adder. Because none of the stages execute serially, this is one of the fastest adders we can implement here. However, because each bit requires the same information as all previous bits, the complexity and size of this hardware would become excessive.

Nesbit and Smith describe a hierarchical carry-lookahead adder that divides the carry-lookahead function into 8-bit blocks, which are each evaluated serially by propagating the carry bit through the circuit [15]. This approach is a trade-off between good speed and moderate resource usage. To describe this adder, we must look at the definition for the full adder. The truth table of the full adder is shown in Figure 3.5 and Karnaugh map in Figure 3.6.

| Ci | $x_i$ | $y_i$ | $C_{i+1}$ | s <sub>i</sub> |

|----|-------|-------|-----------|----------------|

| 0  | 0     | 0     | 0         | 0              |

| 0  | 0     | 1     | 0         | 1              |

| 0  | 1     | 0     | 0         | 1              |

| 0  | 1     | 1     | 1         | 0              |

| 1  | 0     | 0     | 0         | 1              |

| 1  | 0     | 1     | 1         | 0              |

| 1  | 1     | 0     | 1         | 0              |

| 1  | 1     | 1     | 1         | 1              |

|    |       |       |           |                |

Figure 3.5 – Truth Table for Full Adder

| $c_i x_i y_i$ | 00 | 01 | 11 | 10 |

|---------------|----|----|----|----|

| 0             |    |    | 1  |    |

| 1             |    | 1  | 1  | 1  |

Figure 3.6 – Karnaugh Map for Full Adder

From the truth table and k-map, one can see that the carryout bit for a given stage can be determined as:

$$c_{i+1} = x_i y_i + x_i c_i + y_i c_i \tag{3.2}$$

And the sum bit is the XOR of the three input signals:

$$s_i = x_i \overline{y}_i \overline{c}_i + \overline{x}_i y_i \overline{c}_i + \overline{x}_i \overline{y}_i c_i + x_i y_i c_i$$

(3.3)

Factoring the carry-in provides:

$$c_{i+1} = x_i y_i + (x_i + y_i)c_i$$

(3.4)

From this equation, two important functions are defined, *generate* and *propagate*. The *generate* function is defined as:

$$g_i = x_i y_i \tag{3.5}$$

The *propagate* function is defined as:

$$p_i = x_i + y_i \tag{3.6}$$

Leaving the relationship between the carryout and these functions as being:

$$c_{i+1} = g_i + p_i c_i \tag{3.7}$$

So, let's look at the carryout of our first 8-bit block,  $c_8$ :

$$c_8 = g_7 + p_7 c_7 \tag{3.8}$$

Expanding this formula provides:

$$c_{8} = g_{7} + p_{7}g_{6} + p_{7}p_{6}g_{5} + p_{7}p_{6}p_{5}g_{4} + p_{7}p_{6}p_{5}p_{4}g_{3} + p_{7}p_{6}p_{5}p_{4}p_{3}g_{2} + p_{7}p_{6}p_{5}p_{4}p_{3}p_{2}g_{1} + p_{7}p_{6}p_{5}p_{4}p_{3}p_{2}p_{1}g_{0} + p_{7}p_{6}p_{5}p_{4}p_{3}p_{2}p_{1}p_{0}c_{0}$$

(3.9)

From this expanded view, we can define the *generate* and *propagate* signals for the entire block:

$$G_{0} = g_{7} + p_{7}g_{6} + p_{7}p_{6}g_{5} + p_{7}p_{6}p_{5}g_{4} + p_{7}p_{6}p_{5}p_{4}g_{3} + p_{7}p_{6}p_{5}p_{4}p_{3}g_{2}$$

$$+ p_{7}p_{6}p_{5}p_{4}p_{3}p_{2}g_{1} + p_{7}p_{6}p_{5}p_{4}p_{3}p_{2}p_{1}g_{0}$$

$$(3.10)$$

And,

$$P_0 = p_7 p_6 p_5 p_4 p_3 p_2 p_1 p_0 \tag{3.11}$$

Which results in,

$$c_8 = G_0 + P_0 c_0 \tag{3.12}$$

Later stages are calculated in the same way:

$$c_{16} = G_1 + P_1 c_8$$

=  $G_1 + P_1 G_0 + P_1 P_0 c_0$  (3.13)

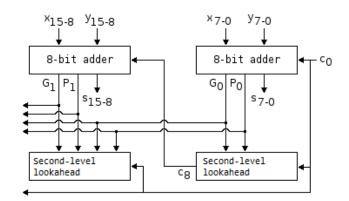

In the modules that handle 2-byte bases, 16-bit adder/subtractors are used. In the modules that handle 4byte bases, 32-bit adder/subtractors are used. Finally, in the modules that handle 8-byte bases, 64-bit adder/subtractors are used. Figure 3.7 shows the generic design of a 16-bit adder using smaller 8-bit lookahead adders.

Figure 3.7 – Adder Design

### 3.3.2 Implementation in Verilog

The above derivations are the basis of the compressor and decompressor designs in Verilog. Source files for these designs are included in Appendix A. The general structures of the designs are highlighted here to show the modularity of the designs and the significance of the adders.

#### Compressor

The structure of the compressor design in Verilog, including the test bench used to verify the design, is as follows:

```

testbench (compressor_testbench.v)

compressor (compressor.v)

bdi (bdi.v)

hadder8 (hadder8.v)

bdi32 (bdi32.v)

hadder8 (hadder8.v)

bdi16 (bdi16.v)

hadder8 (hadder8.v)

```

Figure 3.8 – HDL Structure of Compressor

The module **hadder8**, implements the 8-bit adder block from a hierarchical carry-lookahead adder. That is, it outputs the block generate  $(G_i)$  and block propagate  $(P_i)$  functions rather than the carryout  $(c_{i+1})$  as does a typical ripple-carry adder.

The next module up implements as many of these 8-bit blocks as are necessary to perform the subtraction function. These modules are also responsible for inverting the input to turn **hadder8** into a subtractor.

- bdi implements a 64-bit adder, so 8 instances of hadder8 for "base 8" compression

- bdi32 implements a 32-bit adder, so 4 instances of hadder8 for "base 4" compression

- bdi16 implements a 16-bit adder, so 2 instances of hadder8 for "base 2" compression

These modules evaluate all delta sizes in parallel. For example, **bdi** outputs three valid bits: one for base 8 delta 4, one for base 8 delta 2, and one for base 8 delta 1.

The top module, **compressor**, is responsible for instantiating blocks of **bdi**, **bdi32**, and **bdi16** on the cache line to check for all three base sizes in parallel.

- 8 instances of **bdi** for "base 8" compression on a 512-bit cache line

- 16 instances of **bdi32** for "base 4" compression on a 512-bit cache line

- 32 instances of bdi16 for "base 2" compression on a 512-bit cache line

Module **compressor** then takes all valid bits and determines which compression scheme will be used, if any.

#### **Testbench Strategy**

To test the functionality of the compressor, testing was performed using Xilinx ISE WebPACK [17]. Input stimulus to the compressor module is the 512-bit uncompressed cache line. Test points were chosen as the boundary conditions for each of the six base/delta combinations as well as a simple zeros and repeating values lines. A similar approach was taken to first test the Base-Delta-Immediate model in SimpleScalar. Test cases are shown in Table 3.6 and the compressor output is shown functioning in Figure 3.9.

| Test Case                 | Base (S <sub>0</sub> =S <sub>3</sub> ==S <sub>n</sub> ) | Delta (S1=S2)                       | Expected result        |

|---------------------------|---------------------------------------------------------|-------------------------------------|------------------------|

| Zeros                     | 0 (0x00)                                                | 0 (0x00)                            | Zeros pass.            |

| Repeating Values          | -1 (0xF…F)                                              | -1 (0xF…F)                          | Repeating values pass. |

| Base 8 Delta 1 Lower Fail | 0 (0x00)                                                | -129 (0xFFFFFFFFFFFFFFFFFF          | B8D1 fail. B8D2 pass.  |

| Base 8 Delta 1 Lower Pass | 0 (0x00)                                                | -128 (0xFFFFFFFFFFFFFFF80)          | B8D1 pass.             |

| Base 8 Delta 1 Upper Fail | 0 (0x00)                                                | 128 (0x00000000000000000)           | B8D1 fail. B8D2 pass.  |

| Base 8 Delta 1 Upper Pass | 0 (0x00)                                                | 127 (0x000000000000007F)            | B8D1 pass.             |

| Base 8 Delta 2 Lower Fail | 0 (0x00)                                                | -32,769 (0xFFFFFFFFFFFFFFFFF)       | B8D2 fail. B8D4 pass.  |

| Base 8 Delta 2 Lower Pass | 0 (0x00)                                                | -32,768 (0xFFFFFFFFFFFF8000)        | B8D2 pass.             |

| Base 8 Delta 2 Upper Fail | 0 (0x00)                                                | 32,768 (0x000000000008000)          | B8D2 fail. B8D4 pass.  |

| Base 8 Delta 2 Upper Pass | 0 (0x00)                                                | 32,767 (0x000000000007FFF)          | B8D2 pass.             |

| Base 8 Delta 4 Lower Fail | 0 (0x00)                                                | -2,147,483,649 (0xFFFFFFFFFFFFFFFF) | Not compressible.      |

| Base 8 Delta 4 Lower Pass | 0 (0x00)                                                | -2,147,483,648 (0xFFFFFFFF80000000) | B8D4 pass.             |

| Base 8 Delta 4 Upper Fail | 0 (0x00)                                                | 2,147,483,648 (0x00000008000000)    | Not compressible.      |

| Base 8 Delta 4 Upper Pass | 0 (0x00)                                                | 2,147,483,647 (0x000000007FFFFFF)   | B8D4 pass.             |

| Base 4 Delta 1 Lower Fail | 0 (0x00)                                                | -129 (0xFFFFFFFF)                   | B4D1 fail. B4D2 pass.  |

| Base 4 Delta 1 Lower Pass | 0 (0x00)                                                | -128 (0xFFFFF80)                    | B4D1 pass.             |

| Base 4 Delta 1 Upper Fail | 0 (0x00)                                                | 128 (0x0000080)                     | B4D1 fail. B4D2 pass.  |

| Base 4 Delta 1 Upper Pass | 0 (0x00)                                                | 127 (0x000007F)                     | B4D1 pass.             |

| Base 4 Delta 2 Lower Fail | 0 (0x00)                                                | -32,769 (0xFFFF7FFF)                | Not compressible.      |

| Base 4 Delta 2 Lower Pass | 0 (0x00)                                                | -32,768 (0xFFFF8000)                | B4D2 pass.             |

| Base 4 Delta 2 Upper Fail | 0 (0x00)                                                | 32,768 (0x00008000)                 | Not compressible.      |

| Base 4 Delta 2 Upper Pass | 0 (0x00)                                                | 32,767 (0x00007FFF)                 | B4D2 pass.             |

| Base 2 Delta 1 Lower Fail | 0 (0x00)                                                | -129 (0xFF7F)                       | Not compressible.      |

| Base 2 Delta 1 Lower Pass | 0 (0x00)                                                | -128 (0xFF80)                       | B2D1 pass.             |

| Base 2 Delta 1 Upper Fail | 0 (0x00)                                                | 128 (0x0080)                        | Not compressible.      |

| Base 2 Delta 1 Upper Pass | 0 (0x00)                                                | 127 (0x007F)                        | B2D1 pass.             |

Table 3.6 – Compressor Test Cases

| lame                   | 0 | ns   |       | 500 ns       |           |            | 1,000 ns            |       | 1,500 ns           |        | 2,000 ns         |         | 2,5       |

|------------------------|---|------|-------|--------------|-----------|------------|---------------------|-------|--------------------|--------|------------------|---------|-----------|

| 64-Byte Cache Line     |   |      |       |              |           |            |                     |       |                    |        |                  |         |           |

| x[511:0]               | 0 |      | 0)    | 0 <u>)</u> 0 | χοχο      | χ <u>ο</u> | (0 X 0 X 0 X        | οχο)  | <u>(0 ) (0 ) (</u> | χοχο   | <u>(0) (0) (</u> | οχοχο   | <u>x</u>  |

| Compressed Cache Lines | ; |      |       |              |           |            |                     |       |                    |        |                  |         |           |

| 🔣 zeros[7:0]           |   |      |       |              |           |            | 00                  |       |                    |        |                  |         |           |

| 📲 repeats[63:0]        | 0 | (ff) |       | 000          | 000000000 | 00000      |                     | )(ff) | ff                 |        | (0)(0)(0         | οχοχο   | <u>x-</u> |

| b8d1[127:0]            | 0 |      | 00000 | 0 \ 0        | χ00000    | χ000       | <u>0 χοσοσο χ</u>   | 0χ0   | 0                  | χοχο   | (0)(0)(          | οχοχο   | <u>x-</u> |

| 🔣 b4d1[159:0]          | 0 |      | 0)(0) | 0 \ 0        | χο χο     | χο)        | (0) (0)             | 0χ0   | 00000 XC           | χοχοοο | φοχοχα           | οχοχο   | <u>}</u>  |

| Ng b8d2[191:0]         | 0 |      | 0)(0) | 0 <u>0</u>   | χ00000    | χο)        | <u>(0 x 00000 x</u> | 0χ0   | 0X0X0              | χοχο   | (0)(0)(          | 0 у0 у0 | <u>}</u>  |

| <pre>b2d1[271:0]</pre> | 0 |      | 0)    | 0 <u>0</u>   | χοχο      | χο         | (0 X 0 X 0 X        | οχο   | 0 <u>x</u> 0 x0    | χοχο   | (0)(0)(          | Dχ00000 | <u>}</u>  |

| 🏹 b4d2[287:0]          | 0 |      | 0)(0) | 0 0          | χοχο      | χο         | (0 X 0 X 0 X        | 0χ0   | 0                  | χοχοοο | φοχοχα           | οχοχο   | <u>}</u>  |

| 🏹 b8d4[319:0]          | 0 |      | 0)(0) | 0 (0         | χο χο     | χο         | <u>(0 x 00000 x</u> | 0χ0   | 0                  | χοχο   | (0)(0)(          | 0       | :*        |

| Valid Bits             |   |      |       |              |           |            |                     |       |                    |        |                  |         |           |

| 🕼 zeros_valid          |   |      |       |              |           |            |                     |       |                    |        |                  |         |           |

| 🕼 repeats_valid        |   |      |       |              |           |            |                     |       |                    |        |                  |         |           |

| 🔓 b8d1_valid           |   |      |       |              |           |            |                     |       |                    |        |                  |         |           |

| 🔓 b4d1_valid           |   |      |       |              |           |            |                     |       |                    |        |                  |         |           |

| 🔓 b8d2_valid           |   |      |       |              |           |            | L                   |       |                    |        |                  |         |           |

| 🔓 b2d1_valid           |   |      |       |              |           |            |                     |       |                    |        |                  |         |           |

| 🗓 b4d2_valid           |   |      |       |              |           |            |                     |       |                    |        |                  |         |           |

| 🗓 b8d4_valid           |   |      |       |              |           |            |                     |       |                    |        |                  |         |           |

Figure 3.9 – Testbench Waveforms for Compressor in Xilinx ISE

#### Decompressor

The structure of the decompressor design in Verilog, including the test bench used to verify the design, is as follows:

```

testbench (decompressor_testbench.v)

decompressor (decompressor.v)

hadd (hadd.v)

hadder8 (hadder8.v)

hadd32 (hadd32.v)

hadder8 (hadder8.v)

hadder8 (hadder8.v)

hadd16 (hadd16.v)

hadder8 (hadder8.v)

```

Figure 3.10 – HDL Structure of Decompressor

The **hadder8** module is identical to that of the compressor. The key differences between the decompressor and compressor are that the second level modules (**hadd**, **hadd32**, and **hadd16**) do not convert **hadder8** into a subtractor and they do not have to evaluate delta overflow. These modules strictly build the 64-bit, 32-bit, and 16-bit hierarchical carry-lookahead adders.

- hadd implements a 64-bit adder, so 8 instances of hadder8 for "base 8" decompression

- hadd32 implements a 32-bit adder, so 4 instances of hadder8 for "base 4" decompression

- hadd16 implements a 16-bit adder, so 2 instances of hadder8 for "base 2" decompression

The top module, **decompressor**, has much more work to do than that of the compressor. This module must instantiate adders for each compression scheme, not just for each base.

- 8 instances of hadd for "base 8 delta 1" decompression on a 128-bit cache line

- 8 instances of hadd for "base 8 delta 2" decompression on a 192-bit cache line

- 8 instances of hadd for "base 8 delta 4" decompression on a 320-bit cache line

- 16 instances of hadd32 for "base 4 delta 1" decompression on a 160-byte cache line

- 16 instances of hadd32 for "base 4 delta 2" decompression on a 288-byte cache line

- 32 instances of hadd16 for "base 2 delta 1" decompression on a 272-byte cache line

With all these instances, module **decompressor** attempts decompress an input cache line using all 8 methods at once and even outputs a 512-bit decompressed cache line for each. Only the line with an associated valid bit contains the correct data. Module **decompressor** sets this valid bit based on the input encoding bits.

# Chapter 4

## **Simulation Methodology**

In this chapter, we discuss the method for evaluating the performance of the new compression and prefetching architecture. The tools required to perform this analysis are discussed as well as the environment used to perform testing.

## 4.1 Methodology

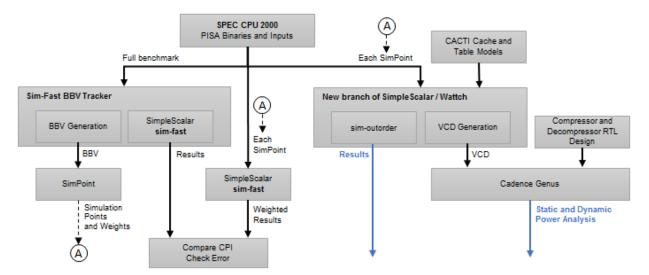

In this section, we describe four key tools used in performing this work: SimPoint, CACTI, SimpleScalar, and Wattch.