# Complete Model-Based Testing Applied to the Railway Domain

### Dissertation

zur Erlangung des akademischen Grades eines Doktors der Ingenieurwissenschaften – Dr.-Ing. –

vorgelegt von

Felix Hübner

im Oktober 2017

Fachbereich 3 (Mathematik / Informatik)

# Complete Model-Based Testing Applied to the Railway Domain

### Dissertation

zur Erlangung des akademischen Grades eines Doktors der Ingenieurwissenschaften – Dr.-Ing. –

vorgelegt von

# Felix Hübner

im Fachbereich 3 (Mathematik / Informatik) der Universität Bremen im Oktober 2017

Datum des Kolloquiums: 10.Januar 2018

Gutachter: Prof. Dr. Jan Peleska (Universität Bremen) Gutachter: Prof. Mohammad Reza Mousavi, Ph.D. (University of Leicester)

# **Summary**

Testing is the most important verification technique to assert the correctness of an embedded system. Model-based testing (MBT) is a popular approach that generates test cases from models automatically. For the verification of safety-critical systems, complete MBT strategies are most promising. Complete testing strategies can guarantee that all errors of a certain kind are revealed by the generated test suite, given that the system-under-test fulfils several hypotheses. This work presents a complete testing strategy which is based on equivalence class abstraction. Using this approach, reactive systems, with a potentially infinite input domain but finitely many internal states, can be abstracted to finite-state machines. This allows for the generation of finite test suites providing completeness. However, for a system-under-test, it is hard to prove the validity of the hypotheses which justify the completeness of the applied testing strategy. Therefore, we experimentally evaluate the fault-detection capabilities of our equivalence class testing strategy in this work. We use a novel mutation-analysis strategy which introduces artificial errors to a SystemC model to mimic typical HW/SW integration errors. We provide experimental results that show the adequacy of our approach considering case studies from the railway domain (i.e., a speed-monitoring function and an interlocking-system controller) and from the automotive domain (i.e., an airbag controller). Furthermore, we present extensions to the equivalence class testing strategy. We show that a combination with randomisation and boundary-value selection is able to significantly increase the probability to detect HW/SW integration errors.

# **Zusammenfassung (auf Deutsch)**

Testen ist die wichtigste Verifikationstechnik, um die Korrektheit eines eingebetteten Systems zu überprüfen. Modellbasiertes Testen (MBT) kommt seit mehreren Jahren eine große Bedeutung zu. Hierbei werden Testfälle automatisch aus Modellen abgeleitet. Besonders vielversprechend für den Test von sicherheitskritischen Systemen sind komplette Testverfahren. Komplette Testverfahren garantieren alle Fehler einer bestimmten Fehlerklasse aufzudecken, sofern das zu testende System einige Eigenschaften erfüllt. In dieser Arbeit setzen wir ein solches Verfahren um. Dieser Ansatz basiert auf der Äquivalenzklassenpartitionierung von Reaktiven Systemen mit einem potentiell unendlich großen Eingabebereich und einer endlichen Menge von internen Zuständen. Der daraus resultierende endliche Automat ermöglicht das Erzeugen einer endlichen Menge an Testfällen, welche Komplettheitseigenschaften aufweist. Da sich die Hypothesen von kompletten Testverfahren für das zu testende System in der Regel nicht beweisen lassen, ist es Ziel dieser Arbeit, experimentell nachzuweisen, dass das entwickelte Testverfahren eine hohe Fehleraufdeckungsrate besitzt. Hierbei verwenden wir ein neuartiges Mutationsanalyse Verfahren, welches künstliche Fehler in ein SystemC-Modell einfügt und somit typische HW/SW Integrationsfehler nachempfindet. Eine akzeptable Fehleraufdeckungsrate konnte für Fallbeispiele aus dem Bahnbereich (ein System zur Zuggeschwindigkeitsüberwachung und eine Stellwerkssteuerung) sowie ein weiteres Fallbeispiel aus dem Automobilbereich (ein Airbag-Steuergerät) nachgewiesen werden. Außerdem zeigen wir, dass sich die Fehleraufdeckungsrate durch die Kombination des Äquivalenzklassenverfahrens mit Randomisierung und Grenzwerttests noch deutlich steigern lässt.

# **Acknowledgements**

At the moment of this writing, I am missing words to describe all the emotions that I am currently experiencing. Though this text appears at the very beginning of this work, I am writing these words at the end of a very long journey. Looking back makes me feel grateful, proud, relieved, happy, and—at the very same time—sad that a journey has now come to an end. It has been three years and five months since I started this work. Right now, I do not remember the first doubts, the first days of stress facing the large challenge of handling all of the time-consuming duties related to teaching on the one hand and a supervisor pushing me to my first publication on the other hand. Instead, I remember the great excitement of the first submission, the first acceptance, the great excitement and gladness after my first teaching experience—especially my first lecture in front of hundreds of students. I remember the great days at my office that I owe to my nice colleagues and my supervisor. I remember the invaluable pleasure of working on a topic that is complex, promising, challenging and offers significant technological advance. It has been exciting to work at the leading edge of technology in the domain of model-based testing. Starting as a doctoral student, I always feared the painful path that lay in front of me. That this path was never painful but instead always pleasurable is mainly due to many people who accompanied me. Therefore, I would like to take the opportunity to say thank you.

First and foremost I want to express my great gratitude to Jan Peleska: Thank you for your invaluable support as my supervisor. At the beginning of my doctoral studies, you pushed, motivated and always praised me at the right moments. You gave me guidance in the right directions and you provided me with the possibility to work on an overly interesting topic. Especially at the end, your precious remarks on this dissertation have greatly influenced this work. Even before I started my doctoral position at your department, you had greatly influenced my academic career. From my time as a young bachelor student on, I was impressed by your ability to make desperately complicated topics enjoyable. This made me attend almost every one of your lectures. I learned a lot, mainly because of your great manner of teaching, which I always admired. Thank you as well for all the motivating words of praise that you generously gave to me. This among other things has made our joint work on publications and teaching a pleasure for me.

Furthermore, I want to thank Mohammad Reza Mousavi for being the second reviewer of this work. I hope that you will enjoy reading this work as I enjoyed writing it. I have known you as a prominent expert of model-based testing since my stay in Halmstad for the Summer School of Testing in 2013. I hope that some of the passion for formal testing methods by which I was inspired in Halmstad can be sensed upon reading this work.

Another thank-you goes to Siemens for the funding of my dissertation. In particular, I want to thank Ralf Pinger and Jens Braband. I very much enjoyed my stays in Braunschweig, where you prepared exciting and well-organised meetings of the Siemens International Rail Automation Graduate School (iRAGS).

As mentioned, every-day life at university was a pleasure. This is due to all the nice colleagues I had the opportunity to work with. Thank you Christoph, Uwe, Wen-ling, Florian, Cécile, Blagoy

and Birgit for the friendly atmosphere at the working group AGBS, for good discussions during lunches and coffee breaks. Christoph, Uwe and Florian were always on the spot for nice talks for distraction, and they also helped med with technical problems whenever I needed assistance. The same is true for Frank, Fabian, Laurens and Niklas who, although not officially part of the working group AGBS, were always on the spot. Special thanks to Niklas for proofreading and helpful remarks.

I am very grateful to the University of Bremen. I started my Bachelor's studies in 2008. Since then, the University of Bremen has become the centre of my everyday life. I enjoyed my time and love the atmosphere of this charming University, which I will always promote with pride as an excellent place to learn and to do research in a great environment. Of course, the University of Bremen as an institution is a union of many people. I would like to personally thank some of them. Thank you to Görschwin Fey, Robert Wille, Martin Gogolla, Daniel Grosse and Ulrich Kühne for offering support as supervisors in the context of the Graduate school of System Design (SyDe). Thank you to all fellow students of SyDe for the SyDe meetings with interesting talks and discussions. I also wish to thank Karsten Hölscher. With your excellence in teaching and your kind, cooperative and humorous nature, you made the otherwise demanding struggles of teaching much less painful. In the end, teaching became an experience that I will remember gladly.

Endless gratitude is devoted to my family. Probably the decision to start doctoral studies often requires some bravery, self-confidence and optimism. The fact that I am in a position to have these prerequisites at hand is possible only due to your unquestionable support. The fact that you always stand by my side without my need to ask or thank you for is invaluable. I know that I can always rely on you, and this made it possible for me to never feel serious doubt. You support me on the hardest journeys and would evidently run the last half of a marathon with me to get me to the finish line.

# Contents

| 1 | Intr | oduction 13                                                           |  |  |  |  |  |  |

|---|------|-----------------------------------------------------------------------|--|--|--|--|--|--|

|   | 1.1  | Model-Based Testing Applied to the Railway Domain                     |  |  |  |  |  |  |

|   | 1.2  | Goals and Contribution                                                |  |  |  |  |  |  |

|   |      | 1.2.1 Relation to Previous Work                                       |  |  |  |  |  |  |

|   |      | 1.2.2 Main Goal of this Work                                          |  |  |  |  |  |  |

|   |      | 1.2.3 Main Contributions                                              |  |  |  |  |  |  |

|   | 1.3  | Structure of this Thesis                                              |  |  |  |  |  |  |

| 2 | Bac  | kground 19                                                            |  |  |  |  |  |  |

|   | 2.1  | The Railway Domain                                                    |  |  |  |  |  |  |

|   |      | 2.1.1 ERTMS and ETCS                                                  |  |  |  |  |  |  |

|   |      | 2.1.2 Interlocking Systems                                            |  |  |  |  |  |  |

|   |      | 2.1.3 On-Board Train Protection                                       |  |  |  |  |  |  |

|   | 2.2  | System Modelling                                                      |  |  |  |  |  |  |

|   |      | 2.2.1 Systems Modeling Language                                       |  |  |  |  |  |  |

|   |      | 2.2.2 SystemC                                                         |  |  |  |  |  |  |

|   | 2.3  | Testing                                                               |  |  |  |  |  |  |

|   |      | 2.3.1 Definitions and Nomenclature                                    |  |  |  |  |  |  |

|   |      | 2.3.2 Requirement-Based Testing                                       |  |  |  |  |  |  |

|   |      | 2.3.3 Model-Based Testing                                             |  |  |  |  |  |  |

|   | 2.4  | Testing Theory of Finite-State Machines                               |  |  |  |  |  |  |

|   |      | 2.4.1 Finite-State Machine Definitions and Notations                  |  |  |  |  |  |  |

|   |      | 2.4.2 Complete Testing Theories                                       |  |  |  |  |  |  |

|   | 2.5  | Complete Model-Based Tests by Equivalence Class Partition Testing 50  |  |  |  |  |  |  |

|   |      | 2.5.1 Reactive Input-Output State-Transition Systems                  |  |  |  |  |  |  |

|   |      | 2.5.2 Input Equivalence Class Partitioning                            |  |  |  |  |  |  |

|   |      | 2.5.3 Fault Domain and the Completeness Property                      |  |  |  |  |  |  |

|   |      | 2.5.4 Independence on Syntactic Model Representations                 |  |  |  |  |  |  |

|   |      | - · · · · · · · · · · · · · · · · · · ·                               |  |  |  |  |  |  |

| 3 | Case | e Studies 69                                                          |  |  |  |  |  |  |

|   | 3.1  | Speed and Distance Monitoring of the European Train Control System 69 |  |  |  |  |  |  |

|   | 3.2  | A Route-Based Interlocking System Featuring Sequential Release        |  |  |  |  |  |  |

|   | 3.3  | Airbag Controller                                                     |  |  |  |  |  |  |

| 4 | Test | ting Methodology 79                                                   |  |  |  |  |  |  |

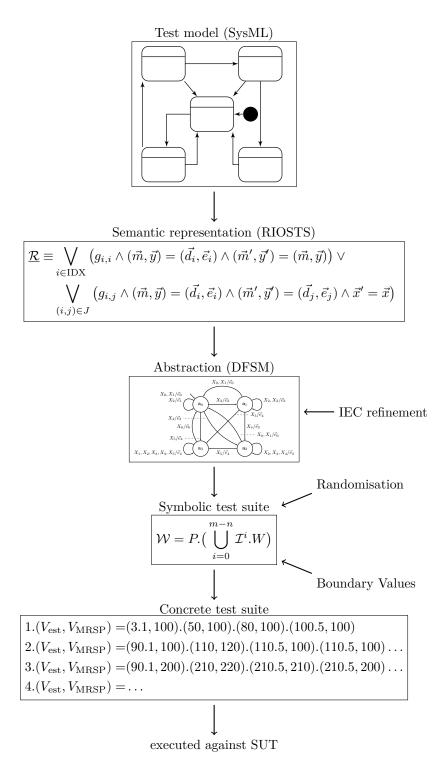

|   | 4.1  | Overview                                                              |  |  |  |  |  |  |

|   | 4.2  | Formal Modelling of Interlocking Systems                              |  |  |  |  |  |  |

|   |      | 4.2.1 Compositional Reasoning Applied to Interlocking Systems         |  |  |  |  |  |  |

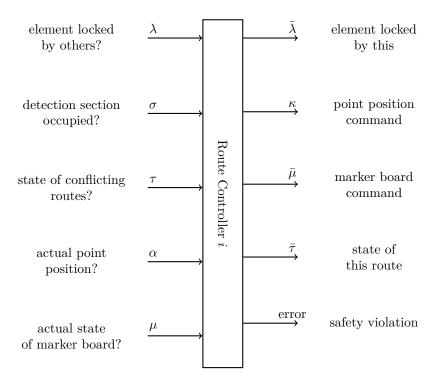

|   |      | 4.2.2 Route-Controller Component Interfaces                           |  |  |  |  |  |  |

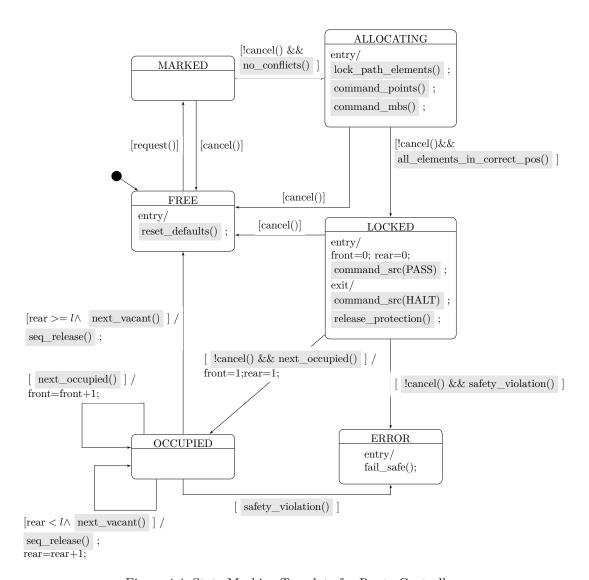

|   |      | 4.2.3 Generic Behaviour of Route Controllers                          |  |  |  |  |  |  |

|   |      | 4.2.4 Extraction of Local Behavior 84                                 |  |  |  |  |  |  |

|     | 4.3                                           | Equiva  | lence Class Partition Testing                                                 | 88  |  |  |  |

|-----|-----------------------------------------------|---------|-------------------------------------------------------------------------------|-----|--|--|--|

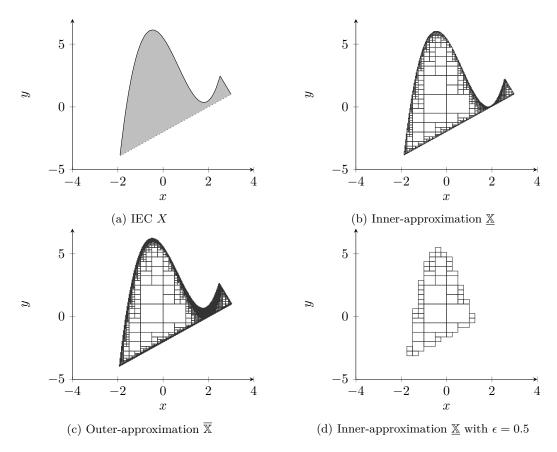

|     | 4.3.1 Refinement of Input Equivalence Classes |         |                                                                               |     |  |  |  |

|     |                                               | 4.3.2   | Randomisation of Concrete Input Selection                                     | 92  |  |  |  |

|     |                                               | 4.3.3   | Boundary-Value Selection                                                      | 101 |  |  |  |

|     |                                               | 4.3.4   | Extension of Test Cases for the Heuristic Exploration of Additional States    | 105 |  |  |  |

|     |                                               | 4.3.5   | Implementation-Efficiency Considerations                                      | 109 |  |  |  |

|     |                                               |         | •                                                                             | 100 |  |  |  |

| 5   |                                               |         | proach to Mutation Analysis for HW/SW Integration Tests                       | 117 |  |  |  |

|     | 5.1                                           |         | on Analysis State-of-the-Art                                                  | 117 |  |  |  |

|     |                                               | 5.1.1   | Model Mutations                                                               | 118 |  |  |  |

|     |                                               | 5.1.2   | SW-Mutation Analysis                                                          | 119 |  |  |  |

|     |                                               | 5.1.3   | HW-Mutation Analysis                                                          | 119 |  |  |  |

|     | 5.2                                           |         | W-Mutation Analysis                                                           | 120 |  |  |  |

|     |                                               | 5.2.1   | The Need for a Formal Fault Model of Typical ${\rm HW/SW}$ Integration Errors | 120 |  |  |  |

|     |                                               | 5.2.2   | Requirements for a Mutant Generation Tool of Typical HW/SW Integra-           |     |  |  |  |

|     |                                               |         | tion Errors                                                                   | 120 |  |  |  |

|     |                                               | 5.2.3   | A SystemC Mutation Tool                                                       | 121 |  |  |  |

| 6   | Evne                                          | rimont  | al Evaluation                                                                 | 127 |  |  |  |

| U   | 6.1                                           |         | mental Setup                                                                  | 127 |  |  |  |

|     | 0.1                                           | 6.1.1   | Compared Strategies                                                           | 127 |  |  |  |

|     |                                               | 6.1.1   | Conduction of Experiments                                                     | 127 |  |  |  |

|     | 6.2                                           | -       |                                                                               | 129 |  |  |  |

|     | $6.2 \\ 6.3$                                  |         | mental Results                                                                | 134 |  |  |  |

|     |                                               |         | ministic Finite-State Machine Experiments for Additional States Mutations     |     |  |  |  |

|     | 6.4                                           |         | s to Validity                                                                 | 138 |  |  |  |

|     |                                               | 6.4.1   | Dependence on Syntactic Model Representation                                  | 138 |  |  |  |

|     |                                               | 6.4.2   | Threats Caused by Model Selection                                             | 138 |  |  |  |

|     |                                               | 6.4.3   | Threats Caused by the Mutant Generator                                        | 138 |  |  |  |

|     |                                               | 6.4.4   | Dependencies on the DFSM Test Strategies Applied                              | 139 |  |  |  |

|     |                                               | 6.4.5   | Runtime Error Detection                                                       | 139 |  |  |  |

|     |                                               | 6.4.6   | Significance of SystemC Mutations as Surrogates for Real HW/SW Integ-         | 100 |  |  |  |

|     |                                               | 0.45    | ration Faults                                                                 | 139 |  |  |  |

|     |                                               | 6.4.7   | Threats Concerning the Deterministic Finite-State Machine Mutations           | 140 |  |  |  |

| 7   | Rela                                          | ted Wo  | ork                                                                           | 141 |  |  |  |

|     | 7.1                                           | Model-  | based Testing                                                                 | 141 |  |  |  |

|     | 7.2                                           | Equiva  | lence Class Partition and Boundary-value Testing                              | 143 |  |  |  |

|     | 7.3                                           | Adapti  | ve Random Testing                                                             | 144 |  |  |  |

|     | 7.4                                           |         | on Analysis and Mutation Testing                                              | 145 |  |  |  |

|     |                                               | 7.4.1   | Model-Based Mutation Testing                                                  | 146 |  |  |  |

|     |                                               | 7.4.2   | SW-Mutation Analysis                                                          | 146 |  |  |  |

|     |                                               | 7.4.3   | HW-Fault Injection                                                            | 147 |  |  |  |

|     |                                               | 7.4.4   | SystemC-Based Fault Injection                                                 | 147 |  |  |  |

|     |                                               | 7.4.5   | High-Order Mutation Testing                                                   | 147 |  |  |  |

| 8   | Con                                           | clusion |                                                                               | 149 |  |  |  |

|     |                                               |         |                                                                               | 173 |  |  |  |

| Bil | bliogr                                        | aphy    |                                                                               | 153 |  |  |  |

| Lis | ist of Figures 163                            |         |                                                                               |     |  |  |  |

|                  | Contents |

|------------------|----------|

| List of Tables   | 165      |

| List of Listings | 167      |

| Glossary         | 169      |

# 1 Introduction

# 1.1 Model-Based Testing Applied to the Railway Domain

Nowadays, embedded systems are becoming more and more complex. At the same time, these systems are used in more contexts and more domains and take over more and more functionality—including safety-related functionality. Though safety once relied on human supervision, it is now replaced by supervision and intervention by embedded systems. Autonomous driving, autonomous flight and train-protection systems are examples of safety-critical functionality that allows for a higher degree of safety. However, the safety functionality provided by an embedded system assumes correct functionality and imposes, in most cases, high reliability and availability constraints on the system. The higher the level of reliability and availability constraints (i.e., the higher the safety criticality), the higher the need for formal methods for the verification and validation of such systems. Among the verification methods to be considered are formal proofs and model checking and testing. While formal proofs and model checking are in most cases applied to formal models, testing can be applied to the final system. In the case of embedded systems, testing can be applied to the final integrated HW/SW system, but also to subsystems running on the final target hardware, or in simulators, HW emulators or combinations of these possibilities. The flexibility of testing—and the fact that testing in most cases is the only way to assess the functional correctness of a system—probably makes it the most important verification technique in practice. No train, no driving assistant, no autopilot, no satellite-control software will get certification credit without being tested.

However, testing is usually incomplete. While formal proofs and model checking allow for absolute statements about the validity of certain properties, it is not usually feasible to test all possible combinations of inputs. Considering the reactive nature of embedded systems, the enormous (possibly infinite) space of input combinations is further magnified, because sequences of element from this infinite space have to be considered. Thus, a finite number of test cases have to be selected from an un-countably infinite set of possibilities. The loss of generality based on this selection process cannot be prevented. Yet, an increase in the number of test cases can raise confidence in the correctness of a system.

In many cases, time to deliver is a critical factor. The success of an embedded-systems supplier is largely dependent on its ability to satisfy complex customer needs within restricted time and monetary budgets. Therefore, testing activities must always be conducted in the limited time-frame of the project. This is why a testing campaign is always assigned end criteria. Usually, a test-end criterion on the system level concerns requirements coverage. Requirement-based testing can be considered the state-of-the-art of functional system-level tests. Safety-related standards [Eur96, ECS09, RTC92] require that every requirement is tested. This is regarded as a practical guideline for a test engineer. Usually, tests will be specified for each requirement and then implemented. Since requirements are in principle as precise, concrete and atomic as possible so they can be implemented by a developer, they can in most cases provide adequate inputs for test-case specification as well. However, in practice, the manual

definition of test cases is time-consuming and error-prone. In most cases, the situation is even worse because of suboptimal requirements, changes in requirements and resulting inconsistencies between requirements, implementation and test cases. The task of keeping a higher-level test-case specification consistent with its concrete implementation is another challenge. All these challenges and issues make testing activities as vulnerable to faults and errors as the developed system-under-test (SUT) that is the target of the testing effort and whose reliability is to be proven by tests.

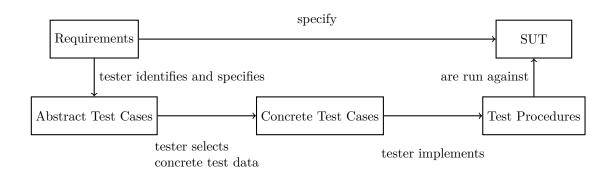

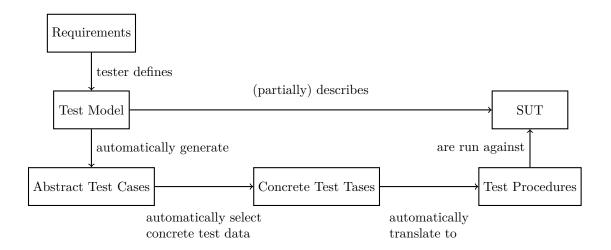

Model-Based Testing (MBT) can provide an answer to these challenges. MBT aims at the automatic generation of test cases from a formal test model. Instead, of manually defining test cases, a test engineer specifies a test model. Then the test-case specification and implementation can be automatically derived from the test model. This shifts the effort needed for manual test-case specification and implementation to the creation of a test model. Since the test model should be described in an abstract modelling language—e.g., Unified Modeling Language (UML)/Systems Modeling Language (SysML) or a Domain Specific Language (DSL)—the abstraction level of this test model should enable the test engineer to focus on the specification of the expected behaviour of the SUT. Additionally, the test model will describe the SUT or parts of the SUT as a whole, making it possible to specify the interaction of requirements in an abstract formalism. System properties that emerge from the implicit interplay of requirements can be described by such models.

The automation that results from the use of MBT allows for more tests in shorter time periods. Furthermore, inconsistencies can be prevented if test-case specification and implementation are generated from the same source. This single source of information eases change management. Requirement changes result in an update of the test model, and the generated test cases automatically reflect these changes. This is less costly and less error-prone than investigating the impact of changed requirements on a set of a thousands of test cases—especially considering the implicit changes that are attributed to the combination of multiple requirements.

If requirements are traced to model elements, MBT can generate test cases to cover the model elements related to a requirement. Thus, requirements coverage can be achieved by using a set of automatically generated tests. However, MBT allows for more sophisticated coverage criteria than requirements coverage. Having a test model that is independent of a concrete test approach usually makes it possible to apply arbitrary testing strategies and model-coverage criteria. Consequently, the use of MBT makes it possible to profit from any advances in MBT, given that these advances are applicable to the test model under consideration.

Most MBT tools are able to generate test suites which fulfil typical structural-coverage criteria—like covering all states or all transitions in a state machine model. These structural criteria are surpassed by testing strategies that are complete. Completeness cannot be achieved in most cases. If, however, assumptions can reasonably be made about the errors an SUT might exhibit, it is possible to derive test suites that are complete with respect to a fault model. The model describes a set of systems that may or may not contain errors. This set of systems and potential errors is, however, restricted by the a-priori assumptions concerning possible faults. Usually, the set of systems fulfilling the a-priori assumptions—named the *fault domain*—is of infinite size. Given that the SUT behaviour is contained in the fault domain, the test suite is complete: i.e., the test suite will pass if and only if the SUT is correct. For Finite-State Machines (FSMs) and Deterministic Finite-State Machines (DFSMs), many complete testing theories exist. This work deals with a testing strategy [HP16a] that is complete with respect to a fault domain but is applicable to a wider range of systems. Instead of FSMs, which require a finite input alphabet, our approach is applicable to state-transition systems with input variables of

potentially infinite domains. The internal and output variables of these systems are required to be of a finite domain.

We will demonstrate the applicability of our approach to real-world case studies from the rail-way domain. Railways are one of the oldest industries building complex systems with high safety criticality. Nowadays, legacy systems, like relay-based interlocking systems, are replaced by modern, digital, interlocking systems. Within the European Train-Control System (ETCS) programme, interlocking systems and on-board computers are digitalised and modernised. The high complexity and safety criticality of railways makes the use of formal verification methods mandatory. For modern interlocking systems, a formal model exists, which has been model checked and proven [VHP17] to fulfil safety properties. Our work builds on these results and uses the formal model for HW/SW integration (HSI) tests of modern interlocking systems. Additionally, a speed-monitoring function of the ETCS train on-board computer serves as another case study, demonstrating the applicability of our MBT approach for railways.

# 1.2 Goals and Contribution

#### 1.2.1 Relation to Previous Work

This work implements a novel MBT testing method originally proposed in [HP16a]. This approach, called Equivalence Class Partition Testing (ECPT) in the following, is based on a sophisticated input-equivalence partitioning which makes it possible to reduce arbitrarily large input domains to a finite number of equivalence classes. Furthermore, the approach has guaranteed (mathematically proven) fault-detection capabilities. This property ensures completeness of the ECPT approach with respect to a formal fault domain: i.e., with respect to a very large, potentially infinite set of potential SUTs. For all members from the fault domain, it is guaranteed that the test suite generated by the ECPT approach is passed if and only if the SUT is correct. Every fault in an SUT that is member of the fault domain will be detected by the test suite.

#### 1.2.2 Main Goal of this Work

This work aims to prove that MBT as a formal verification technique is applicable to a wide range of systems—including complex, real-world case studies from the railway domain. We promote ECPT testing as a way to thoroughly test an SUT with guaranteed completeness with respect to a fault model. To give a convincing argument in favour of ECPT testing, we show that the completeness of our approach actually results in measurable failure-detection capabilities. Therefore, we use a novel mutation analysis that focuses on the test strength evaluation of HSI testing.

#### 1.2.3 Main Contributions

The main contributions of our work to the field of MBT can be summarised as follows:

1. Extension of the ECPT approach: This work presents an implementation of the ECPT approach and extensions to the approach invented by the authors of [HP16a]. The extensions include a heuristic optimisation of concrete test data selection: Tests are characterised

by a sequence of Input Equivalence Classes (IECs). To make these "symbolic" test cases executable against an implementation, concrete values from IECs have to be selected. We will show that the concrete input selection from the IEC has a strong impact on the test strength under "real-world" conditions: i.e., for systems that cannot be proven to be captured by a fault domain that can be anticipated a-priori in case of black-box tests. Our aim is to *improve* ECPT for the detection of real faults that are not necessarily part of an anticipated fault domain.

- 2. Thorough experimental evaluation: To gain evidence for improvements of the fault-detection capabilities, we need a thorough experimental evaluation. This evaluation shall investigate the test strength (defined as the fault-detection capability of a testing approach) of the implemented ECPT approach with different input-selection heuristics. Furthermore, it shall allow for comparison with other testing approaches. This work compares all presented heuristics with Random Testing (RT), which serves as a minimal benchmark that has to be surpassed by any sophisticated testing methodology.

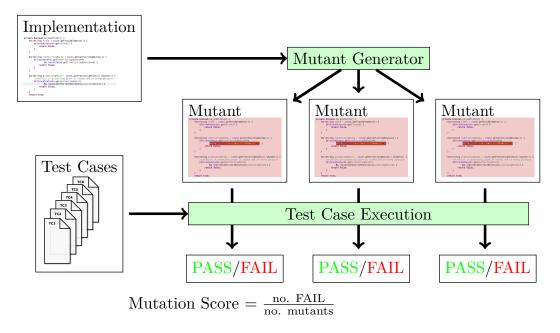

- 3. Proposal of a Novel HW/SW integration test (HSI test) Evaluation Approach: The ECPT approach offers functional testing of embedded systems at high abstraction levels: i.e., at the system and HSI levels. Mutation analysis is a way to evaluate testing approaches. By systematic fault injection to a correct version of the SUT (resulting in an erroneous version of the SUT called mutant), the fault-detection capabilities of a test suite can be measured. A variety of work has been done on SW mutation analysis, some of which yields evidence that artificial mutants serve as good surrogates for real faults. However, in the domain of HSI testing, no real means exist by which to evaluate the test strength. State-of-the-art metrics like code coverage are of limited use if testing approaches are evaluated [JJI+14]. This lack of HSI test mutation analysis led to the development of a novel, completely automated, mutant generator of SystemC models. This mutant generator not only mimics typical HW/SW errors, but also errors that can be introduced by HW/SW incompatibilities.

- 4. Efficiency considerations for the implementation of the ECPT approach: This work also aims to provide some insight into the implementation of the testing approach. We present some core algorithms that render the ECPT approach realisable for real-world examples of considerable complexity.

- 5. Proposal of a generic approach for compositional testing of route controllers: Finally, we provide a formalisation of the generic behaviour of a route controller: i.e., a safety-critical sub-component of modern interlocking systems that controls train movements in a railway network. This formalisation can be used to automatically generate a model of route-controller behaviour that can be used to apply our ECPT to components from modern interlocking systems.

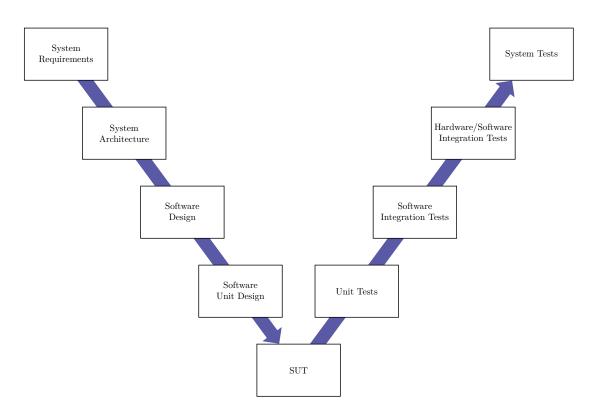

# 1.3 Structure of this Thesis

Chapter 2 summarizes the basics that are needed to understand our approach and to make this work self-contained. Chapter 3 introduces four case studies. Our approach is applied to these models and experiments are conducted on these models. Next, we detail the ECPT approach in Chapter 4 and present our extensions of the ECPT approach. This chapter also details the generic approach for testing route controllers of modern interlocking systems. Chapter 5 introduces our

novel approach for test-strength evaluation of HSI tests. We briefly depict the state-of-the-art of mutation analysis and then motivate and present our new mutation-analysis method by using SystemC mutations. This approach is then used for our experiments. Chapter 6 exhibits and discusses experimental results. Following this, Chapter 7 presents a thorough discussion of related work before this work is concluded in Chapter 8.

# 2 Background

This chapter summarises the basics that are needed to understand our approach and to make this work self-contained. First, we introduce some basics of the railway domain. Section 2.2 introduces two state-of-the-art approaches to the modelling of systems: SysML and SystemC. Section 2.3 and the following introduce terminology related to testing, a complete testing theory for FSMs and finally the complete testing theory based on input equivalence classes that we will apply in this work.

# 2.1 The Railway Domain

#### 2.1.1 ERTMS and ETCS

The European Rail-Traffic Management System (ERTMS) is a European standard for rail-traffic management. It has been established by a directive of the European Council [Eur96]. The objectives of ERTMS are to improve the interoperability, capacity and safety of rail traffic. The reason for ERTMS is the wide variety of existing legacy signalling and train-control systems used in European countries. The existence of these heterogeneous and incompatible systems hampers the cross-border interoperability of different signalling and train-control systems. This is the main challenge that has to be overcome for train traffic at an international level. It is addressed by the ERTMS standard.

ERTMS is composed of ETCS and the Global System for Mobile Communications – Railway (GSM-R). GSM-R is a railway-specific variant of the widely used mobile-communication standard, GSM. ETCS is the subsystem of ERTMS that includes the signalling, train control and train protection functionality.

Safety is a major concern of the ERTMS and ETCS standard. The goal of enhanced safety in rail transport makes the use of formal methods for verification—as presented in this work for example—mandatory. The European Commission Decision [Eur02] mandates to all railway operators of the European member states that newly created and renewed Trans-European, high-speed railway systems must conform to the ERTMS standard. Thus, the following decades will bring the development of modern railway systems that apply to ERTMS. We believe that the high confidence level needed to ensure safe train operation can only be guaranteed by advanced verification techniques—especially testing methods with guaranteed fault-detection capabilities.

Before we present the basics of the formal methods needed to understand this work, we briefly introduce the core elements of modern railway systems to give a general understanding of the technical domain our verification approaches are applied to. These core elements are the signalling system, which comprises the interlocking system and the on-board train-protection system.

# 2.1.2 Interlocking Systems

Under signalling, we understand the process of controlling train movements by signals, block sections and points. A signal can be a physical track-side element or a virtual on-board signal that is visible to the train driver. In general, block sections are fragments of track that are used for the separation of trains. "A train must generally not enter a block section until it has been cleared by the train ahead" [Pac02]. Signalling has to ensure safe operation of trains in a railway network. The signalling includes a number of technical procedures and non-technical operating rules that ensure the safe operation of trains travelling through the network. An interlocking system is the technical part of a signalling system: i.e., the system controlling the signals, points and block sections. Again, the main task of an interlocking system is to ensure the safe travel of trains through the railway network. Therefore, the interlocking system ensures that trains are guided through routes, for which all points are set properly. Conflicting routes are locked, and the track is guaranteed to be clear [Pac02].

This work uses the notions and notations of interlocking systems from [VHP17, PHH16a].

Different types of interlocking systems exist. This work is concerned with route-based interlocking systems. This type of interlocking system is widely used: for example, the complete Danish signalling system is currently replaced by an ETCS-conforming, route-based interlocking system in the context of the Danish signalling programme. In route-based systems, trains are guided through predefined routes. Each route can be exclusively locked for at most one train at a time. This concept makes it possible to prevent hazardous situations such as collisions and derailments. The remainder of this manuscript uses the term interlocking system to refer to route-based interlocking systems.

### 2.1.2.1 Components of an Interlocking System

An interlocking system is composed of a railway network and—in case of route-based interlocking systems—of an interlocking table.

A railway network is the physical/geographical part of an interlocking system. It can be comprehended as the part of a track network that is supervised by the interlocking system. It is composed of different track-side elements: linear sections, points and marker boards.

A linear section is a part of a railway network with at most two neighbouring elements, which can be other linear sections or points. A point is a section of the network with three neighbouring elements. Linear sections and points are so called train-detection sections (or sections for convenience), because the occupancy status (i.e., the status "occupied by train" or "free") can be detected for each section. This detection is usually performed by physical equipment: axle counters or track circuits. The ends of a linear section are named down end and up end. Each linear section can be travelled in an up or down direction. The up and down directions are the directions in which the distance to a reference location from the network is increasing or decreasing, respectively. The ends of a point are called stem end, plus end and minus end. The plus and minus ends are the diverging branches of the stem. The path from stem end to plus end is the straight path through the point, and the path from stem end to minus end is the

<sup>&</sup>lt;sup>1</sup>The Danish signalling programme is of importance, because we will use some of the results elaborated in the context of this initiative [Vu15, VHP17]. [Vu15] proposes a formal method for the verification of route-based interlocking systems. The results in this work will be used by us for the application of MBT to modern interlocking systems.

branching path. A point can be switched from its *PLUS* position to its *MINUS* position and vice versa. In the PLUS position, the train can travel from the stem end to the plus end of the point or from the plus end to the stem end, depending on the travelling direction of the train. In the minus position, it is possible for trains to travel from the stem to the minus end or vice versa. *Marker boards* are virtual signals which perform the same task as physical signals from legacy interlocking systems. Marker boards are virtual in the sense that they have no physical representation. Each marker board is associated with a section together with a position and a direction along this section. If a marker board is in state PASS, trains are allowed to traverse the associated location on the section in the associated direction; they have to stop if the marker board is in state HALT.

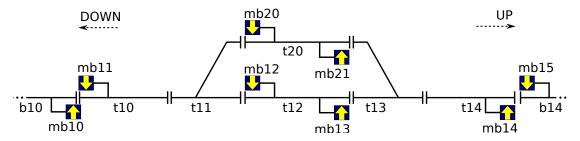

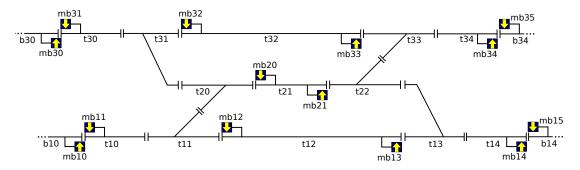

Figure 2.1: Example Railway Network from [VHP17]

**Example 1.** Consider the railway network from [VHP17], shown in Figure 2.1.

The network is composed of the linear sections t10, t12, t20, t14 and of the points t11, t13. Linear section t20 is connected to point t13 on its up end and to point t11 on its down end. t11 is connected to t10 on its stem and to t12 and t20 on its plus and minus ends. The marker board mb13 is associated with linear section t12 in the up direction.

Additionally, a route-based interlocking system is composed of an interlocking table. The interlocking table lists a number of predefined routes, which can be allocated by trains. A route is a sequence of successive sections to be traversed on the route (called path elements of the route), and every route starts and ends at a marker board (called source and destination). Each route defines the states of its elements that are needed to ensure safe traversal of a train from source to destination. This includes the state of points along the path of the route and the state of protecting points and marker boards. To prevent other trains from entering the route from the branching ends (flank protection) of the points or from approaching from the opposite direction (front protection), points from outside the path of the route and marker boards can be used. The state of these additional protecting elements guarantees that no other train can accidentally enter the route while a train is traversing this route. Additionally, each route in the interlocking table is associated with a list of conflicting routes. The list of conflicting routes lists all routes that must not be used simultaneously because of path elements that are common to these routes or because of conflicting states for protecting elements.

**Example 2.** Table 2.1 is an example of a possible interlocking table for the network shown in Figure 2.1. Consider for example route 1. The route starts from marker board mb10 and covers the path from t10 over t11 to t12. The point t11 has to be switched to its plus position. Additionally, t13 is switched to its minus position offering front protection of route 1. Flank protection of point t11 is provided by the marker board mb20. Marker boards mb11 and mb12 offer additional front protection for the sections along the path of route 1.

| Table 2.1: Interlocking Table for the Network Layout in Fig. 2.1 (Taken from [VHP17]; | p means |

|---------------------------------------------------------------------------------------|---------|

| PLUS, m means MINUS.)                                                                 |         |

| $\operatorname{id}$ | src  | dst  | path        | points      | signals                  | conflicts   |

|---------------------|------|------|-------------|-------------|--------------------------|-------------|

| 1                   | mb10 | mb13 | t10;t11;t12 | t11:p;t13:m | mb11;mb12;mb20           | 2;3;4;5;6;7 |

| 2                   | mb10 | mb21 | t10;t11;t20 | t11:m;t13:p | mb11;mb12;mb20           | 1;3;6;7;8   |

| 3                   | mb12 | mb11 | t11;t10     | t11:p       | mb10;mb20                | 1;2;5;6;7   |

| 4                   | mb13 | mb14 | t13;t14     | t13:p       | mb15;mb21                | 1;5;6;8     |

| 5                   | mb15 | mb12 | t14;t13;t12 | t11:m;t13:p | mb13;mb14;mb21           | 1;3;4;6;8   |

| 6                   | mb15 | mb20 | t14;t13;t20 | t13:m       | mb10;mb12;mb13;mb14;mb21 | 1;2;3;4;5;8 |

| 7                   | mb20 | mb11 | t11;t10     | t11:m       | mb10;mb12                | 1;2;3       |

| 8                   | mb21 | mb14 | t13;t14     | t13:m       | mb13;mb15                | 2;4;5;6     |

#### 2.1.2.2 Interlocking Principles

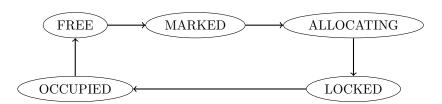

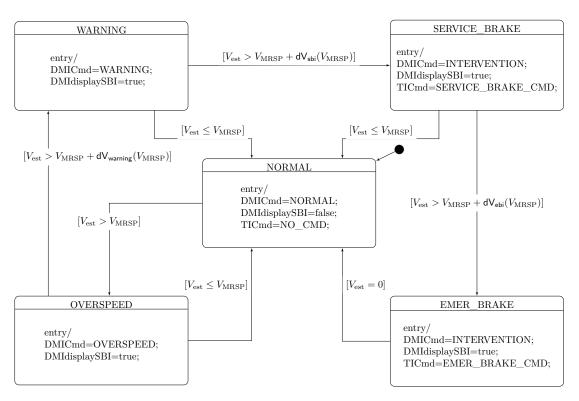

Figure 2.2: State-based Visualisation of the Interlocking Principles

Safety in interlocking systems is ensured by the following rule: A train is only allowed to travel on locked routes and every route is locked exclusively for at most one train at a time.

The locking of a route is performed as visualised in Figure 2.2. Before a route can be locked, it has to be requested or *marked* by the train driver, signalman or traffic management system. The interlocking system starts allocating the route, if no conflicting route is currently in allocating or locked state and all path elements of the route are vacant. Allocation means that all points listed in the interlocking table for the respective route are set to their requested position and all marker boards listed for the route are set to HALT. Once all these track elements have come to their requested position, the route is said to be *locked*. The points are physically locked preventing undesired switches of the points. Thereon the source marker board is switched to PASS allowing the allocating train to enter the route. Once the route is *occupied*, this marker board is switched back to HALT to prevent other trains from entering the route. When the train finally leaves the route the route is set back from *occupied* to *free*.

Additionally to these principles, modern interlocking systems provide the *sequential release* feature. *Sequential release* is the concept of releasing, i.e., unlocking, parts of the route that are completely traversed by a train. Subsequently, the sequentially released path elements of the route can be reused by other routes. This allows for higher concurrency of routes.

**Example 3.** Consider the network from Figure 2.1 and the route table shown in Table 2.1. When a train approaches mb10, it might request route 1 to stay on the main track. In this case, route 1 transits to state MARKED. Given that none of the conflicting routes is in state ALLOCATING or LOCKED and that all path elements (t10, t11, t12) are vacant, the route will transit to state ALLOCATING. Point t11 is commanded to position PLUS and point t13 is commanded

to position MINUS. Signals mb11, mb12 and mb20 are commanded to state HALT. As soon as all of these elements have taken their required state, route 1 transits to state LOCKED. The source marker board mb10 is commanded to state PASS. As soon as the train receives the pass signal from mb10, it is allowed to enter route 1. As soon as the detection status of t10 changes to occupied, route 1 transits to state OCCUPIED and commands mb10 to state HALT. Consider a second train approaching mb10. This train has to stop in front of mb10 because this marker board is in state HALT. The second train might request route 2 from mb10 to mb21. Route 2 transits from FREE to MARKED. Because route 2 conflicts with route 1, the controller of route 2 stays in the MARKED state. As soon as train 1 completely passed t11, route 2 can transit to state ALLOCATING because t10 and t11 were sequentially released by route 1. t11 is commanded to switch to state MINUS. Finally, train 2 is allowed to enter its requested route 2, while route 1 is still in use. When train 1 approaches mb13, it has to request route 4 to continue. Finally, it will be able to enter this route and completely leave t12. This causes route 1 to transit to state FREE again.

### 2.1.3 On-Board Train Protection

A train-protection system has the task to supervise train movements and—in case of human errors—trigger an automatic intervention. This includes the supervision and enforcement of HALT signals and the supervision of the train speed in accordance with the speed limits. In ETCS systems, this task is performed by an on-board system: the European Vital Computer (EVC). The EVC implements speed- and distance-monitoring functionality, among other things, as described in [UNI12]. The speed and distance monitoring function enforces agreement with speed limits. Therefore, the on-board unit of the train reads information from Eurobalises: i.e., trackside beacons with a fixed location. Based on the information communicated by Eurobalises, the train knows its position and the maximum allowed speed. Additionally, the train knows the reference location at which it has to stop: the so-called end of authority (EOA). Based on this information, the speed and distance monitoring function operates and supervises the observance of speed and distance limits. The monitoring function operates in three exclusive modes.

Ceiling-speed Monitoring, Target-speed Monitoring and Release-speed Monitoring. The Ceiling Speed Monitor (CSM) is active when a train is travelling on its route and is still far away from its target location (EOA). In this mode, adherence to the track-dependent speed limit has to be supervised. As soon as the train approaches its EOA, the distance to the target location has to be taken into account. In these situations, the Target Speed Monitor (TSM) is active. Braking curves of the train are calculated to ensure that the train decelerates early enough to allow it to come to a standstill before the EOA. The speed limit at the location of the EOA is zero. Because of inaccuracies of the measured location, this can sometimes lead to situations in which the train is not able to reach the exact target location. Therefore, it is desired to allow the train driver to drive up to a very low speed limit (the release speed limit) when the train is very close to the EOA. This mode is supervised by the Release Speed Monitor (RSM).

# 2.2 System Modelling

This section presents different state-of-the-art approaches to the modelling of systems. We briefly introduce SysML: a very popular modelling language that is favourable because of its wide application in the academic and industrial community and its increasing tool support.

Second, we introduce SystemC. SystemC provides a mode of description for embedded systems and aims at system modelling. We use SystemC as an implementation language in this work. Because of its nature, SystemC is a good candidate for an implementation language which can be used for our mutation experiments aiming at the test-strength evaluation of HSI testing.

# 2.2.1 Systems Modeling Language

SysML [Obj15b] is a standardised modelling language for the abstract description of systems. SysML is standardised by the Object Management Group (OMG) and is closely related to the UML [Obj15a].

Compared to UML, SysML extends UML by some types of diagrams that are specifically needed for the modelling of systems. SysML makes it possible to define the system composition and the interconnection of subsystems (called *blocks*) by block definition diagrams (BDDs) and internal block definition diagrams (IBDs). Furthermore, SysML allows for the definition of requirements in requirement diagrams and supports the tracing from requirements to other model elements. Another system-modelling feature is the modelling of constraints through constraint blocks that can be visualised in parametric diagrams. For behavioural modelling, SysML provides activity diagrams and state machines. Both are adapted from UML and are only extended in some minor details. Therefore, readers who are familiar with activities and state machines in UML can consider the SysML counterparts to be equivalent.

This work uses state machines as a description means for system behaviour. Since state machines are almost equal in UML and SysML, we will call these behavioural diagrams SysML state machines—although the term UML state machines would be correct as well. If no confusion arises, we sometimes use the term state machines.

**SysML State Machines** The remainder of this work uses a subset of the SysML state-machine concept for the behavioural description of systems. We present only the features of state machines that are needed for this work to be self-contained. For a thorough and complete definition of SysML/UML state machines, please refer to the standards [Obj15b, Obj15a].

SysML state machines can be considered a variant of the statecharts originally invented by Harel [Har87]. State machines, based on Harel's statecharts, are visual, graph-based description means which combine control flow and data flow. A statechart is comprised of states (visualised by nodes with rounded-corners) and transitions (visualised by directed edges between nodes) that connect in direction of the arrow, respectively, a source and a target state. Transitions, i.e., arrows  $\stackrel{e[g]/a}{\longrightarrow}$  can be labelled with an event e, a guard-condition g and an action a. A transition is taken if the state machine currently resides in the source state, event e occurs and the guardcondition g is fulfilled. The state machine transits to the target state and performs action a. Data flow in state machines is mainly modelled by actions. An action can be an abstract event or, as in our case, a sequence of assignments to variables. Actions are generally performed in zero-time, which means that a sequence of assignments is performed instantaneously. For the modelling of non-instantaneous reactions, state machines allow for the activation of activities, which are by definition executed in non-zero-time. An action may be associated with a transition. For convenience, state machines allow for entry- and exit-actions and for do-activities in states. Entry- and exit-actions actions are triggered when the associated state is entered, or when the state is left. Do-activities are activities that are started when a state is entered; finally, these activities are stopped when the state is left (or as soon as the activity terminates).

Besides this basic functionality, state machines allow for hierarchy: States are allowed to contain substates (Harel uses the term XOR-states to indicate that the state machine resides in one of these states at a time). In the context of UML and SysML, states containing substates are called composite states or submachine states. These states themselves are state machines which define parts of the system's behaviour. Additionally, states are allowed to contain orthogonal regions (Harel uses the term AND-states to indicate that the state machine resides in one state in all of its orthogonal regions at a time). A region is a subgraph of a state machine (again possibly hierarchical) which defines behaviour that is executed concurrently with its orthogonal regions. Thus, orthogonal regions allow for the modelling of parallelism. Both orthogonal regions and hierarchy allow for comprehensible models even for very complex systems. On the other hand, orthogonal regions and hierarchy impose challenges in the definition of a formal semantics. SysML and UML encounter this challenge by providing only a semi-formal semantics of state machines. Many implementation details are not defined by the standards and are thereby implementation dependant. A formal semantics for Harel's statecharts has been presented in [HN96] together with a thorough discussion of other semantics. This work uses the formal semantics used by the RT-Tester MBT component. The concrete semantics of this tool is laid out in [PVL11]. This tool is based on the semi-formal semantics of the UML standard, though it may violate UML semantics in some details.

The remainder presents some state machine models for real-world systems in the scope of this work. All of these models have in common the fact that they can be expressed (in a comprehensible way) without the use of hierarchy and orthogonal regions. Nonetheless, the reader will find that these models are of considerable complexity. Consider, for example, a route controller that is responsible for the safe operation of trains in routes through large, real-world railway networks. We therefore neglect further explanation of the formal semantics of hierarchic state-machine states and parallelism in state machines. Instead, we intuitively introduce "flat" SysML state machines without hierarchy and parallelism. Note that this is no restriction on the implementation of our approach: Since our approach relies on the RT-Tester MBT component and the semantics [PVL11] implemented therein, the implementation of our approach can be applied to more complex models than are presented in this work. The formal semantics that is based on Reactive Input-Output State-Transition Systems (RIOSTSs) is introduced below, in Section 2.5.1.

**Definition 1** (Flat SysML State Machines). A flat SysML state machine is described by a tuple  $SM = (S, s_0, T, e, x)$ . S denotes the set of states of the state machine that are visualised by rectangular nodes with rounded corners in the graphical representation.  $T \subset S \times G \times A \times S$ denotes the set of transitions in the state machine. A transition  $(s, q, a, s') \in T$  is visualised as an arrow from state s to state s' and is labelled [g]/a. g is called the guard-condition. In this work, guard-conditions are considered first-order-logic predicates over system variables. A guard condition  $g \in G$  is a member of the universe of predicates over system variables, denoted by G.  $a \in A$  is the action associated with the transition. An action a is a finite sequence of assignments to system variables. An assignment a has the form l=r where the left-hand side l is a variable name and r is an expression over system variables. The effect of the assignment is that, in the target state of the transition, the variable referenced by l is set to the value the expression revaluates to in the current system state. The universe of possible actions is denoted by A. A transition  $(s, g, a, s') \in T$  is taken as soon as guard-condition g becomes true, given that the state machine resides in state s. The state machine resides in exactly one state at any moment in time. Taking the transition causes the state machine to switch the state it resides in to the target state s' and perform the exit action x(s) of s, the action a associated with the transition and the entry action e(s') of the target state s'. e and x are partial functions which map a

state to its entry and exit actions, which are again a sequence of assignments. Initially, the state machine resides in the pseudo-initial state  $s_0$ , which is visualised by a black-filled circle. Entry-and exit-actions will be visualised inside of the nodes of a state with the prefixes "entry/" and "exit/". The action of a transition can be empty. In this case, /a is dropped from the graphical representation.

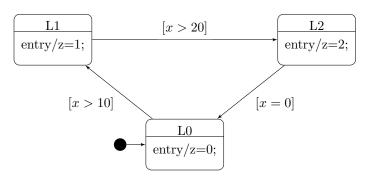

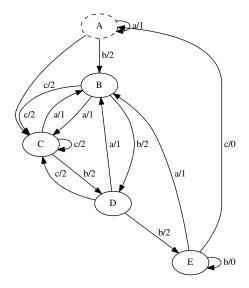

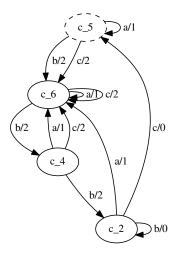

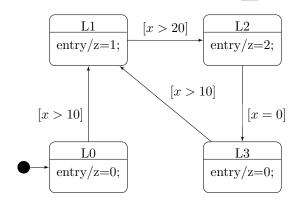

Figure 2.3: Example State Machine

**Example 4.** Figure 2.3 is an example for a flat SysML state machine. Consider the system variable x to be an input variable to the system. Let z be an output variable of the system. Initially, the system resides in the state-machine state "L0". As soon as x becomes greater than 10, the system transitions to state "L1" and the entry action causes z to be set to one. If x becomes greater than 20 the system transitions from "L1" to "L2" and z becomes two. As soon as x becomes zero, the system transitions back to state-machine state L0 and z is set to zero. If the system resides in state "L0" and x changes its value to a value greater than 20, the system will transition to state "L1", and because the guard condition of the outgoing transition of "L1" is fulfilled, the state machine will immediately make this transition as well. The two successive transitions from "L0" over "L1" to "L2" are called a compound transition in the context of UML. The run-to-completion semantics causes the two transitions to be made at once: i.e., in zero-time. The run-to-completion semantics prescribes that transitions are made until a stable system state is reached. In this case, L2 is stable, because no guard condition of an outgoing transition is fulfilled. The system input has to change before the next transition can be made.

Readers who are familiar with the UML/SysML standard will notice that the flat state machines introduced above do not include many of the features that UML/SysML defines. For example, we completely neglect events that are used as triggers in state-machine transitions. It might seem unnatural to use an originally event-based approach like SysML state machines in this case, but the models we present as case studies in Chapter 3 all model control systems that somehow rely on input variables from large domains (analogue inputs or train constellations in a railway network) and make concrete control decision based on these inputs. We believe that systems of this kind are well described by a state-based approach using the state-machine subset as introduced above. However, it has to be emphasised that the testing approach introduced below does not rely on this subset of state machines; it does not even rely on a concrete description means. We will show that every concrete description means that can be translated to a statetransition system with dedicated input and output variables can be equipped with our testing methodology. Note that every event-based model can be translated to an equivalent state-based formal model. Thus, SysML state machines or the variation of state machines as introduced above should be considered an interchangeable front-end to the testing approach implemented in this work.

# 2.2.2 SystemC

SystemC is a high-level system modelling and design language. It is integrated into C++ by means of class libraries. SystemC is technically not a language of its own but rather a set of class libraries in C++ that allow for the modelling of systems. The main goal of SystemC is to bridge the gap between different levels of system abstraction and to allow the co-design of SW- and HW-architecture. A key feature of SystemC therefore is the simulation kernel. This simulation kernel makes it possible to simulate a SystemC model: i.e., to execute the model. The main task of this kernel is the concurrent simulation of functional units, called *modules*. It is the nature of integrated embedded systems that many modules run in parallel. SystemC therefore mostly focuses on the definition of modules, the functionality of modules, communication between modules, and the concurrent execution of the complete model composed of concurrent modules. For a thorough introduction to SystemC, refer to [BABJ10].

The most important elements of the SystemC language that we use throughout this work are *modules*, *signals* and *ports*. These are introduced in subsequent paragraphs. We conclude with a small example of a SystemC model.

**Modules** SystemC makes it possible to design a system by defining modules. A module is a unit that implements some functionality. The behaviour of a module is implemented by an arbitrary number of methods. These methods can either be called directly or called in reaction to a value change of a signal.

Modules make it possible to define a hierarchy: modules can contain other modules, which in turn might contain other modules. This induces a hierarchy that is typical for complex systems that are modelled compositionally.

Technically, modules are implemented by custom classes that extend the common base class sc module.

SystemC Threads and Methods Since modules are instances of custom user classes that extend sc\_module, the functionality of modules is to be implemented in member functions of the module's class. Besides traditional C++ member functions that can be called by the user, SystemC provides two ways to define simulation processes. A simulation process is an executing instance. This may be a SW-thread or a SW-process running on an operating system. In case of hardware, this may be an independently timed hardware module. Simulation processes are executed by the SystemC simulation kernel. They must not be called by the user through function calls, but may only be called by the SystemC simulation kernel. The invocation by the simulation kernel in turn is indirectly caused by sensitivity, events and notification. Because simulation processes are to be called by the simulation kernel, these processes need a common signature. Processes are therefore required to return void and have no parameters. Functionality in these processes therefore needs to use the module's variables as means for input and output.

SystemC distinguishes two types of simulation processes: *methods* and *threads*. While methods are expected to always terminate, a thread may be non-terminating and can be suspended and resumed. Methods are called multiple times by the simulation kernel and the timing model for methods dictate that no (simulated) time passes between the invocation and return of the method. Contrary, threads are called exactly once by the simulation kernel—usually at the beginning of the simulation. These threads usually do not terminate but suspend, allowing simulated time to pass and other simulation processes to be executed. Methods can be registered

to the simulation kernel by using the SC\_METHOD macro, and threads are registered using the SC\_THREAD macro. The registration has to be performed in the constructor of a module. The phase in which the constructors of all modules are called is named *elaboration phase*.

Channels, Interfaces and Ports An important aspect of system modelling is communication. In System C, communication between modules is modelled by channels. Channels interconnect modules and allow the interconnected modules to communicate with each other. A channel is an abstract way to model a communication channel. Channels may be used to model every kind of communication means including high-level communication means like sockets, buses, FIFO-queues; and low-level communication means like physical wires transferring logical values. System C distinguishes between two types of channels: primitive and hierarchical channels. Primitive channels (base class sc\_prim\_channel) represent low-level (i.e., fast and simple) communications. Primitive channels are not hierarchical: i.e., they must neither contain modules nor simulation processes. sc\_signal is an example of a primitive channel. In contrast, hierarchical channels (base class sc\_channel) usually model higher-level communications. A hierarchical channel itself is a module that implements the functionality of the communication. This implies that a channel may contain modules and simulation processes.

Channels provide functionality through *interfaces*. An *interface* (base class sc\_interface) declares a set of methods that the channel has to provide. Usually, a channel implements several interfaces, such as one writer/producer interface and one reader/consumer interface. The concept of interfaces makes it possible to separate the interface of a communication channel from its functionality. Technically, the channel implements interfaces by extending them and overriding virtual member functions defined in the interfaces. Usually, the virtual member functions in the interface are pure virtual functions.<sup>2</sup>

As stated earlier, modules are interconnected via channels. Therefore, ports (class sc\_port) are used to connect (bind) a module to the channel. A module may have multiple ports and every port is bound to a channel (it is also possible to bind one port to multiple channels). Ports are parametrised sc\_port<I> to an interface I. This interface determines the functions that may be called on this port (namely the functions the interface I declares) and the channels that the port may bind to (namely, all channels that implement I). The ports act as proxies that forward an interface function call to the channel the port is bound to.

The connection of modules (i.e., the binding of ports to channels) has to be done in the elaboration phase: i.e., before the simulation has been started. A port that is not bound to a channel is considered a modelling error and will result in an error when the model simulation is started.

**Signals** As mentioned, sc\_signal<T> is a special form of a primitive channel. sc\_signal<T> represents signals of type T in the common meaning originating from HW description languages such as VHDL. Thus, a signal can be considered a type of data storage, and the type of data a signal can hold is customizable. A signal in SystemC can hold values of any of the following C/C++ fundamental types: boolean type, character types (char, signed char, wchar\_t, ...), integer types (int, long int, unsigned int, ...) or floating-point types (float, double, long double).

<sup>&</sup>lt;sup>2</sup>In C++ pure virtual functions are abstract functions that are declared but not implemented. Pure virtual functions correspond to abstract methods in Java for example.

Signals follow the evaluate-update paradigm: The SystemC simulation kernel executes all simulation processes in cycles, so called delta cycles. The order of simulation processes in a delta cycle is not prescribed by the simulation kernel. Processes might be executed in arbitrary order. This may cause problems when multiple modules want to read and potentially update a signal's value. In this case, the order of execution might influence the final result. The evaluate-update paradigm overcomes this problem by the separation of a signal's value to the current and new value. Within a delta cycle, all modules that read the signal value will read the current value. An update of a signal value results in a write to the new value and a notification to the simulation kernel of the changed value. After all processes in a delta cycle have been executed, the change of the value becomes apparent. The current value will be set to the new value, and, in the next delta-cycle, other modules will be able to read this new value.

A special type of signal exists: sc\_clock models a boolean signal that switches its values with a configurable frequency. This type can be used to model cyclic timing in SystemC models.

For the connection of modules to signals, two special ports can be used: sc\_in<T> and sc\_out<T>.sc\_in<T> models an input port that allows to read a signal of type signal<T> and sc\_out<T> models an output port that allows to write a signal of type signal<T>. The special port sc\_inout<T> allows to read and write the signal the port is bound to.

**Events** Besides channels, SystemC provides events as a low-level communication and synchronisation scheme. Events are instances of a class sc\_event. An event can be "fired" or notified by a call to the member function notify(). The firing/notification of an event causes all simulation processes (methods and threads) that are *sensitive* to this event to be simulated: Methods are called and threads, which are suspended, are resumed by the simulation kernel. Again, the order of execution of the processes is not prescribed.

Sensitivity As mentioned before, a module's processes are simulated whenever an event the module is sensitive to is notified. SystemC distinguishes between *static* and *dynamic sensitivity*. Static sensitivity to an event e is declared in the elaboration phase (i.e., in a module's constructor) by a statement: sensitive<<e;. Whenever this event is notified, the simulation process of the module is called. Besides, *dynamic sensitivity* can be changed during simulation. A call to wait(e) will cause a thread to suspend until event e is notified. The thread is only dynamically sensitive to this event, meaning that after the call of wait(e) returned, the thread will not be sensitive until wait is called again.

A module can be sensitive to channels as well. In this case, events are used as the low-level means for the activation of processes by channels. The special primitive channel, sc\_signal, for example, implements member function value\_changed\_event(), which returns an event object that will be notified by the simulation kernel whenever the signal's value changes.

**Example 5.** Listing 1 displays a SystemC model that models a hardware shift register of four bits. The shift register (SystemC module shift\_register) has a boolean input, data (input port data), and is synchronised on a clock (clock input port sync). Every clock cycle, all register values are shifted to the next register and the value of data is written into the first register. The output of the shift register is a four-bit variable (type sc\_uint<4>); see output port out.

The shift register is composed of four single-bit registers implemented by module bool\_register. This module has two input ports: sync is a clock input and in is the input line of the register. The value on this line is read and written to the output of the register on every positive

| Time        | 0 100 | ns 200 | 0 ns 300 | ns 400 | 0 ns 500 | ns 600 | ns |

|-------------|-------|--------|----------|--------|----------|--------|----|

| data        |       |        |          |        |          |        |    |

| result[3:0] | )1    | χ3     | (7       | Œ      | XD       | (B     | (7 |

| result[3]   |       |        |          |        |          |        |    |

| result[2]   |       |        |          |        |          |        |    |

| result[1]   |       |        |          |        |          |        |    |

| result[0]   |       |        |          |        |          |        |    |

|             |       |        |          |        |          |        |    |

Figure 2.4: Waveform View of HW Shift Register Signals

clock edge. This is realised by the simulation process update. The module bool\_register uses static sensitivity, which is declared in the constructor of bool\_register. The statement sensitive<<sync.pos(); makes the register sensitive to positive clock edges.

Module shift\_register contains the four single-bit registers in a special vector (using the SystemC type sc\_vector<bool\_register>). This vector contains exactly four instances of type bool\_register. During the elaboration phase, in the constructor of shift\_register, the four bool\_register modules are interconnected. Their input and output ports are bound to different signals (member variable signals). The shift\_register module uses static sensitivity for its simulation process (member function update). update reads the signal values and composes the boolean values to a four-bit integer value that is written to the output port.

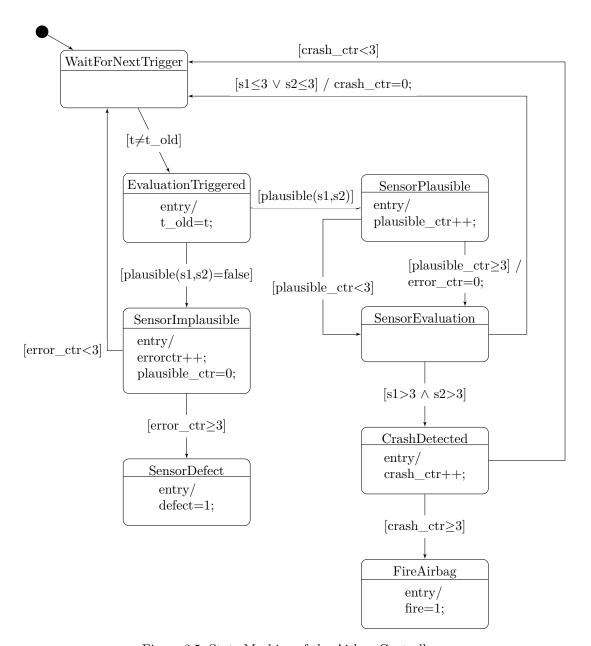

Note that the SystemC model works correctly because of the evaluate-update paradigm used for signals. If we used traditional member variables instead of signals and ports for the registers, the order of execution of the simulation processes of the bool\_register instances would influence the result. The result would only be correct if registers[3] was scheduled before registers[2] which was scheduled before registers[1] and so on. Thus, additional synchronisation to ensure a specific ordering of simulation processes would be needed. Instead, the evaluate-update paradigm ensures that all registers see the signal values that were valid at the beginning of the clock cycle. No additional synchronisation is needed in this case.