# Software Approaches to Manage Resource Tradeoffs of Power and Energy Constrained Applications

by

Ramy Medhat

A thesis presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Doctor of Philosophy in Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2017

© Ramy Medhat 2017

#### **Examining Committee Membership**

The following served on the Examining Committee for this thesis. The decision of the Examining Committee is by majority vote.

| External Examiner:        | Miroslav Pajic<br>Assistant Professor, Duke University<br>Department of Electrical and Computer Engineering                                                                                                                           |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Supervisors:              | Sebastian Fischmeister<br>Associate Professor, University of Waterloo<br>Department of Electrical and Computer Engineering<br>Borzoo Bonakdarpour<br>Assistant Professor, McMaster University<br>Department of Computing and Software |

| Internal Member:          | Catherine Gebotys<br>Professor, University of Waterloo<br>Department of Electrical and Computer Engineering                                                                                                                           |

| Internal Member:          | Rodolfo Pellizzoni<br>Associate Professor, University of Waterloo<br>Department of Electrical and Computer Engineering                                                                                                                |

| Internal-External Member: | Samer El-Kiswany<br>Assistant Professor, University of Waterloo<br>David R. Cheriton School of Computer Science                                                                                                                       |

This thesis consists of material all of which I authored or co-authored: see Statement of Contributions included in the thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### **Statement of Contributions**

In what follows is a list of publications which I have co-authored and used their content and ideas in this dissertation. For each publication, I present a list of my contributions.

The use of the content, from the listed publications, in this dissertation has been approved by all co-authors.

- Ramy Medhat, Borzoo Bonakdarpour, and Sebastian Fischmeister. Power-efficient Multiple Producer-Consumer. In Proceedings of the IEEE 28th International Symposium on Parallel & Distributed Processing (IPDPS), Phoenix, USA, 2014 [96].

- Designed and executed the experimental study.

- Designed the problem formalization.

- Designed the algorithm.

- Implemented the algorithm.

- Designed and executed the experiments.

- Wrote a significant portion of the article.

- Ramy Medhat, Deepak Kumar, Borzoo Bonakdarpour, and Sebastian Fischmeister. Sacrificing a Little Space Can Significantly Improve Monitoring of Time-sensitive Cyber-physical Systems. In Proceedings of the ACM/IEEE International Conference on Cyber-Physical Systems (ICCPS), Berlin, Germany, 2014 [99].

- Designed the problem formalization.

- Designed the algorithm.

- Implemented the algorithm.

- Designed and co-executed the experiments.

- Wrote a significant portion of the article.

- Ramy Medhat, Borzoo Bonakdarpour, Deepak Kumar, and Sebastian Fischmeister. Runtime Monitoring of Cyber-Physical Systems Under Timing and Memory Constraints. In ACM Transactions on Embedded Computing Systems (TECS), vol. 14, issue 4, pp. 79, 2015 [97].

- Designed the problem formalization.

- Designed the algorithm.

- Implemented the algorithm.

- Designed and co-executed the experiments.

- Wrote a significant portion of the article.

- Ramy Medhat, Mike Lam, Barry Rountree, Borzoo Bonakdarpour, Sebastian Fischmeister. Managing the Performance/Error Tradeoff of Floating-point Intensive Applications. In *International Conference on Embedded Software (EMSOFT)*, Seoul, South Korea, 2017 [98].

- Designed the tool.

- Implemented the tool.

- Designed and executed the experiments.

- Wrote a significant portion of the article.

- 5. Ramy Medhat, Shelby Funk, and Barry Rountree. Scalable Performance Bounding under Multiple Constrained Renewable Resources. In 5th International Workshop on Energy Efficient Supercomputing (E2SC), Colorado, USA, 2017 [100].

- Designed the multi-resource model.

- Implemented the model.

- Designed and executed the experiments.

- Wrote a significant portion of the article.

- 6. Ramy Medhat, Borzoo Bonakdarpour, and Sebastian Fischmeister. Energy-efficient Multiple Producer-Consumer. Submitted to *IEEE Transactions on Parallel and Distributed Systems (TPDS)*.

- Designed and executed the experimental study.

- Designed the problem formalization.

- Designed the algorithm.

- Implemented the algorithm.

- Designed and executed the experiments.

- Wrote a significant portion of the article.

#### Abstract

Power and energy efficiency have become an increasingly important design metric for a wide spectrum of computing devices. Battery efficiency, which requires a mixture of energy and power efficiency, is exceedingly important especially since there have been no groundbreaking advances in battery capacity recently. The need for energy and power efficiency stretches from small embedded devices to portable computers to large scale data centers. The projected future of computing demand, referred to as exascale computing, demands that researchers find ways to perform exaFLOPs of computation at a power bound much lower than would be required by simply scaling today's standards.

There is a large body of work on power and energy efficiency for a wide range of applications and at different levels of abstraction. However, there is a lack of work studying the nuances of different tradeoffs that arise when operating under a power/energy budget. Moreover, there is no work on constructing a generalized model of applications running under power/energy constraints, which allows the designer to optimize their resource consumption, be it power, energy, time, bandwidth, or space. There is need for an efficient model that can provide bounds on the optimality of an application's resource consumption, becoming a basis against which online resource management heuristics can be measured.

In this thesis, we tackle the problem of managing resource tradeoffs of power/energy constrained applications. We begin by studying the nuances of power/energy tradeoffs with the response time and throughput of stream processing applications. We then study the power performance tradeoff of batch processing applications to identify a power configuration that maximizes performance under a power bound. Next, we study the tradeoff of power/energy with network bandwidth and precision. Finally, we study how to combine tradeoffs into a generalized model of applications running under resource constraints.

The work in this thesis presents detailed studies of the power/energy tradeoff with response time, throughput, performance, network bandwidth, and precision of stream and batch processing applications. To that end, we present an adaptive algorithm that manages stream processing tradeoffs of response time and throughput at the CPU level. At the task-level, we present an online heuristic that adaptively distributes bounded power in a cluster to improve performance, as well as an offline approach to optimally bound performance. We demonstrate how power can be used to reduce bandwidth bottlenecks and extend our offline approach to model bandwidth tradeoffs. Moreover, we present a tool that identifies parts of a program that can be downgraded in precision with minimal impact on accuracy, and maximal impact on energy consumption. Finally, we combine all the above tradeoffs into a flexible model that is efficient to solve and allows for bounding and/or optimizing the consumption of different resources.

#### Acknowledgements

I would like to thank my supervisors, Professor Sebastian Fischmeister and Professor Borzoo Bonakdarpour for their continuous support and guidance. They have taught me many things, most important of which is how to think about a problem thoroughly and how to improve the problem statement during several rounds of cross-examination. I am grateful for their effort during my studies and could not have asked for more supportive and encouraging advisors.

I would like to thank Professor Barry Rountree for his tremendous support, providing me with space to explore my ideas and collaborate with amazing researchers. I would like to thank Professor Mike Lam for the fruitful collaboration and his consistent availability for brainstorming and feedback. I would also like to thank Professor Shelby Funk for her support, encouragement, and time to have many whiteboard brainstorming sessions. I would also like to thank my committee members: Professor Miroslac Pajic, Professor Rodolfo Pellizzoni, Professor Catherine Gebotys, and Professor Samer Al-Kiswany for taking the time and effort to participate in my examination committee and provide me with valuable feedback.

I would also like to thank my colleagues in the Real-Time Embedded Systems group: Hany Kashif, Samaneh Navabpour, Deepak Kumar, Wallace Wu, Jean-Christophe Petkovic and David Shin.

I cannot express enough gratitude to my parents, Manal and Medhat, for their continuous support every step of the way. They have pushed me forward at every juncture of my life, and without them I would not be writing a PhD thesis acknowledgement. I would like to thank my sister Yara for always believing in her brother and pushing me to strive for improvement.

Finally, I would like to thank my wife, Menna. Thank you for your support, encouragement, and belief. I would also like to thank our son, Mourad, for making my life brighter.

#### Dedication

To my parents, Manal and Medhat. To my sister, Yara. To my wife, Menna. To my son, Mourad.

# **Table of Contents**

| Li | List of Tables x |                                                                                                                                  | xv  |  |  |  |

|----|------------------|----------------------------------------------------------------------------------------------------------------------------------|-----|--|--|--|

| Li | st of            | rigures                                                                                                                          | xvi |  |  |  |

| 1  | Introduction     |                                                                                                                                  |     |  |  |  |

|    | 1.1              | Importance of Power and Energy Efficiency                                                                                        | 1   |  |  |  |

|    | 1.2              | Resource Tradeoffs and the Status Quo                                                                                            | 2   |  |  |  |

|    | 1.3              | Thesis Statement                                                                                                                 | 3   |  |  |  |

|    | 1.4              | Research Problem                                                                                                                 | 3   |  |  |  |

|    | 1.5              | Overview of the Proposed Approach                                                                                                | 4   |  |  |  |

|    |                  | 1.5.1 Energy versus Response Time                                                                                                | 4   |  |  |  |

|    |                  | 1.5.2 Power versus Performance                                                                                                   | 5   |  |  |  |

|    |                  | 1.5.3 Power, Energy and Bandwidth Tradeoffs                                                                                      | 5   |  |  |  |

|    |                  | 1.5.4 Power, Energy and Precision                                                                                                | 5   |  |  |  |

|    |                  | 1.5.5 Generalized Model                                                                                                          | 6   |  |  |  |

|    | 1.6              | Organization                                                                                                                     | 6   |  |  |  |

| 2  | Ene              | gy versus Response Time                                                                                                          | 7   |  |  |  |

|    | 2.1              | $[ntroduction \dots \dots$ | 8   |  |  |  |

| 2.2 | Background                       | 11 |

|-----|----------------------------------|----|

| 2.3 | Producer-Consumer Energy Profile | 13 |

|   |     | 2.3.1   | Producer-Consumer Implementations            | 13 |

|---|-----|---------|----------------------------------------------|----|

|   |     | 2.3.2   | Experimental Settings 1                      | 14 |

|   |     | 2.3.3   | Experimental Results                         | 15 |

|   | 2.4 | Forma   | l Problem Description                        | 19 |

|   |     | 2.4.1   | Approach                                     | 19 |

|   |     | 2.4.2   | System Assumptions                           | 20 |

|   |     | 2.4.3   | The Optimization Problem                     | 20 |

|   | 2.5 | Energ   | y-aware Multiple Producer-Consumer Algorithm | 24 |

|   |     | 2.5.1   | Contiguous Consumer Activations              | 25 |

|   |     | 2.5.2   | Consumer Design                              | 26 |

|   |     | 2.5.3   | Core Manager Design                          | 26 |

|   | 2.6 | Implei  | mentation and Experimental Results           | 29 |

|   |     | 2.6.1   | Experimental Parameters                      | 29 |

|   |     | 2.6.2   | Experimental Metrics                         | 30 |

|   |     | 2.6.3   | Energy Consumption Results                   | 31 |

|   |     | 2.6.4   | Average Response Time Results    3           | 33 |

|   |     | 2.6.5   | Throughput Results                           | 34 |

|   |     | 2.6.6   | Buffer Triggers                              | 35 |

|   |     | 2.6.7   | Discussion                                   | 35 |

|   | 2.7 | Summ    | ary                                          | 37 |

| 3 | Pow | ver ver | sus Performance 3                            | 88 |

|   | 3.1 | Introd  | uction                                       | 38 |

|   | 3.2 | Motiva  | ation                                        | 11 |

|   | 3.3 | Forma   | l Problem Description                        | 43 |

|   |     | 3.3.1   | Task Dependency Graph   4                    | 14 |

|   |     | 3.3.2   | Total execution time                         | 15 |

|   |     | 3.3.3   | Example of a Task Dependency Graph           | 45 |

|   | 3.4 | Online  | e Heuristic for Power Redistribution    | 48 |

|---|-----|---------|-----------------------------------------|----|

|   |     | 3.4.1   | Block Detector                          | 49 |

|   |     | 3.4.2   | Online Heuristic Design                 | 50 |

|   | 3.5 | Optim   | al Solution                             | 52 |

|   |     | 3.5.1   | Task Concurrency Optimization Algorithm | 52 |

|   |     | 3.5.2   | ILP Instance                            | 54 |

|   | 3.6 | Simula  | ation results                           | 57 |

|   | 3.7 | Implei  | mentation and Experimental Results      | 59 |

|   |     | 3.7.1   | Implementation                          | 59 |

|   |     | 3.7.2   | Experimental setup                      | 60 |

|   |     | 3.7.3   | Experimental Results                    | 62 |

|   | 3.8 | Summ    | ary                                     | 64 |

| 4 | Pow | ver, En | nergy and Bandwidth Tradeoffs           | 65 |

|   | 4.1 | Introd  | luction                                 | 65 |

|   | 4.2 | Proble  | em Statement                            | 66 |

|   |     | 4.2.1   | Resource-Constrained Project Scheduling | 67 |

|   | 4.3 | Linear  | Programming Model                       | 68 |

|   |     | 4.3.1   | The Model                               | 68 |

|   |     | 4.3.2   | Constraints                             | 69 |

|   | 4.4 | Model   | ling MPI programs                       | 71 |

|   |     | 4.4.1   | Send/Recv                               | 71 |

|   |     | 4.4.2   | ISend/IRecv                             | 71 |

|   |     | 4.4.3   | IAlltoAll                               | 72 |

|   | 4.5 | LP M    | odel Example                            | 72 |

|   |     | 4.5.1   | Assumptions                             | 73 |

|   |     | 4.5.2   | Network flow solution                   | 73 |

|   |     | 4.5.3   | Proposed schedule                       | 74 |

|   | 4.6 | Advar   | nced modelling $\ldots \ldots 74$      | 4 |

|---|-----|---------|---------------------------------------------------------------------------------------------------------------------|---|

|   |     | 4.6.1   | Modelling local bandwidth bottlenecks                                                                               | 5 |

|   |     | 4.6.2   | Modelling interconnection network topologies                                                                        | 5 |

|   |     | 4.6.3   | Modelling other renewable resources                                                                                 | 5 |

|   |     | 4.6.4   | Modelling non-renewable resources                                                                                   | 6 |

|   | 4.7 | LP M    | odel Benchmark                                                                                                      | 7 |

|   |     | 4.7.1   | Experiment Setup                                                                                                    | 7 |

|   |     | 4.7.2   | Results                                                                                                             | 8 |

|   | 4.8 | Synth   | etic MPI experiments                                                                                                | 0 |

|   |     | 4.8.1   | Experiment Design                                                                                                   | 1 |

|   |     | 4.8.2   | Results                                                                                                             | 1 |

|   | 4.9 | Summ    | nary                                                                                                                | 3 |

|   |     |         |                                                                                                                     |   |

| 5 |     | · · · · | hergy and Precision 84                                                                                              |   |

|   | 5.1 | Introd  | luction $\ldots \ldots $ | 4 |

|   | 5.2 | Prope   | sed Approach                                                                                                        | 7 |

|   |     | 5.2.1   | Problem Statement                                                                                                   | 7 |

|   |     | 5.2.2   | Evolution of Precision Error    8'                                                                                  | 7 |

|   |     | 5.2.3   | Tracing Memory Error                                                                                                | 8 |

|   |     | 5.2.4   | Tracing Instruction Error                                                                                           | 0 |

|   |     | 5.2.5   | Isolating Function Error                                                                                            | 1 |

|   | 5.3 | Mana    | ging the performance / error tradeoff $\ldots \ldots \ldots \ldots \ldots \ldots \ldots $ 92                        | 2 |

|   | 5.4 | Aprilt  | ag detection case study                                                                                             | 4 |

|   |     | 5.4.1   | The Apriltag Library                                                                                                | 4 |

|   |     | 5.4.2   | Test Dataset                                                                                                        | 5 |

|   |     | 5.4.3   | Initial Comparison of Double vs. Single Precision                                                                   | 5 |

|   |     | 5.4.4   | Using the Proposed Approach to Analyze Error                                                                        | 6 |

|   |     | 5.4.5   | Identifying Precision Levels                                                                                        | 8 |

| 5.5 | Experiments and Results                                                                                                                                     |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | 5.5.1 Metrics                                                                                                                                               |

|     | 5.5.2 Experimental setting                                                                                                                                  |

|     | 5.5.3 Speedup results                                                                                                                                       |

|     | 5.5.4 Accuracy results                                                                                                                                      |

|     | 5.5.5 Energy results $\ldots \ldots \ldots$ |

|     | 5.5.6 Raspberry Pi results                                                                                                                                  |

| 5.6 | Discussion                                                                                                                                                  |

| 5.7 | Summary                                                                                                                                                     |

| Gen | eralized Model 109                                                                                                                                          |

| 6.1 | Problem Statement                                                                                                                                           |

| 6.2 | Model                                                                                                                                                       |

|     | 6.2.1 The Producer / Consumer Network                                                                                                                       |

|     | 6.2.2 Resources                                                                                                                                             |

|     | 6.2.3 Resource Flows                                                                                                                                        |

|     | 6.2.4 Resource Bounds                                                                                                                                       |

|     | 6.2.5 Configurations $\ldots \ldots \ldots$ |

|     | $6.2.6  \text{Relationships}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                              |

|     | 6.2.7 Revised definitions                                                                                                                                   |

| 6.3 | Toy Example                                                                                                                                                 |

|     | 6.3.1 Resource Relationships                                                                                                                                |

|     | 6.3.2 Accuracy                                                                                                                                              |

|     | 6.3.3 Resource Flows                                                                                                                                        |

|     | 6.3.4 Resource Bounds                                                                                                                                       |

|     | 6.3.5 Objective                                                                                                                                             |

| 6.4 | Linear Program                                                                                                                                              |

|     | 6.4.1 Quality Fractions                                                                                                                                     |

|     | 5.6<br>5.7<br><b>Gene</b><br>6.1<br>6.2<br>6.3                                                                                                              |

|   |       | 6.4.2   | Non-linear relationships               | 121 |

|---|-------|---------|----------------------------------------|-----|

|   |       | 6.4.3   | Accuracy                               | 122 |

|   |       | 6.4.4   | Objective Function                     | 123 |

|   | 6.5   | Summ    | ary                                    | 123 |

| 7 | Lite  | erature | e Review                               | 125 |

|   | 7.1   | Low-L   | evel Energy-Efficient Algorithms       | 125 |

|   |       | 7.1.1   | DVS Scheduling                         | 126 |

|   |       | 7.1.2   | DPM techniques                         | 128 |

|   |       | 7.1.3   | Energy Models for Concurrency Problems | 132 |

|   | 7.2   | Cross-  | node Power and Energy Management       | 134 |

|   |       | 7.2.1   | Dynamic workload distribution          | 134 |

|   |       | 7.2.2   | Energy saving                          | 137 |

|   |       | 7.2.3   | Task-Level Power Distribution          | 139 |

|   |       | 7.2.4   | Summary                                | 143 |

|   | 7.3   | Precis  | ion Management                         | 145 |

| 8 | Con   | nclusio | n                                      | 146 |

|   | 8.1   | Summ    | ary and Contributions                  | 146 |

|   | 8.2   | Future  | e Work                                 | 149 |

| R | efere | nces    |                                        | 151 |

# List of Tables

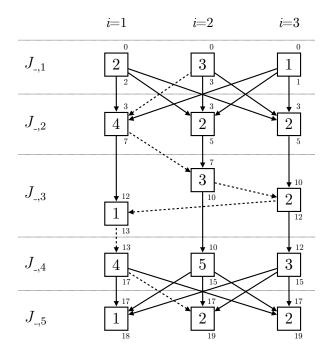

| 3.1 | Max-depths of tasks in Figure 3.4                                                | 53  |

|-----|----------------------------------------------------------------------------------|-----|

| 3.2 | Depth ranges of tasks in Figure 3.4                                              | 54  |

| 4.1 | The execution time of computation tasks in Figure 4.3 at different power bounds. | 73  |

| 4.2 | The execution time of communication tasks in Figure 4.3 at different bandwidths. | 73  |

| 4.3 | Solution of a single iteration of an 8-rank AlltoAll program                     | 79  |

| 5.1 | Apriltags library instruction breakdown                                          | 95  |

| 5.2 | Apriltags levels performance and accuracy.                                       | 102 |

| 5.3 | Apriltags perf statistics.                                                       | 104 |

| 5.4 | Apriltags on Raspberry Pi                                                        | 106 |

| 6.1 | Nodes $v_{[1,4]}$ resource usage                                                 | 117 |

| 6.2 | Coefficients of the accuracies of nodes $v_{[5,8]}$ in Equation 6.13             | 119 |

| 7.1 | Summary of power management techniques for HPC presented in [92]                 | 144 |

# List of Figures

| 2.1  | Overhead due to waking up and idling the CPU.                                                                                                                                                                                                                                               | 12 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2  | Energy consumption for all five implementations when running the $M/M/1/\mathbb{B}$ dataset.                                                                                                                                                                                                | 16 |

| 2.3  | Wakeups/s versus usage $\mu s/s$ for all five implementations when running the $M/M/1/\mathbb{B}$ dataset.                                                                                                                                                                                  | 16 |

| 2.4  | Percentage of time the CPU spends operating at different frequencies for Mutex, Sem, BP, and PBP when running the $M/M/1/c$ dataset                                                                                                                                                         | 17 |

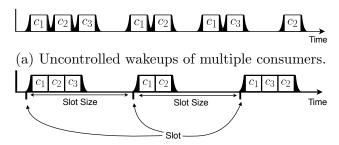

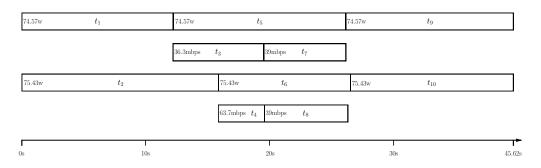

| 2.5  | Uncontrolled vs. aligned wakeups of 3 consumers A, B, and C                                                                                                                                                                                                                                 | 25 |

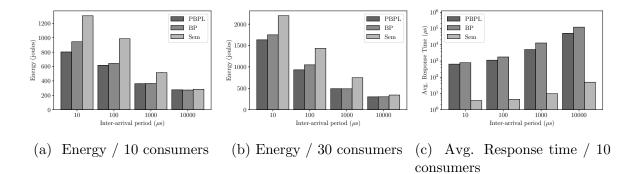

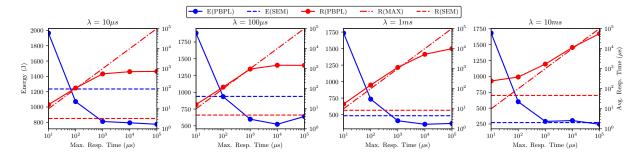

| 2.6  | Plots of energy consumption and average response time at various mean inter-arrival periods of the $M/M/1/\mathbb{B}$ queue                                                                                                                                                                 | 31 |

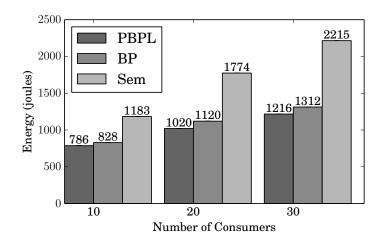

| 2.7  | A plot of energy consumption of all 3 implementations running 10, 20, and 30 concurrent producer-consumer pairs. These experiments are based on the web server dataset.                                                                                                                     | 32 |

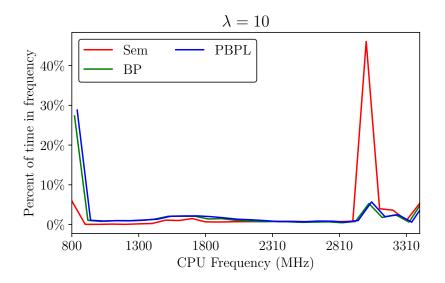

| 2.8  | Percentage of time the CPU spends operating at different frequencies for Sem, BP, and PBPL when running the $M/M/1/\mathbb{B}$ dataset                                                                                                                                                      | 33 |

| 2.9  | A plot of the energy and average response time of the three implementations<br>when running 10 concurrent producer-consumer pairs at different latency<br>presets (Max. Resp. Time). The experiments are executed at various mean<br>inter-arrival periods of the $M/M/1/\mathbb{B}$ queue. | 34 |

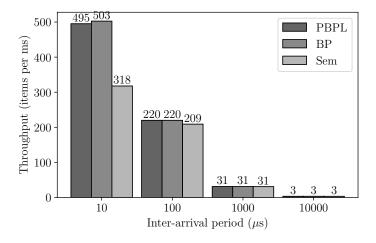

| 2.10 | A plot of the throughput of all 3 implementations running 10 concurrent producer-consumer pairs at various mean inter-arrival periods of the $M/M/1/\mathbb{B}$ queue.                                                                                                                      | 34 |

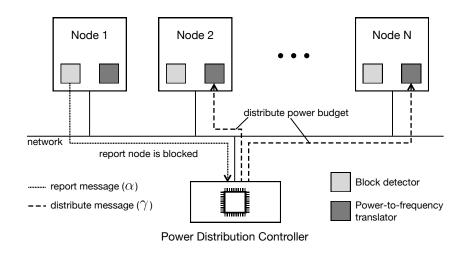

| 3.1  | Block diagram of an HPC cluster equipped with power distribution                                                                                                                                                                                                                            | 40 |

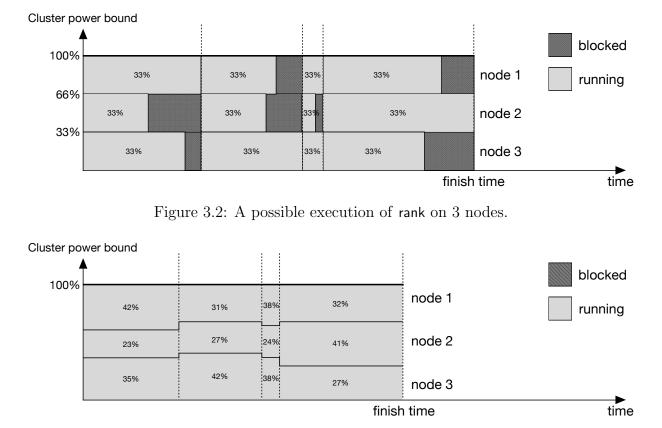

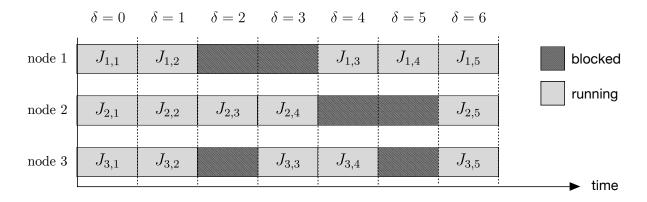

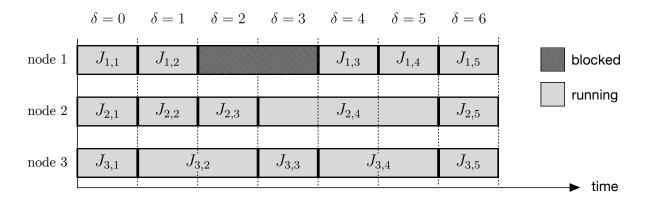

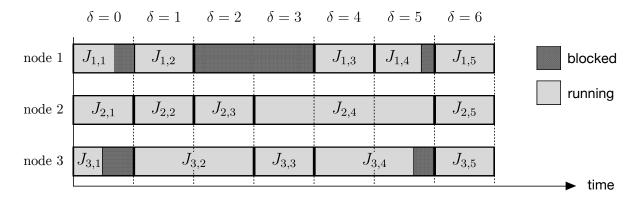

| 3.2  | A possible execution of rank on 3 nodes.                                                                                                                                                                     | 43 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.3  | An optimum execution of rank on 3 nodes using power redistribution                                                                                                                                           | 43 |

| 3.4  | Dependency graph of the program in Listing 3.2                                                                                                                                                               | 47 |

| 3.5  | Task concurrency as indicated by task max-depths                                                                                                                                                             | 54 |

| 3.6  | Task concurrency after applying depth ranges                                                                                                                                                                 | 55 |

| 3.7  | Blackouts in execution due to difference in execution time.                                                                                                                                                  | 55 |

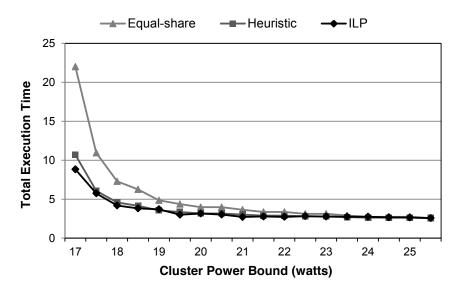

| 3.8  | Simulation results of the dependency graph in Figure 3.4                                                                                                                                                     | 58 |

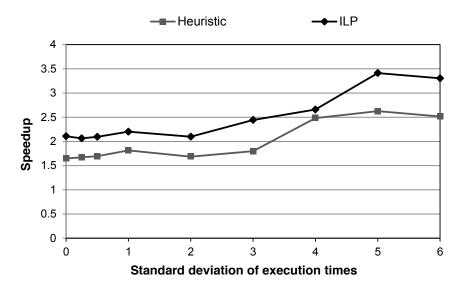

| 3.9  | Simulation results using different standard deviations of execution times.                                                                                                                                   | 59 |

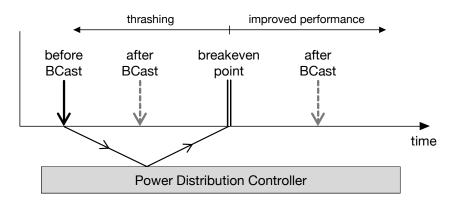

| 3.10 | The break<br>even point at which the report manager checks the buffer                                                                                                                                        | 60 |

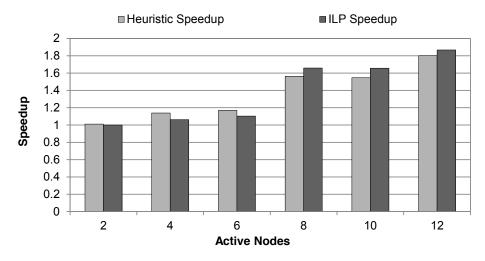

| 3.11 | Heuristic speedup versus ILP speedup of the EP benchmark                                                                                                                                                     | 63 |

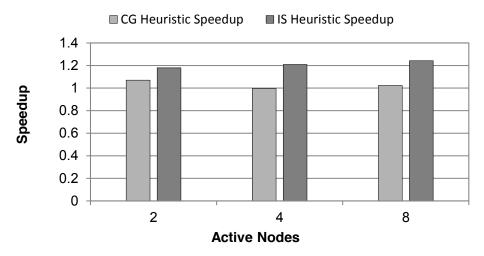

| 3.12 | Heuristic speedup of the CG and IS benchmarks.                                                                                                                                                               | 64 |

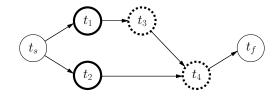

| 4.1  | Simple two rank blocking send / receive. Tasks with a thick solid border are computation tasks, tasks with a thick dotted border are communication tasks, and tasks with a thin border are placeholder tasks | 71 |

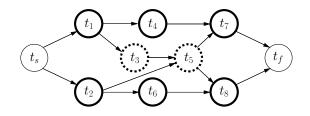

| 4.2  | Simple two rank non-blocking send / receive                                                                                                                                                                  | 72 |

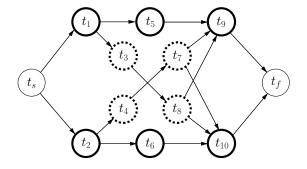

| 4.3  | Simple two rank non-blocking all-to-all                                                                                                                                                                      | 72 |

| 4.4  | A schedule for the IAlltoAll example                                                                                                                                                                         | 74 |

| 4.5  | Randomizing task execution time using the inverse relationship between power and duration.                                                                                                                   | 77 |

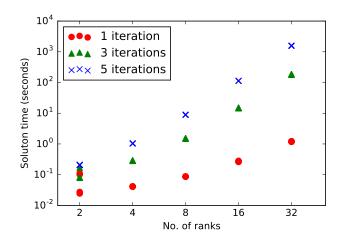

| 4.6  | The solution time of problems of different ranks and number of iterations                                                                                                                                    | 79 |

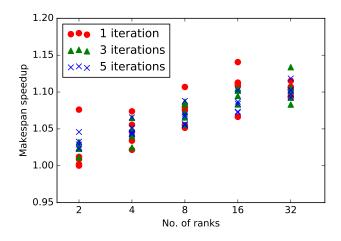

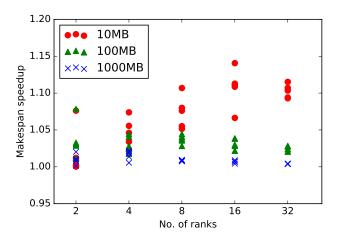

| 4.7  | Speedup of the LP optimized schedule versus a trivial equal share power<br>and bandwidth distribution                                                                                                        | 80 |

| 4.8  | Speedup of the LP optimized schedule grouped by transmitted data size.                                                                                                                                       | 80 |

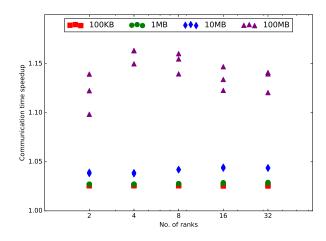

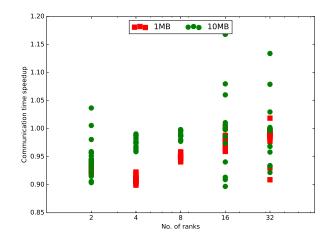

| 4.9  | Speedup of communication time in a ring communication MPI program.                                                                                                                                           | 82 |

| 4.10 | Speedup of communication time in an IAlltoAll communication MPI program                                                                                                                                      | 82 |

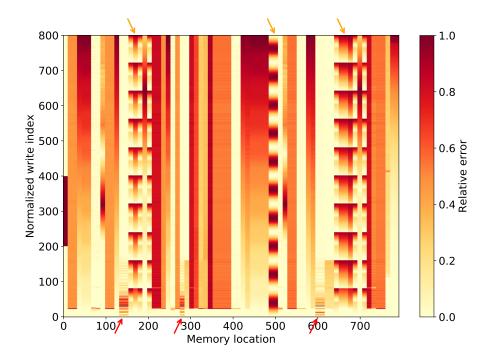

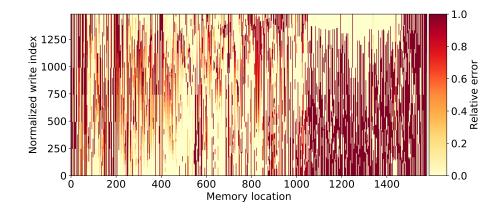

| 5.1  | Error trace per memory location. A darker pixel indicates higher error                                                                                                                                       | 89 |

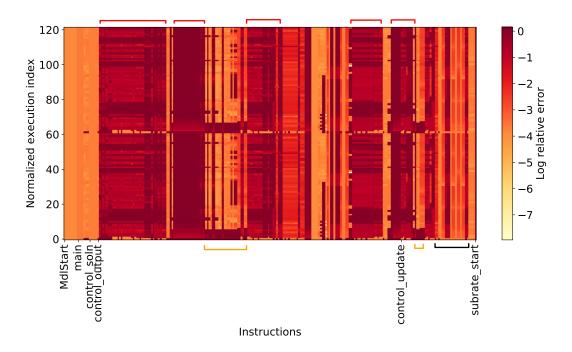

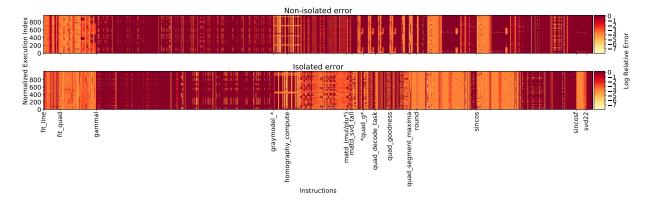

| 5.2  | Error trace per instruction. A darker pixel indicates higher error. Relative error is in $\log_{10}$ scale. | 91  |

|------|-------------------------------------------------------------------------------------------------------------|-----|

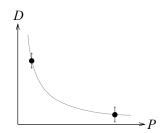

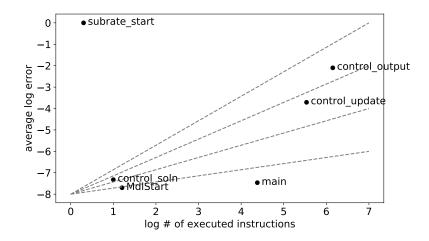

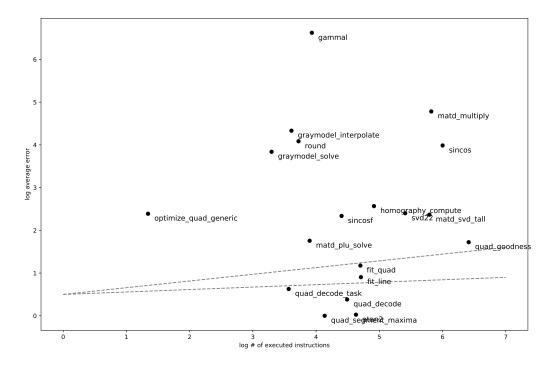

| 5.3  | Tradeoff between performance gain and error for every function. Average error is in $\log_{10}$ scale.      | 93  |

| 5.4  | An Apriltag [4]                                                                                             | 94  |

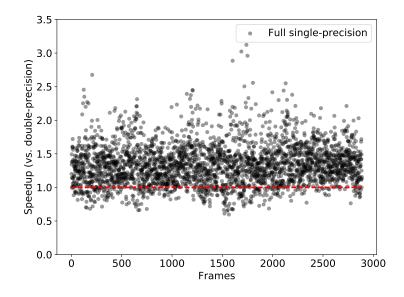

| 5.5  | Speedup of the full single-precision implementation.                                                        | 96  |

| 5.6  | Memory error trace of the Apriltags library                                                                 | 97  |

| 5.7  | Instruction error trace of the Apriltags library isolated per function and non-isolated                     | 98  |

| 5.8  | Tradeoff between performance gain and error for every function in the April-<br>tags library.               | 99  |

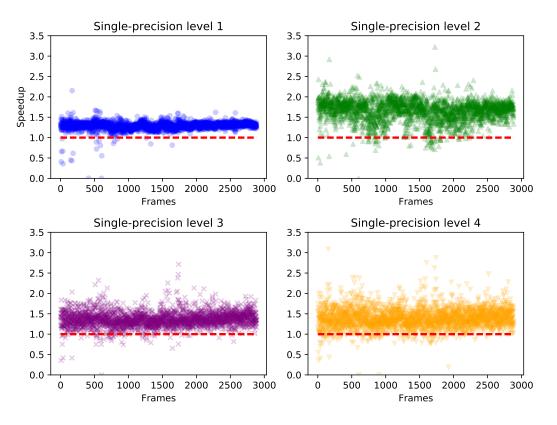

| 5.9  | Speedup per precision level.                                                                                | 102 |

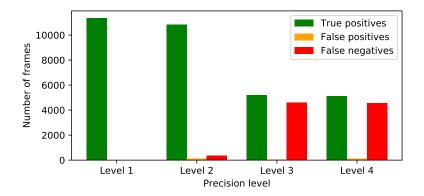

| 5.10 | False positives / negatives for each level.                                                                 | 103 |

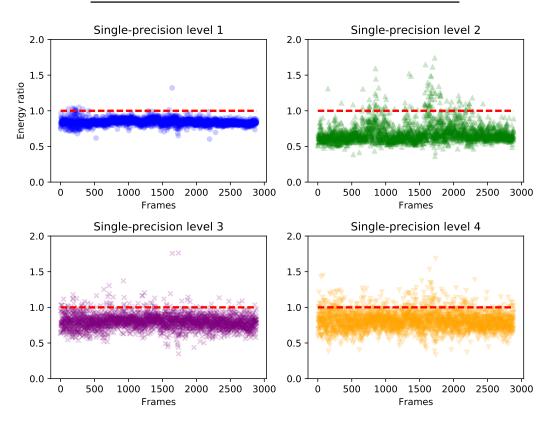

| 5.11 | Energy ratio per precision level                                                                            | 104 |

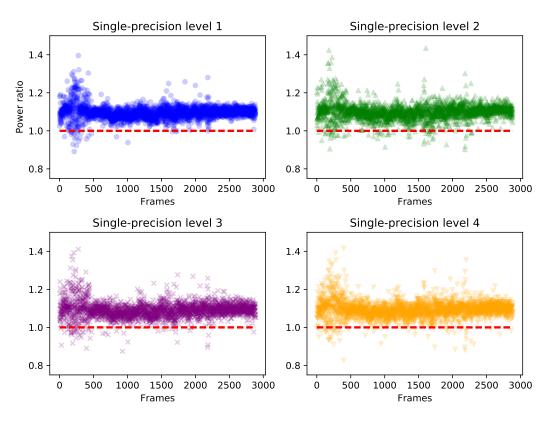

| 5.12 | Power ratio per precision level                                                                             | 105 |

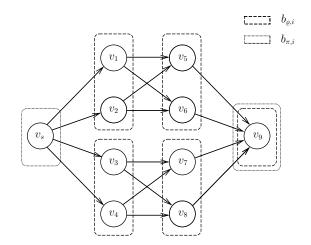

| 6.1  | A simple producer / consumer network                                                                        | 117 |

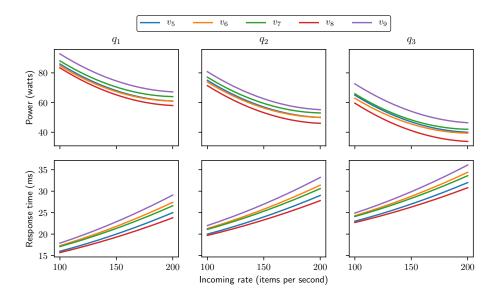

| 6.2  | Relationships of $v_{[5,9]}$ quality and incoming rate versus power and response time.                      | 118 |

## Chapter 1

## Introduction

### **1.1** Importance of Power and Energy Efficiency

Designing low-power computing system architectures has been an active area of research in the recent years, partly due to the increasing cost of energy as well as the high demands on producing and manufacturing environment-friendly devices. While the former is an explicit financial cost-benefit issue, the latter is attributed to green computing. However, with the recent explosion in mobile computing and incredible popularity of smart-phones and tablet computers, energy efficiency in software products has become a prime concern in application design and development and in fact as important as energy-optimal hardware chips.

Energy efficiency plays an important role in large-scale data centers. This can be easily observed in the growing size of data centers that serve internet-scale applications. Currently, such data centers consume 1.3% of the global energy supply, at a cost of \$4.5 billion. This percentage is expected to rise to 8% by 2020 [79]. In fact, power and cooling are the largest cost of a data center. For example, a facility consisting of 30,000 square feet and consuming 10MW, for instance, requires an accompanying cooling system that costs from \$2-\$5 million [106], and the yearly cost of running this cooling infrastructure can reach up to \$4-\$8 million [138]. The rise in energy costs has become so prevalent that the cost of electricity for fours years in a data center is approaching the cost of setting up a new data center [12].

Power efficiency does not always imply energy efficiency. Power efficiency is sometimes the objective regardless of energy efficiency. With the increasing urgency to reach exascale computing, governments must inevitably impose a constraint on the power consumption of data centers [15]. Power efficiency constraints also apply to embedded systems. Certain components are constrained to draw power allowed by the battery installed in the system, thus for instance forcing designers to reduce the clock speed of processors. A lower peak power also extends the lifetime of the battery [135] which is a target for consumer electronics. Thus, system designers often target energy efficiency as well as power constraints.

## **1.2** Resource Tradeoffs and the Status Quo

Multiple resources affect and are affected by power and energy consumption. Time is a resource that is often associated with power consumption. Higher power consumption leads to lower execution time or lower response time. Lower precision of floating point arithmetic reduces energy consumption through faster performance at the cost of accuracy [39]. Higher usage of network bandwidth implies higher power consumption [25]. Moreover, there are subtle tradeoffs that allow power to control resource utilization. For instance, in some cases, parallel tasks can be staggered using power bounds to reduce network bottlenecks, preventing these tasks from sending data at the same time, causing a bottleneck [100].

The tradeoffs between various resources and power and energy are non-trivial to manage, especially in dynamic heterogeneous systems. Identifying the optimal configuration of resources to meet a system's constraints and objectives is a difficult problem. This problem becomes more complicated when we consider the efficiency of the proposed solution. An energy management system running on a battery powered device should be conscious of its own energy footprint, refraining from using costly CPU-intensive algorithms. Moreover, the energy management system should respond to changes in the environment under timing constraints, which is often the case in embedded systems. On the other side of the spectrum, Big data and HPC applications could deploy tens of thousands of tasks. The different characteristics of tasks, nodes, and network infrastructure grossly complicate the tradeoff management of such massively parallel systems.

There is a large body of work on managing the performance energy tradeoff. The work ranges from low-level control at the CPU level [37, 70, 101, 196] to high level control at the task level across multiple nodes [62, 92, 141, 142, 169]. There has been extensive work studying the bandwidth energy tradeoff from the perspective of network design [25,89,140]. Moreover, various articles demonstrated the impact of precision on performance as well as energy [39, 41, 116, 117].

Most of the literature tackles the intricacies of specific tradeoffs and present sophisticated optimizations that impact various application areas. However, the current literature lacks the following in hierarchical order:

- The current literature lacks specific in depth studies on the energy/power tradeoff against specific aspects of resource use. For instance, the tradeoff between energy and response time and throughput of low-level concurrency primitives, as opposed to the extensively studied energy / performance tradeoff.

- The industry's focus on green computing allowed for advanced controls on the power and energy consumption of computing systems in the form of hardware power bounding and drivers for DVFS (Dynamic Voltage and Frequency Scaling) and DPMS (Dynamic Power Management System). Such controls are not robustly available for other resources such as bandwidth and precision. The current literature lacks studies on how to use such power controls to indirectly manage other resources.

- Finally, the current literature lacks work on a generalized model of systems with respect to energy / power and all resources that affect or are affected by energy / power consumption.

The above gaps in the literature culminate to the lack of a generalized system resource model that is centered around power and energy consumption. A model that allows capturing nuanced tradeoffs allows the designer to better optimize performance. By exploring resources that can be controlled using power and energy, a designer can have more control over a wider array of system resources. A model that accounts for a wide array of resources and their interactions allows the designer to optimize systems to their full extent while maintaining granular control over specific resource tradeoffs.

## **1.3** Thesis Statement

In this thesis, we validate the following hypothesis: as opposed to hardware based approaches, exclusively software-based approaches can provide a control mechanism with which engineers can manage the physical resource tradeoffs of their applications running in a power and/or energy constrained setting.

## 1.4 Research Problem

Thus, the high level research question we pose here is how multiple resource tradeoffs can be managed in an environment where power and energy are constrained. More concretely, can we construct a model that captures multiple resource tradeoffs with power and energy and allows for constraining and/or optimizing the consumption of different resources.

In this thesis we tackle the above research problem by setting the following high level objectives:

- Study the tradeoff of power / energy versus performance at different levels of abstraction in order to construct a generalized model.

- Study how power / energy constraints can affect the consumption of resources that are difficult to control explicitly.

- Construct a model that captures the resource tradeoffs involving power and/or energy.

## 1.5 Overview of the Proposed Approach

The thesis begins by studying the nuances of the tradeoff between energy and performance at the level of DVFS and DPMS for stream processing applications. We then move onto a higher task-level abstraction and study the tradeoff of power and performance for batch processing applications. Next, we study how bandwidth can be treated as a resource that can be indirectly managed by power controls. Next, we study how we can manage the tradeoff between precision and power. Finally, we combine the tradeoffs we studied above with other well-established tradeoffs to construct a flexible general model that allows for optimizing and/or constraining resource consumption.

#### 1.5.1 Energy versus Response Time

We begin in Chapter 2 by studying the intricacies of the energy / performance tradeoff of a general concurrency problem: namely the producer consumer problem. The producer consumer problem models a wide range of systems, from sensor processing to web servers to parallel stream processing in Big Data applications. Studying the energy profile of different implementations of this problem gives us insight into the impact of different synchronization primitives on energy consumption with respect to CPU core wakeups and frequency residency. Then, we develop an algorithm to manage the tradeoff between energy consumption and consumer response time. Furthermore, we extend the algorithm to manage the tradeoff between energy and memory footprint and demonstrate that intelligently timed memory allocations can significantly reduce energy consumption.

#### **1.5.2** Power versus Performance

In Chapter 3, we study the power / performance tradeoff at a higher level of abstraction, working towards our end goal of a general model. To that end, we study the collective power consumption of a cluster of machines performing batch computation. While it is well investigated that more power almost always means better performance, we attempt to design an algorithm to maximize performance under a cluster power optimally across the cluster). The problem becomes complicated when there is diversity in both the task load and the node power profiles. First, we introduce an ILP to minimize the makespan of a set of tasks with dependencies under a power bound. Next, we design an online heuristic to reduce the makespan by dynamically and strategically transferring power from one node to another to help long running tasks finish sooner. We demonstrate the effectiveness of the ILP and the heuristic on a well known set of parallel processing benchmarks.

#### 1.5.3 Power, Energy and Bandwidth Tradeoffs

In Chapter 4, we extend the work in Chapter 3 in two ways. First, we study the relationship between power and bandwidth. More concretely, we study how power can be used to create artificial staggering in order to alleviate bandwidth bottlenecks. We demonstrate that millisecond staggering in computation tasks can significantly reduce total communication time, even in over-provisioned network infrastructures. Our results indicate that in stressed networks, staggering can be a significant improvement to execution time. Second, we develop a linear programming model that performs power distribution as well as bandwidth and energy distribution. The linear programming model is significantly more scalable than the ILP in Chapter 3. We demonstrate how the LP can scale to solve larger problems where there are tens of thousands of variables.

#### 1.5.4 Power, Energy and Precision

In Chapter 5, we study the final tradeoff in the thesis: power versus precision. Prior work has demonstrated that programs that use single-precision floating point execute faster than their double-precision counterparts, and thus consume less energy. However, there is a loss in accuracy due to rounding error. We explore whether there is a tradeoff where only part of the program uses single-precision, and this part dictates the energy savings and the loss in accuracy. We refer to control points within the tradeoff as precision levels. Furthermore, we develop a tool that analyses a program that uses double-precision floating point, and identifies functions in the program that are most recommended to be downgraded to single-precision. A highly recommended function is one that saves a significant amount of energy while having minimal impact on accuracy. We demonstrate how our tool allows the developer to manage the energy precision tradeoff by applying the tool on a well-known computer vision application. We demonstrate that the developer can select multiple control points where accuracy is traded for energy and performance. With our tool, we identify one function in the program that can reduce energy consumption by 16% with zero impact on accuracy in our test data set.

#### 1.5.5 Generalized Model

By Chapter 5 we have already studied the tradeoff of power and/or energy with response time, throughput, execution time, bandwidth, and precision. In Chapter 6, we treat all the aforementioned factors as resources, whether renewable (e.g. power, bandwidth, throughput) or non-renewable (energy, time, accuracy). Using this abstraction, we can construct a generalized model that captures all tradeoffs of modelled resources. To that end, we modify the linear program in Chapter 4 to model a network of producers and consumers extending the abstraction of Chapter 2 where all the tradeoffs of the previous chapters are captured. In this model, a node in the network can be both a consumer of data received on its incoming edges and a producer of data on its outgoing edges. We abstract the precision of a node as a quality level at which the node performs its computation. This abstraction captures precision levels as well as algorithm alternatives which can consume varying amounts of resources. Our model allows the system designer to optimize for a specific resource while bounding any / all of the other resources, and is extensible to model more resources that have not been studied in this thesis.

## **1.6** Organization

The thesis is organized as follows: Chapter 2 presents the tradeoff of energy versus response time. Chapter 3 presents the tradeoff of power versus performance. Chapter 4 presents the tradeoff of power and bandwidth. Chapter 5 presents the tradeoff of energy and precision. Chapter 6 presents the generalized model that captures all tradeoffs. Chapter 7 presents the literature review, and finally Chapter 8 concludes the thesis.

## Chapter 2

## Energy versus Response Time

The majority of classic concurrency control algorithms were designed in an era when energy efficiency was not an important dimension in algorithm design. Concurrency control algorithms are applied to solve a wide range of problems from kernel-level primitives in operating systems to networking devices and web services. These primitives and services are constantly and heavily invoked in any computing system and by a larger scale in networking devices and data centers. Thus, even a small change in their energy spectrum can make a huge impact on overall energy consumption for long periods of time.

This chapter focuses on the classic *producer-consumer* problem, which models a wide range of stream processing applications. First, we study the energy profile of a set of existing producer-consumer algorithms. In particular, we present evidence that although the functional goal of these algorithms are the same, these implementations behave drastically differently with respect to energy consumption. Then, we present a dynamic algorithm for the multiple producer-consumer problem, where consumers in a multicore system use learning mechanisms to predict the rate of production, and effectively utilize this prediction to attempt to *latch onto* previously scheduled CPU wake-ups. Such group latching increases the idle time between consumer activations resulting in more CPU idle time and, hence, lower average CPU frequency, which in turn reduces energy consumption. We enable consummers to dynamically reserve more pre-allocated memory in cases where the production rate is too high. Consumers may compete for the extra space and dynamically release it when it is no longer needed. Our experiments show that our algorithm provides a 38%decrease in energy consumption versus a mainstream semaphore-based producer-consumer implementation when running 10 parallel consumers. We validate our algorithm with a set of thorough experiments on varying parameters of scalability. Finally, we present our recommendations on when our algorithm is most beneficial.

## 2.1 Introduction

Classic algorithms in computer science are heavily used in virtually any computing system ranging from web services and networking devices to device drivers and operating systems kernels. However, these algorithms were designed in an era when energy efficiency was not an important dimension in algorithm design. For example, Dijkstra's shortest path algorithm fails in the context of energy-optimal routing problems, as simply evaluating edge costs as energy values does not work [145]. Thus, we argue that many of such classic algorithms need to be re-visited and re-designed, so that on top their functional requirements, energy constraints are treated as a first-class objective as well. Some of these algorithms are applied in such a high capacity that even small improvements in their energy consumption behavior may have a huge impact in the energy profile of large-scale systems and mobile devices in long periods of time.

*Producer-consumer* is a classic problem in concurrent computing, where two processes, the *producer* and the *consumer* share a common bounded-size memory buffer as a queue. The multiple producer-consumer problem extends this setup by having multiple producers and consumers using the same buffer. In this chapter, we study the more general case of a set of producer-consumer *islands* where each island has its own buffer, and its own producers and consumers. We abstract each island as a single producer-consumer pair associated with a separate buffer. This abstraction helps simplify our online analysis and reduction of energy consumption without loss of generality. In that setup, we focus on the interaction between multiple producer-consumer pairs, and in turn their combined energy consumption. The multiple producer-consumer pairs problem applies to a multitude of real-world scenarios in many systems around us, specifically stream processing applications. Examples include:

- Operating systems primitives. Such primitives provide developers with high-level system calls to read and consume data received from I/O devices, e.g., in device drivers. In this setting, each device is a producer, providing data to its respective consumer, i.e. the user application.

- Web servers. HTTP requests produced by web browsers are stored in separate buffers per web application, that are consumed and processed by threads in each application's thread pool.

- *Runtime monitoring.* In runtime monitoring, different events produced by the environment or internal system processes are consumed and processed by multiple runtime monitors with separate buffers.

• *Networking.* In most networking devices (e.g., routers), data packets received from the network need to be removed and processed from internal buffers of the device and routed to different destinations. Buffers separate subnets, Virtual LANs, or QoS levels.

In this chapter, we propose a novel energy-efficient algorithm for the multiple producerconsumer pair problem for multicore systems, where each consumer is associated with one and only one producer. To the best of our knowledge, this is the first instance of such an algorithm. To better understand the vital contributing factors to the energy consumption behavior of the problem, we first conducted a study to analyze the energy profile of existing popular implementations of the producer-consumer problem. The implementations in our analysis consist of a yield-based algorithm, two algorithms based on synchronization data structures (i.e., semaphores and mutexes), and two algorithms that employ batch processing. We observed that these implementations behave drastically differently with respect to energy consumption. While the yield algorithm is the worst in energy efficiency due to high CPU utilization, the algorithms, where the consumer processes data items in batches are the most energy-efficient due to a lower average CPU frequency. In particular, batch processing results in 75% reduction in energy compared to yield and 32% compared to the semaphore-based implementations. This is validated by a strong positive correlation between average CPU frequency and energy consumption. Such a dramatic shift in energy profile clearly motivates the need for designing an energy-aware solution for the producer-consumer problem.

Roughly speaking, our proposed algorithm exploits bounded-time dynamic batch processing. It interprets time as a track with periodic slots. To increase the idle time between wakeups, it dynamically constitutes track slots, so consumers can latch on and exploit a CPU wakeup in groups. Given a set of cores, since each core may host a set of consumers, a *core manager* component targets aligning consumers to the slots in that core's track. The core manager is responsible for managing the slot allocations on the track of its respective core. Consumers are designed so that they can dynamically predict production rate of data items to compute and request appropriate latching time. Furthermore, consumers may lend each other buffer space, so that a consumer dealing with a producer with high production rate can continue latching on other consumers and not cause new wakeups.

Our approach can well-adapt to systems that already employ dynamic voltage and frequency scaling (DVFS). In particular, our design

1. can work with state-of-the-art DVFS schemes by leveraging their energy savings which focus on optimum choices of CPU frequency. Dynamic batch processing benefits from such frequency manipulations such that a batch consumption job consumes minimum energy.

2. reduces energy savings further by reducing the number of CPU wakeups. Thus, a lower number of wakeups coupled with efficient CPU frequency manipulations results in an improved energy consumption.

To demonstrate the effectiveness of our approach, we conduct our experiments over a wide range of varying parameters and explore the strengths and weaknesses of using dynamic batch processing. This allows us to provide a recommendation as to what systems are better suited to employ dynamic batch processing. We argue that our dynamic batch processing approach is particularly beneficial in two application areas:

- 1. According to a Google study [11], web servers are rarely completely idle and seldom operate near their maximum utilization, instead operating most of the time at between 10 and 50 percent of their maximum utilization levels. Moreover, the CPU contributes to more than 50% of Google server power consumption. In such servers, our approach results in longer CPU idle periods, which saves a great deal of energy. This energy saving comes at a cost in terms of response time, which is significantly reduced when using batch processing. However, our approach provides controls with which a user can tune the energy saving versus response time.

- 2. Data-processing-intensive applications are becoming more widespread every day. In such applications, throughput is more important than individual item response time. Our experiments show that our approach results in higher throughput while saving a considerable amount of energy. This makes dynamic batch processing significantly beneficial for applications that can fit in a producer-consumer model.

We validate our claims by conducting thorough experiments using a synthetic queueing theory based arrival pattern, as well as a data set of a web server incoming HTTP requests log [5]. Our results show that our algorithm can lower energy consumption by 51%compared to a semaphore-based implementation of producer-consumer when running 10 parallel consumers. In comparison to a simple batch processing approach, our algorithm provides up to a 15% improvement in energy consumption. We experiment with varying buffer sizes, number of parallel consumers, as well as data item inter-arrival period. The objective of these experiments is to study the scalability of the proposed algorithm and identify its strengths and weaknesses. To that end, we present our results and recommendations on when it is most appropriate to use our dynamic batch processing approach. Our experimental results demonstrate the tradeoffs between response time and energy savings. The results suggest that the selection of consumer implementation should depend on the required maximum response time and the expected mean inter-arrival period.

Organization. The rest of the chapter is organized as follows. In Section 2.2, we describe the background concepts on CPU power states. Section 2.3 presents our findings on energy profile of various implementations of the producer-consumer problem. We formally state the energy optimization objective for the multiple producer-consumer problem in Section 2.4. Our energy-efficient solution to multiple producer-consumer is described in Section 2.5, while Section 2.6 analyzes the results of experiments. Finally, we make concluding remarks in Section 2.7.

## 2.2 Background

Power management technologies approach energy/power efficiency from different perspectives:

- Static power management (SPM) simplifies the power management problem by providing support for low-power modes at the hardware level. A system can statically transition to the low-power modes on demand. An example of this is a cell phone going into idle mode when it is locked, or a sensor periodically sleeping at a predefined period.

- Dynamic power management (DPM) employs dynamic techniques at run time that determine which power state the system should be in. DPM uses different techniques to infer whether or not a transition to a more efficient state is worthwhile, and, which efficient state to transition to.

In DPM, hardware with scalable power consumption is combined with management software to achieve improved efficiency. Hardware support comes in multiple flavors, e.g., Dynamic Voltage Scaling (DVS) and Dynamic Frequency Scaling (DFS). DVS scales the voltage at which the CPU operates, and thus controls its energy consumption. This is based on the basic Watt's law

$$P = V \cdot I$$

where V is the voltage, I is the current, and P is the power. DVS is becoming more prominent in disk drives, memory banks, and network cards [45]. DFS scales the frequency

at which the CPU operates, such that when a high demand occurs, the frequency is raised to meet that demand, at a higher energy cost. When the CPU utilization drops, so does the operating frequency, causing a decrease in energy/power consumption. This is because dynamic power is calculated by

$$P_d = C \cdot V^2 \cdot f$$

where C is the capacitance switched per cycle, V is the voltage, and f is the current CPU frequency. DVS and DFS are often combined into DVFS, where both techniques are used to scale CPU power consumption. CPUs generally support a predefined set of frequency/voltage combinations performance states, known as P-states. These states define the performance of the CPU in terms of power and throughput.

A relatively different approach to power saving is utilizing CPU C-states. C-states are modes at which the CPU operates, differing mainly in their power consumption. This is achieved by turning off parts of the CPU that are needlessly consuming energy. This may include gradually turning off internal CPU clocks, cache, the bus interface, and even decreasing the CPU voltage (DVS). C-states generally start at C0 which indicates the CPU is fully active, and gradually increases the number (C1, C2, ...) until the idle state or in some cases the hibernate state.

*Race-to-Idle* is a well-known energy saving concept based on the premise that it is more energy efficient to execute the task at hand faster (a higher P-state, which indicates a higher CPU frequency) and then go to idle mode (i.e., a deeper C-state, which is a deeper CPU idle state), versus running the task at a lower speed resulting in less idle time. Raceto-idle is based on the fact that idle power is significantly less than active power even at a low frequency. Furthermore, recent CPU chipsets such as the Intel Haswell are even more optimized to save a significant amount of power in idle mode. This indicates that hardware manufacturers are moving towards approaches that attempt to increase CPU residency in deeper C-states. This is especially useful in the context of *core parking*, where specific cores are put in a deep sleep state, reducing their energy consumption significantly.

Although race-to-idle is a valid approach, in the context of the producerconsumer problem - where items are arriving at a certain rate and not in bulk race-to-idle may not be the most appropriate strategy. If the items are arriving in such a way that denies the CPU any actual idle time, voltage scaling will detect that there is a consistent load on the CPU and

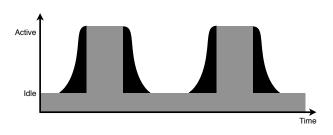

Figure 2.1: Overhead due to waking up and idling the CPU.

thus increase its frequency. Effectively, the

CPU attempts to race-to-idle but never gets a chance to go to idle, and this results in huge energy waste, due to "racing" most of the time without any chance to "rest". This is in addition to the energy wasted due to idling and waking up frequently. In other words, a certain delay must occur in order for idle mode to be advantageous. Figure 2.1 illustrates that more contiguous idle time is more efficient. Thus, a valid energy saving strategy is to increase the contiguousness of idle periods. This approach should be combined with raceto-idle to ensure that a power management strategy targets more idle time with minimum wasted power due to idle-active and active-idle transitions.

## 2.3 Producer-Consumer Energy Profile

In this section, we present experimental evidence showing that different implementations of a widely used concurrency control algorithm exhibit drastically different energy consumption profiles.

### 2.3.1 Producer-Consumer Implementations

The *producer-consumer* problem is a classic multi-process synchronization problem, where a *producer* process produces data items and places them in a memory buffer, and, a *consumer* process consumes the items from the same memory buffer. Since these processes work concurrently, they need to synchronize to prevent deadlocks and race conditions. Most of the implementations we study in this section rely on the use of a circular buffer. The advantage of a circular buffer is that reading from it and writing into it involves two different pointers, and, thus, alleviates the need to put a single counter in a critical section to avoid concurrency issues.

We study the following implementations:

- Yield. This implementation uses sched\_yield within a spinlock to yield the CPU if the buffer is full/empty.

- Mutexes and conditional variables (Mutex). This implementation uses pthread mutex to ensure mutually exclusive concurrent access to a buffer. We use conditional variables to signal when data is available for the consumer and when space is available for the producer.

- Semaphores (Sem). This implementation uses two semaphores used for synchronizing emptiness and fullness of the buffer.

- Batch processing (BP). This implementation is similar to the semaphores implementation, except that the consumer waits until the buffer is full and then processes all items in the buffer in one batch.

- Periodic batch processing (PBP). This implementation is similar to the batch processing implementation, except that the consumer processes the batch within fixed time intervals (using the usleep() system call) instead of whenever the buffer gets filled. The period for this experiment is 1ms.

#### 2.3.2 Experimental Settings

We study the energy consumption of the different producer-consumer implementations using two methods: PowerTop<sup>1</sup> and RAPL (Running Average Power Limit)<sup>2</sup>.

PowerTop is a popular Linux tool that uses CPU performance counters to estimate the power consumption of all running processes in the system. We use PowerTop to measure the number of wakeups per second that a process causes, and the percentage of CPU usage that the process consumes. The unit for CPU usage in PowerTop is microseconds per second, meaning the number of microseconds the process spends executing every second.

RAPL is an interface that provides monitoring and controlling power consumption of specific Intel CPUs. Starting from the second generation Core i7 processor, codenamed Sandy Bridge, RAPL can be used to monitor energy consumption by reading machine specific registers (MSRs). We use the Linux RAPL driver over PAPI to measure energy consumption of each experiment. Our test machine uses an Intel Core i7 Sandy Bridge processor.

Finally, each implementation of producer-consumer is tested using two datasets. First, a synthetic dataset based on an  $M/M/1/\mathbb{B}$  queue [159]. This denotes that the production and processing times are drawn from exponential distributions (M/M), there is 1 consumer (1 consumer for every producer), and the items are buffered in a buffer of size  $\mathbb{B}$ . Second, a real-life dataset based on web server incoming HTTP requests log [5]. We use a portion of the log that covers web requests received over 40 days. Each experiment constitutes running 5 producers/consumers in parallel until the full dataset items are consumed. In the case of

<sup>&</sup>lt;sup>1</sup>https://01.org/powertop/

<sup>&</sup>lt;sup>2</sup>https://01.org/blogs/tlcounts/2014/running-average-power-limit--rapl

the web server data, the log is divided equally such that each producer simulates 8 days of logs. All producers run on one core, and all consumers run on another core. Since cores can be idled separately, this allows us to demonstrate the impact of consumers synchronization on energy consumption regardless of the behavior of producers, which is not in our control. We execute 50 replicates of each experiment for statistical confidence. 95% confidence intervals are calculated for all measurements. We measure five metrics in each experiment:

- Energy (joules). The number of joules consumed by the system when the respective implementation is executed.

- Wakeups/s. The number of CPU wakeups per second due to the respective implementation.

- Usage (ms/s). The number of milliseconds out of every second that the CPU spends executing the respective implementation.

- Core idle percentage. The percentage of idle time that each CPU core spends during the respective implementation.

- Core frequency percentage. The percentage of time the CPU spends operating at each possible frequency while executing the respective implementation.

### 2.3.3 Experimental Results

#### Sanity Checks

We perform the following set of sanity checks to ensure our experimental setup is valid:

- We execute a test with a busy waiting multithreaded program running on two cores of the processor, and we ensure that no experiment reaches the energy consumption found in that implementation.

- We execute a test where no background processes are running except kernel tasks, and we measure energy. We ensure that the energy consumed in this experiment is less than any other experiment we run.

- We measure the statistical confidence interval to ensure that our conclusions are not based on outliers.

#### Energy consumption of producer-consumer implementations

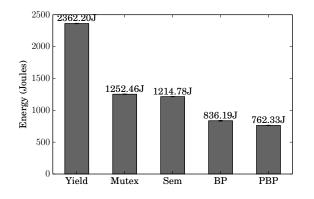

Figure 2.2 shows the energy consumption of each of the five producer-consumer implementations. The energy results are highly consistent, as apparent in the small error bars. The Yield implementation consumes the most energy since the CPU is mostly active during its execution. On average, both CPU cores are idle only 1% of the time when executing Yield. Mutex and Sem have similar energy consumption profiles, using 50% of the energy consumed by Yield. BP reduces energy consumption further down to 35% of Yield, and 68% of Sem. Finally, PBP is consistently the most energy efficient implementation consuming 32% of Yield and 62% of Sem. This indicates that batch-processing-based implementations can improve upon the most widely used implementation today significantly.

#### Understanding root causes of energy profile

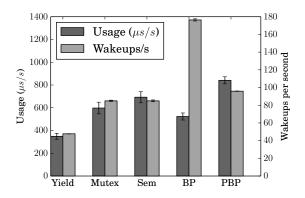

Next, we study the CPU usage and number of wakeups in each implementation (see Figure 2.3). Yield has the lowest number of wakeups which is expected since the CPU is active most of the time. However, the CPU usage of Yield is significantly less than all other implementations. This is counter-intuitive given the high energy consumption of Yield. Upon studying the percentage of time spent in each available CPU frequency, Yield spends on average 99% of the time at the highest CPU frequency of 3.4GHz. Intel SpeedStep dynamic voltage scaling recognizes that the CPU is active most of the time and upgrades its frequency to the maximum.

Figure 2.2: Energy consumption for all five implementations when running the  $M/M/1/\mathbb{B}$  dataset.

Figure 2.3: Wakeups/s versus usage  $\mu s/s$  for all five implementations when running the  $M/M/1/\mathbb{B}$  dataset.

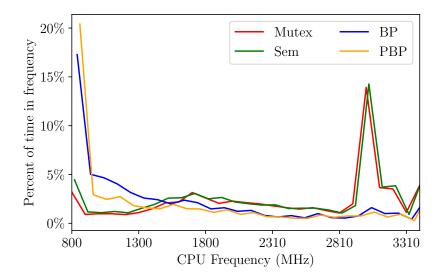

Figure 2.4: Percentage of time the CPU spends operating at different frequencies for Mutex, Sem, BP, and PBP when running the M/M/1/c dataset.

The number of wakeups of Mutex and Sem is similar, as is their energy consumption. BP has a significantly high number of wakeups, which can be explained by the consumers waiting for the buffer to be filled. PBP reaches a compromise by using a periodic activation of consumers, which reduces the number of wakeups by approximately 50%. This decrease in the number of wakeups results in an increase in usage since the CPU has no chance to go to sleep too often.

The key to understanding the energy consumption of the different implementations is the distribution of time spent in different CPU frequencies. As mentioned earlier, Yield spends 99% of its time at the maximum CPU frequency. Figure 2.4 shows the percent of time spent in different CPU frequencies of the remaining four implementations. We omitted Yield from Figure 2.4 to make it more readable for the remaining implementations. Notice that Mutex and Sem have low percentages when residing in lower frequencies, and a spike at 3GHz. This explains their relatively high energy consumption compared to the batch-based implementations. BP on the other hand spends most of the time at the lowest CPU frequency of 800MHz (approx. 18%). PBP spends even less time at frequencies higher than 800MHz.