### Cronfa - Swansea University Open Access Repository

This is an author produced version of a paper published in: *IEEE Journal of the Electron Devices Society*

Cronfa URL for this paper: http://cronfa.swan.ac.uk/Record/cronfa38852

Paper:

Nagy, D., Indalecio, G., Indalecio, G., Garcia-Loureiro, A., Elmessary, M., Elmessary, M., Kalna, K. & Seoane, N. (2018). FinFET versus Gate-All-Around Nanowire FET: Performance, Scaling and Variability. *IEEE Journal of the Electron Devices Society*, 1-1. http://dx.doi.org/10.1109/JEDS.2018.2804383

This item is brought to you by Swansea University. Any person downloading material is agreeing to abide by the terms of the repository licence. Copies of full text items may be used or reproduced in any format or medium, without prior permission for personal research or study, educational or non-commercial purposes only. The copyright for any work remains with the original author unless otherwise specified. The full-text must not be sold in any format or medium without the formal permission of the copyright holder.

Permission for multiple reproductions should be obtained from the original author.

Authors are personally responsible for adhering to copyright and publisher restrictions when uploading content to the repository.

http://www.swansea.ac.uk/library/researchsupport/ris-support/

# FinFET versus Gate-All-Around Nanowire FET: Performance, Scaling and Variability

Daniel Nagy, Guillermo Indalecio, Antonio J. García-Loureiro, Muhammad A. Elmessary, Karol Kalna, and Natalia Seoane

Abstract—Performance, scalability and resilience to variability of Si SOI FinFETs and gate-all-around (GAA) nanowires (NWs) are studied using in-house-built 3D simulation tools. Two experimentally based devices, a 25 nm gate length FinFET and a 22 nm GAA NW are modelled and then scaled down to 10.7 and 10 nm gate lengths, respectively. A TiN metal gate work-function granularity (MGG) and line edge roughness (LER) induced variability affecting OFF and ON characteristics are investigated and compared. In the OFF-region, the FinFETs have over an order of magnitude larger OFF-current that those of the equivalent GAA NWs. In the ON-region, the 25/10.7 nm gate length FinFETs deliver 20/58% larger ON-current than the 22/10 nm gate length GAA NWs. The FinFETs are more resilient to the MGG and LER variability in the sub-threshold compared to the GAA NWs. However, the MGG ON-current variability is larger for the 10.7 nm FinFET than that for the 10 nm GAA NW. The LER ON-current variability depends largely on the RMS height; whereas a 0.6 nm RMS height yields a similar variability for both FinFETs and GAA NWs. Finally, the industry preferred  $\langle 110 \rangle$  channel orientation is more resilient to the MGG and LER variability in both architectures.

*Index Terms*—Drift-Diffusion (DD); Monte Carlo (MC) simulations; Density Gradient (DG) quantum corrections; Schrödinger equation based quantum corrections; Si FinFET; Gate-All-Around (GAA) Nanowire (NW) FET; Metal Grain Granularity (MGG); Line Edge Roughness (LER).

#### I. INTRODUCTION

**F** IN field-effect transistors (FinFETs) are the preferred device architecture for mass production beyond the 32 nm technology node [1], [2] because they offer superior electrostatic control of the channel over planar metal-oxide semiconductor FETs (MOSFETs) [2], [3]. However, further scaling of the transistors is a cumbersome task requiring novel architectures [4]. Gate-all-around (GAA) nanowire (NW) FETs are promising candidates to replace the FinFETs for future technology nodes due to a better control of the channel transport via fully surrounding gate [5]. Therefore, detailed physical investigation of the available technologies is of great importance for future solutions. Further challenges emerge during fabrication processes in the next technology nodes. The

D. Nagy, G. Indalecio, A. J. García-Loureiro and N. Seoane are with the Centro Singular de Investigación en Tecnoloxías da Información, University of Santiago de Compostela, 15782 Santiago de Compostela, Spain (e-mail: daniel.nagy@usc.es; antonio.garcia.loureiro@usc.es; natalia.seoane@usc.es).

G. Indalecio is also with the Institute for Microelectronics, TU Wien, 1040, Vienna, Austria (e-mail: guillermo.indalecio@usc.es)

K. Kalna and M. A. Elmessary are with the Nanoelectronic Devices Computational Group, Swansea University, Swansea, Wales, SA1 8EN, U.K. (e-mail: k.kalna@swansea.ac.uk).

M. A. Elmessary is also with the Department of Engineering Mathematics and Physics, Mansoura University, Mansoura 35516, Egypt (e-mail: moh\_elmessary@hotmail). impact of process variations has become a crucial issue to device design [6] that could impair device performance. The main variability sources affecting the device reliability are: random dopants (RD), oxide thickness variation (OTV), interface trap charges (ITC), metal gate work-function granularity (MGG) and line edge roughness (LER) [7]–[13].

1

Computer-aided-design tools can reduce both the cost and the development time of these novel device architectures [14]. The classical drift-diffusion method assisted by quantum corrections when properly calibrated is a very efficient way of running thousands of simulations and determine device performance. However, at ON-current conditions the carrier transport at nanoscale becomes i) highly non-equilibrium and ii) strongly affected by quantum-mechanical phenomena. Then a quantum corrected ensemble Monte Carlo technique is a more optimal choice [15], [16]. Additionally, the accurate description of 3D device shapes is of equal importance for accurate device simulations at the nanoscale. That description can be achieved using a finite element (FE) approach [17].

In this paper, we present a comparison of the performance, scaling and variability of realistic silicon based FinFETs and GAA NWs. We start with a FinFET and a GAA NW designed for the 16/14 nm CMOS technology when our simulations of I-V characteristics [15], [18] can be compared with experimental data [19], [20], respectively. We then scale these two architectures to dimensions foreseen for the 5 nm Si CMOS technology [21]. The paper is structured as follows. In Section II, the studied devices and simulation models are described. In Section III, a comparison study of the performance between the FinFET and the GAA NW are presented. Two major variability sources for the FinFET and GAA NW, MGG and LER, are studied in Sections IV and V for the OFF-and ON-regions of the device operation, respectively.

#### II. DEVICE DESCRIPTION AND SIMULATION APPROACH

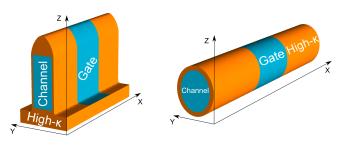

The multi-gate device structures used in this paper are created following published experimental data. In Fig. 1, transistor schematics are shown for the 25 nm gate length FinFET (a) from Ref. [19] and the 22 nm gate length GAA NW (b) from Ref. [20]. After validation of the simulated I-V characteristics against experimental data [15], [18], we have scaled down both devices following the ITRS guidelines [22]. The device dimensions for the experimental and scaled devices are summarised in Table II. Note that when both devices are scaled the maximum doping concentration in the source/drain regions are kept constant and the Gaussian profile is scaled with the same ratio as the gate length. The complex features

2168-6734 (c) 2018 IEEE. Translations and content mining are permitted for academic research only. Personal use is also permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

Figure 1. Schematics of the simulated (a) FinFETs with a rectangular channel shape and (b) GAA NWs with an elliptical channel shape.

of multi-gate transistors, such as the rounded corners seen in Fig. 1, are critical for accurate simulations in the deep nano-regime [23]. An excellent method to achieve a detailed description of the aforementioned device mesh is the 3D finite element (FE) method [17].

Our analysis is carried out using an in-house FE simulator toolbox with capabilities of quantum corrected drift-diffusion (DD) and Monte Carlo (MC) techniques [17]. The DD model is preferred for the simulation of the sub-threshold region due to time efficiency and because the particle based MC method can be noisy at very small currents. The DD simulations are also used to provide an initial solution for the MC to reduce the overall simulation time. In the ON-region of the devices, a non-equilibrium carrier transport dominates, leading to effects like the velocity overshoot, that the DD approach is not able to capture. Therefore, the MC method is used there. The MC engine accounts for all Si related electron scattering mechanisms, acoustic and non-polar optical phonon (intraand inter-valley) [24], [25], ionised impurity scattering using the third body exclusion by Ridley [26], [27], and interface roughness (IR) scattering using Ando's model [28]. The electron screening in the electron-ionised impurity scattering is using a static screening model [29] obtained using Fermi-Dirac statistic with a self-consistently calculated Fermi energy and electron temperature in a real space of device simulation domain. At the nanoscale regime, quantum mechanics play a significant role that requires the inclusion of some kind of quantum correction model. Consequently, a density-gradient (DG) approach is used with the DD simulations [30]. However, this method requires a calibration against experimental data or quantum mechanical simulations, for example, a Non-Equilibrium Green's function (NEGF) [31] or a Poisson-Schrödinger solver [32]. The DD simulations employ the Caughey and Thomas doping dependent low-field electron mobility model [33], together with lateral and perpendicular electric field models [34]. We use electron effective masses as calibration parameters in the DG QCs to mimic the source-todrain tunnelling and quantum confinement effects [18]. Table I lists the relevant calibration parameters in the DD simulations. Note that the quantum corrected DD simulations are only used for a study of the sub-threshold region. Therefore, Schrödinger equation based quantum corrections were implemented in the 3D FE MC simulation toolbox to allow calibration free simulations. More detailed description of the simulation toolbox is available in Refs. [15], [17], [35].

As aforementioned, devices in a deep nano-scale regime exhibit an increased effect of different variability sources. Therefore, in this paper, we also consider two major sources of device variability, the MGG and LER [8]. For the MGG, randomly generated metal gate profiles are created, which are then mapped onto the gate and fed to the simulation toolbox. To create the profiles, we use the Poisson-Voronoi diagrams approach that mimics the "formation" of metal grains with various shapes and sizes, just like in realistic metal gates [36]. Such method is thought to be a more accurate than the square grains approach [37], [38], especially as the size of the gate decreases and the grain size (GS) dimensions become comparable to the gate length. The metal gate material is titanium nitride (TiN) that is considered as one of the most promising gate material for multi-gate transistors [39]. The TiN has experimentally observed work functions of 4.6 eV and 4.4 eV with probability of 60% and 40% formation, respectively [40]. These values are used for a random profile generation. More detailed information on the implementation of the MGG profile generation can be found in Ref. [36].

In case of the LER variability, we use an uncorrelated profile along the transport direction that introduces variation in the width of the device. In order to achieve this, we have used Fourier synthesis with Gaussian autocorrelation [41] as described in Refs. [16], [42]. The generation of the LER profiles is based on the inverse discrete Fourier transformation and the application of a Gaussian filter over a list of random phases. The characteristics of the LER profiles are based on a correlation length (CL) that is set by the width of Gaussian filter, and a root mean square (RMS) value that is set by the amplitude. Fourier spectra are modelled using the following autocorrelation function:

$$S_G(\mathbf{k}) = \sqrt[2]{\pi} \Delta^2 \Lambda e^{(-k^2 \Lambda^2/4)} \tag{1}$$

where  $\Lambda$  is the CL, and  $\Delta$  is the RMS height. The study for the LER is limited to a correlation length of 20 nm, because it was shown that it affects the devices the most [8], [16], with different RMS heights, ranging between 0.6 and 1.0 nm, that were chosen to represent the RMS values observed in experiments [11], [20].

#### III. PERFORMANCE EVALUATION AND SCALING

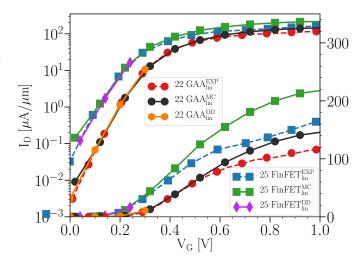

Figs. 2 and 3 show simulated  $I_D$ -V<sub>G</sub> characteristics of the 25 nm gate length FinFET [15] and the 22 nm GAA NW [18] compared with experimental data from Refs. [19] and [20], respectively. The normalised drain current (current per unit length) is obtained by dividing the drain current by the channel-covered periphery. For the FinFET the channelcovered periphery is twice the fin height plus the fin width and for the GAA NW is the circumference of the elliptic channel. The results are for both low (0.05 V) and high (1.0 V) drain biases with a channel orientation of  $\langle 110 \rangle$ , because that is the preferred orientation for manufacturing. Note that at a low drain bias of 50 mV and at gate biases greater than 0.4 V the simulated results start to diverge from the experimental data (see Fig 2). This over-estimation is related to the quantum corrections that mimic the shift of

<sup>2168-6734 (</sup>c) 2018 IEEE. Translations and content mining are permitted for academic research only. Personal use is also permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

3

$Table \ I$ Calibration parameters for the 25/10.7 nm gate length Si FinFET and the 22/10 nm gate length Si GAA NW FETs: saturation velocity (v<sub>sat</sub>), perpendicular critical electric field (E<sub>CN</sub>) and the DG electron mass in the transport direction (m<sub>x</sub>).

| L <sub>G</sub>                        | 25 nm                 |                | 10.7 nm               |                       | 22 nm                   |                         | 10 nm                   |                     |

|---------------------------------------|-----------------------|----------------|-----------------------|-----------------------|-------------------------|-------------------------|-------------------------|---------------------|

| $V_{\rm D}$                           | 0.05 V                | 1.0 V          | 0.05 V                | 0.7 V                 | 0.05 V                  | 1.0 V                   | 0.05 V                  | 0.7 V               |

| v <sub>sat</sub> [cm/s]               | $1.0 \mathrm{x} 10^7$ | $1.0 x 10^{7}$ | $1.0 \mathrm{x} 10^9$ | $1.0 \mathrm{x} 10^9$ | $1.0 \mathrm{x} 10^9$   | $1.0 \mathrm{x} 10^9$   | $1.0 \mathrm{x} 10^9$   | $1.0 \times 10^9$   |

| E <sub>CN</sub> [cm <sup>2</sup> /Vs] | $6.5 \mathrm{x} 10^4$ | $6.5 x 10^4$   | $1.0 \mathrm{x} 10^9$ | $5.0 \mathrm{x} 10^4$ | $4.0 \mathrm{x} 10^{6}$ | $1.3 \mathrm{x} 10^{5}$ | $1.0 \mathrm{x} 10^{7}$ | $2.5 \times 10^{5}$ |

| $m_x [m_0]$                           | 0.32                  | 0.32           | 0.32                  | 0.25                  | 0.4                     | 0.32                    | 0.4                     | 0.25                |

#### Table II

DEVICE DIMENSIONS AND PARAMETERS: SUPPLY VOLTAGE ( $V_{DD}$ ), PHYSICAL GATE LENGTH ( $L_G$ ), PHYSICAL SOURCE/DRAIN LENGTH ( $L_{S/D}$ ), CHANNEL WIDTH/HEIGHT ( $W_{ch}$ ,  $H_{ch}$ ), EFFECTIVE OXIDE THICKNESS (EOT), THE STANDARD DEVIATION FOR GAUSSIAN DOPING IN THE SOURCE/DRAIN ( $\sigma_x$ ), DOPING CONCENTRATIONS FOR CHANNEL ( $N_{ch}$ ), SOURCE/DRAIN ( $N_{S/D}$ ) REGIONS AND EFFECTIVE PERIMETER OF THE GATE FOR THE SIMULATED MULTI-GATE SI TRANSISTORS.

| Symbol                                             | Fir              | ıFET     | GAA NW |       |  |

|----------------------------------------------------|------------------|----------|--------|-------|--|

| Symbol                                             | $25 \mathrm{nm}$ | 10.7  nm | 22  nm | 10 nm |  |

| V <sub>DD,lin</sub> [V]                            | 0.05             | 0.05     | 0.05   | 0.05  |  |

| V <sub>DD,sat</sub> [V]                            | 1.0              | 0.7      | 1.0    | 0.7   |  |

| L <sub>G</sub> [nm]                                | 25               | 10.7     | 22     | 10    |  |

| $L_{S/D}$ [nm]                                     | 25               | 10.7     | 30.8   | 14    |  |

| W <sub>CH</sub> [nm]                               | 12               | 5.8      | 11.3   | 5.7   |  |

| H <sub>CH</sub> [nm]                               | 30               | 15       | 14.22  | 7.17  |  |

| EOT [nm]                                           | 1.12             | 0.62     | 1.5    | 0.8   |  |

| $\sigma_x$ [nm]                                    | 8.07             | 3.45     | 7.1    | 3.23  |  |

| $N_{CH} \ [cm^{-3}] \ (\times 10^{15})$            | 1                | 1        | 1      | 1     |  |

| $N_{S/D}$ [cm <sup>-3</sup> ] (×10 <sup>20</sup> ) | 1                | 1        | 0.5    | 0.5   |  |

| Perimeter [nm]                                     | 72               | 35.8     | 40.21  | 20.29 |  |

the lowest bound state with respect to the conduction band edge [15]. At low drain bias, the weak quantum confinement caused by the dimensions of the fin results in energy levels that are closely placed together. Nonetheless, as the gate bias increases quantum wells will emerge at the sidewalls of the devices, inducing a strong confinement and a separation of the energy levels. Since the transport happens in the sub-bands our simulator is not able to properly capture this because it only includes the confinement through an effective quantum potential. Note that, for this reason, the results at a low drain bias from the MC simulations are not used for any of the performance comparisons or variability studies. However, at a high drain bias, the 3D MC simulations for both devices were able to accurately reproduce the experimental results without any need for post-processing of access resistance or a change in any of material bulk parameters [43]. This is because for larger drain biases, the quantum confinement is reduced and the energy of electrons is larger. Therefore, the transport occurs where the sub-bands are energetically closely packed together and becomes quasi-3D. Note also that the 3D DD simulations have an excellent match in the sub-threshold region at both low and high drain biases with the experimental results. Therefore, we are confident that the DD simulations can very well reproduce transport in the sub-threshold region.

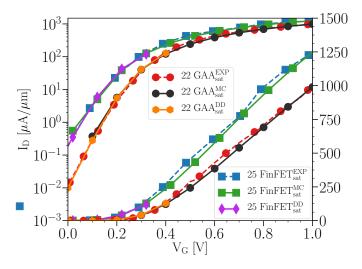

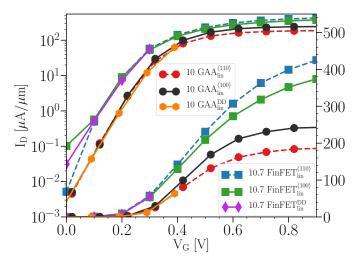

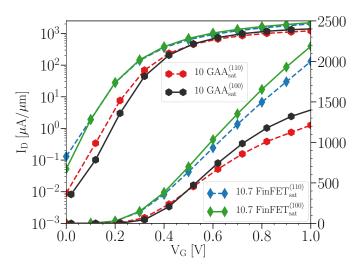

Figs. 4 and 5 show  $I_D$ -V<sub>G</sub> characteristics for the 10.7 nm FinFET and 10 nm GAA NW at both low (0.05 V) and high

Figure 2. Experimental (EXP)  $I_D$ - $V_G$  characteristics at  $V_D$  of 0.05 V (lin) for the 25 nm gate length FinFET [19], the 22 nm GAA NW [20], and the related 3D drift-diffusion (DD) and Monte Carlo (MC) simulations. The experimental and MC simulated devices have a channel orientation of  $\langle 110 \rangle$ .

Figure 3. Experimental (EXP)  $I_D$ - $V_G$  characteristics at  $V_D$  of 1.0 V (sat) for the 25 nm gate length FinFET [19], the 22 nm GAA NW [20], and the related 3D drift-diffusion (DD) and Monte Carlo (MC) simulations. The experimental and MC simulated devices have a channel orientation of  $\langle 110 \rangle$ .

(0.7 V) drain biases with channel orientations of  $\langle 100 \rangle$  and  $\langle 110 \rangle$ .

Figure of merits for two multi-gate transistor architectures are summarised in Table III where the model refers to the simulation method. The extraction of the OFF-current ( $I_{OFF}$ )

Figure 4. Simulated  $I_D\text{-}V_G$  characteristics for the 10.7 nm gate length FinFET [17] and the 10 nm gate length GAA NW [18] at  $V_D=0.05$  V (lin) and with channel orientations of  $\langle 100\rangle$  and  $\langle 110\rangle$ .

Figure 5. Simulated  $I_D$ -V<sub>G</sub> characteristics for the 10.7 nm gate length FinFET [17] and the 10 nm gate length GAA NW [18] at V<sub>D</sub> = 0.7 V (sat) and with channel crystal orientations of  $\langle 100 \rangle$  and  $\langle 110 \rangle$ .

is done at a gate bias (V\_G) of 0.0 V and the drive current (I\_{ON}) at V\_G = V\_D + V\_T.

After scaling the 25 nm gate length FinFET to 10.7 nm, we have found that the V<sub>T</sub> and sub-threshold slope (SS) experience a minimal change which suggests a good control from the gate, however, the DIBL is increased by 28%. Both the OFF- and ON-currents are improved for the 10.7 nm gate length FinFET. The I<sub>OFF</sub> is reduced by 21% and the I<sub>ON</sub> is increased by 9% and 16% for the  $\langle 100 \rangle$  and  $\langle 110 \rangle$  channel orientations, respectively. The reduction of the OFF- current also leads to a 45% reduced power consumption for the 10.7 nm FinFET. Finally, the ON/OFF ratio is increased by about 37% and 46% for the  $\langle 100 \rangle$  and  $\langle 110 \rangle$  channel orientations, respectively, when the FinFET is scaled down.

Following a similar comparison of the GAA NW, we found that the  $V_T$  and SS have also a small change and the DIBL increases by 37% for the 10 nm gate length FET. In case of the

$I_{\rm OFF}$ , we observed a 10% reduction of the current which leads to a 37% reduction of the static power for the 10 nm GAA NW. The  $I_{\rm ON}$  is decreased by 14% and 12% for the  $\langle 100 \rangle$  and  $\langle 110 \rangle$  channel orientations, respectively. Therefore, the comparison of the ON/OFF ratios shows some deterioration for the 10 nm GAA NW when compared to the larger gate length device. The ratio deterioration of the 10 nm GAA NW is caused by the decrease in the ON-current even though the  $I_{\rm OFF}$  improves. The saturation of the  $I_{\rm ON}$ , seen in Fig. 5, is related to the maximum doping level (see Table II), thus an increased doping would eliminate the saturation and lead to an increased drive current for the 10 nm gate length GAA NW.

4

We observed that the 25 and 10.7 nm gate length FinFETs are outperformed by the GAA NWs (22 and 10 nm gate lengths) for the sub-threshold region figures of merit. In case of the SS, the GAA NW has a 9% lower value and more than an order of magnitude smaller OFF-current which also results in over an order of magnitude lower static power. This is achieved due to the better electrostatic control by the surrounding gate of the NW. Finally, notice that the larger V<sub>T</sub> of the GAA NW is related to the thicker EOT (see Table II).

With respect to the ON-region, the FinFET outperforms the GAA NW for both gate lengths. In case of the 25 nm FinFET, the  $I_{\rm ON}$  is 20% greater than that of the 22 nm GAA NW for a channel orientation of  $\langle 110 \rangle$ , which increases to 58% for the 10.7/10 nm gate length devices. However, the ON/OFF ratios of the GAA NW for the 10 nm gate length are still more than an order of magnitude larger than those of the 10.7 nm FinFET devices.

## IV. MGG AND LER VARIABILITY IN THE SUB-THRESHOLD REGION

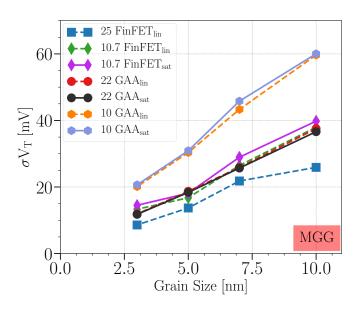

In this section, we analyse the effect of two major sources of variability, MGG and LER, in the sub-threshold region. To obtain accurate prediction of the variability, we have generated 300 random profiles for each GS and RMS height. Fig. 6 shows the standard deviation ( $\sigma$ ) of the threshold voltage (V<sub>T</sub>) due to MGG variability for the FinFET and GAA NW. For both architectures, the drain bias has a negligible effect on the  $\sigma$ V<sub>T</sub> and also, as expected, the variability decreases when the grain size is reduced.

The scaling of the FinFET from the 25 nm to the 10.7 nm gate length increases the MGG variations by 47% for the 10 nm GS. Similarly,  $\sigma V_T$  is increased by about 59% at a GS of 10 nm when the GAA NW is scaled down. Note that  $\sigma V_T$  is more sensitive to the change of the GS for the 10 nm gate length GAA NW (a slope of 5.6 mV/nm) than for the 22 nm gate length (a slope of 3.7 mV/nm). Generally, the larger the gate, the lower the slope and the magnitude of the MGG variability.

Overall, the linear behaviour that is observed for the  $\sigma V_T$  as a function GS is also demonstrated in [9]. However, as the GS becomes comparable to the gate area, this linear trend is likely to change. Moreover, the FinFET is more resilient to the MGG variability in the sub-threshold region than the GAA NW, at both gate lengths. This is due to the fact that the FinFET, unlike the GAA NW, is controlled by the sidewall gates, which leads to less variability of the V<sub>T</sub>, that was

<sup>2168-6734 (</sup>c) 2018 IEEE. Translations and content mining are permitted for academic research only. Personal use is also permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/JEDS.2018.2804383, IEEE Journal of the Electron Devices Society

5

Table III FIGURE OF MERITS FOR FINFET AND GAA NW ARCHITECTURES: THRESHOLD VOLTAGE (V<sub>T</sub>), SUB-THRESHOLD SLOPE (SS), DRAIN-INDUCED BARRIER LOWERING (DIBL), OFF-CURRENT ( $I_{OFF}$ ), ON-CURRENT ( $I_{ON}$ ), STATIC POWER ( $P_{Static}$ ) and the ON/OFF ratio ( $I_{ON}/I_{OFF}$ ).

|       |                                                                             | Fii   | ıFET    | GAA NW |       |  |

|-------|-----------------------------------------------------------------------------|-------|---------|--------|-------|--|

| Model | FoM                                                                         | 25 nm | 10.7 nm | 22 nm  | 10 nm |  |

| MC    | $V_{\rm Tsat}$ [V]                                                          | 0.24  | 0.24    | 0.26   | 0.26  |  |

| DD    | SS <sub>sat</sub> [mV/dec]                                                  | 77    | 76      | 70     | 68    |  |

| DD    | DIBL [mV/V]                                                                 | 60    | 77      | 57     | 78    |  |

| DD    | $I_{\rm OFFsat}$ [nA/ $\mu$ m]                                              | 188   | 149     | 9.9    | 8.9   |  |

| MC    | $\mathrm{I_{ON}^{\langle 100  angle}}$ [ $\mu$ A/ $\mu$ m]                  | 1860  | 2030    | 1590   | 1360  |  |

| MC    | $\mathrm{I_{ON}^{\langle 110 \rangle}}$ [ $\mu \mathrm{A}/\mu \mathrm{m}$ ] | 1600  | 1850    | 1330   | 1170  |  |

| MC/DD | $P_{\rm Static} \; [\mu W/\mu m]$                                           | 188   | 104     | 9.9    | 6.2   |  |

| MC/DD | $\frac{I_{\rm ON}}{I_{\rm OFF}} (\times 10^4) \langle 100 \rangle$          | 0.99  | 1.36    | 16     | 15.3  |  |

| MC/DD | $\frac{I_{\rm ON}}{I_{\rm OFF}} (\times 10^4) \langle 110 \rangle$          | 0.85  | 1.24    | 13.4   | 13.1  |  |

demonstrated in Ref. [44]. The 10 nm FinFET has a 36% smaller V<sub>T</sub> variability with a GS of 10 nm than the NW at a low drain bias.

Figure 6. Comparison of the standard deviation ( $\sigma$ ) of V<sub>T</sub> induced by the MGG variability for the 25 nm [42] and 10.7 nm [8] gate length FinFETs, and for the 22 and 10 nm gate length GAA NWs. The respective drain biases are shown in Table II. The subscript 'lin' refers to a low and 'sat' refers to a high drain bias, respectively.

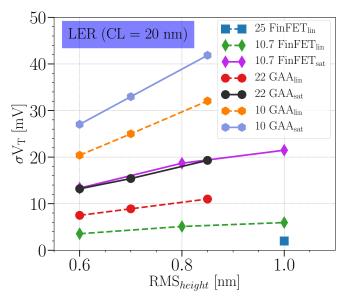

Fig. 7 shows the  $V_T$  variability due to the LER. The 25 nm FinFET has a three times lower  $\sigma V_T$  than the scaled 10.7 nm FinFET (for the 25 nm FinFET, the only available data for comparison is at an RMS of 1 nm). Increasing the drain bias leads to an increasing  $V_T$  variability unlike in case of the MGG. The scaling of the GAA NW from the 22 nm gate length to the 10 nm device leads to a ~ 2.2 times greater  $\sigma V_T$  for all the analysed RMS heights. When comparing both architectures, the 10.7 nm gate length FinFET ( $V_D = 0.7$  V) has a two times lower  $\sigma V_T$  than the GAA NW (0.6 nm RMS height). Note that in case of both FETs the electron density, which exhibits complete volume inversion, is

quantum-mechanically confined into the middle of the channel. However in case of the GAA NW the confinement is much stronger than in the FinFET because of its smaller channel height. Therefore the device with a greater confinement will be more strongly affected by imperfections (induced by the LER) in the confining potential. Note that the slope for the nanowire transistor (59.3 mV/nm) is steeper than for the FinFET (20.3 mV/nm). This suggests that control of the LER parameters during fabrication processes is more crucial for the GAA NW than for the FinFET, which has been also shown (see Fig. 6) for the MGG. The  $V_T$  variability is dominated by the MGG for both device structures and gate lengths. However, at the smallest studied GS and RMS height, the MGG and LER have a comparable effect.

Figure 7. Compares the standard deviation ( $\sigma$ ) of the V<sub>T</sub> induced by the LER variability, for the 25 nm [42] and 10.7 nm [8] gate length FinFETs, and the 22 and 10 nm [18] gate length GAA NWs.

Table IV compares how much the MGG and LER variability sources affect the multi-gate devices (limited to a high drain

<sup>2168-6734 (</sup>c) 2018 IEEE. Translations and content mining are permitted for academic research only. Personal use is also permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

6

bias, sat) with respect to the nominal values. These relative values (in %) are calculated as:

$$\frac{\sigma V_{\rm T}}{({\rm nominal}\ V_{\rm T}/100)},\tag{2}$$

where the corresponding nominal values are taken from Table III. Table IV shows that the MGG affects both the FinFET and GAA NW variability more than the LER. Moreover, the FinFET is more resilient to the MGG and LER variability sources than the GAA NW.

Table IV Comparison of the standard deviation against the nominal values of the 10.7 nm gate length FinFET and the 10 nm GAA NW FET.

|                                   | MGG (C | GS [nm]) | LER (RMS <sub>height</sub> [nm]) |      |  |

|-----------------------------------|--------|----------|----------------------------------|------|--|

|                                   | 5      | 10       | 0.6                              | 0.8  |  |

| OFF-region                        |        |          |                                  |      |  |

| 10.7 FinFET <sub>sat</sub>        | 7.5%   | 16.6%    | 5.5%                             | 9%   |  |

| 10 GAA <sub>sat</sub>             | 11.9%  | 23.1%    | 10.4%                            | 15%  |  |

| ON-region                         |        |          |                                  |      |  |

| 10.7 FinFET $\langle 110 \rangle$ | 3.3%   | 6.2%     | 2.2%                             | 3.4% |  |

| 10.7 FinFET $\langle 100 \rangle$ | 3.4%   | 6.1%     | 2.5%                             | 4.6% |  |

| 10 GAA $\langle 110\rangle$       | 3.6%   | 5.7%     | 4.6%                             | 9.1% |  |

| 10 GAA $\langle 100 \rangle$      | 3.5%   | 5.6%     | 4.3%                             | 8%   |  |

#### V. MGG AND LER VARIABILITY IN THE ON-REGION

In this section, we investigate the ON-region variability of the devices affected by MGG and LER. The MC approach described in Section II was used for these simulations. Due to the time requirement of this method we have limited the number of simulations to a 100 for each GS and RMS height.

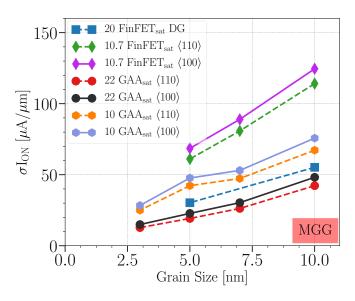

Fig. 8 shows the MGG ON-current variability ( $\sigma I_{ON}$ ) at a high drain bias, for the 20 nm gate length FinFET from Ref. [45], the 10.7 nm gate length FinFET, and the 22/10 nm gate length GAA NWs. Note that the on current variability study in Ref. [45] was carried out using DD simulations with DG quantum corrections. Here, we present these results because there are no known study, to our best knowledge, on similar devices in the ON-region using ensemble MC simulations which has a predictive power.

Analysing the results for the  $\langle 100 \rangle$  channel orientation, the scaling of the 20 nm gate length FinFET to 10.7 nm resulted in twice as large  $\sigma I_{ON}$ , for all grain sizes. The scaling of the 22 nm gate length GAA NW to 10 nm gate length led to around 1.3 times higher  $\sigma I_{ON}$  for all grain sizes. When comparing both architectures, the  $\sigma I_{ON}$  for the 10 nm gate length FinFET is 64/44% higher than that of the equivalent GAA NW at a GS of 10/5 nm. This trend is opposite to the observations in the sub-threshold region where the MGG resulted in a larger variability for the GAA NW. Note that the GAA NW has a smaller channel cross-section than the FinFET which results in a larger confinement in the NW channel, thus the electrons are on average closer to the interface in the FinFET. Therefore, the MGG has a greater effect on the

$\sigma I_{ON}$  for the FinFET architecture. With respect to the channel orientation, the industry preferred  $\langle 110 \rangle$  channel orientation is less affected by the MGG than the  $\langle 100 \rangle$ .

Figure 8. The standard deviation ( $\sigma$ ) of I<sub>ON</sub> induced by the MGG variability, for the 20 nm [45] and the 10.7 nm [8] gate length FinFETs, and for the 22 and 10 nm gate length GAA NW FETs.

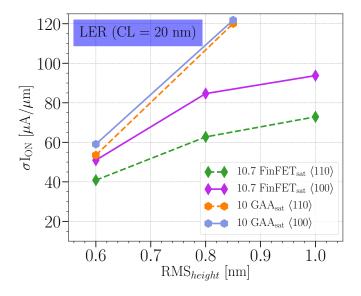

In Fig. 9, we show the  $I_{\rm ON}$  variability due to LER for the 10.7 nm FinFET and 10 nm GAA NW architectures. The study is limited to the scaled devices because there are no published data in the on-region for the larger gate length devices affected by LER. Comparing both architectures for the  $\langle 100 \rangle / \langle 110 \rangle$  channel orientations, the FinFET resulted in a 23/39.3% lower  $\sigma I_{ON}$  than the GAA NW at an RMS height of 0.8 nm. Reduction of the RMS height to 0.6 nm results in a comparable ON-current variability between the FinFET and the GAA NW for the  $\langle 100 \rangle$  channel orientation. However, in case of the  $\langle 110 \rangle$ , at an RMS height of 0.6 nm, the GAA NW has a  $\sigma I_{ON}$  31% larger than the FinFET device. The stronger LER effect for the GAA NW is related to the smaller channel height which causes a stronger confinement than in case of the FinFET. As aforementioned for the sub-threshold region variability, devices with a greater confinement will be more strongly affected by LER deformations. The high degradation observed in the ON-current due to the LER could be a limiting factor for the scaling of the deep nano-scaled GAA NW transistors if the parameters (e.g. RMS height) are not optimised.

Comparing the MGG and LER influence for the ON-region, we found that the FinFET is affected more by the MGG variability source that is shown in Table IV. However, the LER in the GAA NW has a stronger effect on the device than the MGG, which is related to the cross-section variation of the channel due to the LER.

#### VI. CONCLUSION

A combined 3D quantum-corrected FE DD and MC simulation study of the performance, scalability and variability (MGG and LER) is performed for 25/10.7 nm

<sup>2168-6734 (</sup>c) 2018 IEEE. Translations and content mining are permitted for academic research only. Personal use is also permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

Figure 9. The standard deviation ( $\sigma$ ) of I<sub>ON</sub> induced by the LER variability, for the 10.7 nm [8] gate length FinFET, and the 10 nm gate length GAA NW FET.

gate length Si FinFETs and 22/10 nm gate length Si GAA NW FETs. The main conclusions can be summarised as follows.

#### Performance:

- In the OFF-region, the FinFET devices have 9% larger SS values and over an order of magnitude larger OFF-currents that those of the equivalent GAA NW FETs.

- In the ON-region, the 25/10.7 nm gate length FinFETs deliver 20/58% larger ON-currents than the equivalent 22/10 nm gate length GAA NW.

- The ON/OFF ratio of the FinFETs  $(1 \times 10^4 \text{ when } L_G = 10.7 \text{ nm})$  are more than an order of magnitude lower than those of the GAA NWs  $(13 \times 10^4 \text{ when } L_G = 10 \text{ nm})$ .

#### Scalability:

- When the FinFET gate length is scaled from 25 to 10.7 nm: i) the OFF-current is reduced by 21%, ii) the ON-current is increased by 9/16% for the  $\langle 100 \rangle / \langle 110 \rangle$  channel orientations and iii) the ON/OFF ratio is increased by 37/46% for the  $\langle 100 \rangle / \langle 110 \rangle$  channel orientations.

- When the GAA NW gate length is scaled from 22 to 10 nm: i) the OFF-current is reduced by 10%, ii) the ON-current is also reduced by 14/12% for the  $\langle 100 \rangle / \langle 110 \rangle$  channel orientations and iii) the ON/OFF ratio is slightly deteriorated.

#### Variability:

- The FinFETs are more resilient to the MGG and LER variability in the sub-threshold region than the GAA NW FETs.

- The control of the LER parameters (CL and RMS) during the fabrication process is more crucial for GAA NWs than for FinFETs.

- The FinFETs are more affected by the MGG variability in the ON-region than the GAA NWs.  $\sigma I_{ON}$  for the 10 nm

gate length FinFET is 64/44% higher than that of the equivalent GAA NW at a GS of 10/5 nm.

- The FinFETs are more resistant to the LER variability in the ON-region than the GAA NWs.

- The industry preferred  $\langle 110 \rangle$  channel orientation is more resilient to the MGG and LER variability sources in the FinFET and GAA NW FETs than in the  $\langle 100 \rangle$  orientation transistors.

#### ACKNOWLEDGEMENT

This research was supported in part by the Spanish Government under the projects TIN2013-41129-P and TIN2016-76373-P, by Xunta de Galicia and FEDER funds (GRC 2014/008) by the Consellería de Cultura, Educación e Ordenación Universitaria (accreditation 2016-2019, ED431G/08) and from the Spanish Ministry of Economy and Competitiveness and FEDER funds (TEC2014-59402-JIN). The work of G. Indalecio was supported by the Programa de Axudas Etapa Posdoutoral da Xunta de Galicia under grant number 2017/077. We would also like to thank Centro de Supercomputacin de Galicia (CESGA) for the computer resources provided.

#### REFERENCES

- [1] S. D. Kim, M. Guillorn, I. Lauer, P. Oldiges, T. Hook, and M. H. Na, "Performance Trade-offs in FinFET and Gate-All-Around Device Architectures for 7nm-node and Beyond," in *IEEE SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S)*, Oct. 2015, pp. 1–3.

- [2] D. Bhattacharya and N. K. Jha, "FinFETs: From Devices to Architectures," Advances in Electronics, vol. 2014, p. 21, 2014.

- [3] J.-P. Colinge, *FinFETs and Other Multi-Gate Transistors*. New York, NY, USA: Springer-Verlag, 2008.

- [4] Y. Liu, T. Matsukawa, K. Endo, M. Masahara, K. Ishii, S. i. O'uchi, H. Yamauchi, J. Tsukada, Y. Ishikawa, and E. Suzuki, "Advanced Fin-FET CMOS Technology: TiN-Gate, Fin-Height Control and Asymmetric Gate Insulator Thickness 4T-FinFETs," in *Proc. IEEE Electron Devices Meeting (IEDM)*, Dec. 2006, pp. 1–4.

- [5] J.-S. Yoon, T. Rim, J. Kim, M. Meyyappan, C.-K. Baek, and Y.-H. Jeong, "Vertical gate-all-around junctionless nanowire transistors with asymmetric diameters and underlap lengths," *J. Appl. Phys.*, vol. 105, no. 10, p. 102105, 2014.

- [6] Y. S. Wu and P. Su, "Sensitivity of Gate-All-Around Nanowire MOS-FETs to Process Variations – A Comparison With Multigate MOSFETs," *IEEE Trans. on Electron Devices*, vol. 55, no. 11, pp. 3042–3047, Nov. 2008.

- [7] T. Matsukawa, Y. Liu, W. Mizubayashi, J. Tsukada, H. Yamauchi, K. Endo, Y. Ishikawa, S. i. O'uchi, H. Ota, S. Migita, Y. Morita, and M. Masahara, "Suppressing Vt and Gm variability of FinFETs using amorphous metal gates for 14 nm and beyond," in *Proc. IEEE Electron Devices Meeting (IEDM)*, Dec. 2012, pp. 8.2.1–8.2.4.

- [8] N. Seoane, G. Indalecio, M. Aldegunde, D. Nagy, M. A. Elmessary, A. J. García-Loureiro, and K. Kalna, "Comparison of Fin-Edge Roughness and Metal Grain Work Function Variability in InGaAs and Si FinFETs," *IEEE Trans. on Electron Devices*, vol. 63, no. 3, pp. 1209–1216, Mar. 2016.

- [9] X. Wang, A. R. Brown, B. Cheng, and A. Asenov, "Statistical variability and reliability in nanoscale FinFETs," in *Proc. IEEE Electron Devices Meeting (IEDM)*, Dec. 2011, pp. 5.4.1–5.4.4.

- [10] R. Wang, J. Zhuge, R. Huang, T. Yu, J. Zou, D. W. Kim, D. Park, and Y. Wang, "Investigation on Variability in Metal-Gate Si Nanowire MOSFETs: Analysis of Variation Sources and Experimental Characterization," *IEEE Trans. on Electron Devices*, vol. 58, no. 8, pp. 2317–2325, Aug. 2011.

2168-6734 (c) 2018 IEEE. Translations and content mining are permitted for academic research only. Personal use is also permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications/rights/index.html for more information.

- [11] S. Bangsaruntip, G. M. Cohen, A. Majumdar, Y. Zhang, S. U. Engelmann, N. C. M. Fuller, L. M. Gignac, S. Mittal, J. S. Newbury, M. Guillorn, T. Barwicz, L. Sekaric, M. M. Frank, and J. W. Sleight, "High performance and highly uniform gate-all-around silicon nanowire MOSFETs with wire size dependent scaling," in *Proc. IEEE Electron Devices Meeting (IEDM)*, Dec. 2009, pp. 1–4.

- [12] T. Linton, M. Chandhok, B. J. Rice, and G. Schrom, "Determination of the line edge roughness specification for 34 nm devices," in *Proc. IEEE Electron Devices Meeting (IEDM)*, Dec. 2002, pp. 303–306.

- [13] S.-D. Kim, H. Wada, and J. C. S. Woo, "TCAD-based statistical analysis and modeling of gate line-edge roughness effect on nanoscale MOS transistor performance and scaling," *IEEE Trans. Semicond. Manuf.*, vol. 17, no. 2, pp. 192–200, May 2004.

- [14] P. Lugli, "The Monte Carlo method for semiconductor device and process modeling," *IEEE Trans. Comput.-Aided Design Integr. Circuits Syst.*, vol. 9, no. 11, pp. 1164–1176, Nov. 1990.

- [15] M. Aldegunde, A. J. García-Loureiro, and K. Kalna, "3D Finite Element Monte Carlo Simulations of Multigate Nanoscale Transistors," *IEEE Trans. on Electron Devices*, vol. 60, no. 5, pp. 1561–1567, May 2013.

- [16] N. Seoane, G. Indalecio, E. Comesana, M. Aldegunde, A. J. García-Loureiro, and K. Kalna, "Random Dopant, Line-Edge Roughness, and Gate Workfunction Variability in a Nano InGaAs FinFET," *IEEE Trans.* on Electron Devices, vol. 61, no. 2, pp. 466–472, Feb. 2014.

- [17] J. Lindberg, M. Aldegunde, D. Nagy, W. G. Dettmer, K. Kalna, A. J. García-Loureiro, and D. Perić, "Quantum Corrections Based on the 2-D Schrödinger Equation for 3-D Finite Element Monte Carlo Simulations of Nanoscaled FinFETs," *IEEE Trans. on Electron Devices*, vol. 61, no. 2, pp. 423–429, Feb. 2014.

- [18] M. A. Elmessary, D. Nagy, M. Aldegunde, N. Seoane, G. Indalecio, J. Lindberg, W. Dettmer, D. Peri, A. J. Garca-Loureiro, and K. Kalna, "Scaling/LER study of Si GAA nanowire FET using 3D finite element Monte Carlo simulations," *Solid-State Electron.*, vol. 128, no. Supplement C, pp. 17 – 24, 2017, extended papers selected from EUROSOI-ULIS 2016.

- [19] V. S. Basker, T. Standaert, H. Kawasaki, C. C. Yeh, K. Maitra, T. Yamashita, J. Faltermeier, H. Adhikari, H. Jagannathan, J. Wang, H. Sunamura, S. Kanakasabapathy, S. Schmitz, J. Cummings, A. Inada, C. H. Lin, P. Kulkarni, Y. Zhu, J. Kuss, T. Yamamoto, A. Kumar, J. Wahl, A. Yagishita, L. F. Edge, R. H. Kim, E. Mclellan, S. J. Holmes, R. C. Johnson, T. Levin, J. Demarest, M. Hane, M. Takayanagi, M. Colburn, V. K. Paruchuri, R. J. Miller, H. Bu, B. Doris, D. McHerron, E. Leobandung, and J. O'Neill, "A 0.063 μm<sup>2</sup> FinFET SRAM cell demonstration with conventional lithography using a novel integration scheme with aggressively scaled fin and gate pitch," in *Proc. VLSI Technol. (VLSIT) Symp*, Jun. 2010, pp. 19–20.

- [20] S. Bangsaruntip, K. Balakrishnan, S. L. Cheng, J. Chang, M. Brink, I. Lauer, R. L. Bruce, S. U. Engelmann, A. Pyzyna, G. M. Cohen, L. M. Gignac, C. M. Breslin, J. S. Newbury, D. P. Klaus, A. Majumdar, J. W. Sleight, and M. A. Guillorn, "Density scaling with gate-all-around silicon nanowire MOSFETs for the 10 nm node and beyond," in *Proc. IEEE Electron Devices Meeting (IEDM)*, Dec. 2013, pp. 20.2.1–20.2.4.

- [21] N. Collaert. (2017) Device architectures for the 5 nm technology node and beyond. [Online]. Available: http://www.semicontaiwan.org/en/icforum-0

- [22] ITRS. (2016) International Technology Roadmap for Semiconductors. [Online]. Available: http://www.itrs2.net/

- [23] M. Stadele, R. J. Luyken, M. Roosz, M. Specht, W. Rosner, L. Dreeskornfeld, J. Hartwich, F. Hofmann, J. Kretz, E. Landgraf, and L. Risch, "A comprehensive study of corner effects in tri-gate transistors," in *Proc. European Solid-State Device Research Conference (ESSDERC)*, Sept. 2004, pp. 165–168.

- [24] K. Tomizawa, Numerical Simulation of Submicron Semiconductor Devices, ser. Artech House materials science library. Artech House, 1993.

- [25] C. Jacoboni and P. Lugli, *The Monte Carlo Method for Semiconductor Device Simulation*, ser. Computational Microelectronics. Springer Vienna, 2012.

- [26] B. K. Ridley, "Reconciliation of the Conwell-Weisskopf and Brooks-Herring formulae for charged-impurity scattering in semiconductors: Third-body interference," *J. Phys. C: Solid State Physics*, vol. 10, no. 10, p. 1589, 1977.

- [27] T. G. V. de Roer and F. P. Widdershoven, "Ionized impurity scattering in Monte Carlo calculations," *J. Appl. Phys.*, vol. 59, no. 3, pp. 813–815, 1986.

- [28] D. Ferry, Semiconductor Transport. Taylor & Francis, 2000.

- [29] A. Islam and K. Kalna, "Monte Carlo simulations of mobility in doped GaAs using self-consistent FermiDirac statistics," *Semicond Sci and Tech.*, vol. 26, no. 5, p. 039501, 2012.

- [30] A. J. García-Loureiro, N. Seoane, M. Aldegunde, R. Valin, A. Asenov, A. Martínez, and K. Kalna, "Implementation of the Density Gradient Quantum Corrections for 3-D Simulations of Multigate Nanoscaled Transistors," *IEEE Trans. Comput.-Aided Design Integr. Circuits Syst.*, vol. 30, no. 6, pp. 841–851, Jun. 2011.

- [31] M. Aldegunde, A. Martinez, and J. R. Barker, "Study of Discrete Doping-Induced Variability in Junctionless Nanowire MOSFETs Using Dissipative Quantum Transport Simulations," *IEEE Electron Device Lett.*, vol. 33, no. 2, pp. 194–196, Feb. 2012.

- [32] E. Gnani, A. Gnudi, S. Reggiani, and G. Baccarani, "Quasi-Ballistic Transport in Nanowire Field-Effect Transistors," *IEEE Trans. on Electron Devices*, vol. 55, no. 11, pp. 2918–2930, Nov. 2008.

- [33] D. M. Caughey and R. E. Thomas, "Carrier Mobilities in Silicon Empirically Related to Doping and Field," in *Proc. IEEE*, vol. 55, no. 12, Dec. 1967, pp. 2192–2193.

- [34] K. Yamaguchi, "Field-dependent mobility model for two-dimensional numerical analysis of MOSFET's," *IEEE Trans. on Electron Devices*, vol. 26, no. 7, pp. 1068–1074, Jul. 1979.

- [35] M. A. Elmessary, D. Nagy, M. Aldegunde, J. Lindberg, W. G. Dettmer, D. Perić, A. J. García-Loureiro, and K. Kalna, "Anisotropic Quantum Corrections for 3-D Finite-Element Monte Carlo Simulations of Nanoscale Multigate Transistors," *IEEE Trans. on Electron Devices*, vol. 63, no. 3, pp. 933–939, Mar. 2016.

- [36] G. Indalecio, A. J. García-Loureiro, N. S. Iglesias, and K. Kalna, "Study of Metal-Gate Work-Function Variation Using Voronoi Cells: Comparison of Rayleigh and Gamma Distributions," *IEEE Trans. on Electron Devices*, vol. 63, no. 6, pp. 2625–2628, Jun. 2016.

- [37] X. Wang, A. R. Brown, N. Idris, S. Markov, G. Roy, and A. Asenov, "Statistical Threshold-Voltage Variability in Scaled Decananometer Bulk HKMG MOSFETs: A Full-Scale 3-D Simulation Scaling Study," *IEEE Trans. on Electron Devices*, vol. 58, no. 8, pp. 2293–2301, Aug. 2011.

- [38] H. Nam and C. Shin, "Comparative study in work-function variation: Gaussian vs. Rayleigh distribution for grain size," *IEICE Electronics Express*, vol. 10, no. 9, pp. 20130109–20130109, 2013.

- [39] T. Kamei, Y. Liu, K. Endo, S. O'uchi, J. Tsukada, H. Yamauchi, Y. Ishikawa, T. Hayashida, T. Matsukawa, K. Sakamoto, A. Ogura, and M. Masahara, "Experimental Study of Physical-Vapor-Deposited Titanium Nitride Gate with An n + -Polycrystalline Silicon Capping Layer and Its Application to 20 nm Fin-Type Double-Gate MetalOxideSemiconductor Field-Effect Transistors," JPN J. Appl. Phys., vol. 50, no. 4S, p. 04DC14, 2011.

- [40] H. F. Dadgour, K. Endo, V. K. De, and K. Banerjee, "Grain-Orientation Induced Work Function Variation in Nanoscale Metal-Gate Transistors– Part I: Modeling, Analysis, and Experimental Validation," *IEEE Trans.* on Electron Devices, vol. 57, no. 10, pp. 2504–2514, Oct. 2010.

- [41] A. Asenov, S. Kaya, and A. R. Brown, "Intrinsic parameter fluctuations in decananometer MOSFETs introduced by gate line edge roughness," *IEEE Trans. on Electron Devices*, vol. 50, no. 5, pp. 1254–1260, May 2003.

- [42] G. Indalecio, M. Aldegunde, N. Seoane, K. Kalna, and A. J. García-Loureiro, "Statistical study of the influence of LER and MGG in SOI MOSFET," *Semicond Sci and Tech.*, vol. 29, no. 4, p. 045005, 2014.

- [43] A. Islam, B. Benbakhti, and K. Kalna, "Monte Carlo Study of Ultimate Channel Scaling in Si and In<sub>0.3</sub>Ga<sub>0.7</sub>As Bulk MOSFETs," *IEEE Trans. Nanotech.*, vol. 10, no. 6, pp. 1424–1432, Nov. 2011.

- [44] G. Indalecio, N. Seoane, K. Kalna, and A. J. Garca-Loureiro, "Fluctuation Sensitivity Map: A Novel Technique to Characterise and Predict Device Behaviour Under Metal Grain Work-Function Variability Effects," *IEEE Trans. on Electron Devices*, vol. 64, no. 4, pp. 1695–1701, Apr. 2017.

- [45] X. Wang, B. Cheng, A. R. Brown, C. Millar, J. B. Kuang, S. Nassif, and A. Asenov, "Interplay Between Process-Induced and Statistical Variability in 14-nm CMOS Technology Double-Gate SOI FinFETs," *IEEE Trans. on Electron Devices*, vol. 60, no. 8, pp. 2485–2492, Aug. 2013.

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/JEDS.2018.2804383, IEEE Journal of the Electron Devices Society

Swansea University 2016, respectively. He currently holds CITIUS, University tiago de Compostel

**Daniel Nagy** received the M.Res. degree in nanoscience to nanotechnology and the Ph.D. degree in electronic and electrical engineering from Swansea University, Swansea, U.K., in 2013 and 2016, respectively.

He currently holds a post-doctoral position at the CITIUS, University of Santiago de Compostela, Santiago de Compostela, Spain.

**Natalia Seoane** received the Ph.D. degree from the University of Santiago de Compostela, Santiago, Spain, in 2007.

She was a Visiting Post-Doctoral Researcher with the University of Glasgow, Glasgow, U.K., from 2007 to 2009, Edinburgh University, Edinburgh, U.K., in 2011, and Swansea University, Swansea, U.K., from 2013 to 2015. She is currently with the University of Santiago de Compostela.

**Guillermo Indalecio** received the B.S. degree in physics and the Ph.D. degree in semiconductor device simulation from the University of Santiago de Compostela, Santiago de Compostela, Spain, in 2010 and 2016, respectively.

He was a Visiting Researcher with the University of Swansea, Swansea, U.K., in 2015. His current research interests include electronic devices simulation with focus on computational techniques and novel techniques to understand variability sources.

Antonio J. García-Loureiro received the Ph.D. degree from the University of Santiago de Compostela, Santiago de Compostela, Spain, in 1999. He is an Associated Professor with the Department

of Electronics and Computer Science, University of Santiago de Compostela. His current research interests are multidimensional simulations of nanoscale transistors and solar cells.

**Muhammad A. Elmessary** received the B.Sc. degree (Hons.) in computer and systems engineering and the M.Sc. degree in engineering physics from Mansoura University, Mansoura, Egypt, in 2004 and 2010, respectively. He received the Ph.D. degree in semiconductor device simulation from the Swansea University, Swansea, UK in 2017.

He is currently a research assistant at Swansea University, UK.

Karol Kalna received the M.Sc. (Hons.) and Ph.D. degrees from Comenius University, Bratislava, Czechoslovakia, in 1990 and 1998, respectively. He is an Associated Professor leading the Nanoelectronic Devices Computational Group, Swansea University, Swansea, U.K. He has held an EPSRC Advanced Research Fellowship and pioneered III– V MOSFETs since 2002. He has 84 peer-review papers and over 20 invited talks.