| Title                | Modelling and digital control of two-phase interleaved coupled-inductor non-isolated DC-DC converters                                                          |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Author(s)            | Barry, Brendan C.                                                                                                                                              |

| Publication date     | 2016                                                                                                                                                           |

| Original citation    | Barry, B. C. 2016. Modelling and digital control of two-phase interleaved coupled-inductor non-isolated DC-DC converters. PhD Thesis, University College Cork. |

| Type of publication  | Doctoral thesis                                                                                                                                                |

| Rights               | © 2016, Brendan C. Barry.  http://creativecommons.org/licenses/by-nc-nd/3.0/                                                                                   |

| Embargo information  | No embargo required                                                                                                                                            |

| Item downloaded from | http://hdl.handle.net/10468/5338                                                                                                                               |

Downloaded on 2018-08-23T19:24:35Z

# Modelling and Digital Control of Two-Phase Interleaved Coupled-Inductor Non-Isolated DC-DC Converters

Brendan C. Barry

A thesis presented to the National University of Ireland for the degree of Doctor of Philosophy

September 2016

Supervised by Dr. John G. Hayes and Dr. Gordon Lightbody

Industrial Mentor: Dr. Marek S. Ryłko

Department of Electrical and Electronic Engineering

University College Cork

Ireland

## **DECLARATION**

I hereby declare that I am the sole author of this thesis and all of the work undertaken in this thesis is original in content and was carried out by the author. Work carried out by others has been duly acknowledged in this thesis.

This is a true copy of the thesis, including any required final revisions, as accepted by my examiners. The work presented has not been accepted in any other previous application for a degree.

| Signed: | <br> |  |

|---------|------|--|

|         |      |  |

| Date:   |      |  |

### **ABSTRACT**

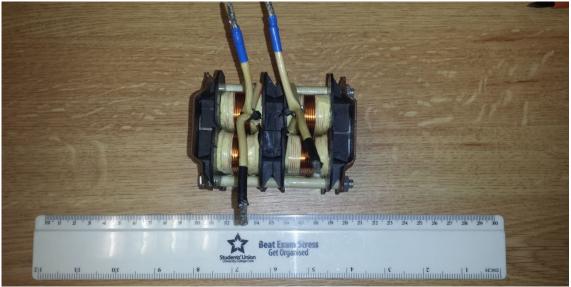

This thesis focuses on the complete mathematical modelling and digital closed-loop control of two-phase interleaved coupled-inductor non-isolated dc-dc converters. Coupled-inductors have been shown to reduce the cost, size, and weight of high-power magnetic components while increasing efficiency.

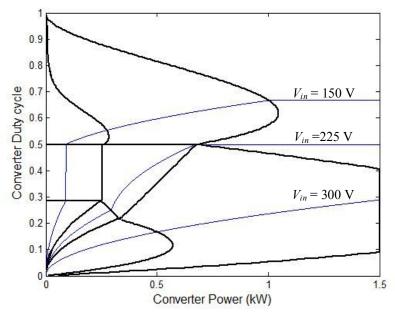

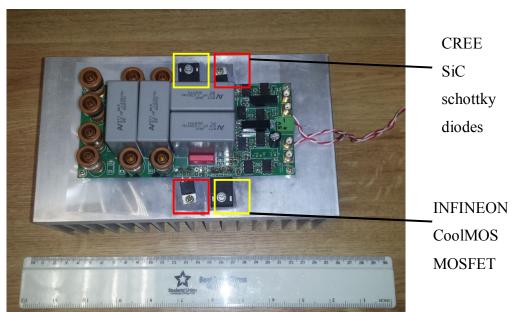

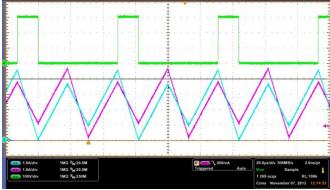

The complete large-signal model of the coupled-inductor boost converter is presented and compared to the traditional single-phase and two-phase discrete inductor dc-dc converters. The CCM-DCM mode maps are presented and discussed for the coupled-inductor boost converter. Sample analyses of several different CCM and DCM modes of operation are also presented. The different CCM and DCM waveforms are experimentally produced by a 1 kW laboratory prototype.

Following on from the large-signal model, the complete small-signal model of the coupled-inductor boost converter is presented. The method of solving for the small-signal models is discussed, and sample analyses of several different CCM and DCM modes of operation are presented. Calculated and experimental frequency sweeps for several of the CCM and DCM modes of operation are produced and compared to verify the accuracy of the small-signal models.

Controllers for the 1 kW prototype are designed from the transfer functions derived from the small-signal models. The control strategy of average-current-mode control is digitally implemented, which uses an outer voltage loop and an inner current loop to eliminate any error between the output and the desired output. The FPGA used in testing is the Altera Cyclone III FPGA. Initially, PI controllers are developed and compared to simulated results.

In order to improve the closed-loop performance of the converter, the inner current loop PI controllers are replaced with Type II compensators. Several compensators are designed as examples for a number of CCM and DCM modes of operation. Finally, to increase the stability of the converter, bumpless PI control and forced-output control utilizing the Type II compensators are introduced and implemented.

Additional analyses and results are presented in the appendix.

### ACKNOWLEDGEMENTS

I wish to thank all individuals who have contributed to my work. This thesis would not have been possible without their support and guidance.

Firstly, I wish to thank my academic supervisors Dr. John Hayes, and Dr. Gordon Lightbody. It was a pleasure getting to know, and working with John through the last four years, and I hope to collaborate again in future. I wish to thank Dr. Maeve Duffy and Dr. Kevin McCarthy for examining my thesis.

I wish to thank the Irish Research Council for their scholarship and financial support. I wish to thank dtw for their financial and technical support. I would also like to greatly express my gratitude to my industrial supervisor Dr. Marek Ryłko for his support and friendship throughout the last four years. I would not be where I am without it.

The support I received from the R&D staff at dtw is greatly appreciated, and I cannot thank them enough. I wish to thank Jurek Masłon, Marcin Kacki, and Miłosz Handzel. Special thanks must go to Dr. Adam Penczek, Dr. Robert Stala, Dr. Andrzej Mondzik, Miłosz Szarek, and Sławek Szot for their friendship and support. It was truly invaluable.

I wish to thank all the staff of the Department of Electrical Engineering at University College Cork. Particular mention must go to Ralph O' Flaherty, Niamh O' Sullivan, Mary O' Leary, and Claudia Cashman for their administrative support, and to Mick O' Shea, Tim Power, and Hillary Mansfield for their invaluable skills.

I would also like to thank James Griffiths for his expert support over the last four years. His technical knowledge and friendship helped me on many occasions, and for that I'm very grateful.

I would also like to thank my fellow postgraduate students, both past and present. The company that I kept with over the last four years made the PERL lab a wonderful place to work, and I cannot express my gratitude enough. Special mention must go to Kevin Hartnett, Donal Murray, Diarmaid Hogan, Jack Bermingham, Conor O' Shea, Kilian O' Donoghue, Edward O' Dwyer, Yeny Vazquez-Guitierrez, Patrick Xie, Alex Jaeger, Robert Ryan, Daniel O' Keefe, and Oliwier Melon. I would especially like to thank Adrian O' Sullivan and Kevin Davis for making our section of the lab a pleasure to work in.

I also wish to thank Brian Boland, Dylan Burke, Brian Foley, David Hegarty, John McCarthy, Karen McCarthy, Martin McCarthy, Niall McNamara, Kevin Mulcahy, Cian O' Callaghan, Kevin O' Leary, and Adrian Twomey.

My sincere gratitude goes to my family for helping me through these last four years. To my sisters, Margaret and Karen, and to my brothers, Patrick, Paul, Martin, and Kieran, thank you.

Finally, I would like to thank my mother, Pauline, and late father, Gus, for all the love and support throughout these few years and all my life, it is a debt I will never be able to repay.

Thank you.

### LIST OF PUBLICATIONS

#### Journal Papers

- B. C. Barry, J. G. Hayes, and M. S. Ryłko, "CCM and DCM operation of the interleaved two-phase boost converter with discrete and coupled-inductors," *IEEE Transactions on Power Electronics*, vol. 30, no. 12, pp. 6551-6567, December 2014.

- 2. K. J. Hartnett, J. G. Hayes, M. S. Ryłko, B. C. Barry, and Jerzy W. Masłoń, "Comparison of 8 kW CCTT IM and discrete inductor interleaved boost converter for renewable energy applications," *IEEE Transactions on Industry Applications*, vol. 51, no. 3, pp. 2455-2469, December 2014.

#### **Conference Papers**

- B. C. Barry, J. G. Hayes, M. G. Egan, M. S. Ryłko, Jerzy W. Masłoń, and K. J. Hartnett "CCM and DCM operation of the integrated-magnetic interleaved two-phase boost converter," 29th Annual IEEE Applied Power electronics Conference and Exposition, Fort Worth, Texas, March 2014.

- B. C. Barry, J. G. Hayes, M. S. Ryłko, Jerzy W. Masłoń, and K. J. Hartnett, "Two-phase interleaved boost converters for distributed generation," *IEEE* 5th International Symposium on Power Electronics for Distributed Generation, Galway, Ireland, June 2014.

- 3. B. C. Barry, J. G. Hayes, M. S. Ryłko, and Jerzy W. Masłoń, "Discontinuous conduction mode operation of the two-phase integrated-magnetic boost converter," *IEEE Energy Conversion Congress and Exposition, Pittsburgh, Pennsylvania*, September 2014.

- 4. B. C. Barry, J. G. Hayes, M. S. Ryłko, R. Stala, A. Penczek, A. Mondzik, and R. T. Ryan, "Small-signal model and control of the interleaved two-phase coupled-inductor boost converter," *IEEE Energy Conversion Congress and Exposition*, Milwaukee, Wisconsin, September 2016.

## TABLE OF CONTENTS

| 1 Introduction                                                | 1  |

|---------------------------------------------------------------|----|

| 1.1 Overview                                                  | 2  |

| 1.2 Thesis Objectives                                         | 5  |

| 1.3 Thesis Structure.                                         | 6  |

| 1.4 Power converters: A General Background                    | 7  |

| 1.4.1 Semiconductor Gate Drivers                              | 7  |

| 1.4.2 Consumer Electronics                                    | 7  |

| 1.4.3 AC Source Renewable Energy Systems                      | 7  |

| 1.4.4 DC Source Renewable Systems                             | 9  |

| 1.4.5 Automotive Applications                                 | 11 |

| 1.5 DC-DC Converter Topologies                                | 15 |

| 1.5.1 Boost Converter                                         | 15 |

| 1.5.2 Buck converter                                          | 16 |

| 1.5.3 Coupled-Inductor DC-DC Converters                       | 16 |

| 1.6 References.                                               | 21 |

| 2 COUPLED-INDUCTOR INTERLEAVED CONVERTER LARGE SIGNAL MODEL   | 27 |

| 2.1 Introduction.                                             |    |

| 2.2 Single-Phase Boost Converter (1L) Modes of Operation      | 30 |

| 2.3 Discrete-Inductor Two-Phase Boost Converter (2L) Modes of |    |

| Operation                                                     | 33 |

| 2.4 Coupled-Inductor Two-Phase Boost Converter (CL) Modes of  |    |

| Operation                                                     | 37 |

| 2.4.1 Modal Analysis                                          | 41 |

| 2.5 CCM Operation & CCM-DCM Boundary Conditions               | 44 |

| 2.6 DCM Characteristics                                       | 47 |

| 2.6.1 DCM 4                                                   | 47 |

| 2.6.2 DCM 9                                                   | 48 |

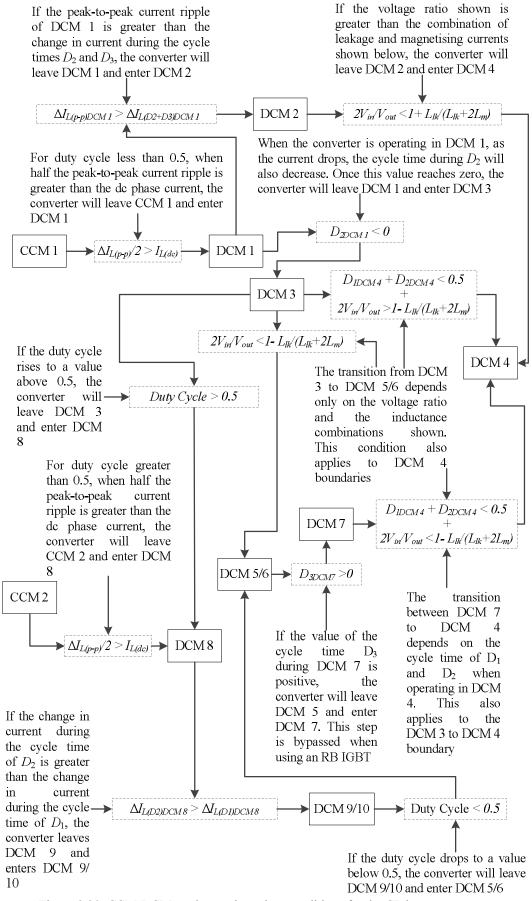

| 2.6.3 Modal Boundary Flowchart                                | 51 |

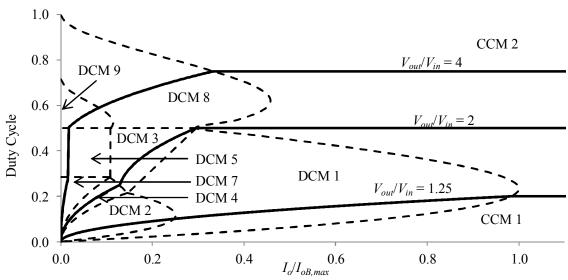

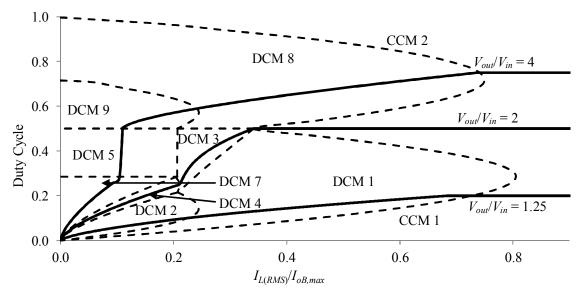

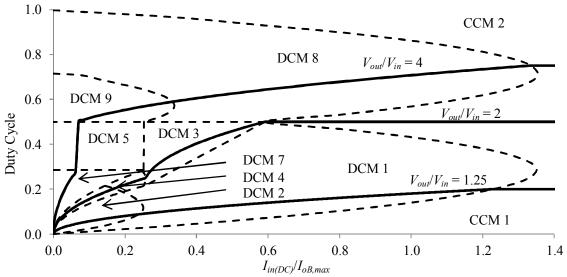

| 2.7 CL Boost Converter CCM-DCM Mode Maps                      | 53 |

| 2.7.1 Effect of Inductance Coupling Factor                    | 56 |

| 2.7.2 72 kW Design Example                                    | 56 |

|     | 2.8 Design of 1 kW Two-Phase Interleaved Coupled-Inductor Boost                  |     |

|-----|----------------------------------------------------------------------------------|-----|

|     | Converter                                                                        | 58  |

|     | 2.9 Experimental Results                                                         | 62  |

|     | 2.10 Conclusions                                                                 | 67  |

|     | 2.11 References                                                                  | 68  |

| 3 ( | COUPLED-INDUCTOR INTERLEAVED CONVERTER SMALL-SIGNAL AND TRANSFER FUNCTION MODELS | 71  |

|     | 3.1 Introduction                                                                 | 72  |

|     | 3.2 Linearisation and Transfer Function Models of the DC-DC                      |     |

|     | Converter Family                                                                 | 74  |

|     | 3.2.1 Converter Linearisation                                                    | 74  |

|     | 3.2.2 Converter Transfer Function Models                                         | 75  |

|     | 3.3 Single-Phase Boost Converter (1L) Small-Signal Model                         | 77  |

|     | 3.3.1 Small-Signal Models of 1L Boost Converter in CCM                           | 77  |

|     | 3.3.2 Small-Signal Models of 1L Boost Converter in DCM                           | 80  |

|     | 3.4 Two-Phase Boost Converter (2L) Small-Signal Model                            | 83  |

|     | 3.4.1 Small-Signal Models of 2L Boost Converter in CCM                           | 83  |

|     | 3.4.2 Small-Signal Models of 2L Boost Converter in DCM                           | 84  |

|     | 3.5 Coupled-Inductor Boost Converter (CL) Small-Signal Model                     | 86  |

|     | 3.5.1 Small-Signal Models of the CL Boost Converter in CCM                       | 86  |

|     | 3.5.2 Small-Signal Models of the CL Boost Converter in DCM 4                     | 88  |

|     | 3.5.3 Small-Signal Models of the CL Boost Converter in DCM 1                     | 90  |

|     | 3.5.4 Small-Signal Models of the CL Boost Converter in DCM 8                     | 93  |

|     | 3.6 Verification of Small-Signal Models                                          | 97  |

|     | 3.6.1 Coupled-Inductor CCM Small-Signal Model Verification                       | 97  |

|     | 3.6.2 Coupled-Inductor DCM 4 Small-Signal Model Verification                     | 99  |

|     | 3.6.3 Coupled-Inductor DCM 8 Small-Signal Model Verification                     | 100 |

|     | 3.6.4 Coupled-Inductor DCM 2 Small-Signal Model Verification                     | 100 |

|     | 3.6.5 Coupled-Inductor DCM 9 Small-Signal Model Verification                     | 101 |

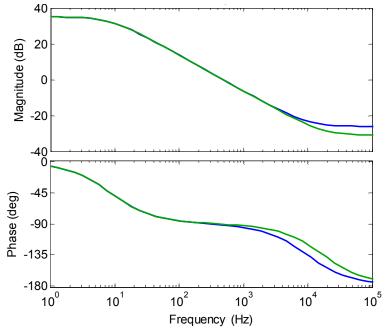

|     | 3.7 Comparison of 2L and CL CCM Small-Signal Models                              | 103 |

|     | 3.7.1 Duty Cycle-to-Output voltage Frequency Response                            | 103 |

|     | 3.7.2 Duty Cycle-to-Inductor Current Frequency Response                          | 104 |

|     | 3.7.3 Inductor Current-to-Output Voltage Frequency Response                      | 104 |

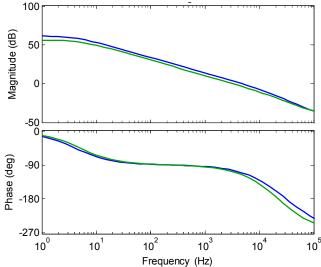

|     | 3.8 Comparison of 2L and CL DCM Small-Signal Models                              | 106 |

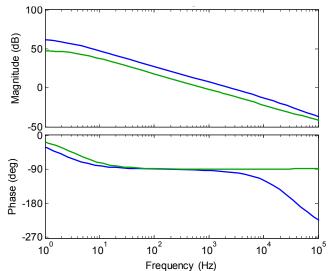

|     | 3.8.1 Duty Cycle-to-Output Voltage Frequency Response of DCM 1                   | 106 |

|     | 3.8.2 Duty Cycle-to-Output Voltage Frequency Response of DCM 2         | . 106 |

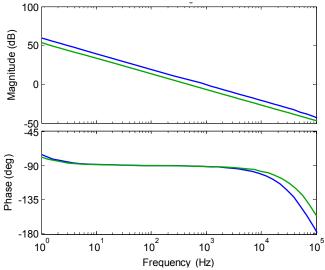

|-----|------------------------------------------------------------------------|-------|

|     | 3.8.3 Duty Cycle-to-Output Voltage Frequency Response of DCM 3         | . 107 |

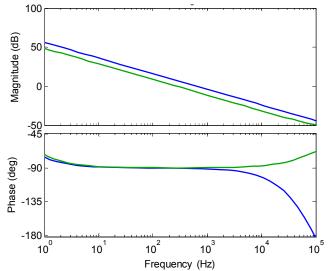

|     | 3.8.4 Duty Cycle-to-Output Voltage Frequency Response of DCM 4         | . 107 |

|     | 3.8.5 Duty Cycle-to-Output Voltage Frequency Response of DCM 7         | . 107 |

|     | 3.8.6 Duty Cycle-to-Output Voltage Frequency Response of DCM 8         | . 108 |

|     | 3.8.7 Duty Cycle-to-Output Voltage Frequency Response of DCM 9         | . 108 |

|     | 3.8.8 Discussion on Comparisons                                        | . 109 |

|     | 3.9 Conclusions                                                        | . 111 |

|     | 3.10 References                                                        | . 112 |

| 4 ( | COUPLED-INDUCTOR INTERLEAVED CONVERTER CLOSED-LOOP PI DIGITAL CONTROL  | . 115 |

|     | 4.1 Introduction                                                       | . 116 |

|     | 4.2 DC-DC Converter Control.                                           | . 117 |

|     | 4.2.1 Voltage Mode Control                                             | . 117 |

|     | 4.2.2 Hysteretic Control                                               | . 118 |

|     | 4.2.3 Peak-Current Mode Control.                                       | . 118 |

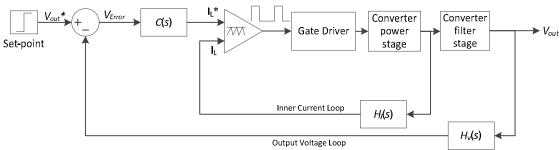

|     | 4.2.4 Average-Current Mode Control                                     | . 120 |

|     | 4.2.5 Coupled-Inductor Converter Controller                            | . 121 |

|     | 4.3 Digital Controller Design Parameters                               | . 122 |

|     | 4.3.1 Design Parameters                                                | . 122 |

|     | 4.3.2 Implementation Parameters                                        | . 123 |

|     | 4.4 CL Converter PI Controller Design and Implementation.              | . 125 |

|     | 4.4.1 Design of Inner Current Loop PI Controller for CCM Operation     | . 126 |

|     | 4.4.2 Design of Outer Voltage Loop PI Controller for CCM Operation     | . 128 |

|     | 4.4.3 Simulation and Experimental Results of PI Controllers in ACMC of |       |

|     | the CL Boost Converter operating in CCM                                | . 130 |

|     | 4.4.4 CCM Designed PI Controllers for DCM 1 Operation                  | . 131 |

|     | 4.4.5 Design of Inner Current Loop PI Controller for DCM 1/DCM 9       |       |

|     | Operation                                                              | . 132 |

|     | 4.4.6 Simulation and Experimental Results of PI Controllers in ACMC of |       |

|     | the CL Boost Converter operating in DCM 1/DCM 9                        | . 135 |

|     | 4.5 Conclusions                                                        | . 139 |

|     | 4.6 References.                                                        | . 140 |

| 5 ( | COUPLED-INDUCTOR INTERLEAVED CONVERTER CLOSED-LOOP TYPE II             |       |

|     | DIGITAL CONTROL                                                        |       |

|     | 5.1 Introduction                                                       | 144   |

|     | 5.2 Type II Compensator Structure and Implementation                | . 145 |

|-----|---------------------------------------------------------------------|-------|

|     | 5.2.1 Analogue Implementation of the Type II Compensator            | . 145 |

|     | 5.2.2 Digital Implementation of the Type II Compensator             | . 146 |

|     | 5.3 CL Converter Type II Compensator Design and Implementation for  |       |

|     | CCM Operation                                                       | . 148 |

|     | 5.3.1 Design of Inner Current Loop Type II Compensator              | . 148 |

|     | 5.3.2 Simulation and Experimental Results for Type II Compensator   | . 152 |

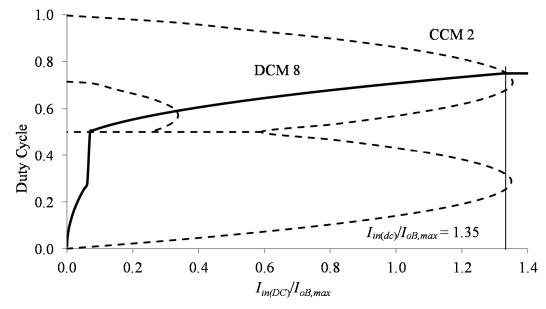

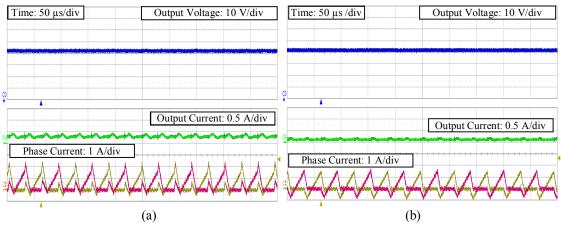

|     | 5.3.3 CCM Designed Type II Compensators for DCM 8 Operation         | . 153 |

|     | 5.3.4 Design of Inner Current Loop Type II Compensators for DCM     |       |

|     | Operation                                                           | . 155 |

|     | 5.3.5 Simulation and Experimental Results of Type II Controllers in |       |

|     | ACMC of the CL Boost Converter operating in DCM                     | . 158 |

|     | 5.4 Forced-Output Control of CL Converter                           | . 161 |

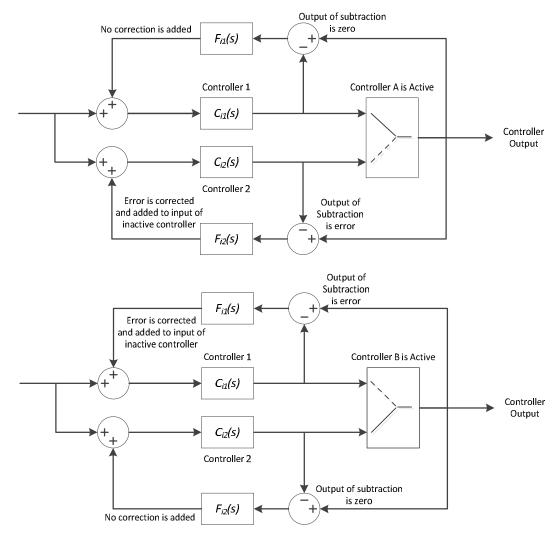

|     | 5.4.1 Bumpless Control                                              | . 161 |

|     | 5.4.2 Mode Determination                                            | . 162 |

|     | 5.4.3 Bumpless PI Control                                           | . 163 |

|     | 5.4.4 Forced-Output Control                                         | . 166 |

|     | 5.4.5 Simulation and Experimental Results of Type II Controllers in |       |

|     | ACMC of the CL Boost Converter operating in DCM using               |       |

|     | Forced-Output Control                                               | . 169 |

|     | 5.5 Conclusions                                                     | . 175 |

|     | 5.6 References                                                      | . 176 |

| 6 C | ONCLUSIONS                                                          | . 177 |

|     | 6.1 Chapter Summaries                                               | . 178 |

|     | 6.1.1 Chapter 1                                                     | . 178 |

|     | 6.1.2 Chapter 2                                                     | . 178 |

|     | 6.1.3 Chapter 3                                                     | . 178 |

|     | 6.1.4 Chapter 4                                                     | . 179 |

|     | 6.1.5 Chapter 5                                                     | . 179 |

|     | 6.2 Contributions                                                   | . 181 |

|     | 6.3 Future Work                                                     | . 183 |

| 7 A | PPENDIX                                                             | . 185 |

|     | Appendix A.                                                         | . 186 |

|     | Appendix B.                                                         | 102   |

|     | Appellula D                                                         | . 192 |

# **LIST OF FIGURES**

| Figure 1.1. Observed globally averaged combined land and ocean surface temperature anomaly 1850-2012 [1.2] | 2  |

|------------------------------------------------------------------------------------------------------------|----|

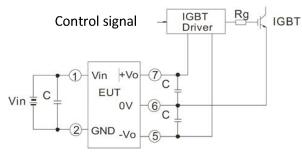

| Figure 1.2. IGBT gate driver circuit featuring a dc-dc converter [1.20]                                    | 7  |

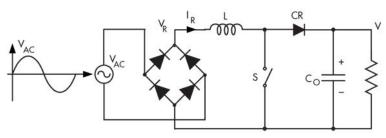

| Figure 1.3. Power-factor correction boost converter [1.54].                                                | 7  |

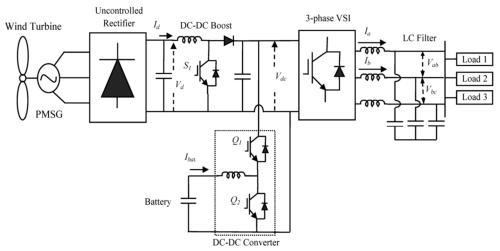

| Figure 1.4. Variable speed wind energy supply system [1.51].                                               | 8  |

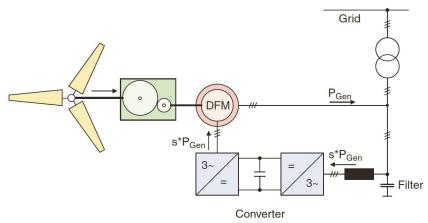

| Figure 1.5. Wind turbine generator utilizing a DFIG setup [1.29]                                           | 9  |

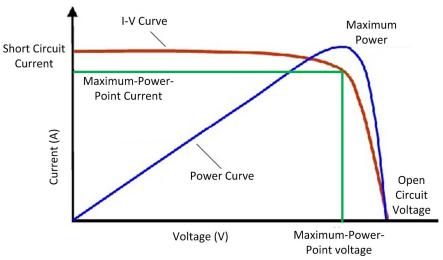

| Figure 1.6. The I-V characteristics of a PV cell [1.52]                                                    | 9  |

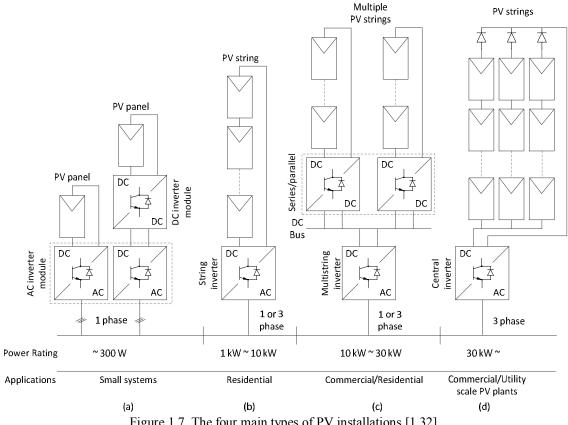

| Figure 1.7. The four main types of PV installations [1.32]                                                 | 10 |

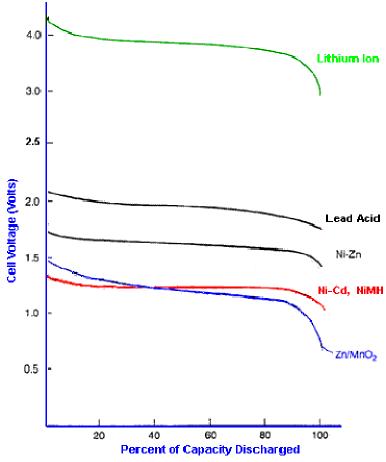

| Figure 1.8. Cell voltage vs. state of charge of typical batteries [1.35].                                  | 12 |

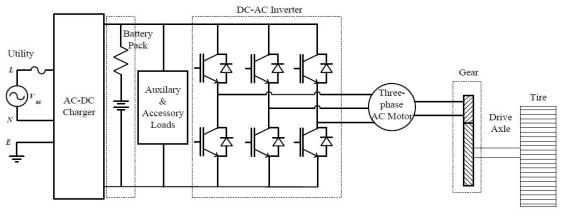

| Figure 1.9. Block diagram of electric vehicles drive train [1.36]                                          | 12 |

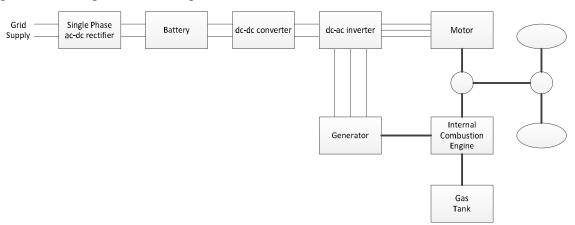

| Figure 1.10. Series/parallel plug-in HEV drive train.                                                      | 13 |

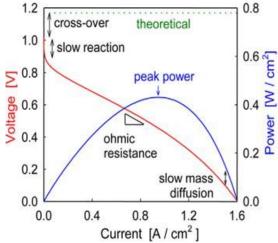

| Figure 1.11. A typical fuel-cell polarization curve [1.41]                                                 | 14 |

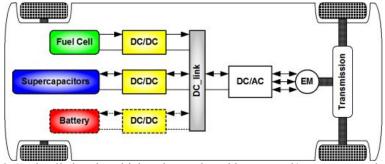

| Figure 1.12. Fuel-cell electric vehicle using on-board battery and/or super capacitors [1.42].             | 14 |

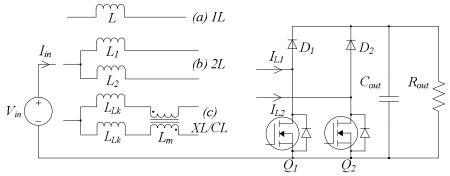

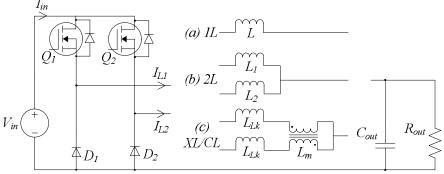

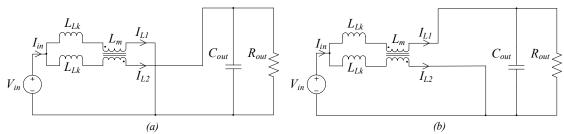

| Figure 1.13. The (a) 1L, (b) 2L and (c) CL boost converter topologies.                                     | 15 |

| Figure 1.14. The (a) 1L, (b) 2L and (c) CL boost converter topologies.                                     | 16 |

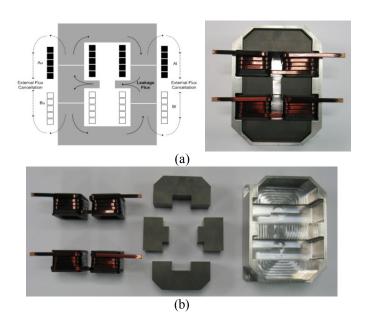

| Figure 1.15. CCTT SWIM 72 kW prototype (a) assembled and (b) disassembled                                  | 18 |

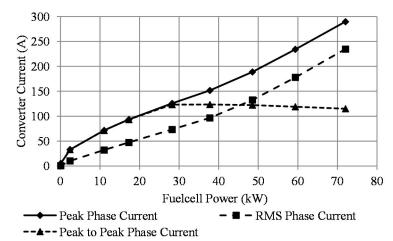

| Figure 1.16. Peak, RMS and peak-peak per-phase currents for 2L converters                                  | 19 |

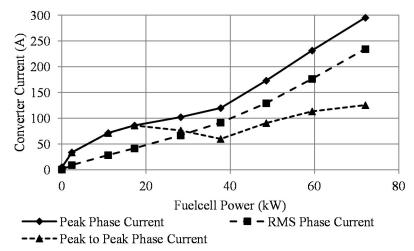

| Figure 1.17. Peak, RMS and peak-peak per-phase currents for CCTT CL converters.                            | 19 |

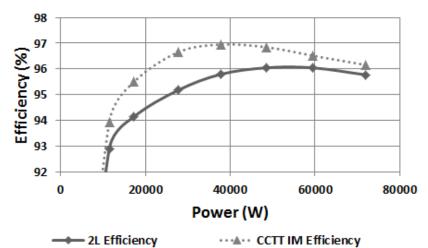

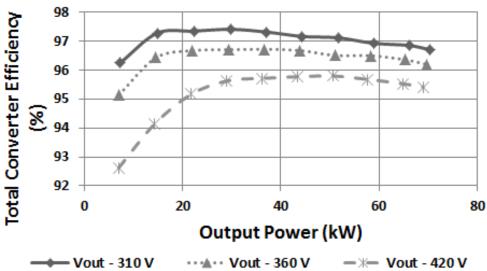

| Figure 1.18. Predicted CCTT CL and 2L converter efficiency as fuel-cell power varies.                      | 20 |

| Figure 1.19. CCTT CL converter experimental efficiencies at $V_{in} = 155 \text{ V}$                       | 20 |

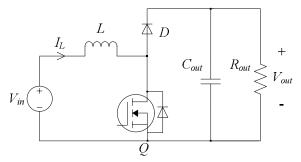

| Figure 2.1. The single-phase boost converter.                                                              | 30 |

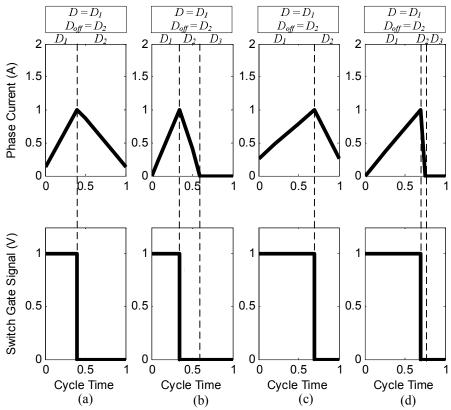

| Figure 2.2. Current and gate-drive waveforms of (a) 1L CCM 1, (b) 1L DCM 1, (c) 1L CCM 2 and (d) 1L DCM 2  | 30 |

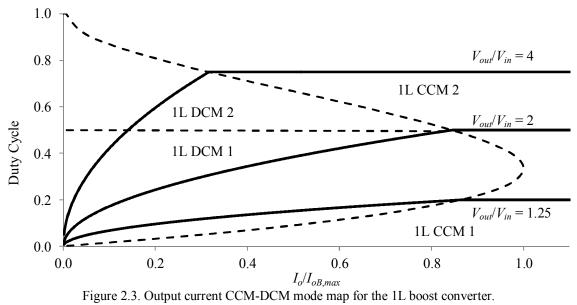

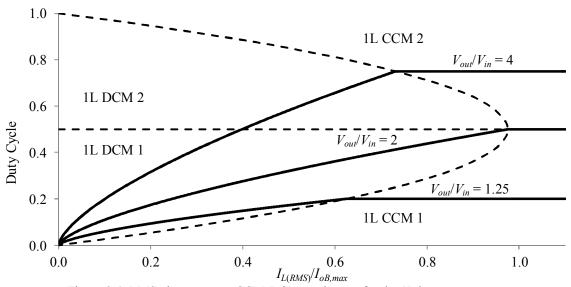

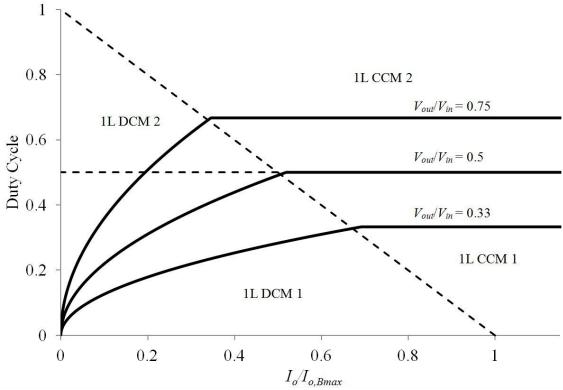

| Figure 2.3. Output current CCM-DCM mode map for the 1L boost converter                                     | 32 |

| Figure 2.4. RMS phase current CCM-DCM mode map for the 1L boost converter                                  | 32 |

| Figure 2.5. Input current CCM-DCM mode map for 1L boost converter                                                                                | 32 |

|--------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.6. Two-phase discrete-inductor boost converter.                                                                                         | 33 |

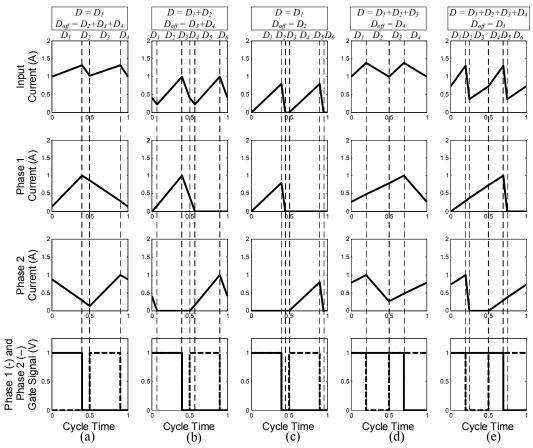

| Figure 2.7. Current and gate-drive waveforms of (a) 2L CCM 1, (b) 2L DCM 1, (c) 2L DCM 2, (d) 2L CCM 2 and (e) 2L DCM 3                          | 34 |

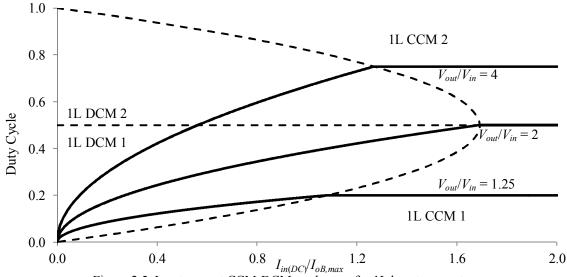

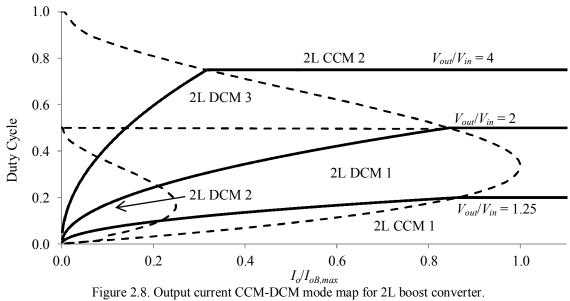

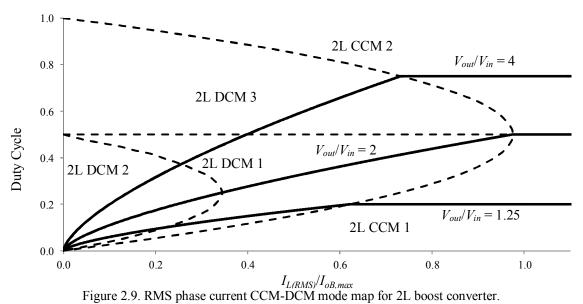

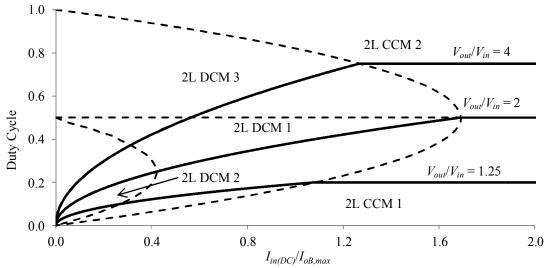

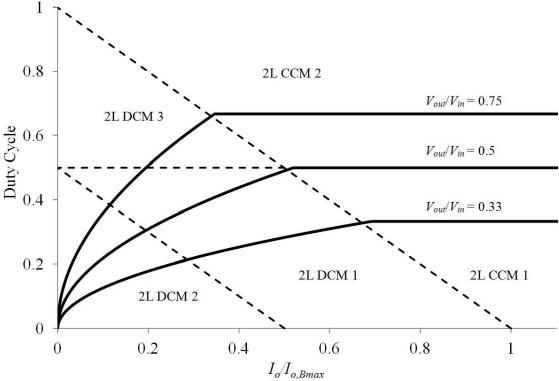

| Figure 2.8. Output current CCM-DCM mode map for 2L boost converter.                                                                              | 35 |

| Figure 2.9. RMS phase current CCM-DCM mode map for 2L boost converter                                                                            | 35 |

| Figure 2.10. Input current CCM-DCM mode map for 2L boost converter                                                                               | 35 |

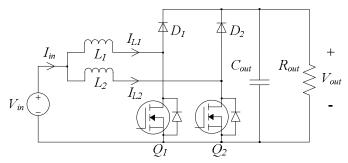

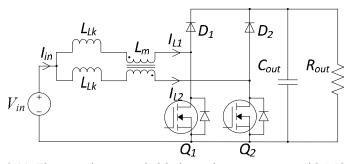

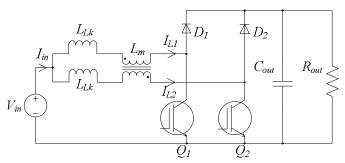

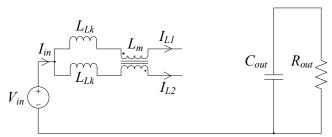

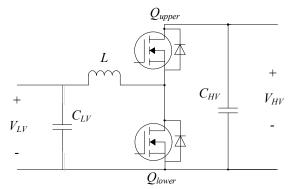

| Figure 2.11. The two-phase coupled-inductor boost converter with MOSFETs                                                                         | 37 |

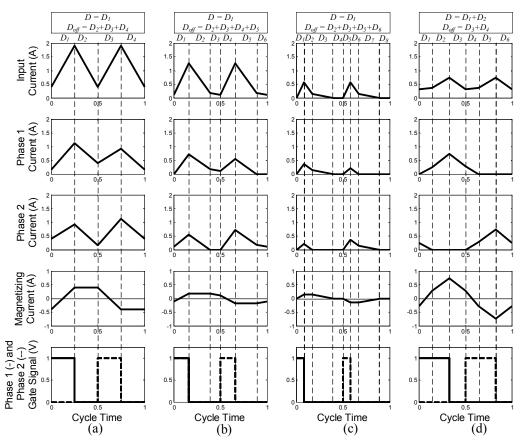

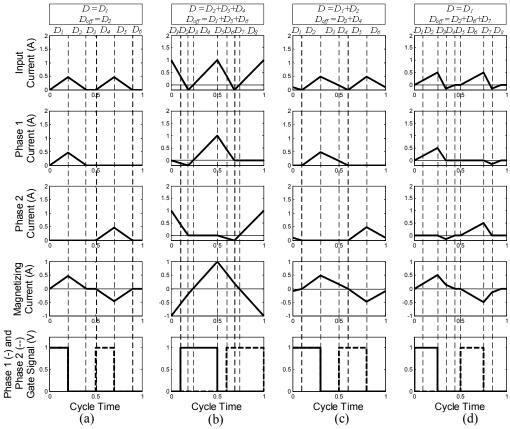

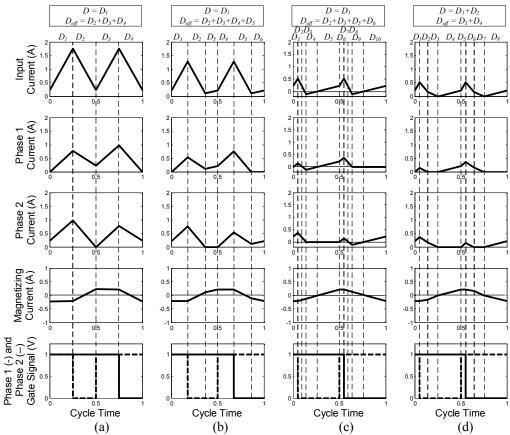

| Figure 2.12. Current and gate-drive waveforms of (a) CCM 1, (b) DCM 1, (c) DCM 2 and (d) DCM 3 of a CL boost converter.                          | 38 |

| Figure 2.13. Current and gate-drive waveforms of (a) DCM 4, (b) DCM 5, (c) DCM 6 and (d) DCM 7 of a CL boost converter.                          | 38 |

| Figure 2.14. Current and gate-drive waveforms of (a) CCM 2, (b) DCM 8, (c) DCM 9 and (d) DCM 10 of a CL boost converter.                         | 39 |

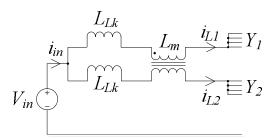

| Figure 2.15. Simplified coupled-inductor boost converter with quad-state outputs                                                                 | 41 |

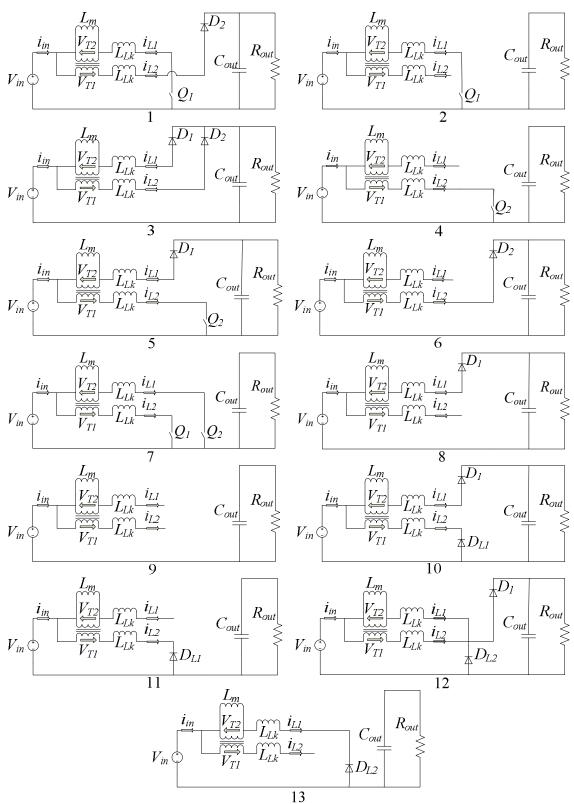

| Figure 2.16. Sub-modes of operation for the 2L and CL boost converters                                                                           | 42 |

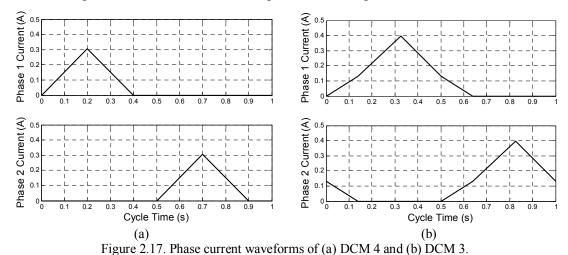

| Figure 2.17. Phase current waveforms of (a) DCM 4 and (b) DCM 3.                                                                                 | 48 |

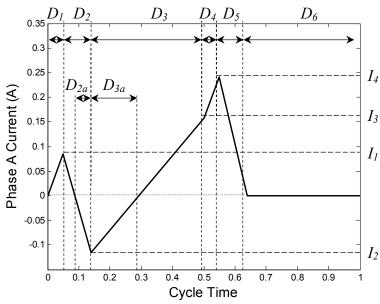

| Figure 2.18. Phase current of DCM 9.                                                                                                             | 49 |

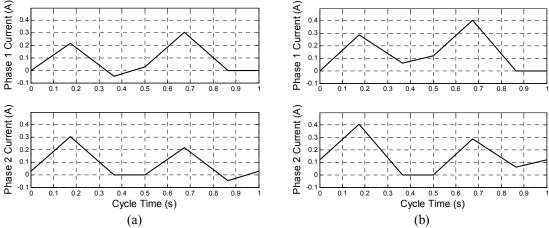

| Figure 2.19. Phase current waveforms of (a) DCM 9 and (b) DCM 8.                                                                                 | 50 |

| Figure 2.20. CCM-DCM mode map boundary conditions for the CL boost converter.                                                                    |    |

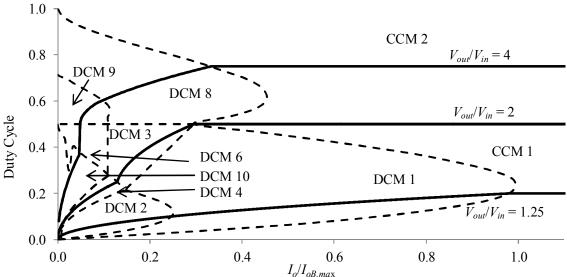

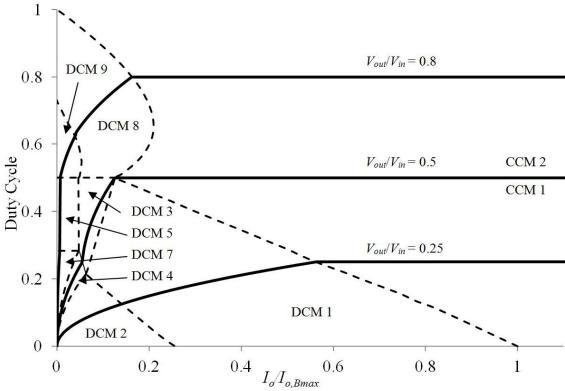

| Figure 2.21. Output current CCM-DCM mode map for CL boost converter                                                                              | 54 |

| Figure 2.22. RMS phase current CCM-DCM mode map for CL boost converter                                                                           | 54 |

| Figure 2.23. Input current CCM-DCM mode maps for CL boost converter                                                                              | 54 |

| Figure 2.24. The two-phase coupled-inductor boost converter with unidirectional switch.                                                          | 55 |

| Figure 2.25. Output current CCM-DCM mode maps for CL boost converter with unidirectional lower switch e.g. IGBT.                                 | 55 |

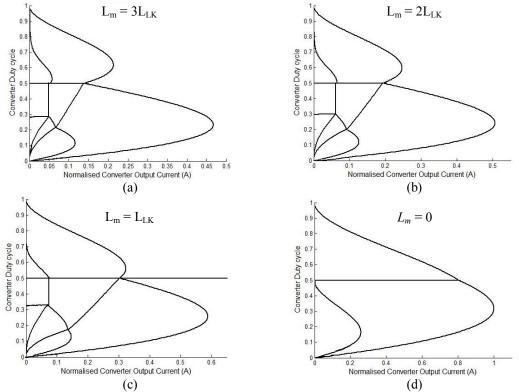

| Figure 2.26. CCM-DCM mode maps of a CL boost converter where (a) $L_{Lk} = 3L_m$ , (b), $L_m = 2 L_{Lk}$ , (c) $L_m = L_{Lk}$ and (d), $L_m = 0$ | 56 |

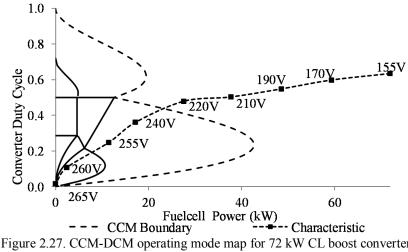

| Figure 2.27. CCM-DCM operating mode map for 72 kW CL boost converter                                                                             | 57 |

| Figure 2.28. 1 kW CL boost converter CCM-DCM mode map.                                                                                           | 59 |

| Figure 2.29. The two-phase interleaved coupled-inductor boost converter                                                                                                                  | 60 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.30. The CCTT integrated magnetic.                                                                                                                                               | 60 |

| Figure 2.31. The converter output capacitor                                                                                                                                              | 60 |

| Figure 2.32. The current and voltage sensors utilised in the 1 kW prototype                                                                                                              | 61 |

| Figure 2.33. The Altera cyclone III FPGA.                                                                                                                                                | 61 |

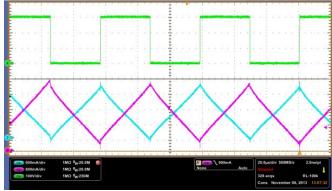

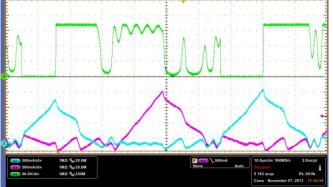

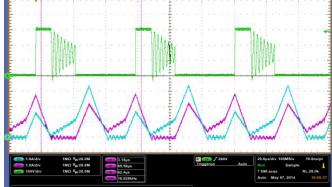

| Figure 2.34. Experimental waveforms of CCM 2. The Q1 voltage (green) is 100V/div, while the phase 1 current (blue) and phase 2 current (purple) are 1A/div each.                         | 62 |

| Figure 2.35. Experimental waveforms of $D = 0.5$ in CCM. The Q1 voltage (green) is 100 V/div, while the phase 1 current (blue) and phase 2 current (purple) are 600 mA/div each.         | 62 |

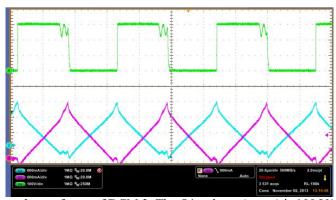

| Figure 2.36. Experimental waveforms of DCM 1. The Q1 voltage (green) is 100 V/div, while the phase 1 current (blue) and phase 2 current (purple) are 1 A/div each.                       | 63 |

| Figure 2.37. Experimental waveforms of DCM 2. The Q1 voltage (green) is 100 V/div, while the phase 1 current (blue) and phase 2 current (purple) are 1 A/div each.                       | 63 |

| Figure 2.38. Experimental waveforms of DCM 3. The Q1 voltage (green) is 100 V/div, while the phase 1 current (blue) and phase 2 current (purple) are 600 mA/div each.                    | 63 |

| Figure 2.39. Experimental waveforms of DCM 4. Q1 voltage (green) is 100V/div, while the phase 1 current (blue) and phase 2 current (purple) are 500 mA/div each                          | 63 |

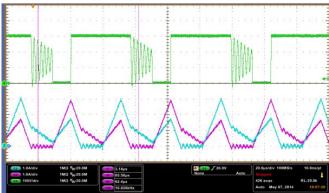

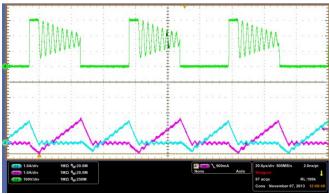

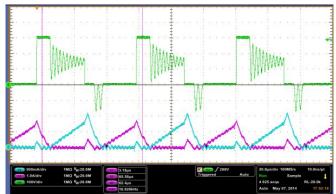

| Figure 2.40. Experimental waveforms of DCM 5. The Q1 voltage (green) is 100 V/div, while the phase 1 current (blue) and phase 2 current (purple) are 1 A/div each.                       | 64 |

| Figure 2.41. Experimental waveforms of DCM 6. The Q1 voltage (green) is 100 V/div, while the phase 1 current (blue) and phase 2 current (purple) are 1 A/div each.                       | 64 |

| Figure 2.42. Experimental waveforms of DCM 7. The Q1 voltage (green) is 50 V/div, while the phase 1 current (blue) and phase 2 current (purple) are 500 mA/div each                      | 64 |

| Figure 2.43. Experimental waveforms of DCM 8. The Q1 voltage (green) is 100 V/div, while the phase 1 current (purple) and phase 2 current (blue) are 1 A/div each.                       | 64 |

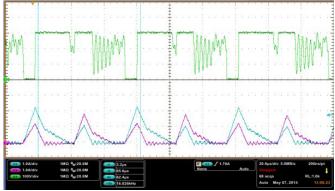

| Figure 2.44. Experimental waveform of DCM 9. The Q1 voltage (green) is 200 V/div, while the phase 1 current (blue) and phase 2 current (purple) are 500 mA/div and 1 A/div respectively. | 65 |

| Figure 2.45. Experimental waveform of DCM 10. The Q1 voltage (green) is 100 V/div, while the phase 1 current (purple) and phase 2 current (blue) are 1 A/div and 900 mA/div respectively. | 65   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 2.46. IGBT breakdown during DCM 6. The Q1 voltage (green) is 100V/div, while the phase 1 current (purple) and phase 2 current (blue) are 1A/div each.                              | 65   |

| Figure 2.47. IGBT breakdown during DCM 10. The Q1 voltage (green) is 100V/div, while the phase 1 current (blue) and phase 2 current (purple) are 1A/div each.                             | 65   |

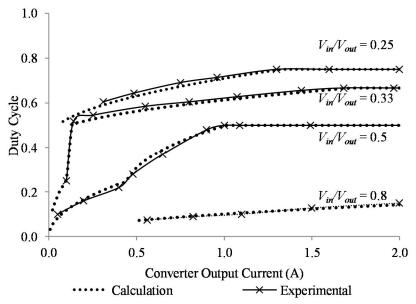

| Figure 2.48. Experimental and calculated values of converter characteristics                                                                                                              | 66   |

| Figure 3.1. Inductor current waveform of a 1L boost converter operating in CCM                                                                                                            | .77  |

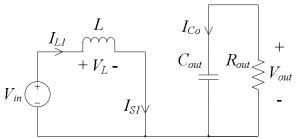

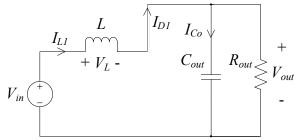

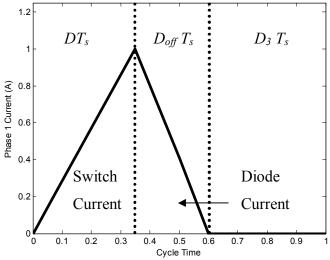

| Figure 3.2. 1L boost converter during cycle time $DT_s$ .                                                                                                                                 | 77   |

| Figure 3.3. 1L boost converter during cycle time $(1-D)T_s$                                                                                                                               | 78   |

| Figure 3.4. Inductor current waveform of a 1L boost operating in DCM                                                                                                                      | 80   |

| Figure 3.5. 1L boost converter during cycle time $D_3T_s$ .                                                                                                                               | 80   |

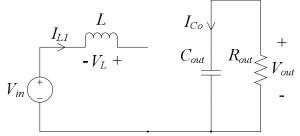

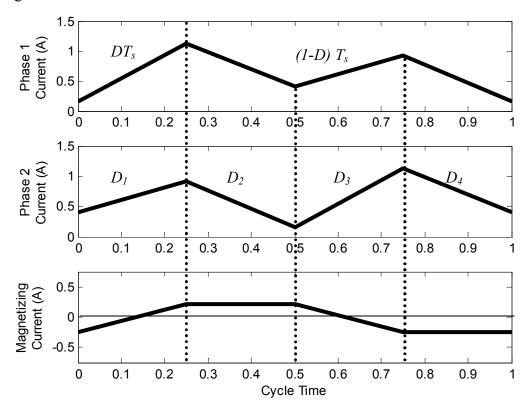

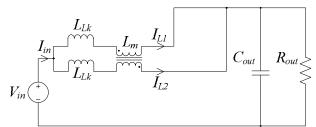

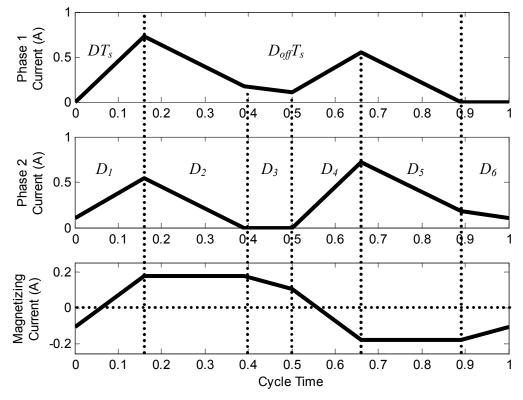

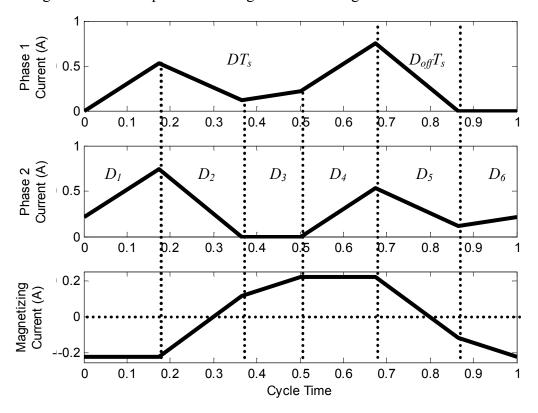

| Figure 3.6. Current waveforms of phase 1, phase 2, and magnetising currents                                                                                                               | . 86 |

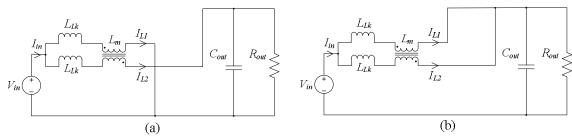

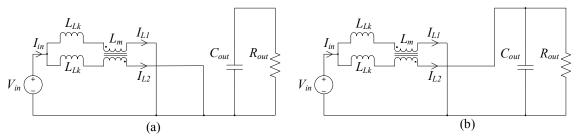

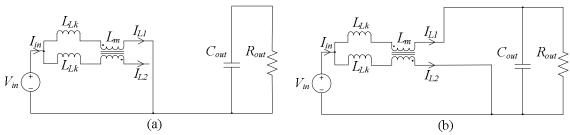

| Figure 3.7. CL boost converter operating in region (a) D <sub>1</sub> and (b) D <sub>3</sub>                                                                                              | 87   |

| Figure 3.8. CL boost converter operating in regions D <sub>2</sub> and D <sub>4</sub>                                                                                                     | 87   |

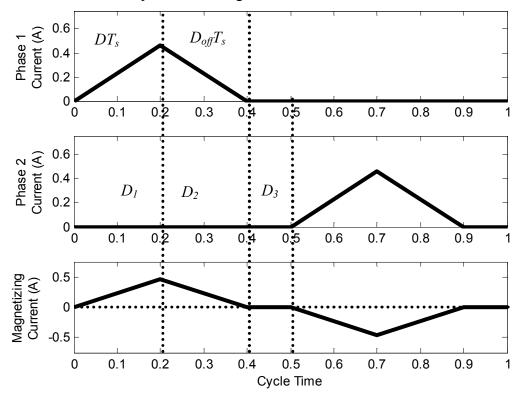

| Figure 3.9. Phase and magnetising currents of CL boost converter operating in DCM 4.                                                                                                      | . 88 |

| Figure 3.10. The sub-modes of operation (a) D <sub>1</sub> and (b) D <sub>2</sub> of DCM 4                                                                                                | 88   |

| Figure 3.11. The sub-mode of operation D <sub>3</sub> of DCM 4.                                                                                                                           | 88   |

| Figure 3.12. Phase and magnetising currents of CL boost converter operating in DCM 1                                                                                                      | . 90 |

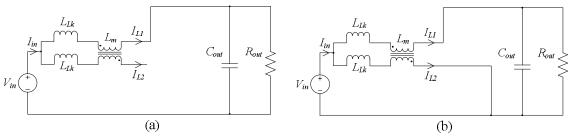

| Figure 3.13. The sub-modes of operation (a) D <sub>1</sub> and (b) D <sub>2</sub> and D <sub>5</sub> of DCM 1                                                                             | 91   |

| Figure 3.14. The sub-modes of operation (a) D3 and (b) D4 of DCM 1.                                                                                                                       | 91   |

| Figure 3.15. Phase and magnetising currents of CL boost converter operating in DCM 8.                                                                                                     | 93   |

| Figure 3.16. The sub-modes of operation of (a) D <sub>1</sub> and D <sub>4</sub> and (b) D <sub>2</sub> of DCM 1                                                                          | 93   |

| Figure 3.17. The sub-modes of operation of (a) D <sub>3</sub> and (b) D <sub>5</sub> of DCM 1                                                                                             | 94   |

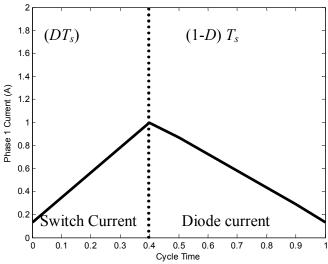

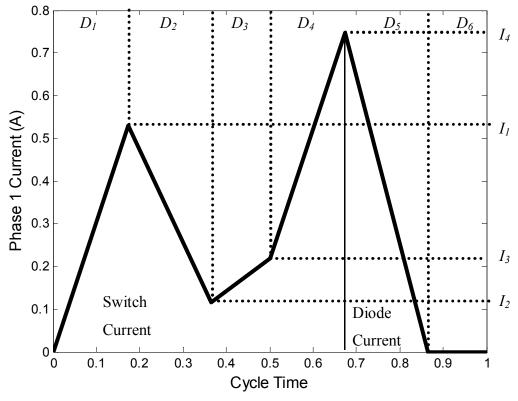

| Figure 3.18. Phase 1 inductor current waveform of DCM 8.                                                                                                                                  | 94   |

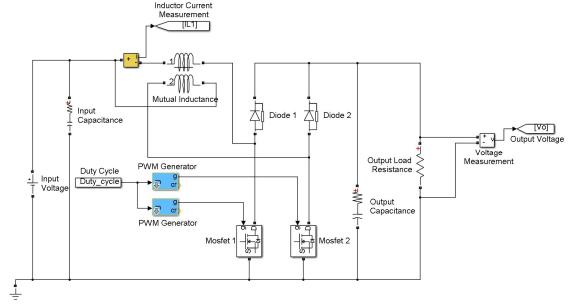

| Figure 3.19. Matlab/Simulink block Diagram of the 1 kW CL boost converter prototype.                                                                                                      | .97  |

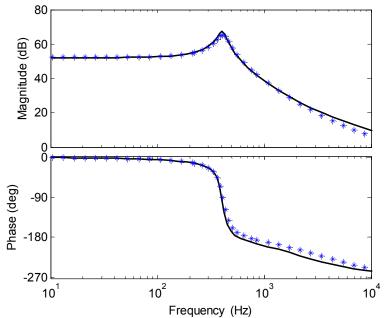

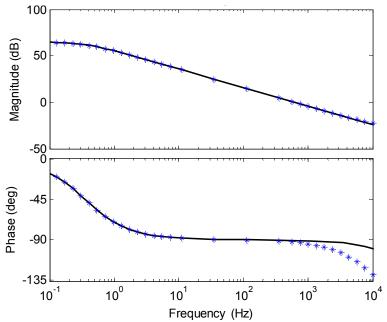

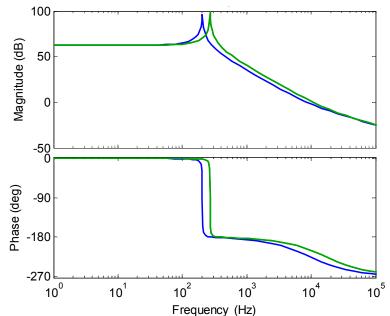

| Figure 3.20. Frequency response of simulated (*) and calculated (-) $G_{vd}(s)$ , the duty cycle –to-output voltage transfer function of the coupled-inductor boost converter operating in CCM.   | 8(  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

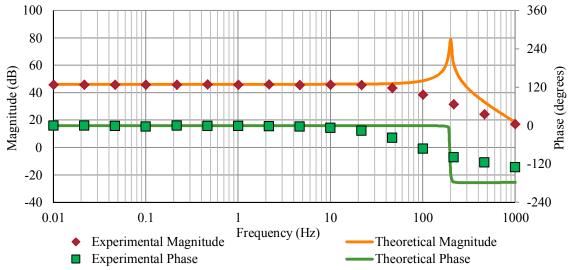

| Figure 3.21. Experimental Frequency sweep vs. theoretical frequency sweep of the CL boost converter operating in CCM for $G_{vd}(s)$ , the duty cycle-to-output voltage transfer function.        | 8   |

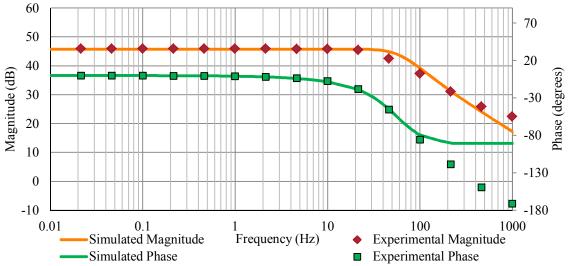

| Figure 3.22. Experimental Frequency sweep vs. simulated frequency sweep of the CL boost converter operating in CCM for $G_{vd}(s)$ , the duty cycle-to-output voltage transfer function.          | 9   |

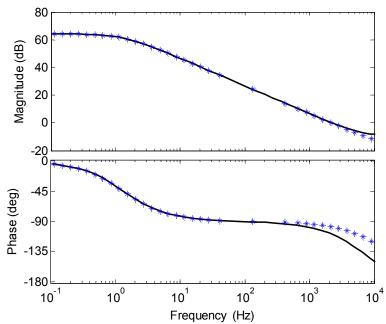

| Figure 3.23. Frequency Response of simulated (*) and calculated (-) $G_{vd}(s)$ , the duty cycle –to-output voltage transfer function of the coupled-inductor boost converter operating in DCM 4. | 9   |

| Figure 3.24. Frequency Response of simulated (*) and calculated (-) $G_{vd}(s)$ , the duty cycle –to-output voltage transfer function of the coupled-inductor boost converter operating in DCM 8. | )C  |

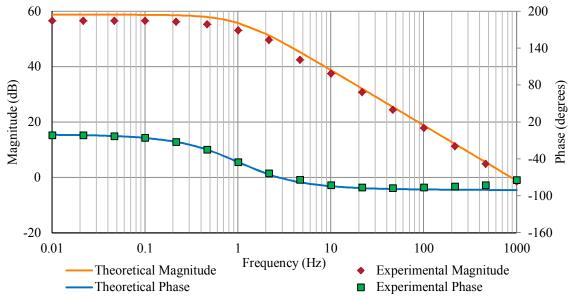

| Figure 3.25. Experimental Frequency sweep vs. theoretical frequency sweep of the CL boost converter operating in DCM 2 for $G_{vd}(s)$ , the duty cycle-to-output voltage transfer function.      | ) 1 |

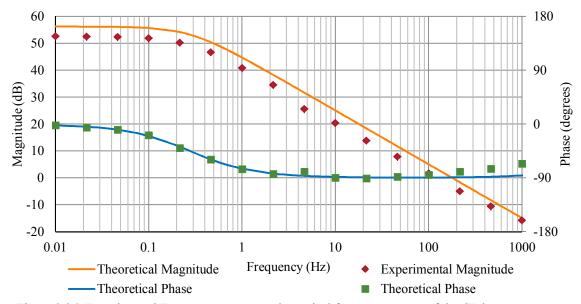

| Figure 3.26. Experimental Frequency sweep vs. theoretical frequency sweep of the CL boost converter operating in DCM 9 for $G_{vd}(s)$ , the duty cycle-to-output voltage transfer function.      | )1  |

| Figure 3.27. Current Waveforms of DCM with showing resonance due to the equivalent output capacitance of MOSFETs. 10                                                                              | )2  |

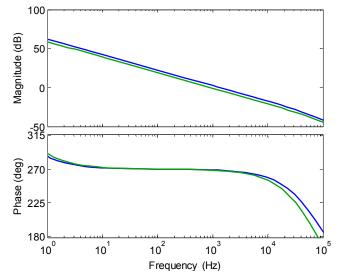

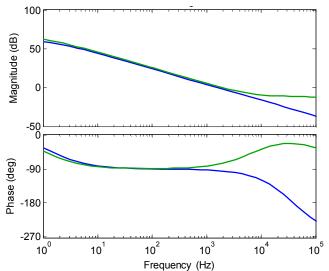

| Figure 3.28. Bode plots of the transfer function $G_{vd}(s)$ for the 2L (blue) and CL (green) boost converters.                                                                                   | )4  |

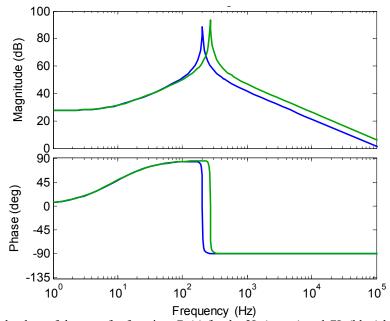

| Figure 3.29. Bode plots of the transfer function $G_{id}(s)$ for the 2L (green) and CL (blue) boost converters.                                                                                   | )4  |

| Figure 3.30. Bode plots of the transfer function $G_{id}(s)$ for the 2L (green) and CL (blue) boost converters.                                                                                   | )5  |

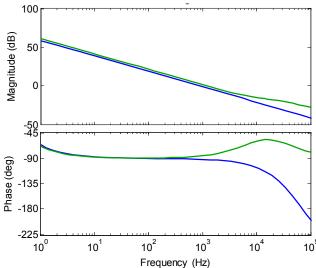

| Figure 3.31. Bode plots of the transfer function $G_{vd}(s)$ for the 2L (blue) and CL (green) boost converters in DCM and DCM 1                                                                   | )6  |

| Figure 3.32. Bode plots of the transfer function $G_{vd}(s)$ for the 2L (blue) and CL (green) boost converters in DCM and DCM 2.                                                                  | )6  |

| Figure 3.33. Bode plots of the transfer function $G_{vd}(s)$ for the 2L (blue) and CL (green) boost converters in DCM and DCM 3.                                                                  | )7  |

| Figure 3.34. Bode plots of the transfer function $G_{vd}(s)$ for the 2L (blue) and CL (green) boost converters in DCM and DCM 4                                                                   | )7  |

| Figure 3.35. Bode plots of the transfer function $G_{vd}(s)$ for the 2L (blue) and CL (green) boost converters in DCM and DCM 7.                                                                  | 8(  |

| Figure 3.36. Bode plots of the transfer function $G_{vd}(s)$ for the 2L (blue) and CL (green) boost converters in DCM and DCM 8.                            | . 108 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Figure 3.37. Bode plots of the transfer function $G_{vd}(s)$ for the 2L (blue) and CL (green) boost converters in DCM and DCM 9.                            | . 109 |

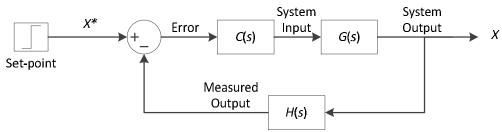

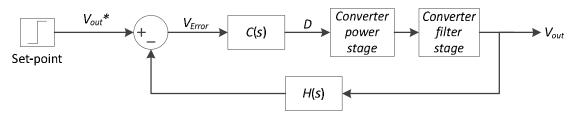

| Figure 4.1. Typical closed-loop control block diagram.                                                                                                      | . 116 |

| Figure 4.2. Voltage-mode control scheme for a dc-dc converter.                                                                                              | . 117 |

| Figure 4.3. Block diagram of hysteretic control.                                                                                                            | . 118 |

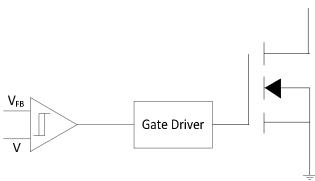

| Figure 4.4. Block diagram of peak-current-mode control.                                                                                                     | . 119 |

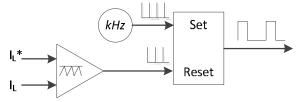

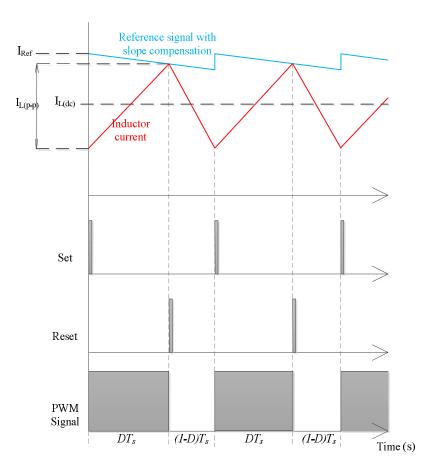

| Figure 4.5. Comparator diagram of peak-current mode control                                                                                                 | . 119 |

| Figure 4.6. PWM signal generator for peak-current mode control                                                                                              | . 120 |

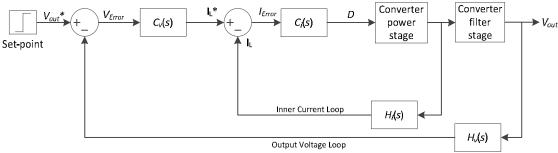

| Figure 4.7. Block diagram of average-current mode control.                                                                                                  | . 121 |

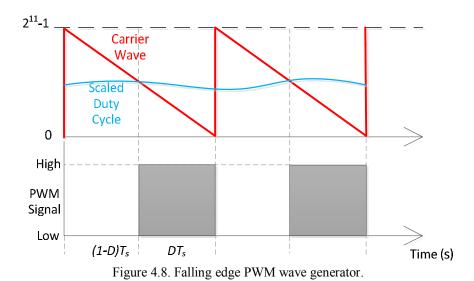

| Figure 4.8. Falling edge PWM wave generator.                                                                                                                | . 124 |

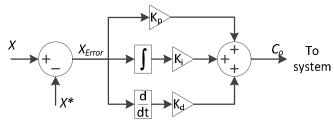

| Figure 4.9. Block diagram of PID controller.                                                                                                                | . 125 |

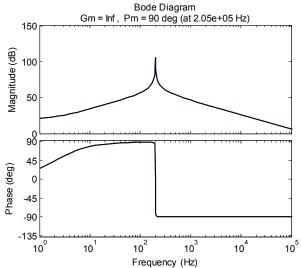

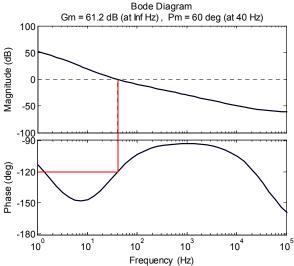

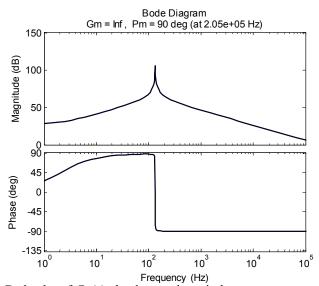

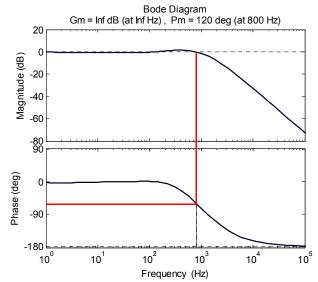

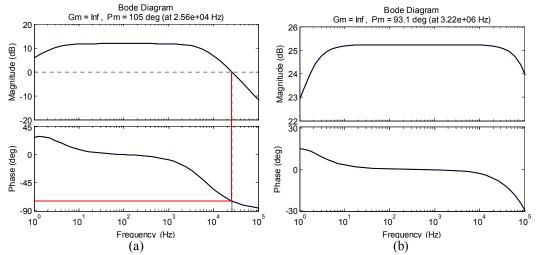

| Figure 4.10. Theoretical Bode plot of $G_{id}(s)$ , the duty cycle-to-inductor current transfer function.                                                   | . 126 |

| Figure 4.11. Theoretical Bode plot of the open-loop current loop of the CL boost converter in CCM.                                                          | . 127 |

| Figure 4.12. Theoretical Bode plot of the closed-loop current loop of the CL boost converter in CCM.                                                        | . 128 |

| Figure 4.13. Theoretical Bode plot of $G_{vi}(s)$ , the inductor current-to-output voltage transfer function.                                               | . 128 |

| Figure 4.14. Theoretical Bode plot of the open-loop current loop of the CL boost converter in CCM.                                                          | . 129 |

| Figure 4.15. Theoretical Bode plot of the closed-loop current loop of the CL boost converter in CCM.                                                        | . 129 |

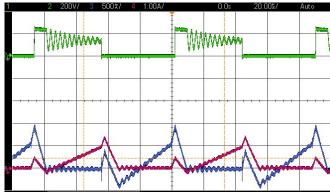

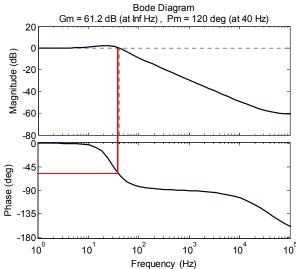

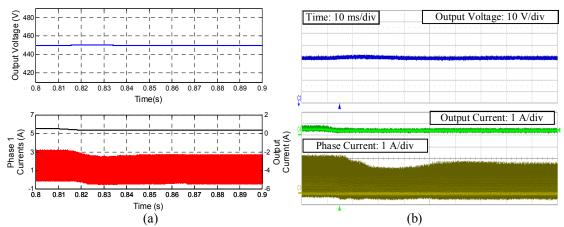

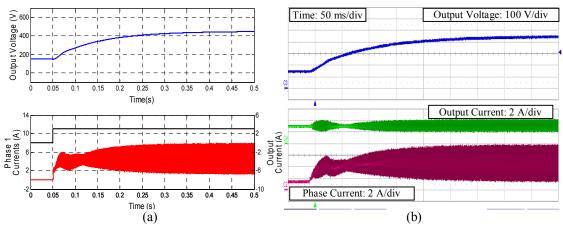

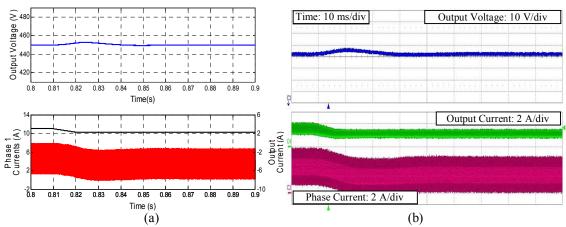

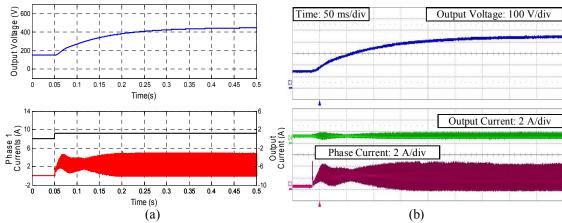

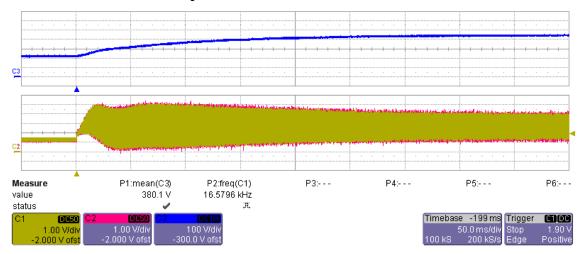

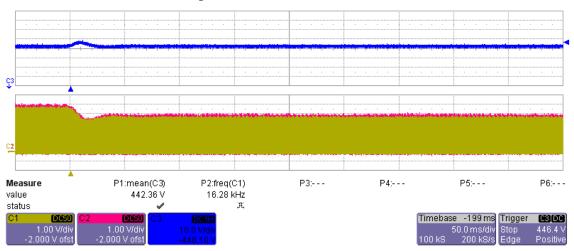

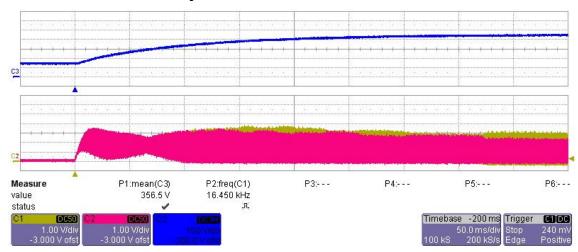

| Figure 4.16. Simulated (a) and experimental (b) response of the closed-loop CL boost converter operating in CCM during start-up.                            | . 130 |

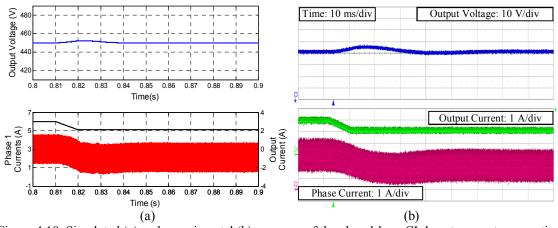

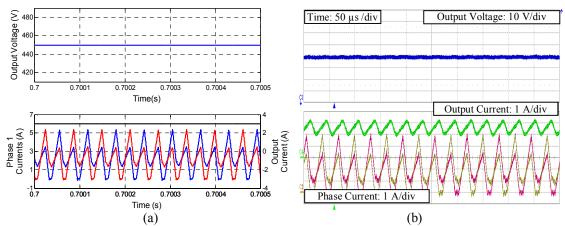

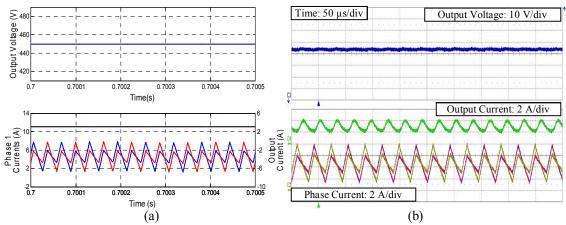

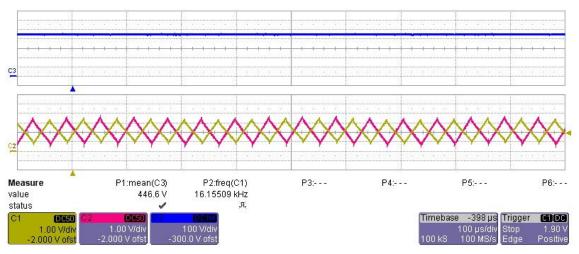

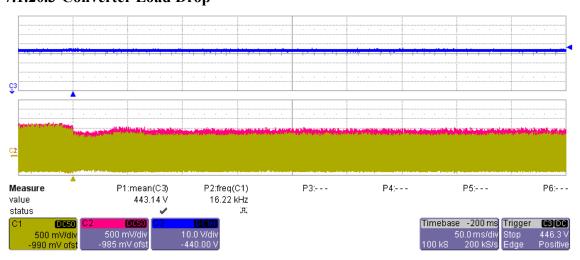

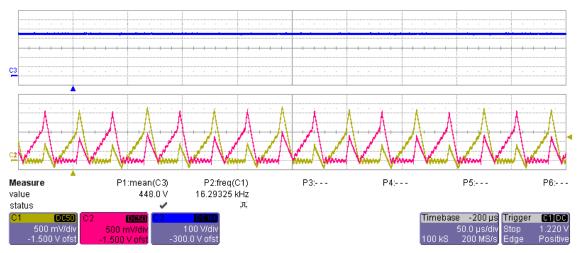

| Figure 4.17. Simulated (a) and experimental (b) response of the closed-loop CL boost converter operating in CCM during steady-state operation.              | . 131 |

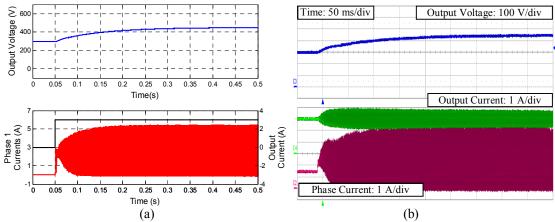

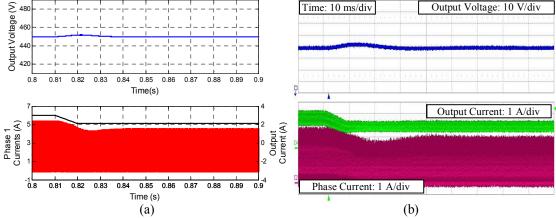

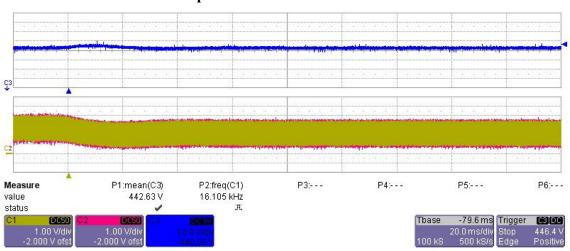

| Figure 4.18. Simulated (a) and experimental (b) response of the closed-loop CL boost converter operating in CCM during load step test                       | . 131 |

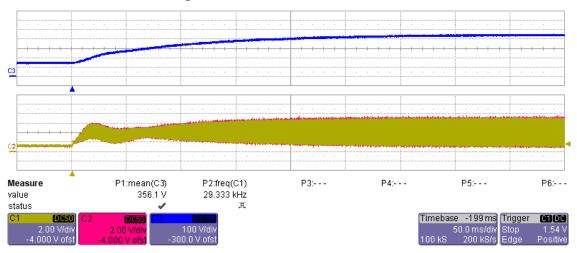

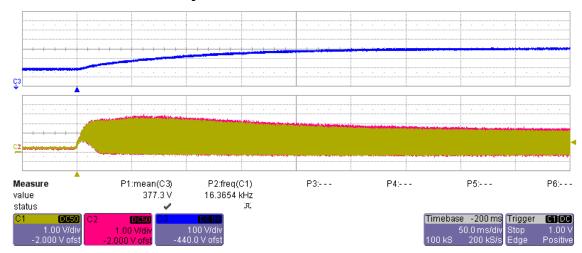

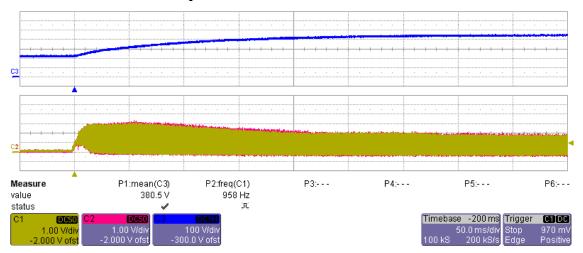

| Figure 4.19. Simulated (a) and experimental (b) response of the closed-loop CL boost converter utilizing CCM controllers operating in DCM 1 during start-up | . 132 |

| Figure 4.20. Simulated (a) and experimental (b) response of the closed-loop CL boost converter utilizing CCM controllers operating in DCM 1 during steady-state.         | 132   |

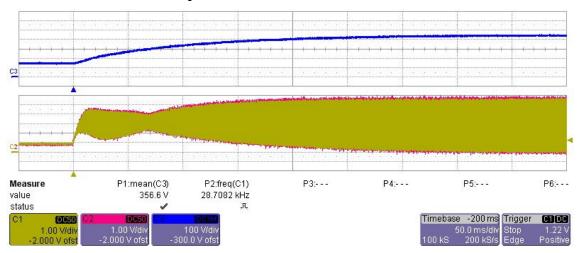

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Figure 4.21. Simulated (a) and experimental (b) response of the closed-loop CL boost converter utilizing CCM controllers operating in DCM 1 during a load step response. | . 132 |

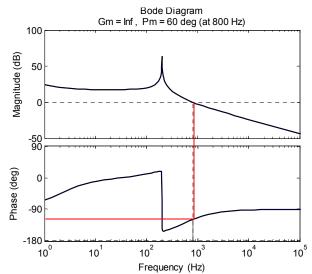

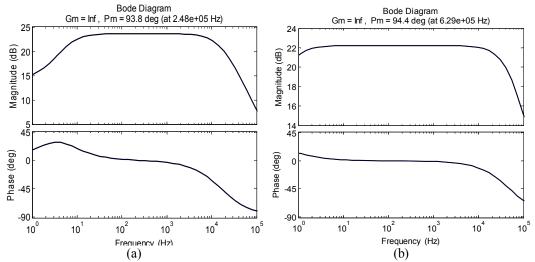

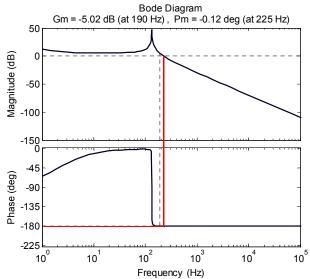

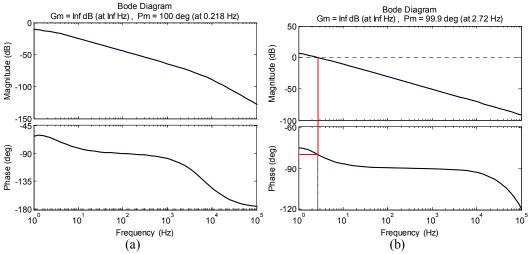

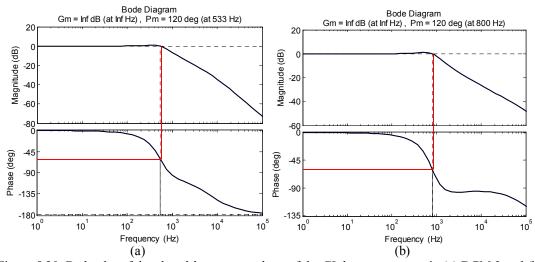

| Figure 4.22. Bode plot of $G_{id}(s)$ , the duty cycle-to-inductor current transfer function of (a) DCM 1 and (b) DCM 9.                                                 | . 133 |

| Figure 4.23. Bode plot of the open-loop current loop of the CL boost converter in (a) DCM1 and (b) DCM 9.                                                                | 134   |

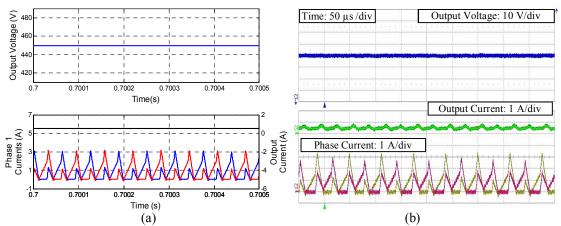

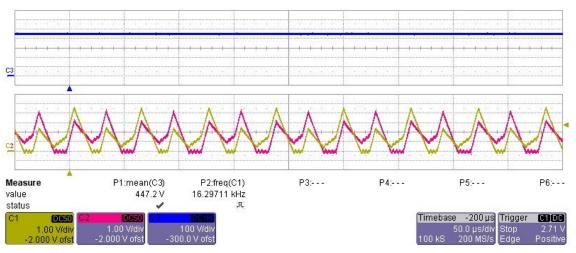

| Figure 4.24. Bode plot of the closed-loop current loop of the CL boost converter in (a) DCM 1 and (b) DCM 9.                                                             | . 134 |

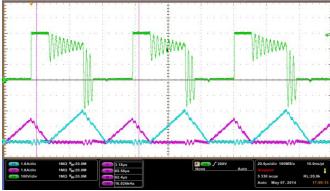

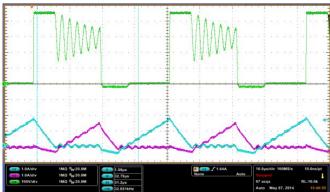

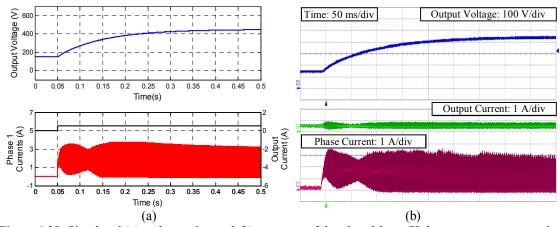

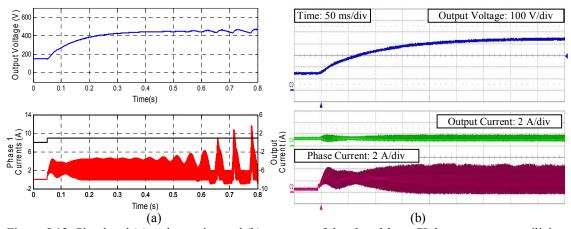

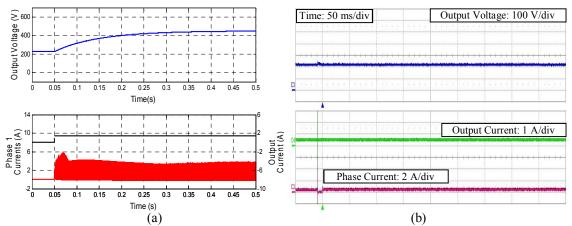

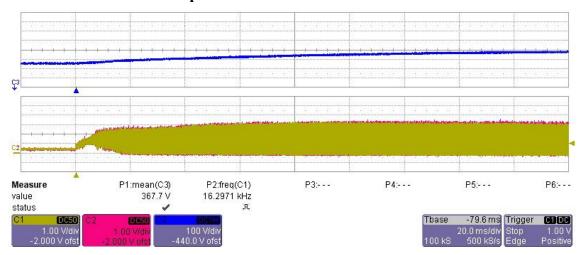

| Figure 4.25. Simulated (a) and experimental (b) response of the closed-loop CL boost converter operating in DCM 1 during start-up.                                       | . 135 |

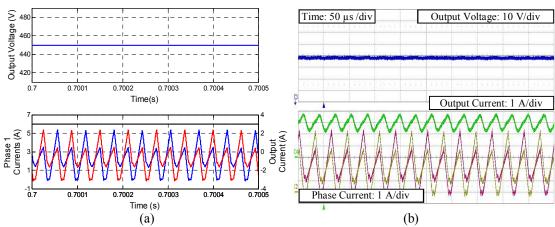

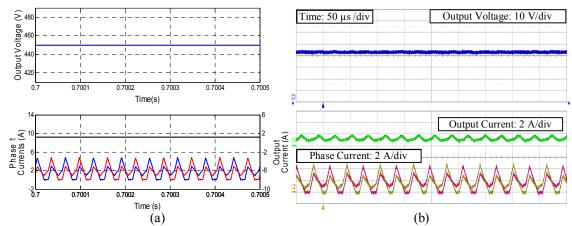

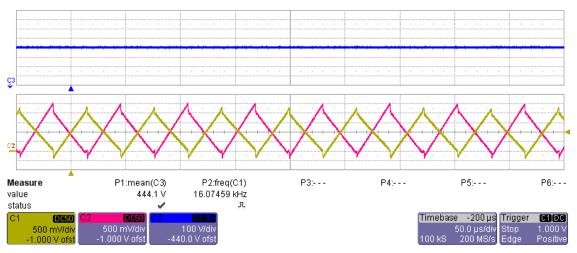

| Figure 4.26. Simulated (a) and experimental (b) response of the closed-loop CL boost converter operating in DCM 1 during steady-state operation.                         | 135   |

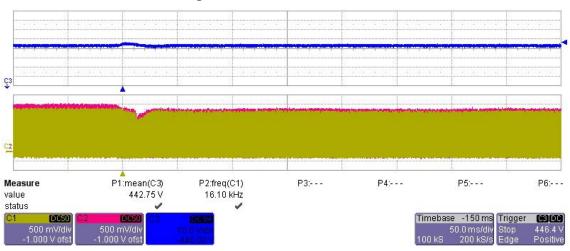

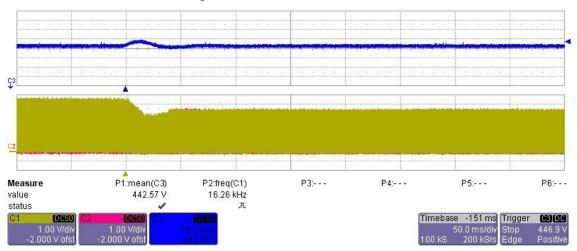

| Figure 4.27. Simulated (a) and experimental (b) response of the closed-loop CL boost converter operating in DCM 1 during load step test.                                 | . 136 |

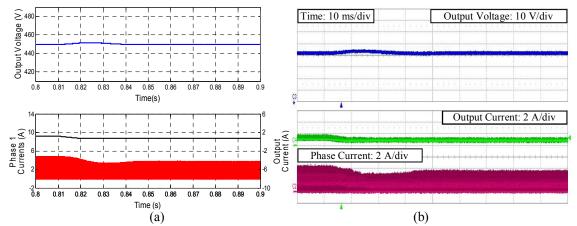

| Figure 4.28. Simulated (a) and experimental (b) response of the closed-loop CL boost converter operating in DCM 9 during start-up.                                       | . 136 |

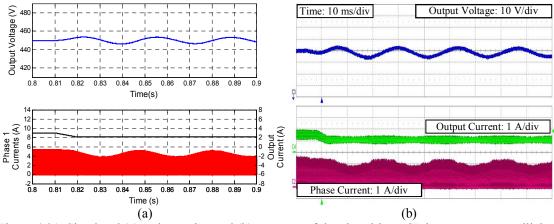

| Figure 4.29. Simulated (a) and experimental (b) response of the closed-loop CL boost converter operating in DCM 9 during steady-state operation.                         | 137   |

| Figure 4.30. Simulated (a) and experimental (b) response of the closed-loop CL boost converter operating in DCM 9 during load step test.                                 | . 137 |

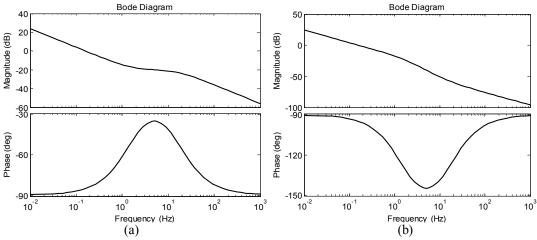

| Figure 5.1. Bode plots of Type II compensator when (a) $\omega_z < \omega_p$ , and (b) $\omega_z > \omega_p$                                                             | 145   |

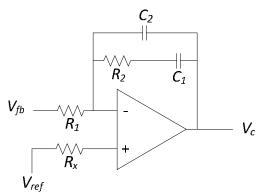

| Figure 5.2. Op-amp design of Type II compensator.                                                                                                                        | 146   |

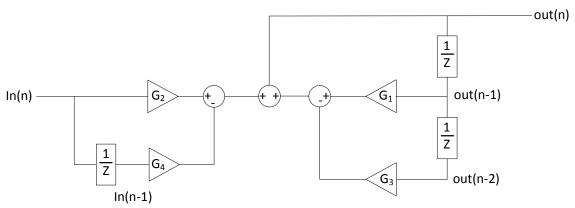

| Figure 5.3. Block diagram of the difference equation for a Type II compensator                                                                                           | . 147 |

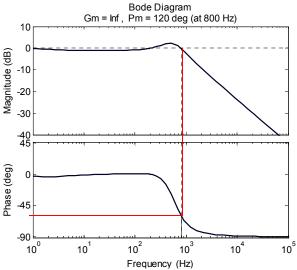

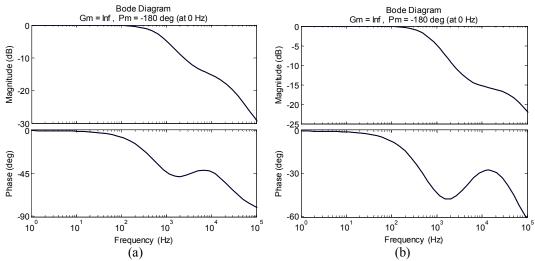

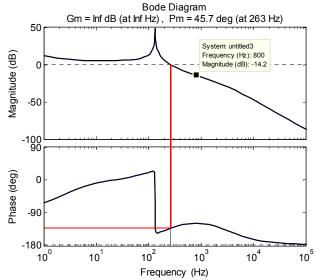

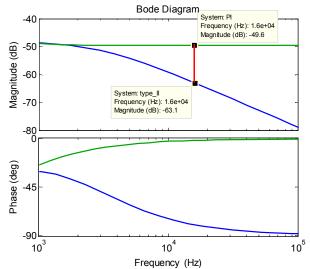

| Figure 5.4. Bode plot of $G_{id}(s)$ , the duty cycle-to-inductor current transfer function.                                                                             | . 148 |

| Figure 5.5. The effect of the addition of the integrator in the $G_{id}(s)$ during CCM operation.                                                                        | . 149 |

| Figure 5.6. Open-loop Bode plot of the Type II compensator and system with controller gain set to 1                                                                      | 150   |

| Figure 5.7. Open-loop frequency response of the inner current loop utilising a Type II compensator                                                                       | 150   |

| Figure 5.8. Closed-loop frequency response of inner current loop utilising a Type II compensator                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 5.9. Frequency response of C(s) as a PI controller (green) and a Type II compensator (blue)                                                                     |

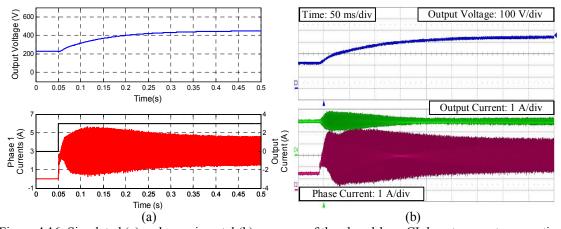

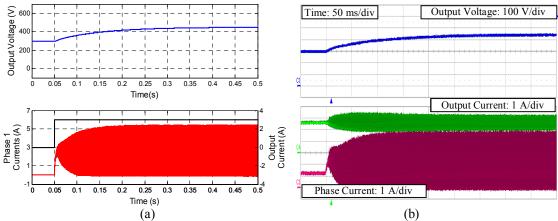

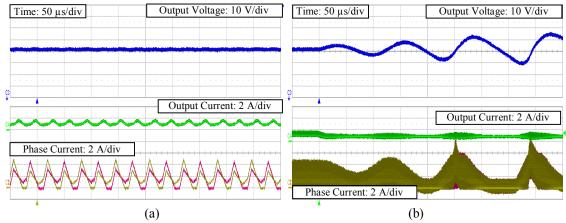

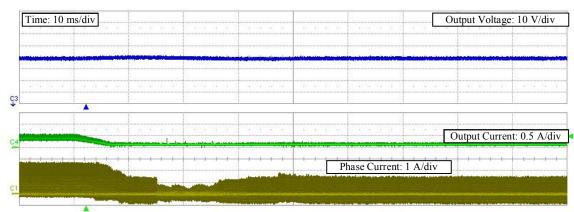

| Figure 5.10. Simulated (a) and experimental (b) response of the closed-loop CL boost converter operating in CCM during start-up.                                       |

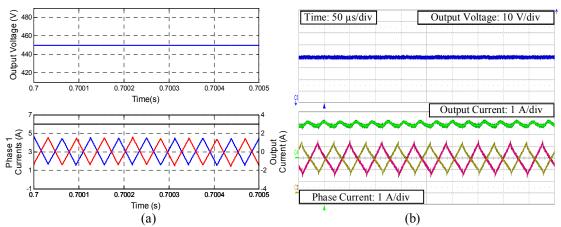

| Figure 5.11. Simulated (a) and experimental (b) response of the closed-loop CL boost converter operating in CCM during steady-state operation                          |

| Figure 5.12. Simulated (a) and experimental (b) response of the closed-loop CL boost converter operating in CCM during load-step test                                  |

| Figure 5.13. Simulated (a) and experimental (b) response of the closed-loop CL boost converter utilizing CCM controllers operating in DCM 3 during start-up 154        |

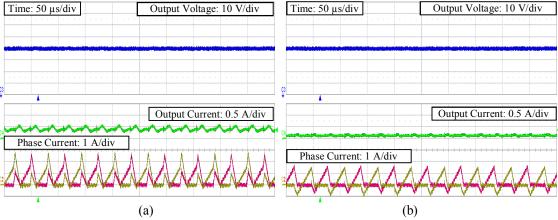

| Figure 5.14. Experimental response of the closed-loop CL boost converter utilizing CCM controllers operating in DCM 8 during steady-state (a), and load-step test (b). |

| Figure 5.15. Experimental response of the closed-loop CL boost converter operating in CCM during steady-state operation at 0.7 A (a), and 1.2 A (b)                    |

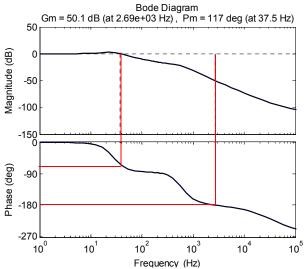

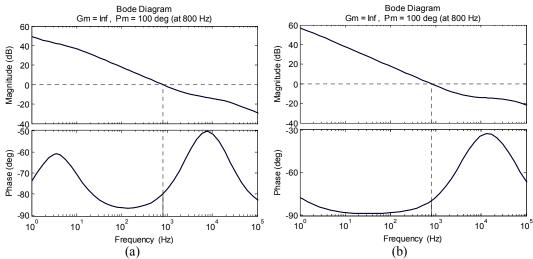

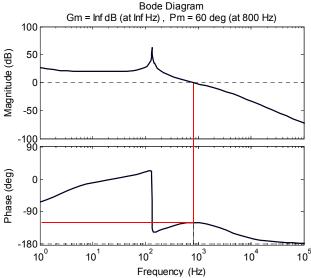

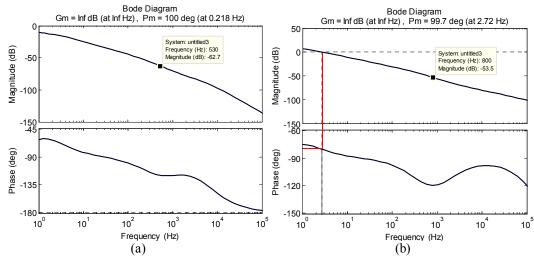

| Figure 5.16. Bode plot of $G_{id}(s)$ , the duty cycle-to-inductor current transfer function of (a) DCM 3 and (b) DCM 8.                                               |

| Figure 5.17. The effect of the addition of the integrator in the $G_{id}(s)$ during (a) DCM 3 and (b) DCM 8.                                                           |

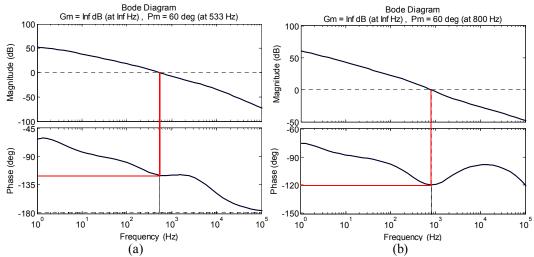

| Figure 5.18. Open-loop Bode plot of the Type II compensator and system with controller gain set to 1 during (a) DCM 3, and (b) DCM 8                                   |

| Figure 5.19. Open-loop frequency response of the inner current loop utilising a Type II compensator during (a) DCM 3 and (b) DCM 8.                                    |

| Figure 5.20. Bode plot of the closed-loop current loop of the CL boost converter in (a) DCM 3 and (b) DCM 8 utilizing a Type II compensator                            |

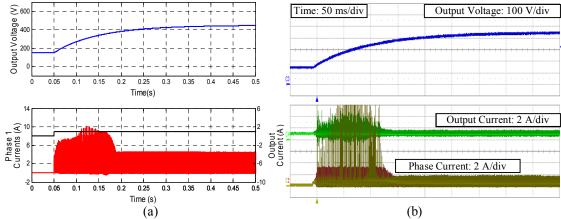

| Figure 5.21. Simulated (a) and experimental (b) response of the closed-loop CL boost converter operating in DCM 3 during start-up.                                     |

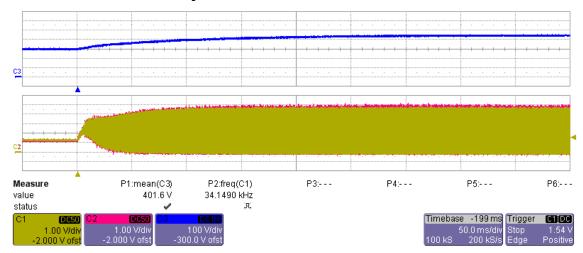

| Figure 5.22. Simulated (a) and experimental (b) response of the closed-loop CL boost converter operating in DCM 8 during start-up over 500 ms                          |

| Figure 5.23. Simulated (a) and experimental (b) response of the closed-loop CL boost converter operating in DCM 8 during start-up over 100 ms                          |

| Figure 5.24. Bumpless control strategy                                                                                                                                 |

| Figure 5.25. CCM-DCM mode map of the CL converter, showing the input current at which the converter leaves CCM 2 and enters DCM 8                                      |

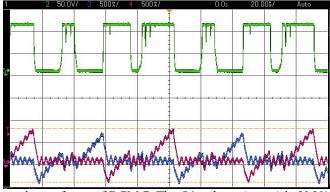

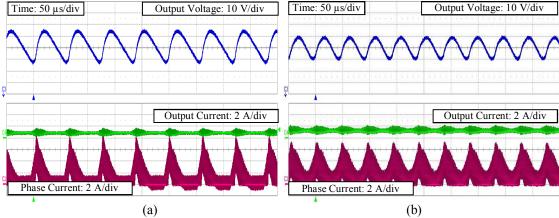

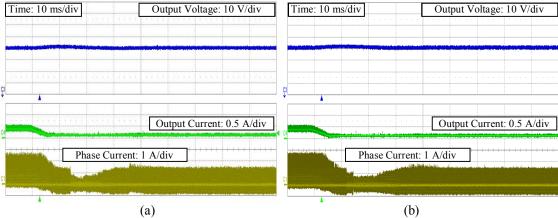

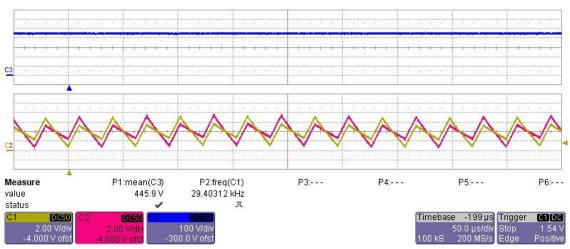

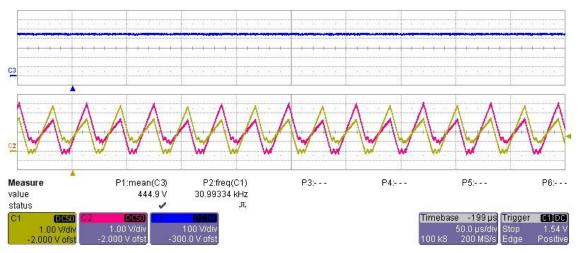

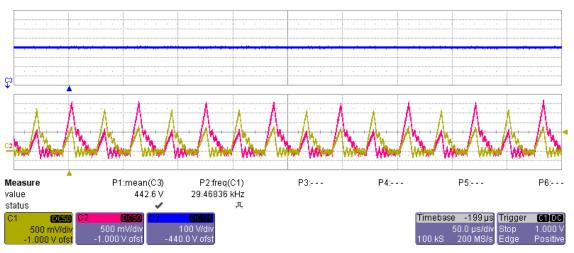

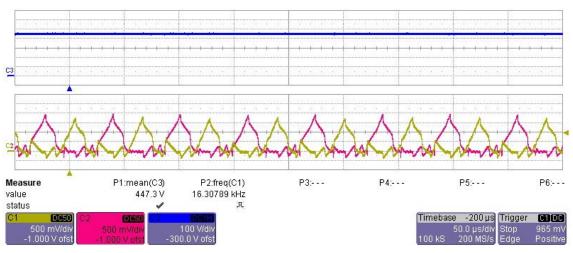

| Figure 5.26. Experimental steady-state waveforms of DCM 9 (a) and DCM 7 (b) under PI control                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

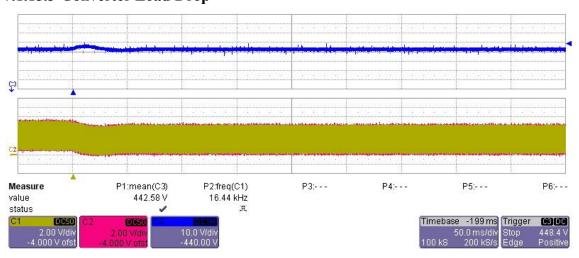

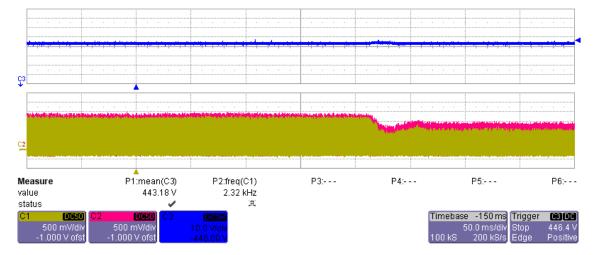

| Figure 5.27. Experimental results of the load-step drop, causing the converter to leave DCM 9 and enter DCM 7 utilising PI controllers with bumpless control 164        |

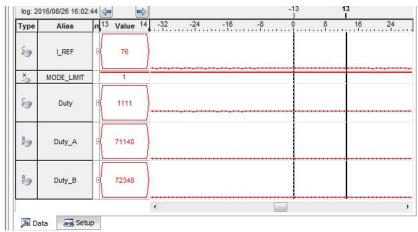

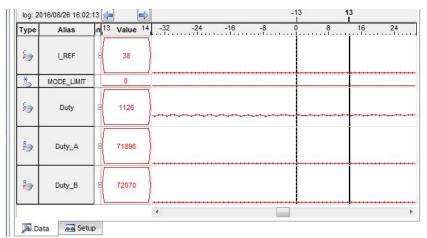

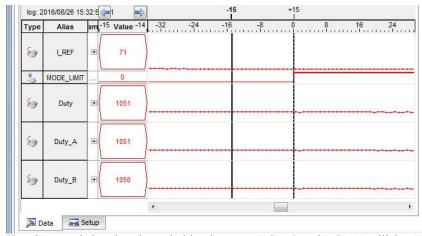

| Figure 5.28. SignalTap tool showing operation during DCM 9 utilising PI controller with bumpless control                                                                |

| Figure 5.29. SignalTap tool showing operation during DCM 7 utilising PI controller with bumpless control                                                                |

| Figure 5.30. SignalTap tool showing the moment of switching between DCM 9 and DCM 7 utilising PI controller with bumpless control                                       |

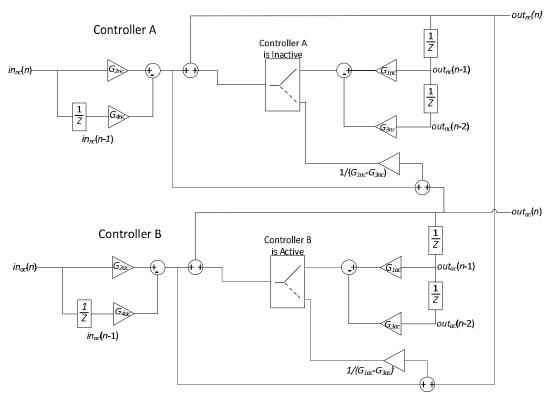

| Figure 5.31. Block Diagram of Forced-Output Control for two Type II compensators                                                                                        |

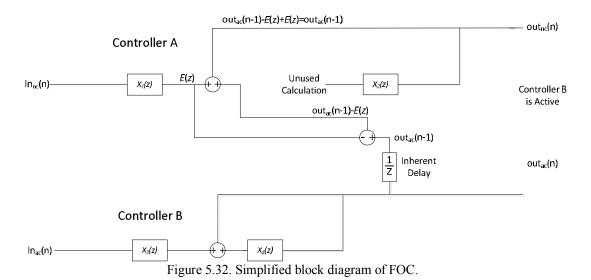

| Figure 5.32. Simplified block diagram of FOC. 169                                                                                                                       |

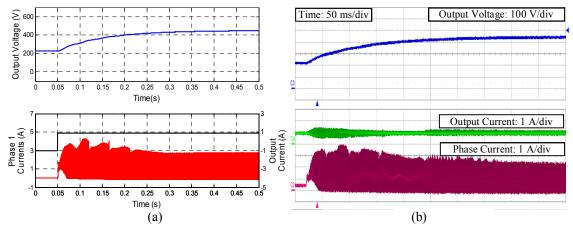

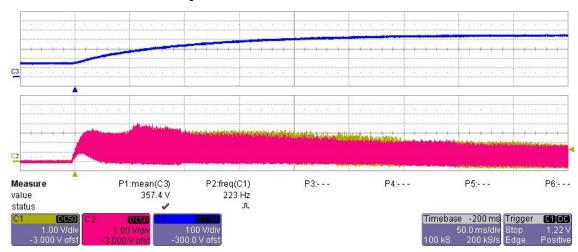

| Figure 5.33. Simulated (a) and experimental (b) response of the closed-loop CL boost converter operating in CCM during start-up                                         |

| Figure 5.34. Simulated (a) and experimental (b) response of the closed-loop CL boost converter operating in CCM during steady-state operation                           |

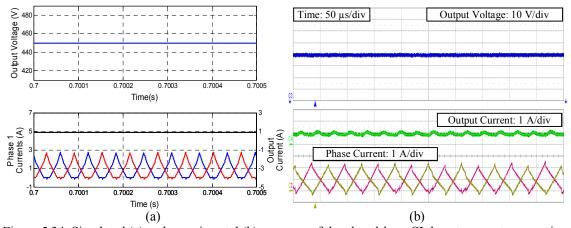

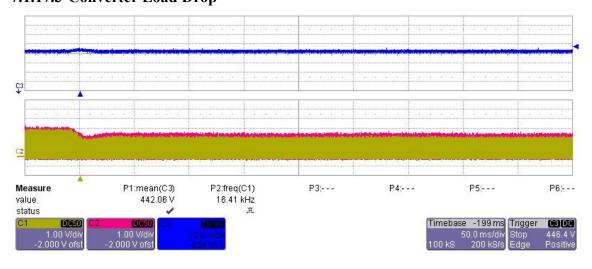

| Figure 5.35. Simulated (a) and experimental (b) response of the closed-loop CL boost converter operating in CCM during load-step test                                   |

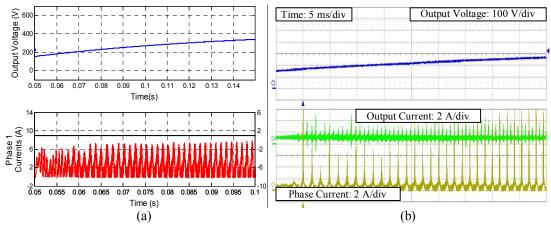

| Figure 5.36. Simulated (a) and experimental (b) response of the closed-loop CL boost converter operating in CCM during start-up                                         |

| Figure 5.37. Simulated (a) and experimental (b) response of the closed-loop CL boost converter operating in CCM during steady-state operation                           |

| Figure 5.38. Simulated (a) and experimental (b) response of the closed-loop CL boost converter operating in CCM during load-step test                                   |

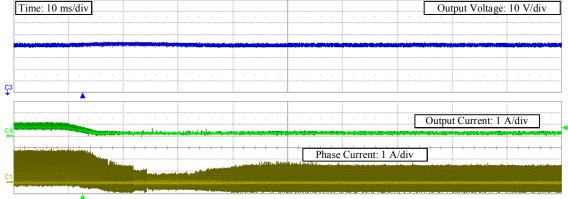

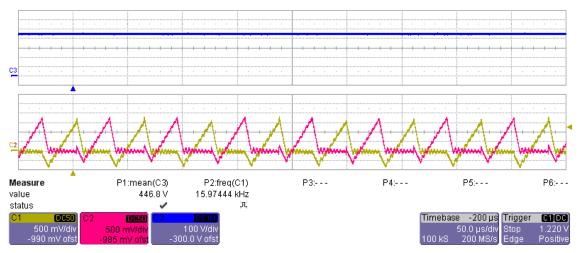

| Figure 5.39. Experimental steady-state waveforms of DCM 9 (a) and DCM 7 (b) under Type II compensator control                                                           |

| Figure 5.40. Experimental results of the load-step drop, causing the converter to leave DCM 9 and enter DCM 7 utilising Type II compensators with FOC                   |

| Figure 5.41. A comparison of controller and mode change from DCM 9 to DCM 7 utilising FOC (a) and bumpless control (b)                                                  |

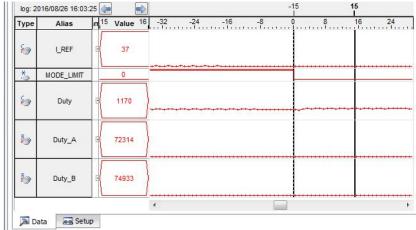

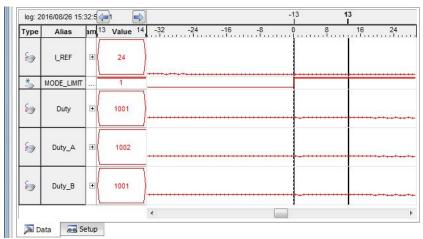

| Figure 5.42. SignalTap tool showing the switching between DCM 9 and DCM 7 utilising Forced-Output control controller with bumpless control (Duty cycles before switch). |

| Figure 5.43. SignalTap tool showing the switching between DCM 9 and DCM 7 utilising Forced-Output control controller with bumpless control (Duty cycles after switch).  |

| Figure 7.1. Bidirectional dc-dc converter with dc motor and battery | 186 |

|---------------------------------------------------------------------|-----|

| Figure 7.2. Output current CCM-DCM mode map for 1L buck converter   | 187 |

| Figure 7.3. Output current CCM-DCM mode map for 2L buck converter   | 188 |

| Figure 7.4. Output current CCM-DCM mode map for CL buck converter.  | 189 |

# LIST OF TABLES

| (2L) interleaved boost converter                                                                                                     | 43  |

|--------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 2.2. Sub-modes of operation and quad-state Y solutions for a CL interleaved boost converter.                                   | 43  |

| Table 2.3. Peak-to-peak ripple currents for the input, magnetizing and phase currents of a CL boost converter when operating in CCM. | 46  |

| Table 3.1. Leakage inductance values of the boost CL converters for the same peak-to-peak conditions as a 2L converter.              | 103 |

| Table 7.1. Peak-to-peak ripple currents for the input, magnetizing and phase currents of a CL buck converter when operating in CCM.  | 189 |

## NOMENCLATURE

| dc                                   | direct current                                                                                                                                                                                                           |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ac                                   | alternating current                                                                                                                                                                                                      |

| CCM                                  | Continuous conduction mode                                                                                                                                                                                               |

| DCM                                  | Discontinuous conduction mode                                                                                                                                                                                            |

| BCM                                  | Boundary conduction mode                                                                                                                                                                                                 |

| 1L                                   | Single-phase converter                                                                                                                                                                                                   |

| 2L                                   | Two-phase converter                                                                                                                                                                                                      |

| CL                                   | Coupled-inductor converter                                                                                                                                                                                               |

| RMS                                  | Root-mean-square                                                                                                                                                                                                         |

| PV                                   | Photovoltaic                                                                                                                                                                                                             |

| EV                                   | Electric vehicle                                                                                                                                                                                                         |

| HEV                                  | Hybrid electric vehicle                                                                                                                                                                                                  |

| FCEV                                 | Fuel-cell electric vehicle                                                                                                                                                                                               |

| SiC                                  | Silicon Carbide                                                                                                                                                                                                          |

| GaN                                  | Gallium Nitride                                                                                                                                                                                                          |

| PFC                                  | Power factor correction                                                                                                                                                                                                  |

| THD                                  | Total harmonic distortion                                                                                                                                                                                                |

|                                      |                                                                                                                                                                                                                          |

| MPPT                                 | Maximum-power-point tracking                                                                                                                                                                                             |

|                                      | Maximum-power-point tracking  Power control unit                                                                                                                                                                         |

| PCU                                  |                                                                                                                                                                                                                          |

| PCUSWIM                              | Power control unit                                                                                                                                                                                                       |

| PCUSWIM                              | Power control unit Split winding integrated magnetic Field-programmable gate array                                                                                                                                       |

| PCUSWIMFPGAOC                        | Power control unit Split winding integrated magnetic Field-programmable gate array                                                                                                                                       |

| PCUSWIMFPGAOCRB IGBT                 | Power control unit Split winding integrated magnetic Field-programmable gate array Open-circuit                                                                                                                          |

| PCUSWIMFPGAOCRB IGBTPWM              | Power control unit Split winding integrated magnetic Field-programmable gate array Open-circuit Reverse blocking IGBT                                                                                                    |

| PCUSWIMFPGAOCRB IGBTPWMACMC          | Power control unit Split winding integrated magnetic Field-programmable gate array Open-circuit Reverse blocking IGBT Pulse-width modulation                                                                             |

| PCUSWIMSWIMSPGAOC                    | Power control unit Split winding integrated magnetic Field-programmable gate array Open-circuit Reverse blocking IGBT Pulse-width modulation Average-current-mode control                                                |

| PCUSWIMFPGAOCRB IGBTPWMACMCVMCVMC    | Power control unit Split winding integrated magnetic Field-programmable gate array Open-circuit Reverse blocking IGBT Pulse-width modulation Average-current-mode control Peak-current-mode control                      |

| PCUSWIMFPGAOCRB IGBTPWMACMCVMCADCADC | Power control unit Split winding integrated magnetic Field-programmable gate array Open-circuit Reverse blocking IGBT Pulse-width modulation Average-current-mode control Peak-current-mode control Voltage-mode control |

| RHP Zero              | Right half plane zero                                                |

|-----------------------|----------------------------------------------------------------------|

| ESR                   | Equivalent series resistance                                         |

| $G_{\text{m}}$        | Gain margin                                                          |

| P <sub>m</sub> .      | Phase margin                                                         |

| PLC_                  | Phase lead/lag compensator                                           |

| FOC                   | Forced-output control                                                |

| NEDC                  | New European driving cycle                                           |

| EMI_                  | Electromagnetic interference                                         |

| CM                    | Common mode                                                          |

| V <sub>in.</sub>      | Input voltage                                                        |

| V <sub>out</sub>      | Output voltage                                                       |

| V <sub>Llkx.y</sub>   | Leakage inductance voltage drop over cycle time x in phase y         |

| $V_{Tx.y}$            | Magnetizing inductance voltage drop over cycle time $x$ in phase $y$ |

| I <sub>in(DC)</sub>   | _dc input current                                                    |

| $I_{Lx}$              | _Inductor current of phase x                                         |

| $I_{L(DC)}$           | _dc inductor current                                                 |

| $I_{L(RMS)}$          | Inductor RMS current                                                 |

| <i>I</i> <sub>o</sub> | _dc output current                                                   |

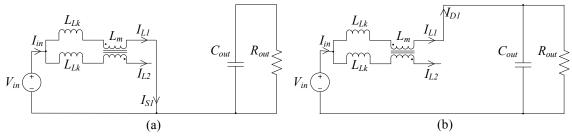

| $I_{SI}$              | _dc switch current                                                   |

| $I_{DI}$              | _dc diode current                                                    |

| $I_{oB}$              | Output current when converter is in BCM                              |

| $I_{oB,max}$          | Maximum output current when converter is in BCM                      |

| $\Delta I_{L(p-p)}$   | Peak-to-peak inductor current                                        |

| $\Delta I_{m(p-p)}$   | Peak-to-peak magnetizing current                                     |

| $\Delta I_{in(p-p)}$  | Peak-to-peak input current                                           |

| $I_{LxB}$             | Phase current of phase x when converter is in BCM                    |

| $T_s$                 | PWM switching cycle time                                             |

| $f_s$                 | PWM switching frequency                                              |

| <i>L</i>              | Phase inductance                                                     |

| $L_x$                 | Phase inductance of phase x                                          |

| $L_{Lk}$              | Leakage inductance                                                   |

| $L_{m}$               | Magnetizing inductance                                               |

| Rout                  | Output resistance                                                    |

| Cout                  | Output capacitance                                                   |

| $C_{in}$              | Input capacitance                                                    |

| $P_{in}$              | _Input power                                              |

|-----------------------|-----------------------------------------------------------|

| P <sub>out</sub> .    | Output power                                              |

| η                     | Efficiency                                                |

| D                     | _Duty cycle                                               |

| $D_{\it off}$         | Diode conduction time                                     |

| $D_x$                 | Cycle time x                                              |

| <i>Qx</i>             | Semiconductor switch in phase <i>x</i>                    |

| $V_{Qx}$              | Pole voltage across the semiconductor switch of phase $x$ |

| $V_{LV}$              | Low-side voltage                                          |

| $V_{HV}$              | High-side voltage                                         |

| $C_{LV}$              | _Low-side capacitance                                     |

| $C_{HV}$              | High-side capacitance                                     |

| $G_{vv}(s)$           | Input voltage-to-output voltage transfer function         |

| $G_{vd}(s)$           | Duty cycle-to-output voltage transfer function            |

| $G_{vi}(s)$           | _Inductor current-to-output voltage transfer function     |

| $G_{di}(s)$           | Duty cycle-to-output voltage transfer function            |

| <i>G</i> ( <i>s</i> ) | Plant transfer function                                   |

| <i>C</i> ( <i>s</i> ) | Controller transfer function                              |

| <i>H</i> ( <i>s</i> ) | Sensor transfer function                                  |

| fc                    | _crossover frequency                                      |

| $\varphi_m$           | Phase margin                                              |

| $\varphi_{boost}$     | Desired phase injection                                   |

| <i>N</i>              | Ratio of leakage inductance to magnetizing inductance     |

| $K_p$                 | Proportional gain                                         |

| <i>K</i> <sub>i</sub> | _Integral gain                                            |

| $K_d$                 | _Derivative gain                                          |

| <i>K</i> <sub>c</sub> | Type-II compensator gain                                  |

| $\omega_p$            | Frequency of pole                                         |

| $\omega_{z_{$         | Frequency of zero                                         |

| $T_{Ds}$              | Discrete sampling time                                    |

## 1 Introduction

This chapter presents an overview of the research topics discussed in this thesis. The body of work presented is focused on the implementation, mathematical modelling and control of non-isolated multi-phase dc-dc converters utilizing coupled inductors. The applications of dc-dc converters range from the high-power, high-current automotive and renewable sectors, to the low-power, low-current consumer electronics sector, such as laptop and mobile phone chargers. This chapter presents the current technology used in such applications, as well as the motivation for the development and implementation of high-efficiency, low-box-volume magnetic components.

#### 1.1 Overview

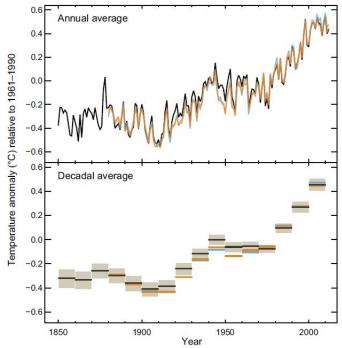

The year 2015 is on record for being, on average, the warmest year since official records began in 1880 [1.1]. Figure 1.1 presents the average global temperature difference per year for over the last 100 years [1.2].

Figure 1.1. Observed globally averaged combined land and ocean surface temperature anomaly 1850-2012 [1.2].

As can be seen from Figure 1.1, the global temperature has risen by approximately 1°C in the last 100 years. A growing worry among the scientific community is that this temperature rise may be man-made, due to the high levels of greenhouse gases such as carbon dioxide being produced every day. Another worrying trend in today's economy is the volatility of oil prices, as well as the threat of oil and gas shortages. The current estimation of oil reserves left globally is approximated at 1,500 billion barrels, much of which are located in countries with volatile political and social environments [1.3].

Hence, in recent years there has been a growing push into the area of clean and renewable energy. In 2014, it was estimated that 19% of the world's energy consumption was supplied via renewable energy sources, 9% of which is coming from traditional biomass, while the remaining 10% coming from modern renewable energy sources such as wind turbines, hydroelectric dams, and photovoltaic (PV) cells [1.4]. Global leaders such as the United States and China are beginning to invest heavily in the renewable energy sector while in Europe, Germany is spearheading a PV initiative in an attempt to completely phase out nuclear power from the country. Smaller countries are also beginning to take part in this energy revolution. For example, in 2015,

24% of both the Republic of Ireland's and Northern Ireland's energy demands were met with wind power, supplied by a total of 235 wind farms on the island [1.5].

Another global initiative which is gaining traction in recent years is the introduction of environmentally-friendly vehicles. A large portion of the greenhouse gases produced globally comes from the transportation sector, with an estimated 26% of emissions coming from transportation in 2014 [1.6]. In an effort to cut down on these emissions, Electric Vehicles (EV), Hybrid Electric Vehicles (HEV), and Fuel-Cell Electric Vehicles (FCEV) are quickly becoming more favourable than internal combustion engine vehicles. Companies such as Tesla, Nissan, GM, and Ford have realised the market potential for such technology, and are spearheading this transportation revolution.

A key part of HEVs and FCEVs is the power converter. Various types of power converter topologies are found in many areas of this industry. For example, a high-power boost converter is essential in a fuel-cell vehicle to buffer the poorly-regulated output voltage of the PEM fuel-cell, and efficiently distribute this voltage to the traction-motor inverters [1.7]-[1.10]. Similarly, the THS II HEV power-train, developed by the Toyota Motor Company, features a high-power single-phase dc-dc converter to interface the battery pack to the high-voltage dc link [1.11]-[1.12]. In regards to renewable energies, dc-dc converters are essential in PV systems for stabilization of the dc-link voltage as well as for Maximum-Power-Point Tracking (MPPT) [1.13]-[1.16]. Power converters are also critical components of ac and dc microgrids [1.17]. The utilization of power converters in microgrids can contribute to grid stability, as well as improved efficiency when importing from the national grid to on-site microgrids.

For renewable and automotive applications, the single-phase buck or boost converter is the most commonly used converter. With the ever growing demand for higher power, designers are now looking at multi-phase converters, so as to reduce size, cost, and power losses. The downside to this approach is the addition of more magnetic components into the system; more specifically inductors. In addition, the recent advancements in wide-band-gap materials such as the Silicon-Carbide (SiC) and Gallium-Nitride (GaN) greatly reduce switching losses in semiconductor devices. This allows power converters to operate at a much higher frequency and power-density [1.18].

For these reasons, developers are now looking into decreasing the size and weight of the magnetic components, while increasing the power density. A common solution to this is the use of coupled-inductors and integrated-magnetics. In interleaving applications, coupled-inductors have been shown to reduce the size and weight of the magnetic components when compared to their discrete inductor counterparts, without forfeiting efficiency [1.19].

The objective of this chapter is to give a brief introduction to the layout, motivation and current technology used in today's power converters. Section 1.1 gives a brief overview of the motivation for this body of work, while Section 1.2 presents the objectives of the thesis. Section 1.3 gives a brief summary of each chapter, while Section 1.4 discusses the applications and current technology of power converters. Finally, Section 1.5 gives a brief overview of the dc-dc converters analysed in this thesis, as well as the coupled-inductor used in experimental testing.

# 1.2 Thesis Objectives

The objective of this thesis is the complete mathematical modelling and digital control of the two-phase interleaved coupled-inductor dc-dc converter.

The first objective is to derive the large-signal characteristics of the converter. Due to the nature of a coupled-inductor converter, many of the current waveforms in both Continuous-Conduction Mode (CCM) and Discontinuous-Conduction Mode (DCM) are vastly different to a discrete-inductor converter. This, in turn, causes the converter characteristics to differ greatly, especially in DCM. These characteristics are fully derived for all CCM and DCM modes of the coupled-inductor boost and buck converters.

The second objective is to derive the small-signal model of each CCM and DCM mode of operation. In dc-dc converters, controllers, either analogue or digital, decide the duty cycle so as to ensure that the output voltage on the dc link is at a suitable level. One of the most efficient ways to design such controllers is to first find the transfer functions of the system, and to begin controller design at this starting point. As with the large-signal model, the small-signal models of the coupled-inductor converter differ greatly from the discrete-inductor converter. These models are fully derived for the coupled-inductor boost and buck converters.

The final objective is the complete closed-loop control of the coupled-inductor boost converter. There are several methods of control in power converters. Many ac-dc and dc-dc converters implement voltage-mode control, average-current-mode control, peak-current-mode control and hysteretic control. Due to the number of modes available in a coupled-inductor converter, a control method is implemented for each mode, with the ability to determine which mode the converter is operating in, and determining which controller to use.

Experimental results of each of these objectives are provided.

#### 1.3 Thesis Structure

This thesis is split into five chapters. Chapter 1 gives a brief overview of the motivation and objectives of the research undertaken. The various areas in which power converters are used are discussed. The current technology utilized in today's power electronics industry is investigated, as well as the components.