# Copper Diffusion Barrier Deposition on Integrated Circuit Devices by Atomic Layer Deposition Technique

#### **Kai-Erik Elers**

Laboratory of Inorganic Chemistry

Department of Chemistry

University of Helsinki

Finland

#### **Academic Dissertation**

To be presented with the permission of the Faculty of Science of the University of Helsinki for public criticism in Auditorium A110 of the Department of Chemistry, A. I. Virtasen aukio 1, on November 18<sup>th</sup> 2008 at 12 o'clock noon.

## **Supervisors**

Prof. Markku Leskelä

## **Reviewers**

Prof. David Cameron Dos. Jyrki Molarius

## **Opponent**

Prof. Hyungjun Kim

ISBN 978-952-92-4674-8 (Paperback)

ISBN 978-952-10-5085-5 (PDF)

<a href="http://ethesis.helsinki.fi">http://ethesis.helsinki.fi</a>

Multiprint

Helsinki 2008

#### **ABSTRACT**

Transfer from aluminum to copper metallization and decreasing feature size of integrated circuit devices generated a need for new diffusion barrier process. Copper metallization comprised entirely new process flow with new materials such as low-k insulators and etch stoppers, which made the diffusion barrier integration demanding. Atomic Layer Deposition technique was seen as one of the most promising techniques to deposit copper diffusion barrier for future devices.

Atomic Layer Deposition technique was utilized to deposit titanium nitride, tungsten nitride, and tungsten nitride carbide diffusion barriers. Titanium nitride was deposited with a conventional process, and also with new in situ reduction process where titanium metal was used as a reducing agent. Tungsten nitride was deposited with a well-known process from tungsten hexafluoride and ammonia, but tungsten nitride carbide as a new material required a new process chemistry. In addition to material properties, the process integration for the copper metallization was studied making compatibility experiments on different surface materials. Based on these studies, titanium nitride and tungsten nitride processes were found to be incompatible with copper metal. However, tungsten nitride carbide film was compatible with copper and exhibited the most promising properties to be integrated for the copper metallization scheme. The process scale-up on 300 mm wafer comprised extensive film uniformity studies, which improved understanding of non-uniformity sources of the ALD growth and the process-specific requirements for the ALD reactor design. Based on these studies, it was discovered that the TiN process from titanium tetrachloride and ammonia required the reactor design of perpendicular flow for successful scale-up.

The copper metallization scheme also includes process steps of the copper oxide reduction prior to the barrier deposition and the copper seed deposition prior to the copper metal deposition. Easy and simple copper oxide reduction process was developed, where the substrate was exposed gaseous reducing agent under vacuum and at elevated temperature. Because the reduction was observed efficient enough to reduce thick copper oxide film, the process was considered also as an alternative method to make the copper seed film via copper oxide reduction.

#### **PREFACE**

This work that eventually resulted in my dissertation was started at ASM Microchemistry Oy in year 1999. This work comprised an early phase of copper diffusion barrier studies, and since then a lot of new results have been published by several authors.

I am grateful to my astonishing and unforgettable team in ASM Microchemistry Oy including Sari Kaipio, Ville Saanila, Pekka J. Soininen, Wei-Min Li, and Juhana Kostamo, as well as all other co-authors for their great contribution. From my foreign co-authors I wish to thank particularly Alessandra Satta, Steven Smith, and Wim Besling with whom I worked very closely.

I am very grateful to Prof. Markku Leskelä who has offered me support whenever it was needed. Without his flexibility and patience for my never ending studies, this work would not have taken place. I express my kind gratitude to Prof. Mikko Ritala for introducing me to the wonderful world of ALD.

I am thankful for Pekka Reinikainen who volunteered to read proof of my thesis and made good suggestions.

I am thankful for my loving parents, Marjatta and Nils-Erik who have always given me unquestionable support. Most of all, I am grateful to my wife, Virpi who has been standing close by and been supportive towards my studies.

#### LIST OF PUBLICATIONS

Thesis is composed of the publications listed below. The publications are listed in chronological order and they are referred in the text with a Roman number.

- I A.Satta, M. Baklanov, O. Richard, A. Vantomme, H. Bender, T. Conard, K. Maex, W. M. Li, K.-E. Elers, and S. Haukka: Enhancement of ALCVD TiN growth on Si-O-C and α-SiC:H films by O<sub>2</sub>-based plasma treatments, *Microelectronic Engineering*, 60 (2002) 59.

- II K.-E. Elers, V. Saanila, P.J. Soininen, W.-M. Li, J.T. Kostamo, S. Haukka, J. Juhanoja, W.F.A. Besling: The diffusion barrier deposition on copper surface by atomic layer deposition technique, *Chem. Vap. Deposition*, 8 (2002) 149.

- III S. Smith,W.-M. Li, K.-E. Elers, K. Pfeifer: Physical and electrical characterization of ALCVD TiN and WN<sub>x</sub>C<sub>y</sub> used as a copper diffusion barrier in dual damascene backend structures (08.2), *Microelectronic Engineering*, 64 (2002) 247.

- IV K.-E. Elers, V. Saanila, W.-M. Li, P.J. Soininen, J.T. Kostamo, S. Haukka, J. Juhanoja, W.F.A. Besling: Atomic layer deposition of W<sub>x</sub>N/TiN and WN<sub>x</sub>C<sub>y</sub>/TiN nanolaminates, *Thin Solid Films*, 434 (2003) 94.

- V P.J. Soininen, K.-E. Elers, V. Saanila, S. Kaipio, T. Sajavaara, S. Haukka: Reduction of Copper Oxide Film to Elemental Copper, *Journal of the Electrochemical Society*, 152 (2005) G122.

- VI K.-E. Elers, J. Winkler, K. Weeks, S. Marcus: TiCl<sub>4</sub> as a Precursor in the TiN Deposition by ALD and PEALD, *Journal of the Electrochemical Society*, 152 (2005) G589.

- VII K.-E. Elers, T. Blomberg, M. Peussa, B. Aitchison, S. Haukka, S. Marcus: Film Uniformity in Atomic Layer Deposition, *Chem. Vap. Deposition*, 12 (2006) 13.

#### OTHER PUBLICATIONS BY THE SAME AUTHOR

This work resulted in the following US patents:

- 1) Method for bottomless deposition of barrier layers in integrated circuit metallization schemes.<sup>1</sup>

- 2) Production of elemental thin films using a boron-containing reducing agent.<sup>2</sup>

- 3) Deposition of transition metal carbides.<sup>3</sup>

- 4) Method of growing electrical conductors by reducing metal oxide film with organic compound containing -OH, -CHO, or -COOH.<sup>4</sup>

- 5) Process for growing metalloid thin films utilizing boron-containing reducing agents.<sup>5</sup>

- 6) Sealing porous structures.<sup>6</sup>

- 7) Method of modifying source chemicals in an ALD process.<sup>7</sup>

- 8) Method of depositing transition metal nitride thin films.<sup>8</sup>

- 9) Method for depositing nanolaminate thin films on sensitive surfaces.<sup>9</sup>

- 10) Metal nitride deposition by ALD with reduction pulse. 10

- 11) Multilayer metallization. 11

- 12) Oxygen bridge structures and methods to form oxygen bridge structures. 12

- 13) Conformal lining layers for damascene metallization. <sup>13</sup>

- 14) Process for producing integrated circuits including reduction using gaseous organic compounds. 14

## **CONTENTS**

| ABSTRACT                                                                                        | 3  |

|-------------------------------------------------------------------------------------------------|----|

| PREFACE                                                                                         | 4  |

| LIST OF PUBLICATIONS                                                                            | 5  |

| OTHER PUBLICATIONS BY THE SAME AUTHOR                                                           | 6  |

| CONTENTS                                                                                        | 7  |

| 1. Introduction                                                                                 | 10 |

| 2. Motivation for the Present Study                                                             |    |

| 3. Background                                                                                   |    |

| 3.1. Diffusion Barriers Prior to Copper Metallization                                           | 14 |

| 3.2. Copper Metallization                                                                       | 17 |

| 3.2.1. Process Flow                                                                             | 18 |

| 3.2.2. Surface Cleaning and Reduction                                                           | 19 |

| 3.2.3. Copper Diffusion Barrier                                                                 |    |

| 3.2.4. Compatibility Requirements of the Diffusion Barrier                                      | 22 |

| 3.2.5. Copper Seed and Copper Metal                                                             | 25 |

| 3.3. Atomic Layer Deposition                                                                    |    |

| 3.3.1. Principle of ALD                                                                         | 27 |

| 3.3.2. ALD Deposition Equipments                                                                |    |

| 3.3.3. Copper Diffusion Barrier Deposition by ALD                                               | 30 |

| 3.3.3.1 Titanium Nitride                                                                        | 30 |

| 3.3.3.2. Tungsten Nitride                                                                       |    |

| 3.3.4. Seed Layer for ECD-Cu                                                                    | 32 |

| 4. Experimental                                                                                 | 33 |

| 4.1. Film Growth                                                                                | 33 |

| 4.2. Film Characterization                                                                      | 34 |

| 5. Results                                                                                      |    |

| 5.1. Copper Diffusion Barrier Deposition                                                        | 36 |

| 5.1.1. Deposition of TiN Film                                                                   | 36 |

| 5.1.1.1. <i>In situ</i> Reduction of TiCl <sub>4</sub>                                          | 38 |

| 5.1.1.2. Comparison of ALD- and PEALD-TiN                                                       | 39 |

| 5.1.2. Deposition of W <sub>x</sub> N Film                                                      | 41 |

| 5.1.3. Deposition of WN <sub>x</sub> C <sub>y</sub> Film                                        | 41 |

| 5.2. Process Integration                                                                        | 43 |

| 5.2.1. Barrier Compatibility with Copper and SiO <sub>2</sub>                                   |    |

| 5.2.3. Deposition of W <sub>x</sub> N/TiN and WN <sub>x</sub> C <sub>y</sub> /TiN Nanolaminates | 44 |

| 5.2.4. Compatibility of TiN with Low-k and an Etch Stopper                                      |    |

| 5.2.5. TiN and WN <sub>x</sub> C <sub>y</sub> Films in Dual-Damascene Structure                 |    |

| 5.2.6. Film Uniformity of the Diffusion Barrier                                                 | 48 |

| 5.3. Reduction of Copper Oxide Film to Elemental Copper                                         |    |

| 6. New Discoveries of the TiN Process                                                           |    |

| 7. New Discoveries of W <sub>x</sub> N and WN <sub>x</sub> C <sub>y</sub> Processes             | 60 |

| 7.1. W <sub>x</sub> N Process                                                                   | 60 |

| 7.2. WN <sub>x</sub> C <sub>y</sub> Process                                                     | 61 |

| 8. Conclusions                                                                                  |    |

| DEEDENCES                                                                                       | 60 |

#### LIST OF ABBREVIATIONS AND ACRONYMS

AFM atomic force microscope

ALD atomic layer deposition

ALE atomic layer epitaxy

AR aspect ratio

ASM advanced semiconductor materials

ASML ASM litography

BTS bias temperature stress

CMOS complementary metal-oxide semiconductor

CMP chemical-mechanical polishing

CV capacitance voltage

CVD chemical vapor deposition

ECD electrochemical deposition

EDS energy dispersive spectroscopy

EELS electron energy-loss spectroscopy

FIB-SEM focused-ion-beam SEM FSG fluoro-silicate glass

FTIR Fourier transform infrared

HRTEM high resolution TEM

HVM high volume manufacturing

IC integrated circuit

IMP ionized metal plasma

IPVD ionized PVD

LEIS low-energy ion scattering

MEMS microelectromechanical system

MOS metal-oxide-semiconductor

MPU microprocessor unit

PEALD plasma enhanced ALD

PVD physical vapor deposition

R&D research and development

RBS Rutherford backscattering spectroscopy

RC resistance times capacitance

REALD radical enhanced ALD

RMS root mean square

SEM scanning electron microscope

TDMAT tetrakis(dimethylamido)titanium

TEB triethyl boron

TEM Transmission electron microscopy

TEMAT tetrakis(ethylmethylamido)titanium

TFEL thin film electroluminescent

TMA trimethyl aluminium

TOF-ERDA time-of-flight elastic recoil detection analysis

VLSI very large scale of integration

XPS x-ray photoelectron spectroscopy

XRR x-ray reflectometer

#### 1. Introduction

In April 1965 Intel's co-founder, Gordon Moore, published a paper in *Electronics* magazine, where he introduced a "legendary" figure that has been referred to as Moore's Law. 15 This figure depicted that the number of transistors in a square inch of silicon doubles every 12 months. Legend it became after the prediction was found correct until nearly these days, although a slight deceleration down to 18 months has occurred. After the first microprocessor that contained about 2,200 transistors, the progress has been tremendous. For example, Intel's 8080 processor in 1974 contained 6,000 transistors, the first Pentium processor in 1993 contained 3,100,000 transistors, and Pentium 4 in 2004 contained already 125,000,000 transistors on the chip when the chip size was only 112 mm<sup>2</sup>, which equals the size of a finger tip. Today, when industry moves towards 45 nm process technology node, Core<sup>TM</sup>2 quad-core processor comprises more than 500 million transistors. Such a transistor can be switched on and off approximately 300 billion times a second. Since the magnitude of these numbers is often very difficult to visualize, some simplifications are needed. For example: 1) you could fit more than 2000 transistors (45 nm) across the width of a human hair, 2) 300 billion times a second means that one switch equals the time a beam of light travels a couple of centimeters.

For the further discussion of the development of the integrated circuit (IC) industry later in this thesis, the background of Moore's Law has been explained here. Understanding of the background is important because it helps to understand many decisions made in the IC industry, as well as possible future predictions. Although the performance of processors has improved with increased number of transistors, Moore was primarily interested in shrinking transistor costs instead of improving transistor performance in his paper. Moore's paper also introduced a less known cost/integration curve that depicts how the relative manufacturing cost per component changes as a function of the number of component per integrated circuit. This figure shows that the manufacturing cost decreases rapidly with increased level of integration cutting down packaging cost. This continues until the integration challenges become overwhelming, thus increasing defect yield and manufacturing cost. The lowest point of this curve is a combination of certain major factors such as: 1) the maximum number of transistors, 2) the average number of defect per square inch, 3) the size of wafer, and 4) the costs

associated with producing multiple components like packaging costs. Consequently, the figure referred to as the Moore's Law, shows an important parameter how the cost/integration curve can function. When the feature sizes are shrinking, the cost/integration curve moves downwards. In other words, Moore's law was one of the major factors leading to the reducing of costs in the IC manufacturing. The cost-driven factors are also dominating when new process technologies are chosen for the IC manufacturing.

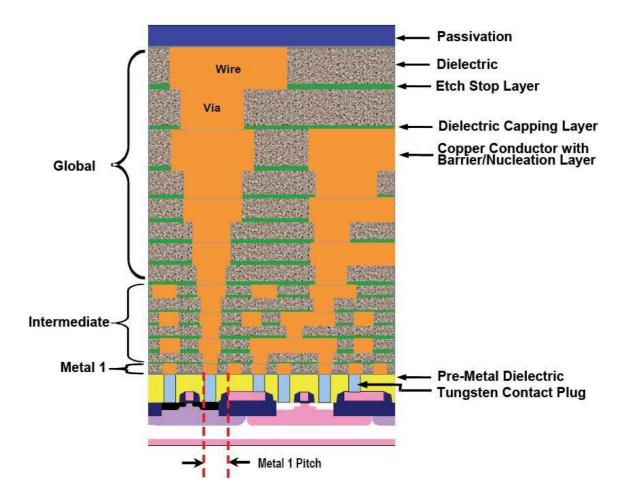

Moore's Law has led to increasing function density in the chip, defining the number of interconnected devices per chip area. As the minimum feature size of an IC decreases, the active device density increases. The device integration became more demanding because the area occupied by the interconnection lines on the chip surface extended more rapidly than the area needed to accommodate the active devices. Eventually, minimum chip area became interconnect-limited. At this point, continued shrinking of complementary metal-oxide semiconductor (CMOS) transistors produced less circuit-performance benefits. This dilemma was solved by a multilevel-interconnection system in which the area needed by the interconnect lines is shared among two or more levels (Figure 1). In 2010, the functional density of active devices in microprocessor unit (MPU) is so high that the number of metal levels is expected to be 12. Furthermore, because there are more gates, a larger number of connections between gates must be made, and the average length of the interconnection lines will increase. Total length of interconnects in MPU is expected be over 2 km/cm<sup>2</sup> when global wires are excluded.

As in all process steps, the cost impact of the multilevel metallization scheme had to be carefully considered. Although it made possible to manufacture more dies per wafer and reducing the cost per chip in that manner, it brought additional cost factors for the development, manufacturing, and the device reliability. For example: 1) new materials had to be used comprising significant R&D work, 2) process challenges meant some negative impact to the manufacturing yield, 3) new failure modes such as electromigration, corrosion, and hillock formation was expected to influence the circuit reliability. The question was whether the chip-size reduction and enhanced chip value will produce a margin of profit that is greater than the amount lost due to

additional incurred process costs and yield and reliability loss. Evidently, the multilevel metallization scheme became cost-effective and successful.

Figure 1. Cross-section of hierarchical scaling of MPU device. <sup>16</sup>

In late 1990s, it was found obvious that the increasing length of interconnects was leading to the increase in the resistance times capacitance (RC) time delay of interconnects, and in sub-quarter-micron device nodes the propagation delay passed the intrinsic delay that comprises the MOS transistor delay. The multilevel metallization was facing new challenges that required major changes in materials and the process flow. Minimization of the RC delay forced a transition from aluminium-copper (Al-Cu), tungsten (W), and silicon dioxide (SiO<sub>2</sub>)-based interconnects to the Cu metal and the low-dielectric constant (κ) insulator metallization scheme.

In addition to the RC delay, conventional aluminum metallization was facing overwhelming challenges because aluminum is sensitive for electromigration, also

known as "electron wind effect". When the current density increases, aluminum atoms can move in the lattice and cause severe device failures such as voids and "hillocks". <sup>17</sup> In the worst case, the wire will be open or shorting with other wire. Alternative metals such as tungsten, silver and gold were considered since they have better electromigration properties. However, tungsten has about twice as high electrical resistivity than pure aluminum, and gold and silver have a high cost. Copper metal was found to be an attractive option because of its high electromigration resistance and low bulk resistivity (1.7  $\mu\Omega$  cm versus 2.7  $\mu\Omega$  cm for aluminum). After all, one of the most important reasons for a successful breakthrough of the copper metallization was the great progress achieved in the process development of robust and cost-effective copper deposition and patterning.

Because the copper metallization comprised entirely new process flow and new materials, new diffusion barrier for copper was needed. Atomic Layer Deposition (ALD) technique was seen as one of the most promising techniques to deposit copper diffusion barrier for future devices, when the design node was shrinking.

Discussion in this thesis is presented in chronological order. The discussion in the chapter of Background is limited to the publications that were available when the experimental work was done. Publications which have become available later are discussed in the chapter of New Discoveries.

#### 2. Motivation for the Present Study

Since most of the work was done in ASM, Inc. which is a tool and process supplier for the IC manufacturers, motivation for this work was based on possible business opportunities in the metallization market. The copper diffusion barrier process is perceived as a part of back-end-of the line market that is the biggest market sector in the IC equipment market. Entire capital spending on IC equipment in year 2007 totaled \$44.5 billion. The reason for bigger back-end-of the line market is very obvious because the MPU devices require 9-12 metallization layers multiplying the need of process equipments. Contrary to back-end-of the line manufacturing process, the manufacturing process of the transistors is often needed only once, which is a

characteristic for all front-end-of the line processes. The back-end-of the line market has been dominated by the companies named Applied Materials, Tokyo Electron, ASML, and Novellus.

In 1999, the consequences of increase in the number of transistors per chip were expected to increase the need for new diffusion barrier process in the near future. The consequences comprised a new interconnect material and continuously shrinking interconnects, which was eventually expected to make physical vapor deposited (PVD) diffusion barrier inadequate for metallization. Acknowledging the limitations of PVD films, the IC industry was expected to choose the chemical vapor deposited (CVD) or ALD diffusion barrier instead for future devices.

Because of the above business factors being closely involved with this work, the application was well defined prior to studies. The scope of this study has been in the process integration challenges, which minimizes the risk for spending money and resources on processes that may fail in the process integration.

## 3. Background

#### 3.1. Diffusion Barriers Prior to Copper Metallization

The diffusion barrier layer is used to stop diffusion between two different materials. In the IC metallization the barrier is used to separate the insulators and conductors that used to be silicon dioxide (SiO<sub>2</sub>)-based dielectrics and aluminum and tungsten metals. Because the diffusion has a negative impact to the device performance regardless the direction of diffusion, the barrier must work towards both directions.

Barrier materials can be categorized according to the diffusion barrier mechanism.<sup>19</sup> Three major mechanisms are: 1) passive barrier: layer which is immiscible and does not react chemically with other materials; 2) stuffed barrier: a passive barrier with structural defects like grain boundaries, which are stuffed by another materials; 3) sacrificial barrier: a material which reacts chemically with other materials. During chemical reaction interdiffusion is prevented, but the barrier fails as soon as the

material is completely consumed. Historically, polycrystalline liners tend to yield the poorest barrier performance and are thus the least desirable for diffusion barrier applications.<sup>20</sup> This generalization is particularly justified when the film has a columnar structure where the grain boundaries extend throughout the entire film thickness, thus providing an effective pathway for diffusion. Consequently, in the light of crystallinity a desirable diffusion barrier has amorphous or nano-crystalline structure that makes diffusion path complex for atoms and molecules.

Horizontal conductors of the IC devices are mainly made with aluminum metallization. Since the film is deposited on nearly flat surface, there are no high surface morphology requirements, and the film can be deposited with PVD techniques. However, tungsten is often used in vertical vias having higher morphology requirements depending on aspect ratio (AR) of the via. Consequently, tungsten metal is deposited with the CVD technique that offers a better step coverage for the film than the PVD techniques.

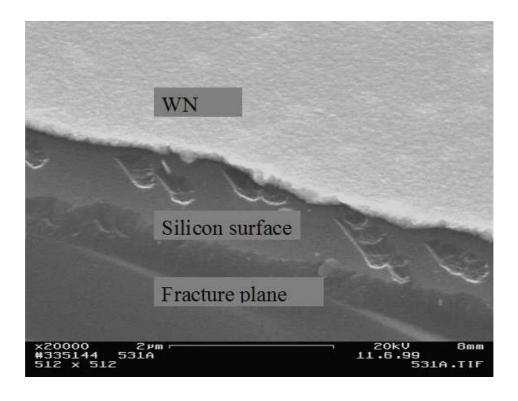

Titanium (Ti) and titanium nitride (TiN) diffusion barrier (film stack for aluminum: TiN/Ti/Al/Ti/TiN) made by PVD has been a "work horse" for the aluminium metallization having effective barrier properties against Al, W, and Si diffusion. <sup>19, 21</sup> It is also adhesion promoter by improving wettability of aluminium interconnect and by enhancing its mechanical stability. Because of this multipurpose they are often called liners. In tungsten plug Ti/TiN reduces contact resistance and improves tungsten adhesion. Titanium nitride has an important role to protect elemental Ti and SiO<sub>2</sub> surface from WF<sub>6</sub> that is often used in the tungsten nitride deposition by CVD. Tungsten hexafluoride reacts with Ti and SiO<sub>2</sub> and forms gaseous TiF<sub>4</sub> and SiF<sub>4</sub>, which can leave behind drastic surface damages (Figure 2).

Figure 2. "Worm holes" on silicon surface caused by tungsten hexafluoride [II].

As mentioned earlier, PVD-TiN has been the technique of choice in the IC industry. Although CVD-TiN has some major advantages like a good step coverage, it has also major disadvantages compared to PVD-TiN. Currently, those disadvantages are more significant for the IC industry than its advantages. One disadvantage of CVD-TiN is its relatively high deposition temperature (> 550 °C) that is required to obtain the film with a low impurity content. The CVD-TiN film often contains some amount of halide or carbon residues depending on which metal precursor was used. Those mobile residues, which can diffuse in the device and degrade its performance, worry the IC industry a lot. Furthermore, there is often extensive growth of ammonium chloride (NH<sub>4</sub>Cl) in cold walls of the CVD reactor. This is raising particle and impurity concerns.

Because the resistivity of diffusion barrier material is higher than that of aluminum or tungsten metal, the thickness of diffusion barrier should be as low as possible to reduce the overall resistance of metal wires. Nevertheless, the diffusion barrier must fulfill its primary mission as a barrier, which limits how thin barrier film can be used.

When tungsten is used to fill vias, a TiN layer of 50Å is enough to protect underlying surface in the bottom of via. <sup>22</sup>

Today, few of the most common techniques used for the PVD-barrier depositions are ionized magnetron sputtering and ionized metal plasma (IMP). Whereas the collimator and long-throw techniques faced major difficulties already with AR of 3:1, the IMP technique offered significant improvement and further extend to smaller design nodes of the IC industry. In IMP technique the sputtered atoms are ionized between the target and the substrate. Since the substrate is biased, the ionized atoms will be accelerated and controlled in certain direction resulting in collision of high yield of atoms to the substrate in perpendicular angle. In ionized magnetron sputtering, the atoms are controlled by magnetic field. Effective utilization of sputtered atoms makes these techniques even more attractive cost-wise comparing to the collimator and long-throw techniques.

## 3.2. Copper Metallization

In 1997 IBM announced that it had developed circuitry where aluminum was replaced with copper metallization. IBM called its technology CMOS 7S and it was a major milestone in semiconductor technology. Six level copper metallization was materialized by using planarization technique called chemical-mechanical polishing (CMP) and electrochemically deposited (ECD) copper.<sup>23</sup> Instead of metal etching, vias and trenches were etched directly in an insulator. Patterned surface was filled by copper and excess copper was removed by CMP. A technique where vias and trenched were made simultaneously for chip wiring was called a dual damascene process. Few years later Intel Corporation was developing their production capability for dual-damascene processing, and the CPU production with the copper metallization was launched for 130 nm process technology node.<sup>24</sup> Copper and dual damascene processing on 300-mm-wafers was quickly establishing its position in the IC industry. Nowadays, industry has moved towards 45 nm process technology node and the copper metallization is facing challenges of increasing resistance due to electron scattering<sup>25,26</sup>, which leads to increasing thermal budget of circuitry. Although copper metal was chosen over aluminum based on its good electromigration properties,

copper wires are still sensitive for stress migrations and electromigration particularly at interfaces.<sup>27</sup>

#### 3.2.1. Process Flow

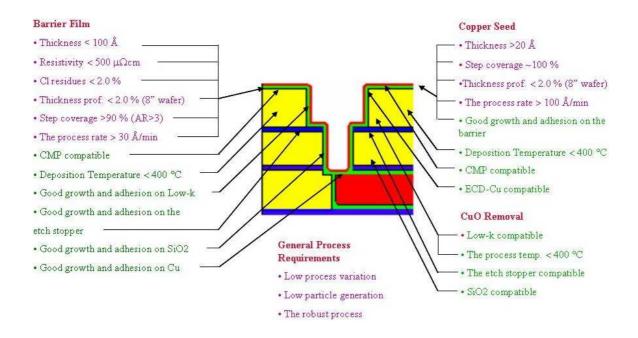

In this chapter, the process flow of copper metallization is presented generally offering reasonable understanding of the process steps before and after the diffusion barrier deposition. As mentioned before, the insulators and etchstopper layers are deposited prior to metallization. An insulator, which is made of silicon oxide or silicon oxide based or made of silicon based low-k or other low-k materials, is etched with conventional wet etching techniques or dry etching. In dual damascene process etchstopper layer, e.g. silicon nitride or silicon carbide, is used to obtain a particular shape of via and trench. Once etching has been performed the pattern of wiring is ready and open copper metal contact of underlying metal layer can be seen in the bottom of via. Prior to the diffusion barrier deposition on patterned features, the surface of insulator and the copper contact must be cleaned. When the cleaning is accomplished, the diffusion barrier is deposited followed by copper seed deposition. The copper seed layer, which is often deposited by IMP technique, is required for the ECD copper process. Then ECD-Cu is used to fill trenches and vias. Excess copper and the diffusion barrier on the top horizontal surface are removed with the CMP technique ensuring that the wires are not shorting. After the surface cleaning the next layer of insulator is deposited for the next metallization level. To avoid reoxidation of copper surface after its reduction it would be an advantage to be able to integrate some of these processes. The next chapters discuss the process integration requirements of the diffusion barrier process comprising the cleaning step prior to the barrier deposition and the copper seed deposition on the diffusion barrier (Figure 3).

Figure 3. Process requirements for the diffusion barrier and copper seed layer integration to the copper metallization. <sup>28</sup>

## 3.2.2. Surface Cleaning and Reduction

After lithography the surface of insulators and the copper contact in the bottom of via contain various residues from the etching process and copper surface is oxidized. Wet<sup>29</sup> as well as plasma cleaning processes have been developed for the surface cleaning. Conventionally, the copper oxide as well as etching residues are removed by argon ion sputtering. One of the major disadvantages of this method is the resputtering of copper from the bottom of via to the side walls of via. Possible Cu agglomeration on side walls is a reliability issue. Alternative methods, such as H<sub>2</sub>/Ar plasma have been developed.<sup>30, 31</sup>

#### 3.2.3. Copper Diffusion Barrier

The choice of copper diffusion barrier material was based on several factors: 1) material properties, 2) process performance, 3) material and process compatibility with the process integration, and 4) overall cost.

*Material properties.*–In 2001, copper diffusion barrier was expected to be thinner than 10 nm in the near future. Decreasing thickness was a natural development in improving the RC delay of metal wiring. Limitations of material thickness were the barrier properties and the step coverage. Resistivity was expected as low as possible, max:  $500 \, \mu\Omega$ cm. Typically, resistivity is measured on the film surface by four-point-probe, which gives an idea about the resistivity in horizontal trench wiring and sidewalls of via. However, in the bottom of via current flow is perpendicular to film surface and the resistance of copper wire and barrier layer are in series and have to be added. Impurities such as halide and carbon residues should be less than 2.0 %. Impurities that often result from precursors used in the barrier deposition are equally unfavorable when they degrade electrical properties of wiring or they are mobile causing impurities to spread out to metal wiring.

Naturally, it was a great challenge to find a material with the best diffusion barrier properties against copper diffusion. One of the challenges in the diffusion barrier evaluation has been non-standardized measurement techniques. Since barrier properties are measured using various techniques, a critical consideration and comparison of different materials and the same materials in different studies have been very challenging. The following techniques were mostly used: 1) Barrier followed by copper film is deposited on silicon substrate after native oxide is removed. The film stack is heated at the elevated temperature in vacuum. If copper diffuses through the barrier film, it reacts with silicon and forms copper silicide (CuSi<sub>x</sub>). The formation can be observed by microscope<sup>33</sup>, XRD<sup>34</sup>, AES<sup>35</sup>, and SEM<sup>36</sup>, <sup>37</sup>. 2) Copper silicide formation can also be verified by "Secco" eth test. <sup>38</sup> 3) Barrier followed by copper film is deposited on thermally grown silicon oxide. Metal-Oxide-Semiconductor (MOS) structure without barrier is made for the reference. Structure is exposed to bias temperature stress (BTS) ageing. Copper drifting is observed in capacitance voltage (C-V) curves. 39, 40 Barrier performance was also studied with etch resistance experiments where barrier on via structure was exposed to HF solution. If the barrier failed in sidewalls of via, underlying silicon was etched. It was often discussed by Process Engineers of IC manufacturers how well this experiment represents the diffusion barrier properties in an actual device.

The process rate must meet the expectation of production capacity. If the process is slow, more deposition equipments are needed to fulfill the capacity requirements and the cost of ownership is higher. The process rate was expected to be higher than 3 nm/min that corresponds a throughput of 10 wafers/hour in single wafer reactor (the target thickness  $\approx 10$  nm). This is very minimum throughput in the IC industry where 20 wafers/hour is not abnormal. Expectation of step coverage requirements changed with the copper metallization since the dual damascene process flow was used. The increase of AR in dual damascene structure has been moderate in new design nodes. Step coverage > 90% was needed as soon as AR was higher than three. Thickness uniformity cross the wafer was becoming more and more important factor of process performance when the wafer size was increasing. The uniformity of the barrier film was expected to be below 2 % (standard deviation, 1 sigma) with 4 mm edge-exclusion.

Various transition metals, their binary and ternary compounds have been suggested for the copper barrier application. The compounds of W, Ta and Ti are the most studied comprising desirable physical, chemical, and electrical properties. Particularly, polycrystalline and amorphous phases of metal nitrides, carbides, <sup>41</sup> and borides have been a subject of interest. Amorphous ternary compounds (M<sub>x</sub>Si<sub>y</sub>N<sub>1-x-y</sub>) have proved to be promising candidates as a copper barrier. Material compatibility with copper has been widely studied improving the understanding of thermodynamical stability of these compounds as well as an influence of their crystal structure to diffusion.<sup>20</sup>

Tantalum nitride  $(TaN_x)$  deposited by PVD technique has been mainly the choice of industry. The PVD technique comprises relatively good methods to control N/Ta ratio. Good methods are needed since tantalum nitride has more than 11 different known phases and one of the most desirable of these phases  $(N/Ta \approx 1)$  is metastable.<sup>42, 43</sup> However, as is the case with tantalum, tantalum nitride is stable thermodynamically with copper being an effective barrier against copper diffusion.

## 3.2.4. Compatibility Requirements of the Diffusion Barrier

In addition to previous film property requirements, the copper diffusion barrier process must fulfill several compatibility requirements in the process integration. Although film properties are promising, process integration may fail due to lack of compatibility of one or several subjects. Since all other process steps around diffusion barrier process are the result of extensive R&D work and financial investments, the IC manufacturers are not usually so eager to change existing processes or materials made in the processes although new diffusion barrier material would require it. There is also a risk that the changes of existing processes or materials would generate new compatibility issues in other processes, and thus escalating the problems. In other words, even one compatibility issue can be the dead-end of new interesting barrier material due to reliability/yield factors, process development time, production/sales objectives, and eventually the cost.

When diffusion barrier is deposited on patterned dual-damascene features, the film must adhere and grow at least on three different surface materials. Because the starting surface is known to be a critical factor for the film growth, the process integration is challenging. The film must grow on insulators in sidewall, etch stopper (e.g. SiN and SiC) between via and trench, and copper surface on the bottom of via. To obtain the same thickness of film everywhere, the growth rate cannot differ significantly on different materials.

When the deposition on insulator is studied, various materials must be considered including conventional silicon oxide. In addition to copper metal, the switching speed can be improved with reducing parasitic capacitance over wiring. This can be done with insulators that have lower dielectric constant than silicon dioxide ( $\kappa$ = 3.9), thus called as low-k materials. There are commercially available various low-k materials such as fluorine and carbon doped silicon dioxide, porous silicon dioxide, porous carbon doped silicon dioxide, organic polymers made by spin-on coating, and porous organic polymers. Fluorinated silicate glass (FSG) was the choice of Intel Corp. for 130 nm process technology node decreasing the dielectric constant to 3.6.<sup>24</sup> In the following nodes (65nm and 45 nm) their process was integrated to low-k material

called Aurora<sup>TM</sup> which is a carbon doped silicon oxide by ASM International. Carbon doping that is also carried out in Applied Materials' Black Diamond and Novellus Systems' Coral, decreases the dielectric constant down to 3.0. Spin-on coated organic polymers, for instance, polyimide, benzocyclobutene, and PTFE have not achieved as much attention as previous materials primarily because of their weak thermal stability and mechanical strength. Nevertheless, there is a significant interest for organic polymers, which, however, limits the deposition temperature of the diffusion barrier below 400 °C.

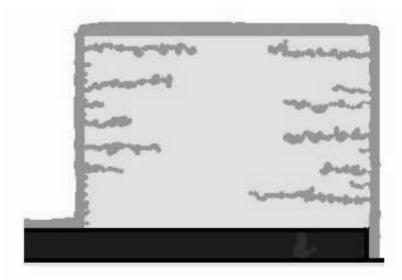

Porous low-k materials are known to bring new integration challenges: 1) the patterning of porous materials is difficult, 44 2) the materials suffer from a low mechanical strength, 3) the depositions of the diffusion barrier and the copper seed layer on porous low-k can be problematic. If conventional diffusion barrier deposited by PVD technique is used, porous sidewalls of vias and trenches make diffusion barrier discontinuous. In other words, the CVD technique with a good surface controlled process, and particularly ALD, can offer a clear advantage when porous insulators are considered. The integration feasibility depends on shape and size of pores. Good step coverage properties of ALD technique can be a concern. The diffusion barrier film can penetrate deep into the sidewall degrading the insulator or inductively generate current to the next wire or even a short (Figure 4). Since the horizontal distance between wires is only few hundred nanometers, even minor penetration can degrade the device performance. This issue has been tried to be addressed in many different ways. One such approach has been to concentrate on engineering of pores in a way that pore size has been decreased and pores are closed forming discontinuous holes for hindering CVD precursors to penetrate into the insulator. Donohue et al. introduced a technique where in situ dry stripping is made on insulator after the plasma etching.<sup>45</sup> Stripping removes the photo resist and makes the sidewall of trench smoother and denser, thus providing the diffusion barrier film with no penetration. Raaijmakers et al. developed a method where the pores are lined in vertical direction. The pore opening on the top is closed for example by melting.<sup>46</sup> Another alternative method comprises the combination of the PVD and ALD methods where the PVD film is used to cover the holes prior to the ALD deposition.

Figure 4. Schematic picture of barrier penetration into the porous low-k dielectric.<sup>28</sup>

In the bottom of via the barrier is deposited on underlying copper metal. Copper surface is covered by etching residues due to the via opening step. Furthermore, the surface has oxidized when it is exposed to air. Consequently, the copper surface must be cleaned prior to the barrier deposition. The etching residues are often cleaned with the Ar plasma in addition to the hydrogen plasma that is known as an effective method to remove oxidized surface.<sup>47</sup> After appropriate cleaning the diffusion barrier is deposited on copper. If CVD technique is used, one must ensure that the precursors used in the deposition are chemically compatible with copper as well as the byproducts of the surface reaction. The adhesion on copper must be very good to make sure that the interface does not open when high current density is driven over the interface. Evidently, it would be more preferable if there is no barrier at all between copper interface, which increases switching speed and makes the circuit more vulnerable. The concept of having selective ALD deposition on the dual damascene structure where the barrier growth does not take place on the copper surface has been considered. 48 In addition to previous compatibility requirements, the diffusion barrier must be compatible with the CMP process. When surplus growth of copper on the top of trench is removed with CMP, the diffusion barrier must tolerate the process.

#### 3.2.5. Copper Seed and Copper Metal

Electrochemical deposition (ECD) was universally chosen as a method to deposit copper. It is low temperature, acid-based, relatively simple and a cost-effective deposition method that can offer bottom-up coverage once it is well optimized. However, the ECD process requires a highly conductive starting surface to obtain uniform copper film cross the wafer. The conductive surface, called seed layer, is usually physical vapor deposited-copper (PVD-Cu) with a thickness of approximately 100 nm. Whereas ECD-Cu was seen as a method of copper filling in next design nodes, the seed layer was a subject of concerns. In order to deposit 10 nm copper on the sidewall of via, one must deposit 100 nm thick film on the top surface. Because of a non-conformal growth of PVD-Cu, there is overhang growth of the top edge of via. Thicker film on the edge causes locally higher current density in the ECD process resulting in a higher growth rate at this spot, and eventually leaving a void in the middle of the via. This subject of concern was a driving force in search for an alternative seed layer process with better step coverage properties.

Only copper metal was considered as a seed material for the ECD-Cu deposition. Low resistivity of copper offered good current distribution across the wafer minimizing "terminal effect" that is the result of lower current density in the middle wafer making the film thicker in the edge and thinner in the middle. Consequently, excess copper was deposited on the edge of wafer making the copper thick enough at the middle of the wafer. The following CMP step became more challenging because more copper removal was required on the edge than the middle of the wafer. Because the cathode contacts were in the edge of wafer in the ECD process, it was clear that increasing wafer size brought more challenges for the terminal effect. In addition to low resistivity, it was obvious that copper seed layer offered the best adhesion for ECD-Cu. One additional reason why no other seed layer materials were considered was the copper interface reliability. There was a concern that the interface was not stable enough thus allowing two materials the possibility to react/diffuse with each other and cause void formation in a high current density. This concern was relevant since copper is known to react with many materials.

#### 3.3. Atomic Layer Deposition

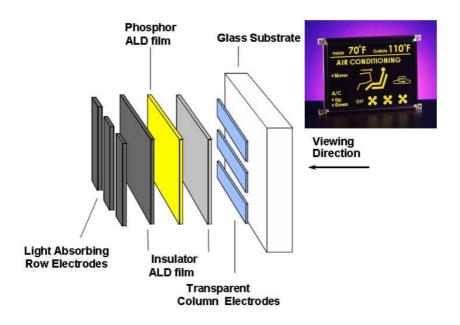

Atomic Layer Deposition is one of the Chemical Vapor Deposition techniques that was developed in Finland in the mid 1970s by Dr. Tuomo Suntola and his co-workers. One of the objectives in this work was to find a deposition technique which could be used to manufacture thin film electroluminescent (TFEL) flat panel displays. After extensive development work with ALD, called Atomic Layer Epitaxy (ALE) at the beginning, the technique was used in high volume manufacturing (HVM) of TFEL displays at Finlux Display Electronics, which later became Planar Systems, Inc (Figure 5). Although one of the earliest papers that describe an ALD type of a technique was published in 1965,<sup>50</sup> the development work that resulted in the first patent of an ALD technique was granted in the mid 1970s.<sup>51</sup> The early phases of ALD development in Finland and Russia has been reviewed by Puurunen.<sup>52</sup>

Figure 5. Electroluminescent flat panel displays of Planar Systems, Inc.

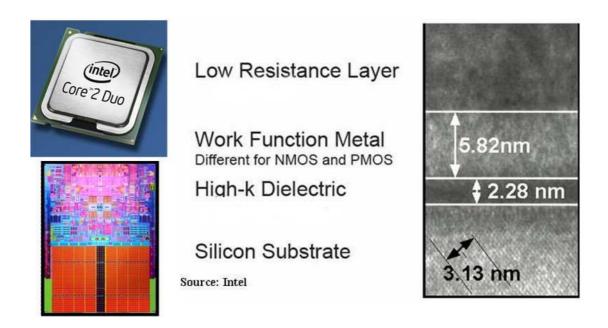

Over two decades ALD technique was hardly used for any other industrial applications. However, it obtained significant academic interest resulting in publications and Ph.D. dissertations. At the end of the 1990s the IC industry became interested in ALD as a result of shrinking feature sizes. In 2006, Intel launched HVM of the first commercial microprocessor (Intel®Core microarchitecture for a 45 nm

design node) that used high-k material deposited by ALD for the gate oxide of CMOS transistor (Figure 6). Recently, the high visibility of ALD has exponentially added interest towards the method, continuously bringing up more applications where the ALD technique could be considered for use. According to some views, the growth of interest towards ALD could even be considered "hype" since quite often production worthy techniques are still conventional deposition techniques in many applications. Increasing interest has also been seen in R&D where new ALD type of techniques have materialized as a deposition system, e.g. plasma-enhanced (PE) ALD, radical-assisted (RA) ALD.

Figure 6. Intel's Core microarchitecture MPU with detailed structure of the transistor.<sup>53</sup>

## 3.3.1. Principle of ALD

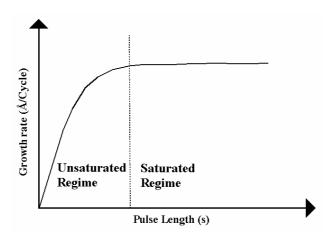

ALD is based on sequential self-saturated surface reactions, leading to the controlled layer-by-layer growth of thin film at the molecular level.<sup>54, 55</sup> The ALD cycle comprises at least two material pulses with a purging pulse or evacuation step after each material pulse. Effective purging step is an absolute requirement of ALD to separate the highly reactive precursors in the gas phase. Figure 7 is often presented as

proof of ALD growth where the growth rate saturates as a function of the precursor pulse length.

Figure 7. Characteristic curve of ALD where the growth per cycle saturates as a function of pulse length of precursor [VII].

#### 3.3.2. ALD Deposition Equipments

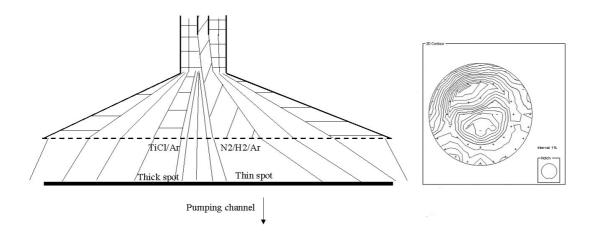

Because the influence of the reactor design to the film uniformity of the diffusion barrier was studied in great detail, some background of the ALD reactor design is discussed here [VII]. Ten years ago there were only few ALD tool suppliers available whereas today there are dozens of tool suppliers and continuously more are entering to share the rapidly increasing market. Consequently, this topic has become very broad and thus it is touched here only briefly.

Since the principle of ALD supports scalability for multiple substrates, ALD reactors were based on batch processing at the beginning to improve their throughput and thus making the production of TFEL displays cost-effective. However, there were research reactors made to handle some small substrates. A need to integrate the ALD process with other process steps by the cluster system brought forth single-wafer reactors. Single wafer processing was also preferred in the IC production. The batch systems in the middle of the process flow would have increased the intermediate storage and decreased the overall yield. The batch system, however, are coming to the IC

manufacturing as a result of never-ending cost reduction. Evidently, the future of ALD processing in production use relies on the development of ALD batch reactors.

Most of ALD reactors are flow-type reactors where the carrier/purging gas is introduced over the substrate as a continuous flow. When the reactor design is good, the flow-type reactor offers an effective purging of the reactor volume making the cycle time short and throughput reasonable. There are also non-flow-type reactors available. In these reactors the substrate is exposed to the precursors while pumping and purging are stopped. The purging step in these reactors takes longer, even minutes in the worst case, and evidently the throughput suffers. Furthermore, the surface chemistry can differ between these reactor types.

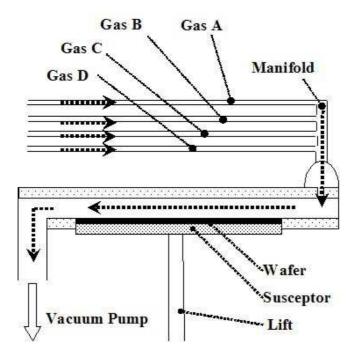

Figure 8. A schematic of the single wafer cross-flow reactor that comprises four gas inlets and a lift mechanism for the wafer transfer [VII].

When the flow is introduced to one end of the substrate and it ends up at the opposite end of substrate, the reactor is called a cross-flow reactor (Figure 8). Nearly all reactors made in the first two decades were of this type. Again, the principle of ALD offers a good explanation why the use of the cross-flow reactor in ALD should be straight forward whereas perpendicular flow is preferred in CVD. The perpendicular

flow that is often carried out with the showerhead on the top of the substrate was also implemented with ALD reactors during the 1990s. Since many traditional CVD tool suppliers began manufacturing ALD reactors, the showerhead was the obvious choice. This particular design, however, faced multiple problems. Small showerhead holes were restricting the flow such that it took very long time to purge the volume inside showerhead. If the purging was not efficient, highly reactive ALD precursors reacted in the gas phase generating particles and clogging the holes. Secondly, since CVD reactors were also traditionally cold-wall reactors, the showerhead were at significantly lower temperature than the substrate. Consequently, precursor condensation and the particle formation inside the showerhead followed. The differences of perpendicular and cross-flow are further discussed in the chapter "Film Uniformity of the Diffusion Barriers".

### 3.3.3. Copper Diffusion Barrier Deposition by ALD

#### 3.3.3.1 Titanium Nitride

The background of the ALD-TiN processes has been extensively reviewed in Juppo's dissertation<sup>56</sup> and Kim's review article<sup>57</sup>. In nearly all studies ammonia was used as a nitrogen source excluding few exceptions. Titanium precursors were the following: TiCl<sub>4</sub>, <sup>58, 59, 60</sup> TiI<sub>4</sub>, <sup>61</sup> Ti[N(C<sub>2</sub>H<sub>5</sub>CH<sub>3</sub>)<sub>2</sub>]<sub>4</sub> (TEMAT), <sup>62</sup> Ti[N(CH<sub>3</sub>)<sub>2</sub>]<sub>4</sub> (TDMAT). <sup>63</sup> Since it is known that tetrakis(dialkylamino)titanium compounds suffer from weak thermal stability, <sup>64</sup> it leaves only few options which can be seriously considered for the ALD-TiN process. Consequently, there have been more studies recently where the fundamental growth mechanism<sup>65, 66, 67</sup> and the process integration<sup>68</sup> for some applications have been explored. Since the growth mechanism studies often require in situ characterization, most of the studies have been made in customized characterization system in which the precursor can be introduced in ALD manner. In other words, the films are not deposited in well designed ALD reactors. Consequently, it can be seen that the analysis of the characterization results can become quite complicated when there are for instance thermal decomposition of precursor, overlapping pulses, and impurity sources from the environment present.<sup>67</sup> Fortunately, there are well designed systems available nowadays where the characterization equipment can be integrated into the ALD reactor. It is also possible to have a cluster system where the samples are transferred under vacuum between various characterization equipment and the ALD reactor.

When the TiN process from metal halides and ammonia is considered, the following overview can be made: 1) depositions are made between 300 °C and 500 °C, 2) the films are polycrystalline having columnar grain structure, 3) halide impurity level stay below 4 at.-% when the deposition temperature is above 350 °C, 4) resistivity of the film is below 500  $\mu\Omega$ cm and, 5) growth rate is 0.05-0.37 Å/cycle.

#### 3.3.3.2. Tungsten Nitride

The ALD- $W_xN$  processes were studied significantly less than the TiN processes prior to our studies. Tungsten hexafluoride (WF<sub>6</sub>), used for the  $W_xN$  deposition widely in CVD, was a challenging tungsten precursor for the ALD reactors made from quartz parts. The reaction by-product, hydrogen fluoride, was an effective etching agent of quartz and caused devastating damage to the reactor. Consequently, these experiments were made in reactors with metal body.

Klaus *et al.* have published two papers about ALD-W<sub>x</sub>N studies.<sup>69, 70</sup> The film was deposited from tungsten hexafluoride and ammonia on high surface area silica powder comprising *in situ* FTIR spectroscopy studies. According to their paper and our knowledge, films were deposited in the non-flow-type reactor where the substrate is exposed to each material pulse for tens of minutes. Based on the results it has been suggested that the surface chemistry can be quite different in the flow-type and the non-flow-type reactor. However, this claim is very weakly studied and not well understood. Starting surface was very carefully treated to make Si–NH<sub>2</sub> terminated surface that resulted in tungsten nitride growth of ~2.5 Å/cycle at 327-527 °C. The growth rate matches that of the W<sub>2</sub>N monolayer. Since metal nitrides deposited in flow-type-reactors usually have the growth rate far below monolayer, a high growth rate has been considered to be caused by the reactor type. The film was smooth, polycrystalline (with strong cubic W<sub>2</sub>N peaks) with the estimated grain size of 11 nm.

The film had a low content of impurities, and its resistivity was 4500 x  $10^3~\mu\Omega$ cm. The resistivity of  $W_xN$  was observed to increase drastically when the nitrogen content exceeded 32 %. <sup>71</sup>

The FTIR studies revealed that the WF<sub>6</sub> half-reaction left  $-WF_x$  terminated surface, and the ammonia half-reaction left  $-NH_2$  terminated surface. Furthermore, it was observed that the surface reaction was limited in the half-reaction of ammonia when the deposition temperature was 227 °C. Only 60 % of the  $-WF_x$  species were removed in the ammonia pulse. Consequently, the nitrogen content decreased. The nitrogen content played an important role with the diffusion barrier property where the failure of barrier occurred due to the release of nitrogen when the film was heated up to 850 °C.<sup>71</sup> In other words, the film was deposited above 327 °C to obtain the best diffusion barrier properties.

## 3.3.4. Seed Layer for ECD-Cu

Copper film was found to be very challenging to deposit in any Chemical Vapor Deposition methods and its good adhesion on all different surface materials in dual-damascene structure was found to be even more challenging.

The ALD-Cu deposition was extensively reviewed by Juppo.<sup>56</sup> All studies show a high sensitivity to the substrate material where the surface can have a catalytic influence to the film growth. The material sensitivity of the copper deposition raises a concern how the deposition can be done on several surface materials of the dual-damascene structure. Furthermore, process repeatability seems weak because some processes did not work so well in other type of reactors. Depending on whether the reactor is of flow-type or non-flow-type, difference can be seen. When metal film is deposited through the reduction of the metal precursor, the results suggest that it might be easier to deposit metals in the non-flow-type reactor. So far, ALD-Cu processes have not been proved to be production worthy.

## 4. Experimental

#### 4.1. Film Growth

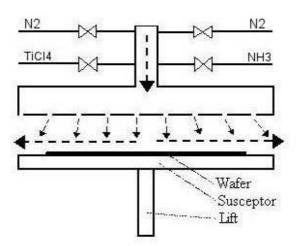

Most of film depositions were carried out with Pulsar® 2000 (for 200-mm-wafer) and Pulsar® 3000 (for 300-mm-wafer) reactors designed and manufactured by ASM Microchemistry Ltd. [I-IV,VI,VII] (Figure 9). Both reactors were designed for single-wafer ALD processing and they are flow-type reactors with a flow rate of 6-10 m/s. The flow is introduced cross the wafer. The operating pressure was maintained below 10 mbar with a dry pump and continuous nitrogen flow from each source line (~ 400 sccm). After reactive filtering, the impurity content of nitrogen was at the ppb level. The reaction chamber was not exposed to air between depositions. The wafer was introduced to the reactor through the load lock.

Figure 9. Pulsar<sup>®</sup> 2000 with stand-alone loader (left) and Pulsar<sup>®</sup> 3000 with Polygon<sup>®</sup> 8300 cluster platform (right).

Depositions were also made in a perpendicular flow reactor where the flow was introduced on the wafer through the showerhead [VII]. These single-wafer reactors for 300-mm-wafer were prototype reactors that were developed for both ALD and the PEALD processing. One reactor was manufactured by ASM Genitech Ltd. (Korea) and one by ASM Japan Ltd. The reactor of ASM Genitech was never commercialized

but a reactor type from ASM Japan, called Emerald was commercialized. The reactors were flow-type reactors where the pressure of ~ 3 torr was controlled with a throttle valve and continuous inert gas flow.

Previously mentioned reactors designed for both ALD and PEALD processing were used in the PEALD studies [VI]. 300-mm-wafer was exposed to direct plasma by exciting the plasma field between the showerhead and the wafer. The radical and ion formation were carried out using a 1 kW 13.56 MHz rf generator. Typical rf power was 100-400 W.

Copper oxide reduction experiments were made in a flow-type ALD reactor (model F-120) manufactured by ASM Microchemistry, Ltd [V]. The reducing agent was introduced with nitrogen gas over substrate as a continuous flow opening an isolation valve between the substrate and the source. The process temperature was controlled within an accuracy of  $\pm 2$  °C and the pressure of the reaction chamber was 5-10 mbar.

#### 4.2. Film Characterization

In publications I-VI different characterization methods were employed and therefore the methods are described separately for each publication:

[I]: 1) Sheet resistance was measured by a four point probe, 2) transmission electron microscopy (TEM), 3) x-ray photoelectron spectroscopy (XPS), and 4) Rutherford backscattering spectroscopy (RBS).

[II]: 1) Wide angle XRD patterns were obtained using a Siemens D500 instrument equipped with a Ni-filtered Cu tube anode, and a scintillation detector, 2) Jandel's four-point probe was used for resistivity measurements, 3) film thickness, impurity content and pitting pictures were obtained using a Link ISIS energy dispersive X-ray spectrometer connected to a Zeiss DMS 962 scanning electron microscope (SEM), 4) high aspect ratio SEM images were taken by a Philips XL30 SEM.

[III]: Following characterizations were made: 1) sheet resistance uniformity, 2) film stress, 3) adhesion, 4) roughness, 5) composition analyzed by EELS, 6) step coverage was seen in the TEM images, and 7) cross-section pictures were made with FIB-SEM.

[IV]: 1) Jandel's four-point probe was used for resistivity measurements, 2) film thickness, impurity content and pitting pictures were obtained using a Link ISIS energy dispersive X-ray spectrometer connected to a Zeiss DMS 962 scanning electron microscope (SEM), 3) SEM images of the copper surface were taken by a Philips XL30 SEM, 4) TEM pictures were taken with an FEI Tecnai 12 working at 120 kV acceleration voltages, 5) TEM cross-section pictures of TiN film and WN<sub>x</sub>C<sub>y</sub>/TiN film stack were obtained with a Philips CM30 operating at 200 kV acceleration voltages, and 6) Auger analysis of the nanolaminate structure was done with a Scanning Auger Microprobe PHI-4300.

[V]: Time-of-flight elastic recoil detection analysis (TOF-ERDA) was used in copper oxide reduction studies to measure the reduction efficiency. TOF-ERDA is an ion beam method in which the high-energy heavy ions (53 MeV <sup>127</sup>I<sup>10+</sup>) are used as projectiles which hit the sample and generate forward recoil sample atoms.<sup>72</sup>

Resistance measurements were made with a simple setup where only major differences were measured. Resistance was measured with a Hewlett-Packard 34401 A multimeter.

[VI]: 1) Sheet resistance of 300 mm wafers was measured with a CDE Resmap using 49 points circular map with 4 mm edge exclusion, 2) film composition, thickness, and impurities were characterized by X-ray reflectometer (XRR), RBS, X-ray photoelectron spectroscopy (XPS), and energy dispersive spectroscopy (EDS), 3) film thickness, density and roughness of PEALD-TiN samples were analyzed with Panalytical X'pert PRO MRD model PW/3040, 4) RBS measurements were made with 2-MeV <sup>4</sup>He<sup>+</sup> ions, and 5) SEM images of PEALD-TiN were made with field-emission-(FE)SEM, JEOL 890, operating at 10 keV.

In all studies thermodynamic calculations were made using various software versions of the HSC Chemistry for Windows (Outotec Oy).

#### 5. Results

In the following chapters the results of this work are reviewed. Comprehensive understanding of experiments and the results can be obtained from corresponding papers [I-VII].

## **5.1.** Copper Diffusion Barrier Deposition

#### 5.1.1. Deposition of TiN Film

Titanium nitride films were deposited with a well-known process where TiCl<sub>4</sub> and ammonia are used as precursors.<sup>58, 59</sup> Titanium tetrachloride is an attractive precursor because it is thermally very stable, it is liquid, and it has relatively high vapor pressure at room temperature. The surface saturation of TiCl<sub>4</sub> on the substrate can be obtained even with 50 ms pulse time that is close to maximum operation speed of commercial pulsing valve. However, the vapor pressure is not so high as to require cooling of the source. In other words, the precursor is ideal for ALD in many point of view. Nevertheless, TiCl<sub>4</sub> requires careful handling because it reacts aggressively with the moisture of air forming hydrogen chloride gas that is dangerous and highly corrosive for the reactor hardware.

Titanium nitride films were deposited at 300-400 °C using nitrogen as a carrier and purging gas with an overall flow of ~400 sccm. The growth rate was as low as previously reported (0.17 Å/cycle) at 400 °C, which was a concern to obtain a reasonable throughput in the TiN process. When the deposition temperature was lowered to 300 °C, the growth rate decreased linearly down to 0.12 Å/cycle. The film was close to stoichiometric, its composition being slightly nitrogen rich (N:Ti = 1.16). Oxygen and carbon residues were found only on the surface. The chlorine residue content was 1.2 at.-% when deposition temperature was 400 °C and increased when temperature was lowered being already 7.0 at.-% at 300 °C.

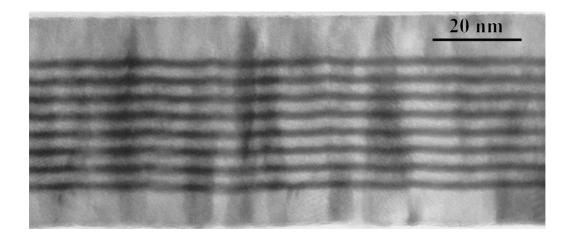

Figure 10. ALD-TiN deposited into ultra high aspect ratio trench (AR=85). Picture shows the bottom of trench.

Films were polycrystalline and continuous in the deposition temperature range. Even though the grains were very closely packed, there was a clear columnar grain structure. The grain size was 15-20 nm. Film density was high,  $(10.8 \times 10^{22} \text{ at./cm}^3)$  close to the bulk density, which was suggesting very narrow boundaries. When the film was deposited in ultra high aspect ratio trench where the aspect ratio was as high as 85, the film growth took place with nearly 100 % step coverage (Figure 10), which is a characteristic for the ALD growth.

Film resistivity was below 200  $\mu\Omega$ cm when the deposition temperature was 400 °C. However, resistivity was drastically increasing when film thickness was less than 20 nm. The sample with 5 nm thick film had resistivity already as high as 790  $\mu\Omega$ cm [III]. Rapid change in electrical properties was the result of the mean free path of conductive electrons. When film thickness became less than the distance of grain boundaries, the change was rapid.

Films deposited at 350-400 °C were very smooth (RMS: 3-5 Å) but exhibited slightly high intrinsic stress. Tensile stress of  $\sim$  1,4 GPa was measured as a wafer bowing for  $\sim$  5 nm thick film. Adhesion on silicon dioxide was found to be good with a simple Scotch tape test. Adhesion was also tested on silicon dioxide and copper with a 4-point bend technique that showed 60-25 J/m² (to SiO<sub>2</sub> – to Cu) [III].

Generally, it can be concluded that the ALD-TiN process is a quite simple when TiCl<sub>4</sub> and NH<sub>3</sub> are used as precursors. Since the process suffers from relatively low growth per cycle, the deposition tool must be well designed to ensure the shortest possible cycle length. Furthermore, when the tool is well designed, there are no contamination problems in the TiN film. The challenges of the process integration are discussed in the following chapters.

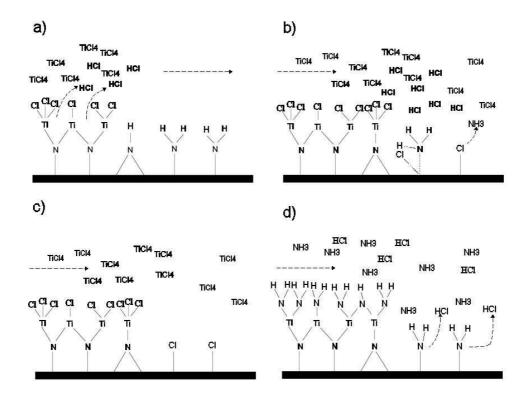

## 5.1.1.1. In situ Reduction of TiCl<sub>4</sub>

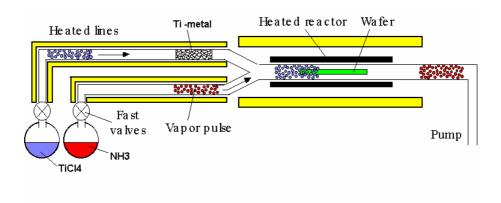

A deposition technique that doubled the growth per cycle of the ALD-TiN film was developed.<sup>74</sup> The technique was based on *in situ* reduction of TiCl<sub>4</sub> when it was introduced to the reaction chamber. Titanium tetrachloride became reduced before being chemisorbed on the substrate when it was exposed to titanium metal at moderate temperature. Figure 11 shows a schematic concept of the ALD-TiN process with an *in situ* reduction of TiCl<sub>4</sub>.

Figure 11. Schematic picture of *in situ* reduction process of ALD-TiN in cross-flow reactor.

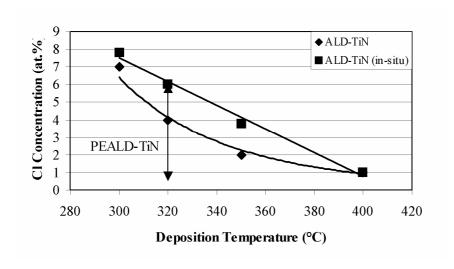

The growth rate of TiN was  $\sim 0.35$  Å/cycle when the deposition temperature was 400 °C. Growth rate decreased linearly with temperature such that it was  $\sim 0.30$  Å/cycle at 350 °C and  $\sim 0.15$  Å/cycle at 300 °C. In other words, the difference in growth rate between standard and *in situ* processes became smaller at lower temperature. No differences were found in the chlorine residue content between standard and *in situ* processes. The content was approximately the same at 300 - 400 °C. When the deposition temperature was lowered the change of content was more linear in the *in situ* than in the standard process (Figure 12). No differences were found in electrical properties.

Figure 12. Chlorine content in TiN film versus deposition temperature.

No further studies were made to understand the fundaments of the mechanism of increased growth rate. However, the mechanism was speculated with thermodynamic calculations. Change in the growth rate was believed to occur via titanium trichloride (TiCl<sub>3</sub>) [1] and/or dimeric, dititanium hexachloride (Ti<sub>2</sub>Cl<sub>6</sub>) [2] formation on the hot titanium metal surface. Additional calculations also suggested that both TiCl<sub>3</sub> and Ti<sub>2</sub>Cl<sub>6</sub> could be more reactive with ammonia than TiCl<sub>4</sub>.

$$TiCl_4(g) + 1/3 Ti(s) \Rightarrow 4/3 TiCl_3(g)$$

,  $\Delta G (400 ^{\circ}C) = 6 \text{ kJ/mol}$  [1]

$$TiCl_4(g) + 1/3 Ti(s) \Rightarrow 2/3 Ti_2Cl_6(g)$$

,  $\Delta G (400 ^{\circ}C) = -40 \text{ kJ/mol}$  [2]

There was no commercial interest for this technique and consequently no further development or studies were done. However, the technique was easy and the depositions were repeatable. Hopefully, there will be further studies made in the future.

## 5.1.1.2. Comparison of ALD- and PEALD-TiN

The PEALD studies are out of scope of this thesis. The topic of PEALD or RE (radical enhanced) ALD is extensive and comprises multiple dissertations itself. If the

reader is interested in this topic, following references can be recommended.<sup>75, 76</sup> However, the results of TiN film deposited from direct plasma with the results of TiN films deposited from a conventional ALD are compared here [VI].

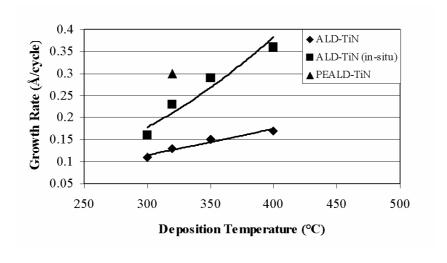

PEALD-TiN films were deposited at 270-370 °C using  $N_2$  (10 sccm) and  $H_2$  (100 sccm) radicals and TiCl<sub>4</sub>. The growth rate of PEALD-TiN was 0.30 Å/cycle at 320 °C that is nearly three times higher than that of conventional ALD-TiN at the same temperature (Figure 13). It was also observed that growth per cycle was very linear from at the very beginning in the PEALD process, which suggests that reactive N\*/H\* species could modify the reactive sites of the substrate.

Figure 13. Growth rate in three different TiN processes between 300 and 400 °C.

Generally, the composition of ALD film (N:Ti = 1.16 at 400 °C) cannot be adjusted with the pulsing parameters, but in the PEALD process the film composition was possible to be adjusted with the plasma power. When the plasma power was 100 W, the N:Ti ratio was ~0.92 and it went up to ~1.1 if the power was increased to 400 W. Slight saturation in the film composition was observed if the power was increased more. Plasma pulsing parameters were also possible to use for controlling chlorine content in the film. Both the rf power and the rf pulse length changed the Cl content. When the film was deposited at 320 °C, rf power was 200 W, and rf pulse length was 6 s, the Cl content was as low as ~0.5 at.-%. If the rf pulse length was 1 s, Cl content went up to ~5.8 at.-%. Results suggest that the reaction kinetics is slow at 320 °C, and long plasma exposures are required to complete the surface reaction.

The surface roughness of PEALD-TiN film was measured with XRR and AFM. PEALD-TiN seemed to be rougher than ALD-TiN. When the ALD-TiN film was 5 nm thick, RMS roughness was ~4 Å. Correspondingly, RMS for PEALD-TiN film was ~13 Å. The roughness of the PEALD-TiN film increased linearly, and RMS roughness was already ~25 Å for 80 nm thick film. PEALD process was assumed to be more aggressive to the surface than a conventional ALD process promoting rougher surface of the PEALD film.

The resistivity of the PEALD-TiN film was below 150  $\mu\Omega$ cm when film thickness was above 30 nm and the film was deposited at 320 °C. Resistance of PEALD-TiN film saturated already with rf pulse of 2 s when rf power was 200 W. In other words, the conductivity of the film was not limited by the chlorine residues when the content was below 3 at.-%. Grain boundary scattering was expected to limit conductivity for both PEALD- and ALD-TiN films.

## 5.1.2. Deposition of W<sub>x</sub>N Film

Tungsten nitride film was deposited from tungsten hexafluoride (WF<sub>6</sub>) and ammonia at 350 °C [II, IV]. Growth rate was high (0.42 Å/cycle) compared to TiN. The film was polycrystalline comprising WN and W<sub>2</sub>N phases exhibiting columnar grain structure. W:N ratio was found to be 1.62, which supports the previous observation about the mixture of phases. Although fluorine residues from WF<sub>6</sub> were only 2.4 at.-%, resistivity was as high as 4500  $\mu\Omega$ cm, which is far above the acceptable value of 500  $\mu\Omega$ cm. Evidently, the resistivity of W<sub>x</sub>N is not limited by halide residues but rather by the high oxidation state of tungsten.

## 5.1.3. Deposition of WN<sub>x</sub>C<sub>y</sub> Film

High resistivity of  $W_xN$  and its suggested source was a driving force to introduce the third precursor for the reduction of tungsten. Triethylboron ( $B(C_2H_5)_3$ ), TEB, was

used as a reducing agent. It is a liquid and has relatively high vapor pressure such that no extra heating is needed. TEB was pulsed after the WF<sub>6</sub> pulse at the beginning but it was soon noticed that the process was more copper compatible when TEB was pulsed after the ammonia pulse. Thus, the pulsing sequence of WF<sub>6</sub>/NH<sub>3</sub>/TEB was chosen.

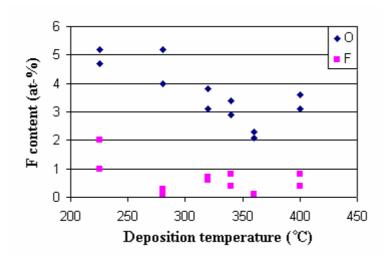

Depositions were made at 300-350 °C where TEB did not decompose yet. Although it was expected that no atoms of TEB would incorporate to the deposited films, a significant amount of carbon was found. The XPS studies revealed the composition of W:N:C to be 55:15:30. The XRD studies suggested that carbon is bound in the form of metal carbide. The W:N:C ratio was almost constant when the deposition temperature was varied between 275 °C and 350 °C. The growth rate of the film was approximately 0.8 Å/cycle when deposition temperature was 300-350 °C. Fluorine content was below 1 at.-%, no boron was found in the film, and the oxygen residues in the film bulk were less than 1 at.-% indicating good barrier properties against oxygen diffusion. Figure 14 depicts the content of oxygen and fluorine when deposition temperature is varied between 225 °C and 400 °C.

Figure 14. Fluorine and oxygen content in WN<sub>x</sub>C<sub>y</sub> films.

The N:C ratio was possible to adjust slightly with TEB and ammonia pulses, which also changed electrical properties of the  $WN_xC_y$  film. It was noticed that elongation of the TEB pulse decreased resistivity whereas the elongation of ammonia pulse increased resistivity. Using optimal pulsing parameters resistivity was as low as 210

$\mu\Omega$ cm, which offered further proof that carbon was not present as an impurity in the film. When film thickness was reduced to 7 nm, resistivity went up to 600-900  $\mu\Omega$ cm. A similar observation was made with the TiN film when film thickness was below 20 nm [III].

## **5.2. Process Integration**

# 5.2.1. Barrier Compatibility with Copper and $SiO_2$

No compatibility issues were found in the deposition of TiN on the  $SiO_2$  surface. When TiN was deposited on ECD-Cu, extensive pitting was found on the copper surface. The holes on the copper surface had the diameter of ~1  $\mu$ m and their density was quite high (~ 1 hole/17  $\mu$ m<sup>2</sup>). The pitting took place in a wide temperature range, from 250 °C to 400 °C. Regardless of pitting, film growth on copper occurred with normal growth rate. Since the source of pitting was unknown, the copper surface was exposed separately to both precursors (TiCl<sub>4</sub> and NH<sub>3</sub>) to see whether the precursors themselves caused the damage. No pitting was observed and it was speculated that pitting must be caused by the reaction by-products of the TiN growth, namely HCl gas that is known to be highly corrosive.

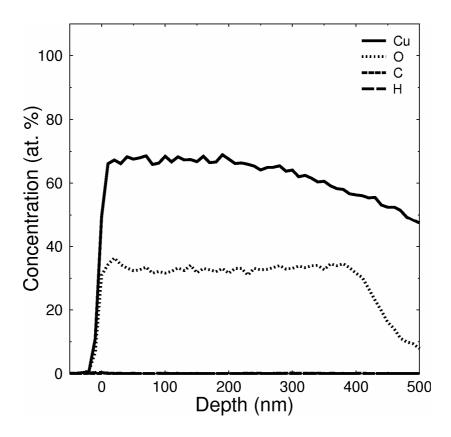

The deposition of  $W_xN$  was found to be problematic on both  $SiO_2$  and the copper surface. In the ALD process, the substrate is exposed to the precursor for a relatively long period of time until the surface is fully covered by deposited film. Consequently, surface materials must be compatible with the precursors. When WF<sub>6</sub> is introduced on a native  $SiO_2$ , it is possible that volatile WOF<sub>4</sub> is formed. As soon as the native oxide layer is consumed, WF<sub>6</sub> reacts with the silicon surface giving rise to volatile  $SiF_4$ , which results in so called "worm holes" on the silicon surface. The copper pitting was also observed in the  $W_xN$  process although it was not as aggressive as in the TiN process. It was observed again that the pitting was not caused directly by the precursors. The HF by-product was suggested to be the source of pitting.