# OPEN

Received: 15 March 2016 Accepted: 07 June 2016 Published: 01 July 2016

# Integration scheme of nanoscale resistive switching memory using bottom-up processes at room temperature for high-density memory applications

Un-Bin Han & Jang-Sik Lee

A facile and versatile scheme is demonstrated to fabricate nanoscale resistive switching memory devices that exhibit reliable bipolar switching behavior. A solution process is used to synthesize the copper oxide layer into 250-nm via-holes that had been patterned in Si wafers. Direct bottom-up filling of copper oxide can facilitate fabrication of nanoscale memory devices without using vacuum deposition and etching processes. In addition, all materials and processes are CMOS compatible, and especially, the devices can be fabricated at room temperature. Nanoscale memory devices synthesized on wafers having 250-nm via-holes showed reproducible resistive switching programmable memory characteristics with reasonable endurance and data retention properties. This integration strategy provides a solution to overcome the scaling limit of current memory device fabrication methods.

Resistive random access memory (ReRAM) has been investigated to be the most important candidate for next-generation memory devices in terms of switching speed, power consumption, and scalability<sup>1–10</sup>. In ReRAM, transition metal oxides are commonly used as resistive switching layers<sup>2,8,11–13</sup>. Synthesis of metal oxide layers is one of the most important factors in development of ReRAM. Transition metal oxide layers have been synthesized by vacuum deposition systems with annealing processes<sup>6,14–16</sup>.

Because metal oxide-based ReRAMs have many potential advantages, including reliable operations, CMOS compatiability, low power consumption, and scalability, efforts have been devoted to improve the properties of ReRAM by using various transition metal oxides such as  $\text{Cu}_2\text{O}^{17,18}$ ,  $\text{NiO}^{19-21}$ ,  $\text{TiO}_2^{22-24}$ , and  $\text{Ta}_2\text{O}_5^{25,26}$ . In particular, various approaches have been investigated to improve their fabrication methods with materials design including electrodes<sup>27-29</sup>, resistive switching layers<sup>12,30-34</sup>, and interfacial layers<sup>35-38</sup>. However, conventional processes mostly use vacuum and annealing processes to deposit transition metal oxides; these methods require long process time and high-temperature annealing.

In addition, fabrication of high-density nanoscale ReRAM has been an important challenge. High-density memory can be achieved by scaling down of memory cell sizes and 3D stacking with cross-point arrays. However, these methods need accurate and expensive fabrication processes, as well as appropriate materials selection for the vertical stacking process. To solve these problems, an alternative approach is to use electrochemical deposition (ECD) to fabricate thin films. ECD has been used to fabricate metal/insulator/metal (MIM) ReRAM structure  $^{39,40}$ . Au/NiO/Au nanowires with nanoscale diameters were synthesized by ECD into nano-templates and thermal oxidation  $^{41}$ . In addition, a Cu<sub>2</sub>O layer was reported to be formed by thermal oxidation of a copper film grown on a Si substrate  $^{17,18}$ . In these methods, the metal oxide film is formed by thermal oxidation of the deposited metal layer by post annealing processes. This fabrication method requires additional process steps including thermal oxidation of electrodeposited metals. Considering the thermal budget device fabrication at low temperature is required.

In this paper, we demonstrate ECD Cu<sub>2</sub>O-based ReRAMs with high reproducibility and reliability. The fabrication cost and process time for ReRAM devices can be effectively reduced since the critical step is a solution process and most device fabrication can be done at room temperature (RT) without any additional oxidation/

Department of Materials Science and Engineering, Pohang University of Science and Technology (POSTECH), Pohang 790-784, Korea. Correspondence and requests for materials should be addressed to J.-S.L. (email: jangsik@postech.ac.kr)

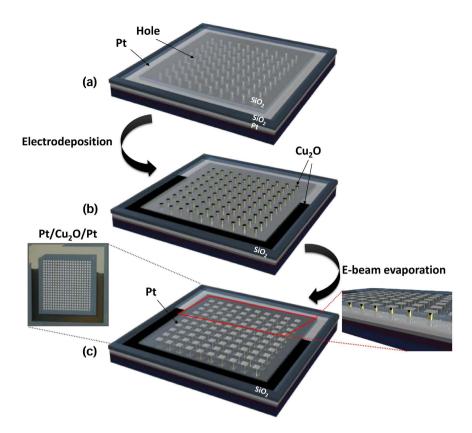

Figure 1. Experimental procedures for fabrication of  $Cu_2O$ -based nanoscale memory devices with 250-nm via-holes patterned on wafer. (a) 250-nm via-hole structures fabricated by lithography and etching processes, (b)  $Cu_2O$  layer formed by ECD, (c) top electrode (Pt) deposition by E-beam evaporation (Left image: optical image of the fabricated sample, Right image: cross-sectional schematic view of the memory device).

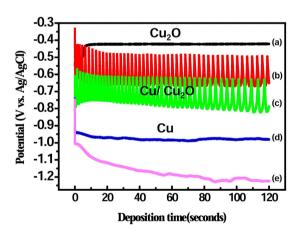

**Figure 2.** Potential profiles during ECD performed at room temperature and pH of 9 at various applied current densities recorded for 120 s: (a) 1 mA/cm<sup>2</sup>, (b) 5 mA/cm<sup>2</sup>, (c) 10 mA/cm<sup>2</sup>, (d) 15 mA/cm<sup>2</sup>, and (e) 20 mA/cm<sup>2</sup>.

annealing processes. ECD enables the fabrication of integrated memory devices with accurate control of materials during the deposition process and various structures/device functions without encountering a scaling limit. This method can form thin oxide films at atmospheric pressure without vacuum conditions. ECD controls the adsorption of atoms by applying bias to the substrate, and can be used to synthesize metal oxides with accurate thickness and stoichiometry at the nanoscale.

# Experimental

**Synthesis of 250-nm via-hole patterns on silicon wafers.** To fabricate nanoscale memory devices, nanoscale via-hole patterns (diameter of 250 nm; thickness of 100 nm) were fabricated on silicon wafers. First plasma-enhanced chemical vapor deposition was used to deposit a 100-nm-thick SiO<sub>2</sub> layer on the Pt bottom

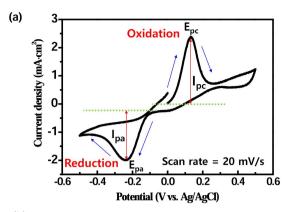

Figure 3. Cyclic voltammogram of  $Cu_2O$  on electrode recorded in 0.6 M  $CuSO_4$  solution at potential sweep rate of 20 mV/s. (a) Reduction peak of  $Cu^{2+}$  to  $Cu_2O$  at -0.23 V vs. Ag/AgCl ( $I_{pa}$ : peak anodic current;  $I_{pc}$ : peak cathodic current;  $E_{pa}$ : oxidation peak;  $E_{pc}$ : reduction peak). (b) Mechanism for reduction of  $Cu^{2+}$  and  $OH^-$  ions in solution.

electrode/Ti/SiO $_2$ /Si substrate. Via-hole patterns (diameter 250 nm) were formed using the optical lithography and etching proesses (KrF lithography and reactive-ion etching) $^{42}$ . The SiO $_2$  layer was used as the sidewall for device isolation; the Cu $_2$ O and top electrode of the memory devices were deposited using ECD and E-beam evaporation.

**Fabrication of 250-nm memory devices.** We fabricated  $Cu_2O$ -based nanoscale memory devices using 250-nm via-hole structures on silicon wafers. The  $Cu_2O$  as the resistive switching layer of nanoscale memory devices was deposited using ECD. The  $Cu_2O$  layer was synthesized using  $0.6 \, \mathrm{M}$   $\mathrm{CuSO_4} \cdot \mathrm{5H_2O}$  aqueous solution amended with 3 M lactic acid (Sigma Aldrich) to stabilize  $\mathrm{Cu}$  (II) ions. The aqueous solution was adjusted to pH of 9 by adding 2 M NaOH (Sigma Aldrich) then stirred overnight using a magnetic stirrer. ECD was performed using a potentiostat/galvanostat (Reference 3000, GAMRY) with a three-electrode system. Ag/AgCl (3 M KCl) was used as the reference electrode and carbon was used as the counter electrode. The  $\mathrm{Cu_2O}$  layer was deposited at  $J = 1 \, \mathrm{mA/cm^2}$  at 25 °C. The deposition thickness of  $\mathrm{Cu_2O}$  was ~70 nm. A Pt layer with 100-nm thickness as the top electrode was deposited using an e-beam evaporator.

**Characterization.** A potentiostat/galvanostat was used for ECD and cyclic voltammetry. ECD of  $Cu_2O$  was conducted using galvanostatic polarization. A cyclic voltammogram was measured using potential scanning from open circuit potential (OCP, vs. Ag/AgCl). The surface morphology and composition of  $Cu_2O$ -based nanoscale memory device were observed using a high-resolution transmission electron microscope (HR-(S)TEM-I; JEM 2100F with a Cs corrector on STEM, JEOL). Before TEM observations, the samples were prepared using a focused ion beam (FIB; Helios, FEI). The crystal structure and phase of the  $Cu_2O$  thin films were investigated using x-ray diffraction (XRD, D/MAX-2500/PC, RIGAKU) using Cu K $\alpha$  radiation ( $\lambda$  = 1.54178 Å). The electrical properties of nanoscale memory devices were measured using a semiconductor parameter analyzer (SPA, 4200-SCS, KEITHLEY). All electrical measurements were performed at RT and atmospheric condition, except data retention property measured at 85 °C.

### **Results and Discussion**

The 250-nm sized  $Cu_2O$ -based ReRAMs with solution processes were fabricated as follows (Fig. 1). A Si wafer having an array of 250-nm via holes was fabricated using lithography (Fig. 1a). A Pt layer was used as the bottom electrode as well as a seed layer for ECD. The  $Cu_2O$  film as the resistive layer was deposited using ECD (Fig. 1b). ECD induces an electric bias in a solution containing the precursor of the material, and this bias causes an oxidation/reduction reaction which precipitates ions to form the thin film (Figure S1). The  $Cu_2O$  layer synthesized with ECD on a Pt via-hole substrate can be used as the resistive switching layer at RT without annealing processes. A  $Cu_2O$  layer was grown in Pt via-hole of 250 nm diameter by applying bias to the Pt bottom electrode. Finally, e-beam evaporation was used to deposit the top Pt electrode ( $\sim$ 100 nm) on the  $Cu_2O$  layer using a shadow mask

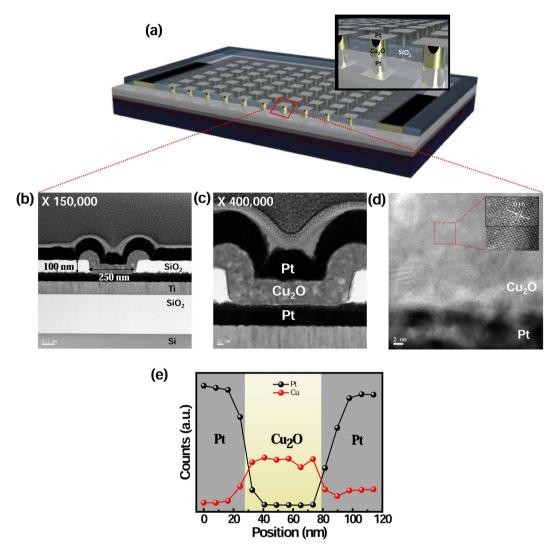

**Figure 4.** (a) Schematic illustration of Pt/Cu<sub>2</sub>O/Pt resistive memory devices. (b-d) Cross-sectional TEM images of Pt/Cu<sub>2</sub>O/Pt device at different magnifications, (e) EDS composition profile of Pt/Cu<sub>2</sub>O/Pt structure.

(Fig. 1c). We chose a symmetric cell with Pt electrodes to avoid unintended factors that might be caused when top and/or bottom electrodes were constructed with reactive metals.

Potential oscillation was observed during ECD (Fig. 2). Potential vs. deposition time was measured at pH 9 and J=1, 5, 10, 15, and 20 A/cm² for 120 s. At J=1 mA/cm² and negative potential  $\leq$  –0.45 V, pure Cu<sub>2</sub>O films were obtained (Fig. 2a). In contrast, at  $J\geq$  15 mA/cm² and negative potential  $\geq$  –0.95 V, pure Cu films were obtained (Fig. 2d,e). At J=5 and 10 mA/cm², Cu-Cu<sub>2</sub>O composite films were obtained, and the range of potential oscillated by about 0.2 V (Fig. 2b,c). Previous research reported a similar trend during ECD<sup>43,44</sup>. The oscillations in potential are induced by the formation and breakdown of a Cu<sub>2</sub>O at the interface between electrode and solution, and by alteration of the surface pH during ECD<sup>43</sup>. During the growth process, the electrode potential of Cu<sub>2</sub>O at equilibrium is higher than that of Cu. Therefore, a Cu<sub>2</sub>O layer can be deposited on the electrode. The pH in the solution decreased locally to deplete OH<sup>-</sup> and Cu²+ in the migration region. OH<sup>-</sup> depletion causes the standard electrode potential (E°) of Cu<sub>2</sub>O to become lower than E° of the reaction. The decrease of the pH results in the formation of metallic Cu. However, when the nucleation and growth of Cu occur, the quantity of Cu²+ ions in the migration region gradually decrease; eventually, the concentration of OH<sup>-</sup> ion increases again, and E° of Cu<sub>2</sub>O exceeds E° of the reaction. Therefore, potential oscillations occur due to formation of Cu-Cu<sub>2</sub>O composite films formed during ECD.

Accordingly, pure  $Cu_2O$  films were obtained at low J. In addition,  $Cu_2O$  films are thermodynamically favored in alkaline solution due to formation of  $Cu_2O$  by combination of  $OH^-$  ions with  $Cu^{2+}$  ions in the solution. Consequently,  $Cu_2O$  for the resistive switching layer of nanoscale memory devices was synthesized at J=1 mA/cm² and pH of 9.

To investigate the electrochemical properties and mechanism for redox reaction of  $Cu_2O$ , the electrical behavior of Cu ions in the  $CuSO_4$  solution was observed using a potentiostat/galvanostat. The cyclic voltammogram of  $Cu_2O$  was obtained during ECD at a scan rate of  $20\,\text{mV/s}$  (Fig. 3). Oxidation and reduction showed peak cathodic

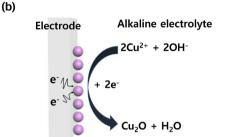

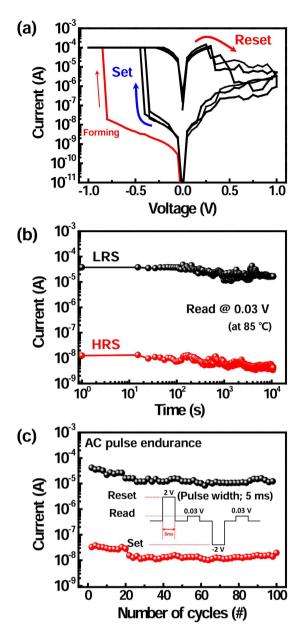

Figure 5. Electrical characteristics of the Pt/Cu<sub>2</sub>O/Pt device with a 250-nm device size. (a) I-V curves of Cu<sub>2</sub>O-based nanoscale ReRAM. (b) Data retention characteristic of the device. (c) AC pulse endurance characteristic of the device (Inset: applied pulse conditions).

$i_{\rm pc}$  and anodic  $i_{\rm pa}$  currents (Fig. 3a). The cathodic and anodic peaks showed a potential range between -0.5 V and 0.5 V. The oxidation  $E_{\rm pa}$  and reduction  $E_{\rm pc}$  peaks were observed at 0.14 V and -0.23 V, respectively. According to the Nernst equation, the electrode potential of Cu and/or Cu<sub>2</sub>O is determined by the Cu<sup>2+</sup> concentration. During reduction, Cu<sub>2</sub>O film is formed on the electrode surface<sup>45</sup>. The electric potential difference between working electrode and counter electrode generates electrons (e<sup>-</sup>), which combine in solution with Cu<sup>2+</sup> ions and OH<sup>-</sup> ions. Then the Cu<sup>2+</sup> ions are precipitated as Cu<sub>2</sub>O (Fig. 3b):

$$2Cu^{2+} + 2OH^{-} + 2e^{-} \Rightarrow Cu_{2}O + H_{2}O$$

A  $Cu_2O$  film is formed on the electrode by nucleation and growth. An optimized  $Cu_2O$  resistive switching layer was obtained by changing J at RT. The oxide layer was formed inside via-holes selectively by using this method.

To confirm crystal structure and composition of thin films using ECD, the XRD analysis of  $Cu_2O$  layer was done (Figure S2). The diffraction peak of the  $Cu_2O$  was obtained using samples deposited at  $J=1\,\text{mA/cm}^2$  and RT; results indicate that  $Cu_2O$  crystalline phase is formed on the Pt electrode. The  $Cu_2O$  film showed mostly (111) orientation, mostly due to the (111) oriented Pt bottom electrodes. Additionally, XRD pattern showed no other structures such as metallic Cu or CuO.

Using the aforementioned ECD process,  $Cu_2O$ -based nanoscale memory devices were fabricated in Pt-via hole (diameter of 250 nm) wafer (Fig. 4a). A high-resolution transmission electron microscopy (HR-TEM) image of the  $Cu_2O$ -based ReRAM confirms the 250-nm diameter of the via-hole with the synthesized ECD-based  $Cu_2O$  layer of 70 nm thickness (Fig. 4b-d). Furthermore, EDS composition analysis confirmed the well synthesis of each layer in ReRAM with the Pt- $Cu_2O$ -Pt structure (Fig. 4e). These results confirm that the bottom-up approach using ECD can successfully be employed to fabricate nanoscale memory devices without vacuum deposition systems and high temperature processes. It is demonstrated that the synthesis of oxide layers with good crystallinity, pure phase, and a smooth interface using ECD.

The electrical properties of the  $Cu_2O$ -based ReRAMs are shown in Fig. 5. The bottom Pt electrode was grounded; the top Pt electrode was biased. To avoid permanent breakdown, compliance current of  $10^{-4}$  A was set. When negative bias is applied to the top electrode, the conductive filament is formed because of the positively charged Cu ions in  $CuO_x$ . The initial resistance state of the device is changed from high resistance state (HRS) to the low resistance state (LRS), which is called forming operation. The forming process can be done at less than -1 V, which can be attributed to easy diffusion of ionized Cu in the  $Cu_2O$  layer<sup>46</sup>. In addition, the migration of  $Cu^+$  ions is controlled by applied voltage and bias polarity. Since the forming process provides strong one-directional electric field for a device, it can induce the asymmetric  $Cu^+$  ion distribution between the bottom and top electrodes, resulting in asymmetric electrical characteristics of the  $Cu_2O$ -based ReRAM. Accordingly, the electrical polarity strongly depends on the initial forming operation<sup>4</sup>. To change the resistance state opposite bias was applied.

After the first forming operation, the conductive filament of the Cu<sub>2</sub>O switching layer is formed by a set process at negative bias. By contrast, when positive bias is applied to the top electrode, the conductive filament is dissolved by a reset process. That is, set voltage of the device is occurred at -0.36 V, whereas reset voltage is occurred at +0.31 V (Fig. 5a). To examine the reliability of the ReRAM, the time-dependent data retention and program/ erase endurance were measured. The retention property was measured at 85 °C. Once the filament was formed in the Cu2O layer, continuous read voltage of 0.03 V was applied to confirm LRS. In addition, HRS retention was measured by applying continuous read voltage of 0.03 V after reset. The on/off ratio was >10<sup>3</sup>, and did not degrade noticeably more than  $\sim 10^4$  s (Fig. 5b). Program/erase endurance of the device was evaluated as a function of the number of AC set/reset pulses (Fig. 5c). The inset of Fig. 5c describes set and reset pulse conditions for endurance assessment. After applying set and reset bias pulses, read voltage was followed to read memory states of the ReRAM. We could not observe any noticeable degradation for more than 100 cycles. In addition, cell-to-cell characteristics were measured to confirm the uniformity of memory devices (10 devices, Figure S3). The cumulative probability of HRS and LRS currents are shown in Figure S4. In this paper, we have mainly focused on evaluation of the feasibility of using ECD to fabricate high-density memory devices. Cu<sub>2</sub>O-based ReRAM exhibited reasonable data retention and endurance with uniform electrical properties, which are suitable for non-volatile memory applications.

It is very important to investigate the switching mechanism in RRAM devices. Both cations and anions can participate in switching behaviors. It is also reported that different conditions could result in different predominant defects<sup>47</sup>. Recent studies showed that both cations and anions could be mobile in transition metal oxides<sup>48</sup>. Further work will be carried out to investigate the exact switching mechanism in our memory devices based on defect chemistry.

### Conclusions

In conclusion, we demonstrated ECD to fabricate  $\mathrm{Cu_2O}$ -based nanoscale ReRAMs at RT without annealing process. The  $\mathrm{Cu_2O}$  layer used as the resistive switching layer in ReRAM was successfully synthesized using bottom-up growth into 250-nm diameter via-holes patterned in Si wafer. The ReRAM exhibited high on/off ratio and reasonable data retention/endurance reliability; all of these traits make it applicable for non-volatile memory applications. This study suggests that ECD may be a simple and cost-effective approach to fabricate next-generation high density memory devices beyond the current scaling limit.

### References

- 1. Pan, F., Gao, S., Chen, C., Song, C. & Zeng, F. Recent progress in resistive random access memories: Materials, switching mechanisms, and performance. *Mater. Sci. Eng. R. Rep.* **83**, 1–59 (2014).

- 2. Yang, Y. & Lu, W. Nanoscale resistive switching devices: mechanisms and modeling. Nanoscale. 5, 10076–10092 (2013).

- 3. Yang, J. J., Strukov, D. B. & Stewart, D. R. Memristive devices for computing. *Nat. Nanotechnol.* 8, 13–24 (2013).

- 4. Yanagida, T. et al. Scaling effect on unipolar and bipolar resistive switching of metal oxides. Sci. Rep. 3, 1657 (2013).

- Park, S. et al. Nanoscale RRAM-based synaptic electronics: toward a neuromorphic computing device. Nanotechnology. 24, 384009 (2013).

- Jang, J., Pan, F., Braam, K. & Subramanian, V. Resistance switching characteristics of solid electrolyte chalcogenide Ag<sub>2</sub>Se nanoparticles for flexible nonvolatile memory applications. Adv. Mater. 24, 3573–3576 (2012).

- Cheng, C. H., Yeh, F. S. & Chin, A. Low-power high-performance non-volatile memory on a flexible substrate with excellent endurance. Adv. Mater. 23, 902–905 (2011).

- 8. Waser, R., Dittmann, R., Staikov, G. & Szot, K. Redox-Based Resistive Switching Memories Nanoionic Mechanisms, Prospects, and Challenges. *Adv. Mater.* **21**, 2632–2663 (2009).

- 9. Waser, R. & Aono, M. Nanoionics-based resistive switching memories. Nat. Mater. 6, 833-840 (2007).

- Lee, J. S. Progress in non-volatile memory devices based on nanostructured materials and nanofabrication. J. Mater. Chem. 21, 14097–14112 (2011).

- 11. Gao, S. et al. Tuning the switching behavior of binary oxide-based resistive memory devices by inserting an ultra-thin chemically active metal nanolayer: a case study on the Ta<sub>2</sub>O<sub>5</sub>-Ta system. *Phys. Chem. Chem. Phys.* 17, 12849–12856 (2015).

- 12. Yang, Y. C., Choi, S. & Lu, W. Oxide Heterostructure Resistive Memory. Nano Lett. 13, 2908-2915 (2013).

- 13. Kim, Y. M. & Lee, J. S. Reproducible resistance switching characteristics of hafnium oxide-based nonvolatile memory devices. *J. Appl. Phys.* **104**, 114115 (2008).

- 14. Singh, B., Mehta, B. R., Varandani, D., Savu, A. V. & Brugger, J. CAFM investigations of filamentary conduction in Cu<sub>2</sub>O ReRAM devices fabricated using stencil lithography technique. *Nanotechnology.* 23, 495707 (2012).

- Wang, S.-Y., Huang, C.-W., Lee, D.-Y., Tseng, T.-Y. & Chang, T.-C. Multilevel resistive switching in Ti/Cu<sub>x</sub>O/Pt memory devices. J. Appl. Phys. 108, 114110 (2010).

- Yasuhara, R. et al. Inhomogeneous chemical states in resistance-switching devices with a planar-type Pt/CuO/Pt structure. Appl. Phys. Lett. 95, 012110 (2009).

- Liang, K. D. et al. Single CuO<sub>x</sub> nanowire memristor: forming-free resistive switching behavior. ACS Appl. Mater. Interfaces. 6, 16537–16544 (2014).

- 18. Chen, A. et al. Switching characteristics of Cu<sub>2</sub>O metal-insulator-metal resistive memory. Appl. Phys. Lett. 91, 123517 (2007).

- 19. Choi, D. & Soo Kim, C. Coexistence of unipolar and bipolar resistive switching in Pt/NiO/Pt. Appl. Phys. Lett. 104, 193507 (2014).

- Lee, M. J. et al. A Simple Device Unit Consisting of All NiO Storage and Switch Elements for Multilevel Terabit Nonvolatile Random Access Memory. ACS Appl. Mater. Interfaces. 3, 4475–4479 (2011).

- Son, J. Y., Shin, Y. H., Kim, H. & Jang, H. M. NiO Resistive Random Access Memory Nanocapacitor Array on Graphene. ACS Nano. 4, 2655–2658 (2010).

- 22. Li, Q. J. et al. Memory Impedance in TiO<sub>2</sub> based Metal-Insulator-Metal Devices. Sci. Rep. 4, 4522 (2014).

- 23. Tang, G. et al. Programmable complementary resistive switching behaviours of a plasma-oxidised titanium oxide nanolayer. Nanoscale. 5, 422–428 (2013).

- 24. Bae, Y. C. et al. Oxygen Ion Drift-Induced Complementary Resistive Switching in Homo TiOx/TiOy/TiOx and Hetero TiOx/TiON/TiOx Triple Multilayer Frameworks. Adv. Funct. Mater. 22, 709–716 (2012).

- 25. Lee, M. J. et al. A fast, high-endurance and scalable non-volatile memory device made from asymmetric Ta<sub>2</sub>O<sub>5-x</sub>/TaO<sub>2-x</sub> bilayer structures. *Nat. Mater.* 10, 625–630 (2011).

- 26. Tsuruoka, T. et al. Effects of Moisture on the Switching Characteristics of Oxide-Based, Gapless-Type Atomic Switches. Adv. Funct. Mater. 22, 70–77 (2012).

- 27. Tappertzhofen, S., Waser, R. & Valov, I. Impact of the Counter-Electrode Material on Redox Processes in Resistive Switching Memories. ChemElectroChem. 1, 1287–1292 (2014).

- 28. Ge, N. et al. Electrode-material dependent switching in TaOx memristors. Semicond. Sci. Technol. 29, 104003 (2014).

- 29. Chen, C. et al. Effect of electrode materials on AlN-based bipolar and complementary resistive switching. ACS Appl. Mater. Interfaces 5, 1793–1799 (2013).

- Tian, X. Z. et al. Bipolar Electrochemical Mechanism for Mass Transfer in Nanoionic Resistive Memories. Adv. Mater. 26, 3649–3654 (2014).

- 31. Shang, J. et al. Thermally Stable Transparent Resistive Random Access Memory based on All-Oxide Heterostructures. Adv. Funct. Mater. 24, 2171–2179 (2014).

- 32. Wong, H. S. P. et al. Metal-Oxide RRAM. Proc. IEEE. 100, 1951-1970 (2012).

- 33. Yao, J., Sun, Z. Z., Zhong, L., Natelson, D. & Tour, J. M. Resistive Switches and Memories from Silicon Oxide. *Nano Lett.* 10, 4105–4110 (2010).

- 34. Akinaga, H. & Shima, H. Resistive Random Access Memory (ReRAM) Based on Metal Oxides. Proc. IEEE. 98, 2237-2251 (2010).

- 35. Tsuruoka, T. et al. Redox Reactions at Cu,Ag/Ta<sub>2</sub>O<sub>5</sub> Interfaces and the Effects of Ta<sub>2</sub>O<sub>5</sub> Film Density on the Forming Process in Atomic Switch Structures. Adv. Funct. Mater. 25, 6374–6381 (2015).

- 36. Lubben, M. et al. Graphene-Modified Interface Controls Transition from VCM to ECM Switching Modes in Ta/TaOx Based Memristive Devices. Adv. Mater. 27, 6202–6207 (2015).

- 37. Valov, I. Redox-Based Resistive Switching Memories (ReRAMs): Electrochemical Systems at the Atomic Scale. *ChemElectroChem.* 1, 26–36 (2014).

- 38. Kever, T., Böttger, U., Schindler, C. & Waser, R. On the origin of bistable resistive switching in metal organic charge transfer complex memory cells. *Appl. Phys. Lett.* **91**, 083506 (2007).

- Song, J.-M. & Lee, J.-S. Self-assembled nanostructured resistive switching memory devices fabricated by templated bottom-up growth. Sci. Rep. 6, 18967 (2016).

- Han, U.-B. & Lee, J.-S. Bottom-up synthesis of ordered metal/oxide/metal nanodots on substrates for nanoscale resistive switching memory. Sci. Rep. 6, 25537 (2016).

- 41. Perego, D. et al. Engineered fabrication of ordered arrays of Au-NiO-Au nanowires. Nanotechnology. 24, 045302 (2013).

- 42. Lee, S., Woo, J., Lee, D., Cha, E. & Hwang, H. Internal resistor of multi-functional tunnel barrier for selectivity and switching uniformity in resistive random access memory. *Nanoscale Res. Lett.* 9, 7 (2014).

- 43. Switzer, J. A. et al. Potential oscillations during the electrochemical self-assembly of copper cuprous oxide layered nanostructures. *J. Mater. Res.* 13, 909–916 (1998).

- 44. Tang, J. & Azumi, K. Optimization of pulsed electrodeposition of aluminum from AlCl<sub>3</sub>-1-ethyl-3-methylimidazolium chloride ionic liquid. *Electrochim. Acta.* **56**, 1130–1137 (2011).

- 45. Filipic, G. & Cvelbar, U. Copper oxide nanowires: a review of growth. Nanotechnology. 23, 194001 (2012).

- Tappertzhofen, S. et al. Generic Relevance of Counter Charges for Cation-Based Nanoscale Resistive Switching Memories. ACS Nano. 7, 6396–6402 (2013).

- Dieckmann, R. Point defects and transport in non-stoichiometric oxides: Solved and unsolved problems. J. Phys. Chem. Solids. 59, 507–525 (1998).

- 48. Wedig, A. et al. Nanoscale cation motion in TaOx, HfOx and TiOx memristive systems. Nat. Nanotechnol. 11, 67-74 (2016).

## **Acknowledgements**

This work was supported by National Research Foundation of Korea (NRF-2015R1A2A1A15055918). This work was also supported by Future Semiconductor Device Technology Development Program (10045226) funded by the Ministry of Trade, Industry & Energy (MOTIE)/Korea Semiconductor Research Consortium (KSRC). In addition, this work was partially supported by Brain Korea 21 PLUS project (Center for Creative Industrial Materials).

### **Author Contributions**

J.-S.L. conceived and designed the experiments. U.-B.H. performed experiments under the supervision of J.-S.L. J.-S.L. and U.-B.H. wrote the paper.

### Additional Information

Supplementary information accompanies this paper at http://www.nature.com/srep

Competing financial interests: The authors declare no competing financial interests.

**How to cite this article**: Han, U.-B. and Lee, J.-S. Integration scheme of nanoscale resistive switching memory using bottom-up processes at room temperature for high-density memory applications. *Sci. Rep.* **6**, 28966; doi: 10.1038/srep28966 (2016).

This work is licensed under a Creative Commons Attribution 4.0 International License. The images or other third party material in this article are included in the article's Creative Commons license, unless indicated otherwise in the credit line; if the material is not included under the Creative Commons license, users will need to obtain permission from the license holder to reproduce the material. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/